Rectangular steiner tree method of super large size integrated circuit avoiding barrier

A large-scale integrated circuit, barrier technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problem of not being applicable to large-scale wire networks, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0128] Firstly, the core idea of the "right-angle Steiner tree method considering obstacles" involved in this patent application is specifically analyzed.

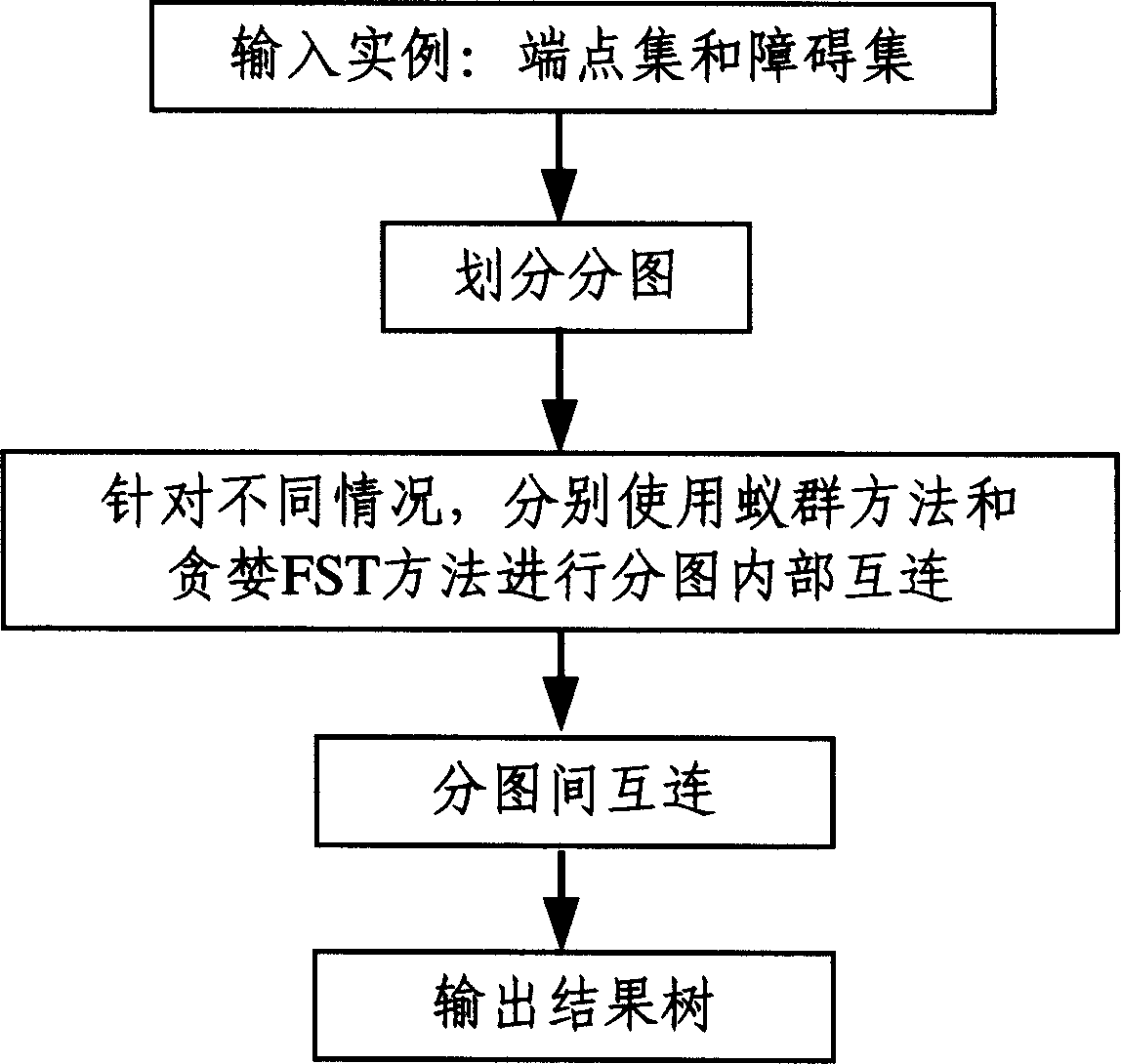

[0129] After reading and processing the information of circuit obstacles and wire nets, the core part of this method is the process of constructing the Steiner tree. The overall flow chart is as follows figure 1 shown. The idea of this method is different from the previous methods. The method is divided into three steps to construct the final result tree: the first step is to find the FST (fulsome Steiner tree) of all endpoints, and delete the FST that intersects with obstacles; Construct the sub-Steiner tree in the subgraph composed of the FST below; the third step uses the detour method to connect all the sub-Steiner trees into a complete Steiner tree. The three steps of the method are described below.

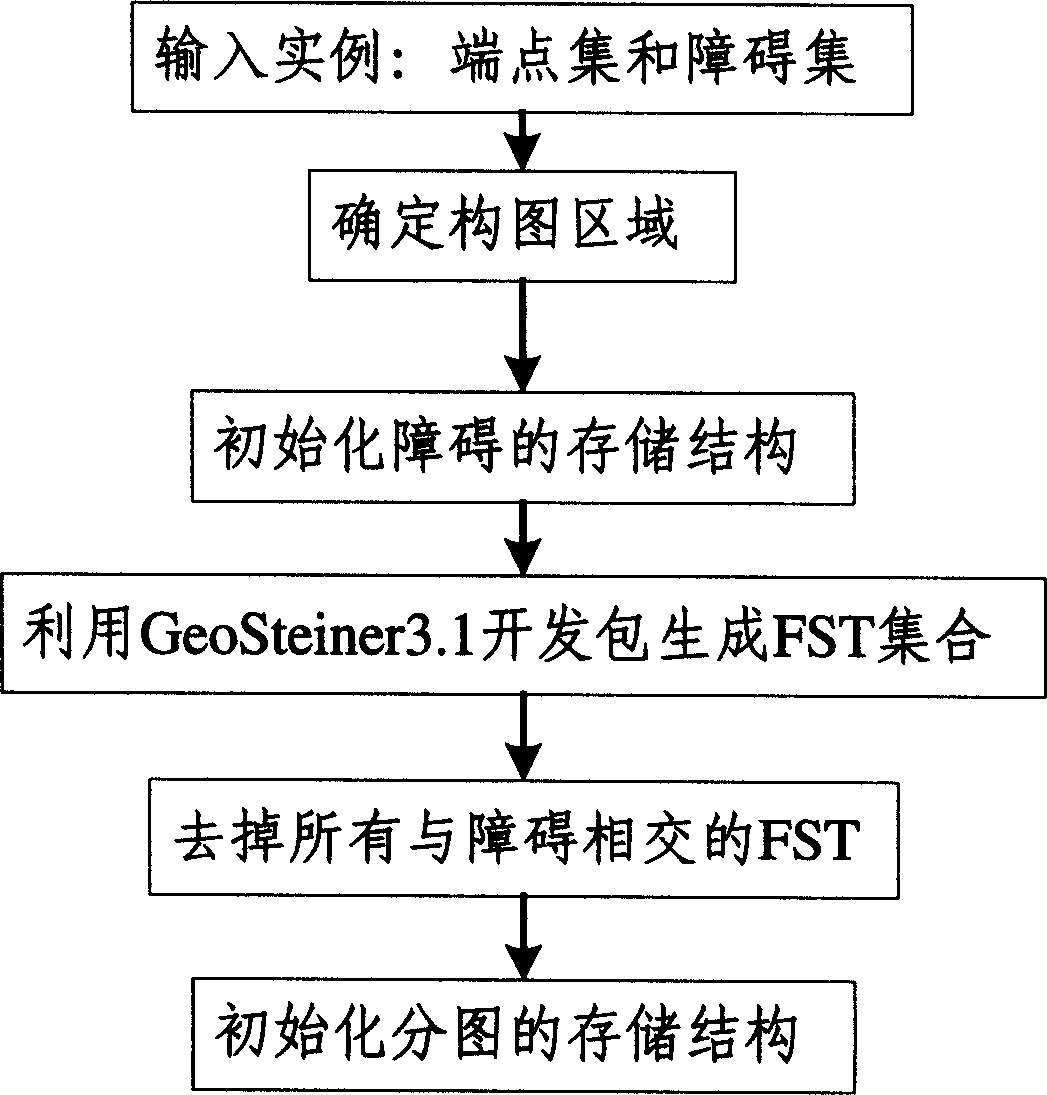

[0130] Step 1: Find the FST (fulsome Steiner tree) of all endpoints, and delete the FST that intersects with obs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More