Multilayer obstacle-avoiding Steiner minimal tree construction method for very large scale integration

A technology of large-scale integrated circuits and construction methods, which can be applied in gene models, electrical digital data processing, special data processing applications, etc., and can solve problems affecting the quality of wiring solutions, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

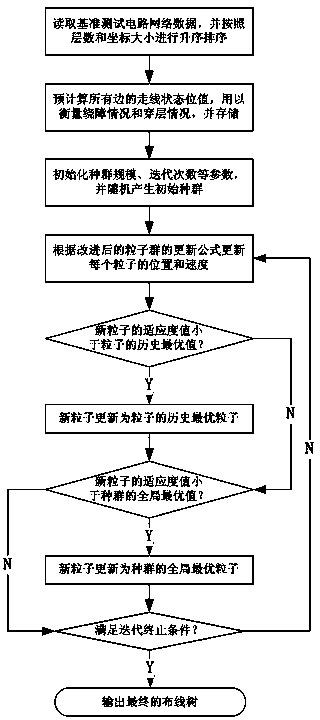

[0047] VLSI multi-layer detour Steiner minimum tree construction method of the present invention, such as figure 1 shown, including the following steps:

[0048] Step 1: Read the benchmark test circuit network data and sort them in ascending order according to the number of layers and coordinate size. Before entering the iterative process, the method pre-calculates and stores the routing status bits of all possible routing edges, and directly queries the required routing status bit values during iteration, so as to reduce the calculation times of the routing status bits.

[0049] Step 2: Initialize the parameters such as population size and number of iterations, encode the optimization parameters and randomly generate the initial population.

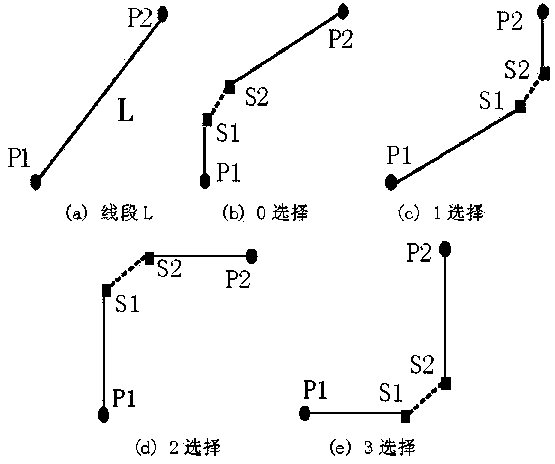

[0050] This method adopts the edge point pair encoding method suitable for X structure and multilayer wiring to encode the X structure multilayer Steiner tree: use the edge set of the wiring tree to encode the corresponding Steiner t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More