Method for making MOS transistor with source-drain on insulating layer

A technology of MOS transistors and manufacturing methods, applied in the field of manufacturing MOSFET transistors, to achieve the effects of easy control, good short channel characteristics, and high practical value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

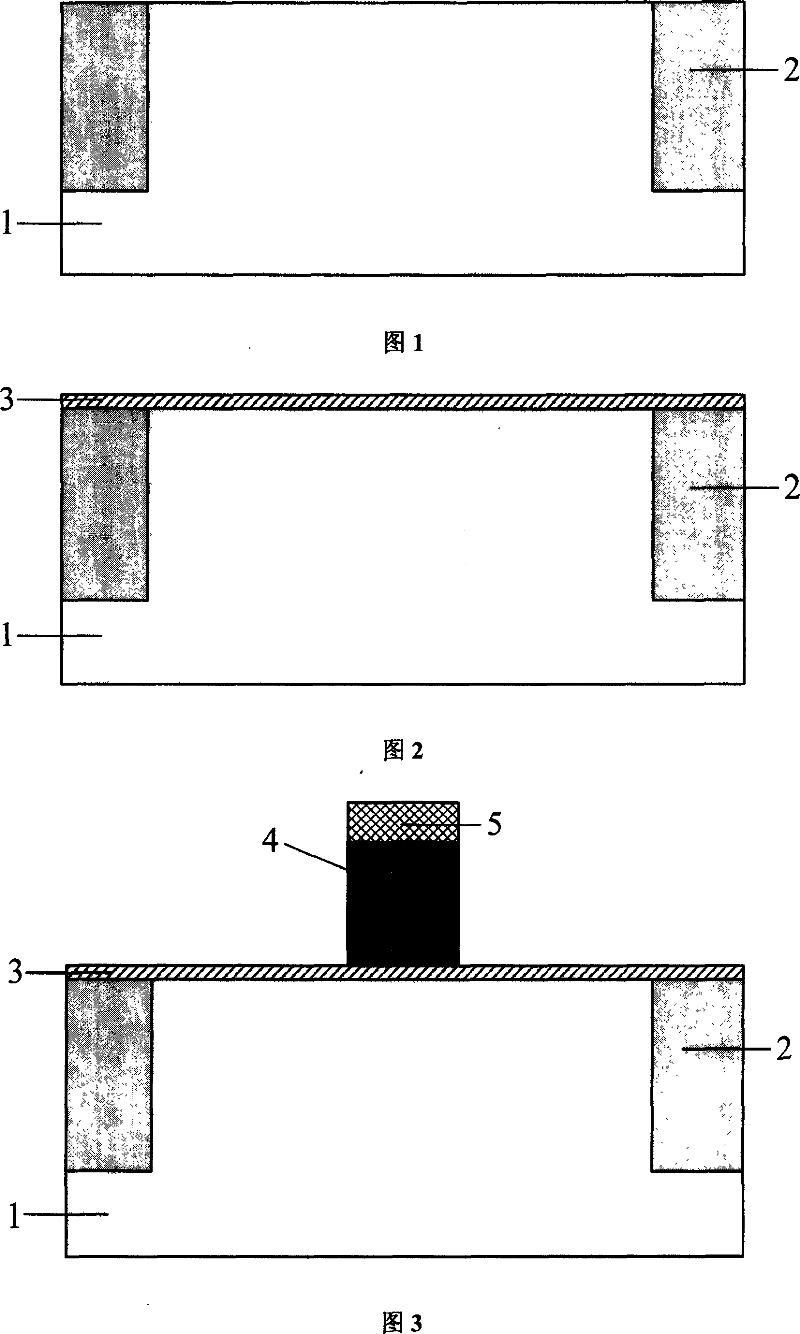

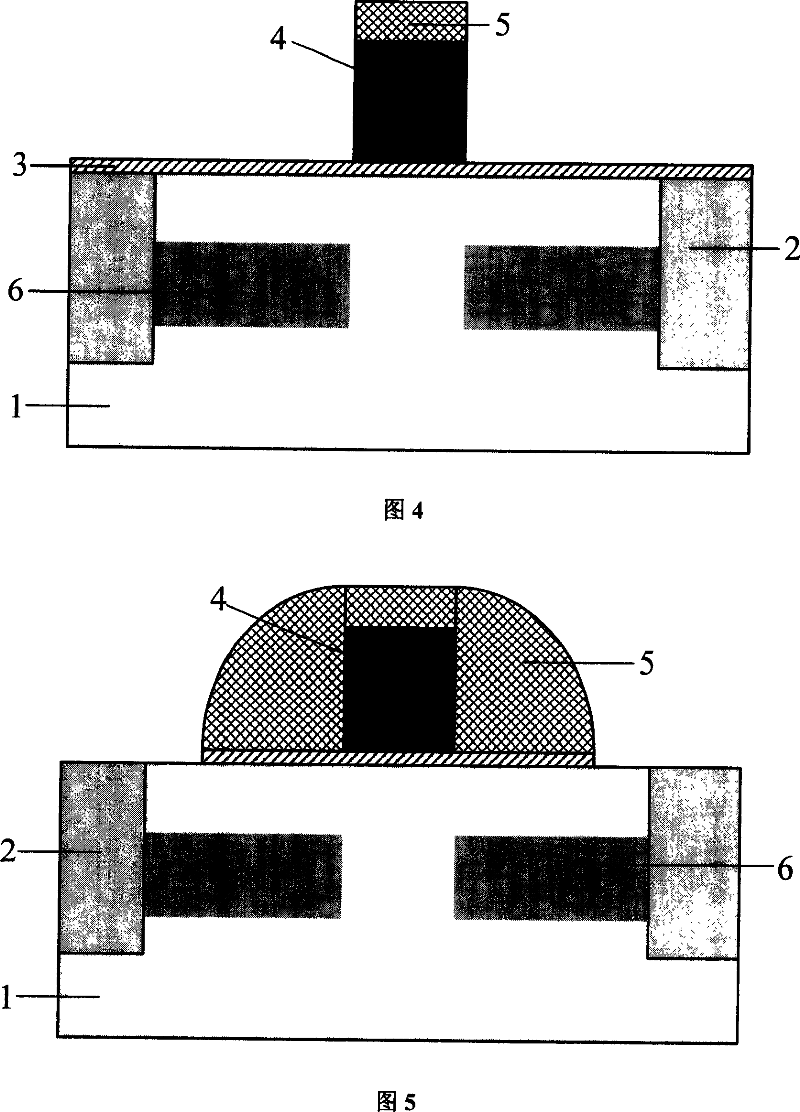

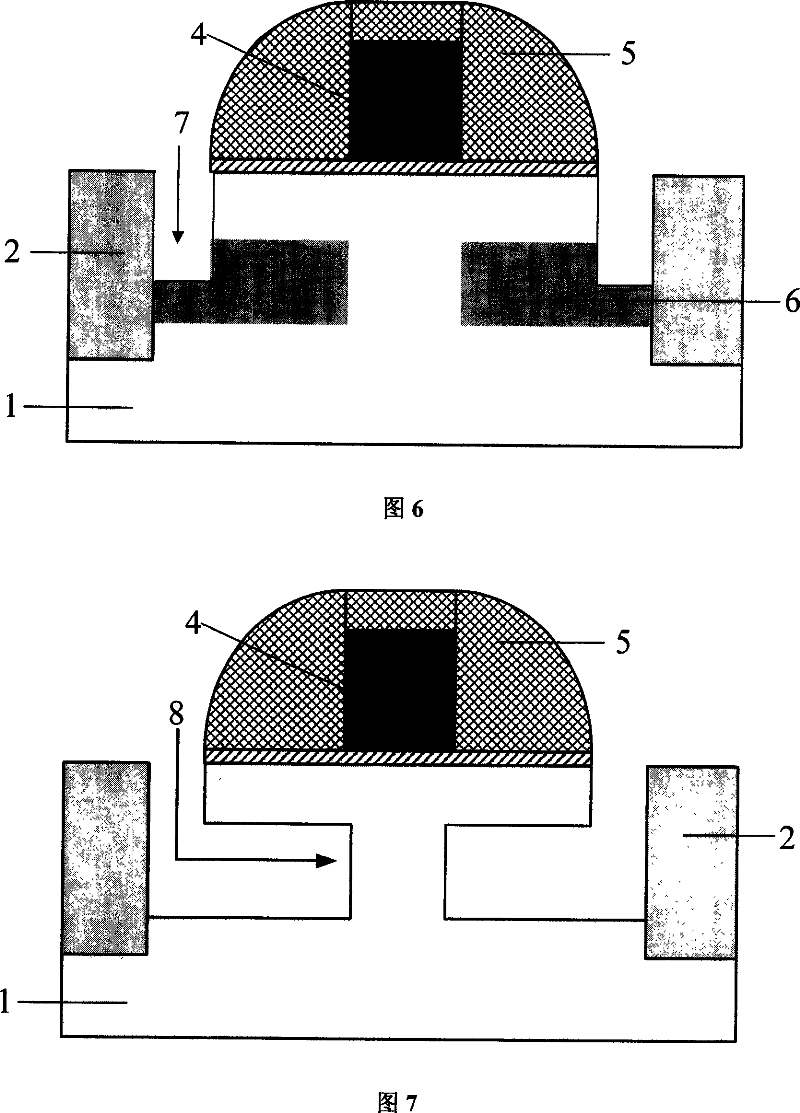

[0044] A specific embodiment of the manufacturing method of the present invention comprises the process steps shown in Fig. 1 to Fig. 9:

[0045] The crystal orientation of the single crystal silicon substrate used is (100), the body region is initially lightly doped, and the active region isolation layer is fabricated on the silicon substrate using conventional CMOS shallow trench isolation technology, as shown in Figure 1.

[0046] Then a gate dielectric layer is grown, the gate dielectric layer is silicon dioxide, and its thickness is 1-1.5nm. The gate dielectric can also be formed by one of the following methods: conventional thermal oxidation, nitrogen-doped thermal oxidation, chemical vapor deposition (CVD), and physical vapor deposition (PVD), as shown in FIG. 2 .

[0047] A gate electrode layer polysilicon layer and a sacrificial dielectric layer silicon nitride are deposited, the thickness of the polysilicon layer is 80-150nm, and the thickness of the silicon nitride ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More