InGaAs MOSFET device structure

A device structure and channel technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., to achieve the effects of reducing device parasitic resistance, reducing lithography difficulty, and reducing source-drain parasitic resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

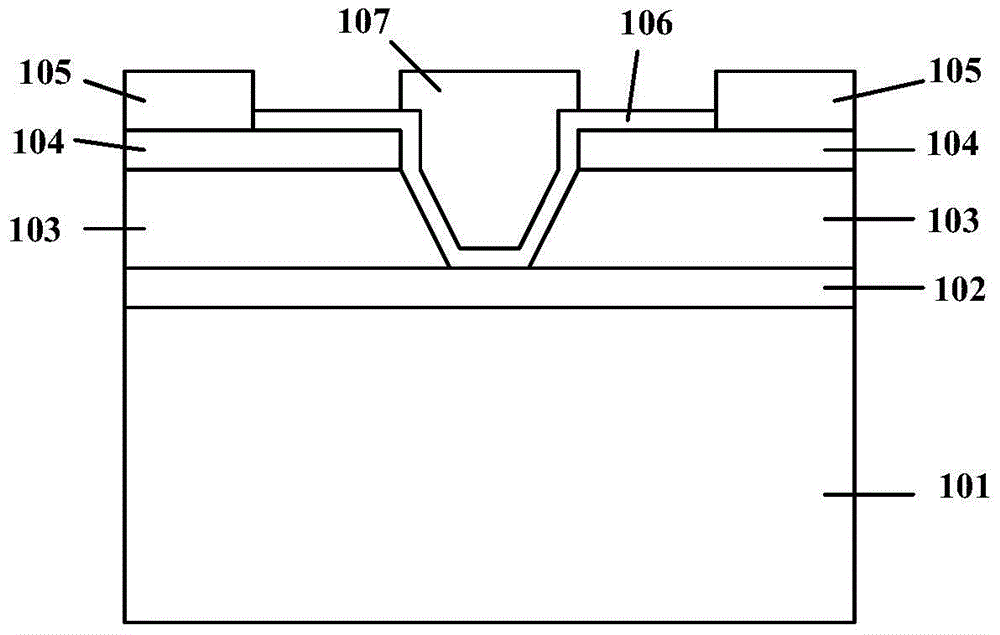

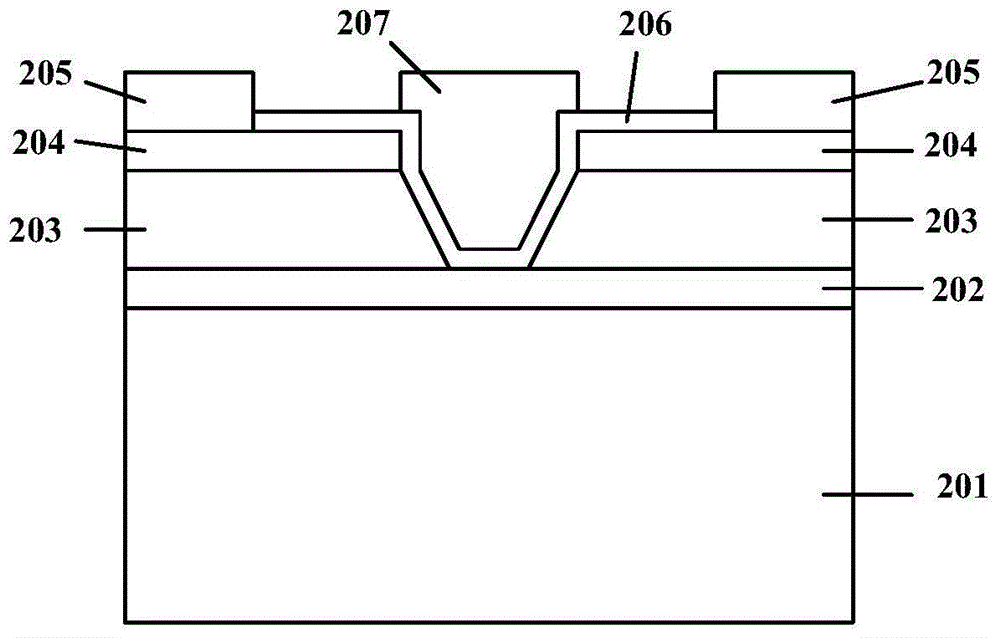

[0025] The source-drain self-aligned MOS device structure provided by the present invention specifically includes the following:

[0026] (1) a P-type InGaAs semiconductor layer (202) of 10 nanometers on a semi-insulating indium phosphide substrate (201) with a crystal orientation of (100);

[0027] (2) N-type heavily doped InP layer (203) 100 nanometers formed on the p-type InGaAs semiconductor layer;

[0028] (3) The N-type heavily doped InGaAs cap layer (204) formed on the N-type heavily doped InP layer is 20 nanometers;

[0029] (4) forming Ti / Pt / Au source and drain metal (205) on the N-type heavily doped InGaAs cap layer;

[0030] (5) A trapezoidal gate groove structure is formed in the N-type heavily doped InP lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More