Method for making MOS transistor with source-drain on insulating layer

A technology of a MOS transistor and a manufacturing method, which is applied to the manufacturing field of MOSFET transistors, can solve the problems of large source-drain parasitic capacitance and leakage, and the threshold voltage swing is difficult to eliminate, and achieves small source-drain parasitic resistance, high practical value, and improved performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

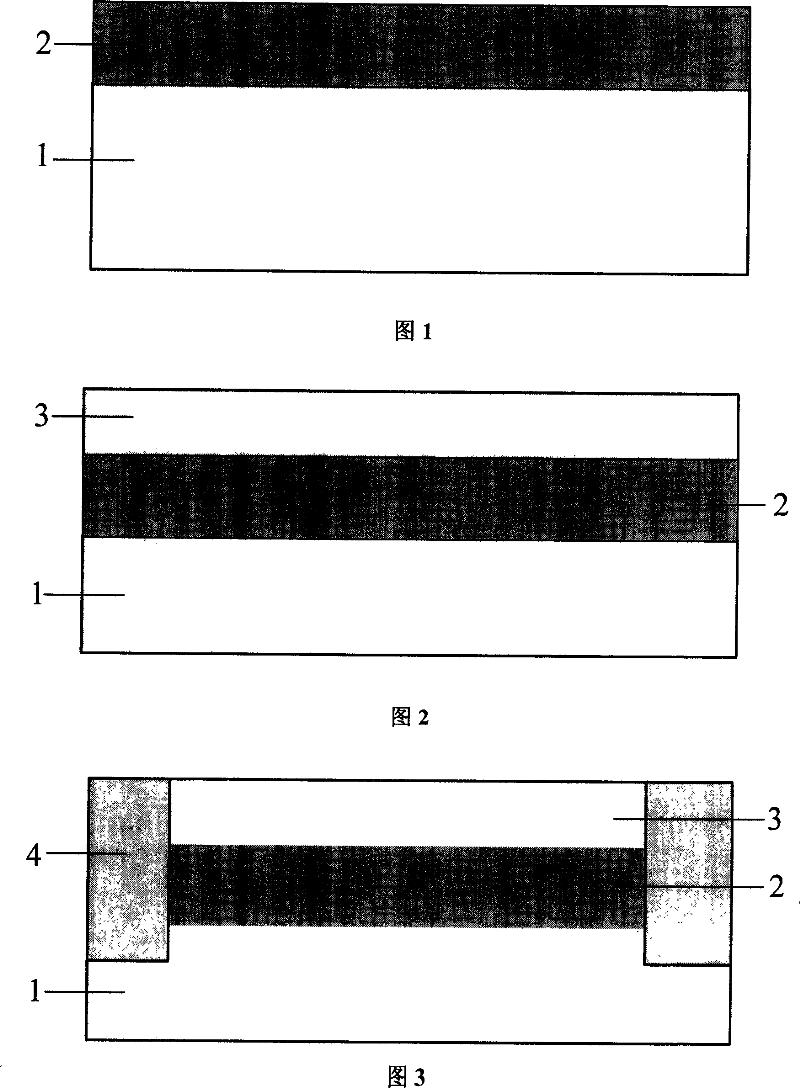

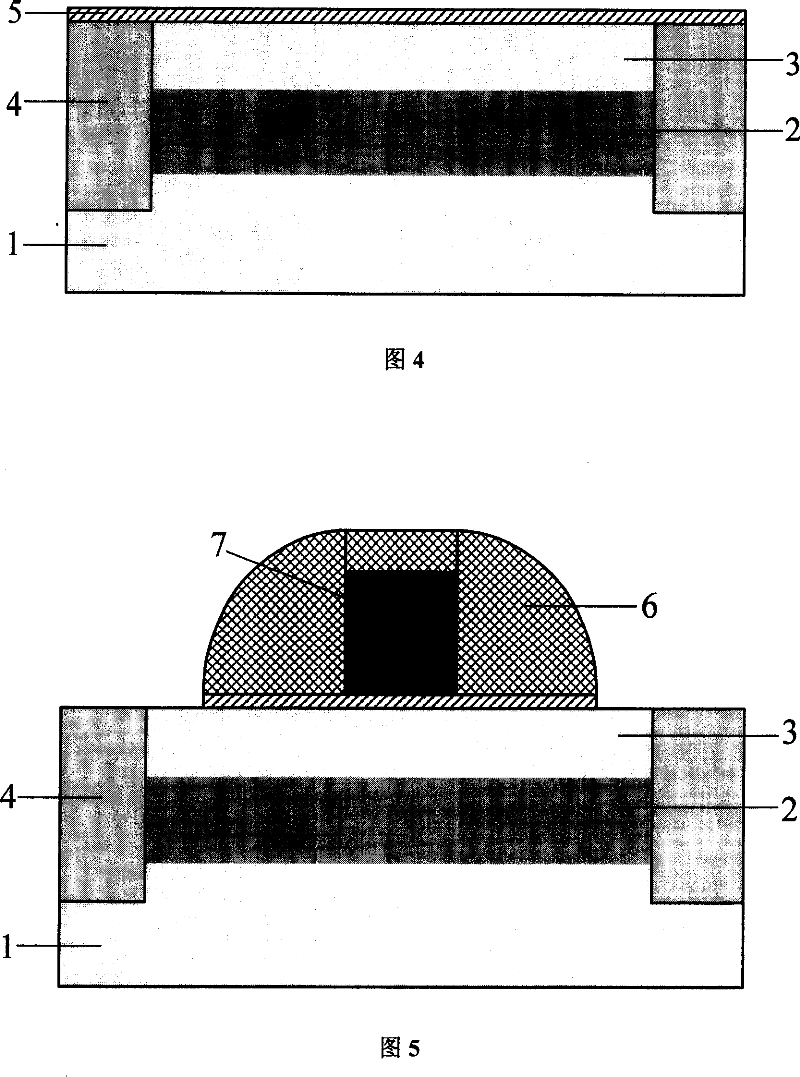

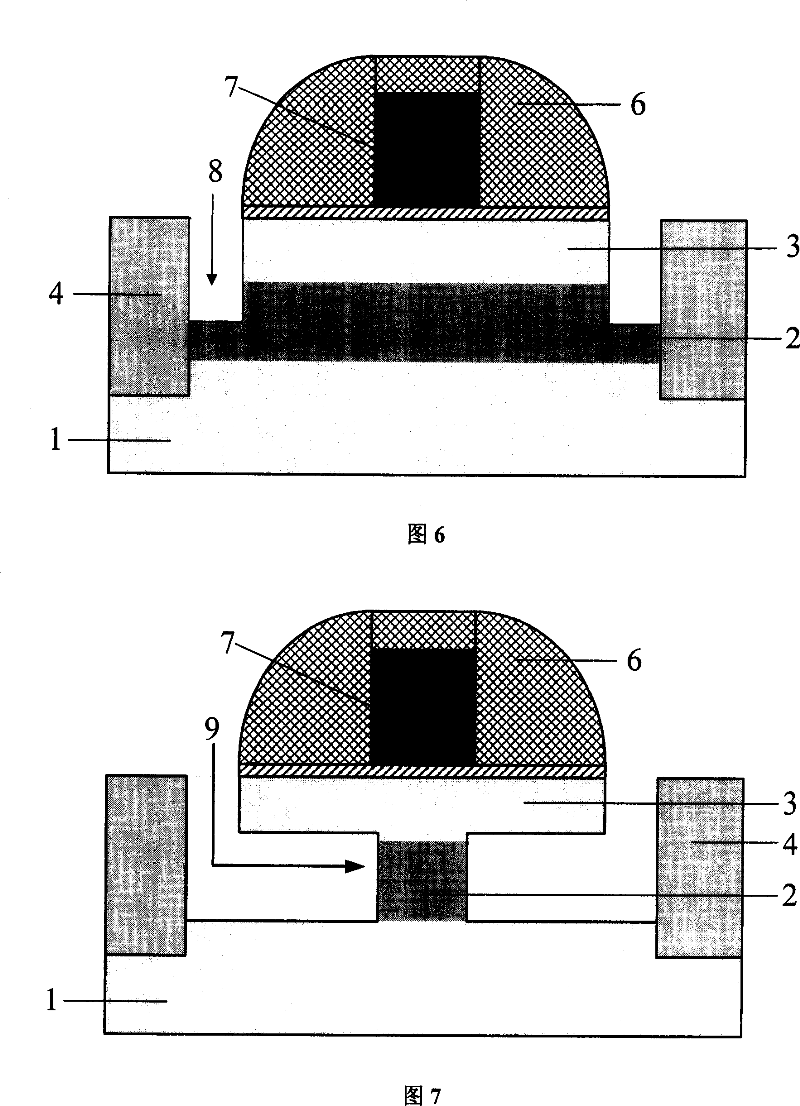

[0052] A specific embodiment of the manufacturing method of the present invention comprises the process steps shown in Fig. 1 to Fig. 9:

[0053] The crystal orientation of the single crystal silicon substrate used is (100), the body region is initially lightly doped, B + Ion implantation, the implantation dose is 1e+16 / cm -2 , the implantation energy is 20KeV, and a highly doped silicon region is obtained on the surface, as shown in FIG. 1 .

[0054]An undoped silicon film is epitaxially grown on highly doped silicon with a thickness of 5-30 nm, as shown in FIG. 2 .

[0055] The active region isolation layer is fabricated by conventional CMOS shallow trench isolation technology, as shown in FIG. 3 .

[0056] Then a gate dielectric layer is grown, the gate dielectric layer is silicon dioxide, and its thickness is 1-1.5nm. The gate dielectric can also be formed by one of the following methods: conventional thermal oxidation, nitrogen-doped thermal oxidation, chemical vapor d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More