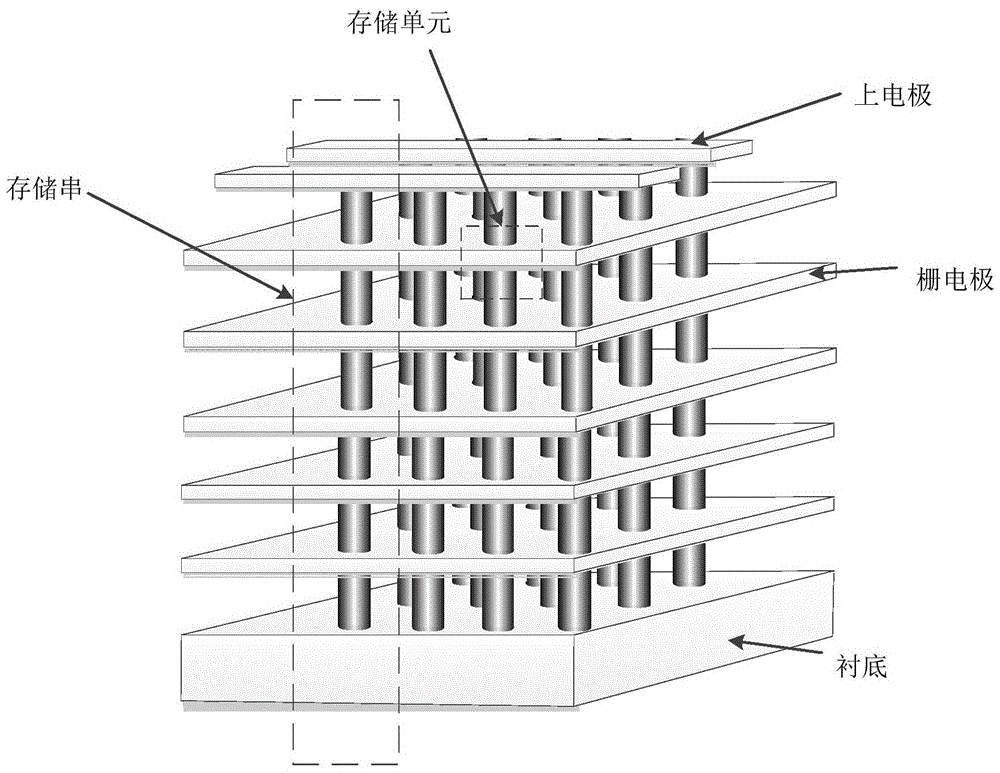

A kind of non-volatile three-dimensional semiconductor memory and its preparation method

A non-volatile, semi-conductive technology, applied in the direction of semiconductor devices, electrical solid-state devices, electrical components, etc., can solve the problems of short-channel effect, different doping concentration, etc., achieve enhanced control ability, good thermal stability, and avoid short-circuit ditch effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

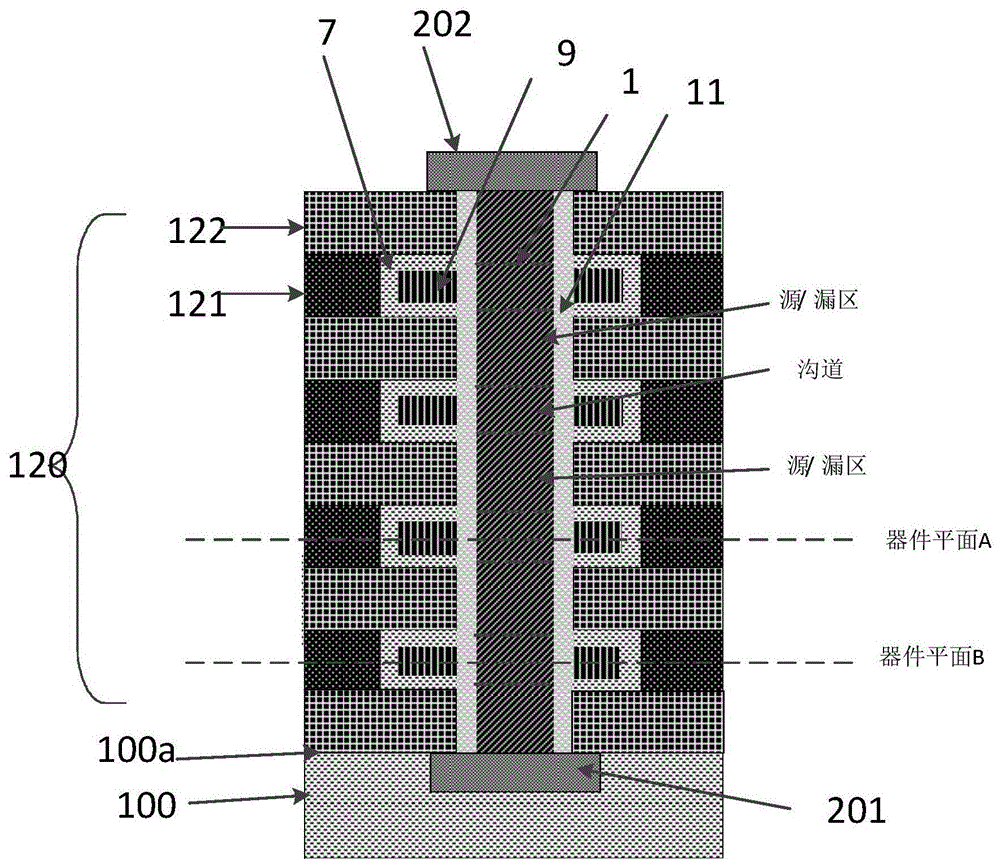

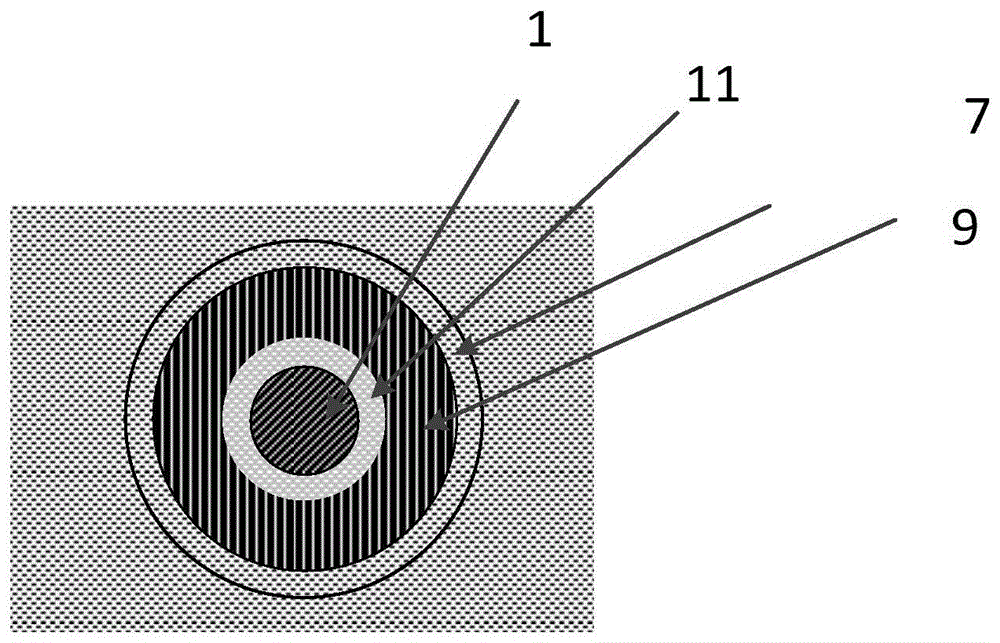

[0064] The invention also provides a method for preparing a nonvolatile three-dimensional semiconductor memory, such as Figure 3-Figure 12 As shown, the preparation process of the NAND storage string specifically includes the following steps:

[0065] Step 1: as reference image 3 As shown, a multi-layer film stack structure 120 is deposited on the substrate 100 on which the lower electrodes 201 have been distributed. Then perform deep hole etching in the formed stacked structure to form via holes 80, such as Figure 4 shown.

[0066] Wherein, the control gate electrode 121 and the insulating medium 122 can be deposited on the substrate by any suitable deposition method, such as sputtering, CVD, molecular beam epitaxy (MBE, MOLECULAR BEAM EPITAXY) and the like. The control gate electrode 121, insulating medium 122 may be 6 to 100 nanometers thick. In this embodiment, the control gate electrode 121 can be a conductor (such as metal or metal alloy) or a semiconductor (such ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More