Non-junction field-effect transistor

A field effect transistor, junctionless technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as poor stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

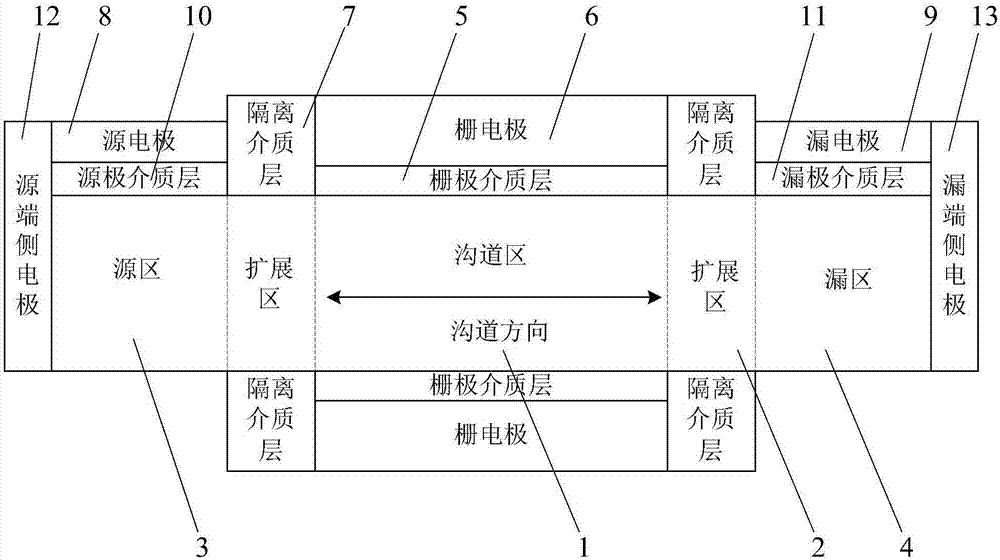

[0041] Please refer to figure 1 , which is a schematic structural diagram of a junctionless field effect transistor provided by an embodiment of the present invention, as shown in figure 1 As shown, the junctionless field effect transistor includes a channel region 1 , a source region 3 , a drain region 4 , a gate electrode 6 , a source electrode 8 and a drain electrode 9 .

[0042] Wherein, the source region 3 and the drain region 4 are symmetrically arranged on both sides of the channel region 1, so that the carriers in the channel region 1 can flow from the source region 3 to the drain region 4 or from the drain region 4 to the source region 3. transport, and the arrangement direction of the source region 3 and the drain region 4 can be understood as the channel direction to indicate the transport direction of carriers; in an exemplary embodiment, the source region 3 and the channel region 1 can also be An extension region 2 is provided, and an extension region 2 may also ...

Embodiment 2

[0066] Please refer to Figure 5 , is a schematic structural diagram of a tri-gate junctionless field effect transistor provided by an embodiment of the present invention. Such as Figure 5 As shown, the junctionless field effect transistor includes a channel region 1, an extension region 2, a source region 3 and a drain region 4; wherein, the channel region 1, the extension region 2, the source region 3 and the drain region 4 each include a top surface and two side surfaces, and the channel region 1, the extension region 2, the source region 3 and the drain region 4 are all set on the substrate 12, the substrate 12 may be a silicon substrate or the like, which is not limited in the embodiment of the present invention; The gate dielectric layer 5 covers the top surface and all sides of the channel region 1, and the gate electrode 6 covers the gate dielectric layer 5 to form a triple-gate structure, thereby enhancing the control ability of the gate electrode 6 to the channel r...

Embodiment 3

[0069] Please refer to Image 6 , is a schematic diagram of the structure of a gate-all-around junctionless field effect transistor provided by an embodiment of the present invention, as shown in Image 6 As shown, the junctionless field effect transistor includes a channel region 1, an extension region 2, a source region 3 and a drain region 4; wherein, the channel region 1, the extension region 2, the source region 3 and the drain region 4 are all cylindrical structure; the gate dielectric layer 5 is arranged around the outer periphery of the channel region 1, and the gate electrode 6 is further arranged around the outer periphery of the gate dielectric layer 5 to form a gate-ring structure; the isolation dielectric layer 7 is arranged around the outer periphery of the extension region 2, Thereby realizing isolation between the source electrode 8 and the gate electrode 6, and between the drain electrode 9 and the gate electrode 6; the source dielectric layer 10 is arranged a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More