Heterojunction tunneling field effect transistor with heterogeneous gate dielectric and manufacturing method thereof

A tunneling field effect and heterogeneous dielectric technology, applied in the field of transistors, can solve the problems of small on-state current and serious bipolar effect, and achieve the effect of increasing the on-state current, suppressing bipolar effect, and increasing the tunneling area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

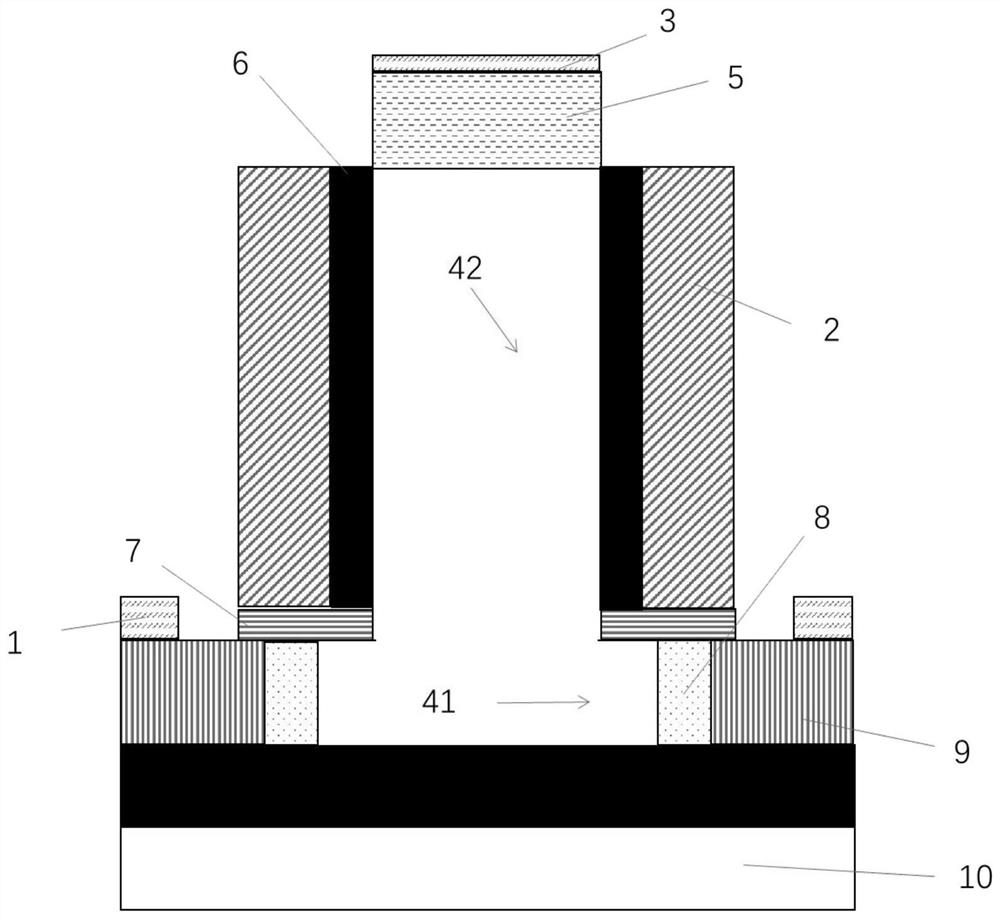

[0033] The present invention provides a heterojunction tunneling field effect transistor of a heterogate dielectric, the tunneling field effect transistor

[0036] Optionally, the material of the first heterogeneous medium 6 is a low-K dielectric material, and / or

[0037] The material of the second heterogeneous medium 7 is a high-K dielectric material.

[0038] Optionally, the first heterogeneous medium 6 is silicon dioxide, and / or the second heterogeneous medium 7 is hafnium oxide.

[0039] Optionally, the tunneling field effect transistor also includes two sides of the source 1 and the "one" portion

[0040] Optionally, the tunneling field effect transistor further includes an SOI substrate 10 under the "a" portion. SOI

[0041] Optionally, the length of the SOI substrate 10 is equal to the length of the "one" part and the length of the "one" part

[0043] N

[0044] P

[0047] N

Embodiment 2

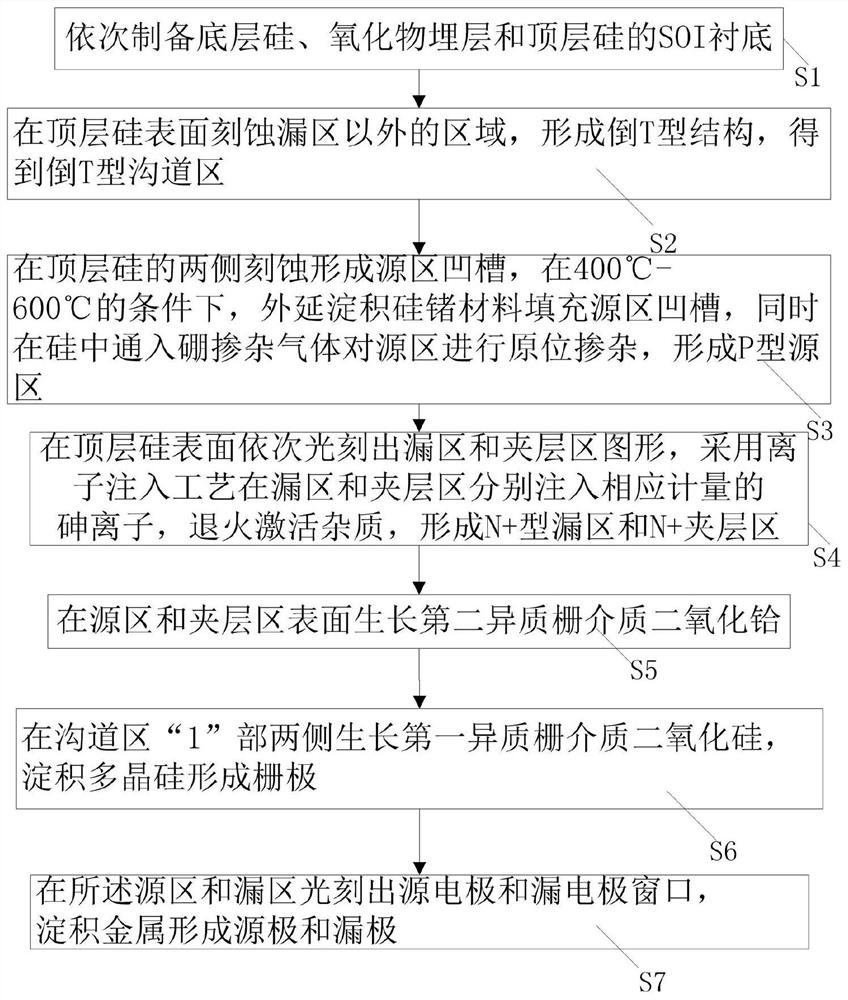

[0050] The present invention also provides a method for making a heterojunction tunneling field effect transistor based on the above-mentioned heterogate dielectric.

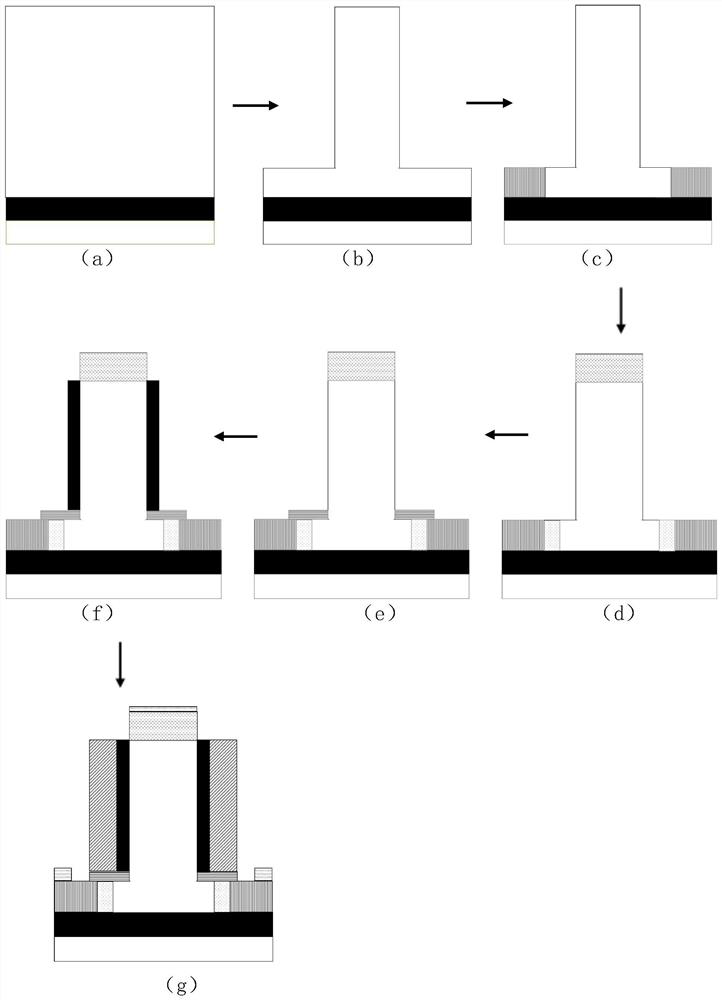

[0052] S1: The SOI substrate 10 of the bottom layer silicon, the oxidized physical layer and the top layer silicon is sequentially prepared.

[0057] S2: Etching the area other than the drain region on the top silicon surface to form an inverted T-type structure to obtain an inverted T-type channel region.

[0058] S21: grow a layer of SiO on the top layer silicon surface

[0064] S33: using a selective epitaxial growth process to deposit a silicon germanium material in the source region groove, and feeding boron doping gas at the same time

[0071] S5: growing a second hetero-gate dielectric hafnium dioxide on the surface of the source region and the interlayer region.

[0075] Step 6: growing a first hetero-gate dielectric 6 silicon dioxide on both sides of the channel region "1", and depositing polysilicon to form...

Embodiment 3

[0086] S12: a silicon epitaxial layer is formed on the surface of the buried oxide layer by epitaxial growth to form an SOI substrate 10;

[0095] S33: using the selective epitaxial growth process to deposit germanium-silicon material in the source region groove, and feeding boron doping gas at the same time

[0097] S4: the preparation doping concentration is 5×10

[0101] Wash off the photoresist, then wash with a hydrofluoric acid HF solution to remove the SiO

[0102] S5: prepare a second hetero-gate dielectric HfO with a thickness of 3 nm

[0106] S6: prepare a first hetero-gate dielectric SiO with a thickness of 3 nm

[0107] S61: using a chemical vapor deposition process at 600° C., the obtained device on both sides of the channel region “1”

[0108] S62: use a dry etching process to etch the gate pattern to form a gate groove; epitaxy in the gate region groove

[0110] S64: use a photoresist mask to protect the gate region and the drain region 5, and selectively etch using ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More