A two-dimensional semiconductor material negative capacitance field effect transistor and its preparation method

A two-dimensional semiconductor and capacitive field technology, applied in the field of nanoelectronics, can solve the problems of severe interface state and deteriorating device subthreshold slope, and achieve the effects of small contact resistance, improved Fermi pinning of metal contacts, and good stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be further described through the embodiments below in conjunction with the accompanying drawings.

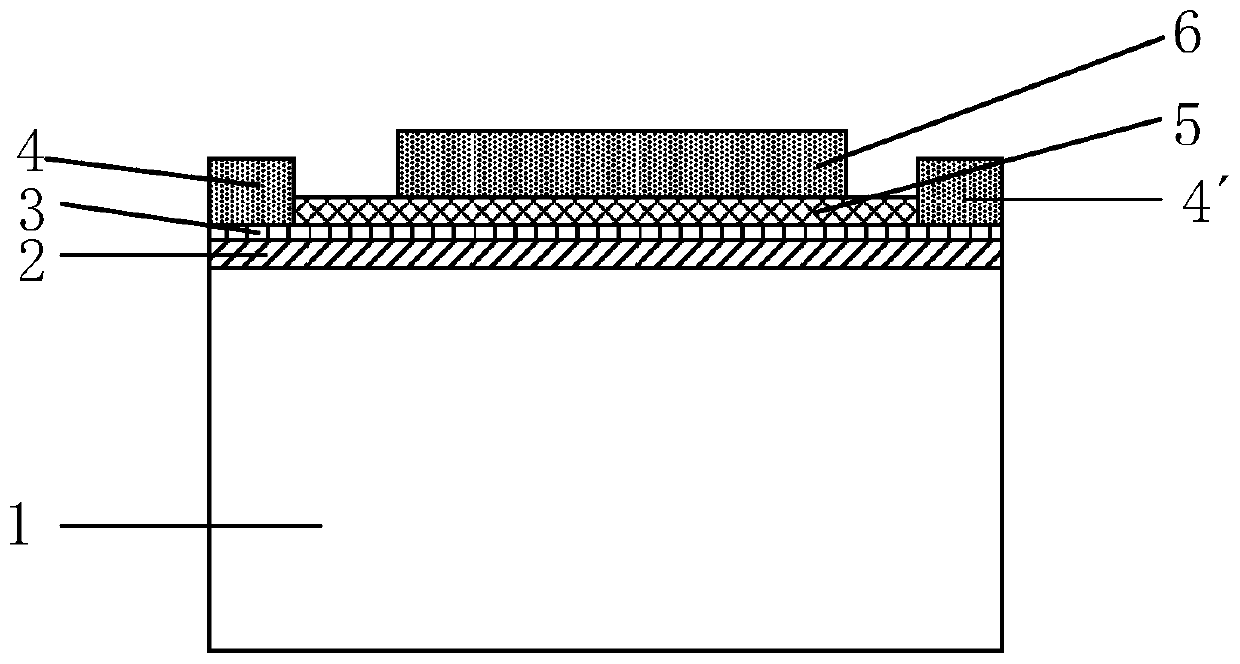

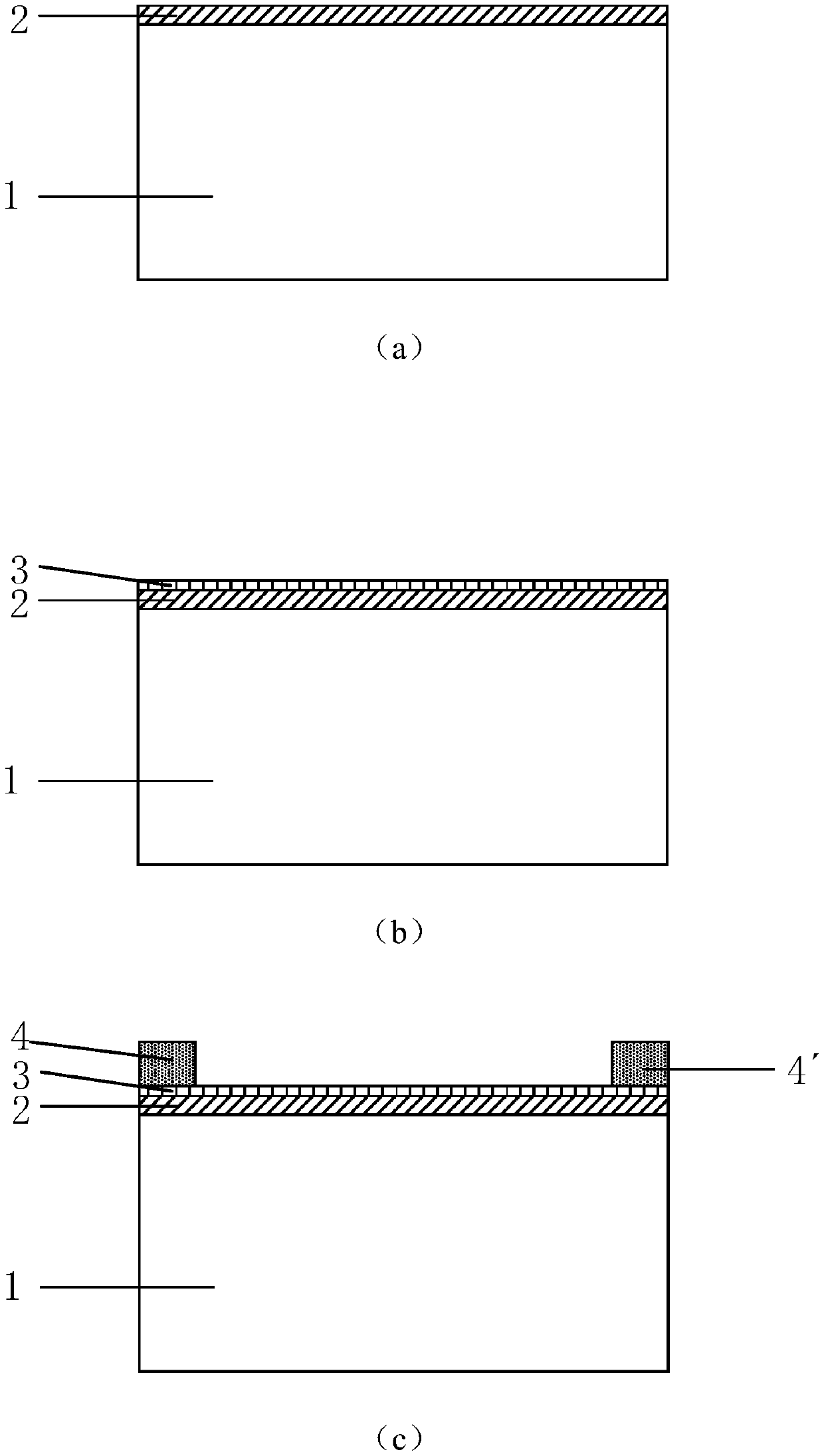

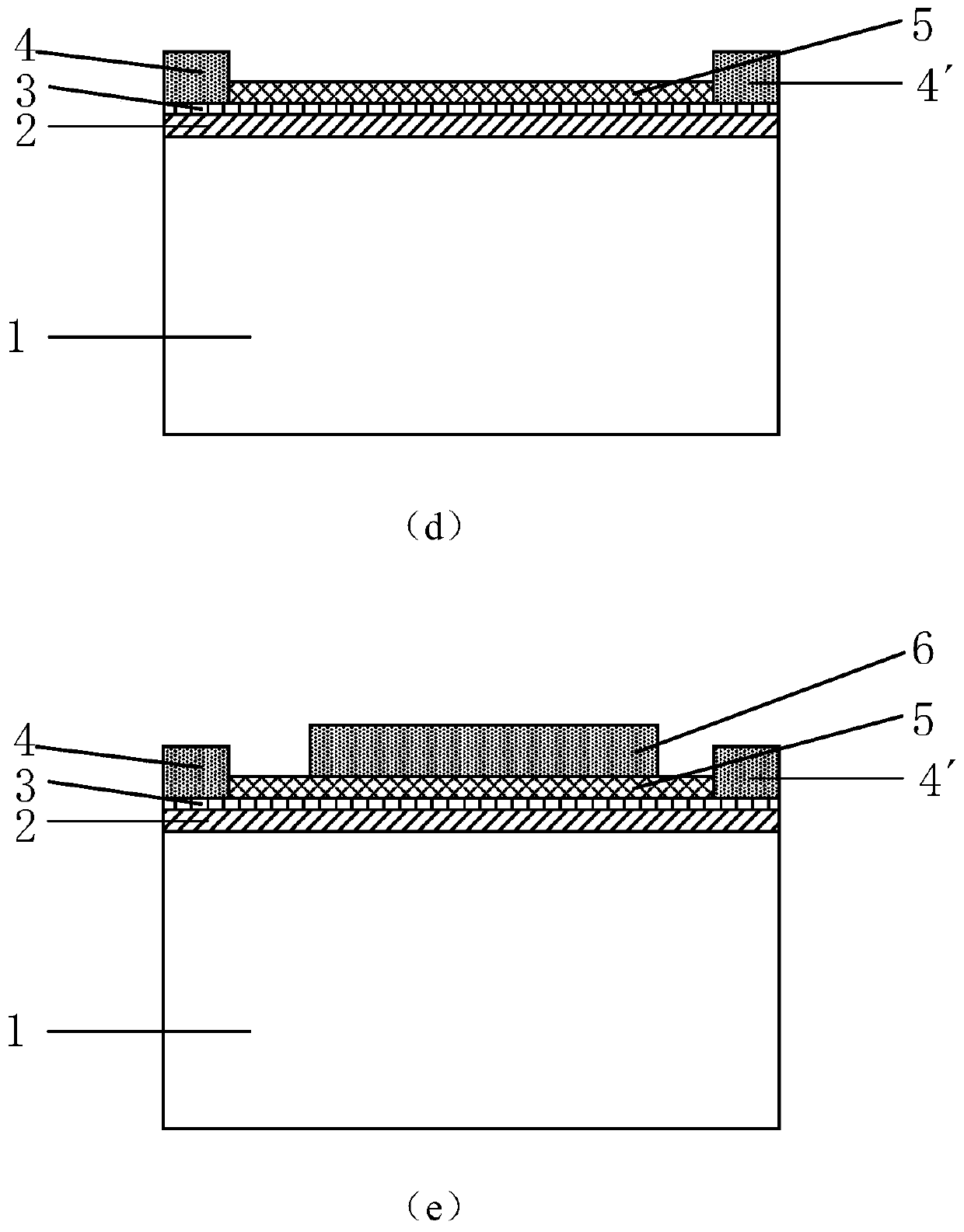

[0044] Such as figure 1 As shown, the negative capacitance field effect transistor based on the two-dimensional semiconductor material of the present invention includes an insulating substrate 1, a two-dimensional alloy semiconductor material HfZrSe 2 Layer 2, a HfZrO with ferroelectric properties 2 Dielectric layer 3 , a metal source electrode 4 , a metal drain electrode 4 ′, a high-k gate dielectric layer 5 , and a control gate electrode 6 . Among them, HfZrO with ferroelectric properties 2 The dielectric layer 3 is located in the two-dimensional alloy semiconductor material HfZrSe 2 Above layer 2, the metal source and drain electrodes 4 and 4' are located on the ferroelectric HfZrO 2 Above the dielectric layer 3, a high-k gate dielectric layer 5 is located between the metal source and drain electrodes. Two-dimensional alloy semiconductor...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More