Patents

Literature

70results about How to "Lower interface state" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

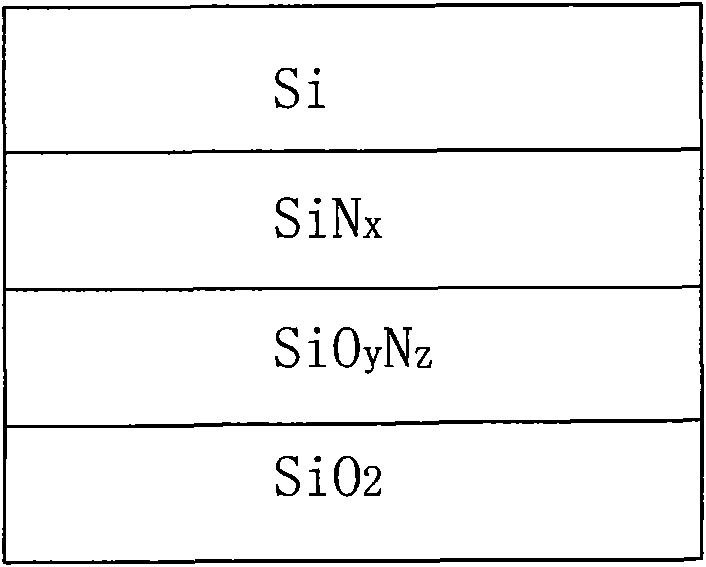

Method for realizing graded laminated passivation film on back surface of solar cell

InactiveCN101964378ALower thermal budgetSave energyChemical vapor deposition coatingPhotovoltaic energy generationNitrogen oxideSolar cell

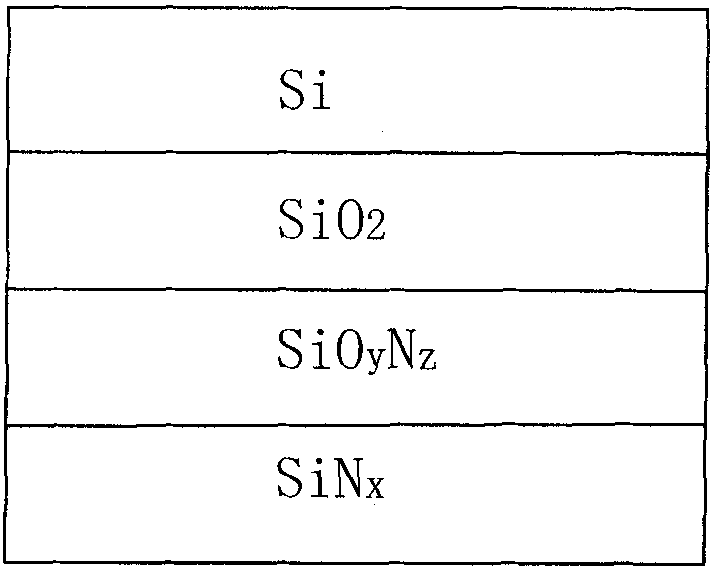

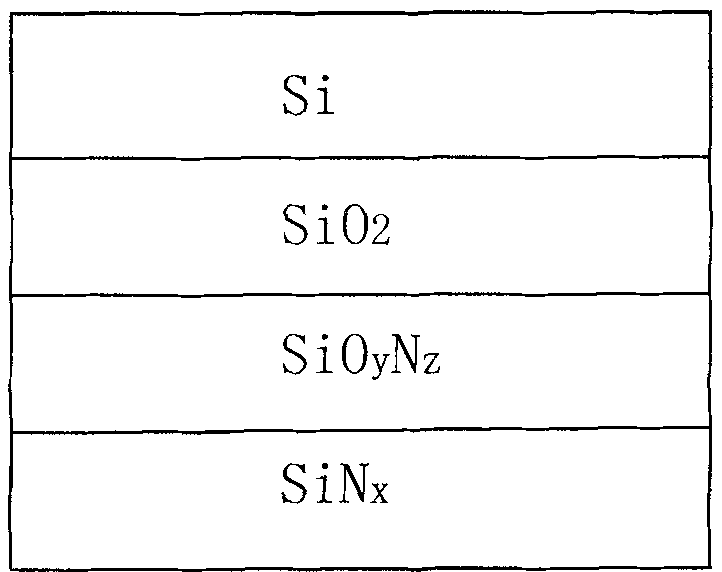

The invention relates to the field of solar cell production method, especially to a method for realizing a laminated passivation film on the back surface of a solar cell. A film is deposited on the backlight surface of a processed solar cell silicon chip according to chemical vapor deposition technology, the mixed gas of SiH4 and N2O is adopted as the gas at the beginning of the deposition, NH3 is gradually added in the process of deposition so that the component of the film is changed from silicon dioxide on the surface of the silicon chip to nitrogen oxide of silicon in the outward direction and then to silicon nitride in the outward direction, and the thickness of the film ranges from 50nm to 300nm. The method has the characteristics of fast deposition speed, high output, being capable of achieving the deposition of a plurality of films at a time, and high tightness of the deposited film. High temperature process is not needed in the technology, the heat budget required is less, and high temperature influence resulted from thermal oxidization is avoided, in addition, such a graded laminated film can effectively reduce interface state caused by the combination of different films, improve thermal stability compared with silicon nitride only, and lessen film stress.

Owner:TRINA SOLAR CO LTD

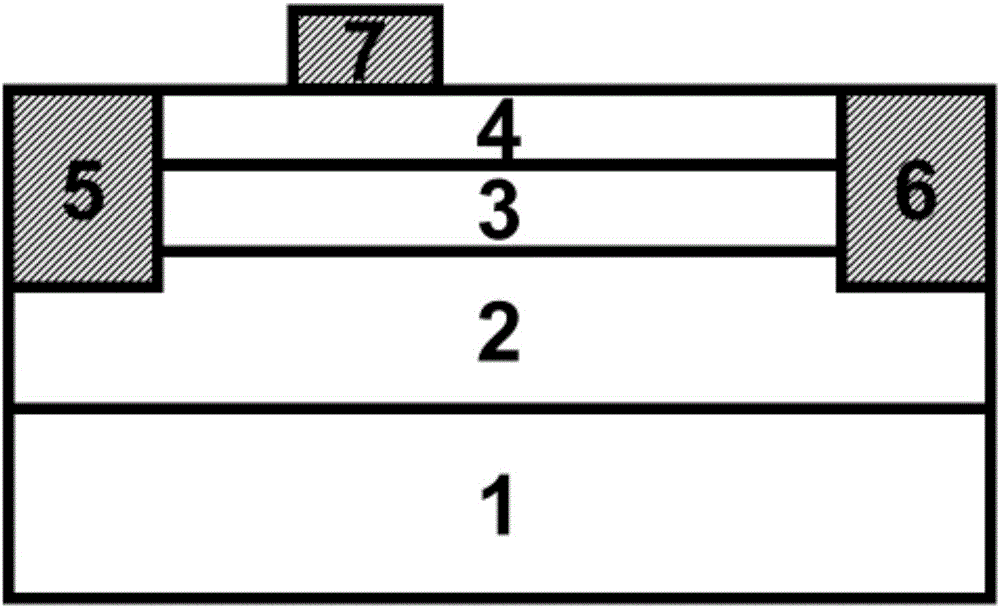

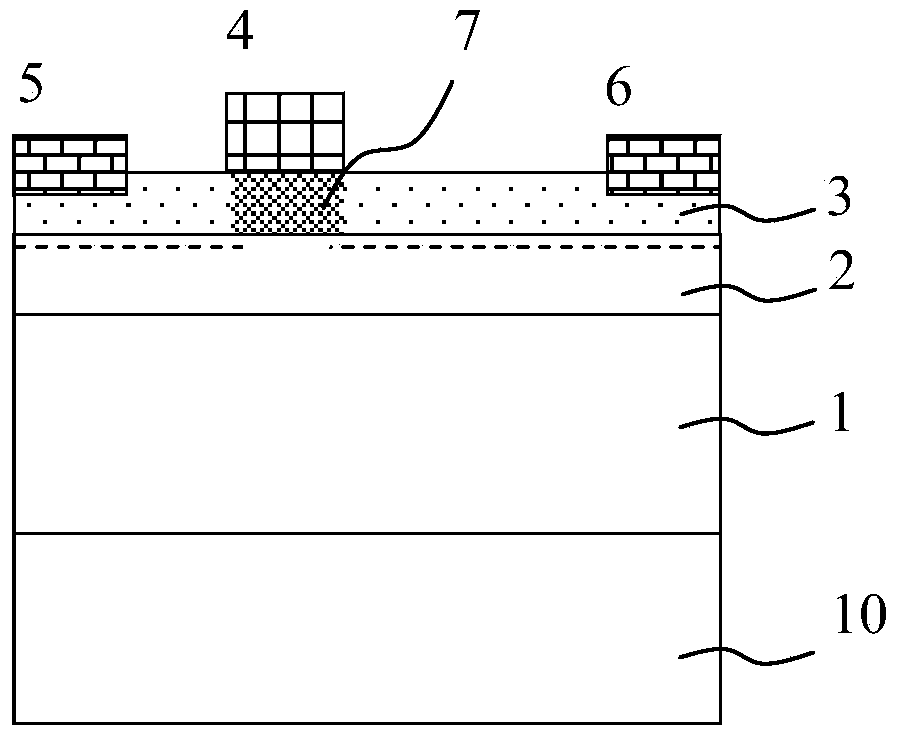

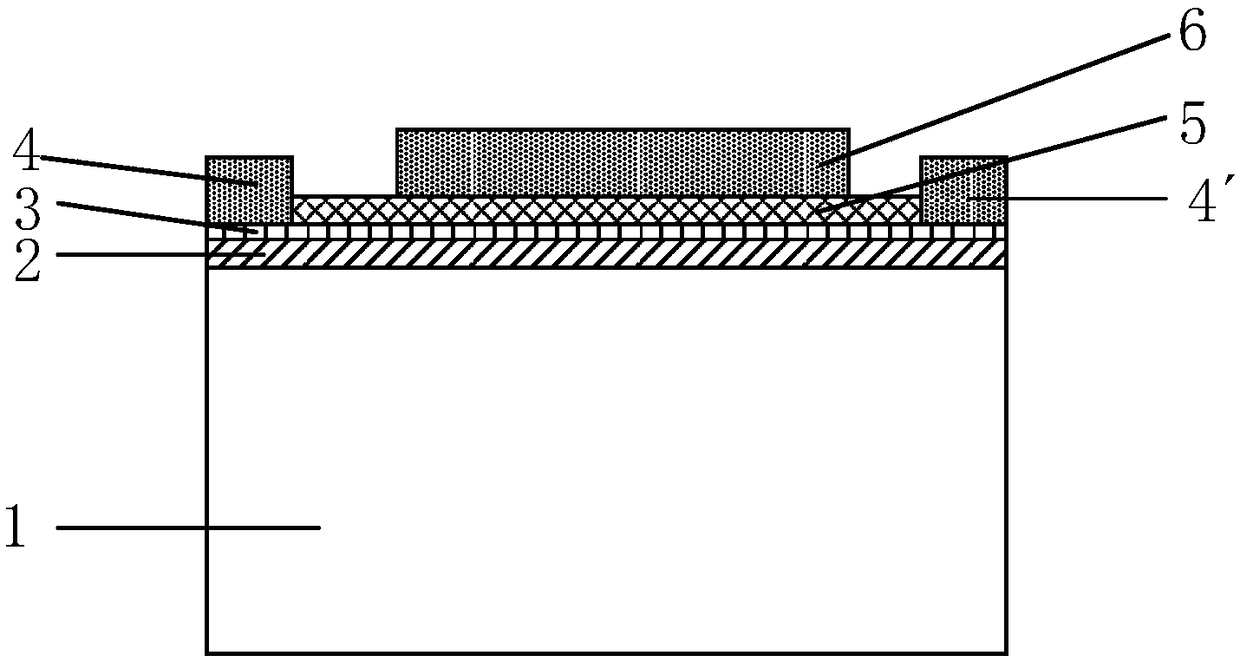

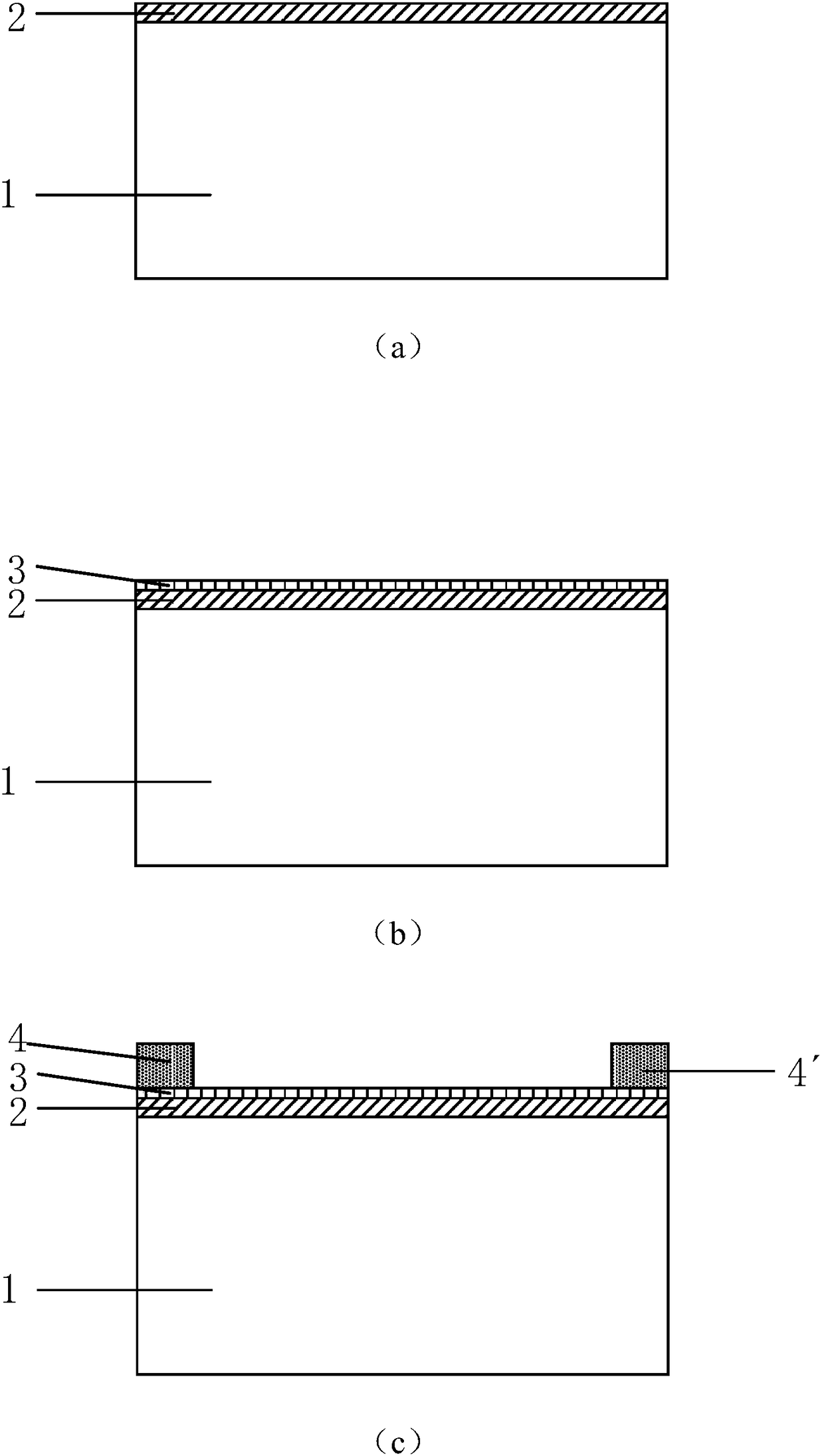

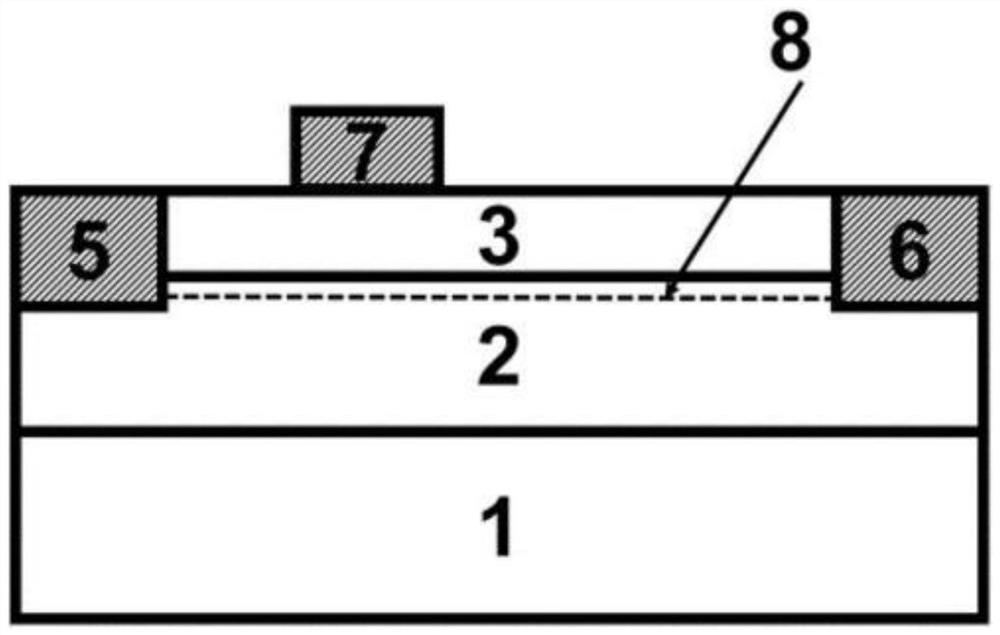

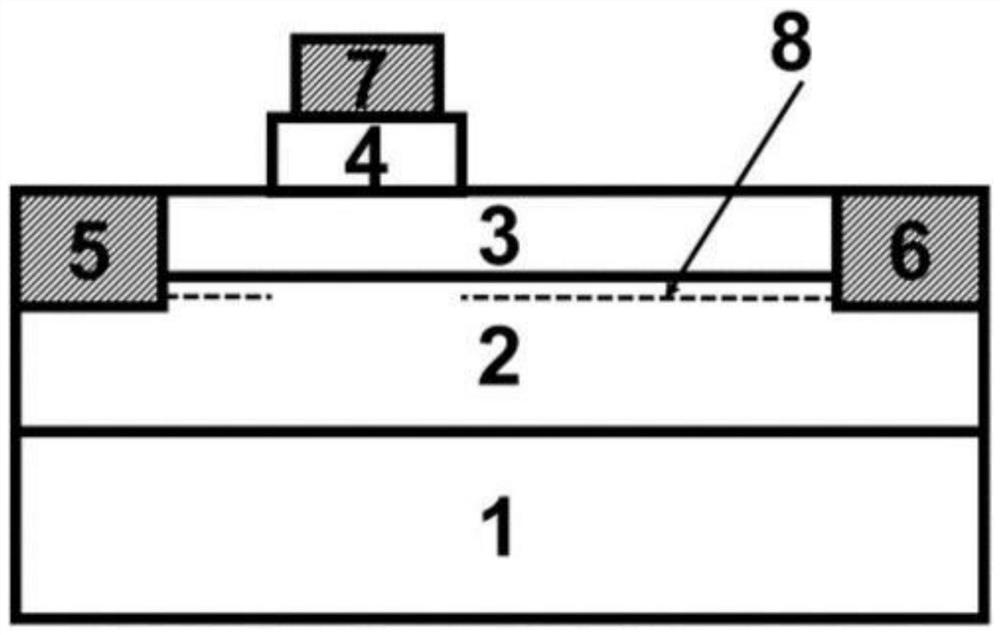

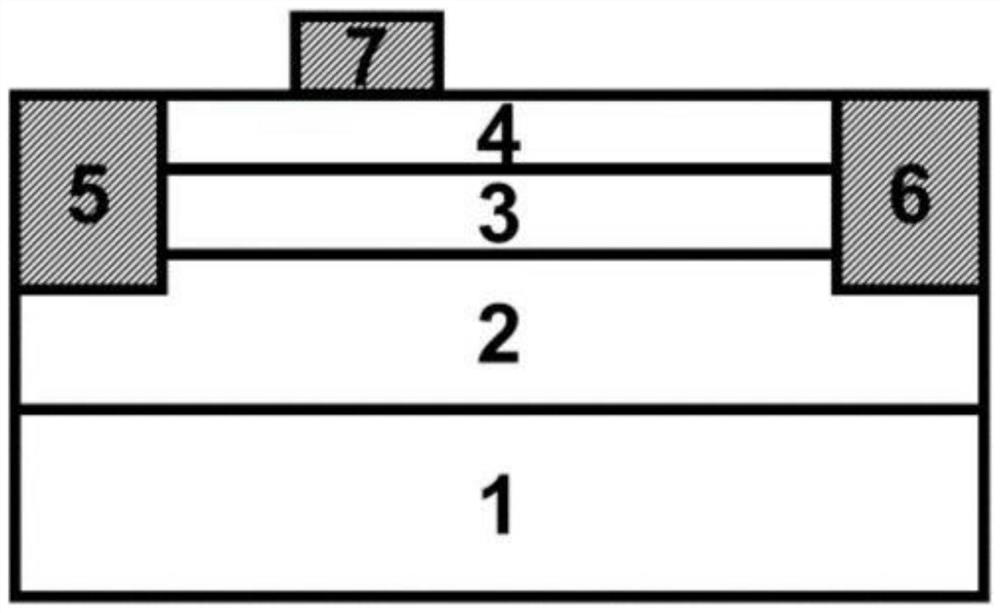

Method for realizing enhanced HEMT (High Electron Mobility Transistor) by virtue of p-type passivation and enhanced HEMT

InactiveCN105870013AAvoid damageLower interface stateSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorRepeatability

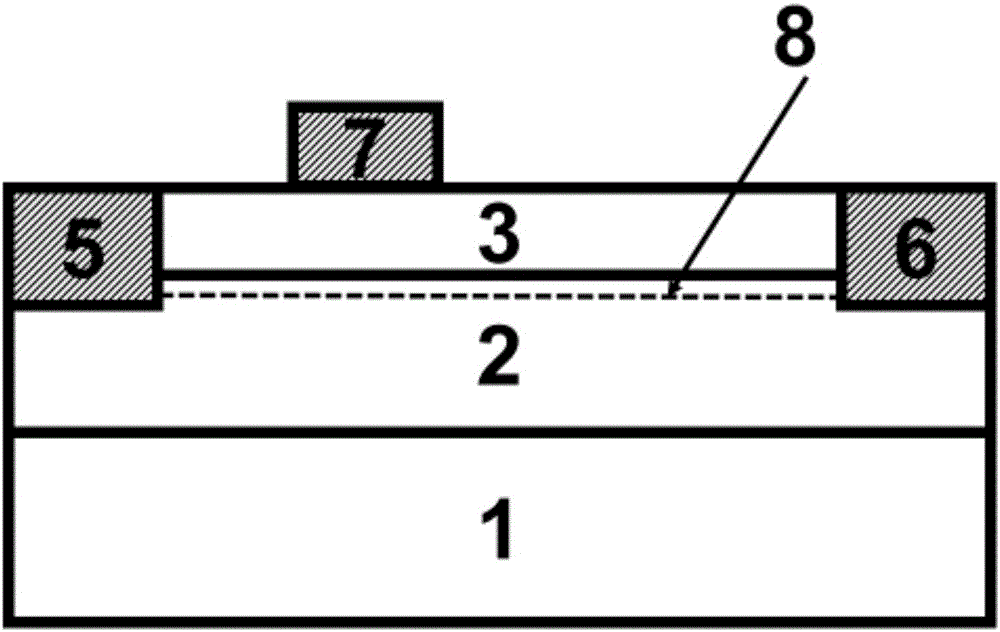

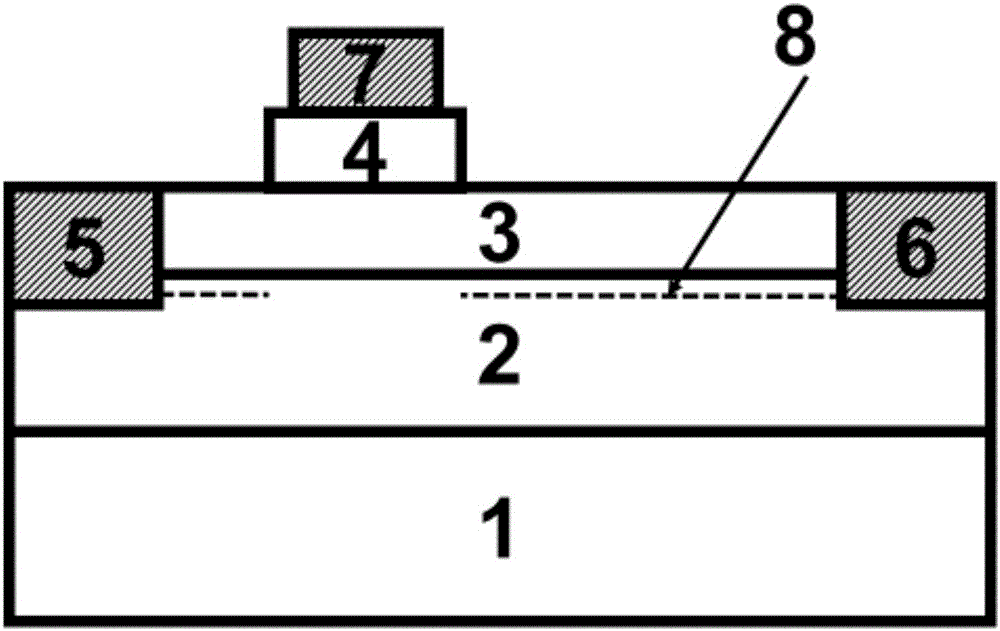

The invention discloses a method for realizing an enhanced HEMT (High Electron Mobility Transistor) by virtue of p-type passivation. The method comprises the following steps: providing a heterostructure which mainly comprises a first semiconductor and a second semiconductor, wherein the second semiconductor is distributed on the first semiconductor and is provided with a band gap wider than the first semiconductor, and two-dimensional electron gas is formed in the heterostructure; forming a p-type doped third semiconductor on the second semiconductor, performing passivation treatment on a residual region, except for an under-gate region, of the third semiconductor, so that the p-type doped region only exists at the under-gate region, and the under-gate region is distributed under a gate electrode of an HEMT device; manufacturing a source electrode, a drain electrode and a gate electrode connected with the heterostructure, electrically connecting the source electrode and the drain electrode through the two-dimensional electron gas, and enabling the gate electrode to be distributed between the source electrode and the drain electrode. The invention further discloses the enhanced HEMT. The method has the advantages of simple process, high repeatability, stable and favorable device performance, low cost, easiness for large-scale production and the like.

Owner:SUZHOU NENGWU ELECTRONICS TECH

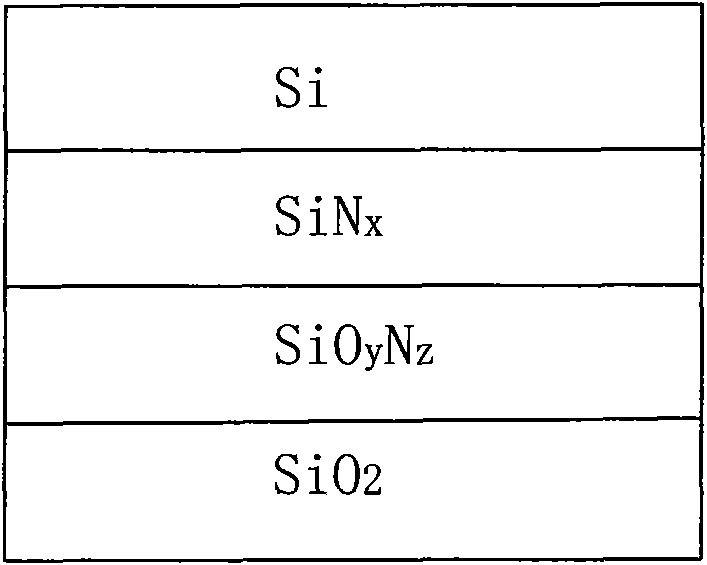

Method for realizing slowly-varying lamination antireflection coating of solar cell

InactiveCN101958365ARefractive index gradientFast depositionFinal product manufactureChemical vapor deposition coatingNitric oxideChemical vapors

The invention relates to the field of solar cell production methods, in particular to a method for realizing a slowly-varying lamination antireflection coating of a solar cell. In the method, a radiation surface of a treated solar cell silicon wafer is subject to deposition antireflection coating by a chemical vapor-phase deposition process, gases at beginning of deposition are mixed gas of SiH4 and NH3 or mixed gas of SiH4 and N2; and N2O is gradually added in a depositing process to ensure that components of the coating is varied from silicon nitride on the surface of the silicon wafer, to nitric oxide of silicon of an outer layer, and to the silicon dioxide to the outset layer, wherein the thickness of the coating is between 50 and 300nm. The method has high deposition speed and high yield and can realize deposition of various coatings at once; and the deposited coating has high compactness, can effectively reduce the interface state caused by different coating combination, and has the unique advantage of the silicon oxynitride and the advantages of silicon oxide and silicon nitride. The method has the advantages of simple and easy control, low cost and high efficiency.

Owner:TRINASOLAR CO LTD

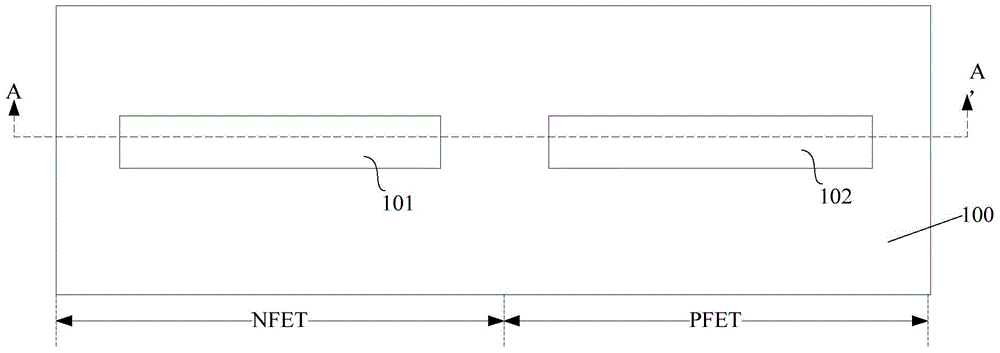

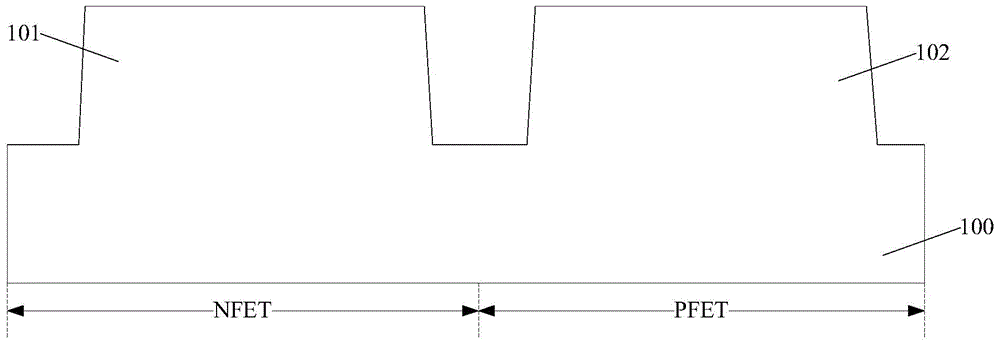

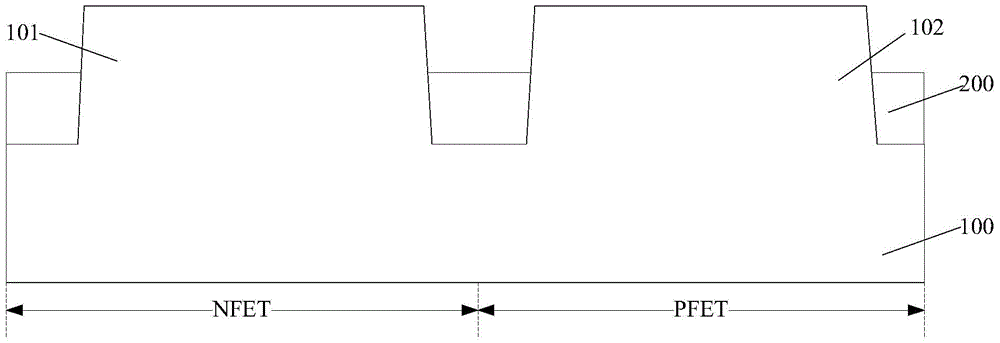

Semiconductor structure and method of forming same

ActiveCN105448730AImprove mobilityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDefect repairEngineering

A semiconductor structure and a method of forming the same are disclosed. The method of forming the semiconductor structure comprises the steps of providing a semiconductor substrate comprising an NFET region and a PFET region, forming with a first fin portion and a second fin portion, the semiconductor substrate being provided with an isolation layer thereon, forming a dielectric layer on the isolation layer, the dielectric layer being provided internally with a first groove and a second groove, the first groove exposing the first pin portion partially and the isolation layer at the two sides of the first fin portion partially, and the second groove exposing partially the second fin portion and partially the isolation layer at the two sides of the second fin portion; forming a first interface layer on the surface of the first fin portion at the bottom of the first groove, and forming a second interface layer on the surface of the second fin portion at the bottom of the second groove; carrying out defect repair ion doping for the first interface layer; and after the defect repair ion implantation for the first interface layer, forming a first gate structure in the first groove, and forming a second gate structure in the second groove. The method can improve the performance of the formed substrate structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP

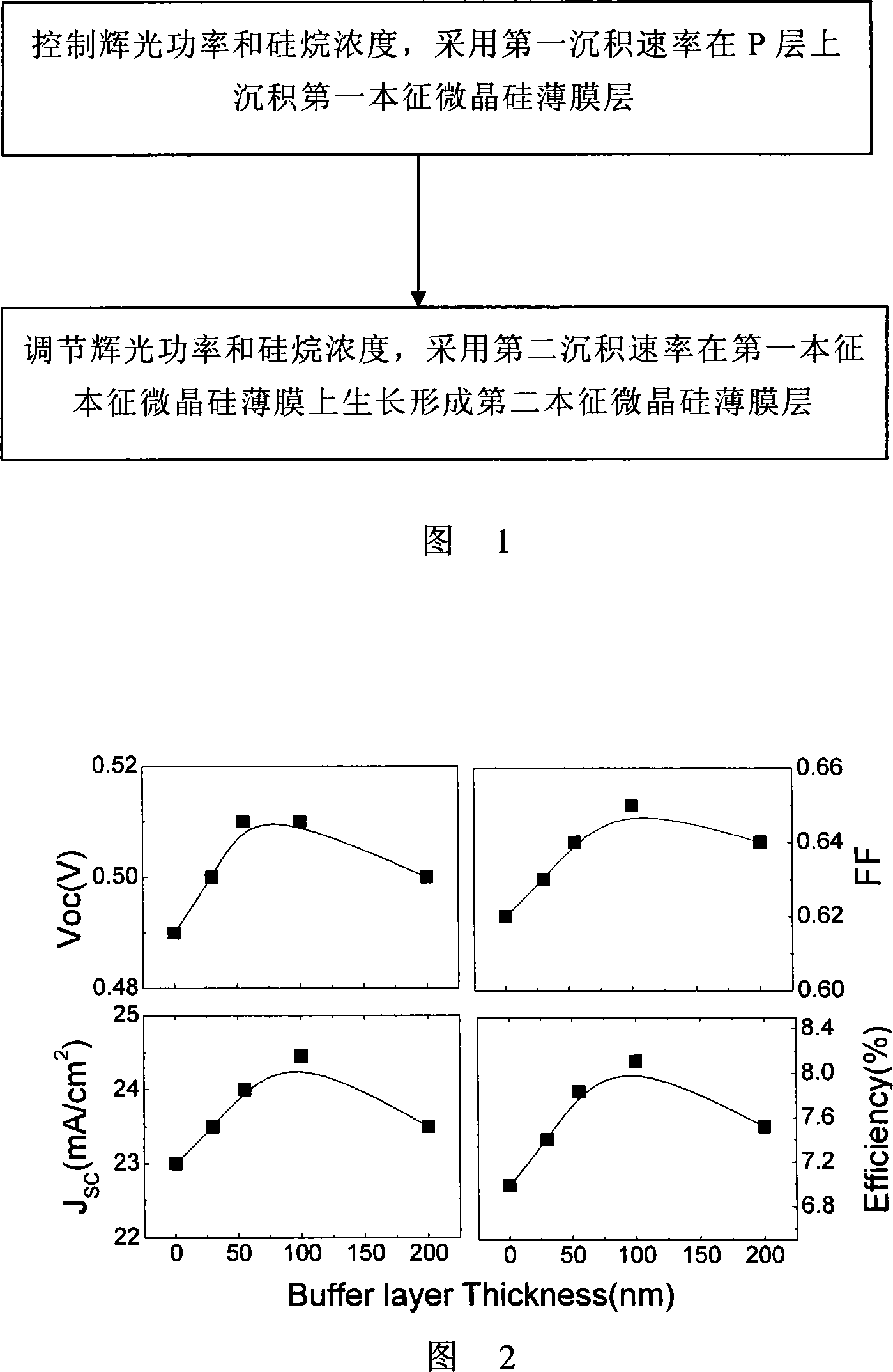

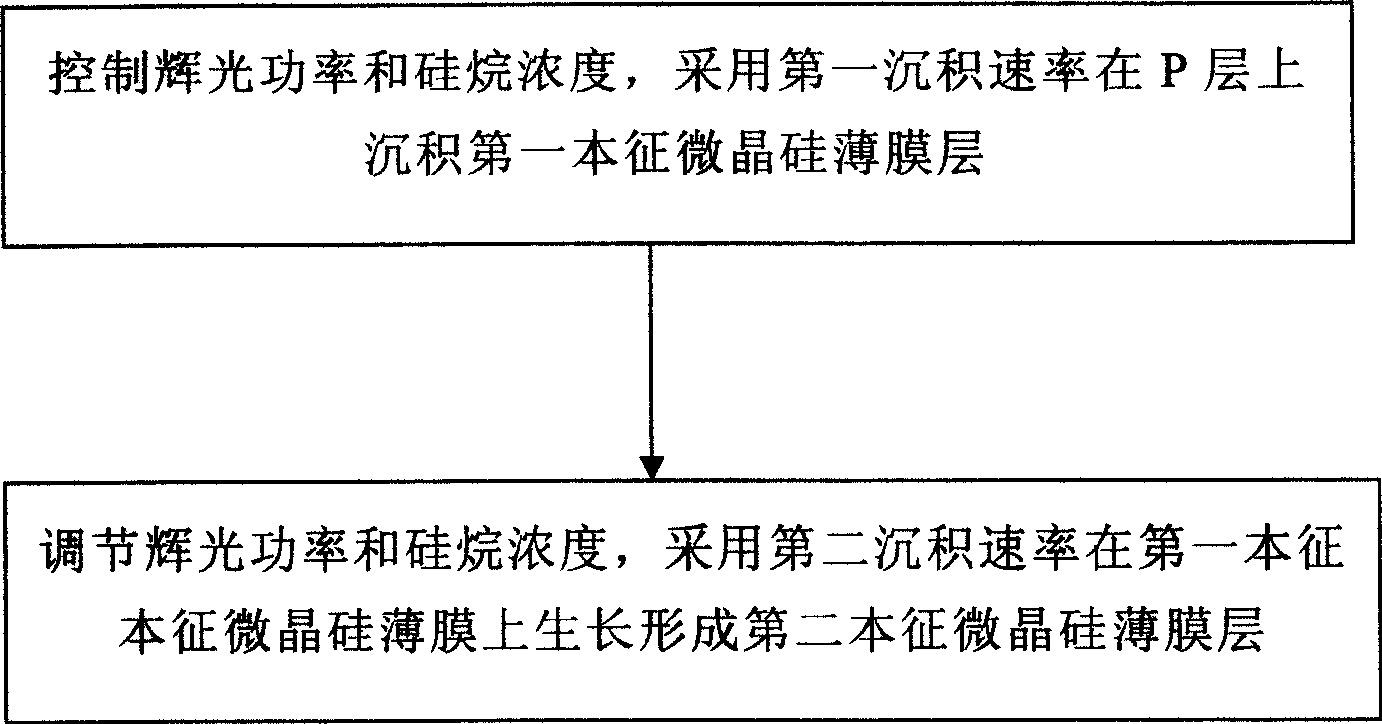

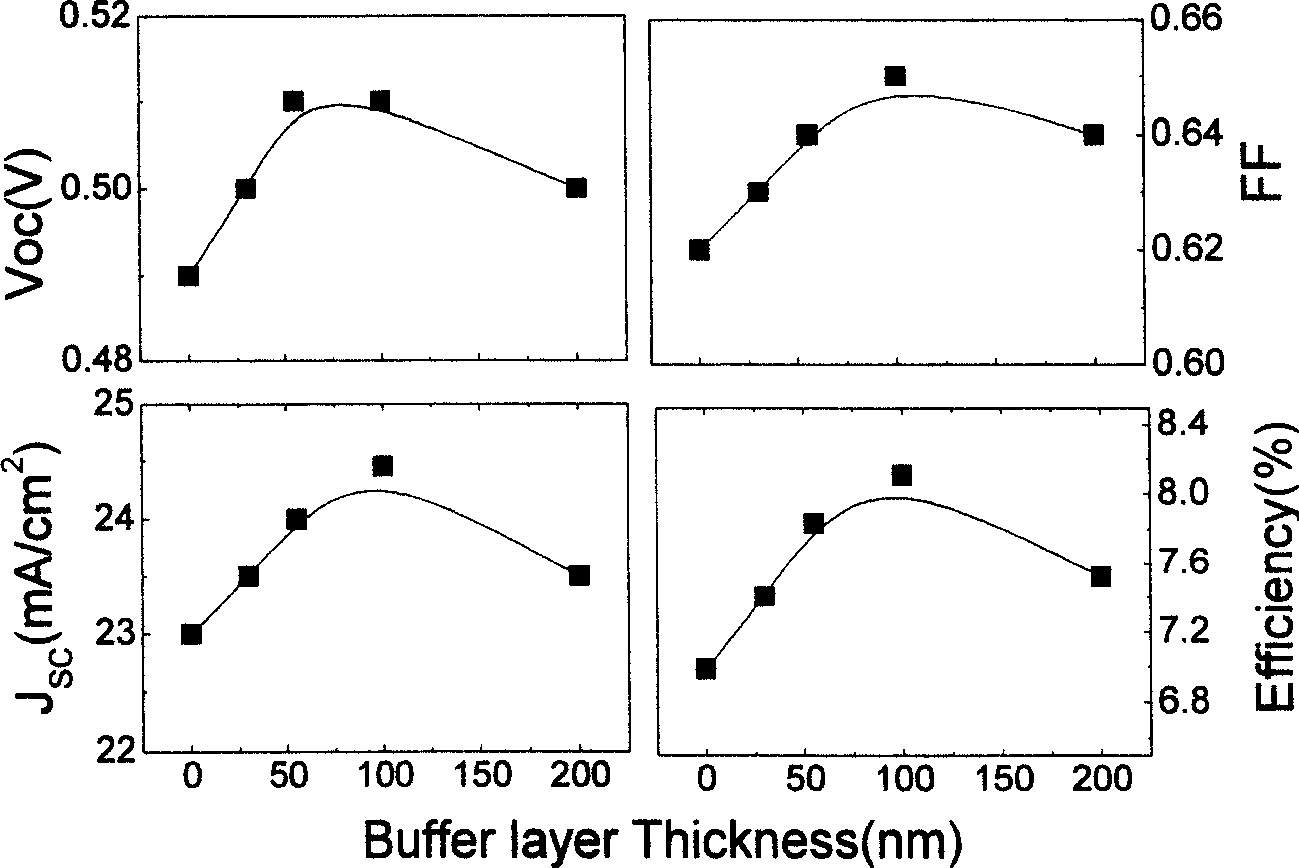

High speed deposition micro crystal silicon solar battery P/I interface processing method

InactiveCN101159295AReduce the density of defect statesLow glow power and small defect state densityFinal product manufactureSemiconductor devicesMicrocrystalline siliconSolar battery

The invention discloses a high-speed deposition method on a P / I interface of a microcrystal silicon solar battery, which comprises controlling glowing power and silicane concentration by ultra-high frequency plasma enhanced chemical vapor deposition method and depositing a first intrinsic microcrystal silicon film layer on a P player with a first deposition rate; adjusting glowing power and silicane concentration without extinguishment of plasma glow and growing a second intrinsic microcrystal silicon film layer on the first intrinsic microcrystal silicon film layer with a second deposition rate, wherein the first deposition rate is smaller than the second deposition rate. The invention uses lower glower power and lower silicane concentration to depose on P layer with smaller deposition rate to obtain high crystallized intrinsic microcrystal silicon film layer with low defect, so as to improve battery efficiency.

Owner:NANKAI UNIV

Method for improving interface state of back surface of PERC battery and battery prepared by same

ActiveCN108091724ALower interface stateImprove EL yieldFinal product manufacturePhotovoltaic energy generationEngineeringSolar cell

The invention discloses a method for improving the interface state of the back surface of a PERC battery and a battery prepared by the same and belongs to the solar cell technical field. The method includes the following steps that: 1) texturing, diffusion, etching and annealing process at an early stage is performed on a silicon wafer; and 2) plasmas are adopted to clean impurities on the back surface of the silicon wafer by means of a tubular plasma enhanced chemical vapor device, and an Al2O3 layer and a SiNx layer are successively deposited. According to the method of the present invention, the Al2O3 layer and the SiNx layer are sequentially deposited on the back surface of the PERC battery, and therefore, the interface state of the back surface of the battery can be reduced, a passivation effect can be improved, an EL problem caused by impurity adsorption during the back surface preparation process of the battery can be solved, the EL yield of battery sheets can be improved, and ahighly efficient high-yield PERC battery can be prepared.

Owner:ZHEJIANG AIKO SOLAR ENERGY TECH CO LTD +1

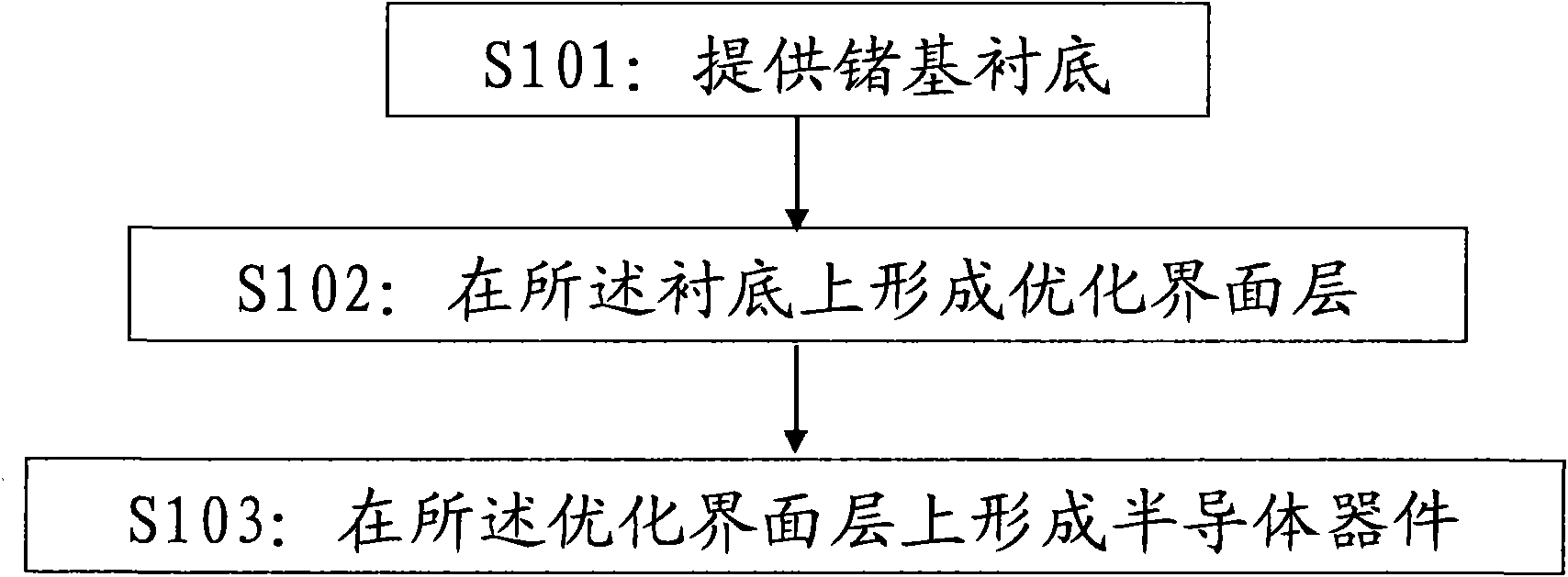

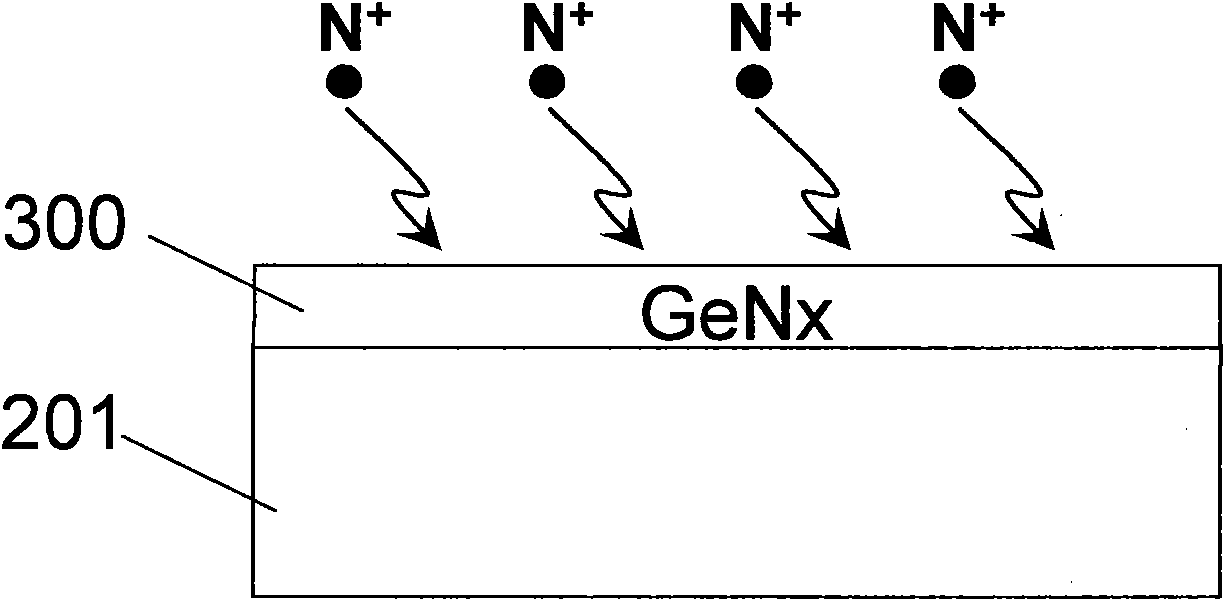

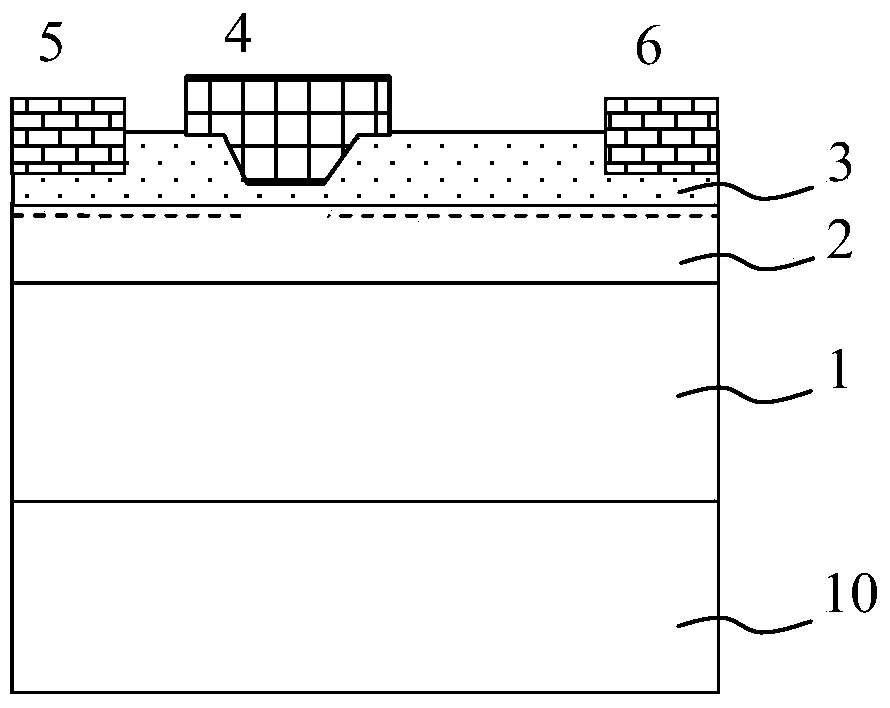

Interface-optimized germanium-based semiconductor device and method for manufacturing same

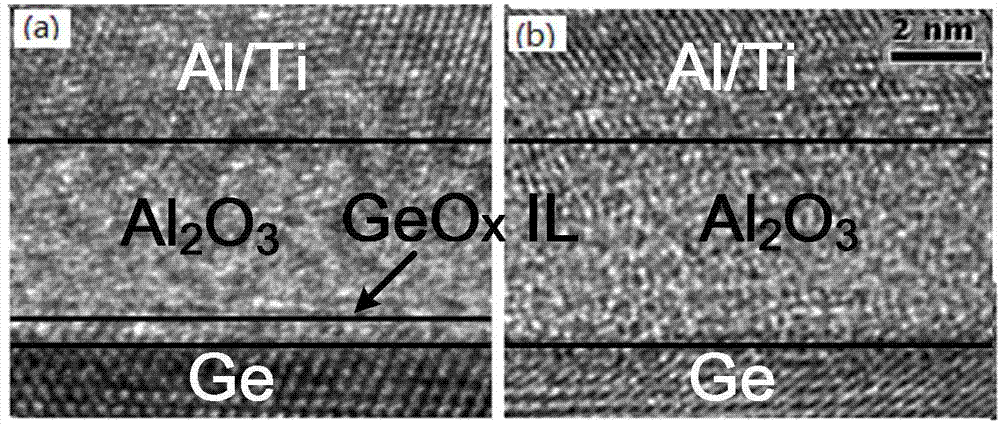

InactiveCN102339736AImprove thermal stabilityImprove compatibilitySemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceInterface layer

The invention discloses an interface-optimized germanium-based semiconductor device and a method for manufacturing the same, wherein an optimized interface layer with high thermostability is formed on a germanium-based substrate, and then a semiconductor device is formed on the optimized interface layer. As the optimized interface layer has higher thermostability and has good compatibility with high k-gate media, the interface thermostability of the device is effectively enhanced; and in addition, the interface charge and the interface state are lowered.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Enhancement mode device based on fluoride ion injection and manufacturing method thereof

ActiveCN103715256AAvoid gatheringImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesTunnel injectionGallium nitride

The invention discloses an enhancement mode device based on fluoride ion injection and a manufacturing method of the enhancement mode device based on fluoride ion implantation. The enhancement mode device based on fluoride ion injection comprises a substrate, an epitaxy multilayered structure formed on the substrate, a grid electrode, a source electrode and a drain electrode, wherein the grid electrode, the source electrode and the drain electrode are arranged on the epitaxy multilayered structure, and fluoride ions are injected in a heterogeneous structure layer below the grid electrode in a tunnel injection mode and are used for using up two-dimensional electron gas in the heterogeneous structure layer. As the fluoride ions are injected in the heterogeneous structure layer below the grid electrode in the tunnel injection mode and use up the two-dimensional electron gas in the heterogeneous structure layer below the grid electrode, the enhancement mode gallium nitride device is achieved. Meanwhile, unstable fluoride ions are removed through high temperature annealing, crystal lattices recover from damage caused when the fluoride ions are injected, and a crystalline state medium layer is utilized for protecting surfaces of nitride materials produced during high temperature annealing.

Owner:ENKRIS SEMICON

Two-dimensional semiconductor material negative capacitance field effect transistor and preparation method thereof

ActiveCN108831928AReduce deteriorationMetal Contact Fermi Pinning ImprovementSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceFerroelectricity

The invention discloses a two-dimensional semiconductor material negative capacitance field effect transistor and a preparation method thereof; a two-dimensional alloy semiconductor material HfZrSe2 is adopted as a channel material, and the surface of the channel material is oxidized in air to generate HfZrO2, and then annealing is carried out to obtain an HfZrO2 dielectric layer with a ferroelectric property; a high-k gate dielectric layer is deposited on the dielectric layer, and a gate dielectric with a mixed structure is formed. By means of the device structure, high gate dielectric and channel two-dimensional semiconductor material interfaces can be obtained, the deterioration of the interface state on the sub-threshold characteristic is reduced, and the super-steep sub-threshold slope is easily obtained; meanwhile, the high-k gate dielectric on the upper layer can protect the HfZrO2 dielectric of the ferroelectric characteristics below, so that the dielectric is isolated from theair, and the stability of the device is greatly improved. The device is simple in preparation process and large-scale production can be realized.

Owner:PEKING UNIV

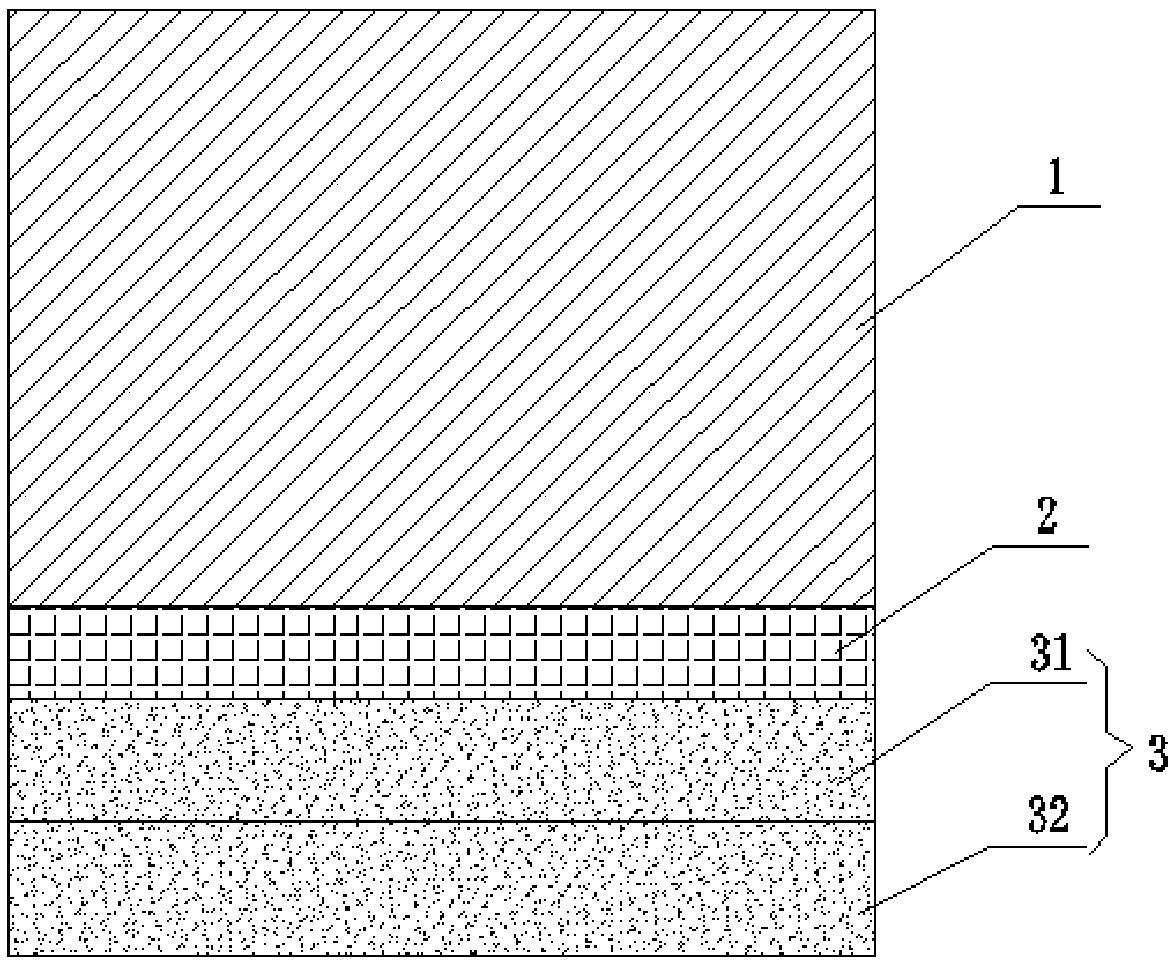

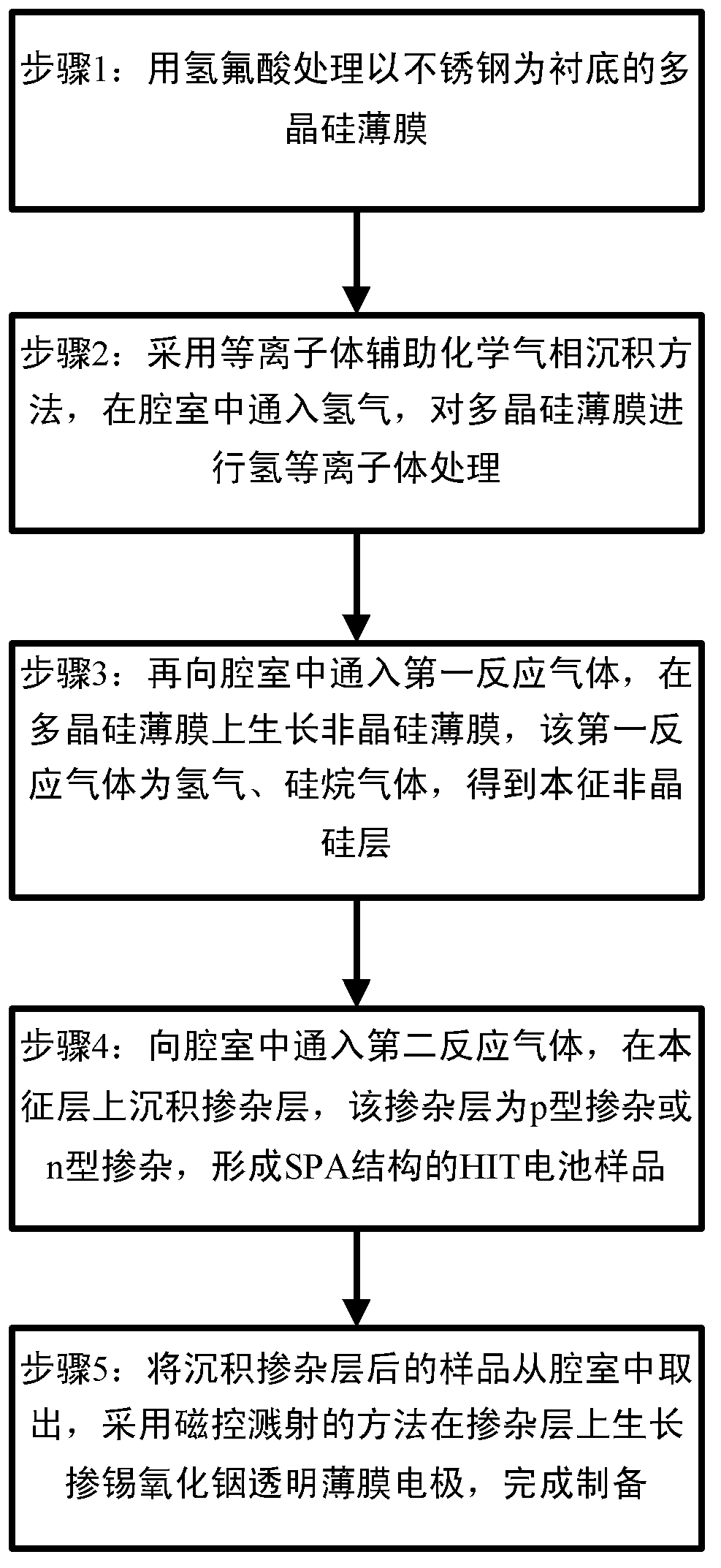

Method for passivating amorphous silicon and polycrystalline silicon film interfaces and manufacturing single junction polycrystalline silicon amorphous silicon (SPA) structure heterojunction with intrinsic thin-layer (HIT) cell

InactiveCN103258919AReduce interface state densityImprove conversion efficiencyFinal product manufactureSemiconductor devicesHeterojunctionGas phase

The invention discloses a method for passivating amorphous silicon and polycrystalline silicon film interfaces of a solar cell and a method for manufacturing an n-type polycrystalline silicon film single junction polycrystalline silicon amorphous silicon (SPA) structure heterojunction with intrinsic thin-layer (HIT) cell through the method. The method for passivating the amorphous silicon and polycrystalline silicon film interfaces of the solar cell comprises the steps of strengthening chemical vapor depositions through plasma, and carrying out passivation processing on the amorphous silicon and polycrystalline silicon film interfaces of the solar cell under the condition that ammonia is led into a cavity. A surface state of a polycrystalline silicon film can be reduced through hydrogen plasma interface processing. Therefore, interface states of amorphous silicon and polycrystalline silicon films of the SPA structure HIT cell are reduced, synthesis of photon-generated carriers generated under illumination at the positions of the interfaces is reduced, collection of the photo-generated carriers is increased, and conversion efficiency of the cell is improved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

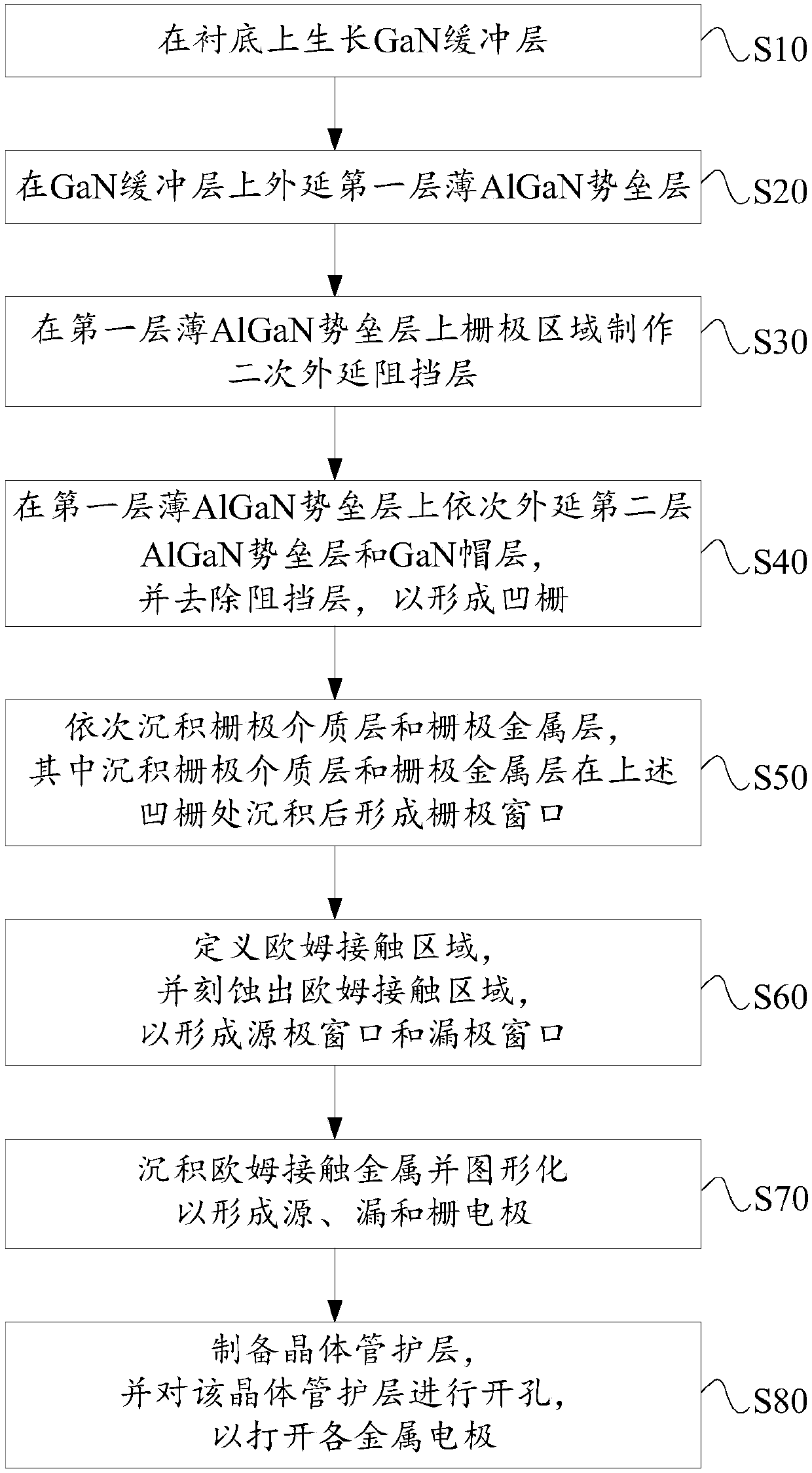

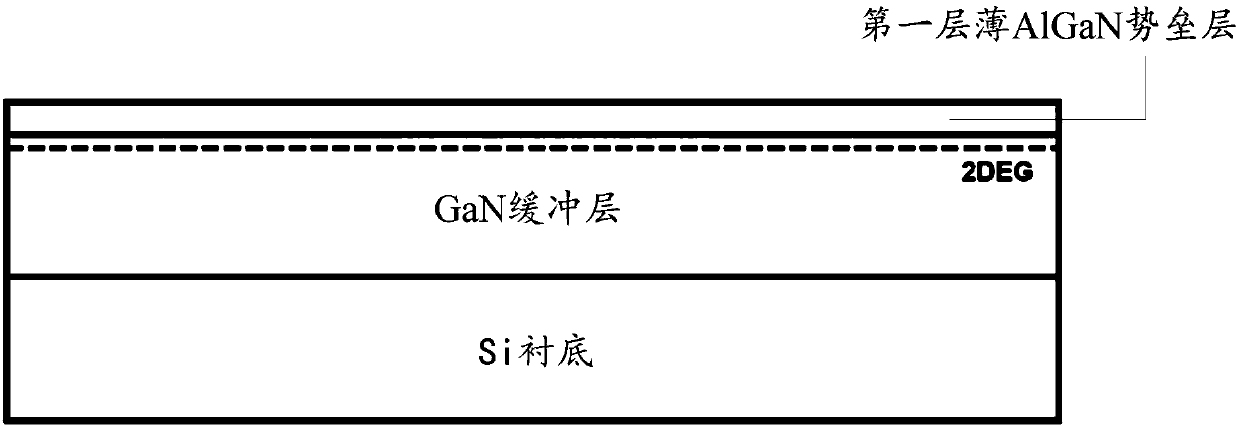

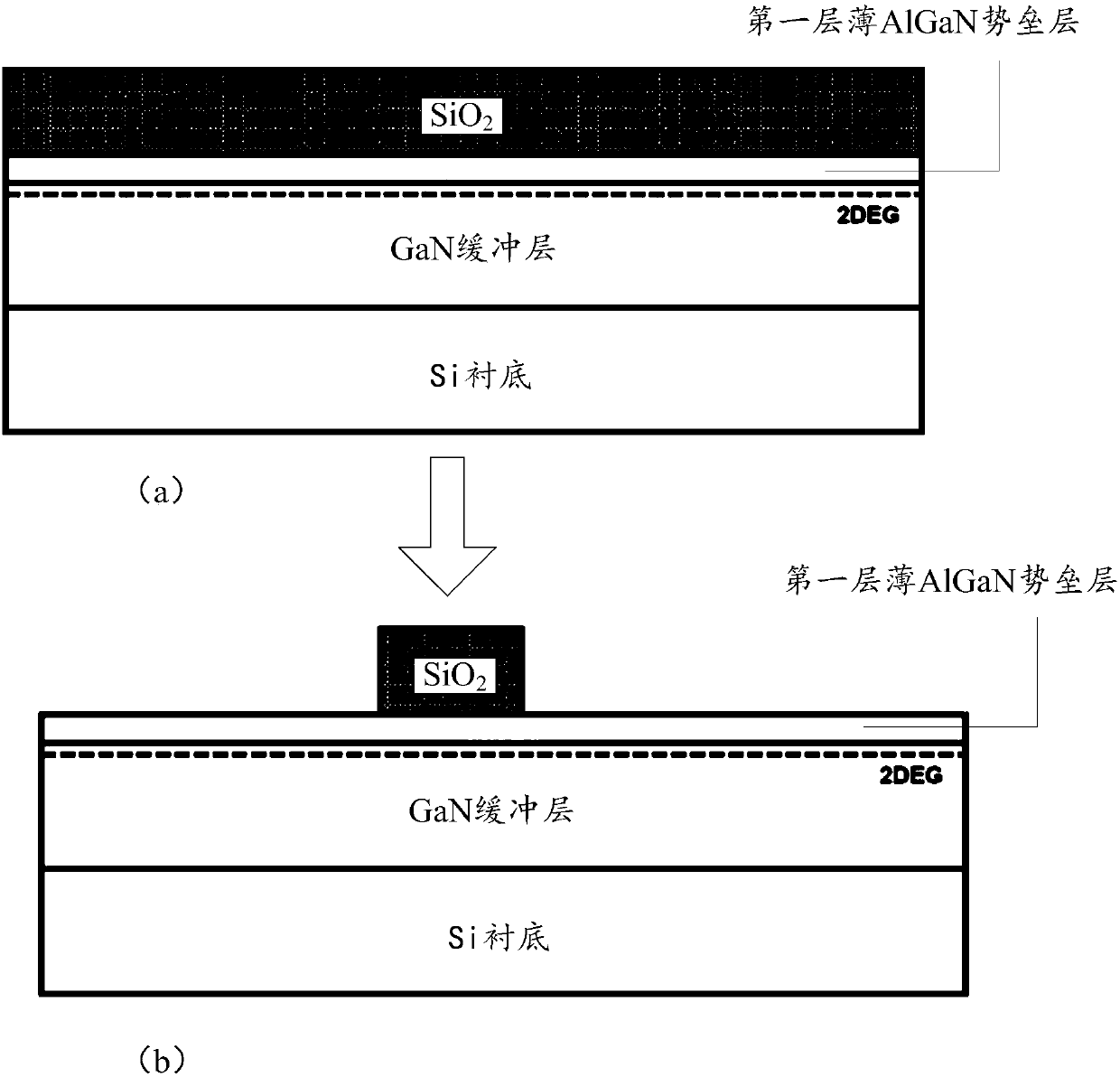

High electron mobility transistor and manufacturing method thereof

InactiveCN107768249AAvoid damageLower interface stateSemiconductor/solid-state device manufacturingSemiconductor devicesSecondary layerPhysics

The invention discloses a high electron mobility transistor and a manufacturing method thereof. A recessed gate is formed through manufacturing a secondary epitaxial barrier layer in a gate area on afirst thin AlGaN barrier layer, epitaxially growing a second AlGaN barrier layer and a GaN cap layer on the first thin AlGaN barrier layer in sequence and removing the barrier layer. Therefore, any dry and wet etching process is not needed when the recessed gate is manufactured, the damage of etching to the surfaces of the AlGaN barrier layers is avoided and the interface state is reduced to ensure excellent performance of the transistor; and in addition, the recessed gate is achieved through secondary epitaxy of AlGaN, so that the transistor has double AlGaN barrier layers, sufficient electrons in a channel are ensured and the transistor has relatively high breakover current.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

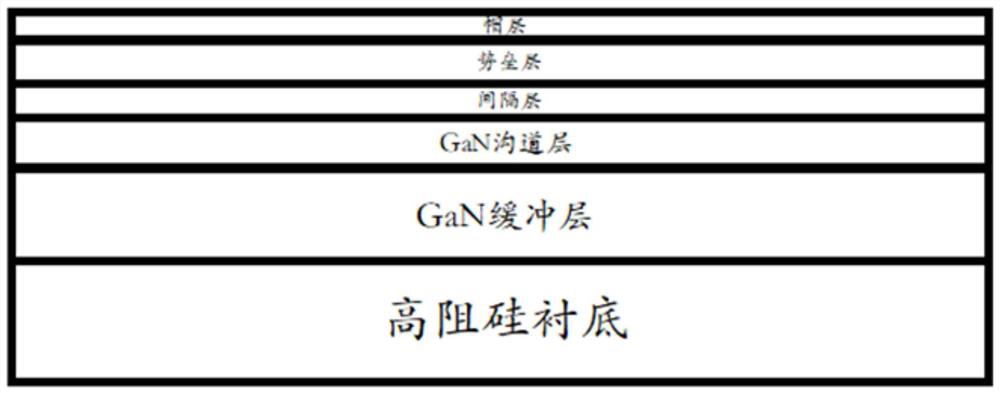

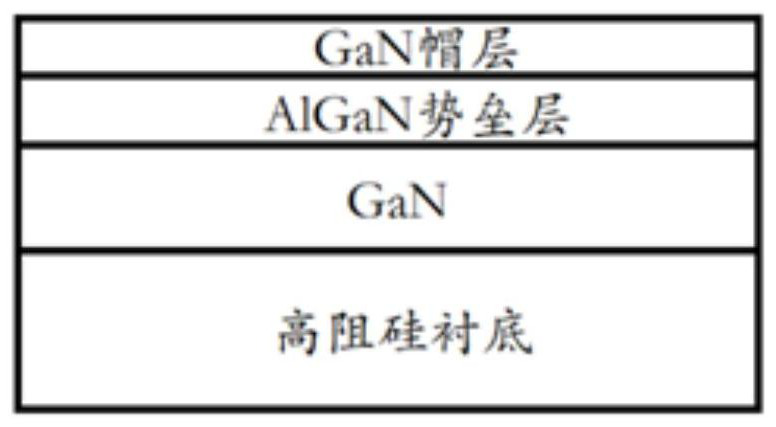

Silicon-based gallium nitride microwave device and preparation method thereof

ActiveCN111739799AObvious price advantageSuppress leakageSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactEngineering

The invention relates to a silicon-based gallium nitride microwave device and a preparation method thereof. The method comprises the steps of preprocessing a substrate, and depositing a first passivation layer; etching to form a groove, then depositing the ohmic contact metal of a source electrode and a drain electrode, and annealing to form the ohmic contact; etching the device; depositing a second passivation layer on the first passivation layer and the ohmic contact, then etching the first passivation layer and the second passivation layer, and depositing a gate metal after preprocessing; depositing a third passivation layer on the surface of the device, annealing, etching, and depositing a thickened metal; and depositing a fourth passivation layer, etching the passivation layer at theconnecting line part needing plate making, exposing the thickened metal, and preparing the connecting line. The method is simple and easy to operate, is low in cost and is capable of effectively reducing the electric leakage of the device.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

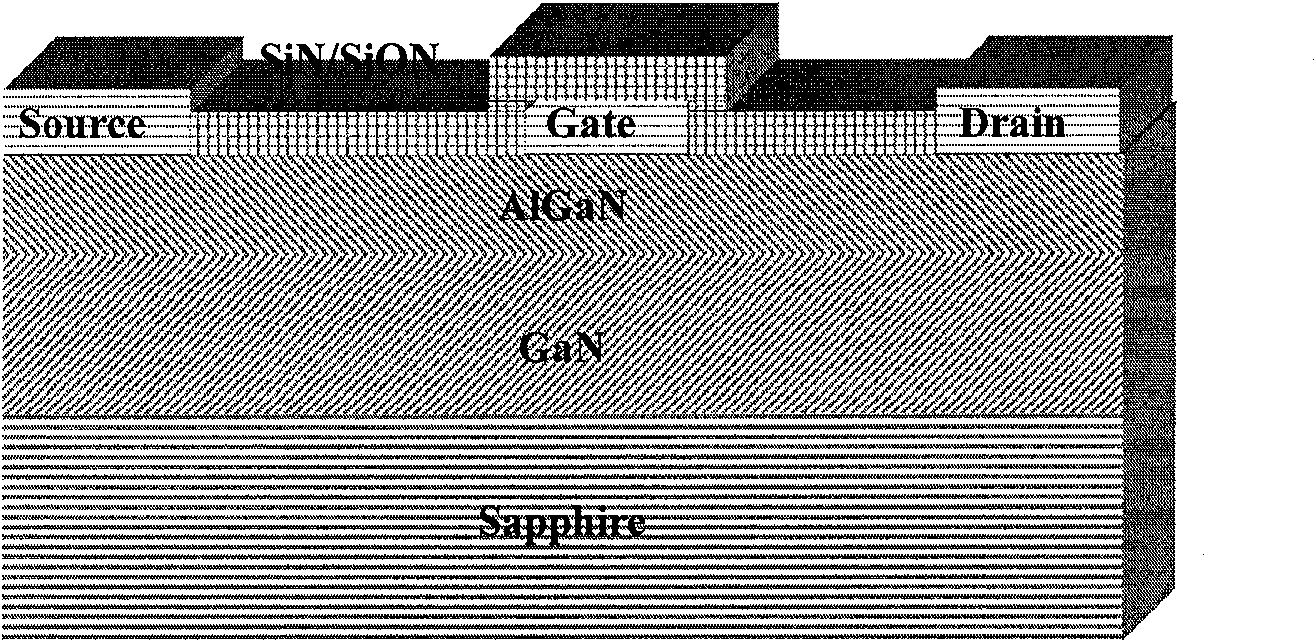

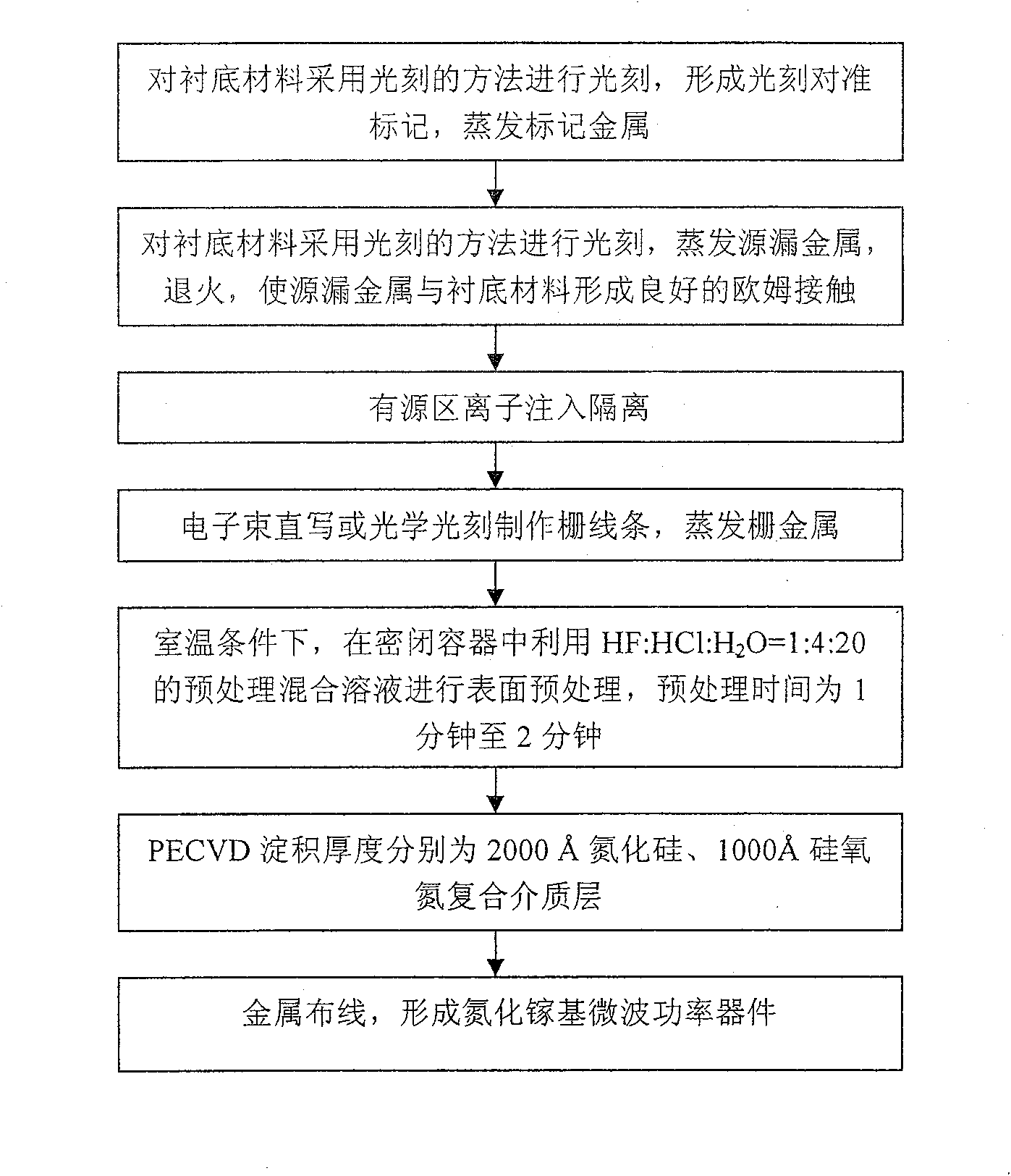

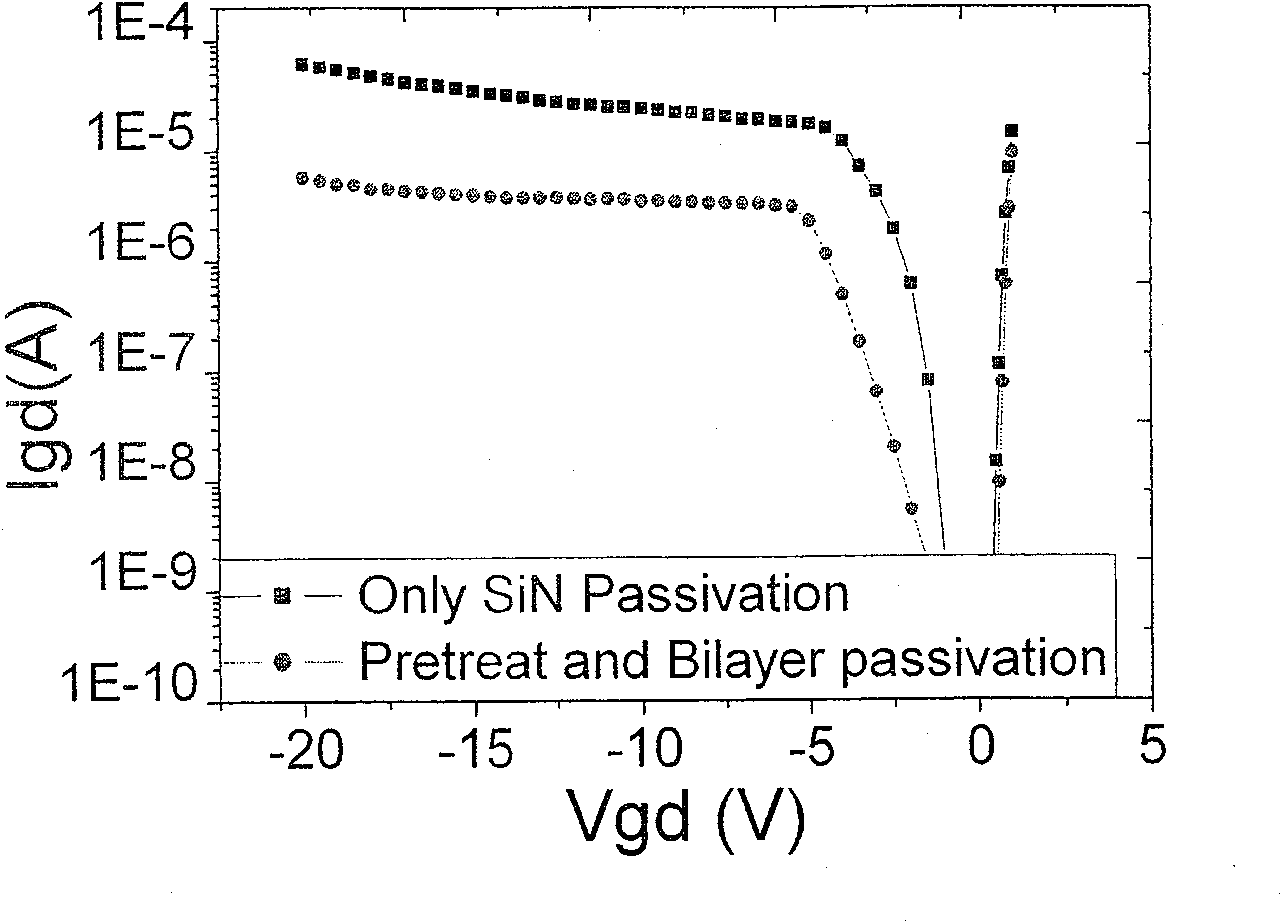

Method for improving the performance of gallium nitride based field effect transistor

InactiveCN100594591CSolve the current collapse effectSolve the collapse effectSemiconductor/solid-state device manufacturingSemiconductor materialsSurface oxidation

The invention relates to the technical field of production of wide bandgap semiconductor materials and devices and discloses a method for improving the performance of a GaN-based field-effect transistor, the method comprises: mixed pre-treatment solution is adopted to carry out the surface pre-treatment of the surface of a device before the passivation of the GaN-based field-effect transistor during the production process of the GaN-based field-effect transistor, then a compound dielectric layer of silicon nitride and oxygen-rich silicon nitride is deposited on the surface of the device afterthe surface pre-treatment, and the GaN-based field-effect transistor is passivated. The use of the method can solve a surface original oxide layer which is existed on the surface of AlGaN for a long time, eliminate the AlGaN surface state which is induced by the surface oxide layer, solve the surface state existing in an AlGaN and silicon nitride interface, the current collapse effect which is induced by the surface original oxide layer and the significant increase of the reverse gate leakage current caused by the conventional passivation and improve the stability and the reliability of GaN-based HEMT.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

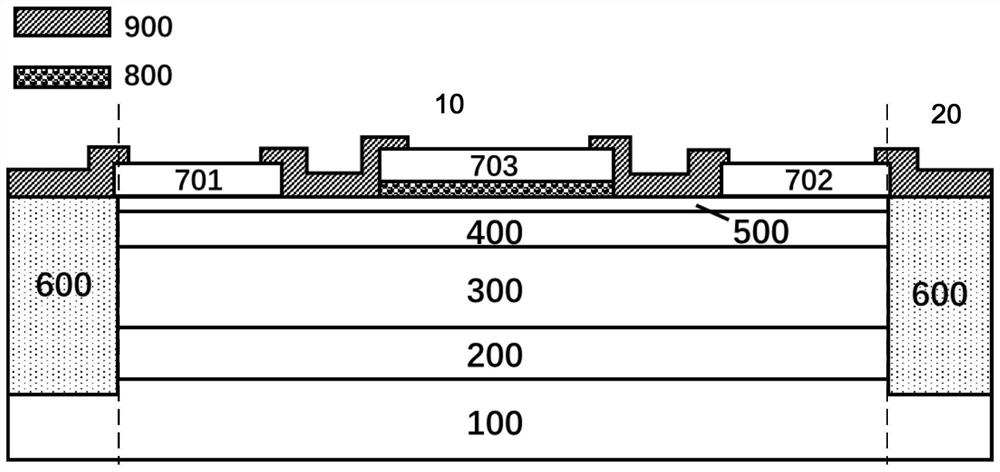

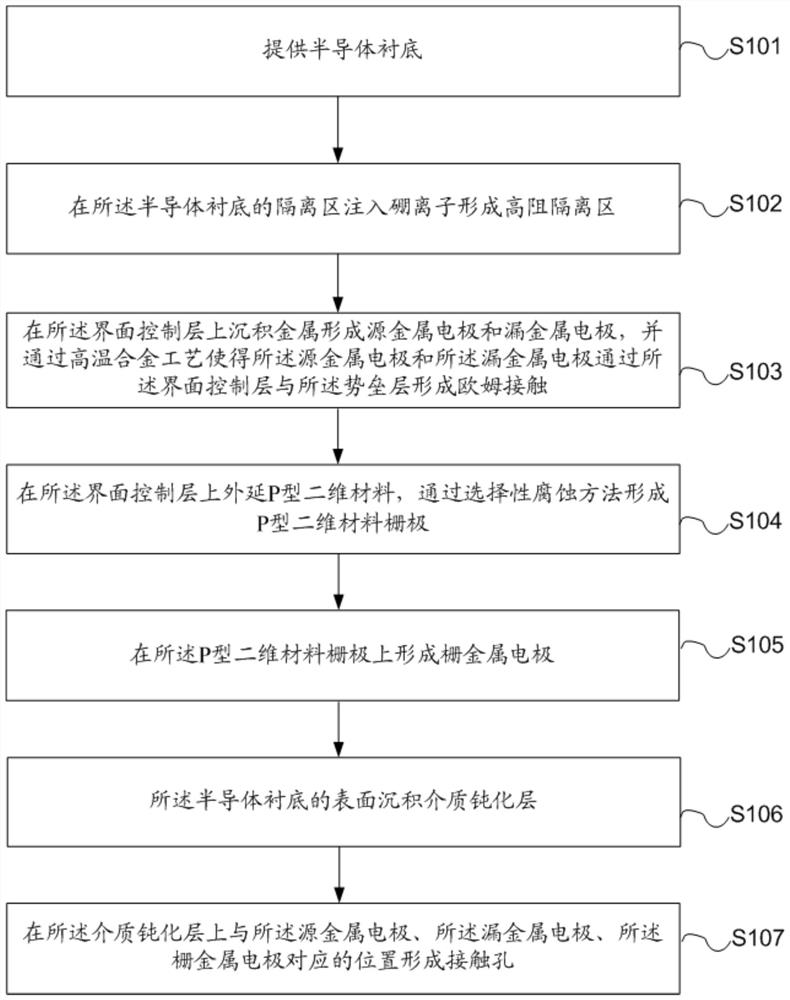

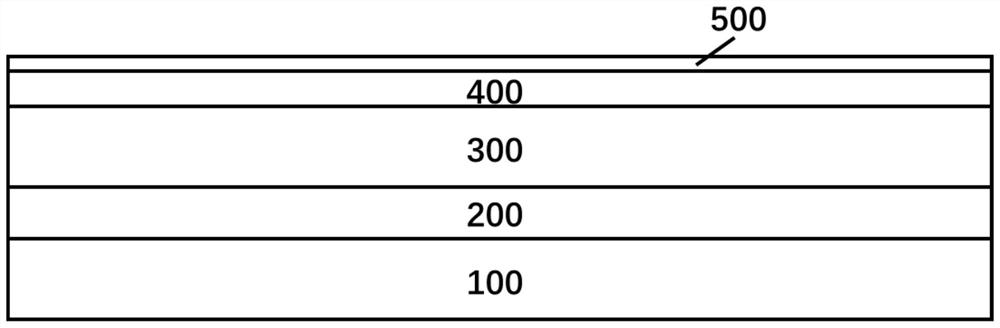

A kind of Gan base enhanced field effect device and its manufacturing method

ActiveCN108258035BGood threshold consistencyLattice matchingSemiconductor/solid-state device manufacturingSemiconductor devicesElectron holeMetallic electrode

The invention provides a GaN-based enhanced field effect device and a manufacturing method thereof. The GaN-based enhanced field effect device comprises an active region and an isolation region surrounded by the active region, wherein the active region comprises a single crystal substrate, a buffer layer, a channel layer, a barrier layer, an interface control layer, a source metal electrode, a drain metal electrode, a grid metal electrode and a dielectric passivation layer and further comprises a P-type two-dimensional material grid; the P-type two-dimensional material grid is inserted below the grid metal electrode, so the two-dimensional electron gas in the channel below the grid can be effectively depleted, and the GaN-based enhanced field effect device is realized. The P-type two-dimensional material is advantaged in that cavity concentration is high, crystal lattice matching and a low interface state are realized, selective removal from the surface of a gallium nitride material can be realized, and process controllability is good, so threshold consistency of the acquired GaN-based enhanced field effect device is good, and a reliability problem caused by current collapse is well suppressed.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

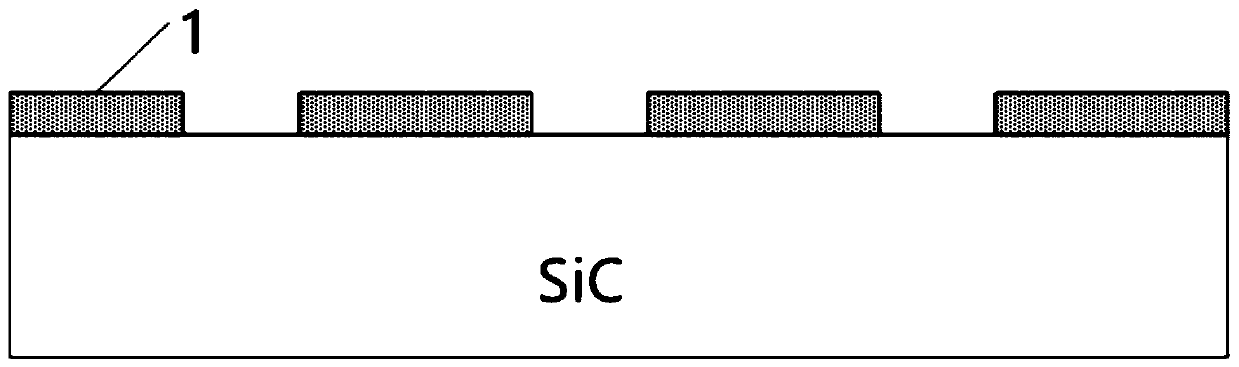

Manufacturing method of SiC power device chip gate oxide layer and power device

ActiveCN111009464AGuaranteed normal consumptionReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryEngineering

The invention discloses a manufacturing method of a SiC power device chip gate oxide layer and a power device. According to the manufacturing method of the gate oxide layer of the SiC power device chip, the number of introduced elements can be accurately controlled through multiple times of injection, a defect elimination effect is guaranteed, and gate reliability reduction caused by introductionof excessive P / B elements is avoided. And element distribution is optimized through multiple times of injection so that a P injection layer is completely consumed in a thermal oxidation process. An injection region is defined through photoetching before thermal oxidation, a P / B injection region is formed on a surface of an SIC, P and N elements jointly form an interface trap, an interface state isreduced, two elements are introduced without NO atmosphere annealing, the interface state is compositely reduced, the reliability of a gate is improved, and manufacturing cost of the device is reduced.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

Germanium-base substrate surface passivation method

ActiveCN102903625ALower interface stateReduce the chance of spreadingSemiconductor/solid-state device manufacturingInterface layerDangling bond

The invention discloses a germanium-base substrate surface passivation method, which comprises the following steps of: cleaning a surface of a germanium-base substrate; putting the cleaned germanium-base substrate into a plasma cavity; utilizing reaction gas corresponding to multiply-bound atoms to generate a plasma; carrying out plasma bath processing on the surface of the germanium-base substrate; and applying a guiding electric field in a plasma bath processing process to guide the plasma to drift to the surface of the germanium-base substrate. Due to the processing, covalently joint of activated the multiply-bound atoms and germanium surface atoms is formed, but an interface layer containing germanium compounds is not generated, so that a surface dangling bond is passivated, the probability that the germanium surface atoms are separated from the surface of the germanium-base substrate to be dispersed is reduced, and simultaneously, the phenomenon that the thinning of the EOT is unfavorable as the interface layer is introduced is avoided. In addition, the guiding electric filed is applied, so that the formation of germanium oxides can be effectively suppressed, the passivation efficiency is improved, and the density of interfacial states is reduced.

Owner:PEKING UNIV

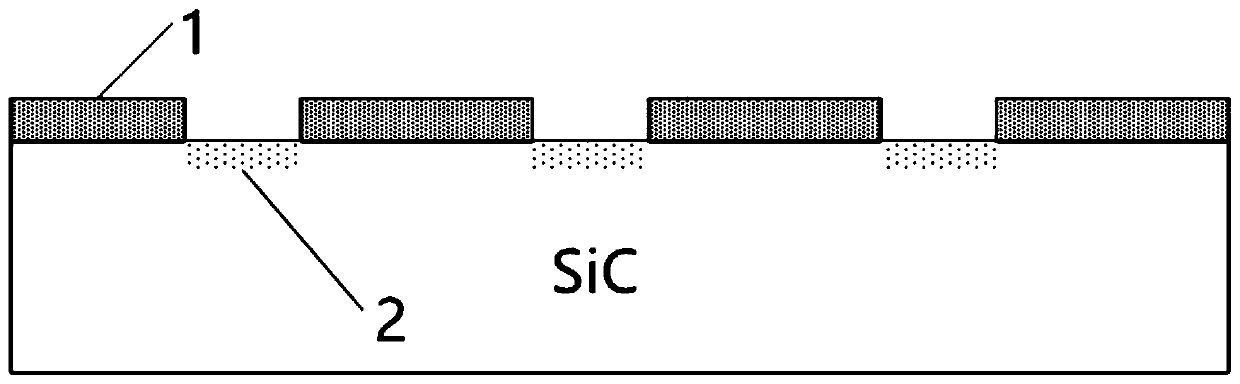

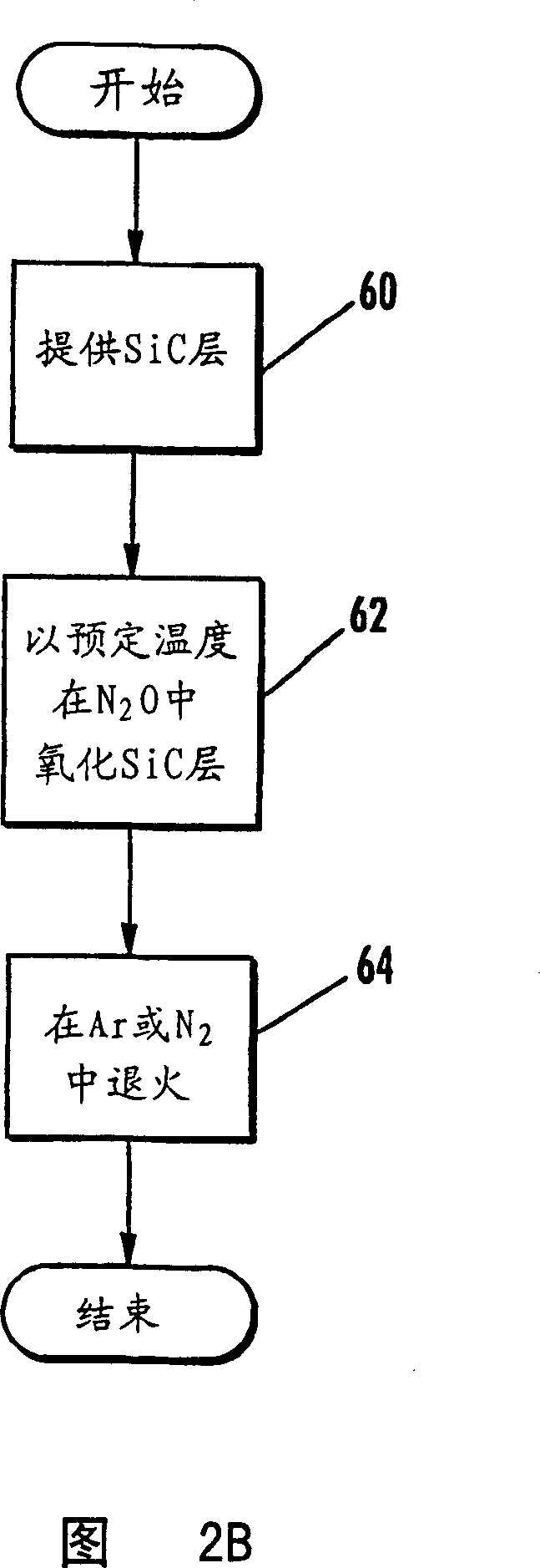

Method of fabricating an oxide layer on a silicon carbide layer utilizing NO2

InactiveCN1311534CLower interface stateSolid-state devicesSemiconductor/solid-state device manufacturingConduction bandSuboxide

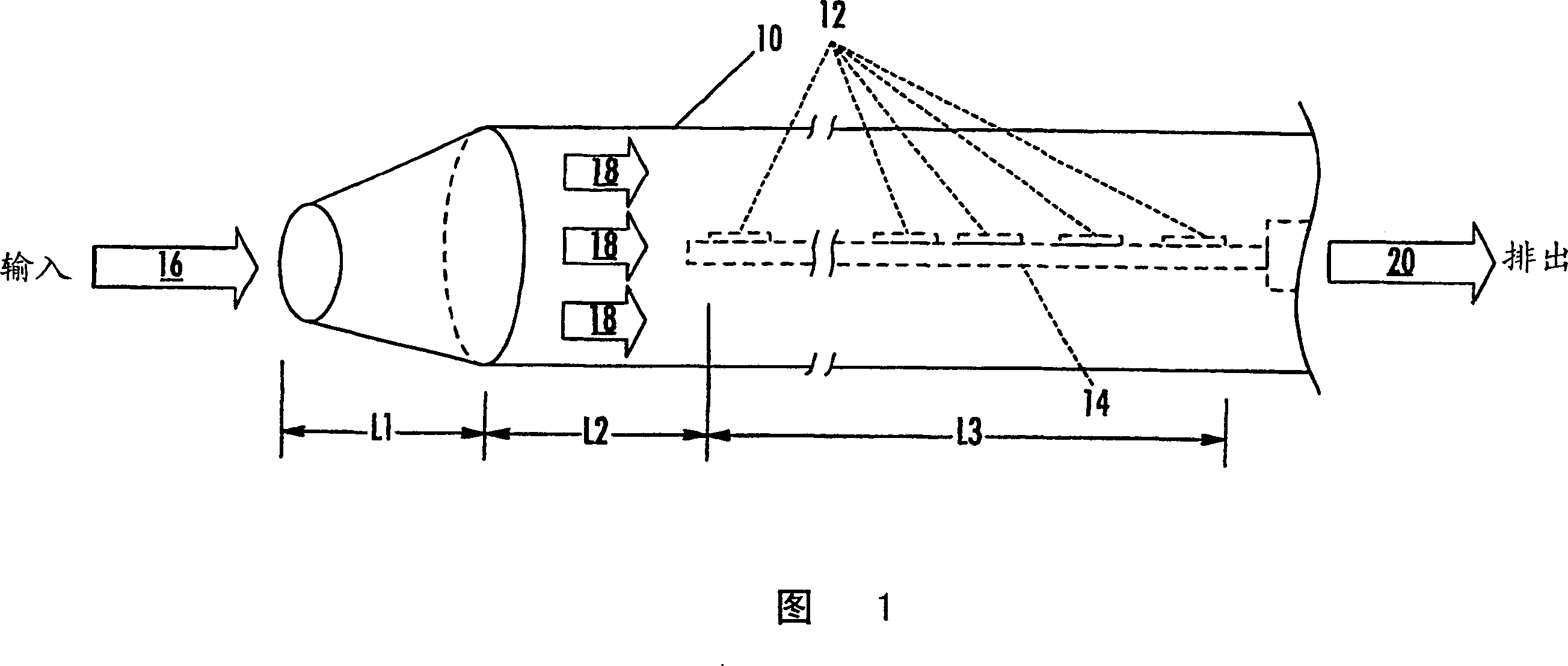

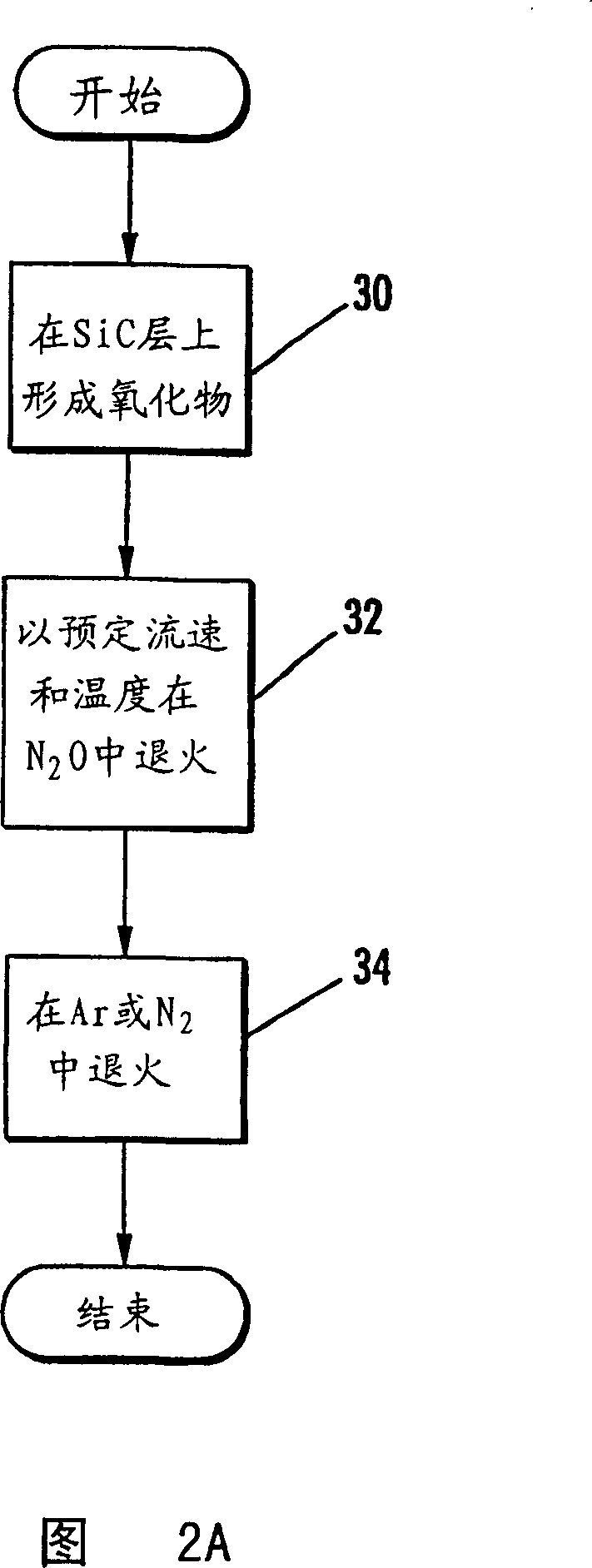

Methods for fabricating a layer of oxide on a silicon carbide layer are provided by forming the oxide layer by at least one of oxidizing the silicon carbide layer in an N2O environment or annealing an oxide layer on the silicon carbide layer in an N2O environment. Preferably, a predetermined temperature profile and a predetermined flow rate profile of N2O are providing during the oxidation or the anneal. The predetermined temperature profile and / or predetermined flow rate profile may be constant or variable and may include ramps to steady state conditions. The predetermined temperature profile and / or the predetermined flow rate profile are selected so as to reduce interface states of the oxide / silicon carbide interface with energies near the conduction band of SiC.

Owner:CREE INC

High speed deposition micro crystal silicon solar battery P/I interface processing method

InactiveCN100487926CReduce the density of defect statesLow glow power and small defect state densityFinal product manufactureSemiconductor devicesSolar batteryMicrocrystalline silicon

The invention discloses a high-speed deposition method on a P / I interface of a microcrystal silicon solar battery, which comprises controlling glowing power and silicane concentration by ultra-high frequency plasma enhanced chemical vapor deposition method and depositing a first intrinsic microcrystal silicon film layer on a P player with a first deposition rate; adjusting glowing power and silicane concentration without extinguishment of plasma glow and growing a second intrinsic microcrystal silicon film layer on the first intrinsic microcrystal silicon film layer with a second deposition rate, wherein the first deposition rate is smaller than the second deposition rate. The invention uses lower glower power and lower silicane concentration to depose on P layer with smaller deposition rate to obtain high crystallized intrinsic microcrystal silicon film layer with low defect, so as to improve battery efficiency.

Owner:NANKAI UNIV

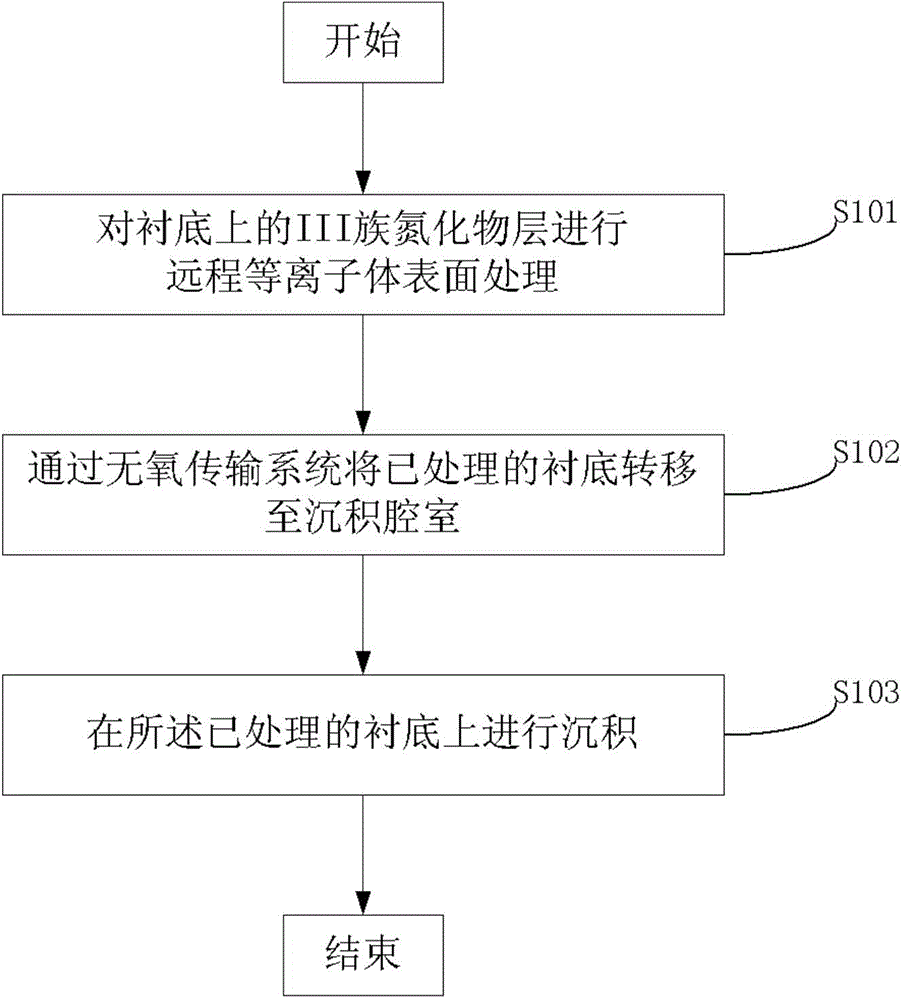

Low-interface-state device and manufacture method thereof

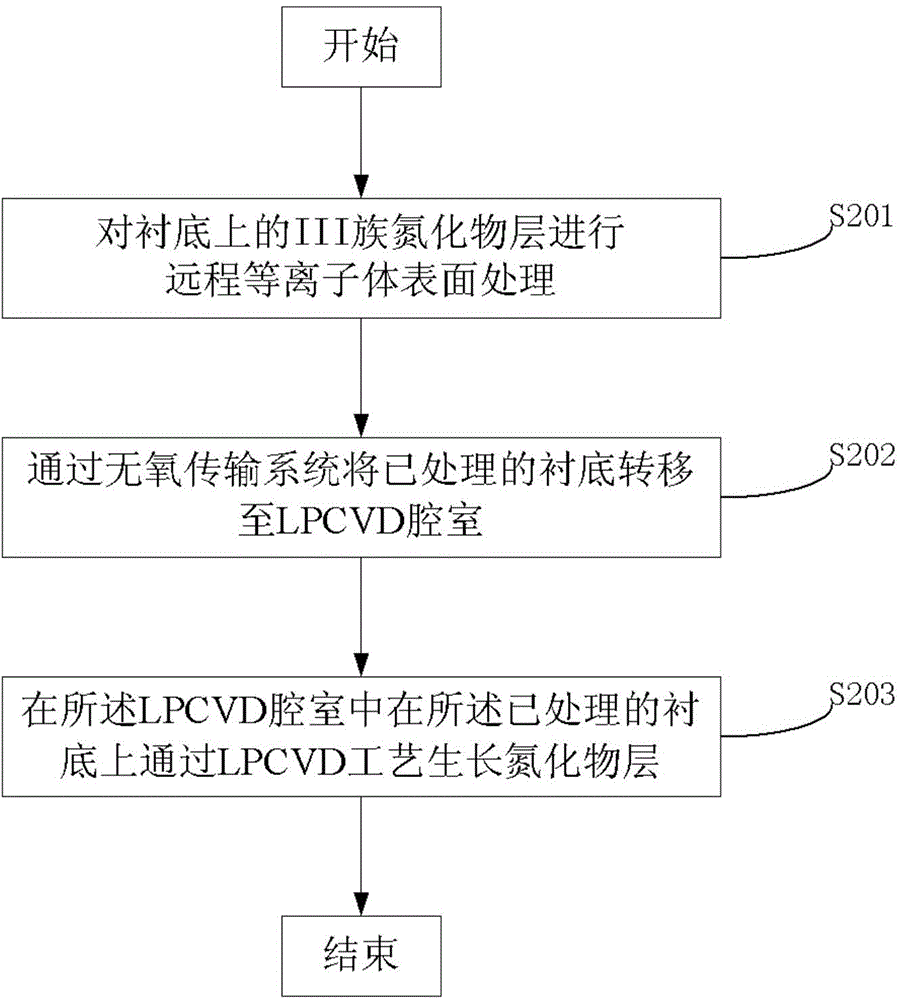

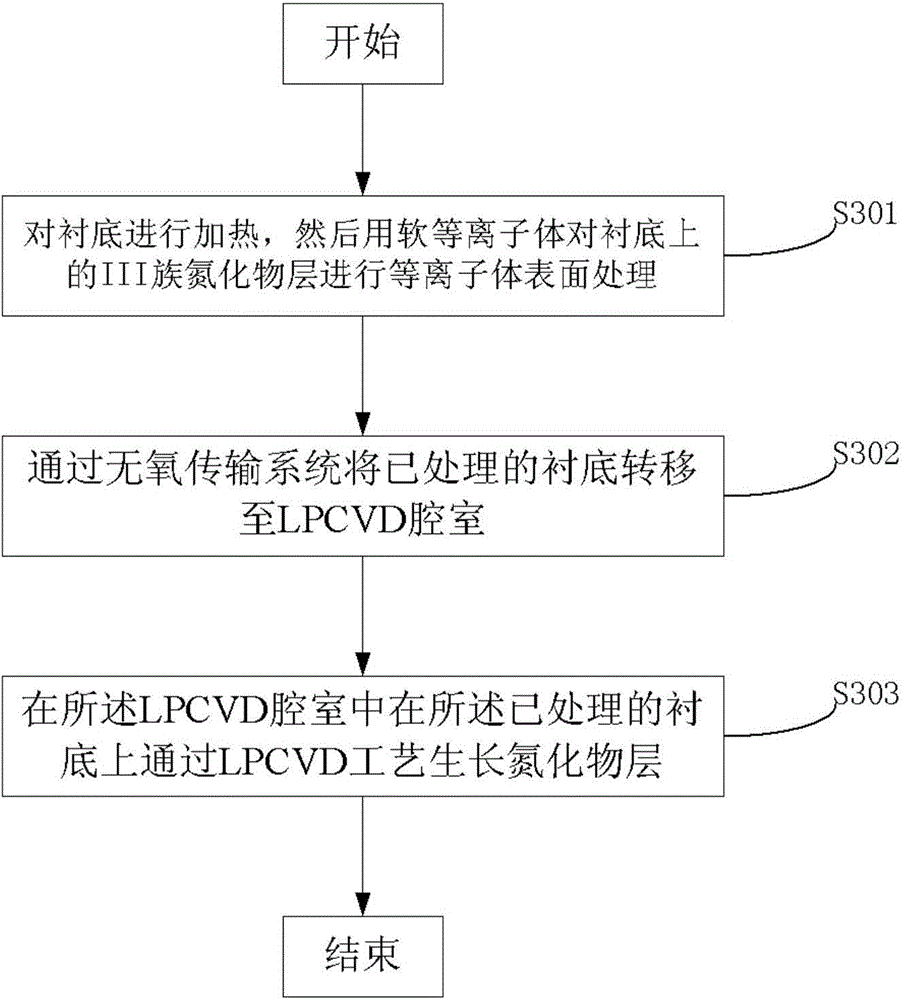

InactiveCN104658894ASurfactantLower interface stateSemiconductor/solid-state device manufacturingChemical vapor deposition coatingTransmission systemRemote plasma

The invention discloses a manufacture method of a low-interface-state device. The manufacture method comprises the following steps: carrying out remote plasma surface treatment on group III nitride layers on a pair of substrates; transferring the treated substrates to a deposition chamber via an anaerobic transmission system; and depositing on the treated substrates in the deposition chamber. The deposition can be low-pressure chemical vapor deposition (LPCVD). The interface state between a surface medium and a group III nitride material can be obviously reduced by integrating low-damage remote plasma surface treatment and the LPCVD technique.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

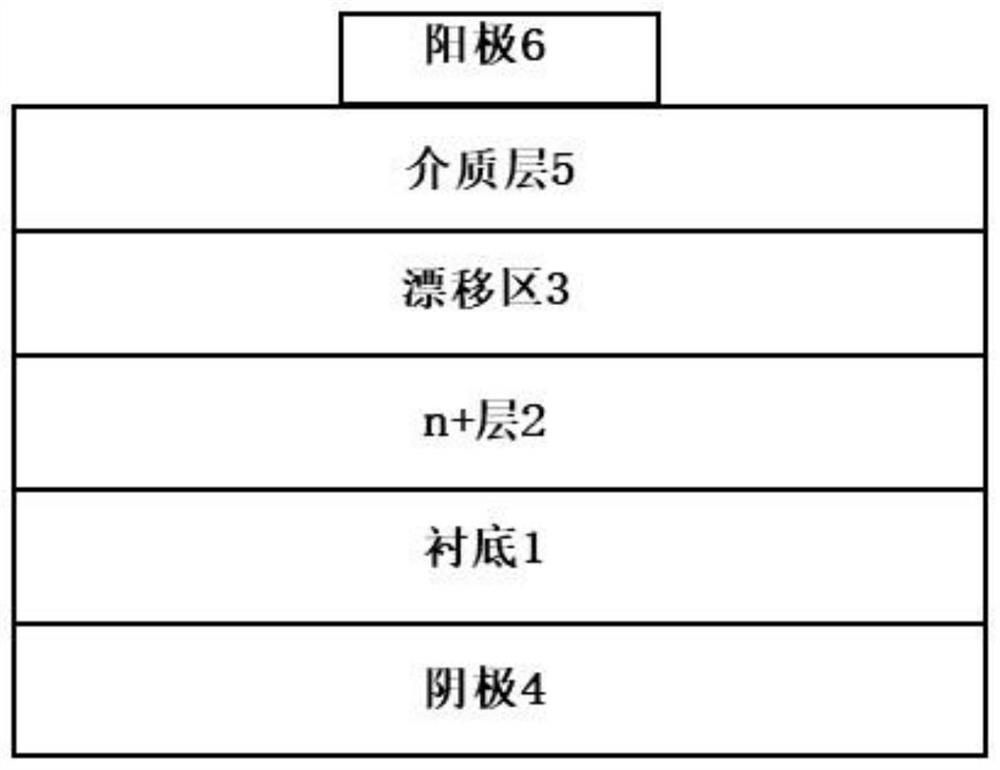

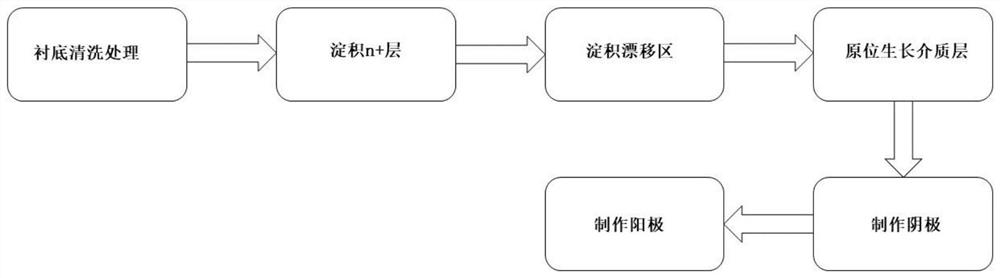

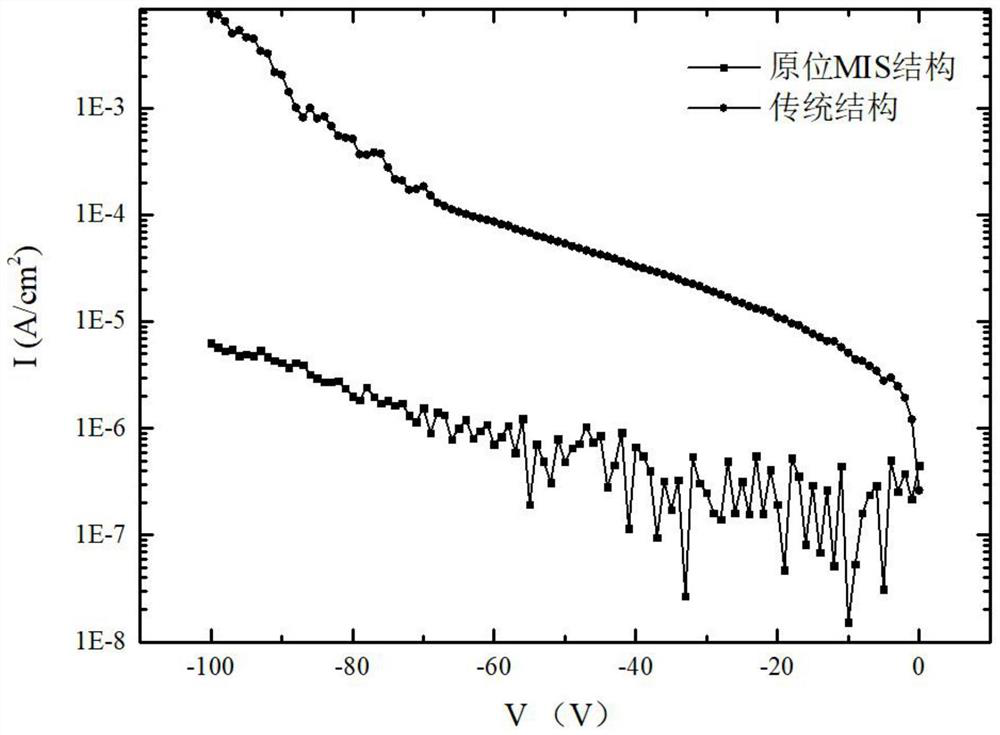

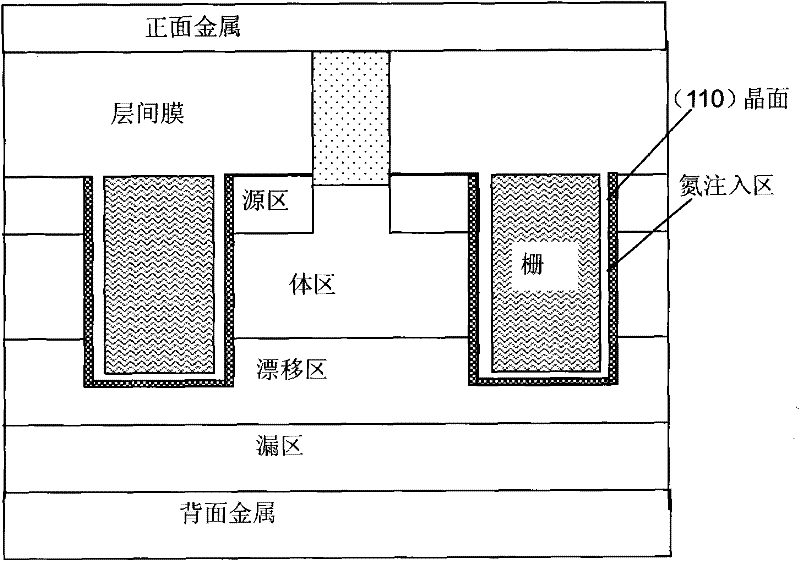

Vertical GaN Schottky diode based on in-situ growth MIS structure and preparation method thereof

ActiveCN113540208ASuppresses reverse leakageLower interface stateSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky diodeDielectric layer

The invention discloses a vertical GaN Schottky diode based on an in-situ growth MIS structure, which comprises a substrate and is characterized in that the bottom of the substrate is provided with a cathode, the top of the substrate is sequentially provided with an n + layer and a drift region from bottom to top, the top of the drift region is provided with an in-situ growth dielectric layer, and the top of the dielectric layer is provided with an anode. The invention also provides a preparation method of the diode, and the method comprises the following steps: S1, providing a substrate, carrying out the pretreatment and heat treatment of the substrate, and depositing an n+ layer on the substrate; S2, depositing a drift region with a thickness of 1-10 [mu]m on the n + layer; S3, directly growing a dielectric layer on the GaN drift region in situ; S4, depositing cathode metal at the bottom of the substrate; and S5, manufacturing a mask on the dielectric layer, and depositing anode metal on the dielectric layer to obtain the Schottky diode. The diode provided by the invention is high in interface quality and beneficial to long-term reliability.

Owner:XIDIAN UNIV

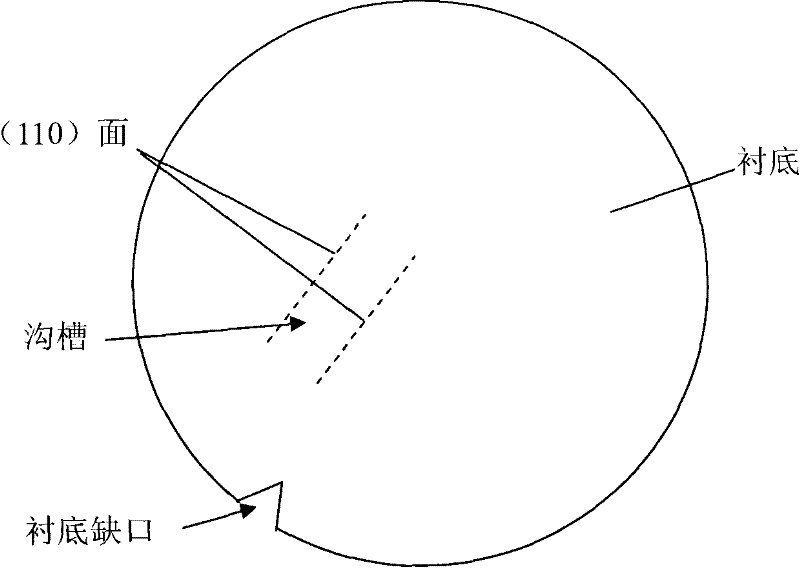

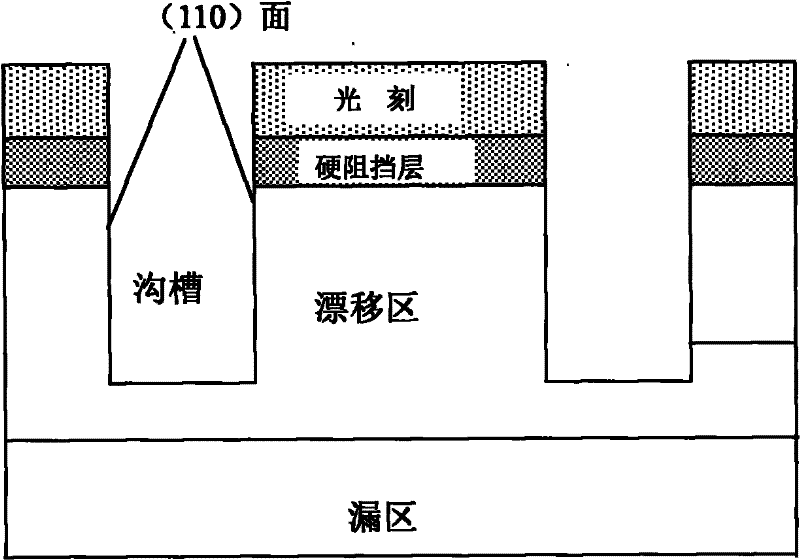

Preparation method of trench PMOS (positive-channel metal oxide semiconductor) enabling side wall of trench to be (110) surface

InactiveCN102130005ASmall sizeLower interface stateSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorIon

The invention discloses a preparation method of a trench PMOS (positive-channel metal oxide semiconductor) enabling the side wall of a trench to be the (110) surface, which comprises the following steps: enabling the side wall surface of the trench after etching to be the (110) crystal surface when defining a trench pattern on a substrate through the photoetching process; injecting nitrogen ions into the inner wall of the trench after forming the trench by etching; and then growing a gate oxide on the inner wall of the trench. By adopting the method, the threshold voltage of the PMOS device can be effectively reduced to achieve the application requirement.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

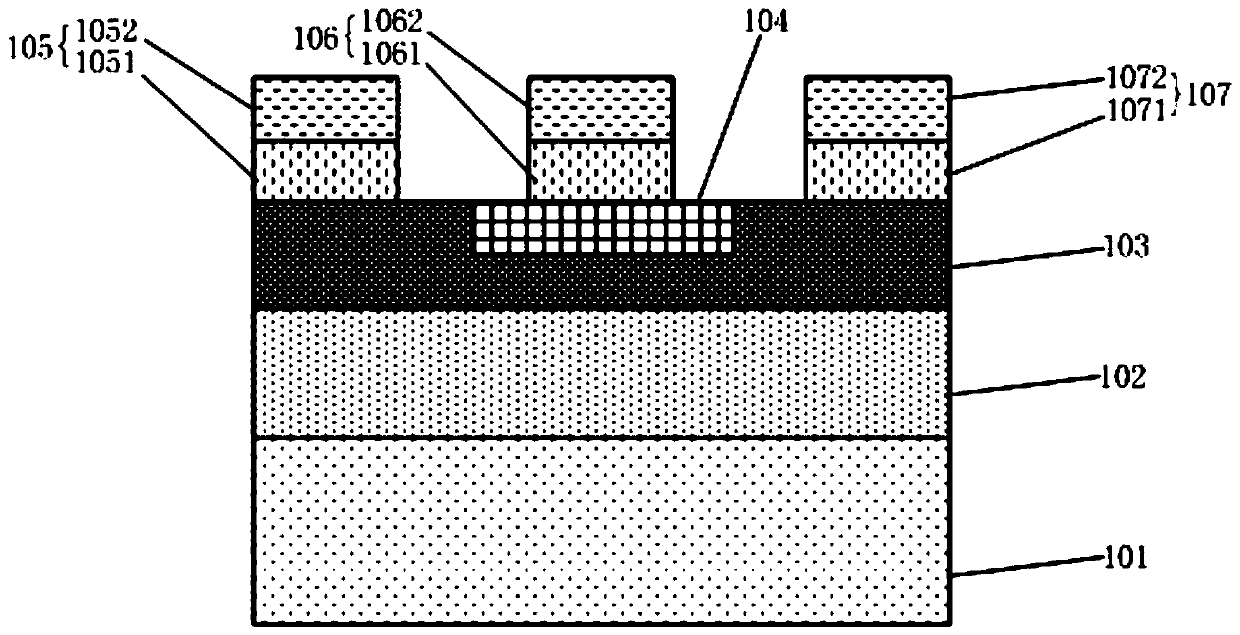

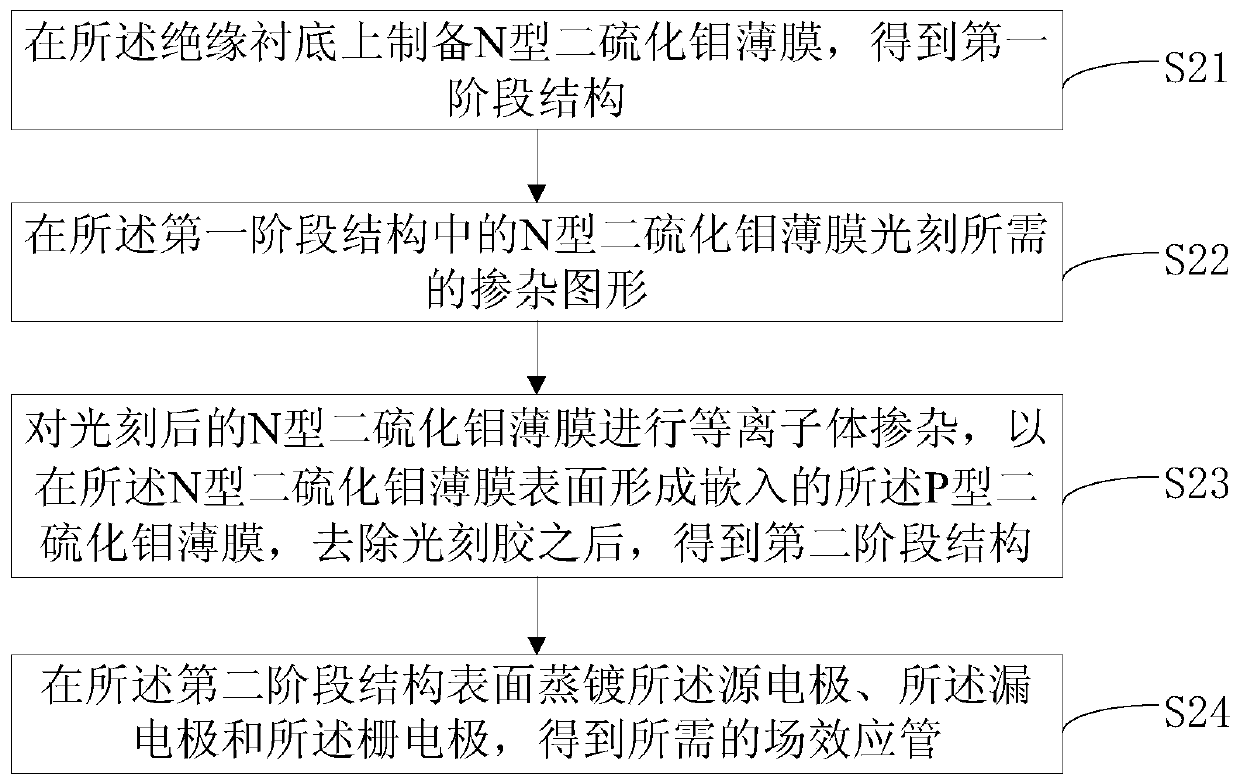

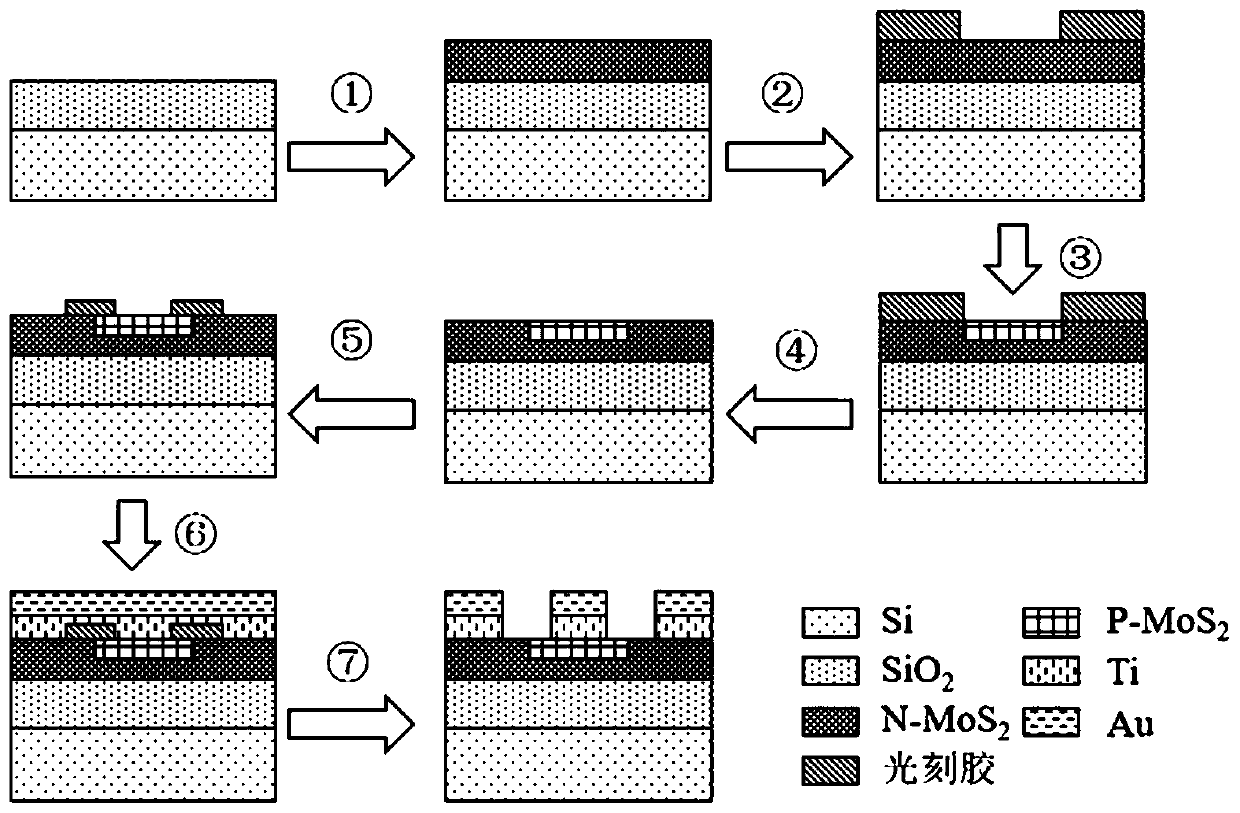

MoS2-based homojunction field effect transistor and preparation method thereof

ActiveCN111463290AImprove mobilityLower interface stateSemiconductor/solid-state device manufacturingSemiconductor devicesThin membraneEngineering

The invention provides a MoS2-based homojunction field effect transistor and a preparation method thereof, the MoS2-based homojunction field effect transistor comprises a silicon substrate, an N-typemolybdenum disulfide thin film, a P-type molybdenum disulfide thin film, a source electrode, a drain electrode and a gate electrode; the N-type molybdenum disulfide thin film is arranged on one side of the silicon substrate, and the P-type molybdenum disulfide thin film is embedded into the surface of the side, opposite to the silicon substrate, of the N-type molybdenum disulfide thin film; the gate electrode is arranged on the surface of the side, opposite to the silicon substrate, of the P-type molybdenum disulfide thin film, the source electrode and the drain electrode are arranged on the surface of the side, opposite to the silicon substrate, of the N-type molybdenum disulfide thin film, and the gate electrode is located between the source electrode and the drain electrode.

Owner:HUAZHONG UNIV OF SCI & TECH

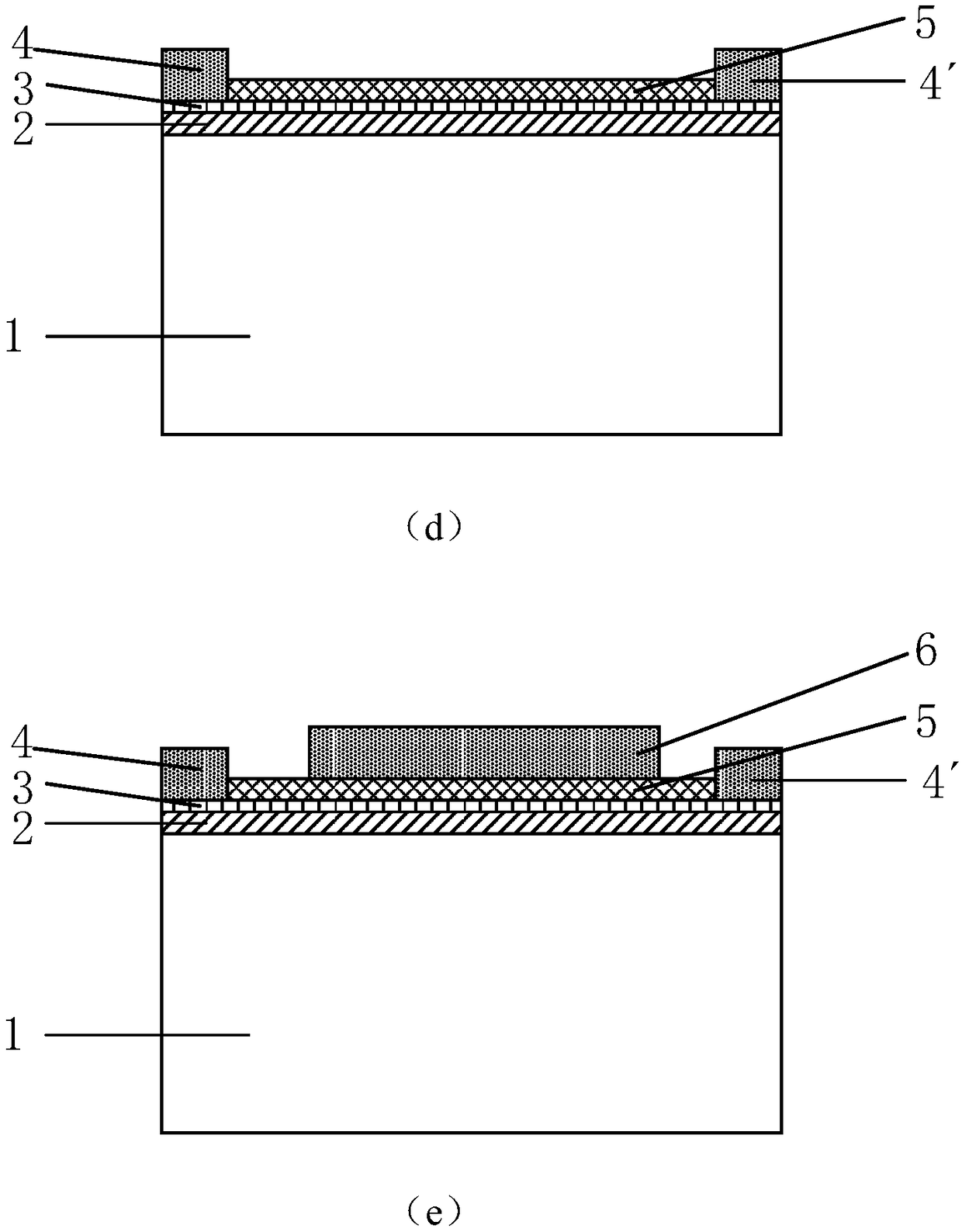

Regrowth method for reducing interface state of HEMT device by utilizing InN protection layer and HEMT device

ActiveCN110620042AImprove interface qualityImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesState densityEngineering

The invention discloses a regrowth method for reducing an interface state of an HEMT device by utilizing an InN protection layer. After the AlGaN / GaN HEMT structure is grown, an InN protection layer is formed through in-situ epitaxy, when a p-GaN gate structure is regrown by adopting MOCVD, the InN protective layer is evaporated at a high temperature in a growth system, and then the p-GaN layer isextended, so C and O impurity pollution caused by exposure of AlGaN in the air is avoided, and the interface state density of p-GaN / AlGaN can be effectively reduced. When the HEMT device is preparedby the method, the p-GaN layer does not need to be etched, so high source-drain contact resistance or interface damage caused by the fact that the etching depth of the p-GaN layer cannot be accuratelycontrolled in a source-drain region in a traditional method is avoided.

Owner:NANJING UNIV

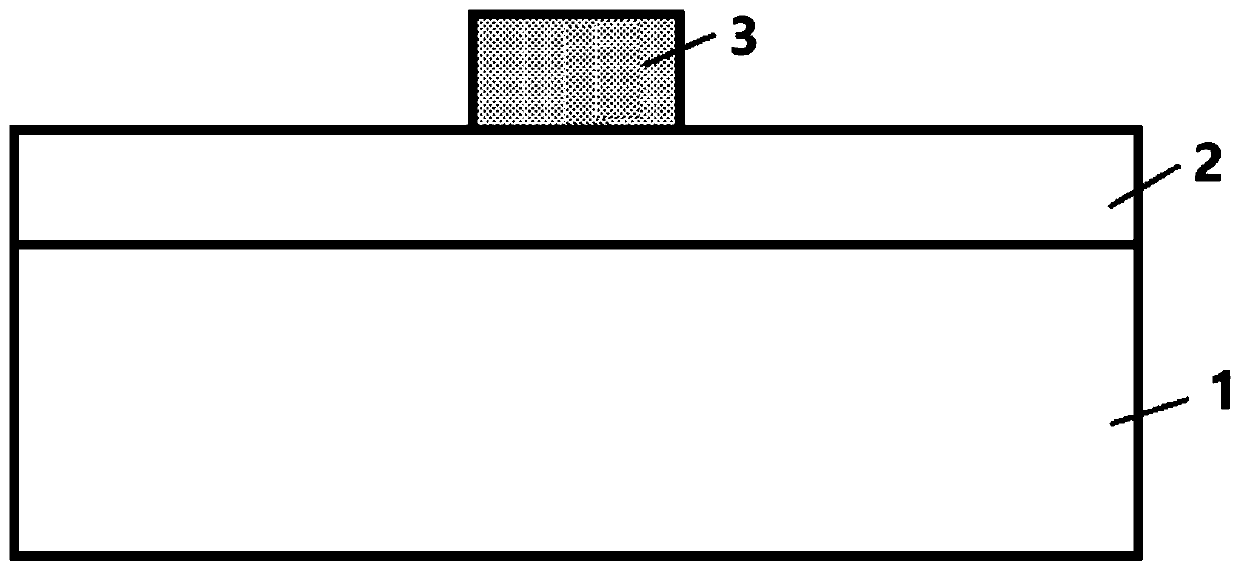

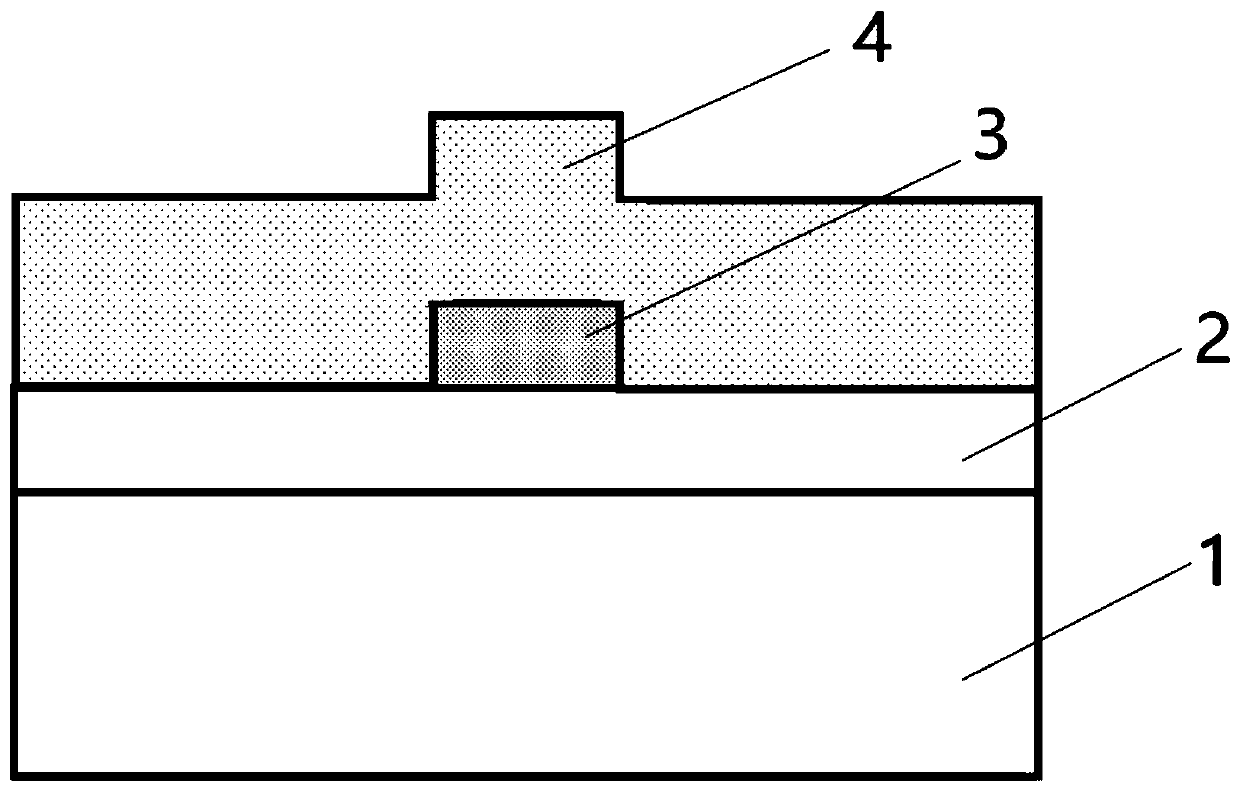

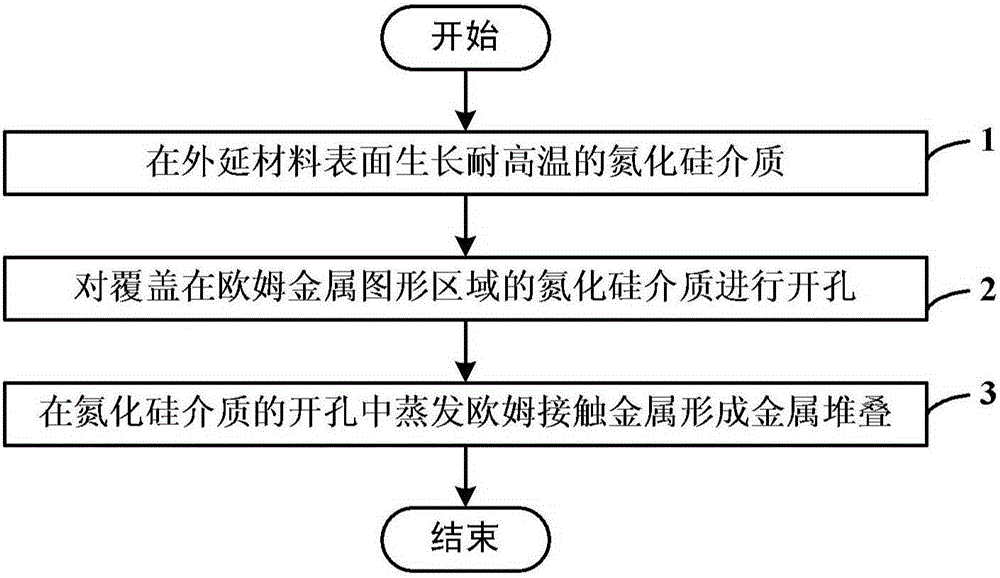

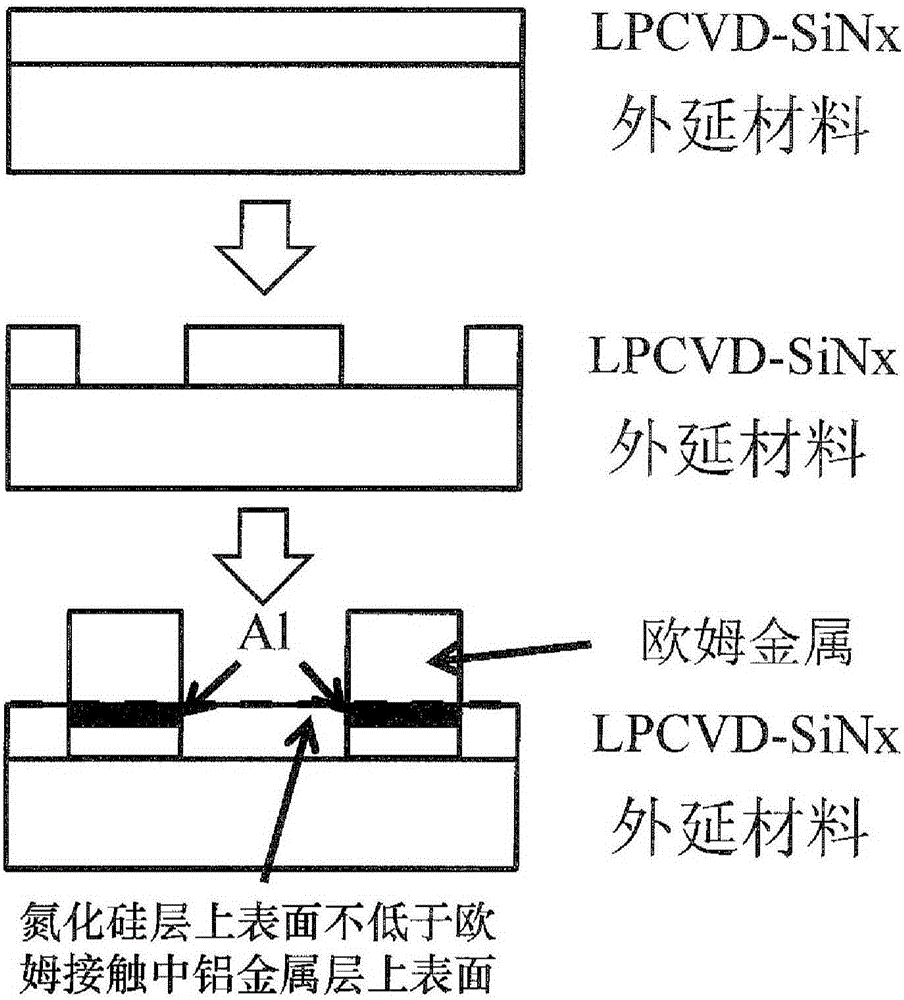

Method for preventing transverse diffusion of ohmic contact aluminum in GaN-based device

InactiveCN105206524ASolve the problem of horizontal diffusionAvoid the risk of contamination deteriorating device performanceSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactEpitaxial material

The invention discloses a method for preventing transverse diffusion of ohmic contact aluminum in a GaN-based device. Ohmic contact aluminum is deposited in pores of a heat-resisting silicon nitride medium, transverse diffusion of ohmic contact aluminum is blocked by the heat-resisting silicon nitride medium, surface protection for ohmic alloy is further realized, and interface pollution and interface state are reduced. The method comprises: the heat-resisting silicon nitride medium grows on the surface of an epitaxial material; pores are formed in the high-temperature silicon nitride medium covering the area of an ohmic contact metal pattern; ohmic contact metal is evaporated in the formed pores of the silicon nitride medium to form metal stacking, wherein the upper surface of the silicon nitride medium is not lower than the upper surface of a stacked metal aluminum layer in the area of the formed pores. The method solves the problem of aluminum transverse diffusion in ohmic contact preparation of the GaN-based device, avoids the risk that the device performance is degraded due to a polluted material surface in a high-temperature alloy technology, further realizes surface protection of ohmic alloy, and reduces interface pollution and interface state.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

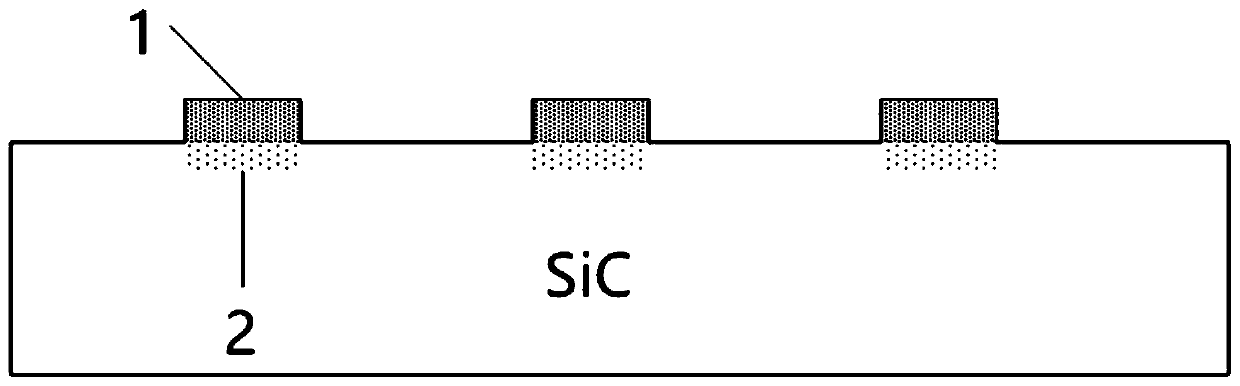

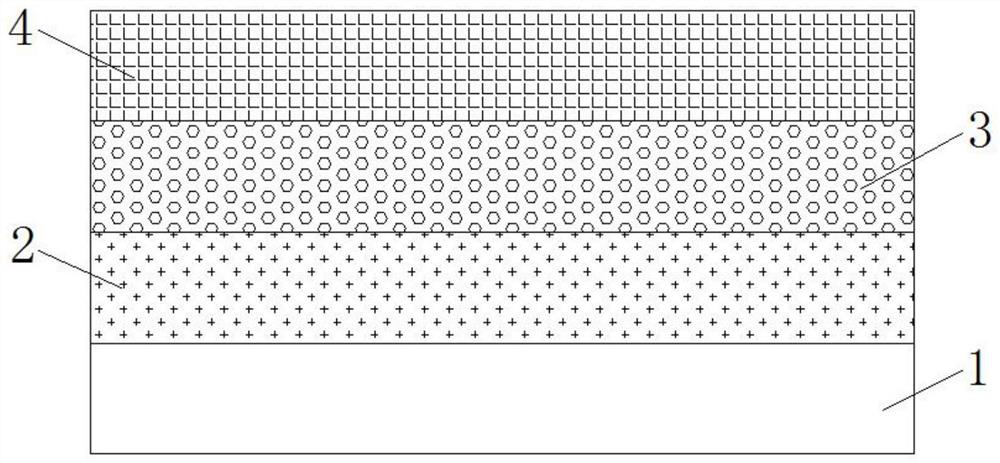

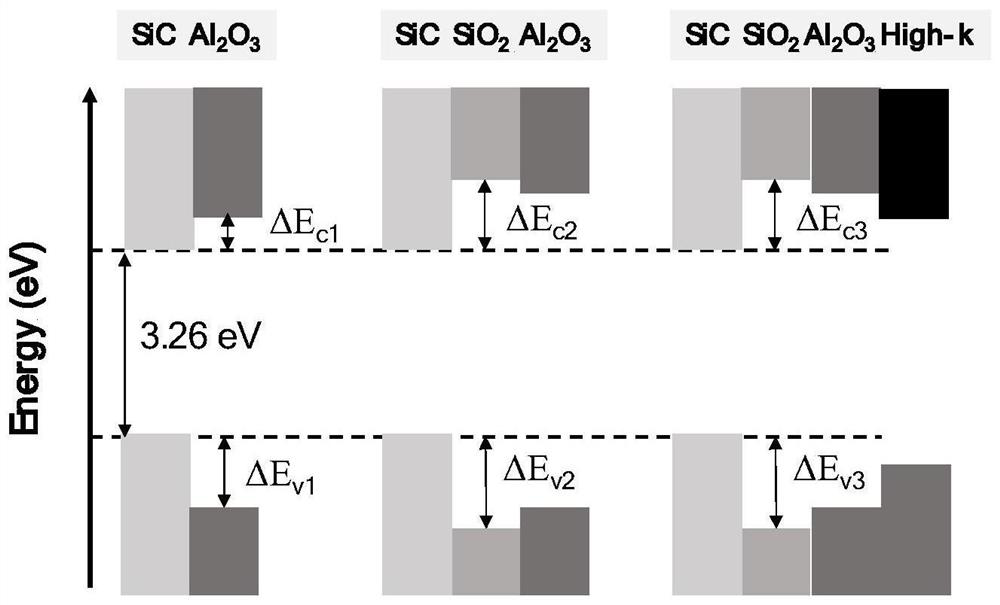

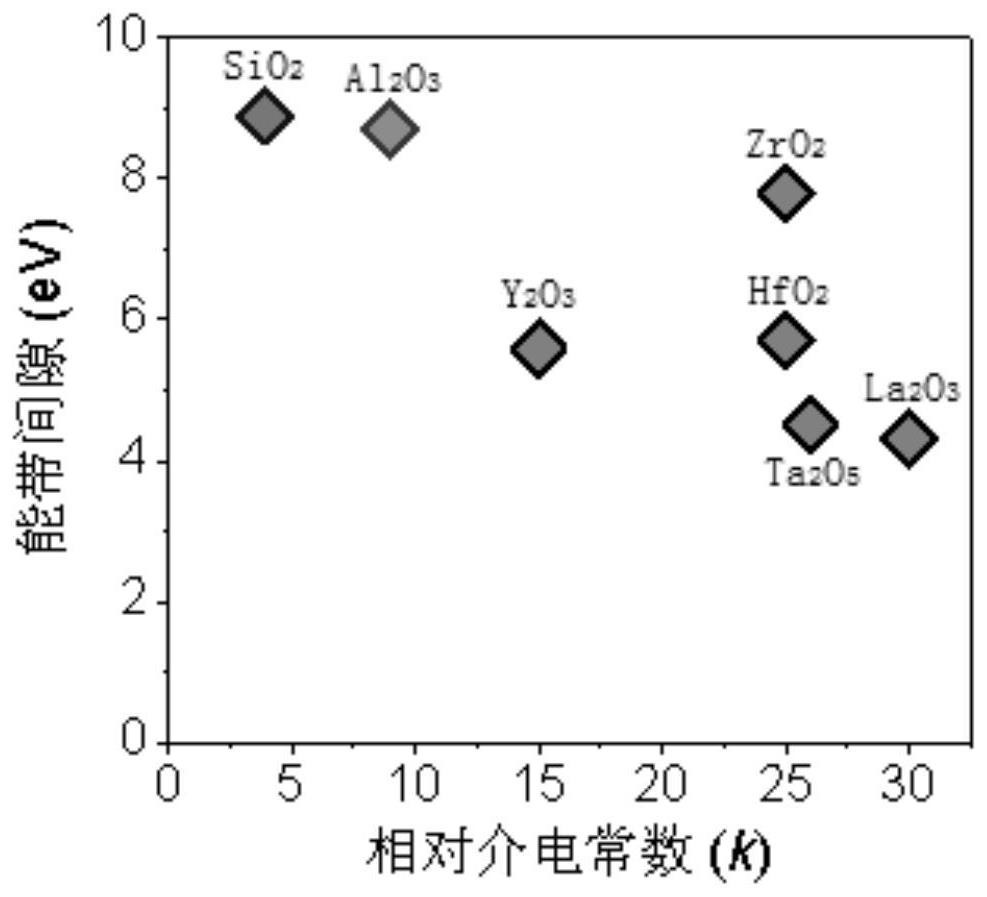

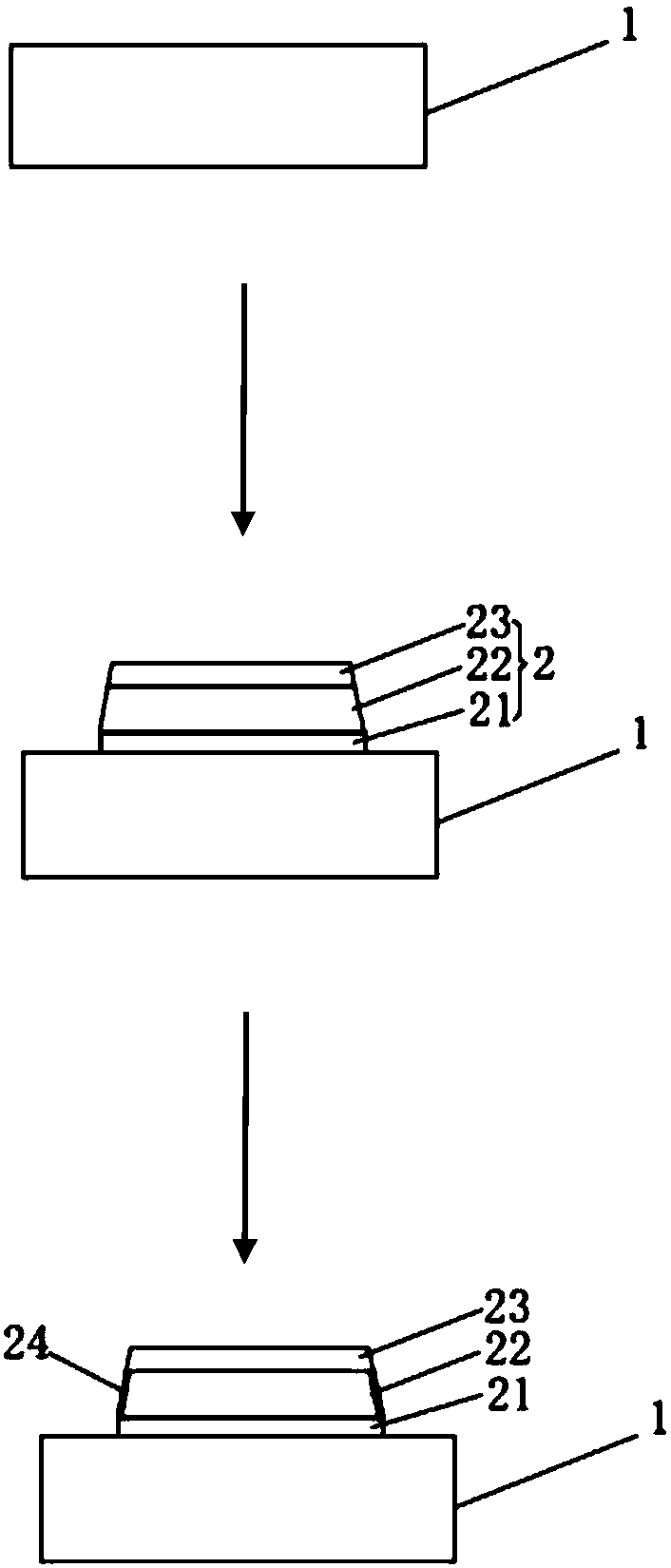

Gate oxide structure and preparation method

PendingCN114300533ALower interface stateImprove reliabilityVacuum evaporation coatingSputtering coatingDielectricPhysical chemistry

The invention relates to a gate oxide structure and a preparation method in the technical field of semiconductors, the gate oxide structure comprises a SiC substrate layer, an oxide layer, an Al2O3 layer and a high dielectric material layer, the oxide layer is arranged on the SiC substrate layer of the gate oxide structure and the preparation method, the Al2O3 layer is arranged on the oxide layer of the gate oxide structure and the preparation method, and the high dielectric material layer is arranged on the high dielectric material layer. According to the gate-oxide structure and the preparation method, the high-dielectric material layer is arranged on one side, far away from the oxide layer, of the Al2O3 layer, so that the gate-oxide structure has the advantages of high channel mobility and small gate energy loss, and breaks through the bottleneck that the gate of the traditional gate-oxide structure is easy to leak current.

Owner:ZHEJIANG UNIV HANGZHOU GLOBAL SCI & TECH INNOVATION CENT

Ohmic contact structure of nitride semiconductor device and manufacturing method thereof

InactiveCN108447780AFacilitate horizontal diffusionReduce pollutionSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactSuperalloy

The present invention discloses a manufacturing method of an Ohmic contact structure of a nitride semiconductor device. The method comprises the steps of: forming a metal stacked structure including an Al layer on a GaN substrate, performing low-temperature oxidation in an oxygen atmosphere to form an aluminum oxide barrier layer at the side wall of the Al layer, and forming Ohmic contact of the metal stacked structure and the GaN substrate through high-temperature alloy. The low-temperature oxidation processing is performed prior to Ohmic contact alloy to allow the outer side of the Ohmic metal to be oxidized to aluminum oxide so as to reduce the interface pollution or improve an interface state; and moreover, the method increases low-temperature oxidation in a traditional GaN device Ohmic metal manufacturing process, is simple in process with no need for introducing other substances and other materials, and is high in practicability and good in effect.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

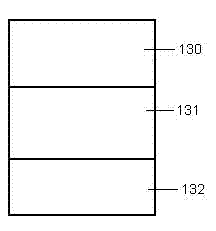

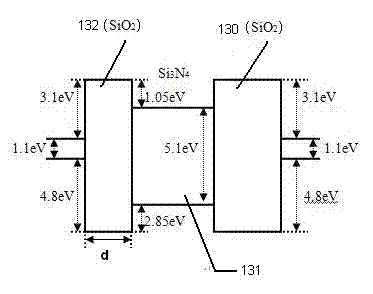

TN (tunnel nitrate)-SONOS (silicon oxide nitrate oxide silicon) memory with composite nitrogen-based dielectric tunneling layer

InactiveCN102820301AImprove retention propertiesImproved retention properties; simultaneously lower barrier heightSolid-state devicesSemiconductor devicesDielectricTrapping

The invention relates to the field of semiconductor memories, and discloses a TN (tunnel nitrate)-SONOS (silicon oxide nitrate oxide silicon) memory with a composite nitrogen-based dielectric tunneling layer. The TN-SONOS memory comprises a semiconductor substrate, a grid electrode and a dielectric laminate; the semiconductor substrate comprises a channel, a source terminal and a drain terminal, and the source terminal and the drain terminal are adjacent to the channel; the dielectric laminate is arranged between the grid electrode and the surface of the channel and comprises a tunneling layer, a charge trapping layer and a stopping layer, the tunneling layer is in contact with the surface of the channel, the charge trapping layer is laminated on the upper side of the tunneling layer, and the stopping layer is laminated on the upper side of the charge trapping layer and is in contact with the grid electrode; and the tunneling layer is the composite dielectric tunneling layer and comprises a first layer consisting of silicon oxynitride SiON(x), a second layer consisting of Si3N4 and a third layer consisting of silicon oxynitride, SiON(y), the first layer is in contact with the surface of the channel, the second layer is adjacent to the first layer, and the third layer is adjacent to the second layer. By the TN-SONOS memory, the performance of a SONOS nonvolatile memory is improved, and the TN-SONOS memory can be applied to extremely small memory devices with high quality.

Owner:EAST CHINA NORMAL UNIV +1

Silicon-germanium heterojunction solar cell and preparation method thereof

ActiveCN105047748AIncrease the open circuit voltageIncrease short circuit currentFinal product manufacturePhotovoltaic energy generationHeterojunctionAluminum doped zinc oxide

The invention discloses a silicon-germanium heterojunction solar cell. The structure of the silicon-germanium heterojunction solar cell sequentially comprises a silver electrode, an aluminum-doped zinc oxide (AZO) conductive layer, n-type monocrystalline silicon, an i-type SiGe alloy buffer layer film, a p-type Ge film and a gold electrode from top to bottom. The silicon-germanium heterojunction solar cell has a broad spectrum response value of 300-1800nm. According to the cell disclosed by the invention, a SiGe alloy buffer layer is deposited between silicon and germanium, thereby being capable of effectively reducing the interface state, reducing interface recombination, and increasing open-circuit voltage of the cell. In addition, a band gap of the buffer layer changes gradually, so that sunlight can be absorbed better, and short-circuit current of the cell is increased. The invention further discloses a preparation method of the silicon-germanium heterojunction solar cell. The preparation method is safe in raw material, capable of directly applying existing equipment and relatively low in cost.

Owner:江苏润阳悦达光伏科技有限公司

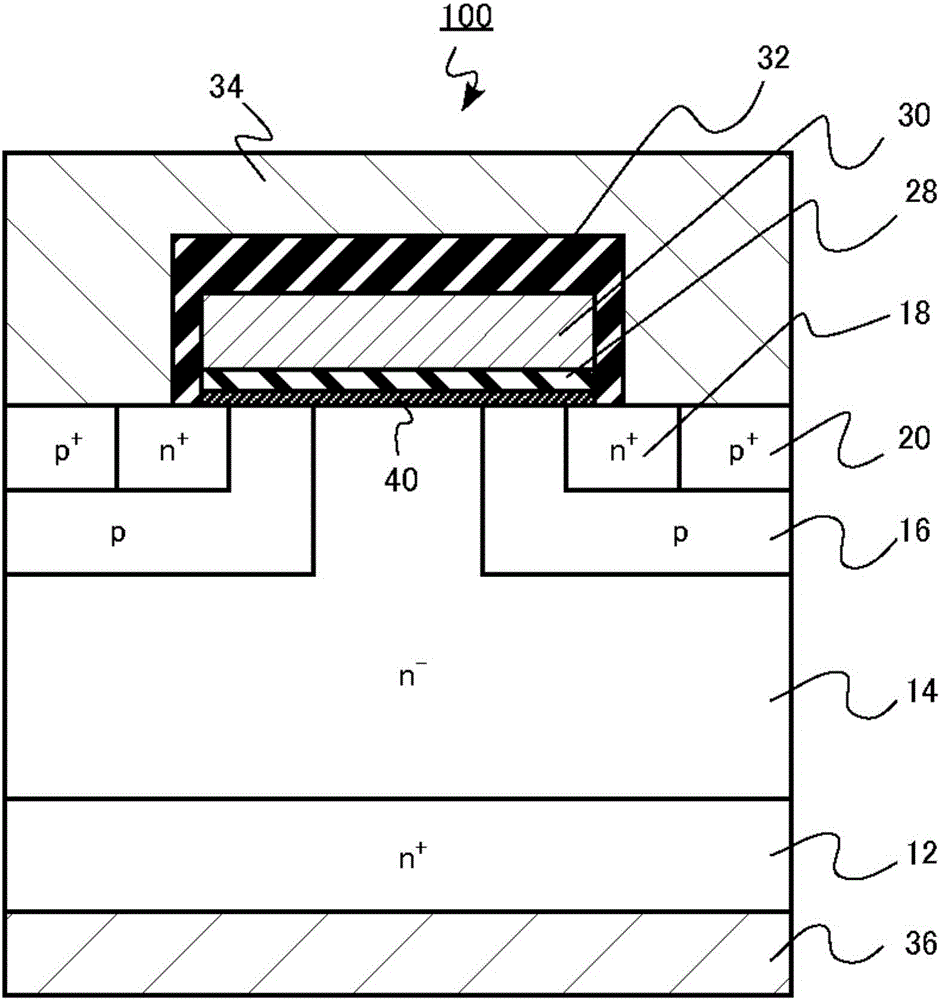

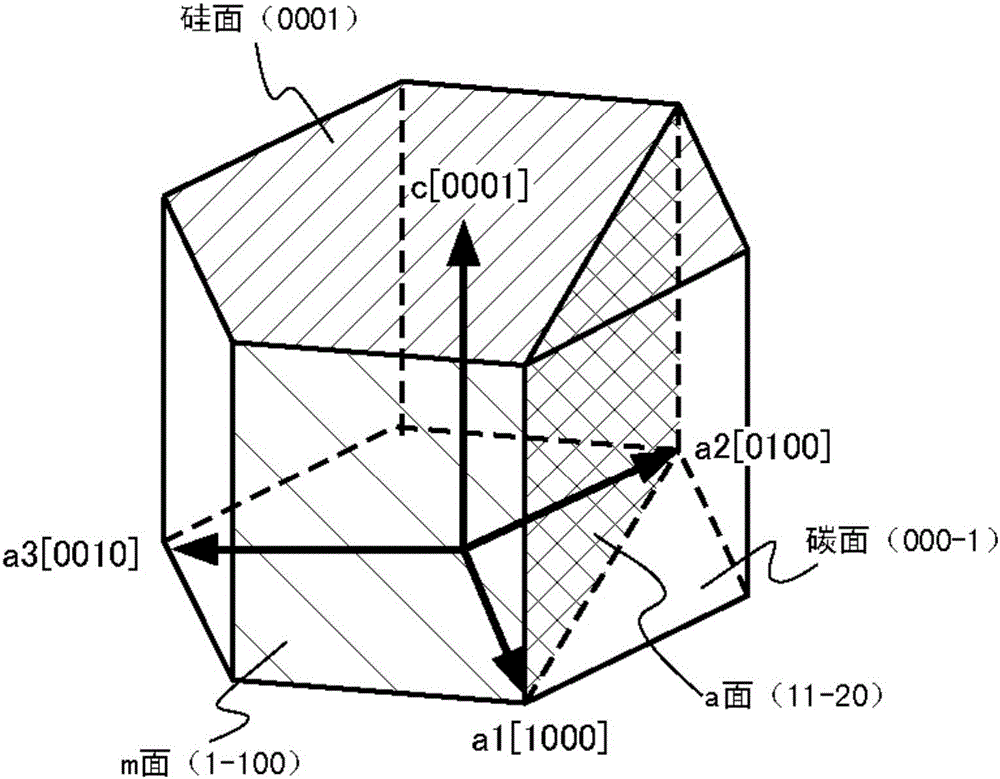

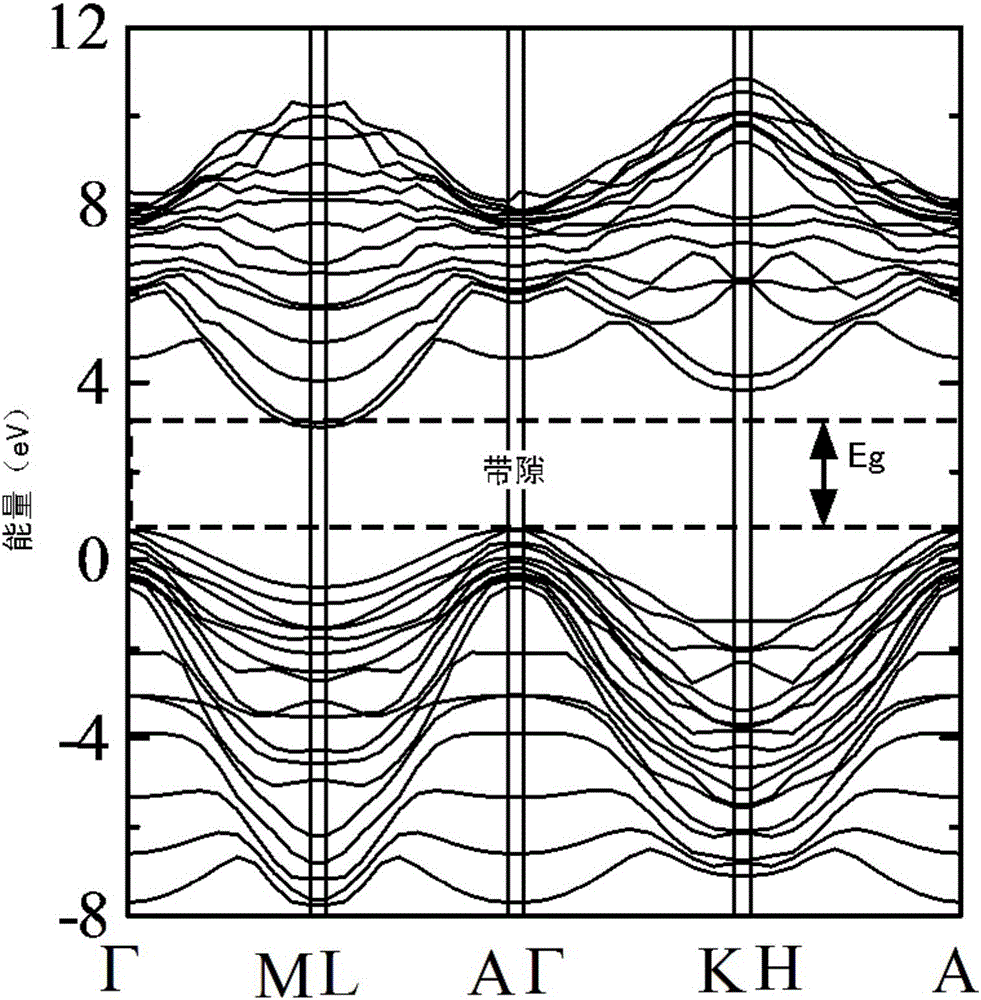

Semiconductor device, inverter circuit, driving device, vehicle, and elevator

ActiveCN106024849ALower interface stateSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialInverter

A semiconductor device according to the embodiments includes a SiC layer having a first plane, an insulating layer, and a region between the first plane and the insulating layer, the region including at least one element in the group consisting of Be (beryllium), Mg (magnesium), Ca (calcium), Sr (strontium), and Ba (barium), a full width at half maximum of a concentration peak of the element being equal to or less than 1 nm, and when a first area density being an area density of Si (silicon) and C (carbon) including a bond which does not bond with any of Si and C in the SiC layer at the first plane and a second area density being an area density of the element, the second area density being equal to or less than 1 2 of the first area density.

Owner:KK TOSHIBA

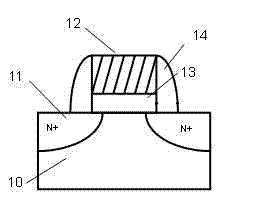

Method for realizing enhanced HEMT through p-type passivation

PendingCN113380623AAvoid damageLower interface stateSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionElectrical connection

The invention discloses a method for realizing an enhanced HEMT (High Electron Mobility Transistor) through p-type passivation, which comprises the following steps of: providing a heterostructure mainly consisting of a first semiconductor and a second semiconductor, distributing the second semiconductor on the first semiconductor and having a band gap wider than that of the first semiconductor, and forming two-dimensional electron gas in the heterostructure; forming a p-type doped third semiconductor on the second semiconductor; carrying out passivation treatment on other regions except the under-gate region in the third semiconductor, so that the p-type doped region only exists in the under-gate region, and the under-gate region is distributed right below the gate of the HEMT device; and manufacturing a source electrode, a drain electrode and a grid electrode which are connected with the heterostructure, enabling the source electrode and the drain electrode to be electrically connected through the two-dimensional electron gas, and enabling the grid electrode to be distributed between the source electrode and the drain electrode. The invention also discloses an enhanced HEMT (high electron mobility transistor). The method has the advantages of simple process, high repeatability, stable and excellent device performance, low cost, easiness in large-scale production and the like.

Owner:SUZHOU NENGWU ELECTRONICS TECH