Semiconductor structure and method of forming same

A technology of semiconductor and gate structure, applied in the field of semiconductor structure and its formation, can solve the problems of low switching rate and low operating frequency, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

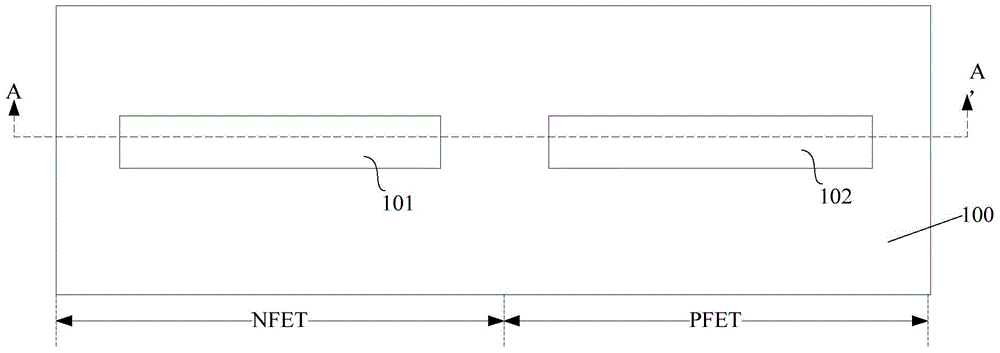

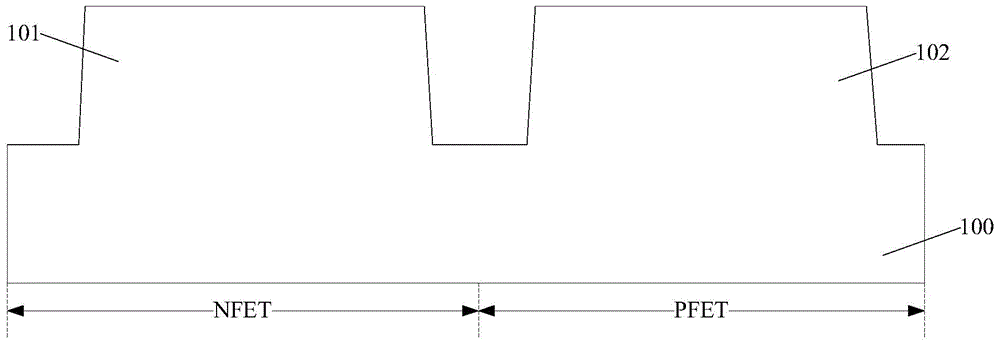

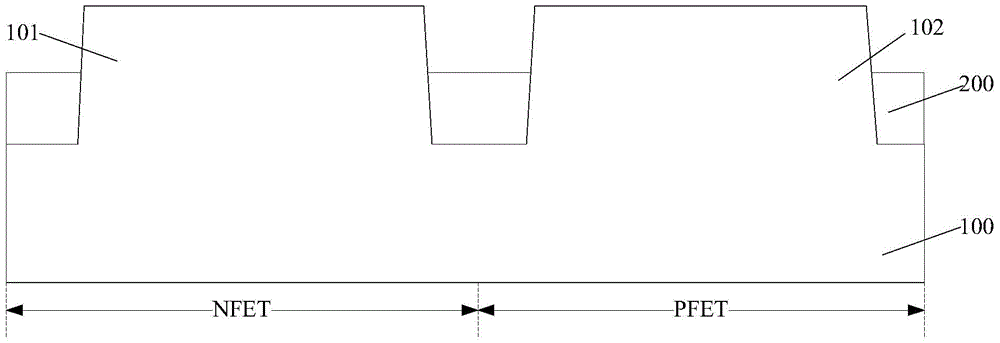

[0032] As mentioned in the background art, the performance of the N-type fin field effect transistor formed in the prior art needs to be further improved.

[0033]In the existing basic semiconductor technology, a wafer with a crystal plane of (100) is mostly used as a semiconductor substrate for forming a transistor. And the sidewall of the fin formed by etching the crystal plane of (100) is a (110) crystal plane, the effective mass of electrons on the (110) crystal plane is relatively large, and the electrons on the (110) crystal plane The mobility decreases, and there are more lattice dislocations on the (110) crystal plane, and the surface roughness is higher, which makes the interface state density on the (110) crystal plane larger, and it is easy to capture electrons, resulting in electron mobility Decrease, thereby affecting the performance of N-type fin field effect transistors.

[0034] Since the sidewall occupies a larger proportion in the channel region of the FinFE...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More