Preparation method of trench PMOS (positive-channel metal oxide semiconductor) enabling side wall of trench to be (110) surface

A trench sidewall and sidewall surface technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as high interface state density, high threshold voltage, and unsatisfactory conditions, and reduce interface state and device size. The effect of reduction and cost reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

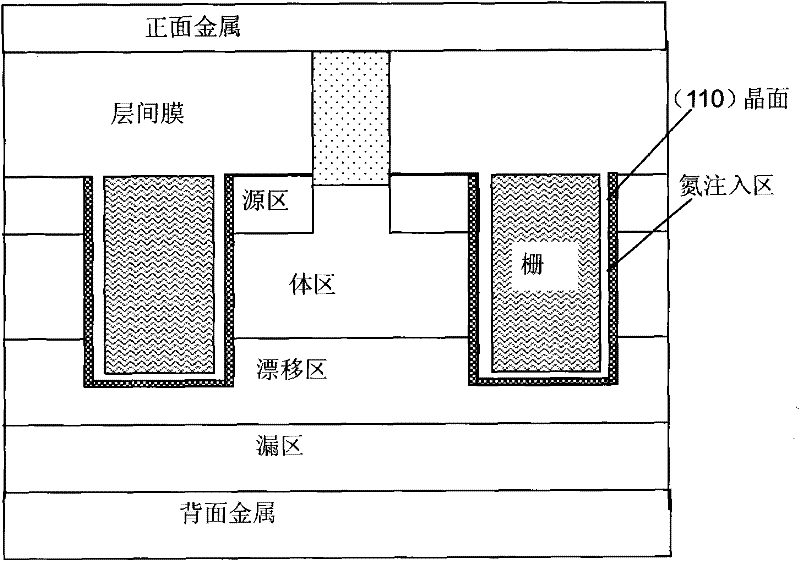

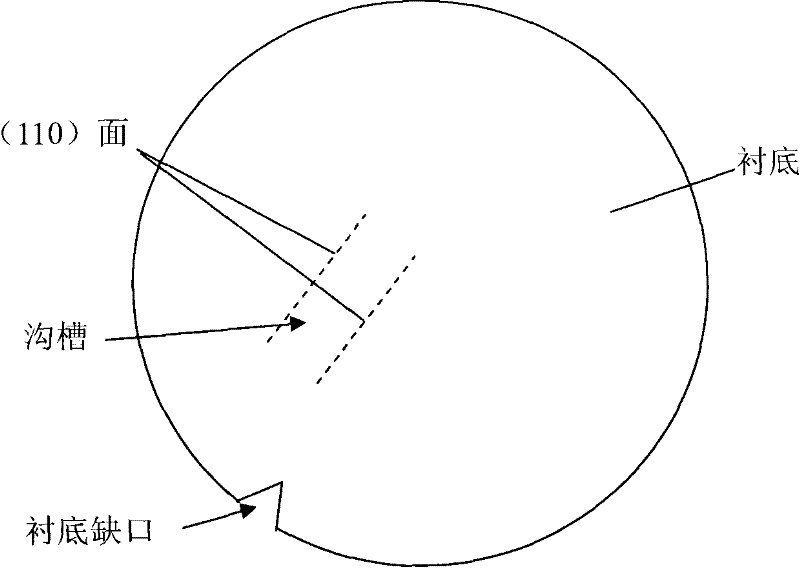

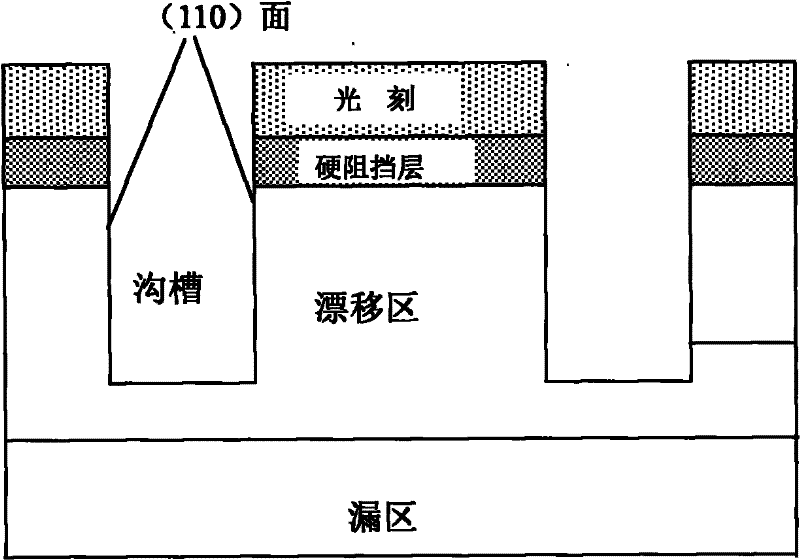

[0012] The trench sidewall of the present invention is the preparation method of the trench PMOS of (110) plane, the substrate plane used in this MOS device is (100) crystal plane, and the sidewall plane of trench is designed as (110) plane, when passing light When the etching process defines the groove pattern on the substrate, the sidewall surface of the groove after etching is made into a (110) crystal plane; after the groove is formed by etching, nitrogen ions are implanted on the inner wall of the groove; The gate oxide is grown on the inner wall of the trench. The implanted nitrogen ions greatly reduce the dangling bonds at the interface between the sidewall of the trench and the gate oxide, thereby greatly reducing the interface state, thus reducing the threshold voltage and being easy to be precisely controlled. The mobility of the PMOS majority carrier holes along the (110) crystal plane is much higher than that along the 110) crystal plane, so that the PMOS with (110...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More