Manufacturing method of SiC power device chip gate oxide layer and power device

A manufacturing method and technology for power devices, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems affecting device reliability, reducing interface state density, reducing interface state density, etc., and improving gate reliability. performance, eliminate defects, and reduce device manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The subject matter of the invention will now be discussed with reference to several exemplary embodiments. It should be understood that these embodiments are discussed only to enable those of ordinary skill in the art to better understand and thus implement the content of the present invention, and do not imply any limitation on the scope of the present invention.

[0032] As used herein, the term "comprising" and variations thereof are to be read as open-ended terms meaning "including but not limited to". The term "based on" is to be read as "based at least in part on". The terms "one embodiment" and "an embodiment" are to be read as "at least one embodiment." The term "another embodiment" is to be read as "at least one other embodiment".

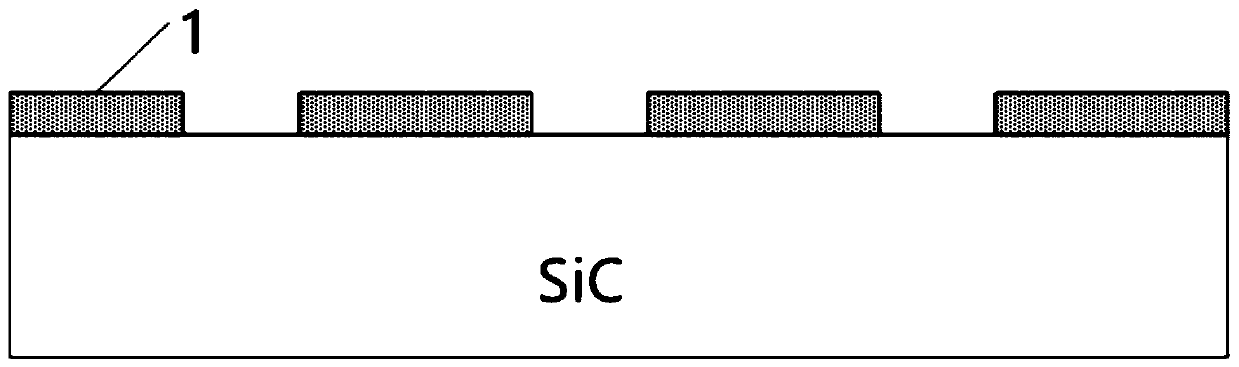

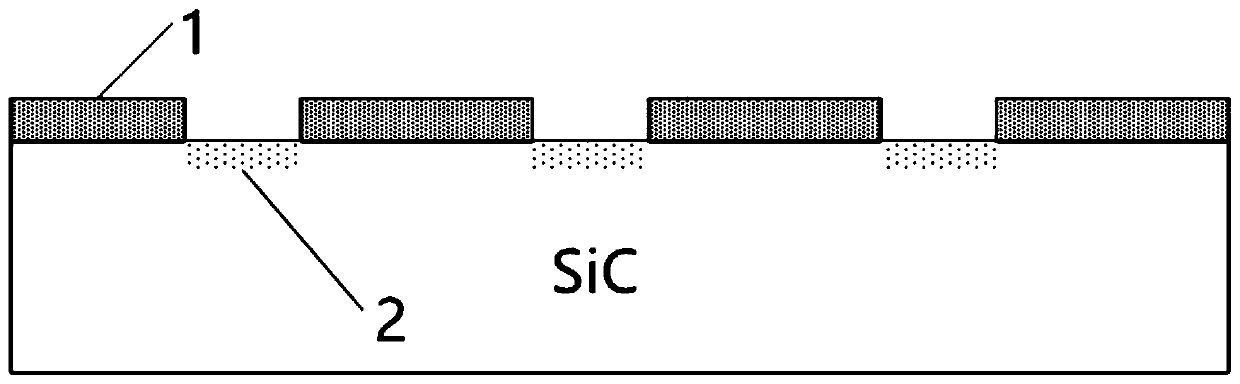

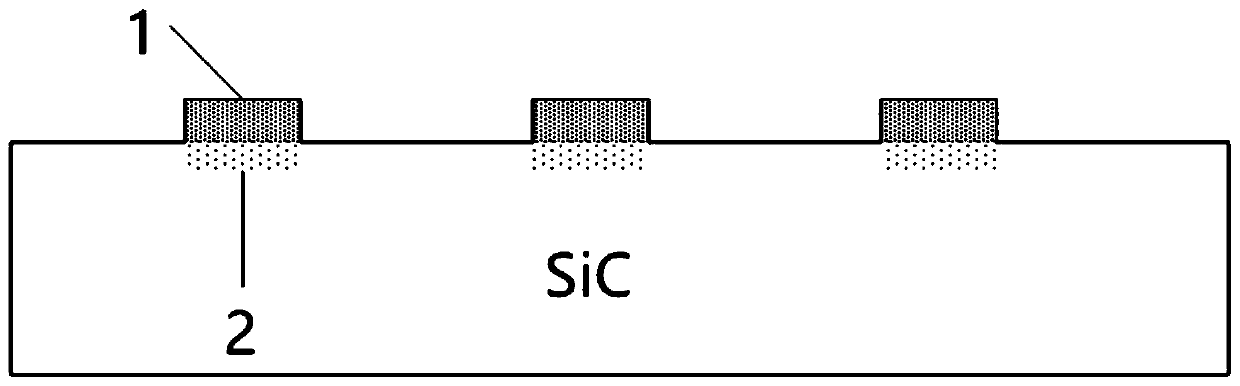

[0033] Such as Figure 1 to Figure 5 Shown is a schematic diagram of the SiC single crystal or epitaxial wafer structure shown according to the steps of preparing the gate oxide layer in the embodiment of the present invention; t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More