Patents

Literature

67results about How to "Improve gate reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

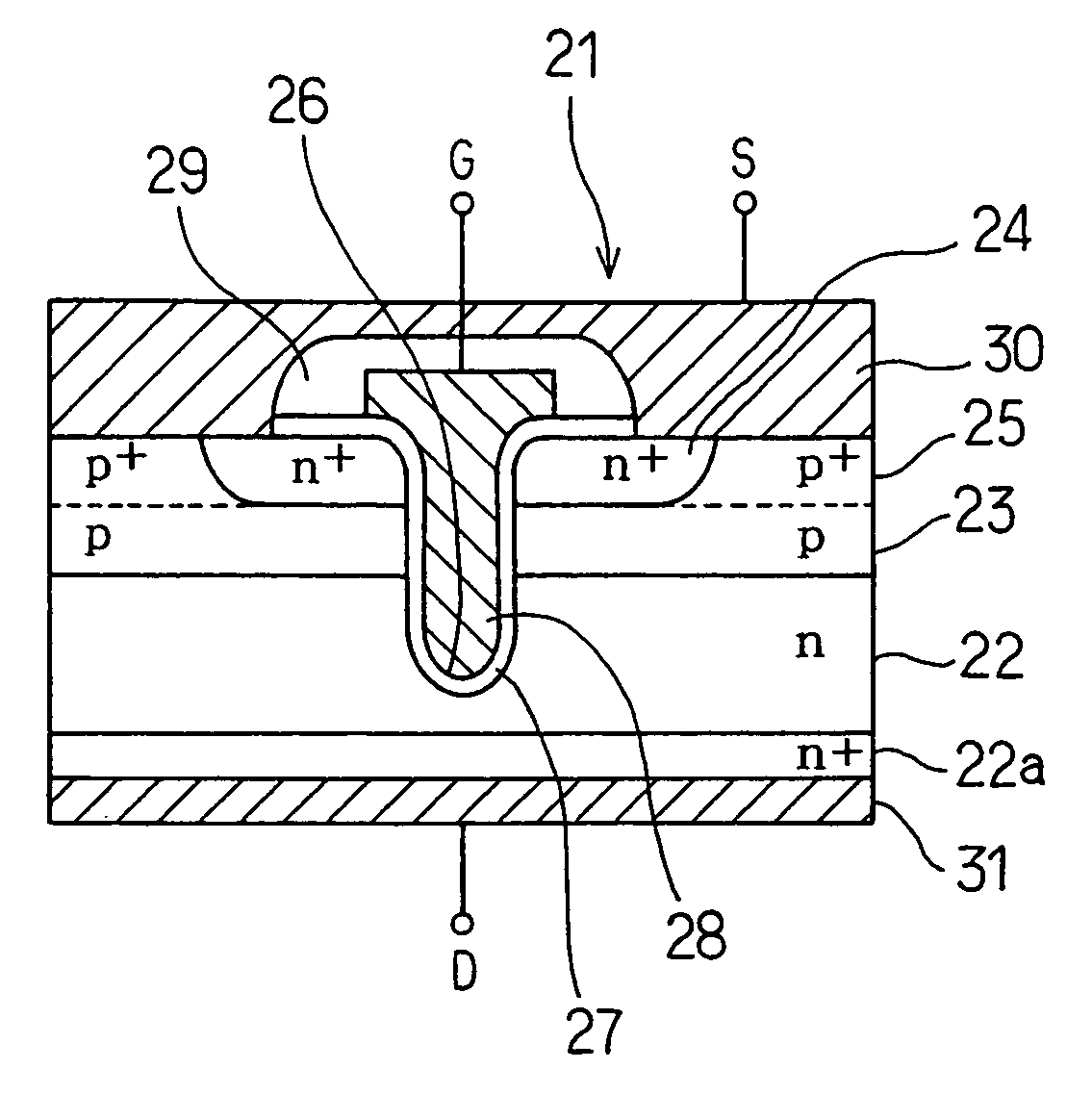

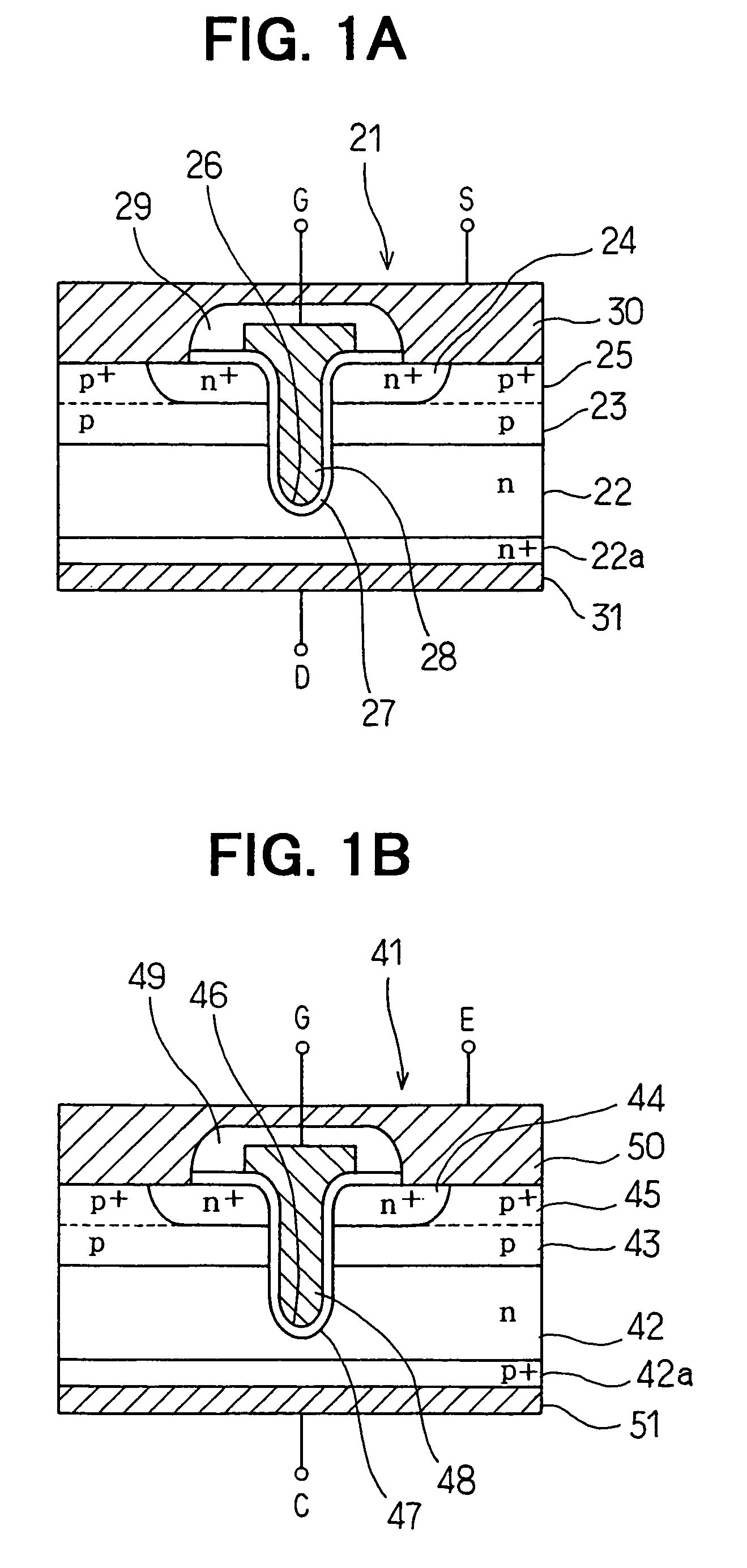

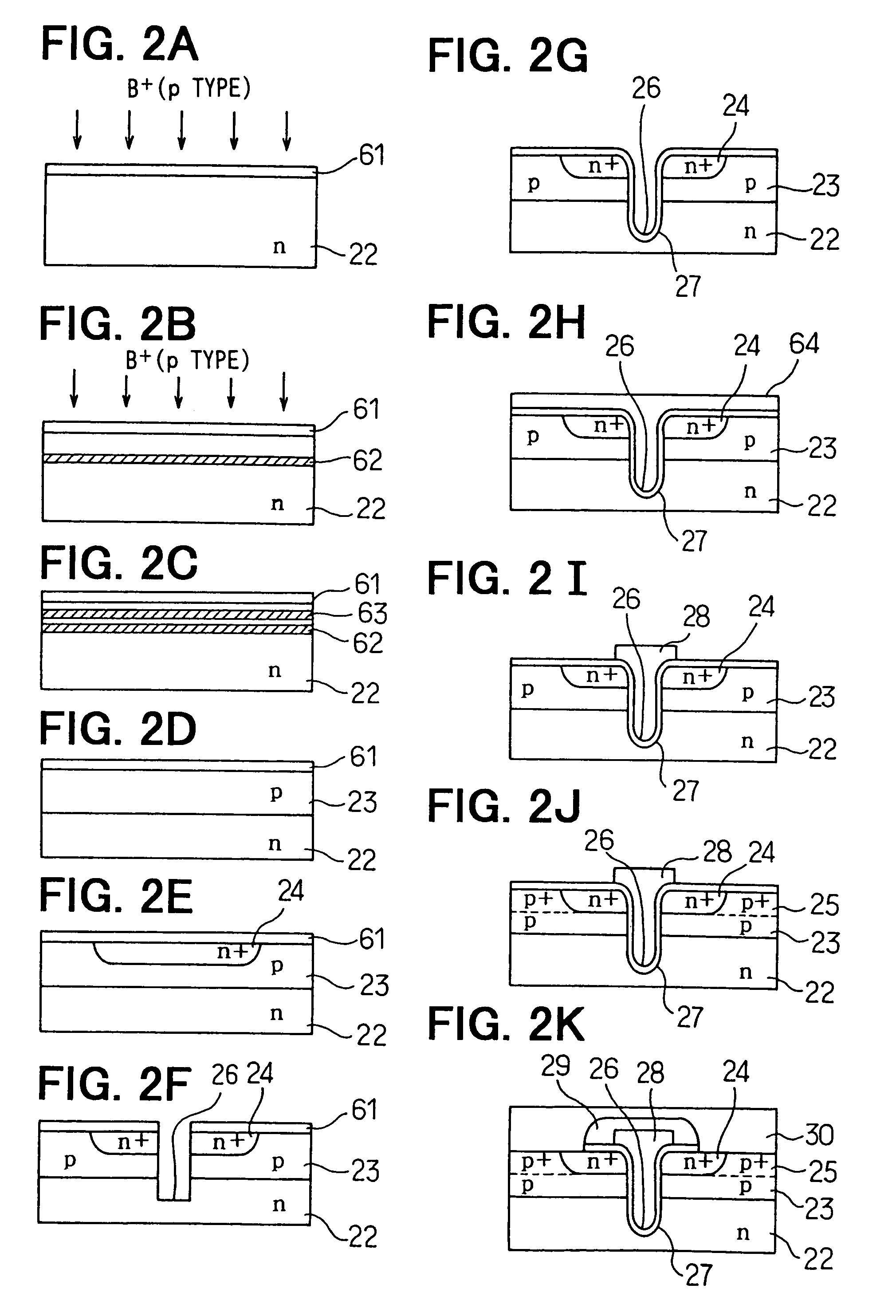

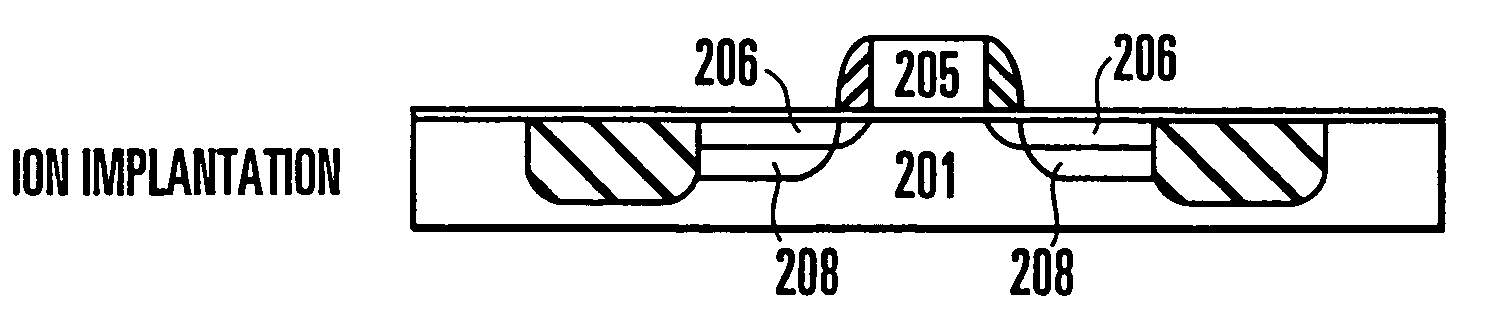

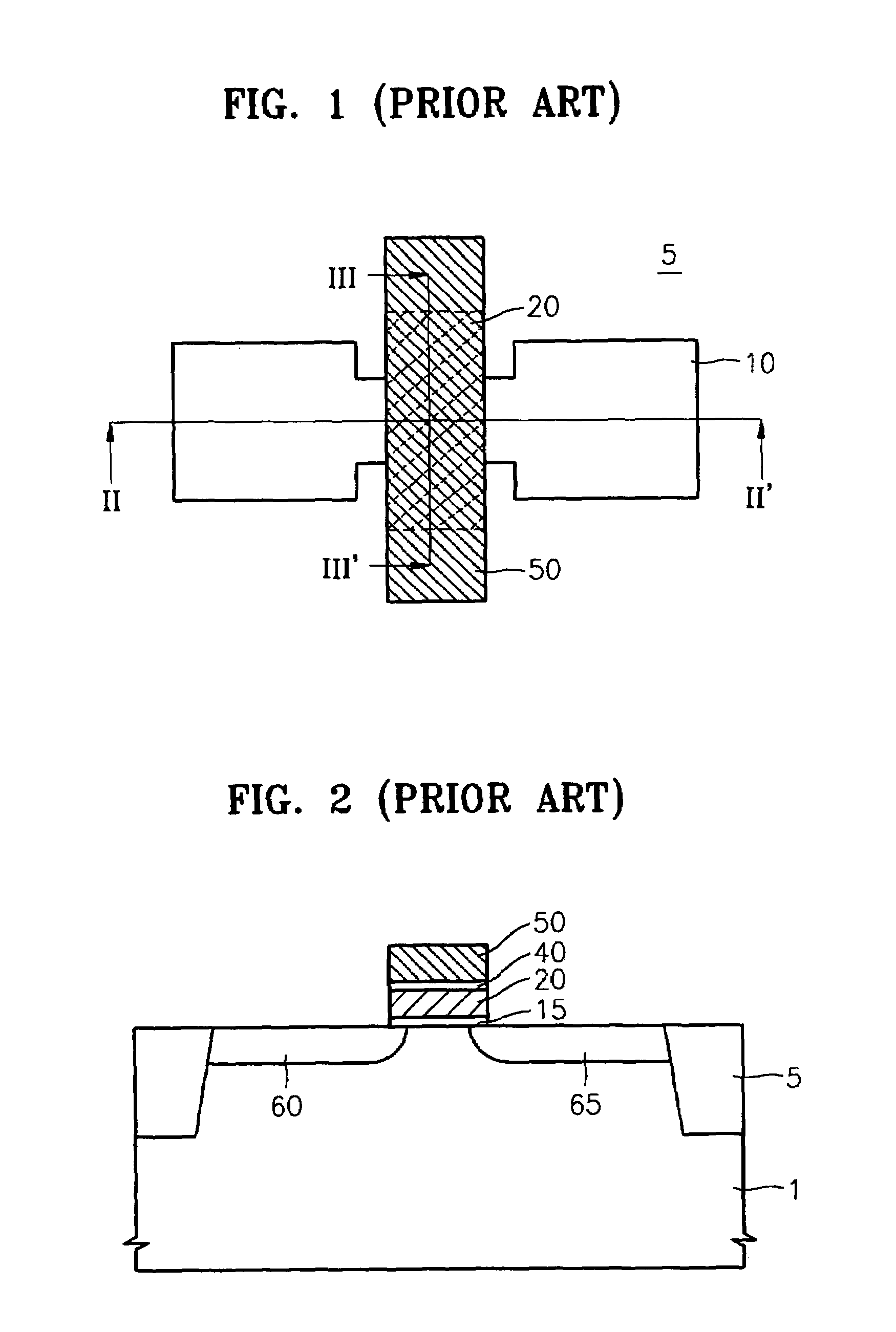

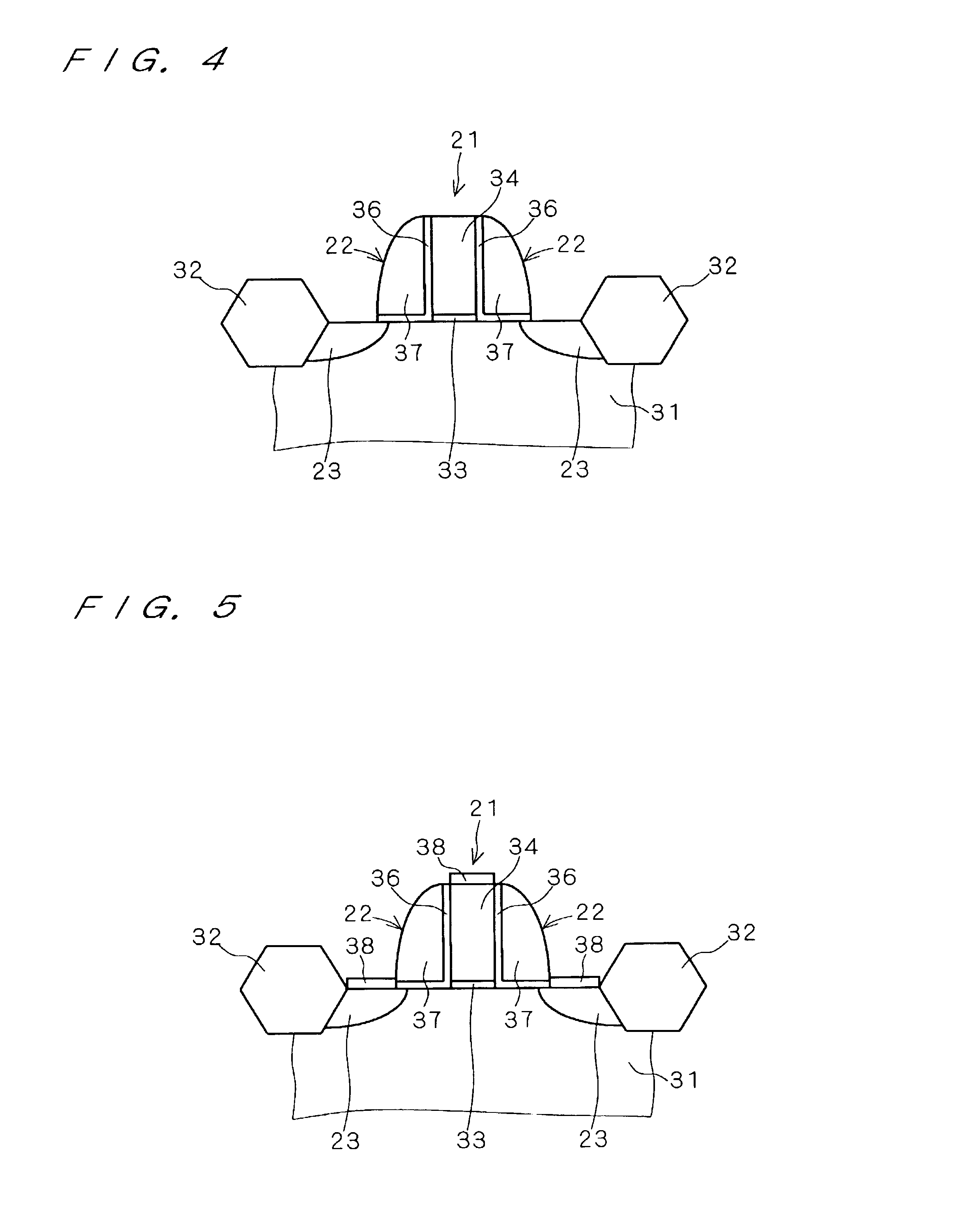

Manufacturing method of semiconductor device

InactiveUS7037788B2Suppress mutationDeterioration of characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesSub thresholdHigh acceleration

By improving profile of impurity concentration in a channel portion of an FET or an IGBT of a trench gate type, variation of threshold value is lessened, and a destruction caused by current concentration is prevented while suppressing deterioration of cut-off characteristics. An island of a base region of p-type is formed in a semiconductor substrate of n-type by carrying out high acceleration ion implantation twice followed by annealing, so that the impurity concentration profile in a channel portion changes gradually in a depth direction. Accordingly, it is possible to lessen variation of the threshold value and to reduce pinch resistance while at the same time improving sub-threshold voltage coefficient and conductance characteristics.

Owner:DENSO CORP

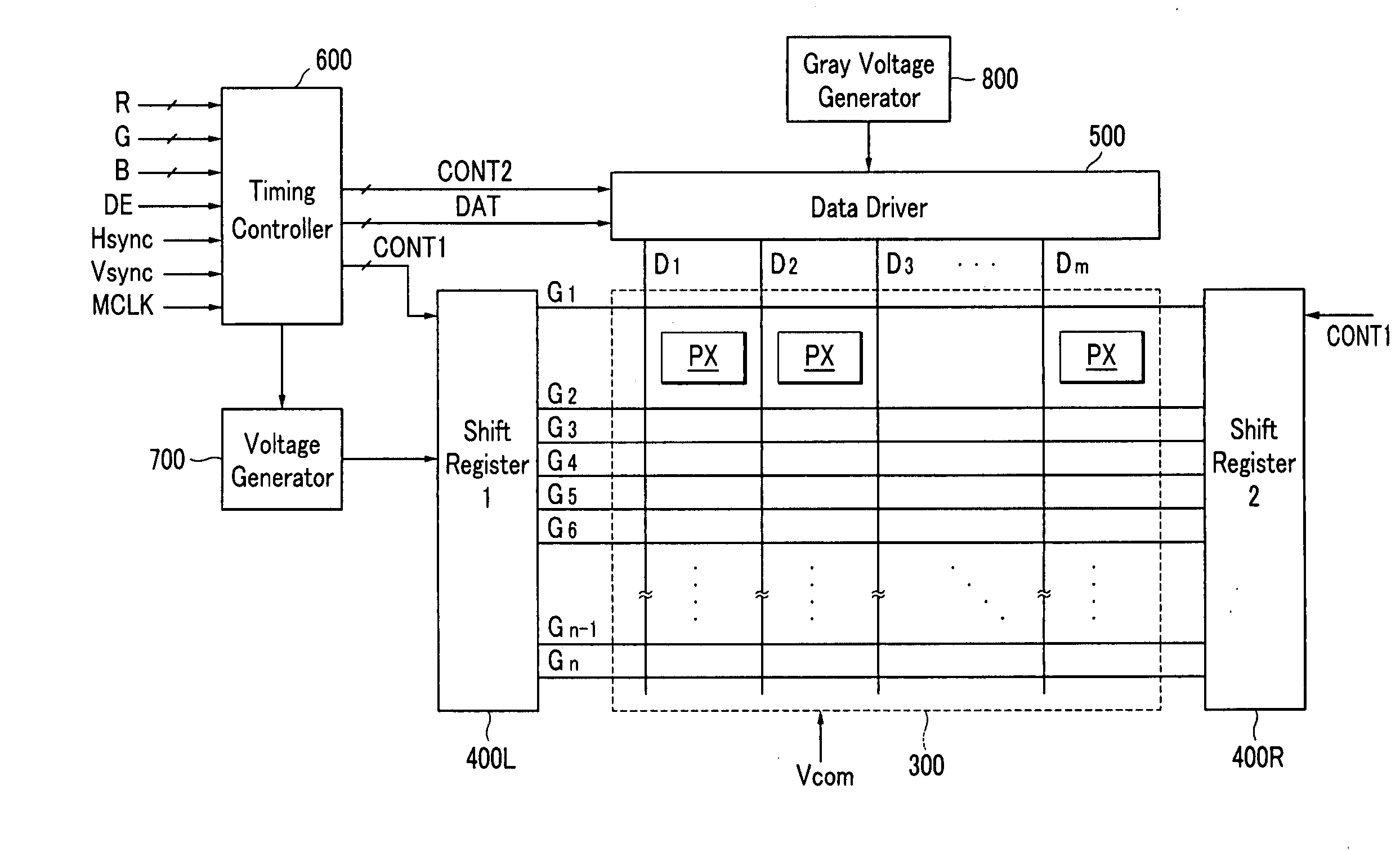

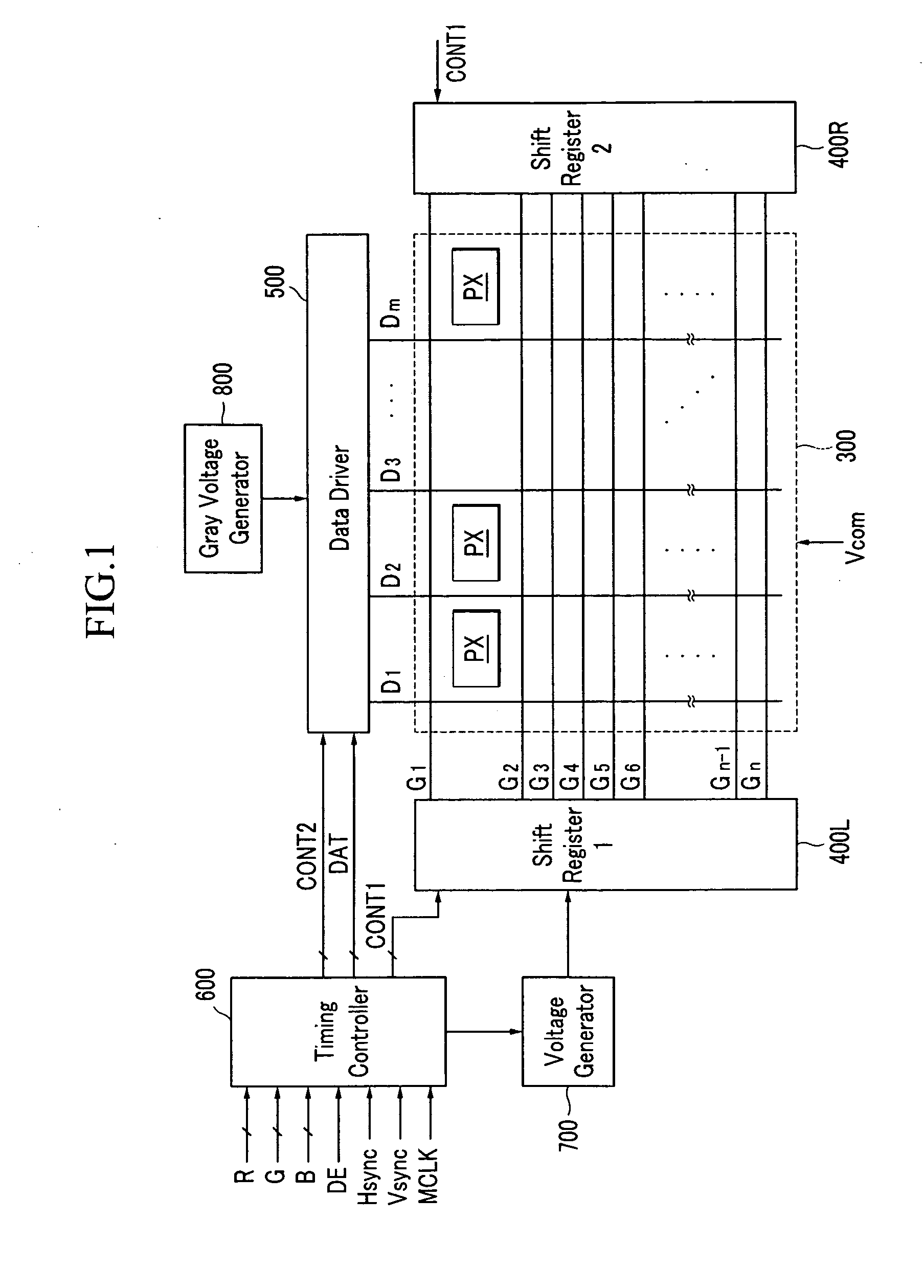

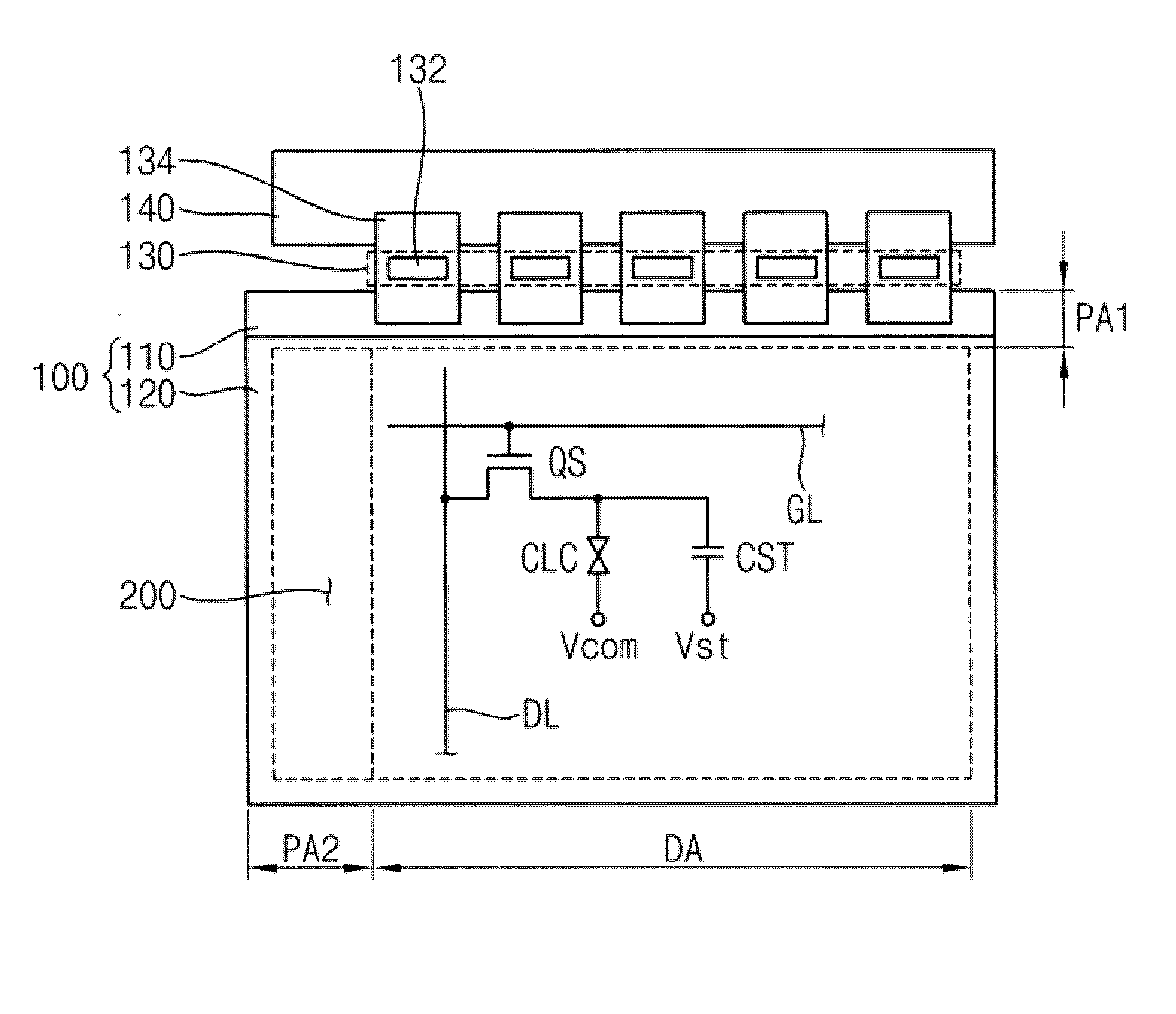

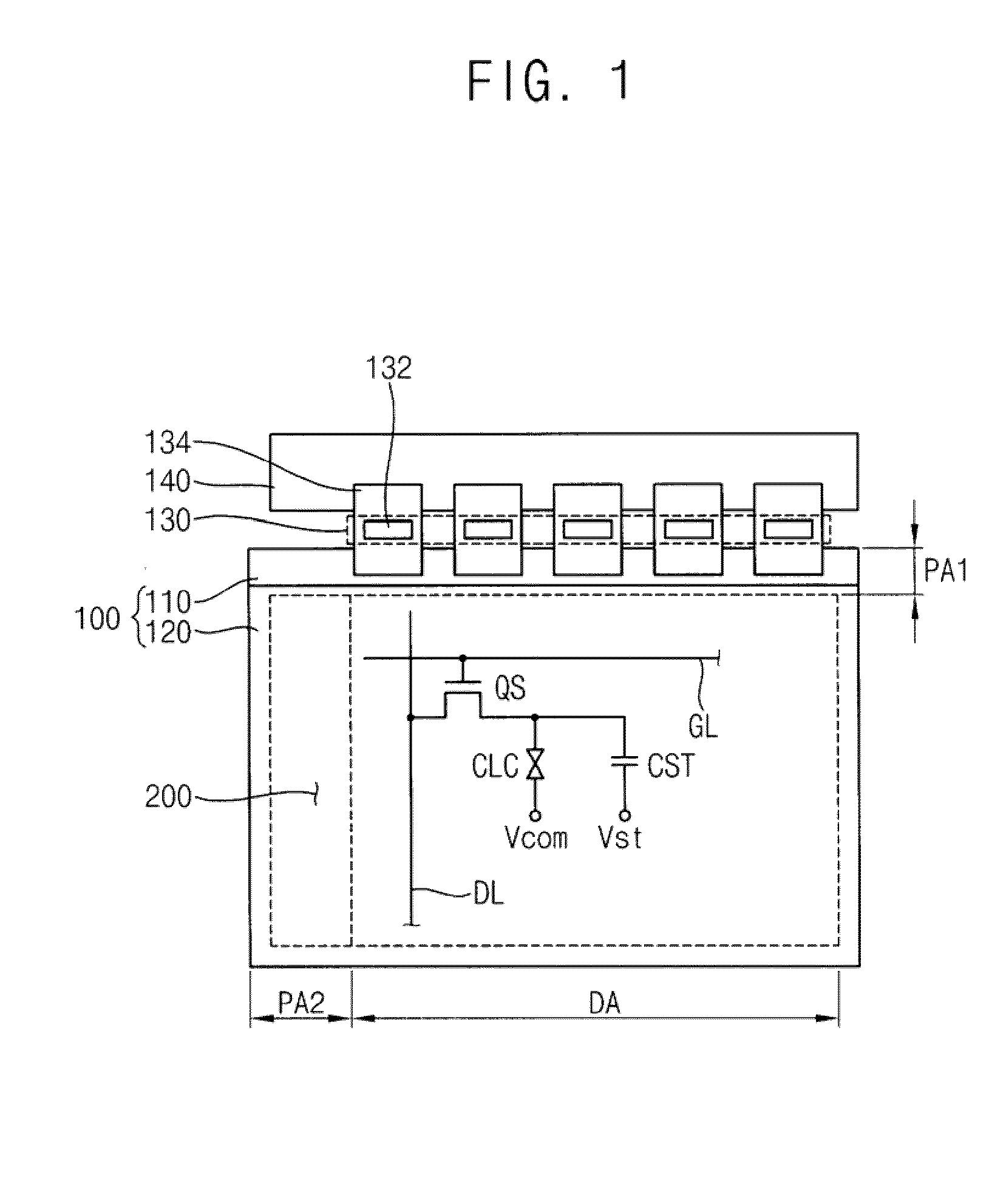

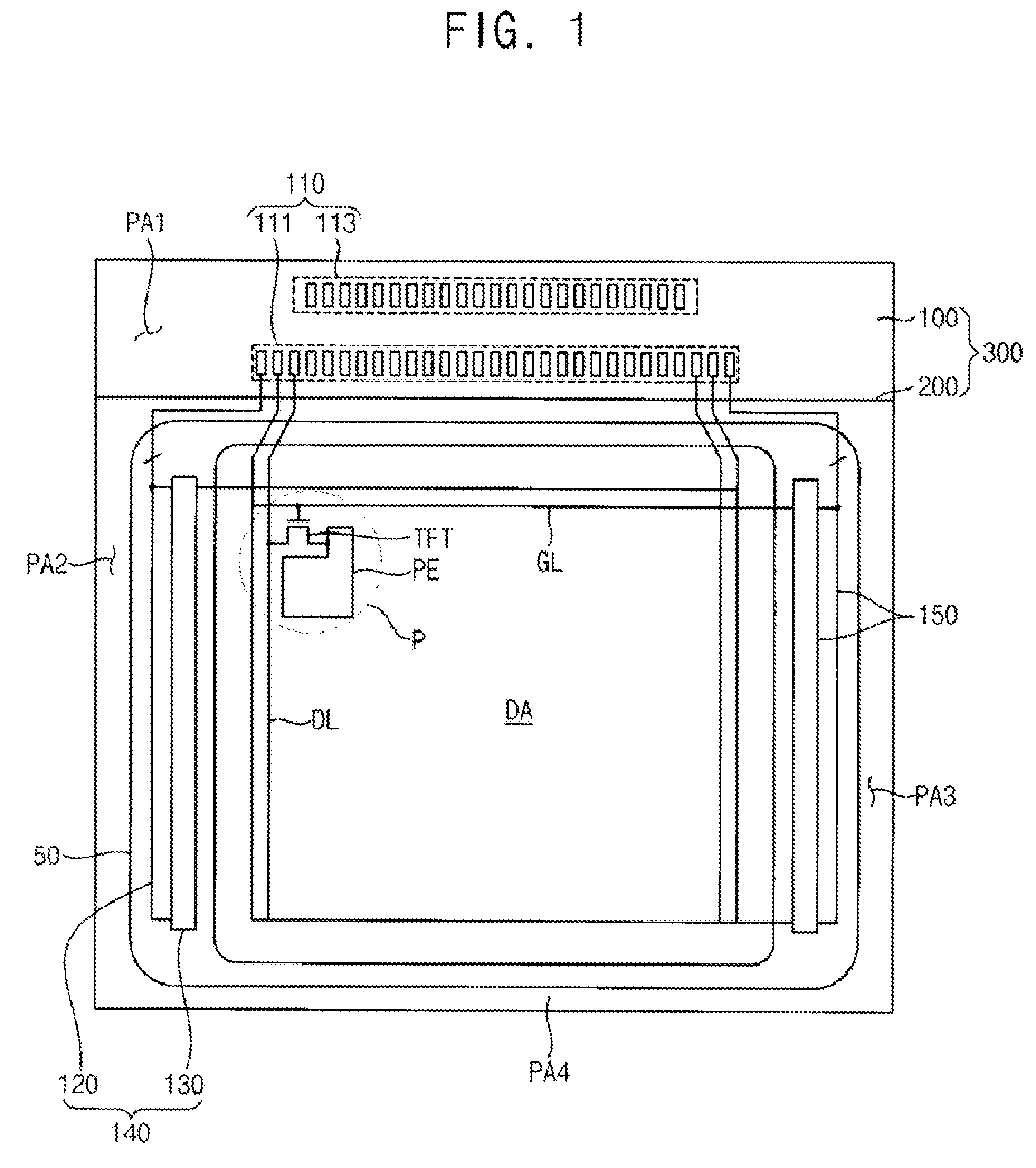

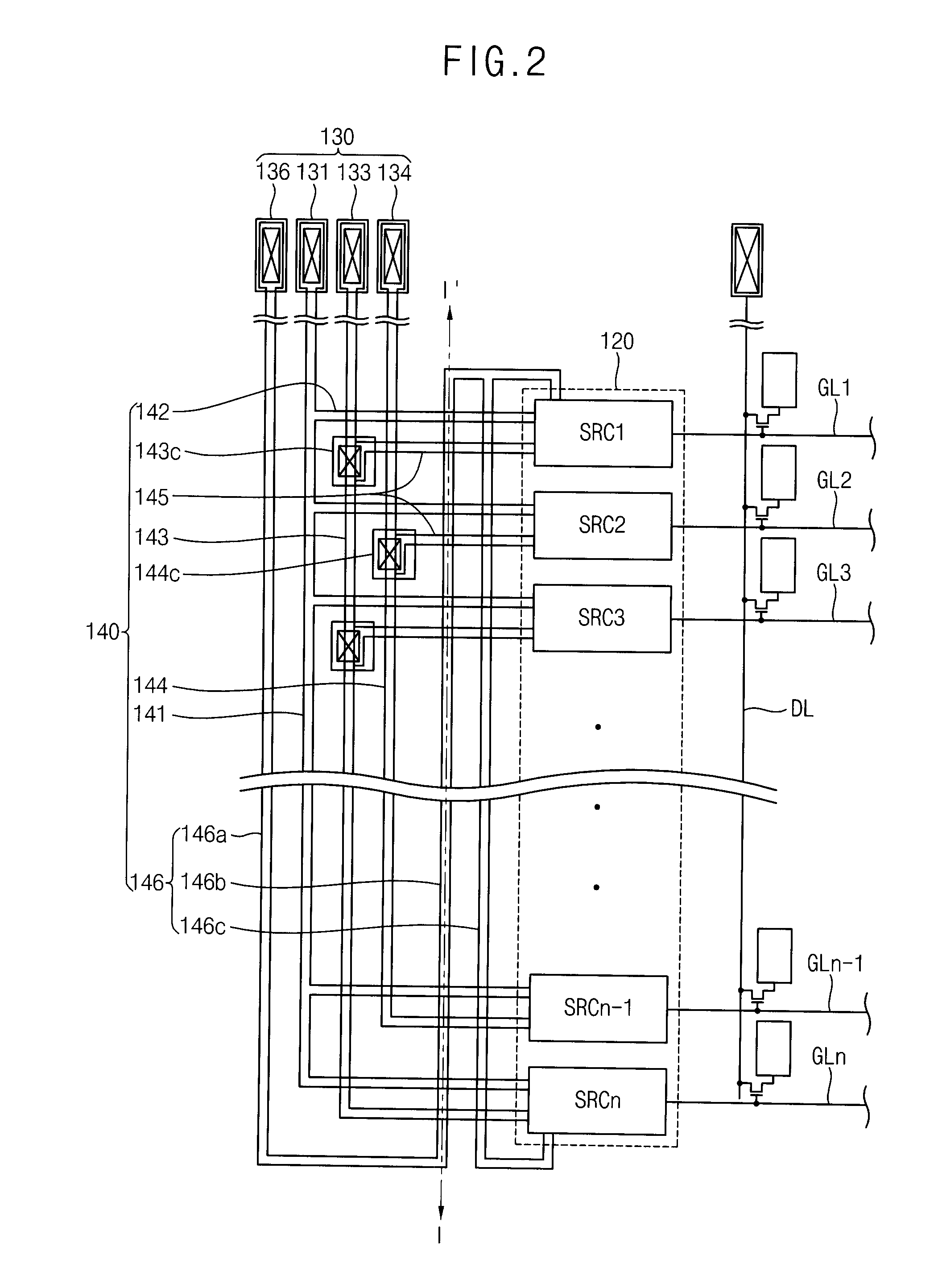

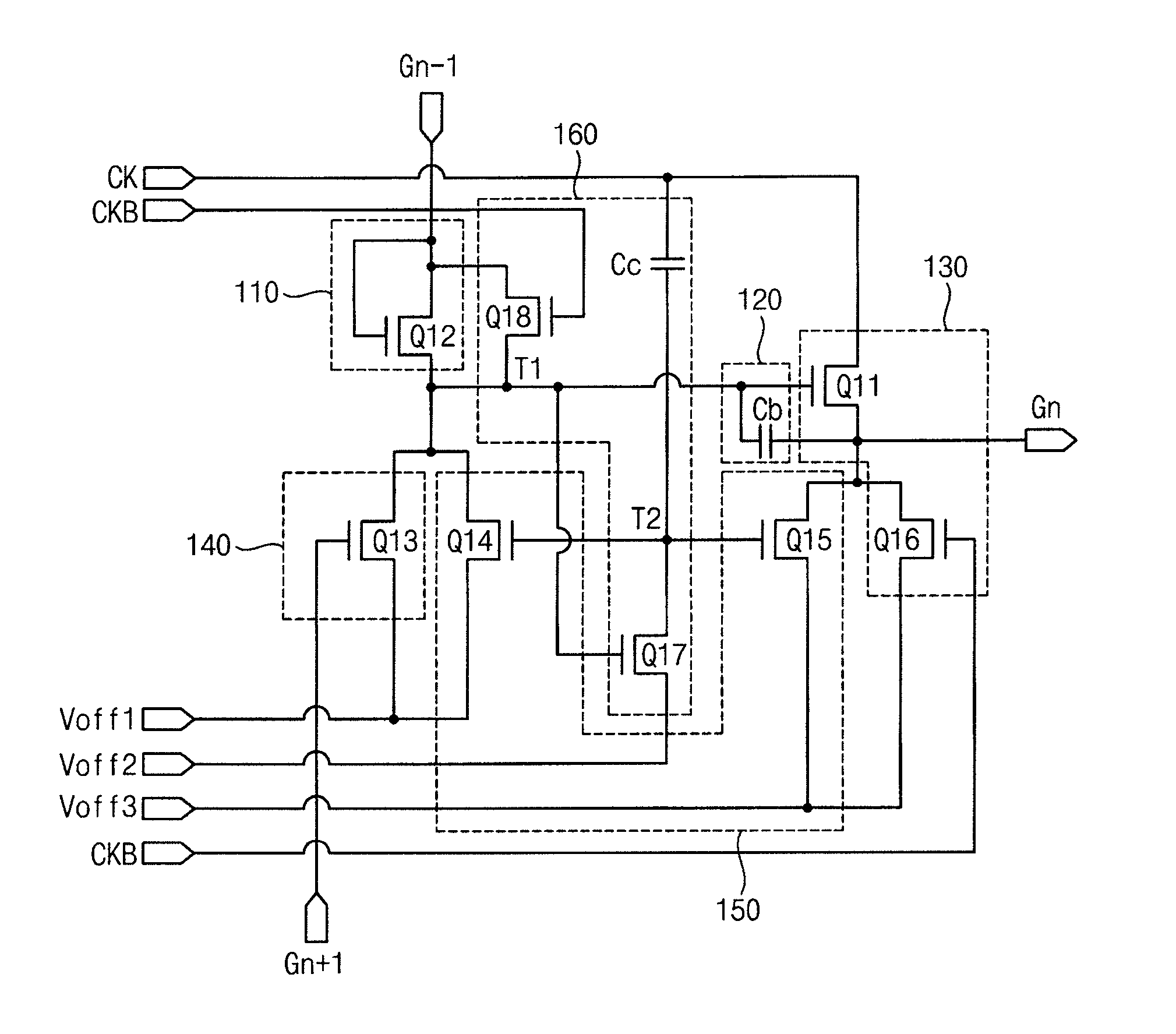

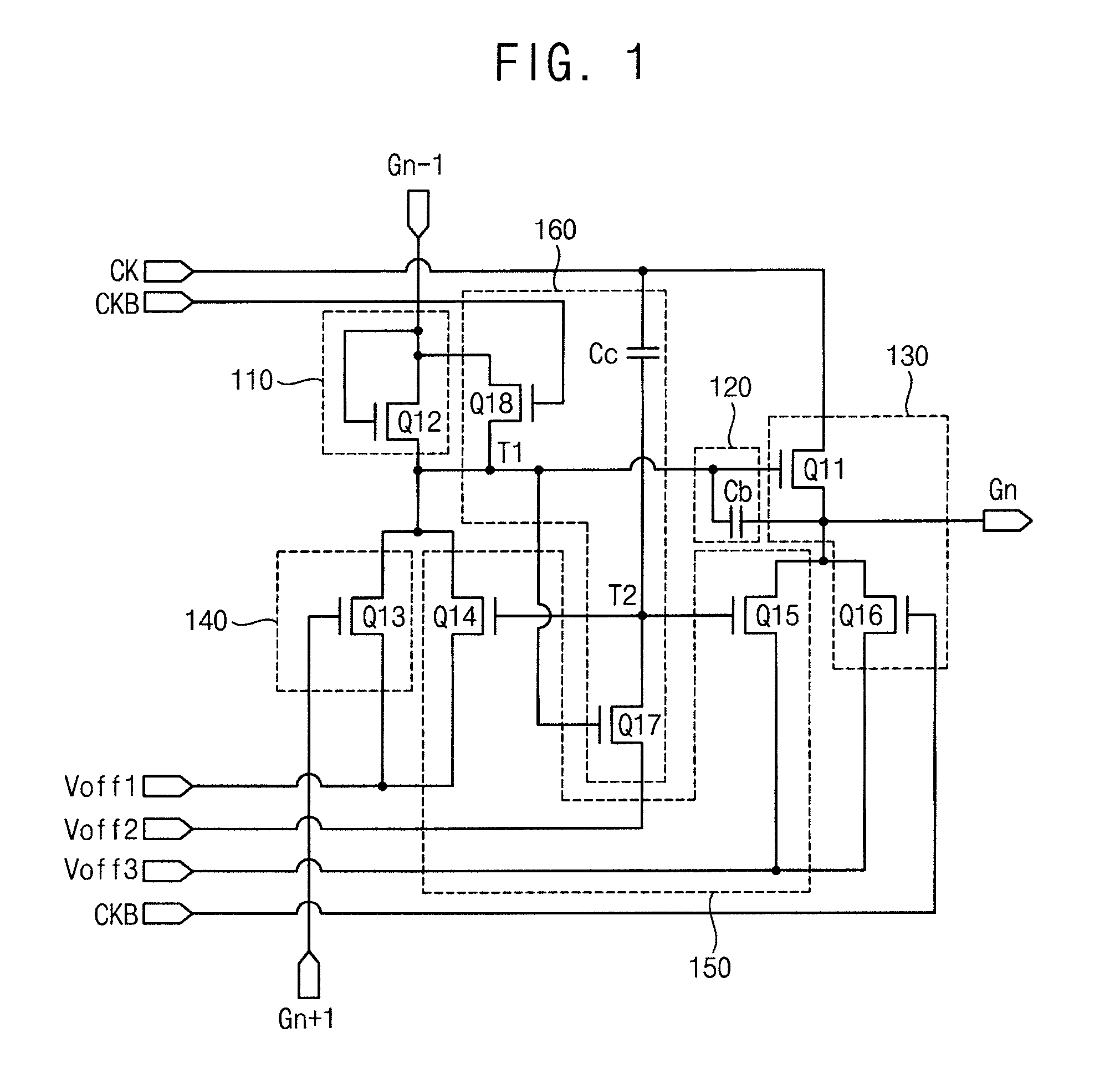

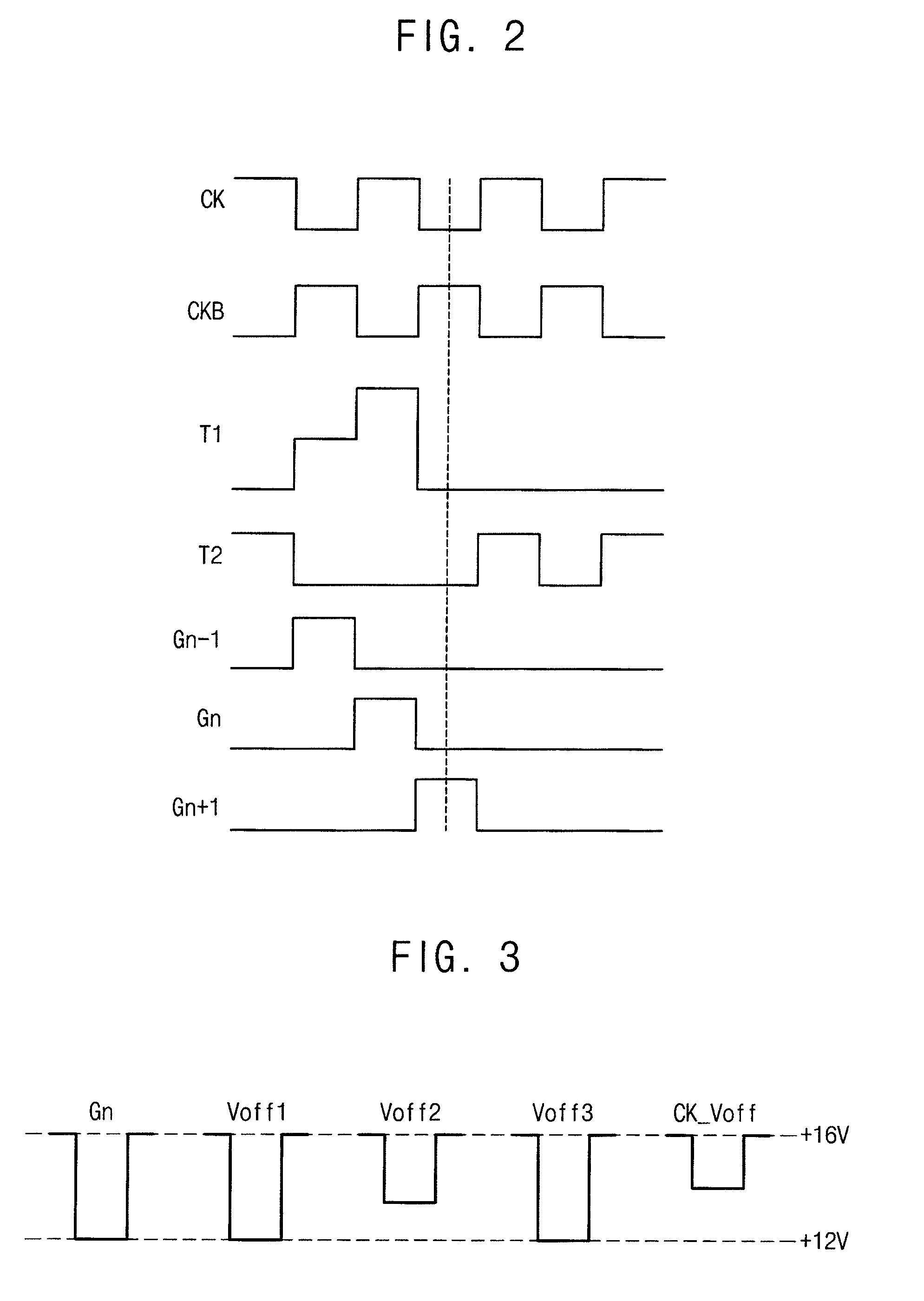

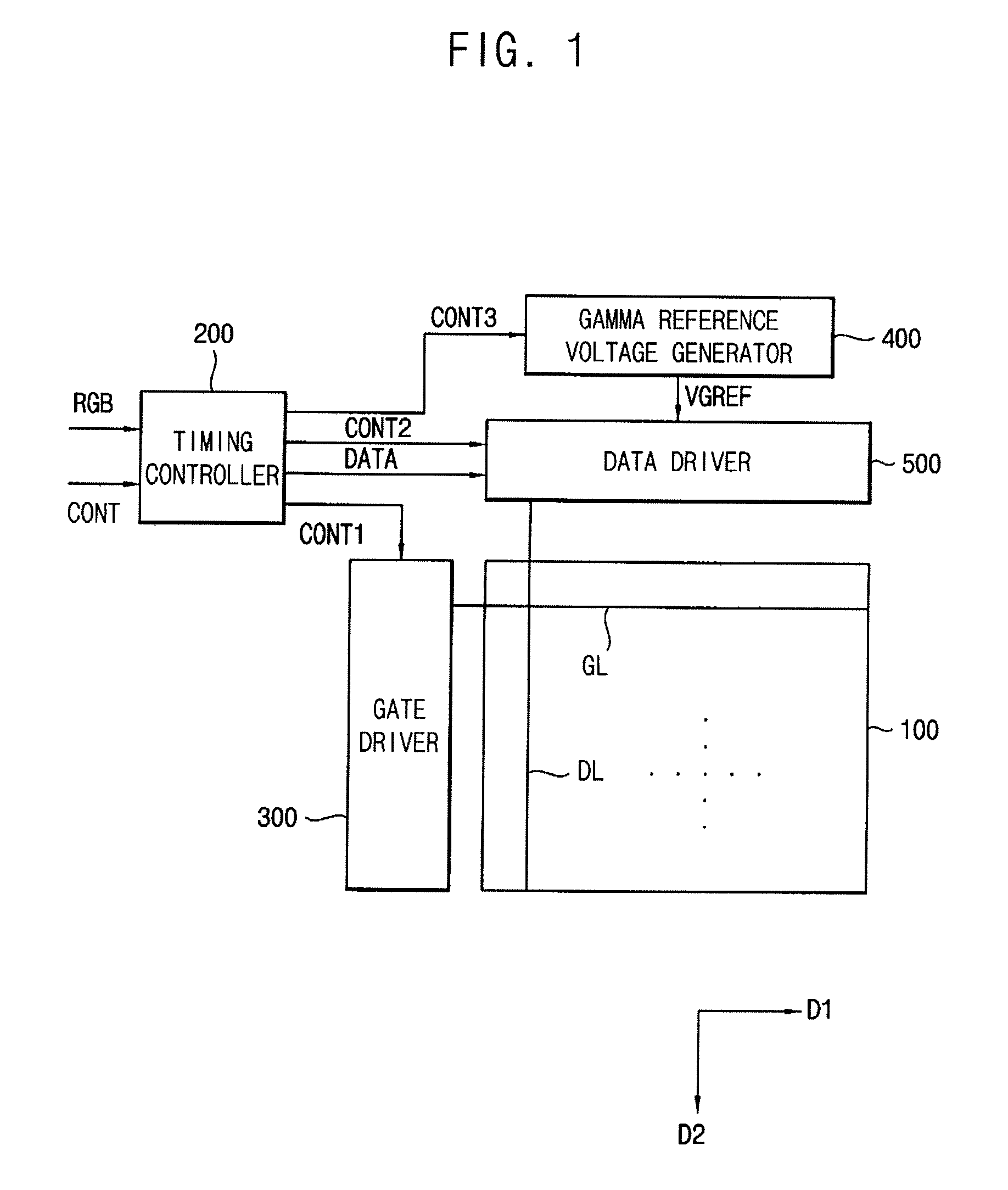

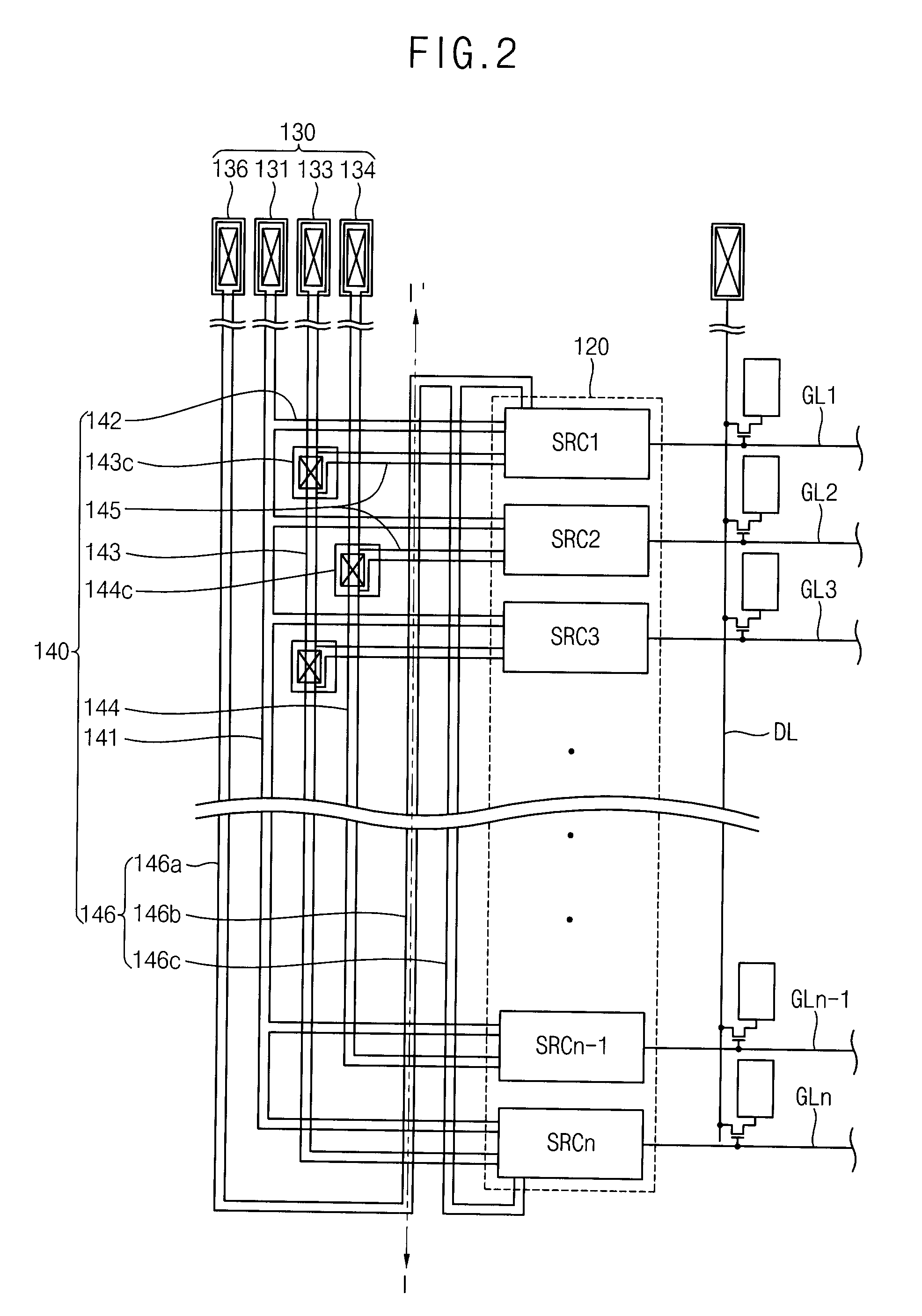

Gate driving circuit and display device having the same

ActiveUS20090040203A1Improve noiseImprove gate reliabilityCathode-ray tube indicatorsDigital storageDisplay deviceEngineering

A gate driving circuit and a display device having the same, a pull-up unit pulls up a current gate signal by using a first clock signal during a first period of one frame. A pull-up driver coupled to the pull-up unit receives a carry signal from one of the previous stages to turn on the pull-up unit. A pull-up unit receives a gate signal from one of the next stages, discharges the current gate signal to an off voltage level, and turns off the pull-up unit. A holder holds the current gate signal at the voltage level. An inverter turns on / off the holder in response to a first clock signal. A ripple preventer has a source and a gate coupled in common to an output terminal of the pull-up unit and a drain coupled to an input terminal of the inverter, and includes a ripple preventing diode for preventing a ripple from being applied to the inverter.

Owner:SAMSUNG DISPLAY CO LTD

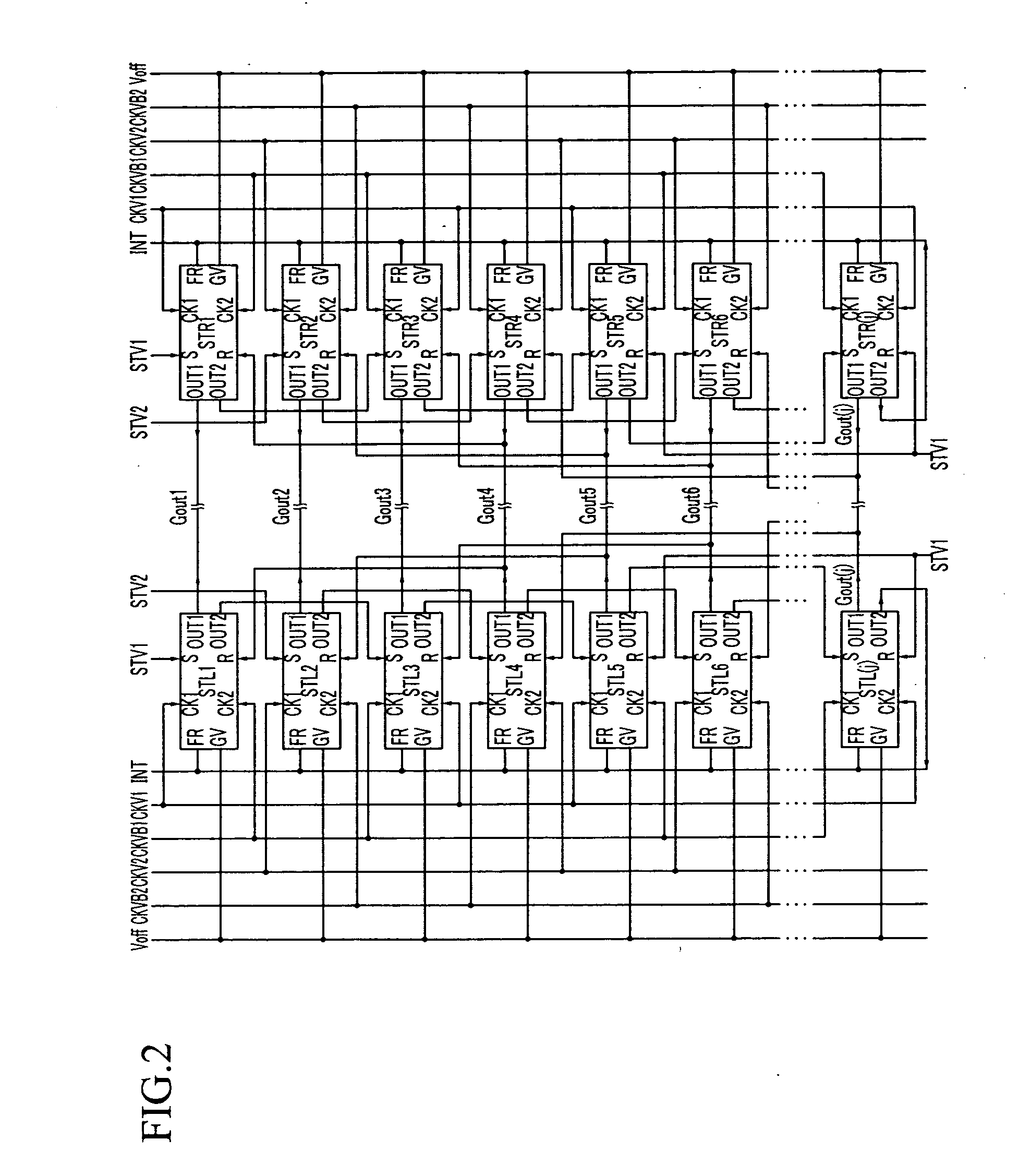

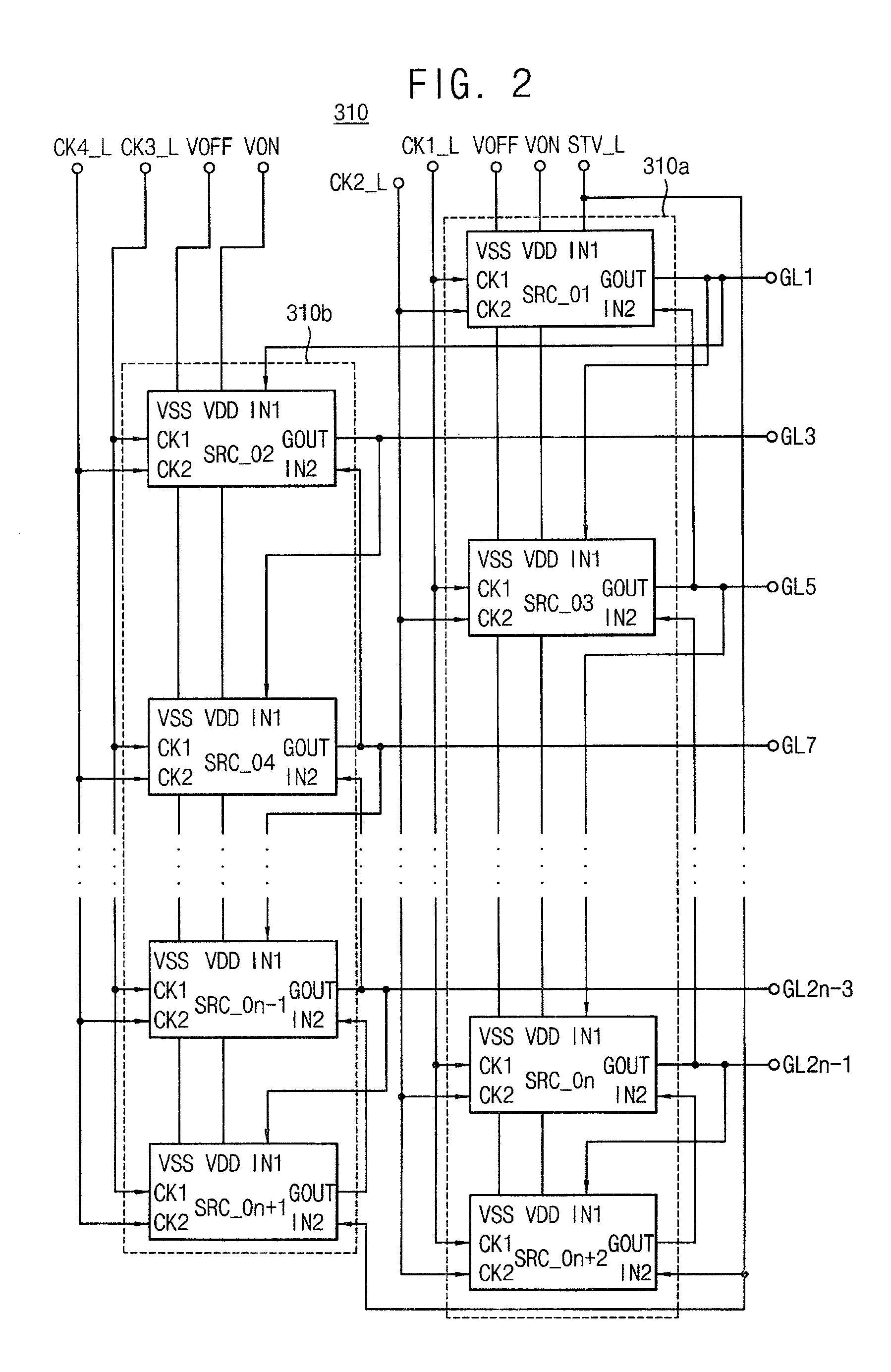

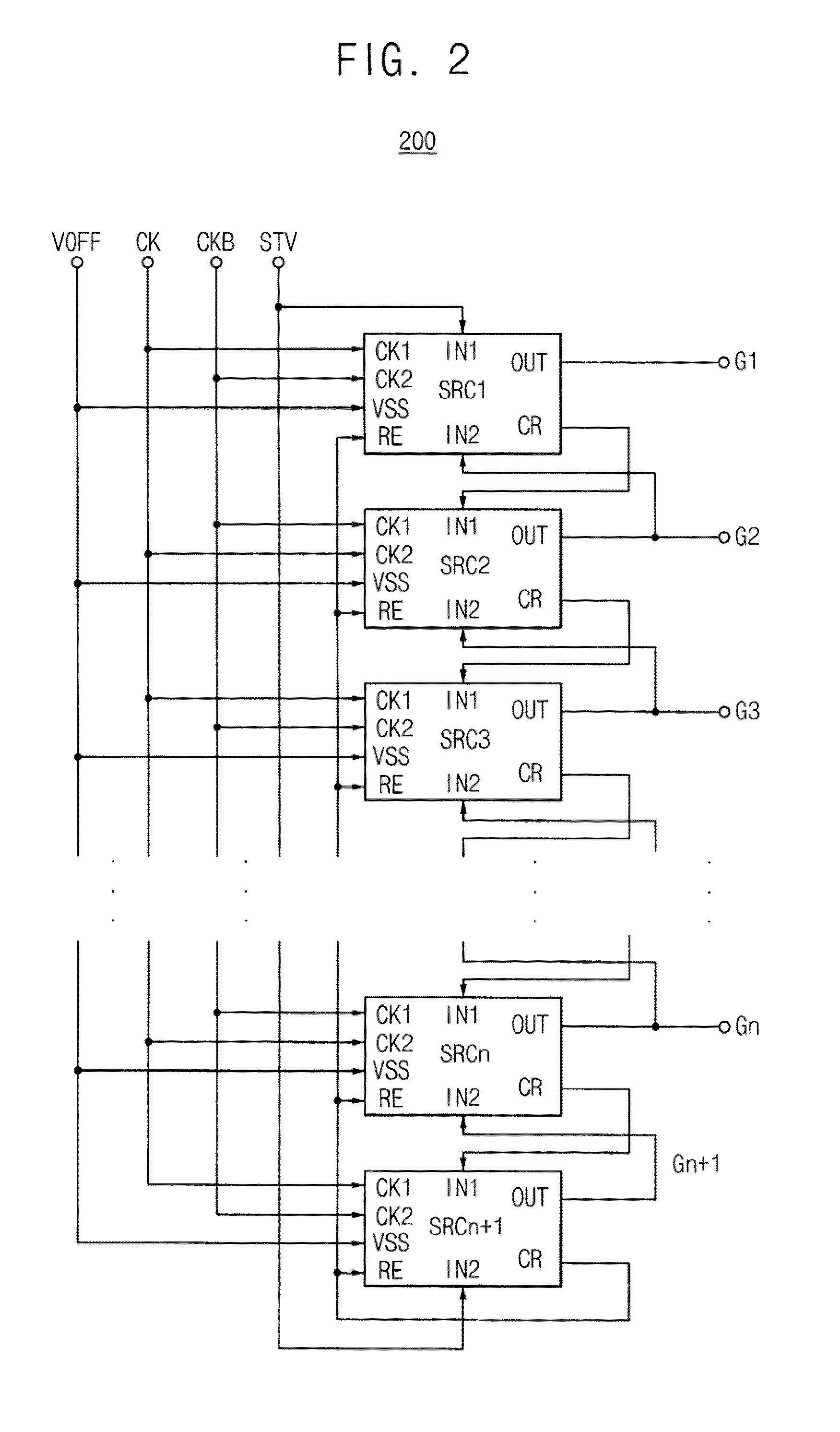

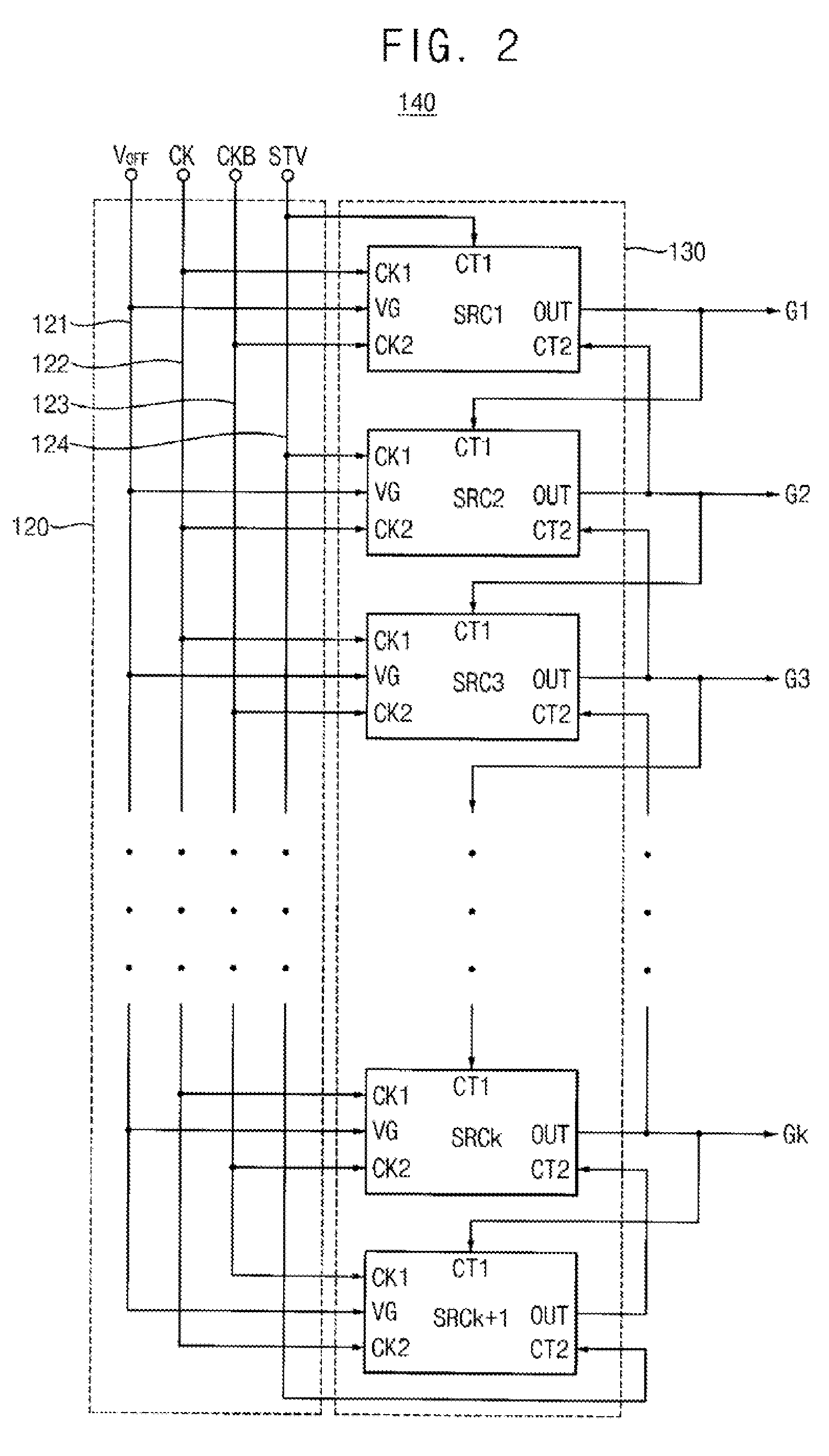

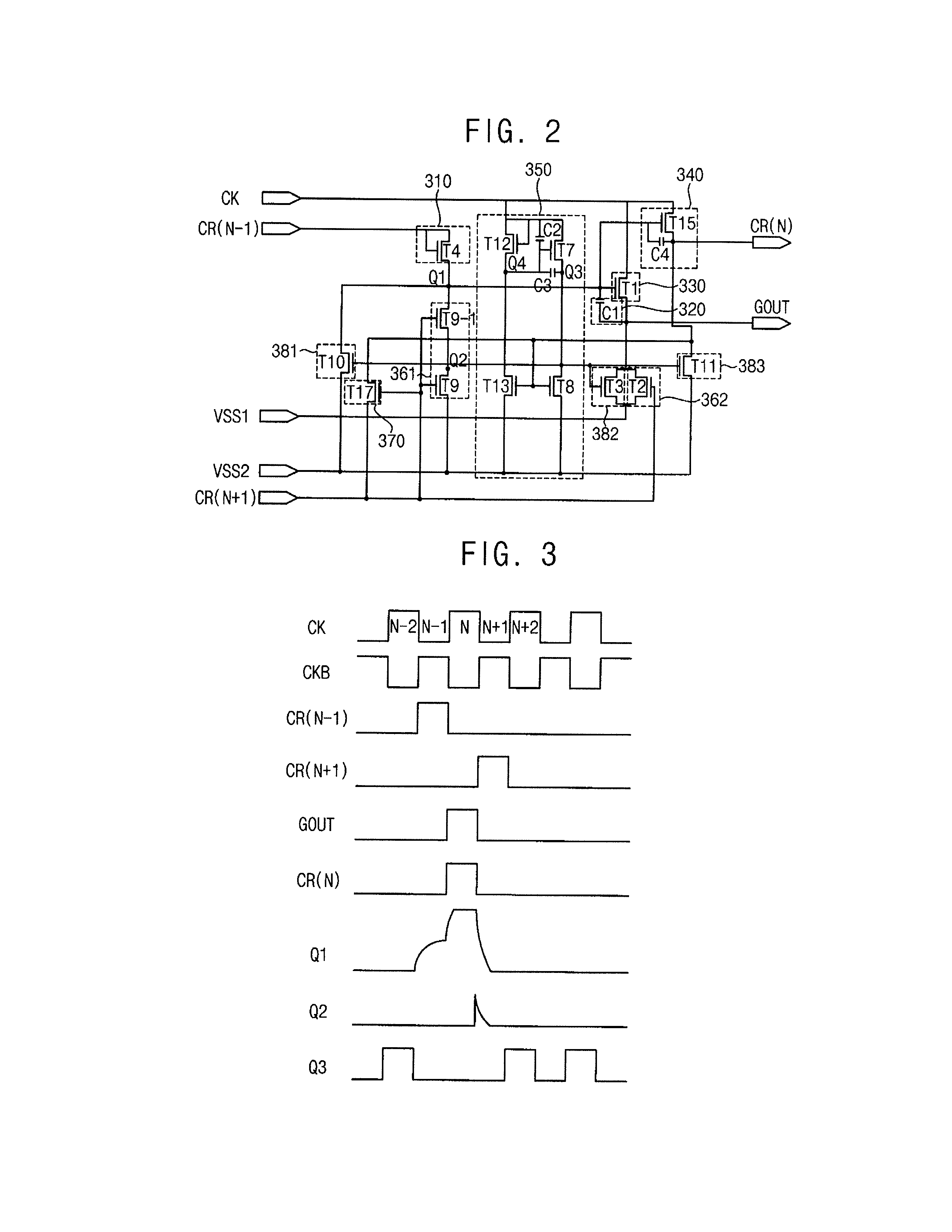

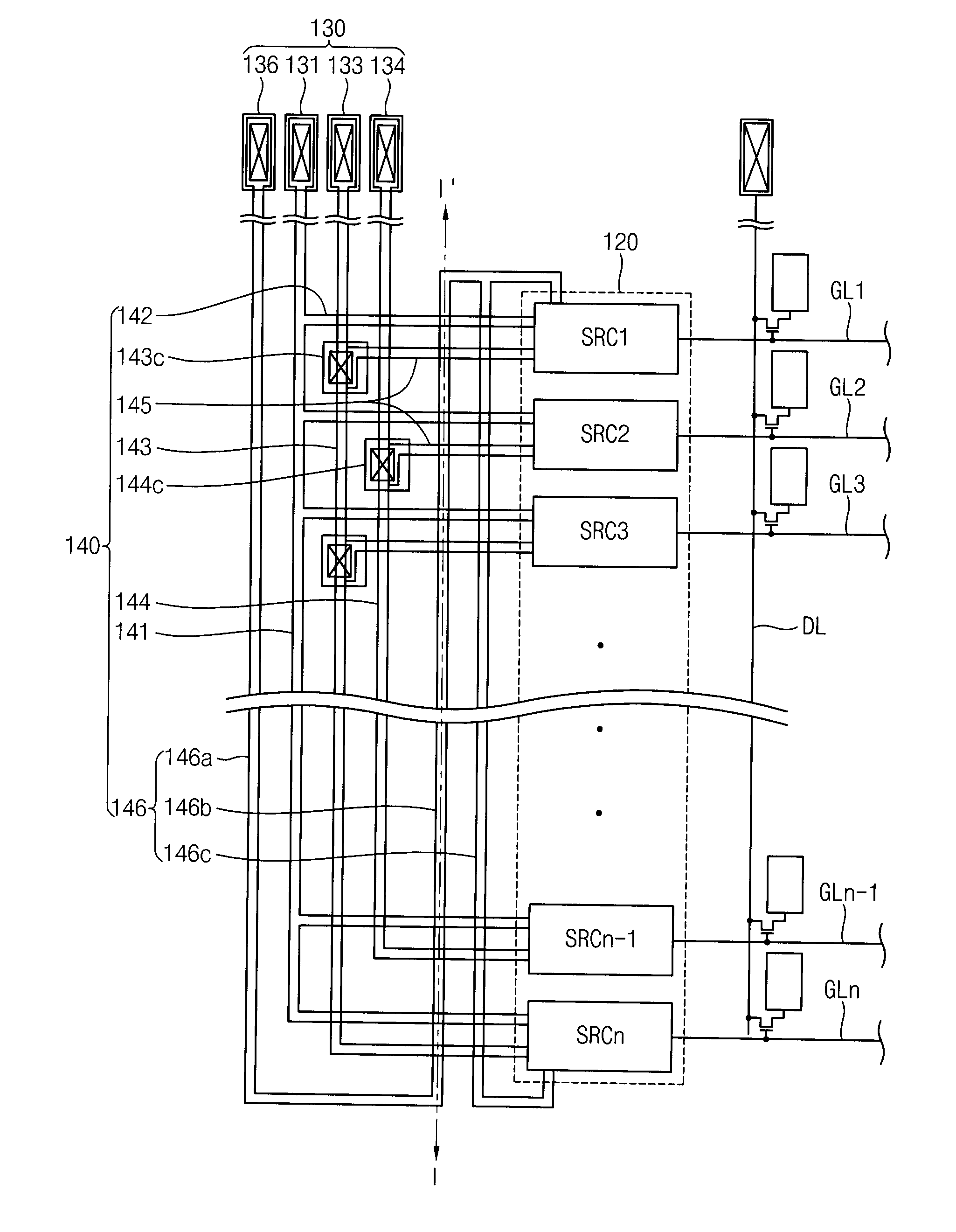

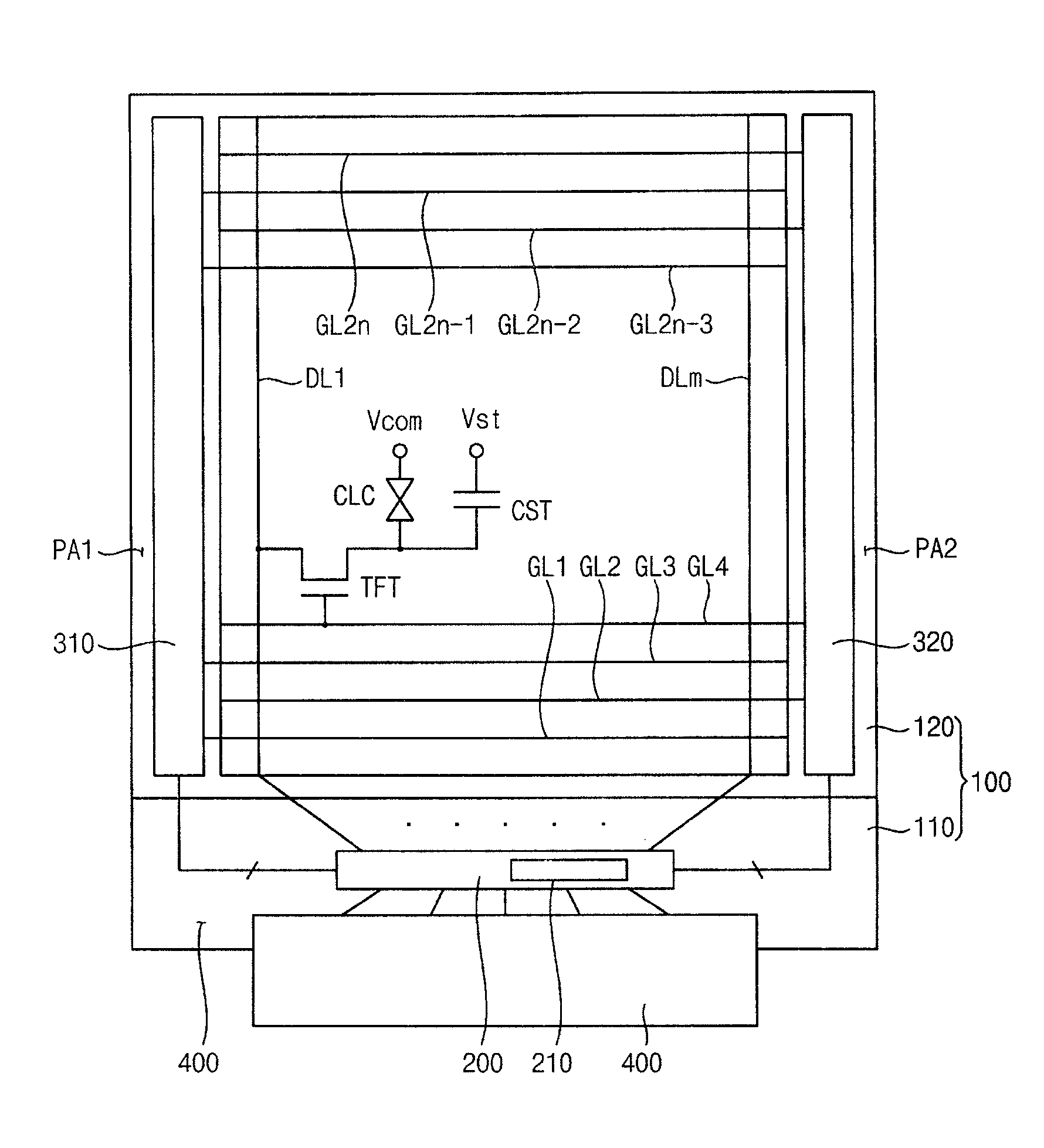

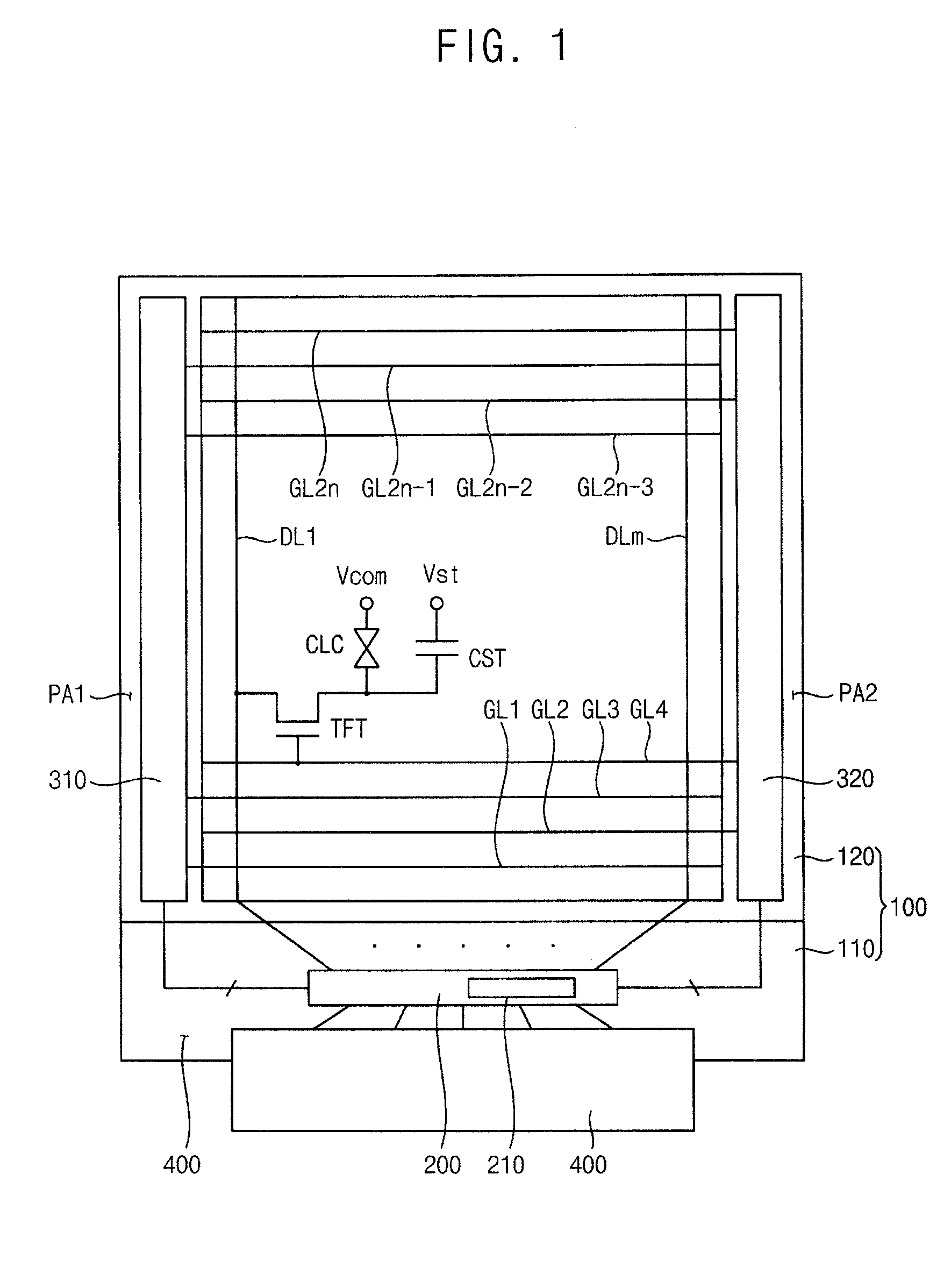

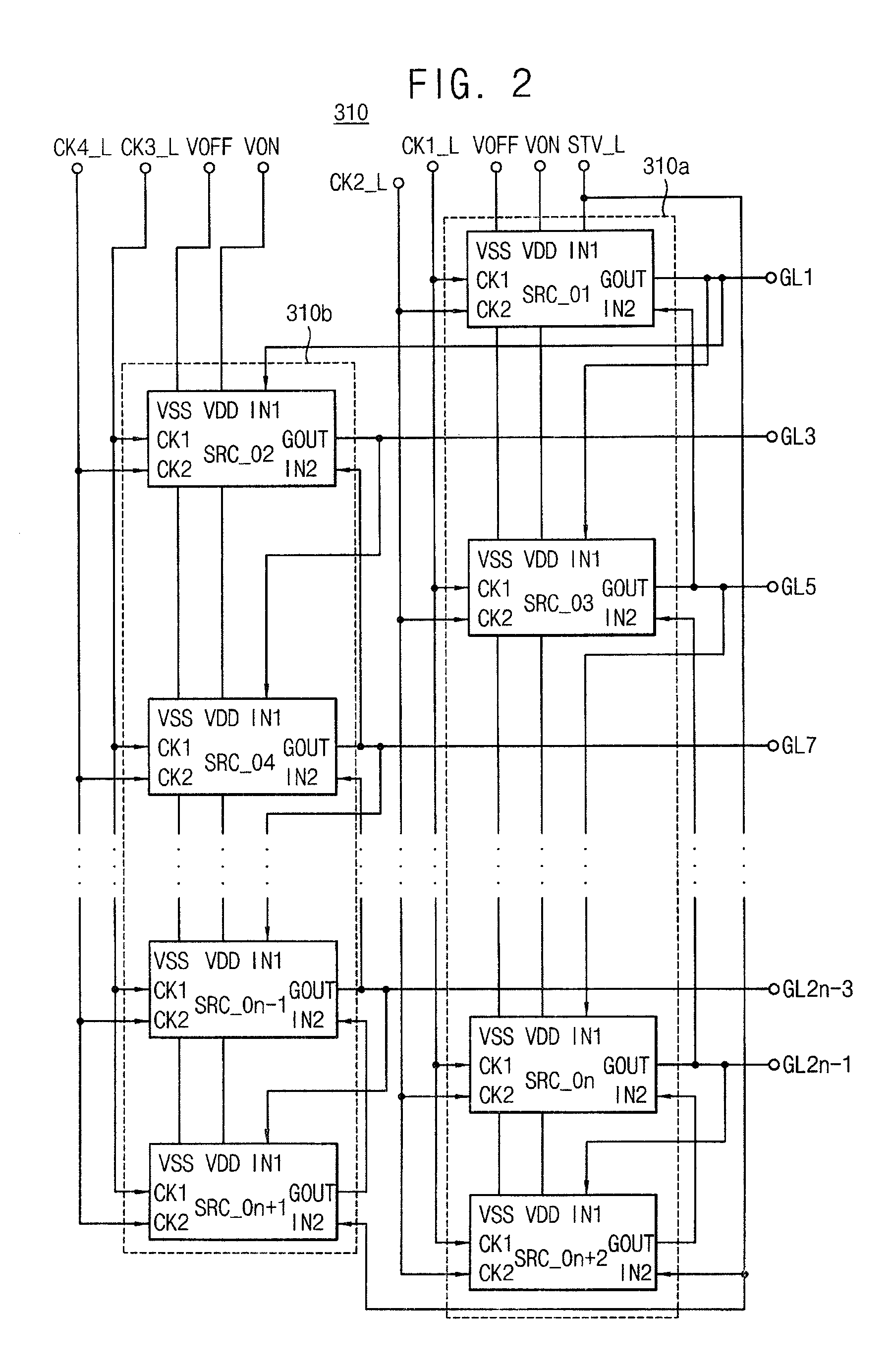

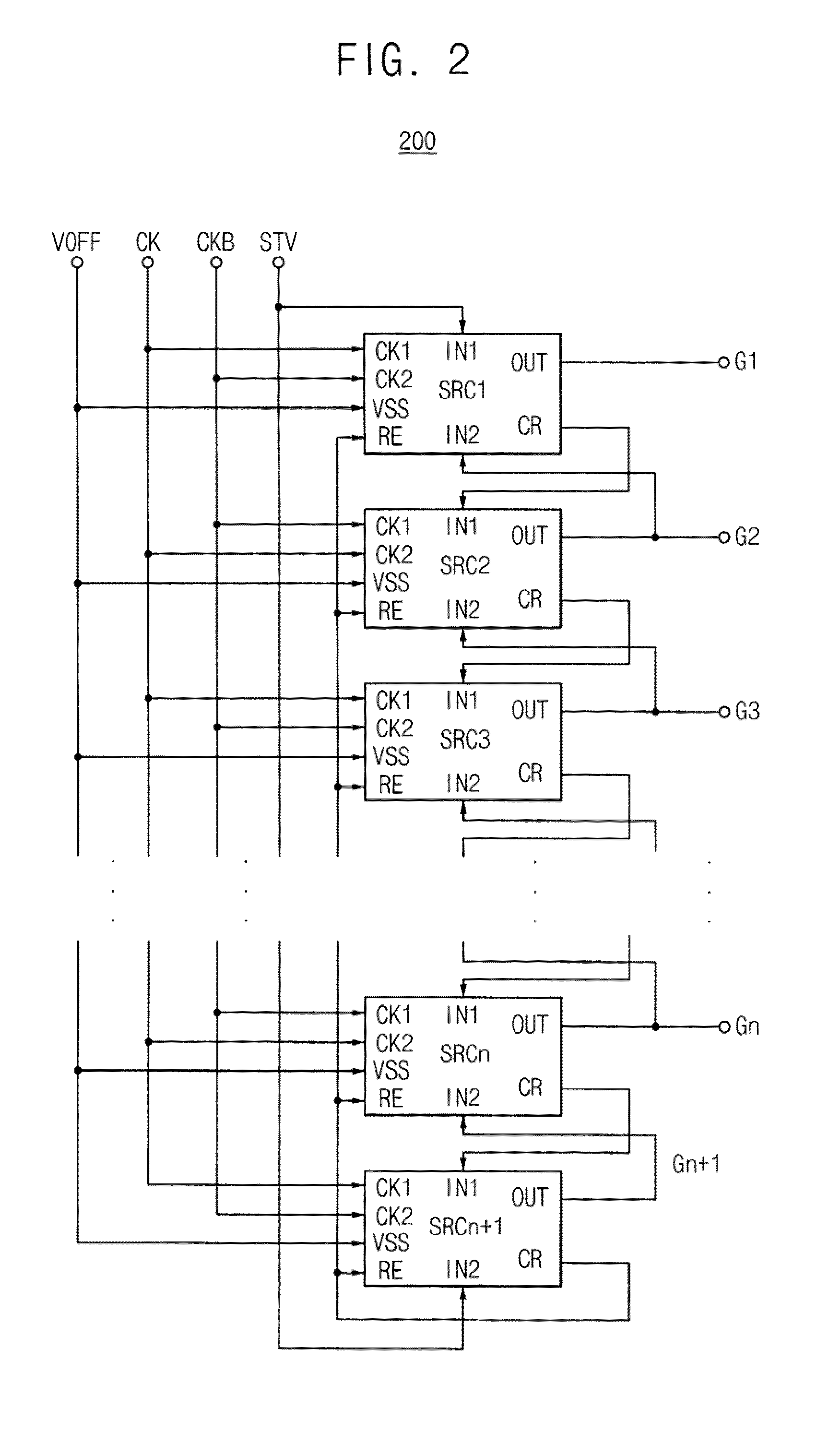

Gate driving circuit and display device having the gate driving circuit

InactiveUS20100164915A1Improve driving reliabilityImprove gate reliabilityCathode-ray tube indicatorsElectric pulse generatorTiming marginShift register

A gate driving circuit includes a first shift register and a second shift register for driving odd gate lines. The first shift register includes a first plurality of cascade-connected stages that sequentially output a plurality of first gate signals. A first stage of the first shift register receives a first vertical start signal. The second shift register includes a second plurality of cascade-connected stages to sequentially output a plurality of second gate signals. The first stage of the second shift register receives an output signal of the first stage of the first shift register as its vertical start signal. A data charging rate may be improved by ensuring the timing margin of each gate signal, so that the driving reliability of the gate driving circuit may be improved.

Owner:SAMSUNG DISPLAY CO LTD

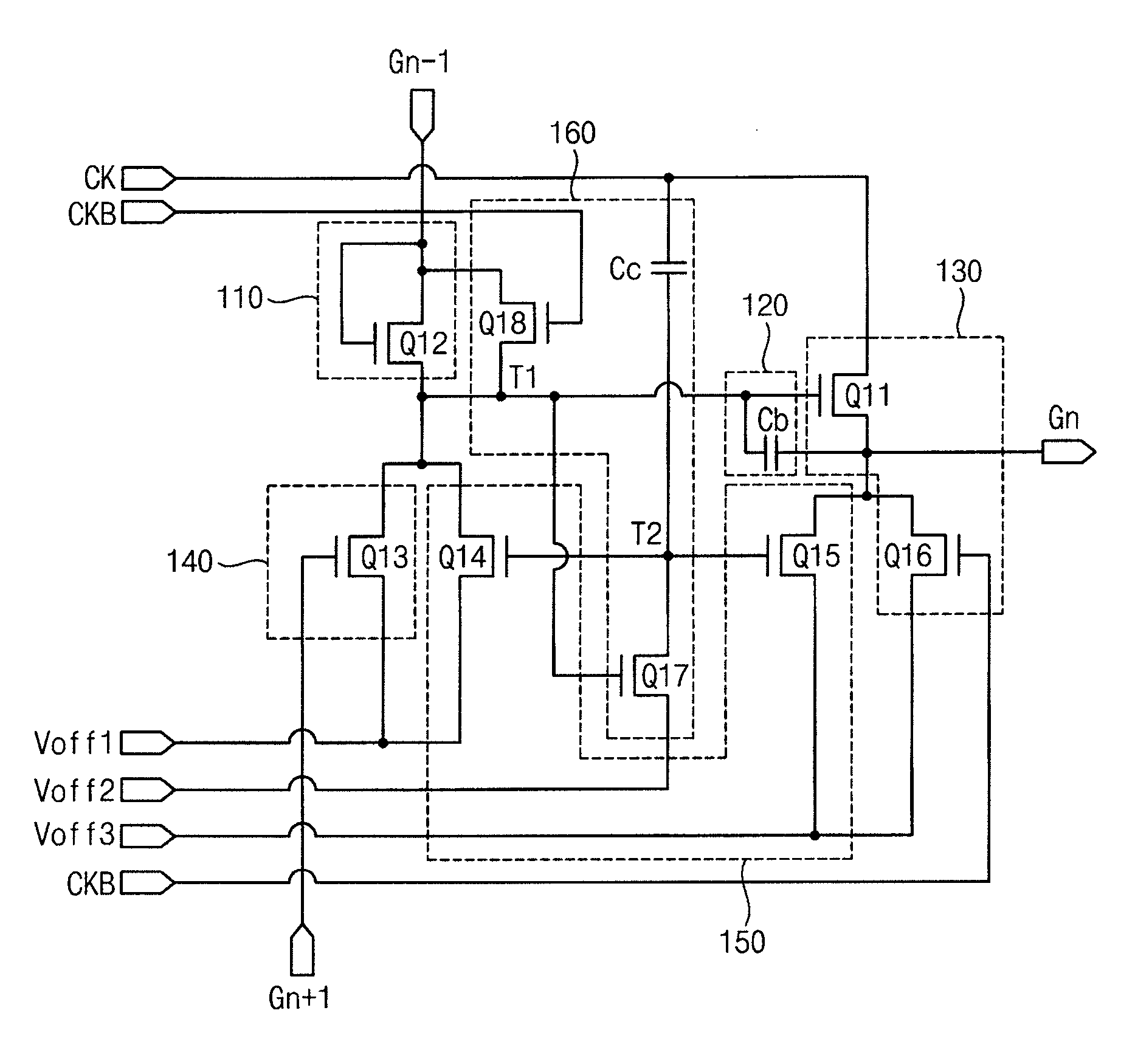

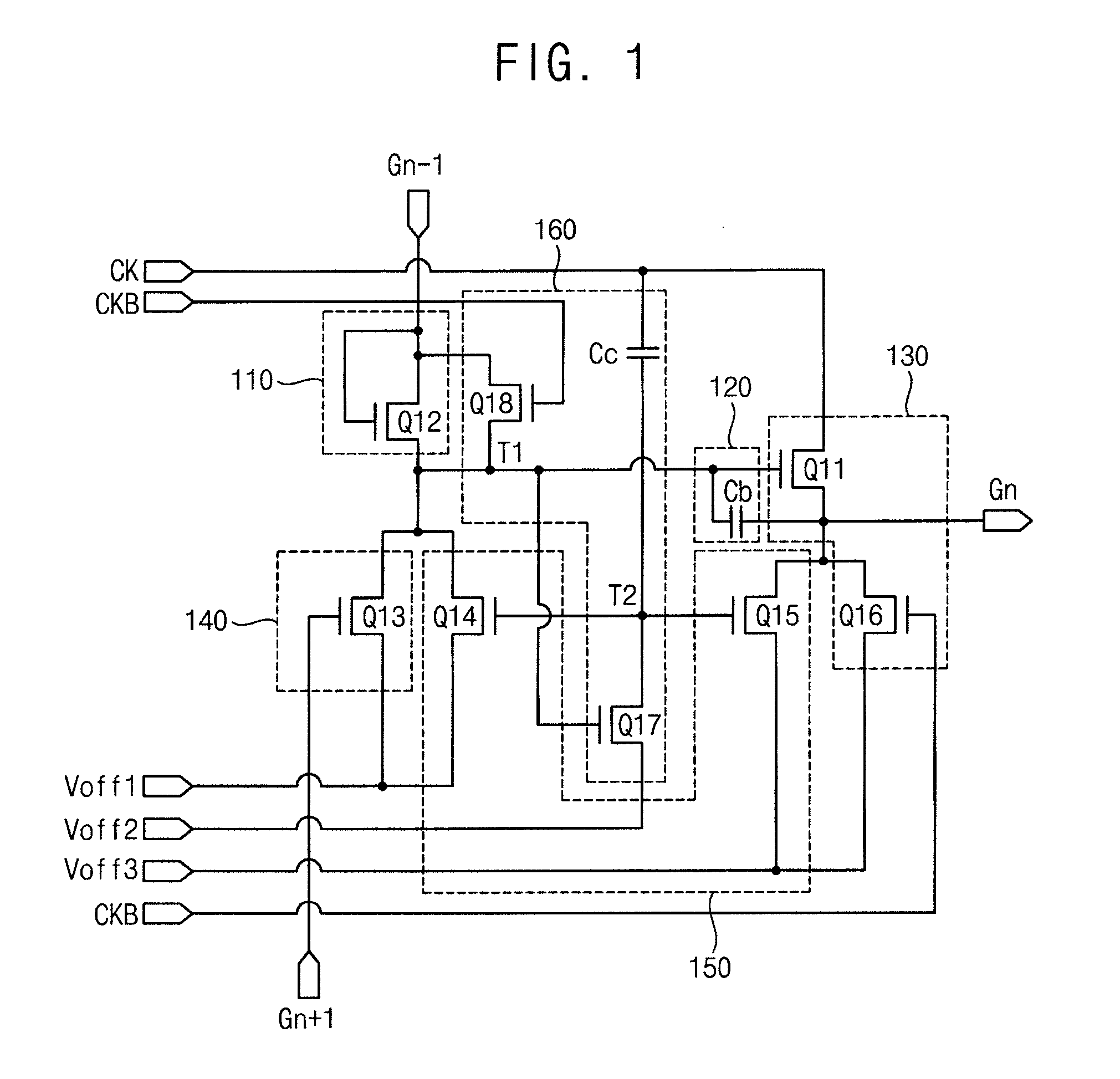

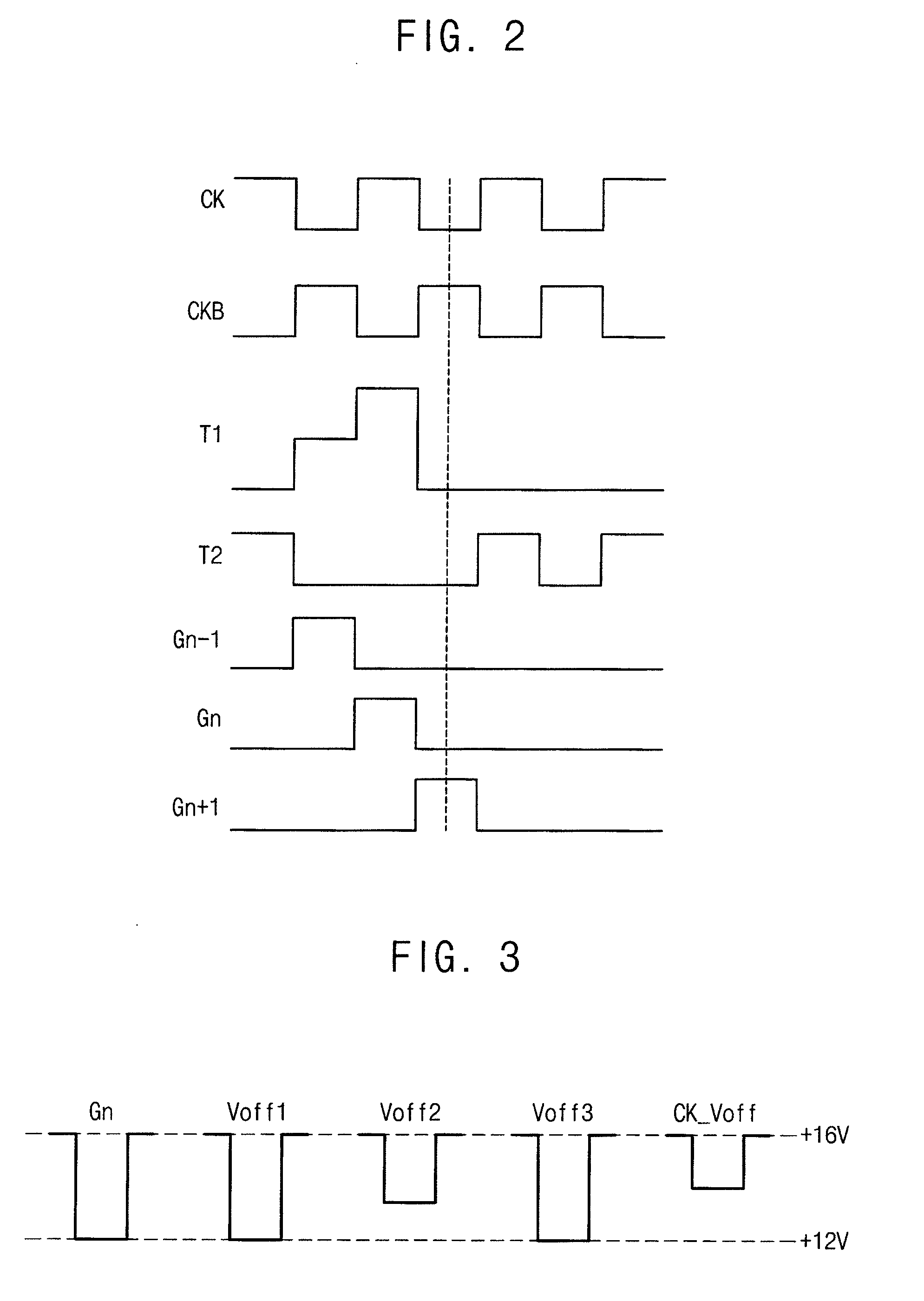

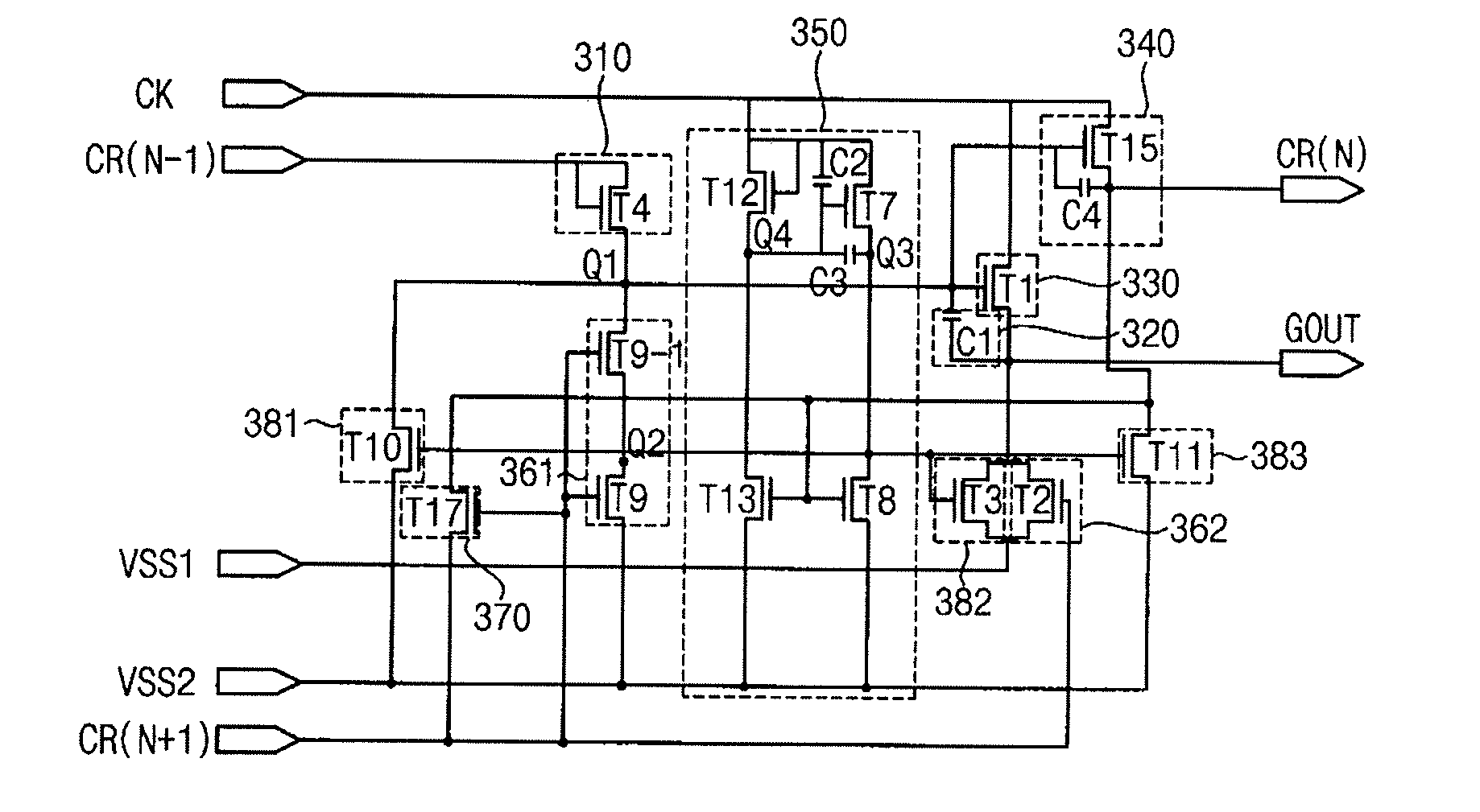

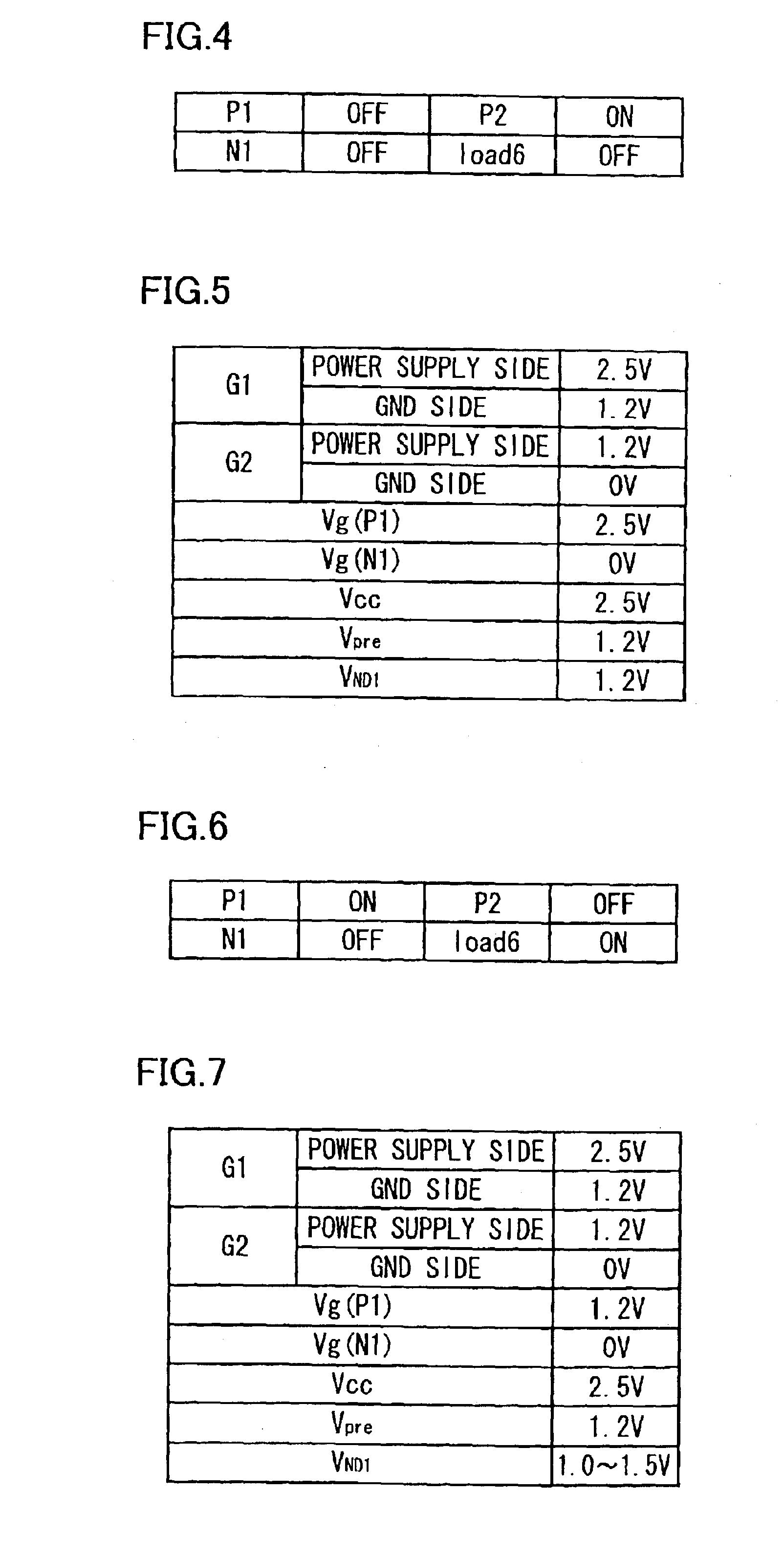

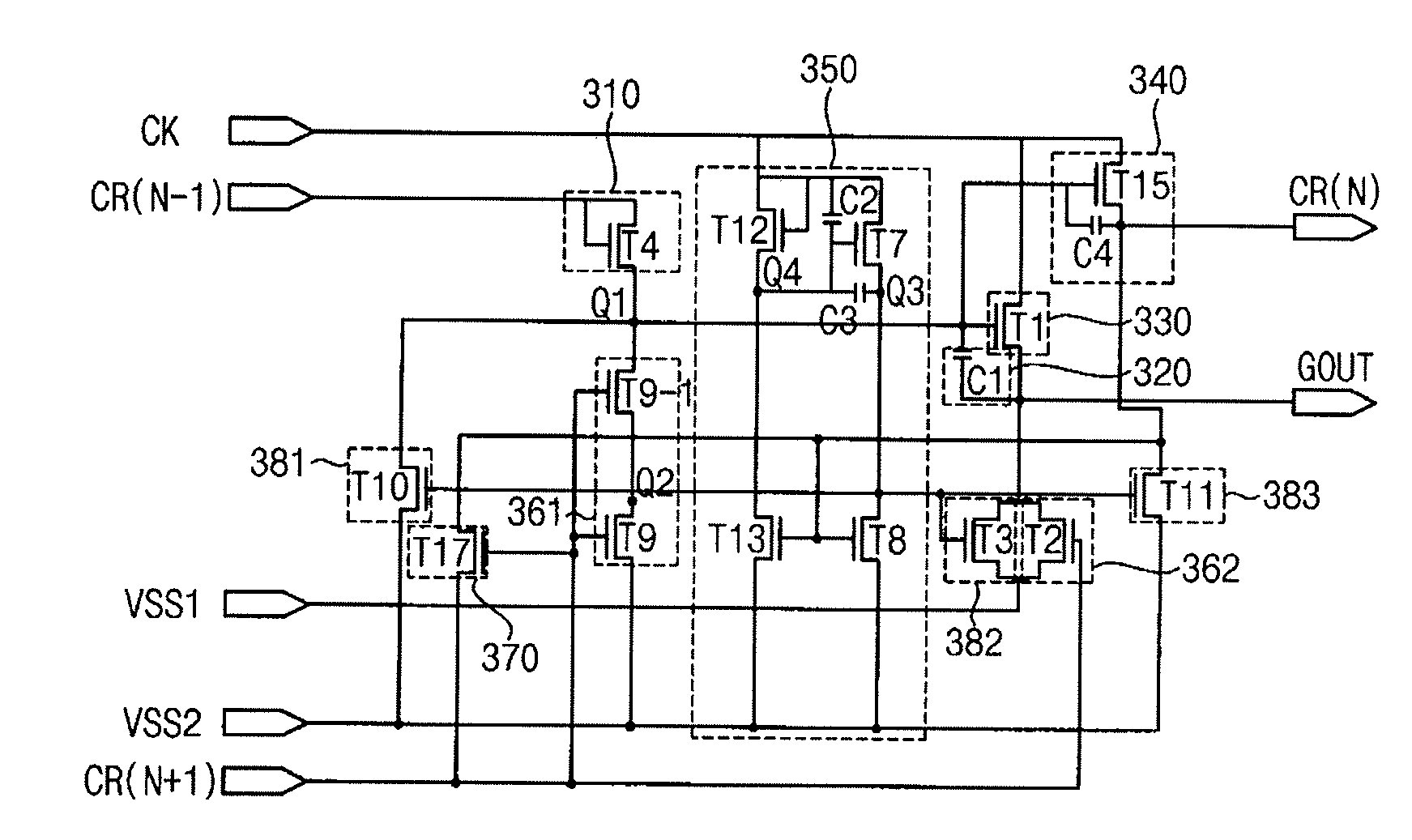

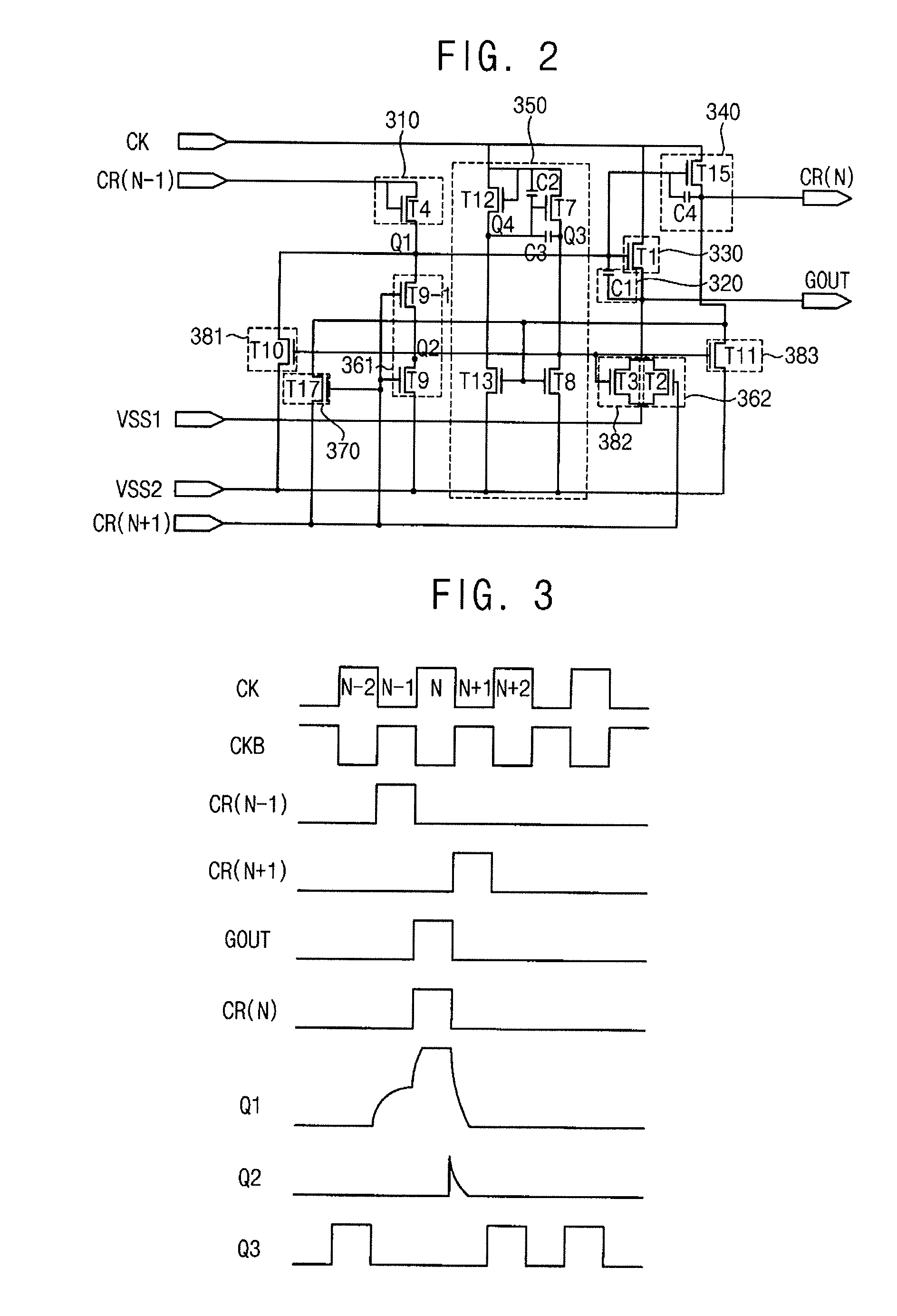

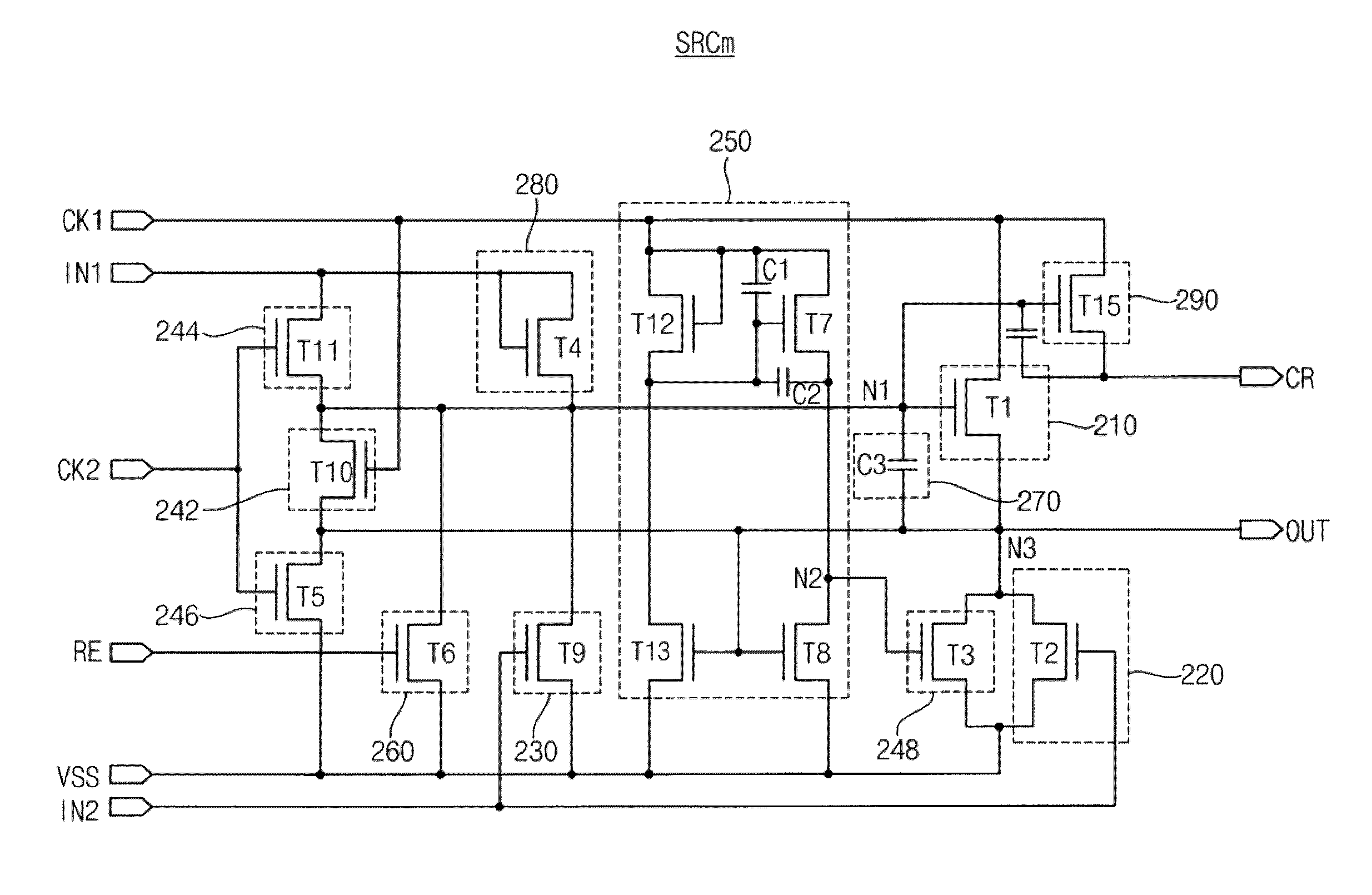

Gate Drive Circuit and Display Apparatus Having the Same

ActiveUS20100171728A1Enhance off-characteristicsImprove gate reliabilityElectric analogue storesElectronic switchingEngineeringClock signal

A gate drive circuit includes a plurality of stages connected one after another to each other. Each of the stages includes a charging section, a driving section, a discharging section, a holding section and a holding control section. The driving section pulls up a high level of a first clock signal to output a gate signal. The discharging section discharges a voltage potential of a first node to a first off-voltage. The holding section holds a voltage potential of the first node to the first off-voltage. The holding control section receives the first clock signal and a second clock signal. The holding control section holds a voltage potential of the holding section to a second off-voltage through a second node in accordance with the second clock signal to prevent floating of the holding section.

Owner:SAMSUNG DISPLAY CO LTD

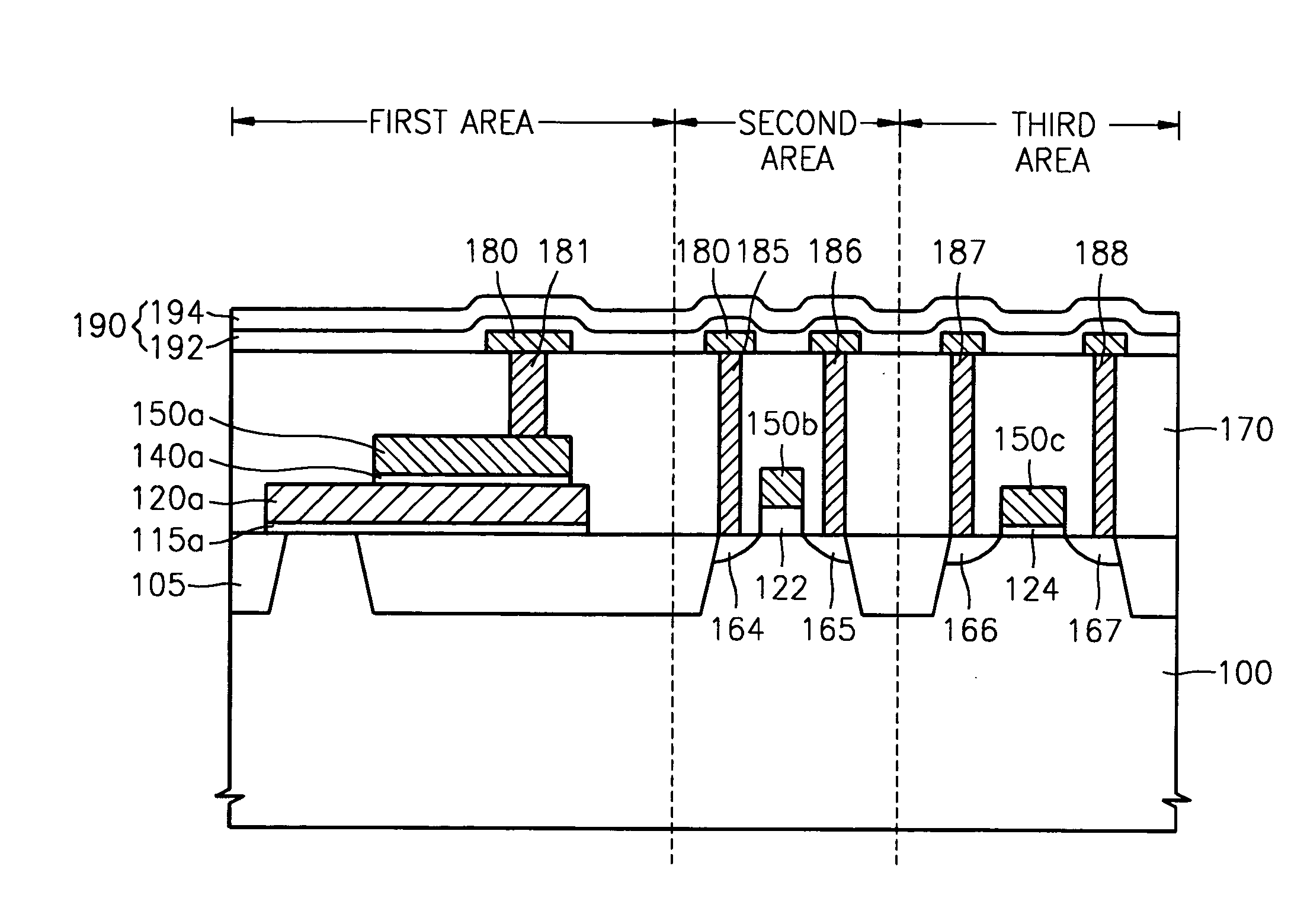

Gate Drive Circuit, Display Device Having the Same and Method of Manufacturing the Gate Drive Circuit

ActiveUS20100164854A1Improve gate reliabilityReduce rippleStatic indicating devicesSolid-state devicesShift registerDisplay device

A gate drive circuit includes a shift register having stages connected to each other in series. An (m)-th stage (‘m’ is a natural number) includes an output part, a discharging part, a first holding part and a second holding part. The output part outputs the first clock signal as a gate signal in response to a first clock signal provided from an external device and discharges the gate signal in response to a second input signal. The output part includes a first transistor having a first channel length. The discharging part discharges a signal of the first node to the second voltage level. The first holding part maintains a signal of the first node at a level of the gate signal, and is discharged to the second voltage level. The first holding part includes a second transistor having a second channel length that is longer than the first channel length. The second holding part maintains a signal of the first node at a level of the second voltage level.

Owner:SAMSUNG DISPLAY CO LTD

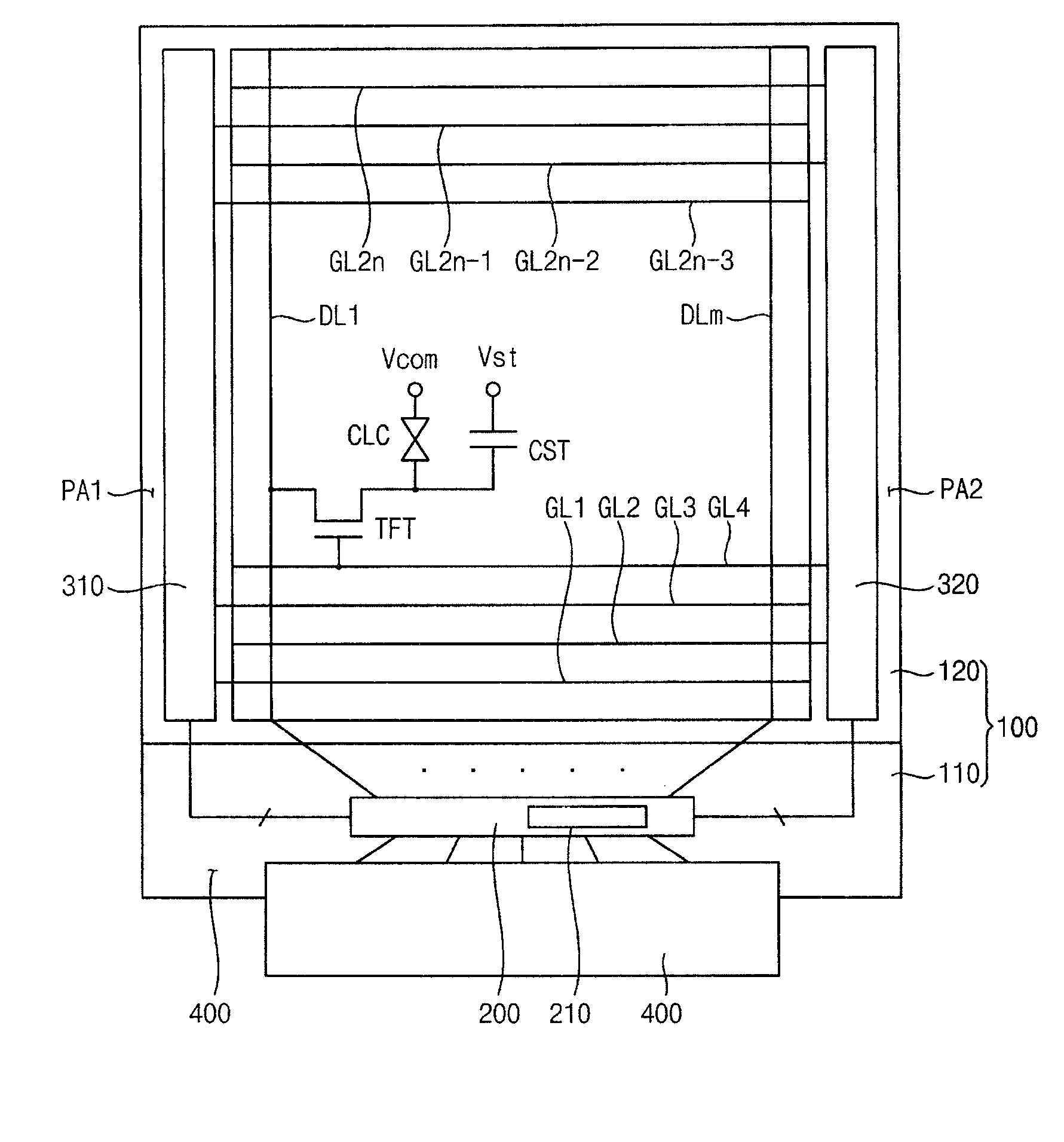

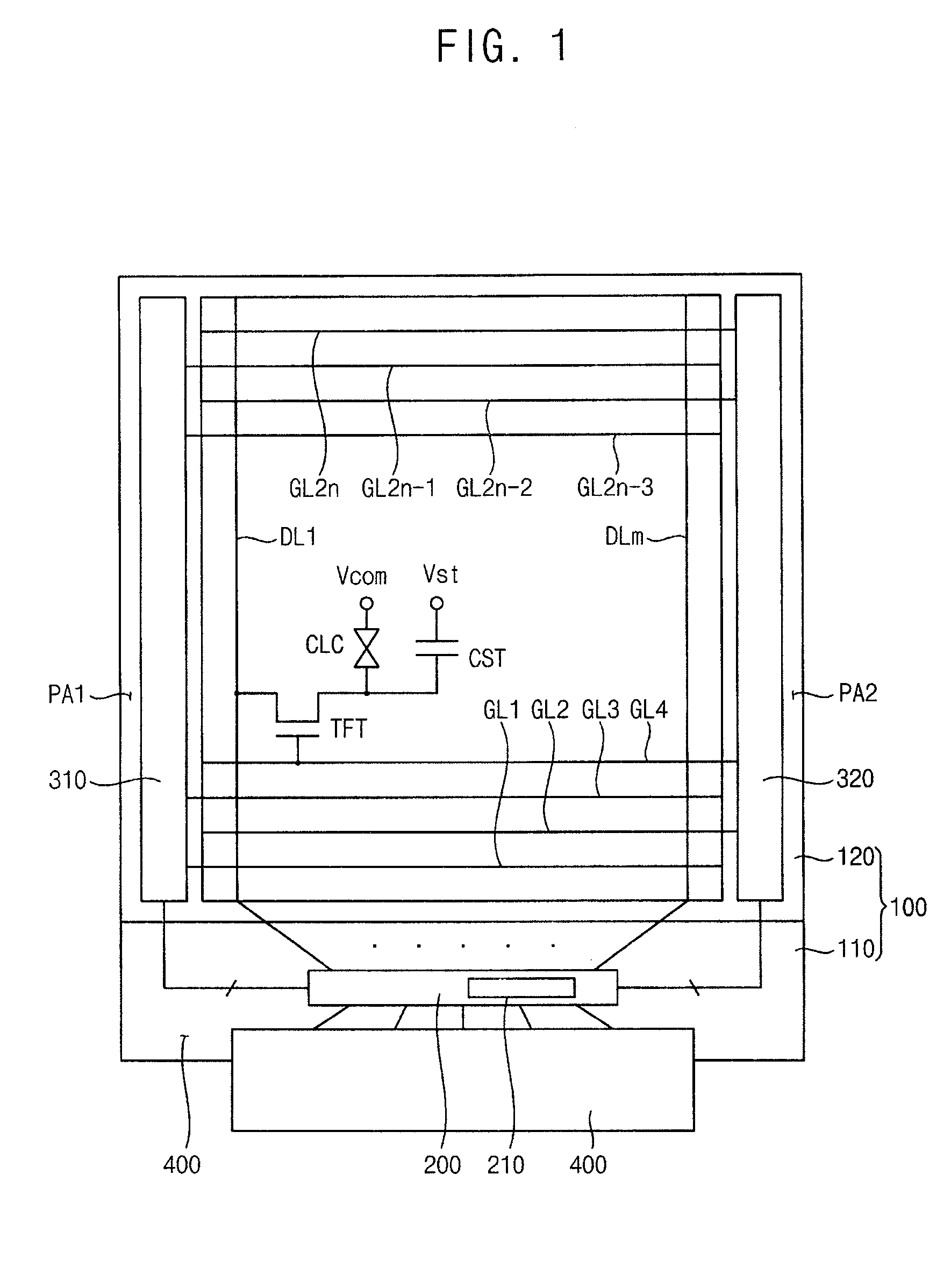

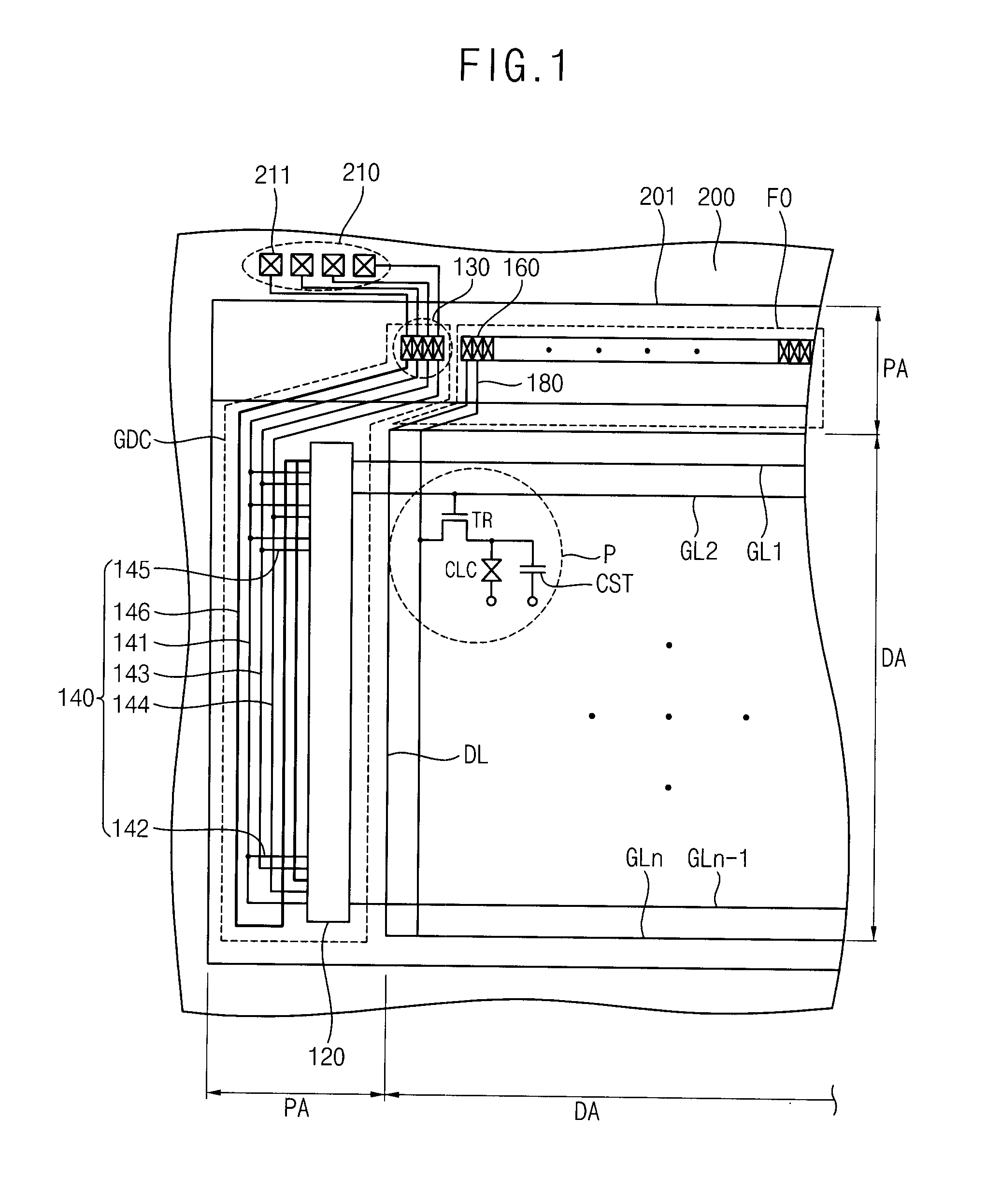

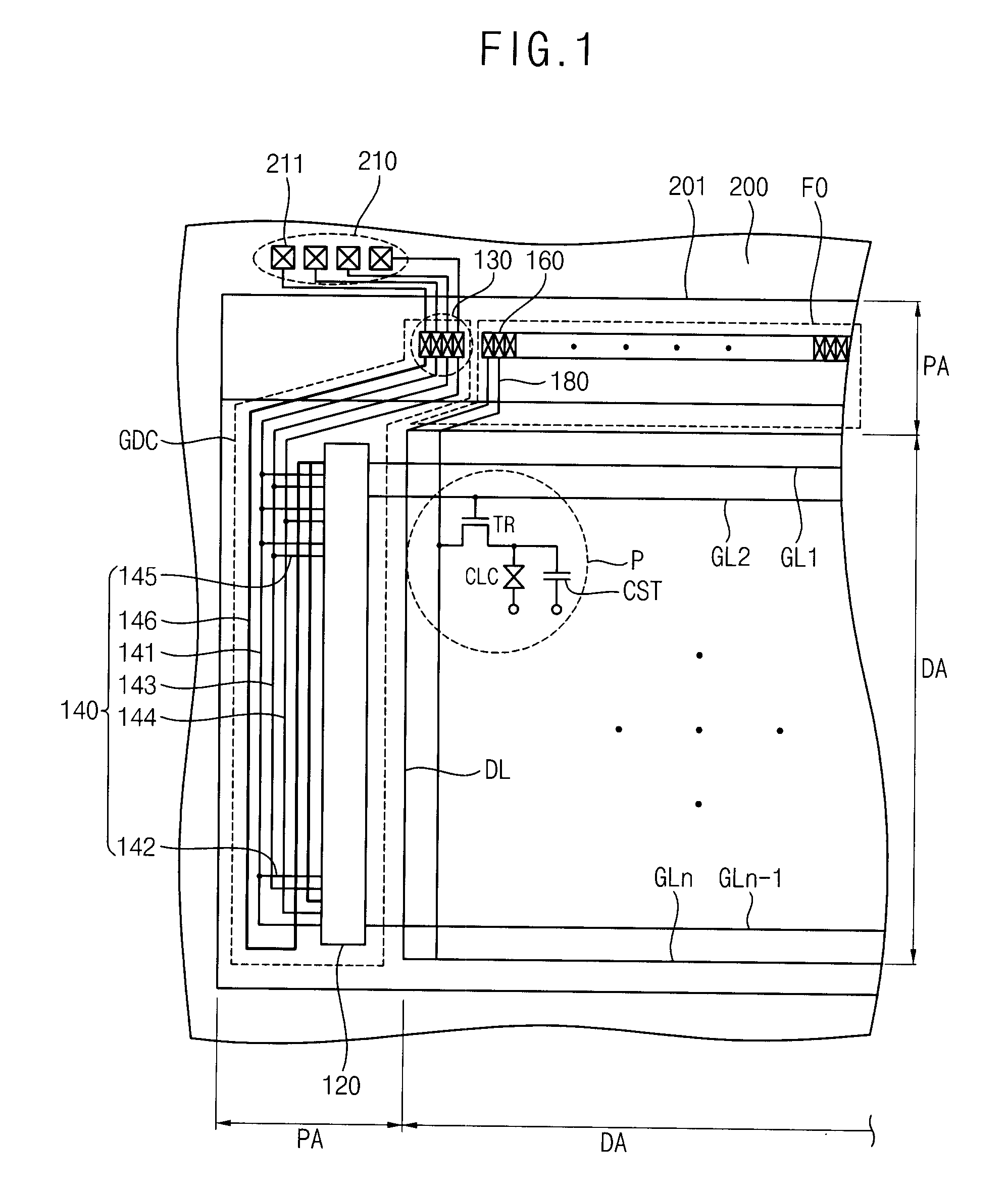

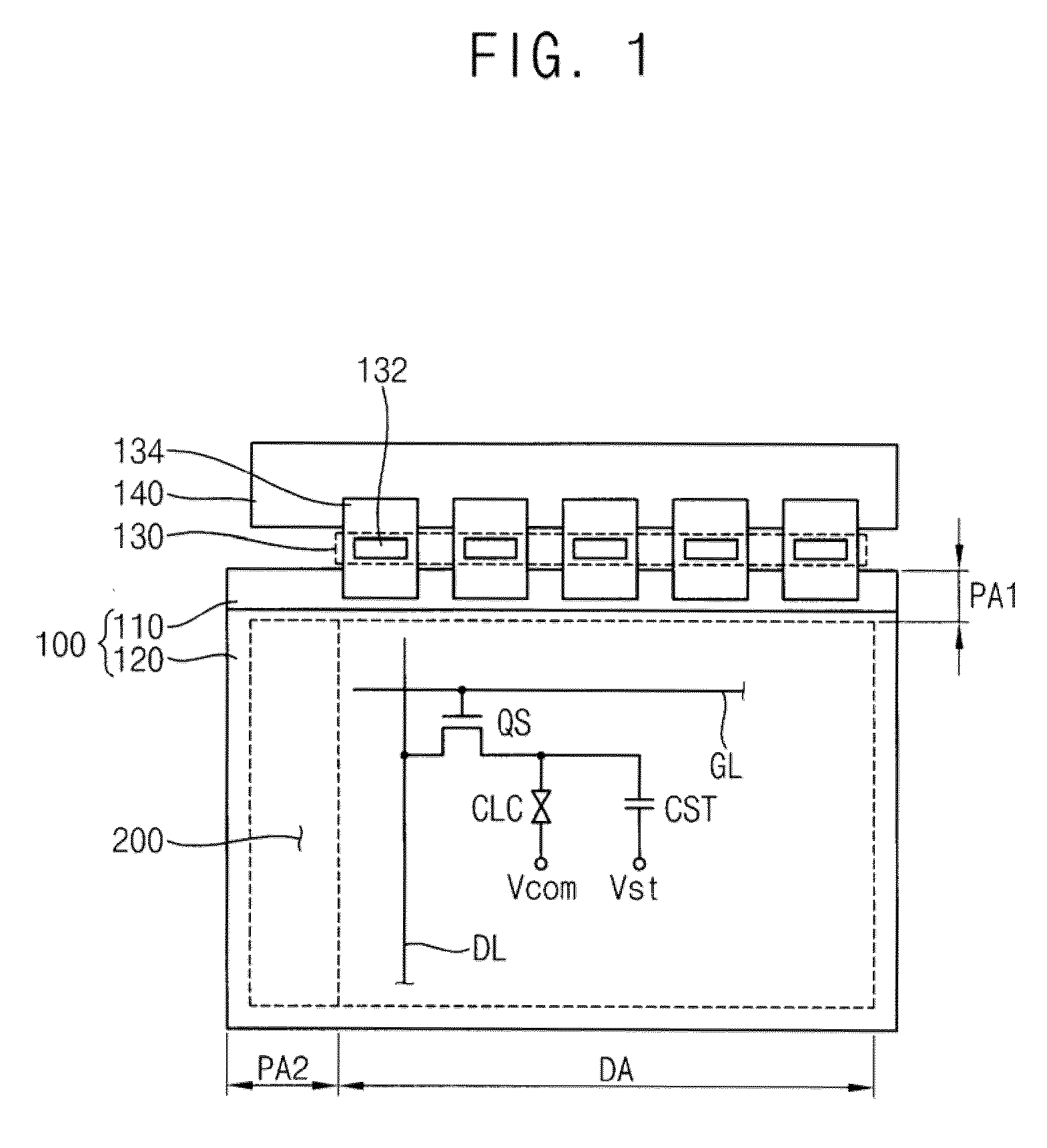

Display substrate and display device having the same

InactiveUS20080018572A1Sufficient marginImprove gate reliabilityStatic indicating devicesNon-linear opticsDisplay deviceEngineering

A display substrate includes gate lines, driving circuit part, signal lines, connection lines and a contact part. Gate lines are formed on a display area and intersect data lines. Driving circuit part is formed on a peripheral area surrounding the display area and provides a gate signal to the gate lines. Signal lines are formed adjacent to the driving circuit part and provide a driving signal to the driving circuit part. Connection lines include a first end portion overlapped the signal lines and a second end portion electrically connected with the driving circuit part. A contact part is formed on the signal lines and connects the first end portion with the signal lines.

Owner:SAMSUNG ELECTRONICS CO LTD

Gate driving circuit and display apparatus having the same

ActiveUS20130181747A1Improve gate reliabilityExtended service lifeStatic indicating devicesDigital storageEngineeringTransistor

A gate driving circuit includes a pull-up control part, a pull-up part, a carry part, a first pull-down part and a second pull-down part. The pull-up control part applies a carry signal from a previous stage to a first node. The pull-up part outputs an N-th gate output signal based on a clock signal. The carry part outputs an N-th carry signal based on the clock signal in response to the signal applied to the first node. The first pull-down part includes a plurality of transistors connected to each other in series. The first pull-down part pulls down a signal at the first node to a second off voltage in response to a carry signal of a next stage. The second pull-down part pulls down the N-th gate output signal to a first off voltage in response to the carry signal of the next stage.

Owner:SAMSUNG DISPLAY CO LTD

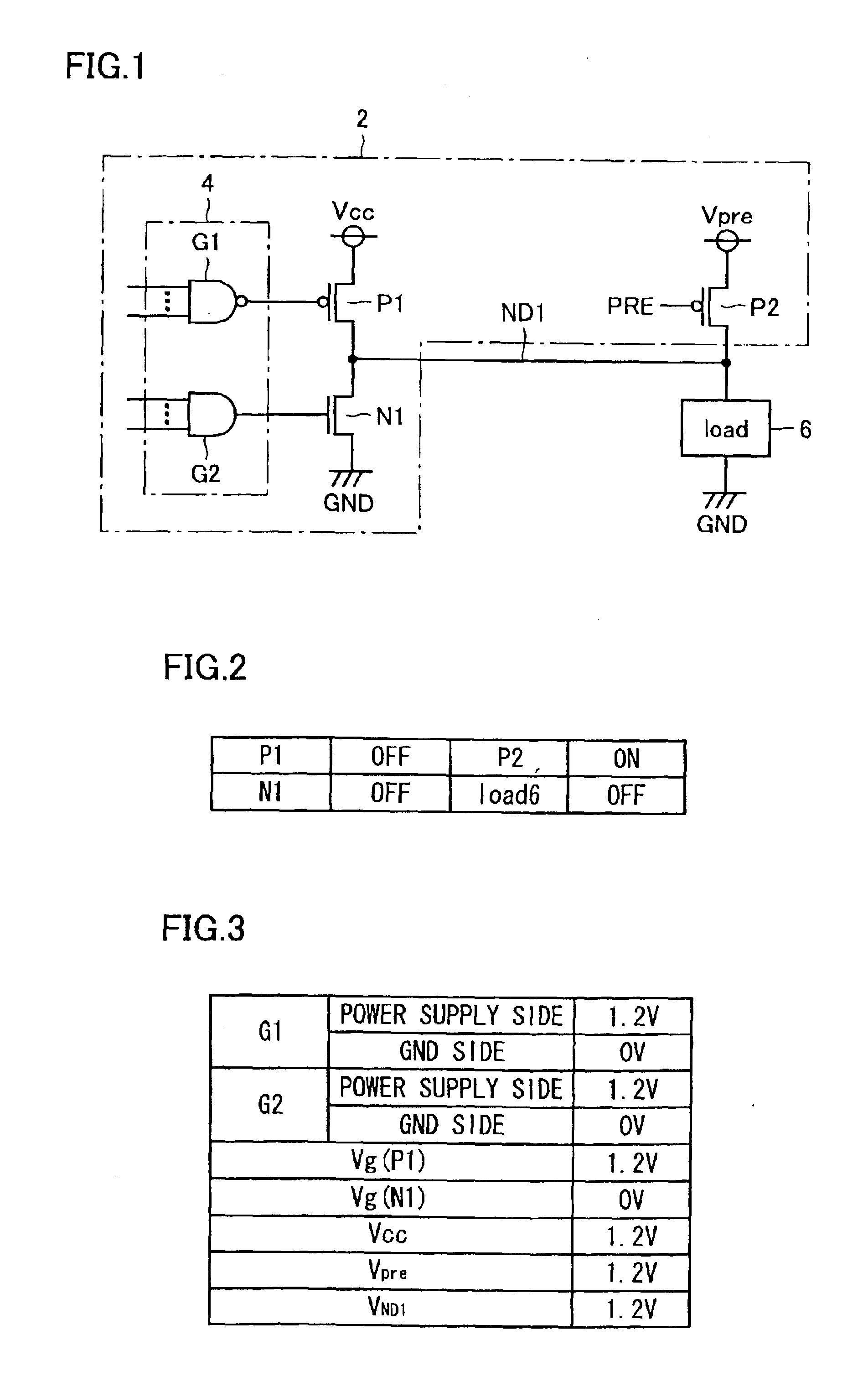

Current drive circuit avoiding effect of voltage drop caused by load and semiconductor memory device equipped therewith

InactiveUS6879513B2Decreasing drive currentImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingLoad circuitDriving current

A current drive circuit operates receiving higher voltage than in a waiting mode at source terminal of a P-channel first driver transistor, when supplying a current to a node connected to a load circuit. In accordance with the rising source potential of the first driver transistor, the gate potential output to the first driver transistor by a gate potential control circuit rises. When the first and second driver transistors are off, a precharge circuit configured with a P-channel MOS transistor precharges the node to a prescribed potential. As a result, the current drive circuit is provided with increased reliability of the gate insulating films of the driver transistors without decreasing the driving current.

Owner:RENESAS ELECTRONICS CORP

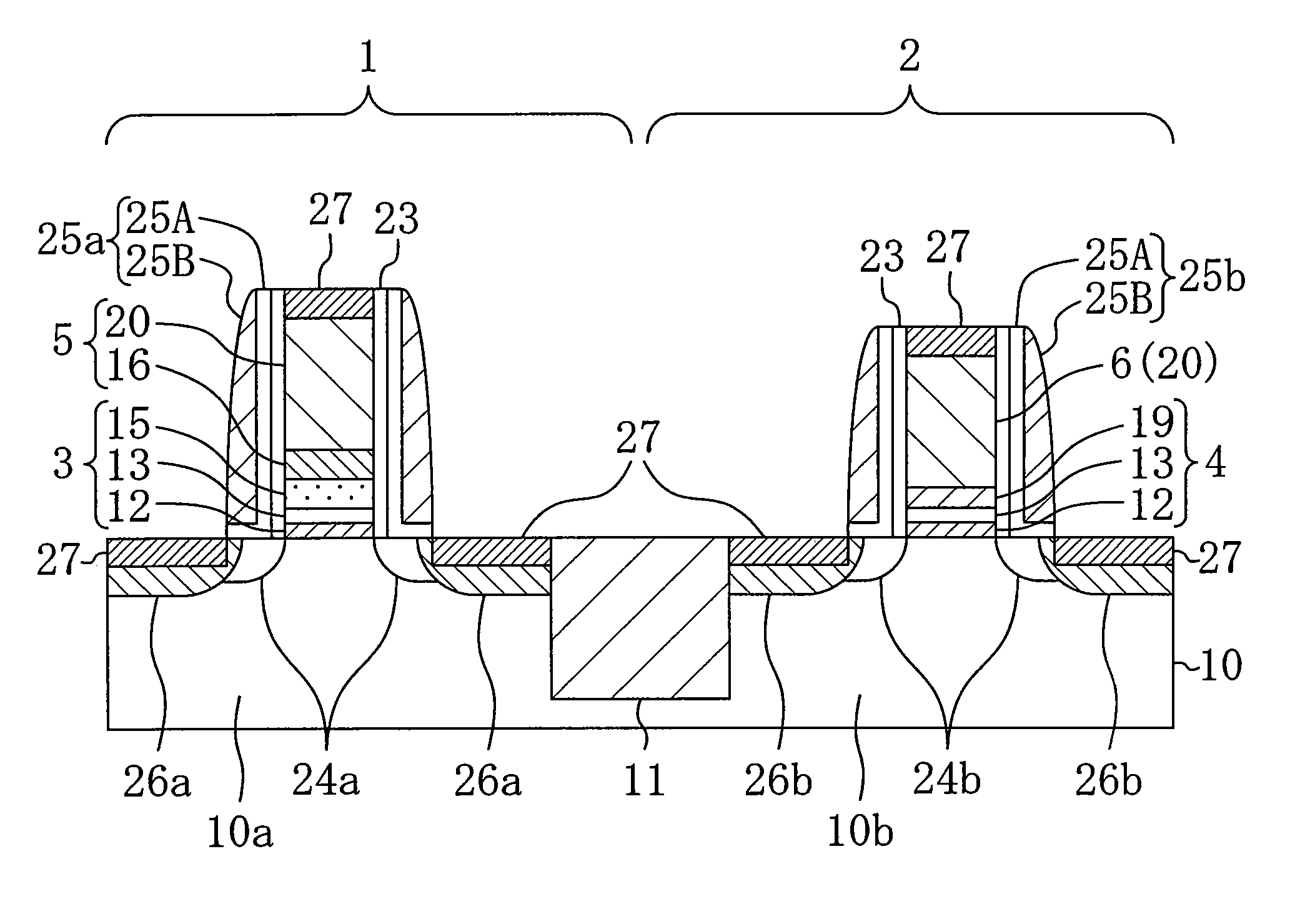

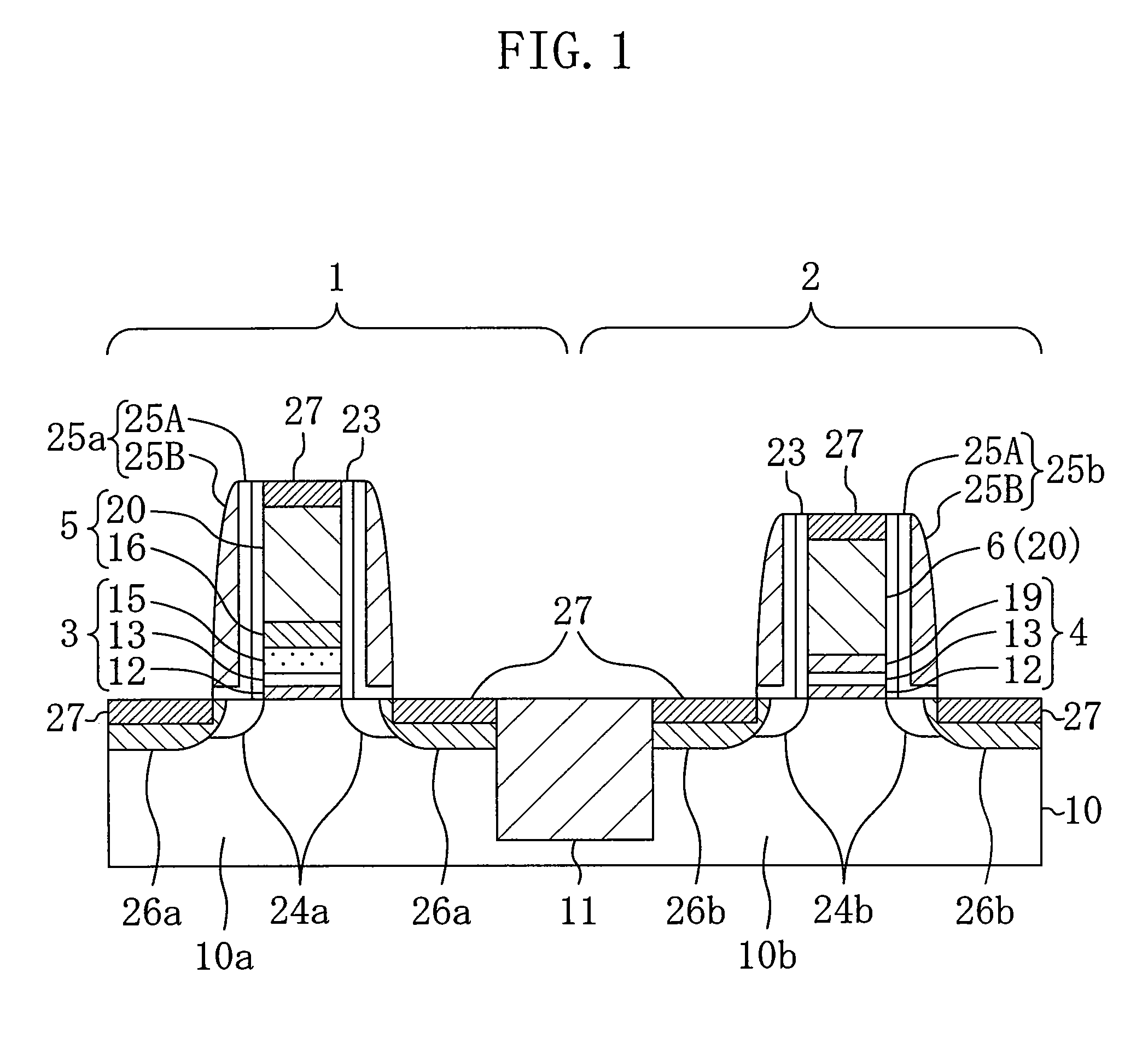

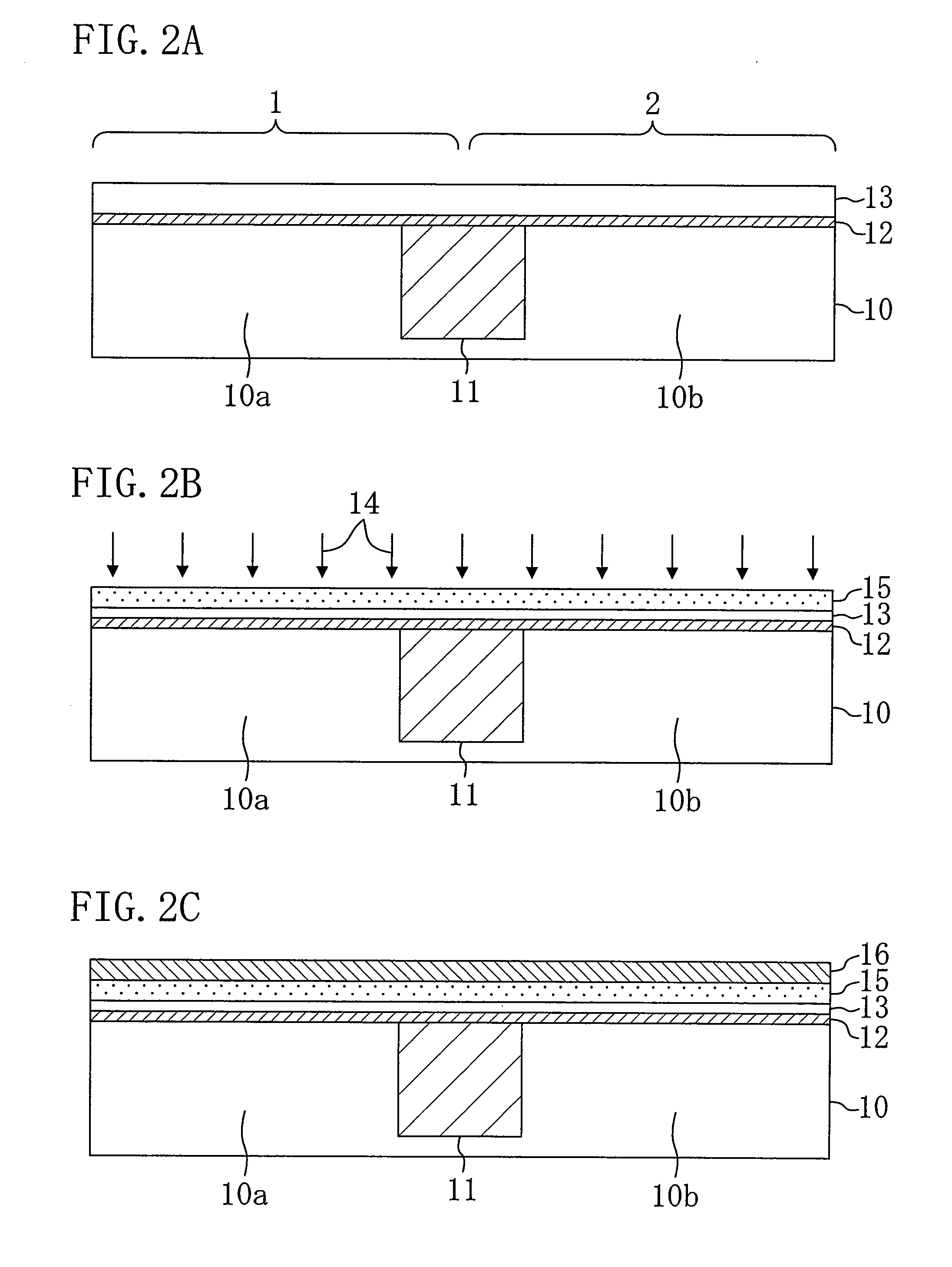

Semiconductor device and method for fabricating the same

ActiveUS20090039437A1Process safety and stabilityEasy to getTransistorSolid-state devicesDevice materialSemiconductor

A semiconductor device includes a first gate electrode formed in a first region on a semiconductor substrate with a first gate insulating film sandwiched therebetween; and a second gate electrode formed in a second region on the semiconductor substrate with a second gate insulating film sandwiched therebetween. The first gate insulating film includes a first high dielectric constant insulating film with a first nitrogen concentration and the second gate insulating film includes a second high dielectric constant insulating film with a second nitrogen concentration higher than the first nitrogen concentration.

Owner:PANNOVA SEMIC

P-channel power MIS field effect transistor and switching circuit

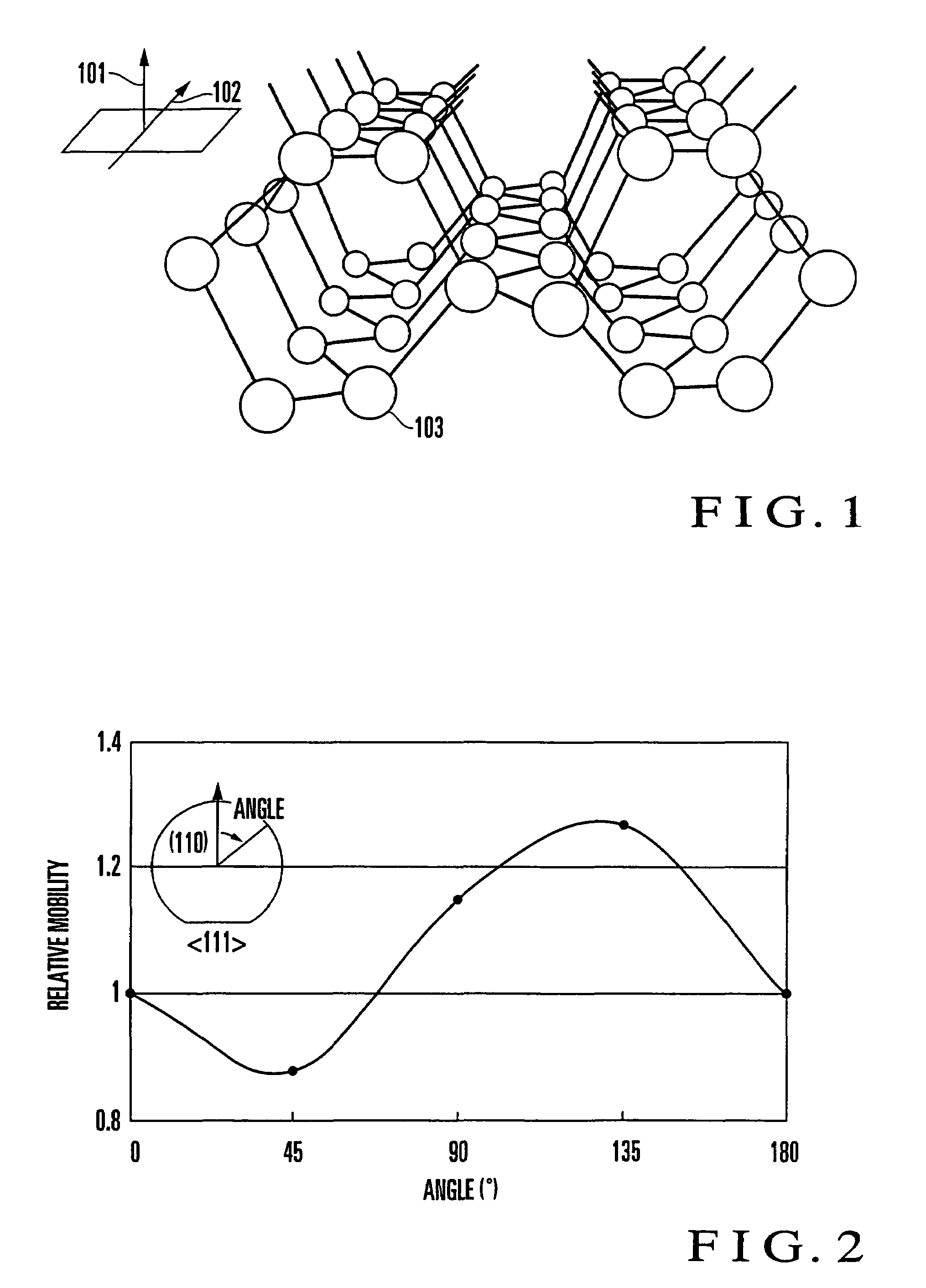

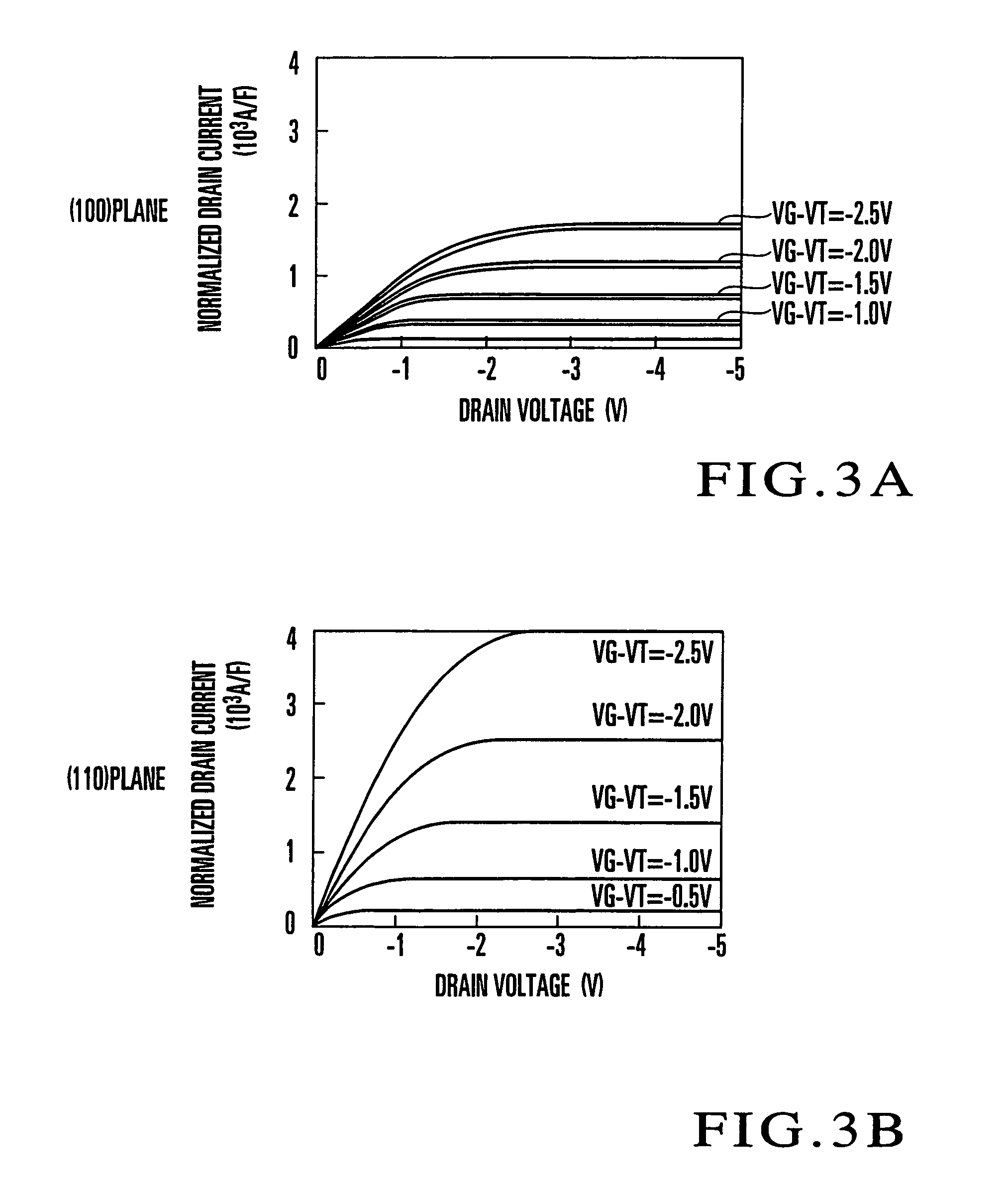

InactiveUS7663195B2Improve flatnessImprove drivabilitySemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorP channel

In a P-channel power MIS field effect transistor formed on a silicon surface having substantially a (110) plane, a gate insulation film is used which provides a gate-to-source breakdown voltage of 10 V or more, and planarizes the silicon surface, or contains Kr, Ar, or Xe.

Owner:OHMI TADAHIRO +1

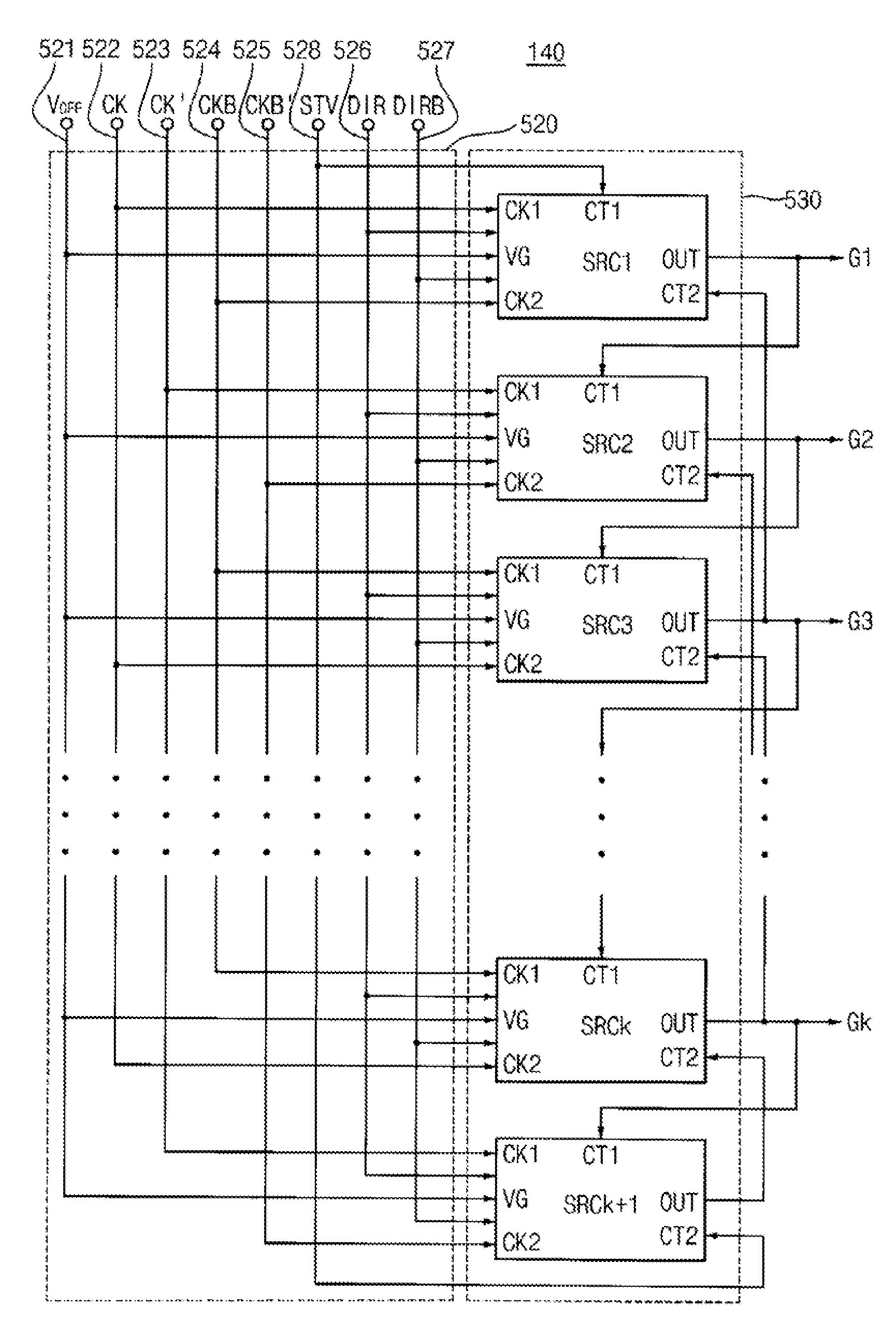

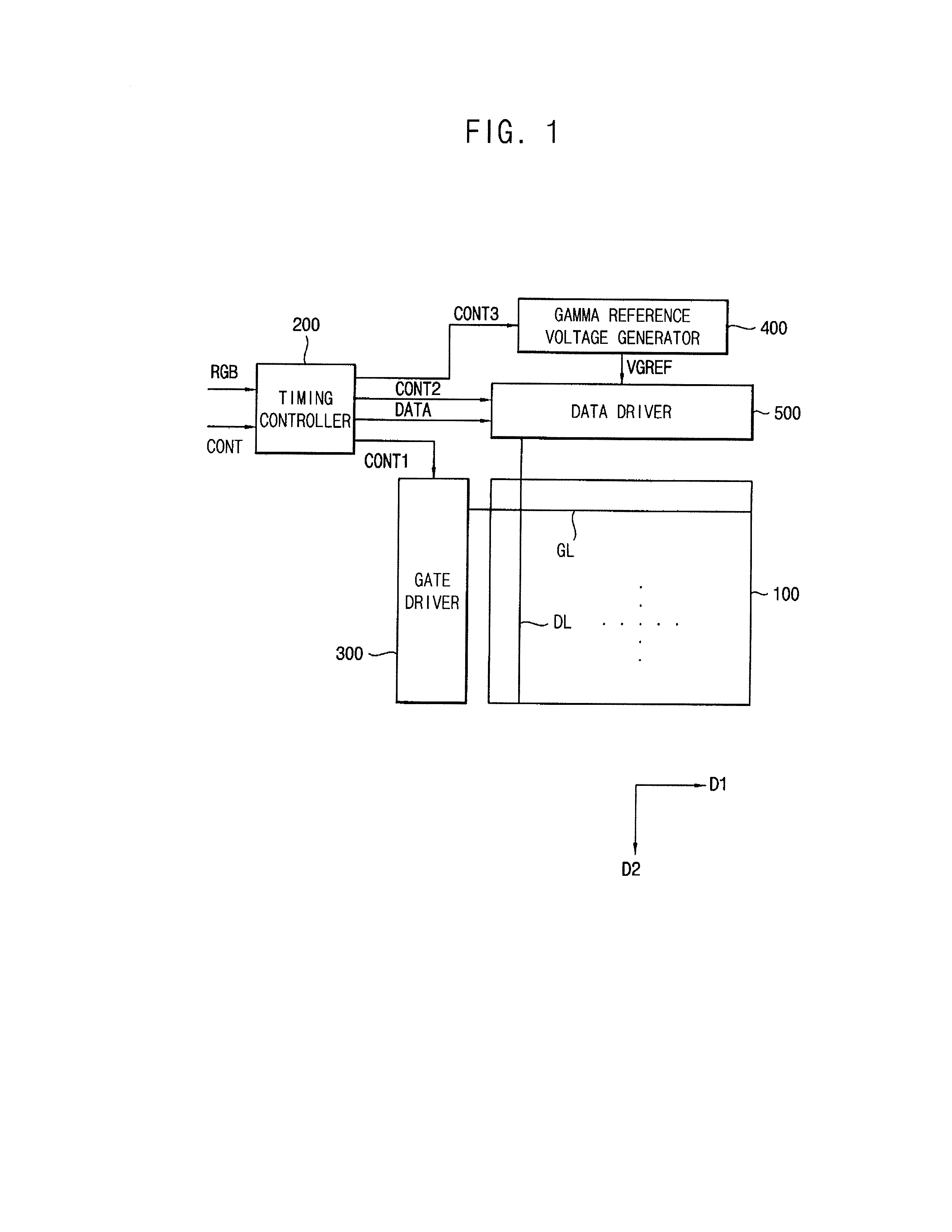

Gate drive circuit, display substrate having the same, and method thereof

ActiveUS20090115690A1Improve driving reliabilityWeaken energyStatic indicating devicesSolid-state devicesElectricityShift register

A gate drive circuit includes a shift register, a clock wiring and a start wiring. The shift resister includes a plurality of stages arranged in a first direction on a base substrate to output a plurality of gate signals. The clock wiring is extended along the first direction. The clock wiring is electrically connected to a plurality of clock connecting wirings extended in a second direction crossing the first direction to deliver a clock signal to the stages. The start wiring includes a first wiring extended along the first direction and a second wiring connected to the first wiring and extended in the first direction to cross with the clock connecting wirings so as to deliver a vertical start signal to a first stage. Therefore, a structure of a signal wiring delivering a vertical start signal is changed, thereby protecting the gate drive circuit from static electricity.

Owner:SAMSUNG DISPLAY CO LTD

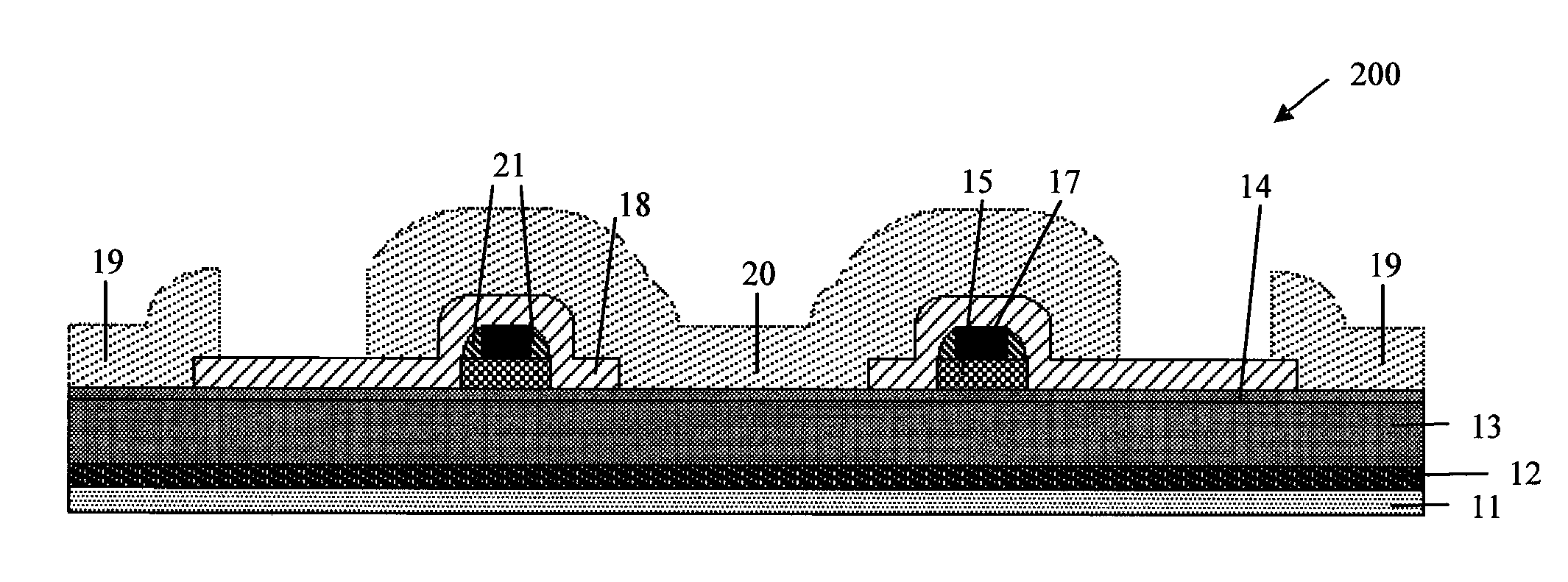

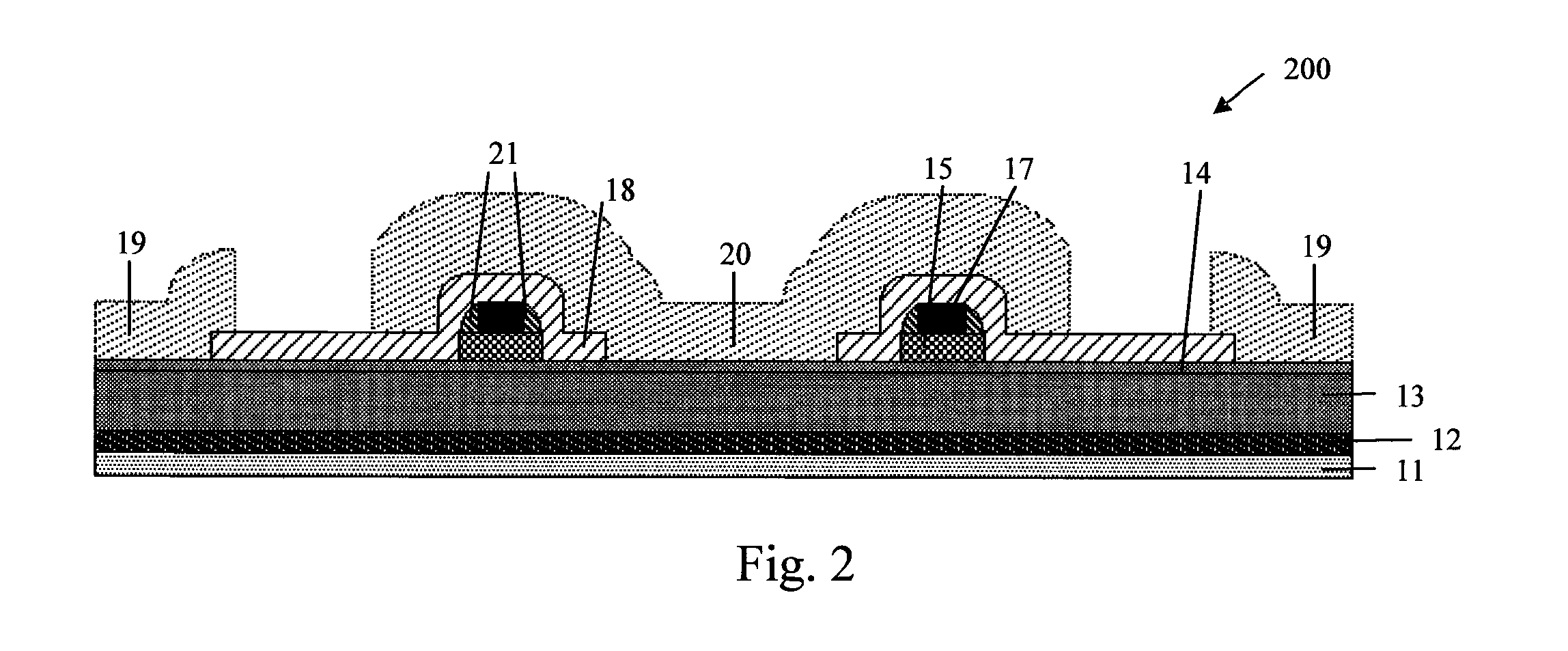

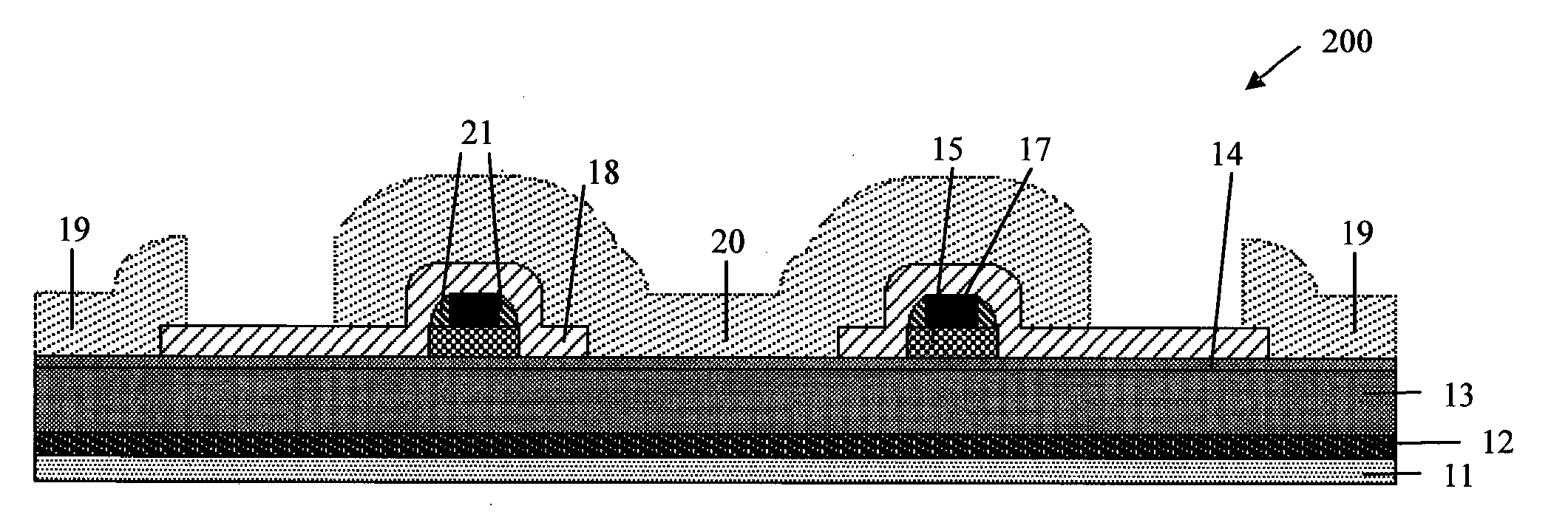

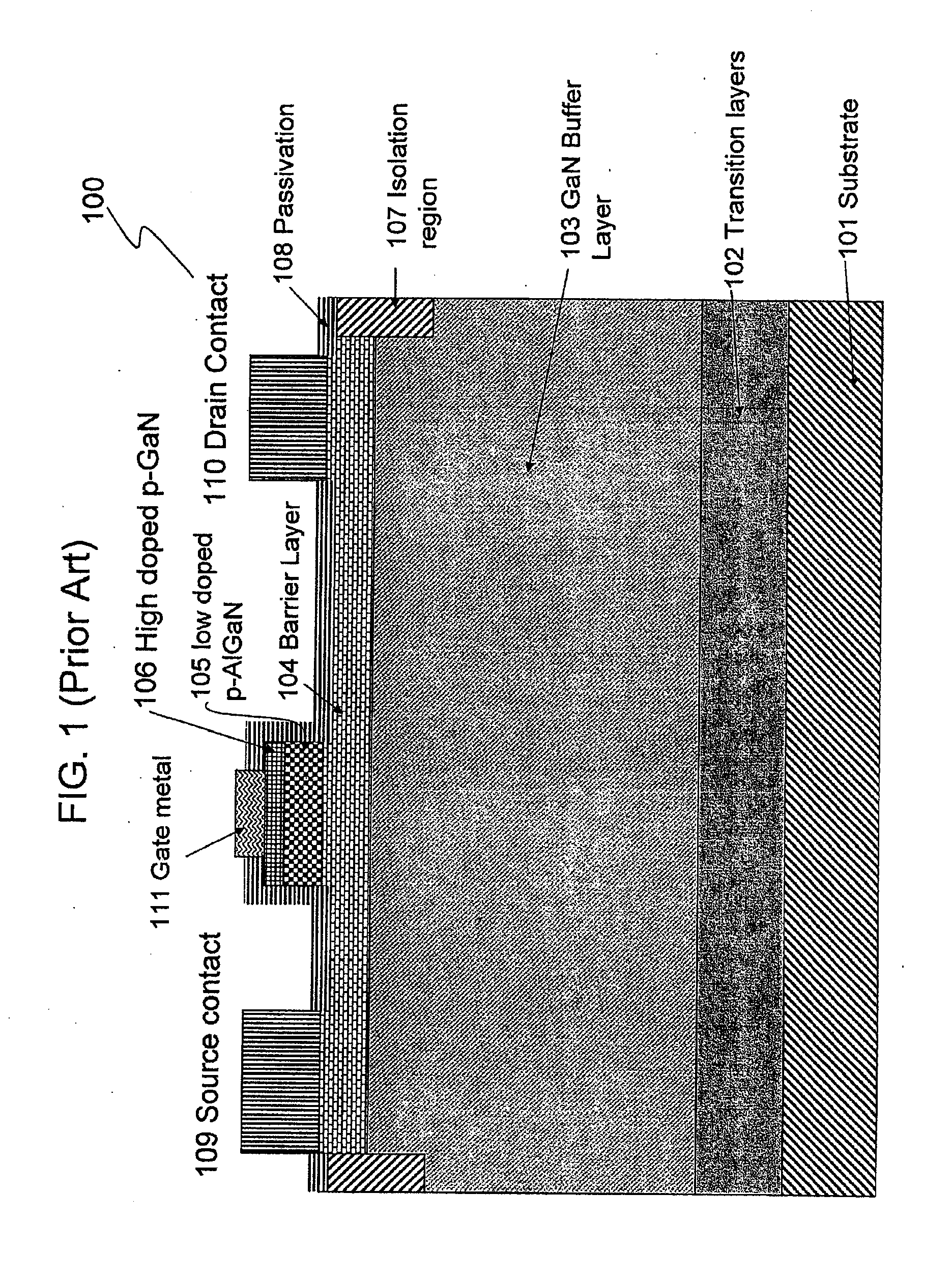

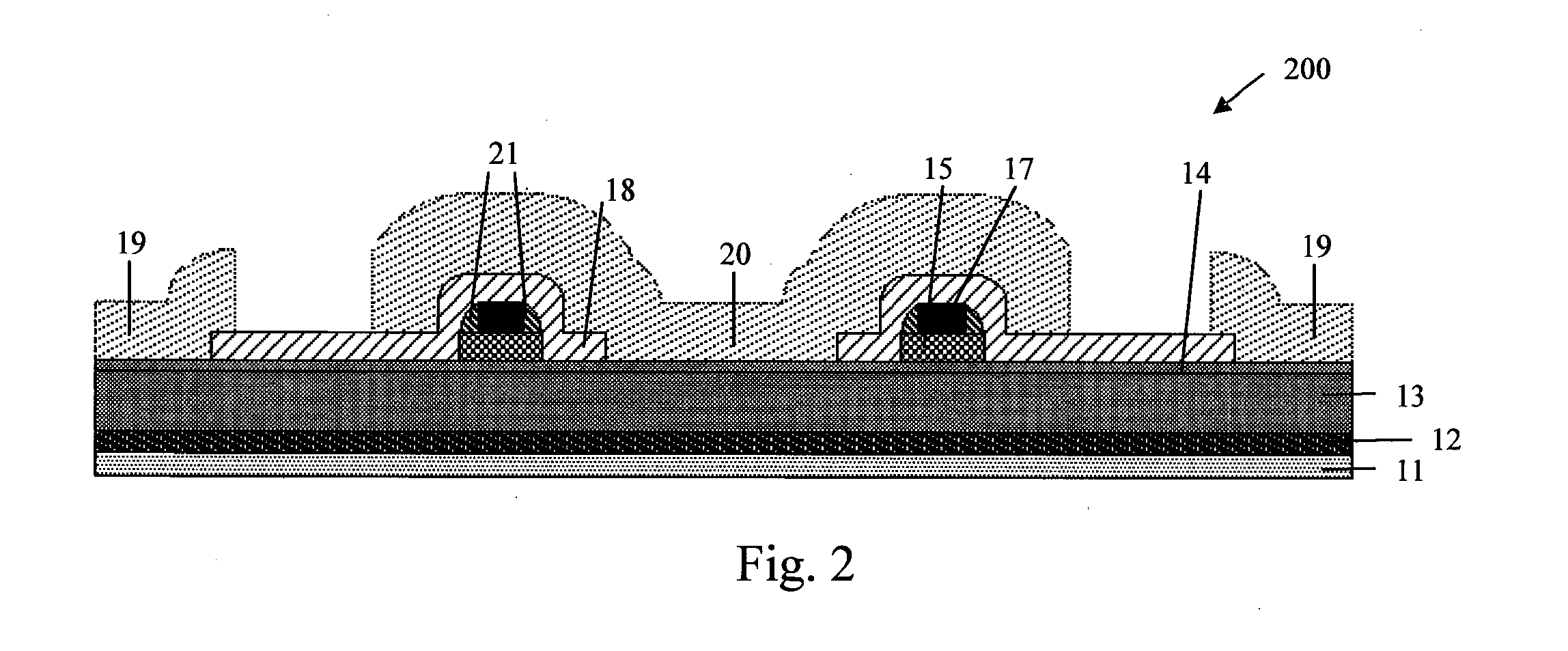

Enhancement mode GaN HEMT device with gate spacer and method for fabricating the same

ActiveUS8823012B2Reduce leakageReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesGate leakage currentOhmic contact

Enhancement-mode GaN devices having a gate spacer, a gate metal material and a gate compound that are self-aligned, and a methods of forming the same. The materials are patterned and etched using a single photo mask, which reduces manufacturing costs. An interface of the gate spacer and the gate compound has lower leakage than the interface of a dielectric film and the gate compound, thereby reducing gate leakage. In addition, an ohmic contact metal layer is used as a field plate to relieve the electric field at a doped III-V gate compound corner towards the drain contact, which leads to lower gate leakage current and improved gate reliability.

Owner:EFFICIENT POWER CONVERSION CORP

Low-K gate spacers by fluorine implantation

ActiveUS7227230B2Reduce capacitanceReduce overlap capacitanceTransistorSolid-state devicesMOSFETPhysics

A MOSFET device and a method of fabricating a MOSFET device having low-K dielectric oxide gate sidewall spacers produced by fluorine implantation. The present invention implants fluorine into the gate oxide sidewall spacers which is used to alter the properties of advanced composite gate dielectrics e.g. nitridized oxides, NO, and gate sidewall dielectrics, such that the low-K properties of fluorine are used to develop low parasitic capacitance MOSFETs.

Owner:GLOBALFOUNDRIES US INC

Gate drive circuit and display apparatus having the same

ActiveUS8643584B2Enhance off-characteristicsImprove gate reliabilityElectric analogue storesElectronic switchingDriving circuitClock signal

A gate drive circuit includes a plurality of stages connected one after another to each other. Each of the stages includes a charging section, a driving section, a discharging section, a holding section and a holding control section. The driving section pulls up a high level of a first clock signal to output a gate signal. The discharging section discharges a voltage potential of a first node to a first off-voltage. The holding section holds a voltage potential of the first node to the first off-voltage. The holding control section receives the first clock signal and a second clock signal. The holding control section holds a voltage potential of the holding section to a second off-voltage through a second node in accordance with the second clock signal to prevent floating of the holding section.

Owner:SAMSUNG DISPLAY CO LTD

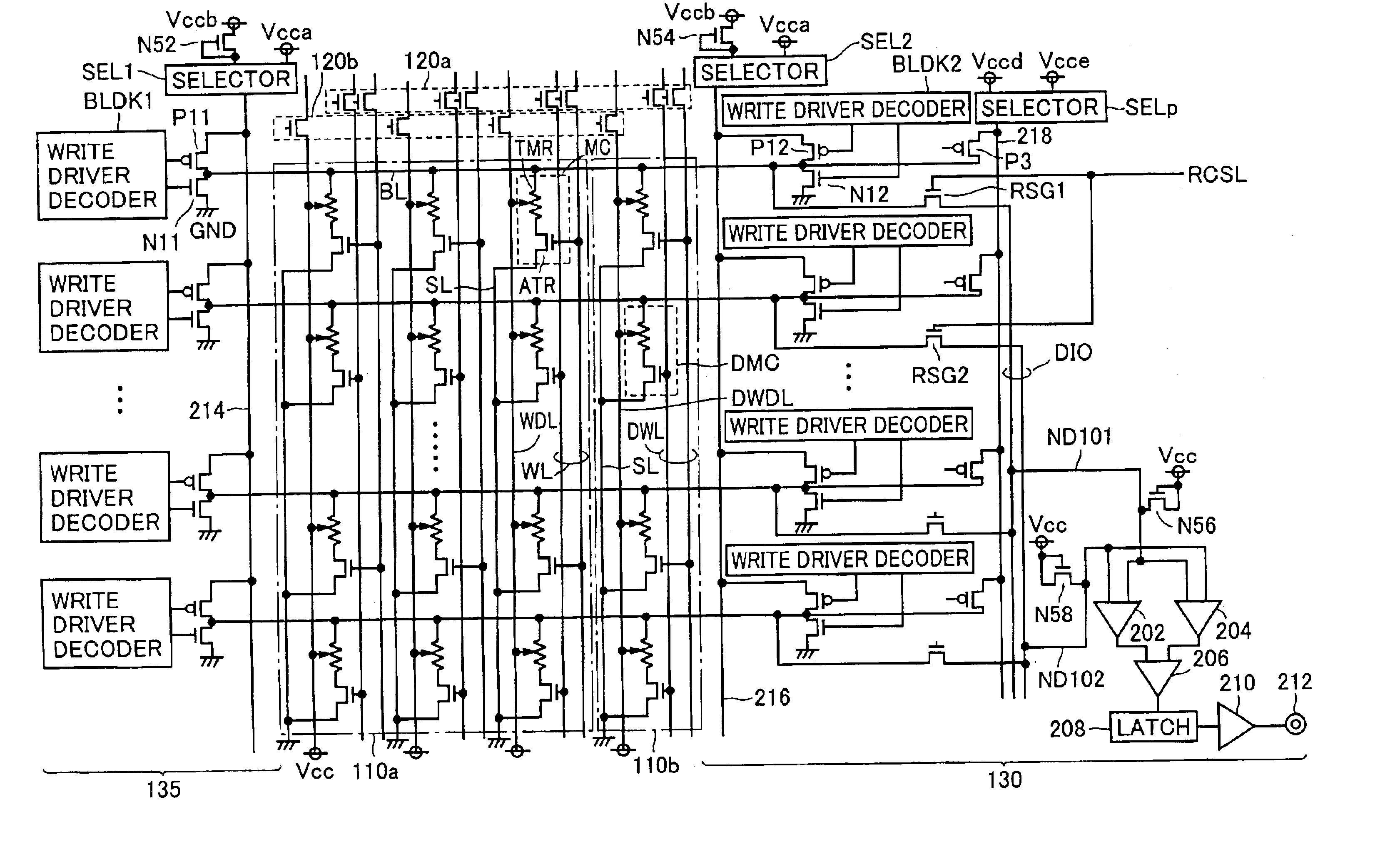

Programmable memory device, integrated circuit including the programmable memory device, and method of fabricating same

InactiveUS7259419B2Reliability of gate can be prevented being deterioratedImprove gate reliabilityTransistorSolid-state devicesGate dielectricLow voltage

An integrated circuit comprises a memory device including an isolation layer for defining an active area of a substrate, a tunnel oxide layer formed on the active area, a floating gate formed over the active area and the isolation layer, an inter-gate dielectric layer formed on the floating gate, and a control gate formed on the inter-gate dielectric layer. The integrated circuit also includes a high and low voltage transistors.

Owner:SAMSUNG ELECTRONICS CO LTD

ENHANCEMENT MODE GaN HEMT DEVICE WITH GATE SPACER AND METHOD FOR FABRICATING THE SAME

ActiveUS20120175631A1Reduce leakageReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesGate leakage currentDielectric membrane

Enhancement-mode GaN devices having a gate spacer, a gate metal material and a gate compound that are self-aligned, and a methods of forming the same. The materials are patterned and etched using a single photo mask, which reduces manufacturing costs. An interface of the gate spacer and the gate compound has lower leakage than the interface of a dielectric film and the gate compound, thereby reducing gate leakage. In addition, an ohmic contact metal layer is used as a field plate to relieve the electric field at a doped III-V gate compound corner towards the drain contact, which leads to lower gate leakage current and improved gate reliability.

Owner:EFFICIENT POWER CONVERSION CORP

Gate driving circuit and display apparatus having the same

ActiveUS8587347B2Improve gate reliabilityExtended service lifeStatic indicating devicesDigital storageEngineeringTransistor

A gate driving circuit includes a pull-up control part, a pull-up part, a carry part, a first pull-down part and a second pull-down part. The pull-up control part applies a carry signal from a previous stage to a first node. The pull-up part outputs an N-th gate output signal based on a clock signal. The carry part outputs an N-th carry signal based on the clock signal in response to the signal applied to the first node. The first pull-down part includes a plurality of transistors connected to each other in series. The first pull-down part pulls down a signal at the first node to a second off voltage in response to a carry signal of a next stage. The second pull-down part pulls down the N-th gate output signal to a first off voltage in response to the carry signal of the next stage.

Owner:SAMSUNG DISPLAY CO LTD

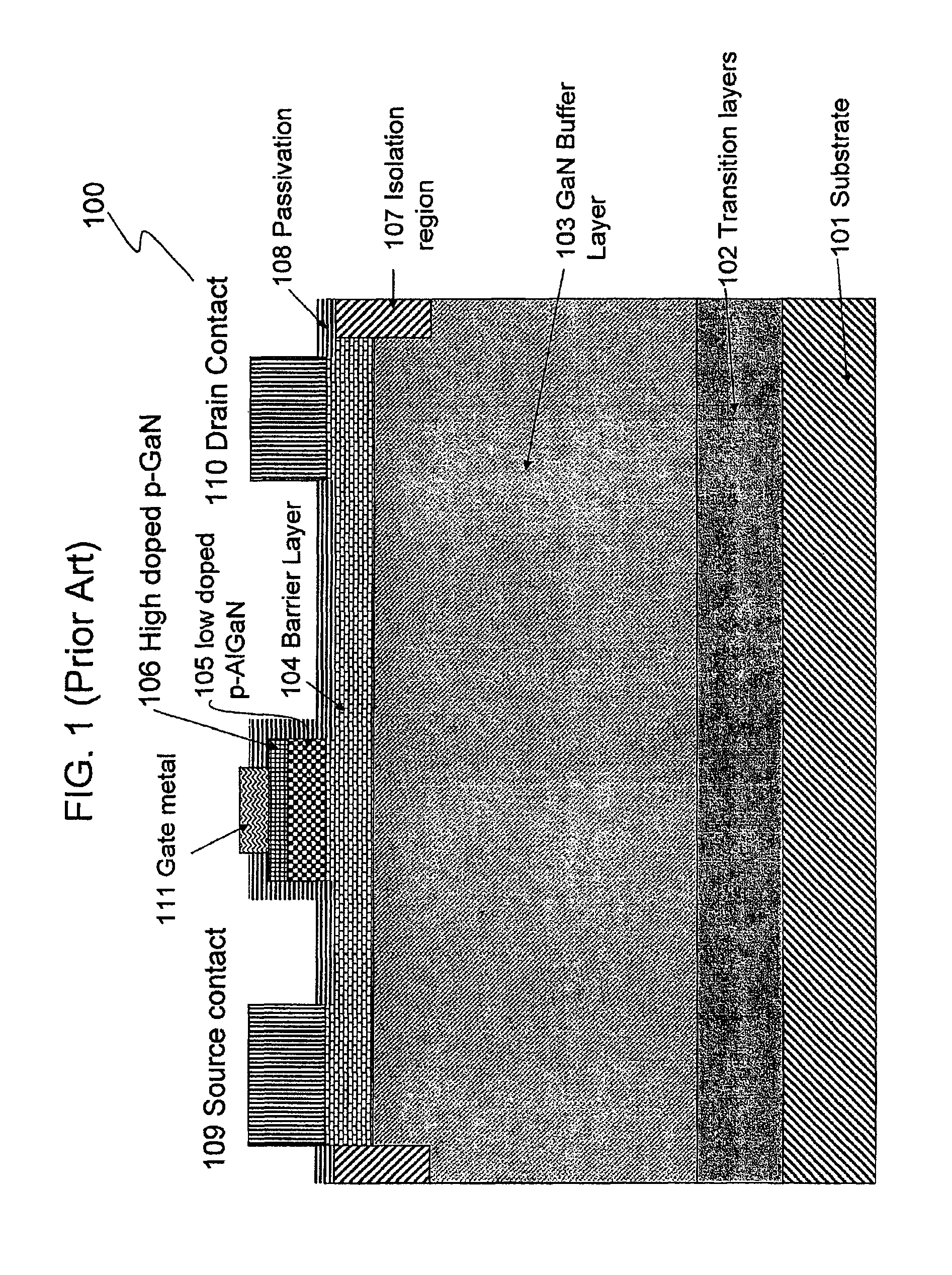

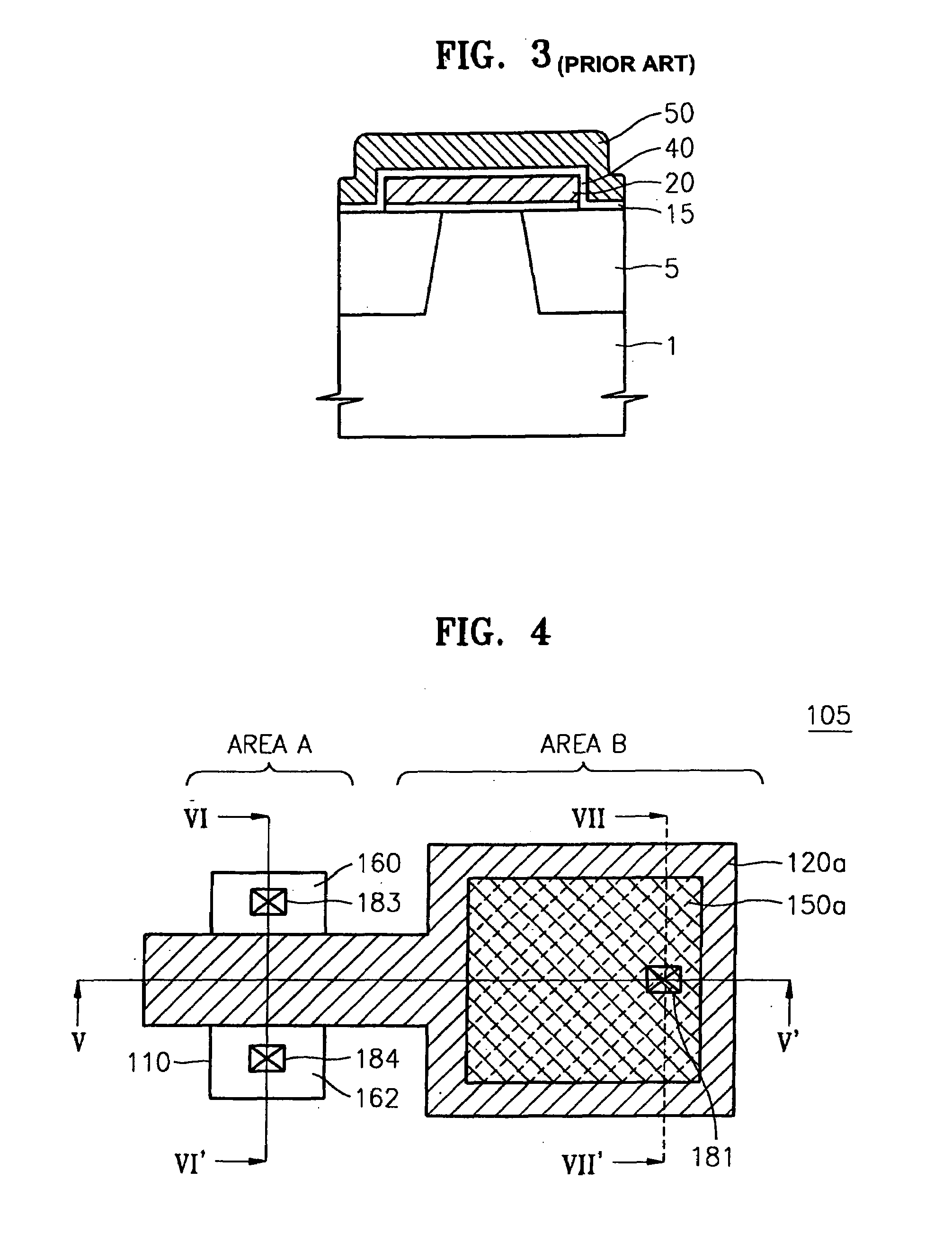

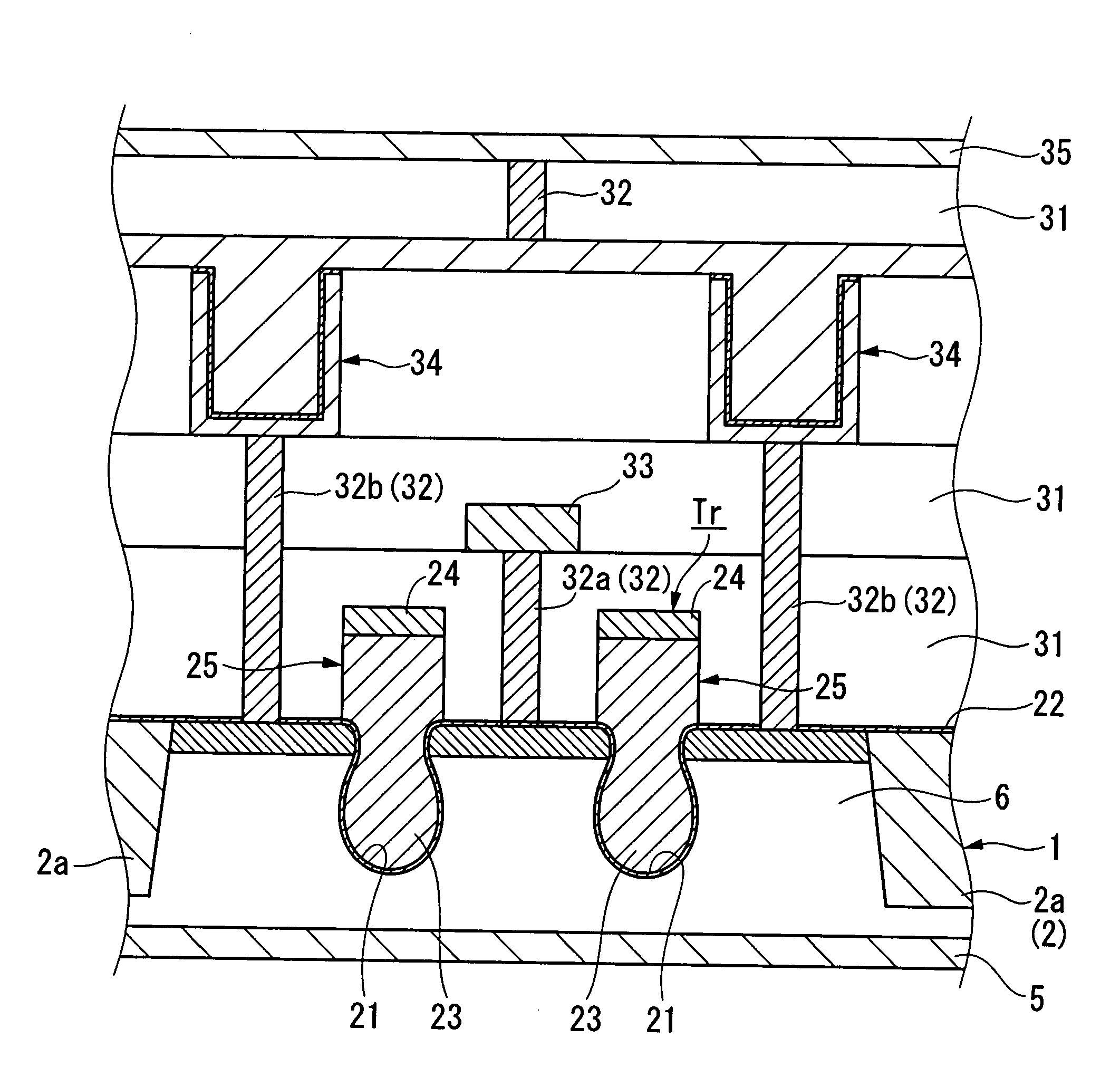

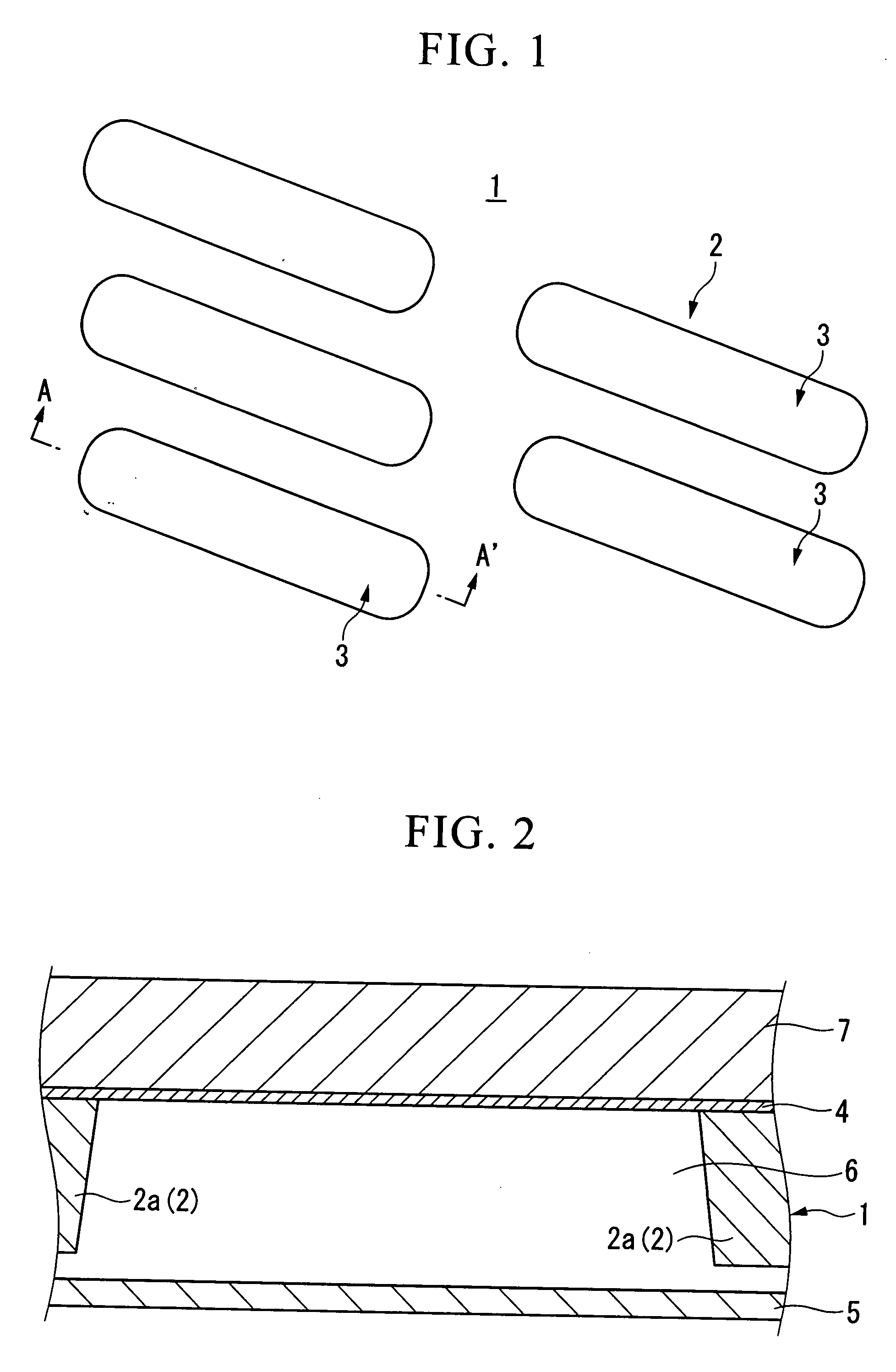

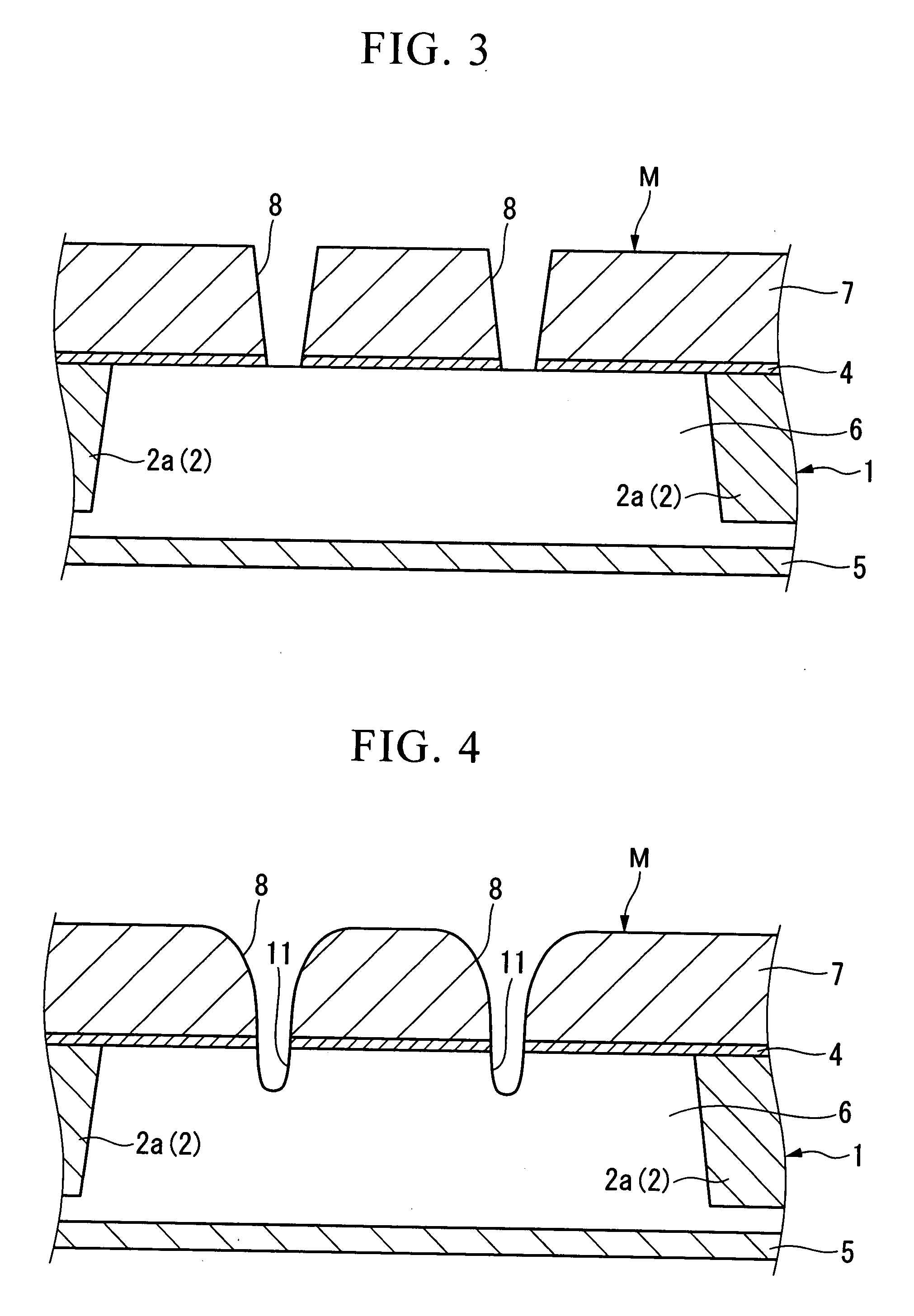

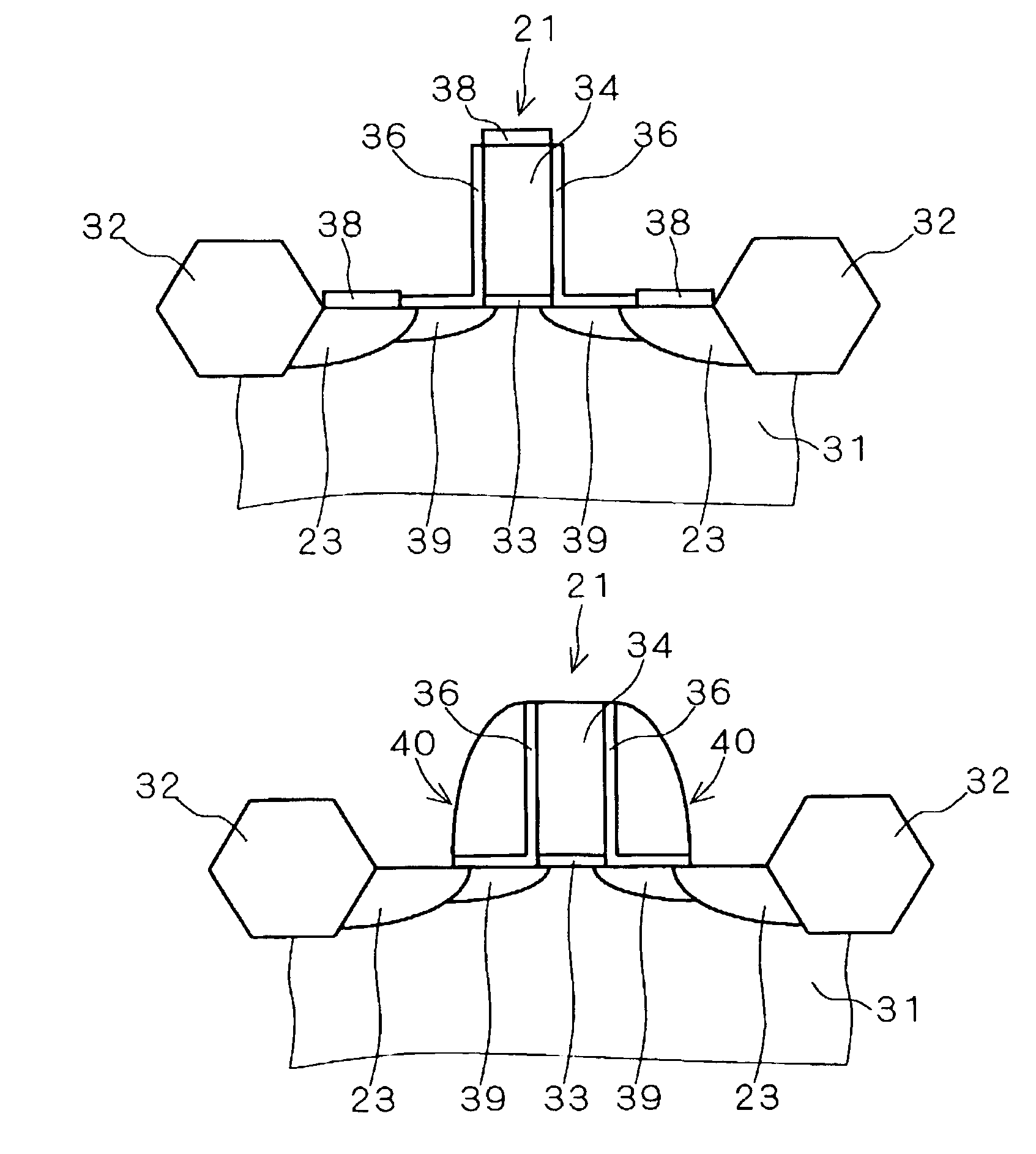

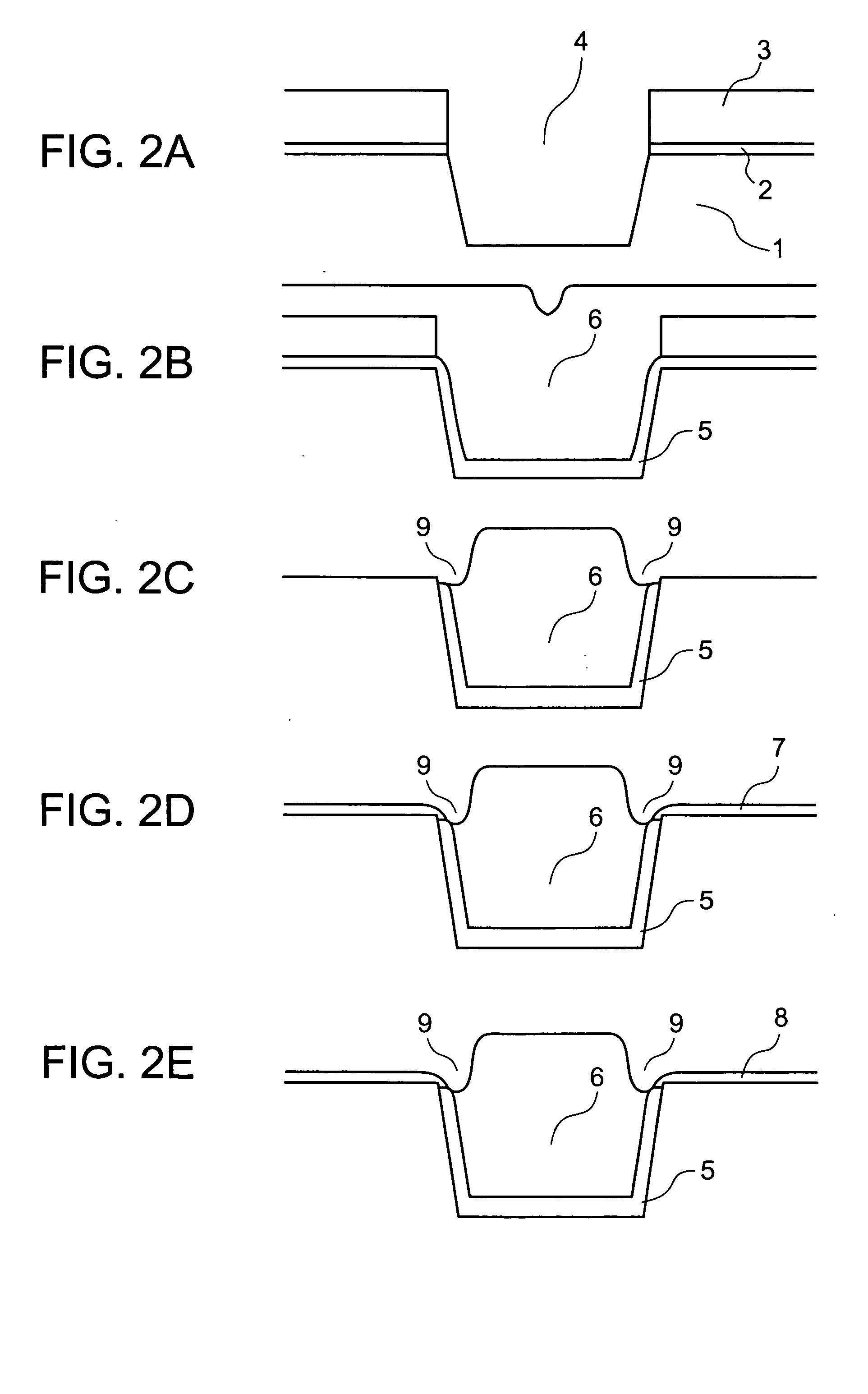

Semiconductor device and method of manufacturing the same

ActiveUS20080073709A1Improve gate reliabilityImprove reliabilityTransistorSolid-state devicesGate dielectricEngineering

A semiconductor device in which the reliability of a gate dielectric film is high and a channel length is sufficiently secured and a method of manufacturing the same are provided. The semiconductor device comprises a trench gate transistor. The trench gate transistor comprises: a trench provided in a semiconductor substrate; a gate electrode formed in the trench through a gate dielectric film; and a diffusion layer formed in the vicinity of the trench. The trench comprises: an opening portion provided in a surface of the semiconductor substrate; a recess curved surface portion whose cross-sectional contour is a substantially circular arc shape; and a connection curved surface portion connecting the recess curved surface portion and the opening portion. The connection curved surface portion and the recess curved surface portion are integrated in a continuous curved surface without interposing a ridge line portion therebetween.

Owner:MICRON TECH INC

Gate driving circuit and display device having the gate driving circuit

InactiveUS8654055B2Improve driving reliabilityImprove gate reliabilityCathode-ray tube indicatorsElectric pulse generatorShift registerTiming margin

Owner:SAMSUNG DISPLAY CO LTD

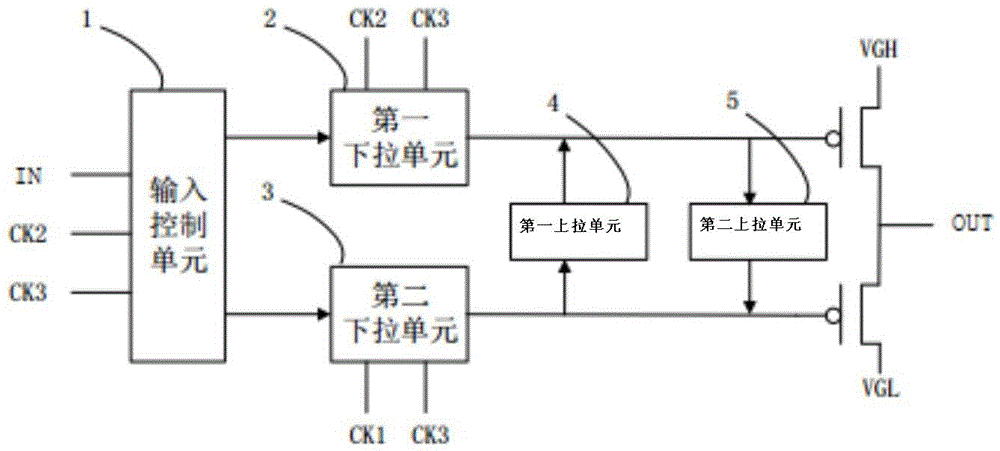

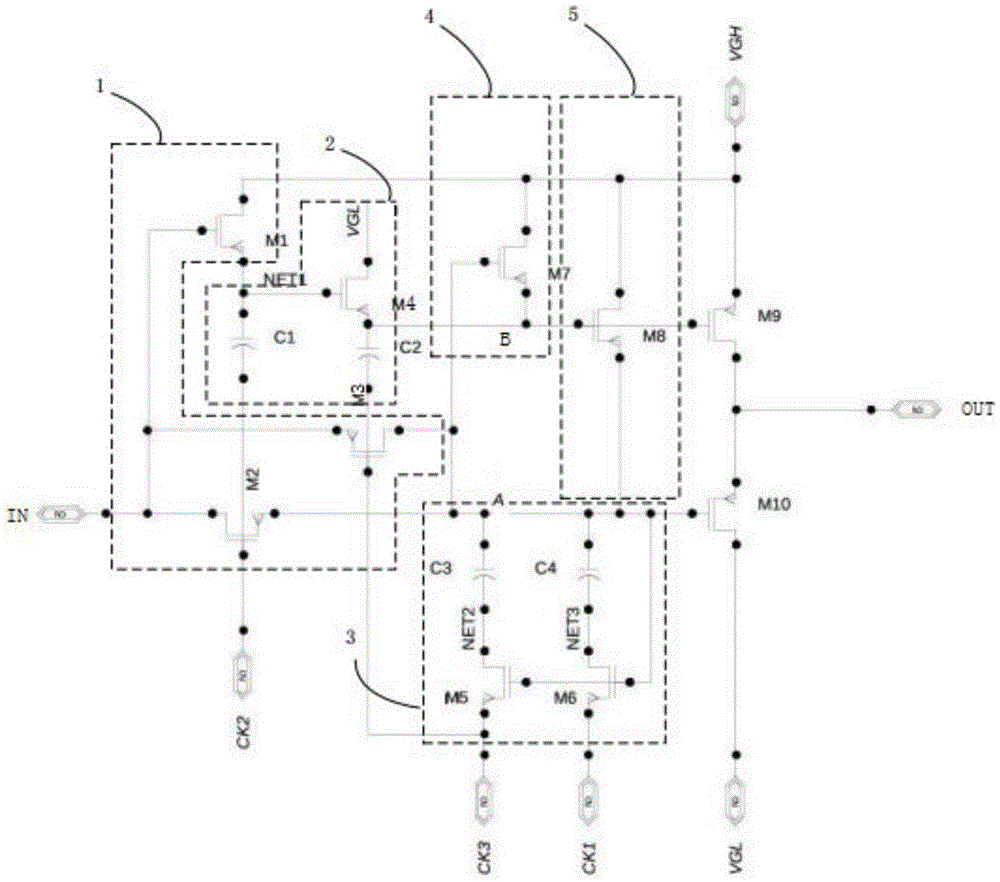

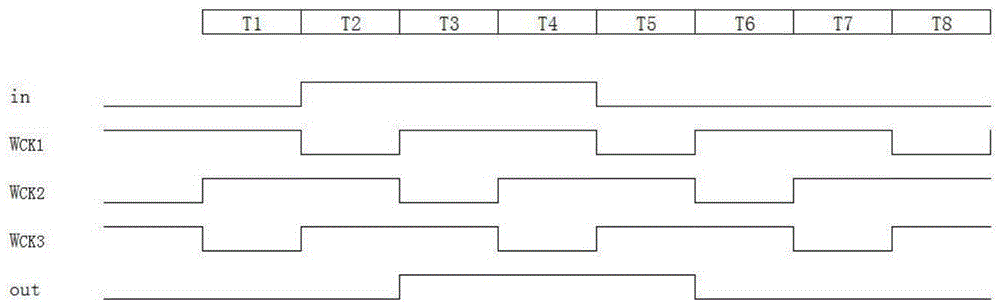

Luminescence control circuit and shift register

ActiveCN105609054AStable output signal waveformStable waveformStatic indicating devicesDigital storageShift registerControl signal

The invention provides a luminescence control circuit which is taken as a shift register unit circuit. The circuit comprises a first clock signal input end, a second clock signal input end, a third clock signal input end, a signal input end, a luminescence control signal output end, a constant high level voltage signal end and a constant low level voltage signal end, wherein an input control unit, a first pull-down unit, a second pull-down unit, a first pull-up unit and a second pull-up unit are connected between the signal input end and the luminescence control signal output end. The invention further provides a shift register, grid control nodes of ninth and tenth film transistors of an output level TFT have stable and controllable work voltages at each work stage, the ninth and tenth film transistors realize conduction by turns, and the simultaneous turn-off situation does not occur. According to the circuit, circuit output signal waveforms are stable, grid reliability is high, after simulation verification, output signal waveforms of each level of cascade circuits are stable.

Owner:TRULY HUIZHOU SMART DISPLAY

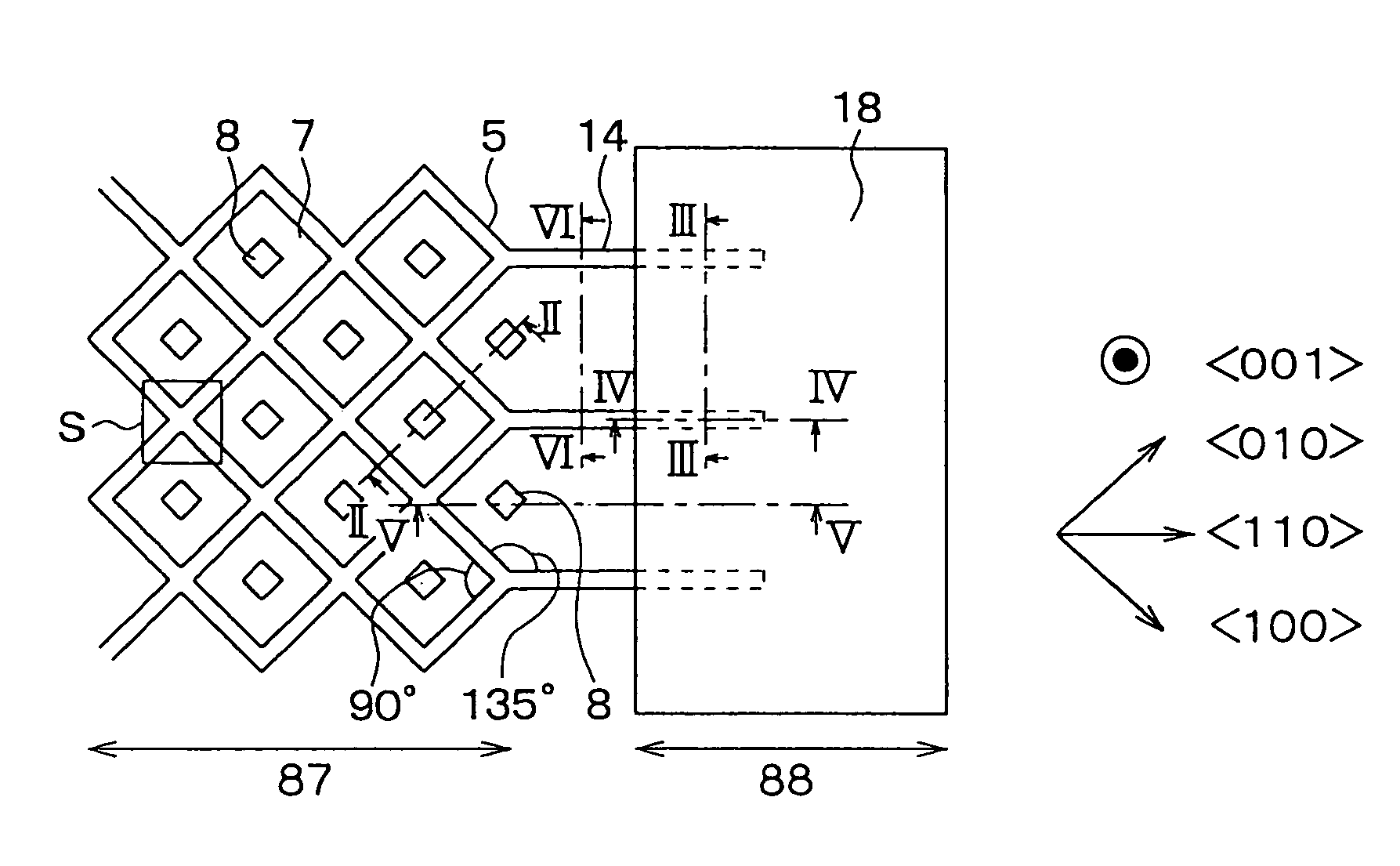

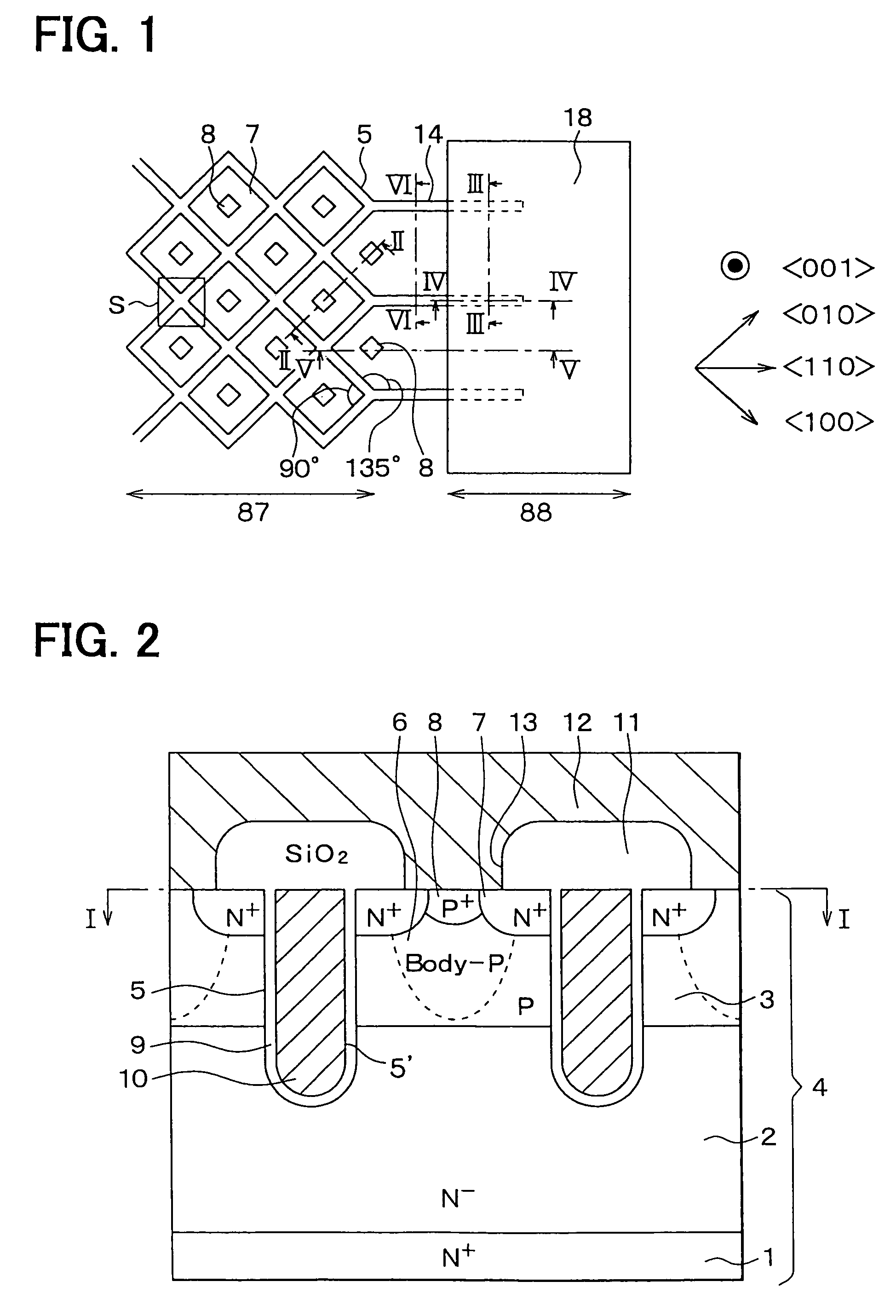

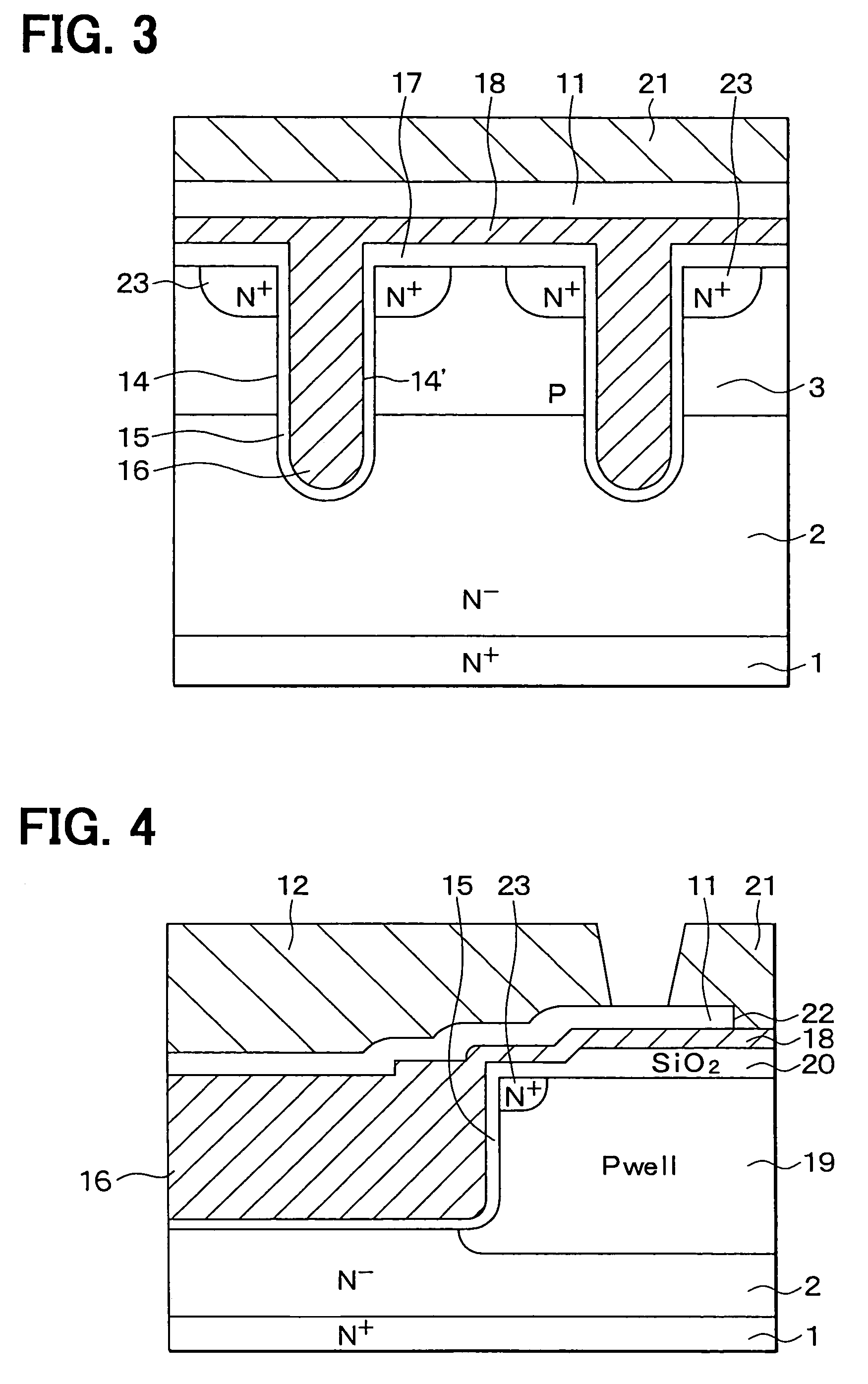

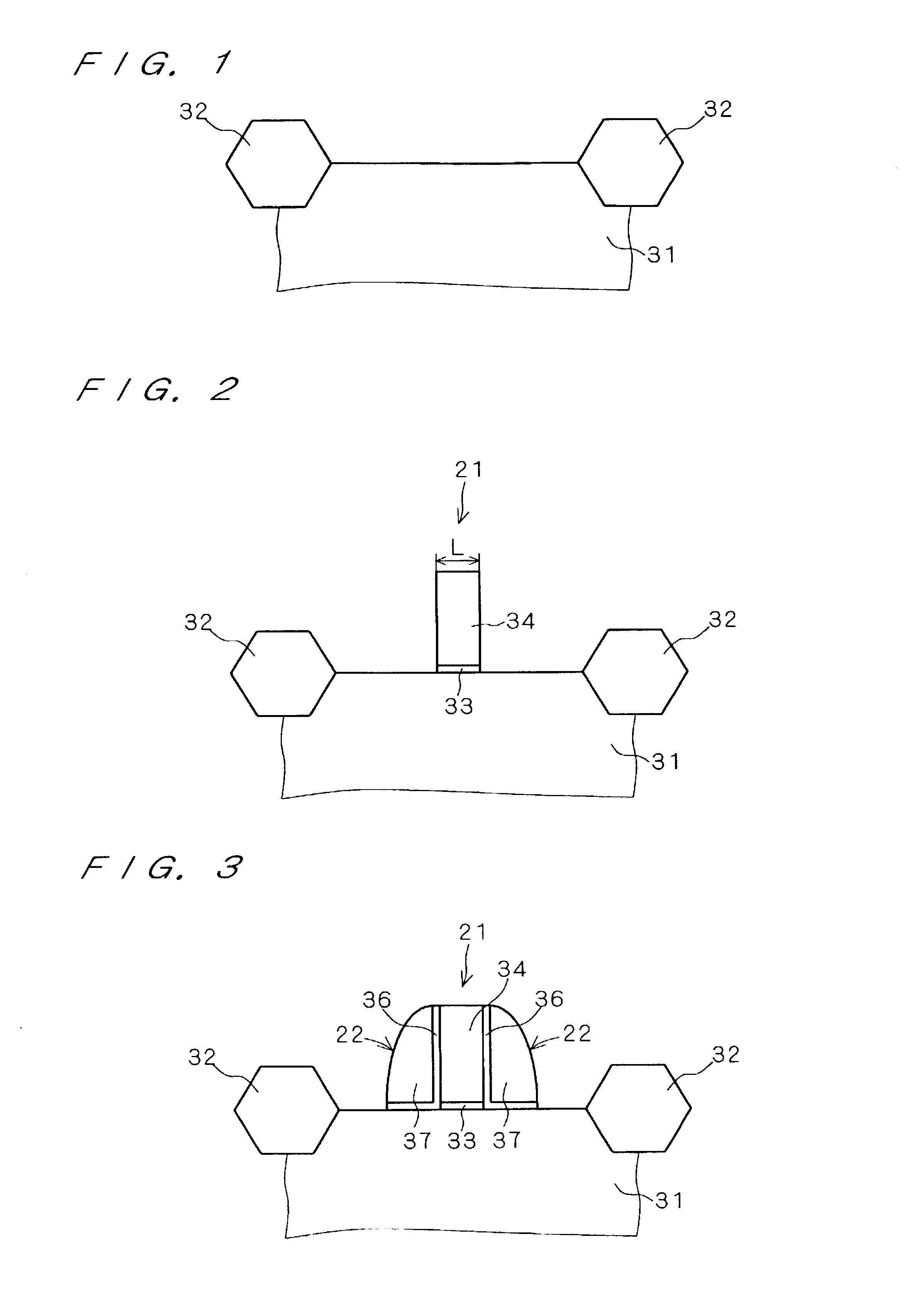

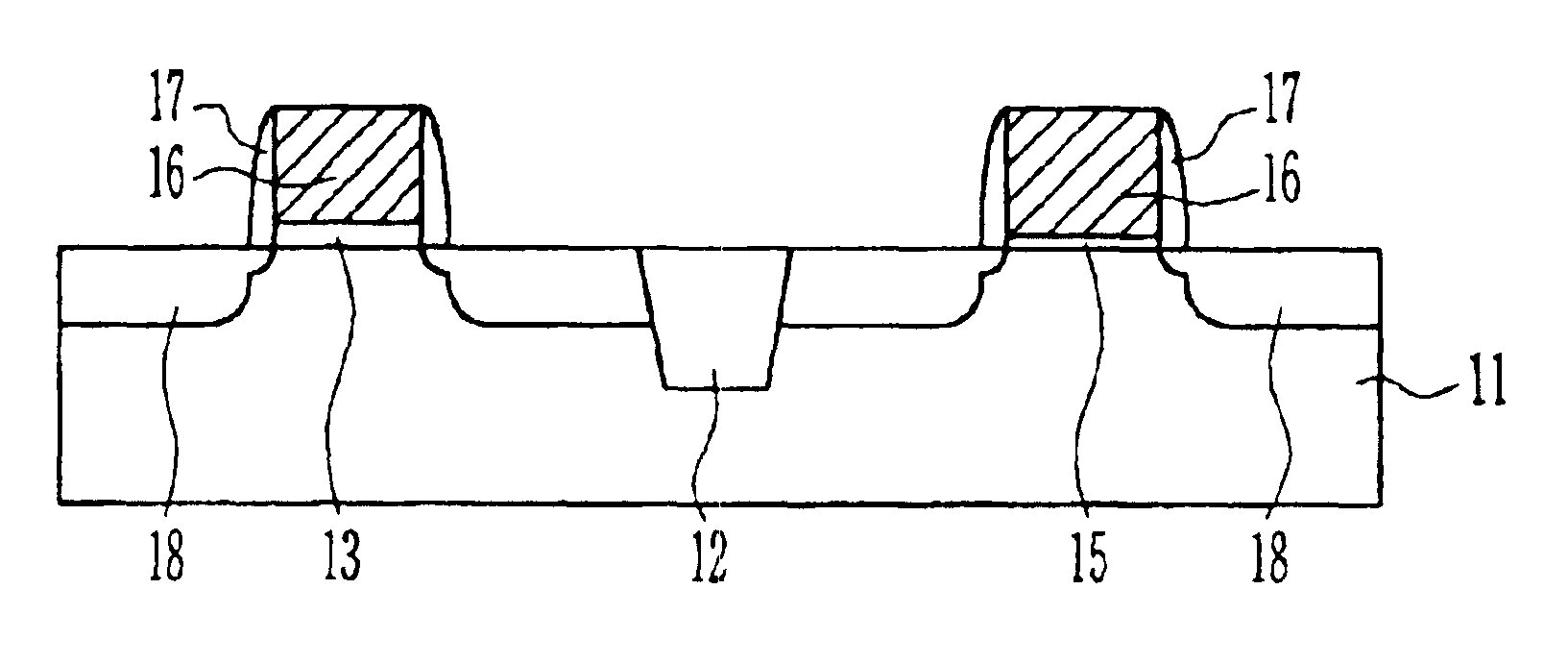

Method of producing a semiconductor device

InactiveUS7026215B2Improve reliabilitySuppression of increase in ON-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesCell regionSemiconductor

A semiconductor device includes a semiconductor substrate, a cell region in a surface portion of the substrate for operating as a transistor, a gate lead wiring region having a gate lead pattern on the substrate, a trench in the surface portion of the substrate extending from the cell region to the gate lead wiring region, an oxide film on an inner surface of the trench, and a gate electrode in the trench insulated with at least the oxide film from the substrate. A speed of formation of a main portion of the sidewalls of the trench at the gate lead wiring region is greater than that of a main portion of the sidewalls of the trench at the cell region, so that a thickness of the oxide film at the gate lead wiring region is greater than that at the cell region.

Owner:DENSO CORP

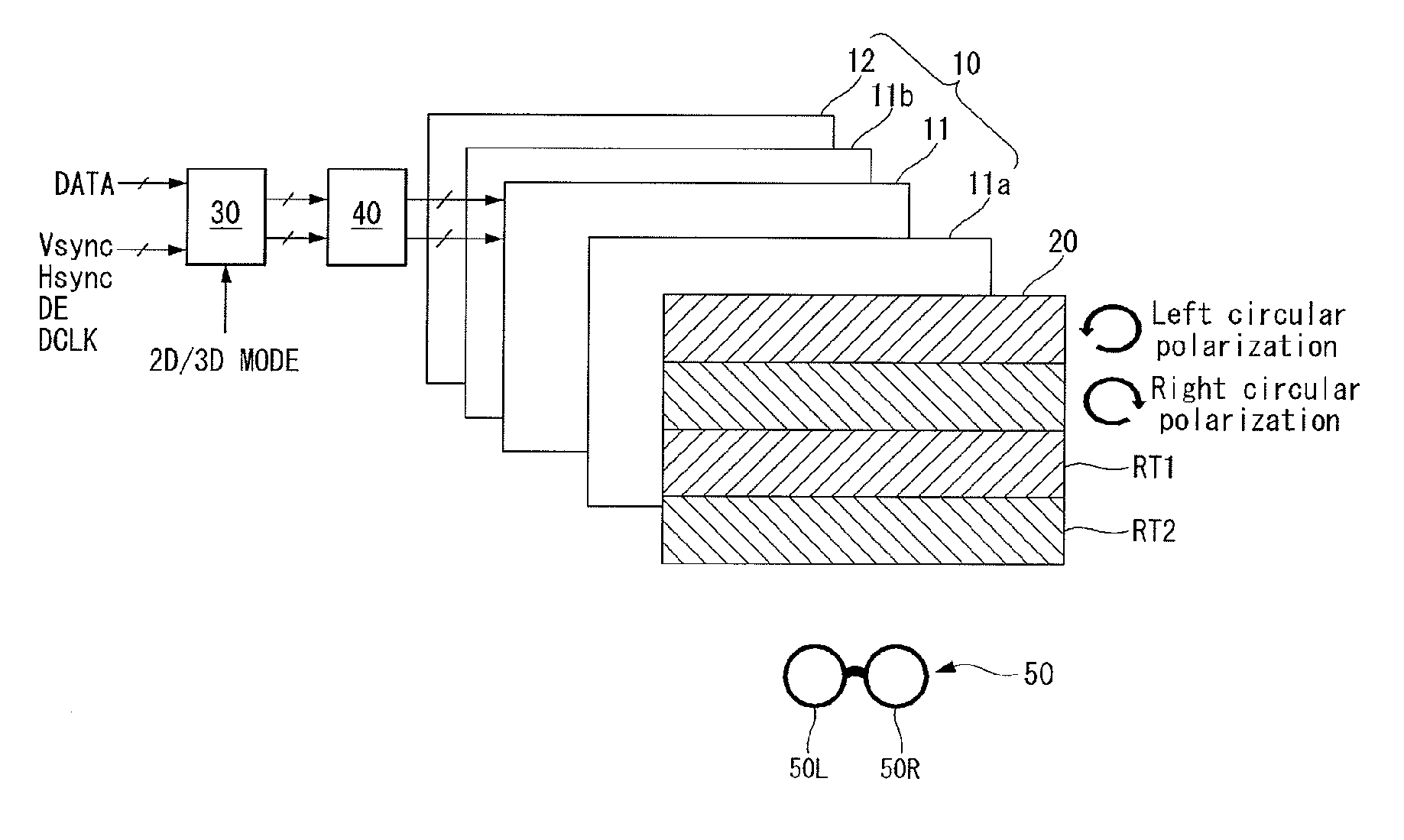

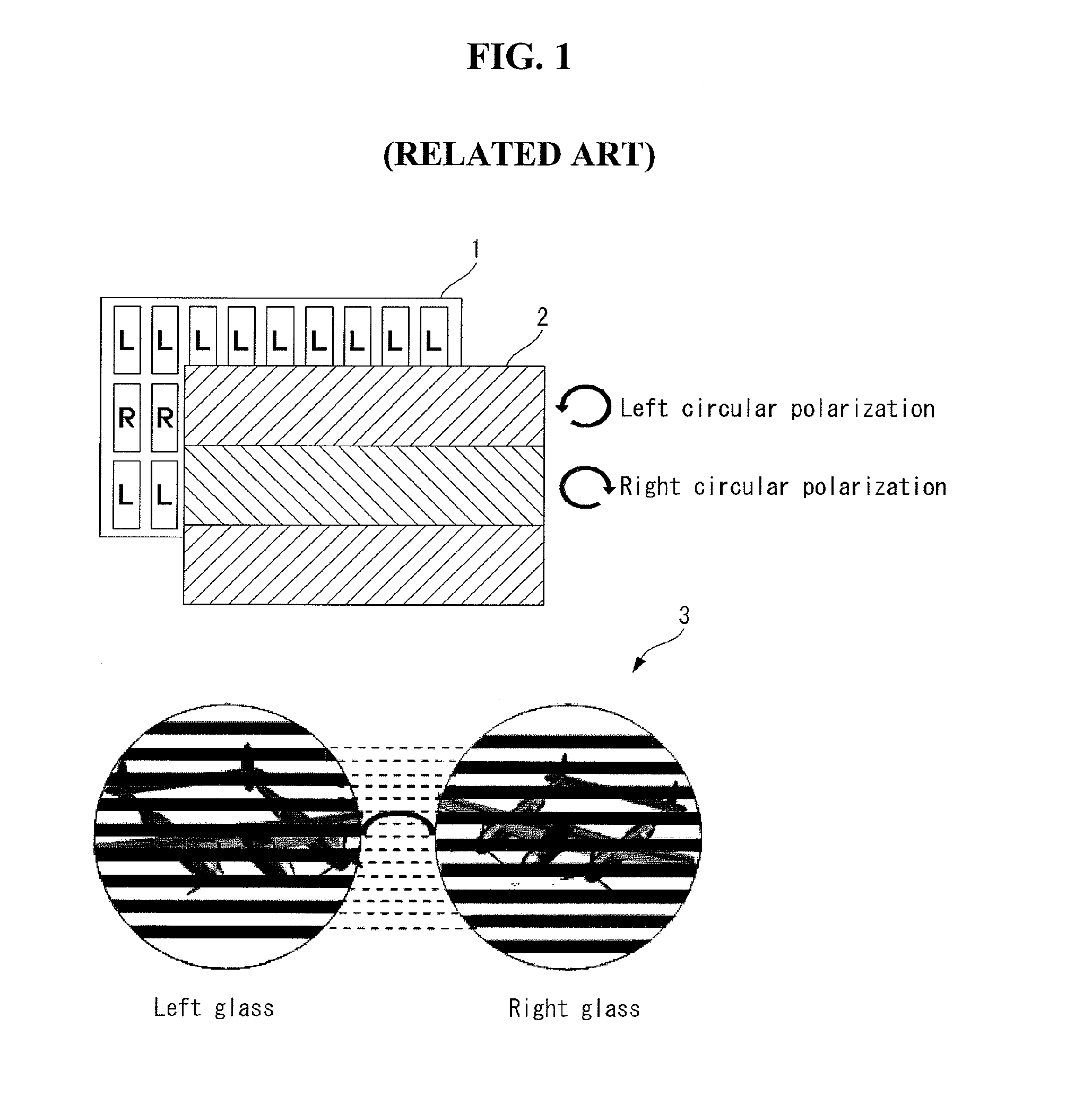

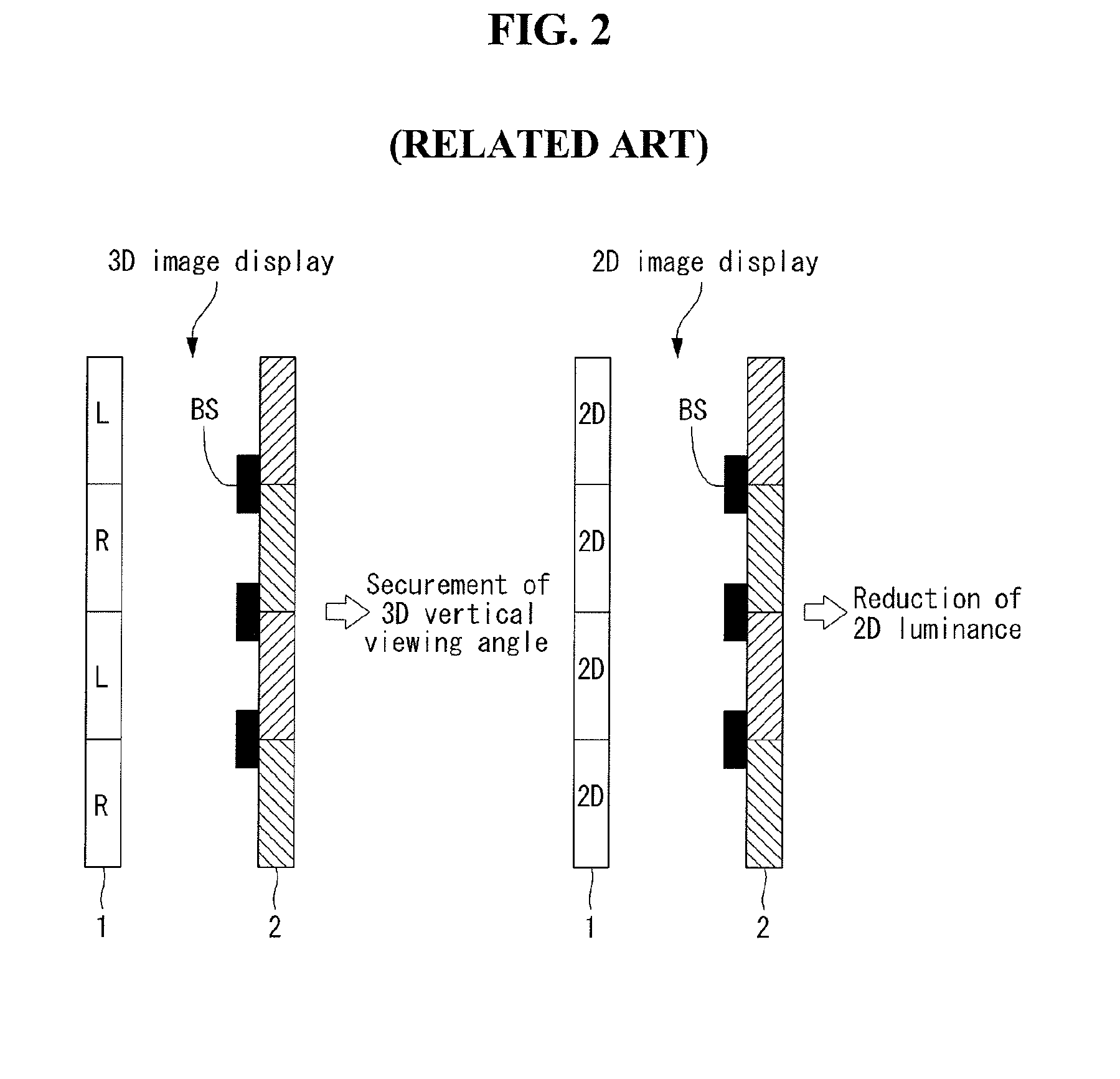

Image display device and method for driving the same

InactiveUS20120268453A1Improve luminanceWiden perspectiveStatic indicating devicesSteroscopic systemsDisplay deviceEngineering

An image display device and a method for driving the same are discussed. The image display device includes a display panel, which includes a subpixel disposed at a crossing between a pair of gate lines and a data line to selectively display a 2D image and a 3D image, a panel driver including a gate driver for driving the pair of gate lines and a data driver for driving the data line, a controller for differently controlling the panel driver in response to a mode selection signal, and a patterned retarder for dividing light from the display panel into first polarized light and second polarized light.

Owner:LG DISPLAY CO LTD

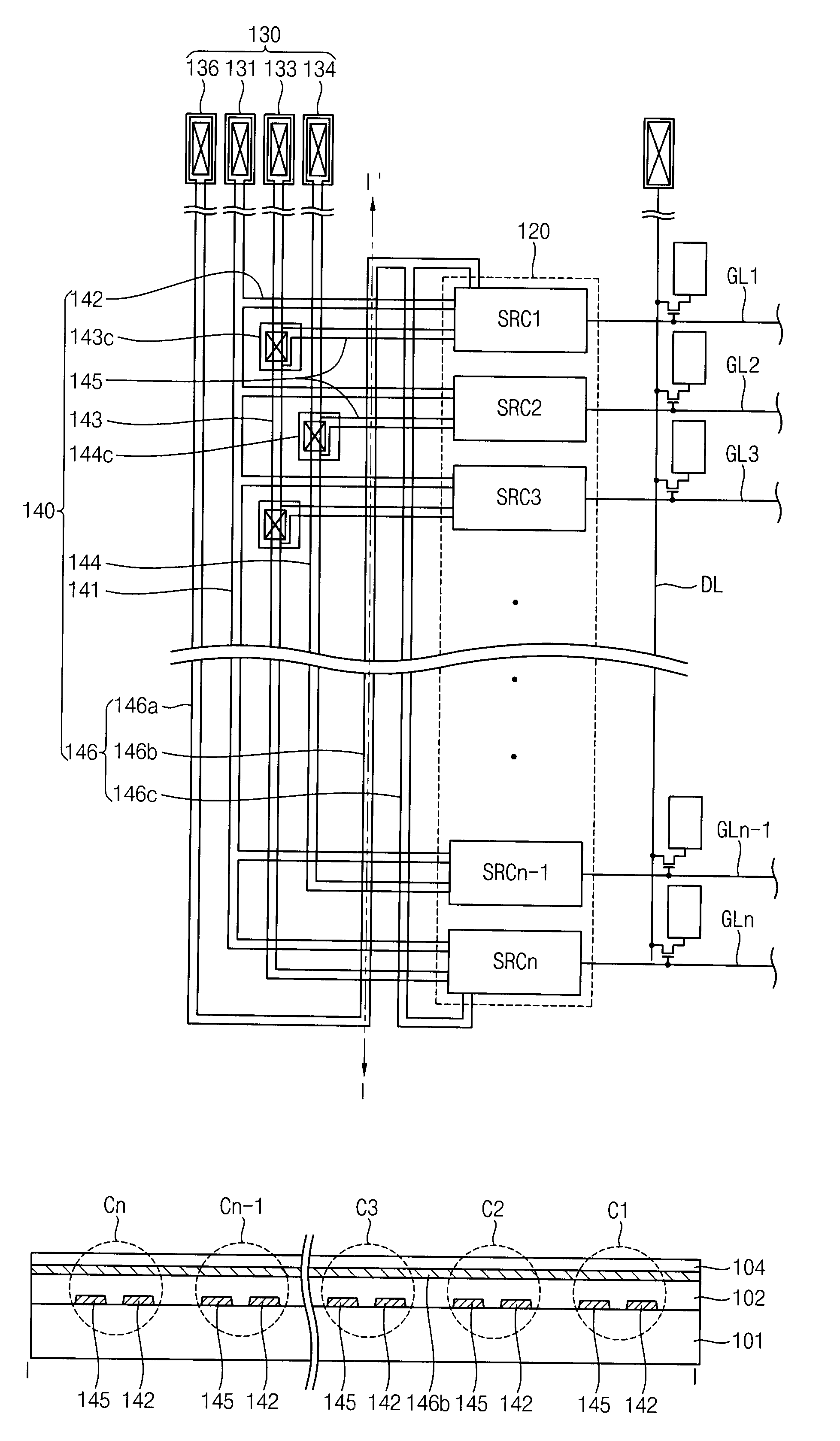

Gate drive circuit, display substrate having the same, and method thereof

ActiveUS8138792B2Improve toleranceImprove gate reliabilityStatic indicating devicesSolid-state devicesShift registerEngineering

A gate drive circuit includes a shift register, a clock wiring and a start wiring. The shift register includes a plurality of stages arranged in a first direction on a base substrate to output a plurality of gate signals. The clock wiring is extended along the first direction. The clock wiring is electrically connected to a plurality of clock connecting wirings extended in a second direction crossing the first direction to deliver a clock signal to the stages. The start wiring includes the first wiring extended along the first direction and a second wiring connected to the first wiring and extended in the first direction to cross with the clock connecting wirings so as to deliver a vertical start signal to a first stage. Therefore, a structure of a signal wiring delivering a vertical start signal is changed, thereby protecting the gate drive circuit from static electricity.

Owner:SAMSUNG DISPLAY CO LTD

Method of manufacturing semiconductor device

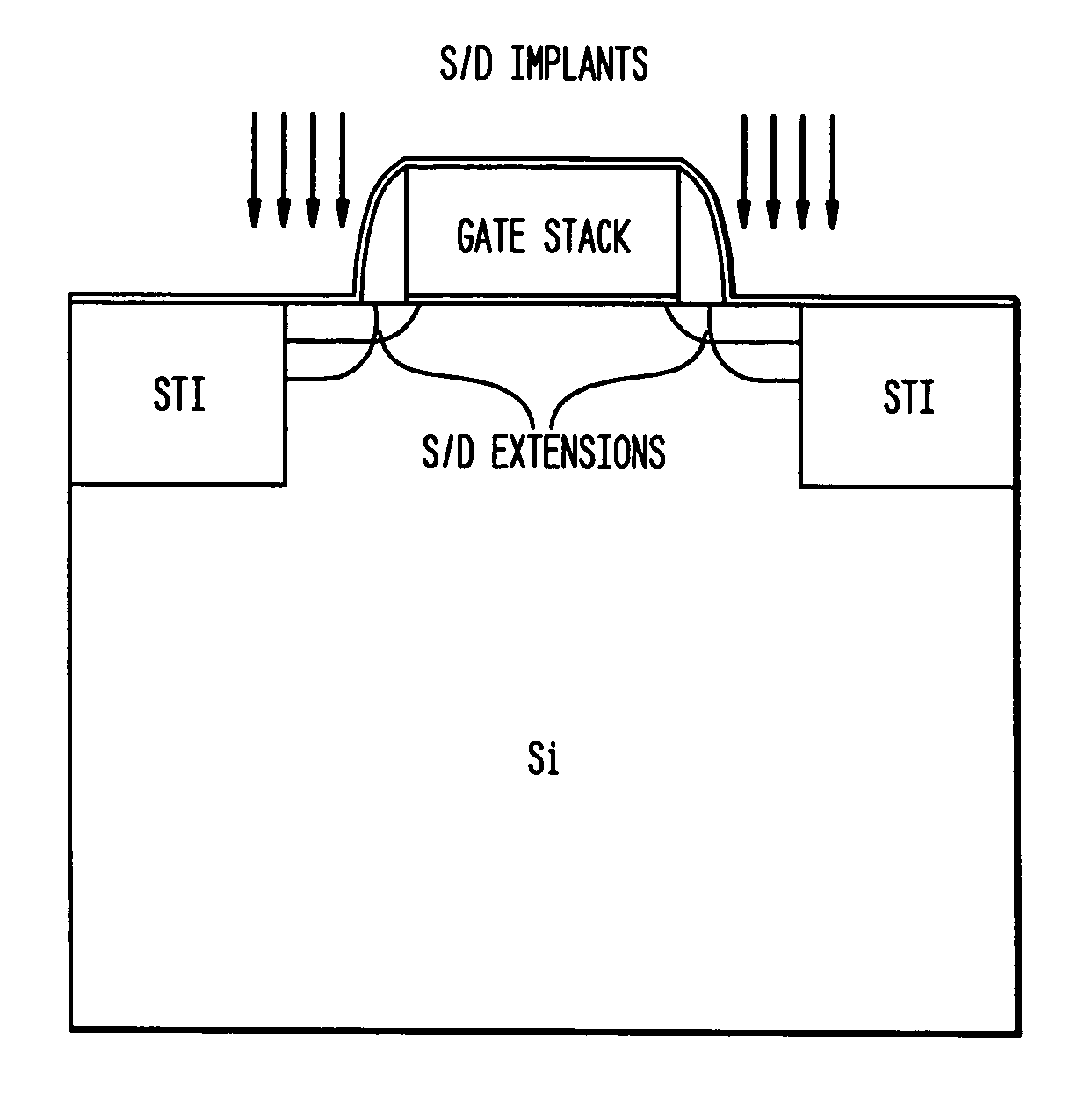

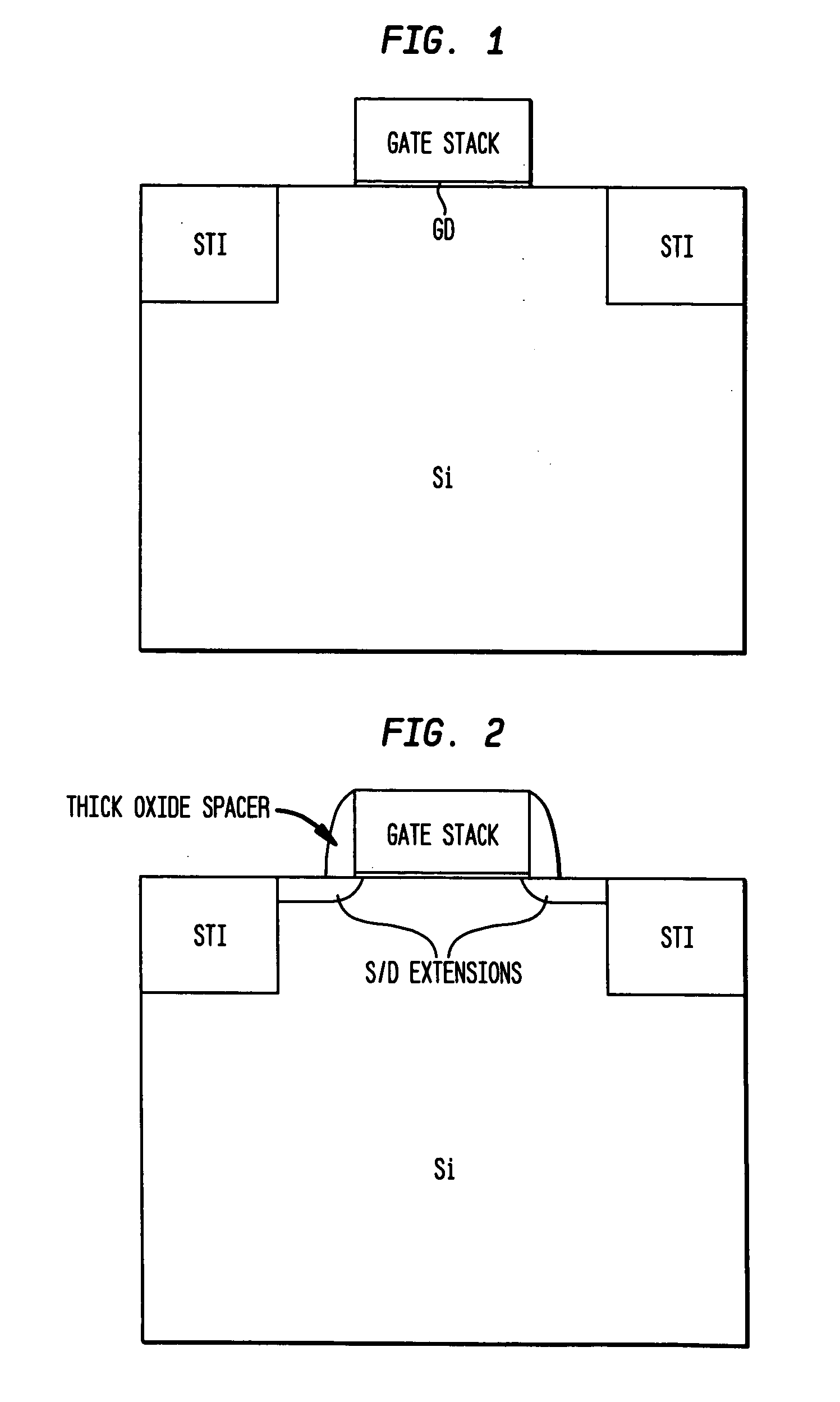

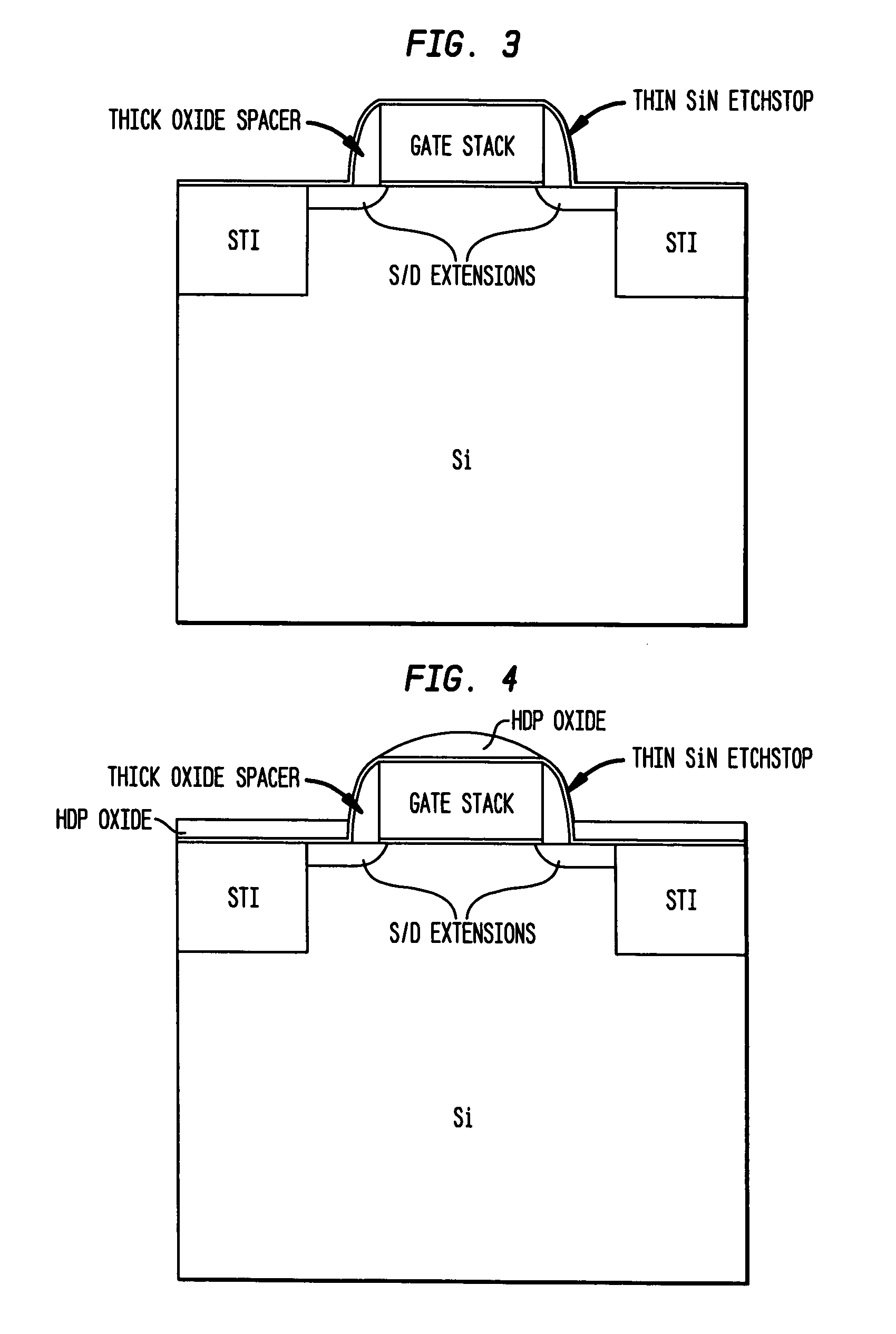

InactiveUS7015107B2Suppress surface roughnessImprove gate reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSurface roughnessEngineering

When a dummy sidewall and source and drain regions are once formed and then the dummy sidewall is removed to extend the source and drain regions, the removal of the dummy sidewall is performed after formation of a protective oxide film on a gate electrode and on the major surfaces of the source and drain regions. This efficiently prevents conventional surface roughness of the upper surface of the gate electrode and the impurity region due to the removal of the dummy sidewall.

Owner:RENESAS TECH CORP

Gate drive circuit having shift register in which plural stages are connected to each other

ActiveUS8462097B2Improve gate reliabilityReduce rippleStatic indicating devicesSolid-state devicesShift registerEngineering

A gate drive circuit includes a shift register having stages connected to each other in series. An (m)-th stage (‘m’ is a natural number) includes an output part, a discharging part, a first holding part and a second holding part. The output part outputs the first clock signal as a gate signal in response to a first clock signal provided from an external device and discharges the gate signal in response to a second input signal. The output part includes a first transistor having a first channel length. The discharging part discharges a signal of the first node to the second voltage level. The first holding part maintains a signal of the first node at a level of the gate signal, and is discharged to the second voltage level. The first holding part includes a second transistor having a second channel length that is longer than the first channel length. The second holding part maintains a signal of the first node at a level of the second voltage level.

Owner:SAMSUNG DISPLAY CO LTD

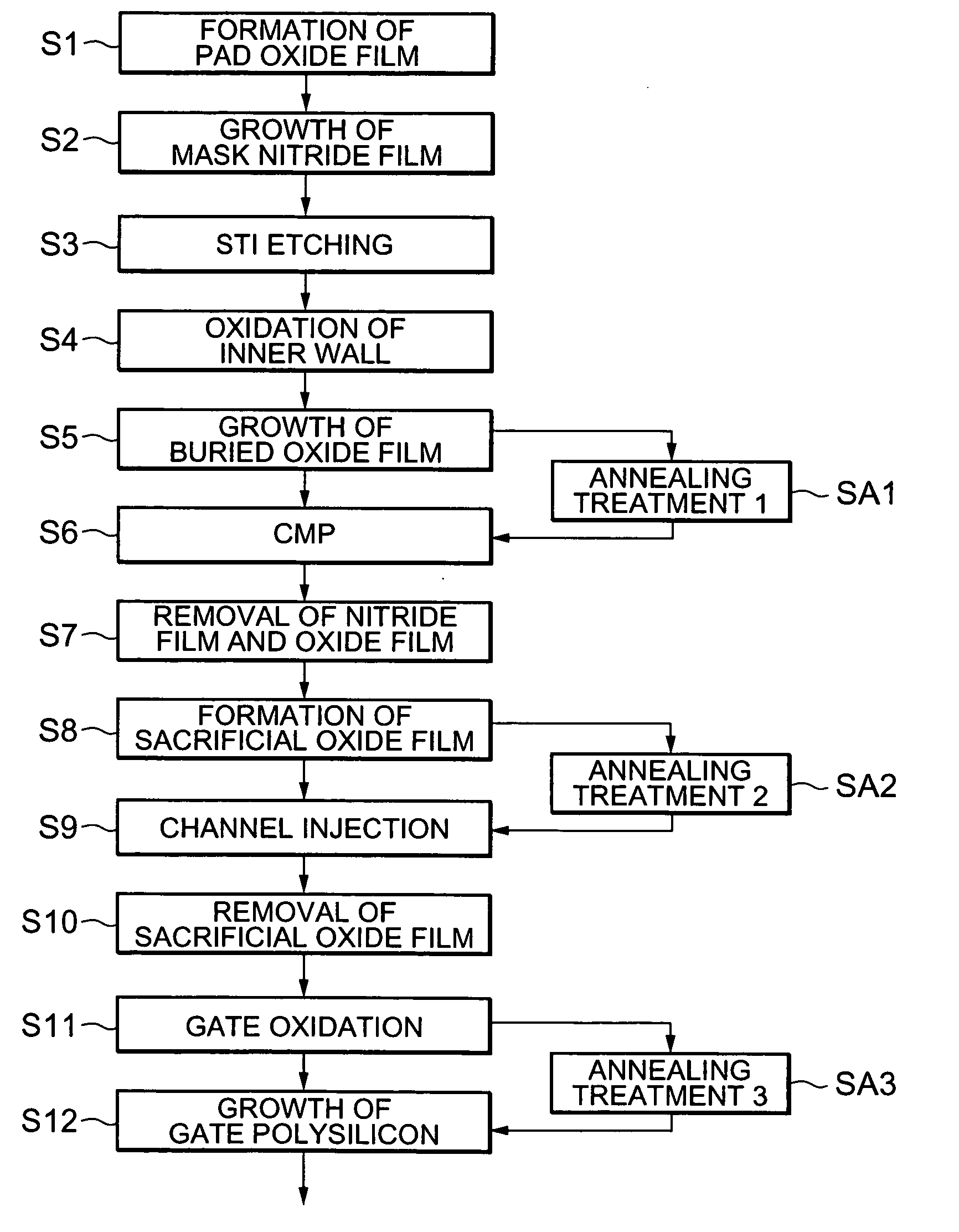

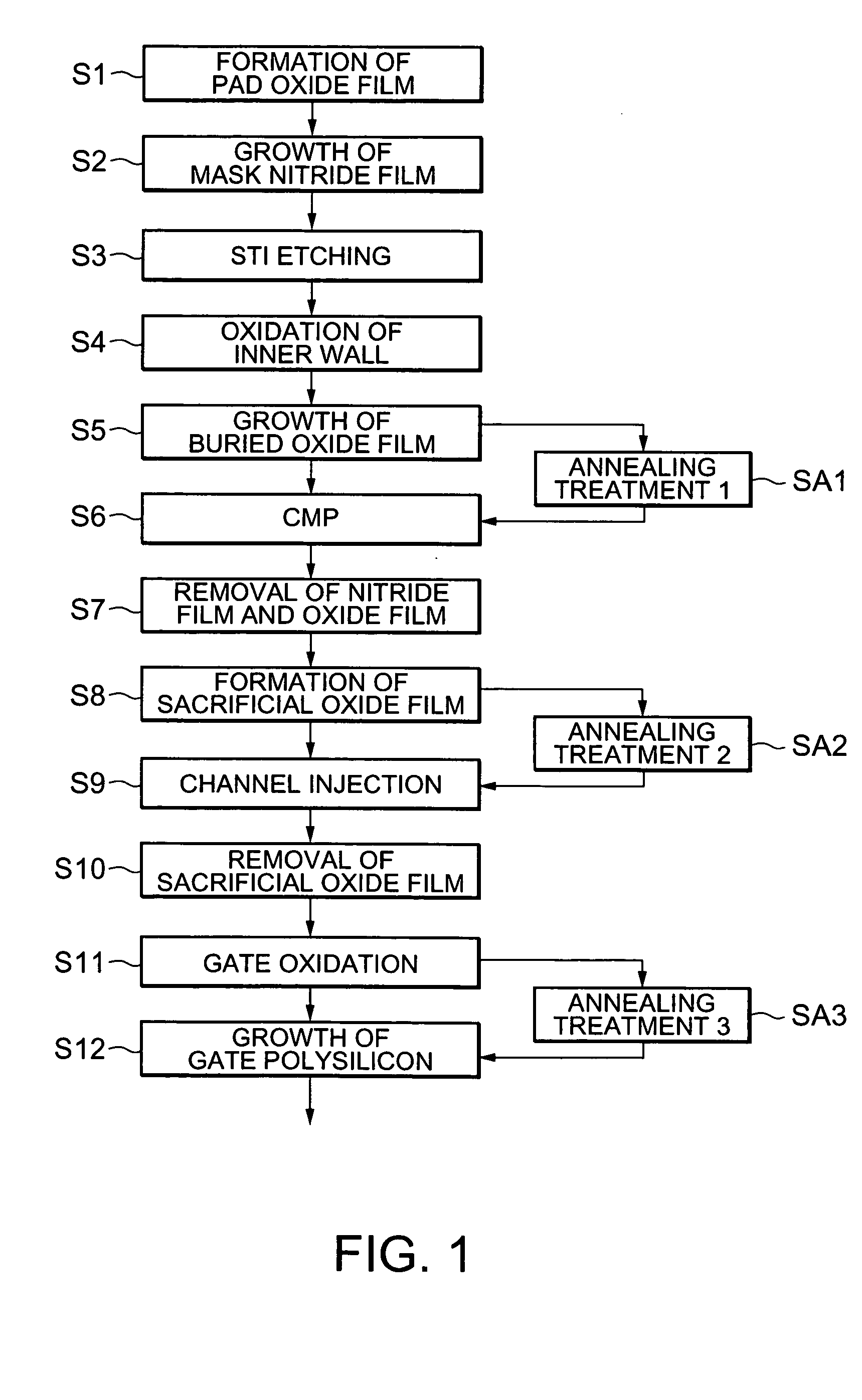

Method for producing semiconductor device

InactiveUS20050227452A1Stable fixed chargeStable interface levelSemiconductor/solid-state device manufacturingSemiconductor devicesNoble gasDevice material

A method for producing a semiconductor device includes the steps of forming a trench for device isolation on a silicon substrate; and annealing the silicon substrate in an atmosphere containing a noble gas at any step after the growth of a buried oxide film until the growth of a gate polysilicon.

Owner:ELPIDA MEMORY INC

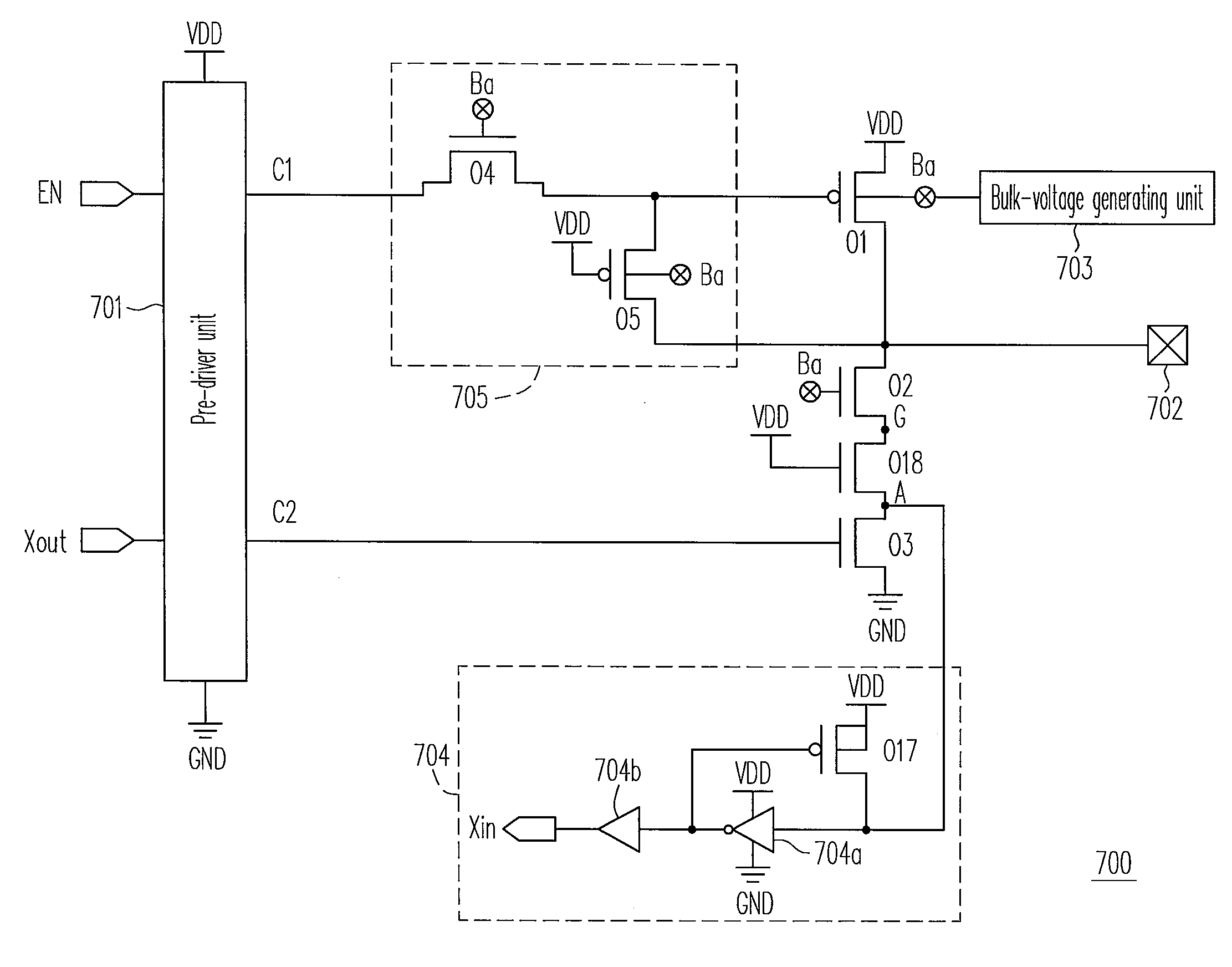

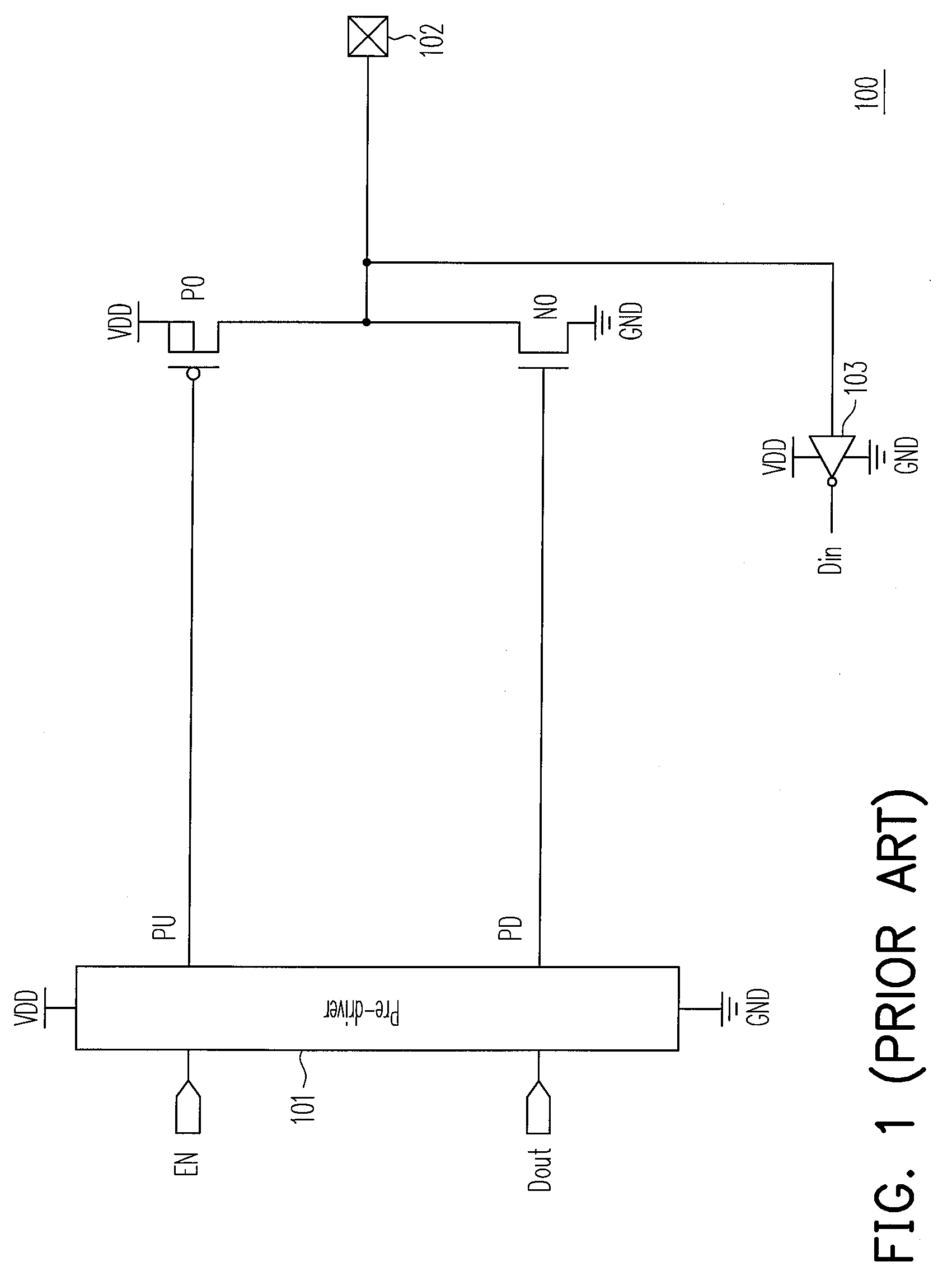

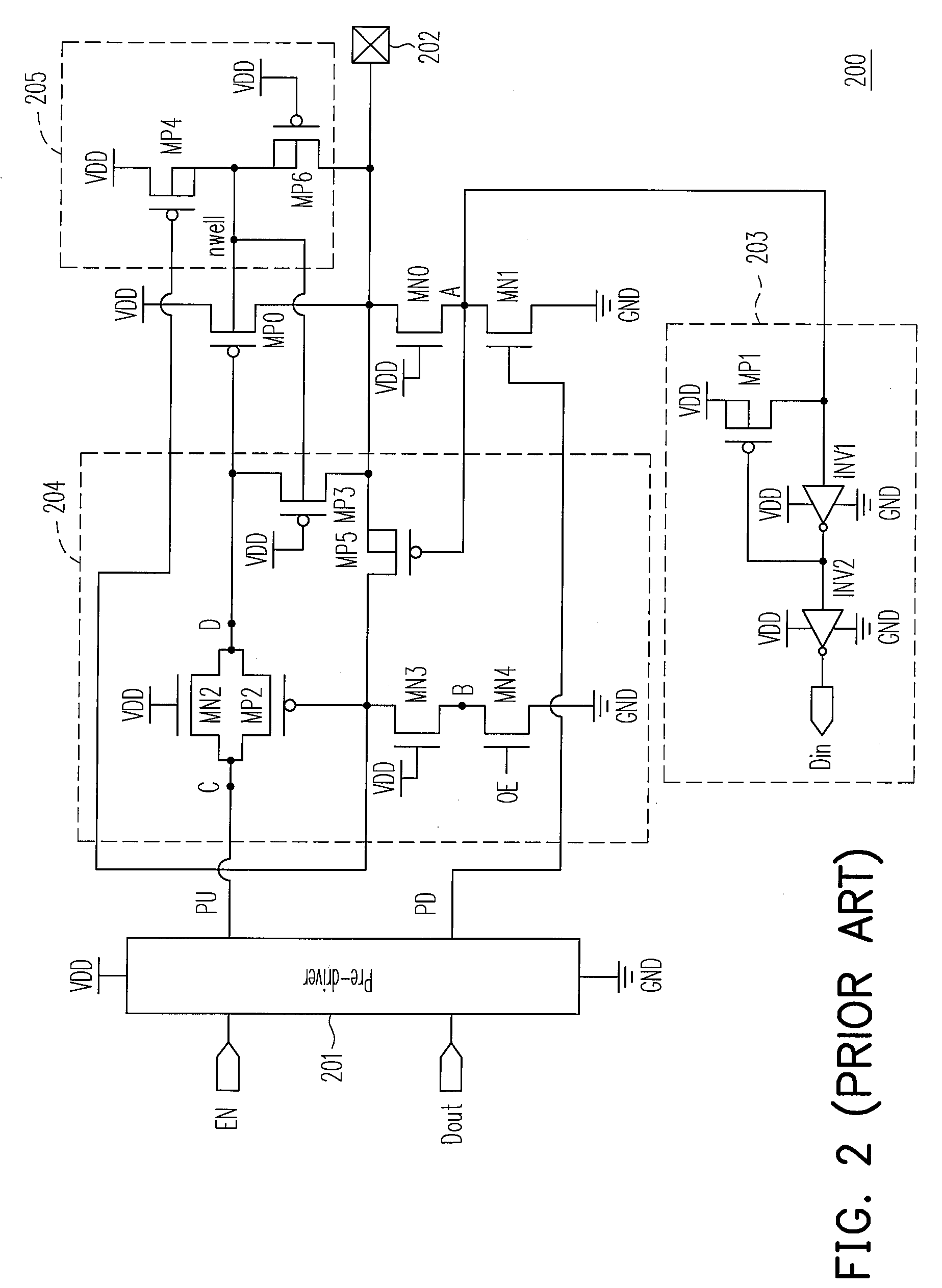

Mixed-voltage I/O buffer to limit hot-carrier degradation

InactiveUS20090002028A1Improve reliabilityVoltage toleranceReliability increase in field effect transistorsLogic circuit coupling/interface arrangementsHot carrier degradationGenerating unit

A Mixed-voltage input and output (I / O) buffer including a pre-driver unit, a bulk-voltage generating unit, a first to a third transistors and an input stage unit is provided. The pre-driver unit outputs a first source / drain and a second signal. The bulk-voltage generating unit determines whether a first voltage or a pad voltage is used as a bulk voltage according to the pad voltage level. A gate of the first transistor receives the first signal, and a bulk, a first source / drain and a second source / drain of the first transistor are respectively coupled to the bulk voltage, the first voltage and the pad. A gate of the third transistor receives the second signal, and a first source / drain and a second source / drain of the third transistor are respectively coupled to the input stage unit for receiving an input signal from the pad and a second voltage.

Owner:AMAZING MICROELECTRONICS

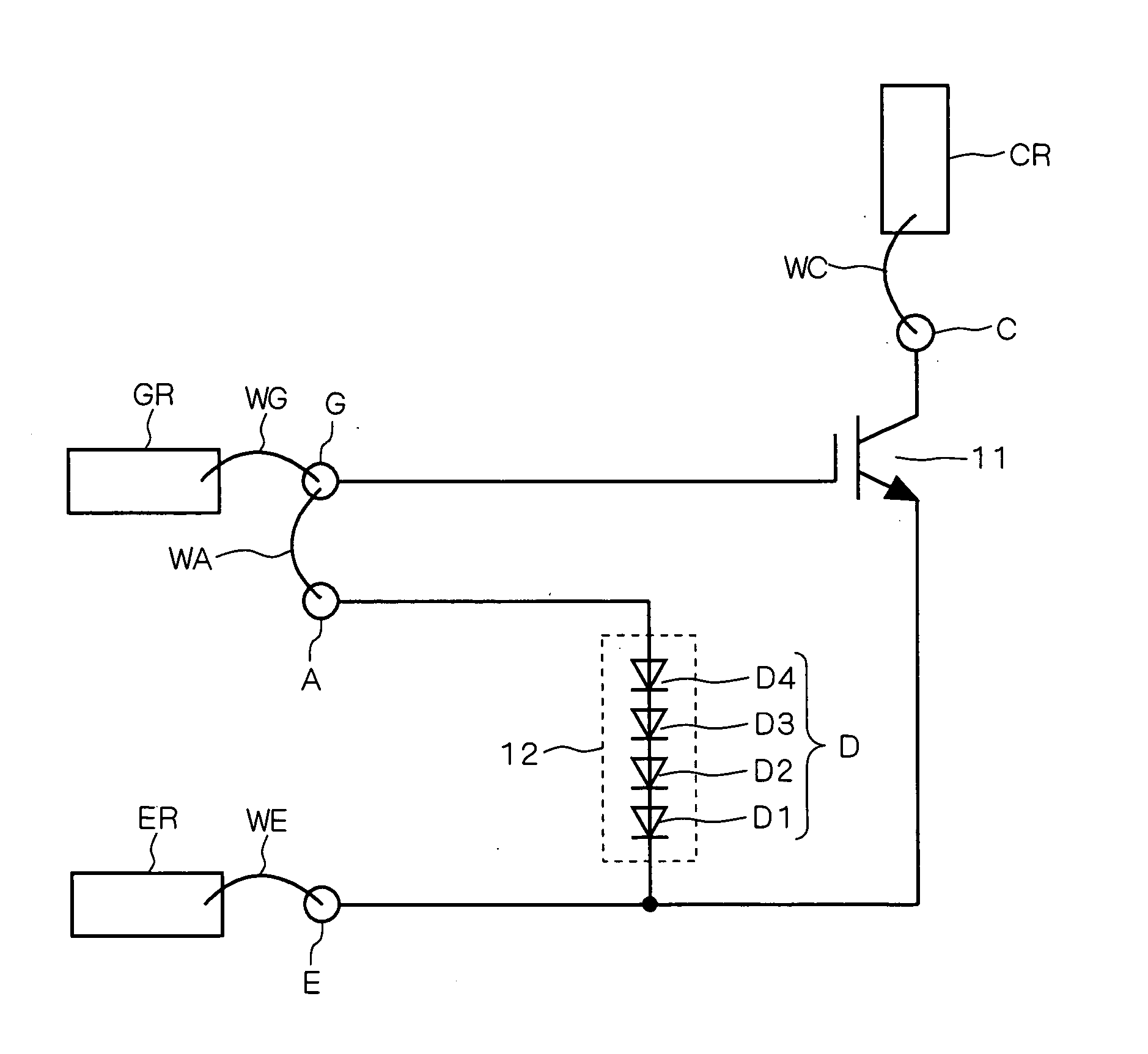

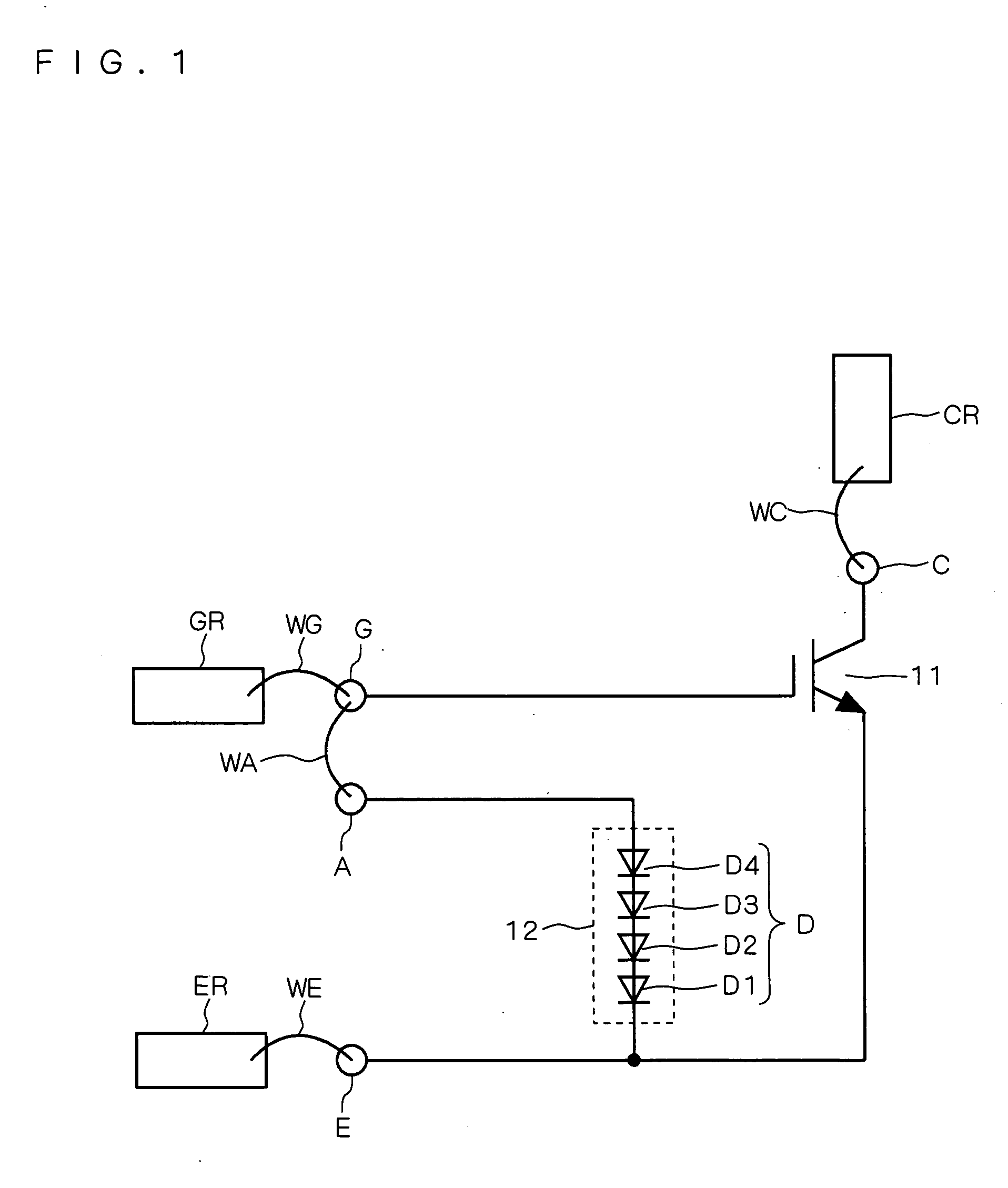

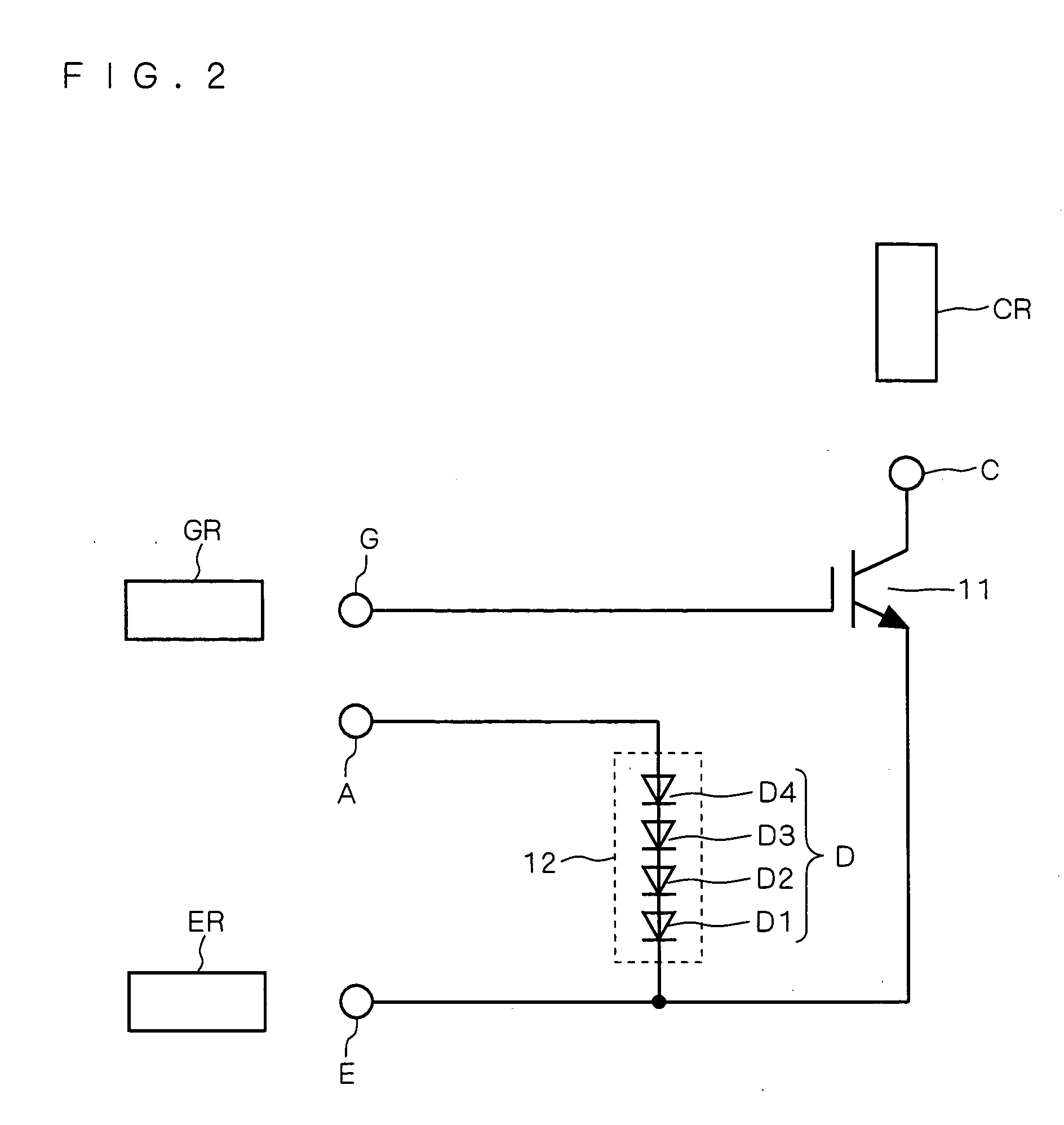

Semiconductor device and method of manufacturing thereof

InactiveUS20050122748A1EliminateImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSemiconductor

The gate of an IGBT is connected to a gate terminal. One end of a clamping element is connected to an anode terminal. A voltage higher than a clamping voltage is applied between the gate and the emitter, to thereby test the dielectric breakdown voltage of a gate insulating film of the IGBT. The IGBT is eliminated which has a gate insulating film at a dielectric breakdown voltage failing to fall within its proper distribution range. Thereafter, a gate terminal and an anode terminal are wire bonded in the normal IGBT.

Owner:MITSUBISHI ELECTRIC CORP

Silicon carbide mosfet device and method for manufacturing the same

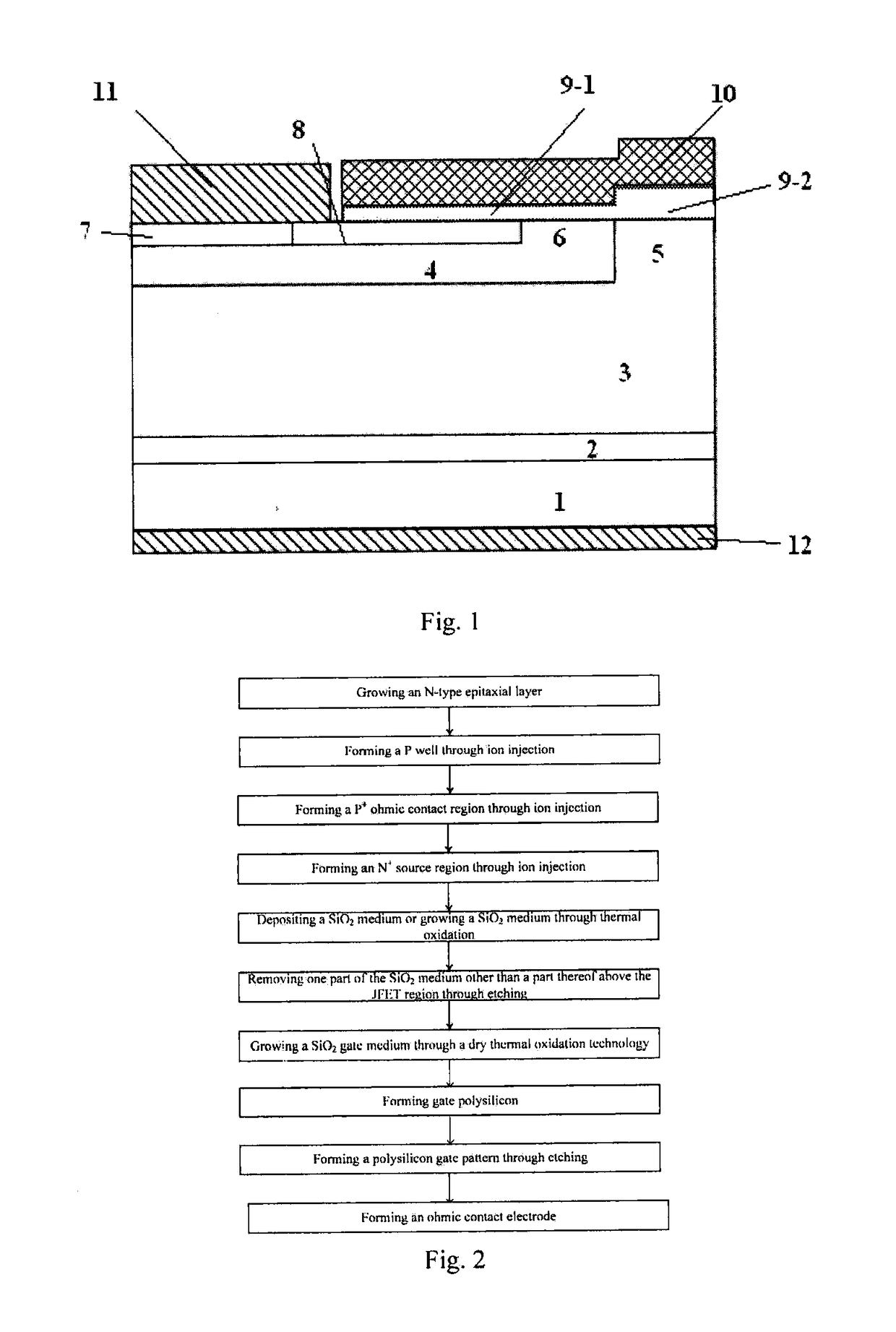

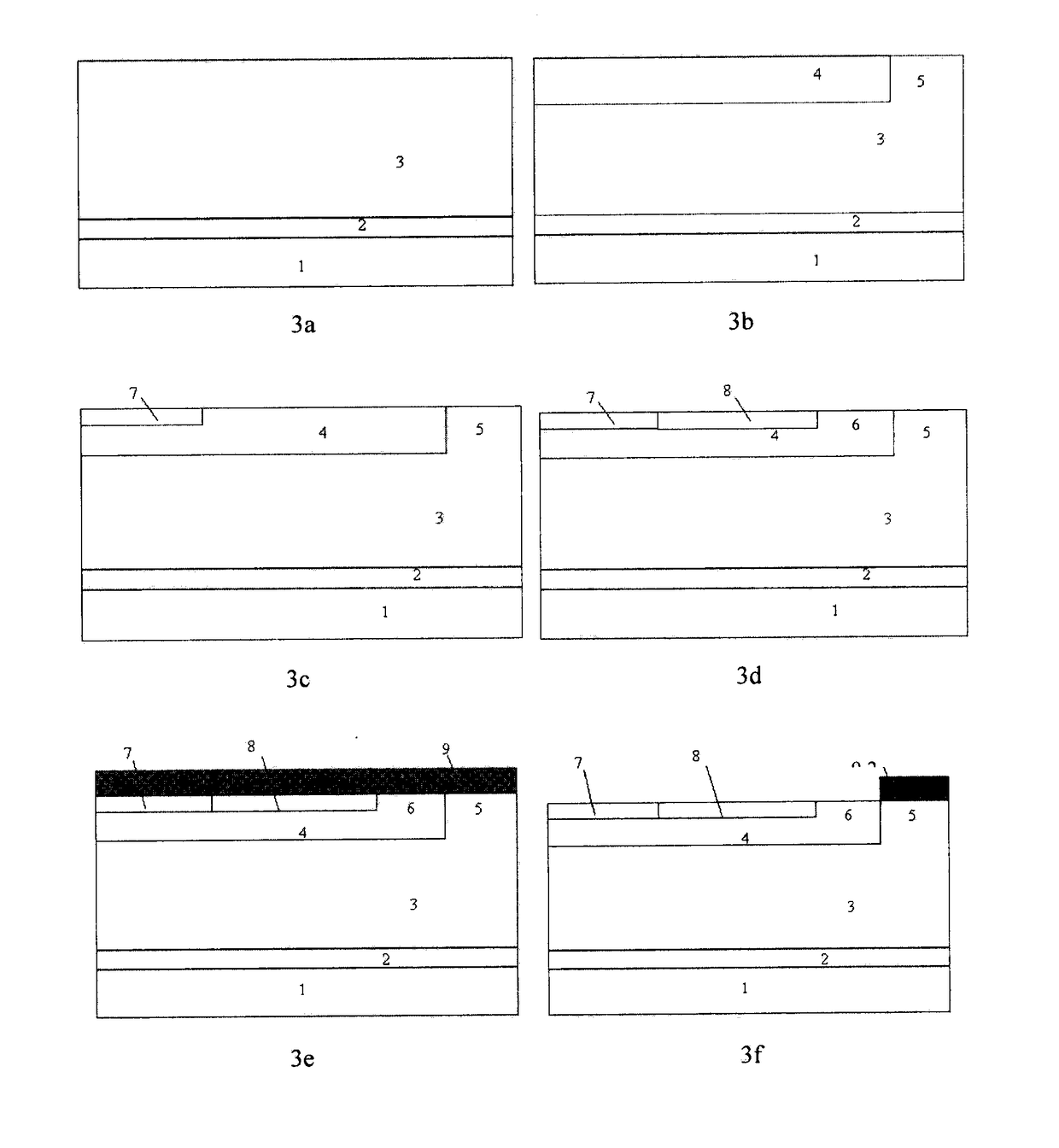

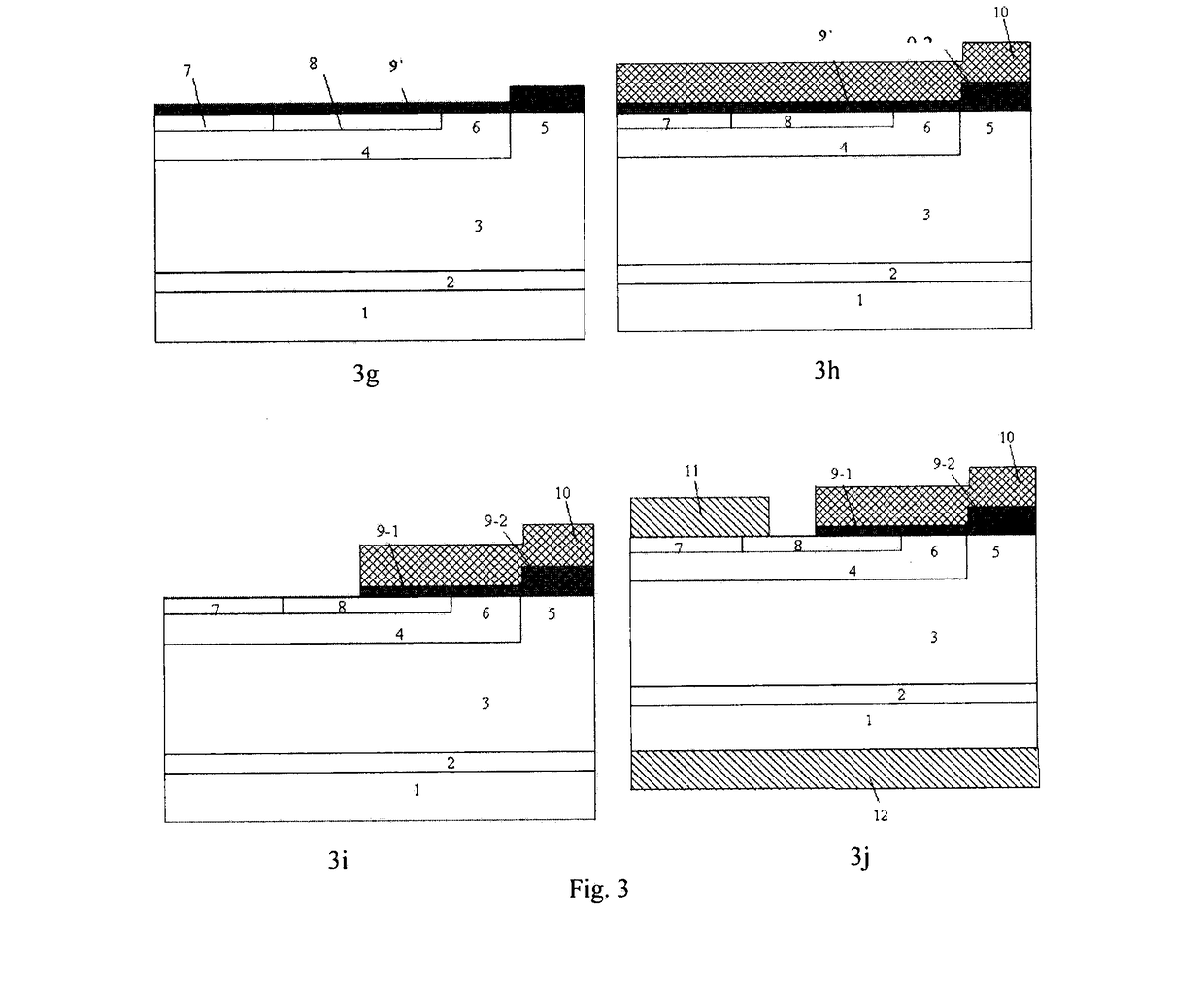

ActiveUS20190027568A1Improved structure and performanceSmall thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate oxide

A silicon carbide MOSFET device is disclosed. The silicon carbide MOSFET device includes a gate oxide layer which is constituted by a first gate oxide layer and a second gate oxide layer. A thickness of the second gate oxide layer is larger than a thickness of the first gate oxide layer. Through dividing the gate oxide layer into two parts with different thicknesses, i.e., enabling the gate oxide layer to have a staircase shape, an electric field strength of the gate oxide layer can be effectively reduced, while a threshold voltage and a gate control property of the device are not affected. An on-resistance of the device can be reduced through increasing a width of a JFET region. A method for manufacturing the silicon carbide MOSFET device is further disclosed.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

Method of manufacturing semiconductor devices

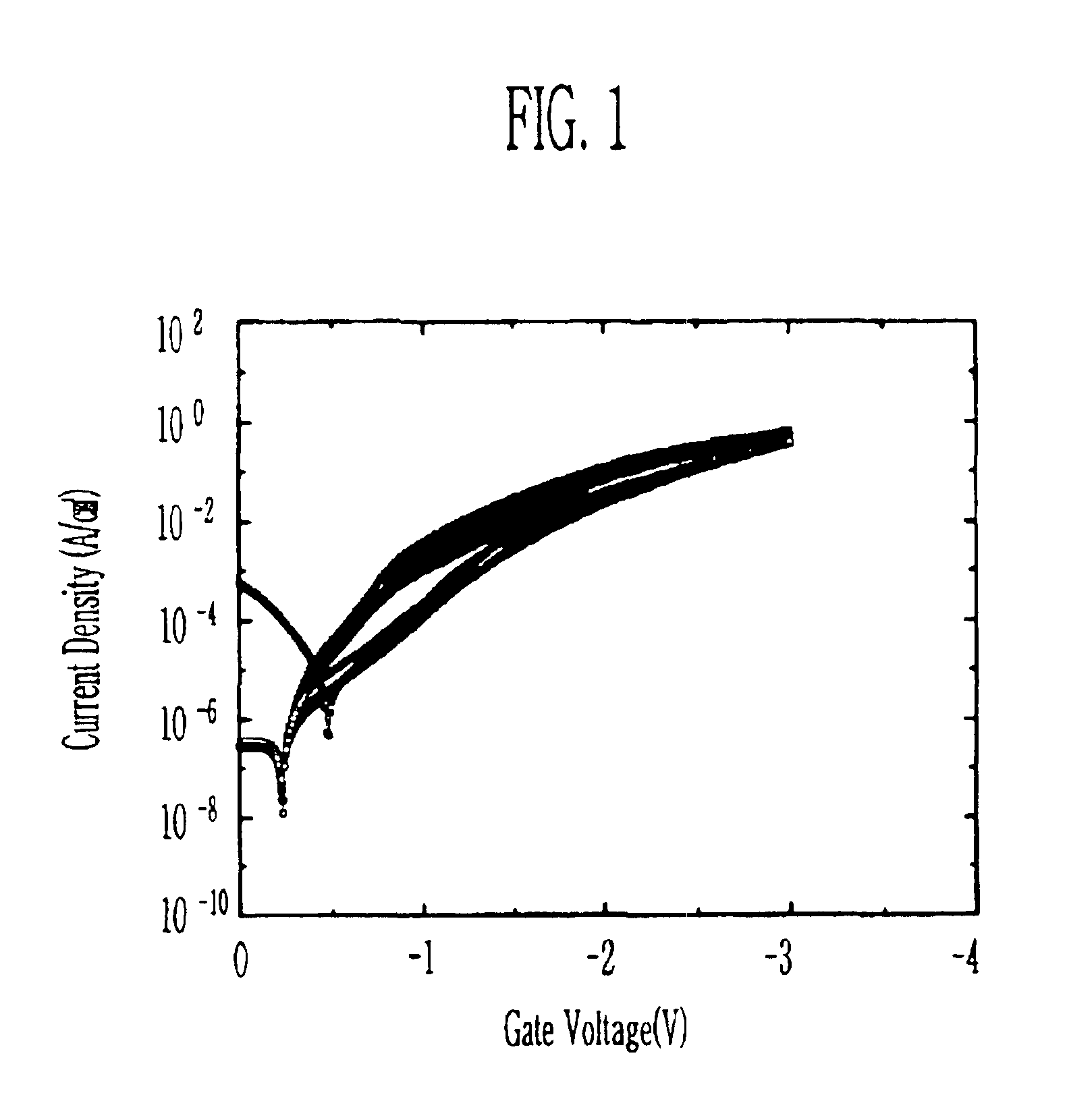

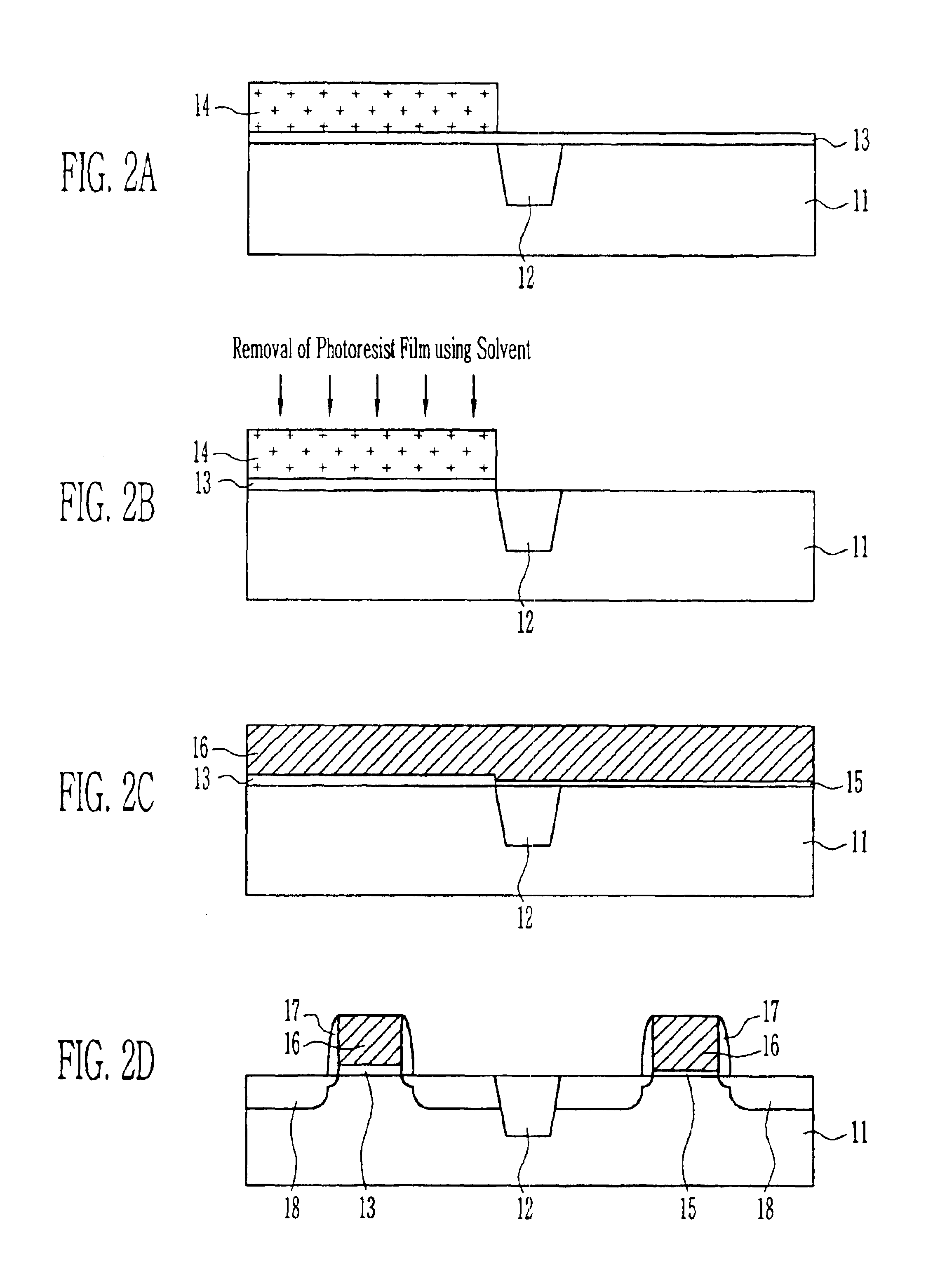

InactiveUS6828184B2Improve gate reliabilityPrevent breakdown voltageSemiconductor/solid-state device manufacturingLow voltageEngineering

Disclosed is a method of manufacturing semiconductor devices. In the process of simultaneously forming a high voltage device and a low voltage device, a photoresist film for patterning a gate oxide film in a high voltage device is removed in a wet mode using a solvent. The polysilicon film used as the gate electrode is then formed without applying a vacuum. It is thus possible to increase reliability of the gate oxide film, and prevent damage of the gate oxide film due to ozone plasma and penetration of a grain protrusion of the polysilicon film into the gate oxide film. Accordingly, the breakdown voltage characteristic of the gate oxide film is improved.

Owner:KEY FOUNDRY CO LTD