Patents

Literature

247results about How to "Improve interface quality" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

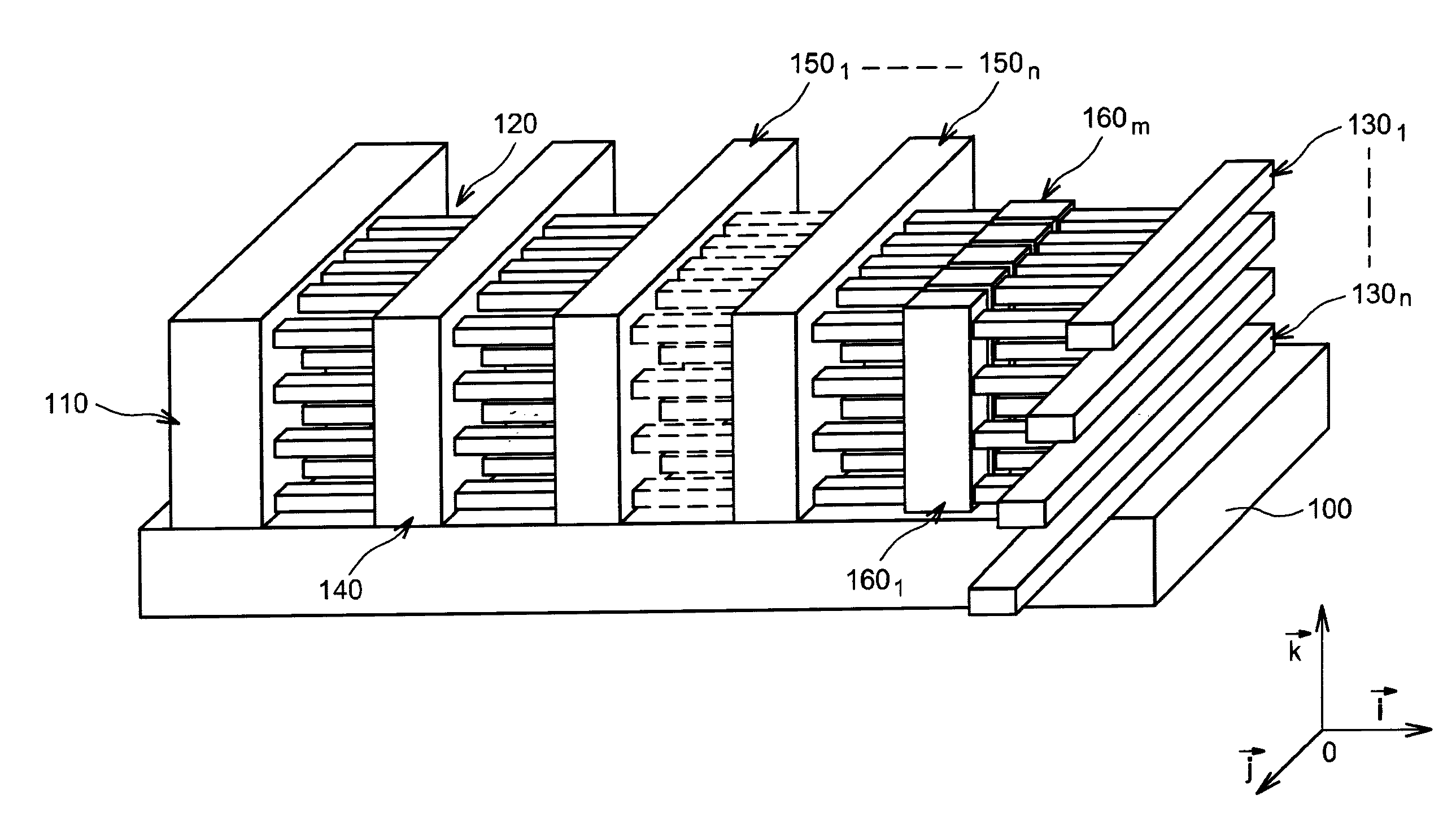

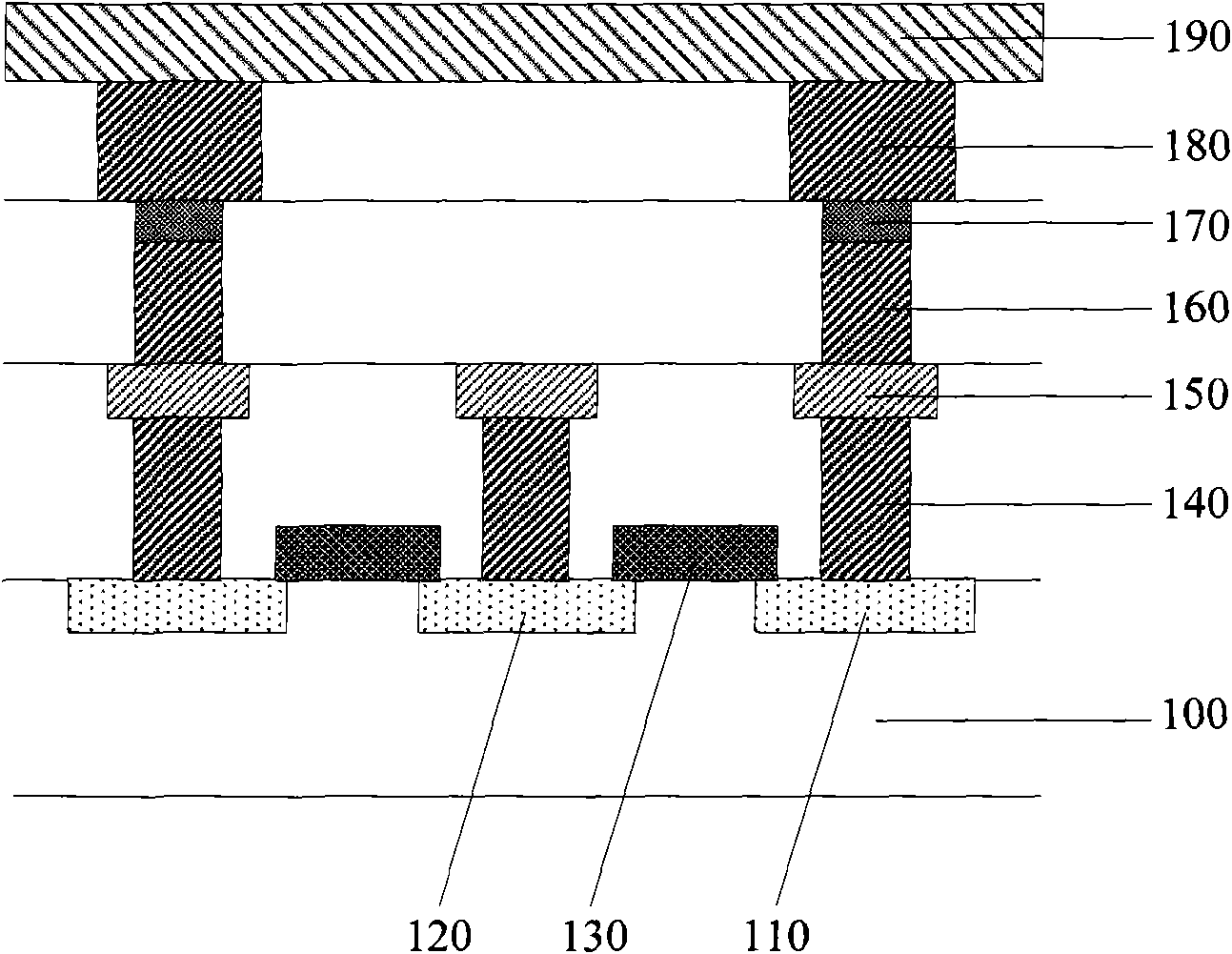

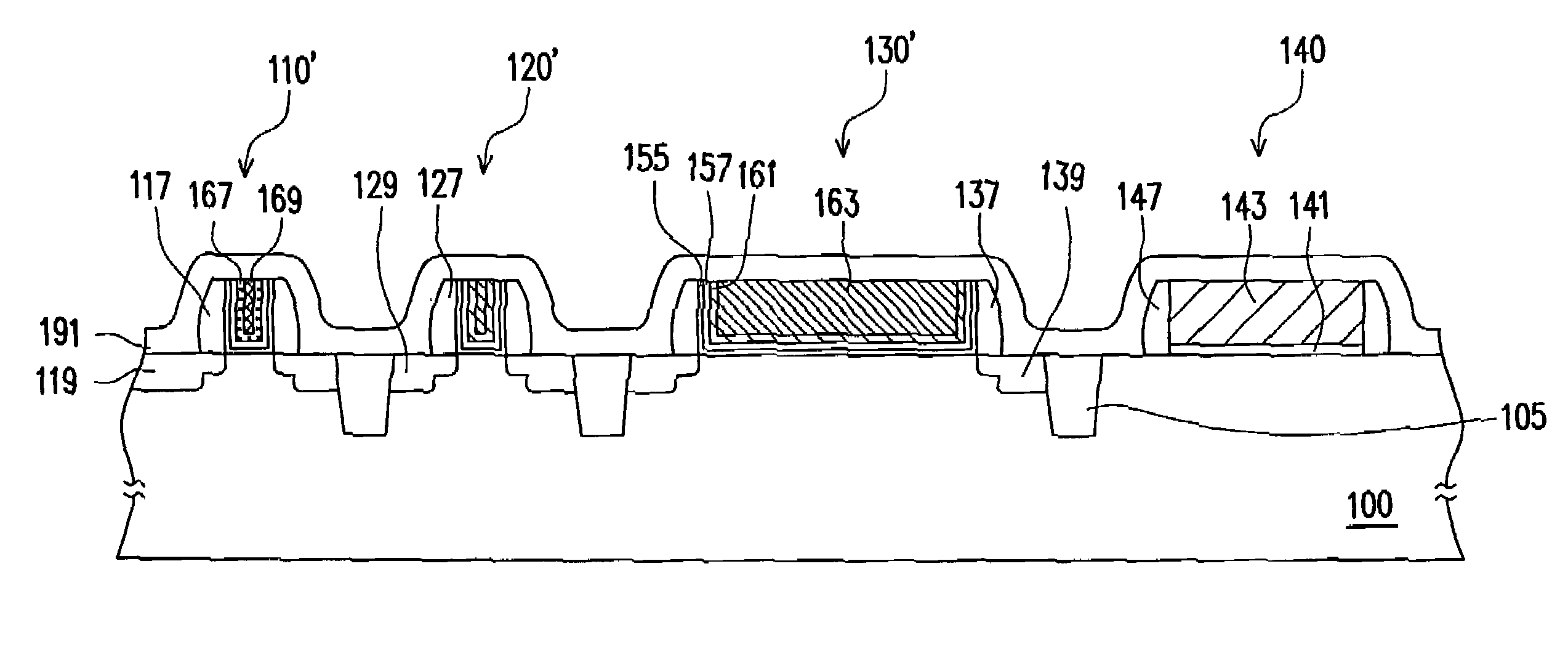

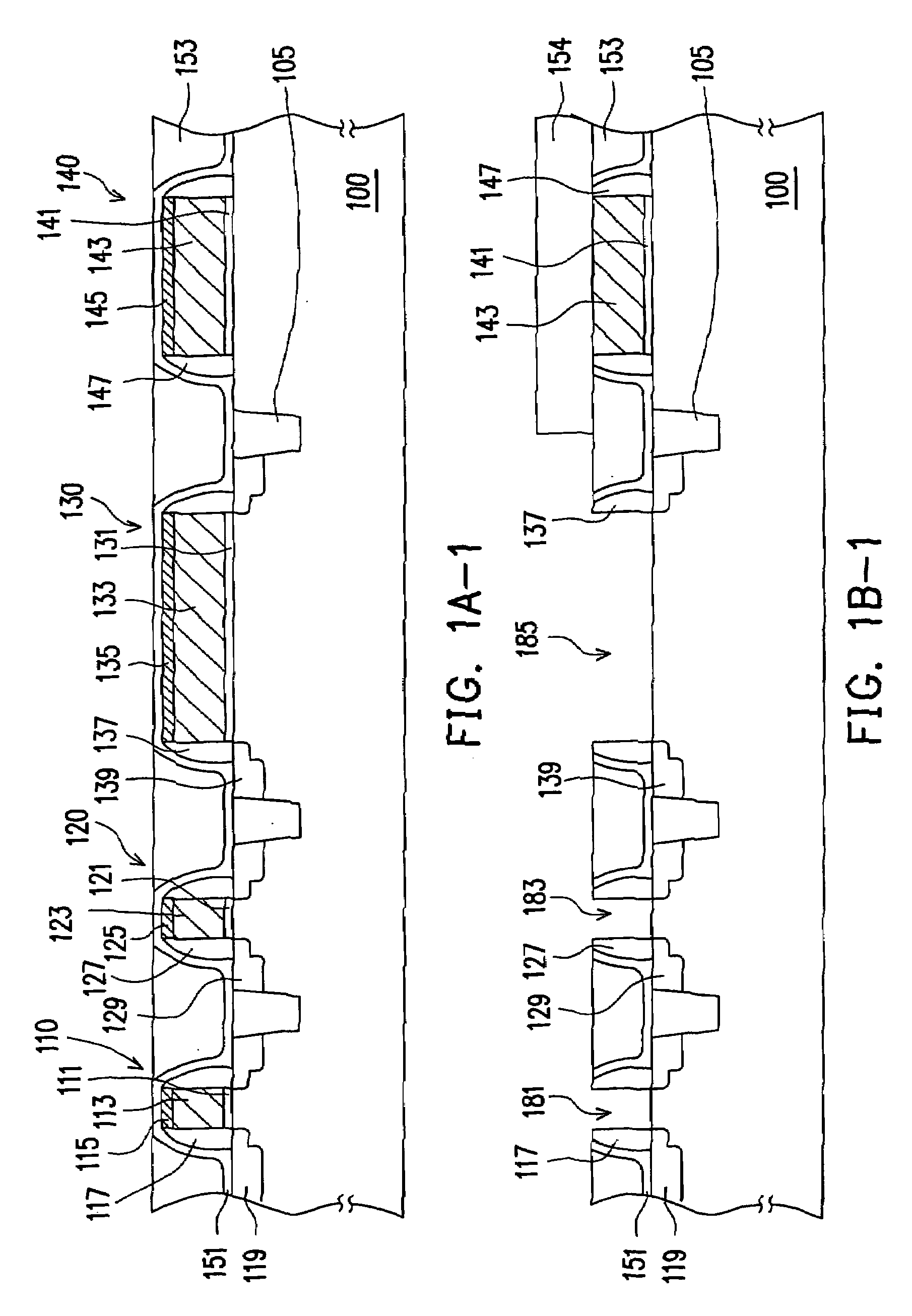

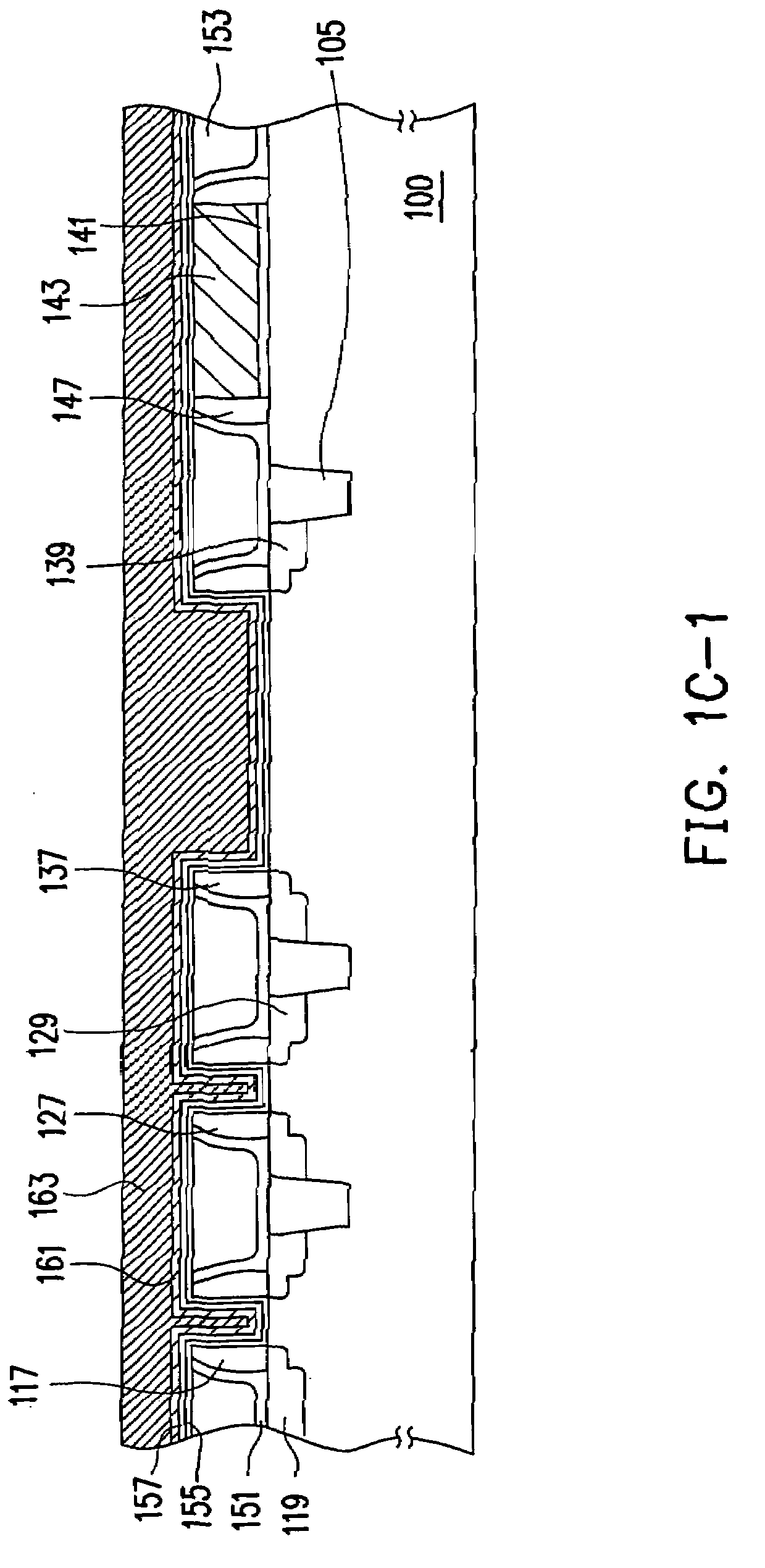

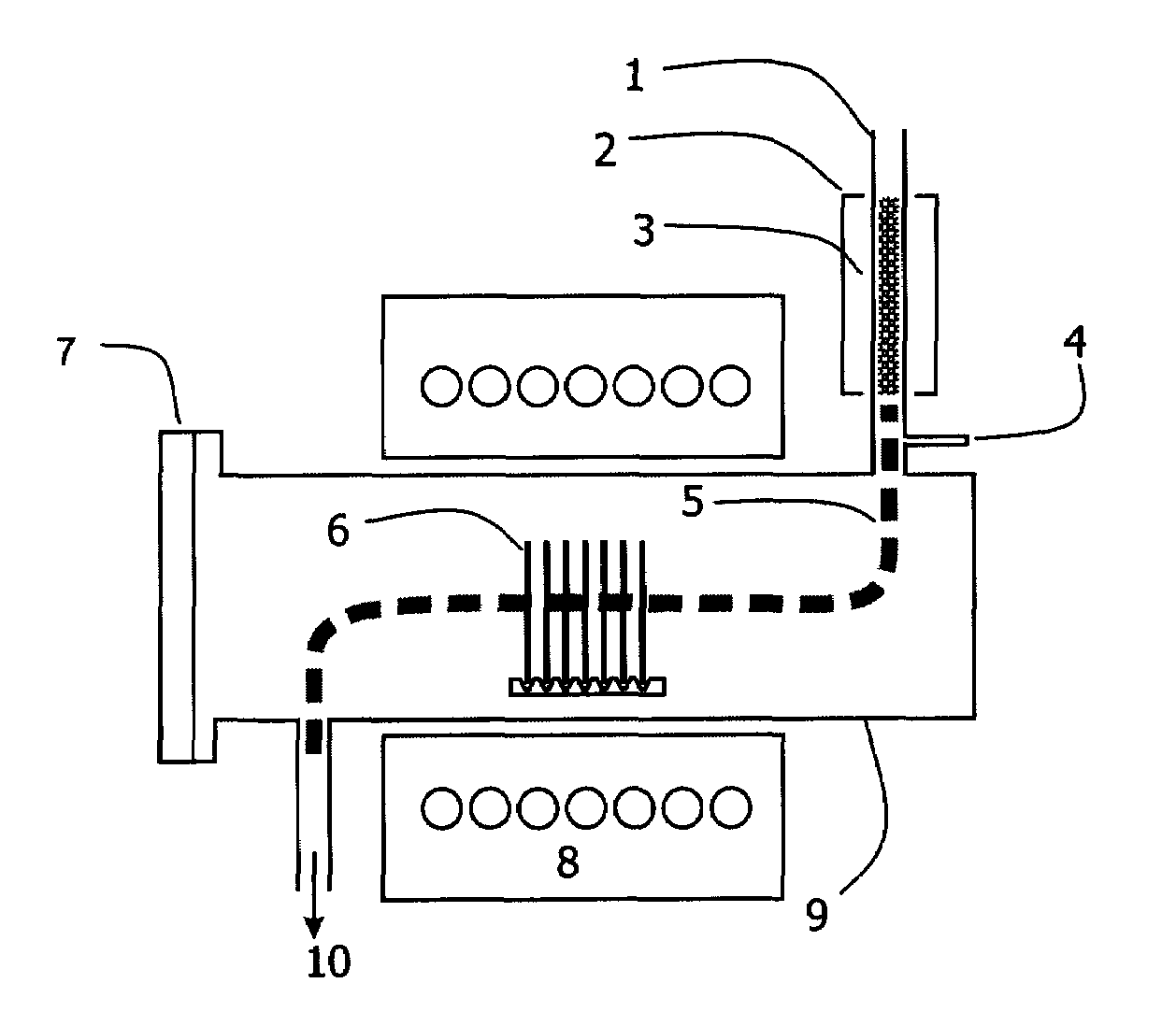

Structure and production process of a microelectronic 3D memory device of flash NAND type

ActiveUS20110169067A1Improve interface qualityAvoid exposureTransistorSolid-state devicesTransistor channelEngineering

A microelectronic flash memory device including a plurality of memory cells including transistors fitted with a matrix of channels connecting a block of common source to a second block on which bit lines rest, the transistors also being formed by a plurality of gates including at least one gate material, including a first selection gate coating the channels, a plurality of control gates coating the channels, a plurality of second selection gates each coating the channels of the same row and the matricial arrangement, at least one or more of the gates based on superposition of layers including at least one first layer of dielectrical material, at least one charge store zone, and at least one second layer of dielectrical material.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

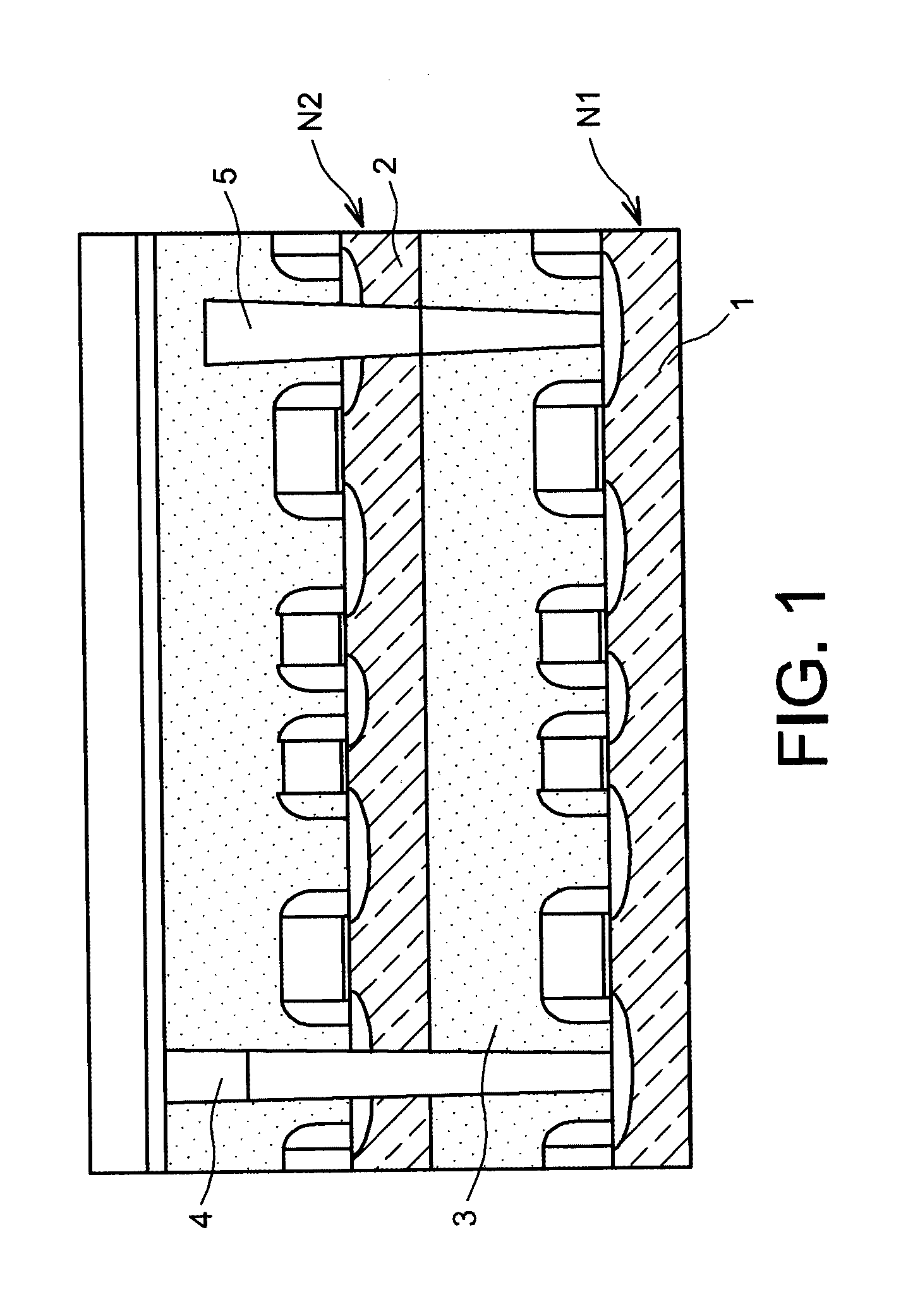

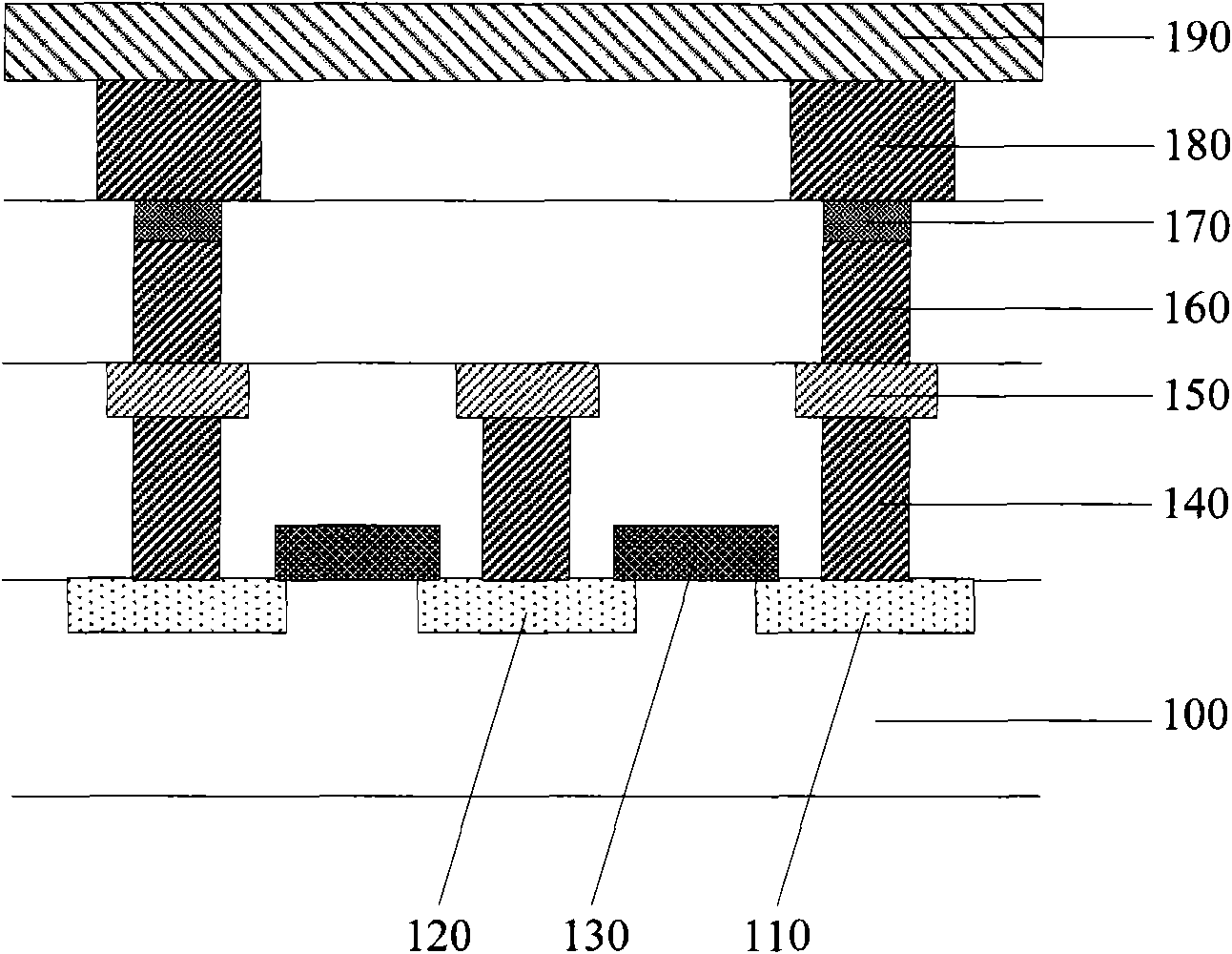

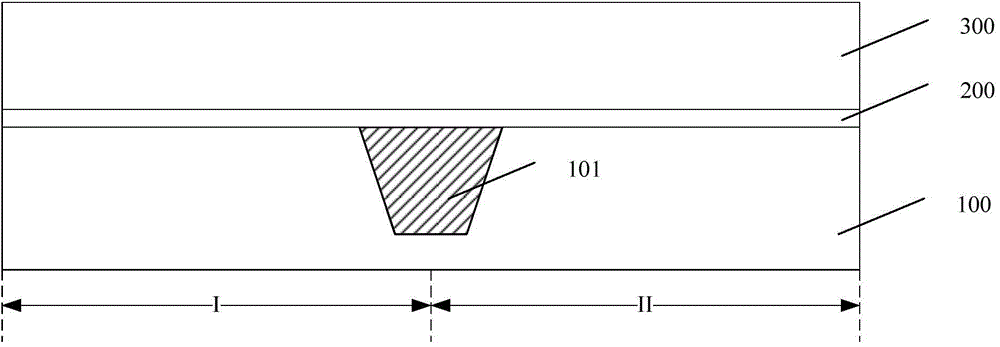

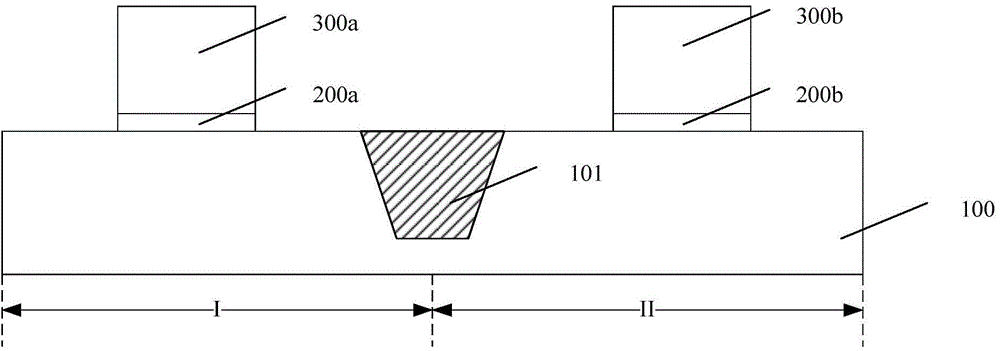

Resistance memory an a method for fabricating integrated circuit with same

ActiveCN101572246ARealize interlayer interconnect structureSimple processSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceCore component

The invention relates to a method for fabricating an integrated circuit with a resistance memory, comprising the following steps: providing an interlaminar dielectric layer comprising a core component area and a peripheral circuit area; forming a first interconnection structure and a second interconnection structure which are respectively formed by a blocking layer and a metal wiring structure in the interlaminar dielectric layer; forming a blocking dielectric layer on the interlaminar dielectric layer; etching the blocking dielectric layer to expose the metal wiring structure of the core component area; forming a first dielectric layer on the metal wiring structure; forming a first conductive layer covering the blocking dielectric layer and the first dielectric layer; forming a masking film on the first conductive layer; etching the first conductive layer and the blocking dielectric layer until the second interconnecting structure is exposed; keeping the first conductive layer and a blocking dielectric layer on the first interconnecting structure; and forming a second conductive layer and a third conductive layer respectively on the first conductive layer and the second interconnecting structure. Due to the adoption of the method for fabricating the integrated circuit with the resistance memory, when the resistance memory is formed, the interlaminar interconnection structures of the core component area and the peripheral circuit area can be also formed.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

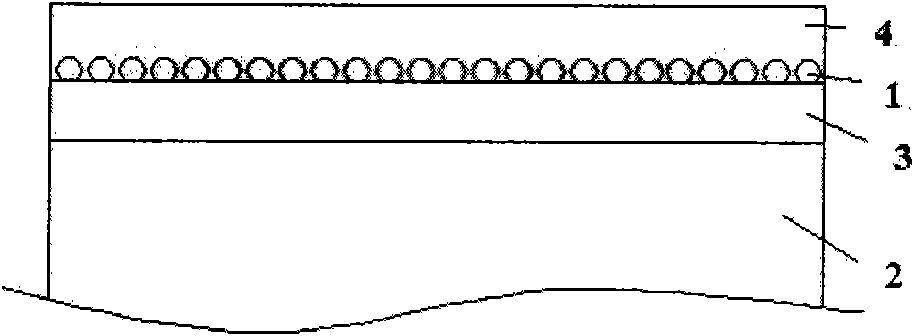

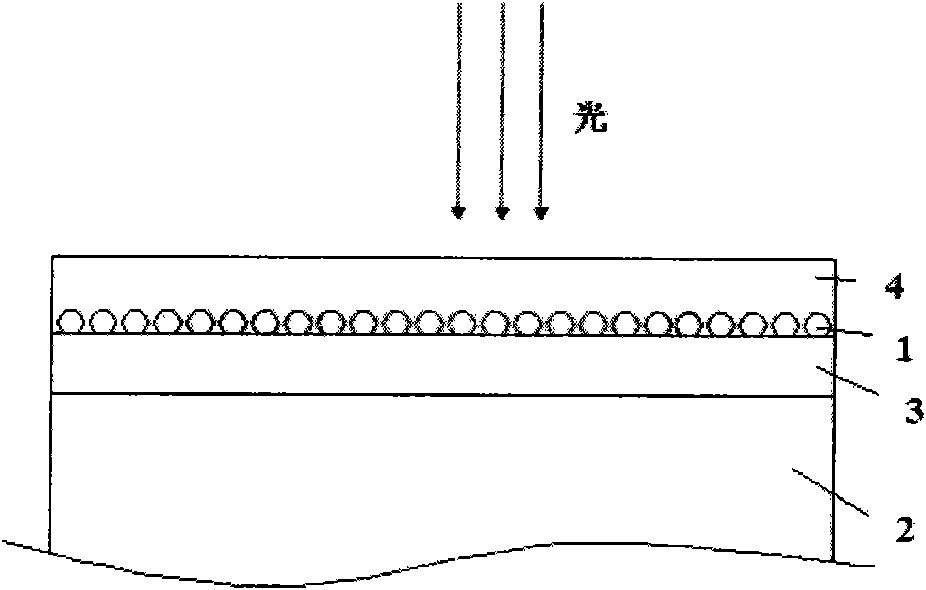

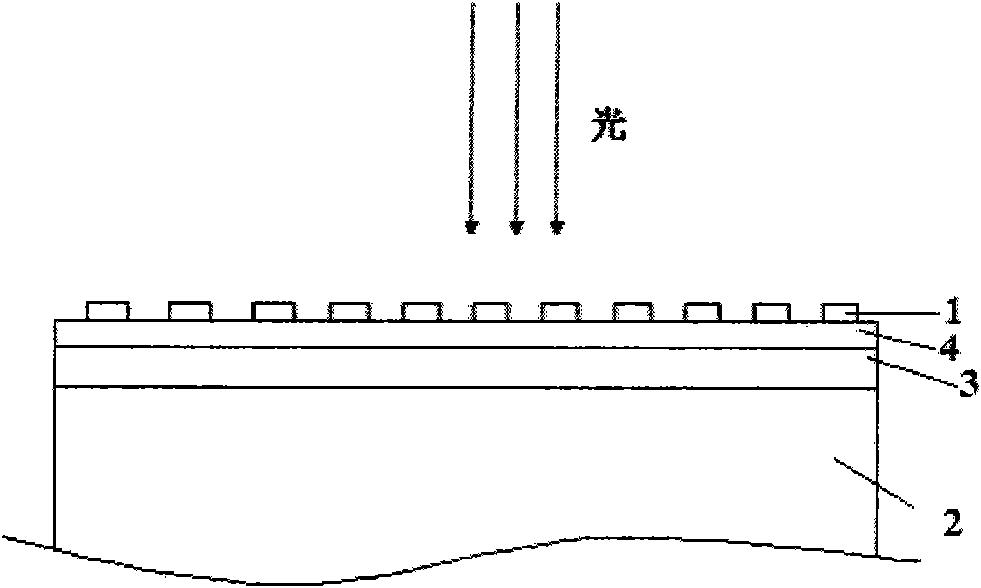

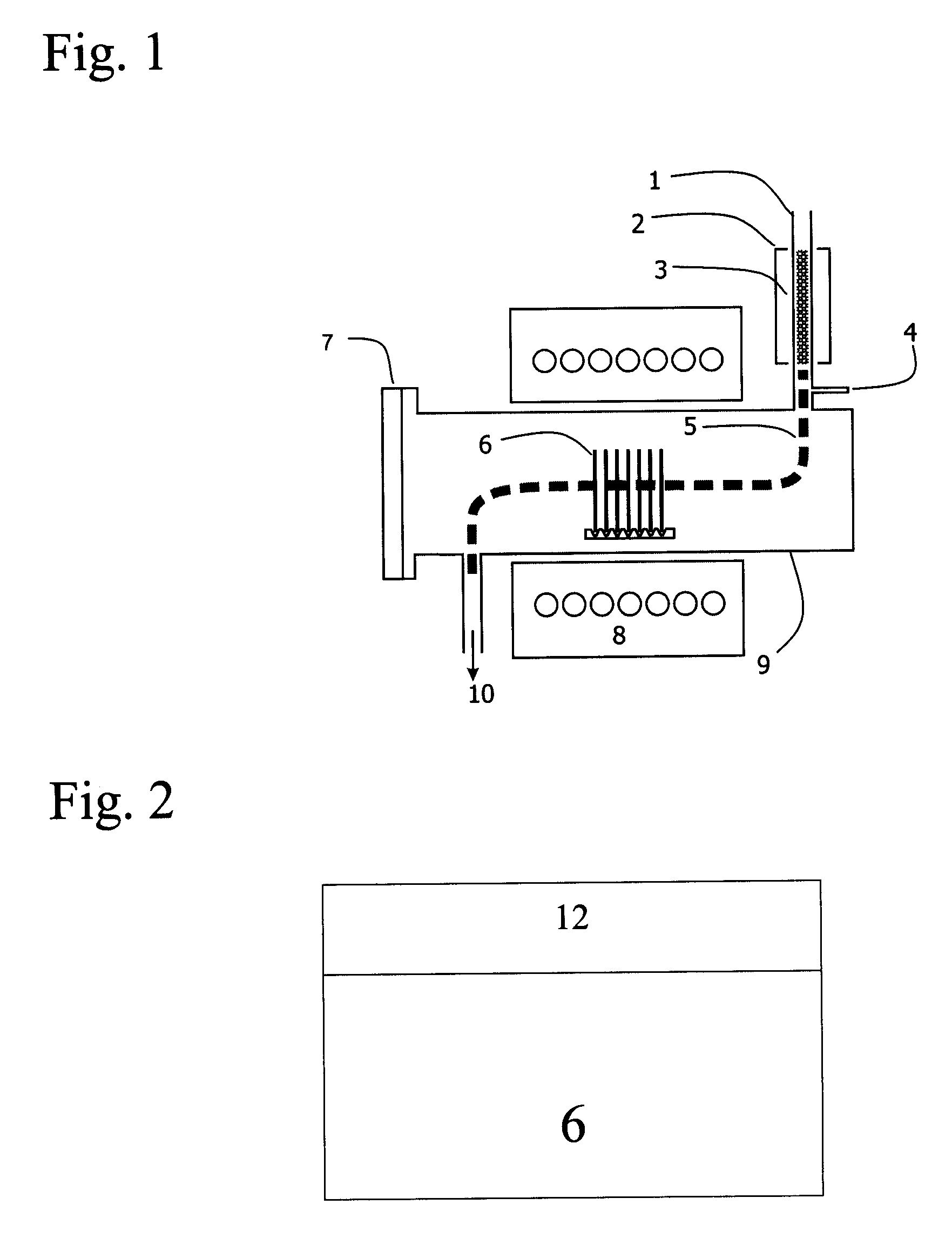

Light trapping structure for thin film silicon/crystalline silicon heterojunction solar battery

InactiveCN101866961AReduce interface state densityImprove performancePhotovoltaic energy generationSemiconductor devicesHeterojunctionSurface plasmon

The invention discloses a light trapping structure for a thin film silicon / crystalline silicon heterojunction solar battery, which comprises a crystalline silicon substrate (2), a doped thin film silicon layer (3) on the crystalline silicon substrate (2), a transparent conductive electrode (4) on the doped thin film silicon layer (3), and a metal nano-structure (1) between the doped thin film silicon layer (3) and the transparent conductive electrode (4), a metal nano-structure (1) above the transparent conductive electrode (4), or a metal nano-structure (1) inside the transparent conductive electrode (4). The connecting surface of the crystalline silicon substrate (2) and the crystalline silicon substrate (2) is not specially woven with velvet. The light trapping structure acquires a light trapping effect by using a surface plasmon effect of the metal nano-structure.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

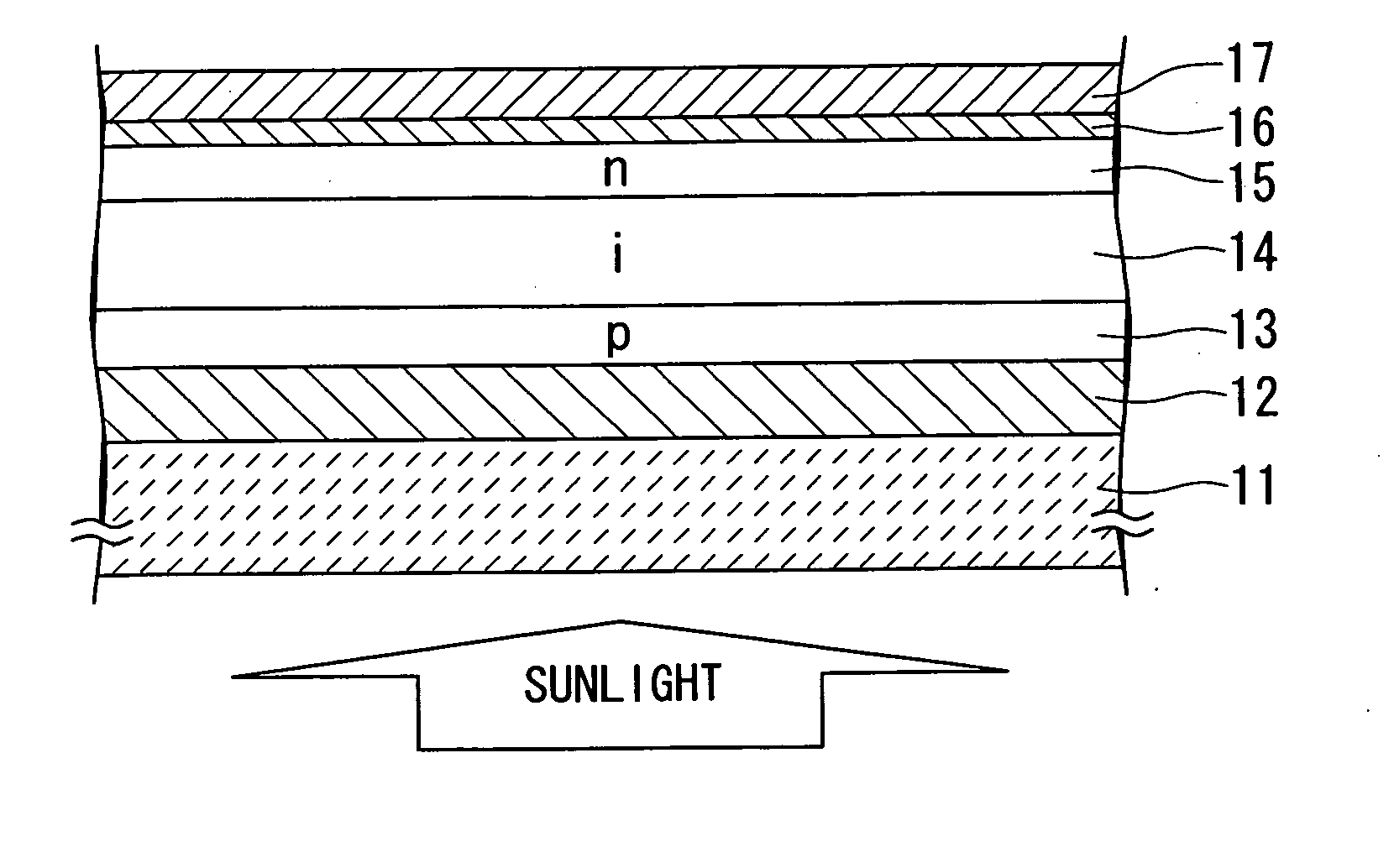

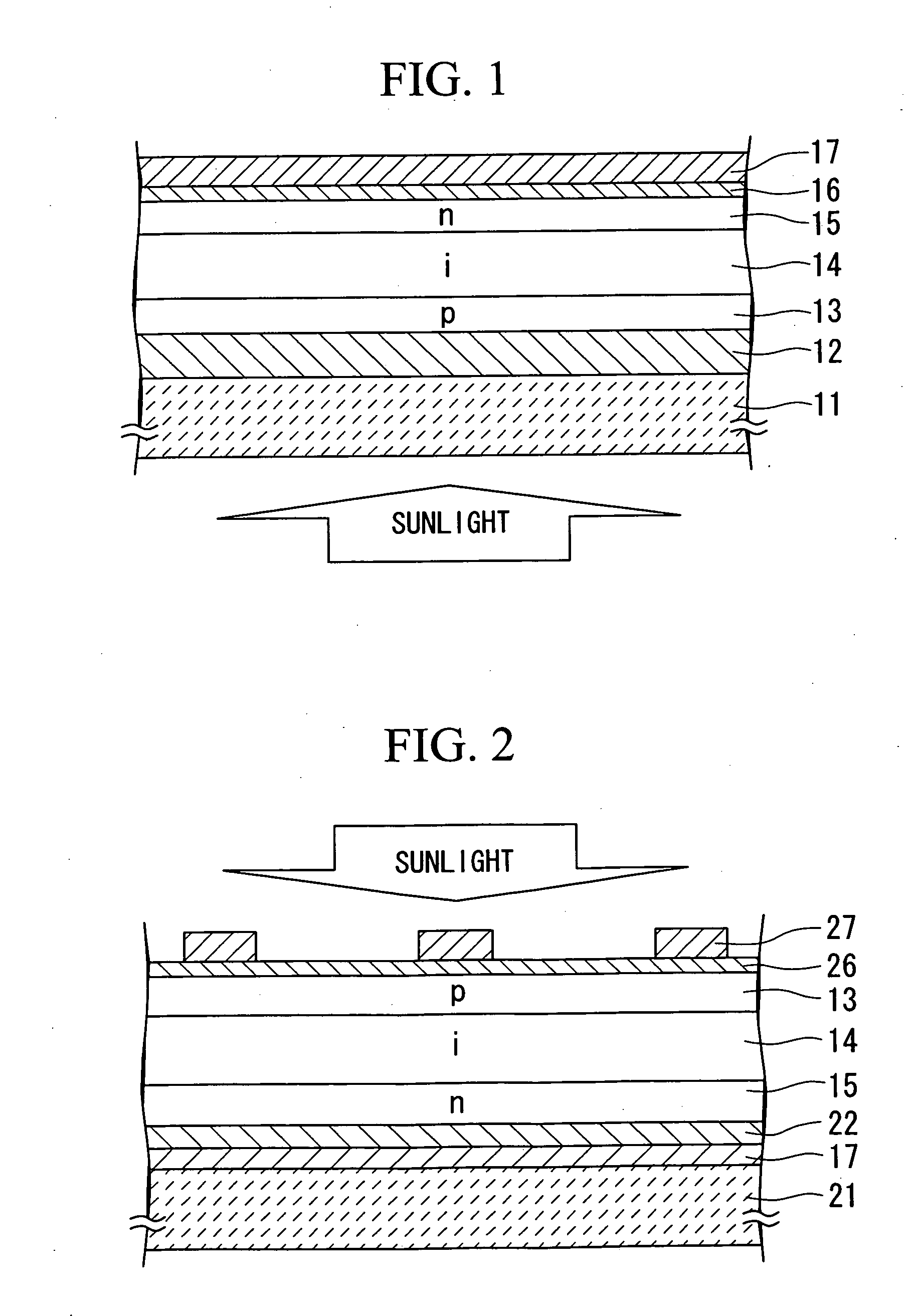

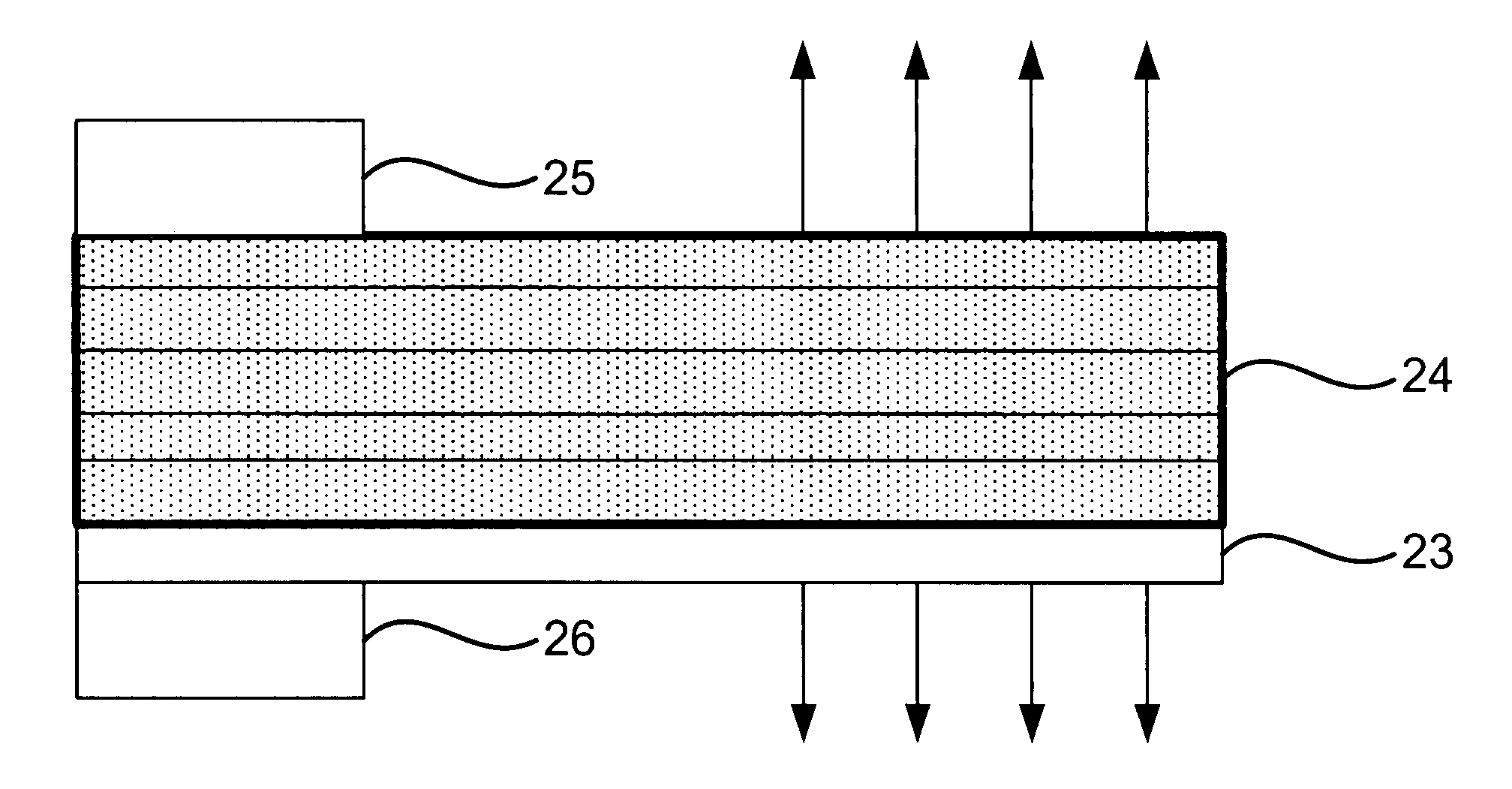

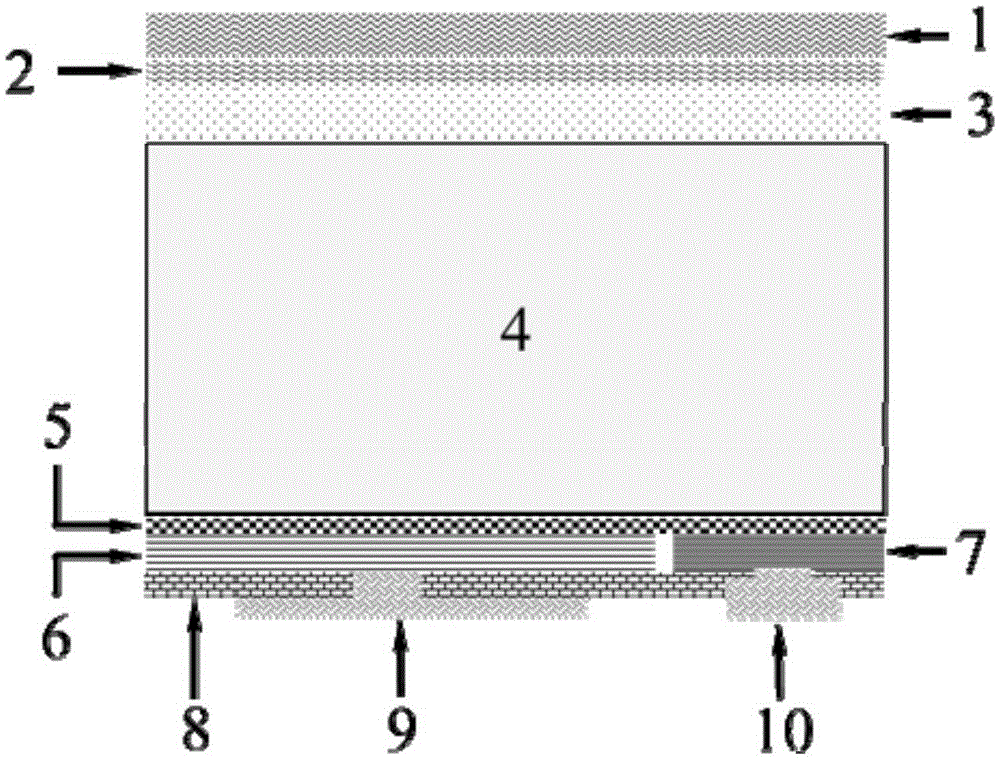

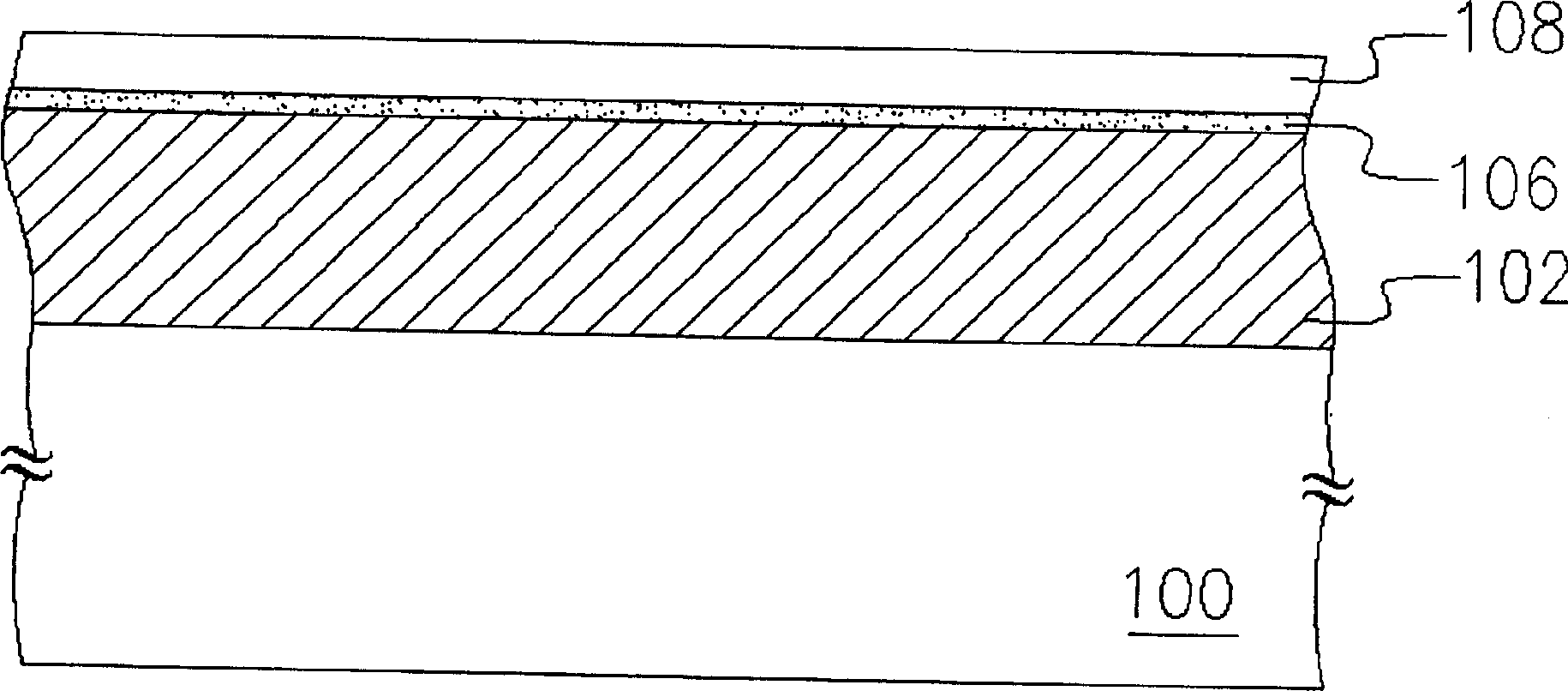

Photovoltaic device

InactiveUS20050205127A1High light transmittanceReduce harmPV power plantsPhotovoltaic energy generationMicrocrystalline siliconP type silicon

A photovoltaic device is formed by depositing at least a first transparent electrode, PIN-structured or NIP-structured microcrystalline silicon layers, a second transparent electrode, and a back electrode in sequence on an electrically insulating transparent substrate. The PIN-structured or NIP-structured microcrystalline silicon layers include a p-type silicon layer, an i-type silicon layer, and an n-type silicon layer. At least one of the first transparent electrode and the second transparent electrode is a ZnO layer doped with Ga, and the Ga concentration is 15 atomic percent or less with respect to Zn.

Owner:MITSUBISHI HEAVY IND LTD

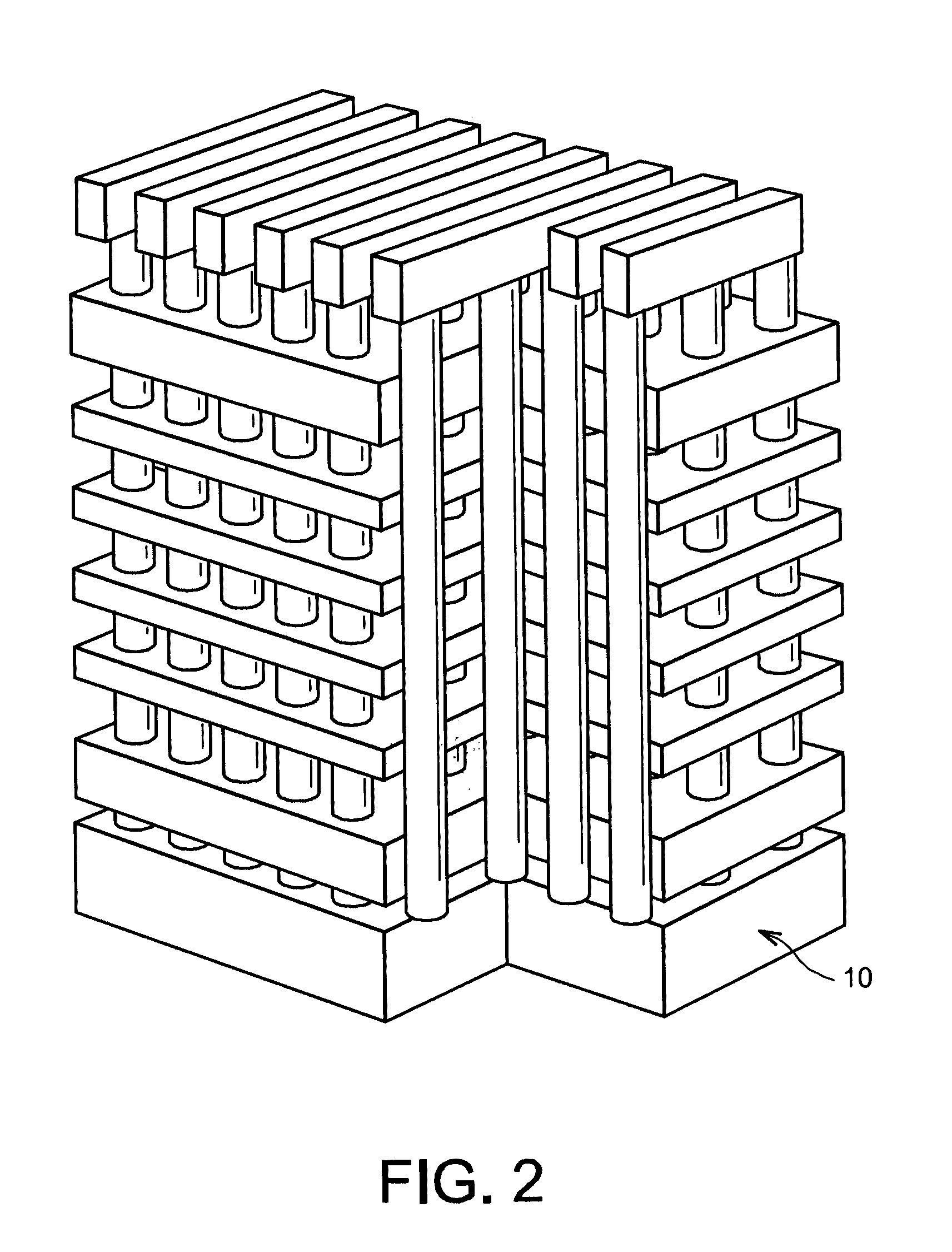

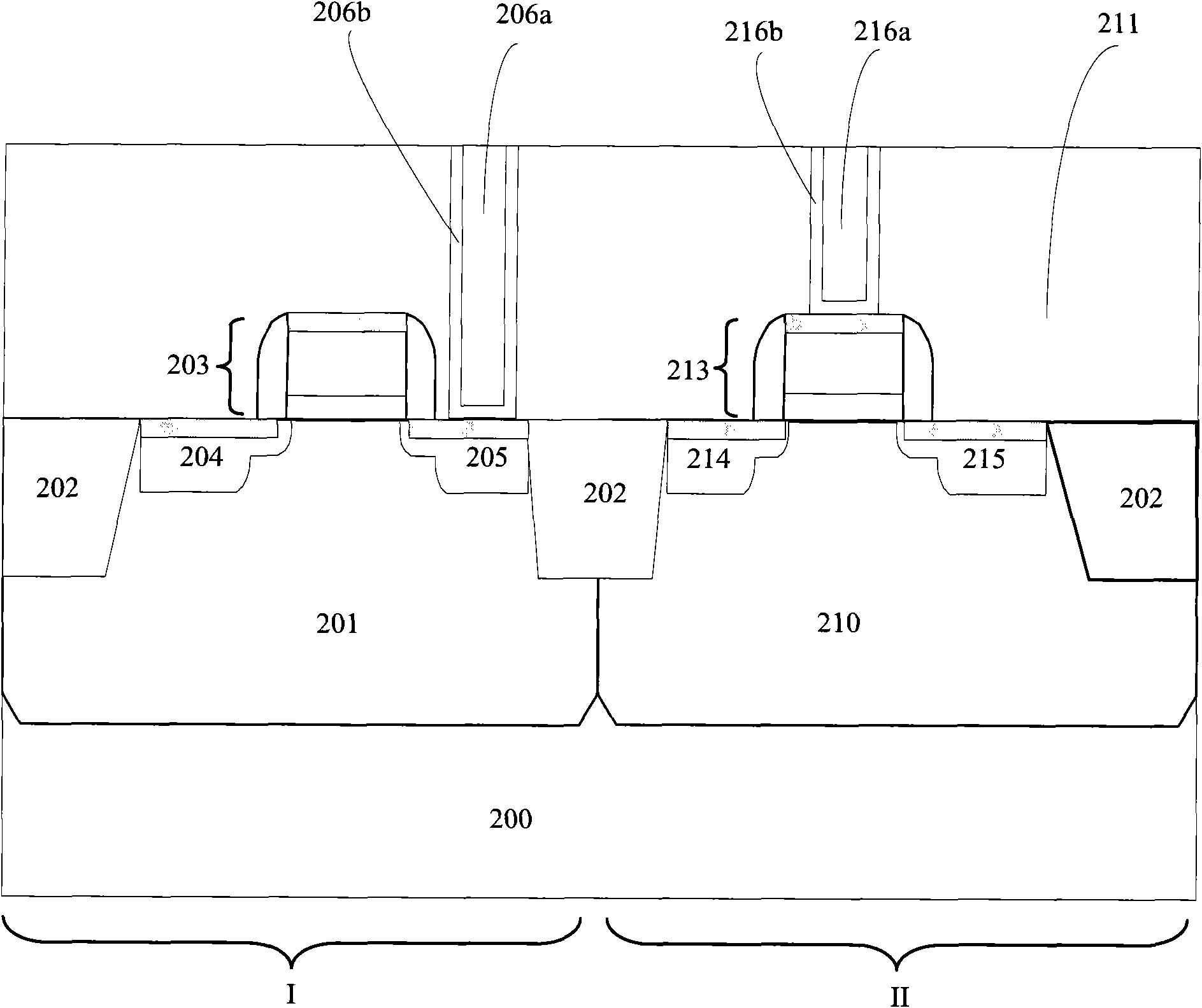

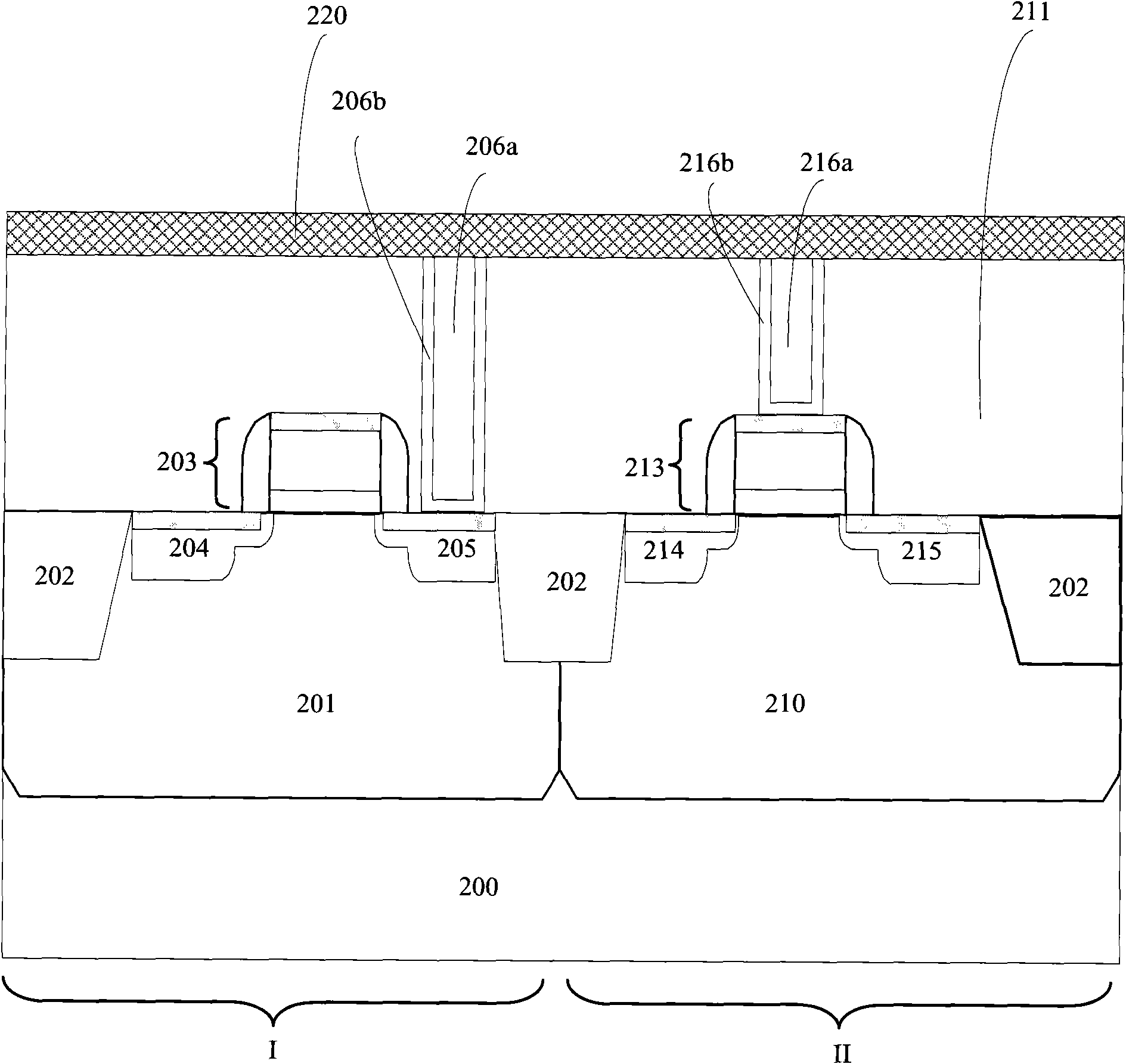

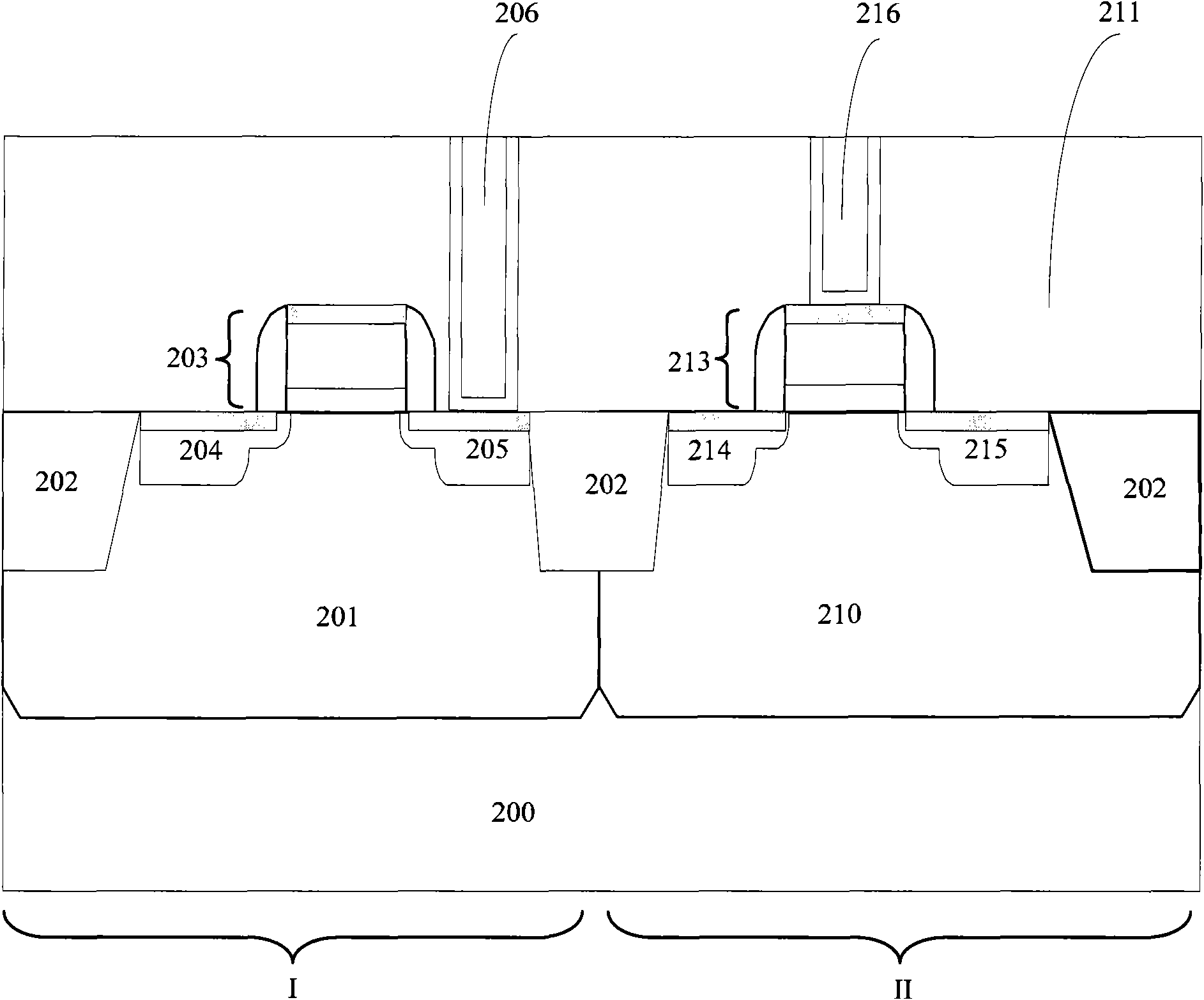

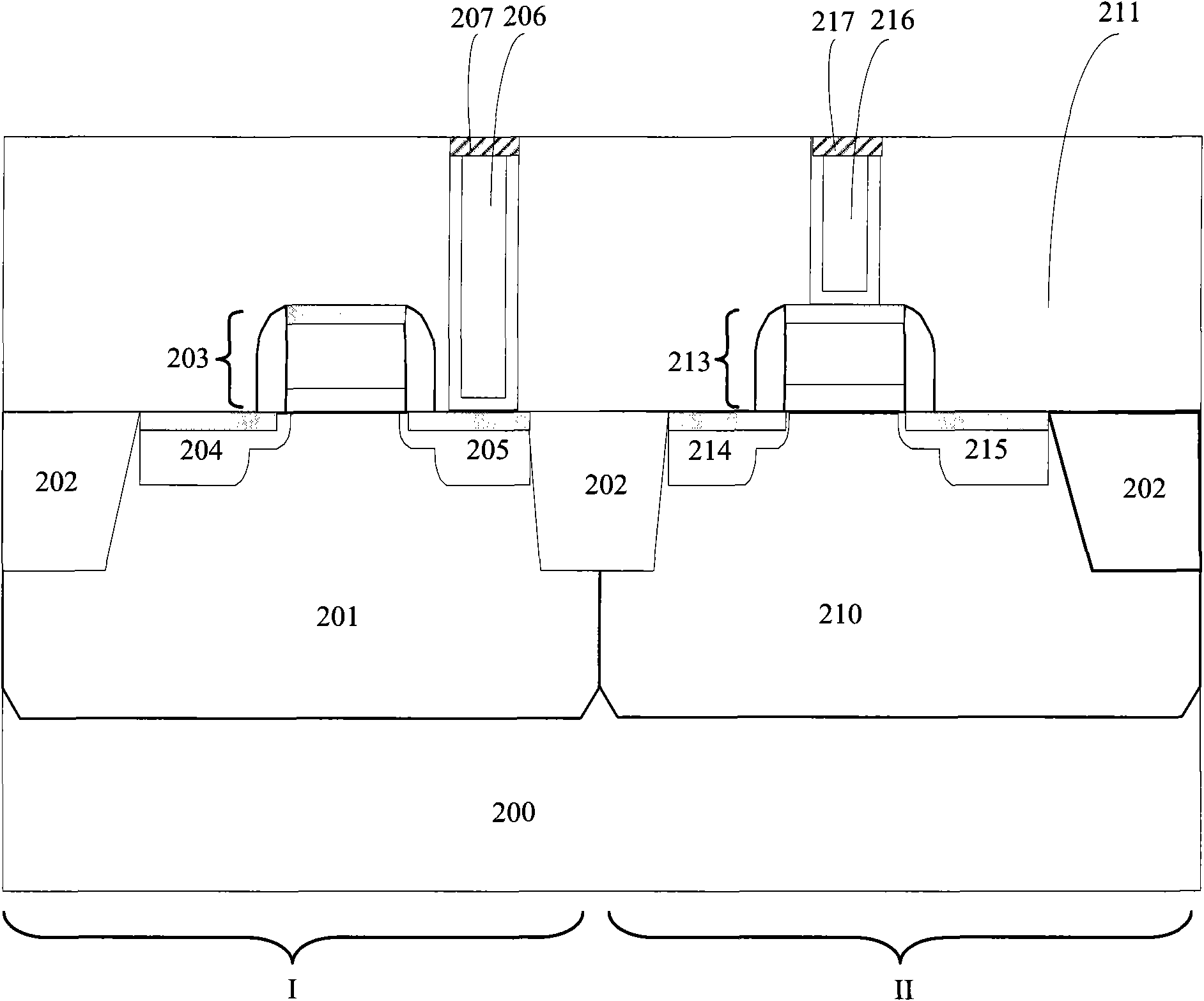

Method for fabricating semiconductor structure and structure of static random access memory

ActiveUS20090242997A1Avoid quality lossAvoid damageSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memorySemiconductor structure

A method for fabricating a semiconductor structure is disclosed. A substrate with a first transistor having a first dummy gate and a second transistor having a second dummy gate is provided. The conductive types of the first transistor and the second transistor are different. The first and second dummy gates are simultaneously removed to form respective first and second openings. A high-k dielectric layer, a second type conductive layer and a first low resistance conductive layer are formed on the substrate and fill in the first and second openings, with the first low resistance conductive layer filling up the second opening. The first low resistance conductive layer and the second type conductive layer in the first opening are removed. A first type conductive layer and a second low resistance conductive layer are then formed in the first opening, with the second low resistance conductive layer filling up the first opening.

Owner:MARLIN SEMICON LTD

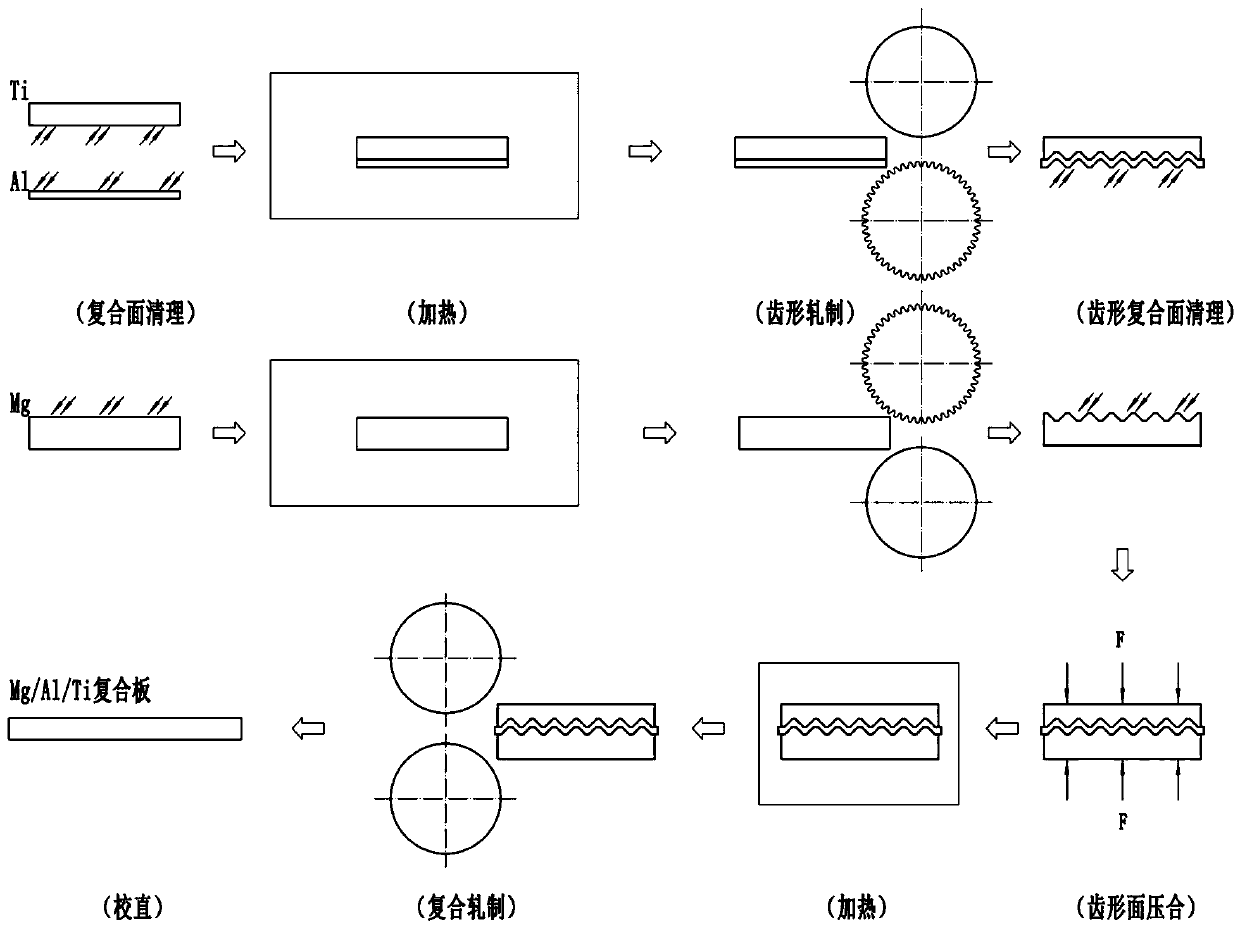

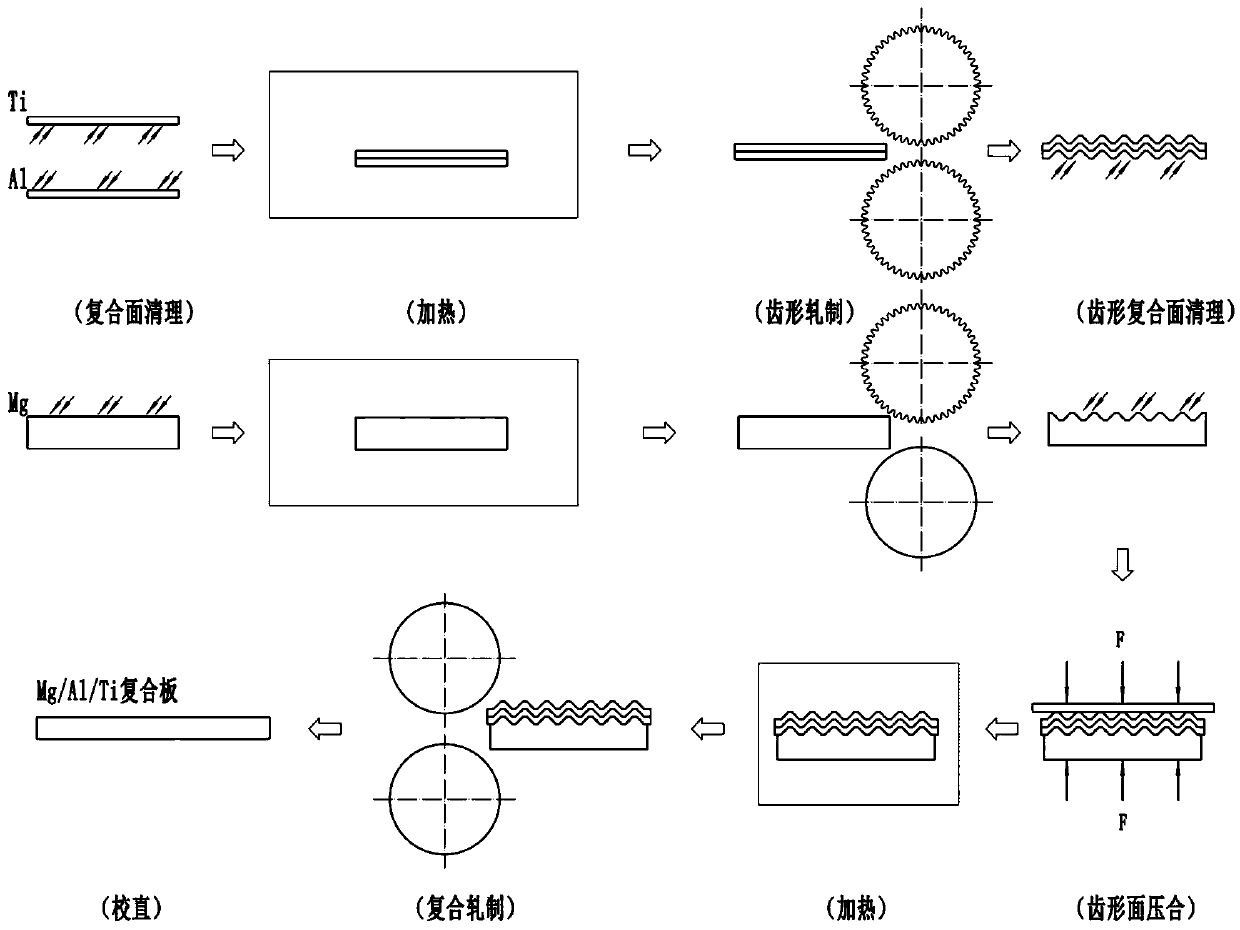

Rolling preparing method of tooth-shaped junction surface of titanium/aluminum/magnesium composite board

InactiveCN109731912APrevent oxidationImprove interface qualityMetal rolling arrangementsTitaniumStressed state

The invention discloses a rolling preparing method of a tooth-shaped junction surface of a titanium / aluminum / magnesium composite board. According to the method, an aluminum alloy sheet serves as a middle transition layer, finally, titanium alloy and aluminum alloy boards are rolled and composited under the high temperature, a composite face is a tooth-shaped face, a magnesium alloy board is rolledunder the high temperature, the face to be composited is the tooth-shaped face, and the tooth-shaped faces of the titanium / aluminum composite board and the magnesium alloy board are engaged and pressed, rolling compositing is carried out at the high temperature, and the titanium / aluminum / magnesium composite plate finished product is obtained. The titanium / aluminum tooth-shaped face composite rolling, magnesium alloy tooth-shaped face rolling and titanium / aluminum / magnesium composite rolling after tooth-shaped face engaging can be carried out under the different temperatures, and rolling composite is achieved; after tooth-shaped composite face engaging, rolling is carried out, synchronous engaging of multiple layers of alloy boards can be facilitated, the composite contact area can be effectively increased, composite face high-temperature oxidization is prevented, the stress state of the composite board interface can be changed, and the advantages that the composite board interface isgood in quality, and strength is high are achieved.

Owner:JILIN UNIV

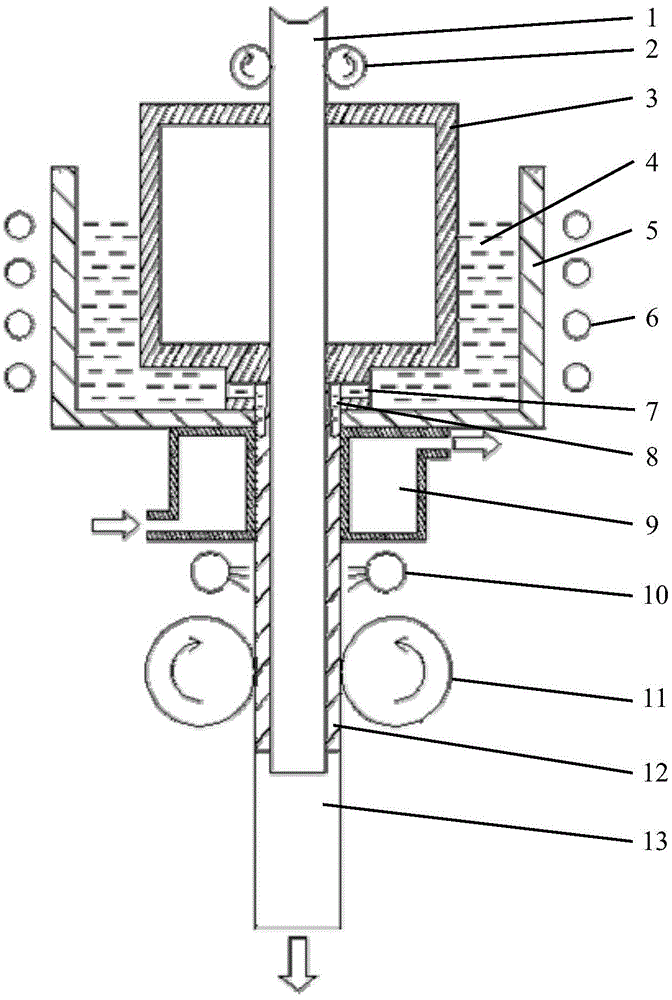

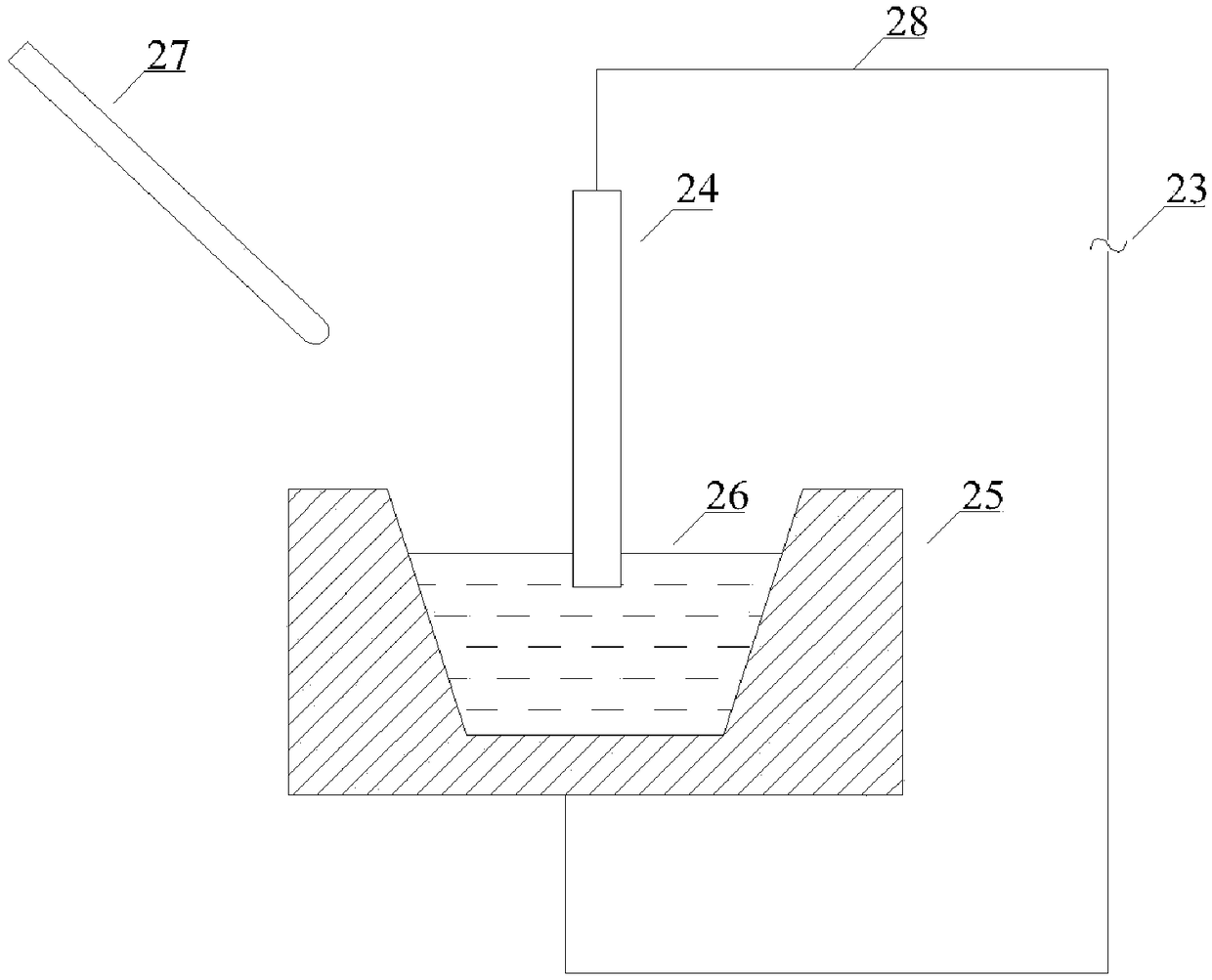

Clad material solid/liquid composite dual-solidification continuous casting and forming equipment and method

The invention belongs to the technical field of clad material continuous casting, in particular to clad material solid / liquid composite dual-solidification continuous casting and forming equipment and method. The clad material solid / liquid composite dual-solidification continuous casting and forming equipment and method are characterized in that inversion solidification and forward solidification continuous casting and forming are combined, the measures that core materials are not heated in advance, an inversion solidification device with small capacity is designed, the core materials are prevented from penetrating through clad layer melt metal for a long time, the melt metal flows out from the bottom of a crucible by relying on self-weight, and the size of the inversion solidification device and the size of a water-cooled crystallizer are controlled effectively are taken, the high quality clad materials of needed shapes and sizes are formed through continuous casting, and the equipment and the method are especially suitable for continuous casting forming of the high quality clad materials with the melting point of the clad layer metal lower than that of the core material metal. The equipment and method have the advantages that the equipment is simple in structure, parts are easy to replace, operation and maintenance are convenient to carry out, layout is reasonable and compact, investment is small, industrialized application and popularization are facilitated, the procedure of the forming process is short, energy is saved, environment is protected, cost is low, the combination freedom of the clad layer metal and the core material metal is large, and the prepared clad materials are good in quality and performance.

Owner:UNIV OF SCI & TECH BEIJING

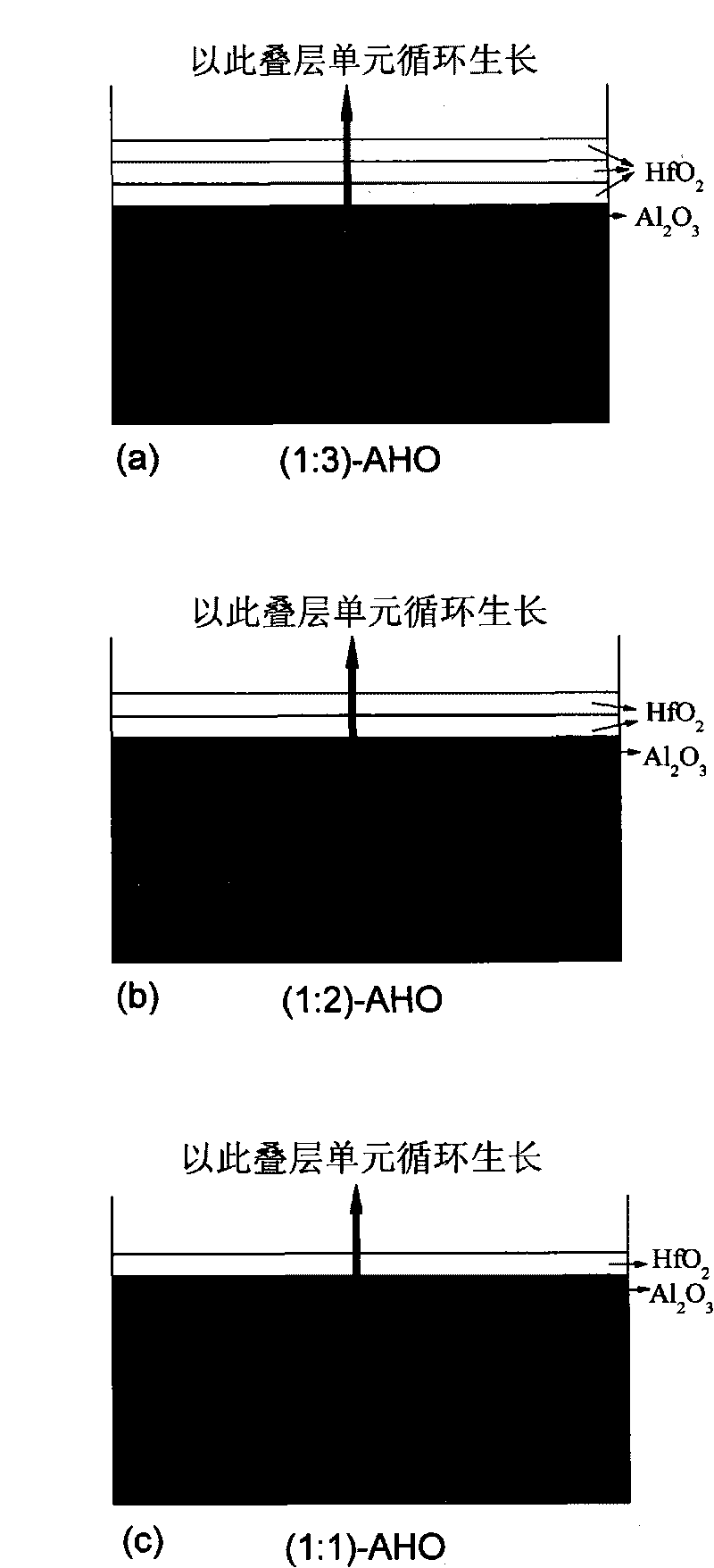

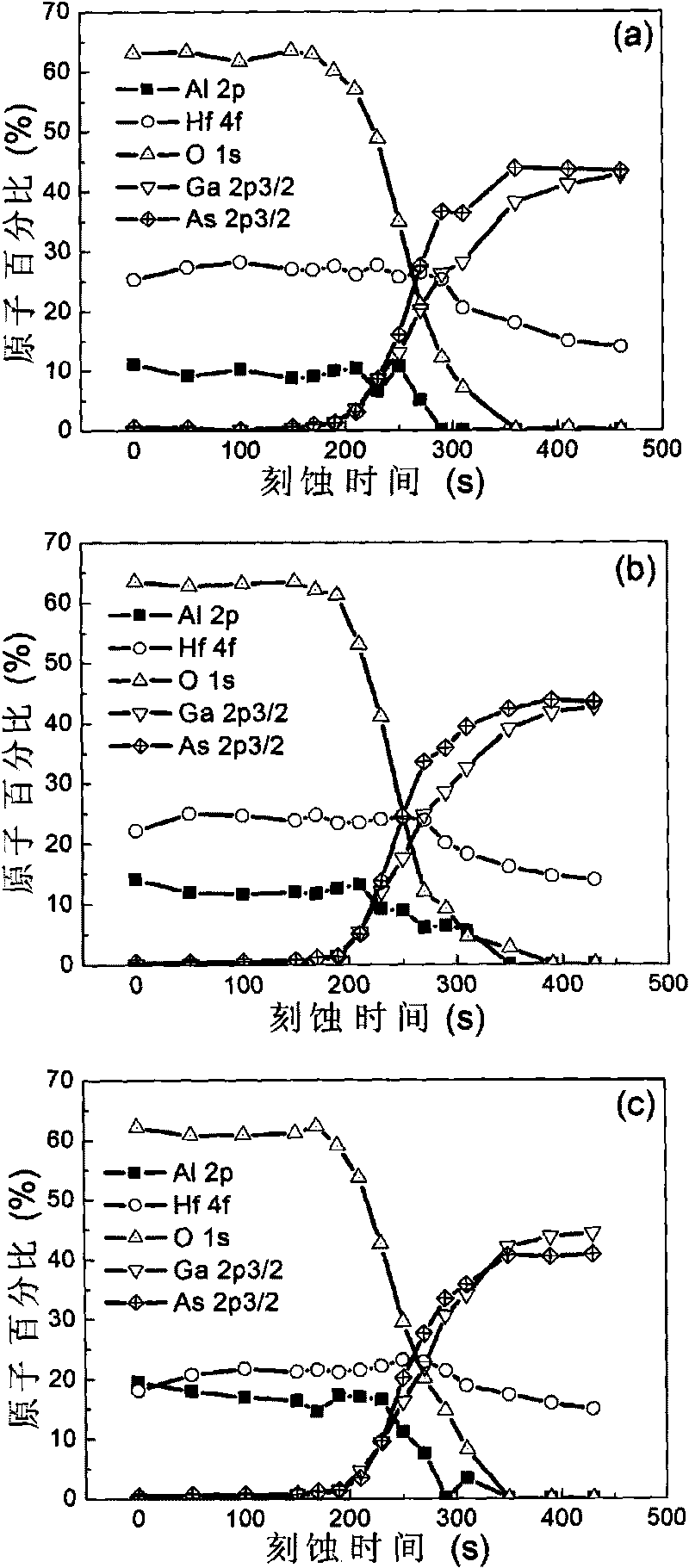

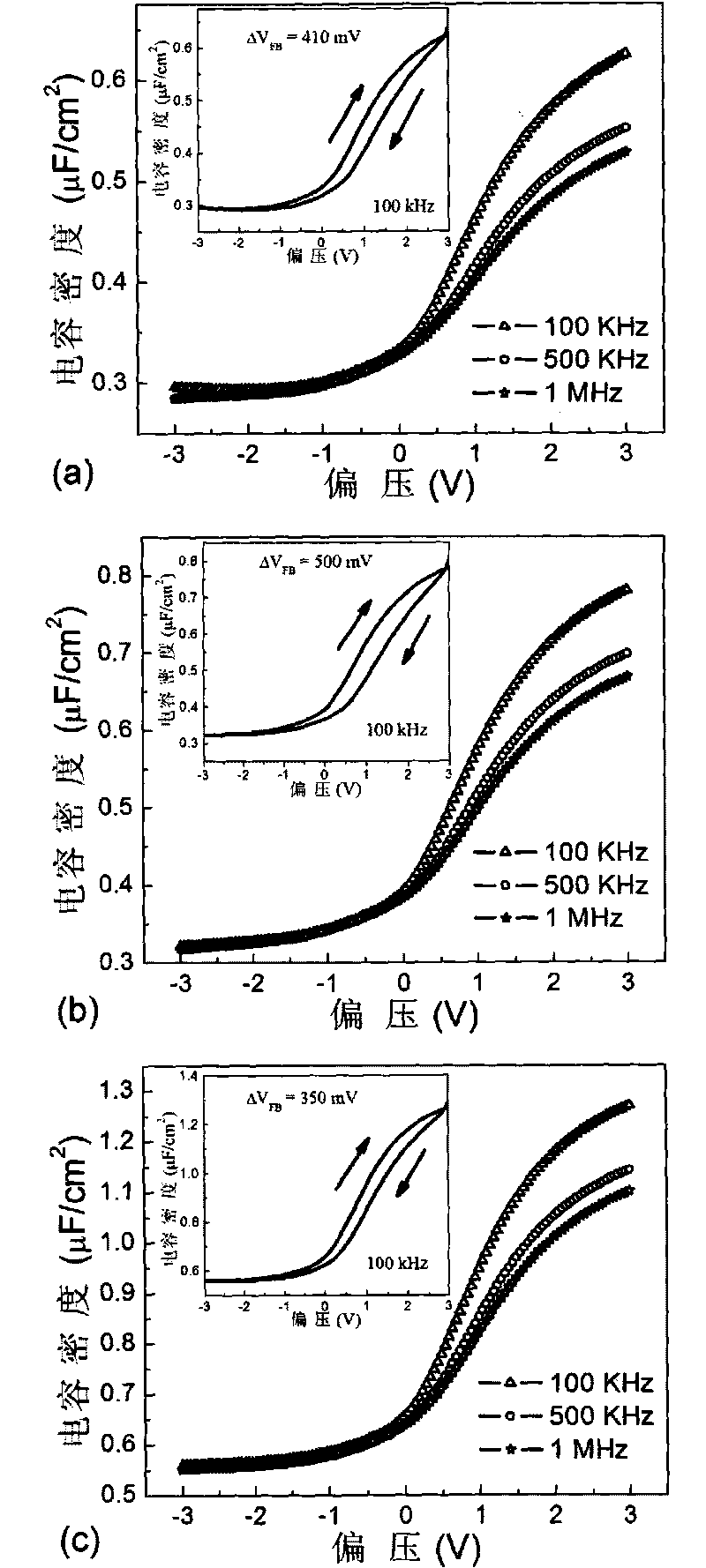

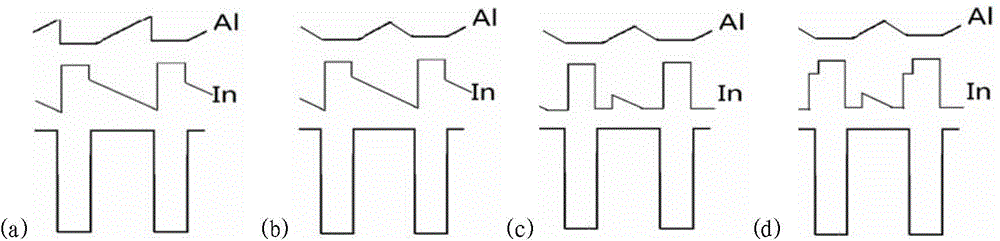

Atomic layer deposition Al2O3/HfO2 method for regulating energy band offset between GaAs semiconductor and gate dielectric

InactiveCN101752236AImprove electrical performanceOptimize and improve interface qualitySemiconductor/solid-state device manufacturingSemiconductor devicesDielectricMOSFET

The invention discloses an atomic layer deposition Al2O3 / HfO2 method for regulating an energy band offset between a GaAs semiconductor and a gate dielectric. The method comprises the following steps of: firstly, cleaning a GaAs substrate to remove oil stains and oxide layers; secondly, immersing the cleaned GaAs substrate in aqueous solution of (NH4)2S to form Ga-S and As-S bonds on the surface of the GaAs substrate and further remove an unnecessary As elementary substance and As oxides; and finally, placing the passivated GaAs substrate into an ALD reaction chamber immediately to perform deposition of a HfO2 / Al2O3 nano laminated film. The method optimizes and improves the interface property between the gate dielectric and the GaAs substrate, regulates the energy band offset between n-GaAs and a gate dielectric film, and improves the electrical properties of the gate dielectric film by changing the Al / Hf proportion, and has the advantages of simple process and important application prospect in preparation of GaAs-based MOSFETs.

Owner:NANJING UNIV

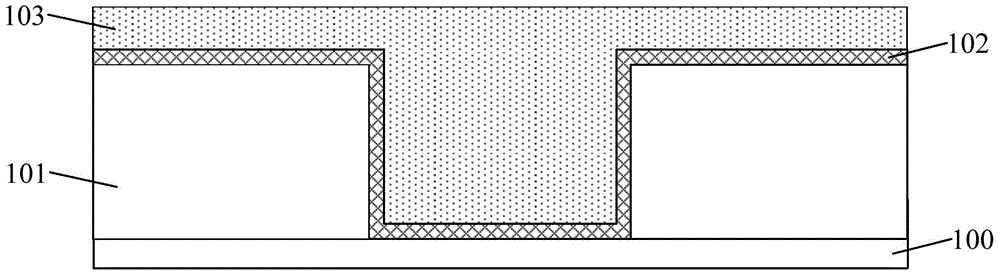

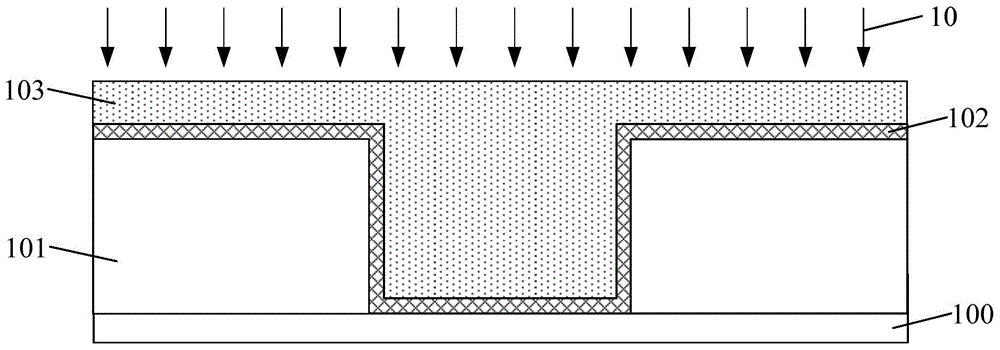

Resistance memory and method for fabricating integrated circuit with same

ActiveCN101572248ARealize interlayer interconnect structureSimple processSemiconductor/solid-state device detailsSolid-state devicesCore componentInterconnection

The invention relates to a method for fabricating an integrated circuit with a resistance memory, comprising the following steps: providing an interlaminar dielectric layer comprising a core component area and a peripheral circuit area; forming a first interconnection structure and a second interconnection structure in the interlaminar dielectric layer; respectively forming a first dielectric layer and a second dielectric layer on the surface of the first interconnection structure and on the surface of the second interconnection structure; forming first conductive layers covering the interlaminar dielectric layer, the first dielectric layer and the second dielectric layer; removing a first conductive layer and a second conductive layer on the peripheral circuit area to expose the second interconnection structure and only keeping the first conductive layer on the first dielectric layer in the core component area; and respectively forming a second conductive layer and a third conductive layer on the first conductive layer of the first dielectric layer and on the second interconnection structure. Due to the adoption of the method for fabricating the integrated circuit with the resistance memory, when the resistance memory is formed, the interlaminar interconnection structure of the core component area and the peripheral circuit area can be also formed.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Semiconductor structure and forming method thereof

ActiveCN105336620ALower Schottky BarrierAlleviate the Fermi level pinning effectSemiconductor/solid-state device manufacturingSemiconductor devicesMetallic materialsOxide

The invention discloses a semiconductor structure and a forming method thereof. The forming method of the semiconductor structure comprises the steps as follows: a semiconductor substrate is provided; a gate structure which covers partial surface of the semiconductor substrate is formed; a source and a drain are respectively formed in the semiconductor substrate at two sides of the gate structure; a dielectric layer is formed on the semiconductor substrate; the surface of the dielectric layer is higher than the top surface of the gate structure; a through hole is formed in the dielectric layer and exposes the surfaces of the source and the drain; an oxidation layer is formed on the surfaces of the source and the drain at the bottom of the through hole; a metal material layer is formed on the surface of the oxidation layer; an annealing treatment is carried out; the metal material layer reacts with the oxidation layer to form a metal oxide layer and a metal semiconductor compound layer; and the metal semiconductor compound layer is located on the surface of the metal oxide layer. The contact resistance between the source and the drain of the semiconductor structure formed by the method and the metal semiconductor compound layer is relatively small.

Owner:SMIC INT NEW TECH DEV SHANGHAI CO LTD

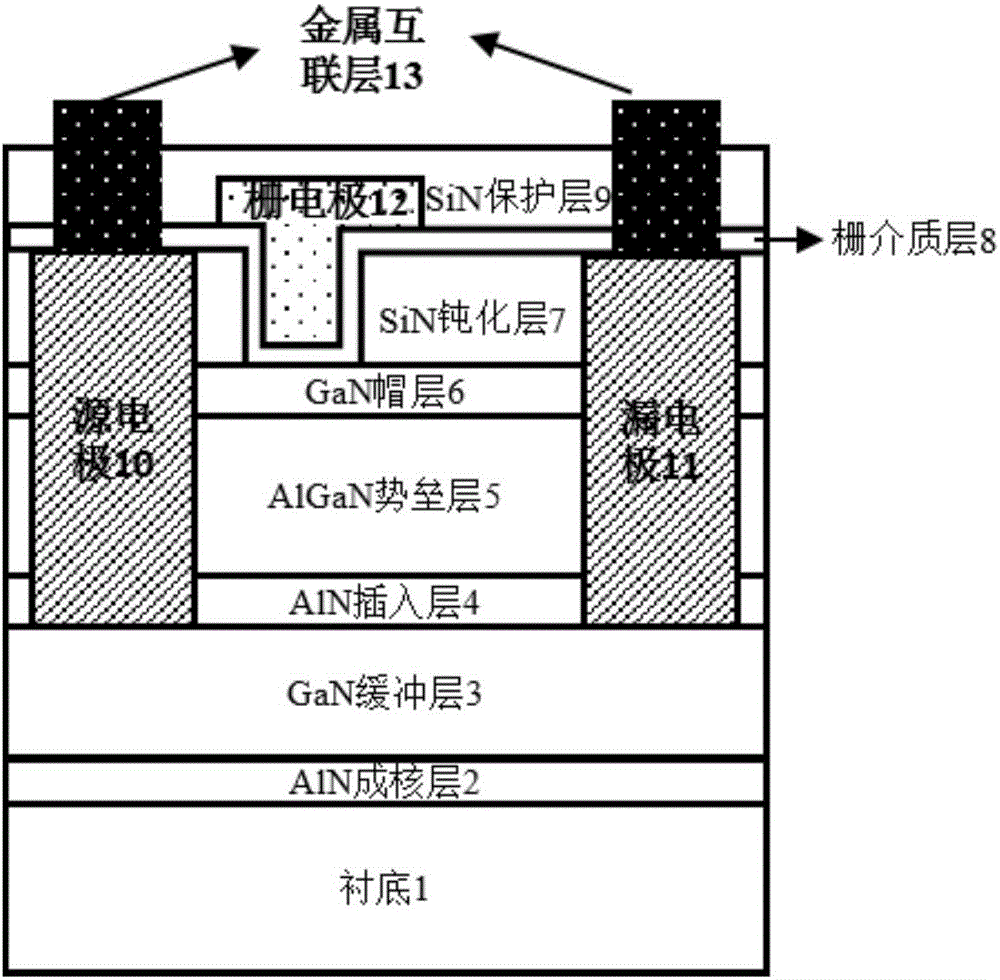

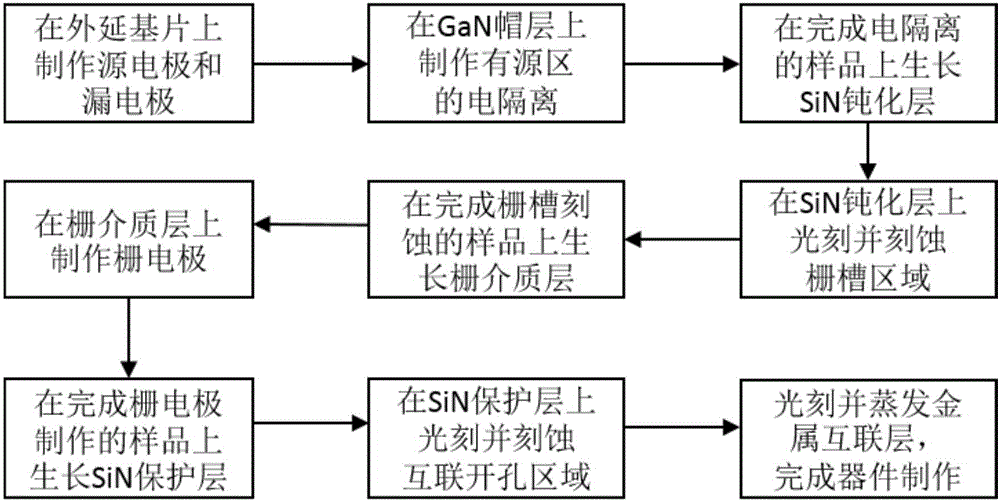

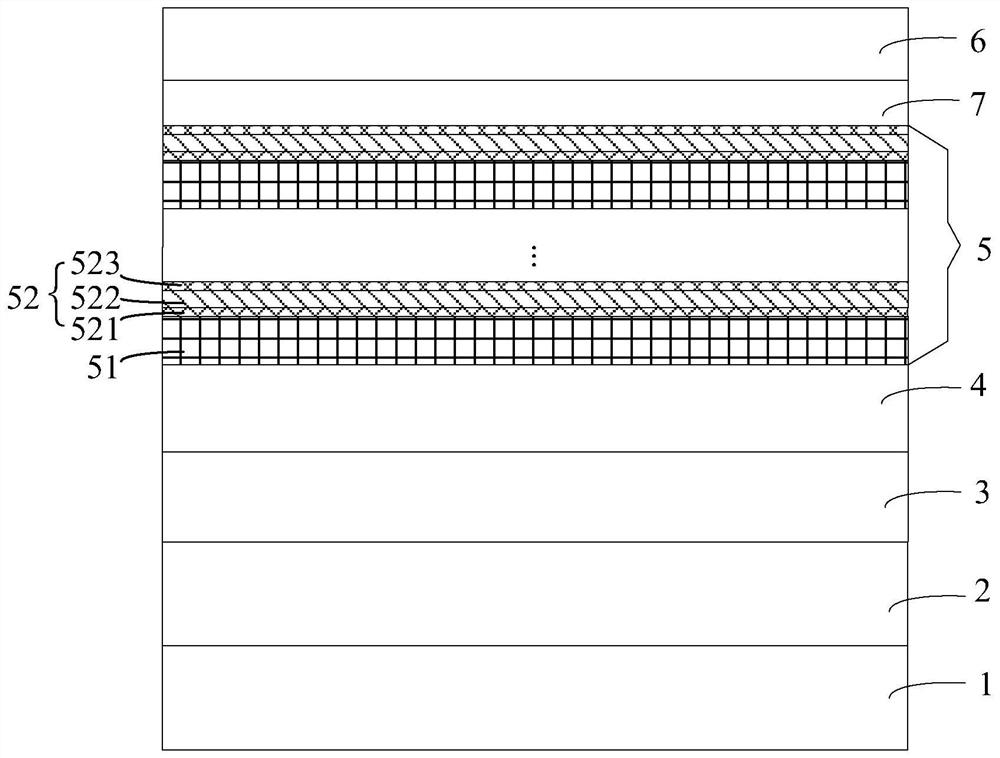

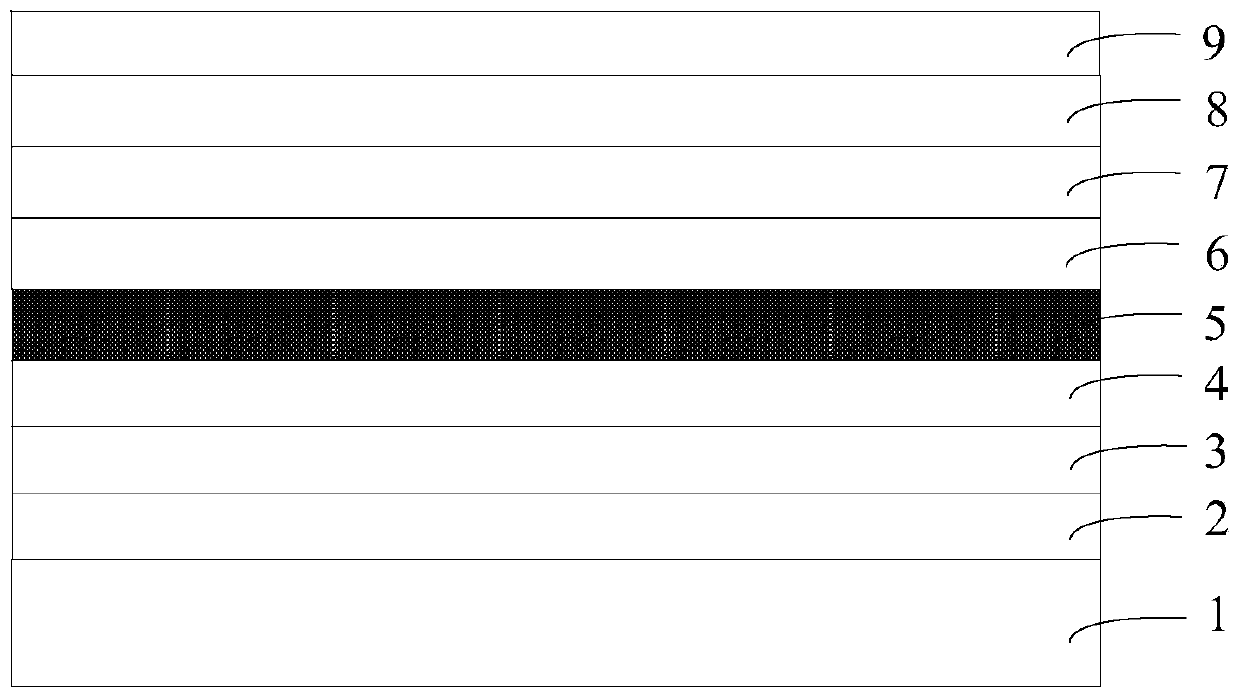

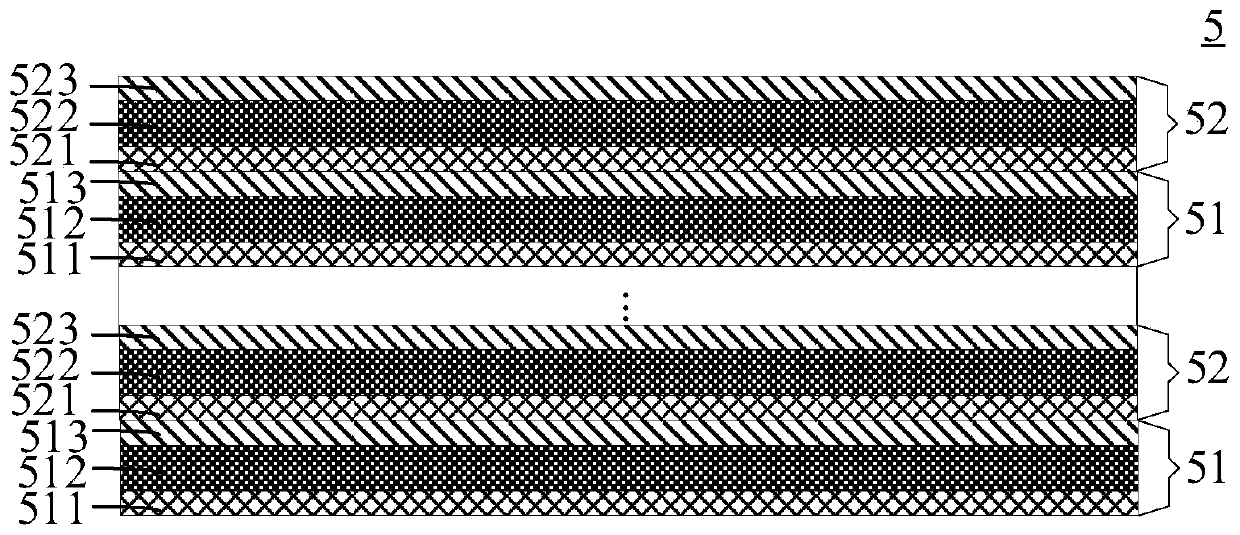

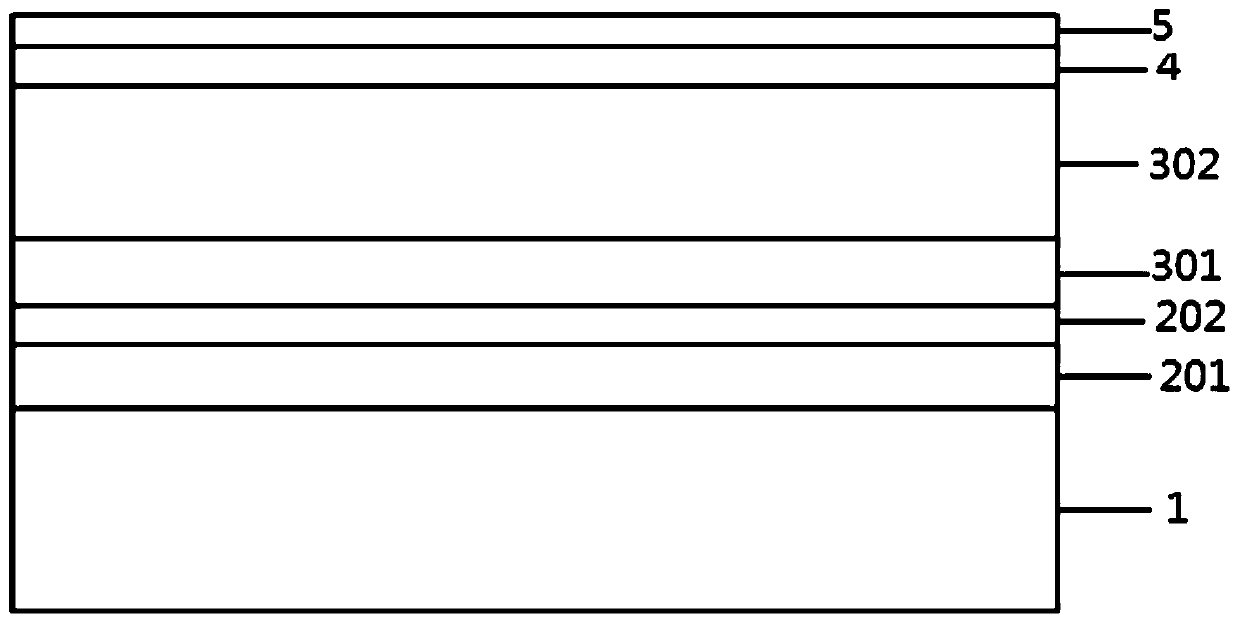

Stacked gate dielectric GaN-based insulated gate high-electron mobility transistor and manufacturing method

InactiveCN106229345AImproved interface quality and gating capabilitiesHigh activitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsHigh-electron-mobility transistor

The invention discloses a stacked gate dielectric GaN-based insulated gate high-electron mobility transistor, mainly to solve the problem that existing similar devices are low in reliability. The device comprises a substrate (1), an AlN nucleation layer (2), a GaN buffer layer (3), an AlN insertion layer (4), an AlGaN barrier layer (5), a GaN cap layer (6), a SiN passivation layer (7), a gate dielectric layer (8) and a SiN protection layer (9) from bottom to top, wherein two ends of the GaN buffer layer (3) are provided with a source electrode (10) and a drain electrode (11); the middle of the gate dielectric layer (8) is provided with a gate electrode (12); a metal interconnection layer (13) is arranged on the source electrode (10) and the drain electrode (11); and the gate dielectric layer (8) adopts a stacked structure formed by an AlN dielectric insertion layer (81) and a high k dielectric layer (82). The interface characteristics and the gate control capability of the device are improved, the reliability is improved, and the stacked gate dielectric GaN-based insulated gate high-electron mobility transistor can serve as a high-efficiency microwave power device.

Owner:XIDIAN UNIV

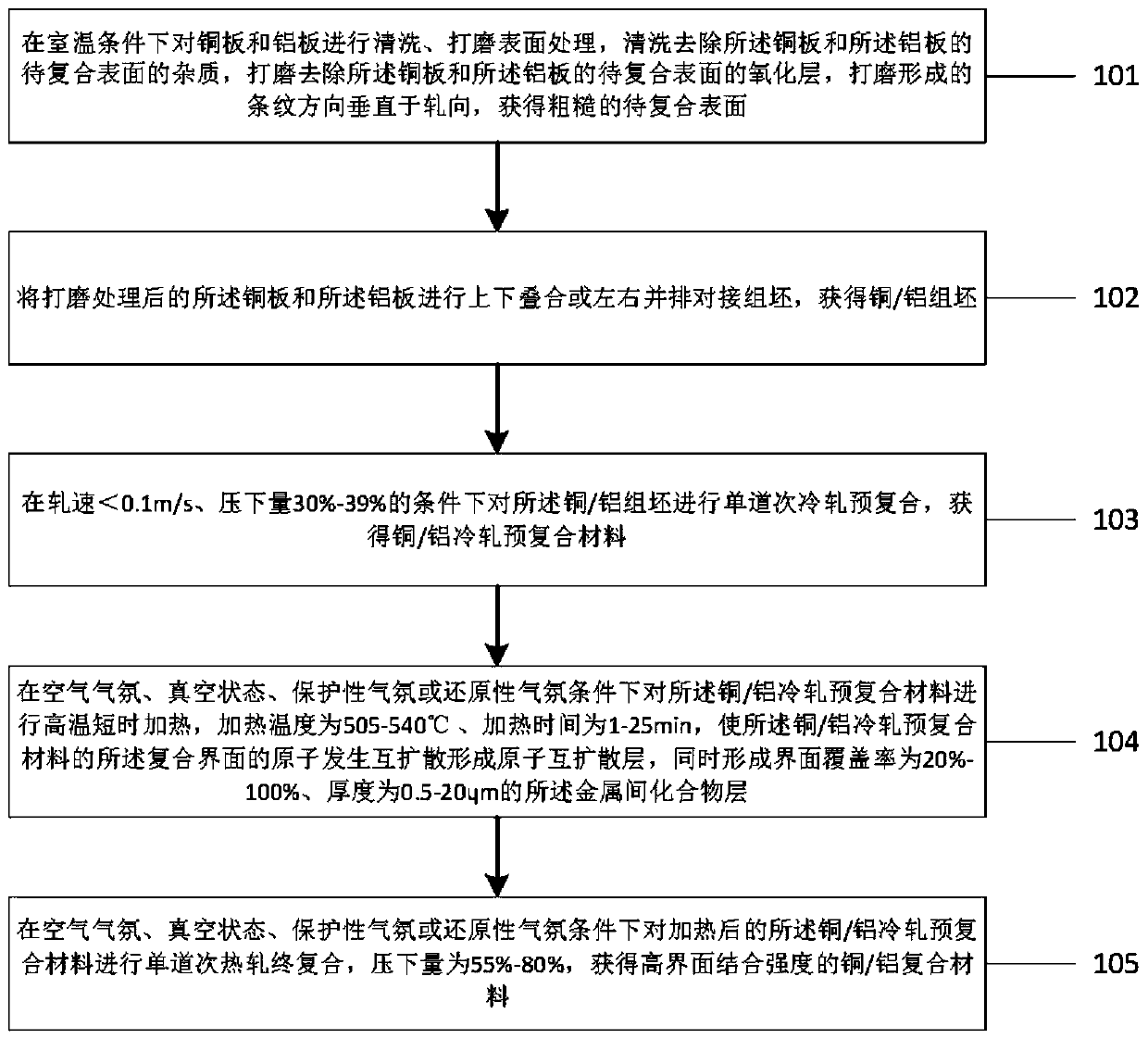

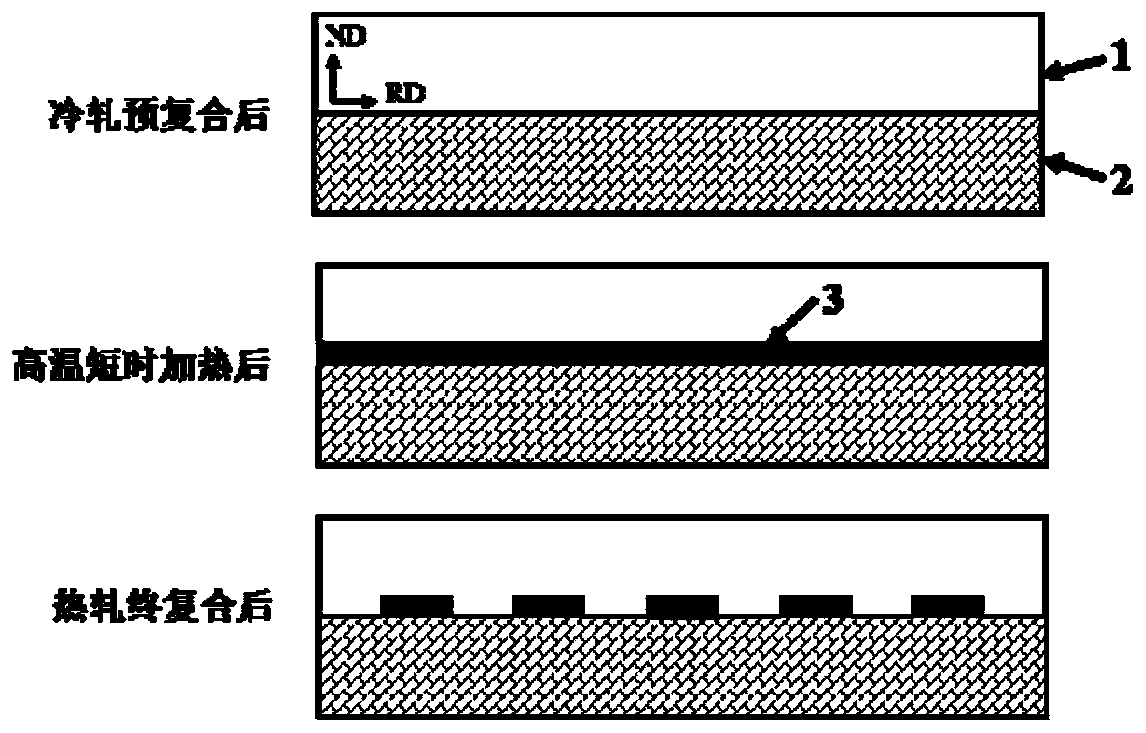

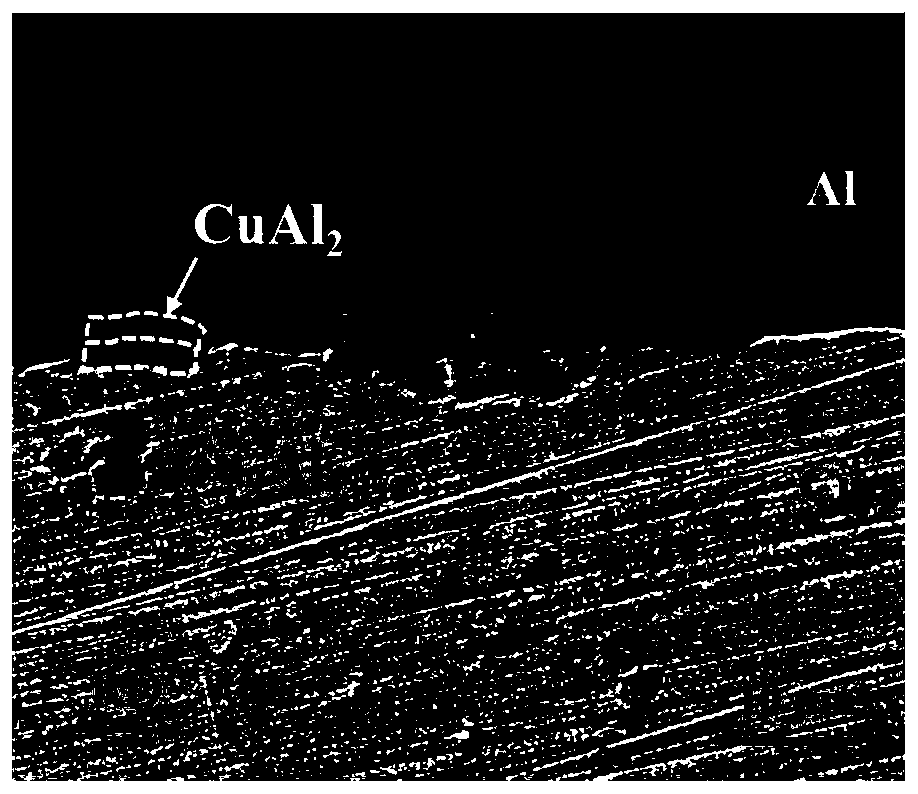

Forming method for high-interface-bonding-strength copper/aluminum composite material

ActiveCN110681694AImprove the bonding strength of the interfaceHigh interface frictionAuxillary arrangementsMetal rolling arrangementsAluminum compositesUltimate tensile strength

The invention discloses a forming method for a high-interface-bonding-strength copper / aluminum composite material, and belongs to the technical field of metal laminar composite material preparing. According to the forming method, to-be-combined surfaces of a copper plate and an aluminum plate are machined, macroscopic rugged to-be-combined surfaces are obtained, a louvre blade is adopted for conducting grinding treatment on the to-be-combined surfaces, the direction of stripes formed through grinding is perpendicular to the rolling direction, then, the copper plate and the aluminum plate are overlapped up and down or arranged left and right side by side to be in butt joint, and a copper / aluminum assembly is obtained; then, single-pass low-rolling-reduction cold rolling pre-composition is conducted, high-temperature short-time heating is conducted, finally, single-pass hot rolling final composition is conducted, and the high-interface-bonding-strength copper / aluminum composite materialis obtained. The forming method has the advantages that the capability requirement for a rolling machine needed for producing the copper / aluminum composite material is low, the technology is simple, the production cost is low, a macroscopic composite interface of a non-flat artificial structure and a microcosmic composite interface of a particle pinning structure can be obtained, the interface bonding strength is larger than or equal to 90 MPa, the applicable copper / aluminum composite material range is wide, and industrial popularization is easy.

Owner:UNIV OF SCI & TECH BEIJING

Epitaxial wafer for flip infrared light-emitting diode

InactiveCN106299058AImprove quantum efficiencyLattice Mismatch ReliefSemiconductor devicesQuantum efficiencyCharge carrier

The invention discloses an epitaxial wafer for a flip infrared light-emitting diode, and belongs to the technical field of epitaxy of light emitting diodes. Layers are epitaxially formed on the same side of a substrate in sequence; an active layer comprises InGaAs quantum well layers and GaAsP barrier layers which alternate periodically; the period number is 2 to 6; the active layer adopts an InGaAs / GaAsP strain compensation quantum well structure; the strain compensation quantum well can restrain carriers to flow in place transversely to form non-radiative recombination by mistake, so that the quantum efficiency is improved.

Owner:YANGZHOU CHANGELIGHT

Formation method of transistor

ActiveCN105336589APrevent peelingPrevent closureSemiconductor/solid-state device manufacturingSemiconductor devicesGas phaseWork function

The invention discloses a formation method of a transistor. The method comprises the following steps: providing a semiconductor substrate including a first area, wherein a dielectric layer is formed on the surface of the semiconductor substrate, and the dielectric layer is internally provided with a first groove exposing a part of the surface of the first area of the semiconductor substrate; forming a gate medium material layer on the surface of the inner wall of the first groove and the dielectric layer; forming a protective material layer on the gate medium material layer; forming an adherence material layer on the protective material layer by use of a physical vapor deposition technology; forming a first work function material layer by use of an atomic layer deposition technology, wherein the material of the adherence material layer is the same as the material of the first work function material layer; forming a grid metal layer on the first work function material layer, wherein the grid metal layer fills up the groove; and performing planarization processing on the grid metal layer, the first work function material layer, the adherence material layer, the protective material layer and the grid medium material layer by taking the surface of the dielectric layer as a stop layer so as to form a first grid structure disposed in the first groove. The method provided by the invention can improve the performance of the transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

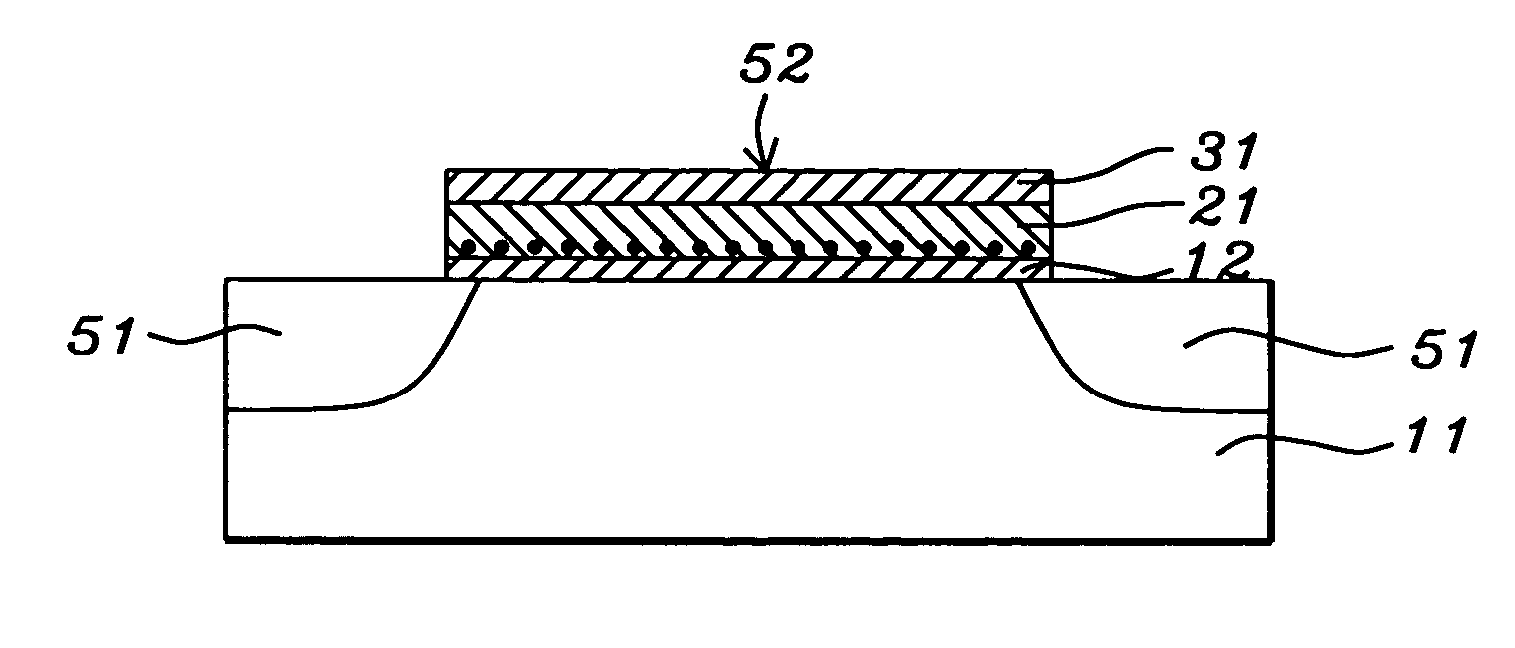

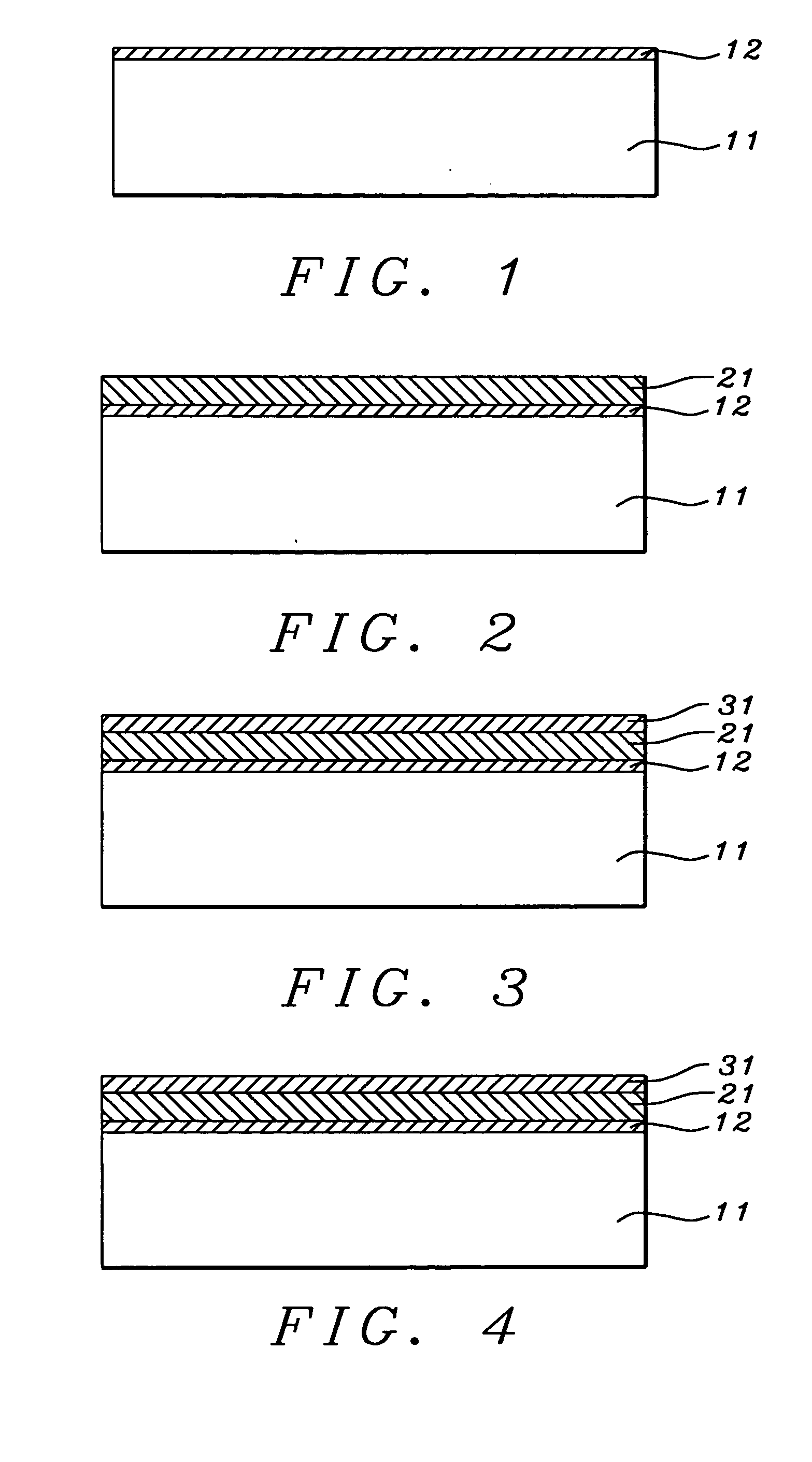

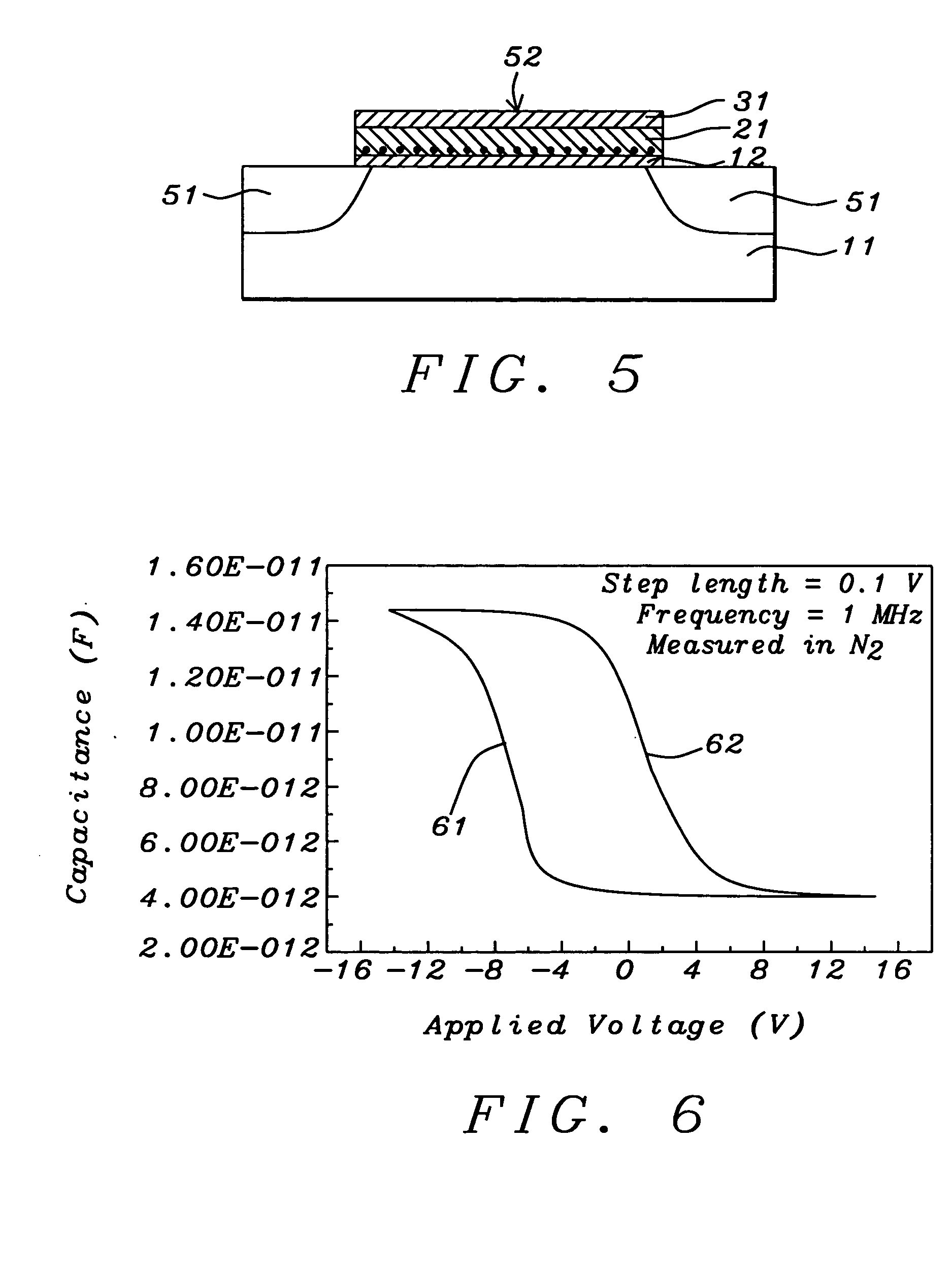

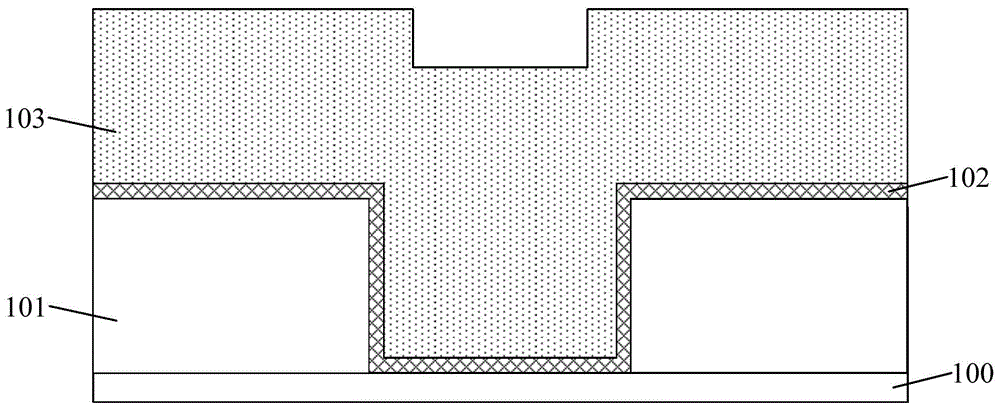

Process to manufacture nonvolatile MOS memory device

InactiveUS20050074939A1Improve interface qualityExcellent charge retentionTransistorNanoinformaticsGas phaseDoped oxide

Devices with embedded silicon or germanium nanocrystals, fabricated using ion implantation, exhibit superior data-retention characteristics relative to conventional floating-gate devices. However, the prior art use of ion implantation for their manufacture introduces several problems. These have been overcome by initial use of rapid thermal oxidation to grow a high quality layer of thin tunnel oxide. Chemical vapor deposition is then used to deposit a germanium doped oxide layer. A capping oxide is then deposited following which the structure is rapid thermally annealed to synthesize the germanium nanocrystals.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Chemical mechanical grinding method

InactiveCN105817991AAvoid scratchesAvoid thickeningSemiconductor/solid-state device manufacturingLapping machinesEngineeringGrinding process

The invention discloses a chemical mechanical grinding method which includes the following steps: a wafer to be ground is arranged on a first grinding pad; first grinding is conducted the wafer by first grinding liquid; the first grinding liquid has a first pH value, so the wafer to be ground can be separated from the first grinding pad; first cleaning liquid is sprayed on the surface of the wafer to be ground to conduct first cleaning; the first cleaning liquid has a second pH value; an absolute value of a difference between the first and second Ph values is no more than 1; after the first cleaning, the wafer to be ground is placed on a second grinding pad; second grinding is conducted to the wafer to be ground via second grinding liquid; the second grinding liquid has a third pH value; and an absolute value of a difference between the third pH value and the second pH value is no more than 1. Acid-base conflict can be prevented for the surface of the wafer to be ground, so plenty of microcosmic particles can be prevented from appearing on the surface of the wafer to be ground; and scraps to the surface of the wafer to be ground by the microcosmic particles during the second grinding can be avoided.

Owner:SEMICON MFG INT (SHANGHAI) CORP

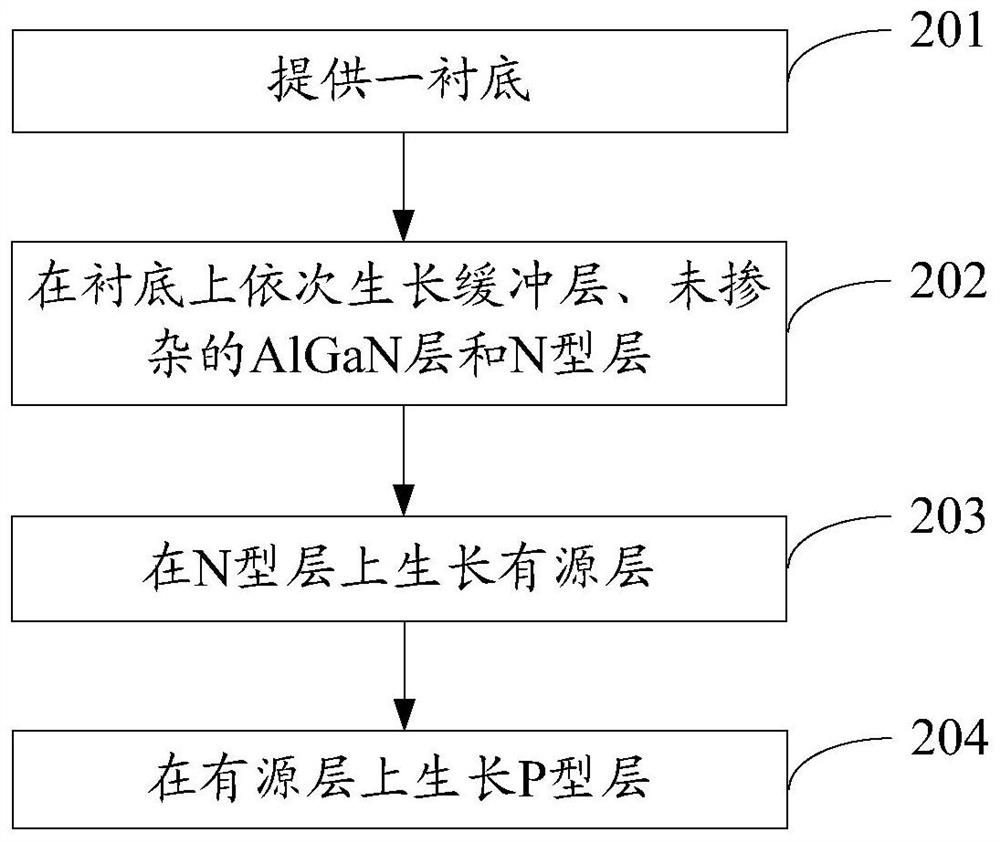

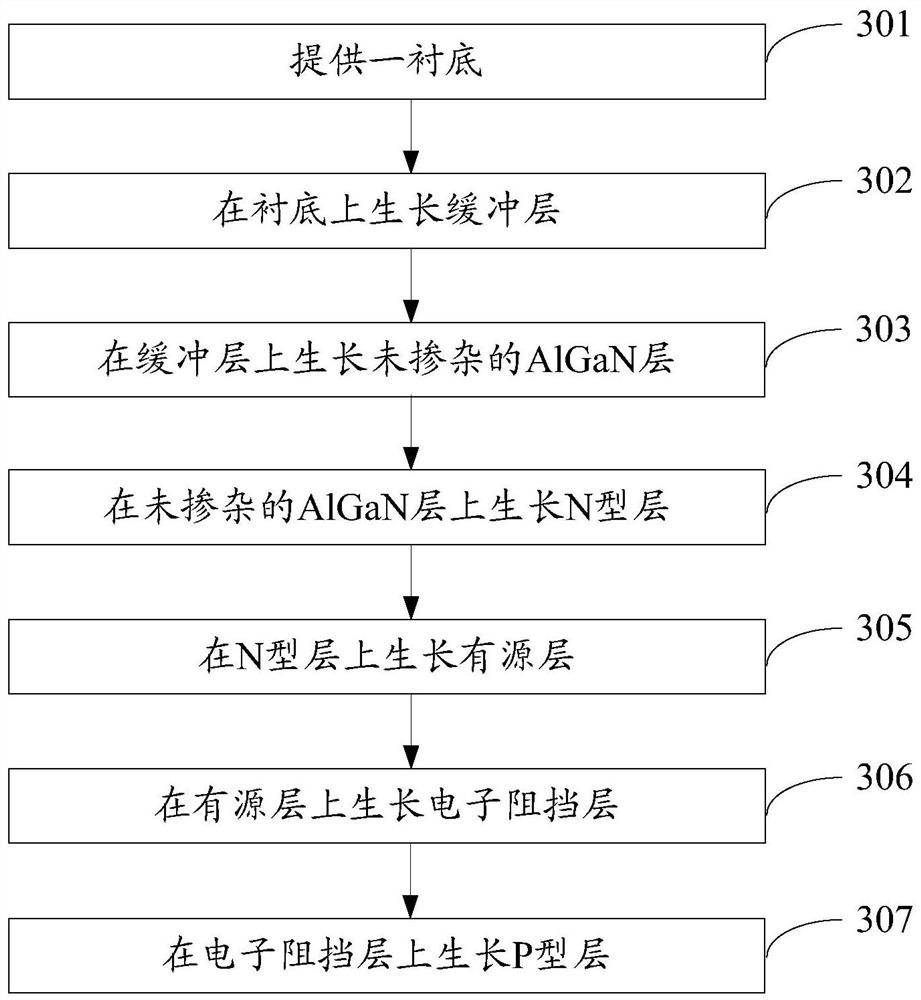

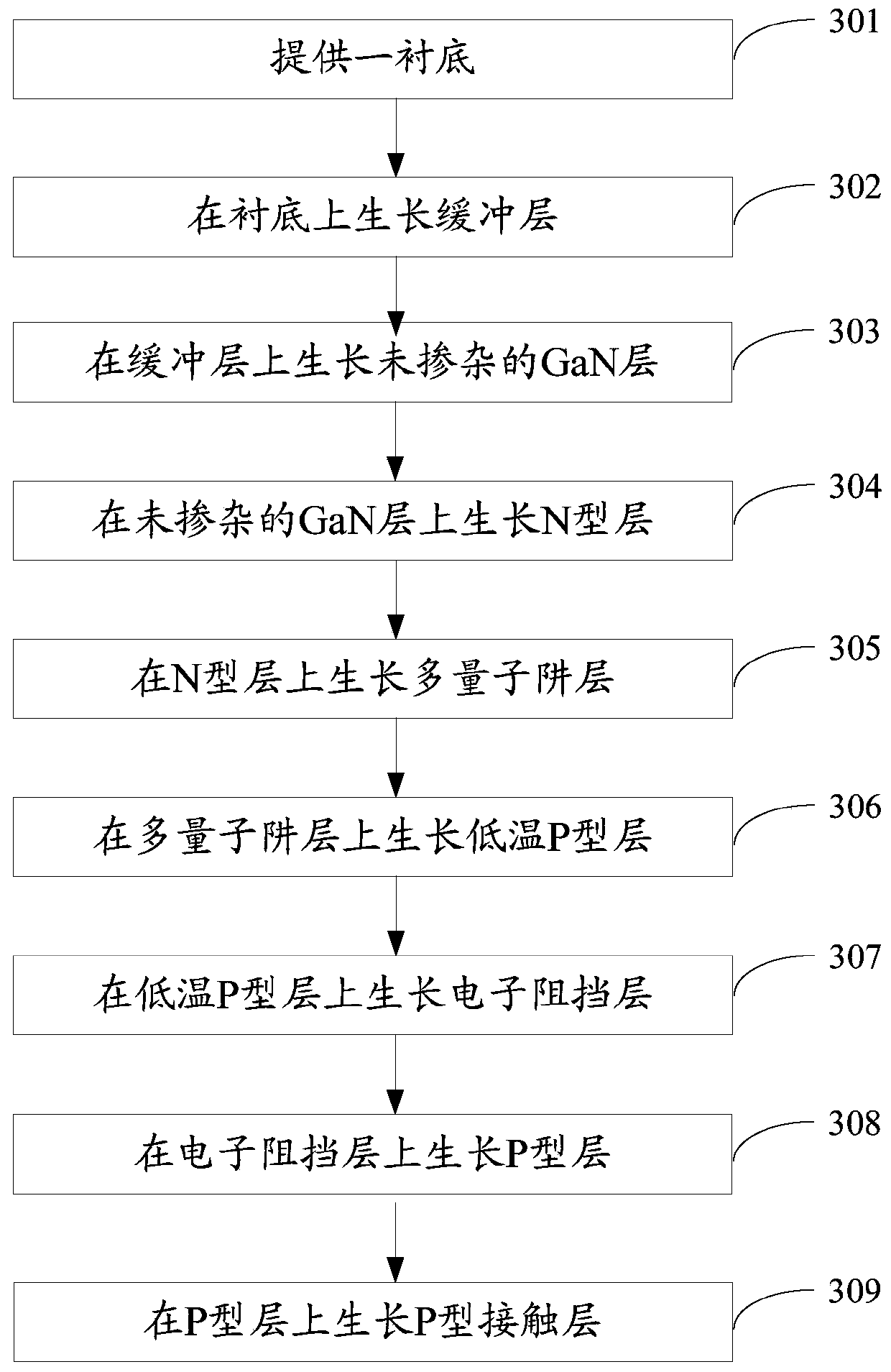

Ultraviolet light emitting diode epitaxial wafer and manufacturing method thereof

ActiveCN112366258AImprove energy band tilt phenomenonProne to overflowSemiconductor devicesUltraviolet lightsMaterials science

The invention provides an ultraviolet light emitting diode epitaxial wafer and a manufacturing method thereof, which belong to the technical field of semiconductors. The ultraviolet light emitting diode epitaxial wafer comprises a substrate, a buffer layer, an undoped AlGaN layer, an N-type layer, an active layer and a P-type layer, the buffer layer, the undoped AlGaN layer, the N-type layer, theactive layer and the P-type layer are sequentially stacked on the substrate, the active layer comprises a plurality of quantum well layers and quantum barrier layers which alternately grow periodically, the quantum well layers are Si-doped AlxGa1-xN layers, x is greater than 0 but smaller than 0.4, thequantum barrier layer is Mg-dopedAlyGa1-yN layer, and y is greater than 0.5 but smaller than 0.7.The ultraviolet light emitting diode epitaxial wafer can effectively shield a built-in electric field generated by a polarization effect in the quantum well layer, so that the wave function overlapping rate of electrons and holes can be improved, the radiation recombination efficiency of the electrons and the holes can be improved, and finally the internal quantum efficiency of the ultraviolet light-emitting diode is improved.

Owner:HC SEMITEK ZHEJIANG CO LTD

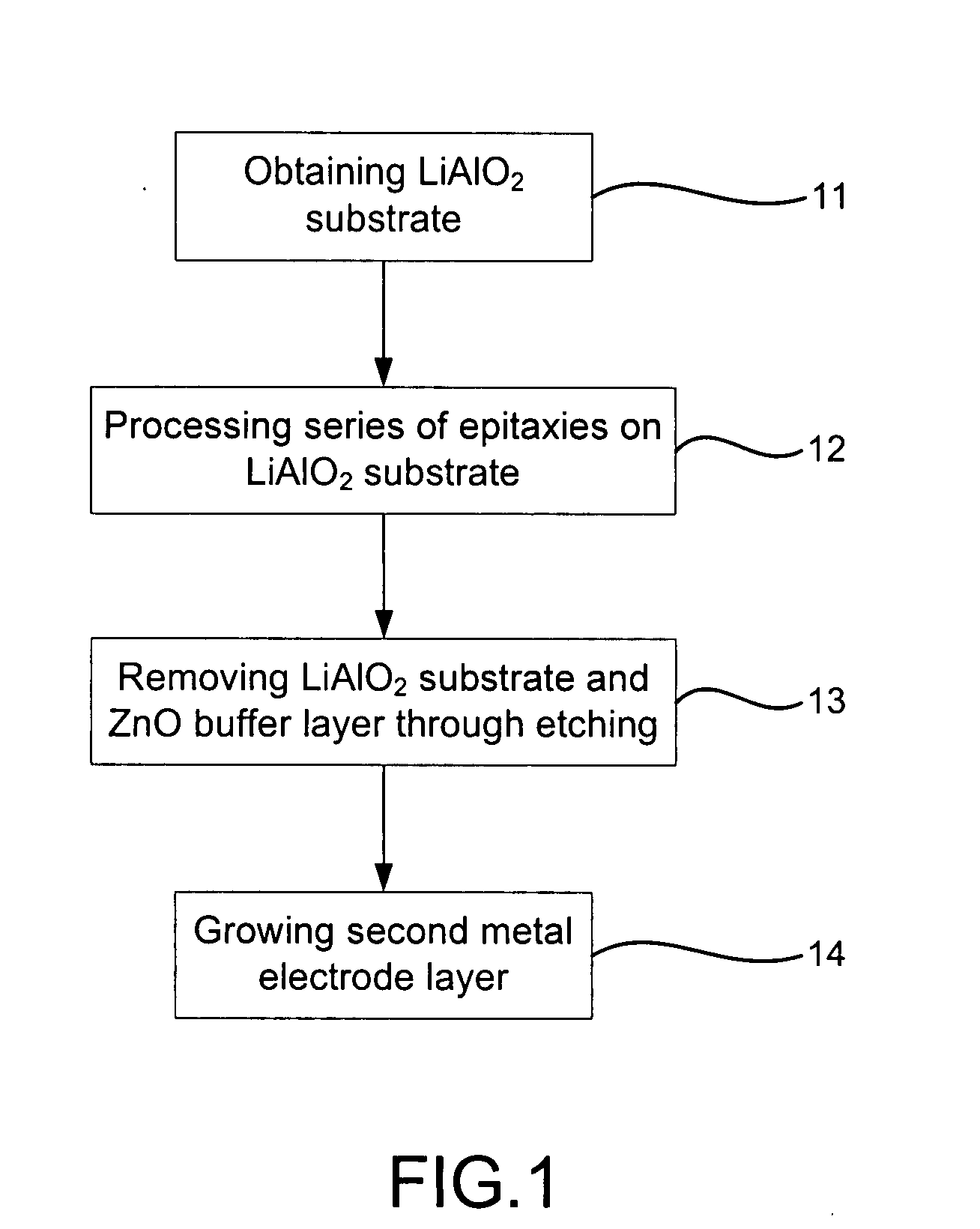

Method of fabricating GaN LED

InactiveUS20080233671A1Convenient lightingReduce defect densitySemiconductor/solid-state device manufacturingSemiconductor devicesSingle crystalZinc

A light emitting diode (LED) is made. The LED had a LiAlO2 substrate and a GaN layer. Between them, there is a zinc oxide (ZnO) layer. Because GaN and ZnO have a similar. Wurtzite structure, GaN can easily grow on ZnO. By using the ZnO layer, the GaN layer is successfully grown as a single crystal thin film on the LiAlO2 substrate. Thus, GaN defect density is reduced and lattice match is obtained to have a good crystal interface quality and an enhanced light emitting efficiency of a device thus made.

Owner:NAT SUN YAT SEN UNIV +1

Light emitting diode epitaxial wafer and manufacturing method thereof

ActiveCN110718612AGuaranteed luminous efficiencyReduce mismatchSemiconductor devicesQuantum efficiencyElectron hole

The invention discloses a light emitting diode epitaxial wafer and a manufacturing method thereof, and belongs to the semiconductor technology field. Each quantum well layer of a multi-quantum well layer of the light-emitting diode epitaxial wafer comprises a first quantum well sub-layer, a second quantum well sub-layer and a third quantum well sub-layer which are stacked in sequence. In / Ga ratioof the second quantum well sub-layer is greater than or equal to the In / Ga ratios of the first quantum well sub-layer and the third quantum well sub-layer. Si is doped in the first quantum well sub-layer. Each quantum barrier layer comprises a first quantum barrier sub-layer, a second quantum barrier sub-layer and a third quantum barrier sub-layer which are stacked in sequence. The Si / Ga ratio ofthe second quantum barrier sub-layer is greater than or equal to the Si / Ga ratios of the first quantum barrier sub-layer and the third quantum barrier sub-layer. The light emitting diode epitaxial wafer can improve an energy band inclination phenomenon in the multi-quantum well layer, an overlapping degree of wave functions of electrons and holes in space distribution is increased and internal quantum efficiency of an LED is improved.

Owner:HC SEMITEK ZHEJIANG CO LTD

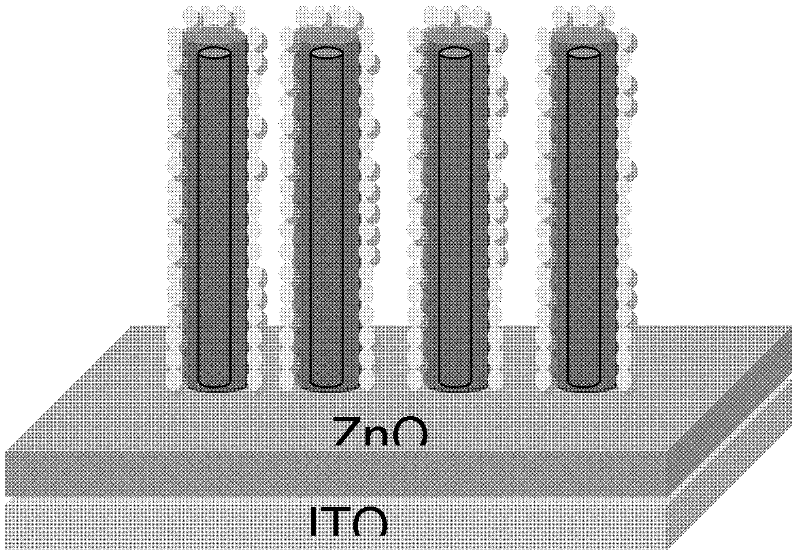

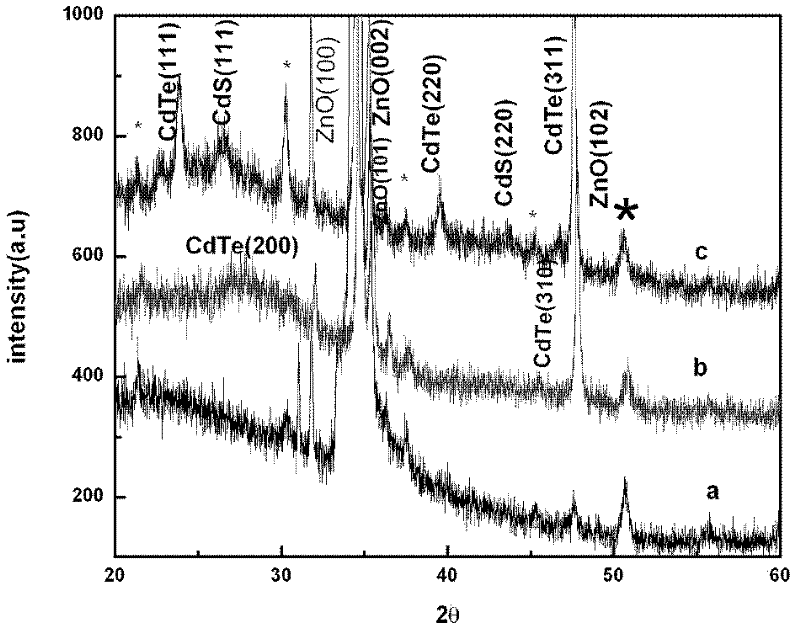

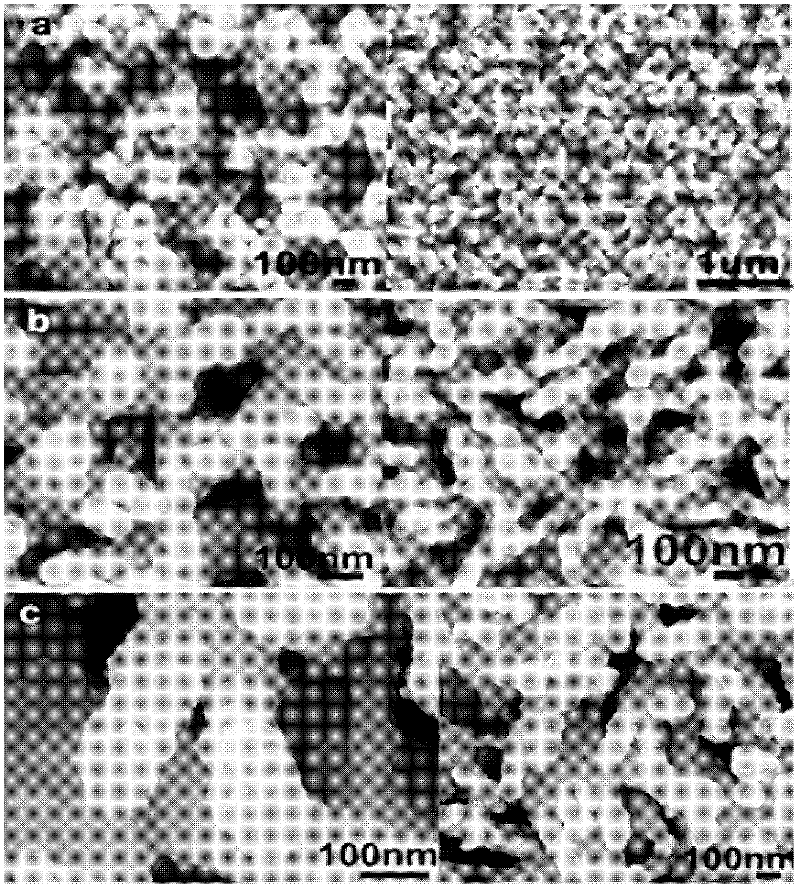

ZnO/CdTe/CdS nanometer cable array electrode and preparation method thereof

InactiveCN102412318AHigh crystallinityImprove interface qualityFinal product manufactureSemiconductor devicesThin layerEngineering

The invention relates to a ZnO / CdTe / CdS nanometer cable array electrode used for a solar battery and a preparation method thereof. The ZnO / CdTe / CdS nanometer cable array electrode is composed of an ITO conductive glass substrate, a ZnO buffering thin layer, a ZnO nanometer line array layer, a CdTe nanometer cable layer and a CdS nanometer crystal protective layer which are arranged from inside to outside; and the saturation photocurrent density of the ZnO / CdTe / CdS nanometer cable array electrode is improved to 12.4 mA / cm<2> through a CdS and CdTe sensitization technology. The ZnO / CdTe / CdS nanometer cable array electrode provided by the invention has the advantages of simple and practicable preparation process, low cost, high productive rate and good market application prospect.

Owner:HUBEI UNIV

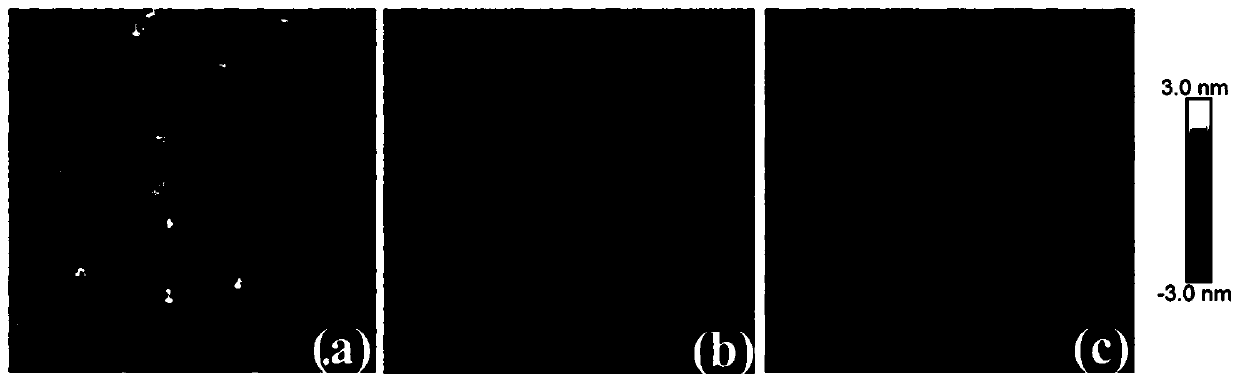

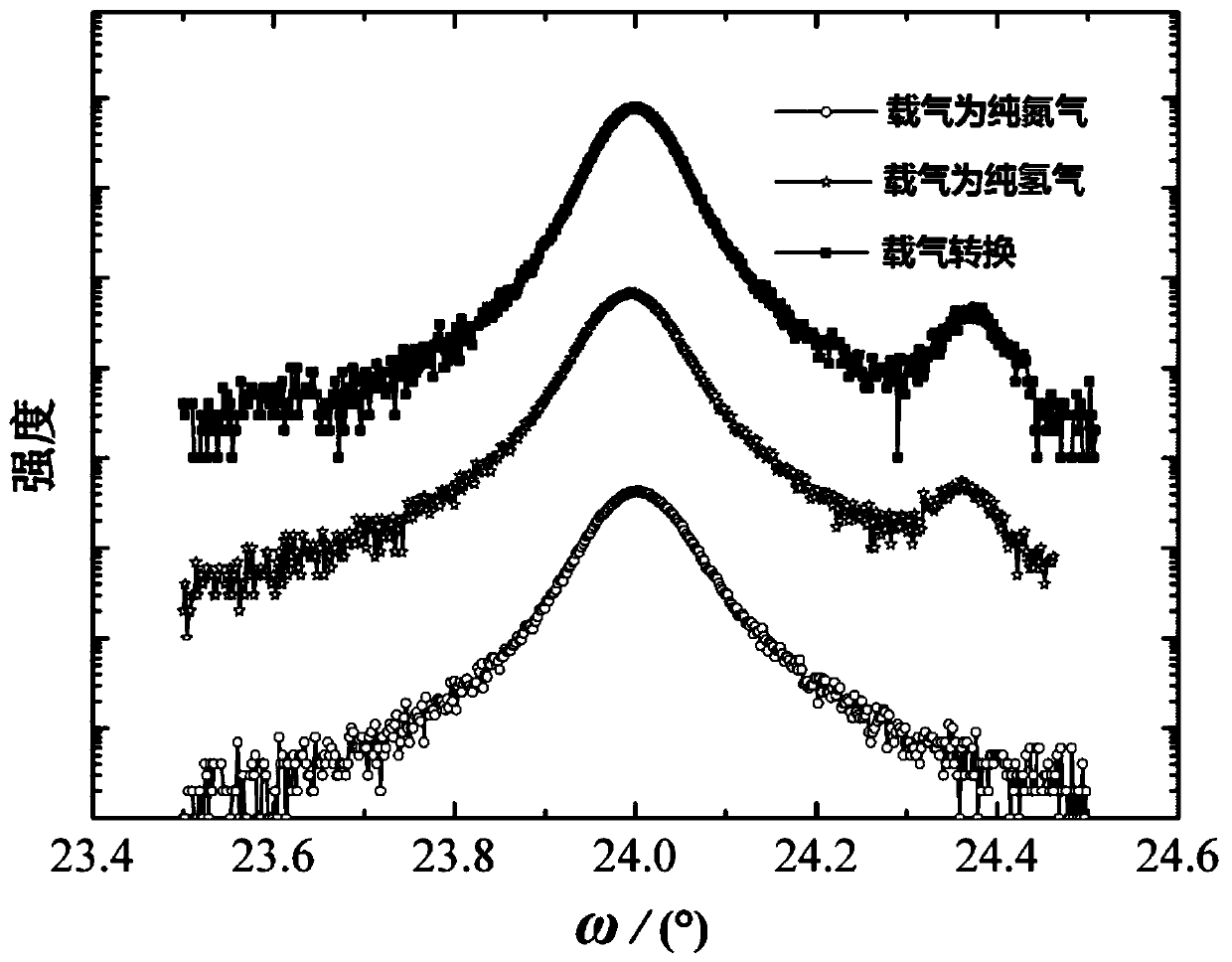

Epitaxial growth method for reducing interface thermal resistance of gallium nitride high-electron-mobility field-effect transistor

ActiveCN110211865AImprove defect densityGrowth interface protectionSemiconductor/solid-state device manufacturingSemiconductor devicesGas phaseNitrogen gas

The invention relates to an epitaxial growth method for reducing interface thermal resistance of a gallium nitride high-electron-mobility field-effect transistor. An epitaxial material is grown through a vapor phase epitaxial growth method of metal organic matter chemical vapor deposition and the like. A gallium nitride epitaxial wafer comprises a substrate, a lower aluminium nitride nucleating layer, an upper aluminium nitride nucleating layer, a gallium nitride transition layer, a gallium nitride buffer layer, a barrier layer and a cap layer from the bottom up in sequence. The carrier gasesused in the growing process of the lower aluminium nitride nucleating layer and the upper aluminium nitride nucleating layer are hydrogen and nitrogen respectively. The carrier gas used in the growingprocess of the gallium nitride transition layer is nitrogen. The carrier gas used in the growing process of the gallium nitride buffer layer is hydrogen or a mixture of hydrogen and nitrogen. Throughthe carrier gas conversion process, the method reduces defect density in the aluminum nitride nucleating layer and the gallium nitride layer, improves interface quality of the aluminum nitride nucleating layer and the gallium nitride layer, and effectively reduces the interface thermal resistance of the gallium nitride high-electron-mobility field-effect transistor.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

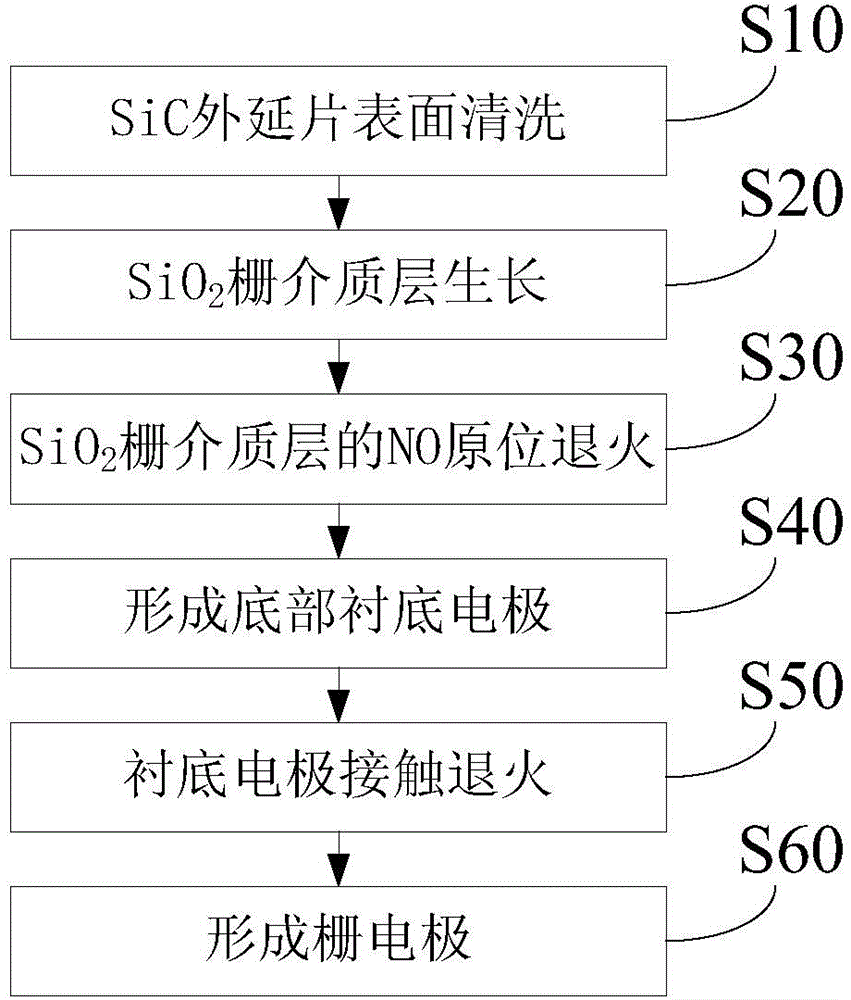

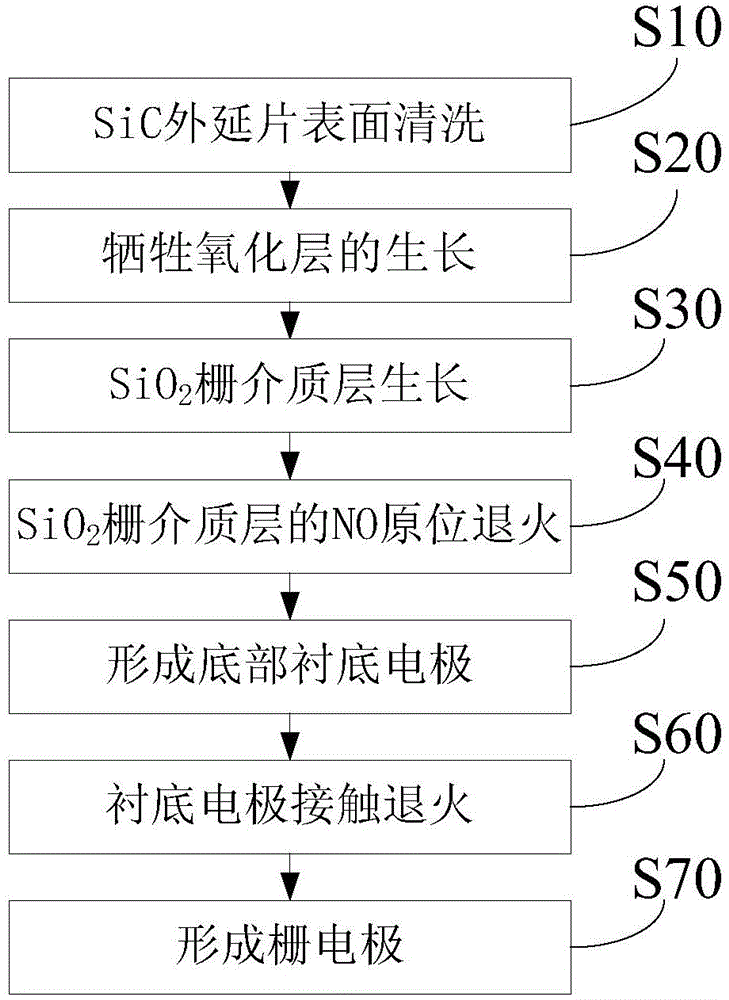

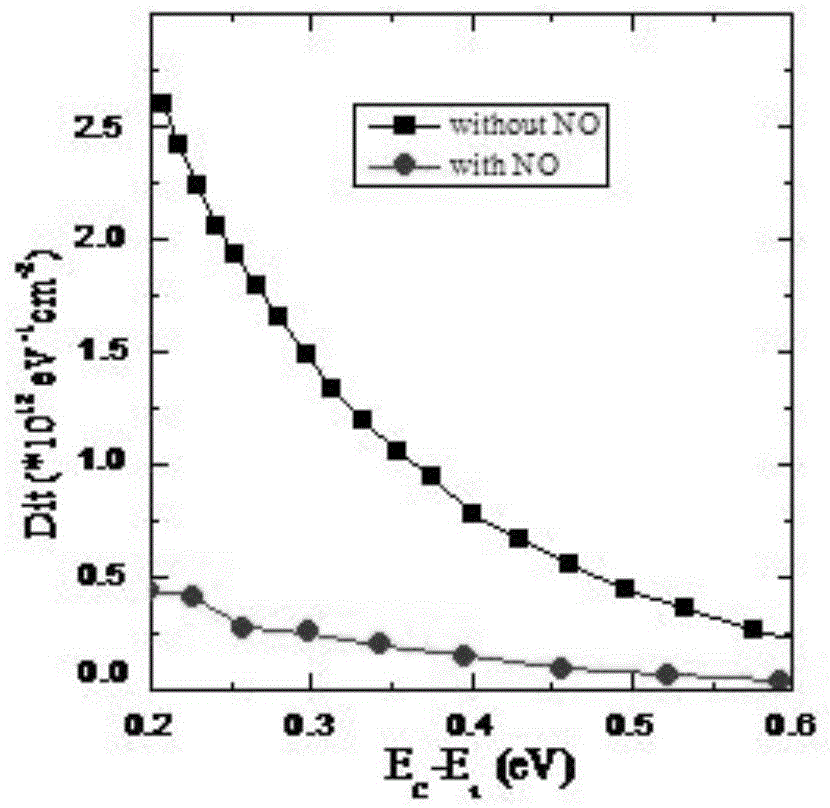

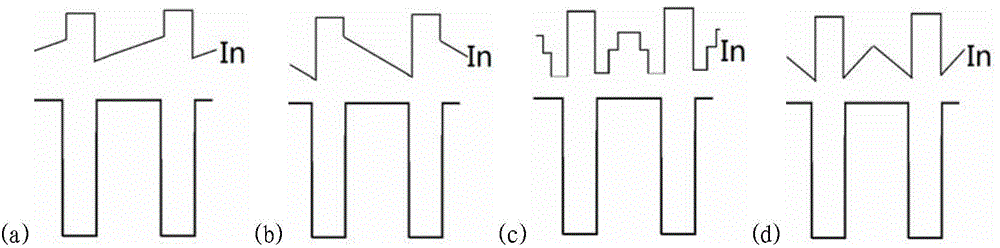

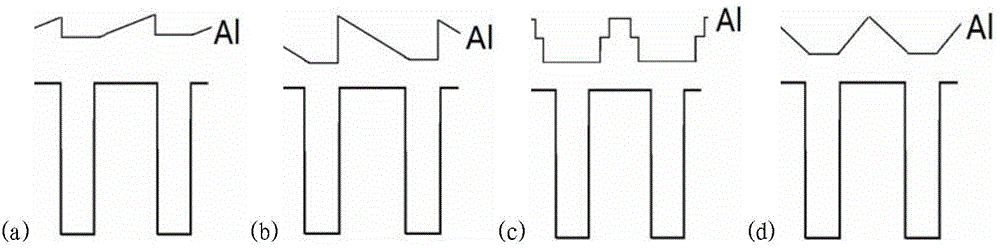

Method for improving SiC and SiO2 interface state density

ActiveCN104966665AReduce interface state densityImprove interface qualitySemiconductor/solid-state device manufacturingGate dielectricState density

The invention provides a method for improving SiC and SiO2 interface state density and relates to the technical field of microelectronics. The method comprises: cleaning the surface of a SiC epitaxial wafer; growing a SiO2 gate dielectric layer; in-situ annealing the SiO2 gate dielectric layer by using NO gas; forming a bottom substrate electrode; contacting annealing the substrate electrode; and forming a gate electrode. The method anneals the SiO2 gate dielectric layer by using NO gas so as to reduce SiC / SiO2 interface state density and improve an interface, gate dielectric quality and device characteristics.

Owner:XIDIAN UNIV

Quantum well structure of photoelectric device

InactiveCN104638073AImprove hole injection efficiencyLess bendingSemiconductor devicesQuantum efficiencyBand bending

The invention provides a new quantum well structure, which can further effectively increase the recombination probability of carrier, improve quantum efficiency and realize optimization and improvement of efficiency of a photoelectric device. AlInGaN is used as a barrier, an In and Al component gradual barrier layer structure is designed to substitute barrier layer structure design of the conventional quantum well structure. The In component is doped into the barrier layer structure of the quantum well, the band bending of the quantum well is reduced, a quantum confined stark effect is weakened, the electron blocking efficiency of an electron barrier layer is improved, a hole injection efficiency of the quantum well is increased, spatial wave function overlap of electrons and space is increased, and these have a positive effect on improvement of luminous efficiency of an LED (Light Emitting Diode); meanwhile the Al component is doped into the barrier layer structure of the quantum well, so migration of the electrons to a P layer is effectively blocked; through the gradual component design of the AlInGaN, the influence of a polarization electric field can be reduced, and the spontaneous emission spectrum strength of the quantum well is improved.

Owner:西安利科光电科技有限公司

Method for making silicon containing dielectric films

InactiveUS6967176B1Fast oxidationSimple methodElectric discharge tubesSemiconductor/solid-state device manufacturingDielectricMicrowave cavity

Method and apparatus for forming thin silicon oxide films on silicon carbide substrates utilizing an afterglow thermal reactor. The method of forming thin silicon oxide film includes the steps of loading a silicon carbide substrate within a tube, which tube is heated, and the contents pressure is controlled. An oxidizing gas is then passed through an afterglow reactor source or microwave cavity where the gas achieves an excited state of energy. When the neutral species of the excited gas contact the silicon carbide substrate within the heated region of the the tube, a thin silicon oxide film forms on the substrate, at a faster rate and lower temperature than has been known. The tube contents are maintained at a temperature between 600° C. to 1,200° C., and at a pressure less than 50 torr.

Owner:UNIV OF SOUTH FLORIDA

Back-surface tunnel oxidation and passivation inter-digitated type back-to-back contact battery production method

InactiveCN106784069AChange interface qualityReduce surface recombinationFinal product manufactureSemiconductor devicesSlurrySilicon dioxide

The invention relates to a back-surface tunnel oxidation and passivation inter-digitated type back-to-back contact battery production method, comprising: removing the damage layer of a silicon wafer and making velvets; and then forming an N + front surface field on the front surface of the silicon wafer; removing the phosphor silicate glass (PSG) layer and performing edge insulation and back polishing; growing an ultra-thin tunnel oxide layer SiO2 on the back of the silicon wafer; forming an inter-digitated type polysilicon layer composed of a polysilicon layer of B-doped and P-doped pairs; depositing an aluminum oxide layer and a hydrogenated amorphous silicon nitride passivation antireflective layer on the surface of the N + front surface field; and growing a silicon layer on the back side of the wafer; printing Ag / Al slurry on the back side of the battery corresponding to the B-doped region through the use of the screen printing method; printing the Ag slurry in the P-doped region; and then, drying the slurries in an oven. The invention utilizes an ultra-thin tunnel oxidation SiO2 layer and an interdigitated phosphorous-doped and boron-doped silicon layer, which greatly alters the interface quality of the silicon substrate and greatly reduces the composition of the back surface metal and the semiconductor surface.

Owner:SHANGHAI SHENZHOU NEW ENERGY DEV

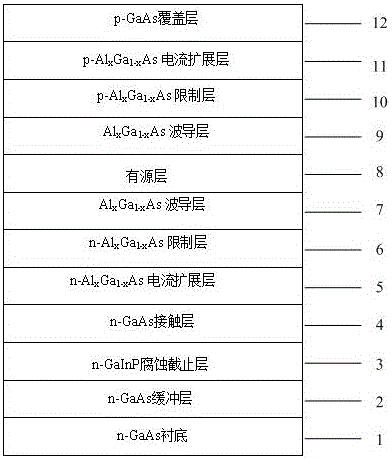

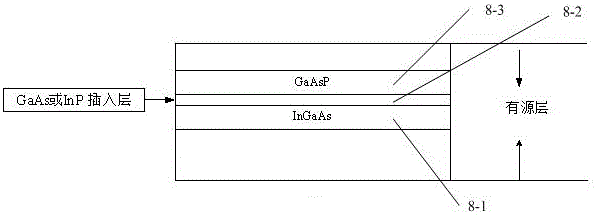

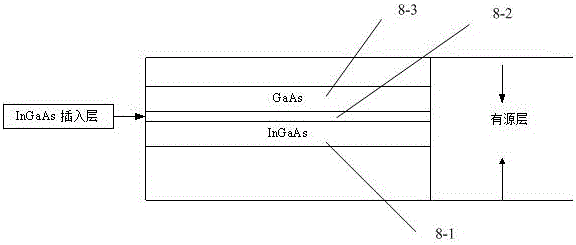

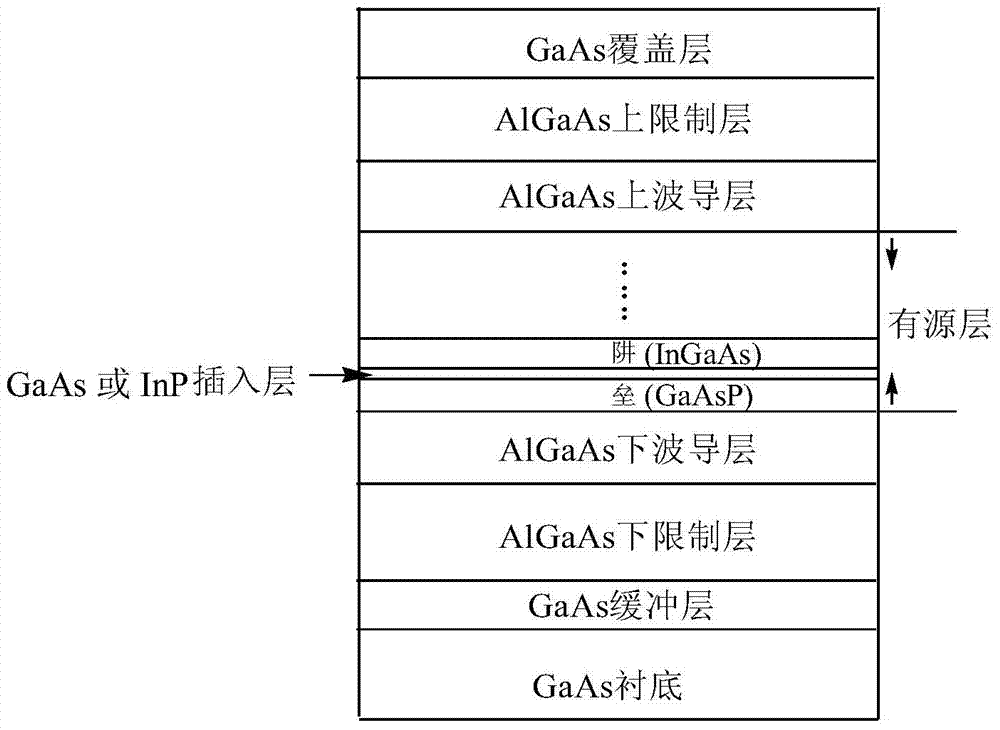

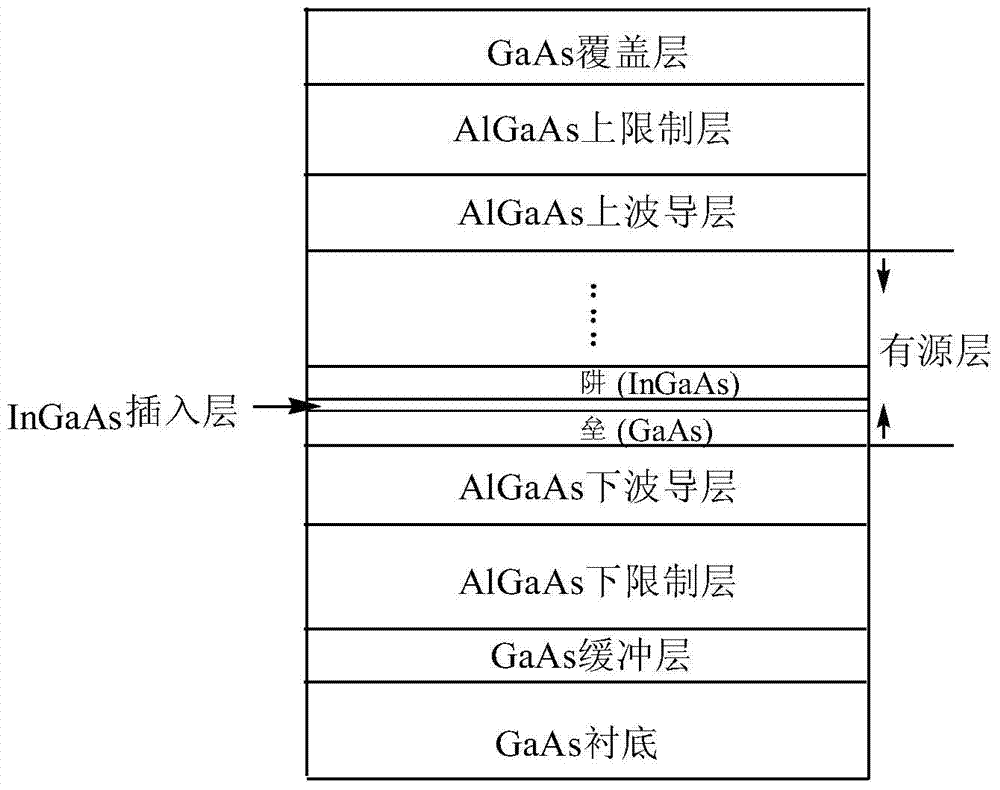

Epitaxial structure with interposed layer quantum well semiconductor laser

InactiveCN103779786AEase character fitImprove photoelectric performanceLaser detailsSemiconductor lasersQuantum wellWaveguide

The invention relates to an epitaxial structure with an interposed layer quantum well semiconductor laser. The invention discloses a preparation method of a semiconductor laser with a special structure. The structure comprises from the top to the bottom a GaAs substrate, a GaAs buffer layer, an AIGaAs lower restriction layer, an AIGaAS lower waveguide layer, an active layer, an AIGaAs upper waveguide layer, an AIGaAs upper restriction layer and a GaAs cover layer. In the structure, a thin InGaAs layer whose GaAs or InP or In component content is quite low (compared to the In component in a quantum well) is inserted between the quantum well and the barrier of the active layer, so that the quality adaption between the quantum well and the barrier can be effectively relieved, the interface quality is improved, the stress is lowered, a quite low threshold current density is obtained, and the photoelectric performance of the semiconductor laser device is improved.

Owner:TAIYUAN UNIV OF TECH +1

Device and method for casting large-sized compound steel ingot by using graphite electrode ring for preheating electroslag

The invention provides a device and method for casting a large-sized compound steel ingot by using a graphite electrode ring for preheating electroslag. The device comprises a T-shaped electric conduction crystallizer, supporting arms and a lined electroslag furnace, wherein two transverse arms on a support are respectively used for lifting and dropping the graphite electrode ring and a self-consuming electrode ring; the lined electroslag furnace is used for slagging and pouring premelting slag into the T-shaped electric conduction crystallizer; and an annular bottom water tank is arranged onan ingot introducing plate. The method comprises the following steps of: (1) putting a core rod in the T-shaped electric conduction crystallizer, slagging the premelting slag in the lined electroslagfurnace, and forming a slag tank by pouring; (2) lowering the graphite electrode ring, and causing the graphite electrode ring, the slag tank, the upper crystallizer, a casting power source and the traverse arms to form an electric conduction loop, and heating the surface of the core rod and the slag tank by electrifying; and (3) when a preset temperature reaches, moving away the graphite electrode ring, inserting the self-consuming electrode ring into the slag tank, and carrying out electroslag casting. The method has high utilization rate of heat, can prevent interlayer slag from being generated on the compound interface of the steel ingot, facilitates the improvement of the quality of the steel ingot and simplifies the production equipment.

Owner:NORTHEASTERN UNIV LIAONING

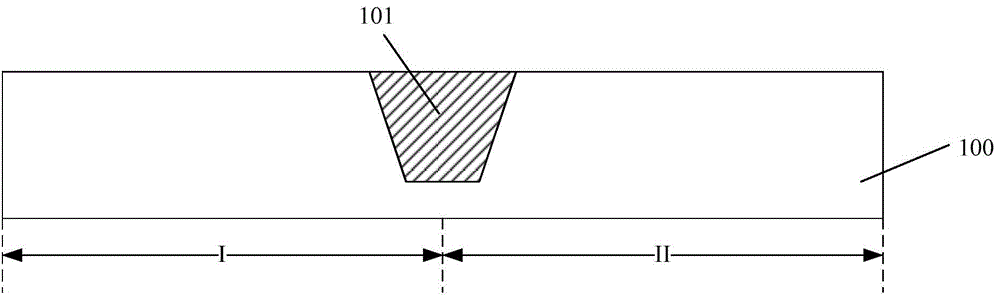

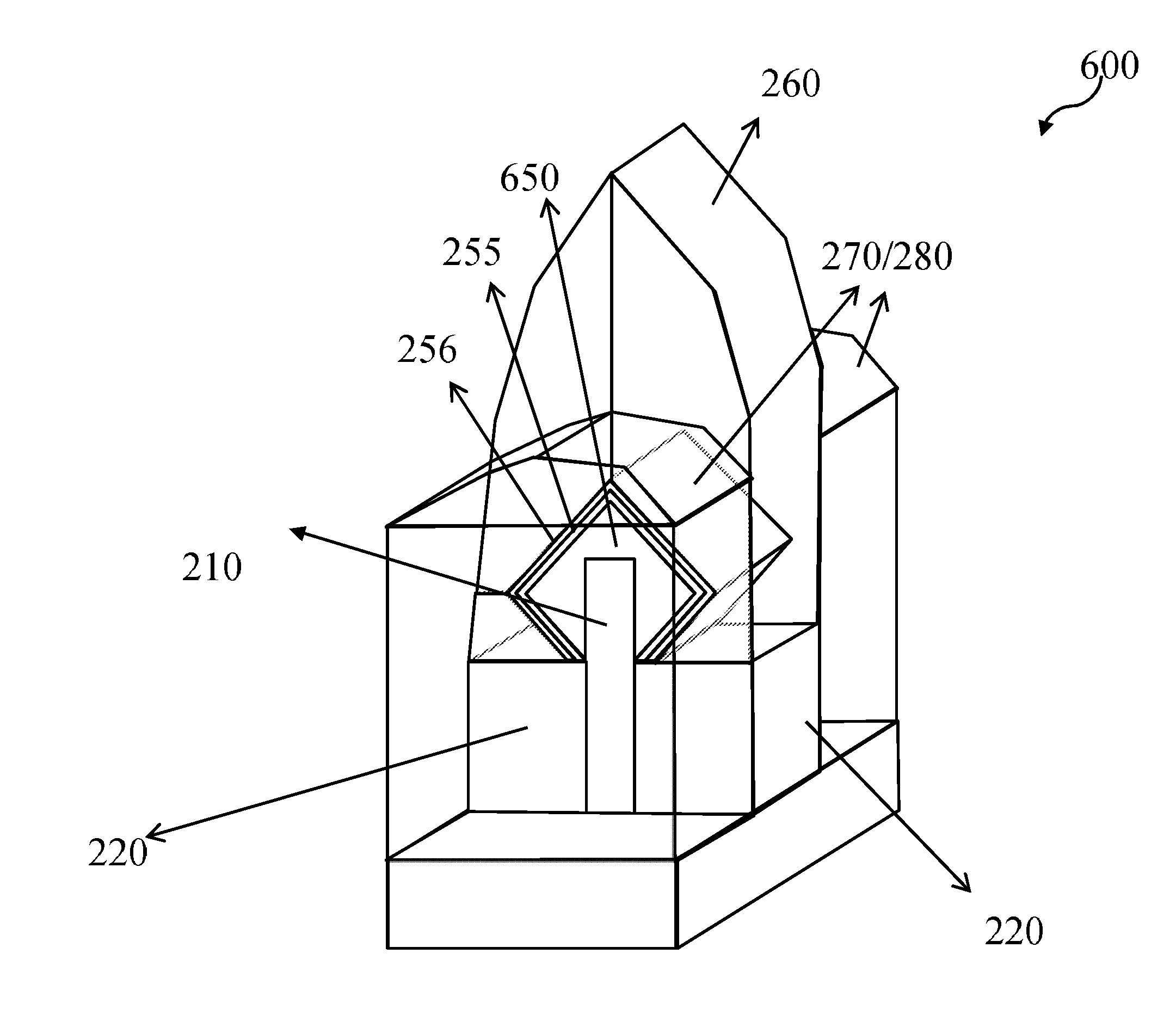

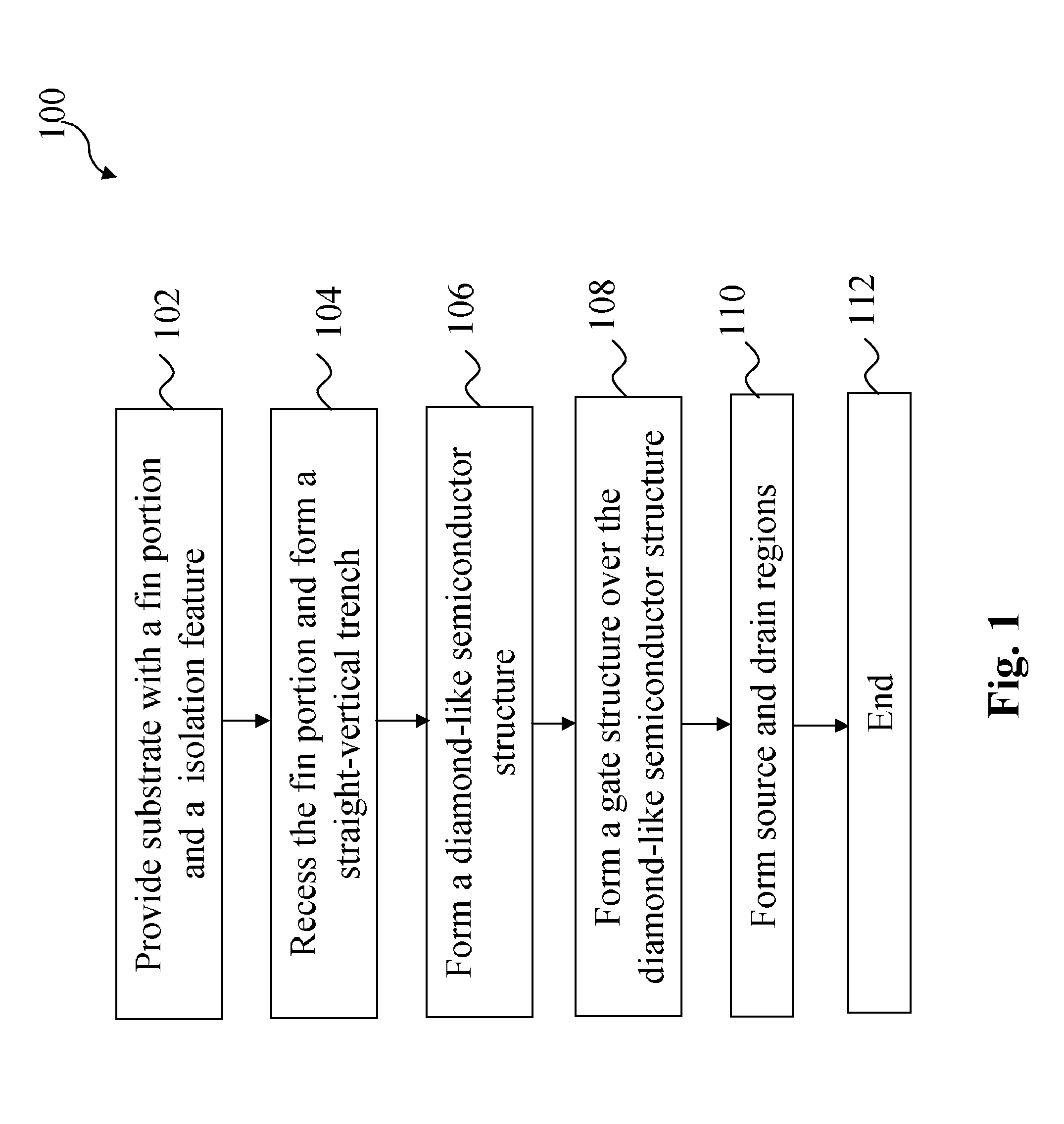

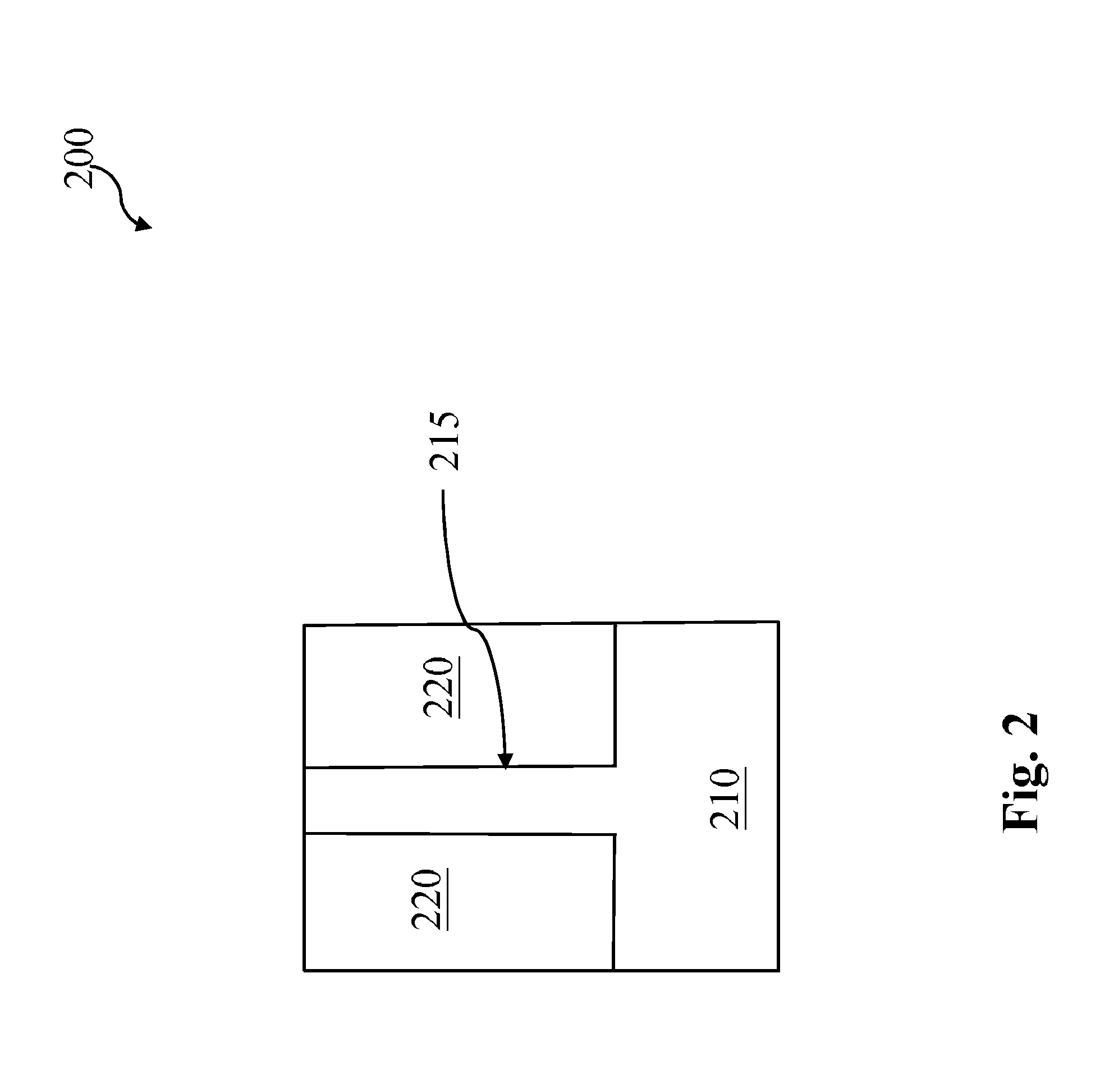

FINFET Device Having A Channel Defined In A Diamond-Like Shape Semiconductor Structure

ActiveUS20150011068A1Improve performanceImprove device densitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsSemiconductor structure

The present disclosure provides a FinFET device. The FinFET device comprises a semiconductor substrate of a first semiconductor material; a fin structure of the first semiconductor material overlying the semiconductor substrate, wherein the fin structure has a top surface of a first crystal plane orientation; a diamond-like shape structure of a second semiconductor material disposed over the top surface of the fin structure, wherein the diamond-like shape structure has at least one surface of a second crystal plane orientation; a gate structure disposed over the diamond-like shape structure, wherein the gate structure separates a source region and a drain region; and a channel region defined in the diamond-like shape structure between the source and drain regions.

Owner:TAIWAN SEMICON MFG CO LTD

Manufacturing method of dielectric layer

InactiveCN1485889ASimple processReduce the number of keysSemiconductor/solid-state device manufacturingOptoelectronicsSilicon oxide

The invention is a dielectric layer making method, placing a substrate in a furnace tube and developing a silicon oxide layer on the substrate, then converting the silicon oxide layer into a silicon oxynitride layer, then, developing a silicon oxide layer on the silicon oxynitride, and a silicon oxynitride / silicon nitride / silicon oxide overlapped layer dielectric layer on the substrate. The technique is completed in the same furnace tube.

Owner:PROMOS TECH INC

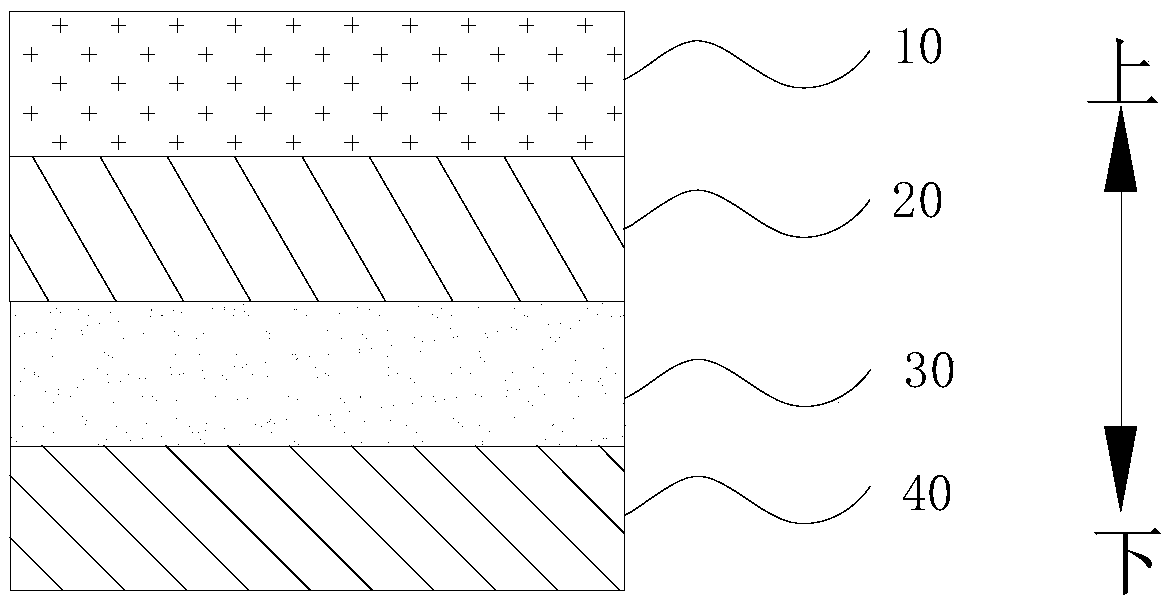

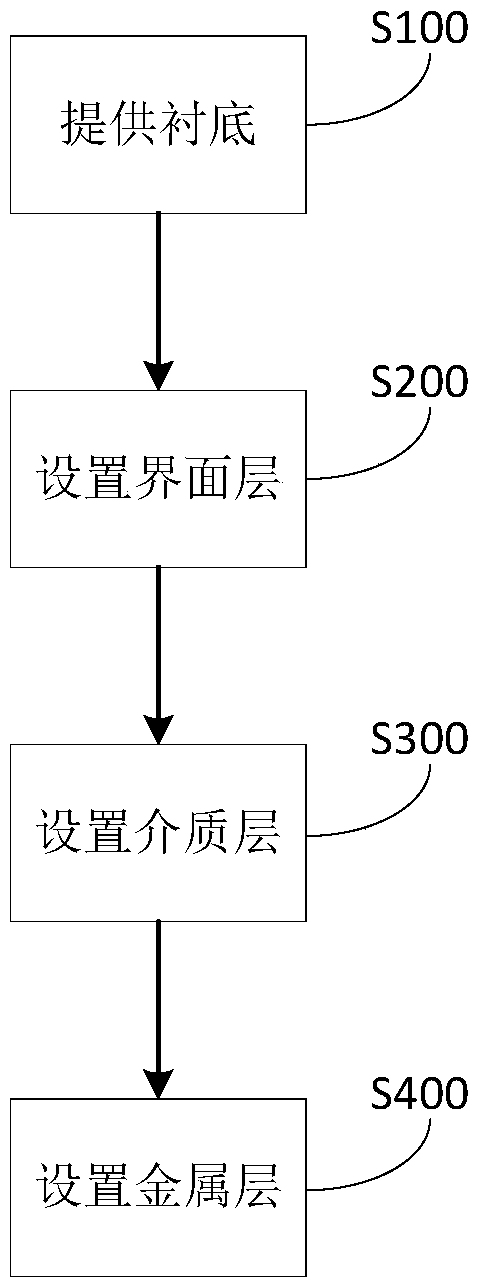

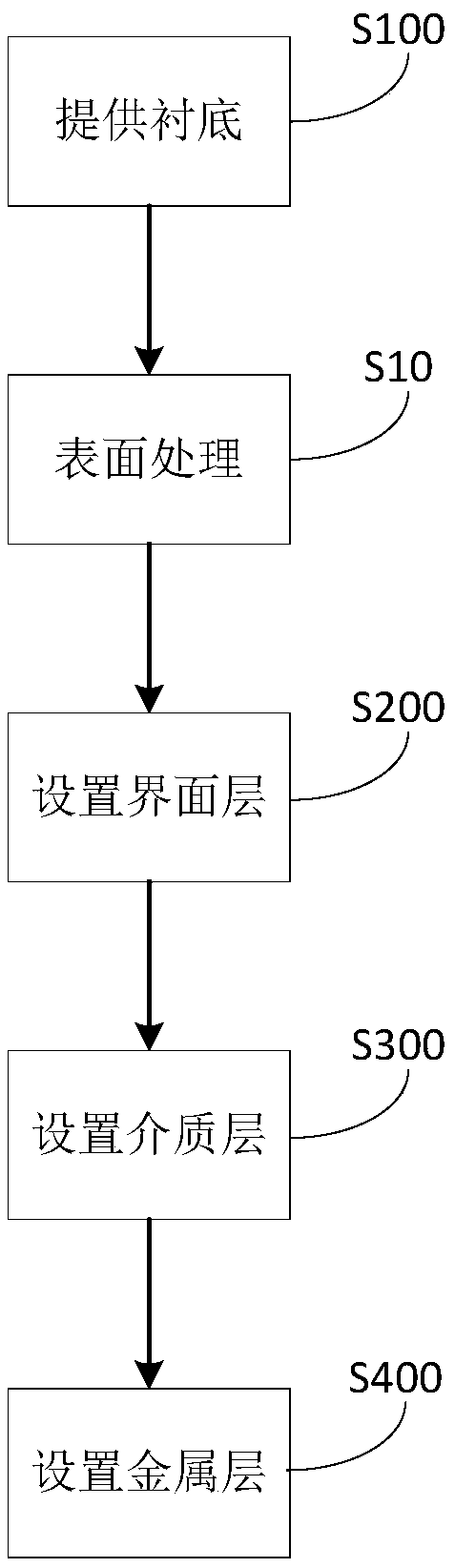

Semiconductor structure, forming method thereof and field effect transistor

InactiveCN105514168AImprove efficiencyGood effectSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureInterface layer

The invention discloses a semiconductor structure, a forming method thereof and a field effect transistor. The semiconductor structure comprises a substrate, an interface layer, a dielectric layer and a metallic layer, wherein at least a part of the upper surface of the substrate is a nonpolar face or semipolar face formed by a nitride semiconductor crystal; the interface layer is formed on the nonpolar face or semipolar face and is prepared from either a nitride or a nitric oxide; the dielectric layer is formed on the surface, far away from the substrate, of the interface layer; the metallic layer is formed on the surface, far away from the interface layer, of the dielectric layer. Thus, the interface layer can be formed on the nonpolar face or semipolar face of the surface of the substrate, then, unstable chemical bonds can be effectively prevented from being formed on the surface of the substrate, the interface quality is improved, and then, the interface performance of the semiconductor structure can be effectively improved.

Owner:TSINGHUA UNIV