Method for improving SiC and SiO2 interface state density

A technology of interface state density and S60, which is applied in the field of microelectronics, can solve the problems of low MOSFET channel mobility, ineffective H element passivation, and obstacles to the expected advantages of SiC devices, so as to improve mobility characteristics and reduce Interface state density, effect of improving interface quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

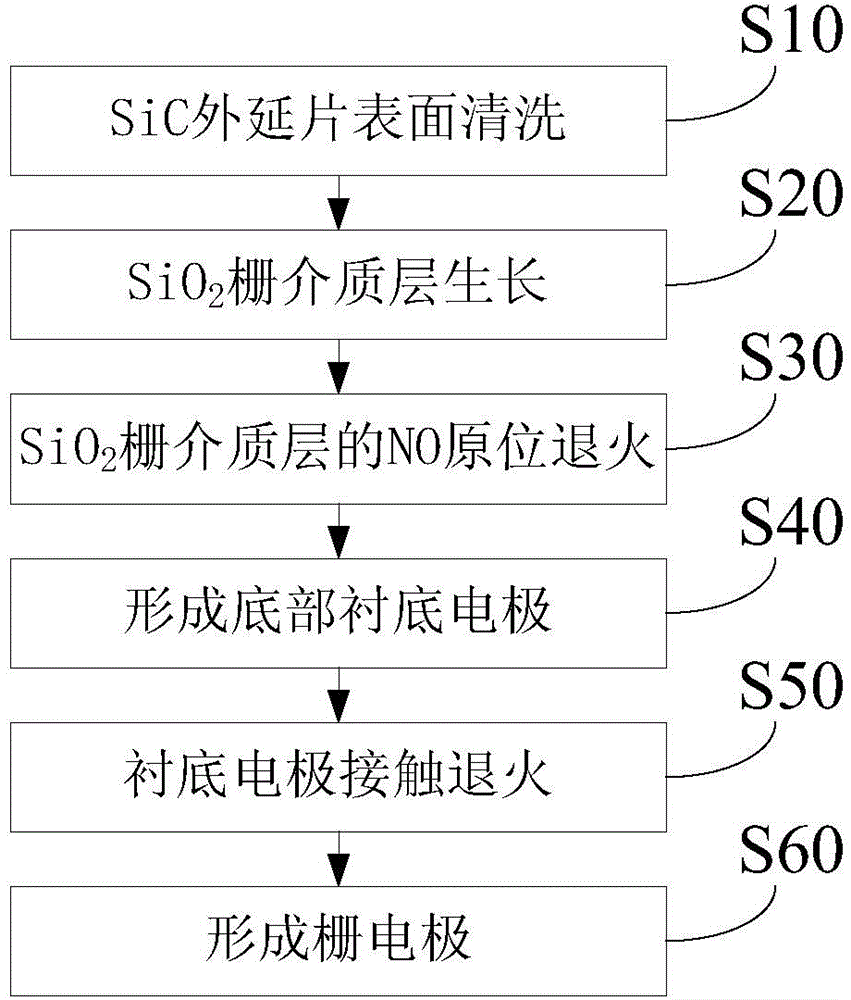

[0025] like figure 1 Shown, the embodiment of the present invention comprises the following steps:

[0026] S10. Cleaning the surface of the SiC epitaxial wafer by a standard cleaning method:

[0027] S101. Remove surface organic matter: immerse the SiC epitaxial wafer in acetone, trichlorethylene, acetone, methanol, and deionized water for 5 minutes each under ultrasonic conditions, and then use N 2 blow dry;

[0028] S102. Remove the intrinsic oxide layer on the surface: place the SiC epitaxial wafer after the first cleaning in HF acid solution for 15 minutes, and then oscillate with deionized water in ultrasonic waves for 5 minutes;

[0029] S103, placing the SiC epitaxial wafer cleaned for the second time in H 2 SO 4 :H 2 o 2 = 1:1 (volume ratio) soaked in the solution for 15min, H 2 SO 4 The concentration is 98%, H 2 o 2 The concentration is 27%, then rinse with deionized water;

[0030] S104, placing the SiC epitaxial wafer after the third cleaning in HF:H 2 ...

Embodiment 2

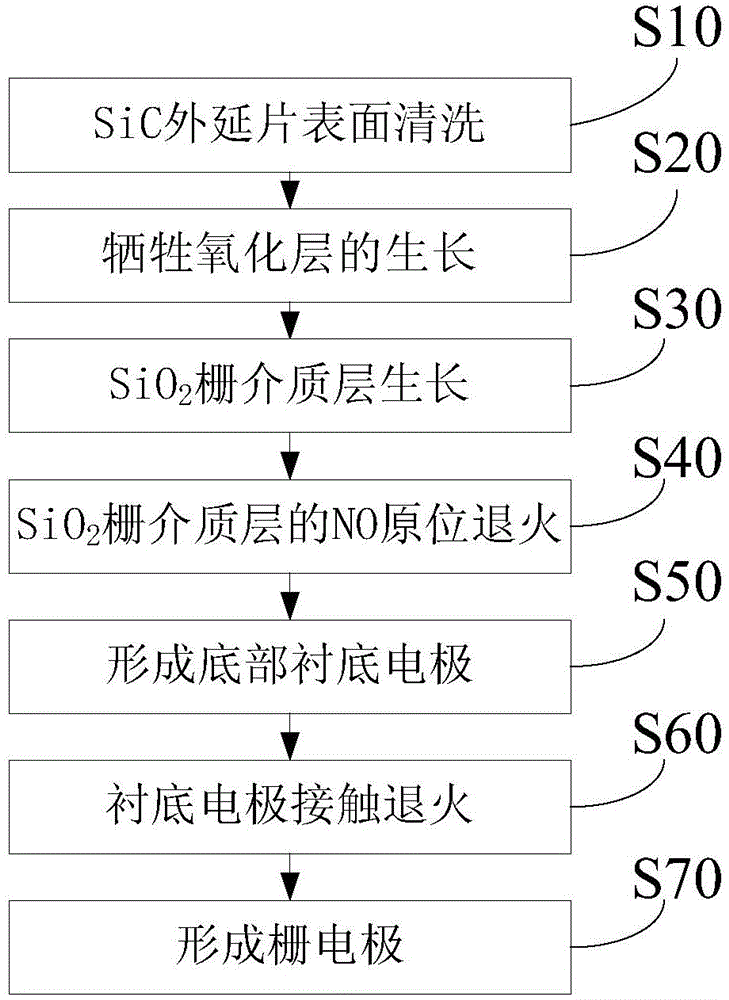

[0075] Compared with Example 1, in this example, on the basis of Example 1, SiO is grown in a large area 2 A sacrificial oxide growth process is added before the gate dielectric layer, which can effectively reduce the interface roughness and effectively improve the interface flatness.

[0076] like figure 2 As shown, this embodiment includes the following steps:

[0077] S10. Cleaning the surface of the SiC epitaxial wafer by a standard cleaning method:

[0078] S101. Remove surface organic matter: immerse the SiC epitaxial wafer in acetone, trichlorethylene, acetone, methanol, and deionized water for 5 minutes each under ultrasonic conditions, and then use N 2 blow dry;

[0079] S102. Remove the intrinsic oxide layer on the surface: place the SiC epitaxial wafer after the first cleaning in HF acid solution for 15 minutes, and then oscillate with deionized water in ultrasonic waves for 5 minutes;

[0080] S103, placing the SiC epitaxial wafer cleaned for the second time i...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com