Manufacturing method of dielectric layer

A manufacturing method and dielectric layer technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as capacitor performance deterioration, large leakage current, and complicated process steps, so as to reduce defects, prevent leakage, and The effect of simplifying the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention is a method for manufacturing a dielectric layer, which is described here by taking the manufacture of a capacitor as an example.

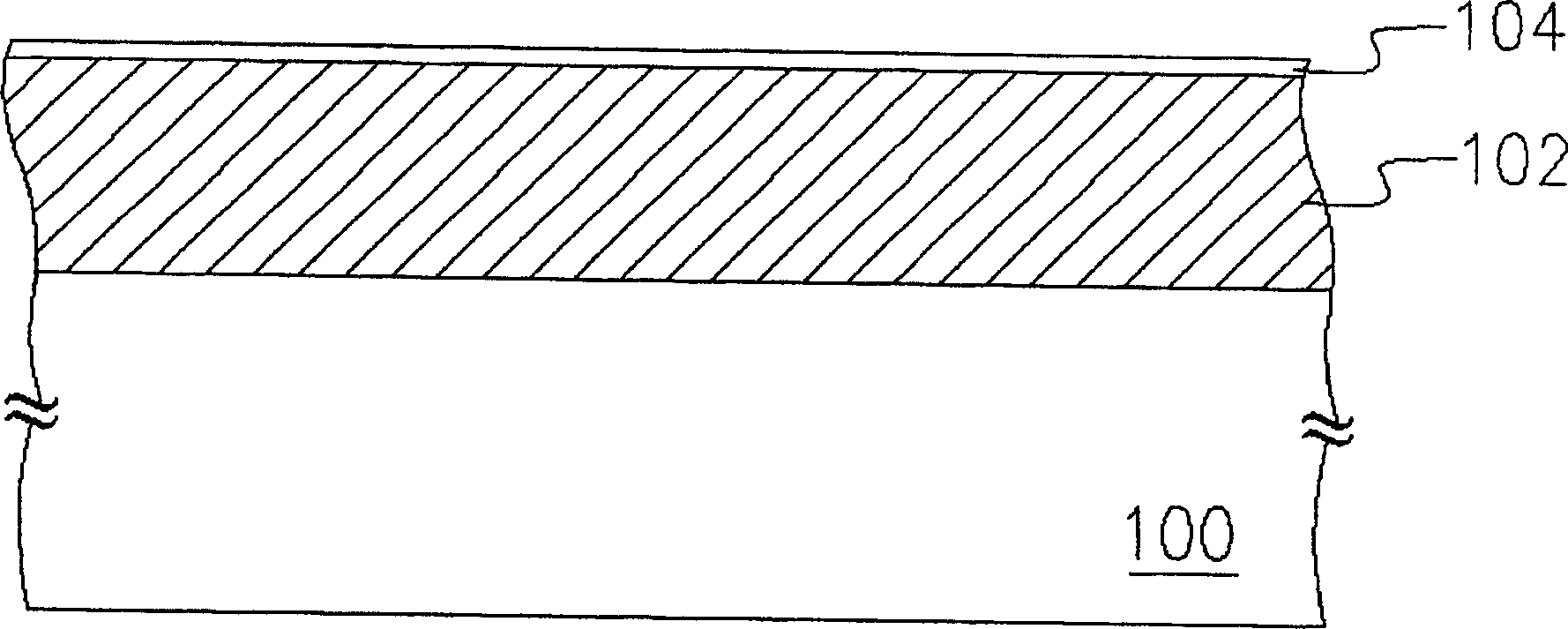

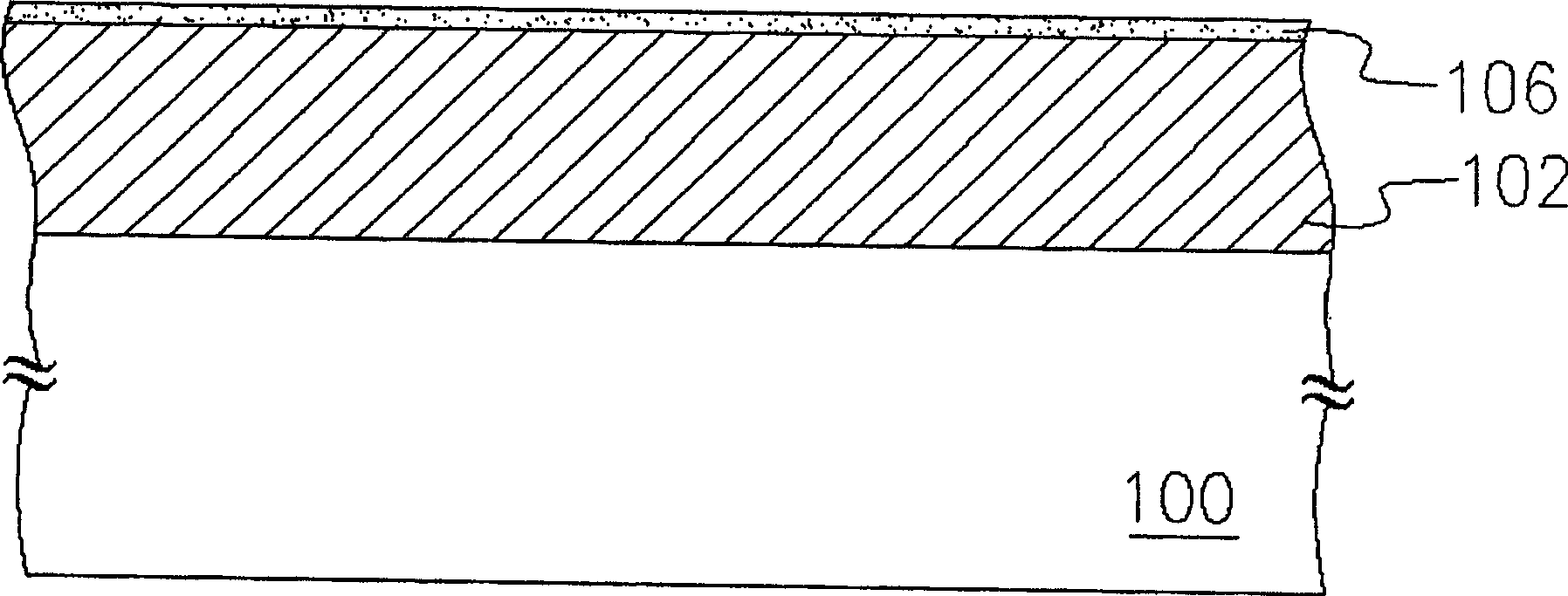

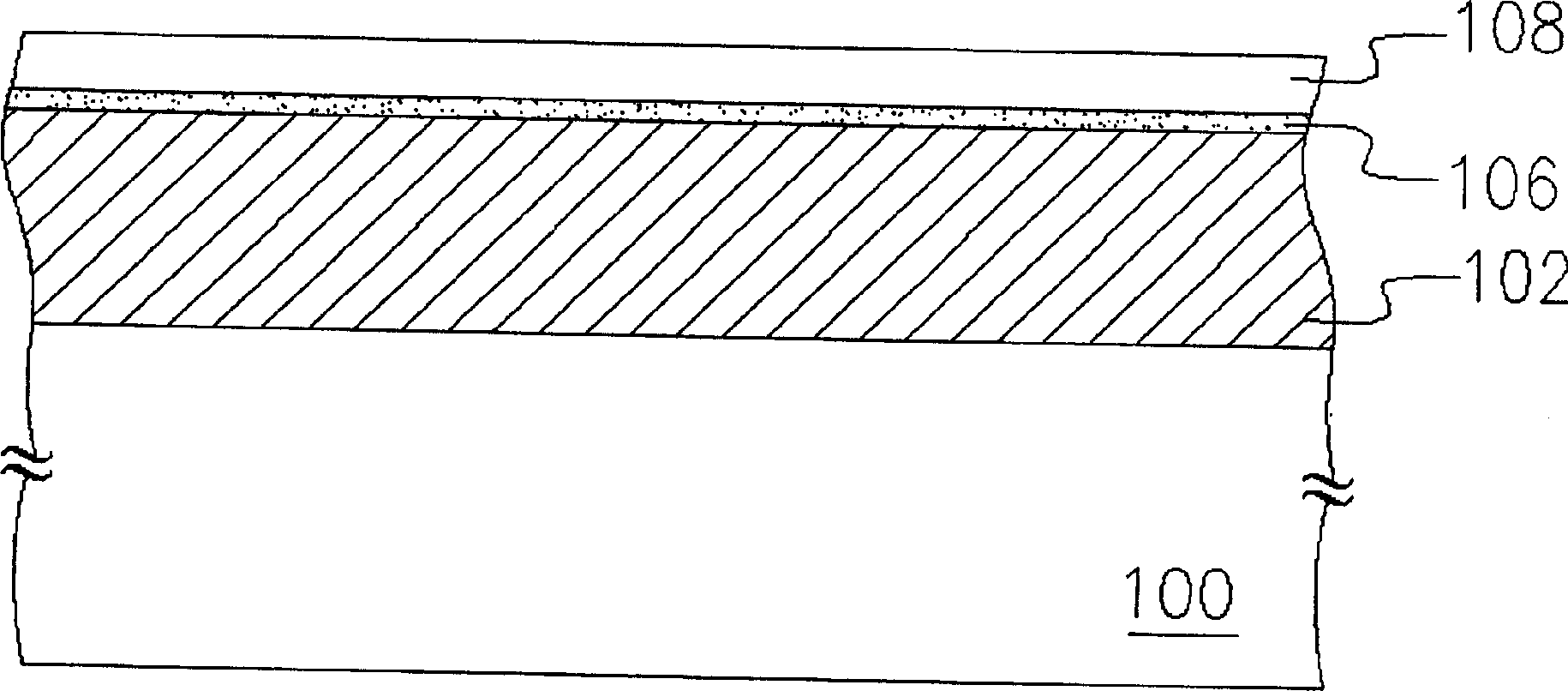

[0024] Figure 1A to Figure 1D It is a flowchart of a manufacturing method of a capacitor according to a preferred embodiment of the present invention.

[0025] Please refer to Figure 1A , a substrate 100 is provided, such as a silicon substrate, and a part of the semiconductor device has been fabricated on the substrate 100, such as a metal-oxide-semiconductor transistor (not shown) has been fabricated. Next, a lower electrode layer 102 of a capacitor is formed on the substrate 100 . The material of the bottom electrode layer 102 is, for example, polysilicon, and its formation method is, for example, chemical vapor deposition, or a part of the silicon substrate is monocrystalline silicon as the bottom electrode. After the lower electrode layer 102 is formed, the surface of the lower electrode layer 102 will undergo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More