Formation method of transistor

A technology of transistors and semiconductors, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems affecting transistor performance, affecting metal layer filling, and increasing difficulty of work function layers, achieving high trench filling capabilities, Improved performance, high interface quality effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

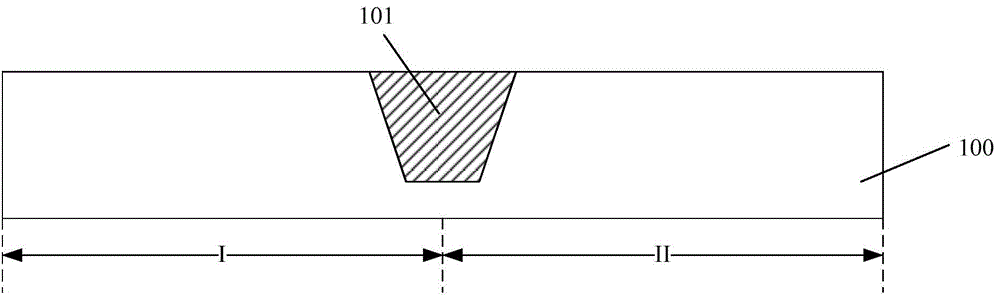

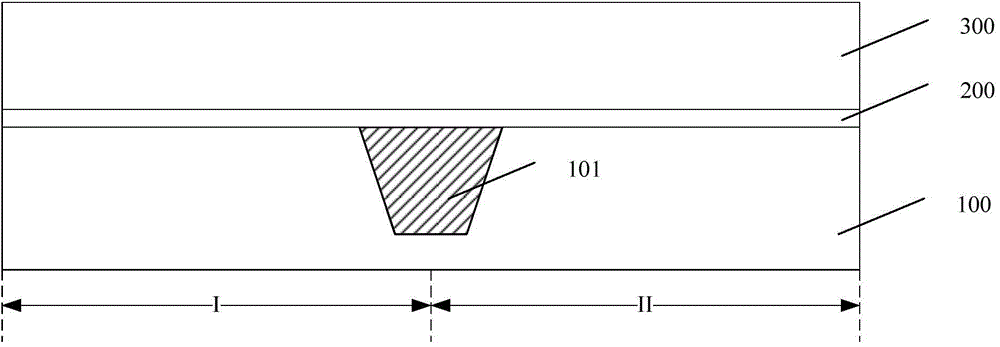

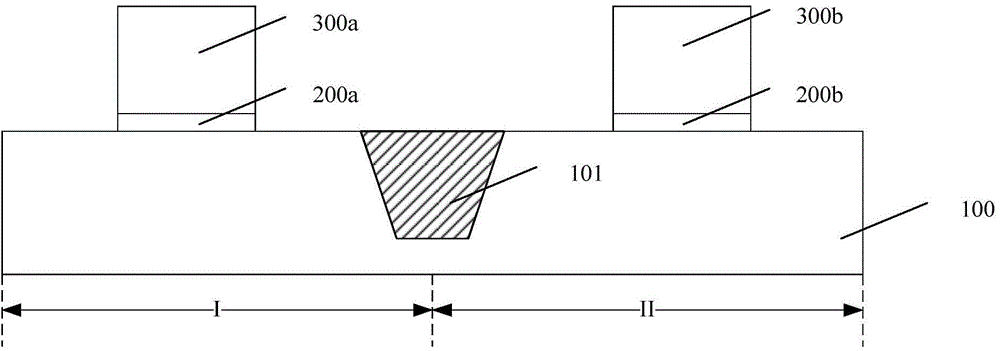

[0027] As mentioned in the background art, in the prior art, the deposition quality of the work function layer formed by the physical vapor deposition process in the groove is poor, which may easily cause the top of the groove to be closed and affect the performance of the formed transistor.

[0028] Research has found that the work function layer can be formed by using an atomic layer deposition process with higher groove filling performance instead of the physical vapor deposition process.

[0029] However, further studies have found that although the atomic layer deposition process is used to form the work function layer, which has a high groove filling ability and will not cause the top of the groove to be closed, it is found in the process of forming the NMOS work function layer that the atomic layer The deposition quality of the NMOS work function layer formed by the deposition process and the quality of the interface with adjacent layers (for example: protective layer) a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More