Patents

Literature

42results about How to "Lower Schottky barrier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Two-dimensional black phosphorus/transitional metal chalcogenide heterojunction device and preparation method therefor

InactiveCN106024861AHigh carrier mobilityGood electrical propertiesMaterial nanotechnologyFinal product manufactureHeterojunctionPhotovoltaic detectors

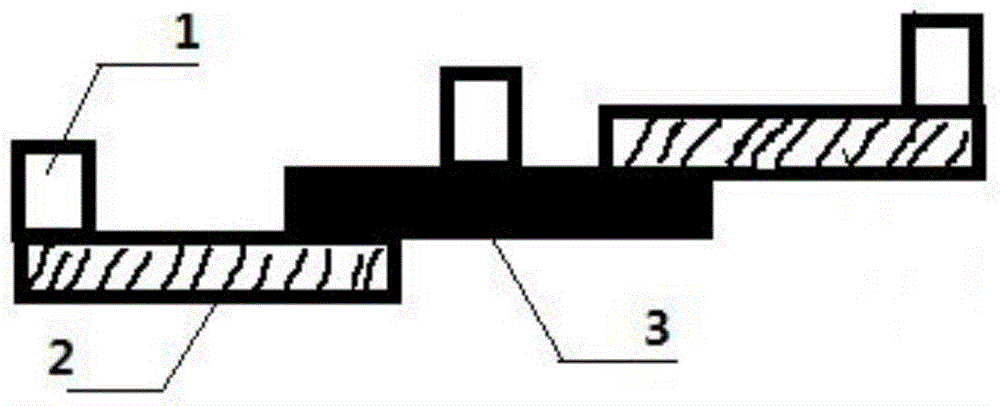

The invention discloses a two-dimensional black phosphorus / transitional metal chalcogenide heterojunction based device. The heterojunction adopts a laminated structure of two-dimensional black phosphorus nanometer slices and two-dimensional transitional metal chalcogenide nanometer slices; the number of the two-dimensional black phosphorus layers is 1-50; the two-dimensional transitional metal chalcogenide comprises 1-50 layers in terms of thickness; the two kinds of two-dimensional materials are prepared and synthesized through chemical vapor deposition, mechanical stripping, liquid phase stripping and the like; and the device can be used for preparing a bipolar transistor, a field effect transistor or a photoelectric detector / photoelectric diode. The two-dimensional black phosphorus / transitional metal chalcogenide heterojunction device has the advantages as follows: a combination of the two kinds of two-dimensional materials of black phosphorus and the transitional metal chalcogenide is adopted to form the brand new pn type heterojunction structure; the heterojunction is combined based on natural van der Waals forces among materials; compared with the conventional heterojunction epitaxial growth process, the heterojunction device provided by the invention is easier to prepare; and compared with the existing bulk material, the heterojunction device provided by the invention is smaller in size, thinner, higher in flexibility and higher in the integration degree, so that the two-dimensional black phosphorus / transitional metal chalcogenide heterojunction device has the potential to be applied to the wearable equipment in the future.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

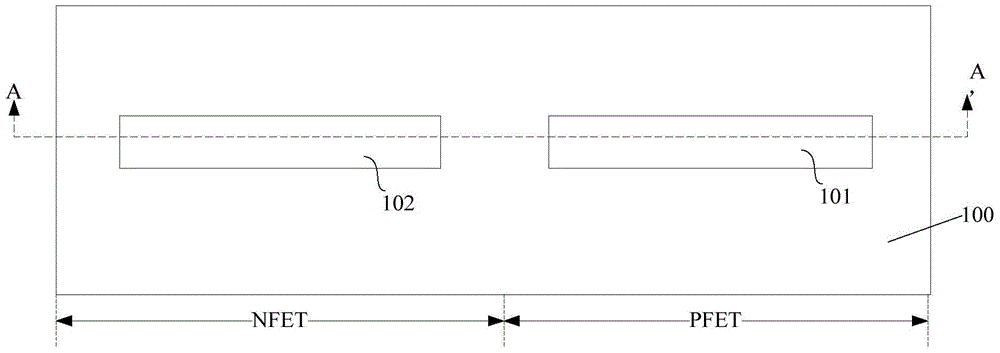

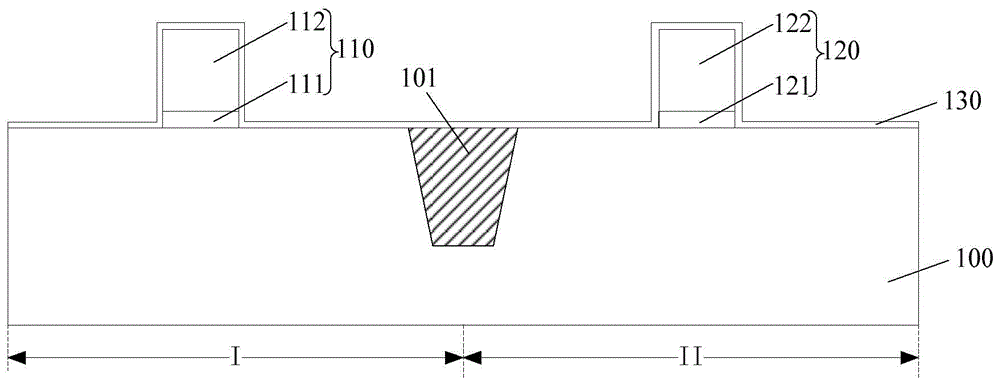

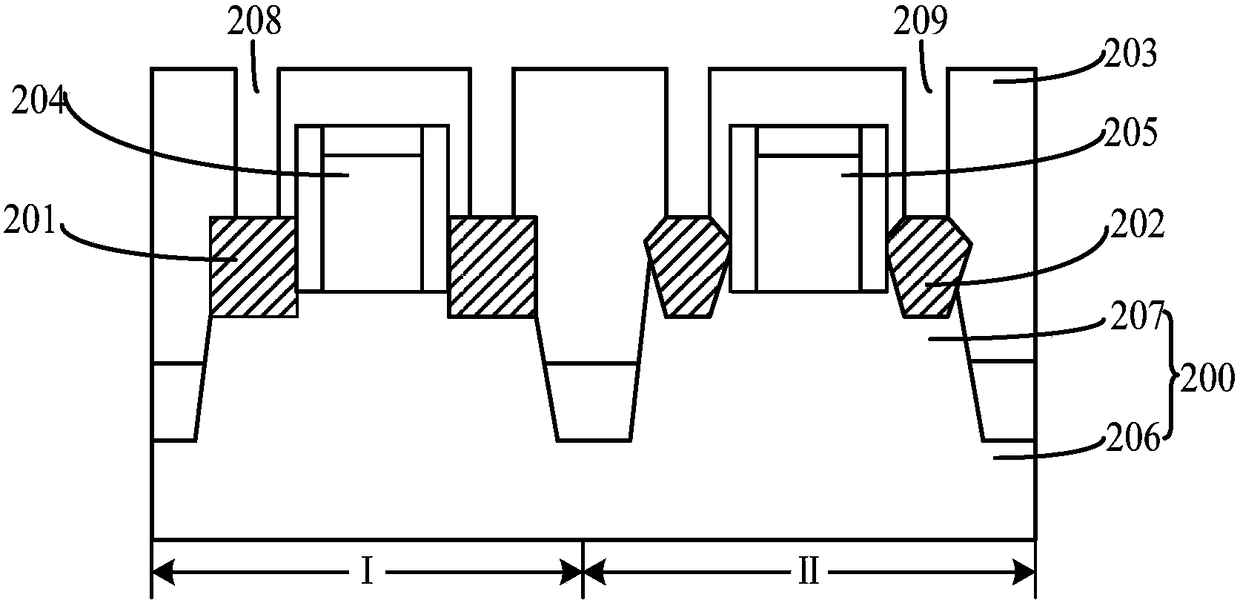

Semiconductor structure and formation method thereof

ActiveCN106158747ALower resistancePrevent proliferationTransistorSolid-state devicesIn situ dopingSemiconductor structure

The invention provides a semiconductor structure and a formation method thereof. The formation method of the semiconductor structure is that a semiconductor substrate is provided, the semiconductor substrate comprises a first region, a first fin part is formed on the first region, and an isolation layer is also formed on the semiconductor substrate; a first gate electrode structure crossing the first fin part is formed on the isolation layer; a first source-drain region is formed in the first fin part of the two sides of the first gate electrode structure; a dielectric layer is formed on the semiconductor substrate, and the dielectric layer covers the semiconductor substrate, the first fin part, the first gate electrode structure and the first source-drain region; the dielectric layer on the first region is etched so that a first contact hole arranged on the surface of the first source-drain region is formed; a first semiconductor epitaxial layer is formed on the surface of the first source-drain region, and the first type of doping ions are enabled to be doped in the first semiconductor epitaxial layer by using an in-situ doping technology; a metal silicide layer is formed on the surface of the first semiconductor epitaxial layer; and a metal plug fully filling the first contact hole is formed. According to the method, parasitic resistance of the formed semiconductor structure can be reduced.

Owner:SEMICON MFG SOUTH CHINA CORP +1

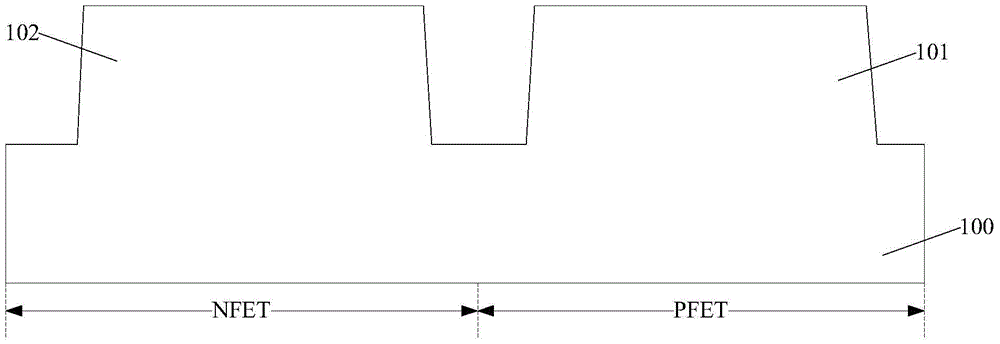

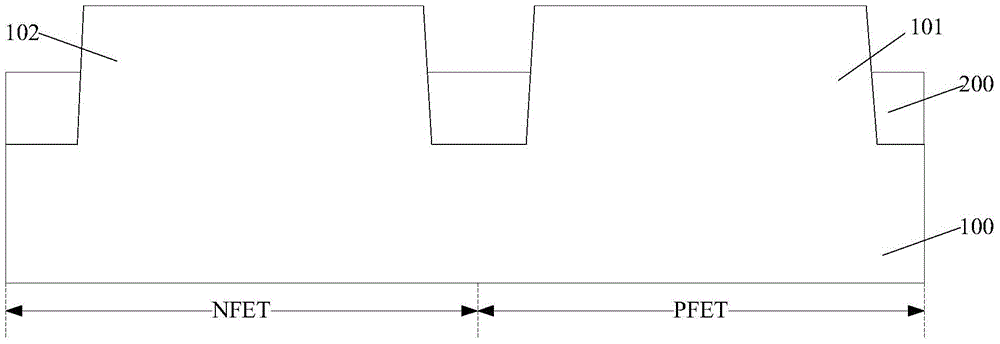

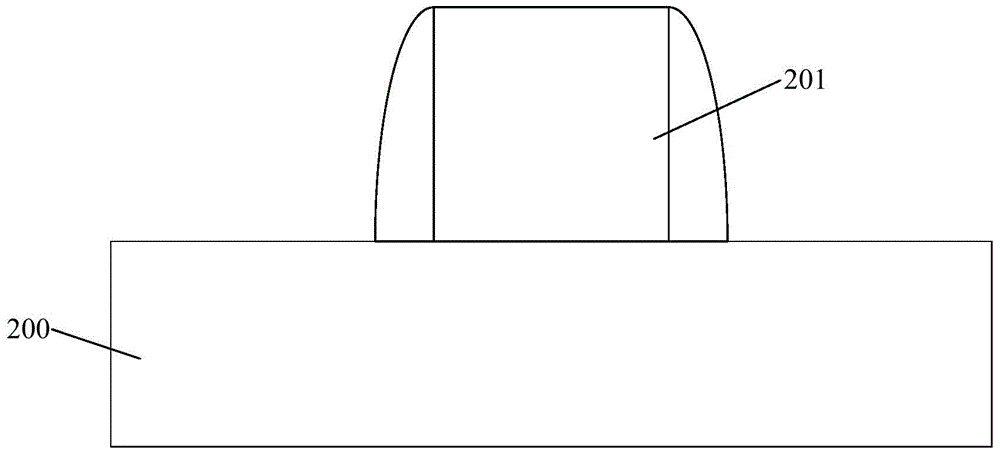

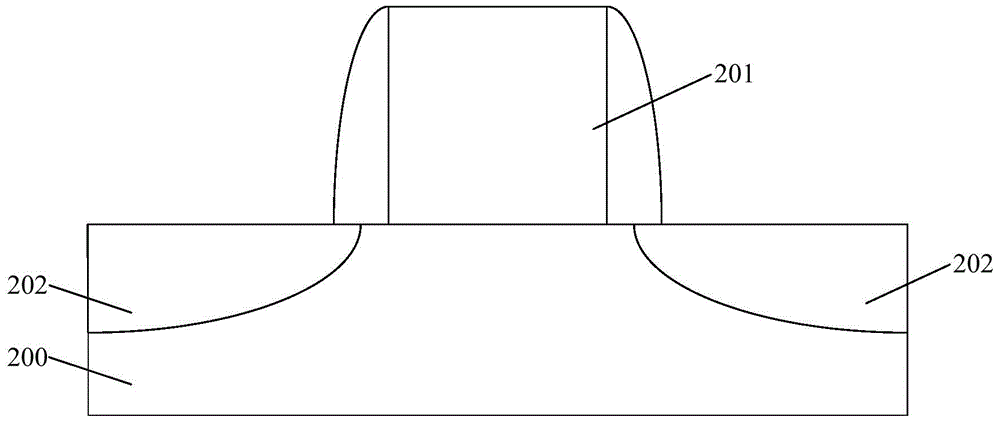

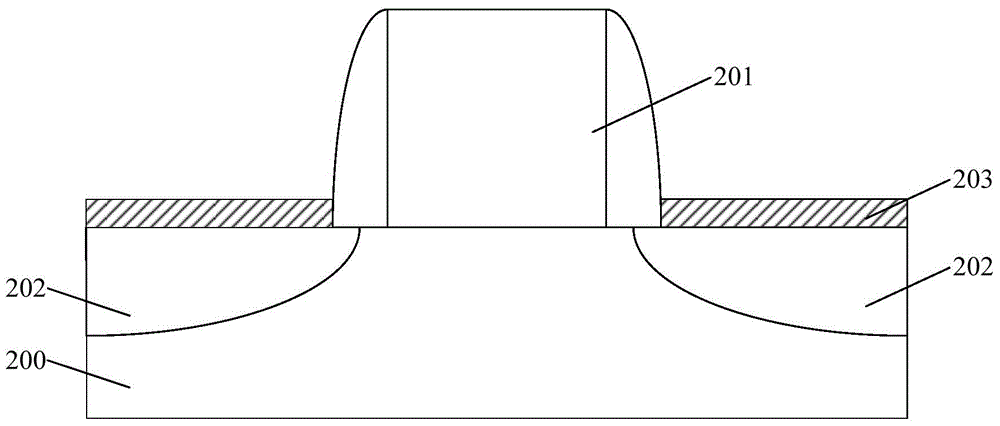

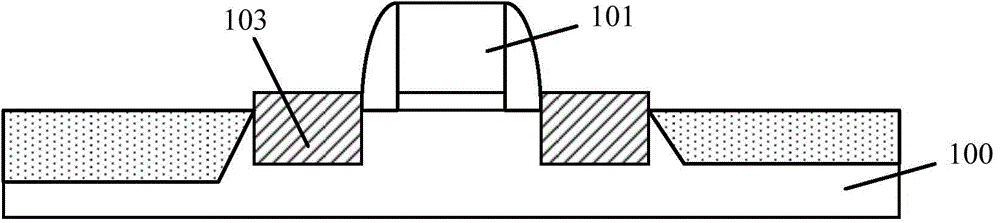

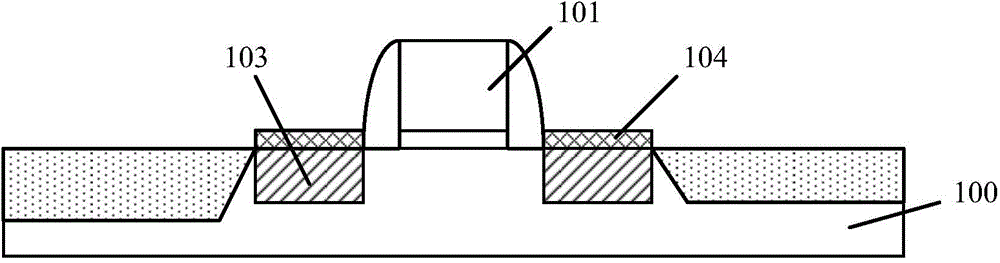

Semiconductor structure and forming method thereof

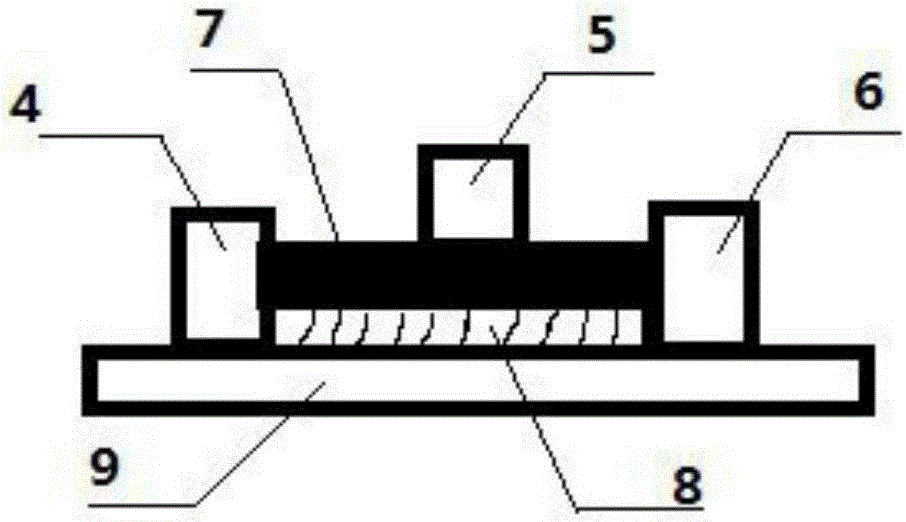

ActiveCN105336620ALower Schottky BarrierAlleviate the Fermi level pinning effectSemiconductor/solid-state device manufacturingSemiconductor devicesMetallic materialsOxide

The invention discloses a semiconductor structure and a forming method thereof. The forming method of the semiconductor structure comprises the steps as follows: a semiconductor substrate is provided; a gate structure which covers partial surface of the semiconductor substrate is formed; a source and a drain are respectively formed in the semiconductor substrate at two sides of the gate structure; a dielectric layer is formed on the semiconductor substrate; the surface of the dielectric layer is higher than the top surface of the gate structure; a through hole is formed in the dielectric layer and exposes the surfaces of the source and the drain; an oxidation layer is formed on the surfaces of the source and the drain at the bottom of the through hole; a metal material layer is formed on the surface of the oxidation layer; an annealing treatment is carried out; the metal material layer reacts with the oxidation layer to form a metal oxide layer and a metal semiconductor compound layer; and the metal semiconductor compound layer is located on the surface of the metal oxide layer. The contact resistance between the source and the drain of the semiconductor structure formed by the method and the metal semiconductor compound layer is relatively small.

Owner:SMIC INT NEW TECH DEV SHANGHAI CO LTD

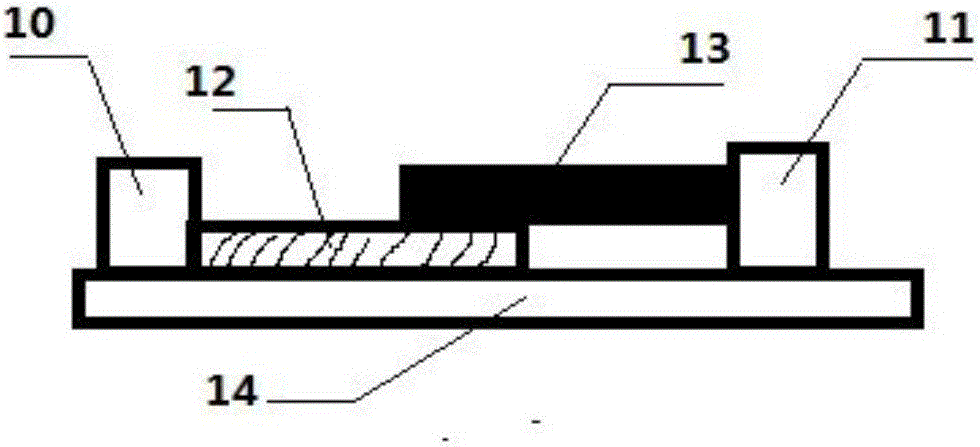

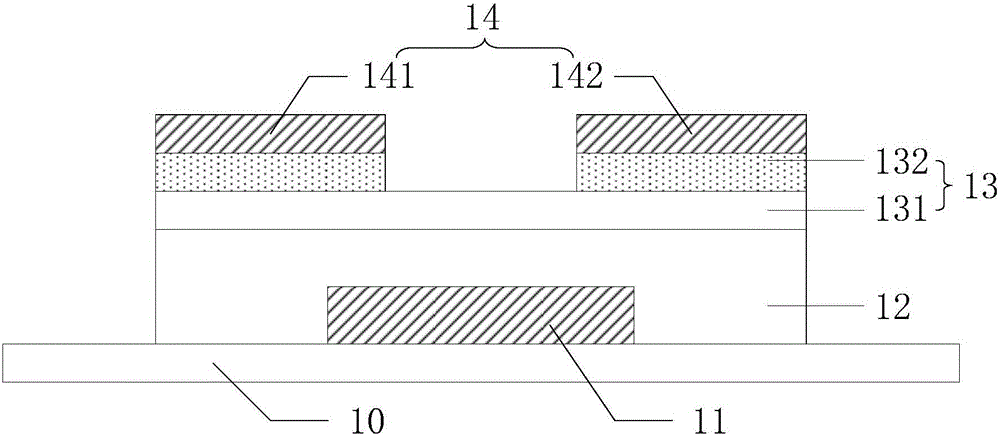

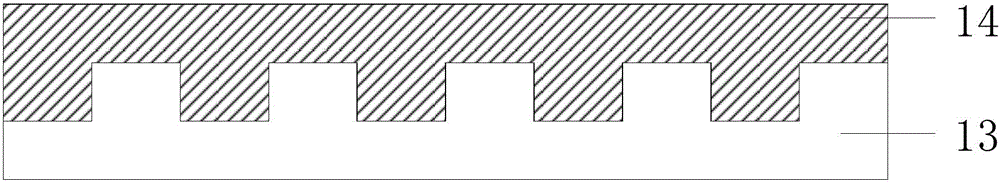

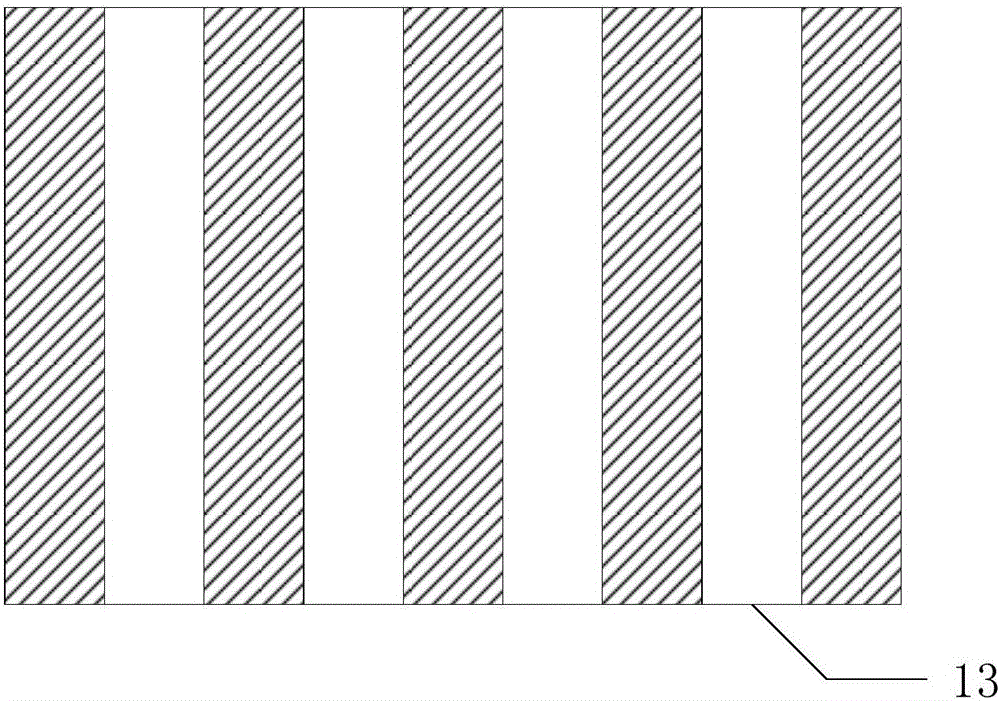

TFT (thin film transistor) array substrate and manufacturing method therefor, and liquid crystal display apparatus

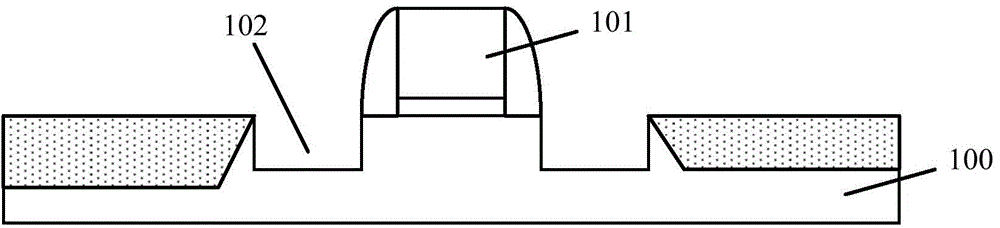

InactiveCN105895638AIncrease contact areaReduce distanceSolid-state devicesSemiconductor/solid-state device manufacturingConvex structureLiquid-crystal display

The invention discloses a TFT (thin film transistor) array substrate and a manufacturing method therefor, and a liquid crystal display apparatus. The TFT array substrate comprises a substrate and the TFT arranged on the substrate; the TFT comprises a semiconductor layer and a source electrode and a drain electrode arranged on the semiconductor layer, wherein the contact surface between the semiconductor layer and the source electrode and / or the drain electrode adopts a concave-convex structure. By adoption of the mode, the contact resistance between the semiconductor layer and a metal layer can be lowered, so that the electrical property of the TFT device is improved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

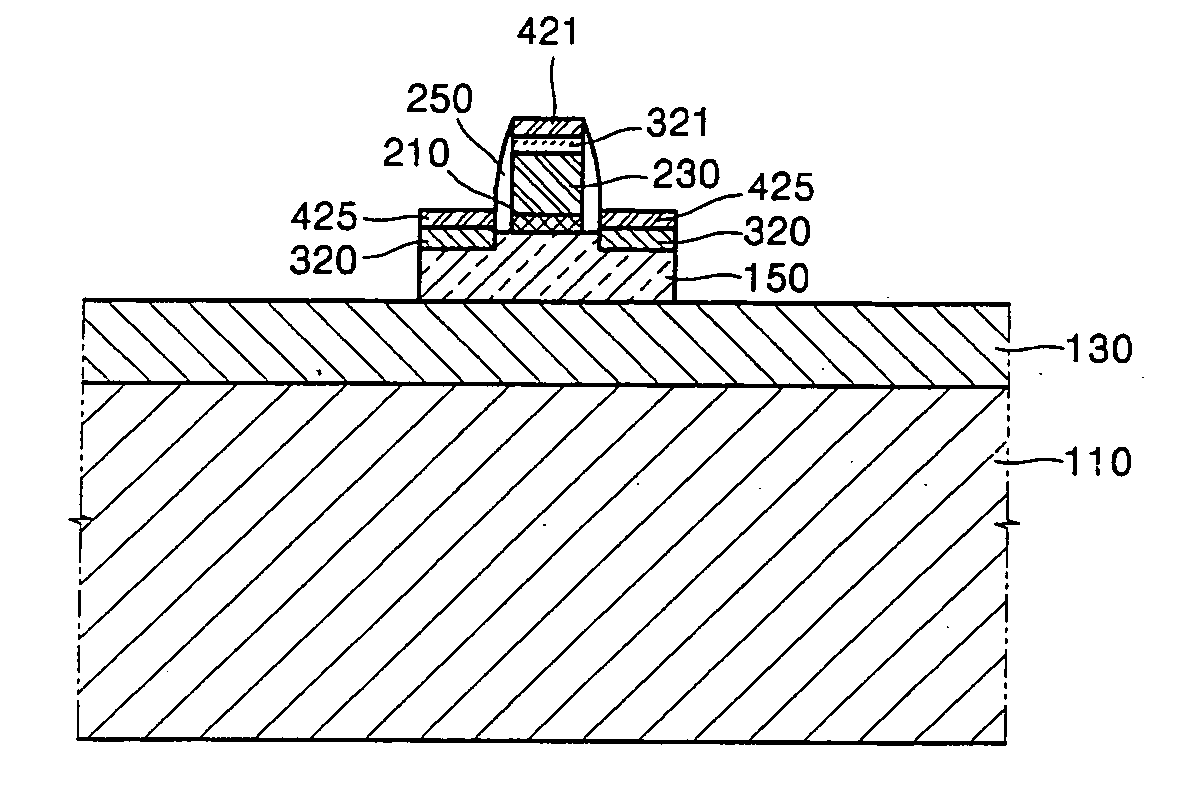

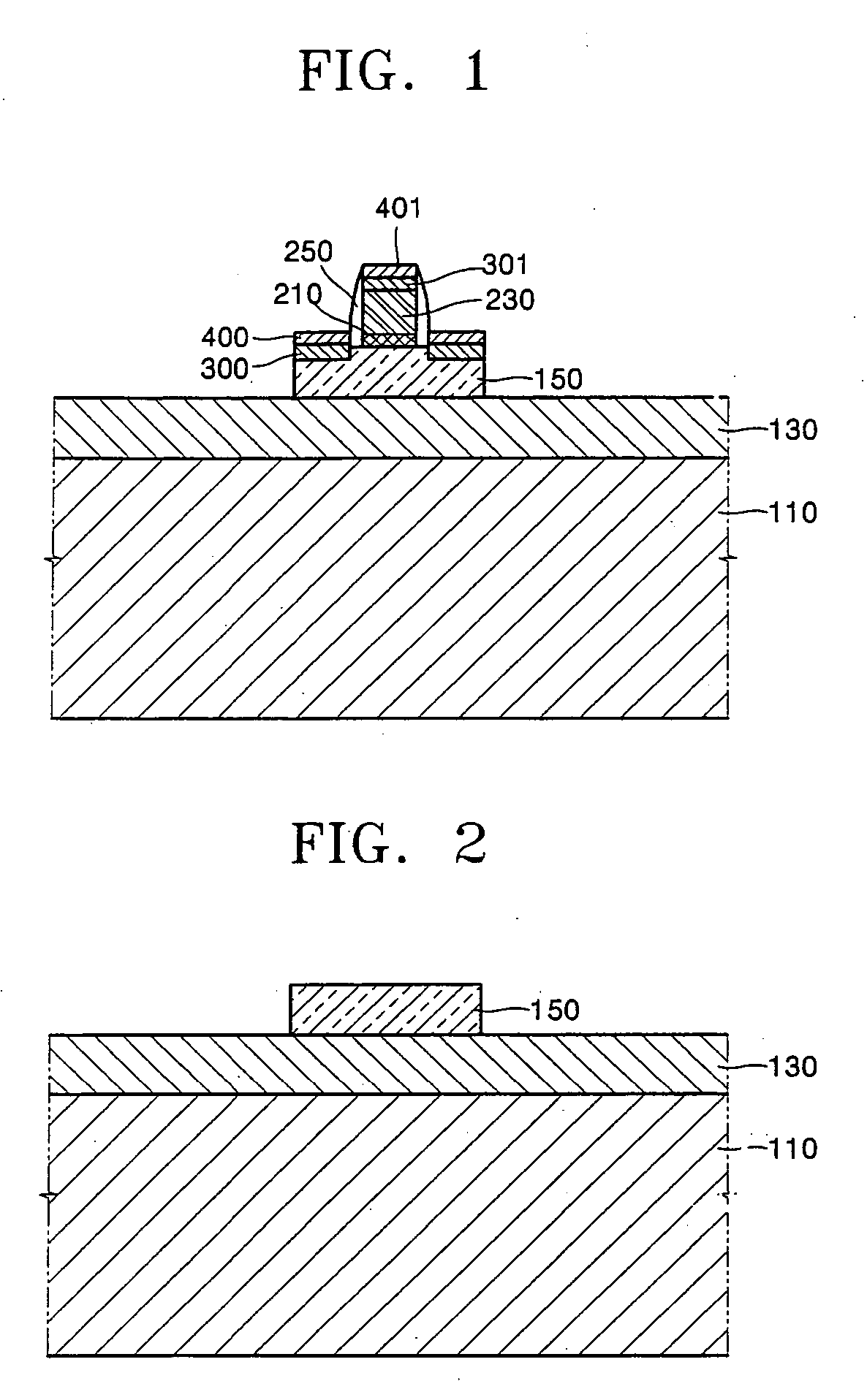

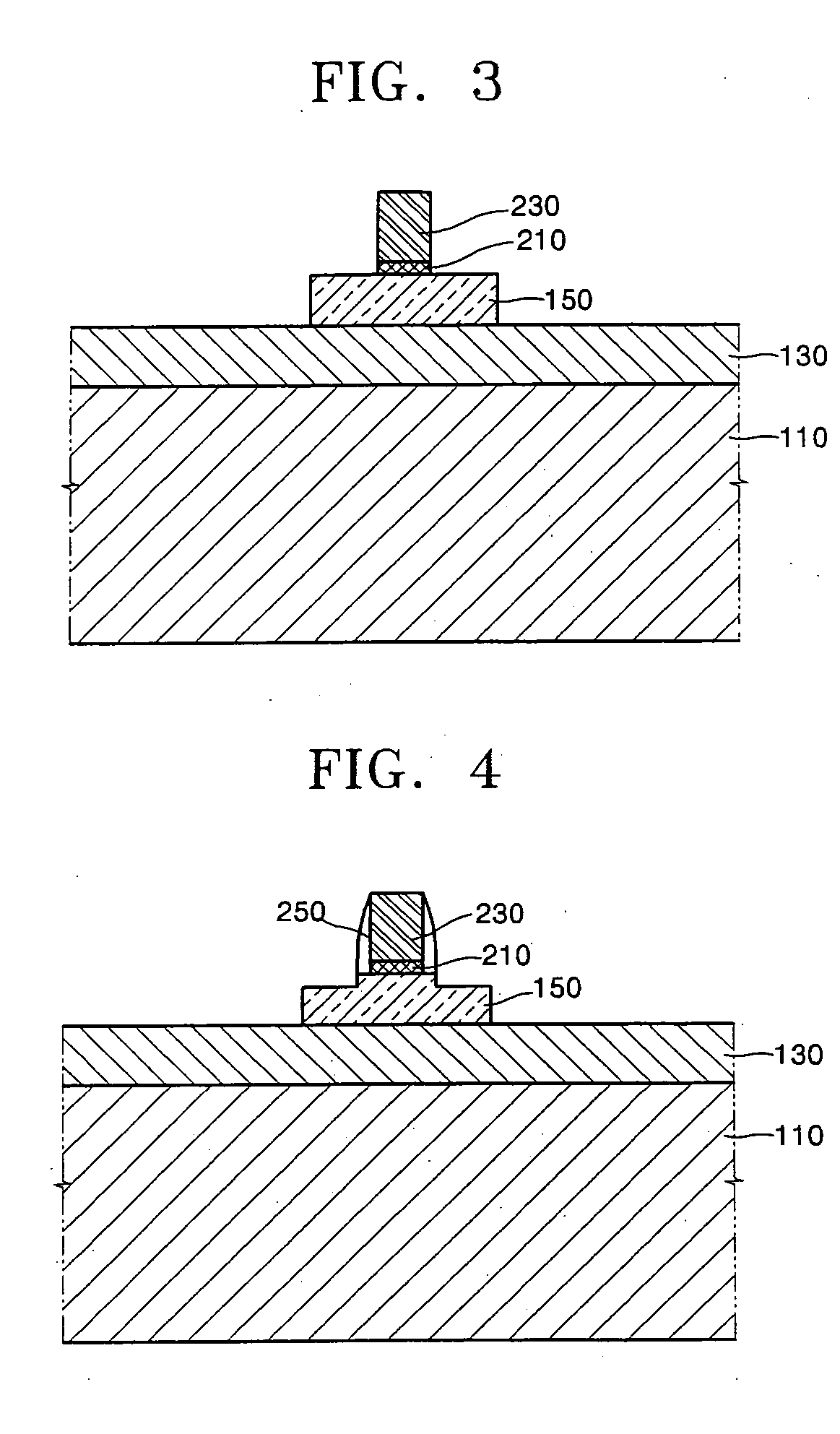

N-type schottky barrier tunnel transistor and manufacturing method thereof

InactiveUS20060131664A1Increase currentImprove conductivitySemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierGate dielectric

An n-type SBTT and a manufacturing method thereof are provided. The SBTT includes a silicon layer, a gate, a double layer that has a rare-earth metal suicide layer and a transition metal silicide layer. The silicon layer has a channel region. The gate is formed in an overlapping manner on the channel region and has a gate dielectric layer on its interface with respect to the silicon layer. The double layer is formed as a source / drain that has the channel region interposed on the silicon layer.

Owner:ELECTRONICS & TELECOMM RES INST

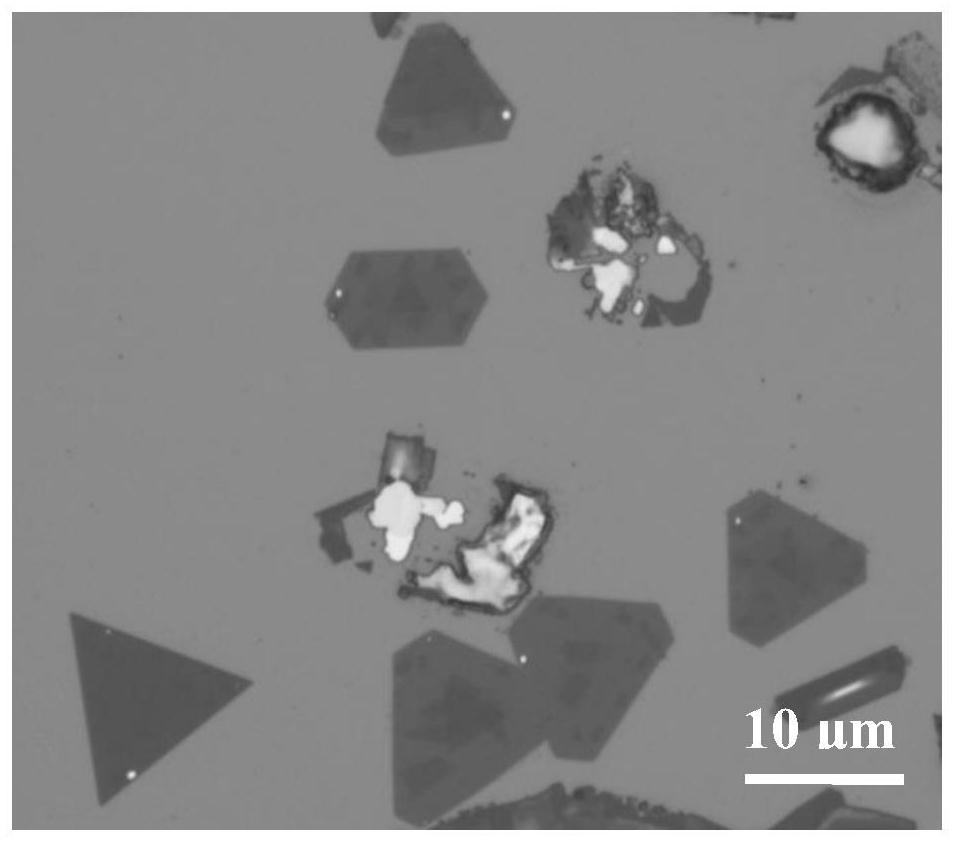

Two-dimensional molybdenum ditelluride vertical heterojunction and preparation method and application thereof

ActiveCN111403475AIncrease contactLower Schottky BarrierSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSchottky barrier

The invention belongs to the field of two-dimensional materials, and particularly discloses a two-dimensional molybdenum ditelluride vertical heterojunction and a preparation method and application thereof. The two-dimensional molybdenum ditelluride vertical heterojunction comprises a 1T'-MoTe<2> part and a 2H-MoTe<2> part, and the two parts are connected through interlayer Van der Waals' force; the preparation method comprises the following steps: S1, drying a mixed solution of ammonium tetramolybdate and sodium chloride, putting the dried mixed solution as a molybdenum source into a reactor,putting a growth substrate on the molybdenum source, putting tellurium powder as a tellurium source into the reactor, and putting the tellurium powder at the upstream of the molybdenum source; and S2, raising the temperature of the molybdenum source and the tellurium source to a reaction temperature, naturally cooling to room temperature, introducing carrier gas into the reactor to bring the tellurium source to the molybdenum source, introducing a reducing agent, and generating the two-dimensional molybdenum ditelluride vertical heterojunction on the growth substrate. The metal phase and semiconductor phase vertically stacked MoTe2 heterostructure prepared by the invention can effectively reduce the Schottky barrier of contact between a metal electrode and a material, and an important thought for improving metal-semiconductor contact is provided.

Owner:HUAZHONG UNIV OF SCI & TECH

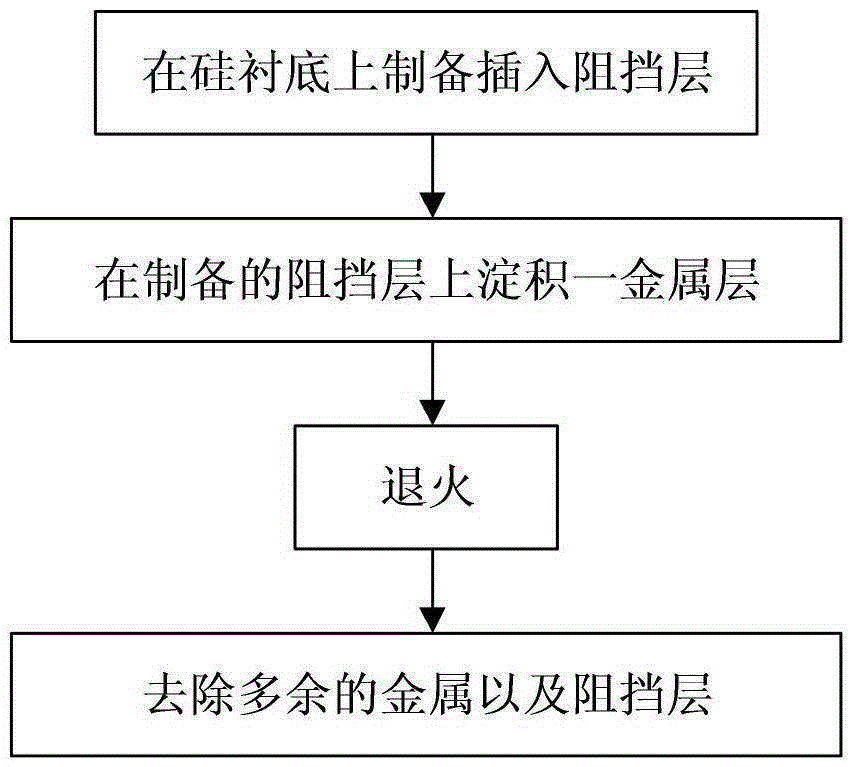

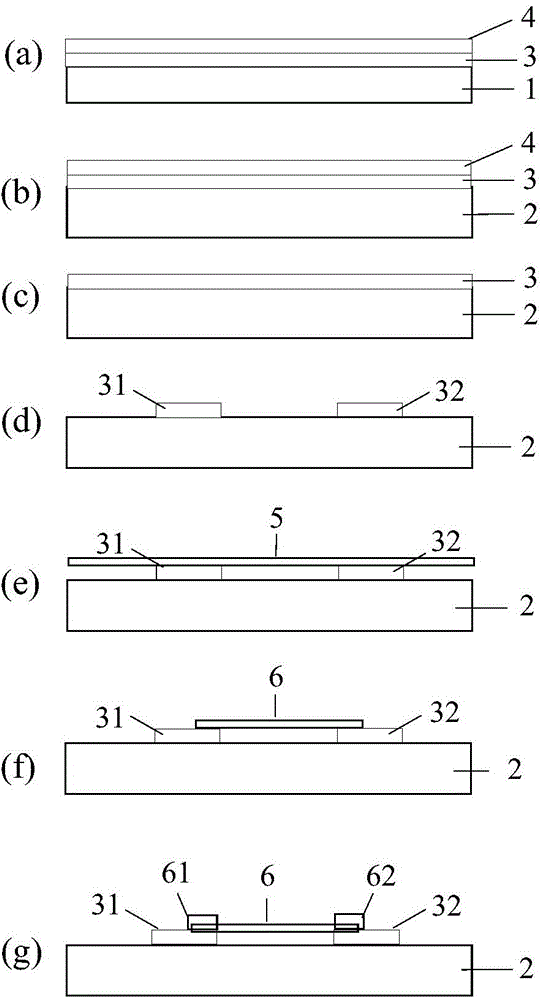

Method of preparing ultrathin silicide

InactiveCN106611704AMeet the requirements of the source and drain key processStrong process controllabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierDeposition process

The invention discloses a method of preparing an ultrathin silicide. The method comprises the following steps: (1) preparing an insertion stop layer on a silicon substrate; (2) preparing a metal layer on the stop layer; (3) annealing the structure obtained in step (2) to make metal in the metal layer diffuse across the insertion stop layer and react with silicon to form an ultrathin silicide; and (4) removing excess metal and the insertion stop layer to get an ultrathin silicide. Through the method, an ultrathin silicide less than 2nm can be prepared. The amount of metal driven in is controlled by changing the thickness of the insertion stop layer, so that silicides made of the same metal but of different phases and thicknesses can be obtained. The process is of high controllability. The formed ultrathin silicide has the characteristics of low resistivity, low Schottky barrier, good uniformity, and good smoothness. Compared with the conventional ultrathin silicide preparation method, the meal deposition process window is widened greatly. The method is completely compatible with a bulk silicon CMOS process. The process is simple and low in cost.

Owner:PEKING UNIV

Formation method of semiconductor device

ActiveCN106158611AIncrease speedImprove electrical performanceTransistorSemiconductor/solid-state device manufacturingSchottky barrierMetal silicide

The invention relates to a formation method of a semiconductor device, which comprises the steps of providing a substrate, wherein the surface of the substrate is provided with a gate structure; carrying out first doping processing on the substrate at both sides of the gate structure, and forming a doped region in the substrate at both sides of the gate structure; forming a metal silicide layer at the surface of the doped region; carrying out second doping processing on the metal silicide layer, wherein the second doping processing is suitable for reducing the Schottky barrier height between the metal silicide layer and the doped region; forming a zinc sulfide-silicon oxide layer at the surface of the top part of the gate structure; forming an interlayer dielectric layer on the metal silicide layer and at the surface of the zinc sulfide-silicon oxide layer; and carrying out annealing processing on the zinc sulfide-silicon oxide layer. The formation method is simple in process for forming the semiconductor device, the operation rate of the semiconductor device is effectively improved, and the electrical performance of the semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

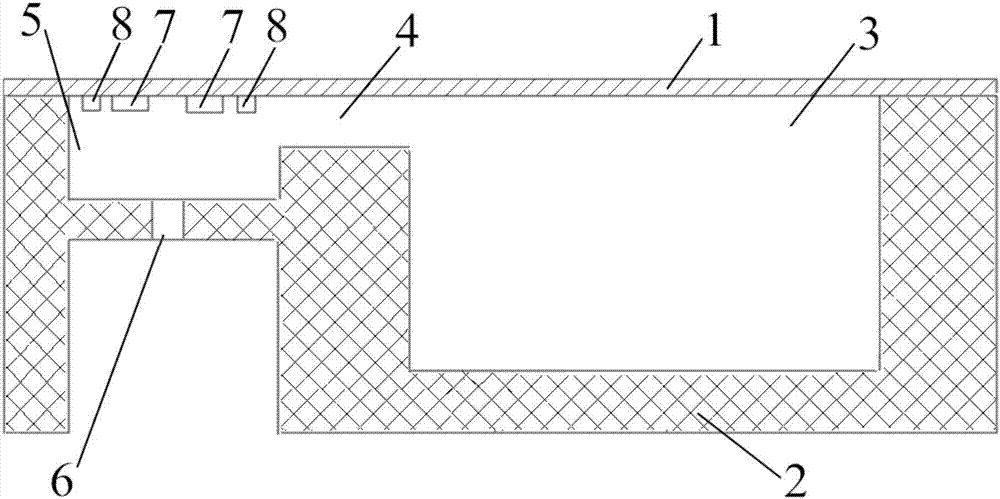

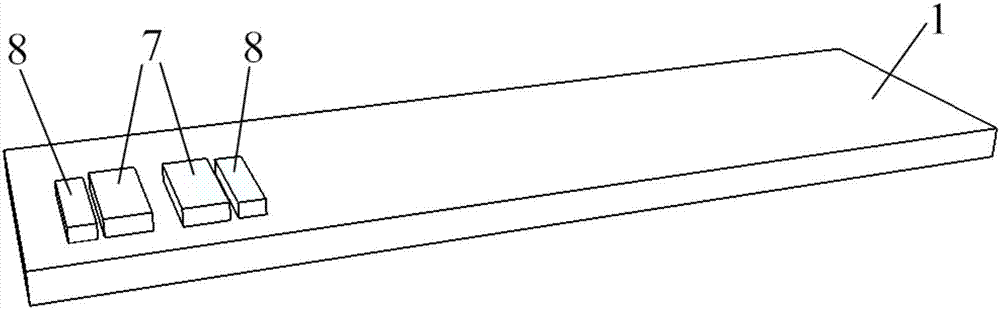

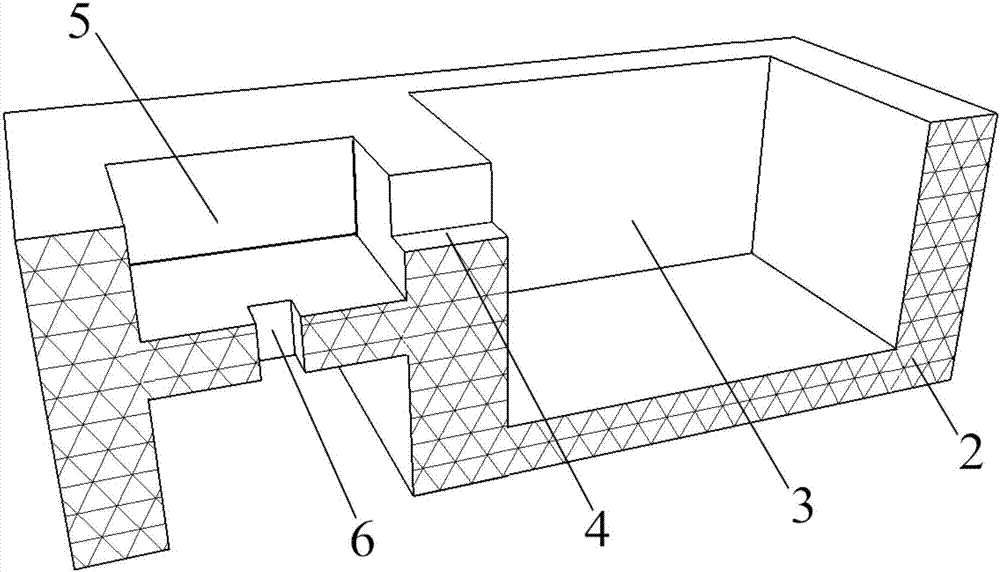

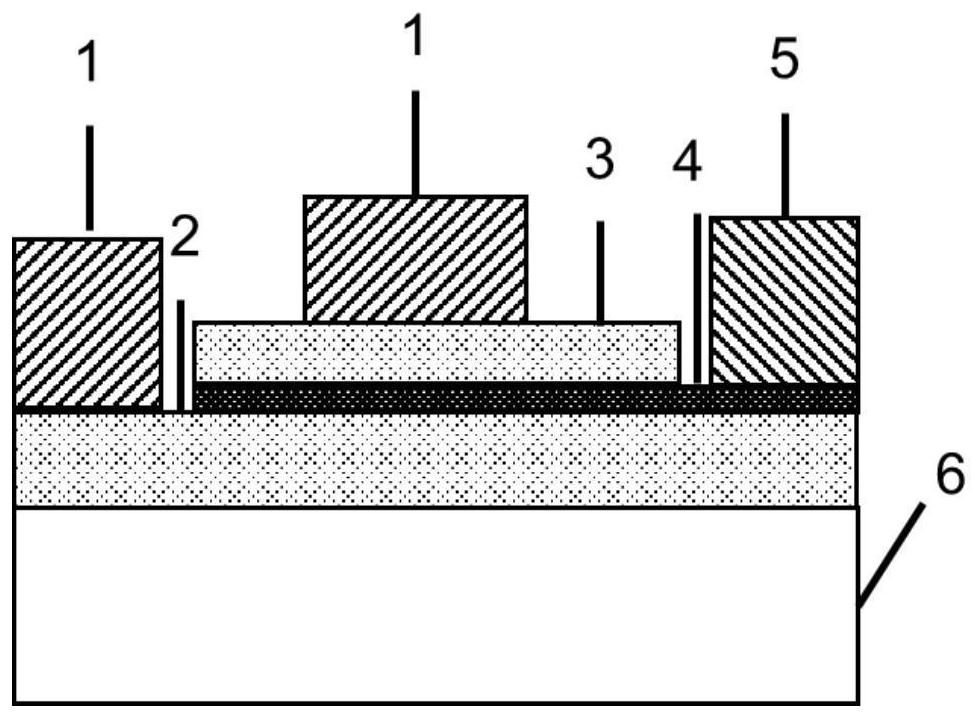

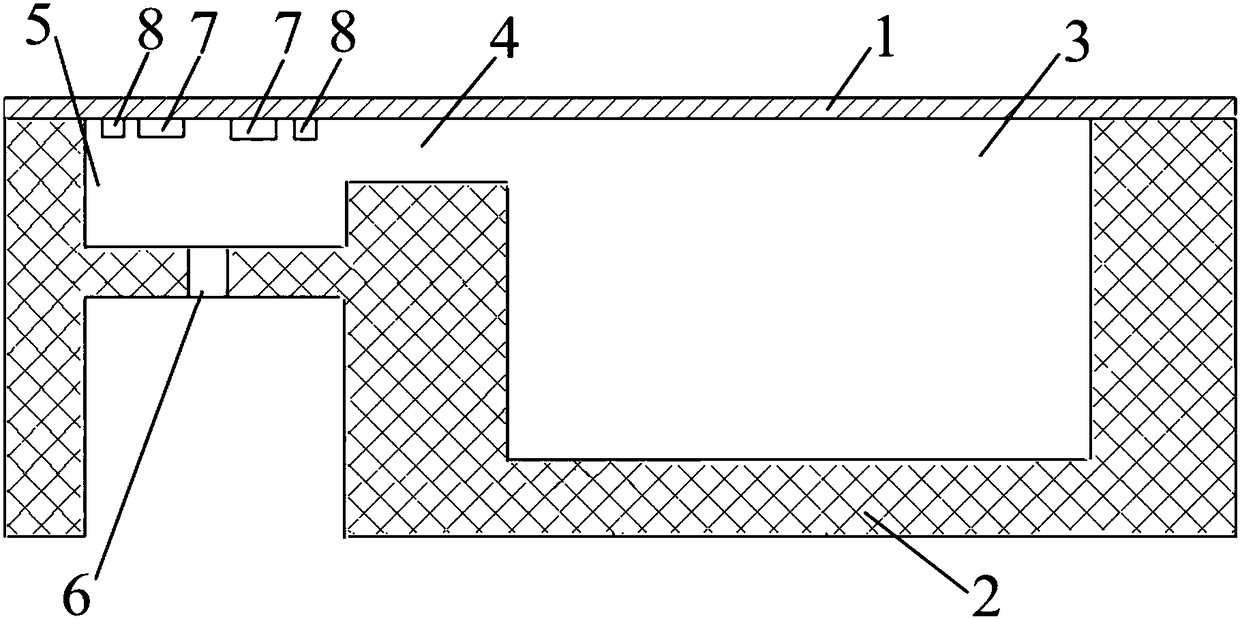

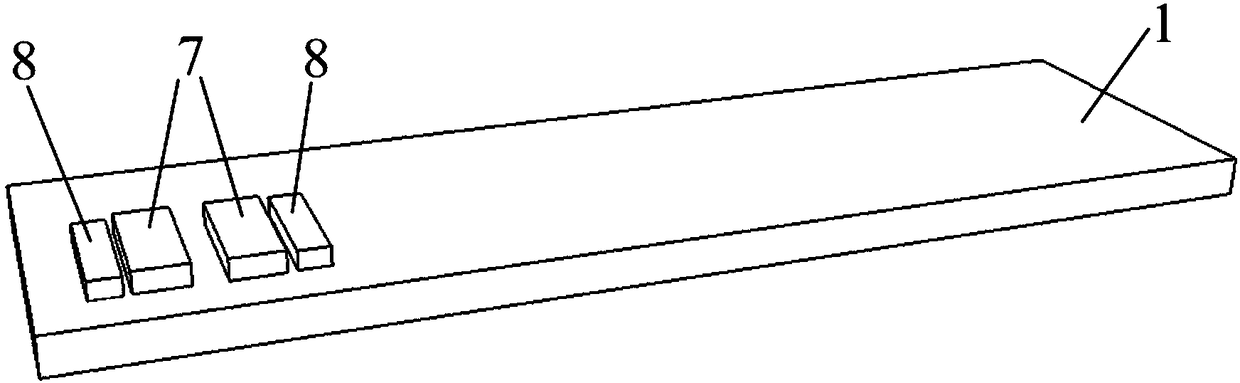

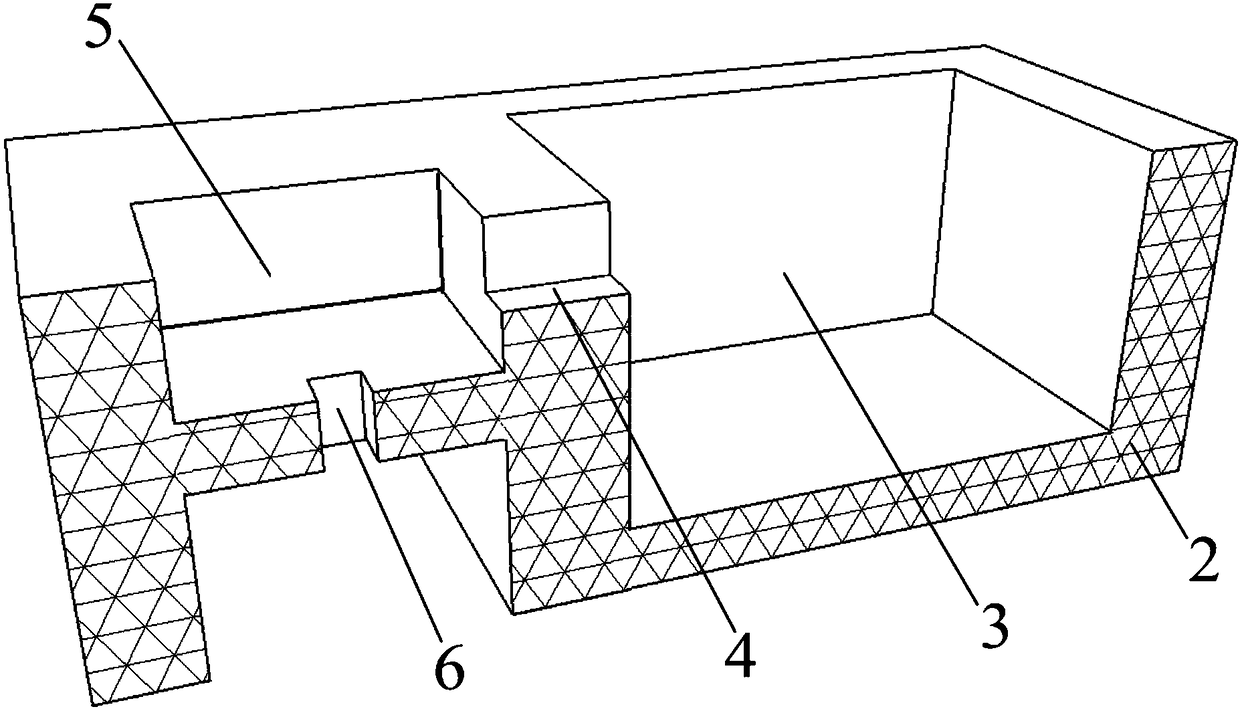

Thermal jet-printing head based on graphene-carbon nanotube composite structure, and preparation method thereof

The invention discloses a thermal jet-printing head based on a graphene-carbon nanotube composite structure, and a preparation method thereof. An ICP process and a surface smoothing process of filling deep grooves with PDMS are adopted, and a main channel, an ink jet chamber, an ink inlet channel, a nozzle and an ink jet channel are prepared in a silicon underlayer; and an anodic bonding process is adopted, graphene pieces are taken as a middle layer, and a glass substrate is bonded with the silicon underlayer. The main channel communicates with the ink jet chamber through the ink inlet channel, the depth of the ink inlet channel is less than the depth of the ink jet chamber; the nozzle is formed in the bottom of the ink jet chamber; and a microbubble generator array with a carbon nanotube-graphene composite structure and a carbon nanotube temperature sensor array are prepared in an area corresponding to the ink jet chamber, of the glass substrate, and arranged in a manner of facing the ink jet chamber. The jet head is reliable in liquid inlet closure, high in bonding strength, not liable to pollute a jet-printing chamber, and capable of easily controlling accuracy during preparation.

Owner:HUAZHONG UNIV OF SCI & TECH

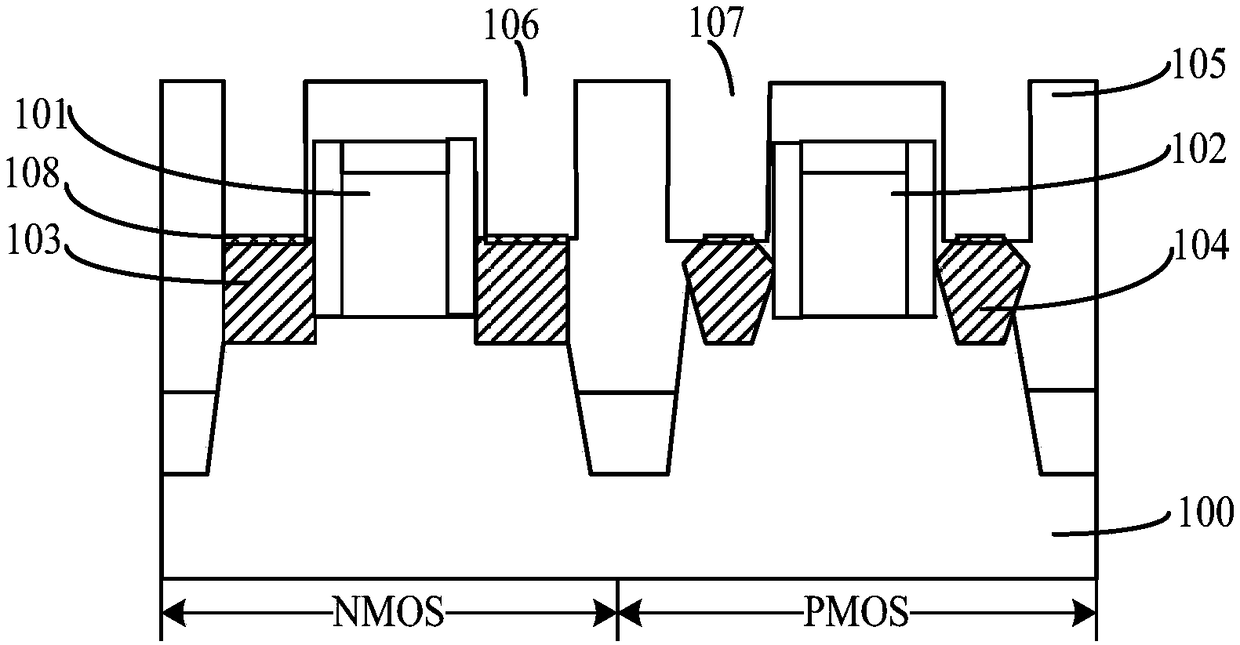

Transistor formation method

ActiveCN106158643ALower resistanceIncrease currentSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowMetal silicide

The invention provides a transistor formation method, which comprises the following steps: providing a substrate; forming a gate structure on the surface of the substrate; forming an opening in the substrate at the two sides of the gate structure; forming a stress layer in the opening; forming a cover layer on the surface of the stress layer, wherein the cover layer is doped by oxygen family element ions; and through metal silicification process, converting the cover layer into an electric contact layer, wherein the electric contact layer is made of metal silicide doped by oxygen family element ions. According to the formed transistor, resistance of the surface of the stress layer is reduced, and working current of the transistor is improved, and performance thereof is stable.

Owner:SEMICON MFG INT (SHANGHAI) CORP

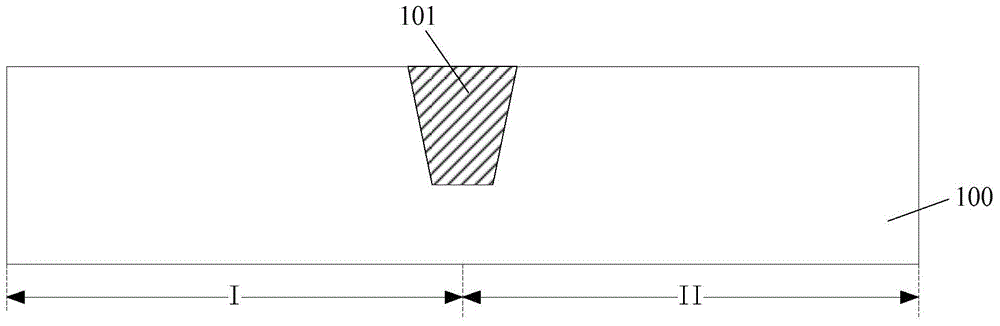

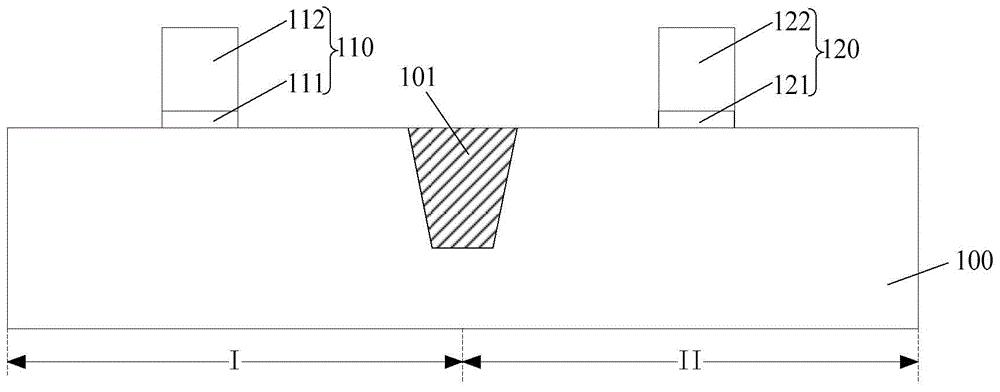

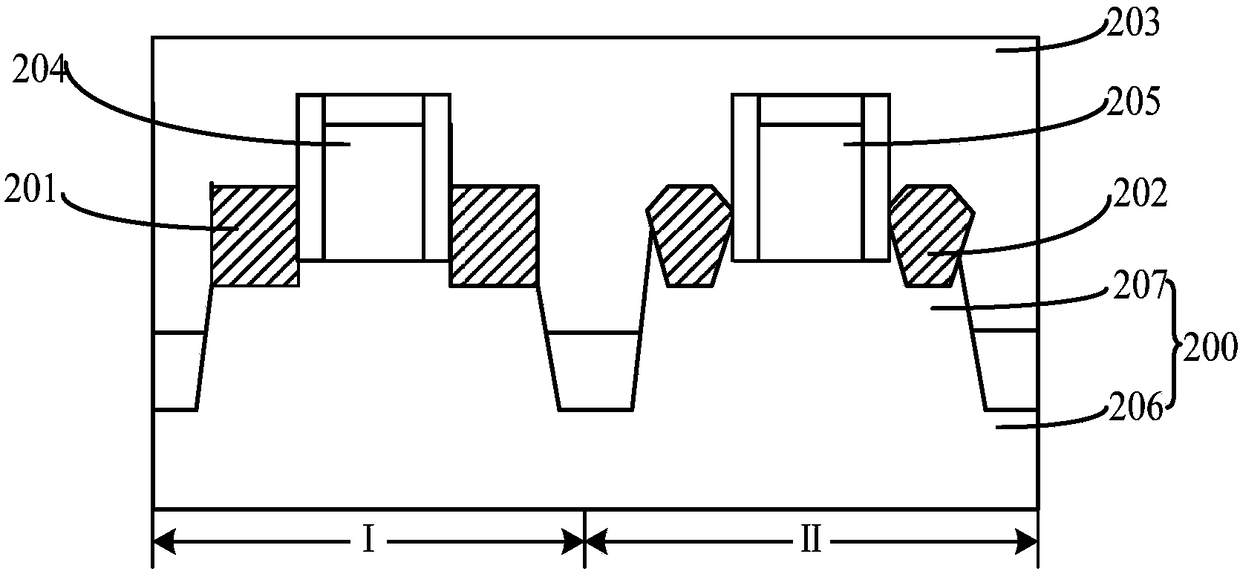

Semiconductor structure and method of forming same

InactiveCN108933107AIncrease contact areaReduce contact resistanceTransistorSolid-state devicesPhysicsMetal silicide

A semiconductor structure and a method of forming the same are disclosed. The method comprises the following steps: a substrate is provided; a source / drain doping region is arranged in the substrate;a dielectric layer is arranged on the substrate and the source / drain doping region; a part, positioned on the source / drain doping region, of the dielectric layer is removed so as to form a dielectricopening; a top part surface of the source / drain doping region is exposed at a bottom part of the dielectric opening; a part, positioned on a bottom part of the dielectric opening, of a source / drain doping region is removed; a source / drain opening is formed in the source / drain doping region; metal silicide layers are formed on a sidewall and a bottom part surface of the source / drain opening; the method can help reduce contact resistance of the semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

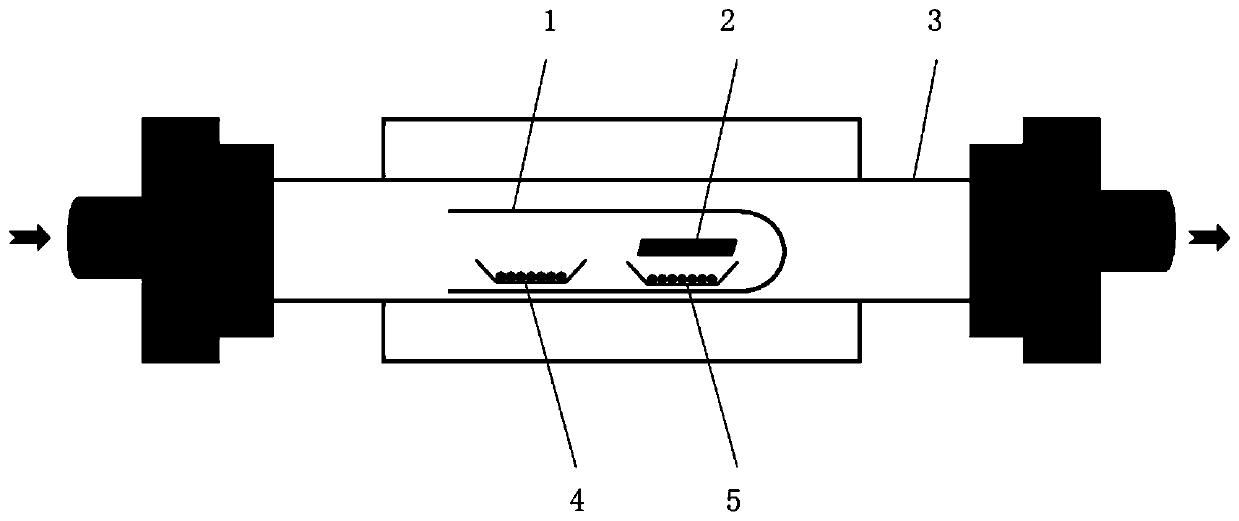

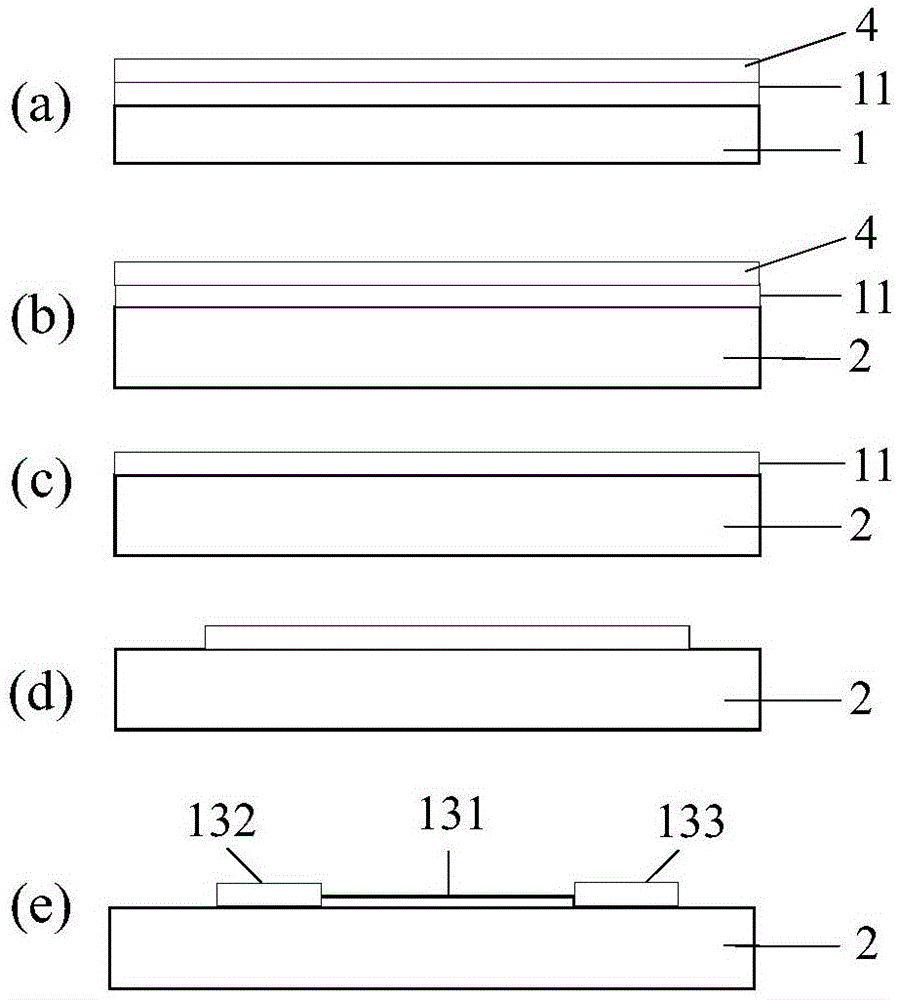

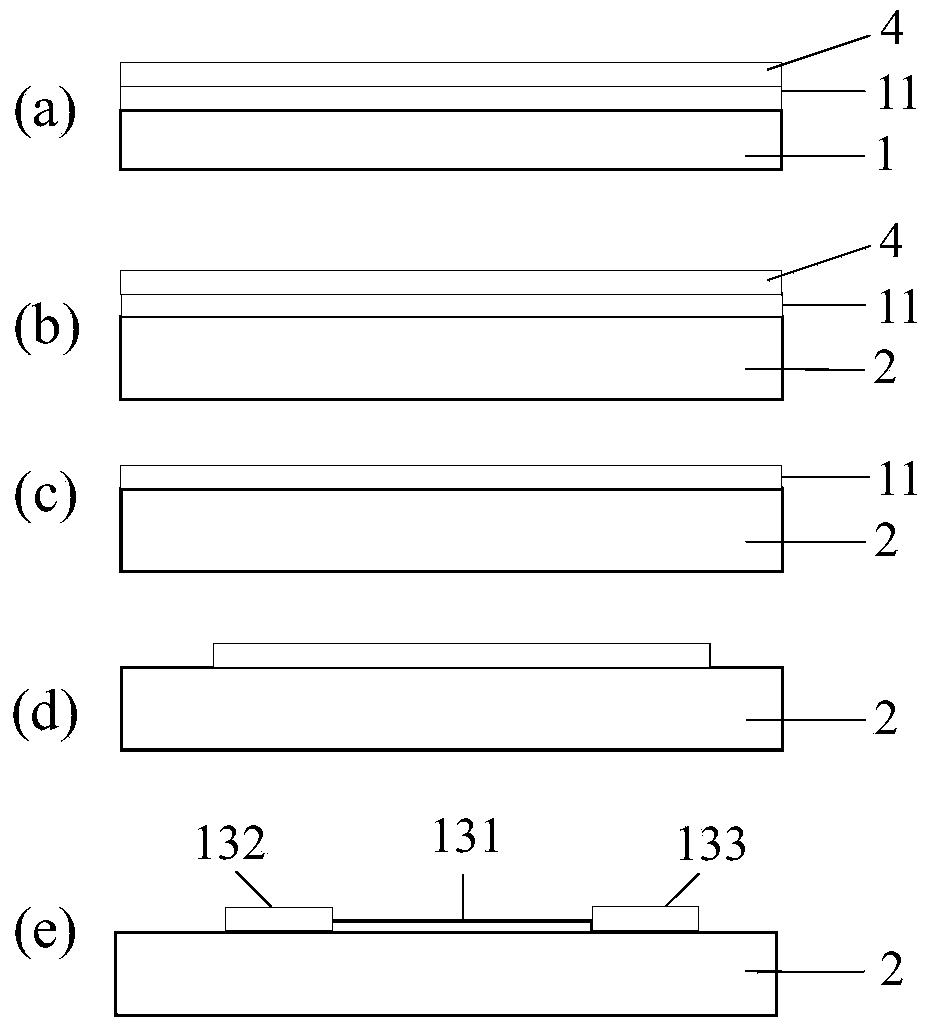

Microbubble generator and preparation method thereof

ActiveCN103769025BReduce usageReduce contact resistanceEnergy based chemical/physical/physico-chemical processesMetal foilCarbon nanotube

The invention discloses a microbubble generator and a preparation method thereof. The microbubble generator comprises a substrate, two electrodes and a carbon nano tube, wherein each of the two electrodes comprises graphene; the carbon nano tube is connected with the two electrodes through the graphene and is used as a heating component. The preparation method comprises the following steps of performing spin-coating on the surface of a metal foil, on which the graphene grows, with PMMA (polymethyl methacrylate); removing the metal foil, transferring the graphene protected by the PMMA to the substrate, and performing thermal treatment to enable the graphene to be tightly combined with the substrate; removing the PMMA; performing photoetching and reaction ion etching to obtain the two graphene electrodes; and covering the substrate with Cu2O nano particles serving as a catalyst, and with a hydrocarbon as a carbon source, growing a horizontal orientated carbon nano tube perpendicular to the graphene electrodes under the temperature of 800-950 DEG C through a low-pressure CVD (chemical vapor deposition) technology. The power consumption of the microbubble generator is reduced, and the service life of the microbubble generator is effectively prolonged; furthermore, the microbubble generator is simple in structure and flexible in design and has good high-frequency response and intensive integration potential.

Owner:HUAZHONG UNIV OF SCI & TECH

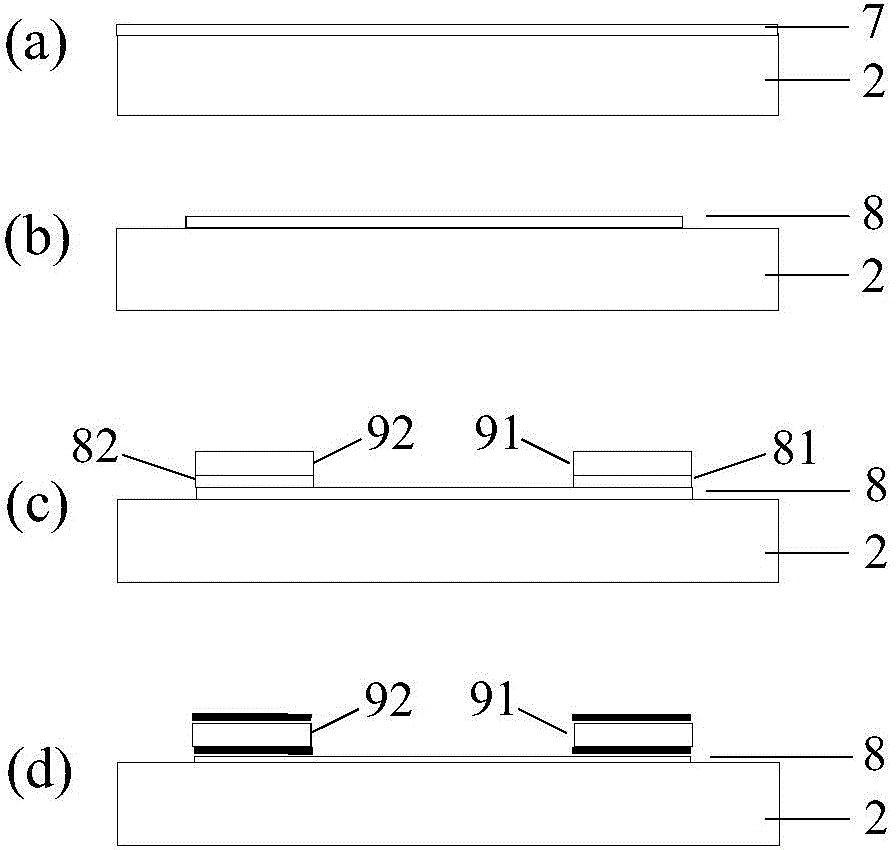

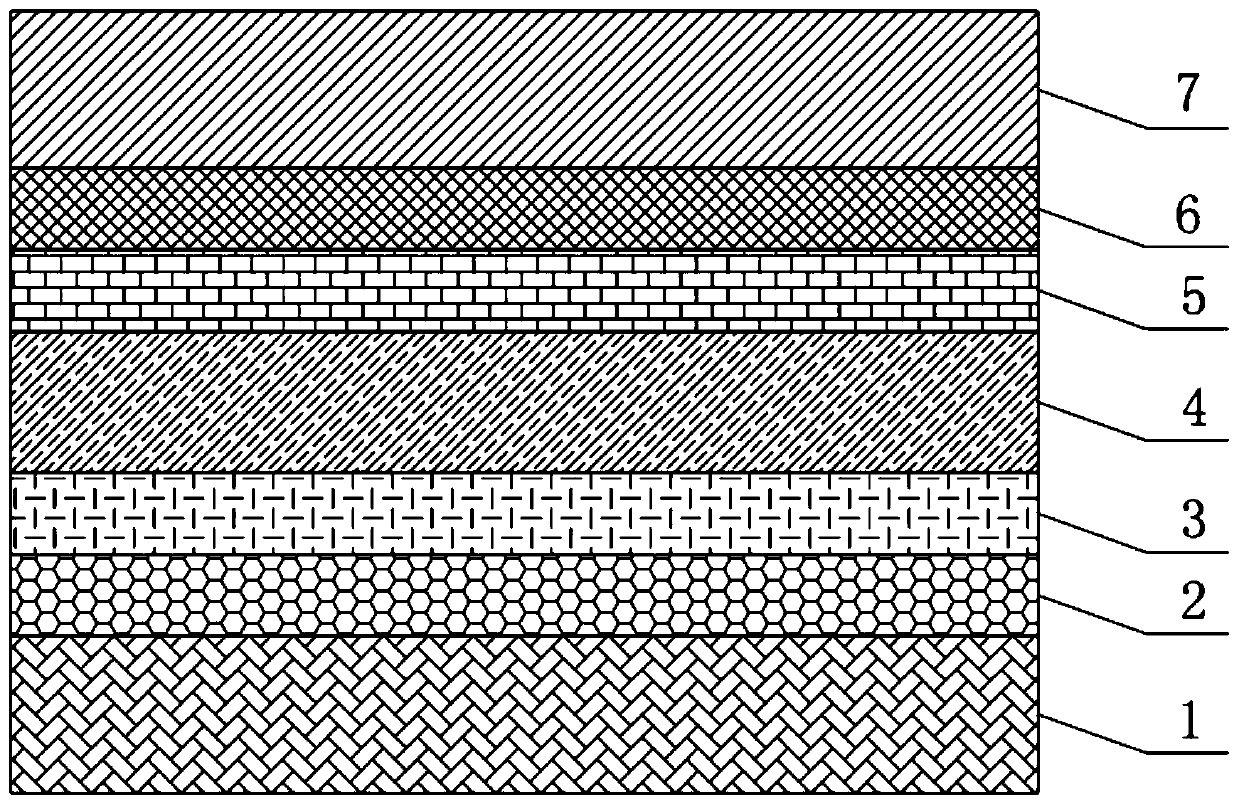

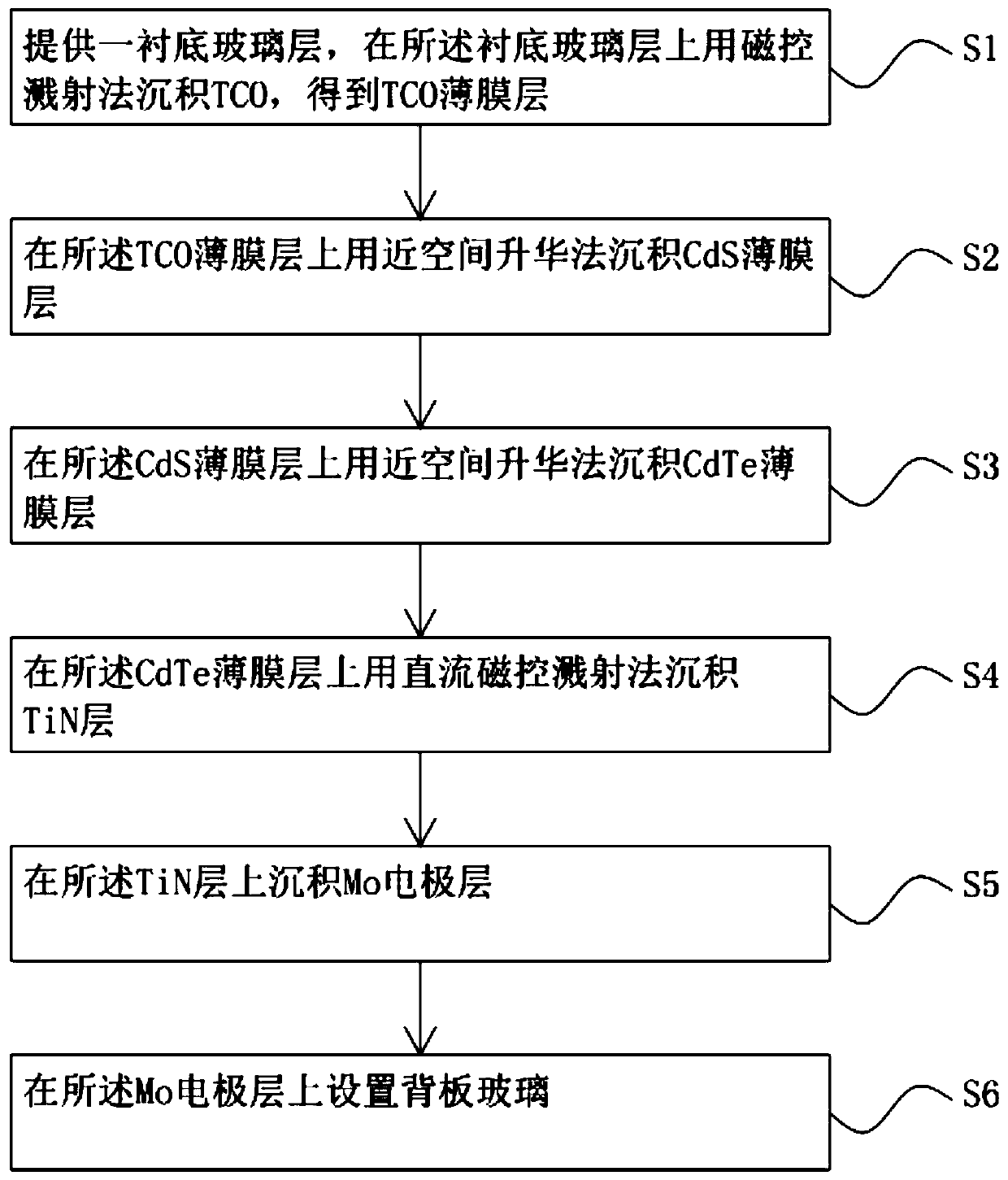

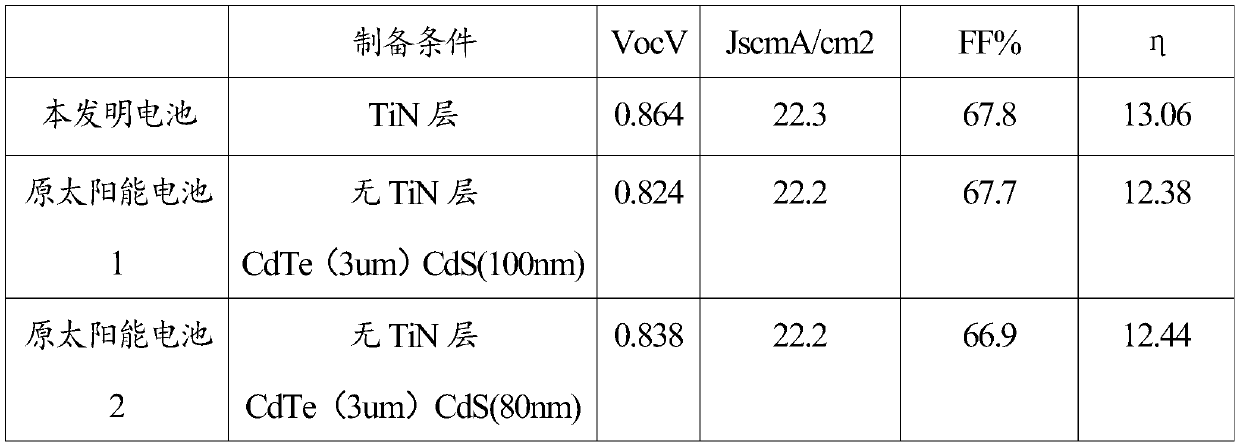

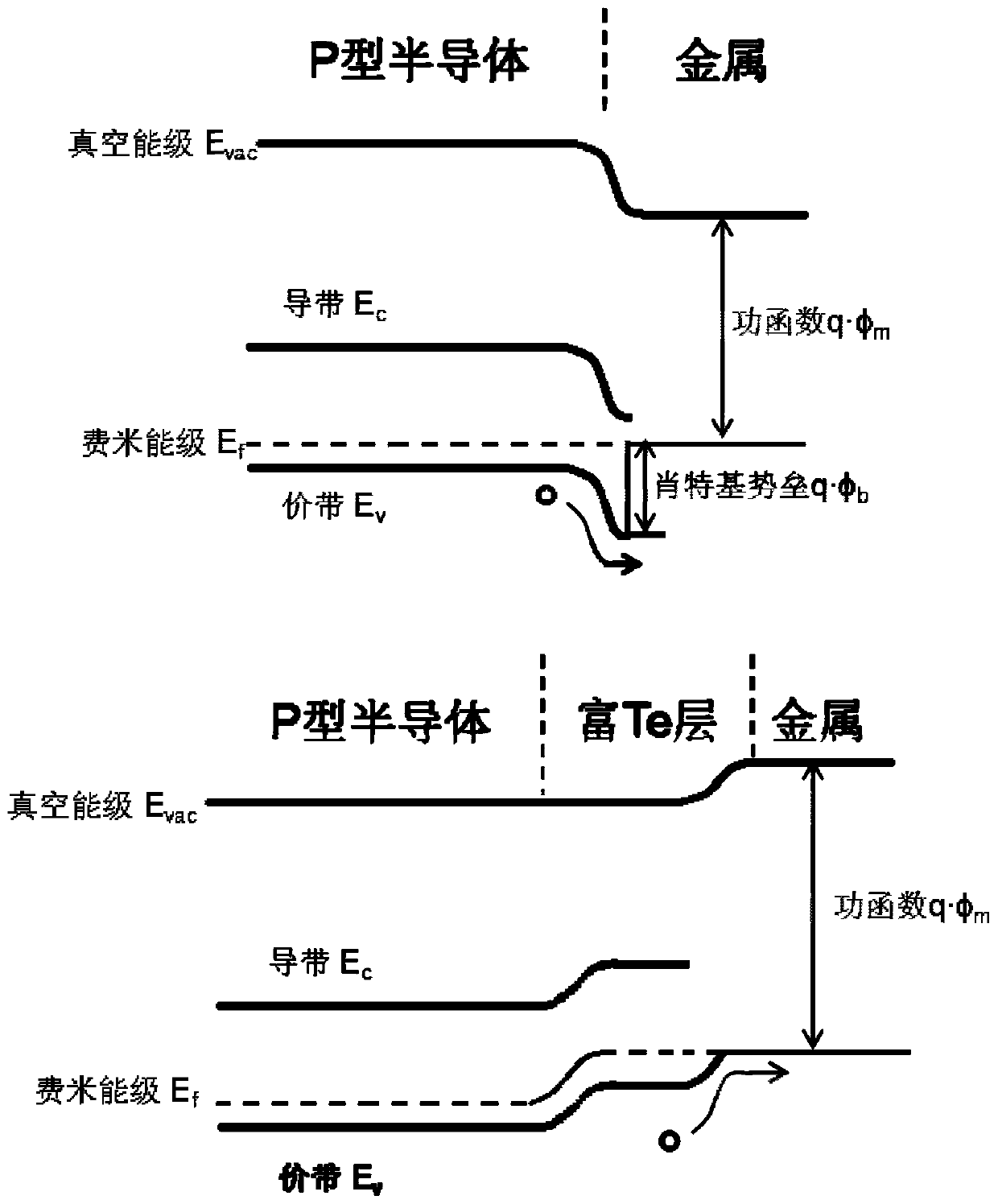

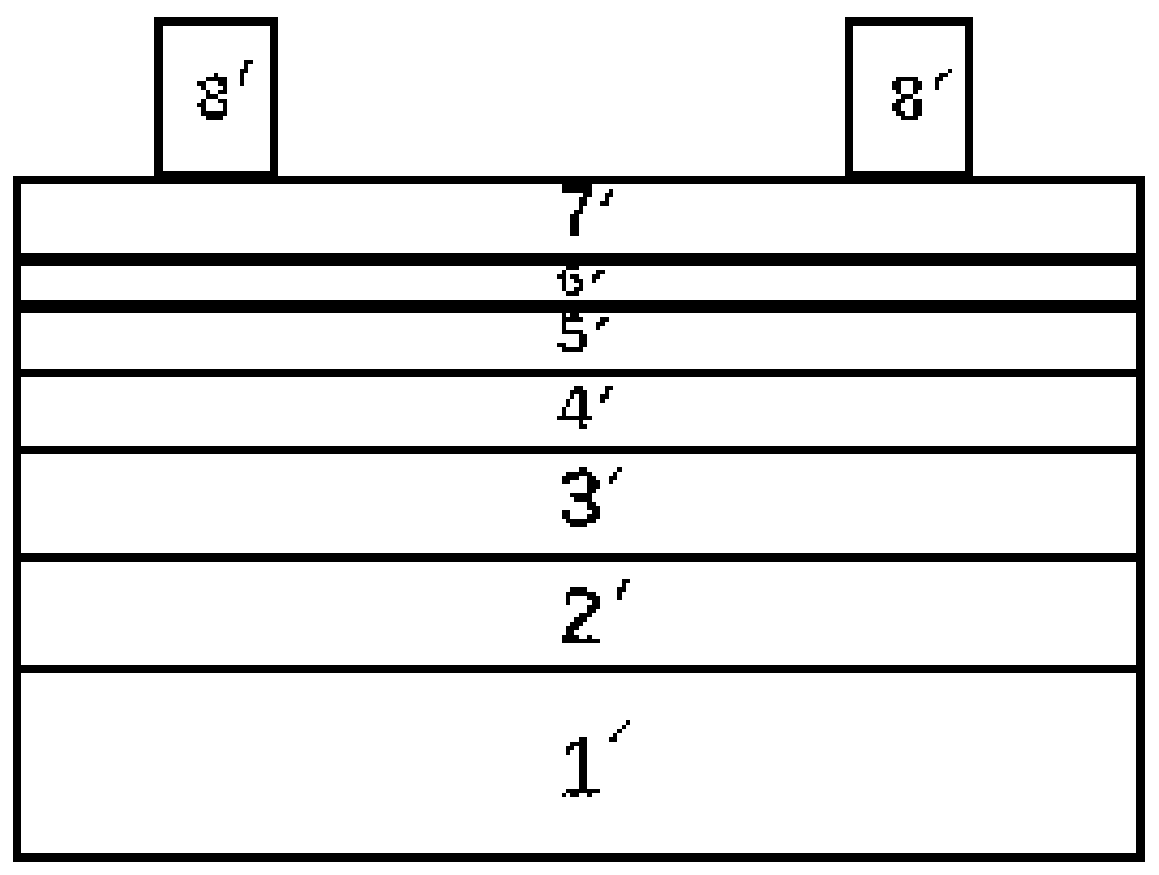

Cadmium telluride thin film solar cell module and preparation method thereof

ActiveCN109830561AImprove stabilityLower Schottky BarrierFinal product manufactureVacuum evaporation coatingSchottky barrierP–n junction

The invention discloses a cadmium telluride thin film solar cell module and a preparation method thereof. The cadmium telluride thin film solar cell module comprises a substrate glass layer, a TCO thin film layer, a CdS thin film layer, a CdTe thin film layer, a diffusion barrier layer, a Mo electrode layer, and a backplane glass layer which are arranged in order from bottom to top. The diffusionbarrier layer is a TiN layer. A TiN thin film is used as a back electrode buffer layer instead of Cu. Since the work function of the TiN is 4.7eV and the work function can be deepened by adjusting theratio of Ti to N, the Schottky barrier of the metal back electrode and the cadmium telluride thin film can be reduced, and the contact between the metal back electrode and the cadmium telluride thinfilm can be optimized. In addition, the TiN layer has good stability and has a stopping effect on Na diffusion in the glass, so that the diffusion of the alkali metal Na in the cadmium telluride thinfilm cell is controllable, and is different from the diffusion of doped copper which may diffuse to an interface between the cadmium telluride and the cadmium sulfide in a late stage, destroys a p-n junction characteristics, and greatly reduces efficiency, thereby prolonging a service life.

Owner:CNBM CHENGDU OPTOELECTRONICS MATERIAL

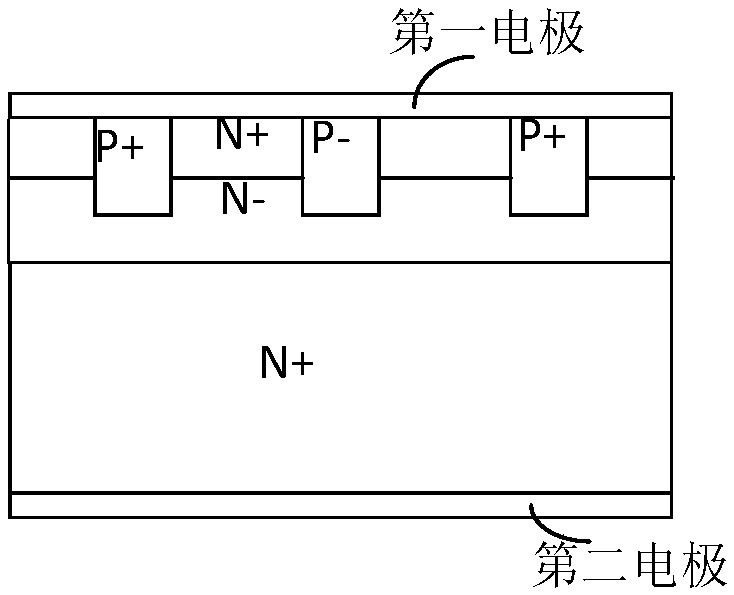

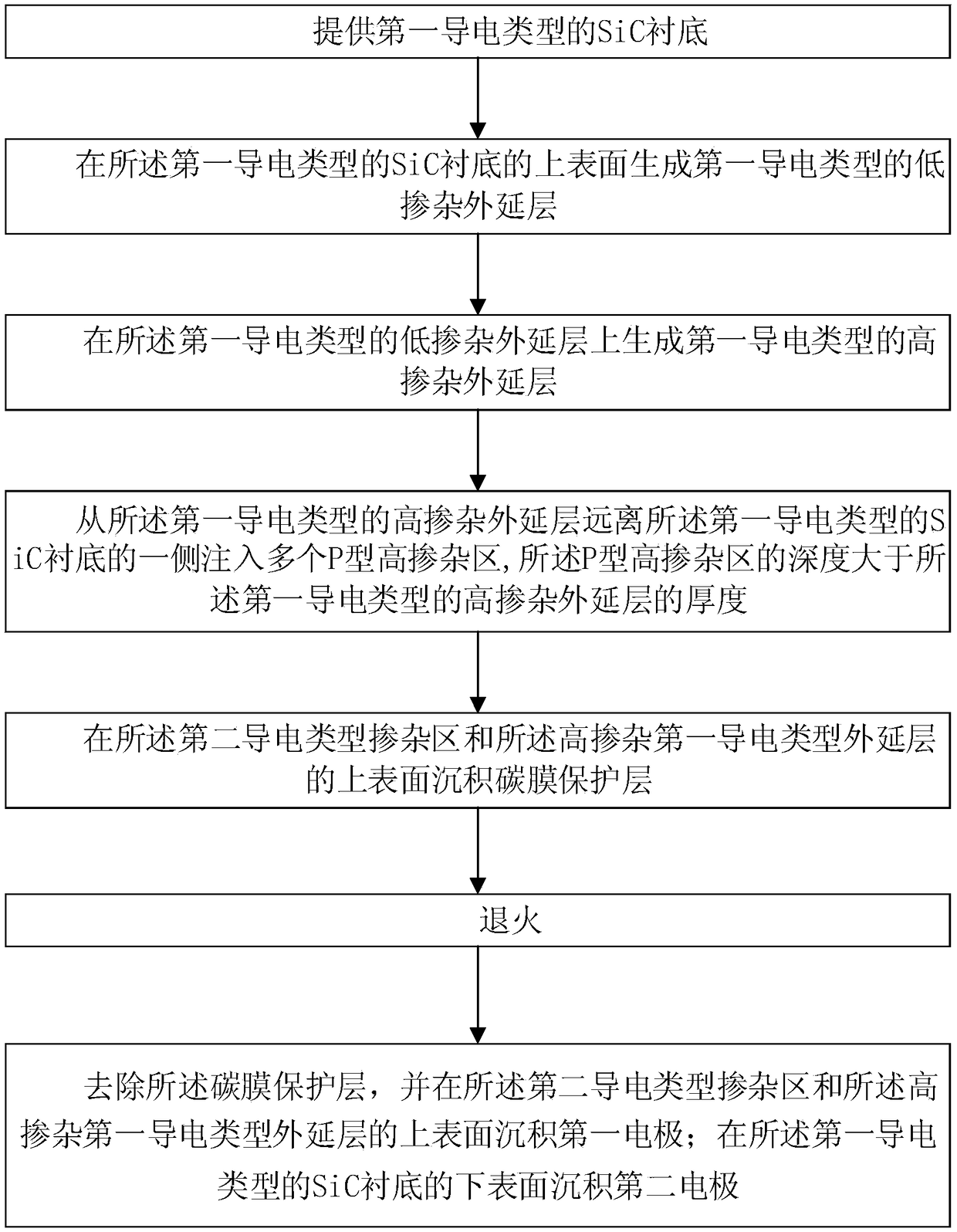

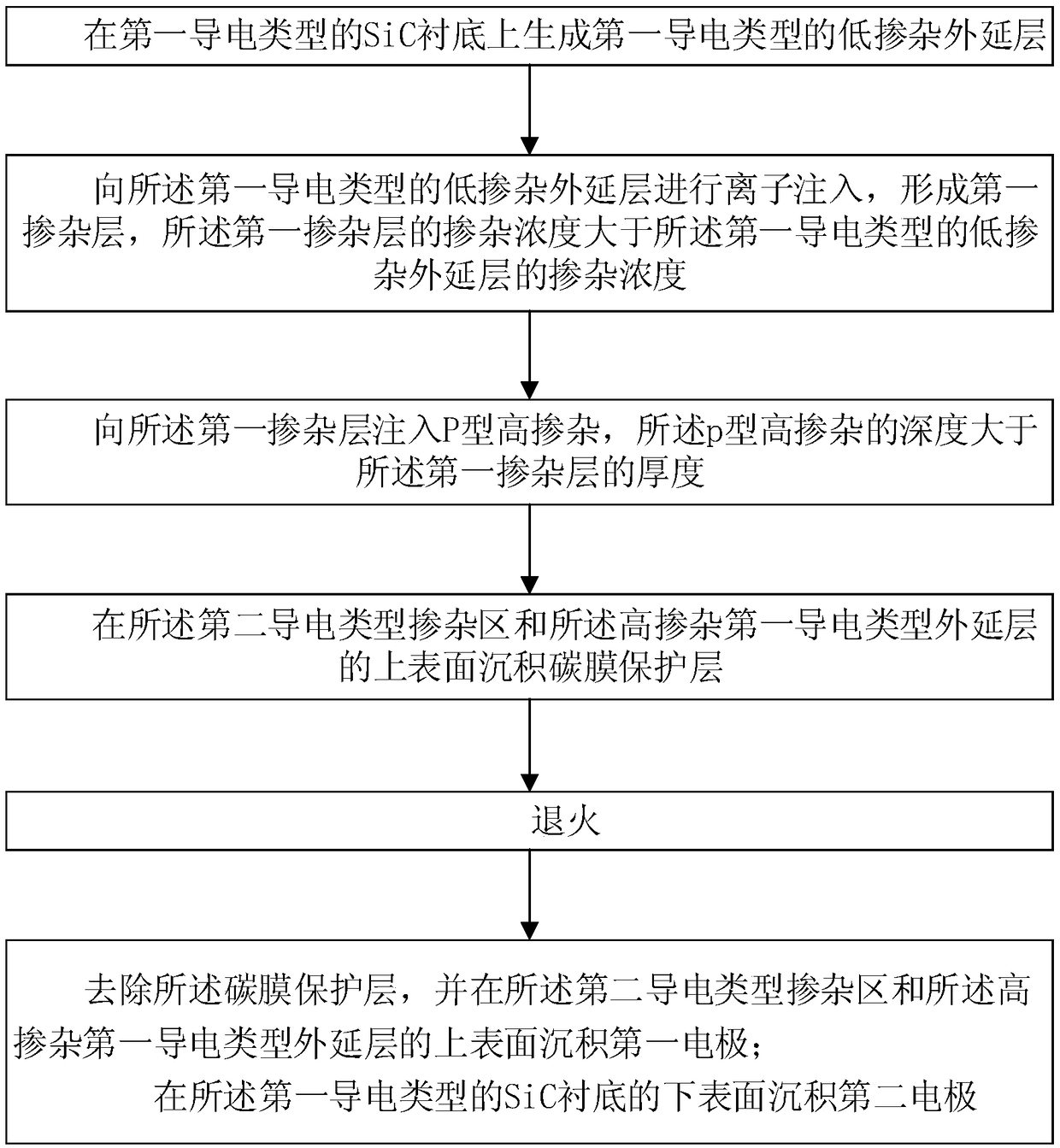

SiC knot barrier Schottky diode and manufacturing method thereof

InactiveCN109461768AAccurately change the effective barrier heightLower Schottky BarrierSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowSchottky diode

The invention relates to a SiC knot barrier Schottky diode and a manufacturing method thereof. The SiC knot barrier Schottky diode comprises a first conductive type SiC substrate layer, a low-doped first conductive type epitaxial layer, a high-doped first conductive type epitaxial layer, and multiple second conductive type doping areas; the depth of the second conductive type doping area is greater than the thickness of the high-doped first conductive type epitaxial layer, a first electrode and a second electrode. By adjusting the surface doping concentration, the barrier width is reduced, sothat the barrier of the diode is reduced, the effective barrier height of the contact of the metal-semiconductor is changed through different doping concentrations, the barrier width is reduced, and the electron with small free path can penetrate the barrier, the forward tunneling current is increased, the on-state resistance is equivalently reduced, and the diode breakover can be realized throughsmall voltage.

Owner:QINHUANGDAO JINGHE SCI & TECH RES INST CO LTD

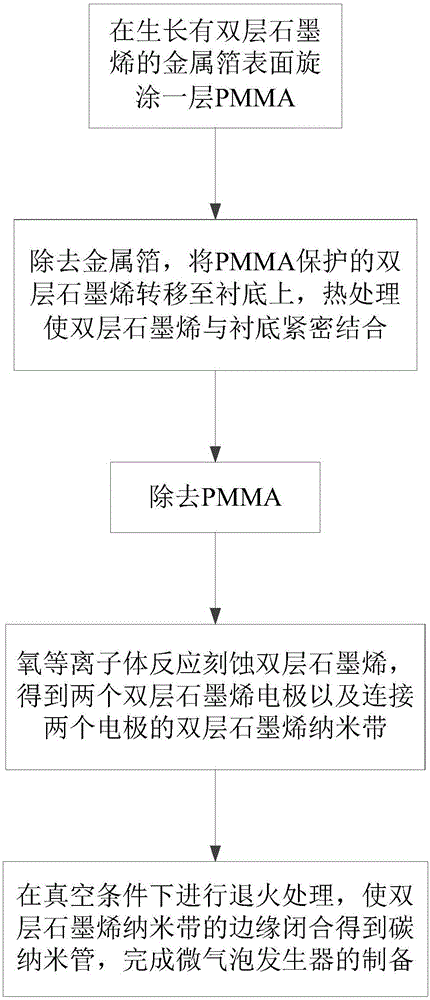

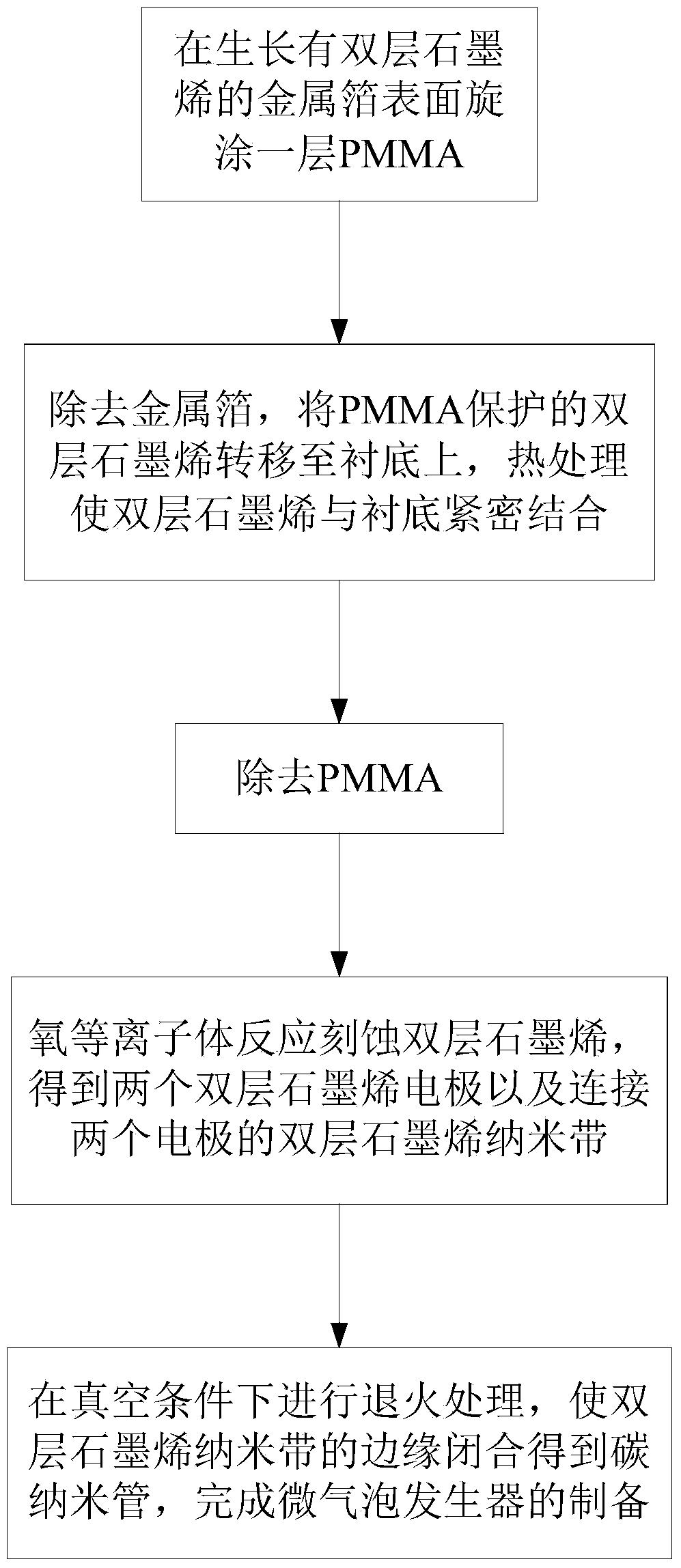

A kind of preparation method of microbubble generator

ActiveCN103832963BReduce usageReduce contact resistanceTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesMetal foilOxygen plasma

The invention discloses a micro-bubble generator and a manufacturing method of the micro-bubble generator. The micro-bubble generator comprises a substrate, two double-layer graphene electrodes and a carbon nano tube. The two double-layer graphene electrodes are located on the substrate, and the distance between the electrodes is 1-8 microns. The carbon nano tube is connected with the two double-layer graphene electrodes to serve as a heating assembly. The manufacturing method includes the following steps that a metal foil surface on which double-layer graphene grows is coated with PMMA in a spinning mode; metal foil is removed, the double-layer graphene protected by the PMMA is transferred to the substrate, and the double-layer graphene is tightly combined with the substrate through heat treatment; the PMMA is removed; an oxygen plasma reaction is performed to etch the double-layer graphene, and the two double-layer graphene electrodes and a double-layer graphene nano belt connecting the two electrodes are obtained; annealing is performed under the vacuum conditions, so that the edge of the double-layer graphene nano belt is closed to form the carbon nano tube, and the micro-bubble generator is manufactured. According to the micro-bubble generator and the manufacturing method of the micro-bubble generator, power consumption of the micro-bubble generator is reduced, the service life of the micro-bubble generator is effectively prolonged, and the micro-bubble generator is simple in structure and flexible in design.

Owner:HUAZHONG UNIV OF SCI & TECH

Two-dimensional Van der Waals bipolar transistor based on tellurium nanosheets and construction method thereof

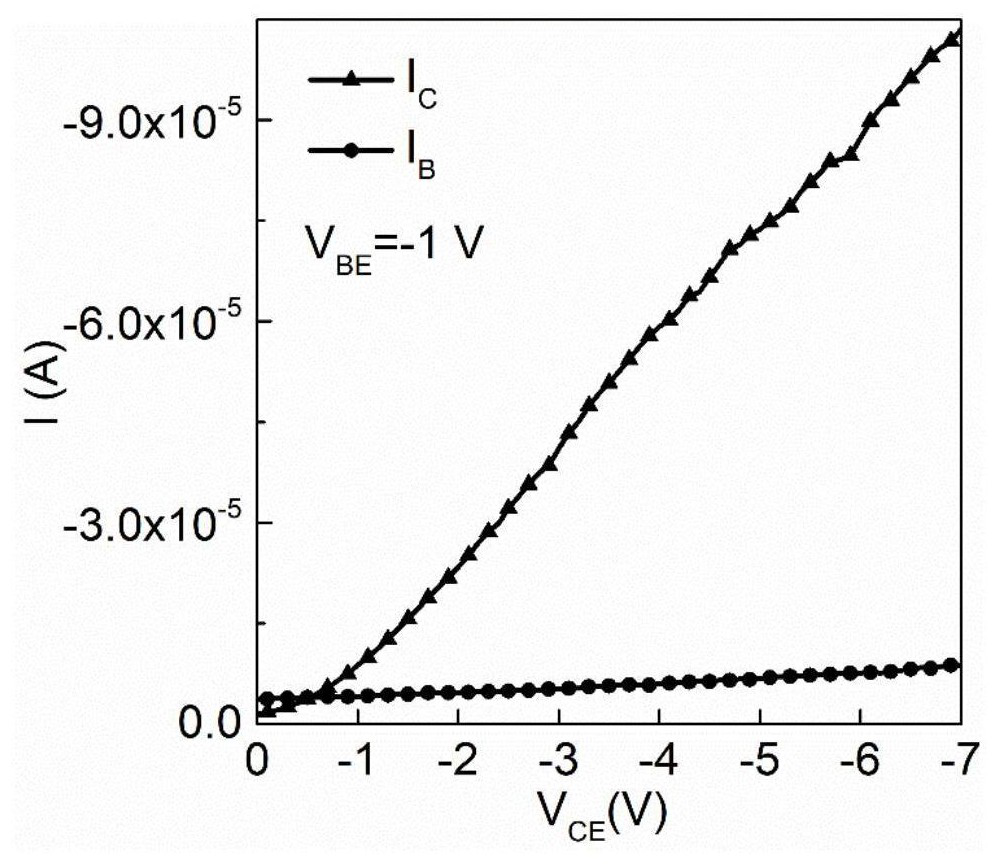

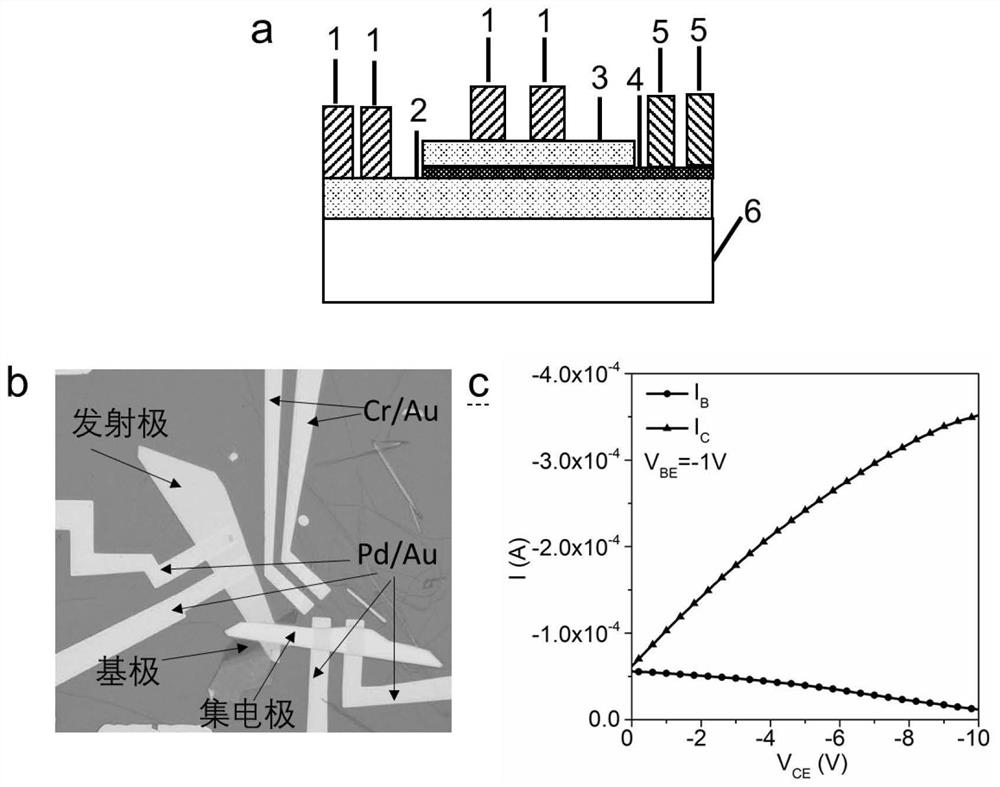

ActiveCN113130637AStrong thickness dependenceFulfil requirementsTransistorSemiconductor/solid-state device manufacturingChemical physicsSchottky barrier

The invention discloses a two-dimensional Van der Waals bipolar transistor based on tellurium nanosheets and a construction method thereof, and belongs to the technical field of semiconductor materials. The two-dimensional Van der Waals bipolar transistor (BJTs) based on the tellurium nanosheets comprises two-dimensional p-type tellurium nanosheets with different thicknesses, a two-dimensional n-type semiconductor material, an electrode and a target substrate. The tellurium nanosheets with different thicknesses and the two-dimensional n-type semiconductor nanosheets are synthesized by adopting a hydrothermal method, the carrier concentration difference is regulated and controlled by changing the thicknesses of the tellurium nanosheets of a collector electrode and an emitter electrode, the tunneling potential barrier of carriers is regulated and controlled by changing the thickness of a two-dimensional n-type semiconductor of a base electrode, vertical lossless stacking of three layers of materials is achieved by means of PPC auxiliary transfer, a p-type semiconductor is designed to be in contact with high-work-function metal, and the n-type semiconductor is designed to be in contact with low-work-function metal, so that a Schottky barrier between the metal and the material is reduced, the performance of BJTs is effectively regulated and controlled, and a good current amplification function is achieved.

Owner:UNIV OF SCI & TECH BEIJING

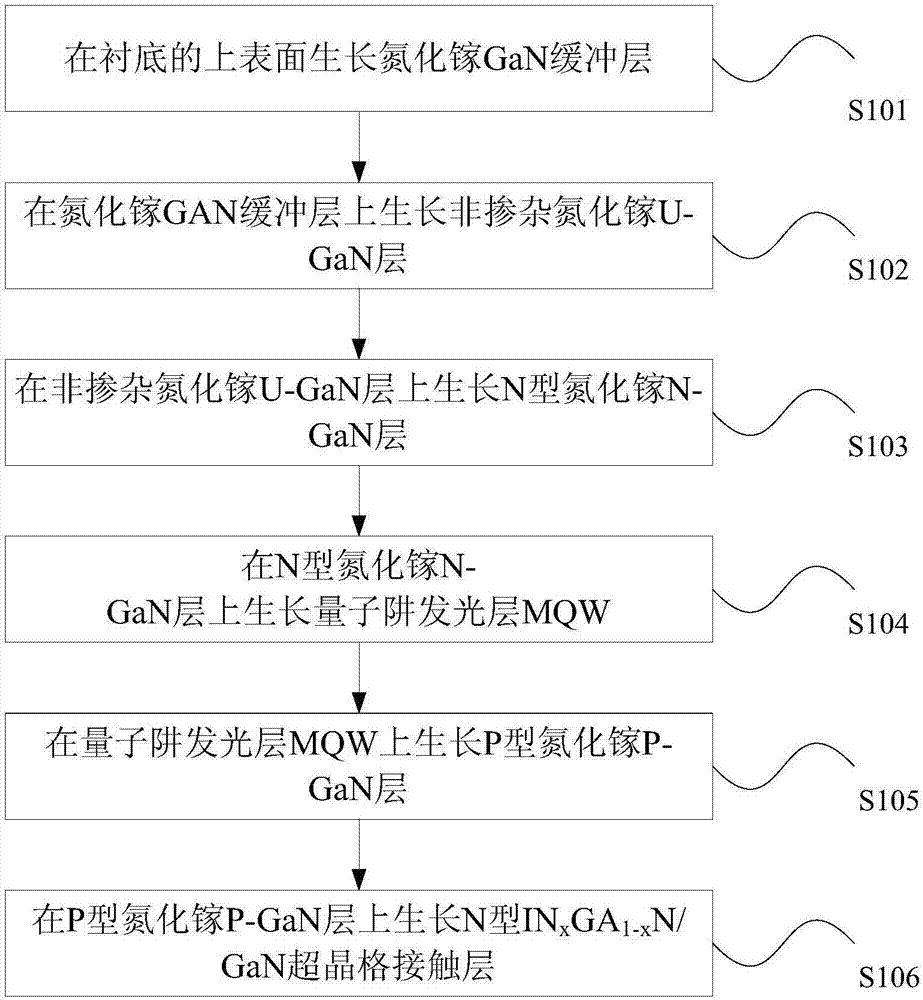

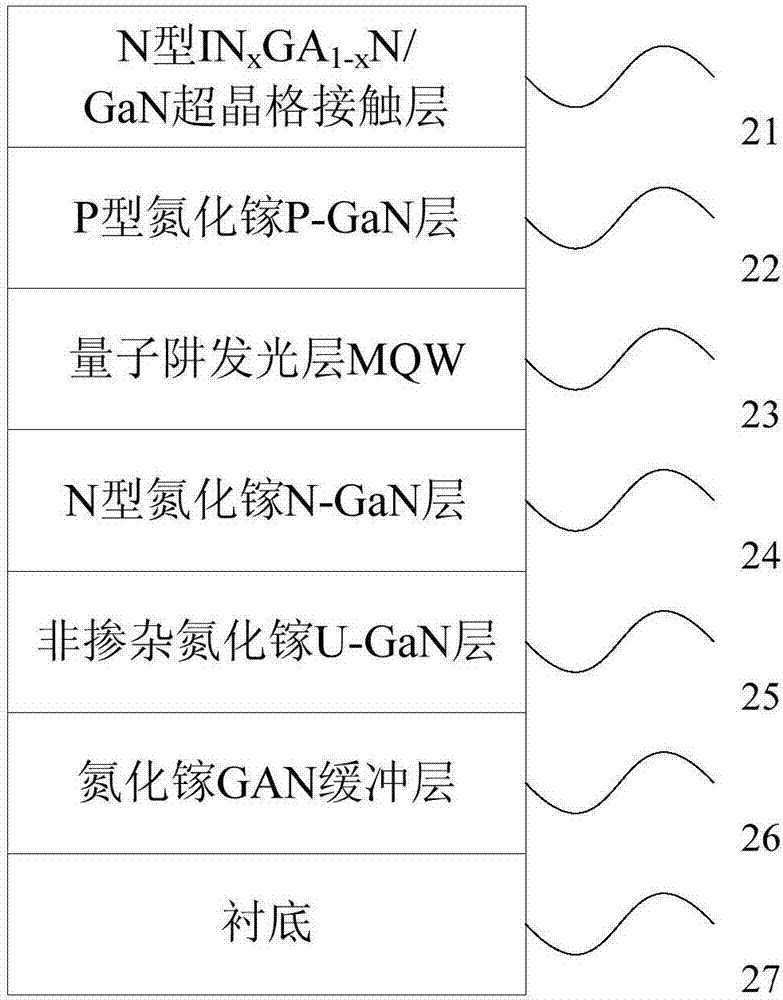

Growth method of N-type superlattice contact layer

InactiveCN106856217ALower Schottky BarrierLower junction temperatureSemiconductor devicesSchottky barrierQuantum well

The embodiment of the invention provides a growth method of an N-type superlattice contact layer. The growth method comprises the steps that a gallium nitride GaN buffer layer is grown on the upper surface of a substrate; an undoped gallium nitride U-GaN layer is grown on the gallium nitride GAN buffer layer; an N-type gallium nitride N-GaN layer is grown on the undoped gallium nitride U-GaN layer; a quantum well luminescent layer MQW is grown on the N-type gallium nitride N-GaN layer; a P-type gallium nitride P-GaN layer is grown on the quantum well luminescent layer MQW; and an N-type INxGA1-xN / GaN superlattice contact layer is grown on the P-type gallium nitride P-GaN layer, wherein x is greater than or equal to 0 and less than 1. The Schottky barrier between a metal electrode and an epitaxial wafer can be reduced by the unique electrical characteristics so that uniformity of current injection can be enhanced, the brightness can be enhanced, junction temperature between an electrode wire and the surface of the metal electrode can be reduced, and the probability of high current core granule breakdown can also be reduced.

Owner:EPITOP PHOTOELECTRIC TECH

How the transistor is formed

ActiveCN106158643BLower resistanceIncrease currentSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowMetal silicide

Owner:SEMICON MFG INT (SHANGHAI) CORP

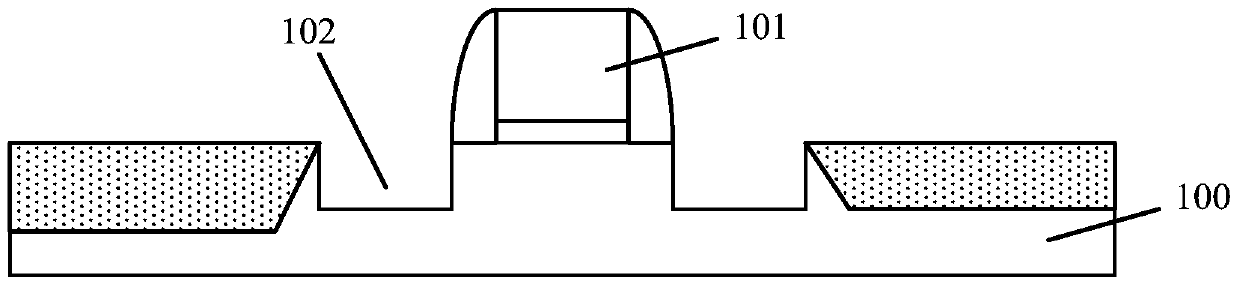

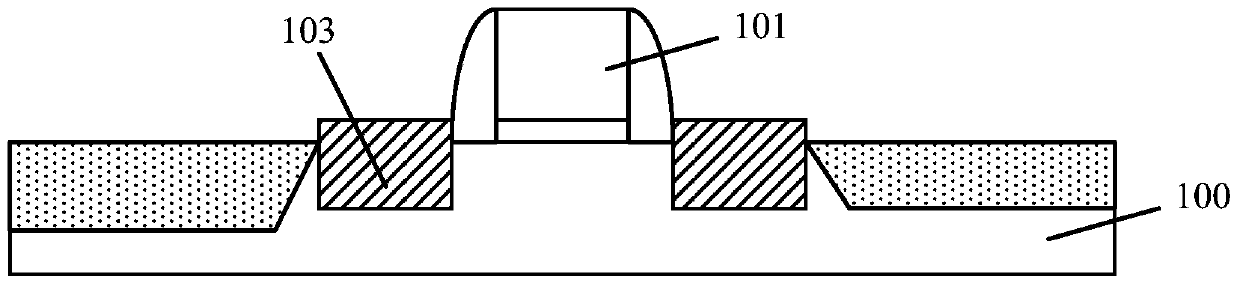

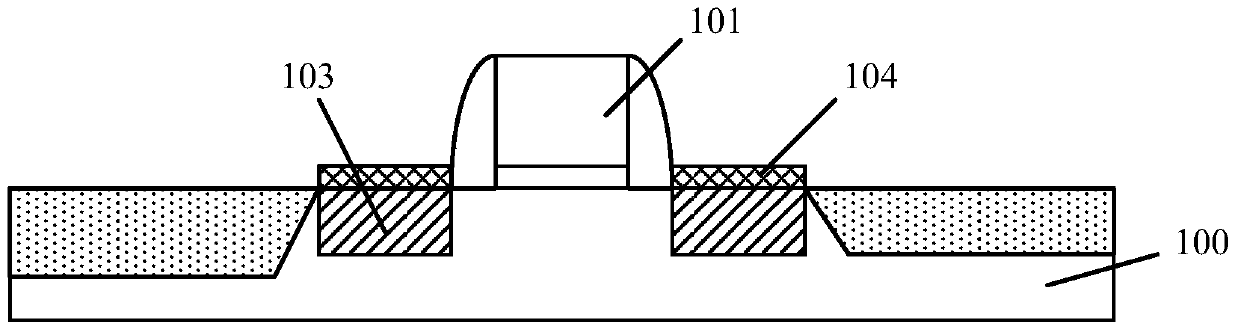

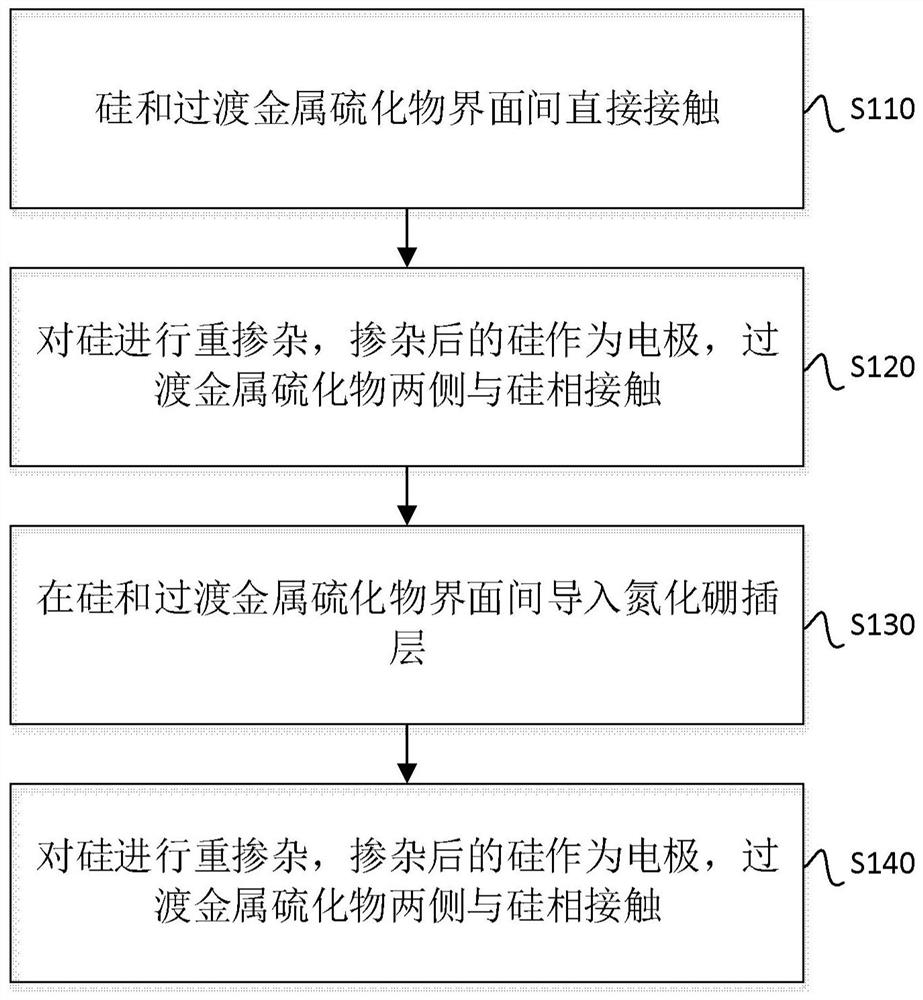

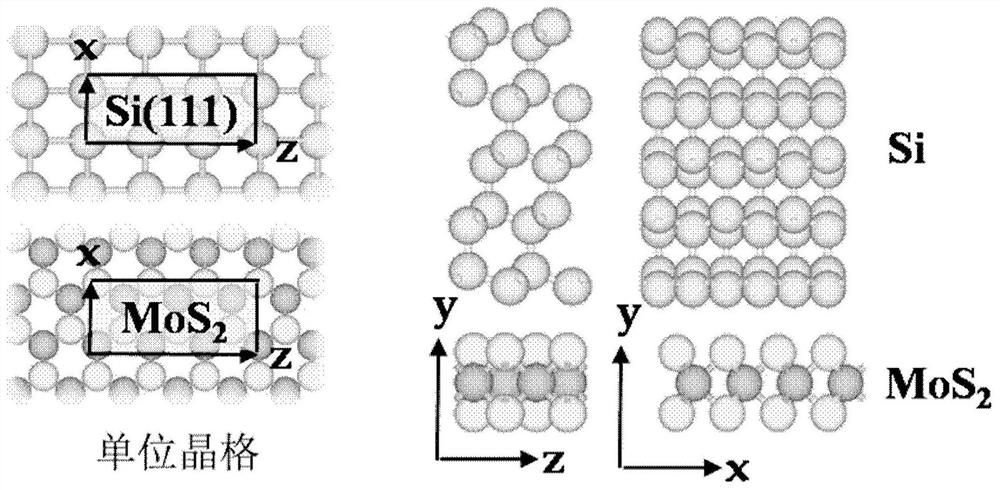

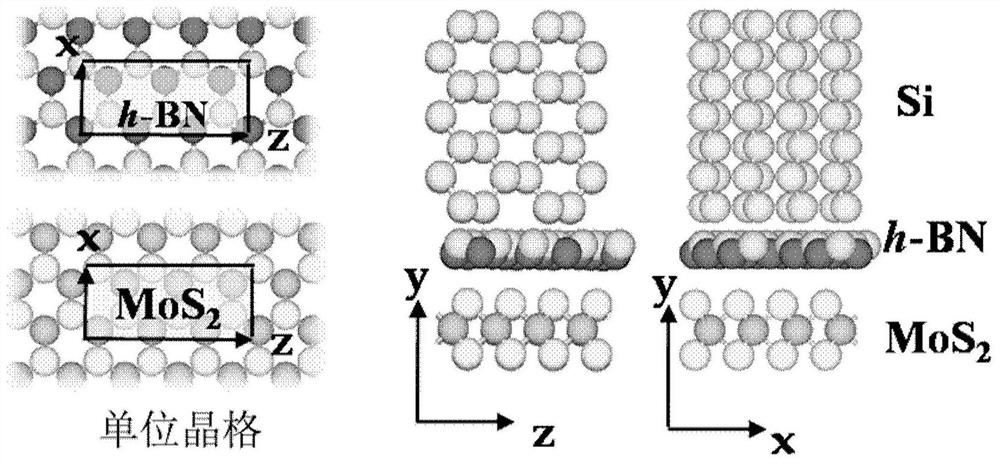

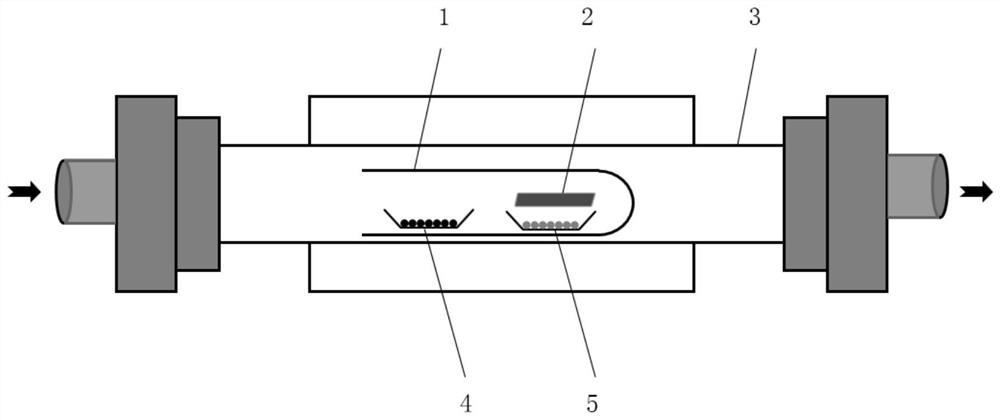

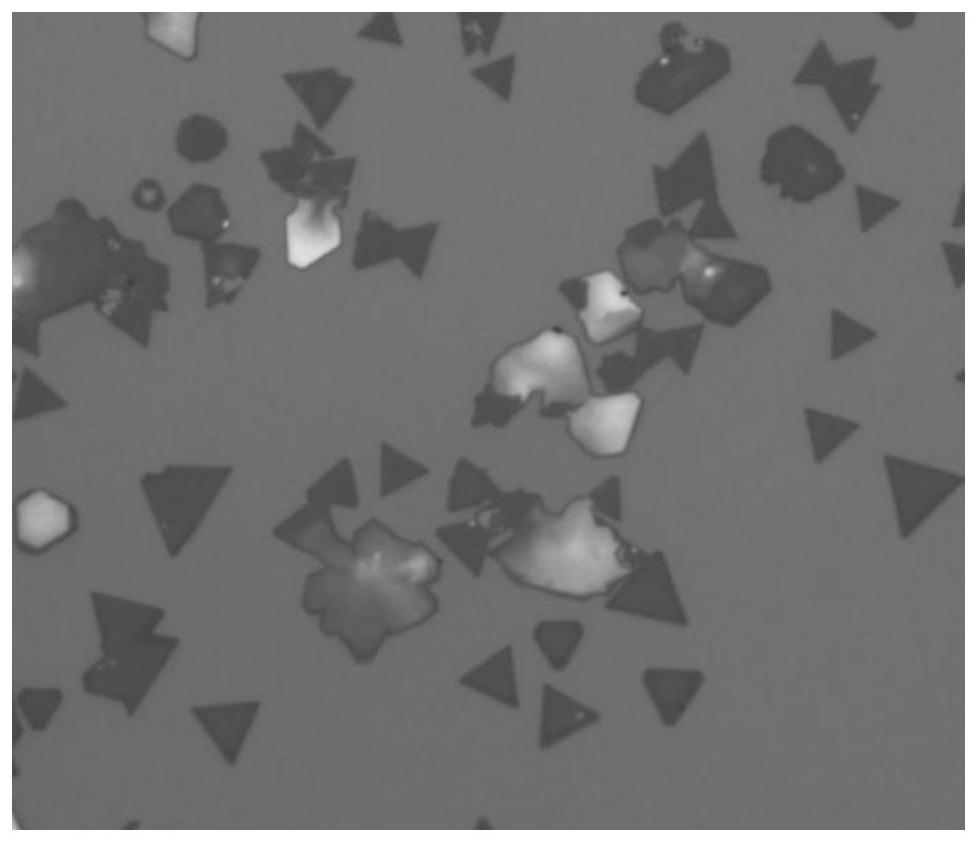

Schottky field effect transistor based on silicon and transition metal sulfide and preparation method

ActiveCN109904238BLower Schottky BarrierSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierField effect

The disclosure provides a Schottky field effect transistor based on silicon and transition metal sulfide and its preparation method, the interface treatment method includes: introducing boron nitride intercalation between the interface of silicon and transition metal sulfide, Si as electrode, MoS 2 As a channel material, a PIP type Schottky field effect transistor is formed. The present disclosure is beneficial in reducing Si-MoS 2 The Schottky barrier of the system has great guiding significance for the integration of two-dimensional materials into traditional silicon materials in future microelectronic devices.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI +1

A two-dimensional molybdenum ditelluride vertical heterojunction and its preparation method and application

ActiveCN111403475BIncrease contactLower Schottky BarrierSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSchottky barrier

The invention belongs to the field of two-dimensional materials, and specifically discloses a two-dimensional molybdenum ditelluride vertical heterojunction and its preparation method and application, which include 1T'‑MoTe 2 and 2H‑MoTe 2 Two parts, and the two parts are connected by interlayer van der Waals force; preparation steps: S1, after drying the mixed solution of ammonium tetramolybdate and sodium chloride, put it into the reactor as a molybdenum source, and place a growth substrate on the molybdenum source, Tellurium powder is put into the reactor as a tellurium source and placed upstream of the molybdenum source; S2 raises the temperature of the molybdenum source and the tellurium source to the reaction temperature and then cools down to room temperature naturally, and at the same time, feeds carrier gas into the reactor to release the tellurium The source is brought to the molybdenum source, and a reducing agent is passed through to form a two-dimensional molybdenum ditelluride vertical heterojunction on the growth substrate. Metal phase and semiconductor phase vertically stacked MoTe prepared by the present invention 2 The heterostructure can effectively reduce the Schottky barrier between metal electrodes and material contacts, and provides an important idea for improving metal-semiconductor contacts.

Owner:HUAZHONG UNIV OF SCI & TECH

Micro-bubble generator and manufacturing method thereof

ActiveCN103832963AReduce usageReduce contact resistanceTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesMetal foilOxygen plasma

The invention discloses a micro-bubble generator and a manufacturing method of the micro-bubble generator. The micro-bubble generator comprises a substrate, two double-layer graphene electrodes and a carbon nano tube. The two double-layer graphene electrodes are located on the substrate, and the distance between the electrodes is 1-8 microns. The carbon nano tube is connected with the two double-layer graphene electrodes to serve as a heating assembly. The manufacturing method includes the following steps that a metal foil surface on which double-layer graphene grows is coated with PMMA in a spinning mode; metal foil is removed, the double-layer graphene protected by the PMMA is transferred to the substrate, and the double-layer graphene is tightly combined with the substrate through heat treatment; the PMMA is removed; an oxygen plasma reaction is performed to etch the double-layer graphene, and the two double-layer graphene electrodes and a double-layer graphene nano belt connecting the two electrodes are obtained; annealing is performed under the vacuum conditions, so that the edge of the double-layer graphene nano belt is closed to form the carbon nano tube, and the micro-bubble generator is manufactured. According to the micro-bubble generator and the manufacturing method of the micro-bubble generator, power consumption of the micro-bubble generator is reduced, the service life of the micro-bubble generator is effectively prolonged, and the micro-bubble generator is simple in structure and flexible in design.

Owner:HUAZHONG UNIV OF SCI & TECH

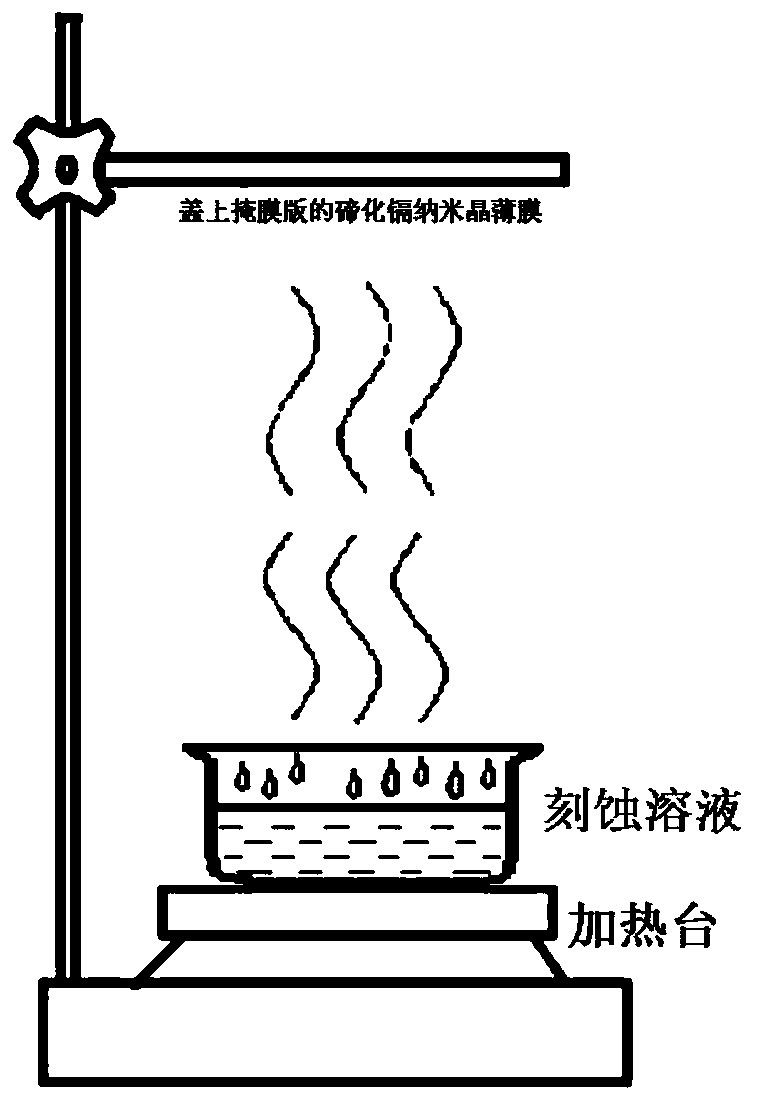

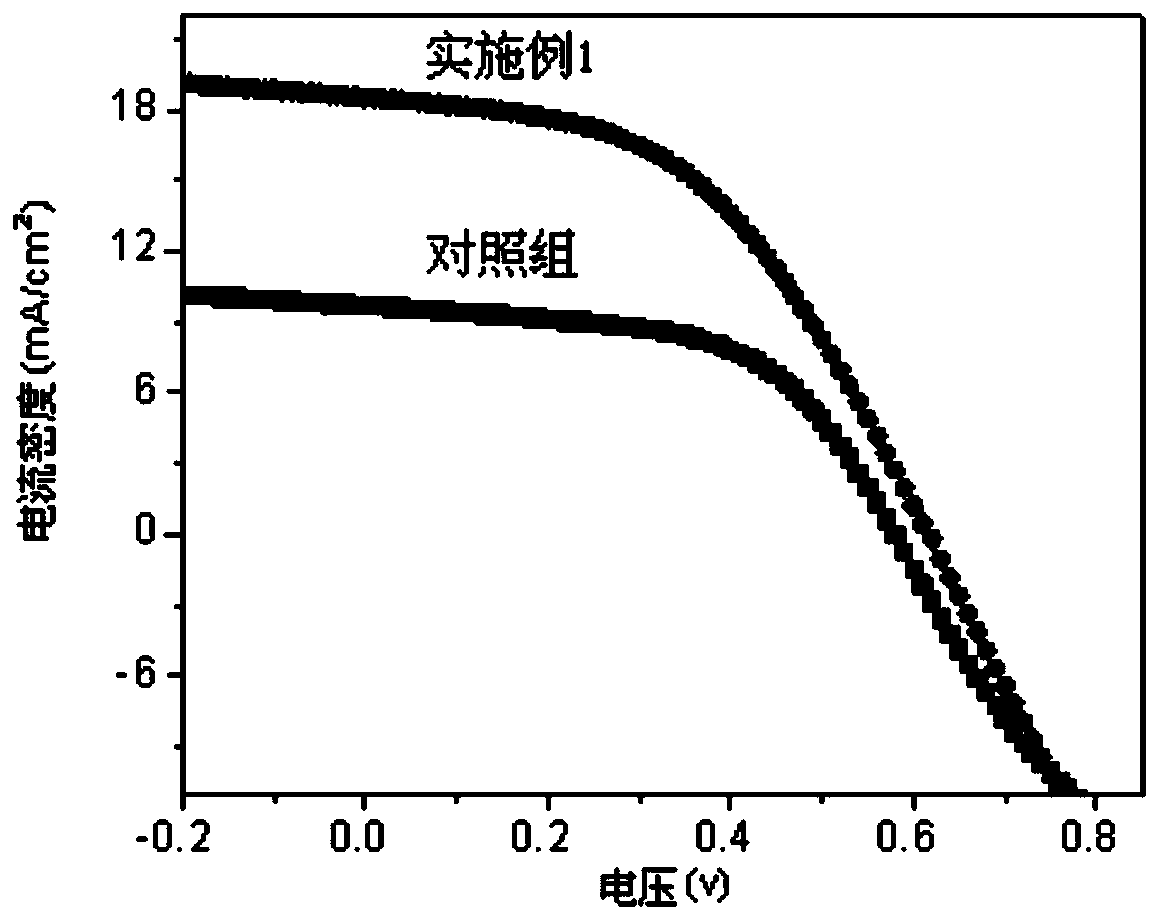

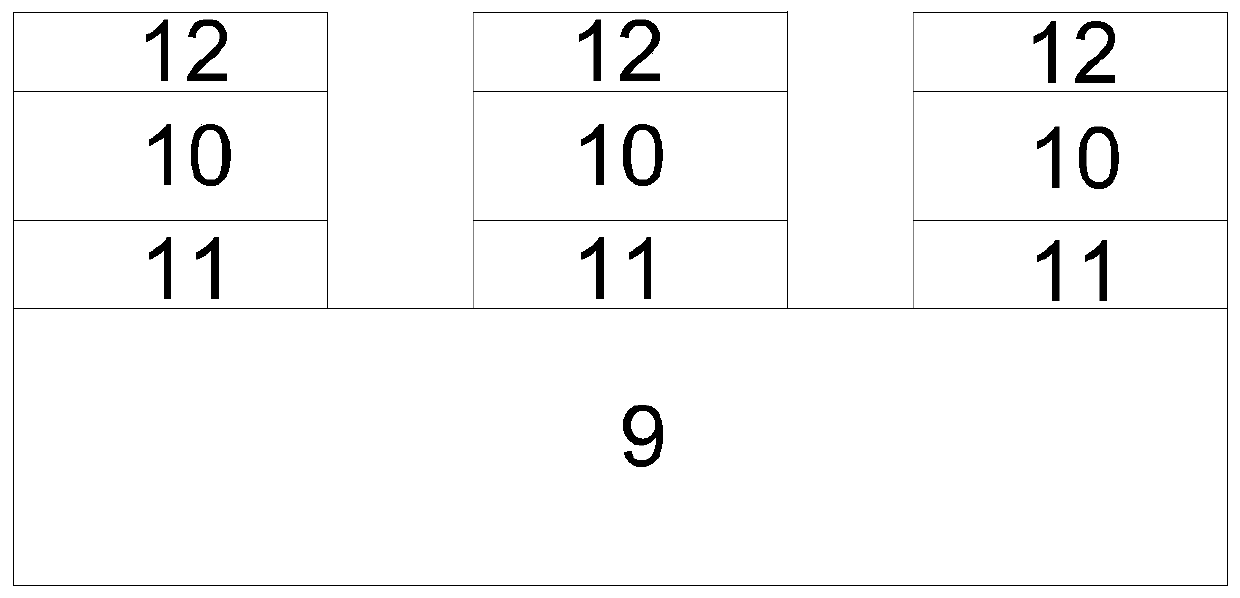

A kind of microetching method of cadmium telluride nanocrystalline film

ActiveCN109065665BPrevent leakageLower Schottky BarrierFinal product manufactureSemiconductor devicesSchottky barrierThin membrane

The invention belongs to the field of photoelectric devices and discloses a microetching method of a cadmium telluride nanocrystalline thin film. A mask plate is cover on that cadmium telluride nanocrystalline thin film, and the surface of the cadmium telluride nanocrystalline thin film is micro-etched by the steam of the etching solution to obtain the etch cadmium telluride nanocrystalline thin film. The method of the invention can avoid the problem of device leakage caused by damaging the PN junction of the thin film, and simultaneously reduce the Schottky barrier between the high work function cadmium telluride and the electrode.

Owner:SOUTH CHINA UNIV OF TECH

A kind of vertical structure LED chip of double insertion layer reflector structure and preparation method thereof

ActiveCN108511568BImprove yieldImprove light output efficiencySemiconductor devicesPhysical chemistryEngineering

The invention discloses a vertical structure LED chip with a double-insertion-layer reflector structure, which comprises an Si substrate, an LED epitaxial wafer, a reflector first insertion metal layer, a nano Ag reflector and a reflector second insertion metal layer, wherein the LED epitaxial wafer grows on the Si substrate, the reflector first insertion metal layer grows on the surface of the LED epitaxial wafer, the nano Ag reflector grows on the surface of the reflector first insertion metal layer, and the reflector second insertion metal layer grows on the surface of the nano Ag reflector. The invention further provides a preparation method of the vertical structure LED chip with the double-insertion-layer reflector structure. The vertical structure LED chip improves the problems of poor adhesion and poor thermal stability of an Ag-based reflector, greatly improves the process stability of the Ag-based reflector and the reflectivity of the reflector, and thus improves the yield and light output efficiency of the vertical structure LED chip.

Owner:HEYUAN CHOICORE PHOTOELECTRIC TECH CO LTD

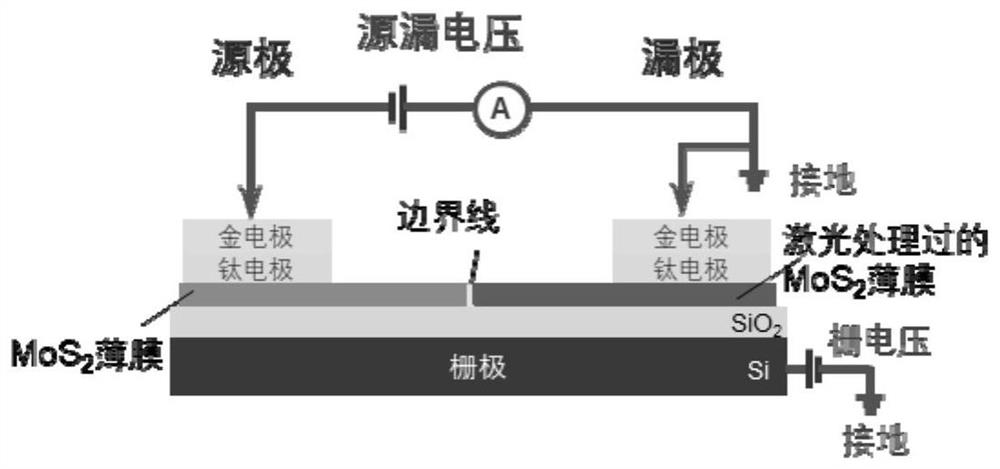

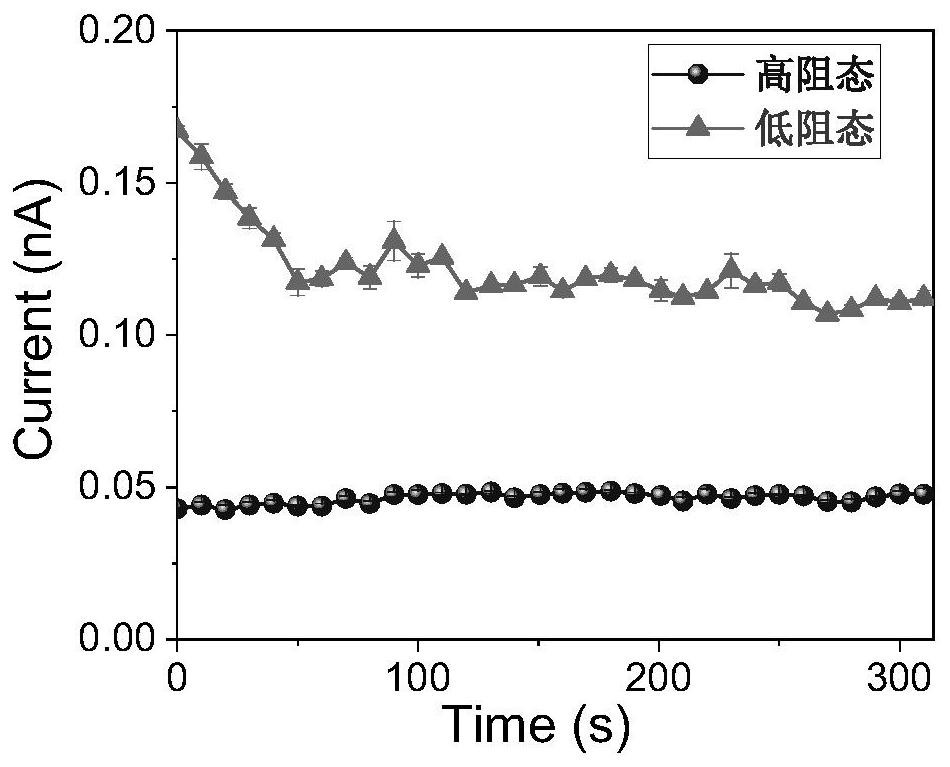

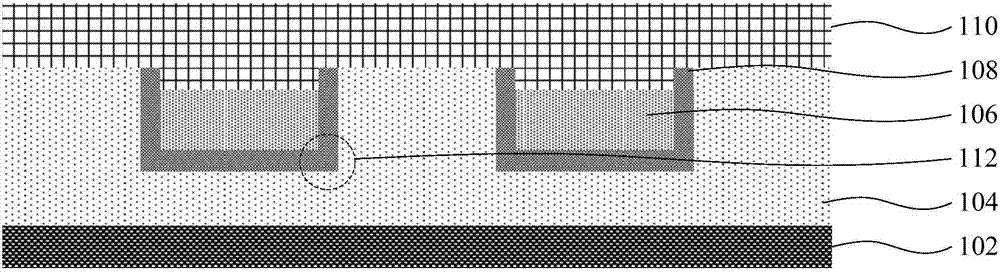

Arrayed neural network capable of artificially designing boundary based on two-dimensional material and preparation method and application thereof

PendingCN113053756ALower Schottky BarrierLower turn-on voltageFinal product manufactureSemiconductor/solid-state device manufacturingPhysicsThin membrane

The invention discloses an arrayed neural network capable of artificially designing a boundary based on a two-dimensional material, and a preparation method and application thereof. The preparation method comprises the following steps of: 1) growing a single crystal transition metal compound thin film on a substrate through adopting a vapor deposition method; (2) transferring the thin film obtained in the step (1) to a substrate with a dielectric layer; (3) irradiating the thin film with the dielectric layer on the substrate in the step (2) by using laser according to a specified path to obtain a sample with a specified heterostructure; and 4) plating a source electrode and a drain electrode on the surface of the sample of the specified heterostructure by adopting an electron beam or thermal evaporation method to obtain the arrayed neural network capable of artificially designing the boundary based on the two-dimensional material. According to the arrayed neural network, and the preparation method and the application thereof, due to the sub-nano-scale thickness, the artificially modulatable boundary and the controllably generated surface defects, the Schottky barrier between the metal and the electrode is effectively reduced, so that the turn-on voltage is reduced, and the energy consumption is further reduced to the human brain level.

Owner:TSINGHUA UNIV

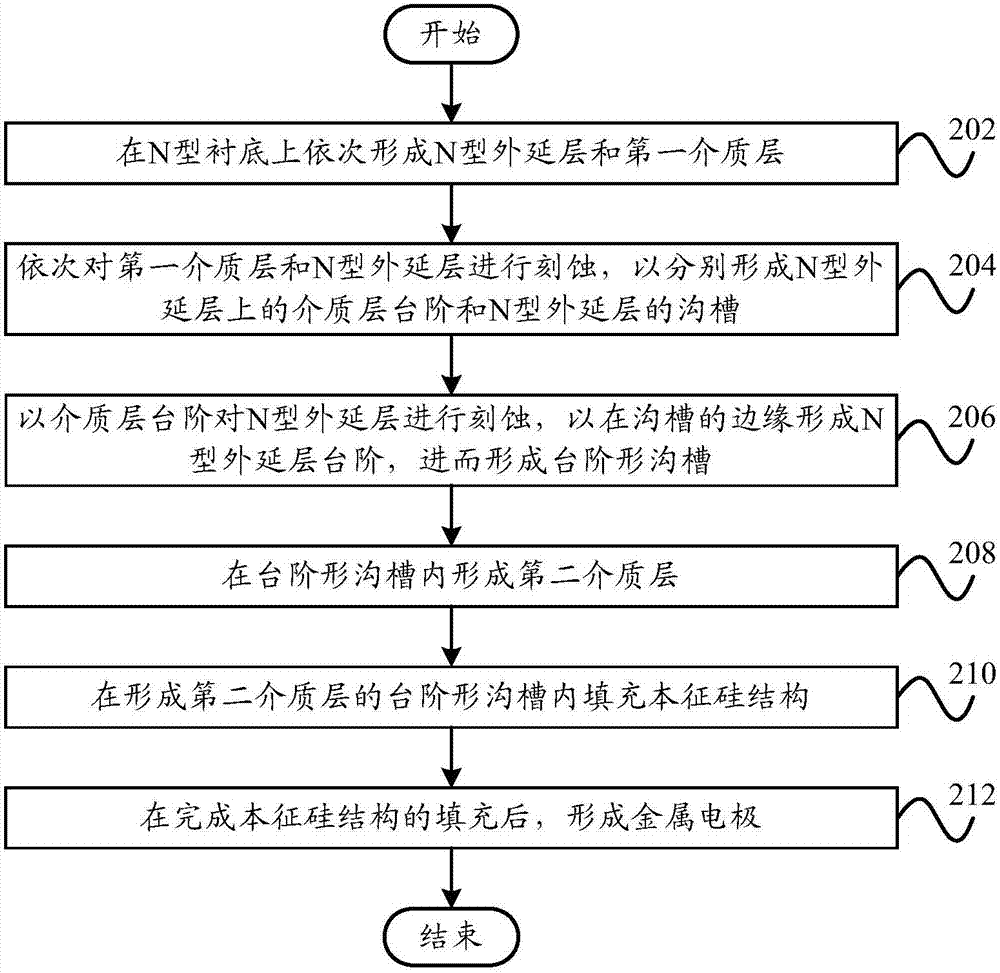

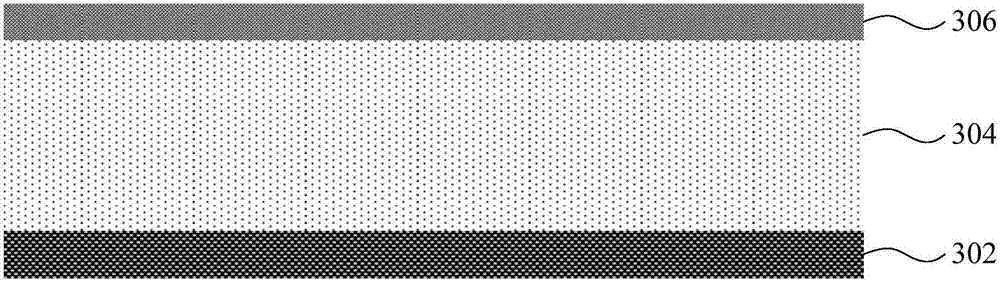

Preparation method of Schottky diode and Schottky diode

InactiveCN107546124AReduce electric field strengthLower Schottky BarrierSemiconductor/solid-state device manufacturingSemiconductor devicesMetal electrodesDielectric layer

The invention provides a preparation method of a Schottky diode and a Schottky diode. The preparation method comprises the steps of sequentially forming an N type epitaxial layer and a first dielectric layer on an N type substrate; performing etching on the first dielectric layer and the N type epitaxial layer in sequence to respectively form a dielectric layer step on the N type epitaxial layer and a trench of the N type epitaxial layer; etching the N type epitaxial layer by taking the dielectric layer step as a mask so as to form an N type epitaxial layer step at the edge of the trench, andthus forming a stepped trench; forming a second dielectric layer in the stepped trench; filling an intrinsic silicon structure in the stepped trench in which the second dielectric layer is formed; andforming a metal electrode at the completion of filling of the intrinsic silicon structure. According to the technical scheme of the invention, the electric field intensity inside the device in the conduction process is reduced, the maximum electric field intensity value is significantly reduced in particular, and thus the Schottky barrier lowering effect of the device is effectively reduced, so that the reverse leakage current is reduced.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

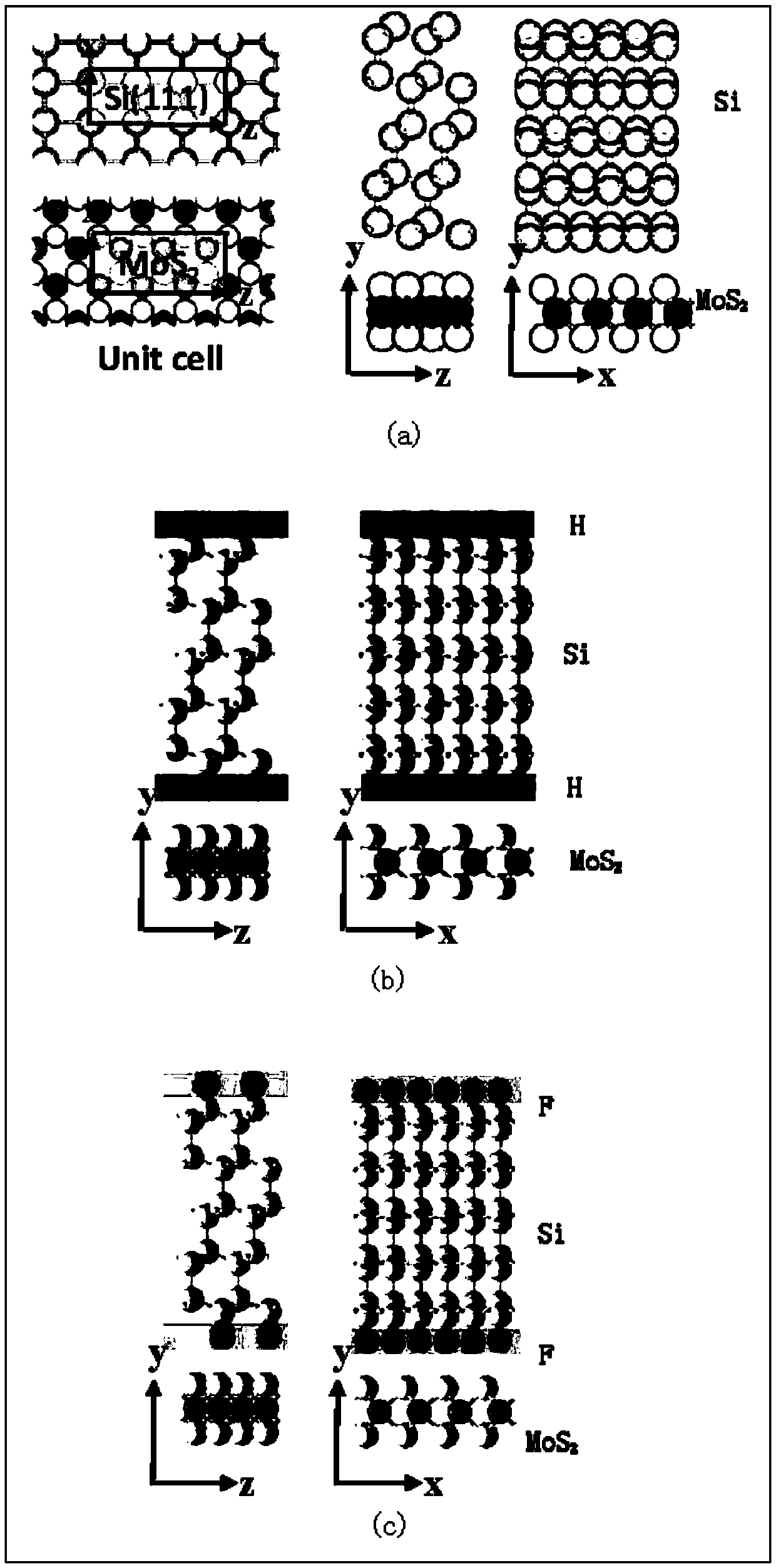

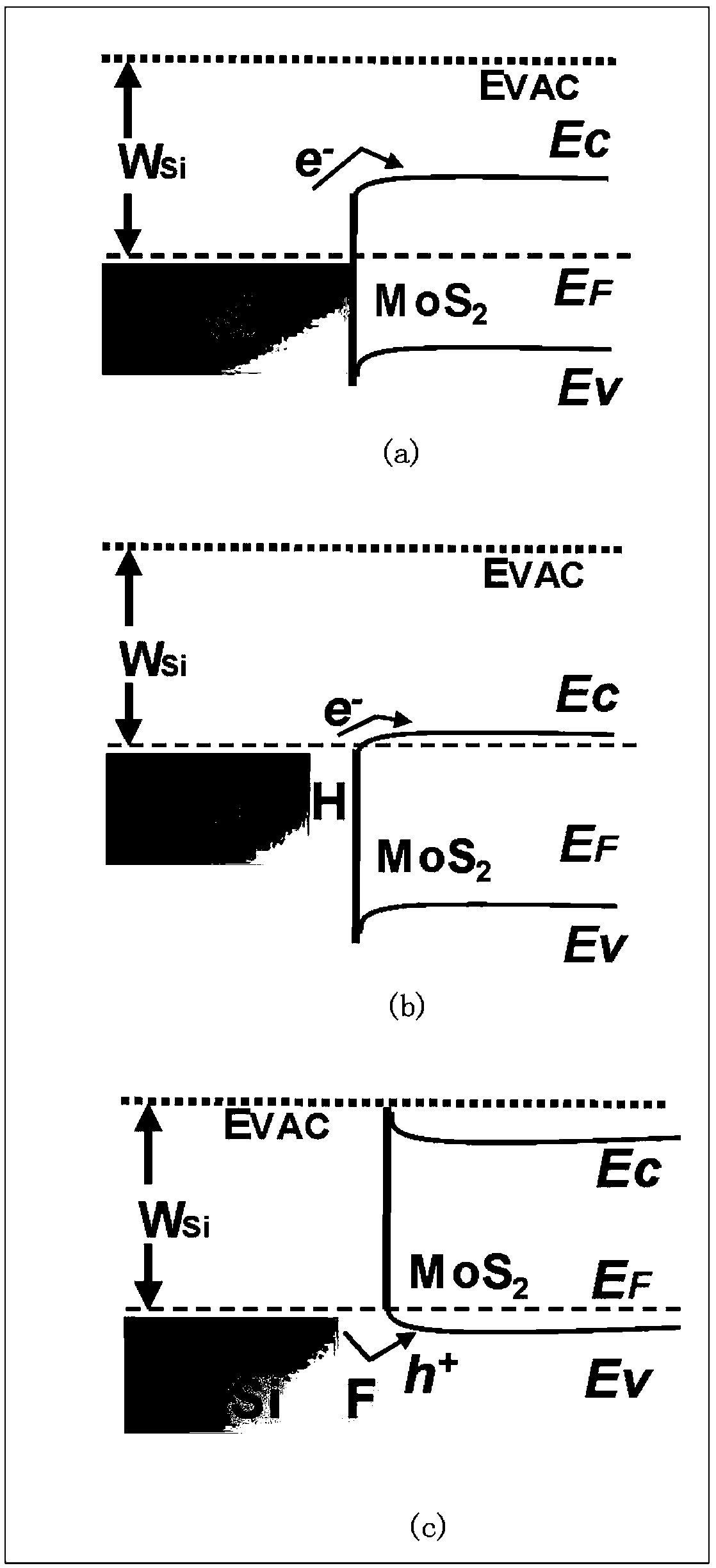

Interface treatment method for reducing silicon and transition metal sulfide semiconductor schottky barrier

InactiveCN109671627ALower Schottky BarrierReduced ohmic contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierHydrogen

The invention discloses an interface treatment method for reducing a silicon and transition metal sulfide semiconductor schottky barrier. Hydrogen or fluorine is used for conducting passivating treatment on the surface of Si, and then the Si and two ends of transition metal sulfide are subjected to surface contact to form an NIN-type schottky field-effect tube or a PIP-type schottky field-effect tube. According to a contact system after the hydrogen is used for passivating the Si surface, energy difference between a fermi level and a conduction band bottom of the transition metal sulfide is reduced so that the schottky barrier of the system can be reduced by passivating the Si surface through the hydrogen; secondly, the fluorine is used for passivating the Si surface, so that original n-type schottky contact can be turned into p-type schottky contact. According to the method, the traditional materials silicon and the transition metal sulfide are selected for surface contact, and through the traditional passivating element hydrogen or fluorine, the Si surface is subjected to passivating treatment so that the schottky barrier of the Si-MoS2 system can be reduced, and the interface treatment method for reducing the silicon and transition metal sulfide semiconductor schottky barrier has significant instructional significance for integration, of two-dimensional materials into the traditional silicon material, of microelectronic devices in the future.

Owner:SHANDONG UNIV

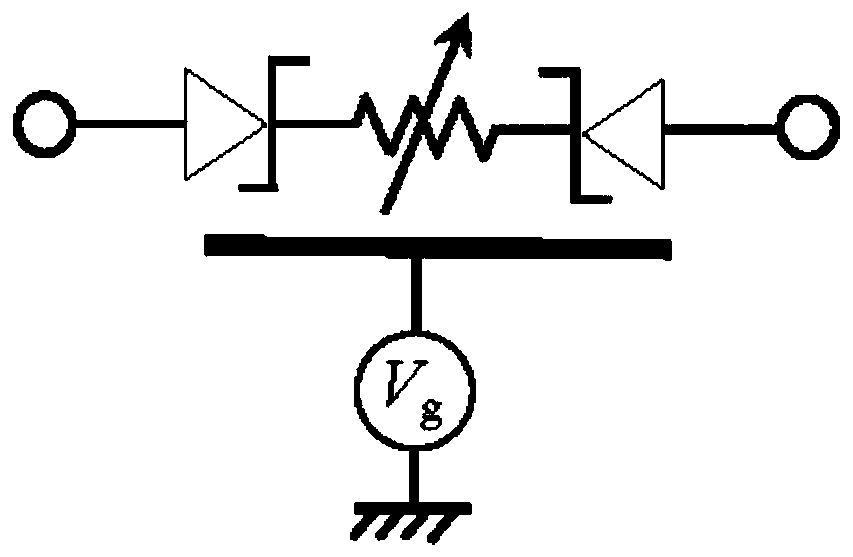

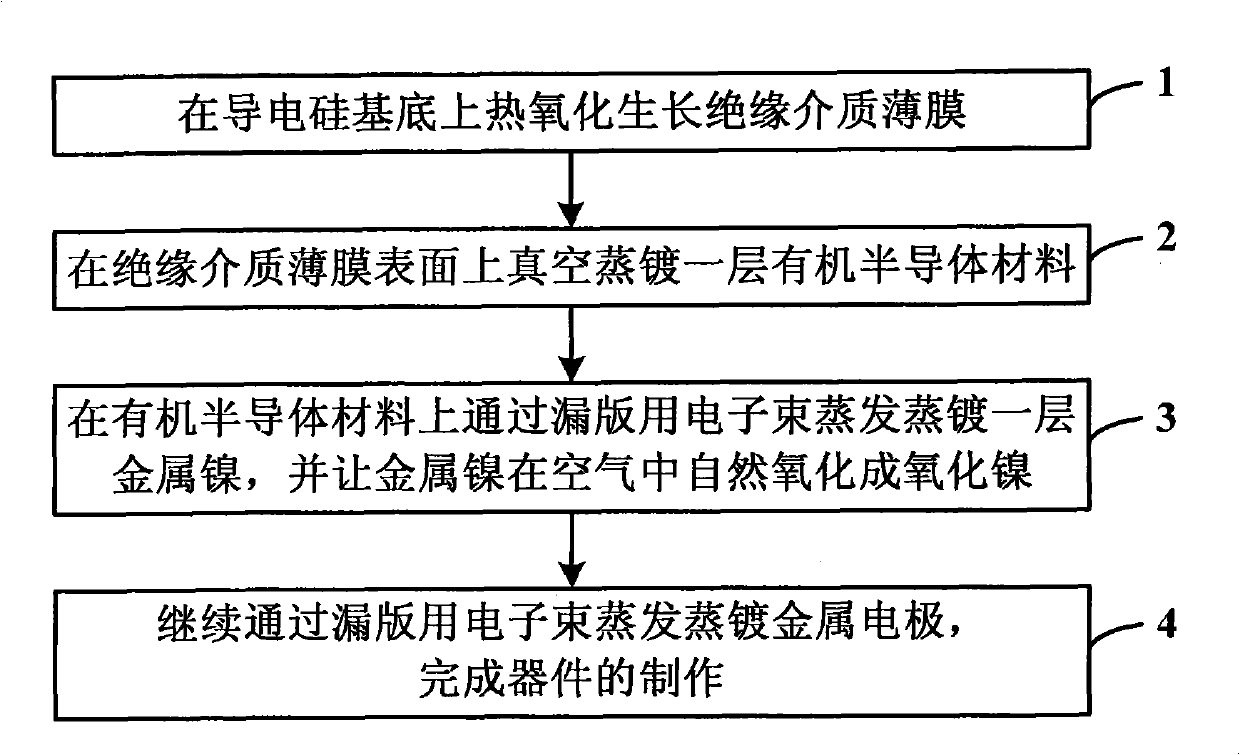

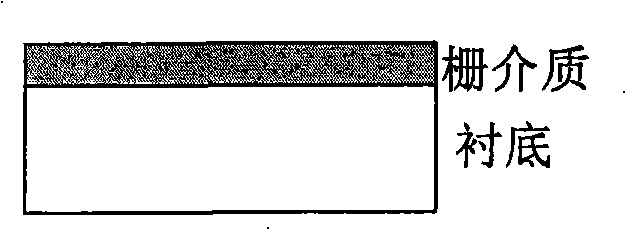

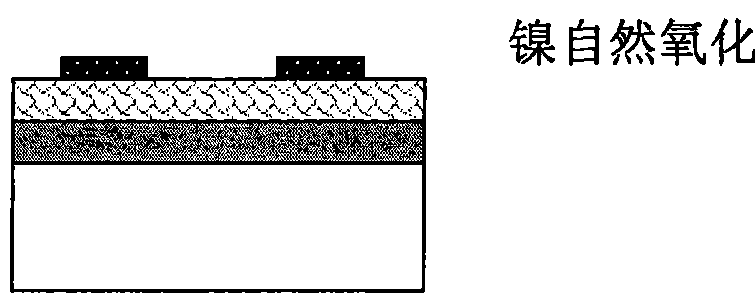

Method for carrying out Fermi energy level modification on top electrode

ActiveCN101783394BReduce penetrationReduced responseSolid-state devicesSemiconductor/solid-state device manufacturingSchottky barrierOrganic semiconductor

The invention discloses a method for carrying out Fermi energy level modification on a top electrode, which comprises the following steps: step 1) carrying out thermal oxidation growth of an insulation dielectric thin film on a conductive silicon substrate; step 2) carrying out vacuum evaporation of a layer of organic semiconductor material on the surface of the insulation dielectric thin film; step 3) using electron beam evaporation for evaporating a layer of metal nickel on the organic semiconductor material through a stencil, and naturally oxidizing the metal nickel to nickel oxide in the air; and step 4) continuously using the electron beam evaporation for evaporating a metal electrode through the stencil and completing the production of a device. The utilization of the method can effectively reduce the infiltration and the reaction of a gold electrode to the organic semiconductor layer; simultaneously, the naturally oxidized nickel oxide layer can be taken as a high-work-functiontransition layer, thereby reducing the Schottky barrier between the gold electrode and the organic semiconductor layer and further improving the contact between the electrode and an active layer.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

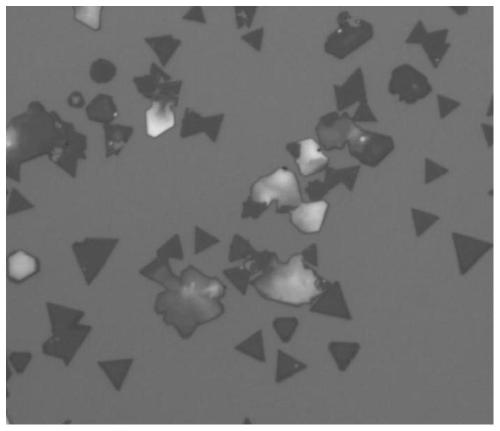

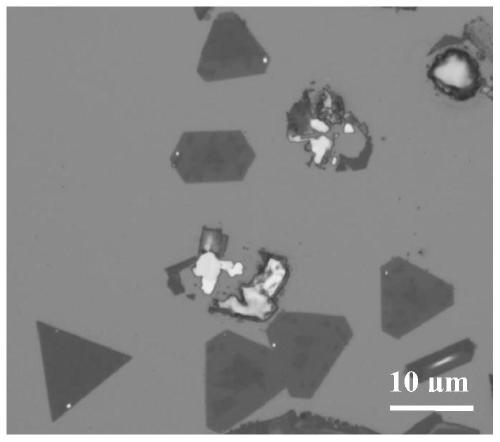

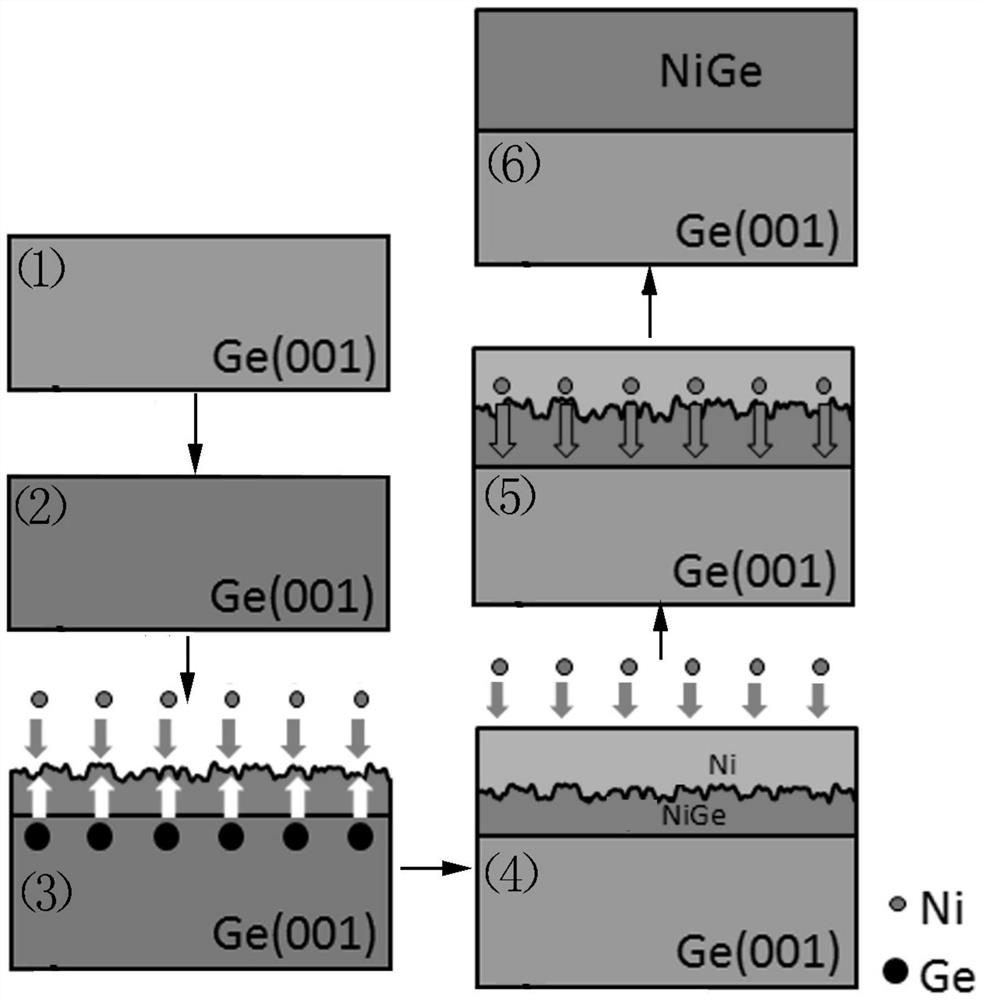

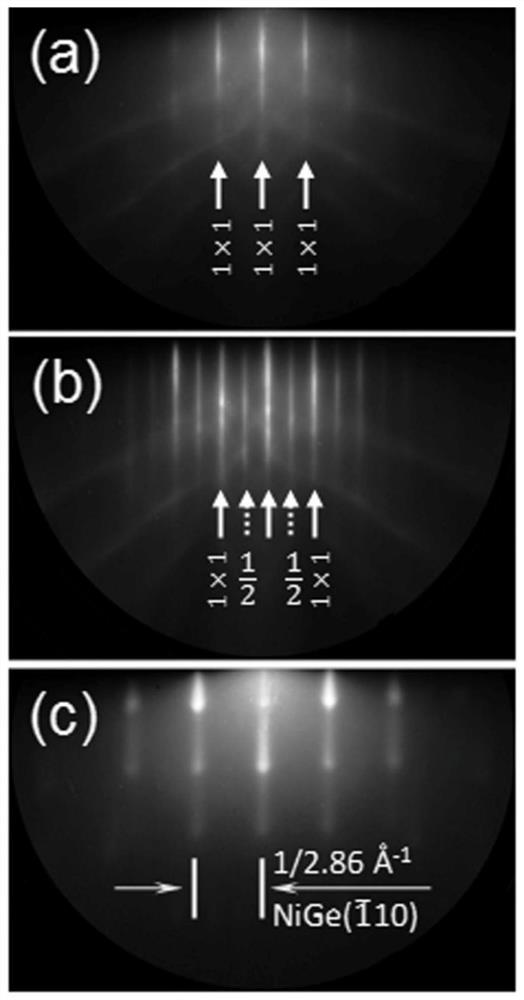

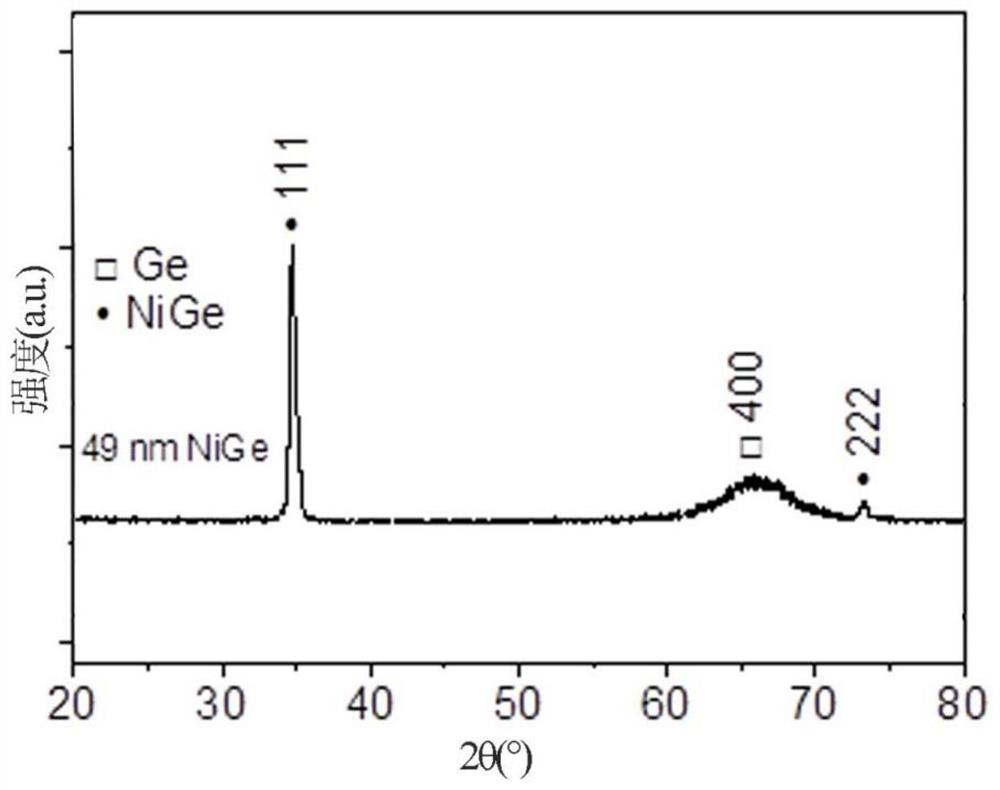

Nige single crystal film with unlimited thickness and its preparation method and application

ActiveCN110060921BReduce mismatchLower Schottky BarrierSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSchottky barrier

The invention relates to the technical field of semiconductor materials, and specifically provides a NiGe single crystal thin film and a preparation method and application thereof. The preparation method comprises the following steps: providing a clean Ge(001) substrate; heating the Ge(001) substrate in a vacuum to obtain a pre-used substrate; performing Ni reactive evaporation treatment on the pre-used substrate under vacuum, Form a layer of NiGe single crystal film on the surface of Ge(001); evaporate a layer of Ni film on the surface of NiGe single crystal film at room temperature; anneal the Ge(001) substrate in an inert atmosphere to make the Ni film diffuse A NiGe single crystal film is passed through, and the NiGe single crystal film is used as a single crystal seed layer, and a solid phase reaction occurs with a Ge(001) substrate to obtain a NiGe single crystal film with an unlimited thickness. The method can obtain NiGe single crystal film with low Schottky potential barrier, small contact resistance and good thermal stability, and is suitable for MOSFET field.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

Thermal jet printing head based on graphene-carbon nanotube composite structure and preparation method thereof

The invention discloses a thermal jet-printing head based on a graphene-carbon nanotube composite structure, and a preparation method thereof. An ICP process and a surface smoothing process of filling deep grooves with PDMS are adopted, and a main channel, an ink jet chamber, an ink inlet channel, a nozzle and an ink jet channel are prepared in a silicon underlayer; and an anodic bonding process is adopted, graphene pieces are taken as a middle layer, and a glass substrate is bonded with the silicon underlayer. The main channel communicates with the ink jet chamber through the ink inlet channel, the depth of the ink inlet channel is less than the depth of the ink jet chamber; the nozzle is formed in the bottom of the ink jet chamber; and a microbubble generator array with a carbon nanotube-graphene composite structure and a carbon nanotube temperature sensor array are prepared in an area corresponding to the ink jet chamber, of the glass substrate, and arranged in a manner of facing the ink jet chamber. The jet head is reliable in liquid inlet closure, high in bonding strength, not liable to pollute a jet-printing chamber, and capable of easily controlling accuracy during preparation.

Owner:HUAZHONG UNIV OF SCI & TECH

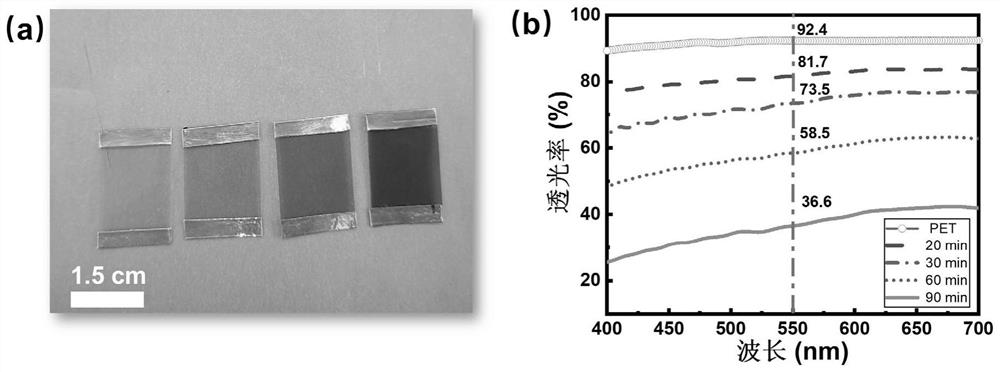

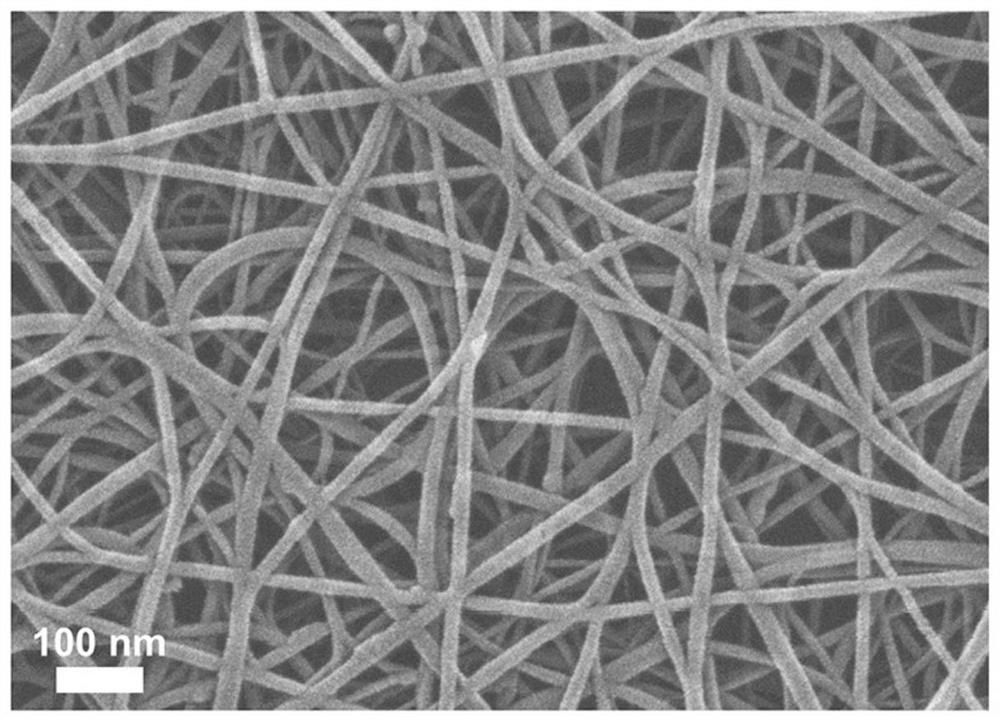

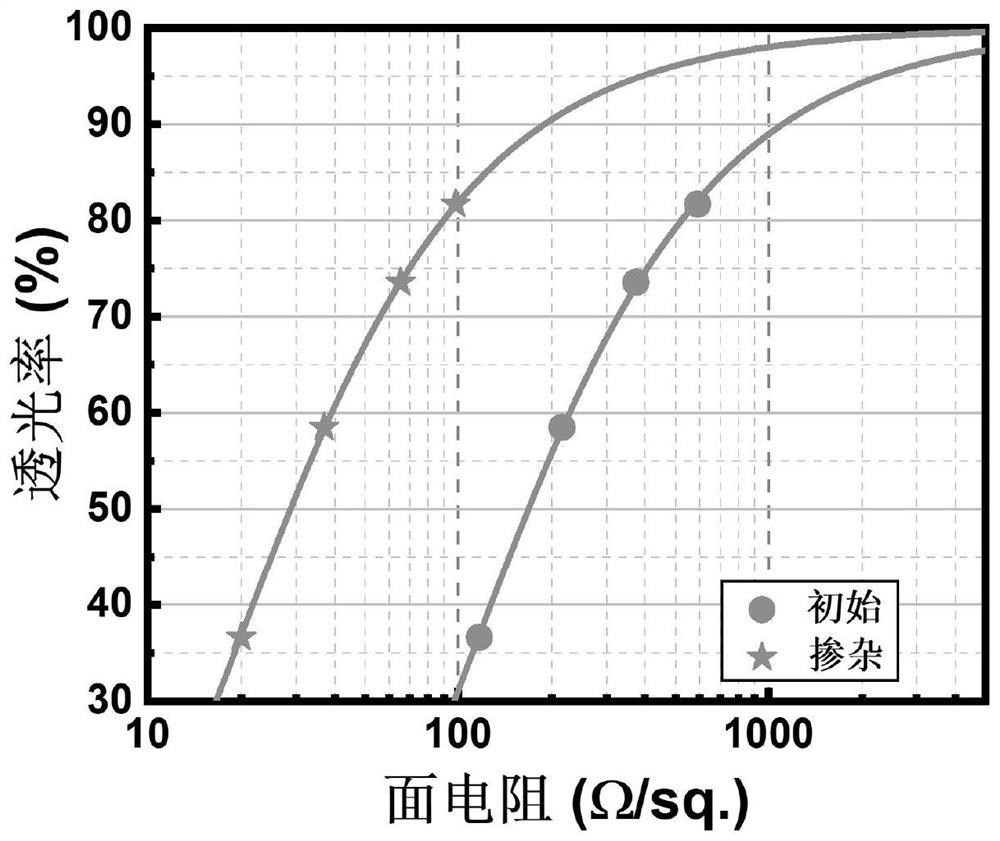

Single-walled carbon nanotube transparent electrothermal film and preparation method thereof

PendingCN114195131AQuality improvementGood electrical conductivityCarbon nanotubesCondensed water formation preventionThin membraneCopper foil

The invention discloses a single-walled carbon nanotube transparent electrothermal film and a preparation method thereof, and belongs to the technical field of electrothermal films. Single-walled carbon nanotubes prepared by a floating catalytic chemical vapor deposition method are subjected to suction filtration through a vacuum pump to a filter membrane with a certain size, single-walled carbon nanotube films with different light transmittances are obtained by controlling suction filtration time, the films are transferred to a substrate through a pressing method, and a single-walled carbon nanotube / substrate film is obtained. And cutting the single-walled carbon nanotube into a specific size, and pasting copper foil adhesive tapes with corresponding sizes on two opposite edges of the single-walled carbon nanotube to obtain the single-walled carbon nanotube transparent electrothermal film, and doping gold chloride to obtain the gold chloride doped single-walled carbon nanotube electrothermal film. The prepared single-walled carbon nanotube transparent electrothermal film is excellent in conductivity, the Schottky barrier between the carbon nanotubes can be reduced through gold chloride doping, the film can be densified, and the heating performance of the electrothermal film is improved through the combined action of gold chloride doping and gold chloride doping.

Owner:DALIAN POLYTECHNIC UNIVERSITY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com