Gate oxide structure and preparation method

A technology of gate oxide structure and oxide layer, which is applied in the field of semiconductors, can solve problems such as increasing the electric field at the gate oxide material, reducing tunneling current, and reliability problems, so as to improve channel mobility, improve forward conduction capability, The effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

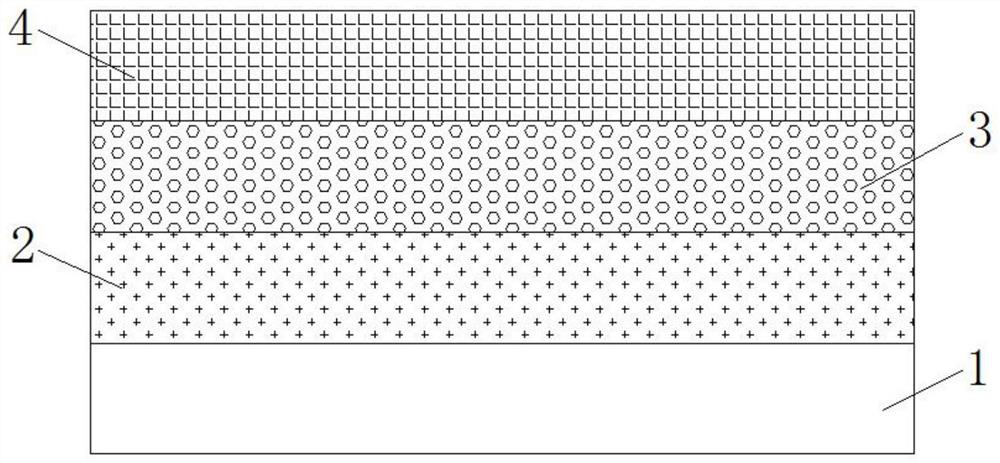

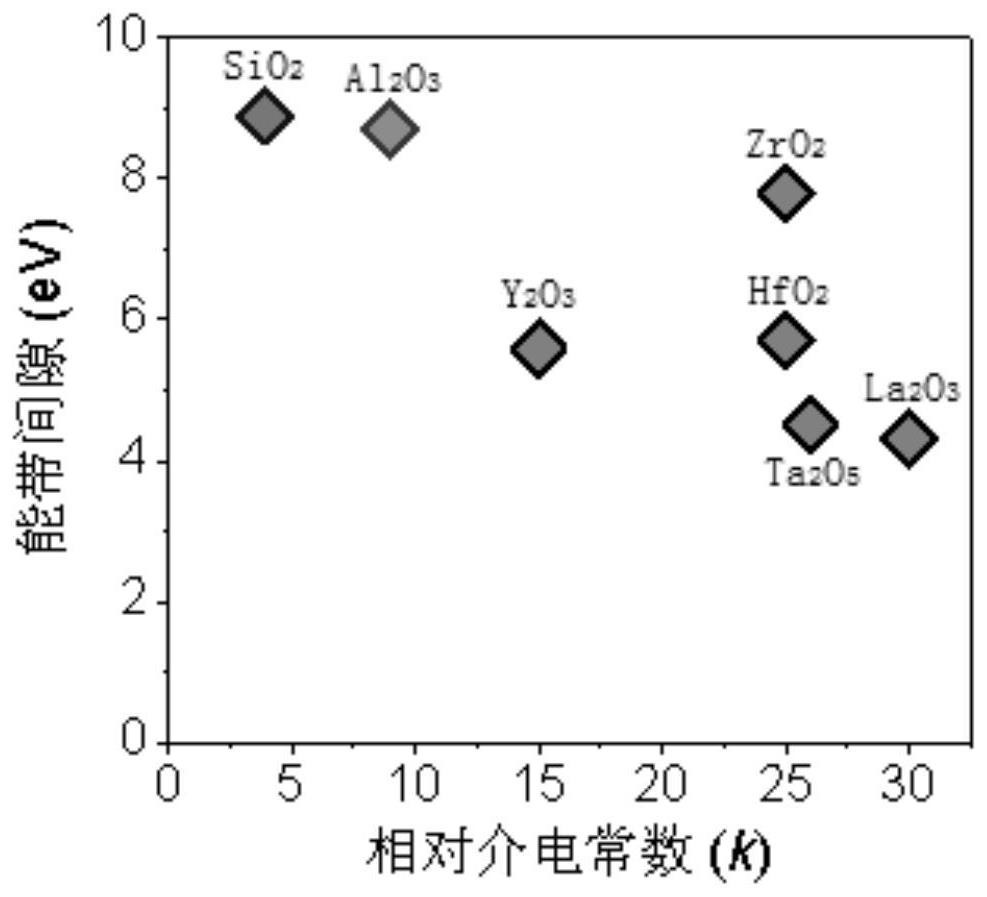

[0032] A gate oxide structure comprising a SiC substrate layer 1, an oxide layer 2, an intermediate layer 3 and a high dielectric material layer 4, the oxide layer 2 is disposed on the SiC substrate layer 1, the intermediate layer 3 is disposed on the oxide layer 2, and the intermediate layer 3 The side away from the oxide layer 2 is provided with a high dielectric material layer 4, and the high dielectric material layer 4 is HfO 2 layer, ZrO 2 Layer or Y 2 o 3 Any one of the layers, the middle layer 3 is Al 2 o 3 layer.

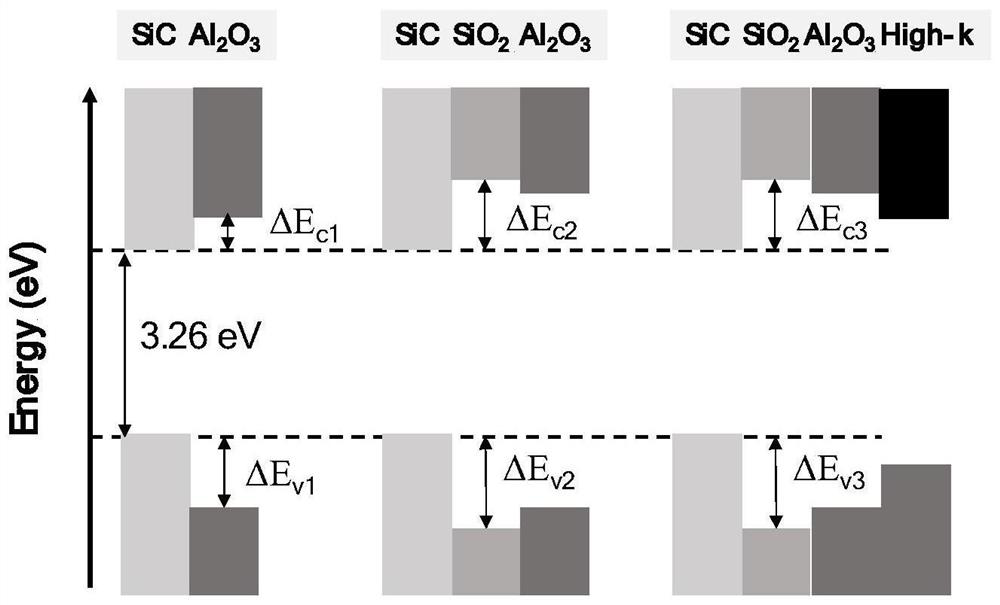

[0033] The traditional gate oxide structure uses SiO 2 Only one layer of Al is added on the layer 2 o 3 layer, but due to Al 2 o 3 The dielectric constant is 9, and the bandgap is 8.7eV, which has both high dielectric constant and bandgap, but due to Al 2 o 3 There are many crystal phases, and in the process of heating and cooling, various crystal phase structures will be converted to each other, and grain boundaries are easily generated, which le...

Embodiment 2

[0040] A method for preparing a gate oxide structure, comprising the following steps: using a cleaning gas to clean surface crystal plane defects of a SiC substrate layer 1 at 500°C, wherein the cleaning gas can be hydrogen; Oxidize the cleaned SiC substrate layer 1 in an oxygen environment at 1500°C to obtain an oxide layer 2, namely SiO 2 layer, while controlling the generated SiO by oxidation time 2 The thickness of the layer; the method of high temperature annealing is used to eliminate the surface dangling bond passivation and interface state defects of the oxide layer 2, wherein the annealing temperature for eliminating the surface dangling bond passivation and interface state defects of the oxide layer 2 is 1350 ° C, and the oxide layer The atmospheric pressure of dangling bond passivation and interface state defects on the surface of 2 is 1.5 Pa, and the atmosphere environment for eliminating the surface dangling bond passivation and interface state defects of oxide la...

Embodiment 3

[0046] In this embodiment, the high dielectric material is also HfO 2 The material is used as an example to describe the preparation process, but the difference between this embodiment and the second embodiment is that the HfO 2 materials were deposited to obtain HfO 2 layer, its obtained thickness is 30nm, and the deposition time of controlled low-pressure vapor deposition at this time is 2 hours.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More