Patents

Literature

34 results about "Tunnel injection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Tunnel injection is a field electron emission effect; specifically a quantum process called Fowler–Nordheim tunneling, whereby charge carriers are injected to an electric conductor through a thin layer of an electric insulator.

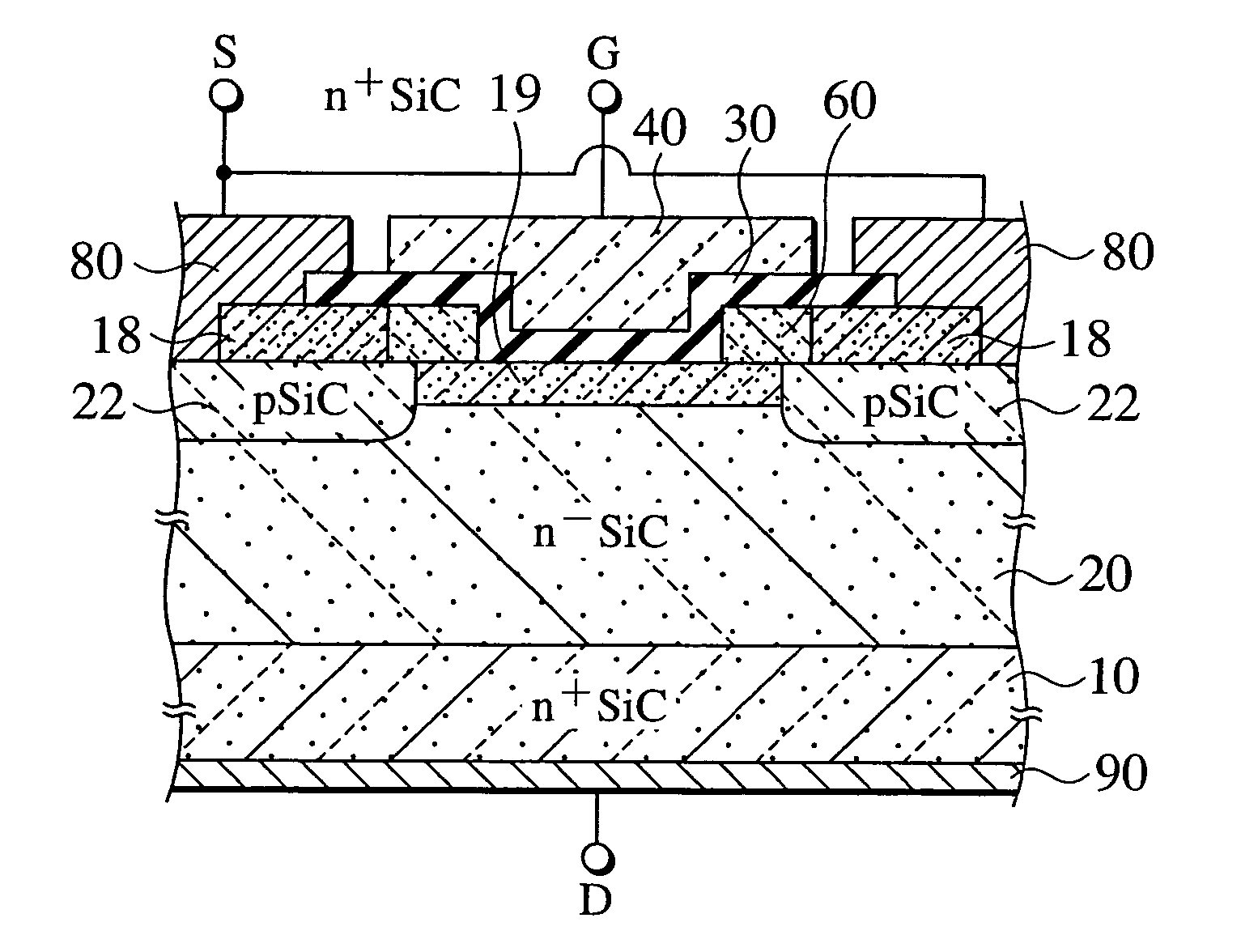

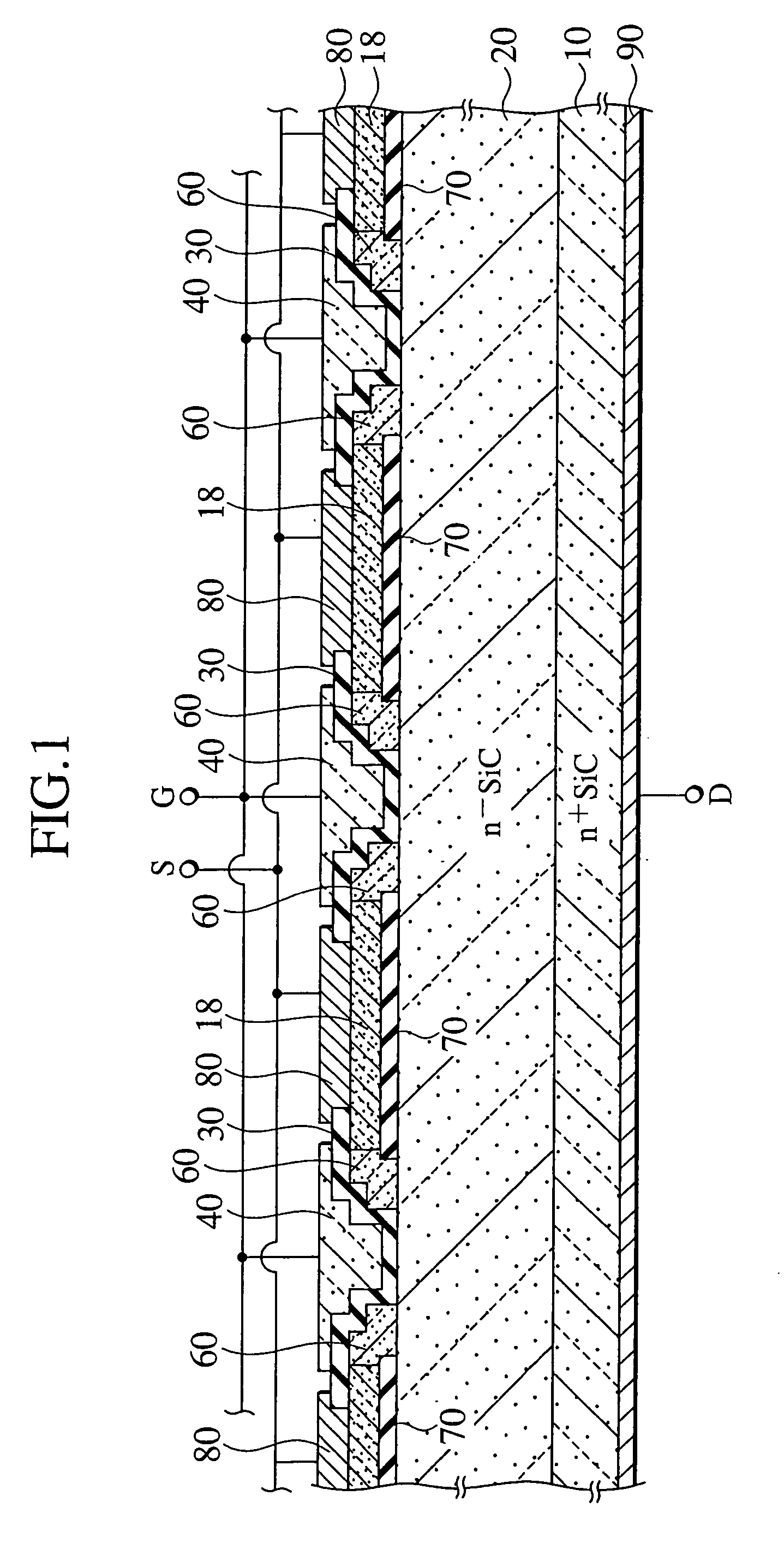

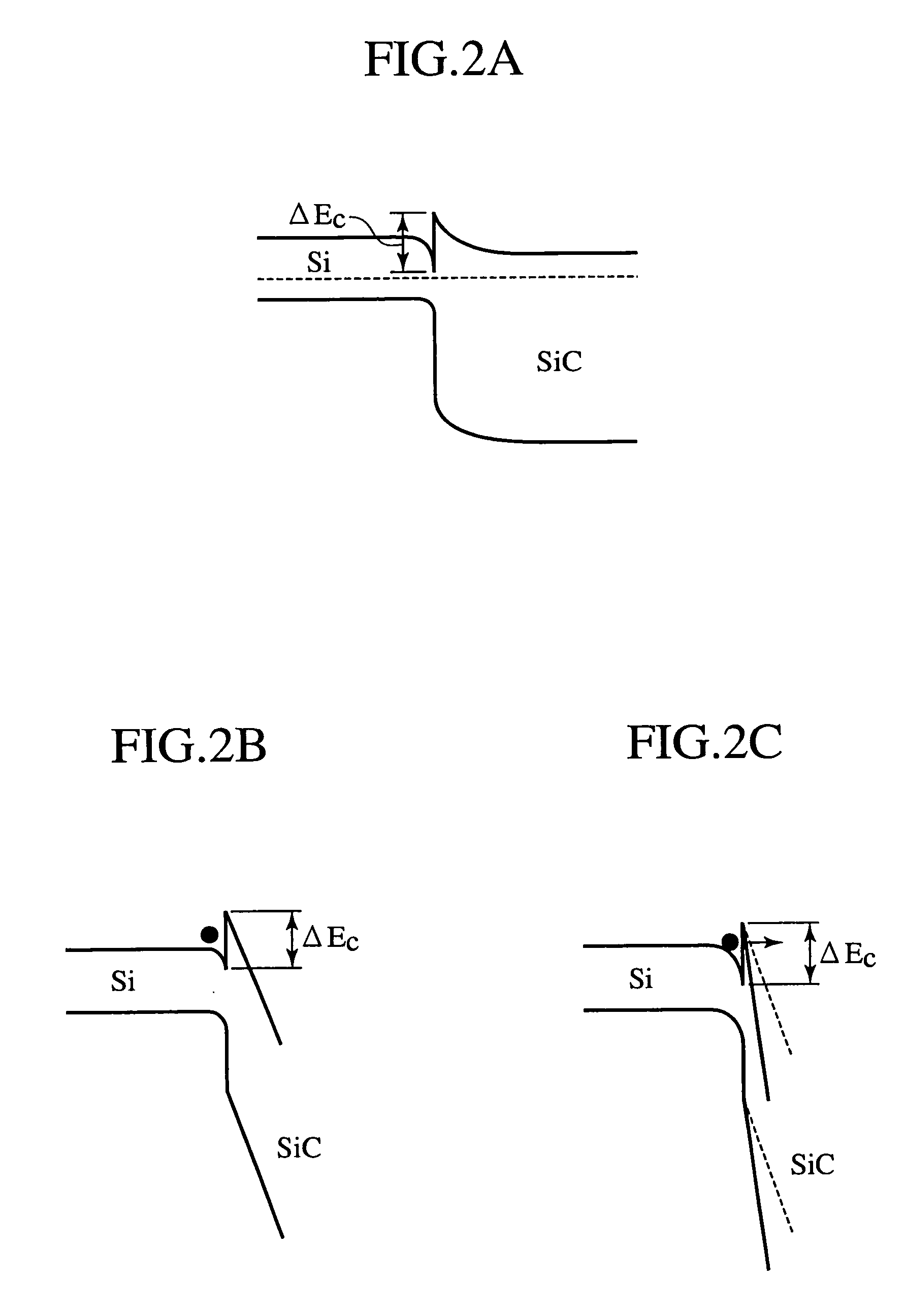

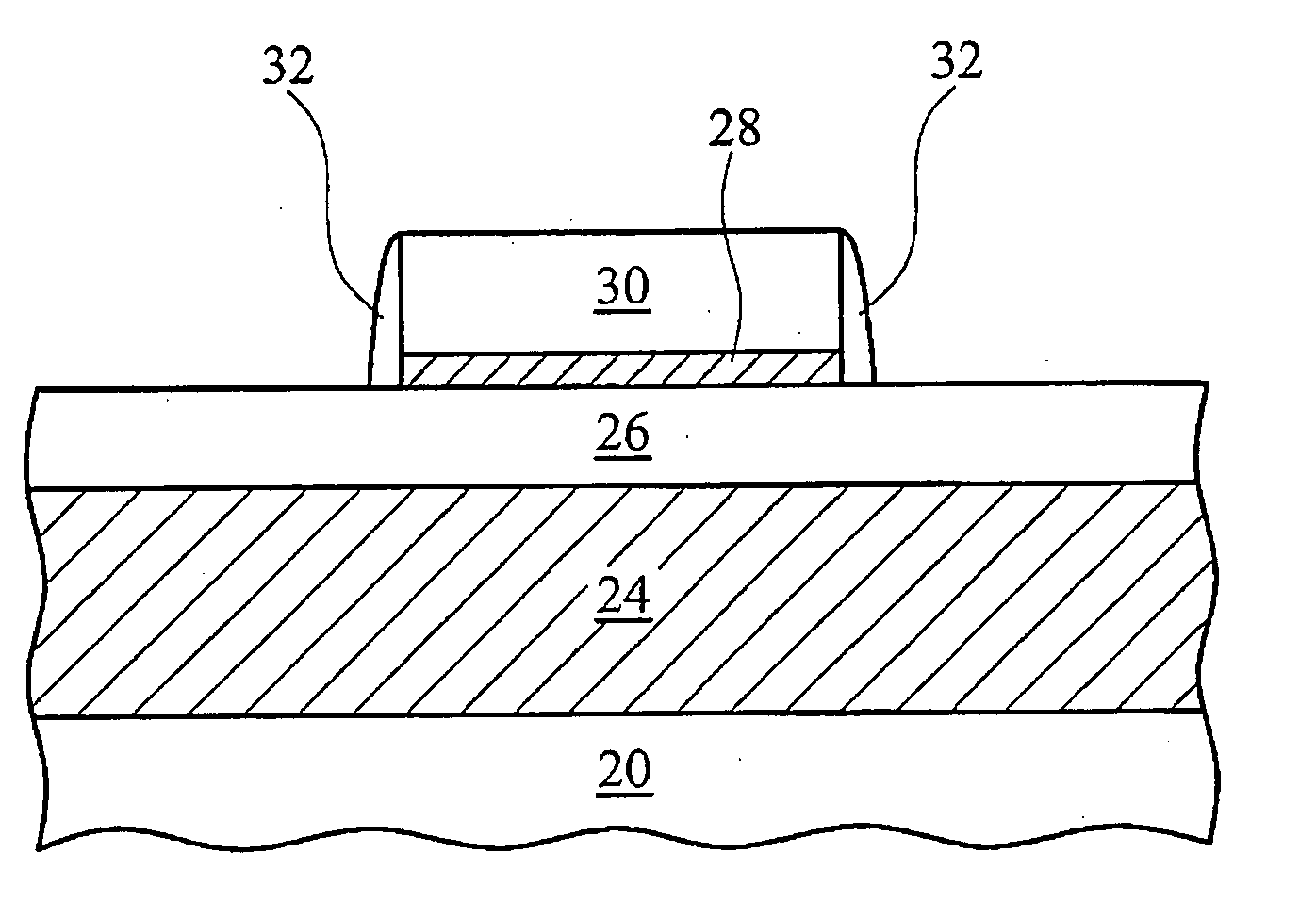

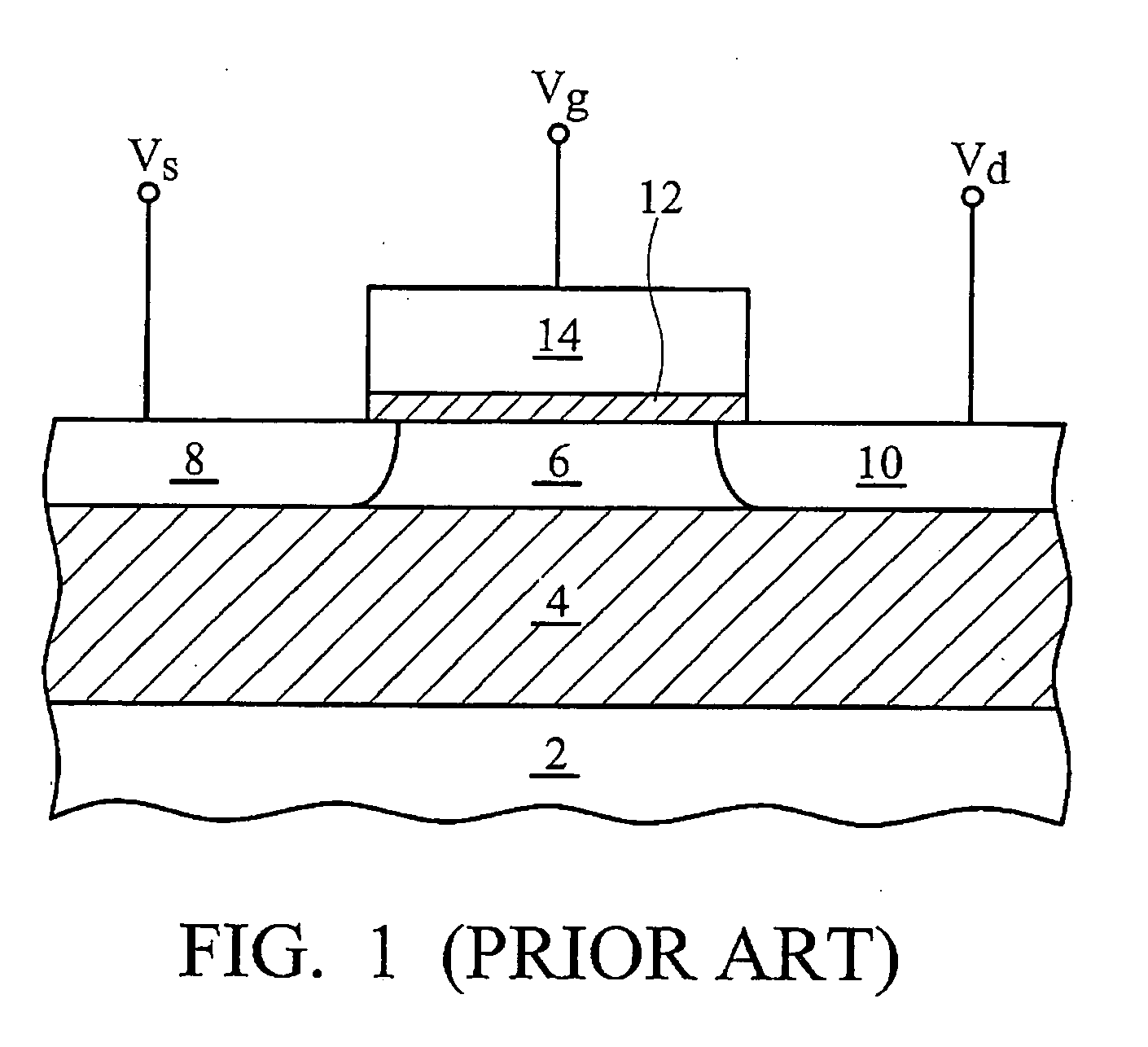

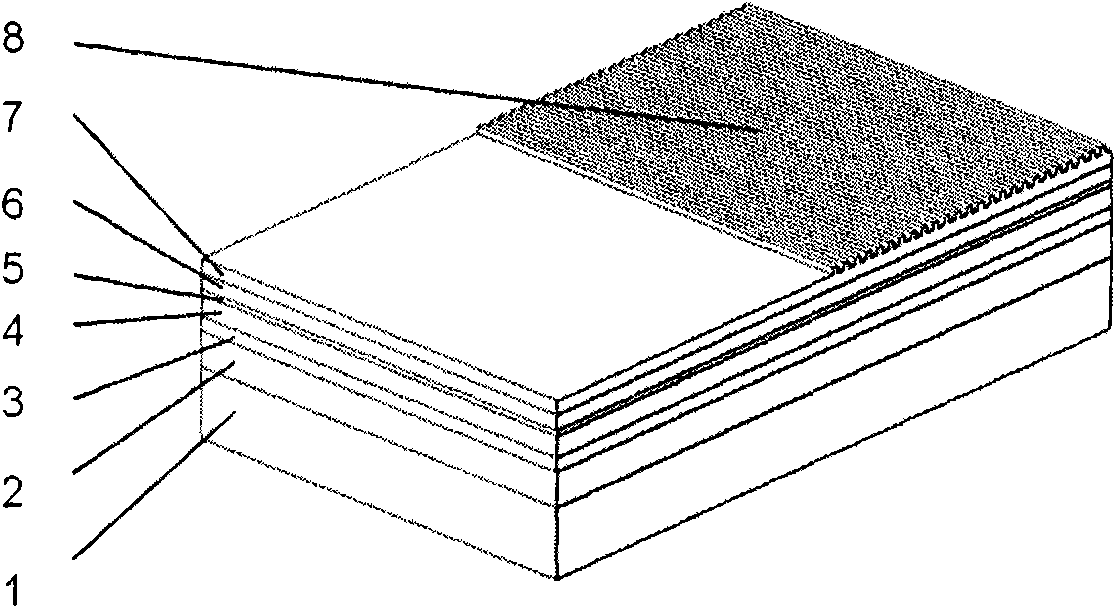

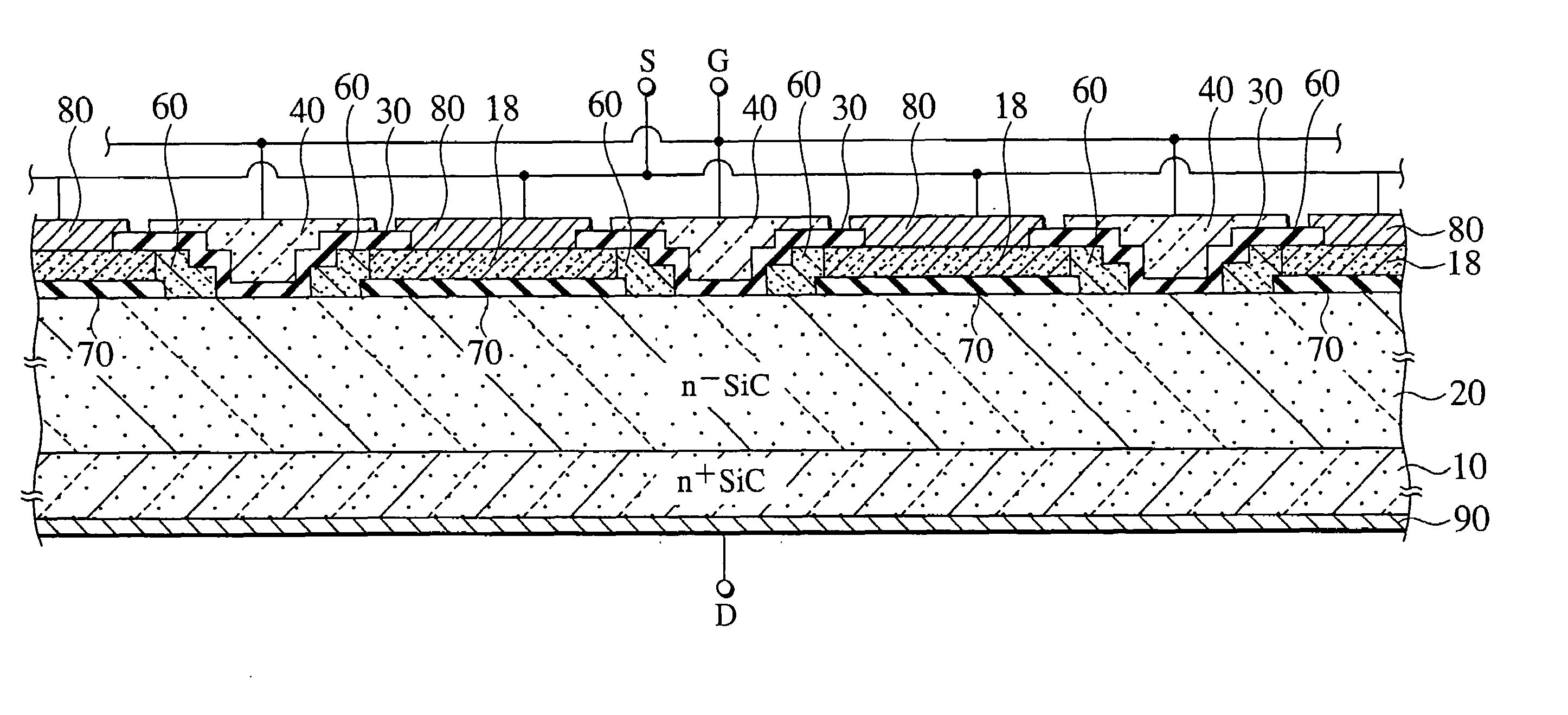

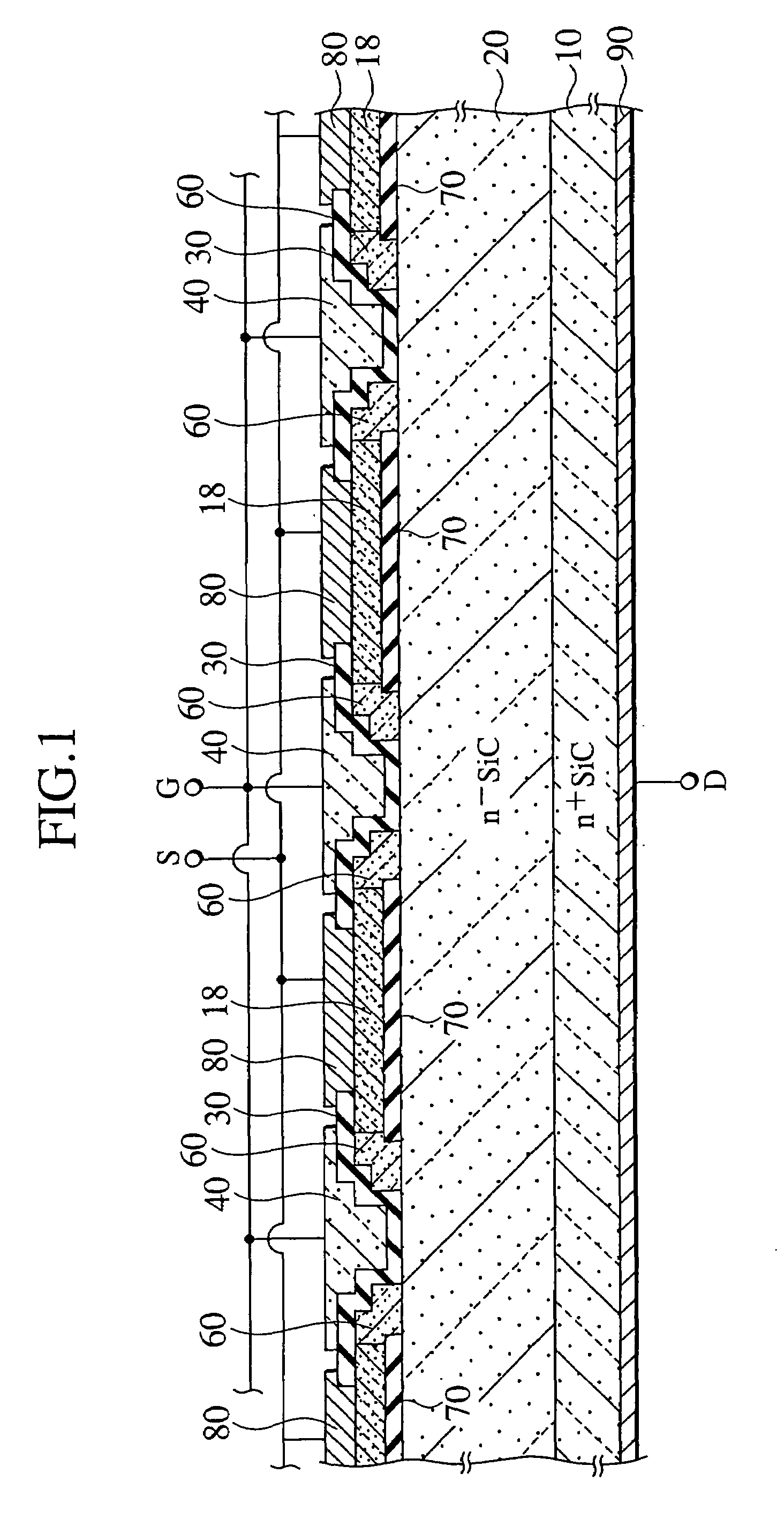

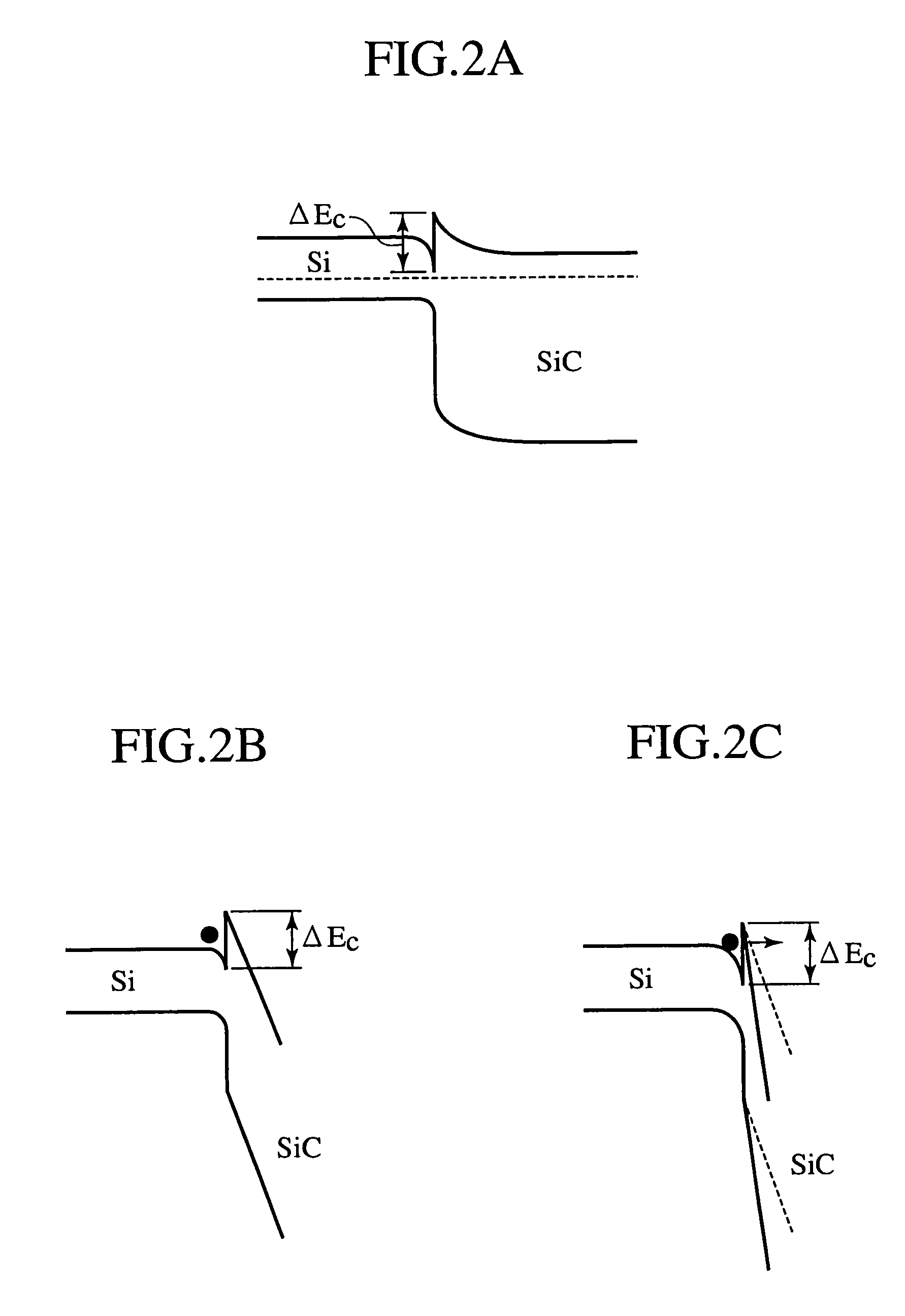

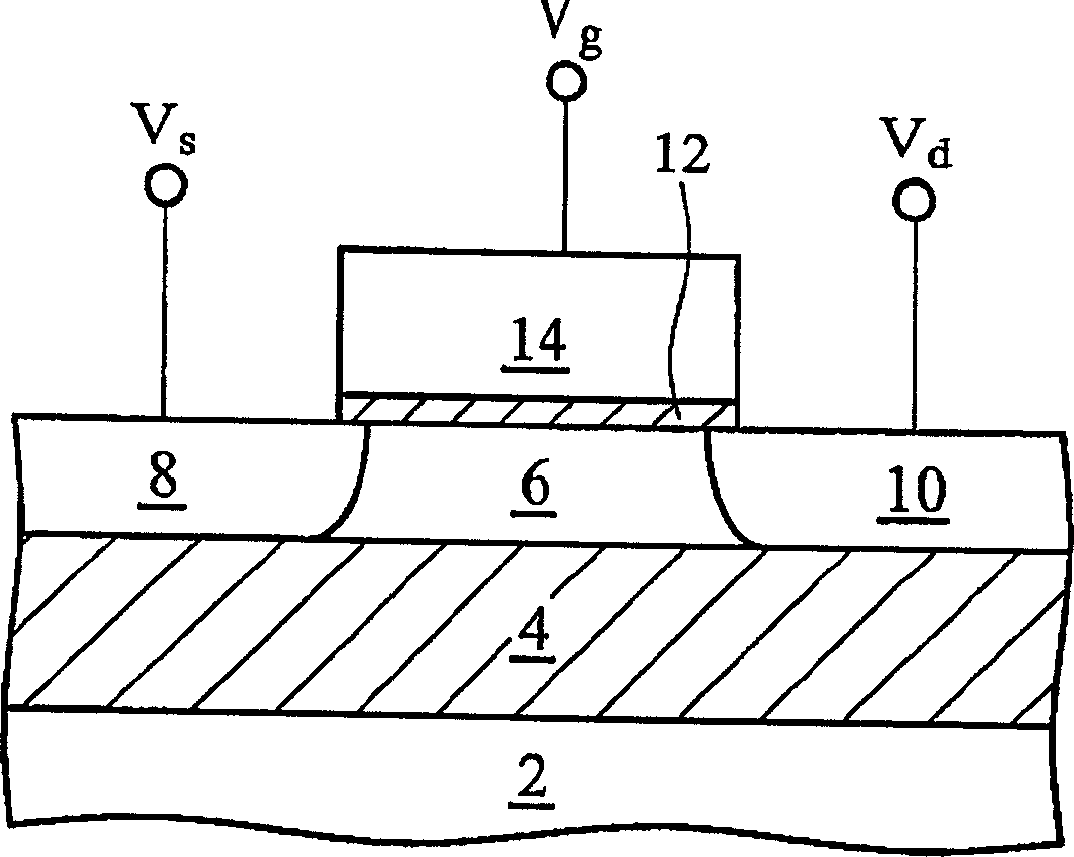

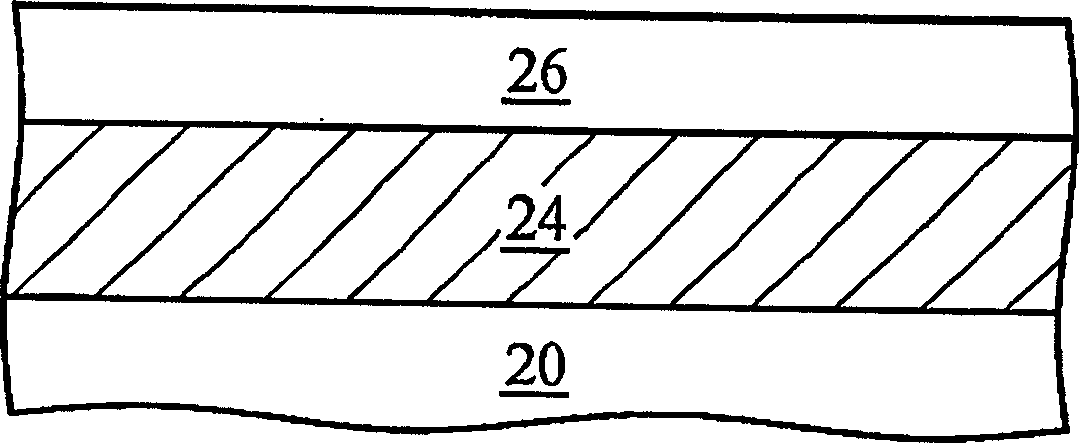

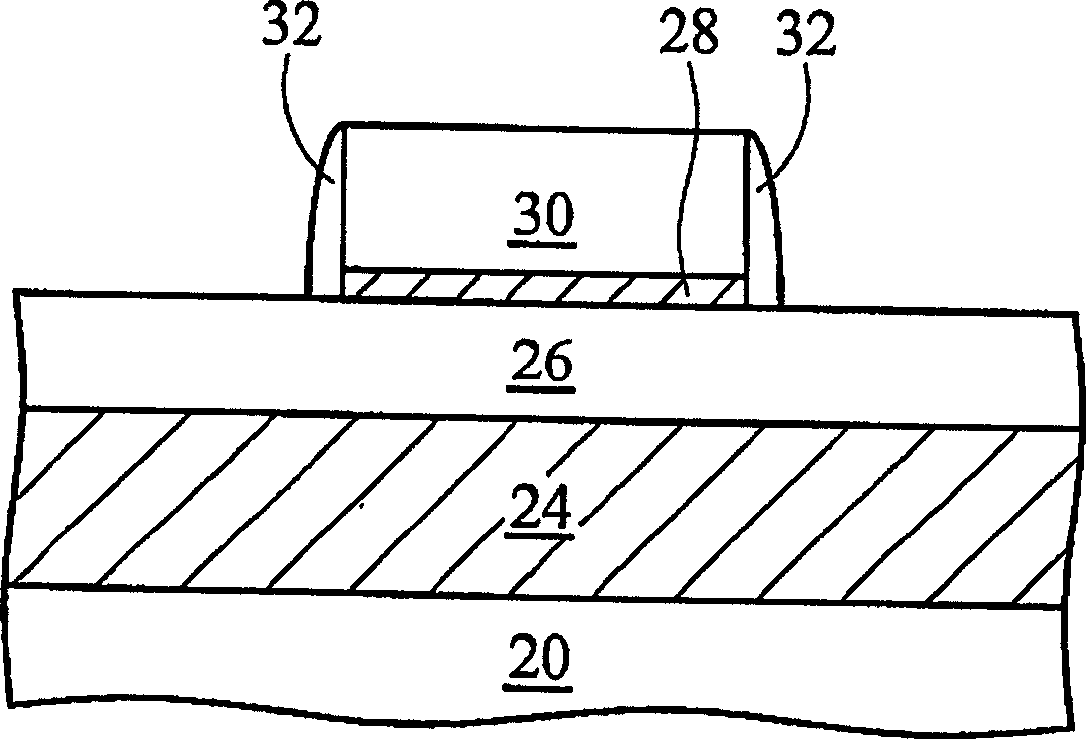

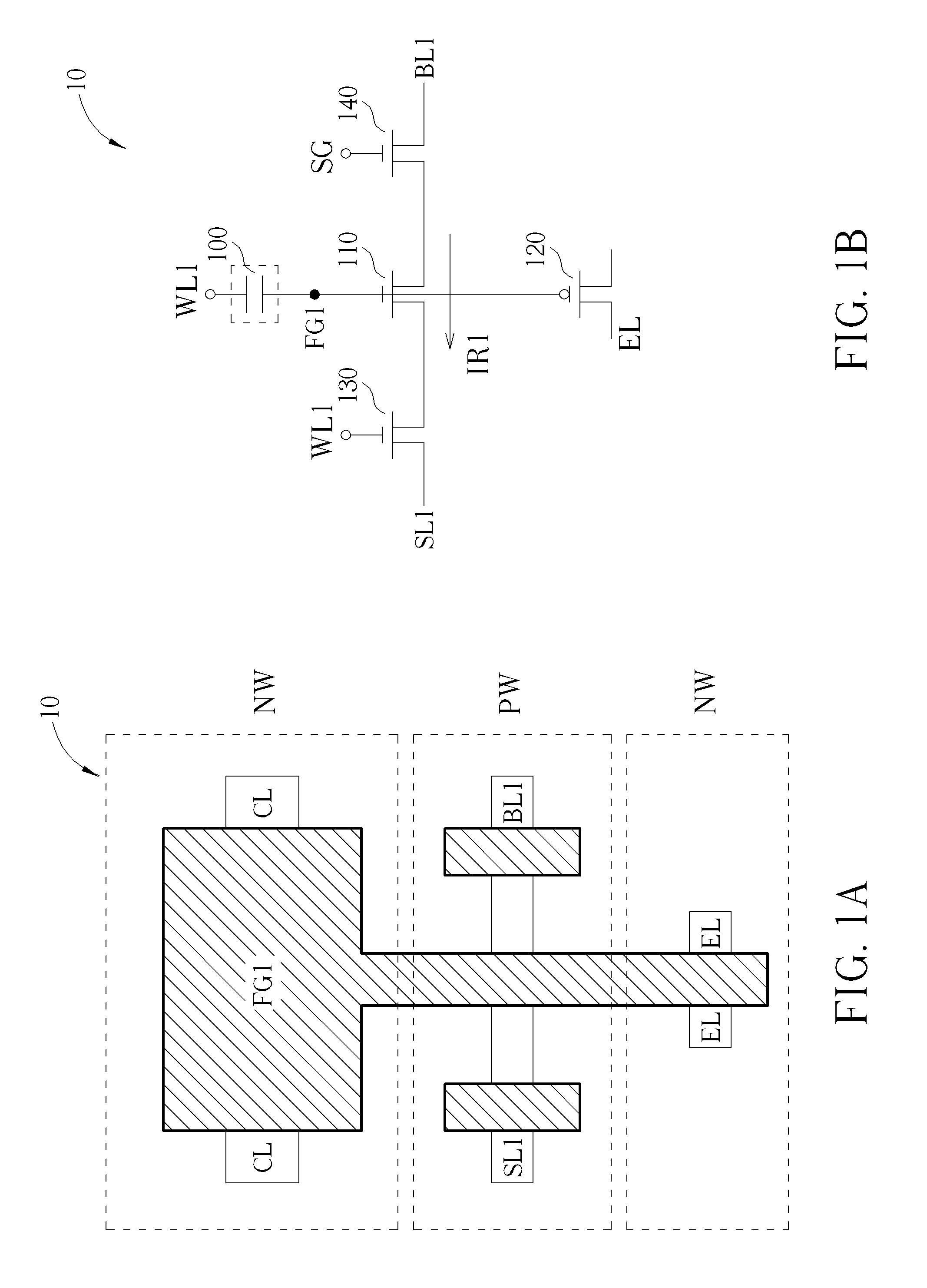

Insulated gate tunnel-injection device having heterojunction and method for manufacturing the same

InactiveUS20040079989A1High breakdown voltage of the gate insulation filmImprove mobilitySemiconductor/solid-state device manufacturingDiodeHeterojunctionTunnel injection

The present invention-provides a tunnel-injection device which encompasses, a reception layer made of a first semiconductor, a barrier-forming layer made of a second semiconductor having a bandgap-narrower than the first semiconductor, being in metallurgical contact with the reception layer, a gate insulating film disposed on the barrier-forming layer. The gate electrode controls the width of the barrier generated at the heterojunction interface between the reception layer and the barrier-forming layer so as to change the tunneling probability of carriers through the barrier. The device further encompasses a carrier receiving region being contact with the reception layer and a carrier-supplying region being contact with the barrier-forming layer.

Owner:NISSAN MOTOR CO LTD

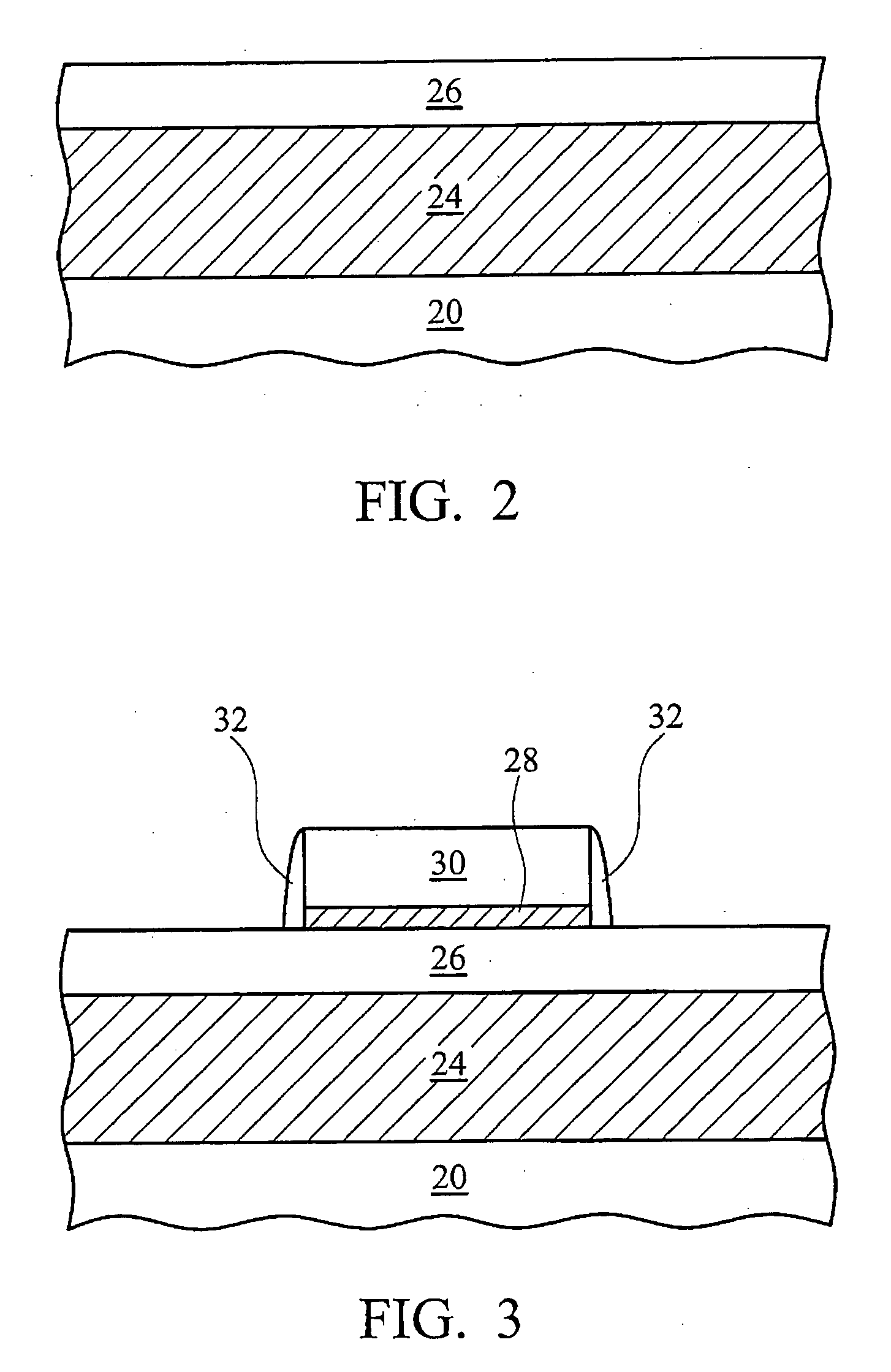

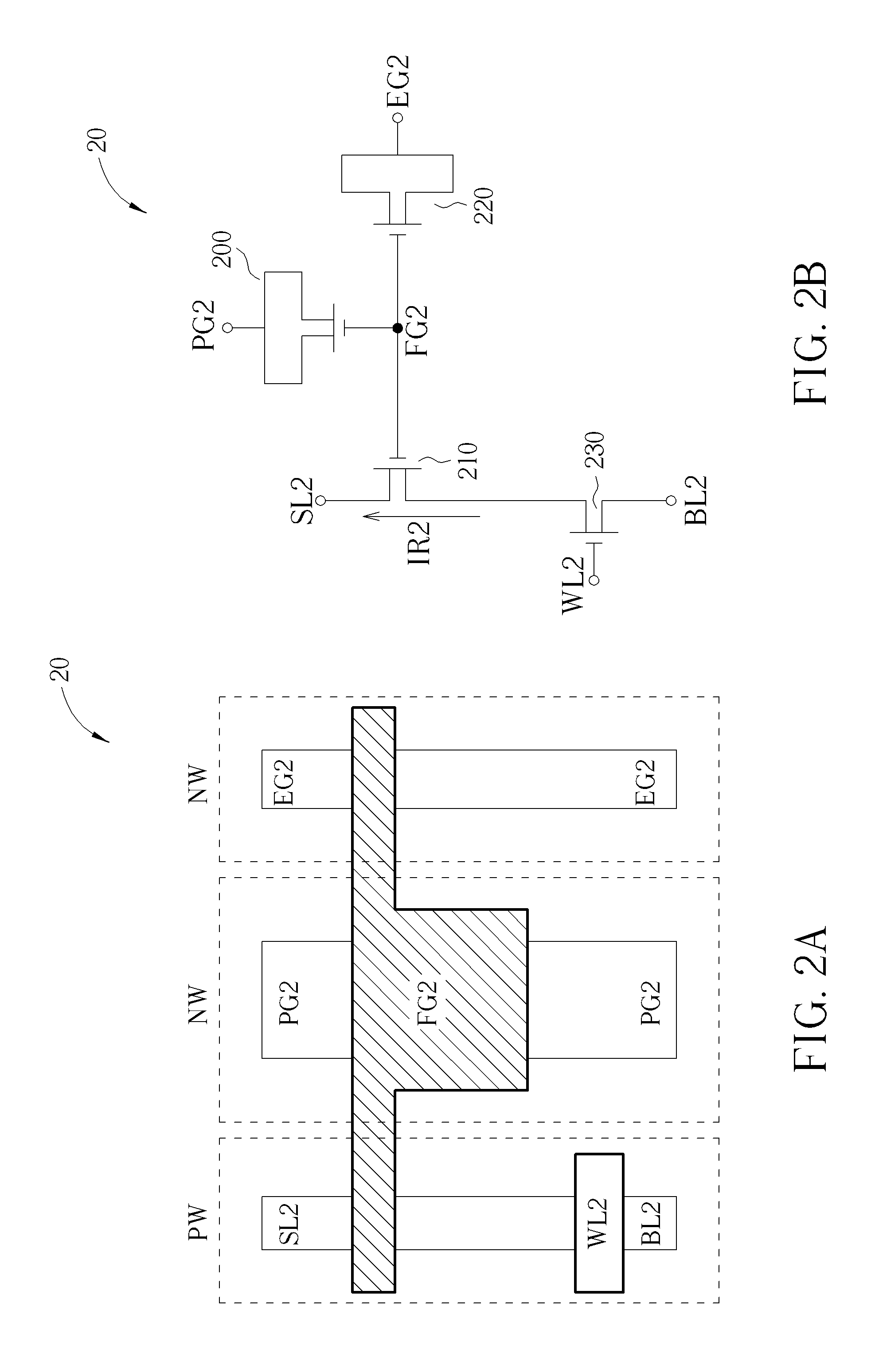

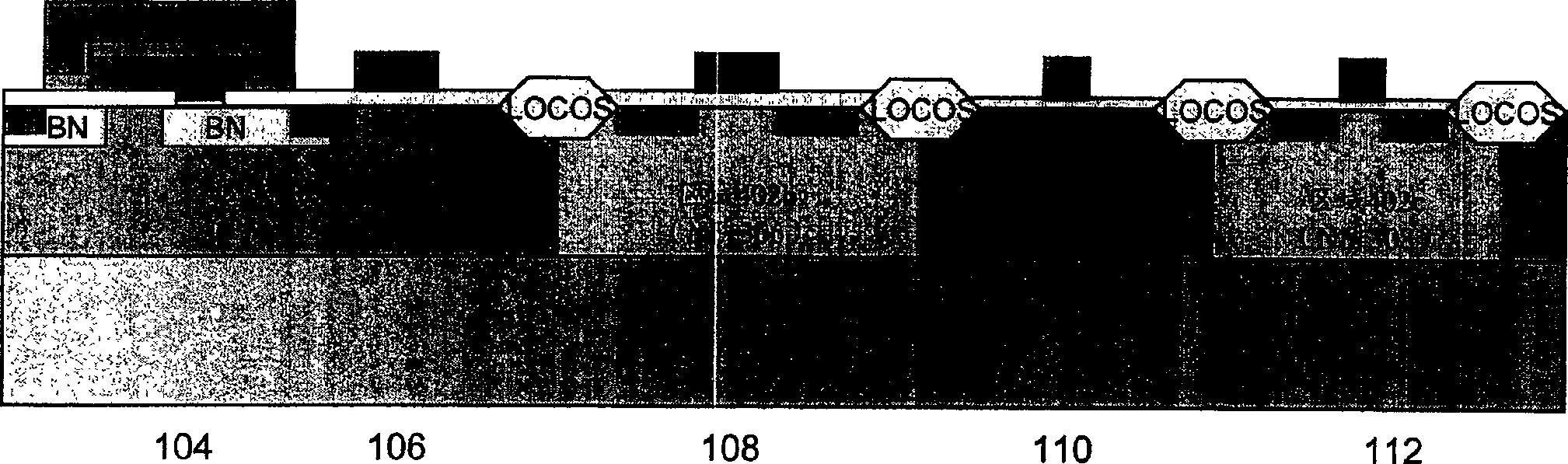

Capacitor-less 1T-DRAM cell with Schottky source and drain

InactiveUS20060125121A1Improve equipment reliabilityLower bandgapTransistorSolid-state devicesCapacitanceGate dielectric

A tunneling injection based Schottky source / drain memory cell comprising: a first semiconductor layer with a first conductivity type overlying an insulating layer, wherein the first semiconductor acts as a body region; a gate dielectric overlying the semiconductor layer; a gate electrode overlying the gate dielectric; a pair of spacers on sides of the gate electrodes; and a first Schottky barrier junction formed on a source region and a second Schottky barrier junction formed on a drain region on opposing sides of the body region. The source and the regions have an overlapping portion with the gate electrode and length of overlapping portion is preferably greater than about 5 Å. Interfacial layers are formed between the first and the second Schottky barrier regions.

Owner:TAIWAN SEMICON MFG CO LTD

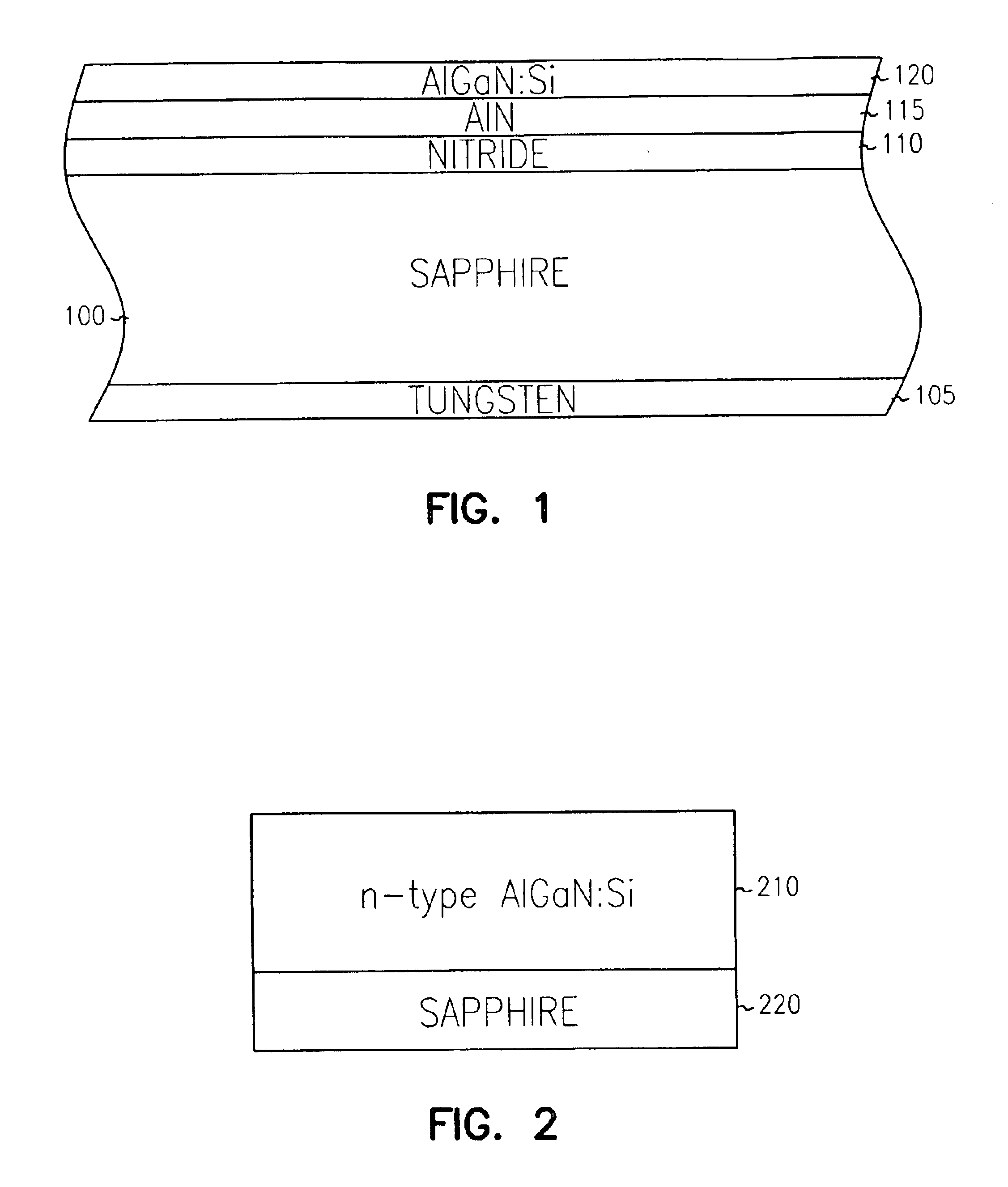

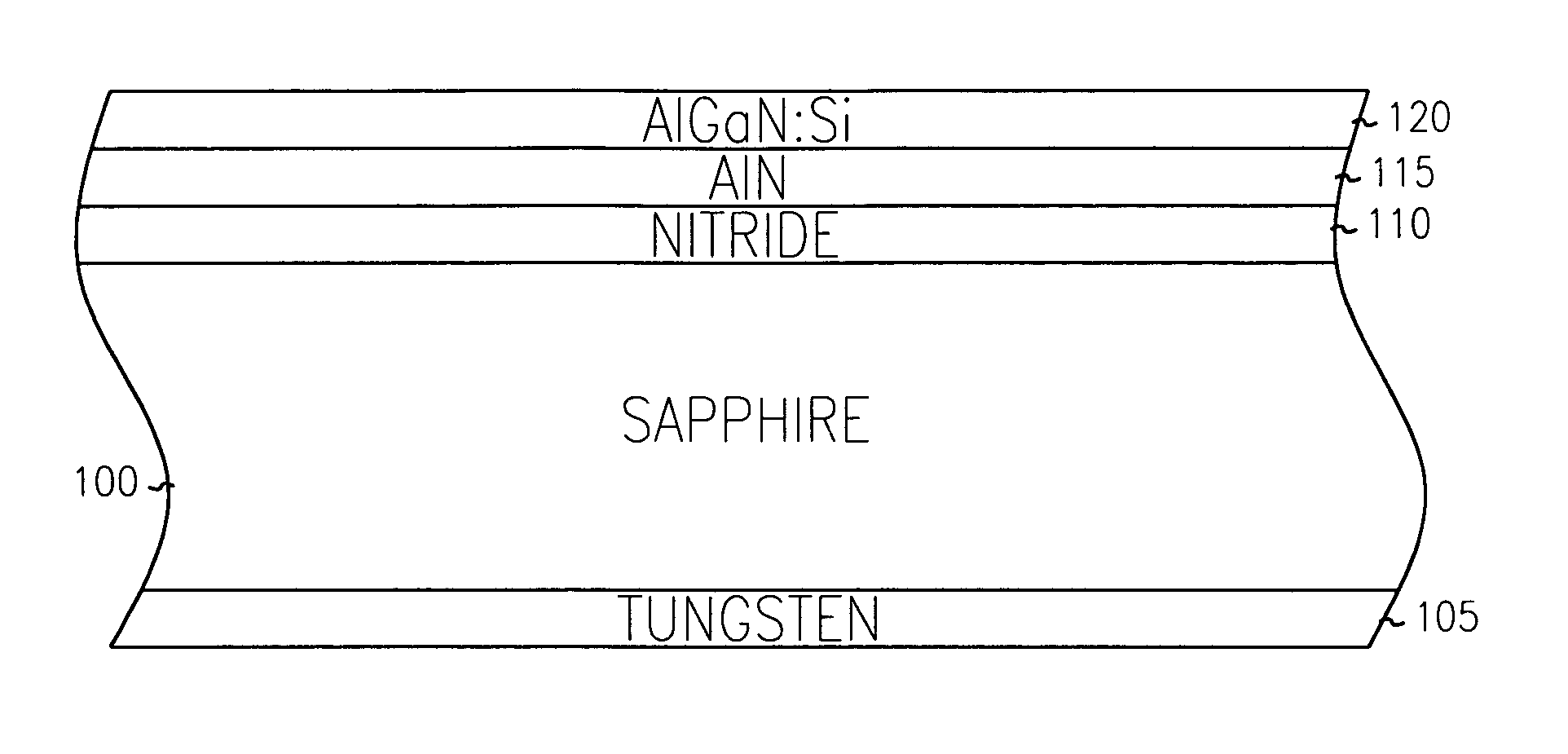

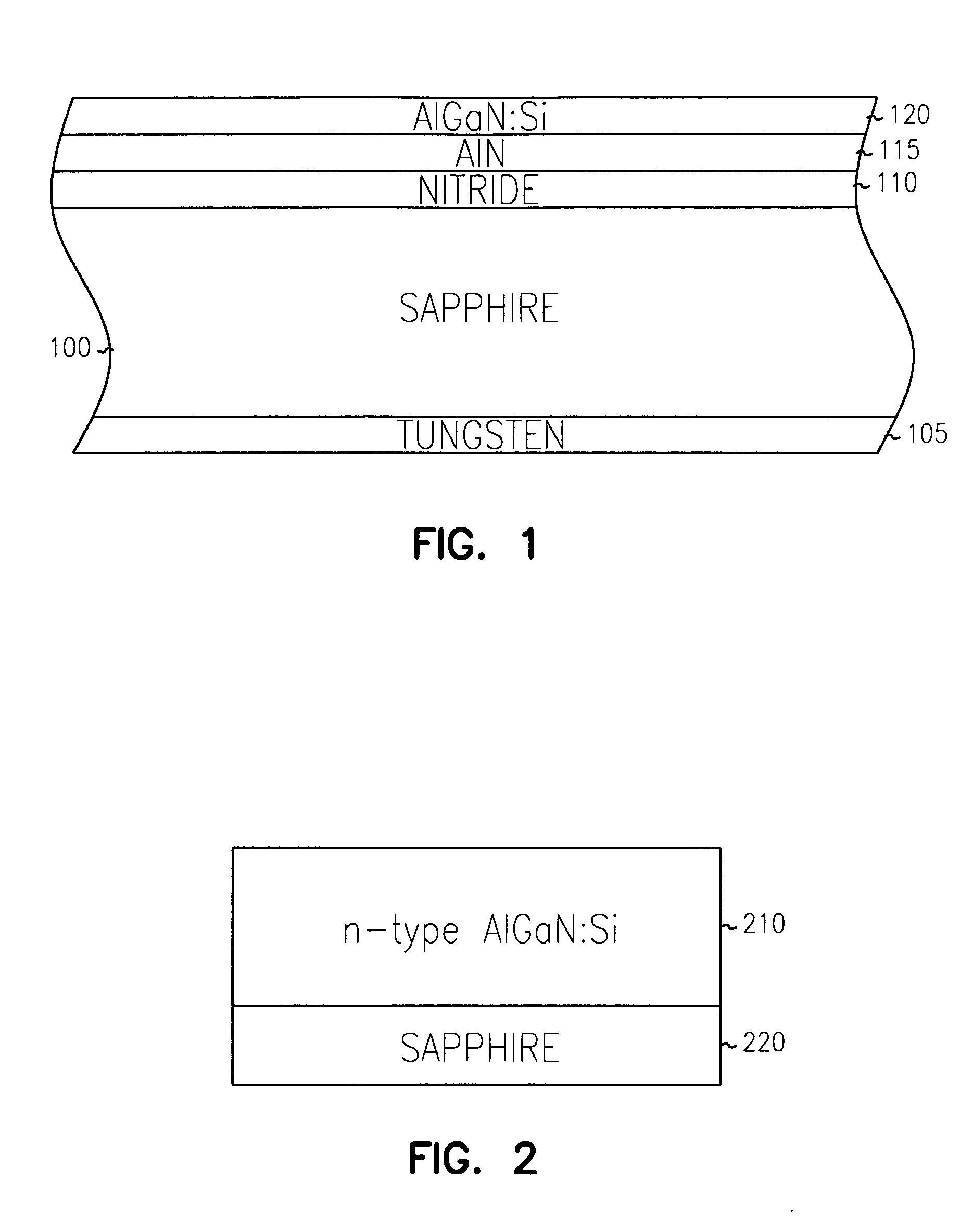

Highly doped III-nitride semiconductors

InactiveUS6888170B2Different doping densityReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesTunnel injectionElectron density

A method of forming a highly doped layer of AlGaN, is practiced by first removing contaminants from a MBE machine. Wafers are then outgassed in the machine at very low pressures. A nitride is then formed on the wafer and an AlN layer is grown. The highly doped GaAlN layer is then formed having electron densities beyond 1×1020 cm−3 at Al mole fractions up to 65% are obtained. These levels of doping application of n-type bulk, and n / p tunnel injection to short wavelength UV emitters. Some applications include light emitting diodes having wavelengths between approximately 254 and 290 nm for use in fluorescent light bulbs, hazardous materials detection, water purification and other decontamination environments. Lasers formed using the highly doped layers are useful in high-density storage applications or telecommunications applications. In yet a further embodiment, a transistor is formed utilizing the highly doped layer as a channel.

Owner:CORNELL RES FOUNDATION INC

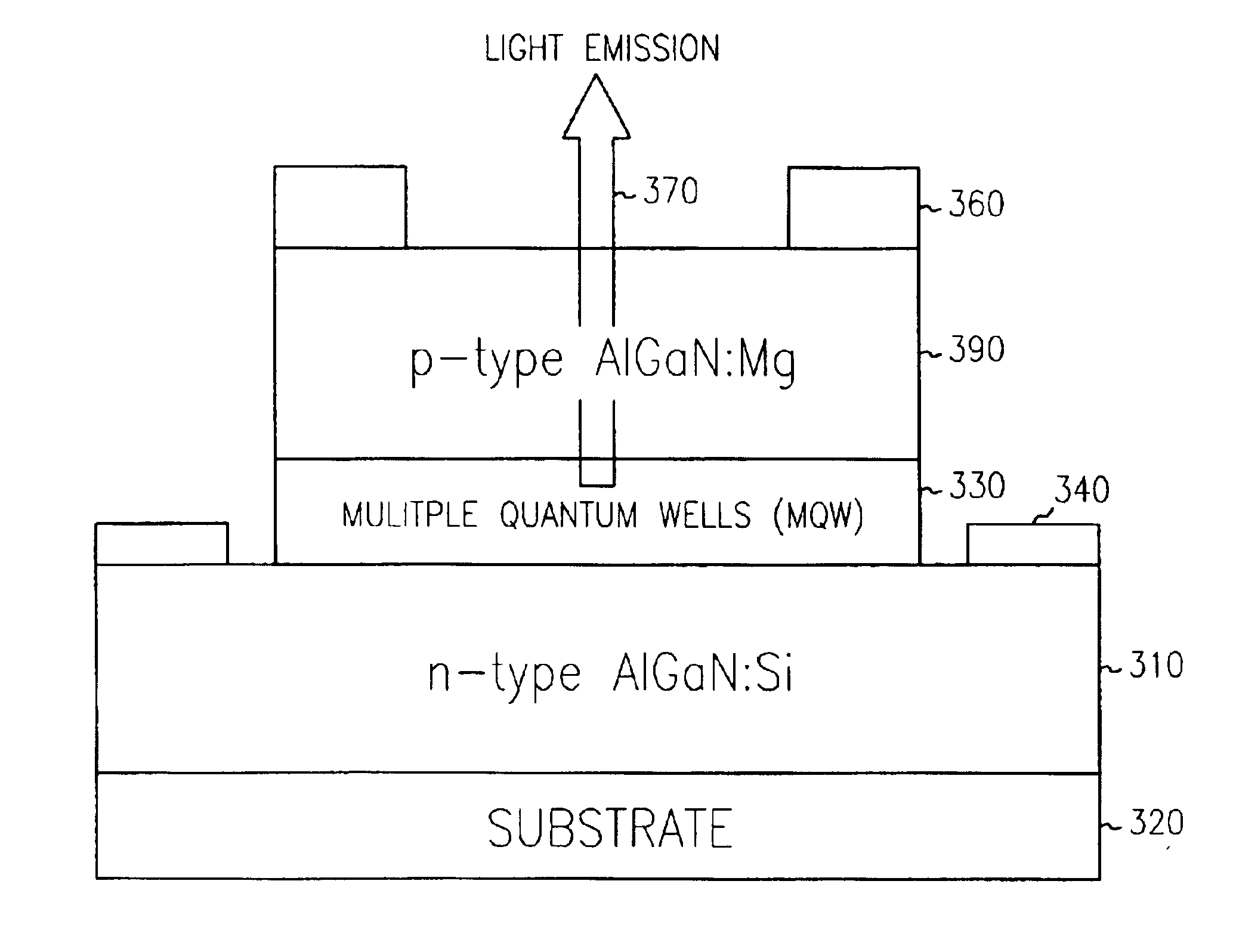

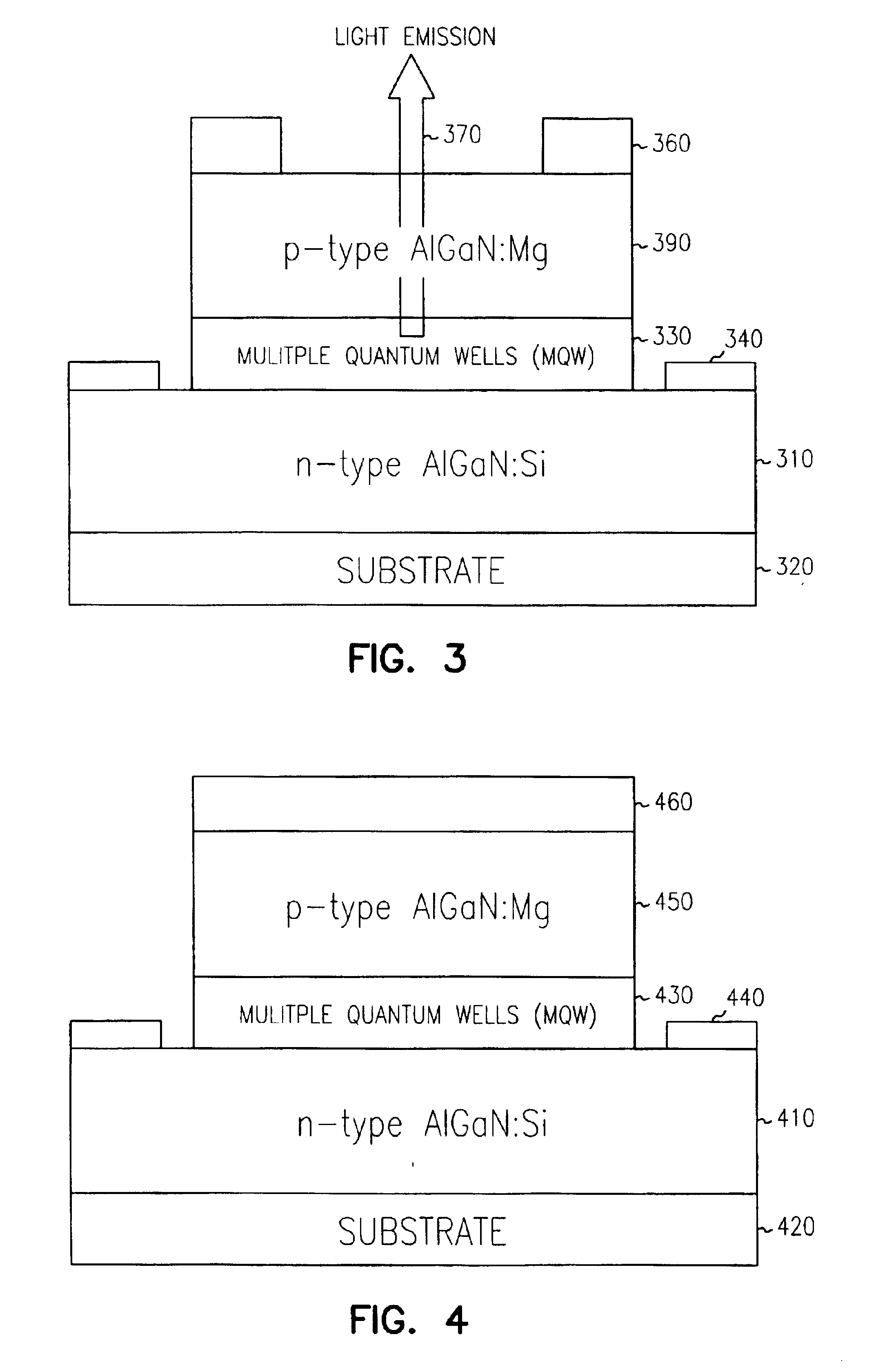

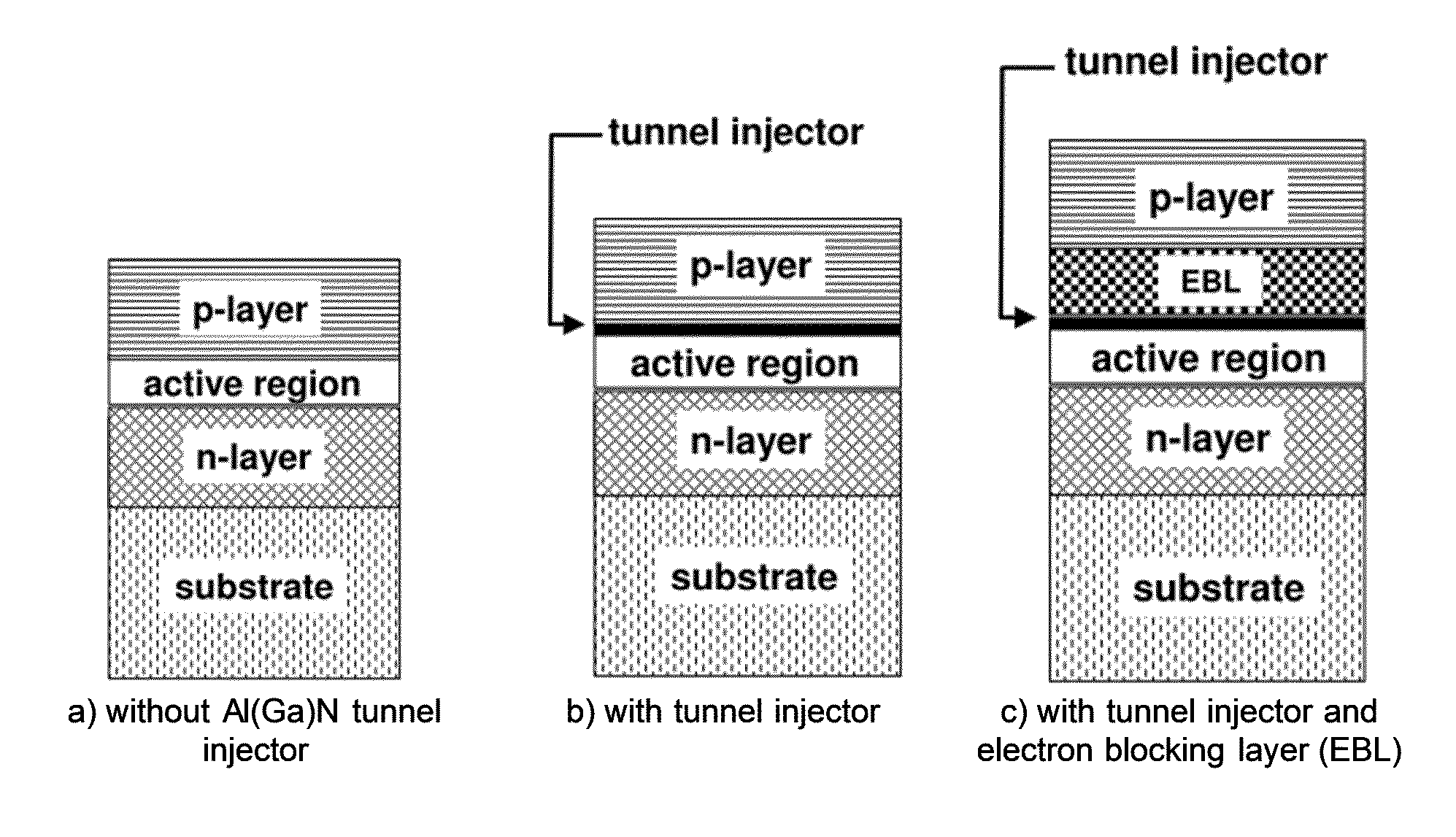

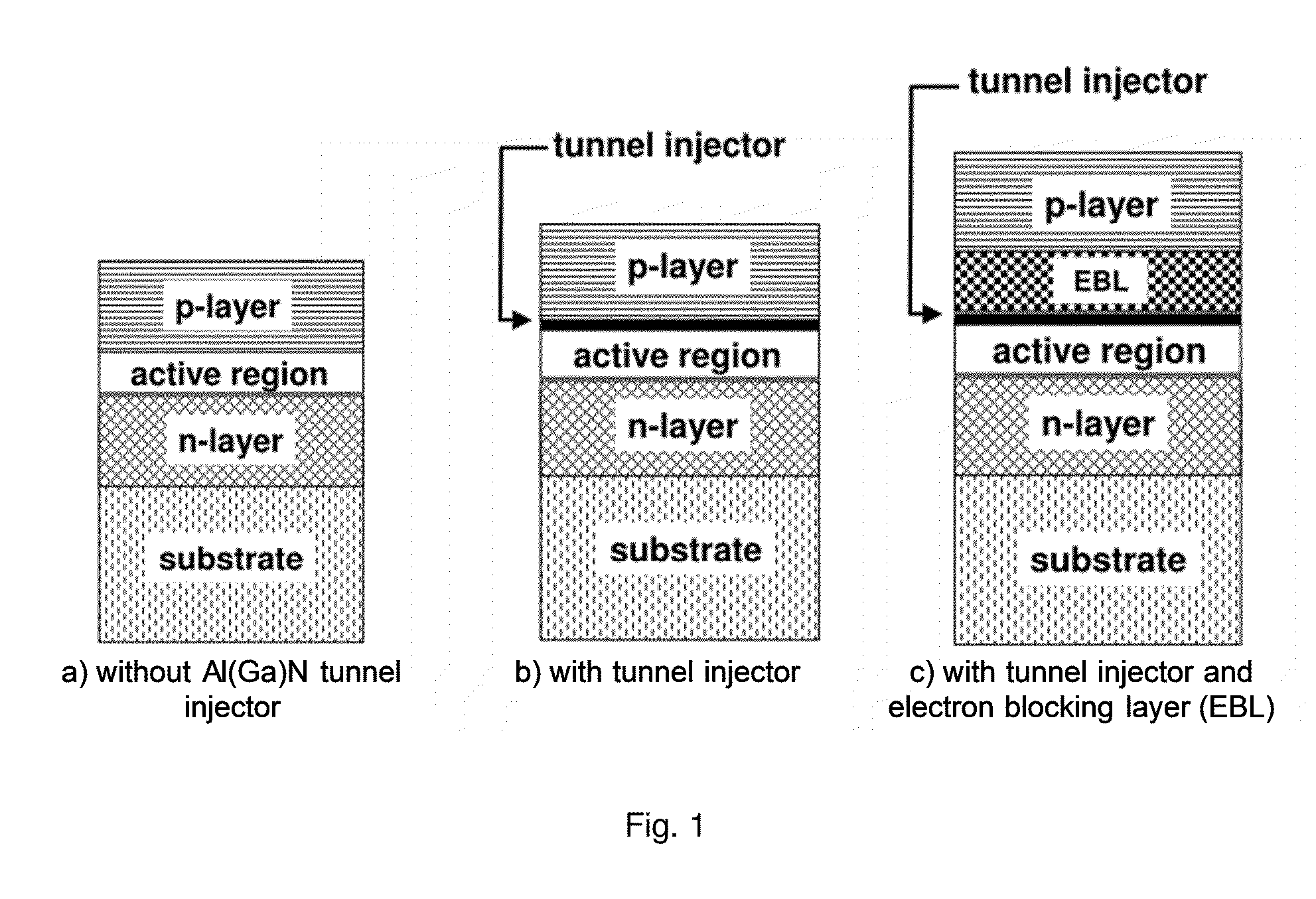

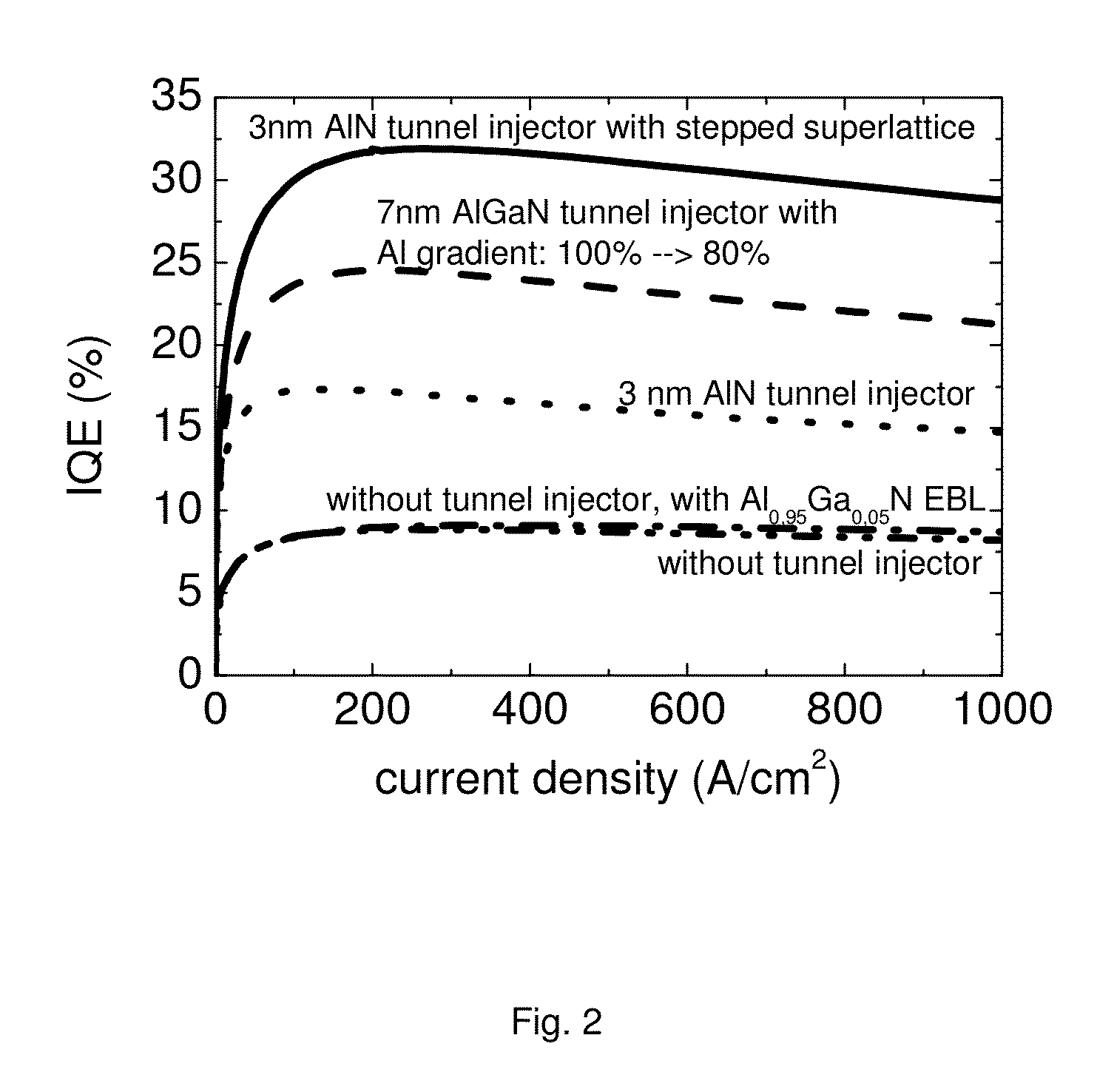

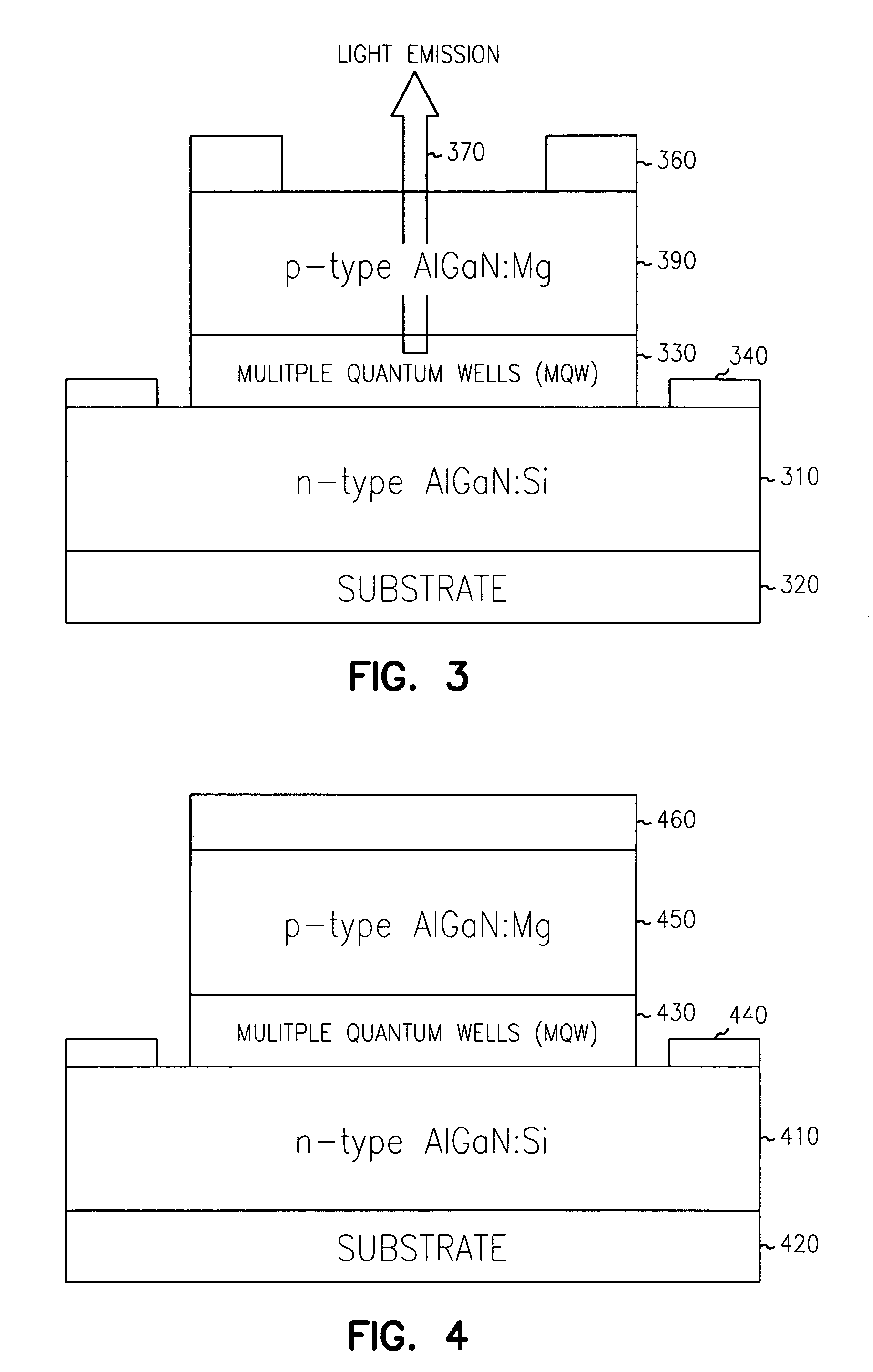

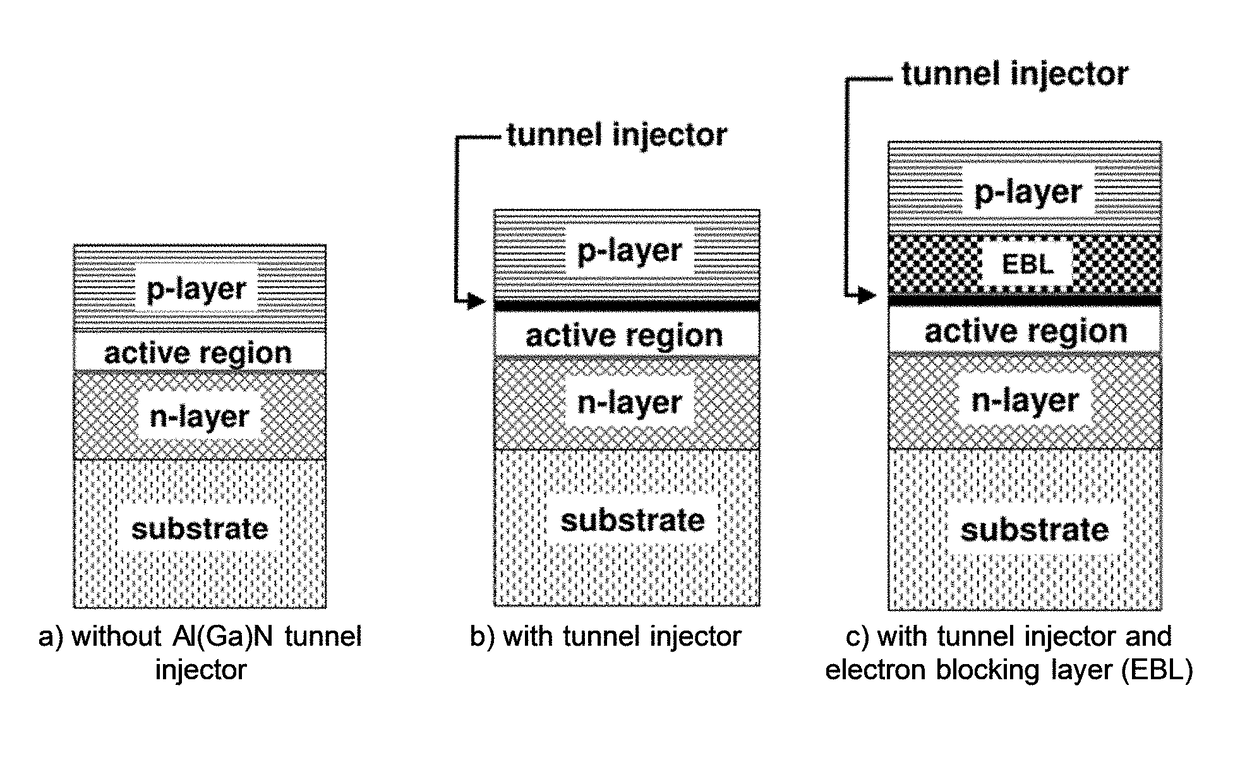

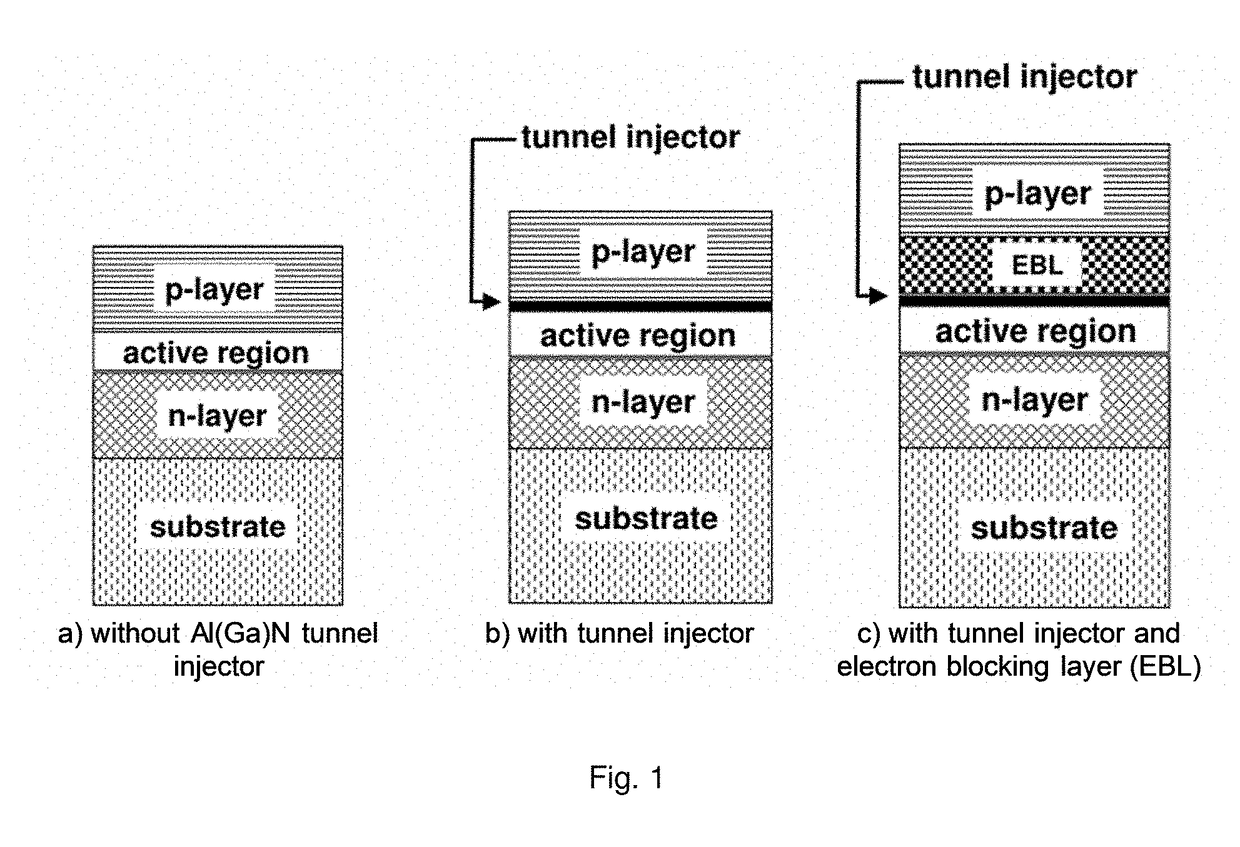

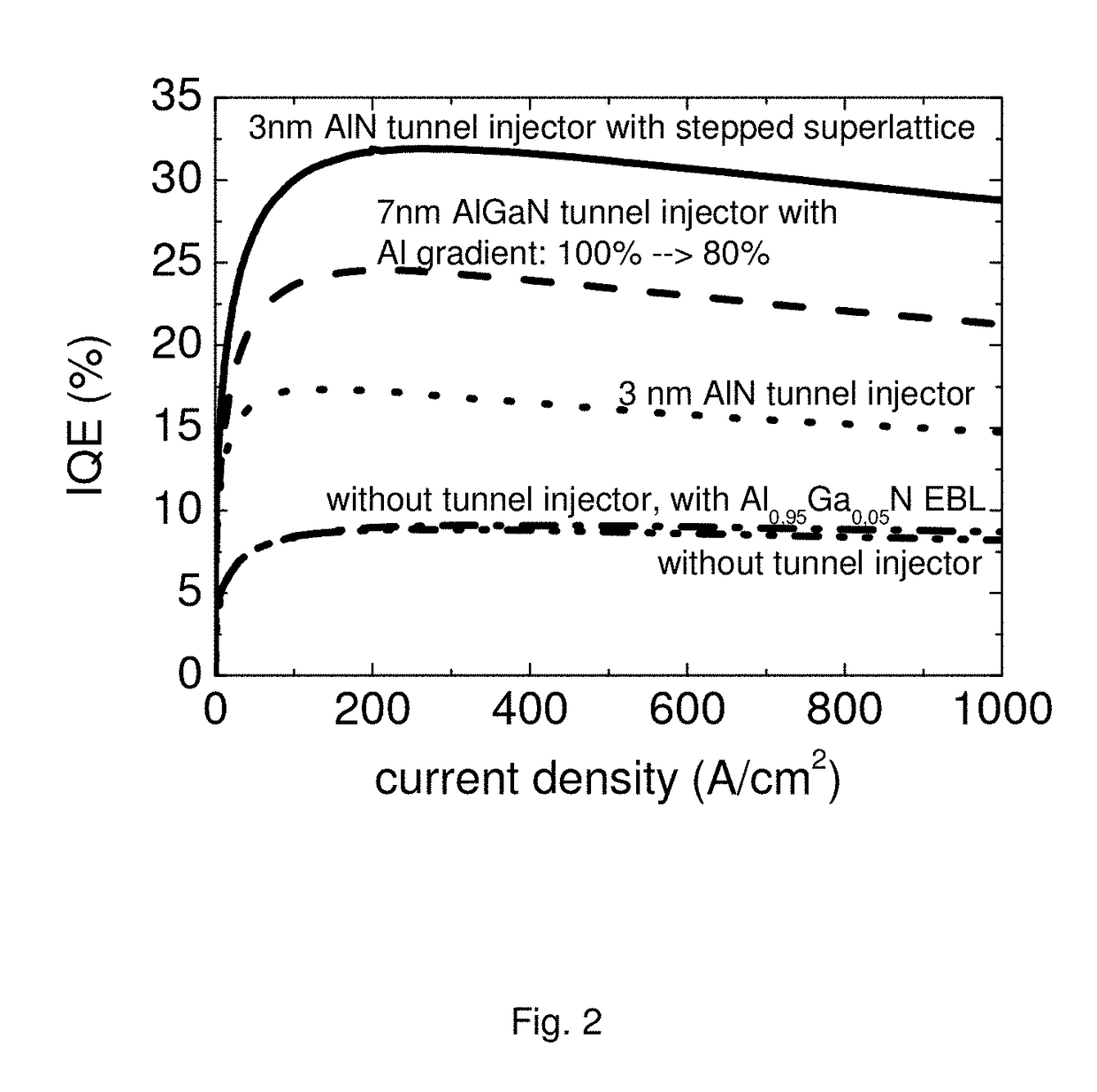

UV LED with tunnel-injection layer

ActiveUS20130277642A1Reduces ancillary luminescenceImprove external quantum efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesTunnel injectionUltraviolet lights

An ultraviolet (UV) light emitting structure, a UV light emitting device, and a method of making a UV light emitting structure or device, wherein the UV light emitting structure or device has an AlN or AlGaN injection layer with high aluminum content between the light emitting active region and the p-doped layers and wherein the injection layer has a thickness such that holes can tunnel from the p-side of the semiconductor-based ultraviolet light emitting diode structure through the injection layer in the active zone and also reducing leakage electrons out of the active zone.

Owner:FERDINAND BRAUN INST GGMBH LEIBNIZ INST FUR HOCHSTFREQUENZTECHNIK +2

Magnetic memory device and method of fabricating the same

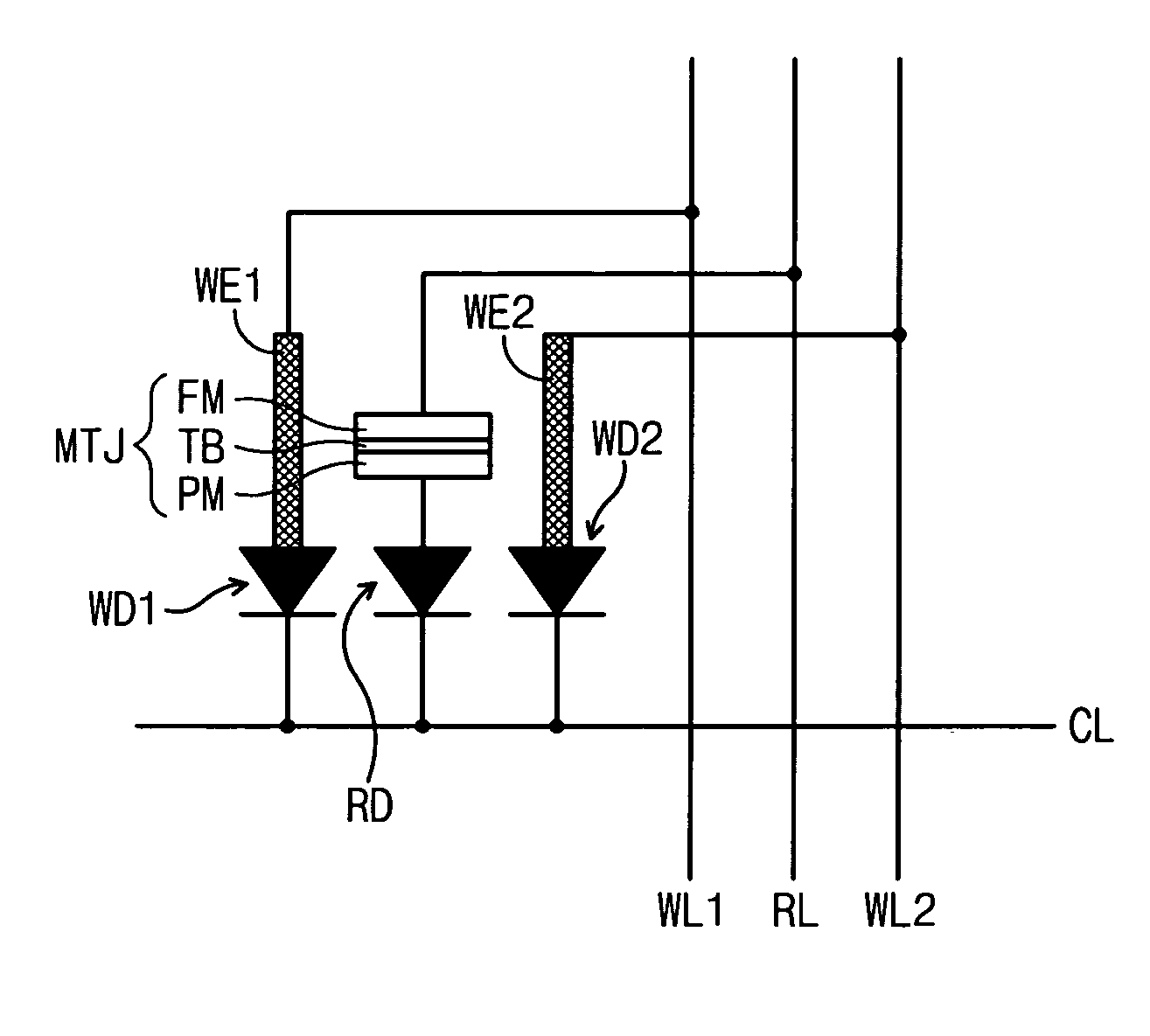

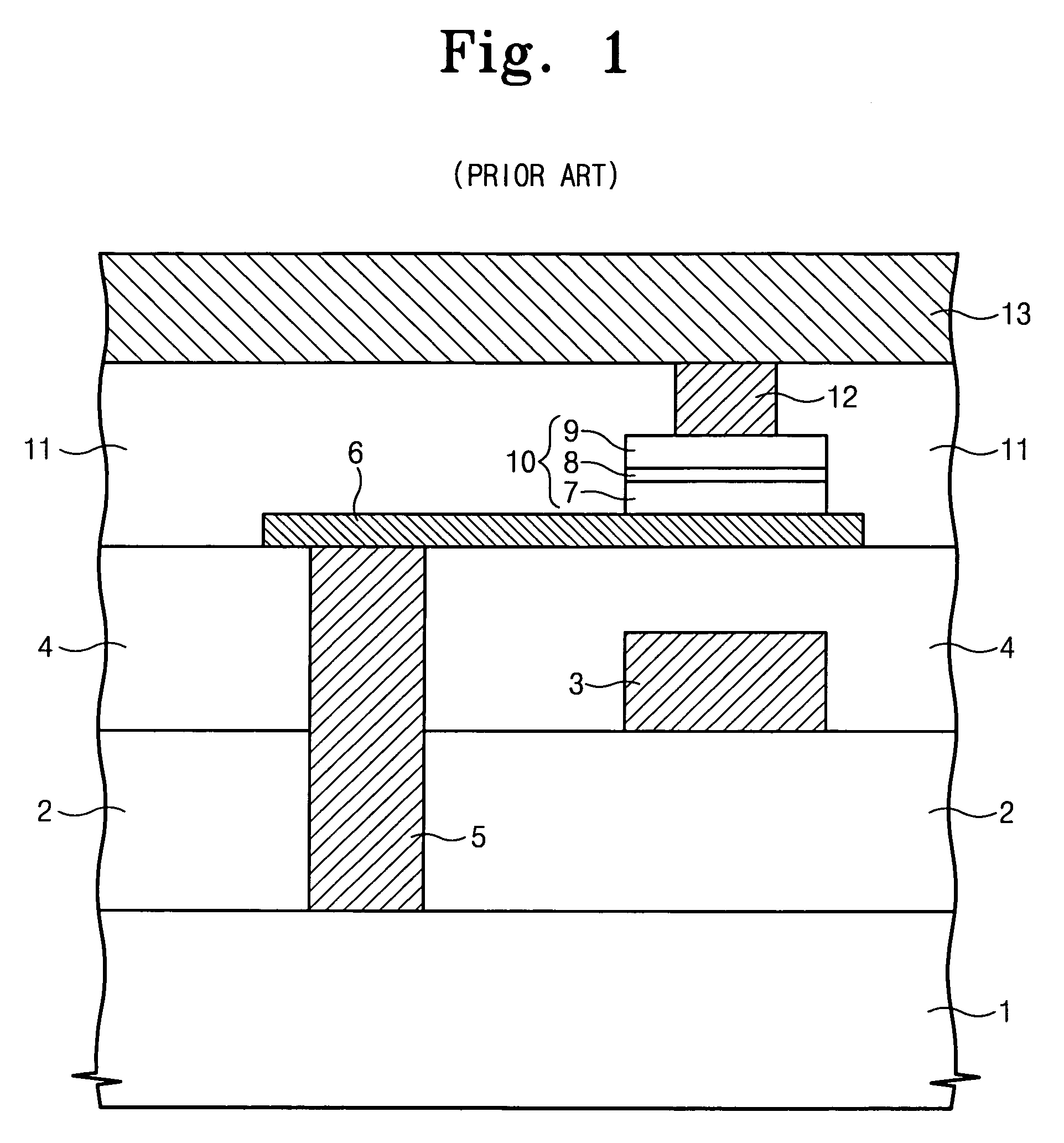

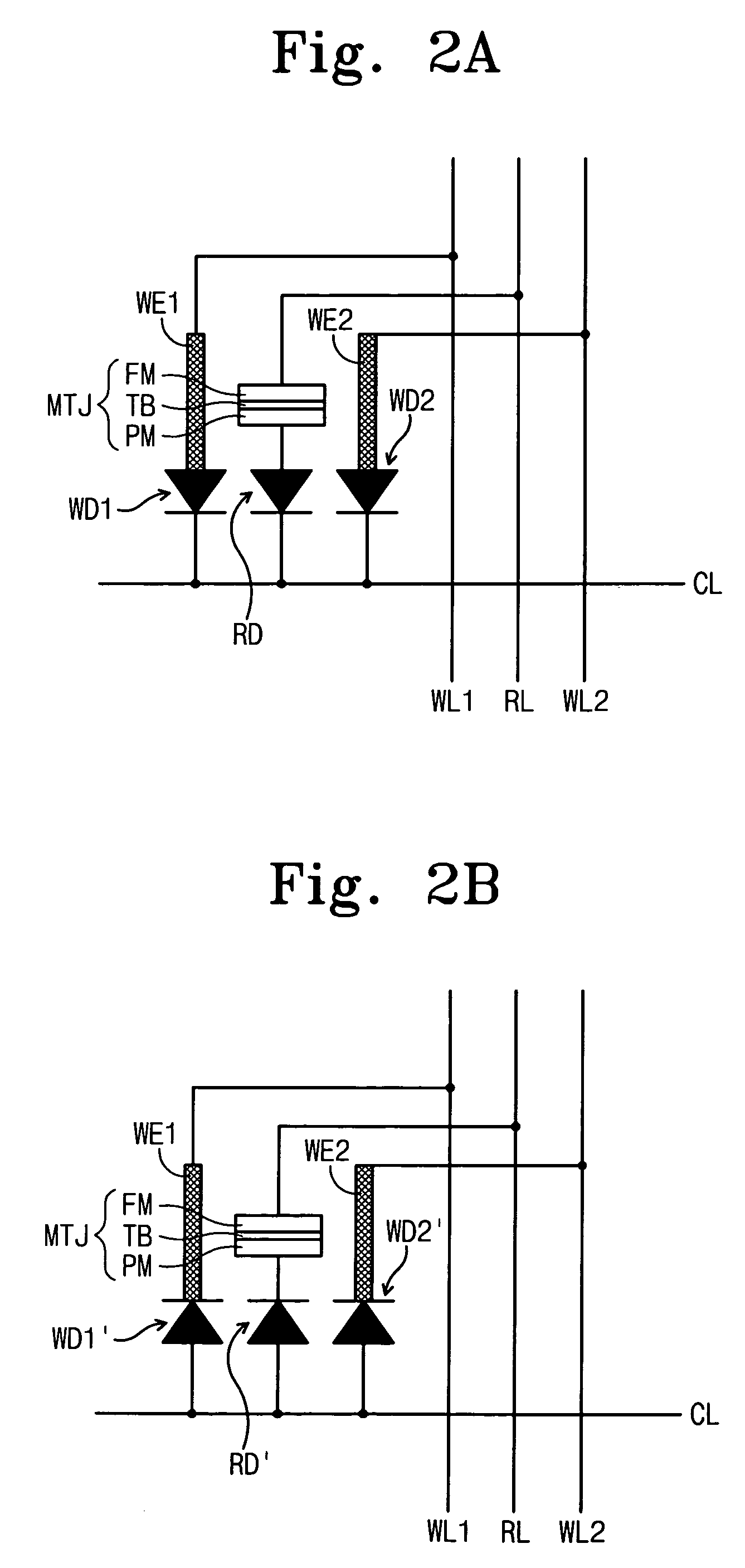

A magnetic memory device includes a common line; a first write-in diode, a readout diode and a second write-in diode being connected to the common line in parallel. The magnetic memory device further includes a magnetic tunnel junction structure connected to the readout diode, first and second write-in conductors disposed at both sides of the magnetic tunnel junction structure and connected to the first and second write-in diodes, respectively and a first write-in line, a readout line and a second write-in line, which are connected to the first write-in conductor, the magnetic tunnel injection structure, and the second write-in conductor, respectively.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for mfg. double layer polysilicon rewritable non-volatile memory

ActiveCN1719595ASimple processShort processing cycleSemiconductor/solid-state device manufacturingLow voltageEngineering

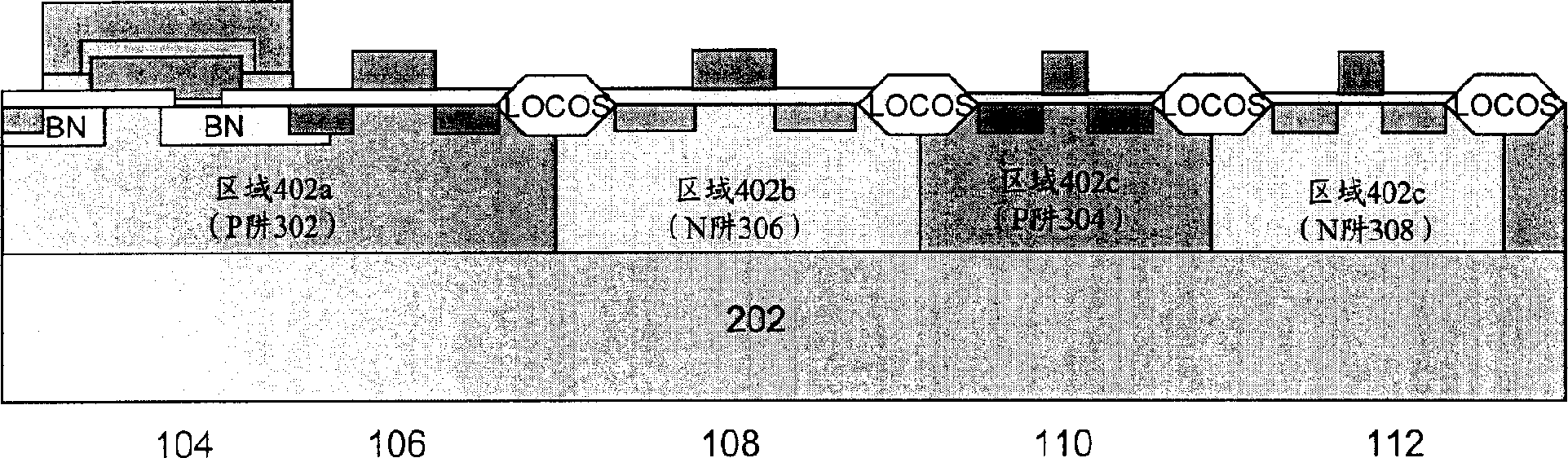

This invention provides a method for manufacturing double-layer polysilicons to re-write fixed storages including the following steps: forming trap N and trap P of high and low voltage MOS devices and multiple isolation zones, carrying out ionic injection dope in a tunnel injection zone of the storage unit, forming a grid oxidation layer of the storage unit, a tunnel penetration window thin grid oxidation layer, polysilicon floating grid and lower electrode of the condenser, depositing ONO complex medium layer and etching it, re-forming a thick grid oxidation layer in the region corresponding to the high voltage MOS device and forming its thin grid oxidation layer corresponding to the low voltage MOS device, depositing a second polysilicon and etching the control grid forming the storage unit and the logic grid forming MOS devices and the upper electrode of the condenser to dope the storage unit, source and drain of the MOS devices.

Owner:ADVANCED SEMICON MFG CO LTD

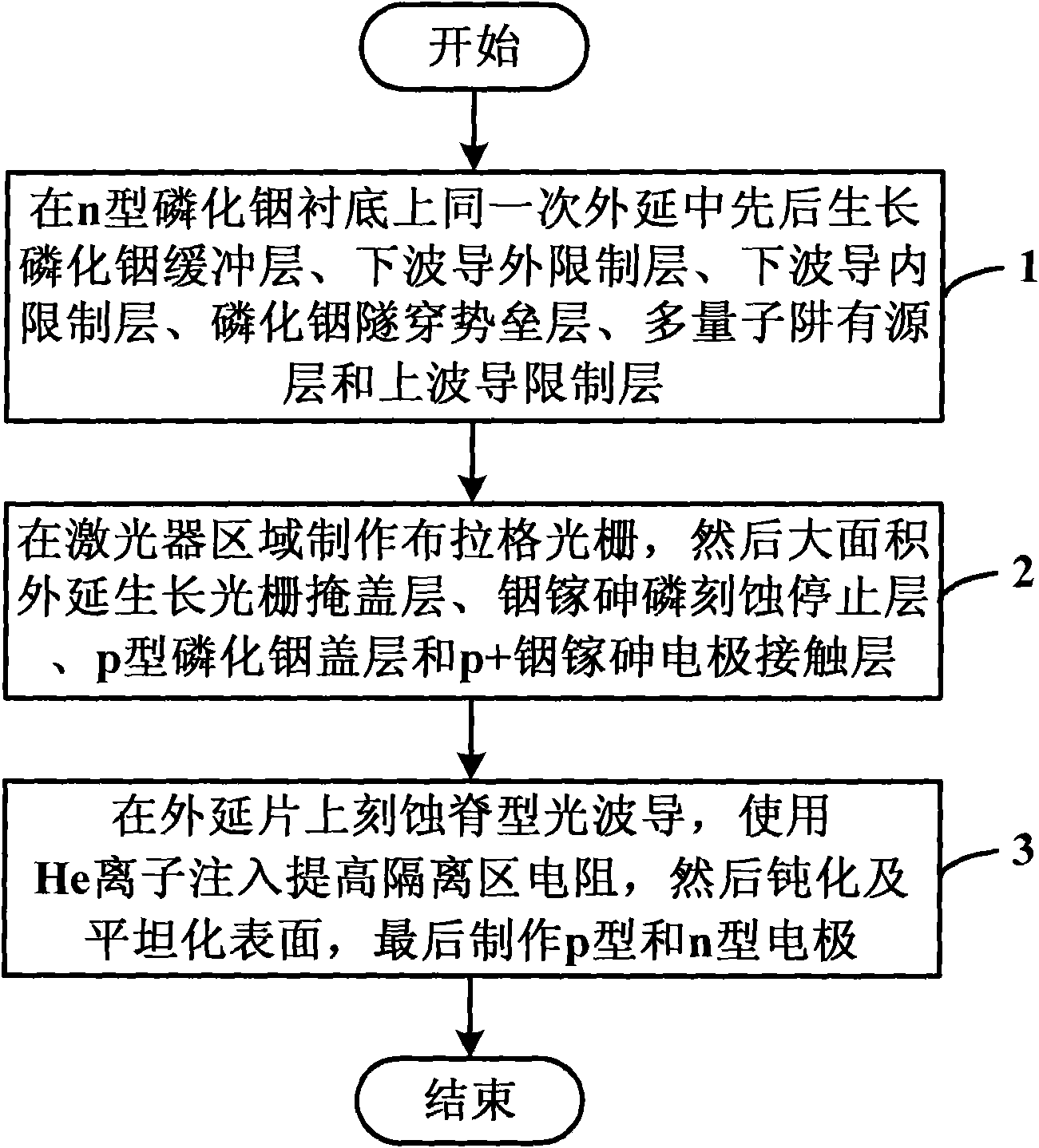

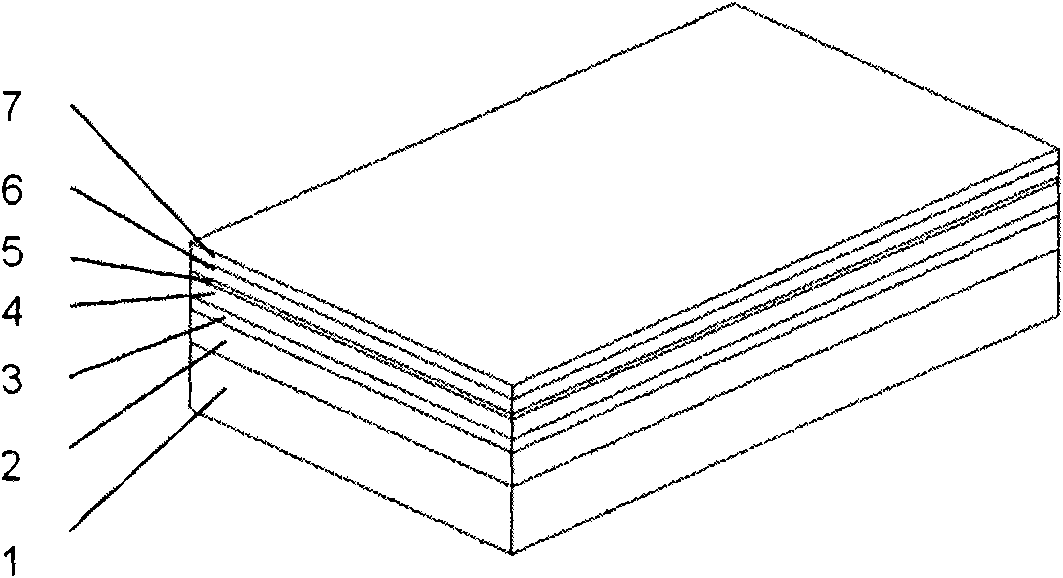

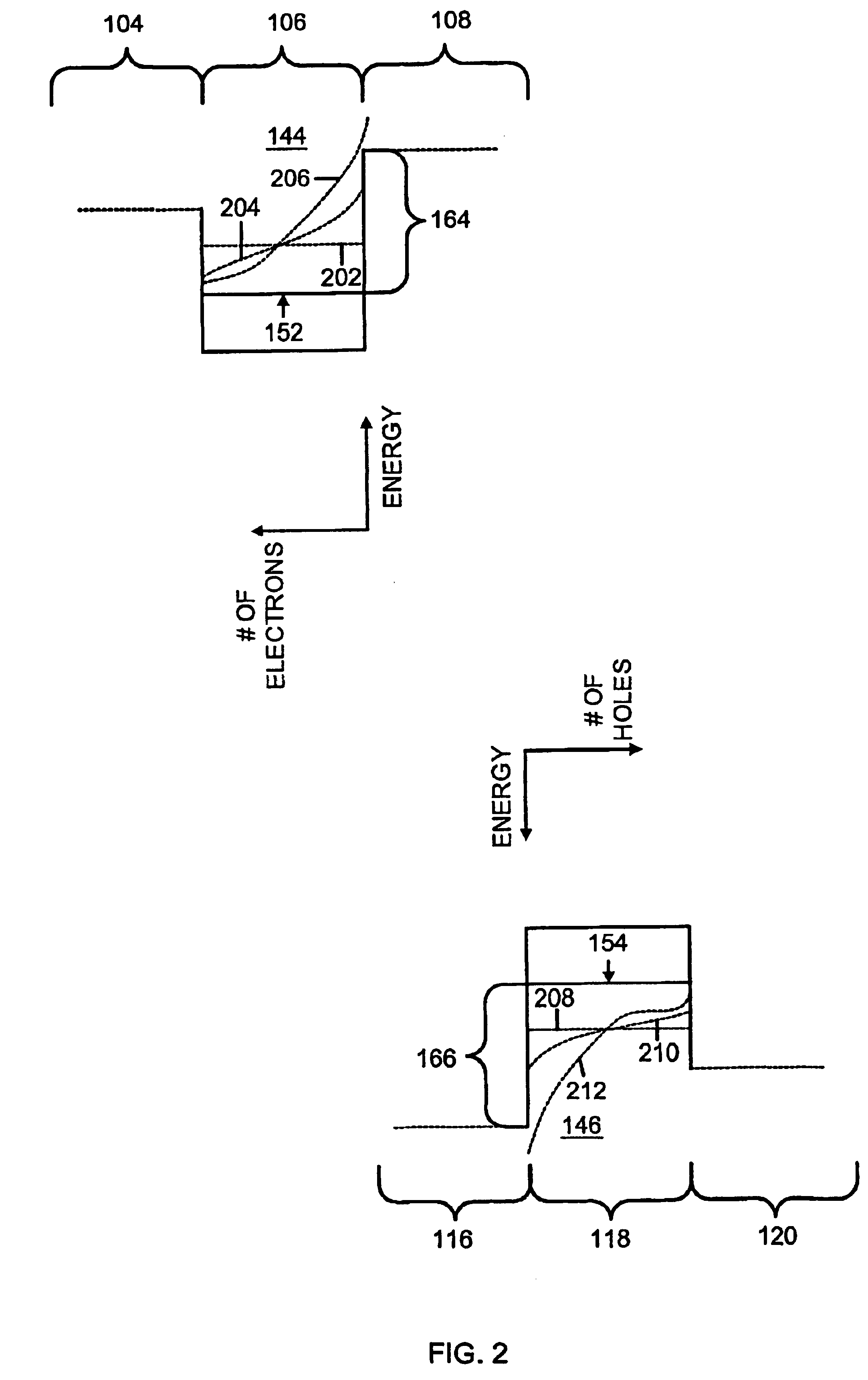

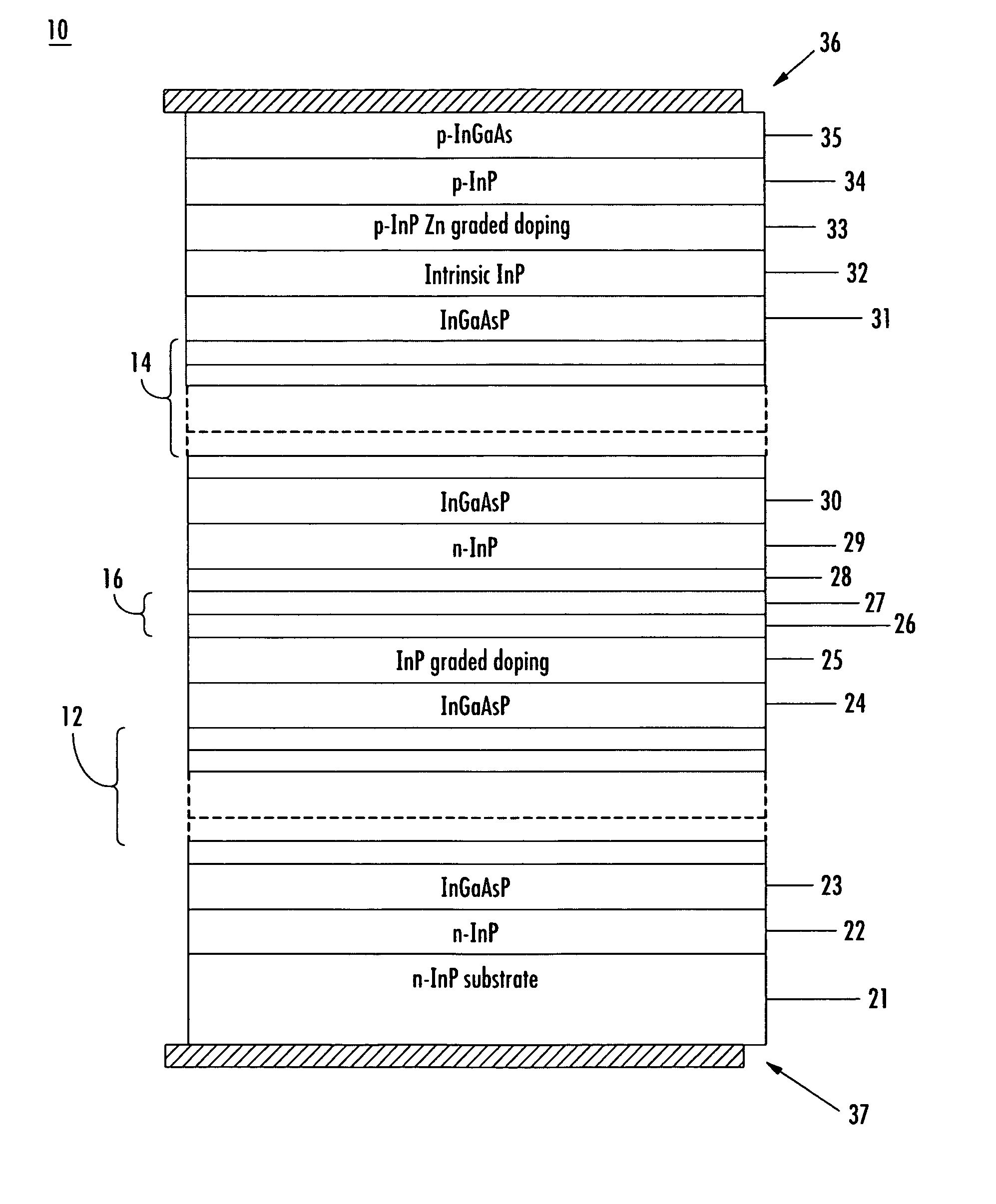

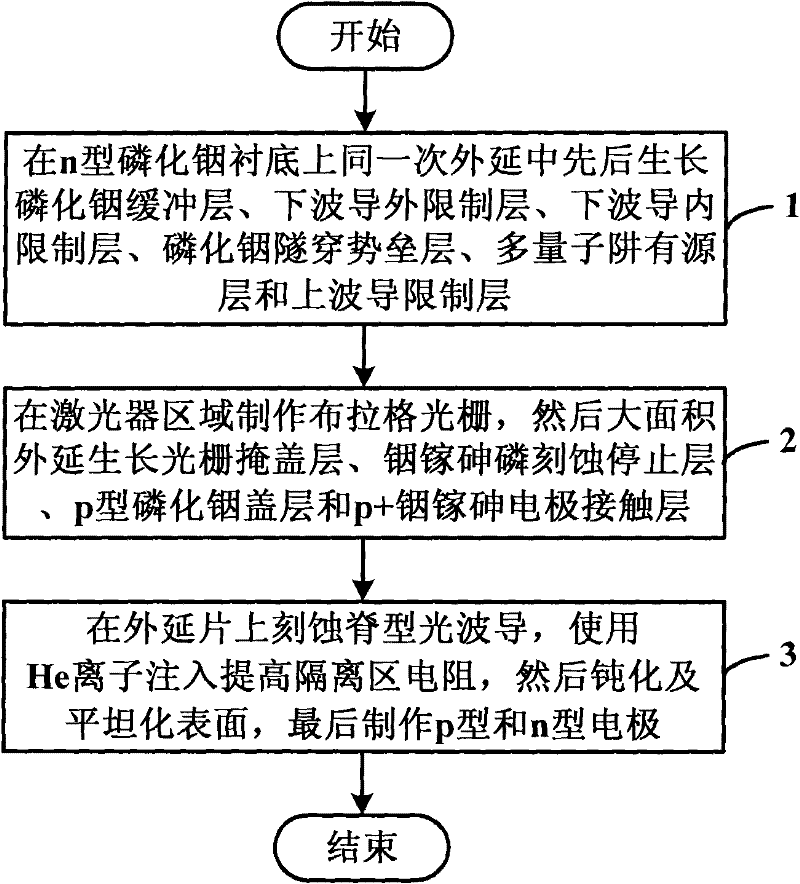

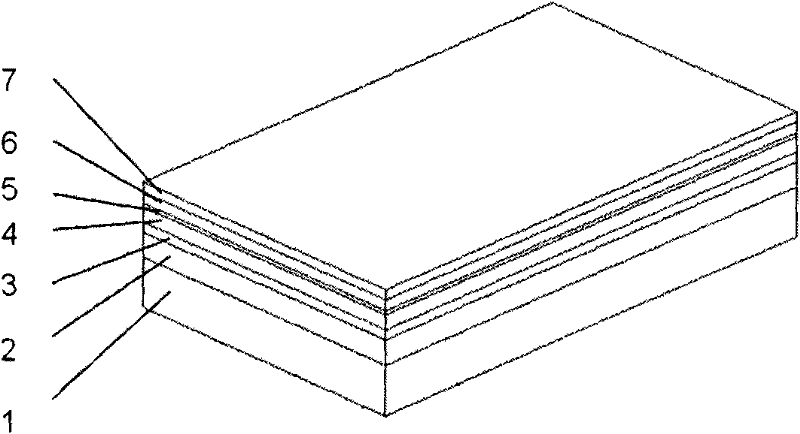

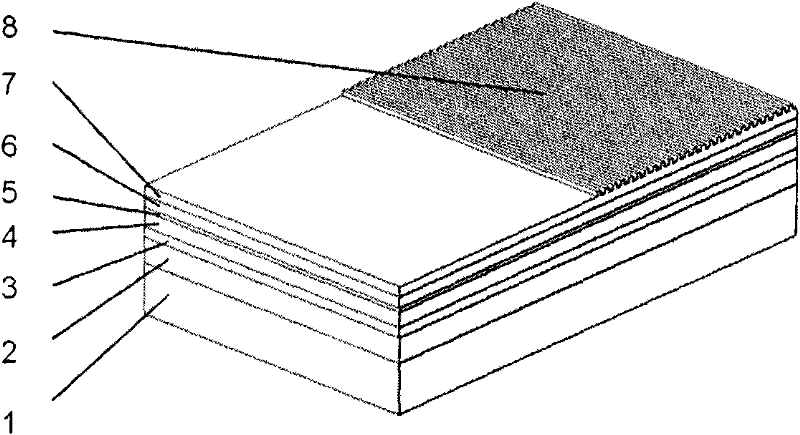

Making method of electrical absorption modulation tunneling injection type distributed feedback semiconductor laser

InactiveCN102055133AEliminate performance impactRaise the characteristic temperatureLaser detailsLaser output parameters controlGratingElectrode Contact

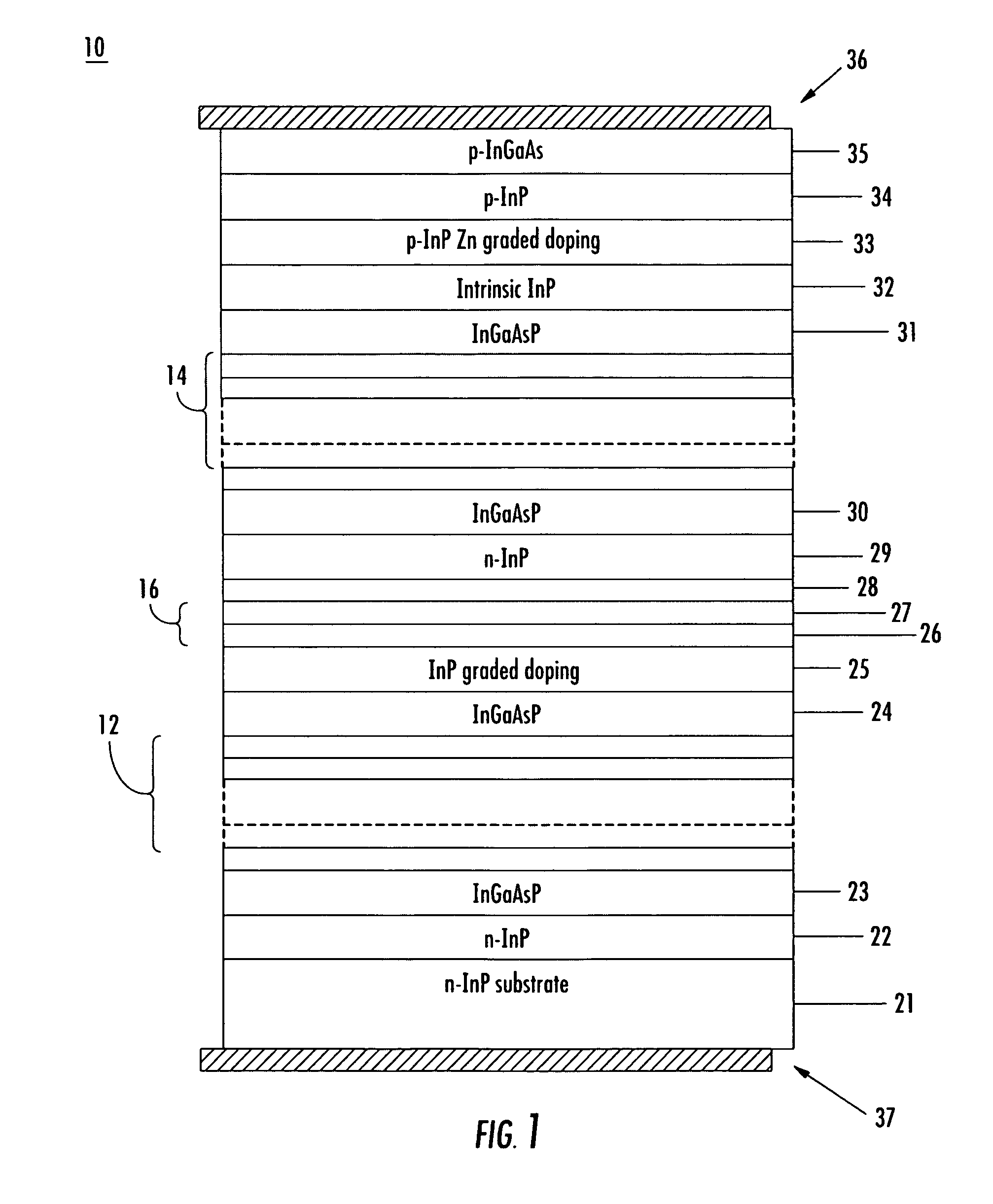

The invention discloses a making method of an electrical absorption modulation tunneling injection type distributed feedback semiconductor laser, which comprises the following steps of: 1, growing an n-type indium phosphide buffer layer, a lower waveguide external limit layer, a lower waveguide internal limit layer, an indium phosphide tunneling barrier layer, a multiple quantum well active layer and an upper waveguide limit layer on an n-type indium phosphide substrate during the same epitaxy; 2, making a Bragg grating in a laser region, then epitaxially growing a p-type indium phosphide grating covering layer, an InGaAsP etching stopping layer, a p-type indium phosphide covering layer and a p+ InGaAs electrode contact layer largely; and 3, etching a ridge type optical waveguide on an epitaxial wafer, injecting with He ions to improve the resistance of an isolation region, and then passivating and flatting the surface and finally making a p-type and an n-type electrodes. The invention has the advantages of simple process and high reliability, eliminates the influence of hot electrons on the property of the laser, improves the characteristic temperature of the laser, and can realize a certain independent optimization on the laser and a modulator.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Insulated gate tunnel-injection device having heterojunction and method for manufacturing the same

InactiveUS7217950B2Improve mobilitySemiconductor/solid-state device manufacturingDiodeHeterojunctionTunnel injection

The present invention-provides a tunnel-injection device which encompasses, a reception layer made of a first semiconductor, a barrier-forming layer made of a second semiconductor having a bandgap-narrower than the first semiconductor, being in metallurgical contact with the reception layer, a gate insulating film disposed on the barrier-forming layer. The gate electrode controls the width of the barrier generated at the heterojunction interface between the reception layer and the barrier-forming layer so as to change the tunneling probability of carriers through the barrier. The device further encompasses a carrier receiving region being contact with the reception layer and a carrier-supplying region being contact with the barrier-forming layer.

Owner:NISSAN MOTOR CO LTD

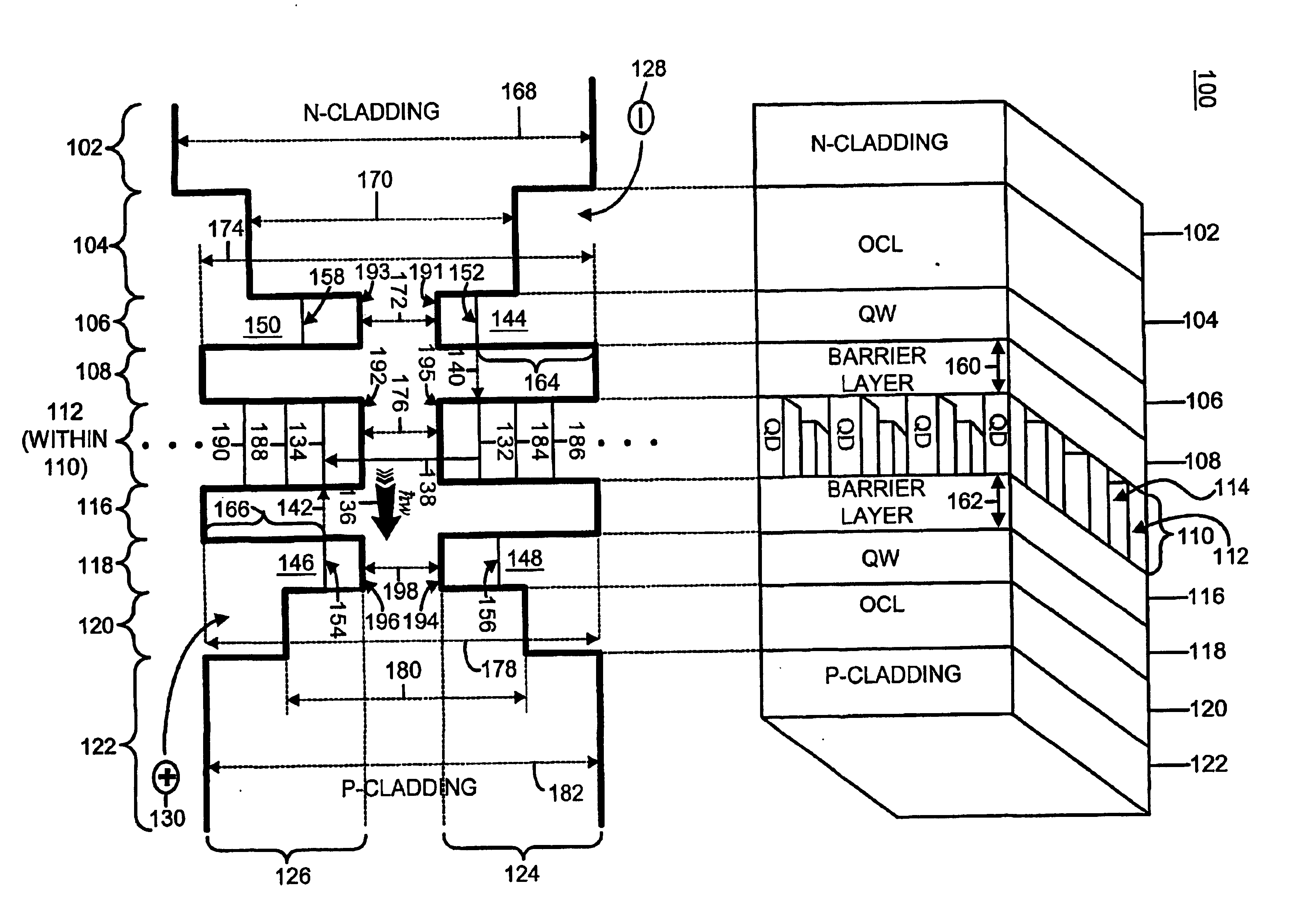

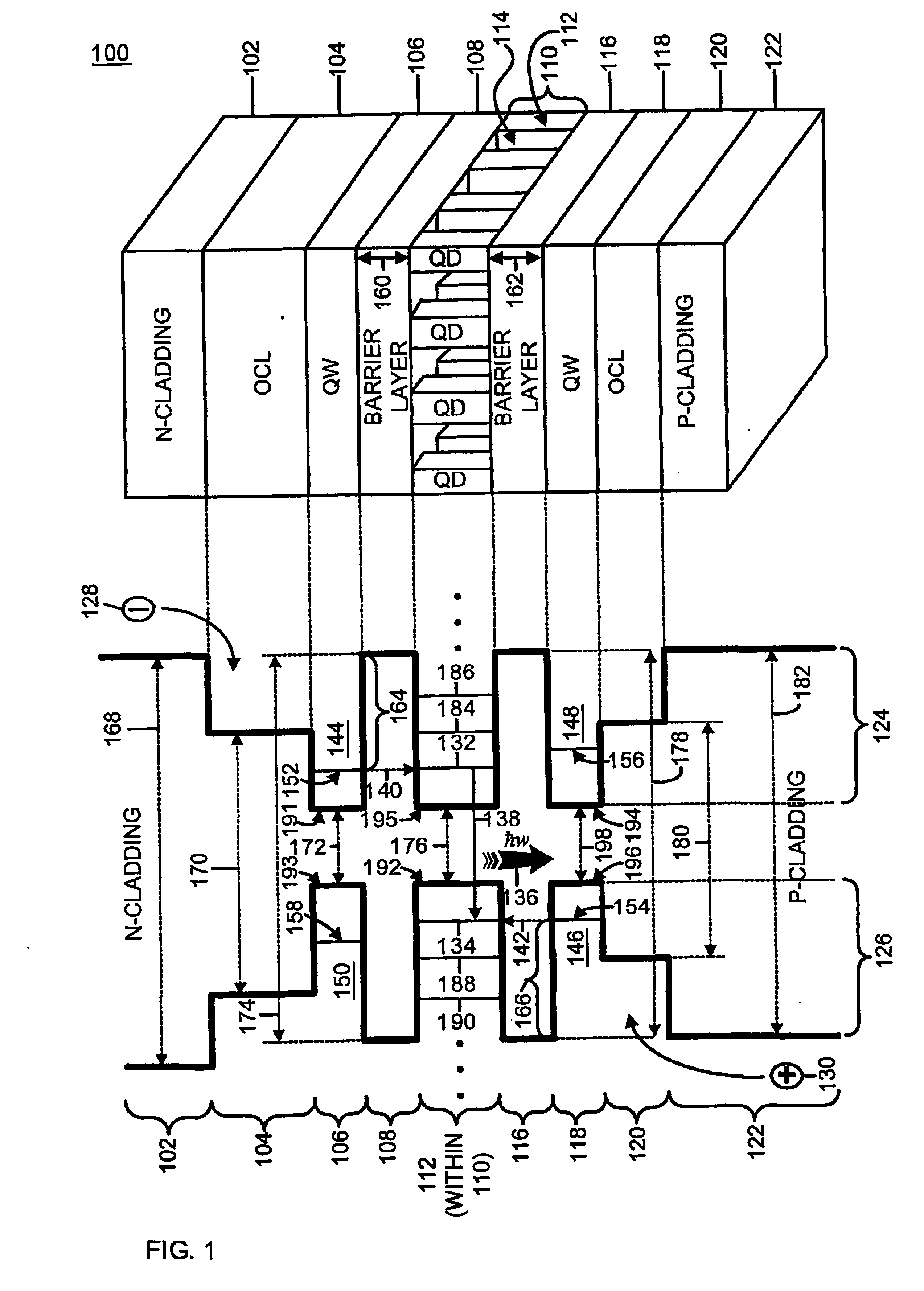

Semiconductor laser with reduced temperature sensitivity

InactiveUS6870178B2Low temperature dependenceOptical wave guidanceLaser active region structureThermionic emissionTemperature independent

A quantum dot (QD) laser having greatly reduced temperature sensitivity employs resonant tunnel-injection of carriers into the QDs from a pair of quantum wells (QWs). The carriers are injected through barrier layers. Because the tunnel-injection process is essentially temperature-independent, and because the tunnel-injection of carriers is the dominant source of current through the device, temperature-dependent currents are virtually eliminated, resulting in a device having a temperature-independent threshold current. In an additional device, carriers are injected into QDs from a pair of optical confinement layers (OCLs), either by tunnelling or thermionic emission. Each barrier layer is designed to have a low barrier height for carriers entering the QDs, and a high barrier height for carriers exiting the QDs. As a result, parasitic current from carriers leaving the QDs is greatly reduced, which enables the device to have low temperature sensitivity even without using resonant tunnel-injection and / or QWs.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

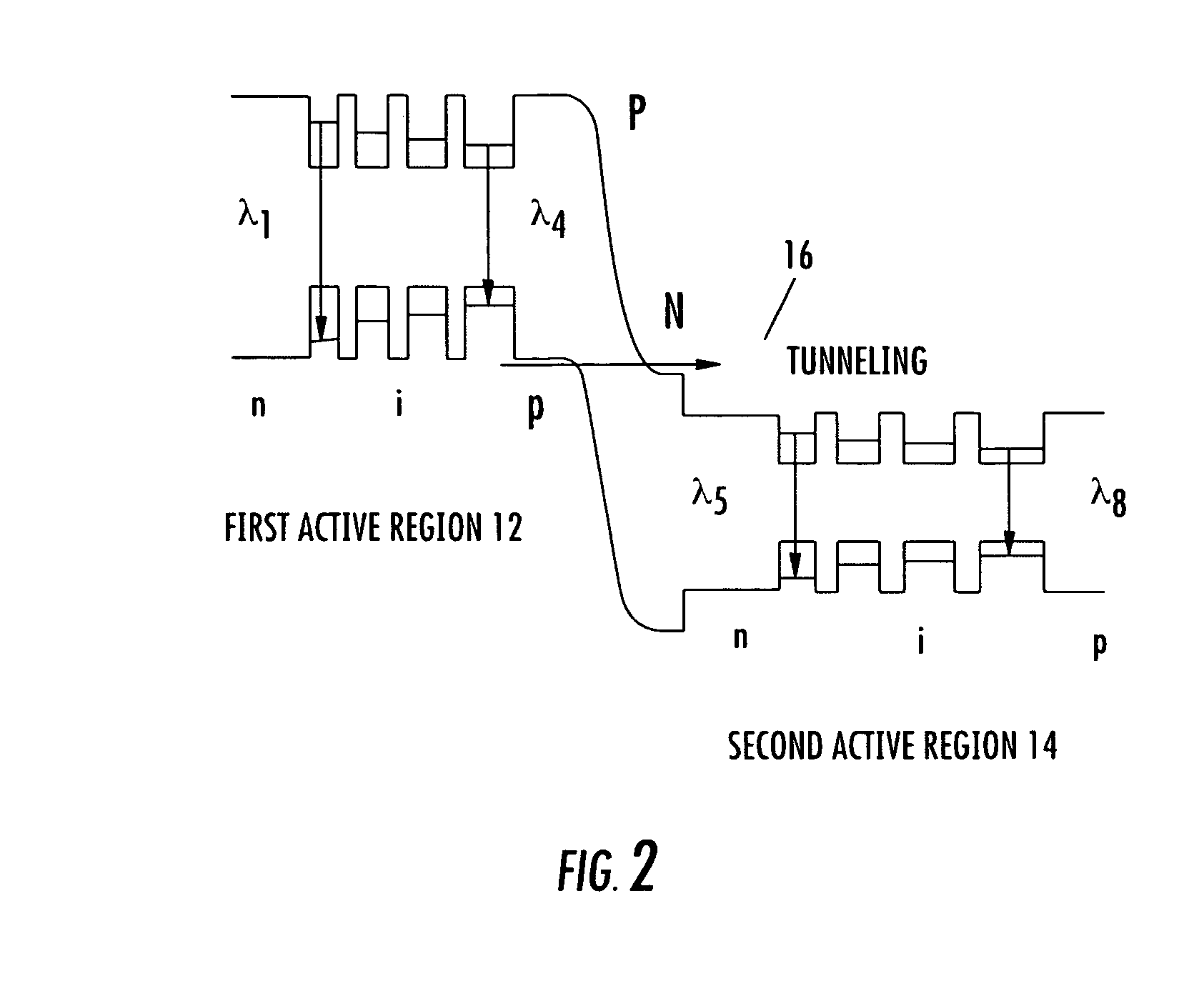

Multi-quantum well optical waveguide with broadband optical gain

InactiveUS20060233213A1Inhibition of excitementNanoopticsSemiconductor lasersTunnel injectionBroadband

A multi-quantum well optical waveguide structure comprises a plurality of active regions including quantum wells with different gain peak wavelengths to provide an ultra broadband optical gain spectrum. Two adjacent sets of active regions having a large band gap difference are connected by a tunneling injection layer to provide smooth electron transport. Single transverse-mode operation is obtained by narrowly tapering the width of the multi-quantum well optical waveguide from the center to the two ends. Higher-order modes are suppressed at the output of the tapered waveguide, even though the center waveguide portion supports higher-order modes. In this way, the multi- quantum well optical waveguide can be utilized for ultra broadband optical amplification using a single mode fiber.

Owner:CHOA FOW SEN +1

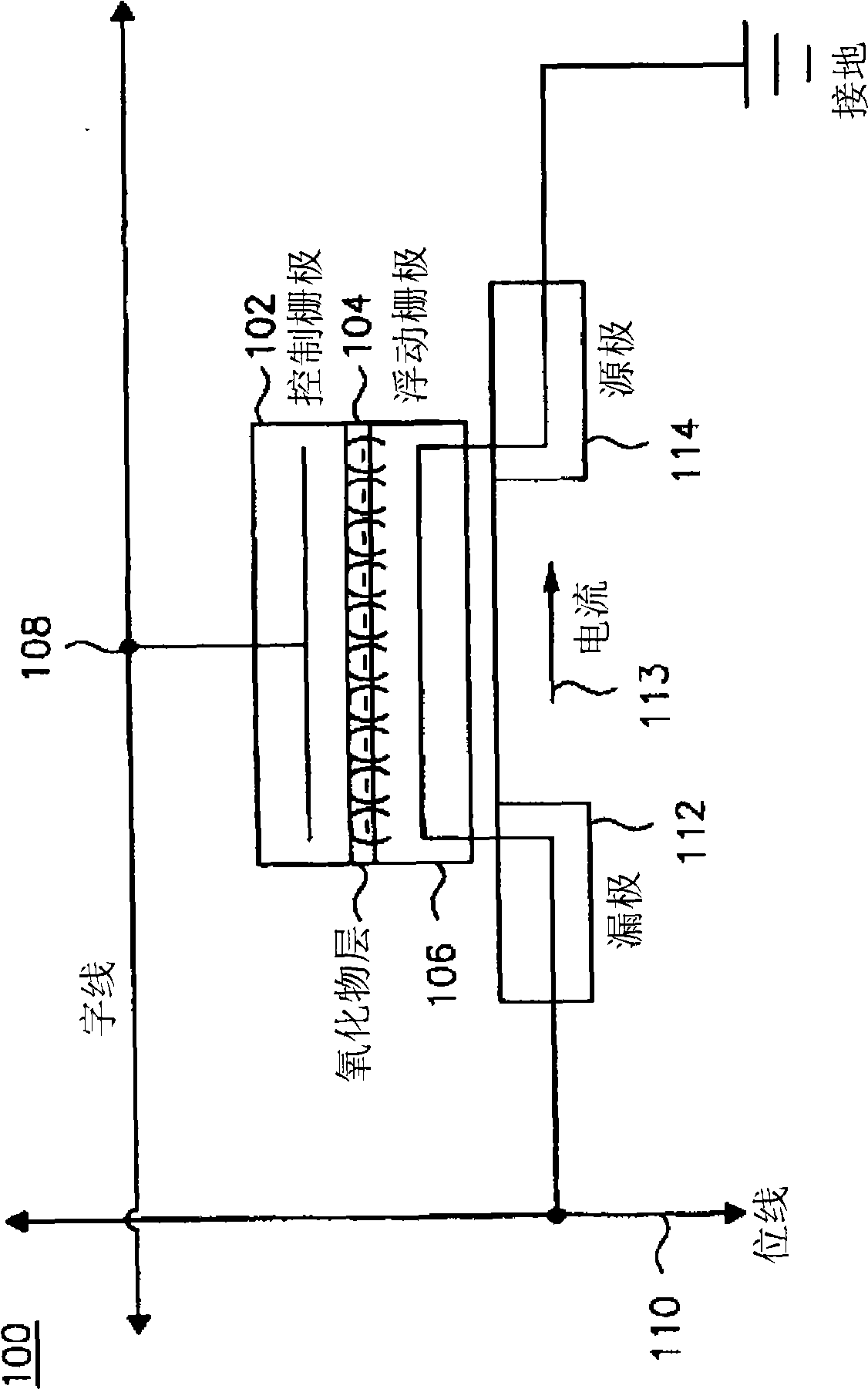

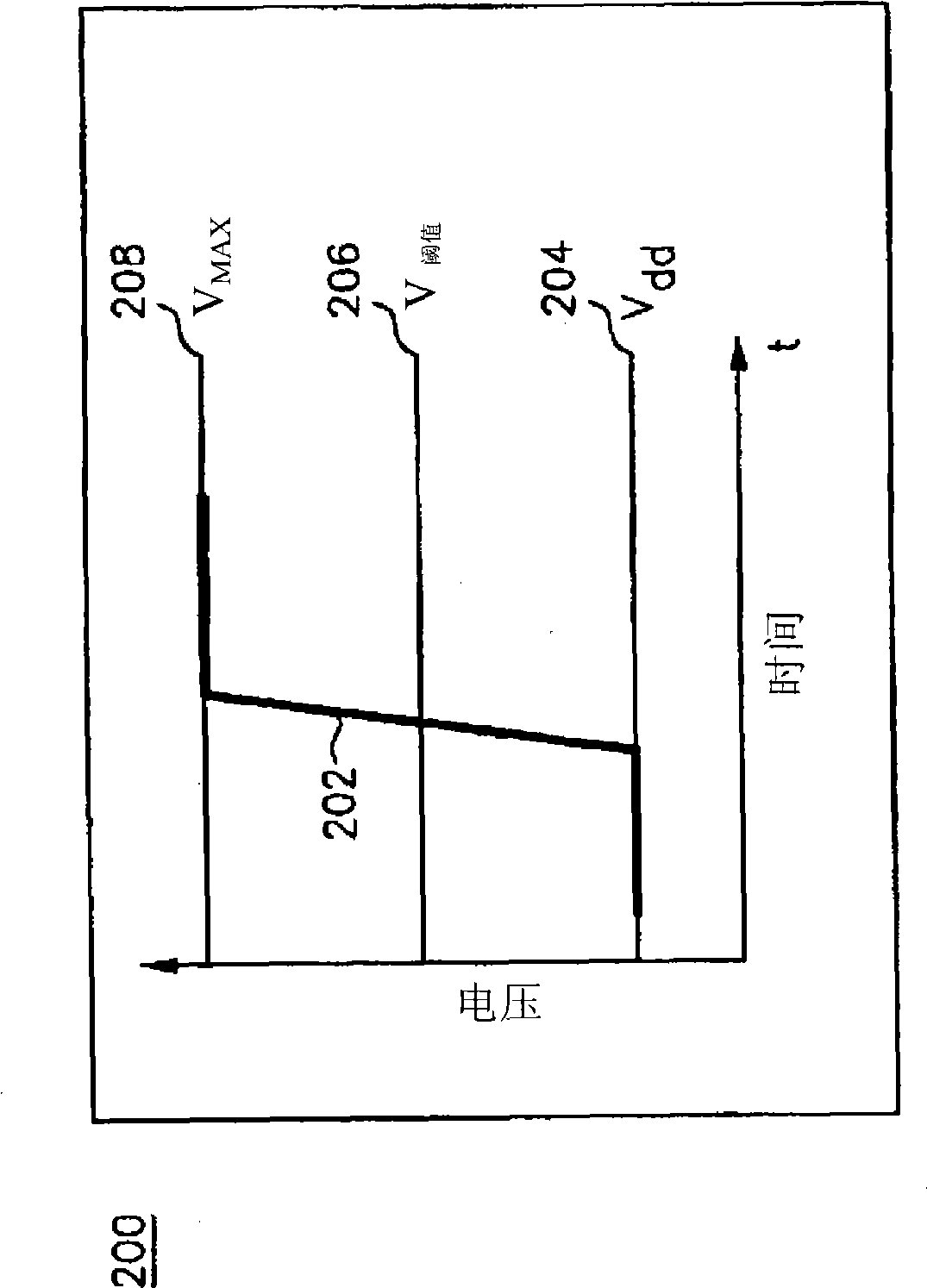

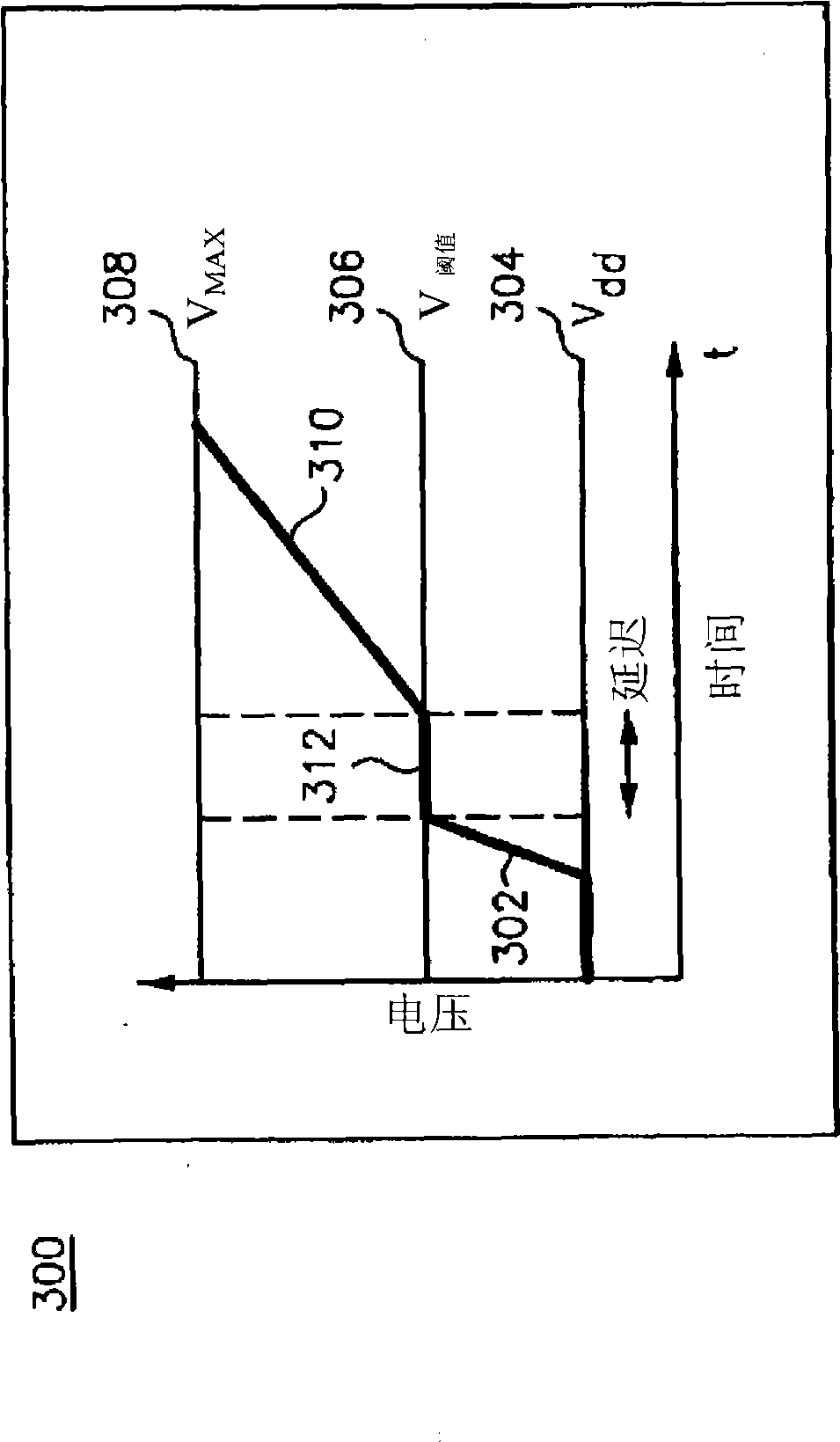

Apparatus and method for charge pump slew rate control

An apparatus and method for improving memory cell reliability is disclosed. The slew rate is reduced in an applied voltage signal used to program a memory cell when Fowler-Nordheim (FN) tunneling injection is detected. The applied programming signal is provided by a charge pump that is preferably a regulated charge pump. The charge pump is selectively controlled by a slew rate control circuit when FN tunneling injection is detected by a voltage level detection circuit at a predetermined threshold voltage level.

Owner:ATMEL CORP

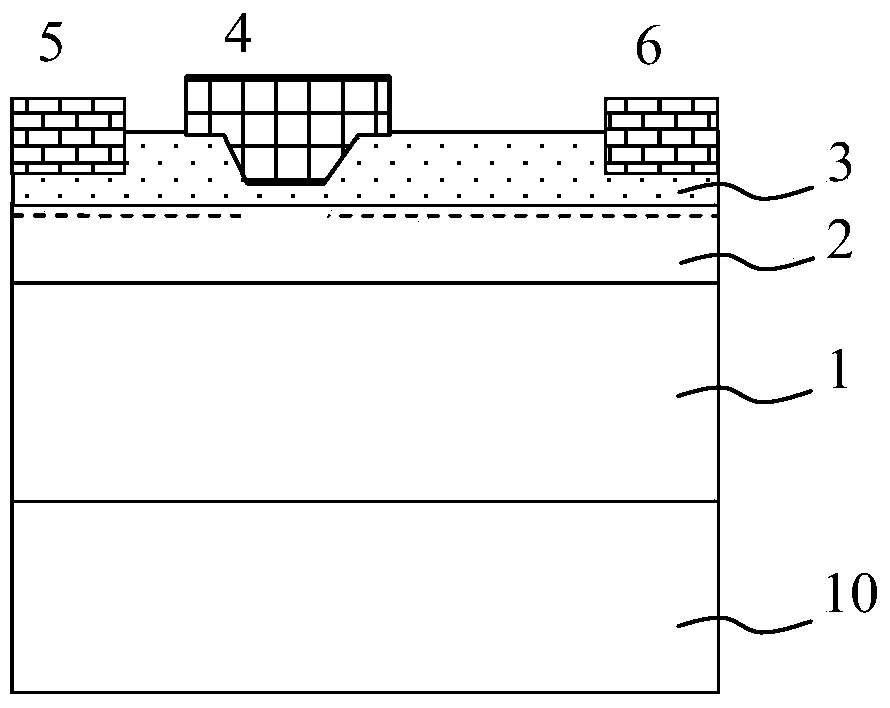

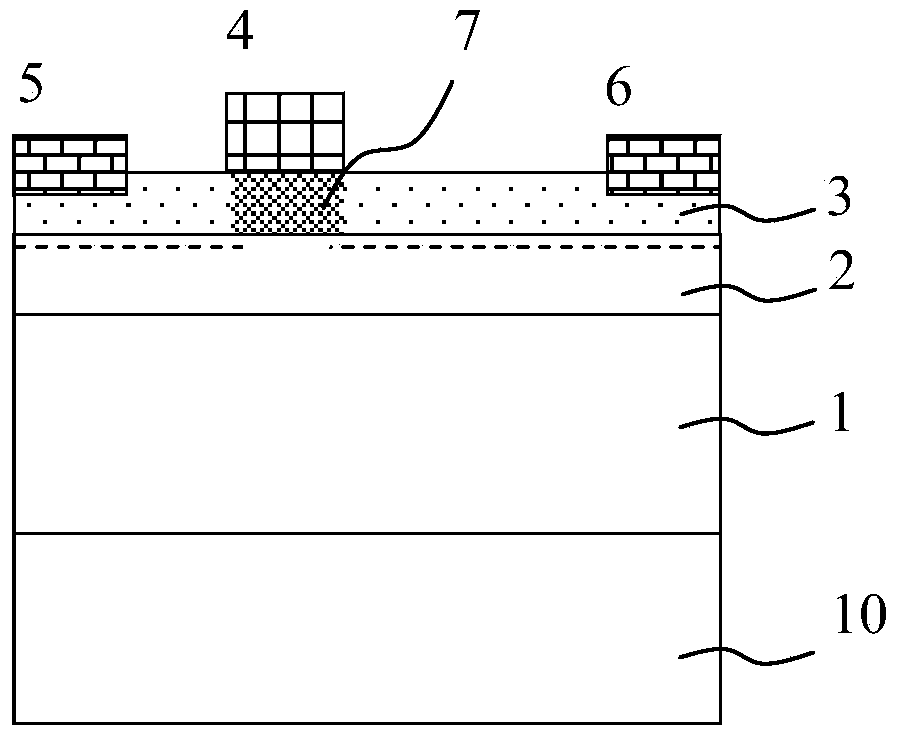

Enhancement mode device based on fluoride ion injection and manufacturing method thereof

ActiveCN103715256AAvoid gatheringImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesTunnel injectionGallium nitride

The invention discloses an enhancement mode device based on fluoride ion injection and a manufacturing method of the enhancement mode device based on fluoride ion implantation. The enhancement mode device based on fluoride ion injection comprises a substrate, an epitaxy multilayered structure formed on the substrate, a grid electrode, a source electrode and a drain electrode, wherein the grid electrode, the source electrode and the drain electrode are arranged on the epitaxy multilayered structure, and fluoride ions are injected in a heterogeneous structure layer below the grid electrode in a tunnel injection mode and are used for using up two-dimensional electron gas in the heterogeneous structure layer. As the fluoride ions are injected in the heterogeneous structure layer below the grid electrode in the tunnel injection mode and use up the two-dimensional electron gas in the heterogeneous structure layer below the grid electrode, the enhancement mode gallium nitride device is achieved. Meanwhile, unstable fluoride ions are removed through high temperature annealing, crystal lattices recover from damage caused when the fluoride ions are injected, and a crystalline state medium layer is utilized for protecting surfaces of nitride materials produced during high temperature annealing.

Owner:ENKRIS SEMICON

Highly doped III-nitride semiconductors

InactiveUS20050179047A1Reduce resistanceImprove electro-optical conversion efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesHazardous substanceVolumetric Mass Density

Owner:CORNELL RES FOUNDATION INC

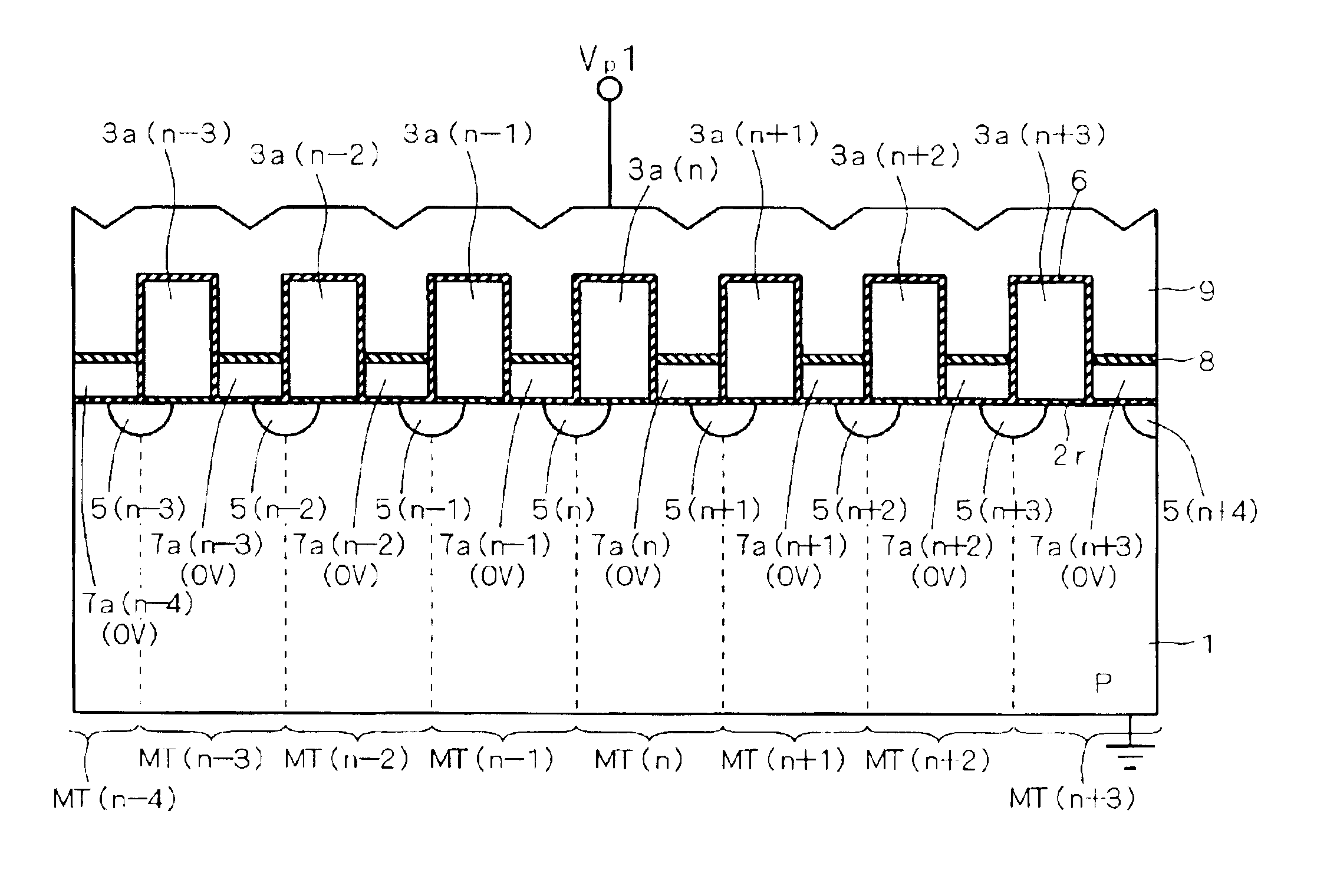

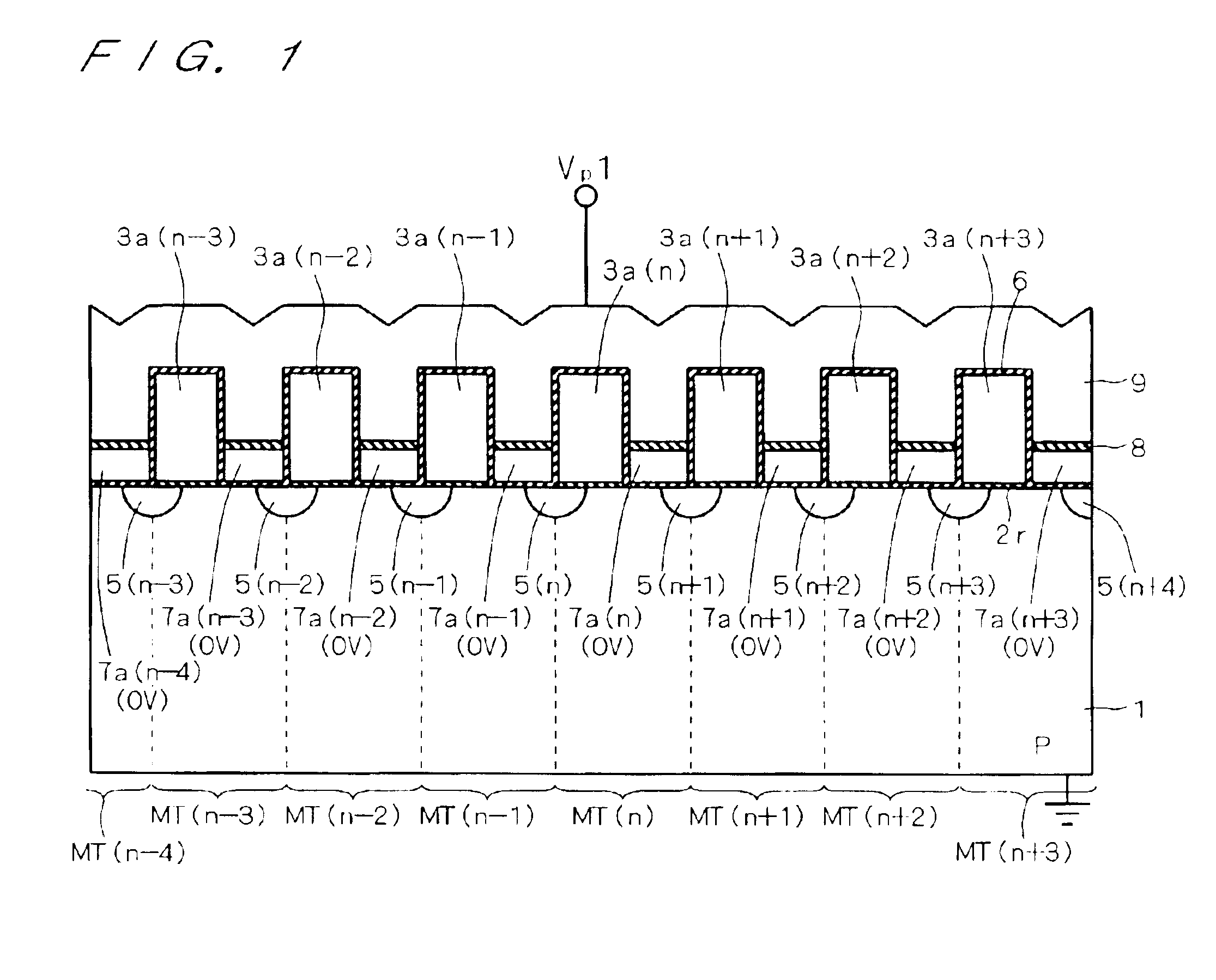

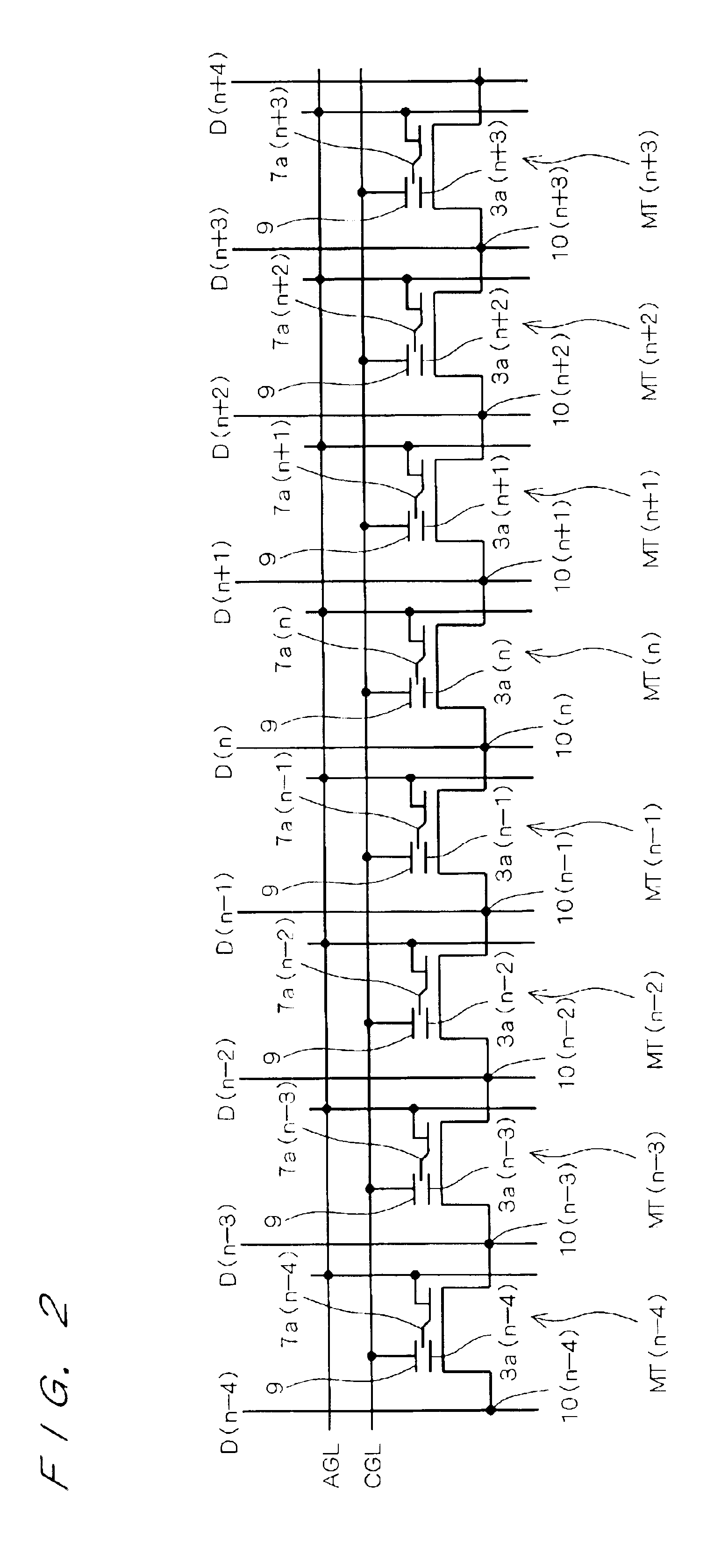

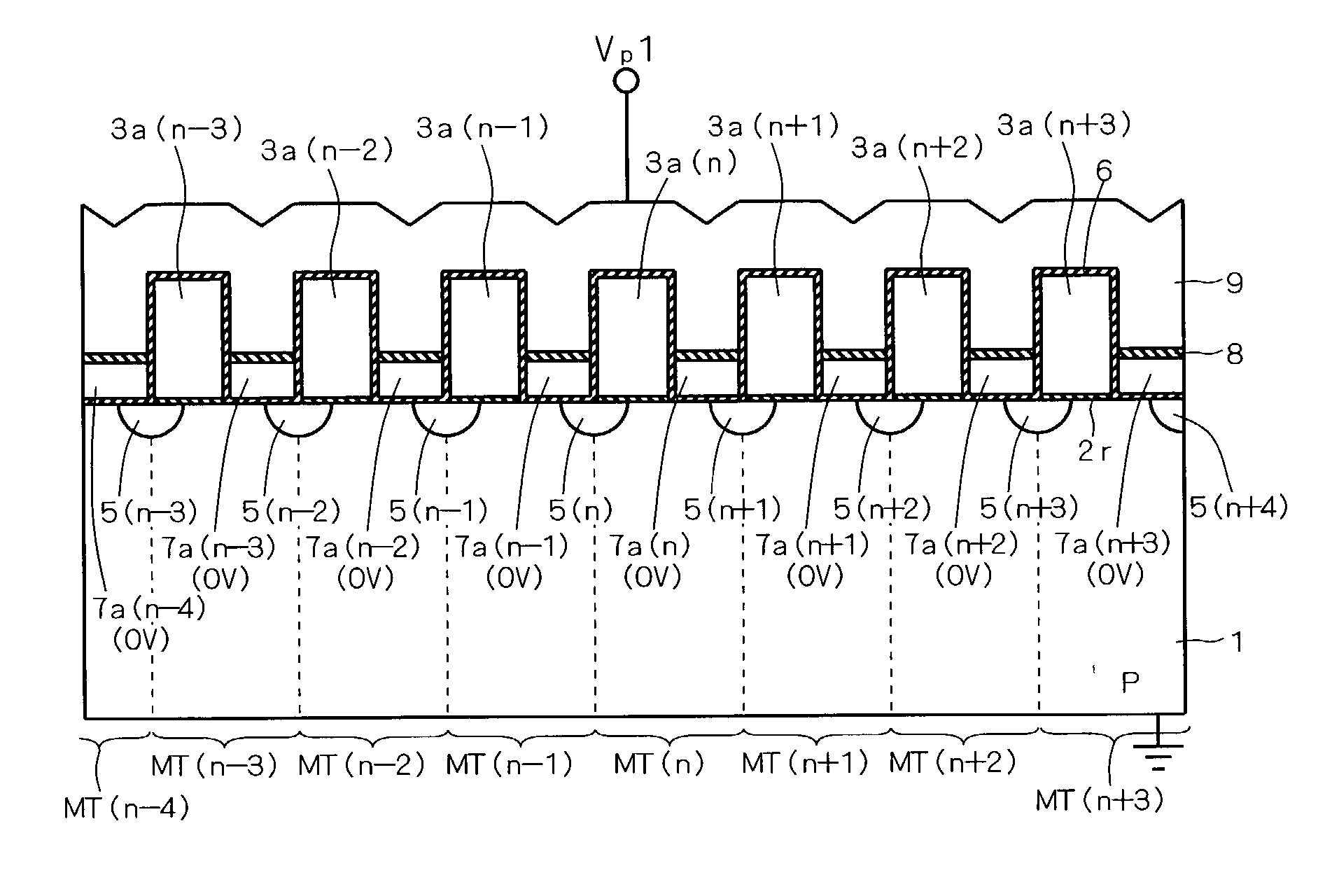

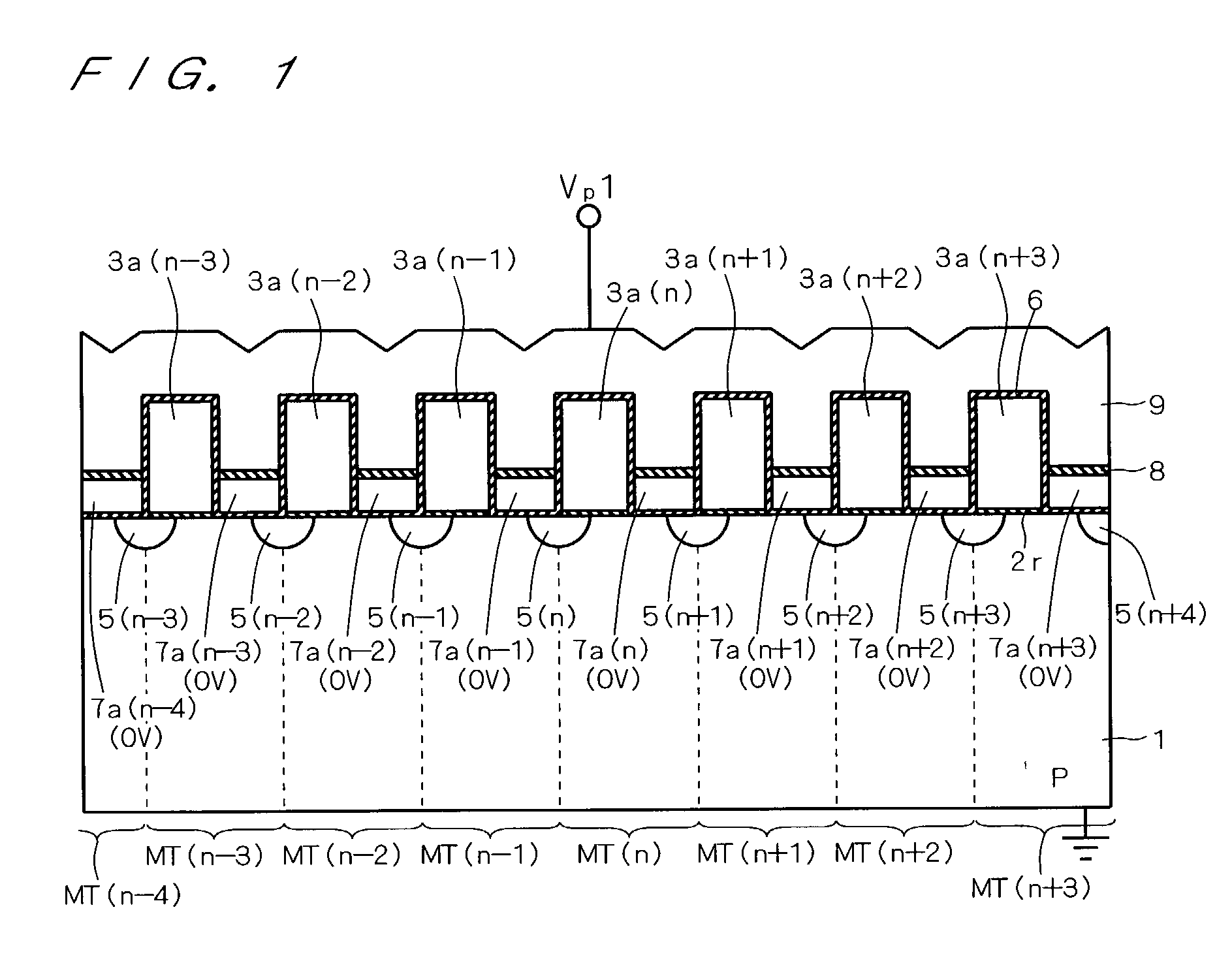

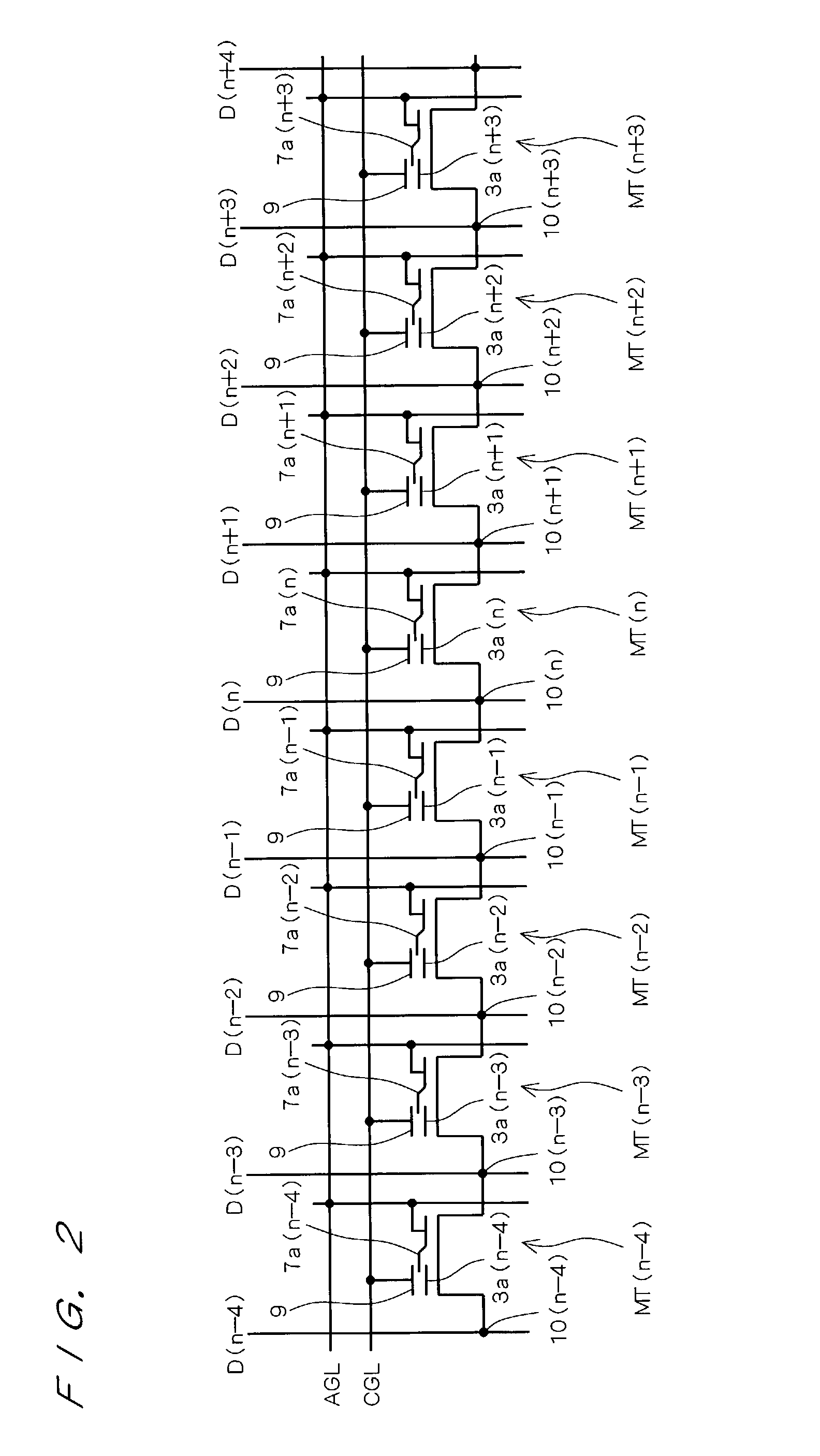

Methods of writing/erasing of nonvolatile semiconductor storage device

A nonvolatile semiconductor storage device can achieve a shortened write time and a reduced absolute value of an operating voltage at the time of erasing. A P-type silicon substrate (1) is set at a ground level, a control gate (109) is set at a high voltage (Vp1), and a voltage of 0 V is applied to an access gate line connected in common to all access gates (7a) to set all the access gates (7a(n-4) to 7a(n+3)) at 0 V. When the threshold voltage of a memory transistor (MT(n)) is set into a written state, an N<+> diffusion region (5(n)) is set at 0V. This causes tunnel injection of electrons into a floating gate (3a(n)) of the memory transistor (MT(n)) and thereby allows the memory transistor MT(n) to be set to a high threshold voltage (Vthp) without being influenced by the contents of writing to adjacent memory transistors.

Owner:RENESAS ELECTRONICS CORP

Storage unit and method for forming a storage unit

ActiveCN1815742AImprove reliabilitySuppression of short channel effectsTransistorSolid-state devicesGate dielectricSchottky barrier

Owner:TAIWAN SEMICON MFG CO LTD

UV LED with tunnel-injection layer

ActiveUS9705030B2Improve efficiencyDecrease in luminanceSemiconductor/solid-state device manufacturingSemiconductor devicesTunnel injectionUltraviolet lights

An ultraviolet (UV) light emitting structure, a UV light emitting device, and a method of making a UV light emitting structure or device, wherein the UV light emitting structure or device has an AlN or AlGaN injection layer with high aluminum content between the light emitting active region and the p-doped layers and wherein the injection layer has a thickness such that holes can tunnel from the p-side of the semiconductor-based ultraviolet light emitting diode structure through the injection layer in the active zone and also reducing leakage electrons out of the active zone.

Owner:FERDINAND BRAUN INST GGMBH LEIBNIZ INST FUR HOCHSTFREQUENZTECHNIK +2

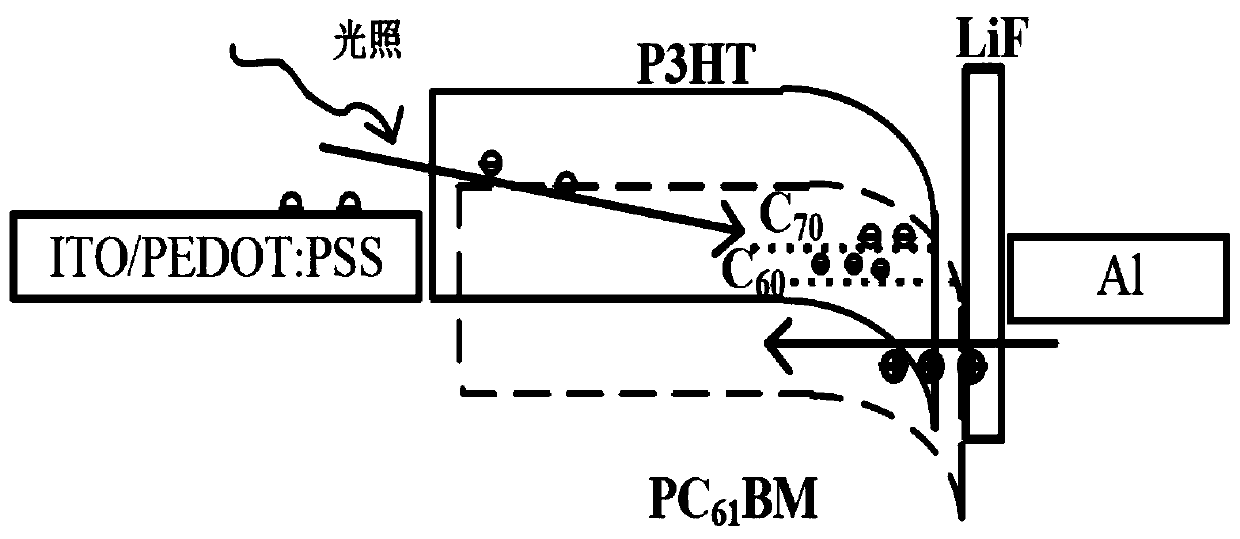

Double-injection multiplication type organic photoelectric detector and preparation method thereof

ActiveCN111883664AImprove photoelectric performanceIncrease chance of tunnelingFinal product manufactureSolid-state devicesHeterojunctionPhotocurrent

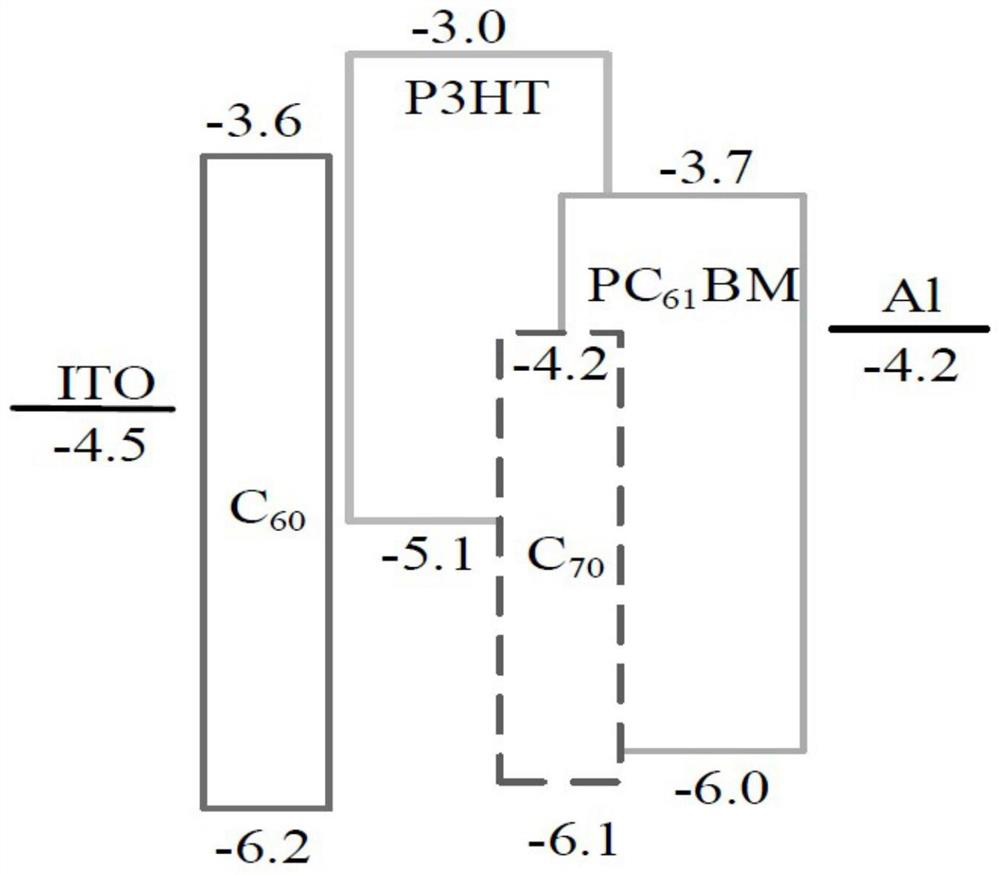

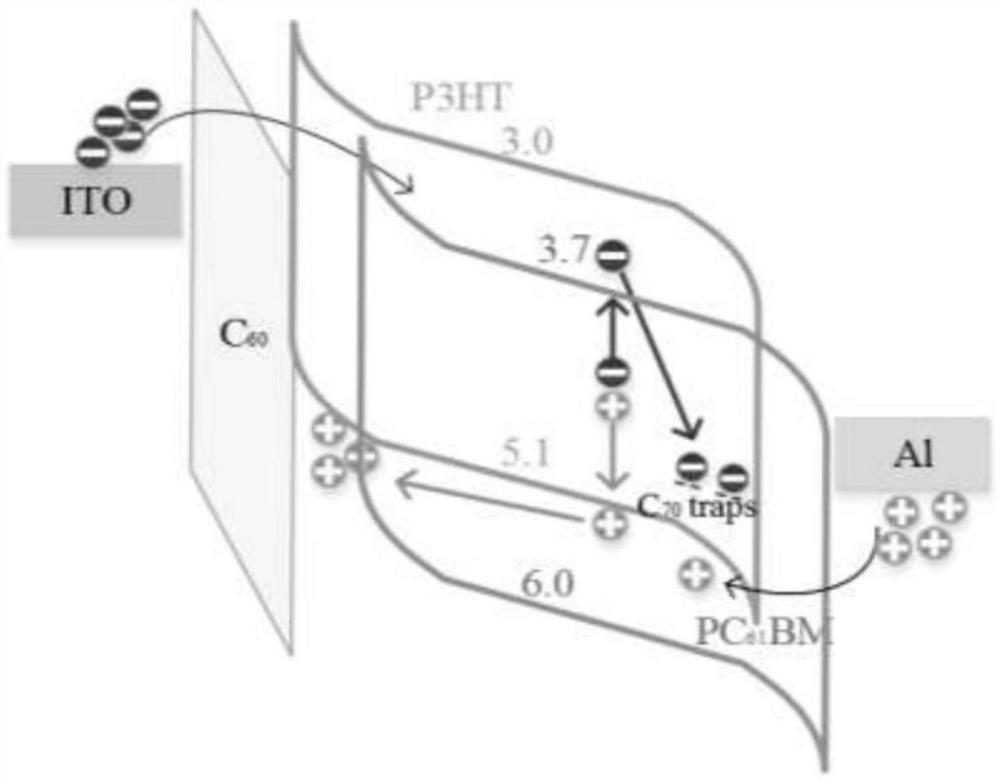

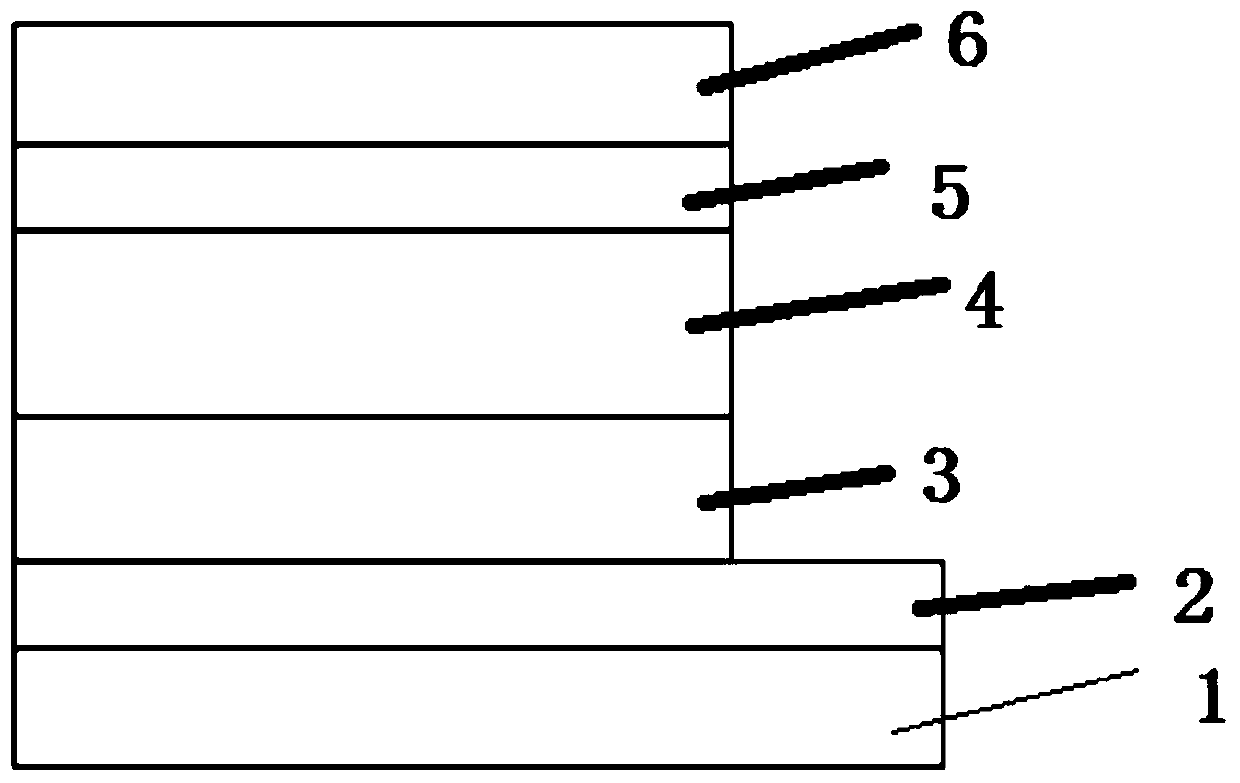

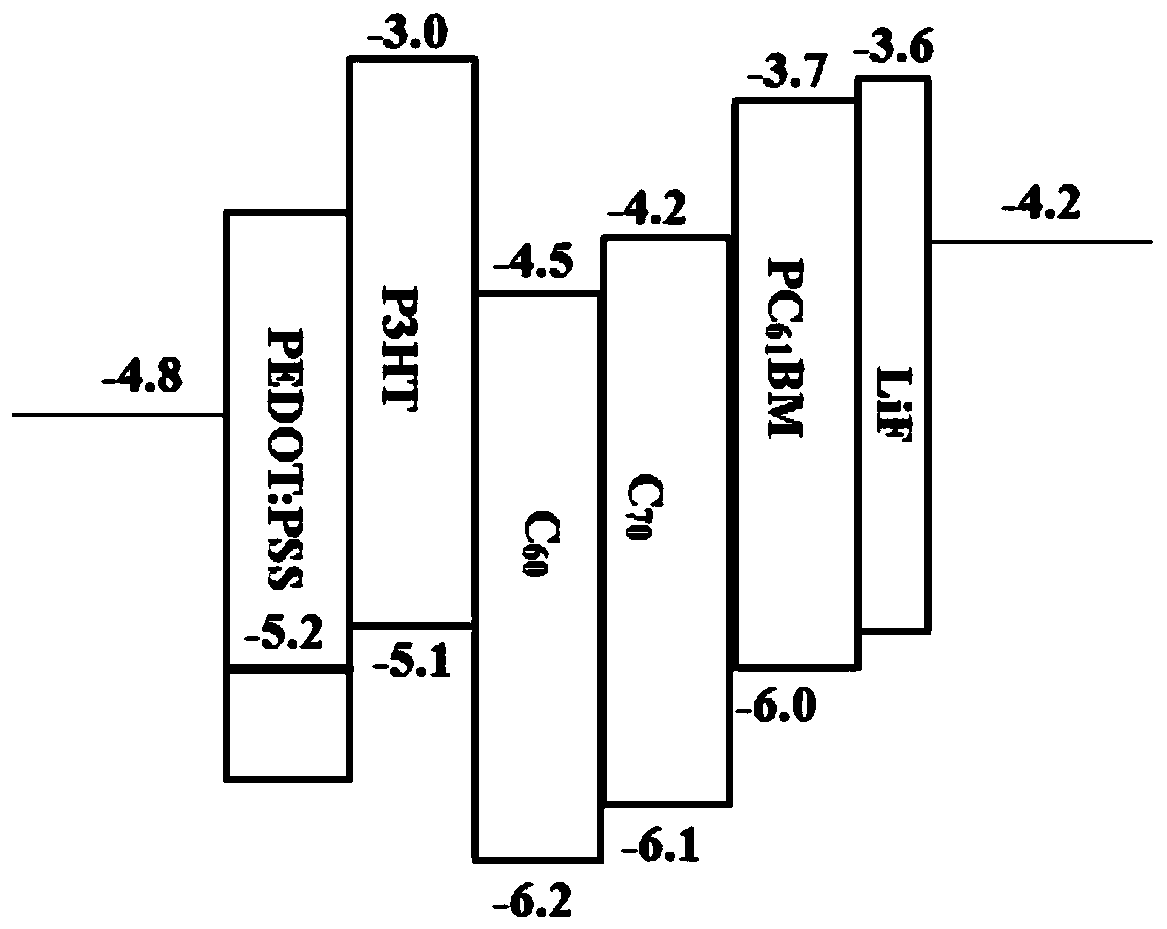

The invention discloses a double-injection multiplication type organic photoelectric detector and a preparation method thereof, and the double-injection multiplication type organic photoelectric detector comprises a glass substrate, wherein the surface of the glass substrate is plated with an ITO electrode layer, and the ITO electrode layer is sequentially coated with an anode buffer layer, an active layer and an Al electrode layer from bottom to top; the anode buffer layer is made of C60, the active layer is made of a mixture of P3HT, PC61BM and C70, and the P3HT, the PC61BM and the C70 forma bulk heterojunction. C60 is added into the device to serve as a hole blocking layer, and meanwhile, a small amount of C70 material is doped into an active layer to serve as an electron trap, so tunneling injection of holes is increased, external quantum efficiency is improved, photocurrent is reduced, and photoelectric performance of the detector is improved; the working voltage is small, and the circuit can work under a small bias voltage of 1V; the preparation method of the double-injection multiplication type organic photoelectric detector is simple to operate and easy to implement.

Owner:XIAN UNIV OF TECH

Organic photoelectric detector and preparation method thereof

ActiveCN109830608AHigher detection rateIncrease the number ofSolid-state devicesSemiconductor/solid-state device manufacturingQuantum efficiencyPhotovoltaic detectors

The invention discloses an organic photoelectric detector and a preparation method thereof. The organic photoelectric detector comprises a glass substrate, the surface of the glass substrate is platedwith an ITO electrode layer, and the ITO electrode layer is coated with an anode buffer layer, an active layer, a cathode buffer layer and an Al electrode layer successively from bottom to top; and material of the active layer includes a mixture of P3HT, PC61BM, C60 and C70. The active layer is doped with C60 and C70 acceptor materials to serve as electron traps, the number of traps is increased,aggregation of the trap material is reduced, tunneling injection of the cavity is increased, and the external quantum efficiency can be improved.

Owner:XIAN UNIV OF TECH

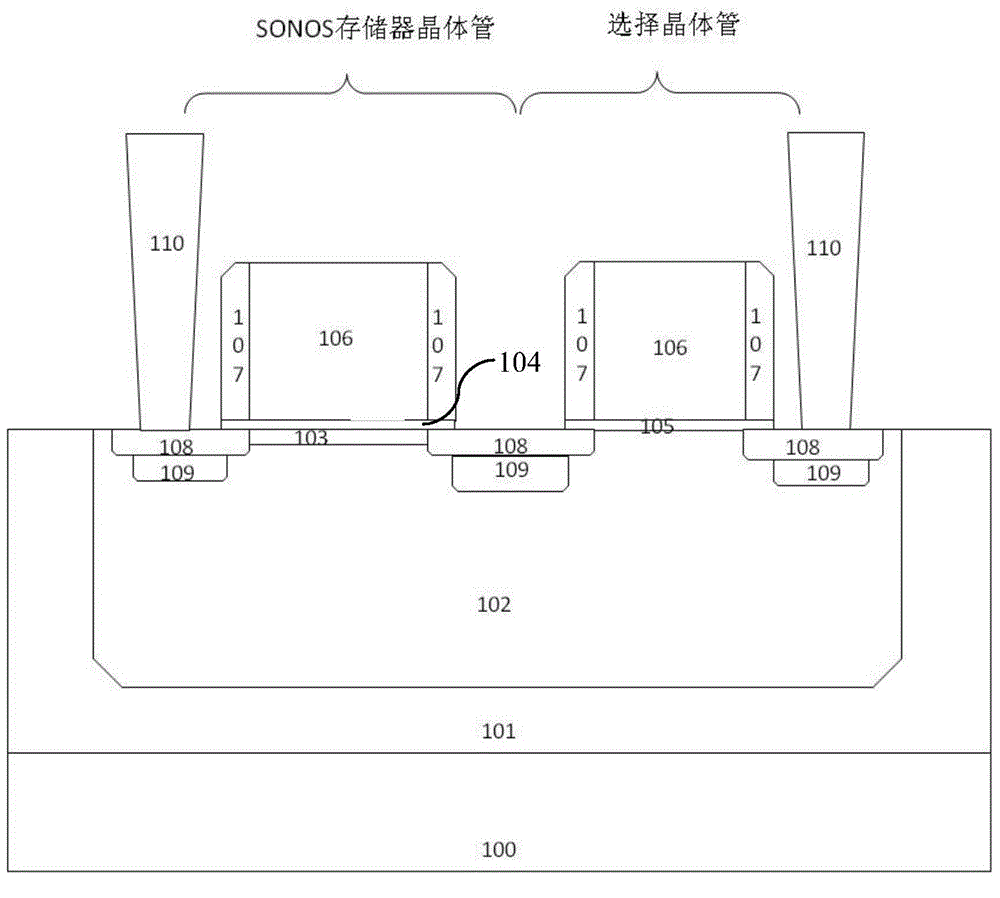

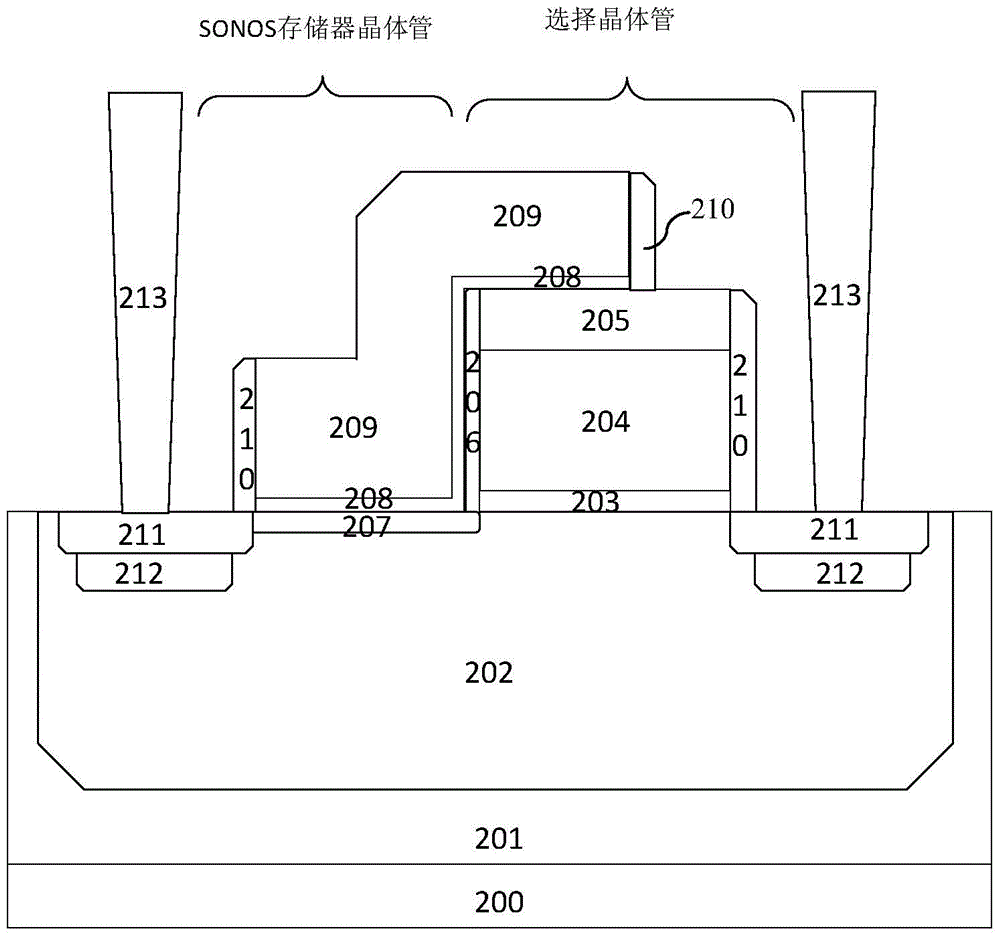

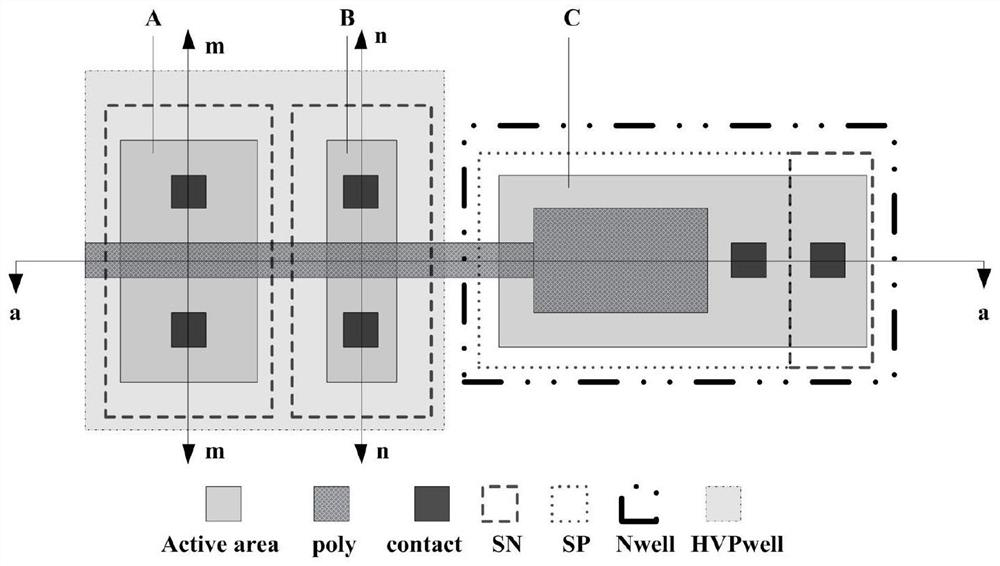

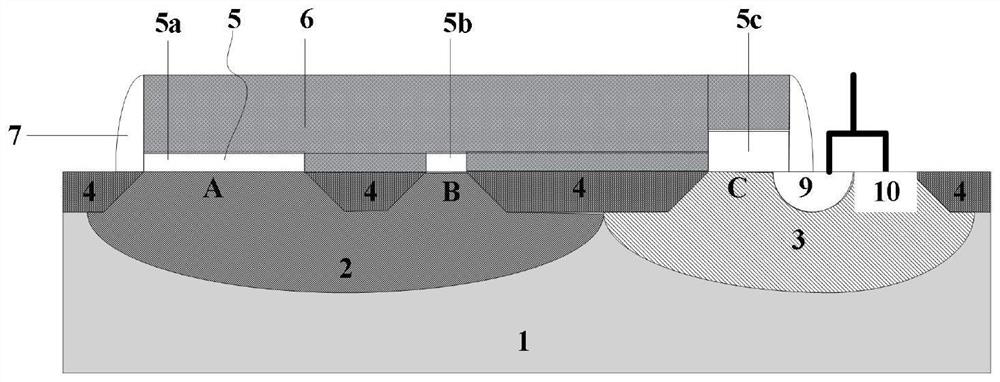

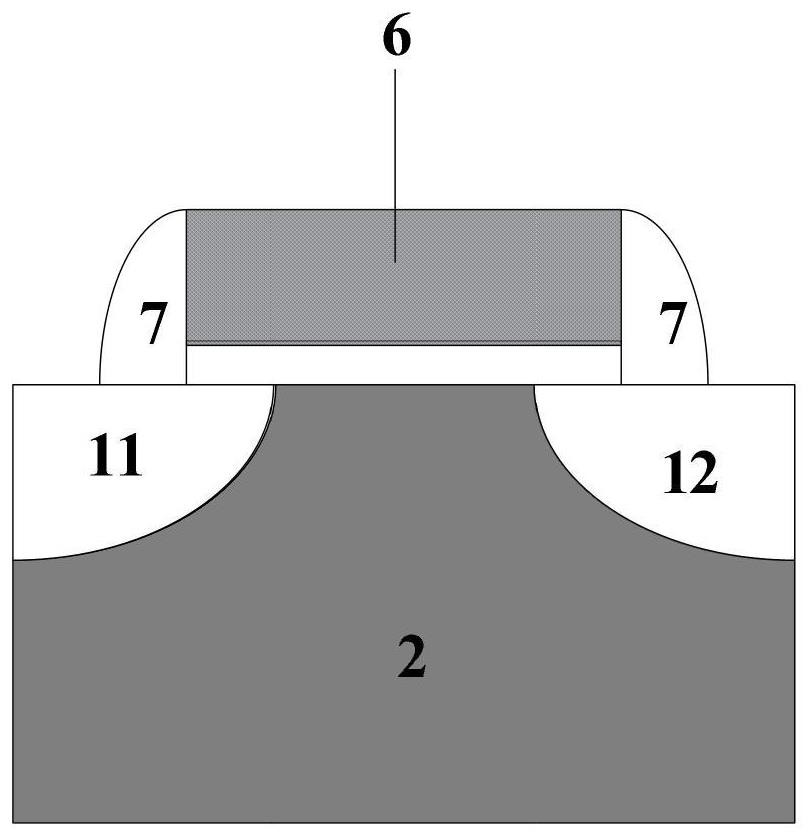

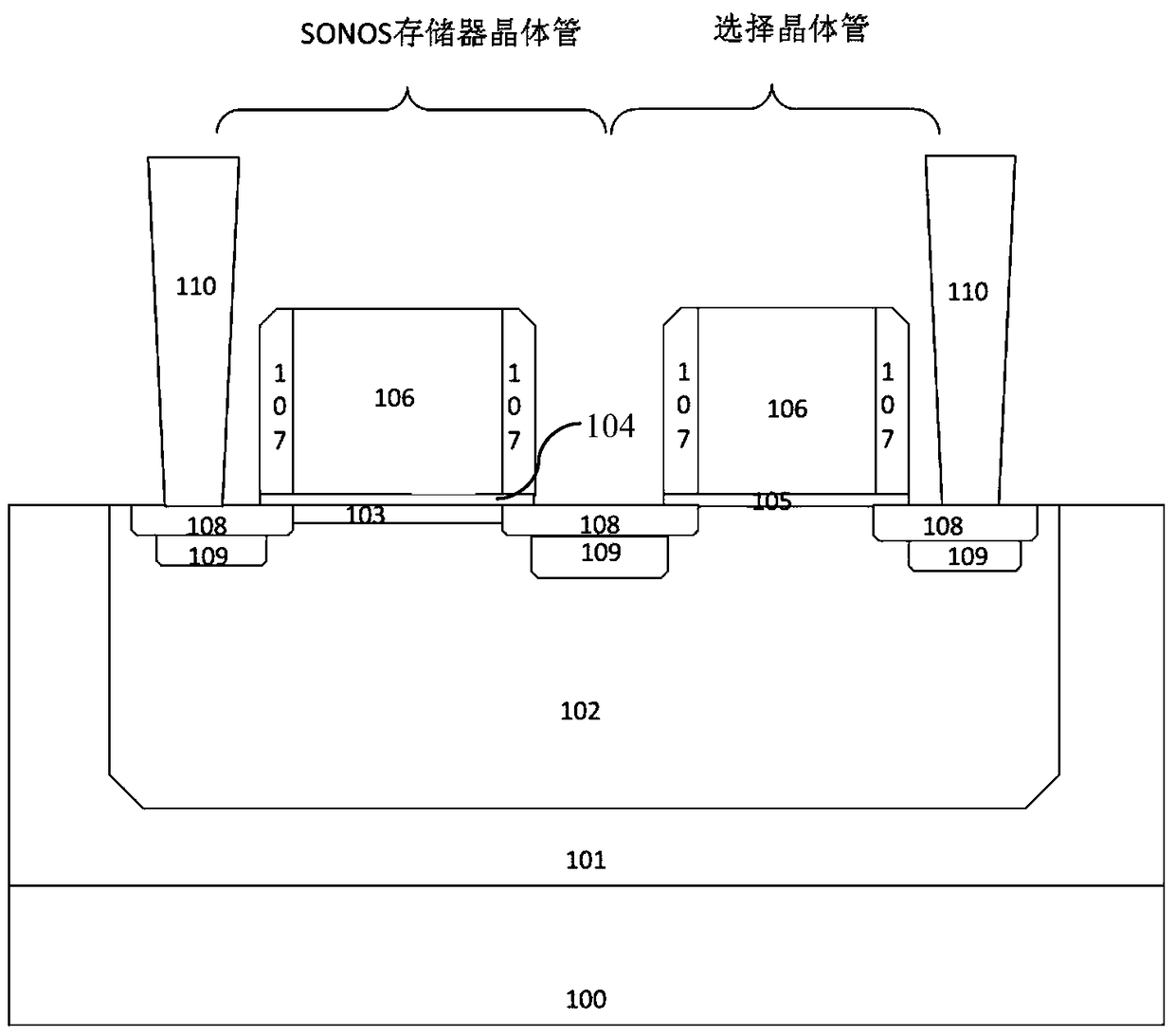

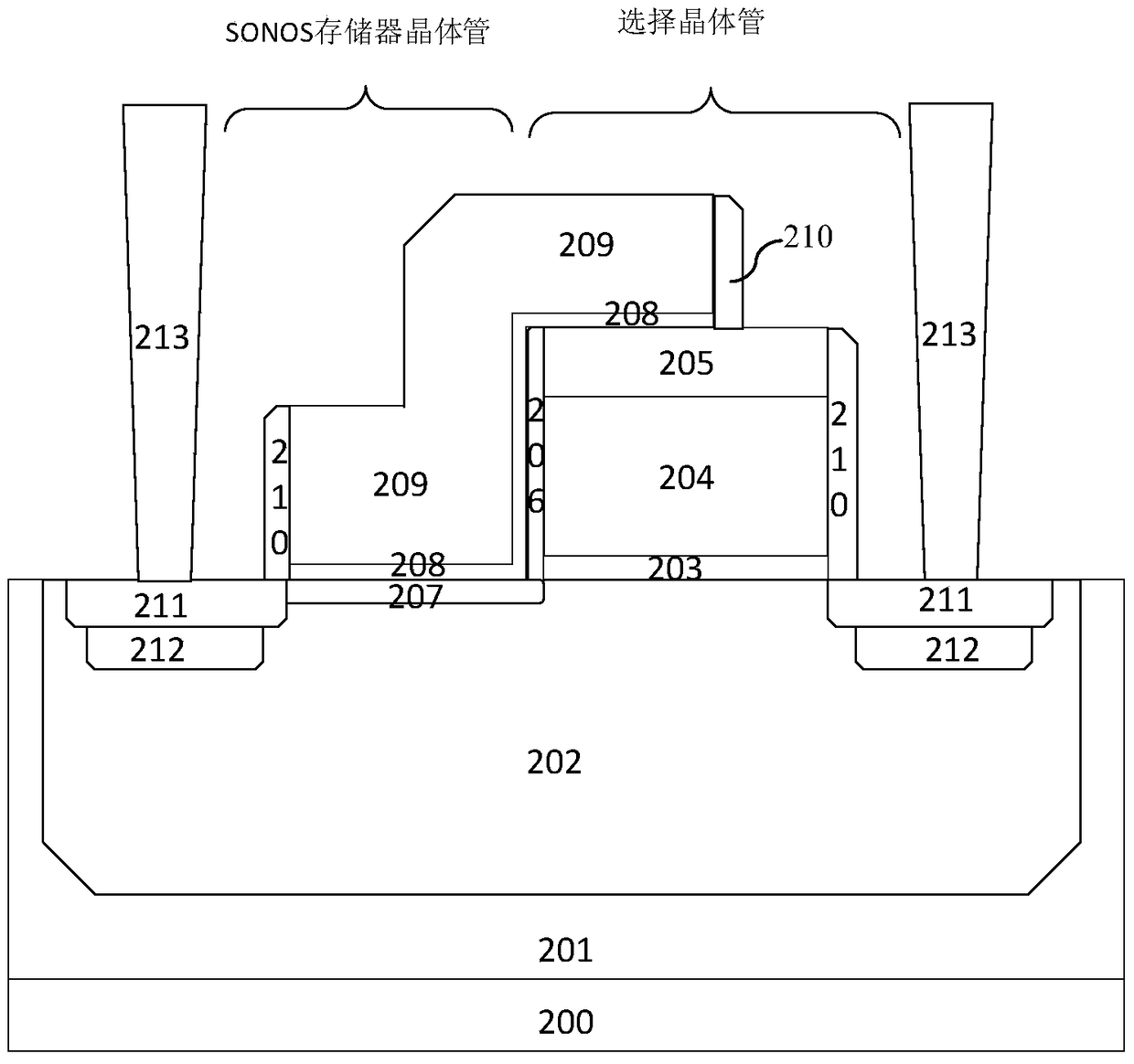

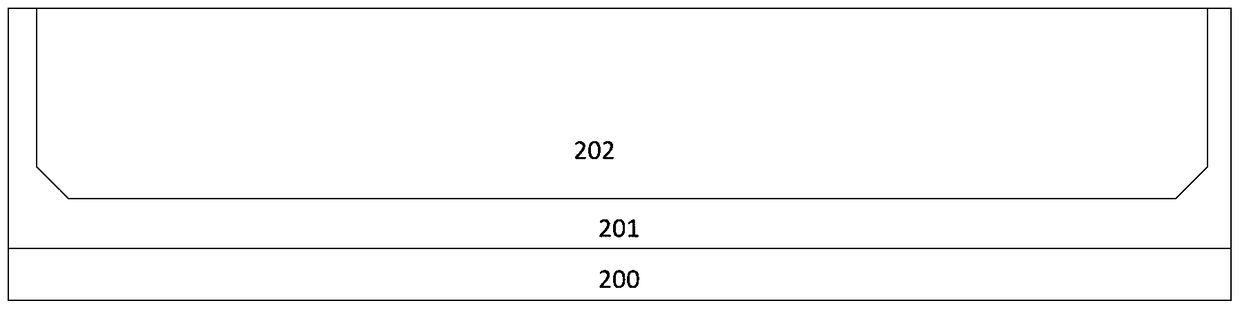

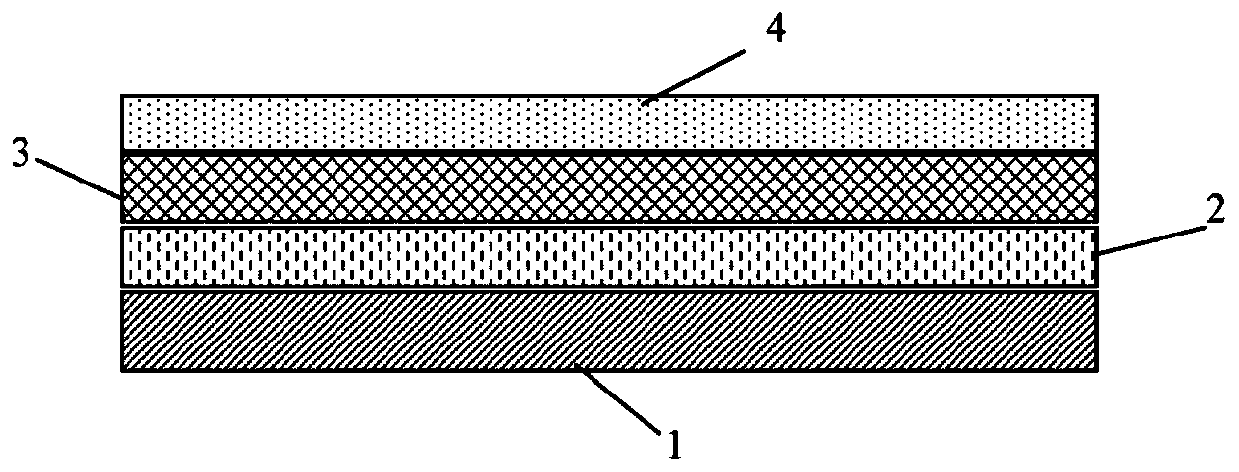

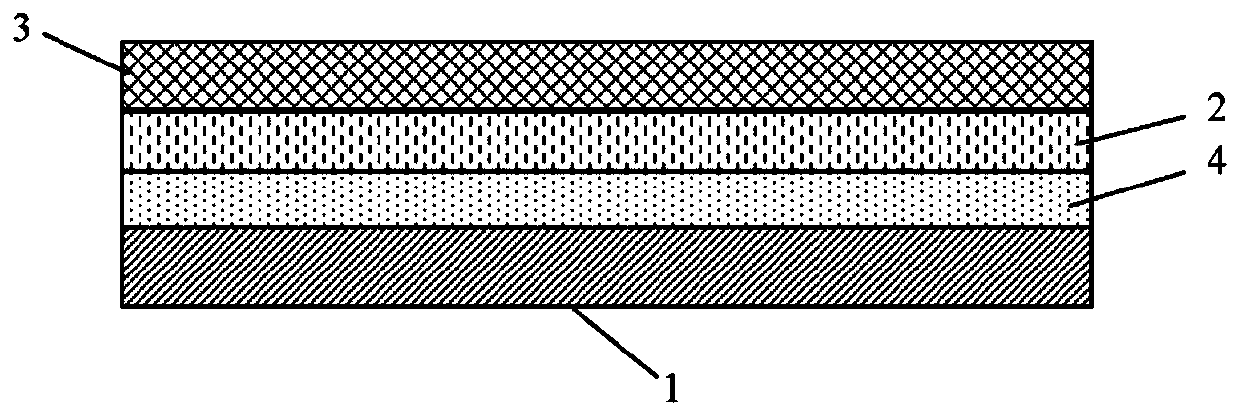

SONOS (silicon oxide nitride oxide semiconductor) nonvolatile memory and manufacturing method thereof

ActiveCN104425500AAvoid enteringReduce areaSolid-state devicesSemiconductor/solid-state device manufacturingTunnel injectionSilicon oxide

The invention discloses a SONOS nonvolatile memory. A grid of a SONOS memory transistor and a grid of a selective transistor of a unit structure of the SONOS nonvolatile memory are of a two-layer isolated overlapped structure; the first side face of the selective transistor is provided with a first insulating medium side wall; a tunnel injection region and an ONO layer of the SONOS memory transistor are aligned with the first insulating medium side wall; the whole unit structure only comprises two source and drain regions; no source and drain regions exist between the grid of the SONOS memory transistor and the selective transistor. The invention also discloses a method for manufacturing the SONOS nonvolatile memory. A source and drain region between grids of the two transistors is omitted directly, the area of the memory unit can be greatly reduced, and an additional etching step is not added.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

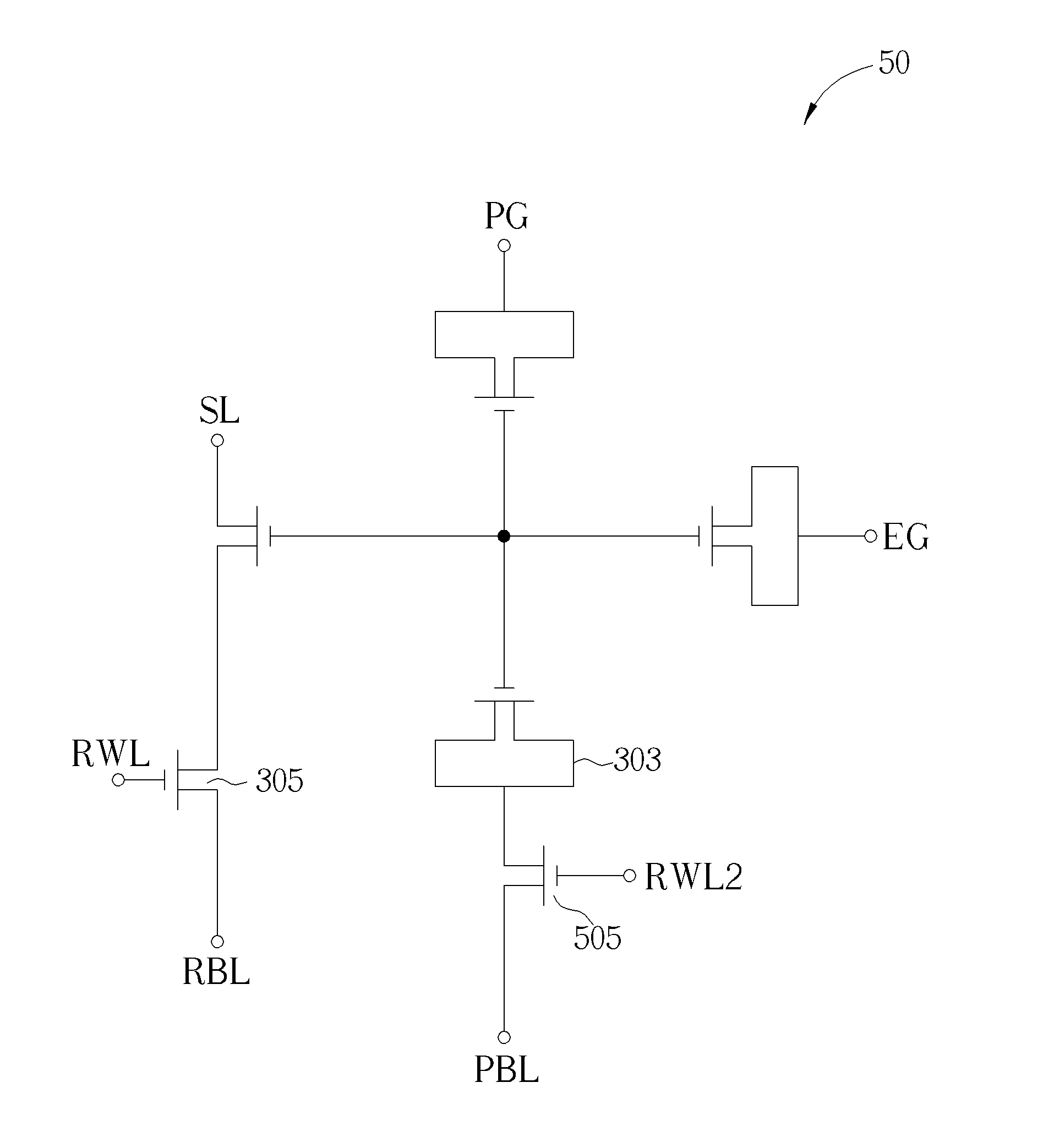

Non-volatile Memory Cell

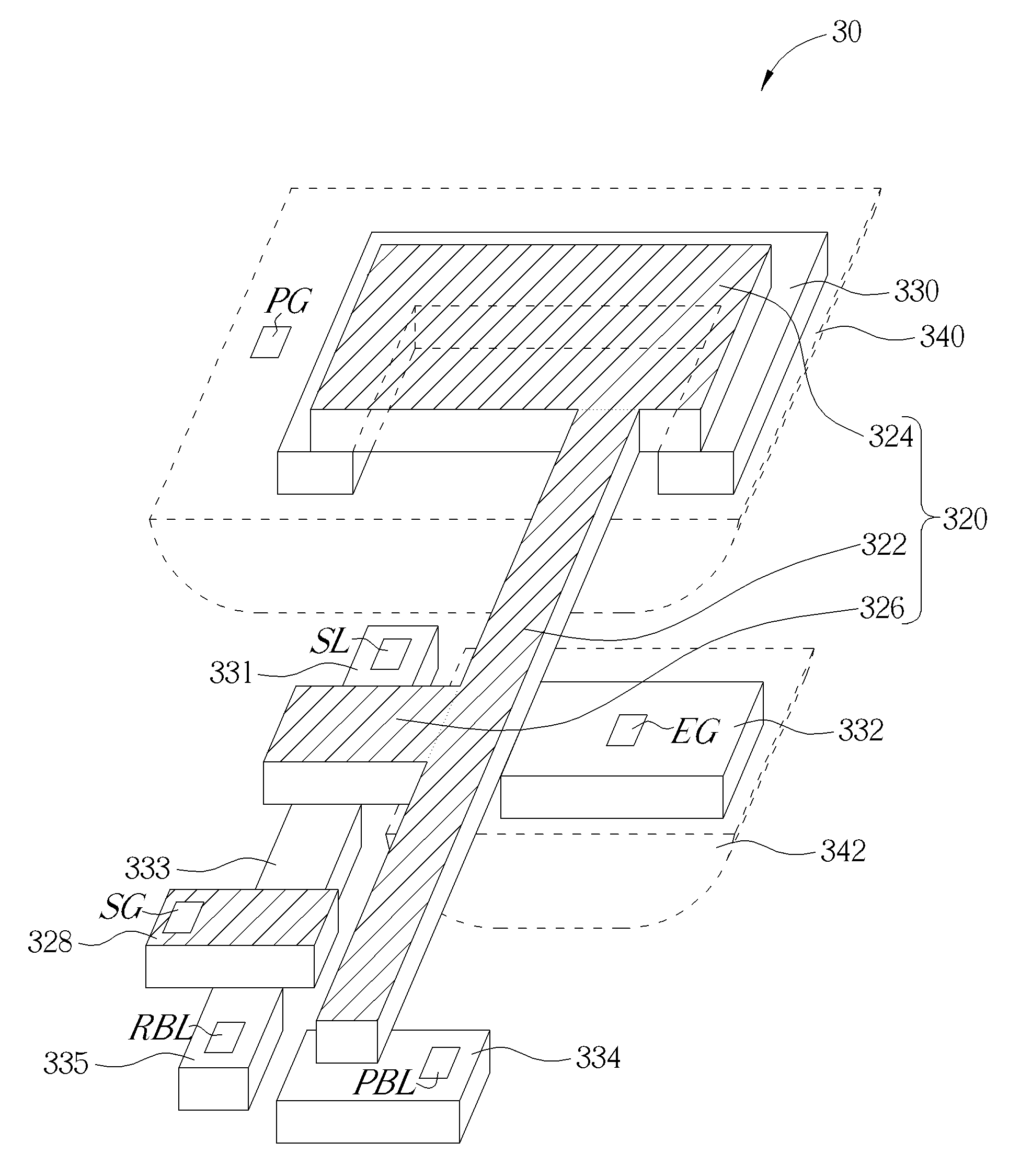

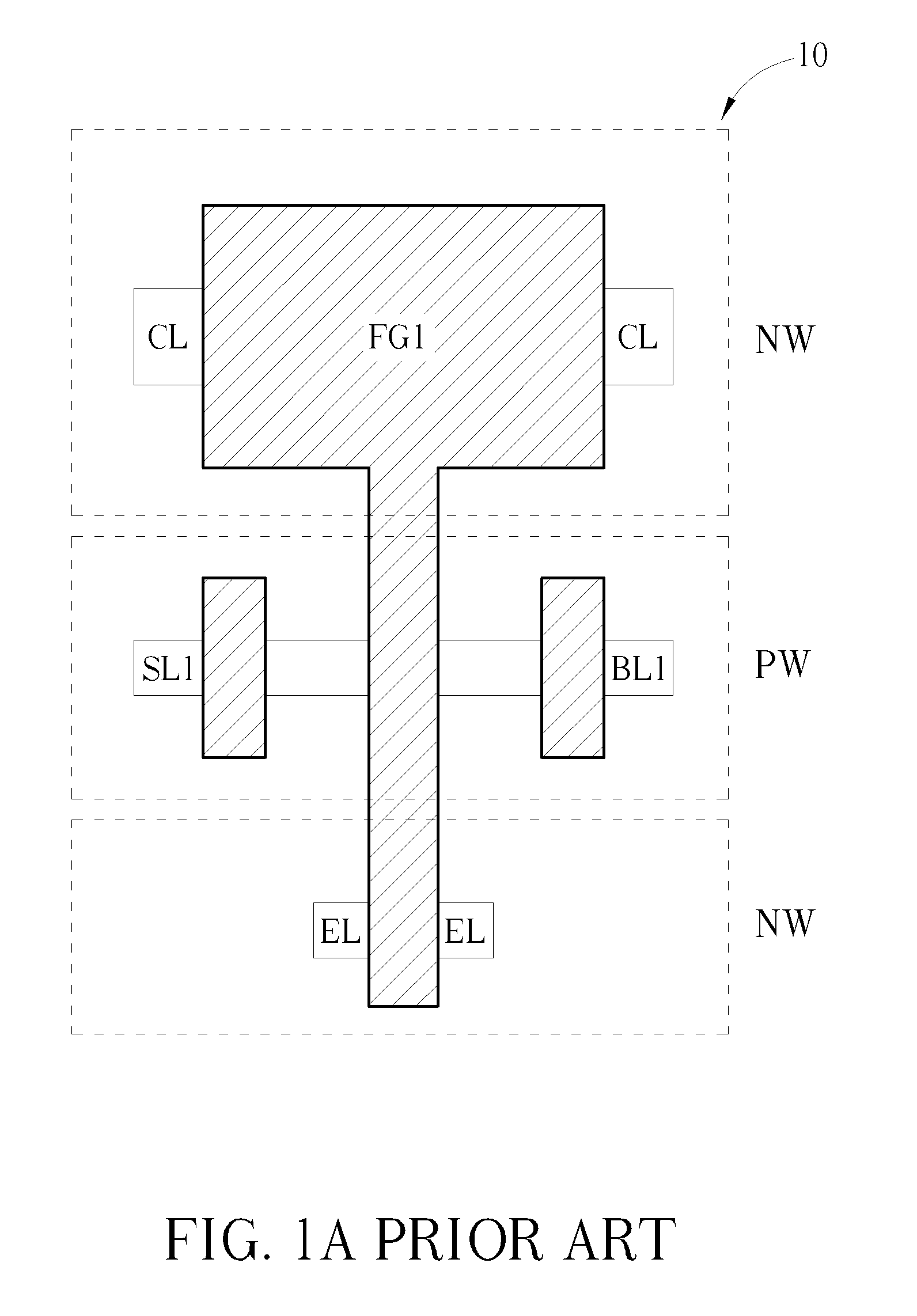

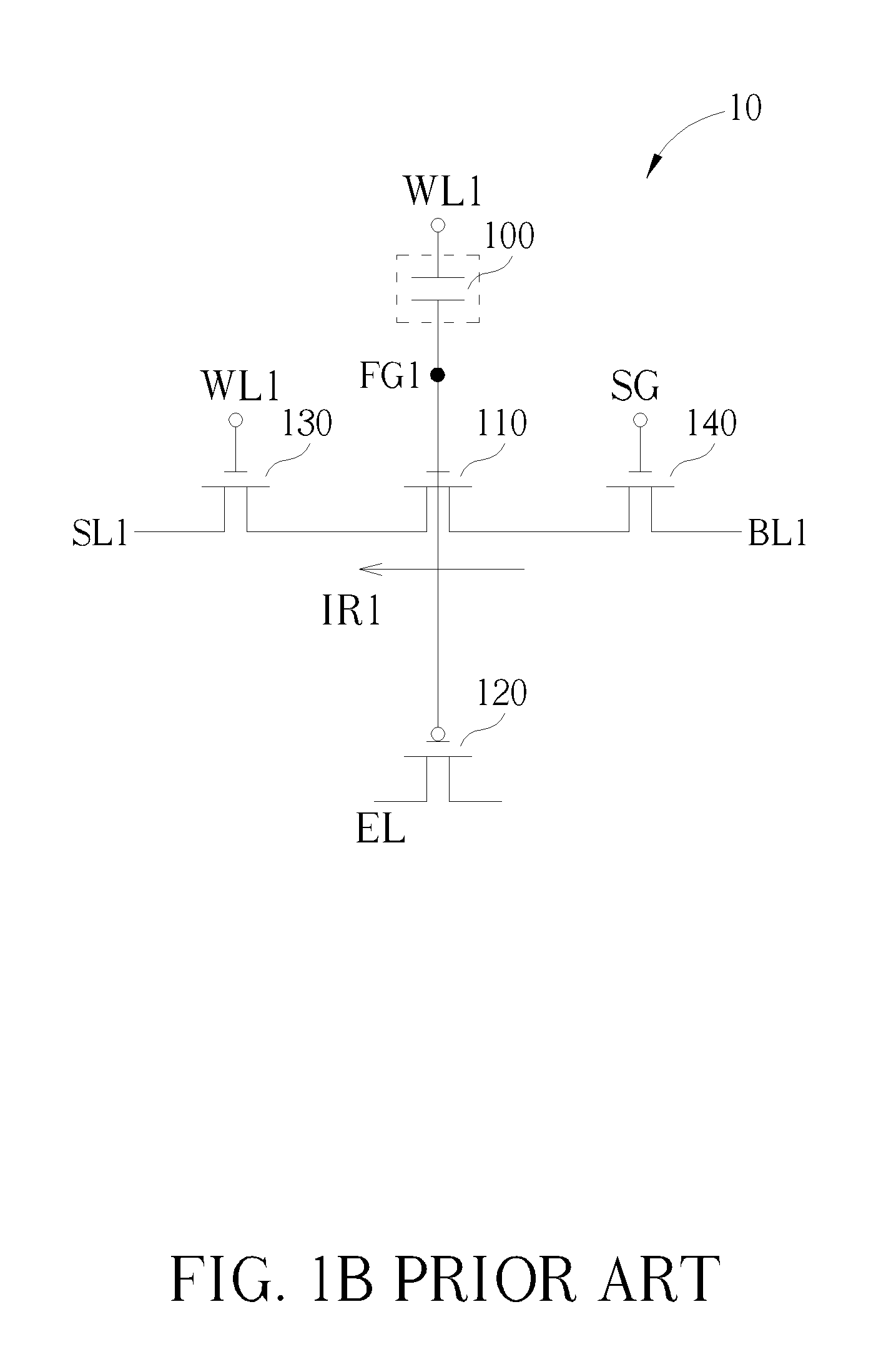

ActiveUS20160211029A1Improve disadvantagesTransistorSolid-state devicesTunnel injectionEmbedded system

A non-volatile memory cell comprises a tunneling part; a coupling device; a read transistor; a first select transistor connected to the read transistor forming a read path with the read transistor in a read mode; an erase tunneling structure forming a tunneling ejection path in an erase mode; and a program tunneling structure forming a tunneling injection path in an program mode; wherein the read path is different from the tunneling ejection path and the tunneling injection path.

Owner:AMIC TECH TAIWAN

Methods of writing/erasing of nonvolatile semiconductor storage device

A nonvolatile semiconductor storage device can achieve a shortened write time and a reduced absolute value of an operating voltage at the time of erasing. A P-type silicon substrate (1) is set at a ground level, a control gate (109) is set at a high voltage (Vp1), and a voltage of 0 V is applied to an access gate line connected in common to all access gates (7a) to set all the access gates (7a(n-4) to 7a(n+3)) at 0 V. When the threshold voltage of a memory transistor (MT(n)) is set into a written state, an N+ diffusion region (5(n)) is set at 0V. This causes tunnel injection of electrons into a floating gate (3a(n)) of the memory transistor (MT(n)) and thereby allows the memory transistor MT(n) to be set to a high threshold voltage (Vthp) without being influenced by the contents of writing to adjacent memory transistors.

Owner:RENESAS ELECTRONICS CORP

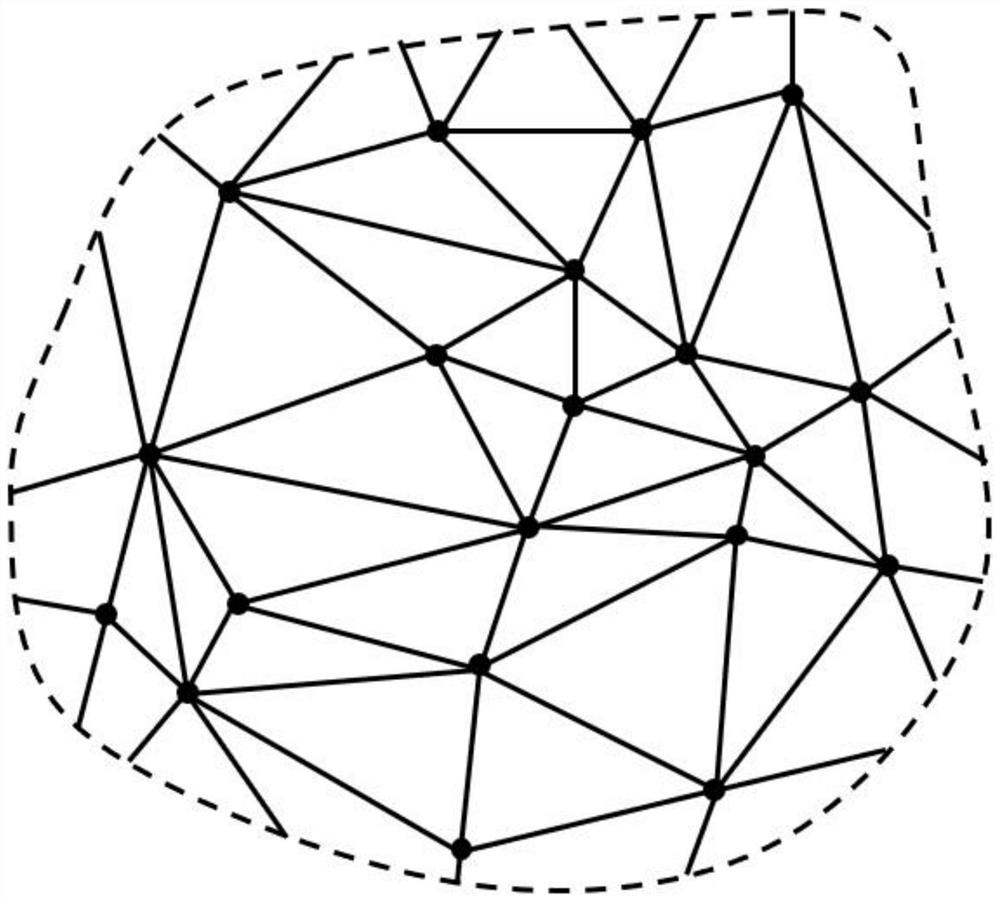

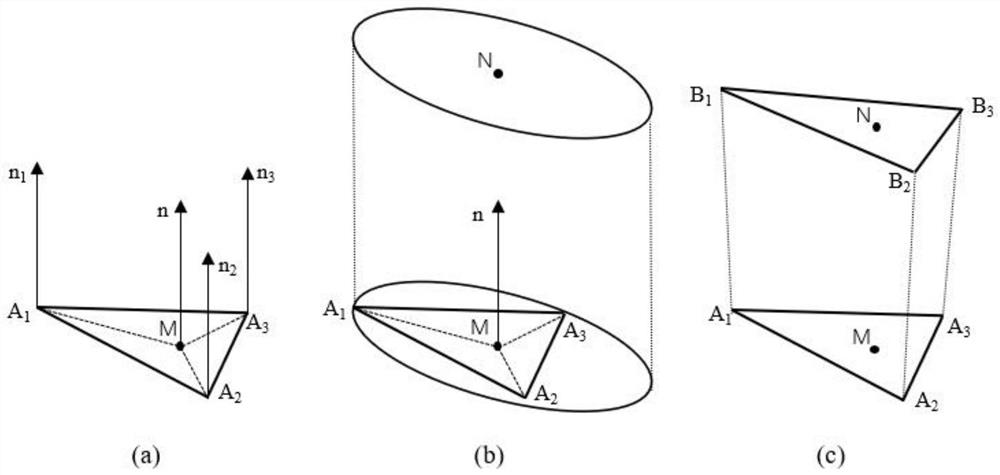

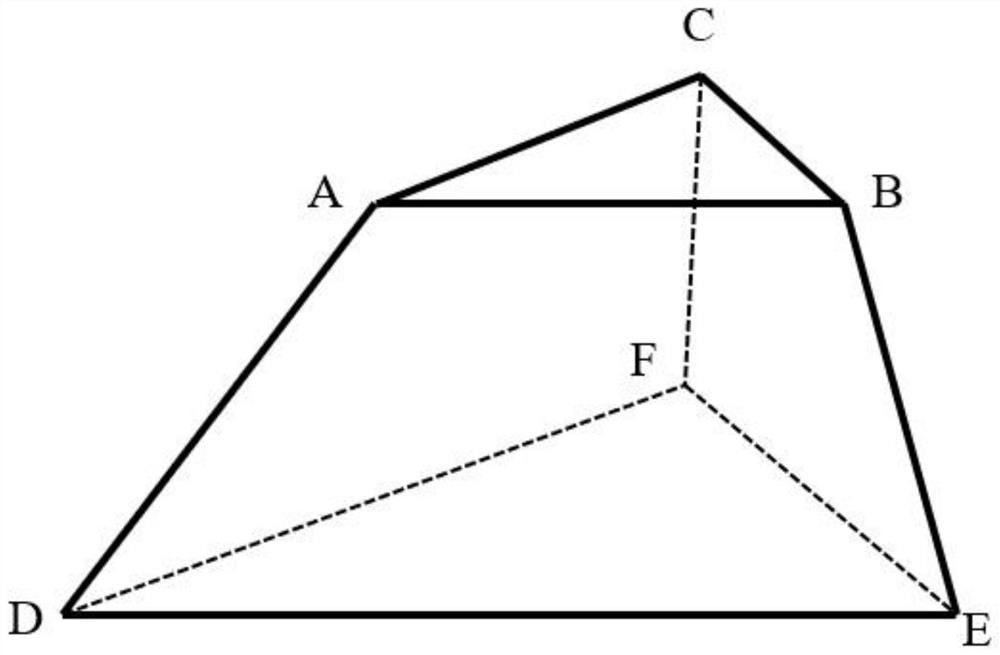

Tunnel injection volume estimation method based on point cloud data processing

The invention provides a tunnel injection volume estimation method based on point cloud data processing, and belongs to the technical field of tunnel engineering. The method comprises the following steps: step 1, carrying out point cloud translation; step 2, designing point cloud preprocessing; step 3, preprocessing the scanning point cloud; step 4, enabling the triangular patches to grow into triangular frustums; and step 5, carrying out square quantity estimation. According to the invention, the point cloud is discretized by triangularizing the set point cloud and growing the triangular patch into the triangular truncated cone; high-accuracy calculation of the total to-be-sprayed square quantity and the local to-be-sprayed square quantity is achieved, environmental perception support isprovided for full-automatic unmanned tunnel guniting operation, and high practical significance is achieved for tunnel engineering machinery automation.

Owner:HARBIN INST OF TECH

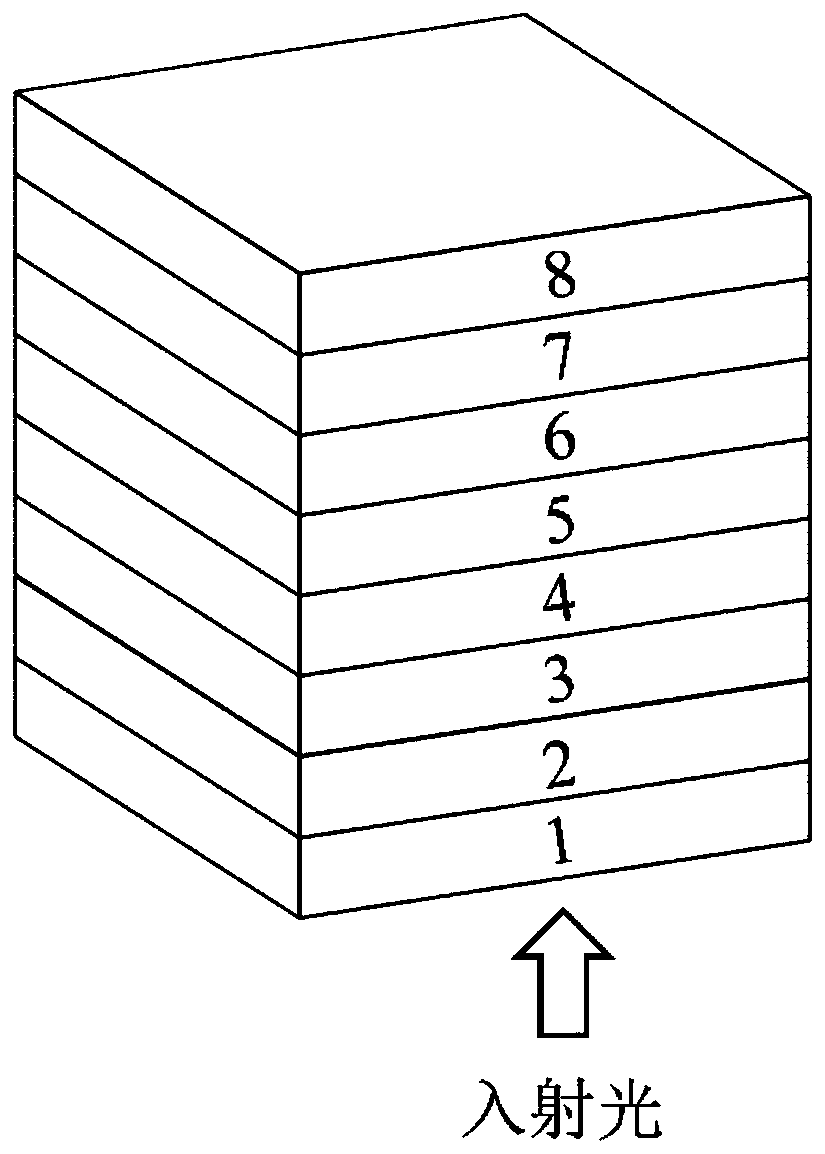

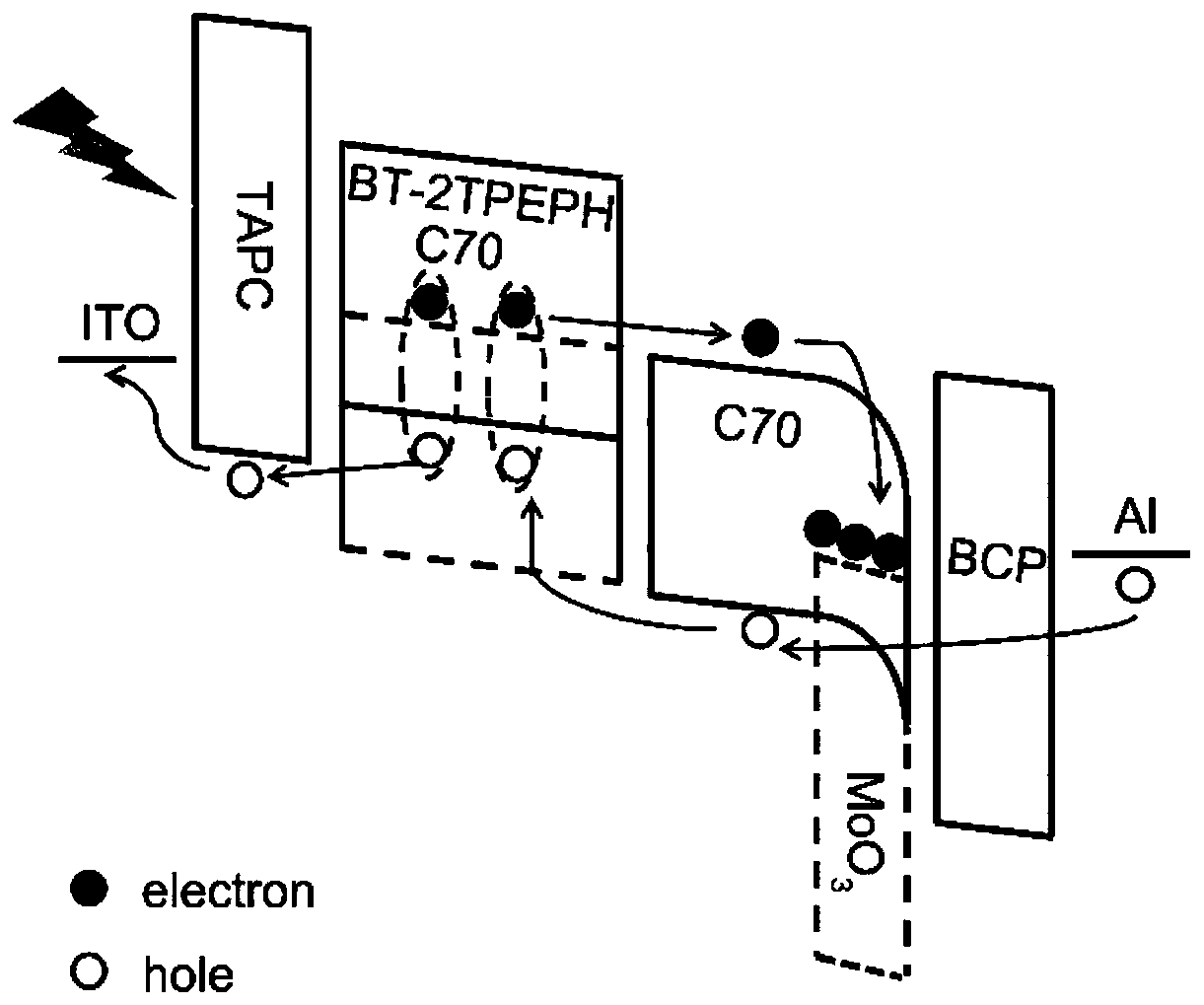

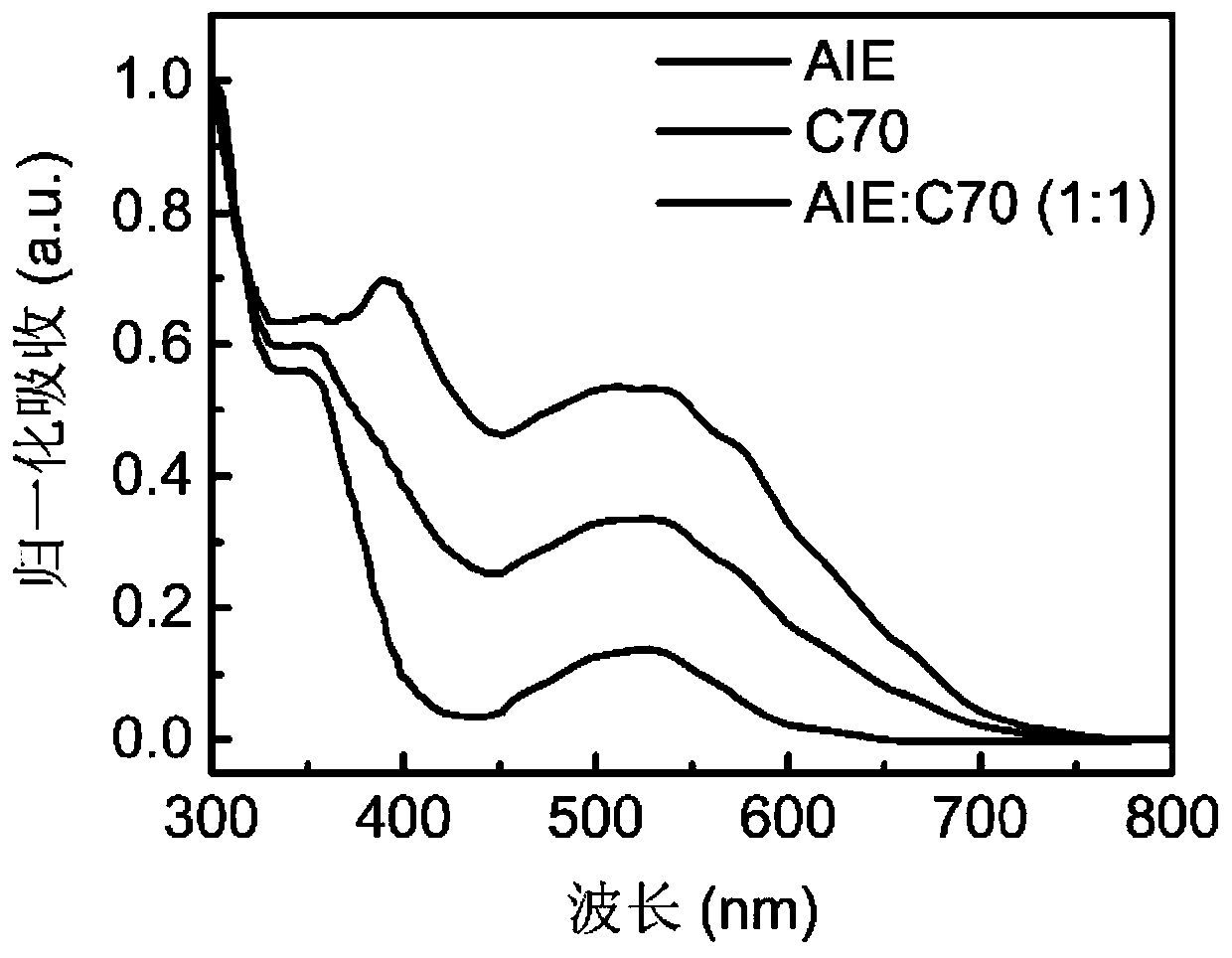

Multiplication type organic photoelectric detector based on AIE material and preparation method thereof

ActiveCN110828670AImprove external quantum efficiencyHigh detection sensitivitySolid-state devicesSemiconductor/solid-state device manufacturingElectron donorHole transport layer

The invention belongs to the field of photoelectric devices, and discloses a multiplication type organic photoelectric detector based on an AIE material and a preparation method thereof. The organic photoelectric detector structure sequentially comprises a transparent substrate, an anode, a hole transport layer, an active layer, a spacer layer, an electron capture layer, an electron transport layer and a metal cathode; the active layer is a blending layer of an electron donor material AIE1 or AIE2 and an electron acceptor material C60 or C70; the spacing layer is C60 or C70; and the electron capture layer is a blending layer of C60 or C70 and MoO3. According to the invention, the AIE material is used as the active layer for the first time, the high-efficiency multiplication type organic photoelectric detector is prepared by using a trapped electron induced hole tunneling injection mechanism, the external quantum conversion efficiency is 60840%, the normalized detection rate is 3.08*1012 Jones, and the application of the AIE material in the field of photoelectric devices is expanded.

Owner:SOUTH CHINA UNIV OF TECH

Non-volatile memory cell

A non-volatile memory cell includes a tunneling part; a coupling device; a read transistor; a first select transistor connected to the read transistor forming a read path with the read transistor in a read mode; an erase tunneling structure forming a tunneling ejection path in an erase mode; and a program tunneling structure forming a tunneling injection path in an program mode; wherein the read path is different from the tunneling ejection path and the tunneling injection path.

Owner:AMIC TECH TAIWAN

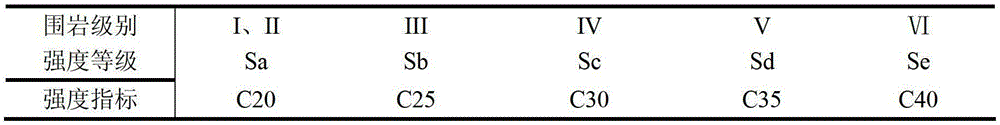

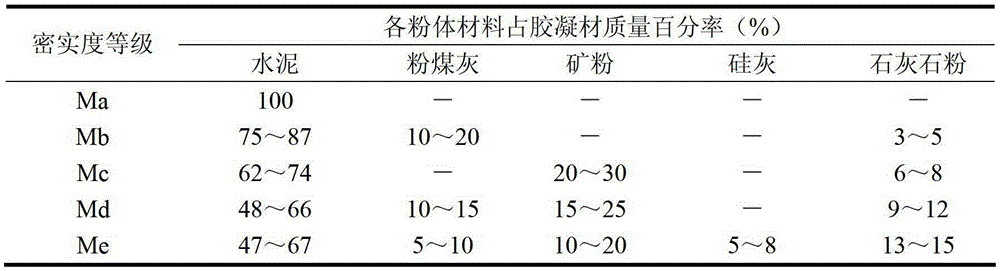

Low-carbon high-performance tunnel shotcrete series

Owner:SOUTHWEST JIAOTONG UNIV

Method for mfg. double layer polysilicon rewritable non-volatile memory

ActiveCN100483690CSimple processShort processing cycleSemiconductor/solid-state device manufacturingLow voltageEngineering

This invention provides a method for manufacturing double-layer polysilicons to re-write fixed storages including the following steps: forming trap N and trap P of high and low voltage MOS devices and multiple isolation zones, carrying out ionic injection dope in a tunnel injection zone of the storage unit, forming a grid oxidation layer of the storage unit, a tunnel penetration window thin grid oxidation layer, polysilicon floating grid and lower electrode of the condenser, depositing ONO complex medium layer and etching it, re-forming a thick grid oxidation layer in the region corresponding to the high voltage MOS device and forming its thin grid oxidation layer corresponding to the low voltage MOS device, depositing a second polysilicon and etching the control grid forming the storage unit and the logic grid forming MOS devices and the upper electrode of the condenser to dope the storage unit, source and drain of the MOS devices.

Owner:ADVANCED SEMICON MFG CO LTD

Making method of electrical absorption modulation tunneling injection type distributed feedback semiconductor laser

InactiveCN102055133BEliminate performance impactRaise the characteristic temperatureLaser detailsLaser output parameters controlGratingElectrode Contact

The invention discloses a making method of an electrical absorption modulation tunneling injection type distributed feedback semiconductor laser, which comprises the following steps of: 1, growing an n-type indium phosphide buffer layer, a lower waveguide external limit layer, a lower waveguide internal limit layer, an indium phosphide tunneling barrier layer, a multiple quantum well active layerand an upper waveguide limit layer on an n-type indium phosphide substrate during the same epitaxy; 2, making a Bragg grating in a laser region, then epitaxially growing a p-type indium phosphide grating covering layer, an InGaAsP etching stopping layer, a p-type indium phosphide covering layer and a p+ InGaAs electrode contact layer largely; and 3, etching a ridge type optical waveguide on an epitaxial wafer, injecting with He ions to improve the resistance of an isolation region, and then passivating and flatting the surface and finally making a p-type and an n-type electrodes. The invention has the advantages of simple process and high reliability, eliminates the influence of hot electrons on the property of the laser, improves the characteristic temperature of the laser, and can realize a certain independent optimization on the laser and a modulator.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Single-polycrystalline EEPROM switch unit structure

PendingCN114284282ATrimming is repeated and preciseRepeatable and precise repeatabilitySolid-state devicesRead-only memoriesTunnel injectionEngineering

The invention discloses a single-polycrystalline EEPROM (Electrically Erasable Programmable Read-Only Memory) switch unit structure, which belongs to the field of microelectronic devices and comprises a p-type Si substrate, a shallow trench isolation (STI), a gate oxide layer, a polycrystalline layer and a liner. A high-voltage p well and a high-voltage n well are formed on the p-type Si substrate; the surface of the p-type Si substrate is divided into three areas, namely a switch tube area, a programming tube area and a control gate area, by a plurality of STIs (shallow trench isolators); a tunneling injection layer is formed on the surface of the programming tube region through n-type ion doping; the gate oxide layer is located on the surface of the p-type Si substrate; the polycrystalline layer is deposited on the surface of the gate oxide layer and covers the switch tube region, the programming tube region, the control gate region and the shallow trench isolation STI; the pads are located on the two sides of the polycrystalline layer, and an N + ion implantation layer and a P + ion implantation layer are formed on the p-type Si substrate through the gate self-alignment process of the pads. According to the invention, a repeated and accurate trimming function can be realized; the method has the prominent advantages of flexible trimming, high trimming yield, low process cost, easy realization of process transplantation and the like.

Owner:58TH RES INST OF CETC

Sonos non-volatile memory and manufacturing method thereof

ActiveCN104425500BAvoid enteringReduce areaSolid-state devicesSemiconductor devicesTunnel injectionUnit structure

The invention discloses a SONOS non-volatile memory. The gates of the SONOS memory transistor and the selection transistor of the unit structure are overlapping two-layer structures isolated by an insulating layer. The first side of the selection transistor is formed with a first insulating dielectric side. wall, the tunnel injection region and the ONO layer of the SONOS memory transistor are all self-aligned with the first insulating dielectric side wall; the entire unit structure only includes two source and drain regions, which do not exist between the gates of the SONOS memory transistor and the selection transistor. Source and drain areas. The invention also discloses a manufacturing method of SONOS non-volatile memory. The present invention directly eliminates a source-drain region between the two transistor gates, can greatly reduce the area of the memory unit, and does not require additional photolithography steps.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

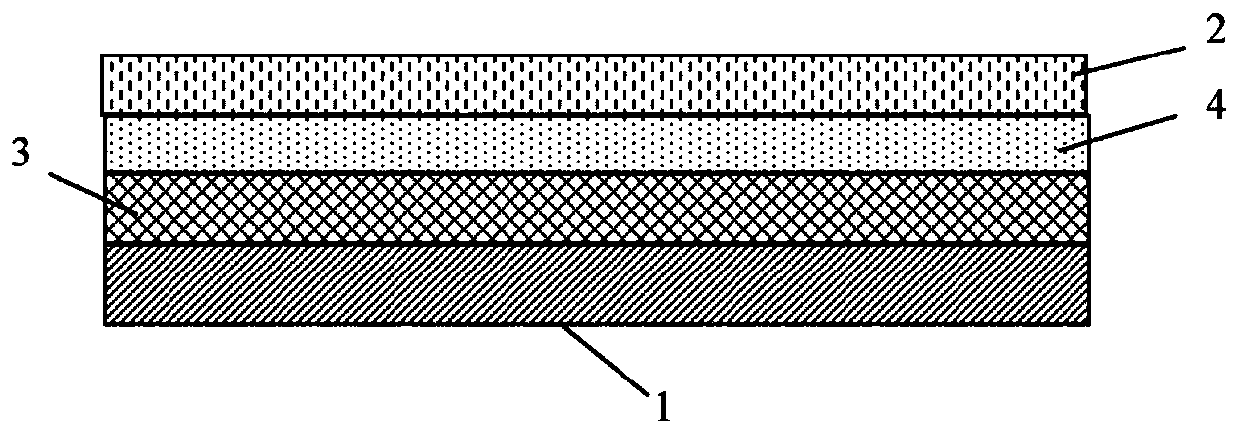

Multilayered electrode and film energy storage device

InactiveCN110192298AThin/thick film capacitorFixed capacitor electrodesTunnel injectionEngineering physics

The present disclosure provides a multilayered electrode comprising an electro-conductive layer and at least one protective layer located on one side of the electro-conductive layer and selected fromthe list comprising a field-planarization layer, a tunneling injection blocking layer and a coulomb blocking layer.

Owner:CAPACITOR SCI