SONOS (silicon oxide nitride oxide semiconductor) nonvolatile memory and manufacturing method thereof

A non-volatile, memory technology, used in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., to achieve the effect of reducing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

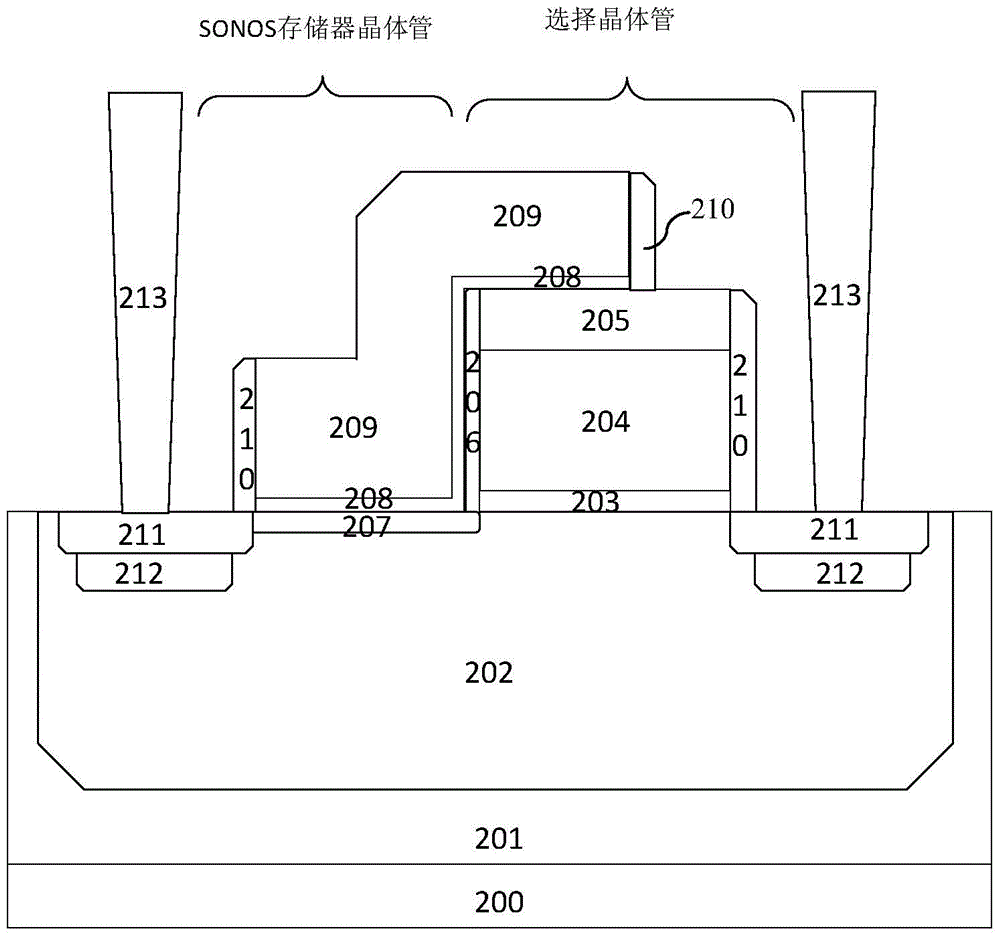

[0042] Such as figure 2 Shown is a cell structure diagram of the SONOS non-volatile memory of the embodiment of the present invention; the cell structure of the SONOS non-volatile memory of the embodiment of the present invention includes a SONOS memory transistor and a selection transistor, and the cell structure is formed in the P well 202 , the P well 202 is formed in the deep N well 201 of the silicon substrate 200 .

[0043] The gate structure of the SONOS memory transistor includes an ONO layer 208 and a first gate conductive material layer 209 sequentially formed on the surface of the P well 202. A three-layer structure composed of an oxide layer, a second nitride layer and a third oxide layer, the ONO layer 208 is used for charge storage; the surface part in the P well 202 at the bottom of the ONO layer 208 is formed with Tunnel implantation region 207, the tunnel implantation region 207 is used to provide electrons for direct tunneling, the tunnel implantation regio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More