Storage unit and method for forming a storage unit

A storage unit, a pair of technology, applied in the direction of electrical components, transistors, electrical solid-state devices, etc., can solve the problems of reducing the life of the gate oxide layer, reducing the reliability of components, and high cost, so as to suppress the short channel effect and enhance Reliability, effect of small size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the above-mentioned purposes, features and advantages of the present invention more obvious and understandable, a preferred embodiment is specifically cited below, and in conjunction with the accompanying drawings, the detailed description is as follows:

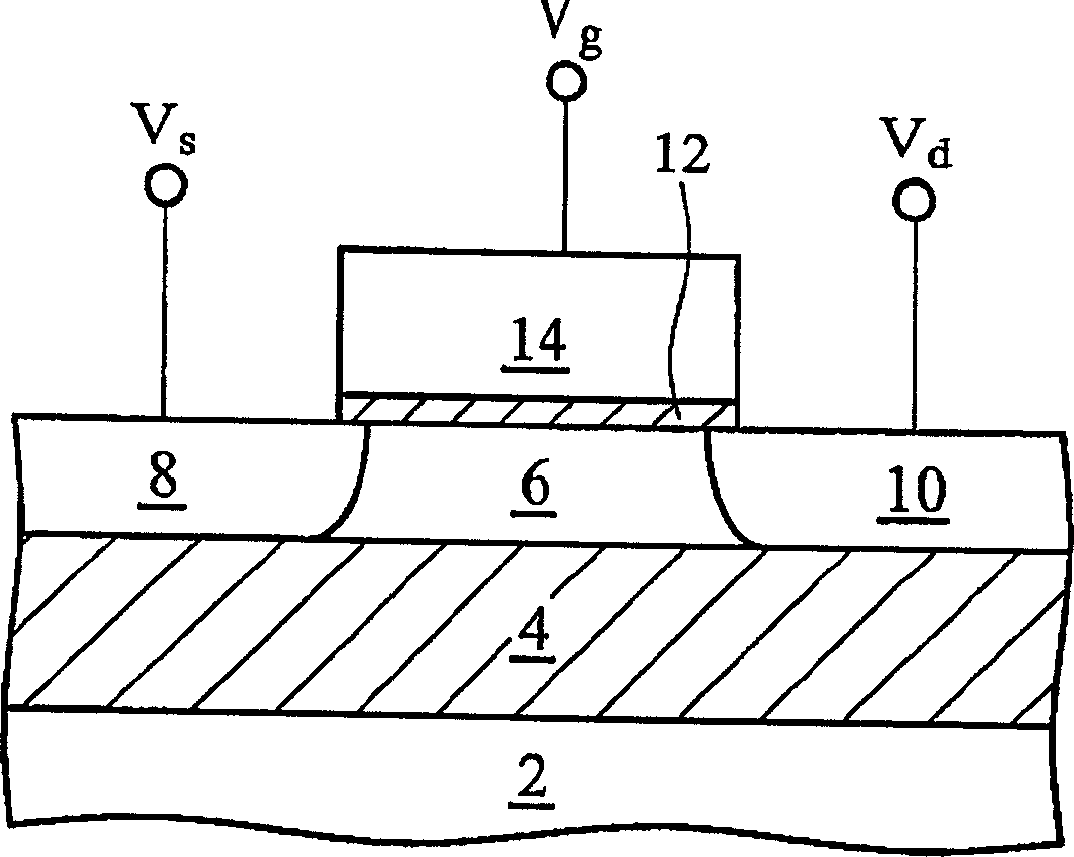

[0032] The structure with Schottky source / drain according to the embodiment of the present invention and its manufacturing method are described below. The intermediate steps of the manufacturing method are illustrated schematically. Then explore the various variations and how they work. The numbers of all illustrations are in one-to-one correspondence with the objects described.

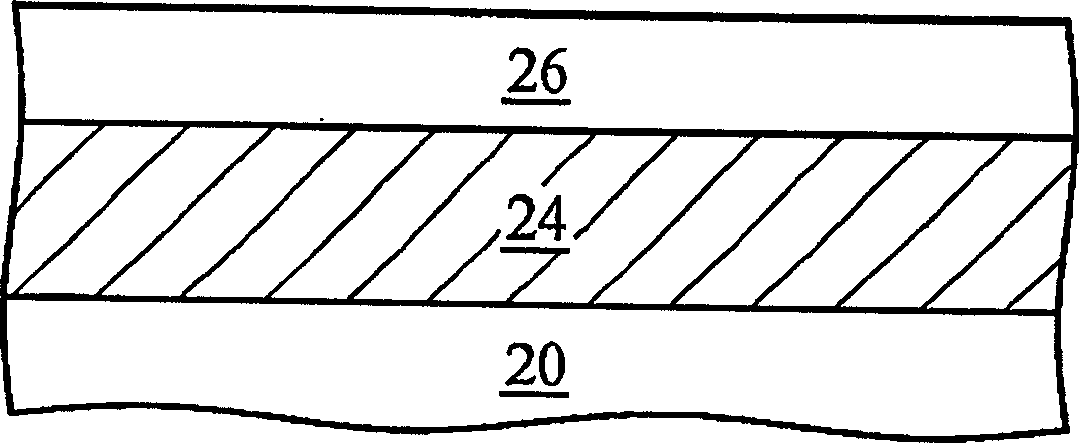

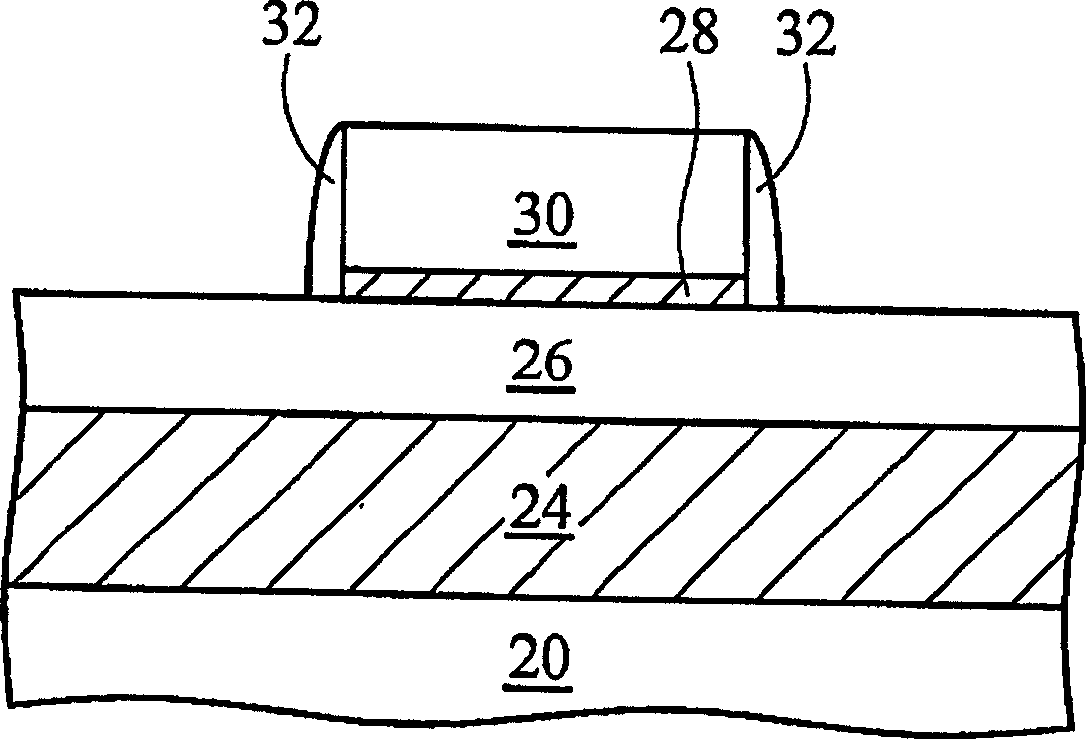

[0033] Figure 2 to Figure 5 are intermediate steps showing the manufacturing method according to the embodiment of the present invention. figure 2 A silicon-on-insulator structure is shown. An insulating layer (insulator) 24 is formed on a substrate (substrate) 20 . A semiconductor layer (semiconductor) 26 is formed o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More