Method for mfg. double layer polysilicon rewritable non-volatile memory

A non-volatile, polysilicon technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of complex manufacturing process, increase production cost, and lengthen process cycle, so as to reduce production cost and simplify process flow , The effect of shortening the process cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The above and other features, nature and advantages of the present invention will become more apparent in the following detailed description in conjunction with the above-mentioned accompanying drawings.

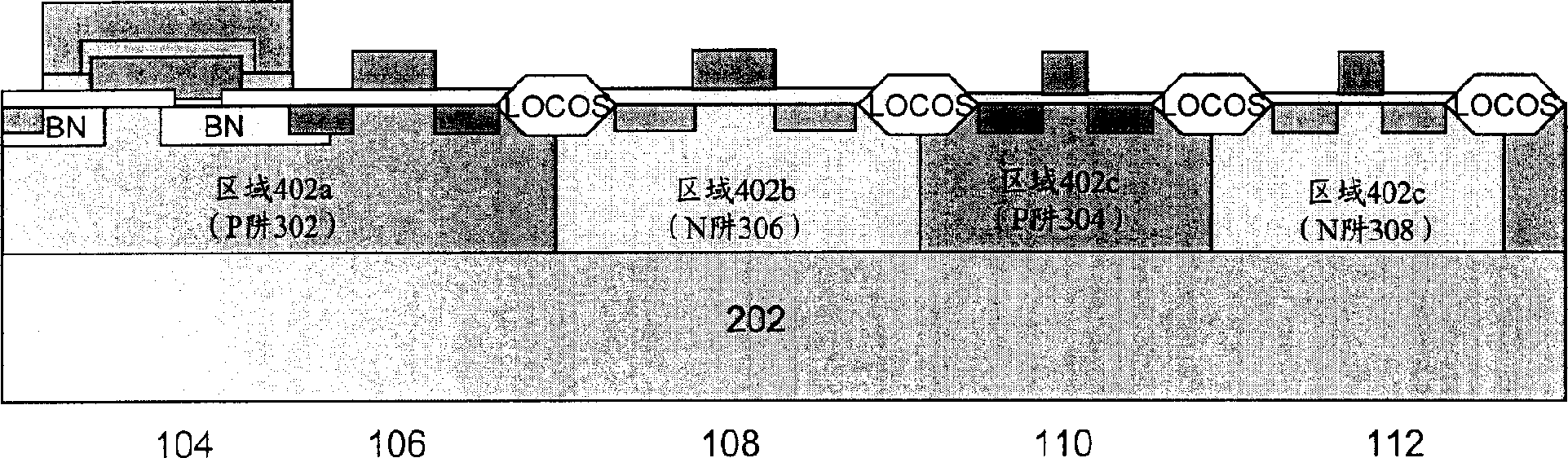

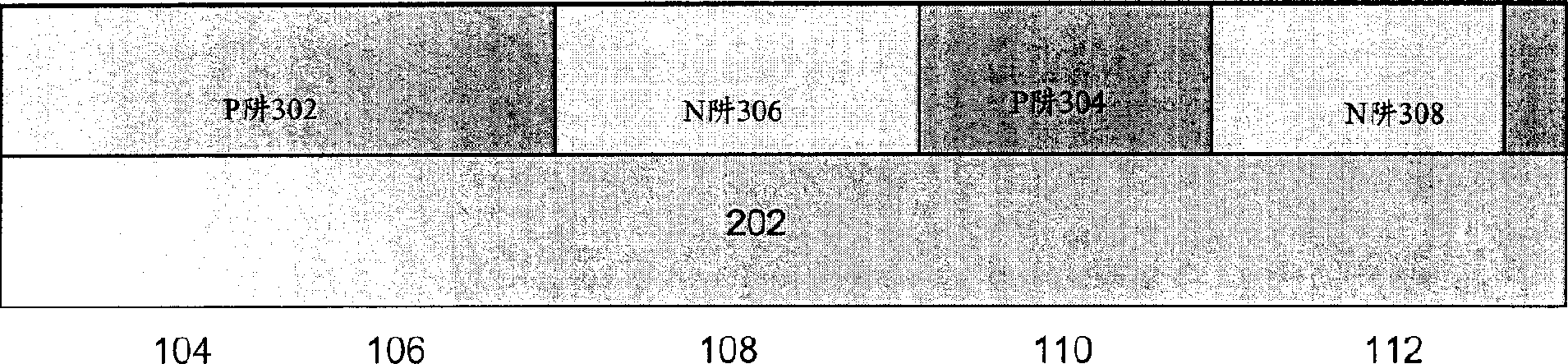

[0037] Figure 11 Shown is a production process flow chart according to an embodiment of the present invention, which depicts the process flow of manufacturing double-layer polysilicon electrically rewritable non-volatile memory, the most important features of which are high-voltage MOS devices and low-voltage MOS devices. The device uses the same N-well and P-well. and Figure 2-Figure 10 The component structure diagram after each process step is revealed in detail. Attached below Figure 2-11 The process flow of this embodiment is described in detail.

[0038] figure 2 Shown is a structural diagram of a silicon substrate used to prepare the double-layer polysilicon electrically rewritable non-volatile memory of the present invention. The present invention ado...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More