Low-power consumption tunneling field effect transistor (TFET) of fork-structure grid structure

A tunneling field effect and transistor technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of insufficient driving current, complex process, increased cost and process complexity, etc., to achieve improved sub-threshold slope and large tunneling Area, the effect of increasing the on-current of the device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described below by example. It should be noted that the purpose of the disclosed embodiments is to help further understand the present invention, but those skilled in the art can understand that various replacements and modifications are possible without departing from the spirit and scope of the present invention and the appended claims of. Therefore, the present invention should not be limited to the content disclosed in the embodiments, and the protection scope of the present invention is subject to the scope defined in the claims.

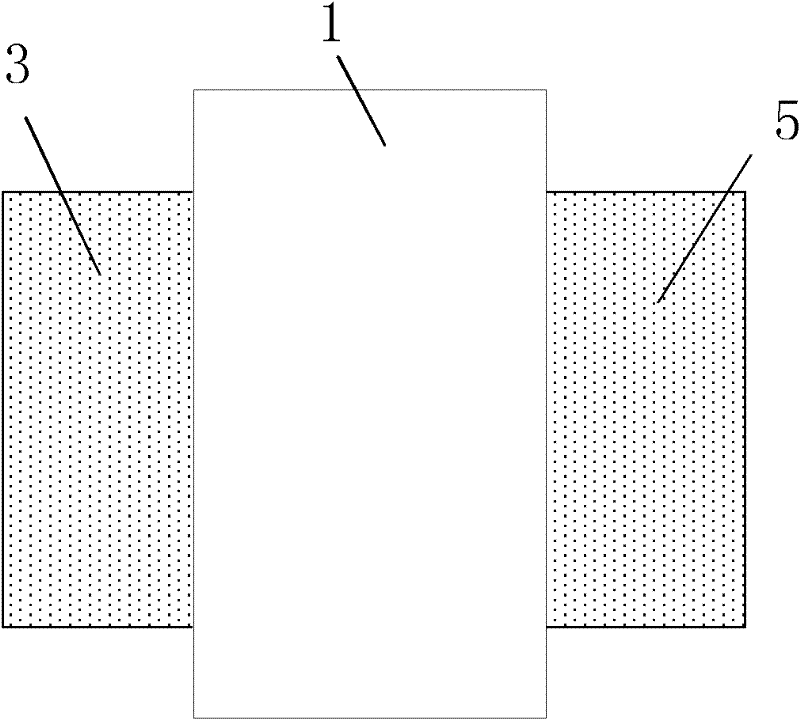

[0024] The invention can be prepared completely by adopting the conventional TFET process flow, and the key part is the layout structure of the grid.

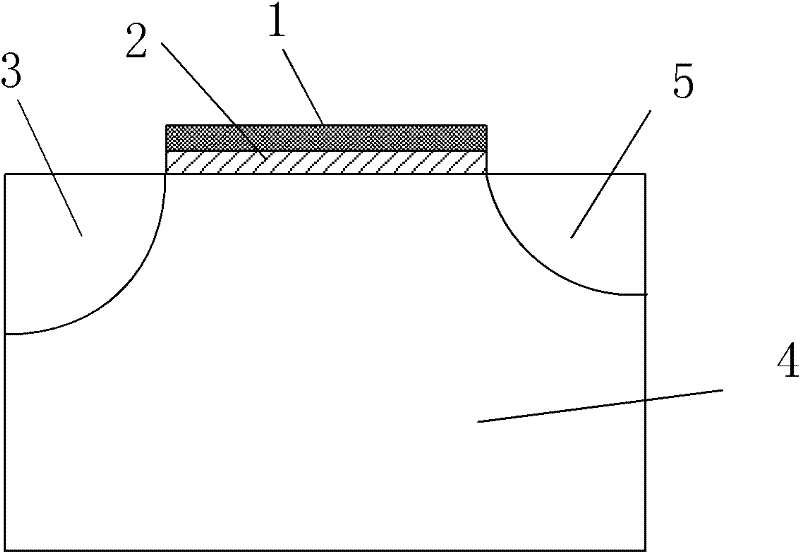

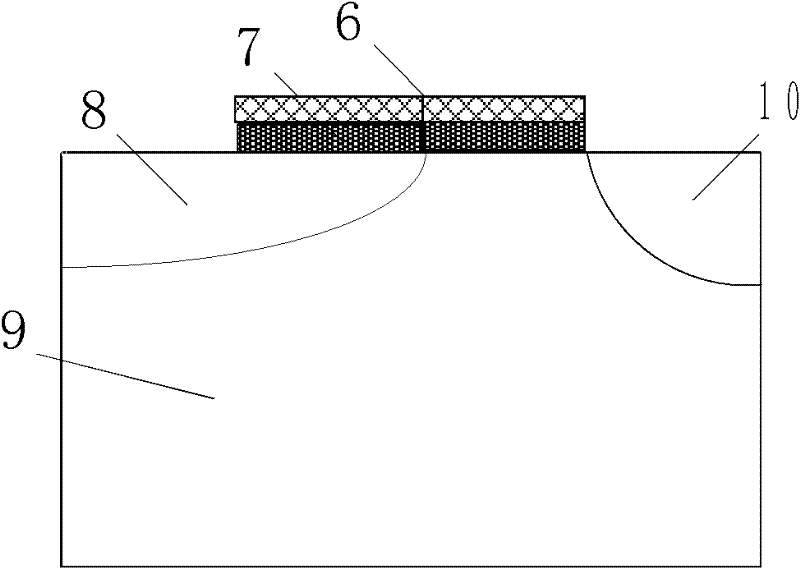

[0025] The specific implementation steps are shown in Figure 3:

[0026] 1. Grow the gate oxide layer 7 on the substrate 9. The smaller the gate thickness, the better the gate control capability of the device. The ideal value is about 4nm-20nm, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More