Patents

Literature

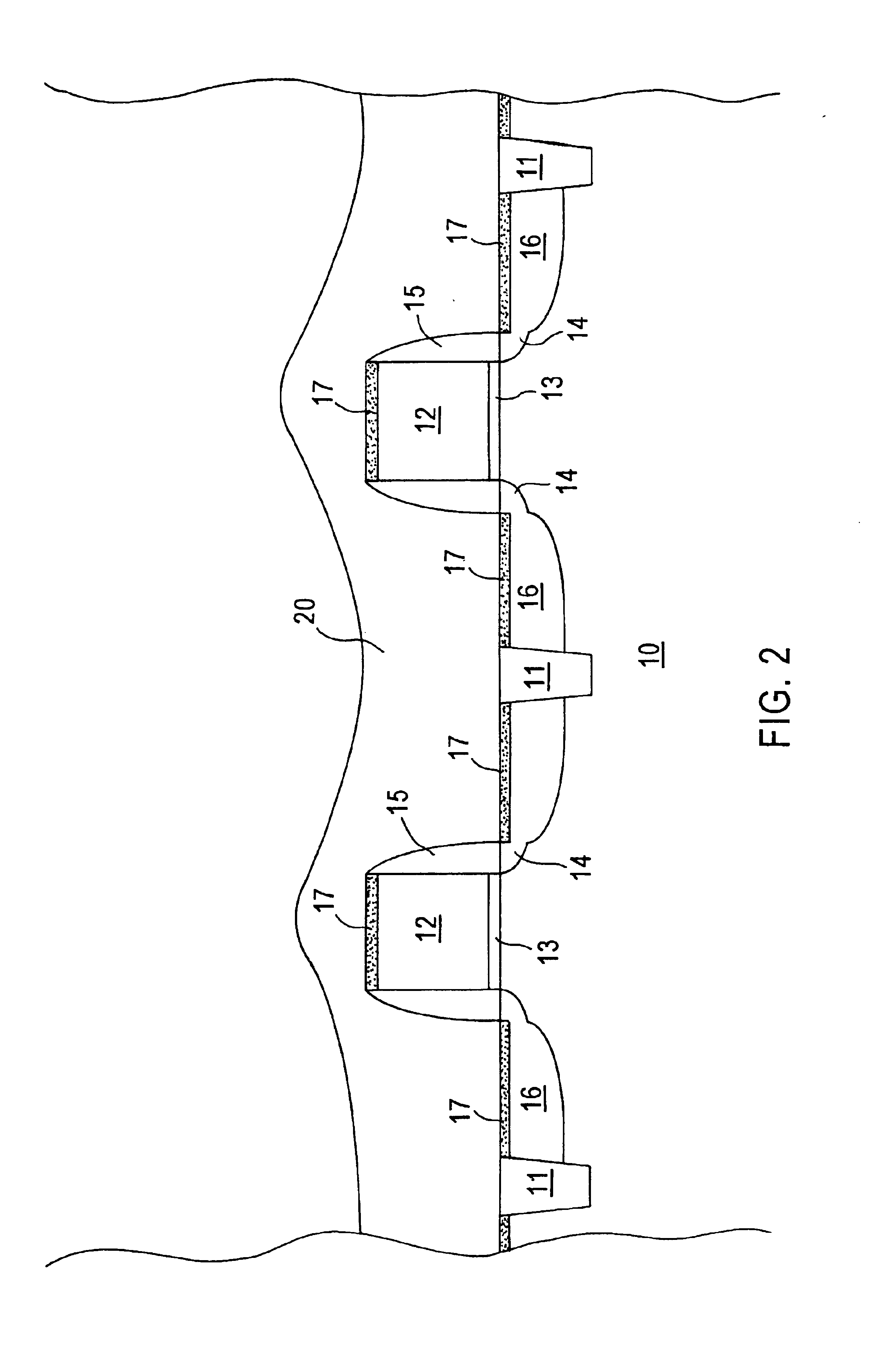

377 results about "Gate resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

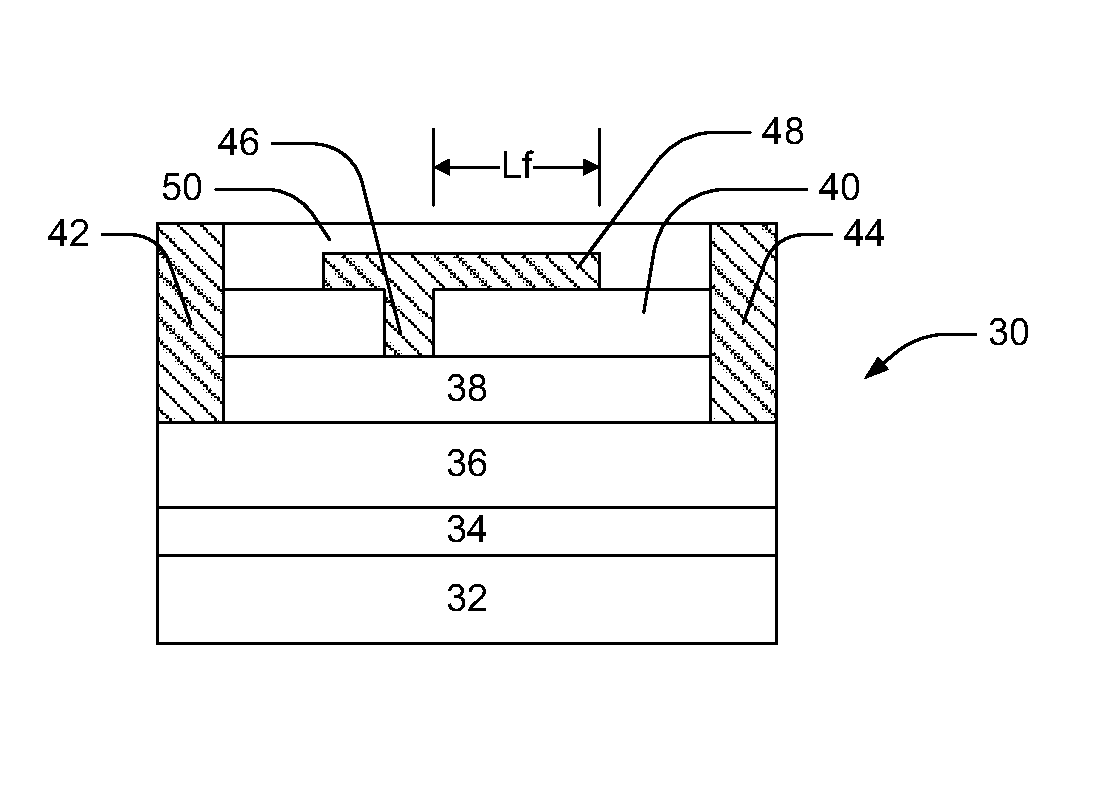

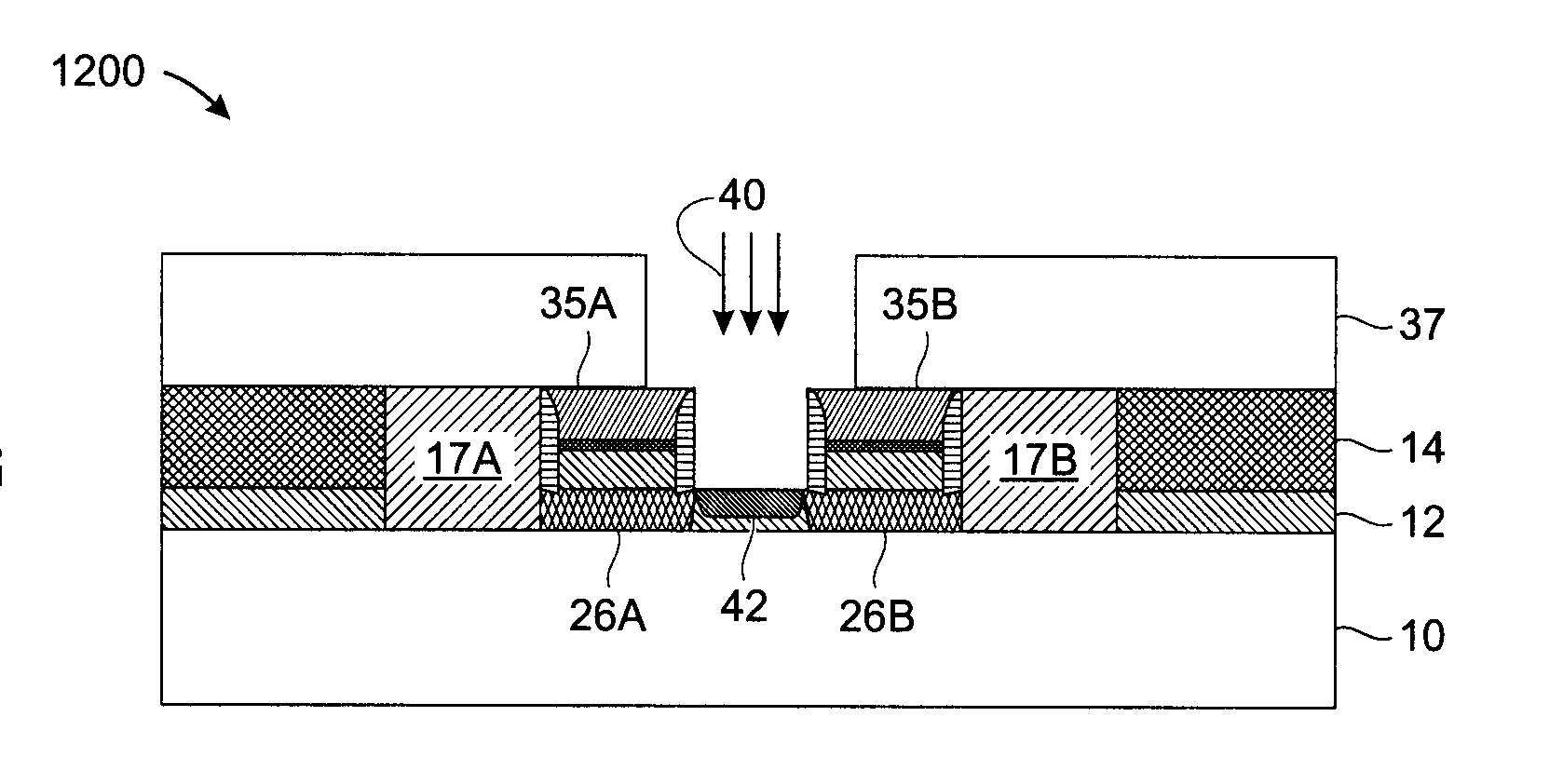

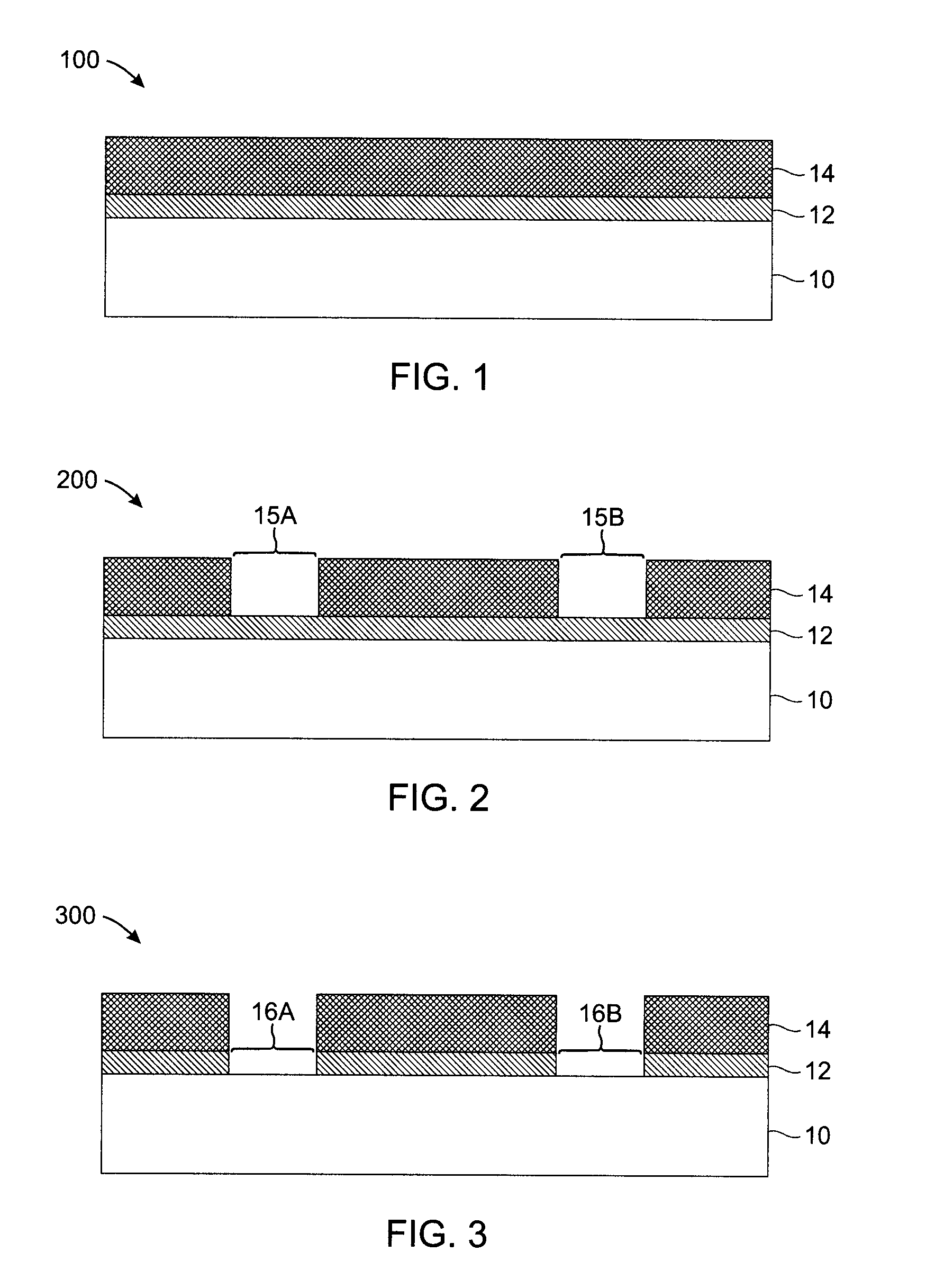

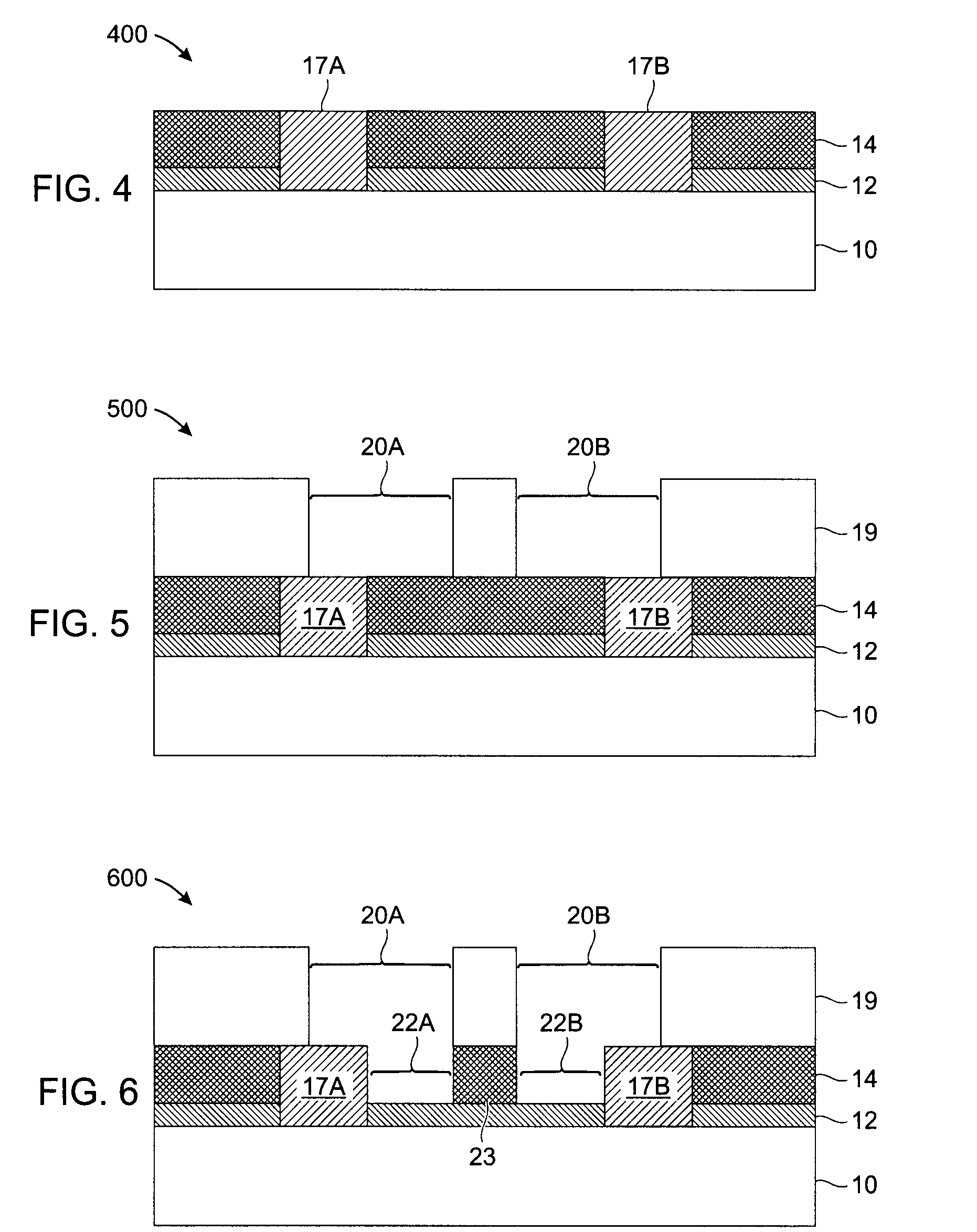

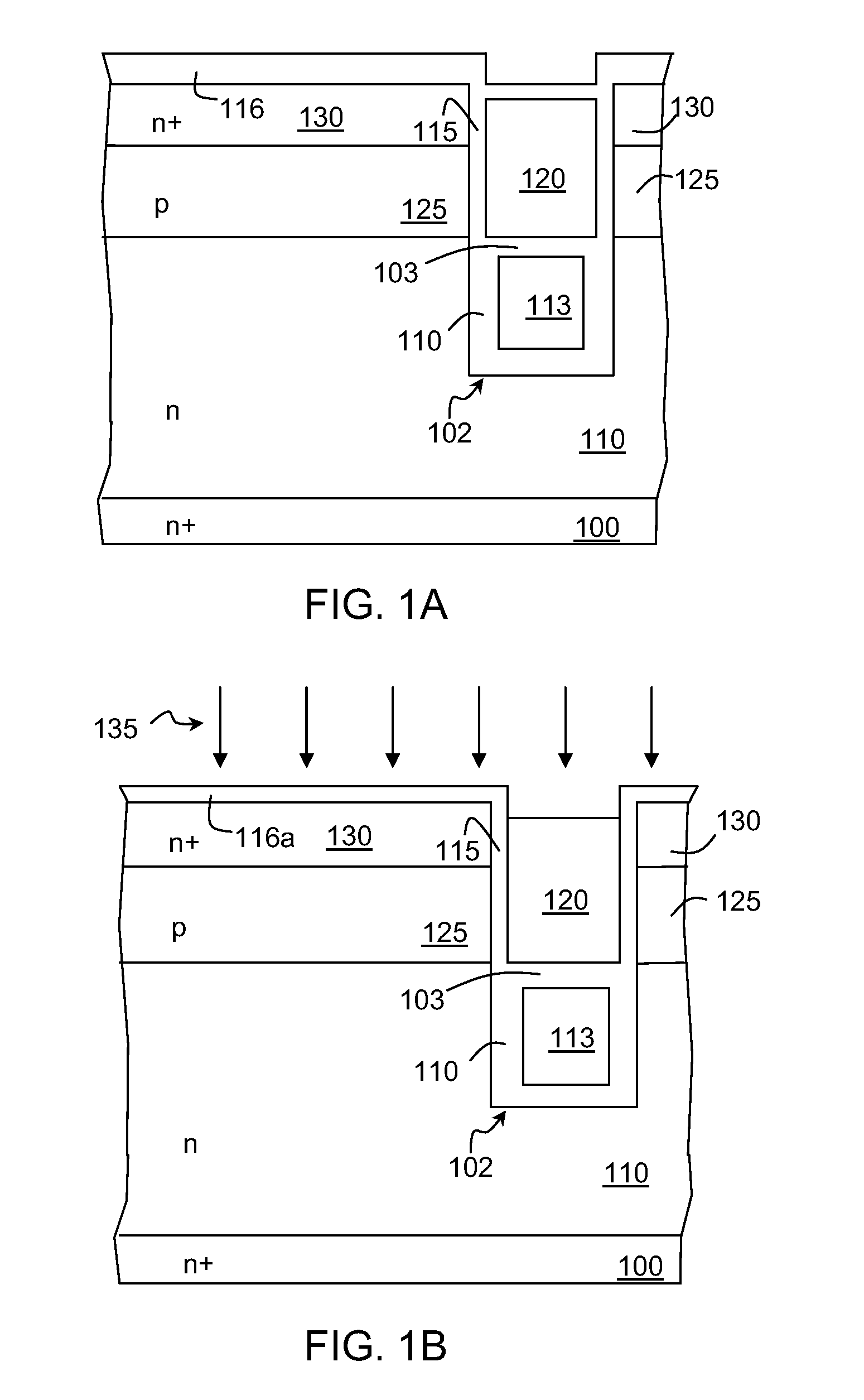

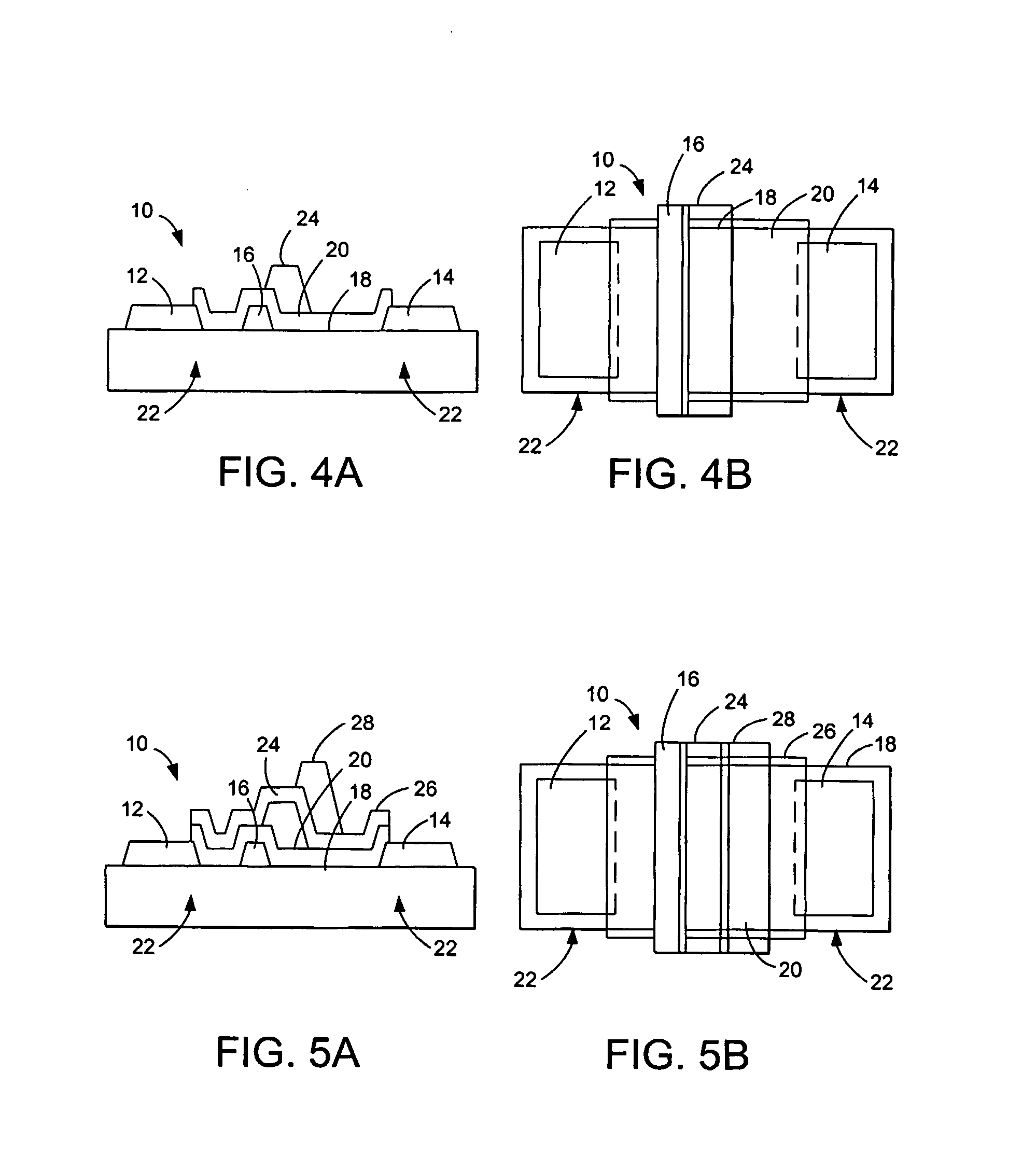

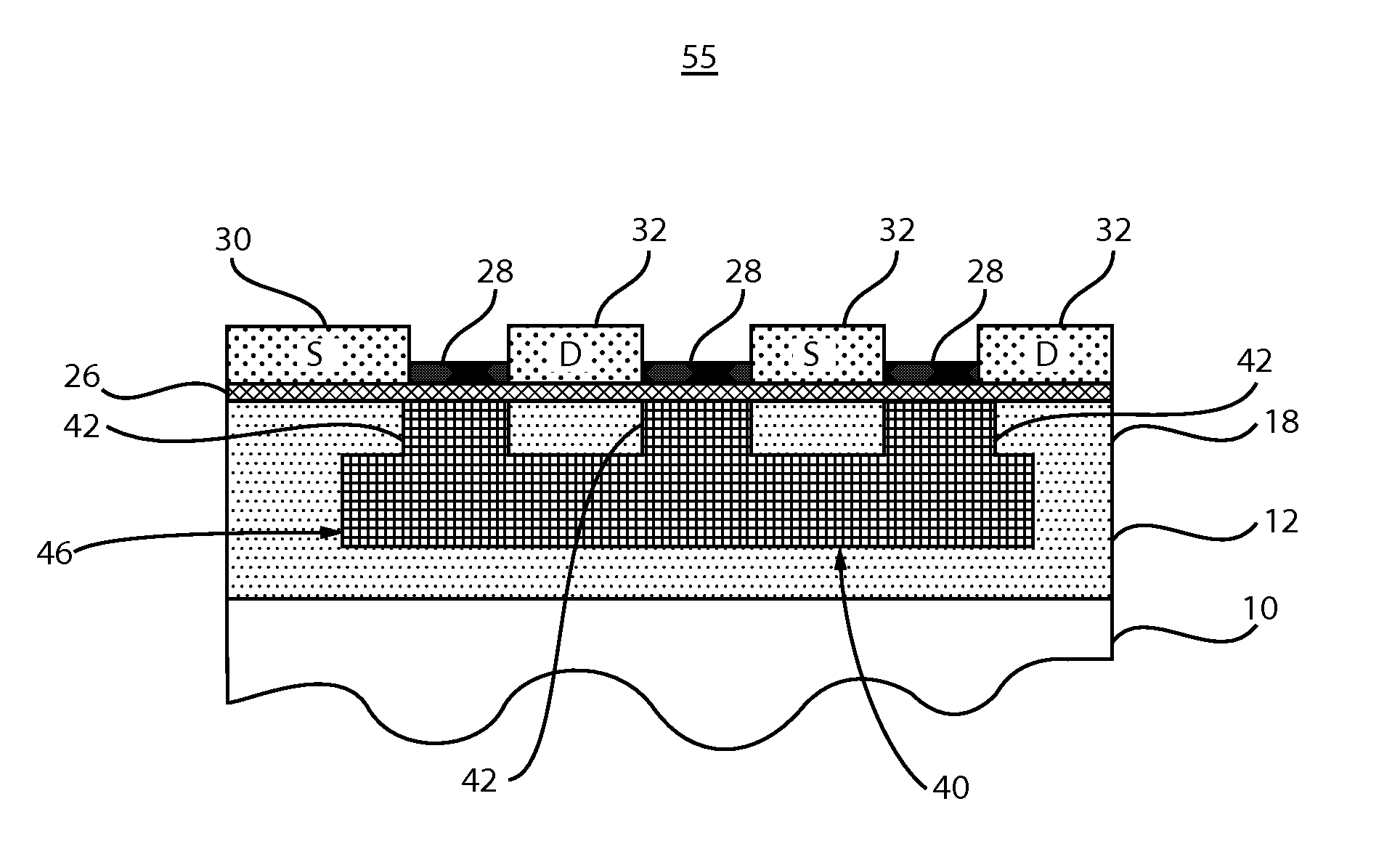

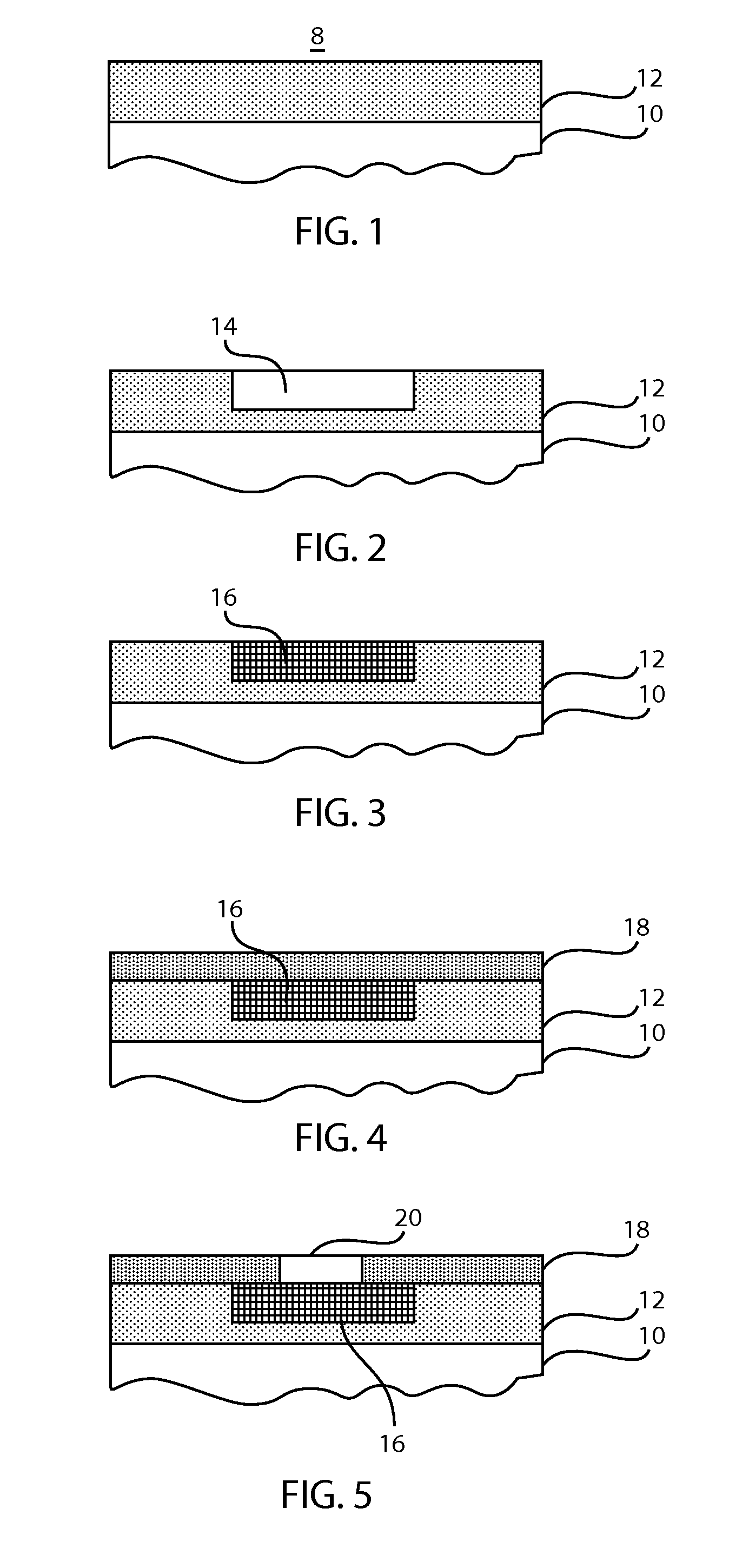

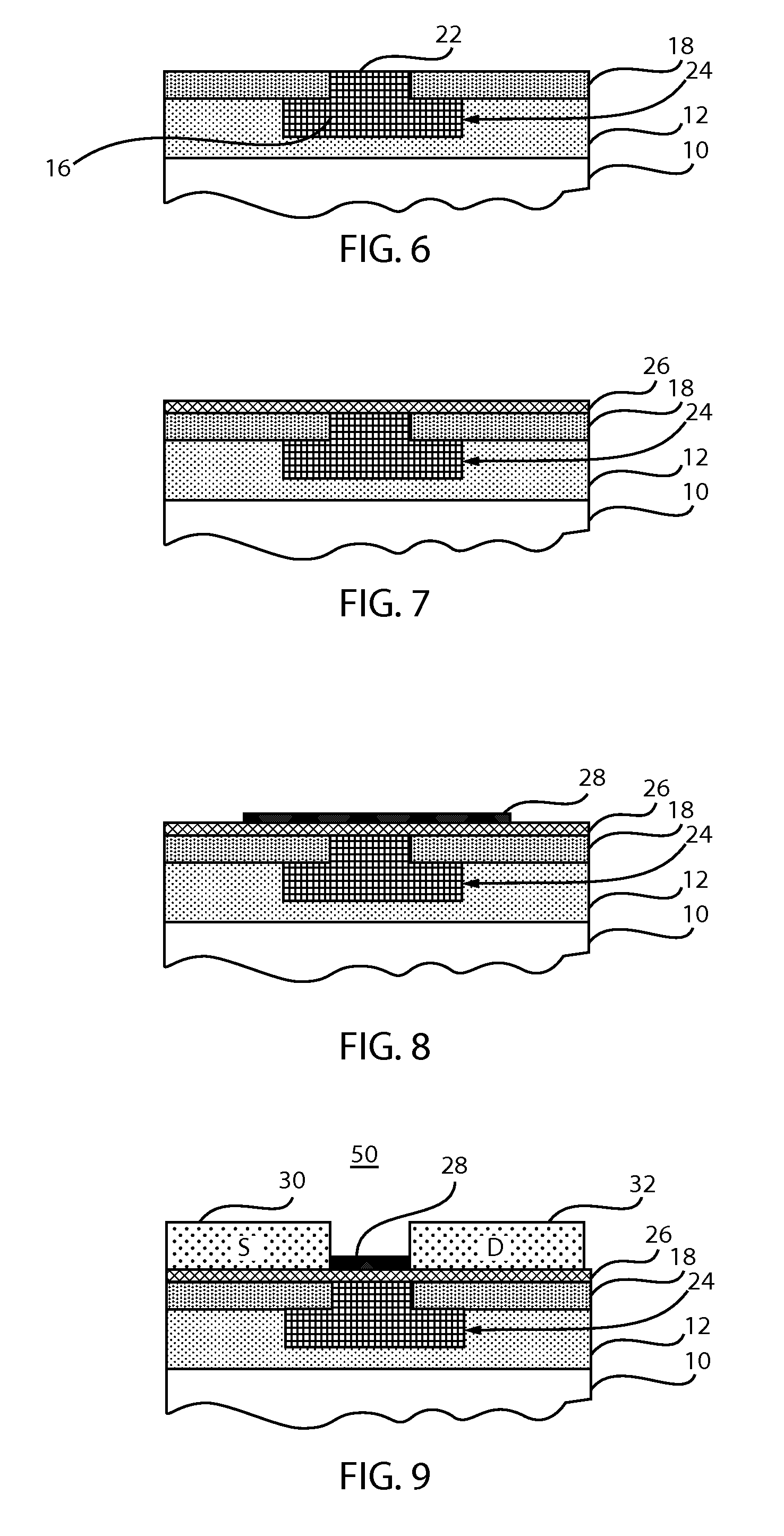

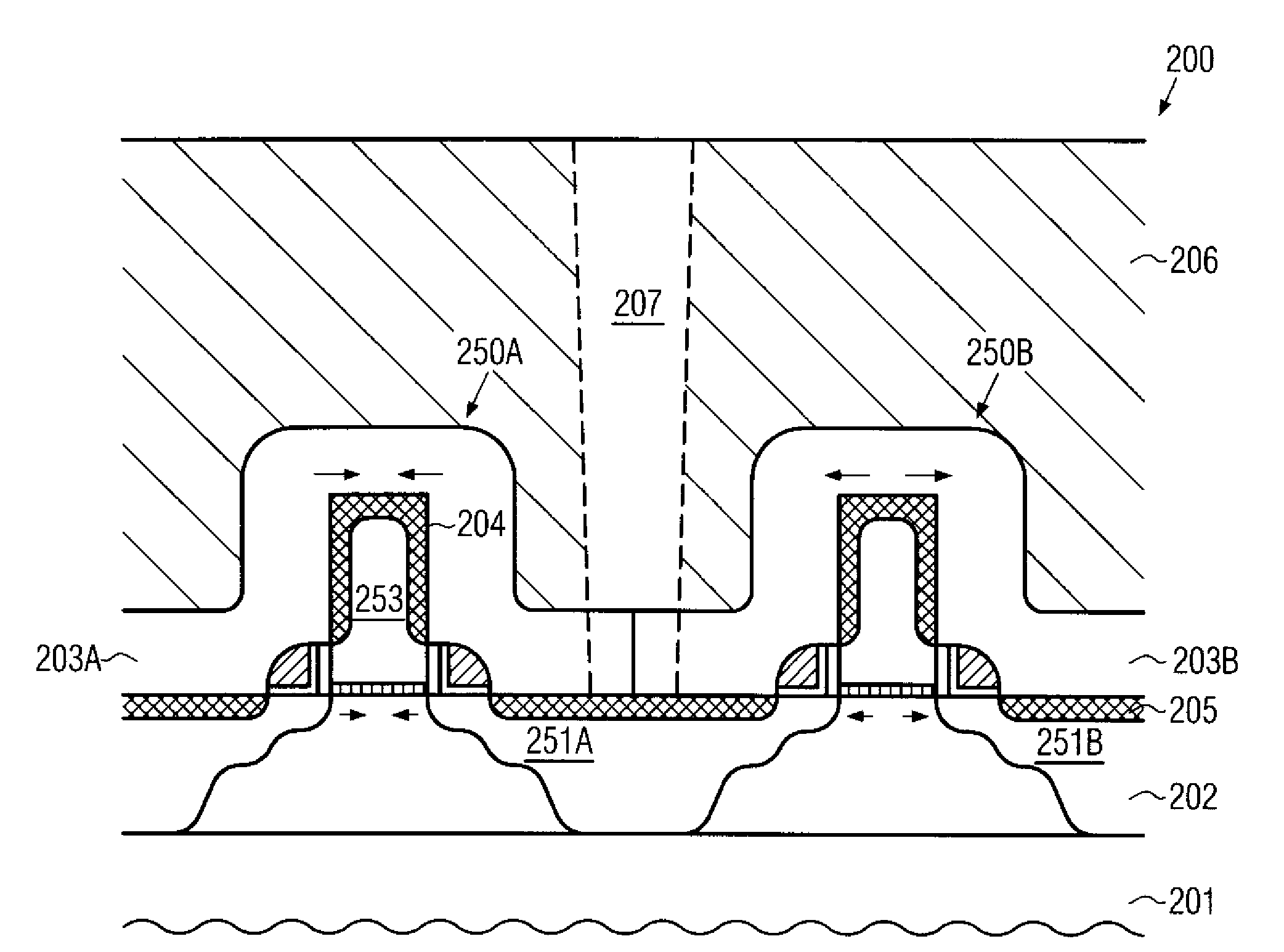

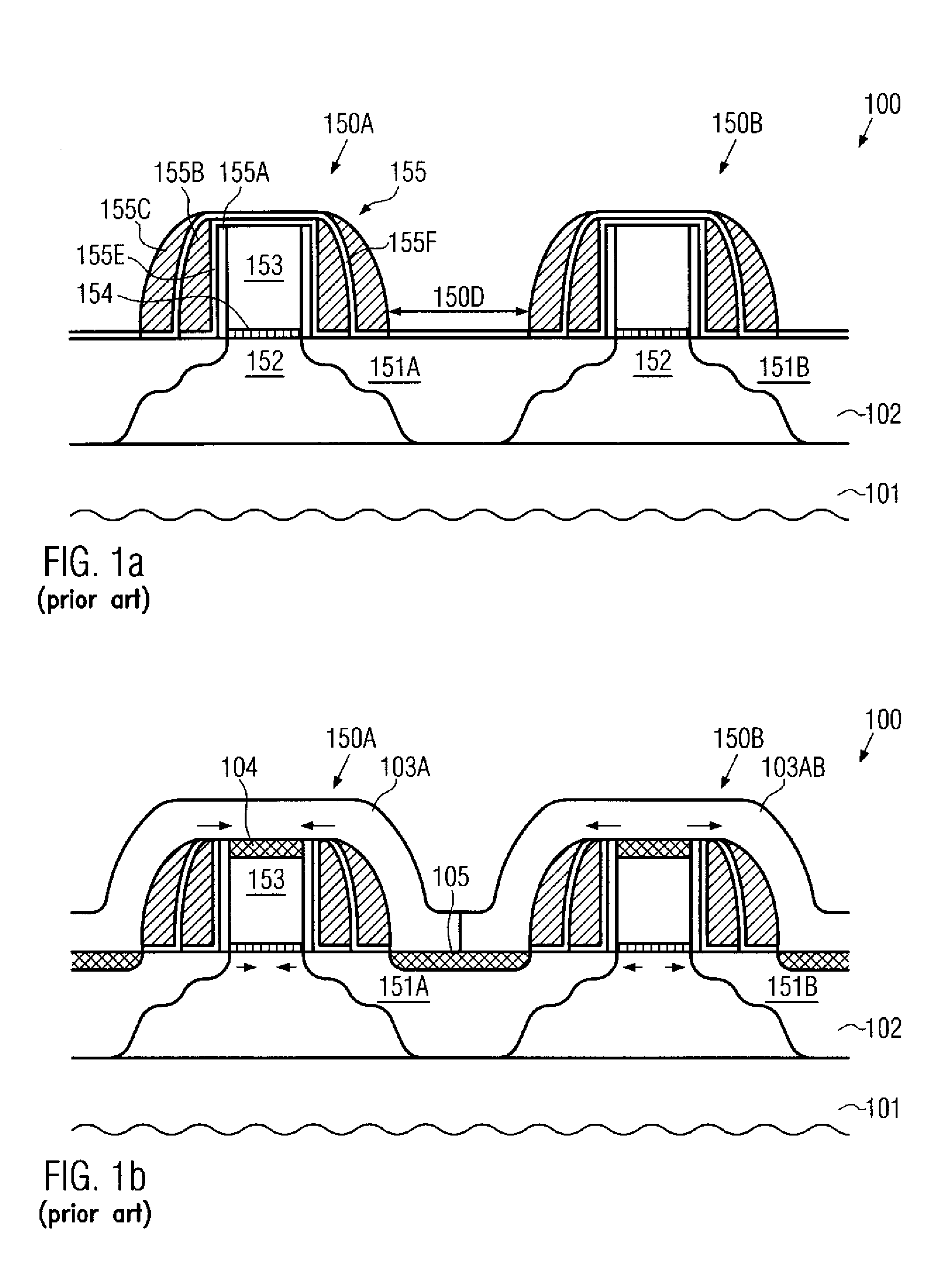

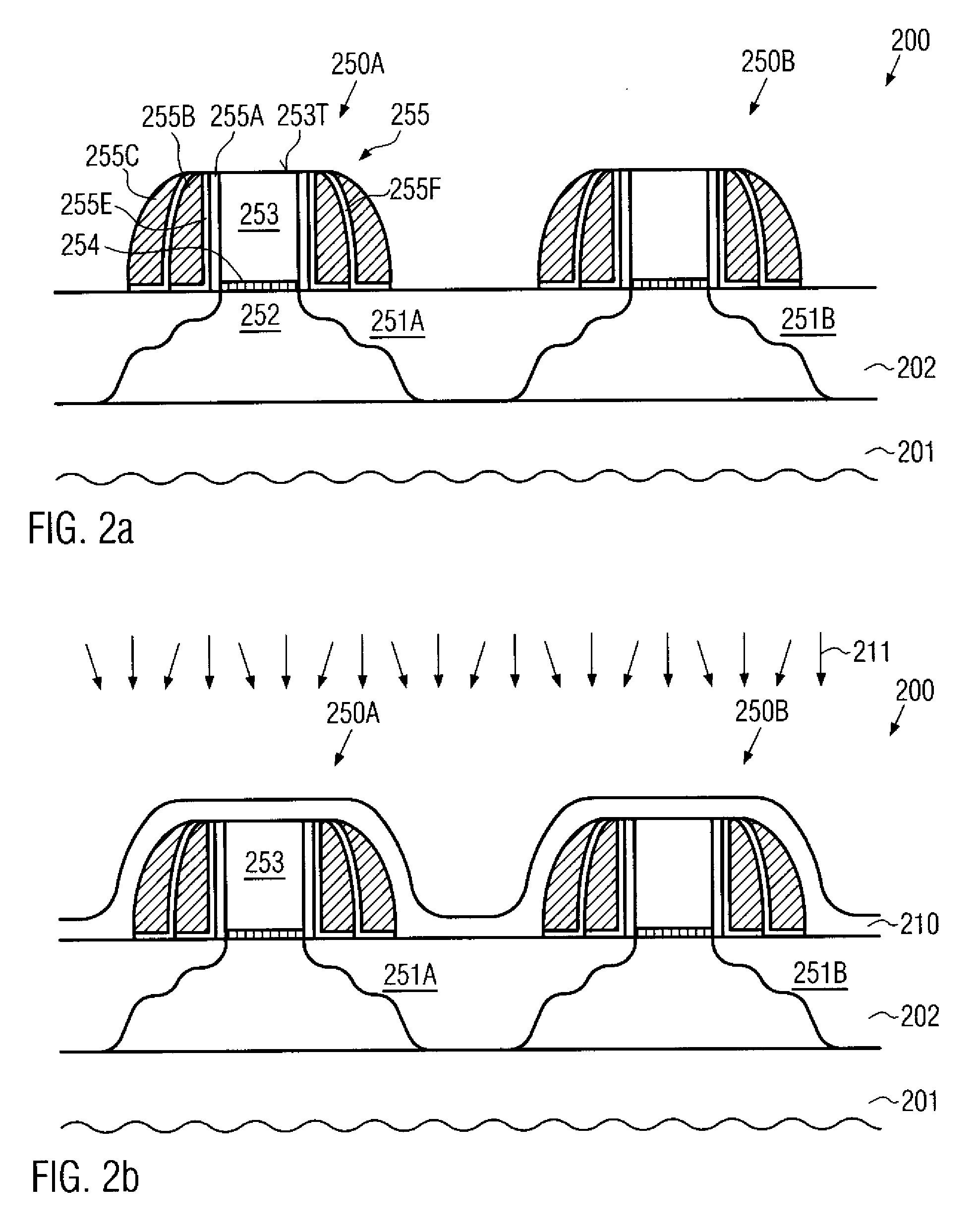

Fabrication of single or multiple gate field plates

ActiveUS7812369B2Strict controlLower gate resistanceSolid-state devicesSemiconductor/solid-state device manufacturingDielectricManufacturing technology

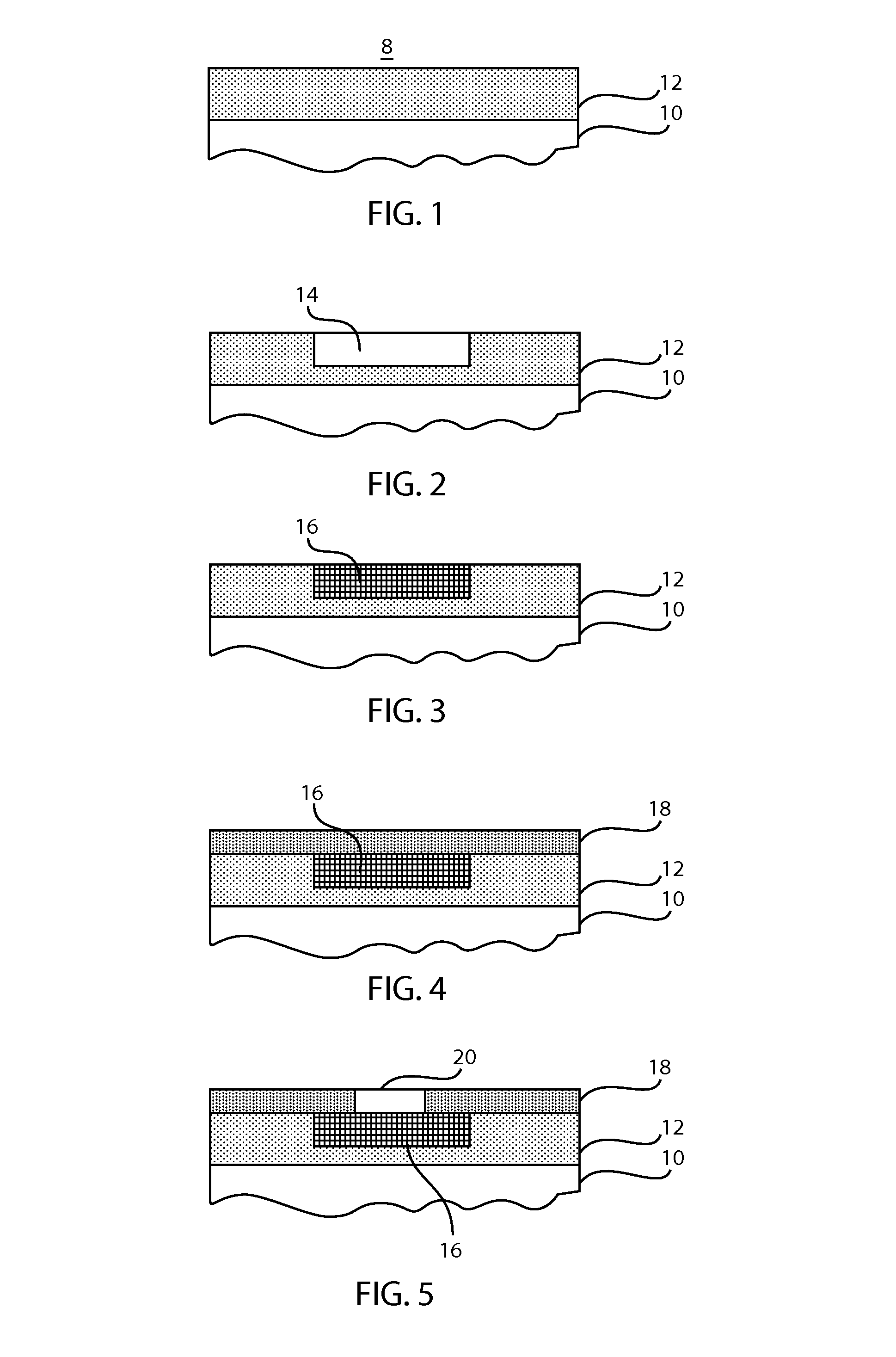

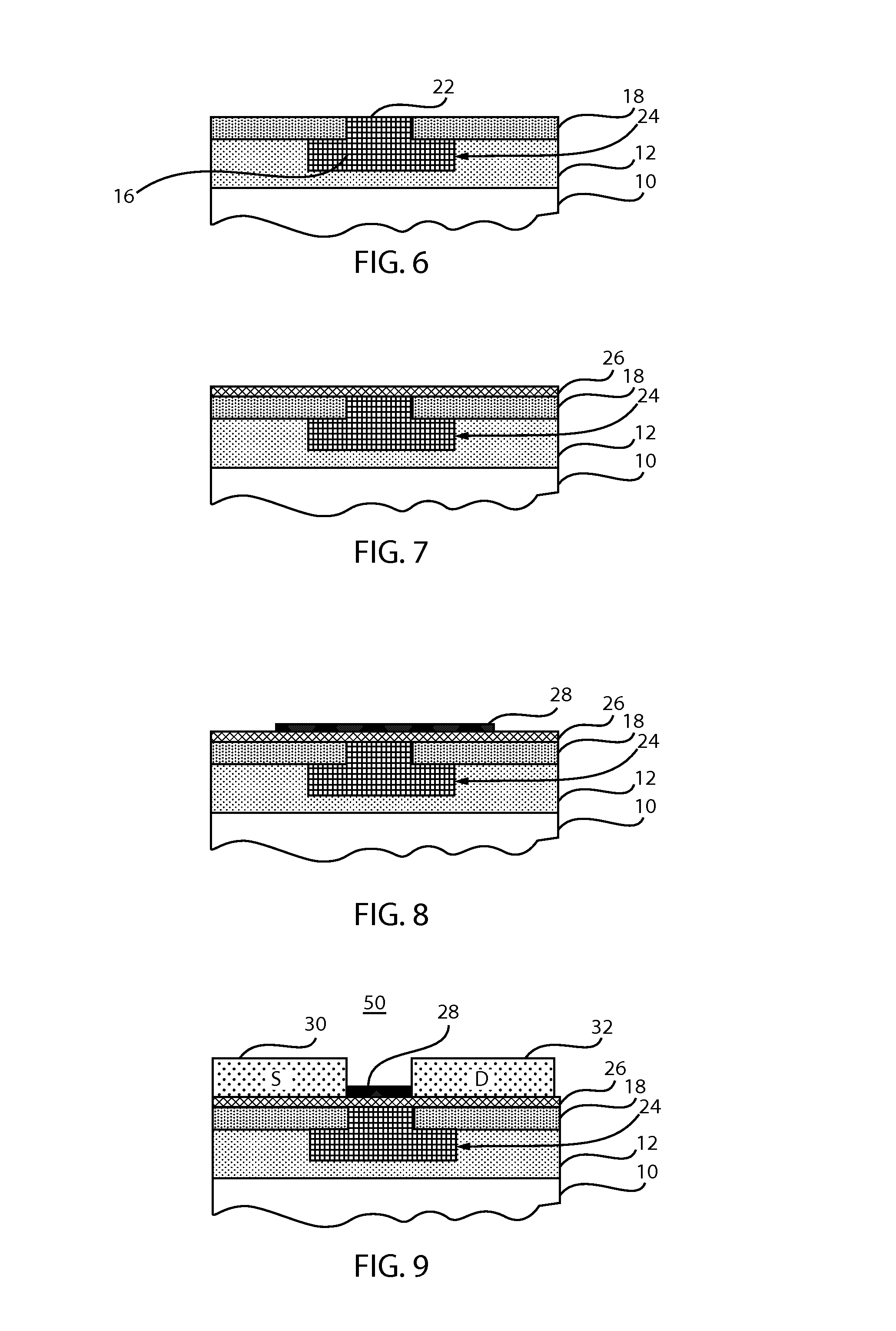

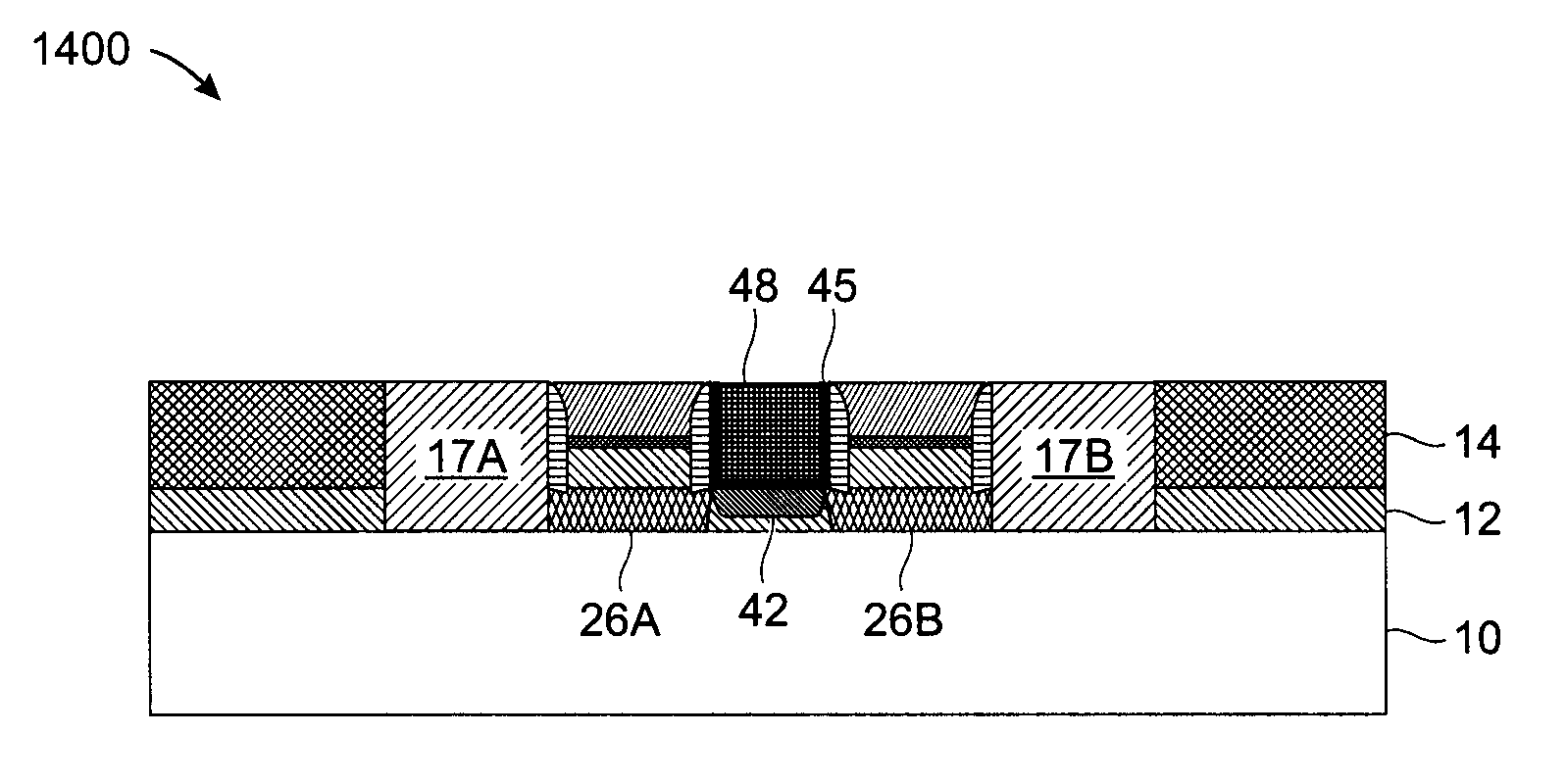

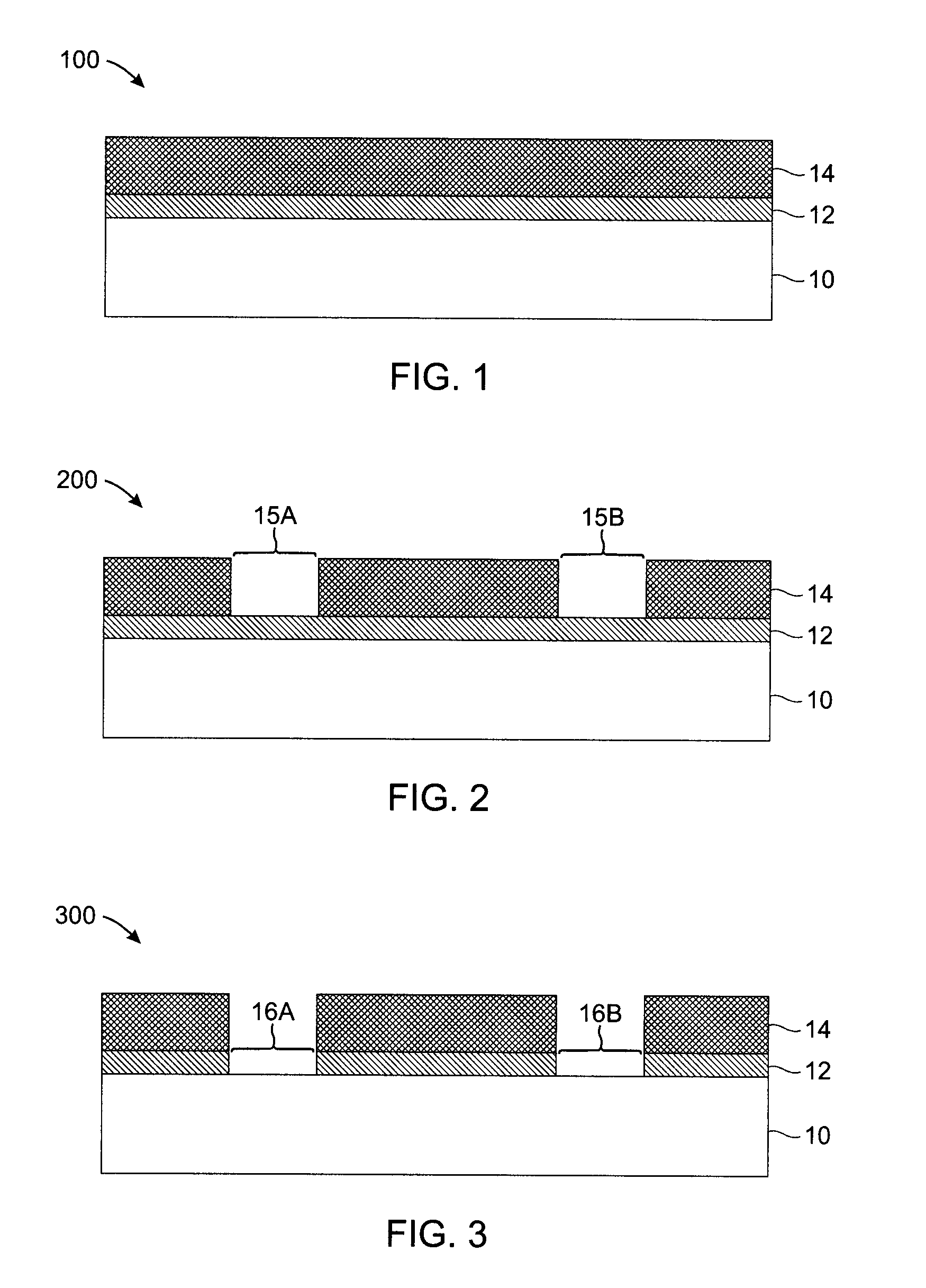

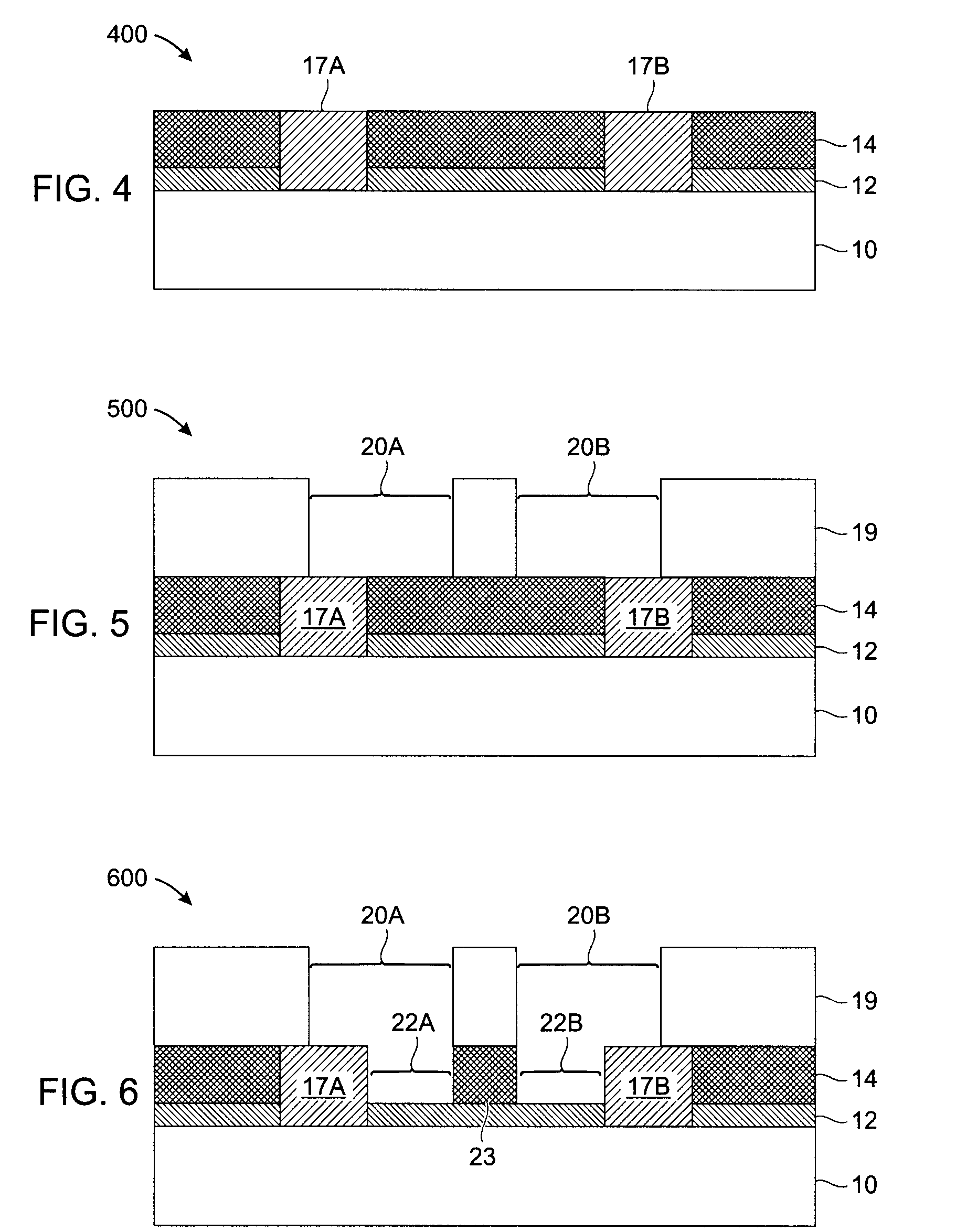

A process for fabricating single or multiple gate field plates using consecutive steps of dielectric material deposition / growth, dielectric material etch and metal evaporation on the surface of a field effect transistors. This fabrication process permits a tight control on the field plate operation since dielectric material deposition / growth is typically a well controllable process. Moreover, the dielectric material deposited on the device surface does not need to be removed from the device intrinsic regions: this essentially enables the realization of field-plated devices without the need of low-damage dielectric material dry / wet etches. Using multiple gate field plates also reduces gate resistance by multiple connections, thus improving performances of large periphery and / or sub-micron gate devices.

Owner:RGT UNIV OF CALIFORNIA +1

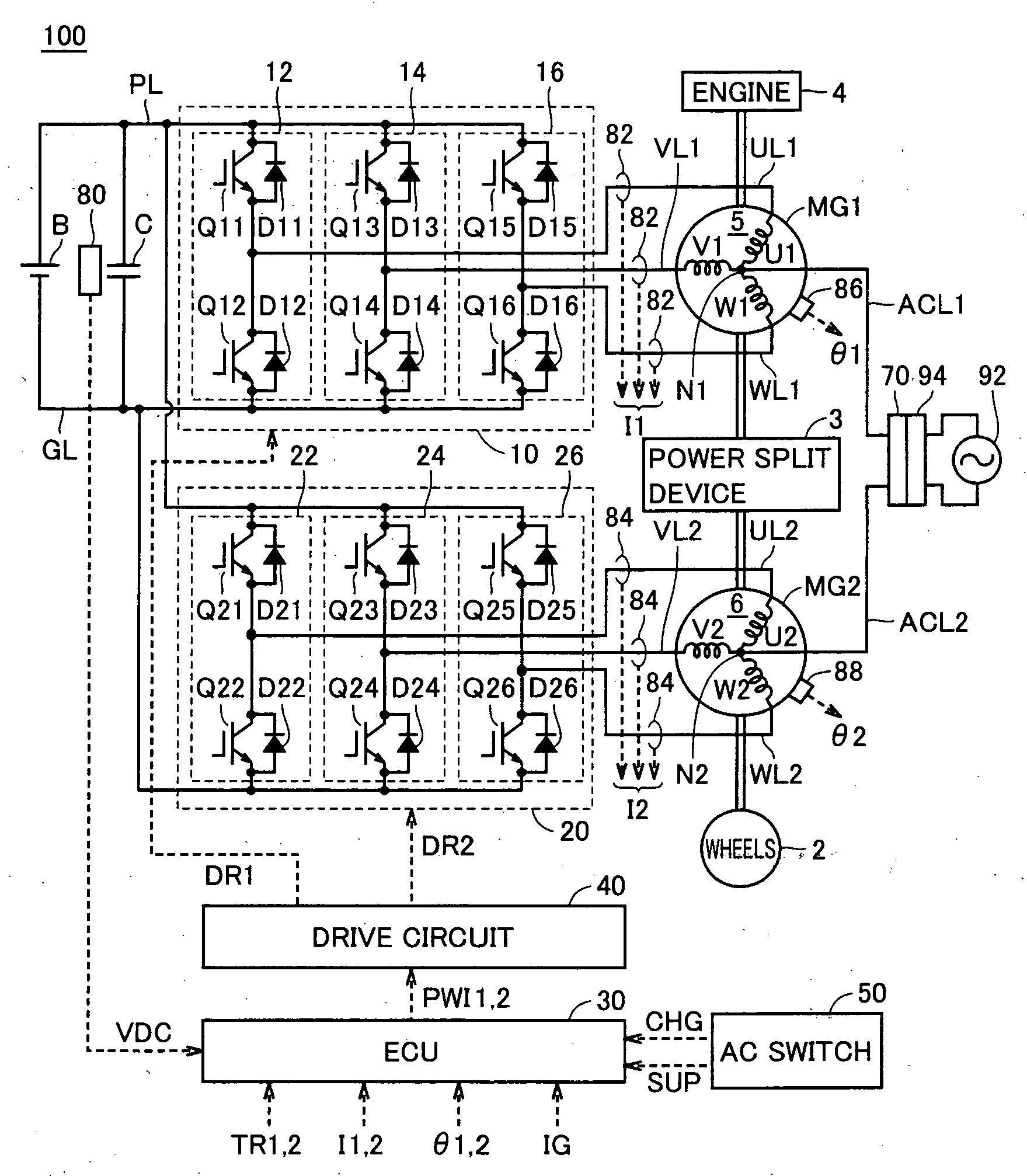

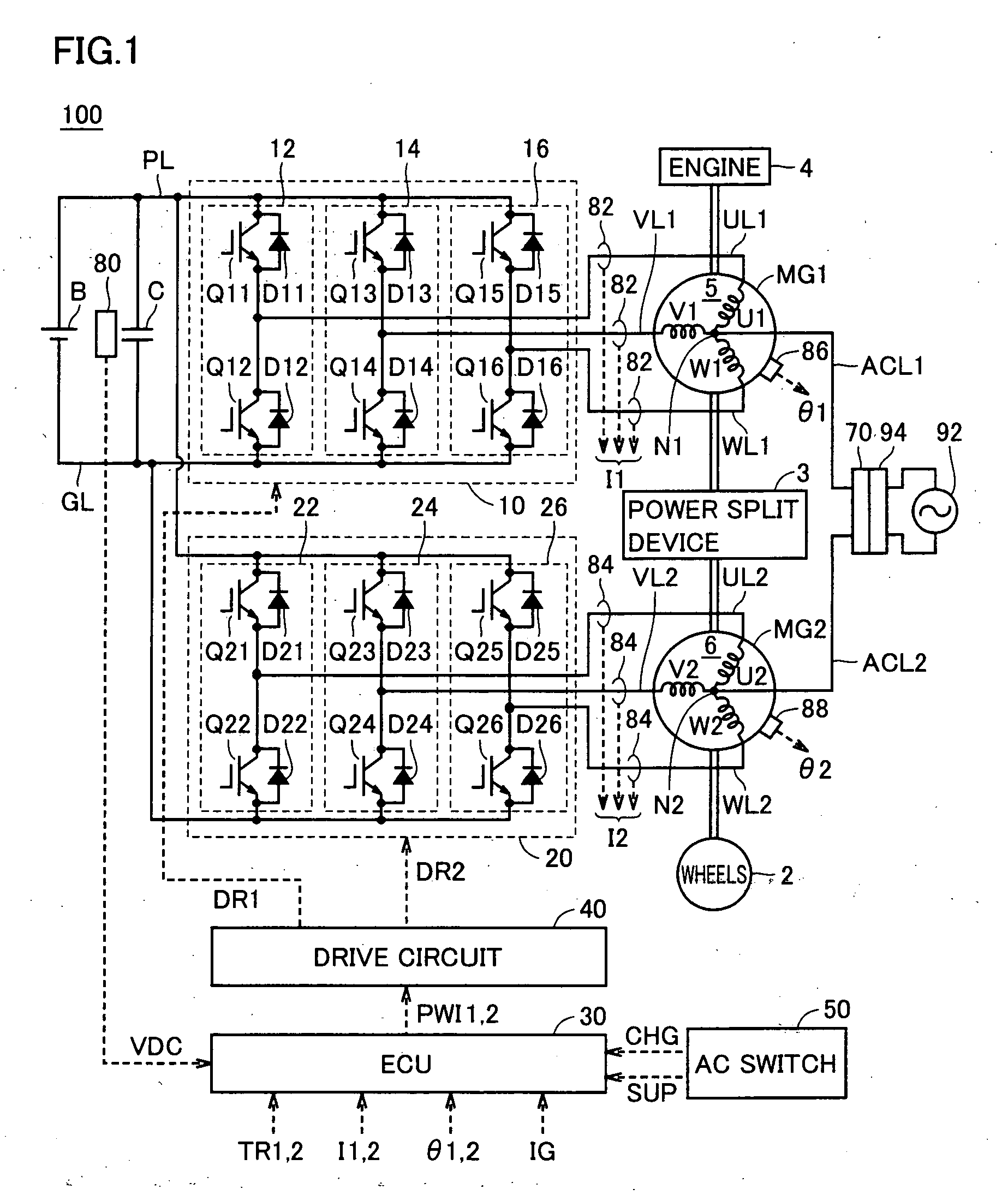

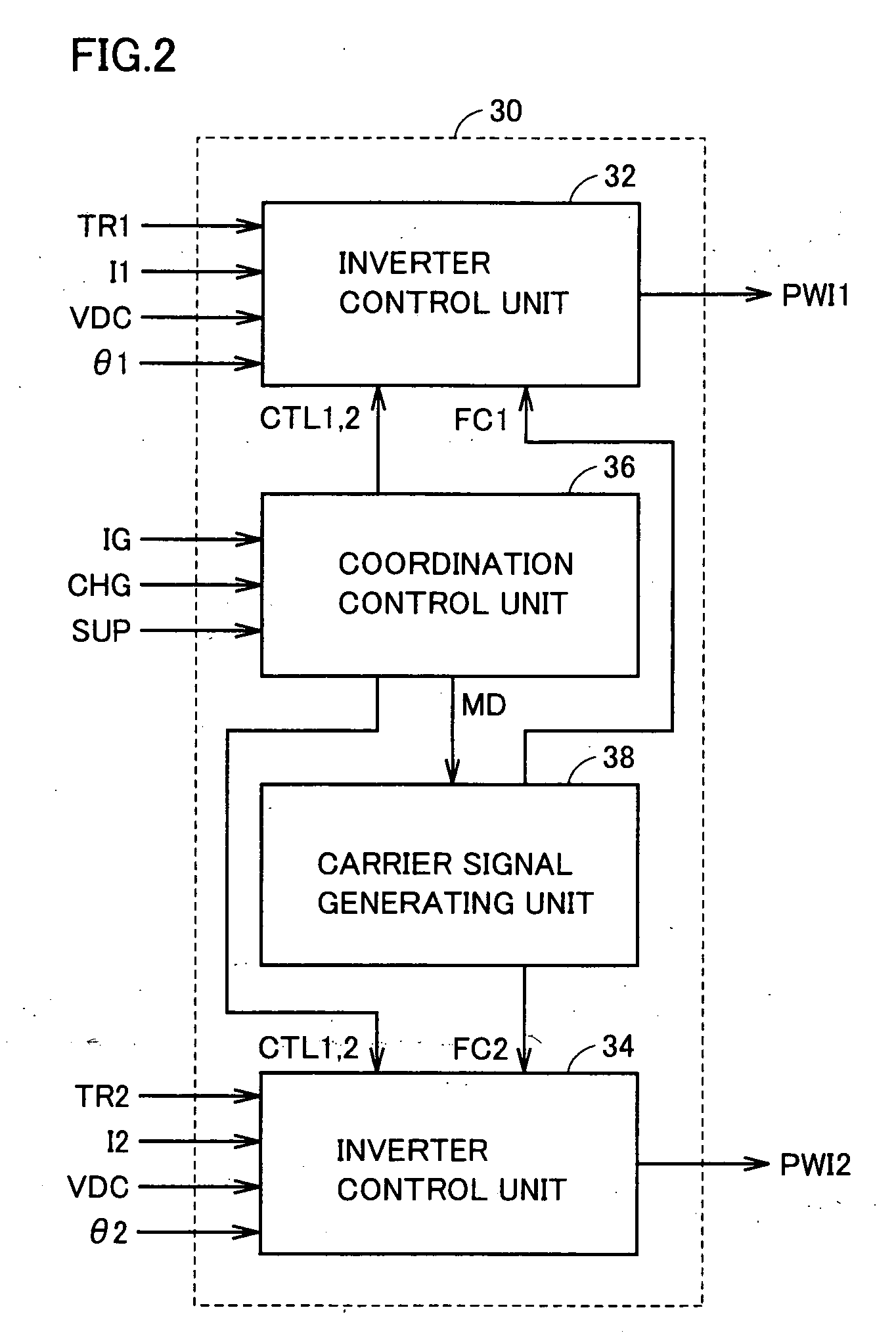

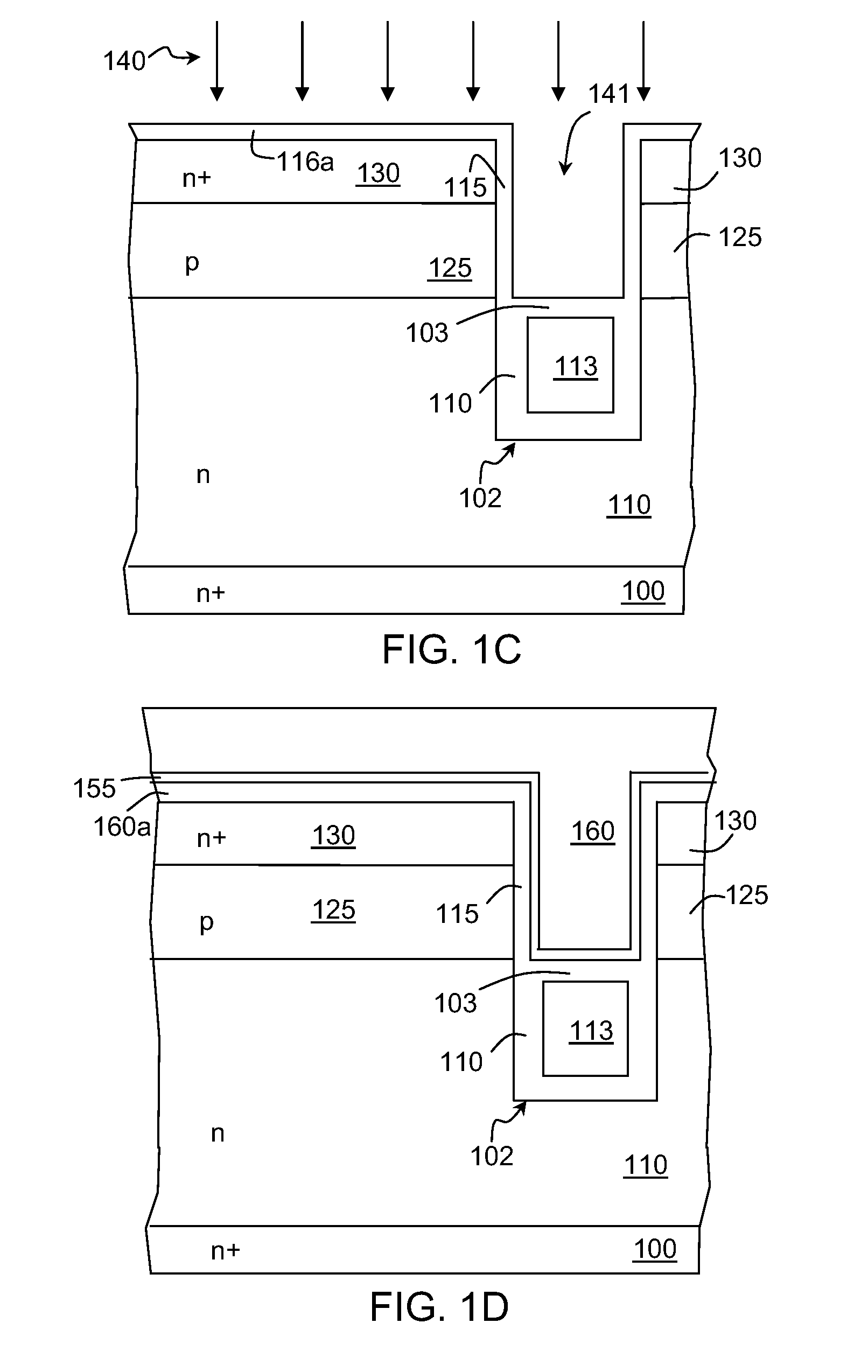

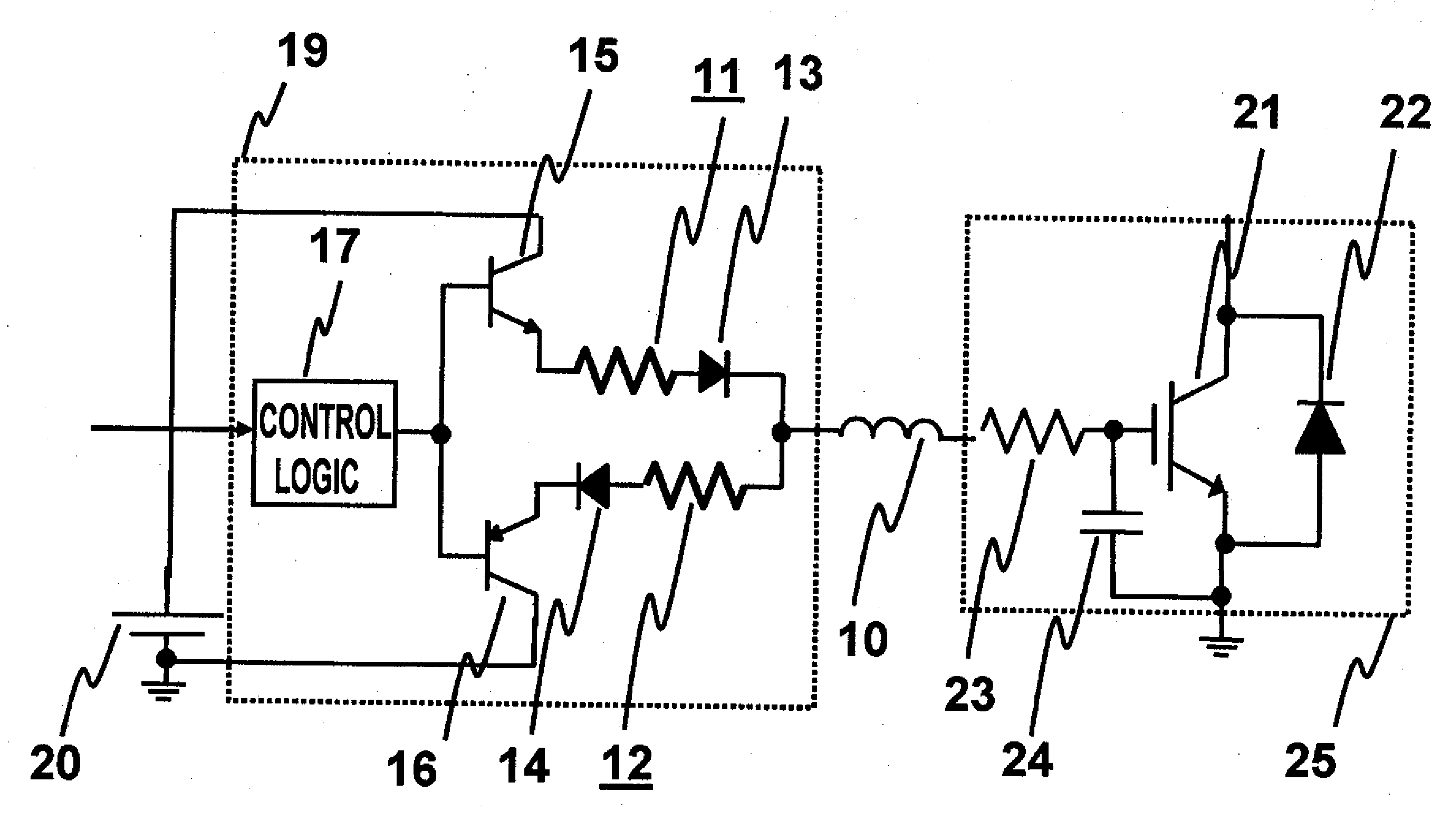

Electrically Powered Vehicle

InactiveUS20090184681A1Reduce noiseReduce electromagnetic noiseBatteries circuit arrangementsAC motor controlElectrical resistance and conductanceElectric power

In a charge / discharge mode, an inverter performs power conversion between a power storage device and a commercial power supply electrically connected to a neutral point through a power line. In the charge / discharge mode, ECU sets a carrier frequency of the inverter to a frequency higher than in a running mode. Further, in the charge / discharge mode, a drive circuit drives the inverter using a gate resistance higher than in the running mode.

Owner:TOYOTA JIDOSHA KK

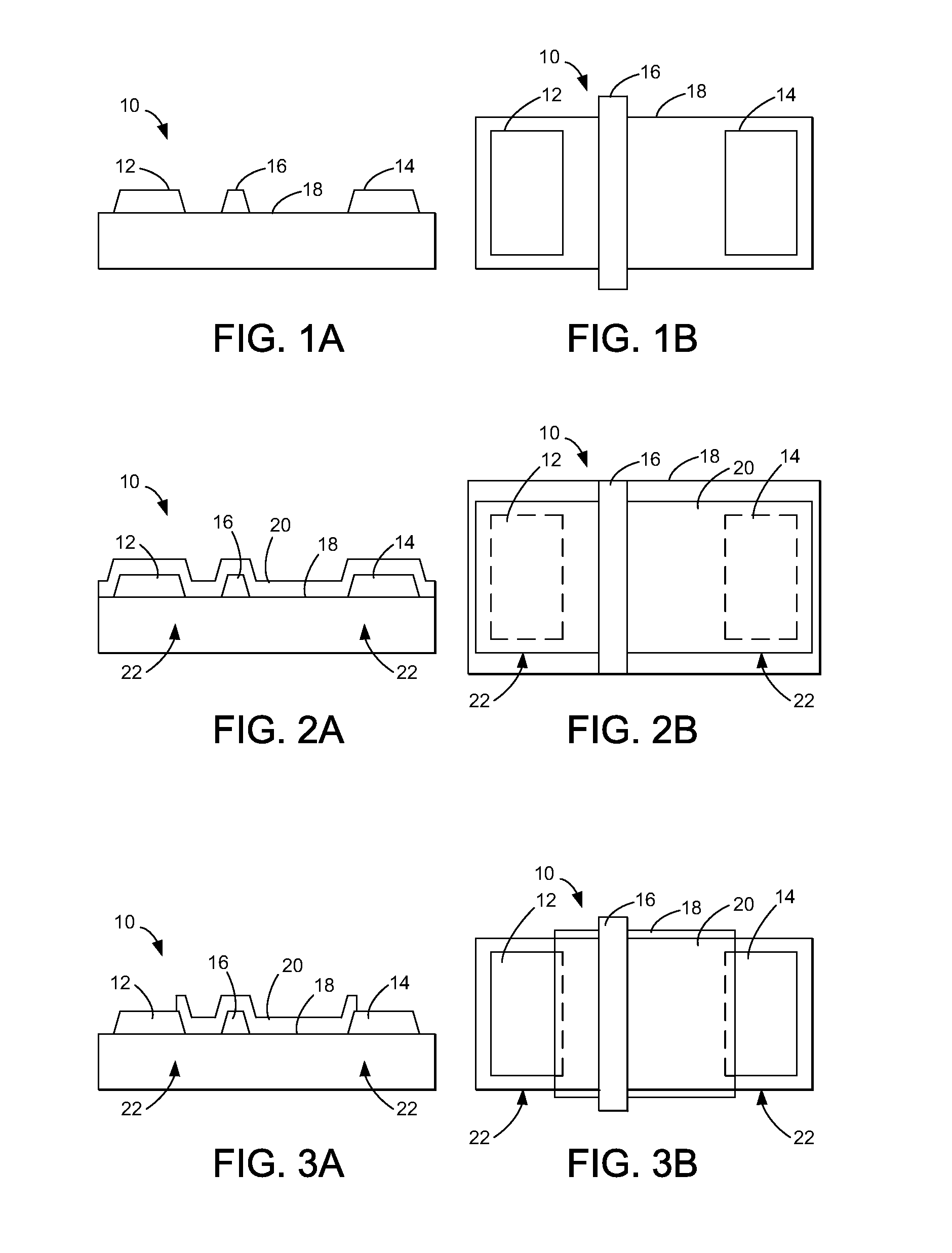

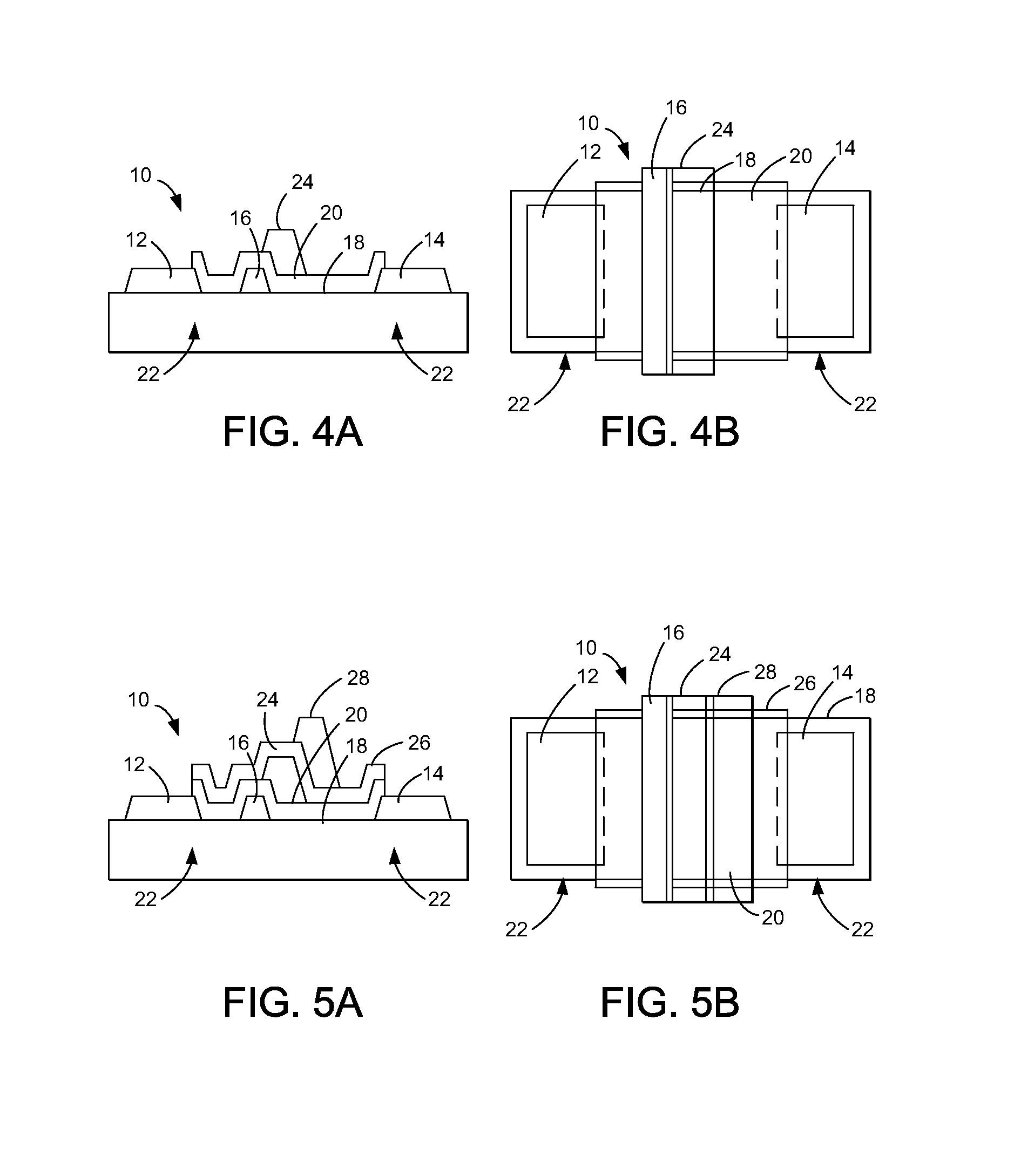

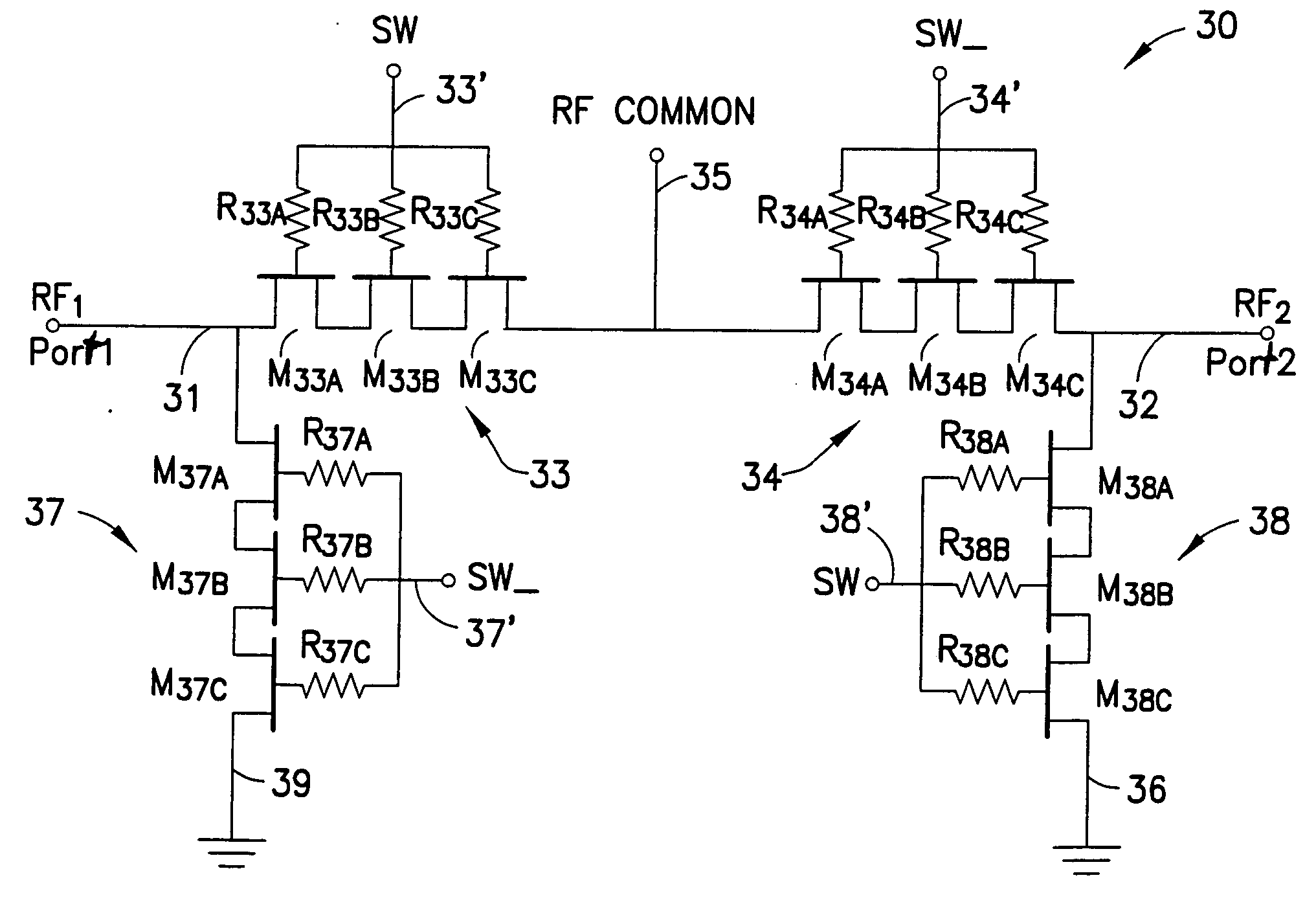

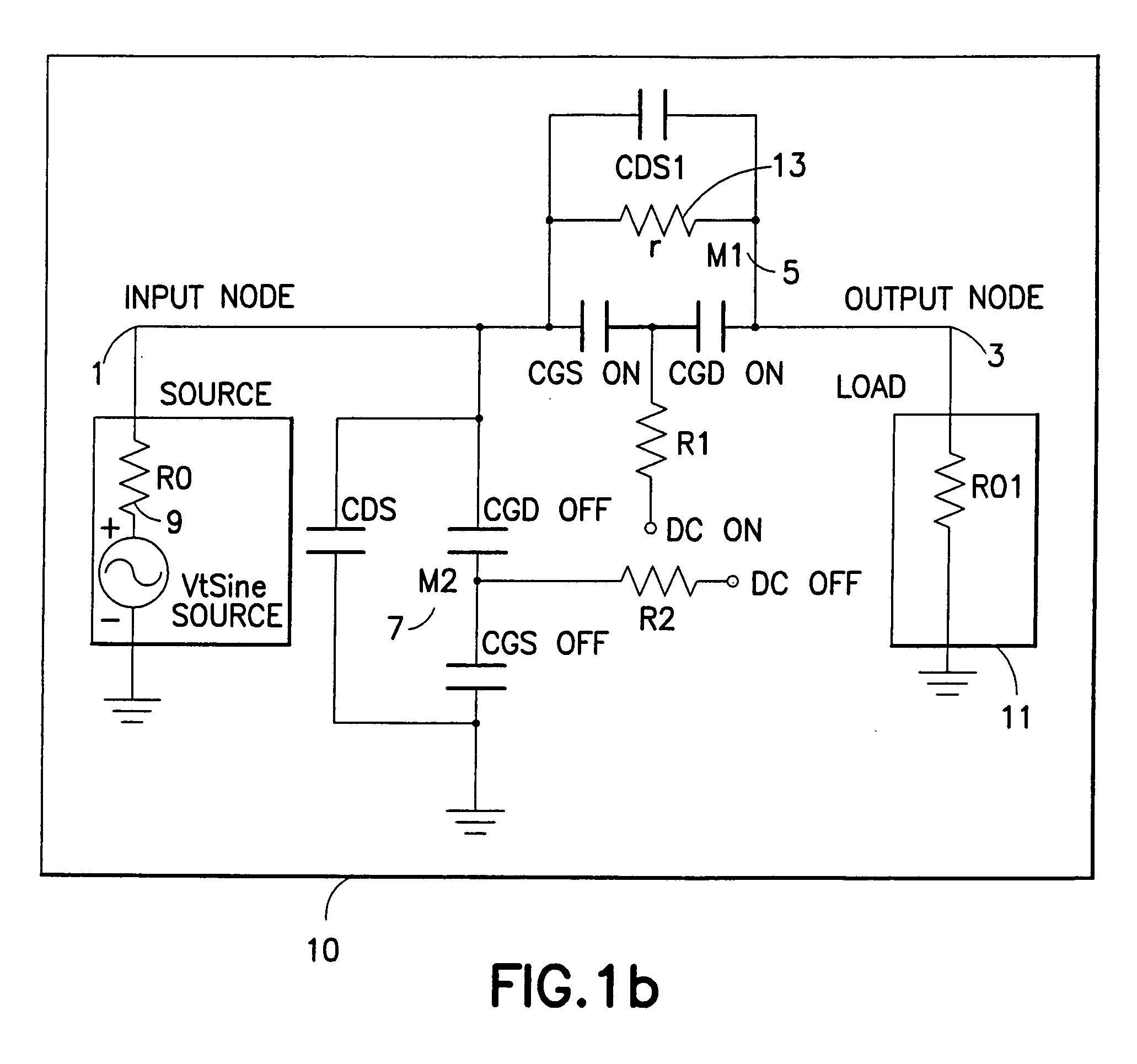

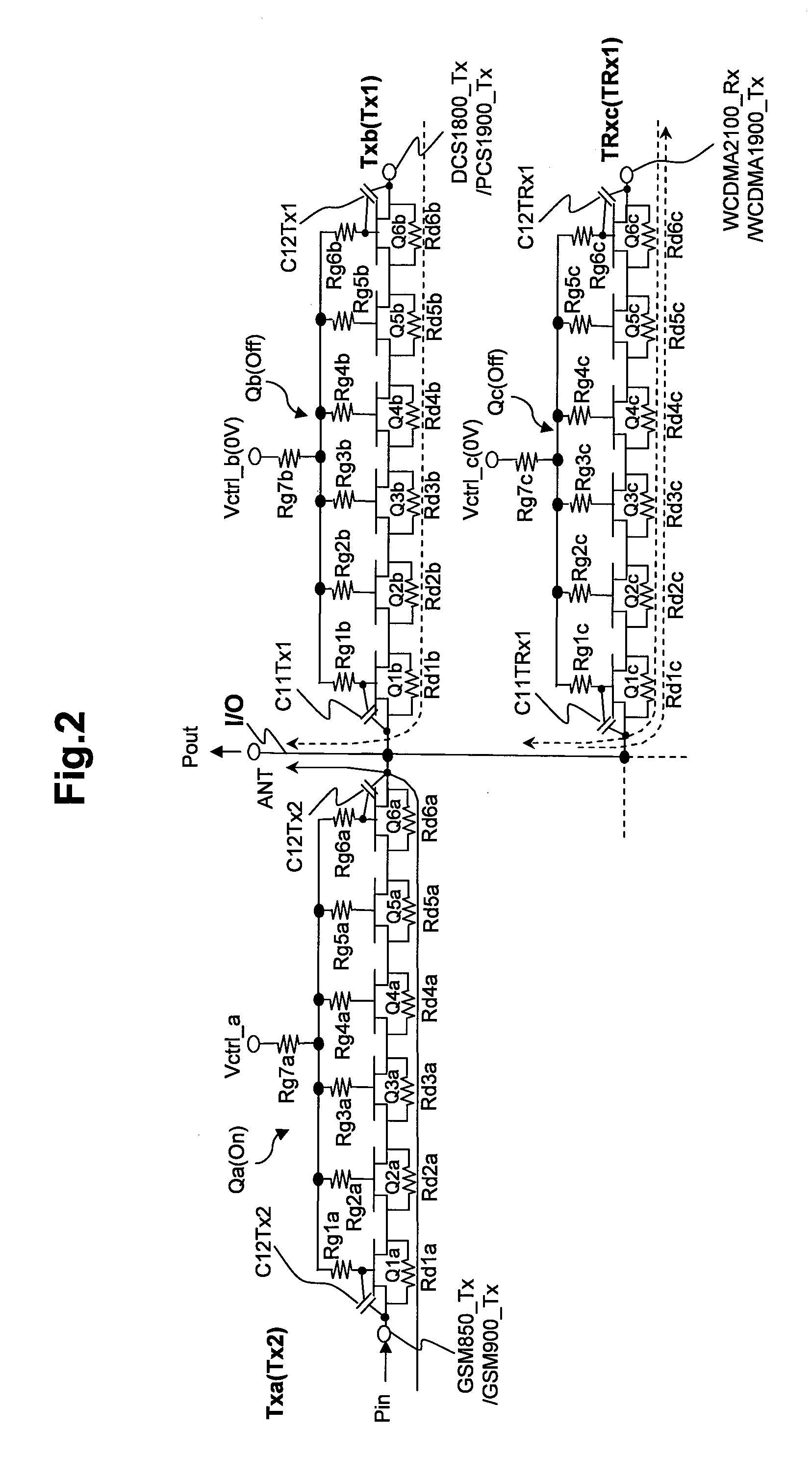

Switch circuit and method of switching radio frequency signals

InactiveUS20050017789A1Improving RF switch isolationRaise the compression pointTransistorSolid-state devicesMOSFETEngineering

A novel RF buffer circuit adapted for use with an RF switch circuit and method for switching RF signals is described. The RF switch circuit is fabricated in a silicon-on-insulator (SOI) technology. The RF switch includes pairs of switching and shunting transistor groupings used to alternatively couple RF input signals to a common RF node. The switching and shunting transistor grouping pairs are controlled by a switching control voltage (SW) and its inverse (SW_). The switching and shunting transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. The stacking of transistor grouping devices, and associated gate resistors, increase the breakdown voltage across the series connected switch transistors and operate to improve RF switch compression. A fully integrated RF switch is described including digital control logic and a negative voltage generator integrated together with the RF switch elements. In one embodiment, the fully integrated RF switch includes a built-in oscillator, a charge pump circuit, CMOS logic circuitry, level-shifting and voltage divider circuits, and an RF buffer circuit. Several embodiments of the charge pump, level shifting, voltage divider, and RF buffer circuits are described. The inventive RF switch provides improvements in insertion loss, switch isolation, and switch compression.

Owner:PSEMI CORP

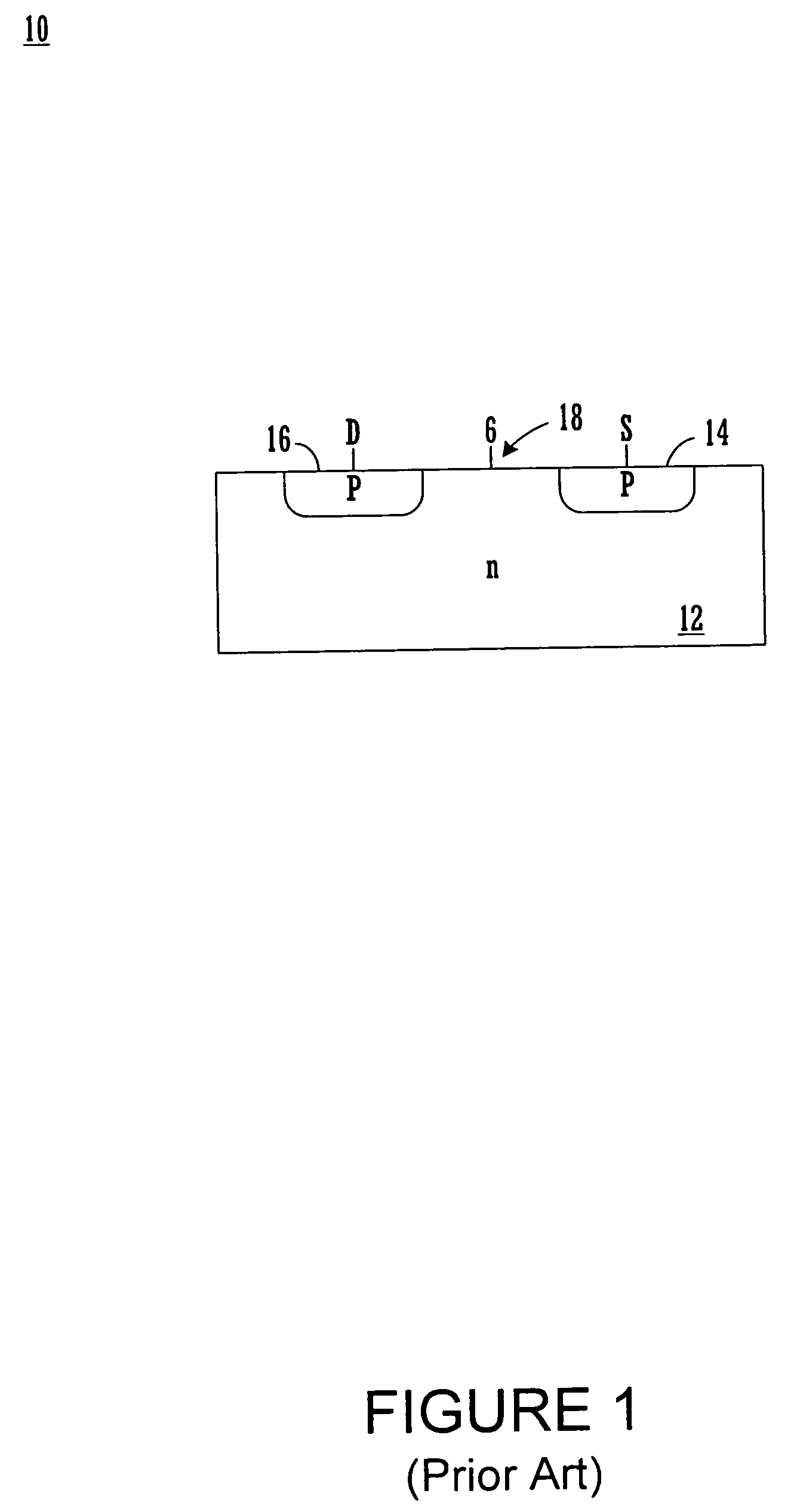

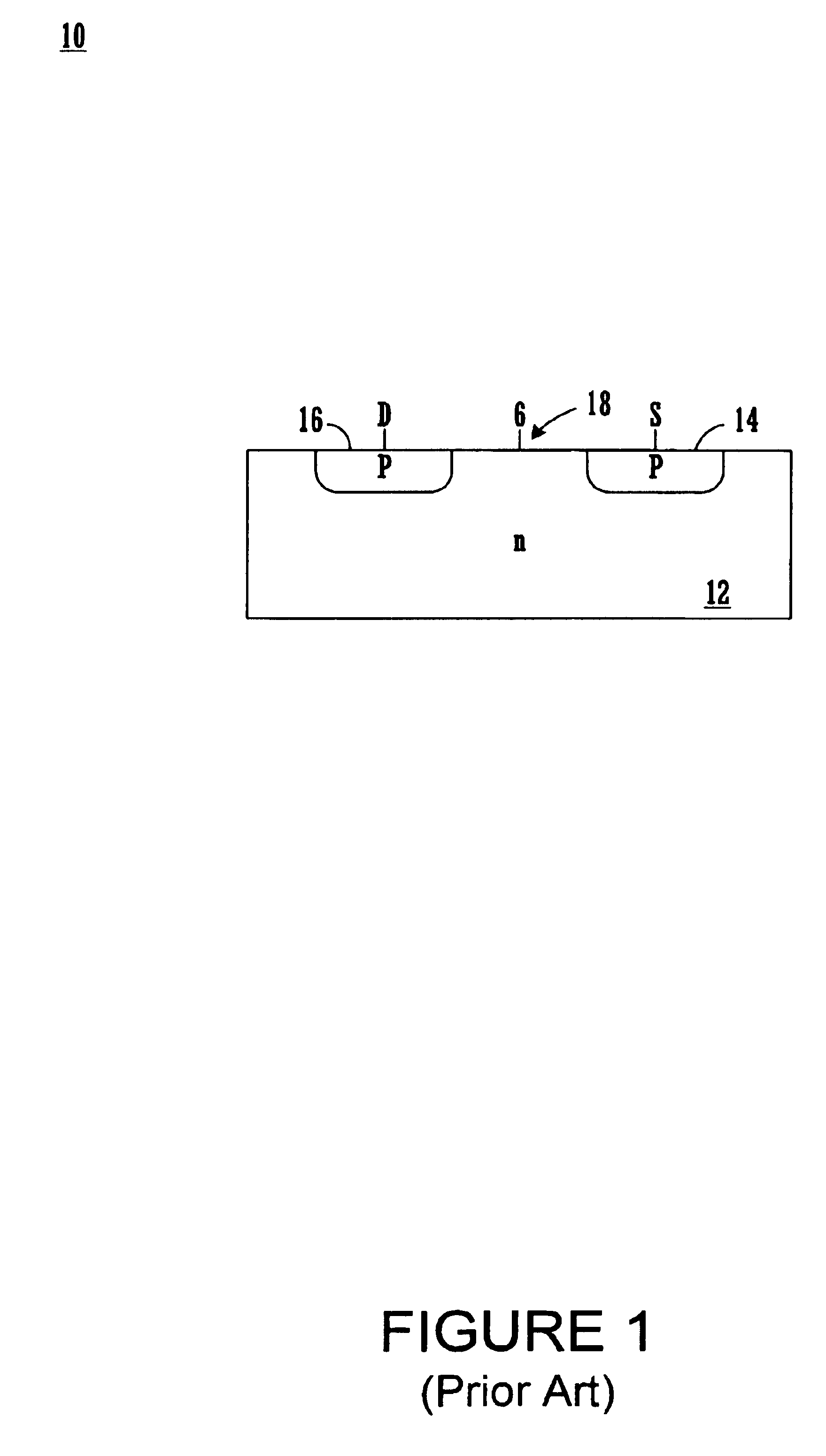

JFET and MESFET structures for low voltage high current and high frequency applications

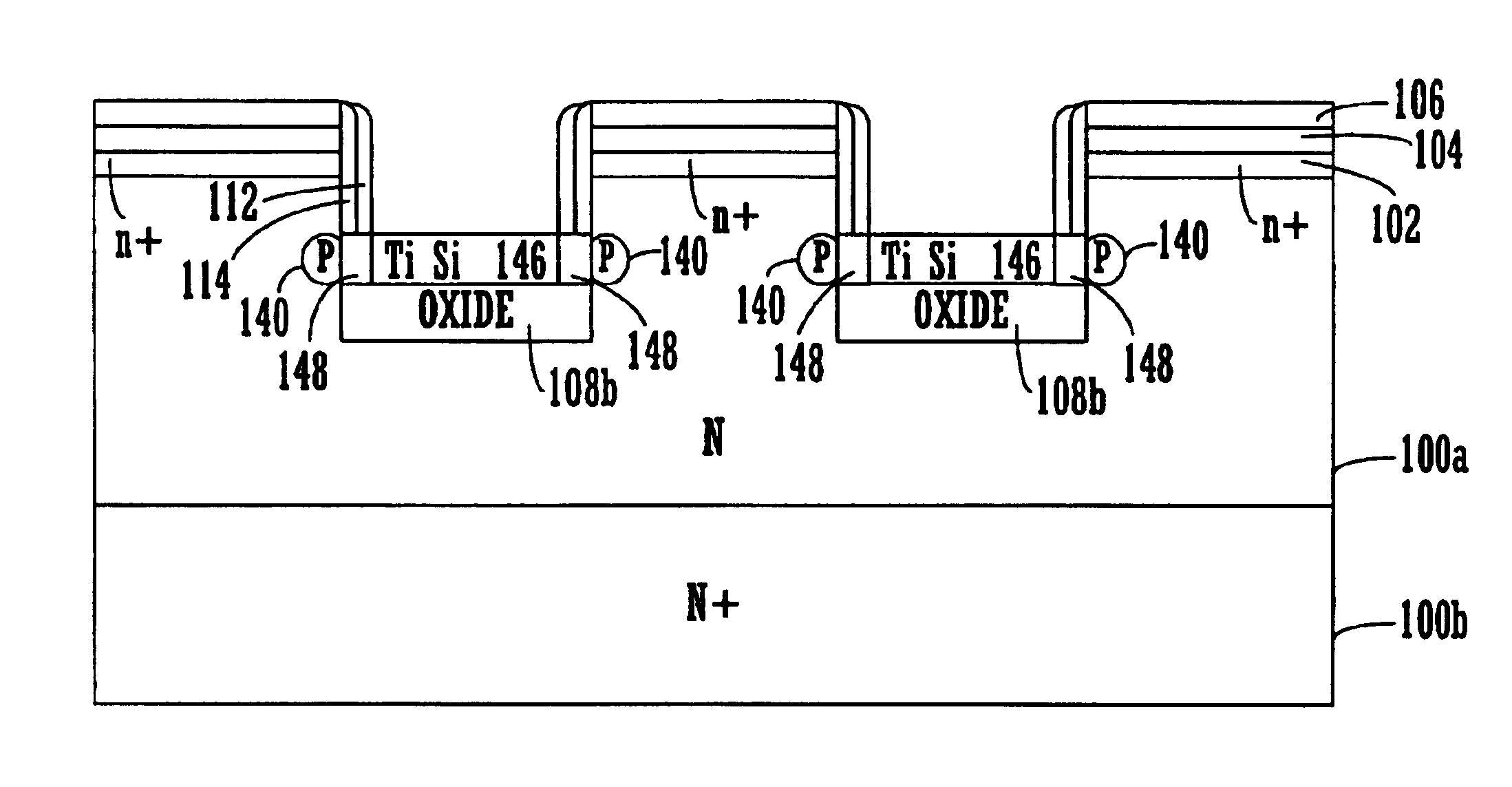

InactiveUS7045397B1Easy to controlLower junction capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceLow voltage

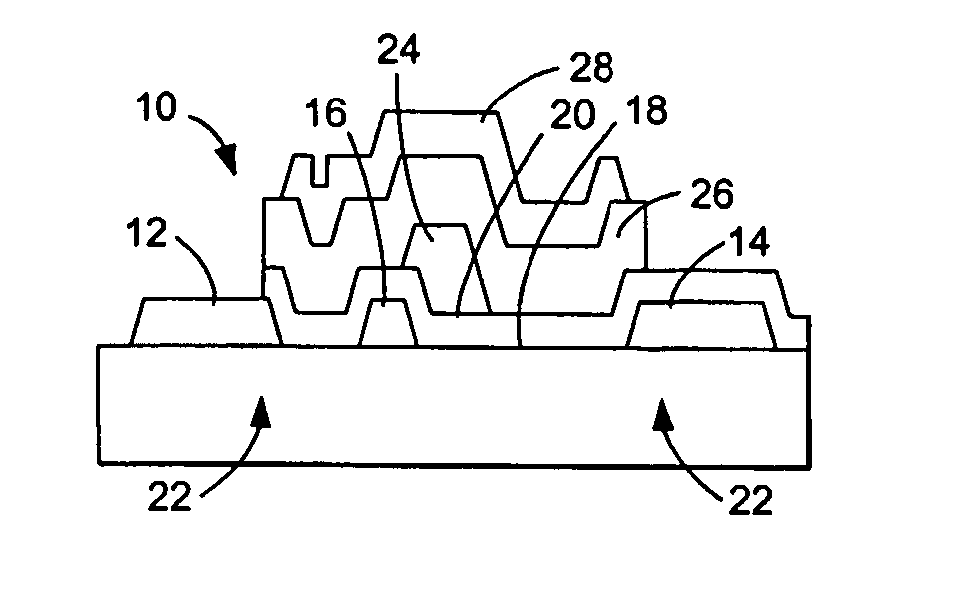

JFET and MESFET structures, and processes of making same, for low voltage, high current and high frequency applications. The structures may be used in normally-on (e.g., depletion mode) or normally-off modes. The structures include an oxide layer positioned under the gate region which effectively reduces the junction capacitance (gate to drain) of the structure. For normally off modes, the structures reduce gate current at Vg in forward bias. In one embodiment, a silicide is positioned in part of the gate to reduce gate resistance. The structures are also characterized in that they have a thin gate due to the dipping of the spacer oxide, which can be below 1000 angstroms and this results in fast switching speeds for high frequency applications.

Owner:POWER INTEGRATIONS INC

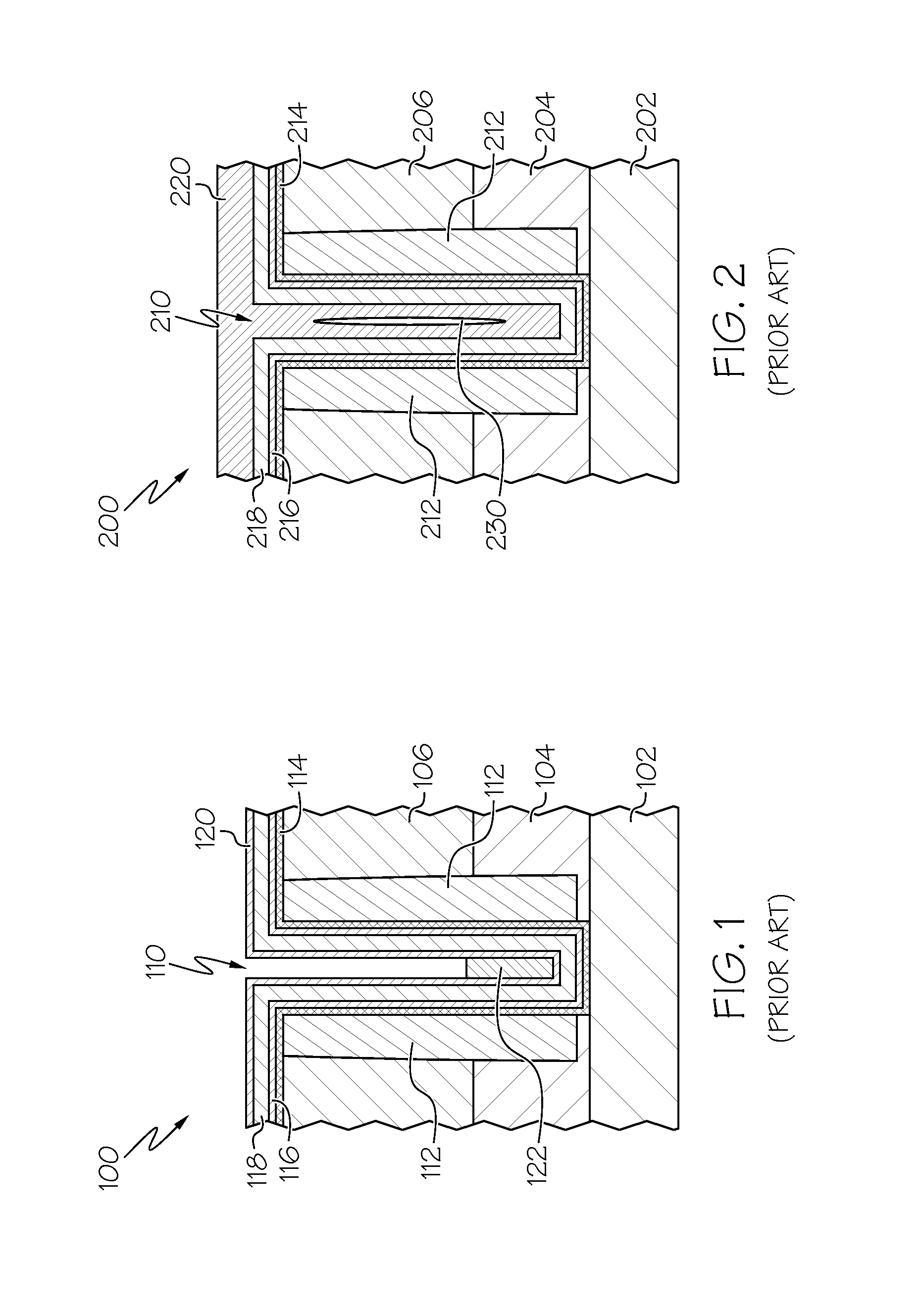

Ultra-thin SOI mosfet method and structure

InactiveUS20050112811A1Minimize gate resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETLithographic artist

An ultra-thin, scaleable MOSFET transistor and fabrication method are described. The transistor features fully self-aligned, raised source / drain junctions on a thin SOI wafer and exhibits low contact resistance, low gate resistance and good device isolation characteristic. No extra lithographic mask steps are required beyond those required by conventional processes. The transistor is completely “bracketed” or surrounded by STI (shallow trench isolation), providing inherent isolation between it and any other devices on the SOI wafer. Gate sidewall spacers are formed outside of the gate area so that the scalability is limited solely by lithography resolution.

Owner:GLOBALFOUNDRIES INC

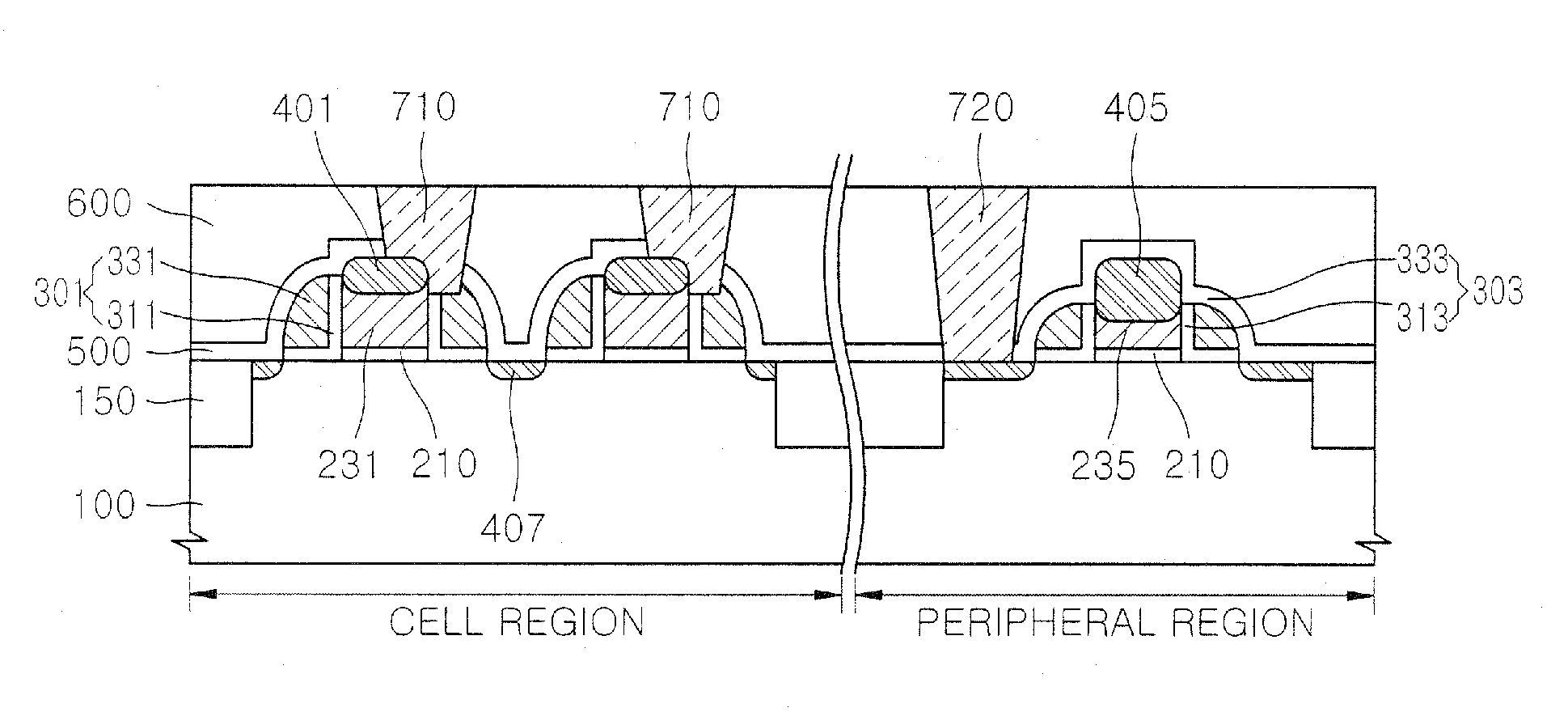

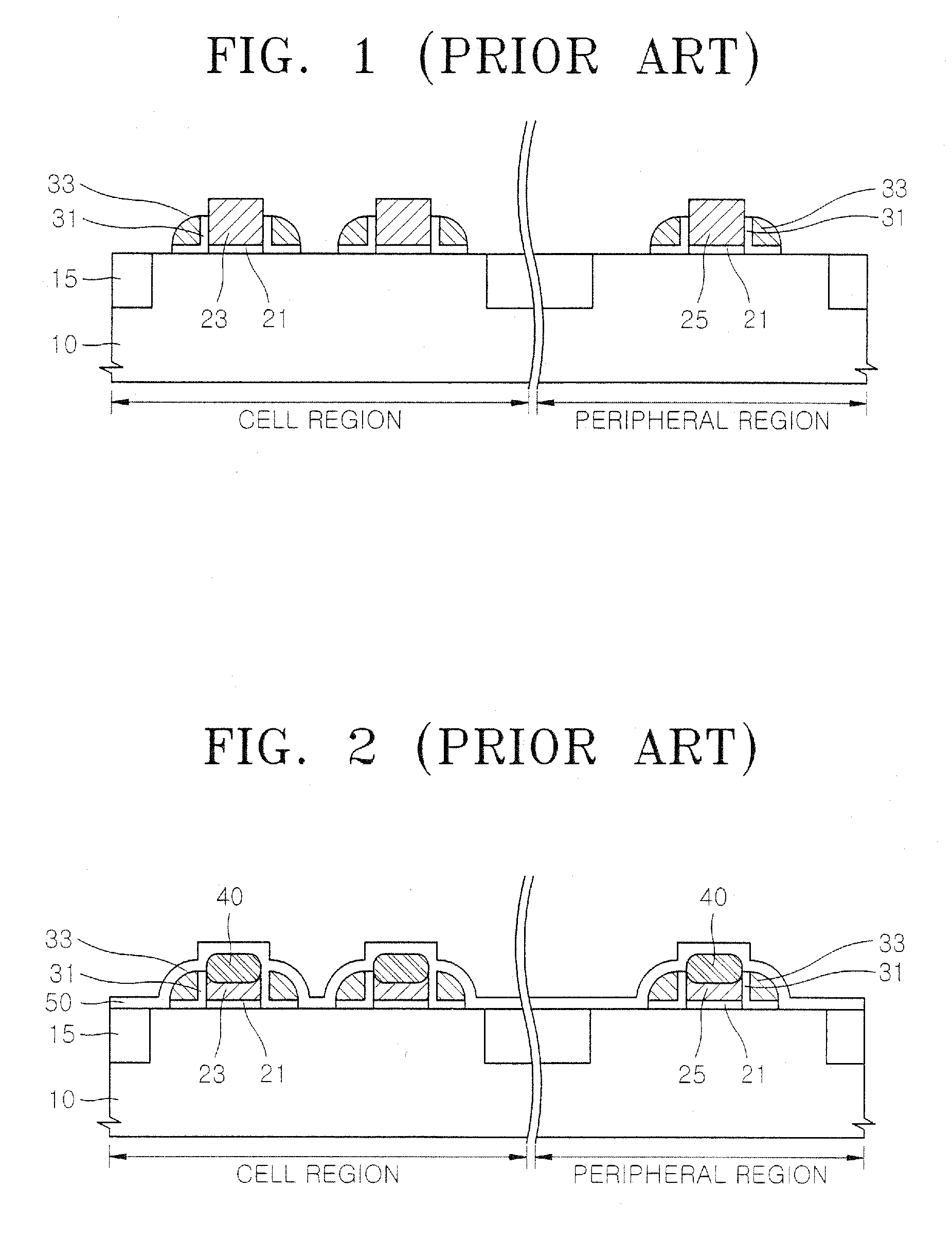

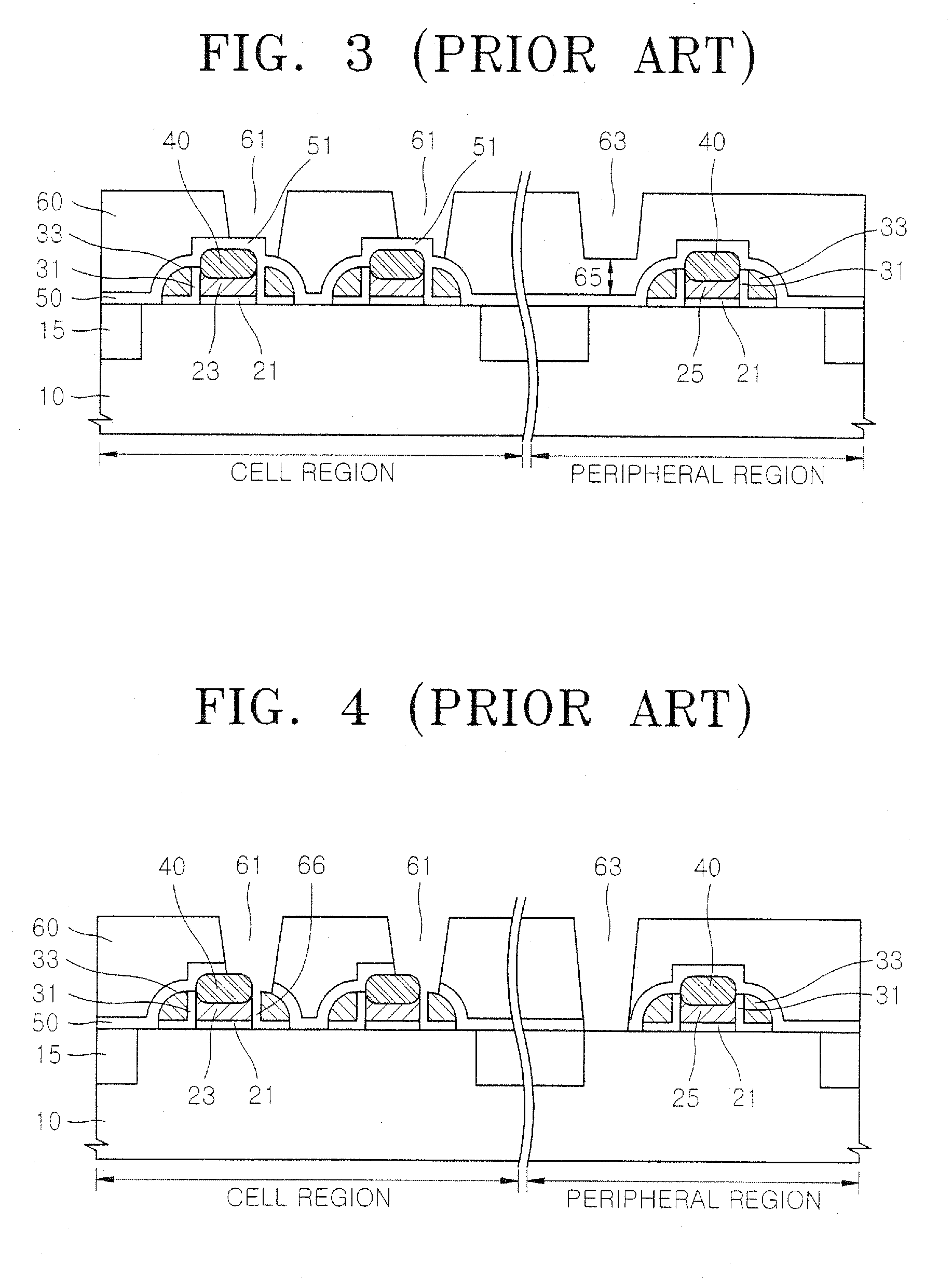

Semiconductor device with improved gate resistance and method of its manufacture

A semiconductor device is formed with a normal, non-recessed, spacer structure in a cell region and a recessed spacer structure in a peripheral region. The recessed spacer structure is formed as by etch masking those in the cell region and exposing those in the peripheral region, then performing an etch process. The increased height of the cell region spacers is adapted to further prevent over-etching during gate interconnect formation which would otherwise result in etching through the spacer to the substrate and subsequent short circuit. Therefore, it is also possible to prevent bridge defects due to over-etching, which occurs because the barrier metal layer for a subsequent interconnection contact is accidentally connected to the underlying substrate. Also, since the recessed spacer structure is provided in the peripheral region, it is possible to remarkably enhance a resistance distribution of a cobalt silicide layer occurring in a gate line width of 100 nm or less.

Owner:SAMSUNG ELECTRONICS CO LTD

Enhanced silicidation of polysilicon gate electrodes

InactiveUS6867130B1TransistorSemiconductor/solid-state device detailsPlasma depositionMetal silicide

Semiconductor devices exhibiting reduced gate resistance and reduced silicide spiking in source / drain regions are fabricated by forming thin metal silicide layers on the gate electrode and source / drain regions and then selectively resilicidizing the gate electrodes. Embodiments include forming the thin metal silicide layers on the polysilicon gate electrodes and source / drain regions, depositing a dielectric gap filling layer, as by high density plasma deposition, etching back to selectively expose the silicidized polysilicon gate electrodes and resilicidizing the polysilicon gate electrodes to increase the thickness of the metal silicide layers thereon. Embodiments further include resilicidizing the polysilicon gate electrodes including a portion of the upper side surfaces forming mushroom shaped metal silicide layers.

Owner:ADVANCED MICRO DEVICES INC

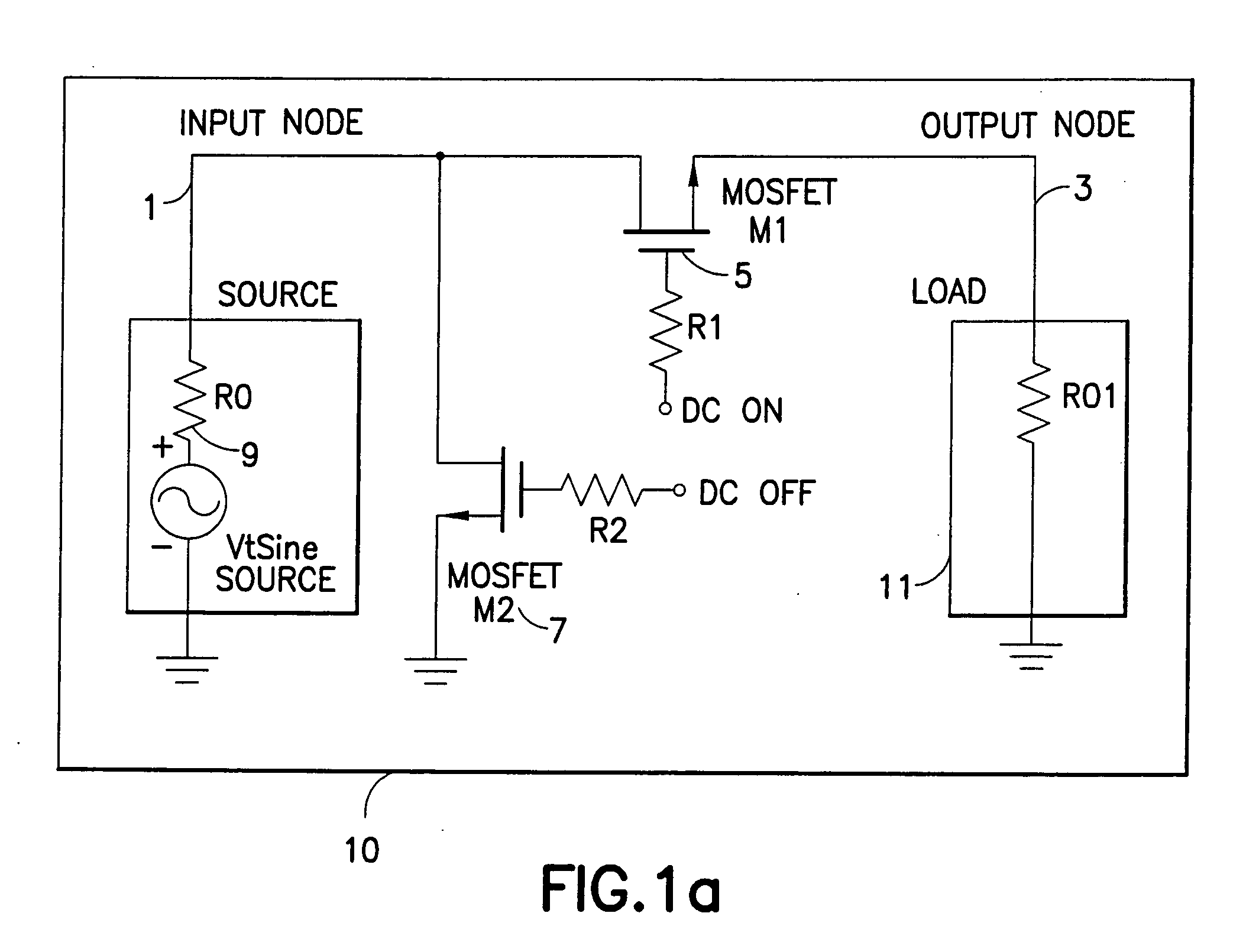

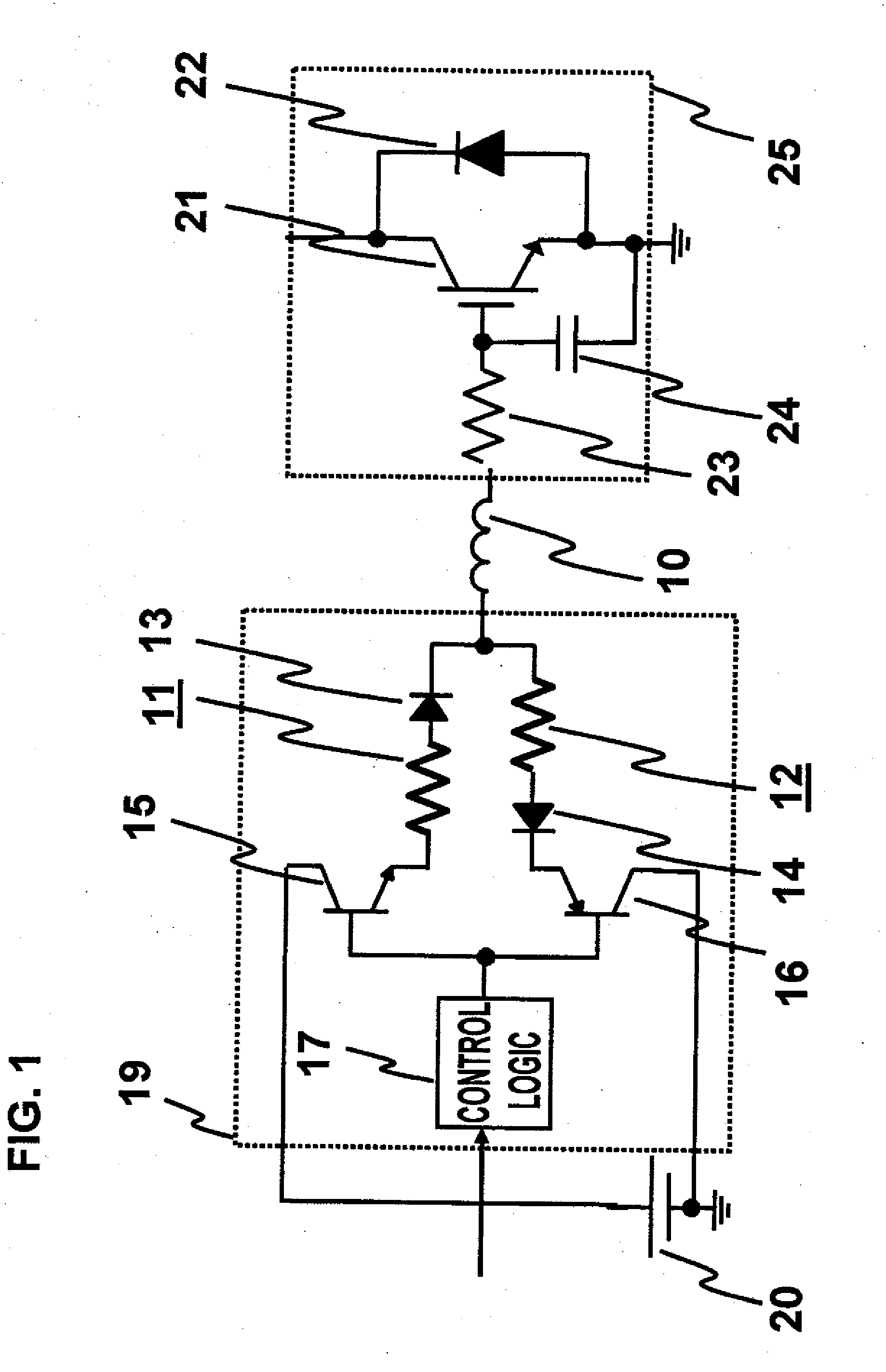

Power mosfet with integrated gate resistor and diode-connected mosfet

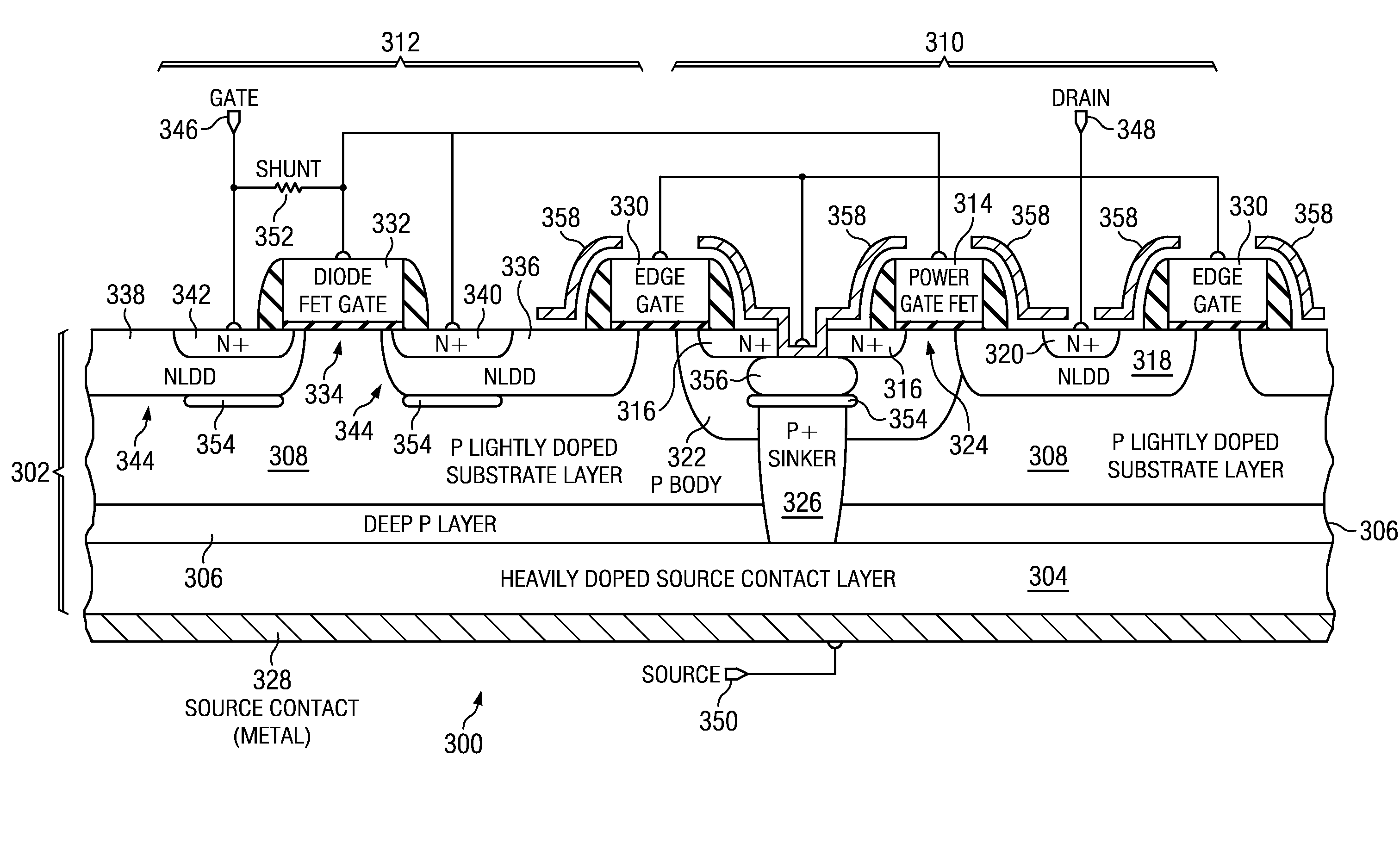

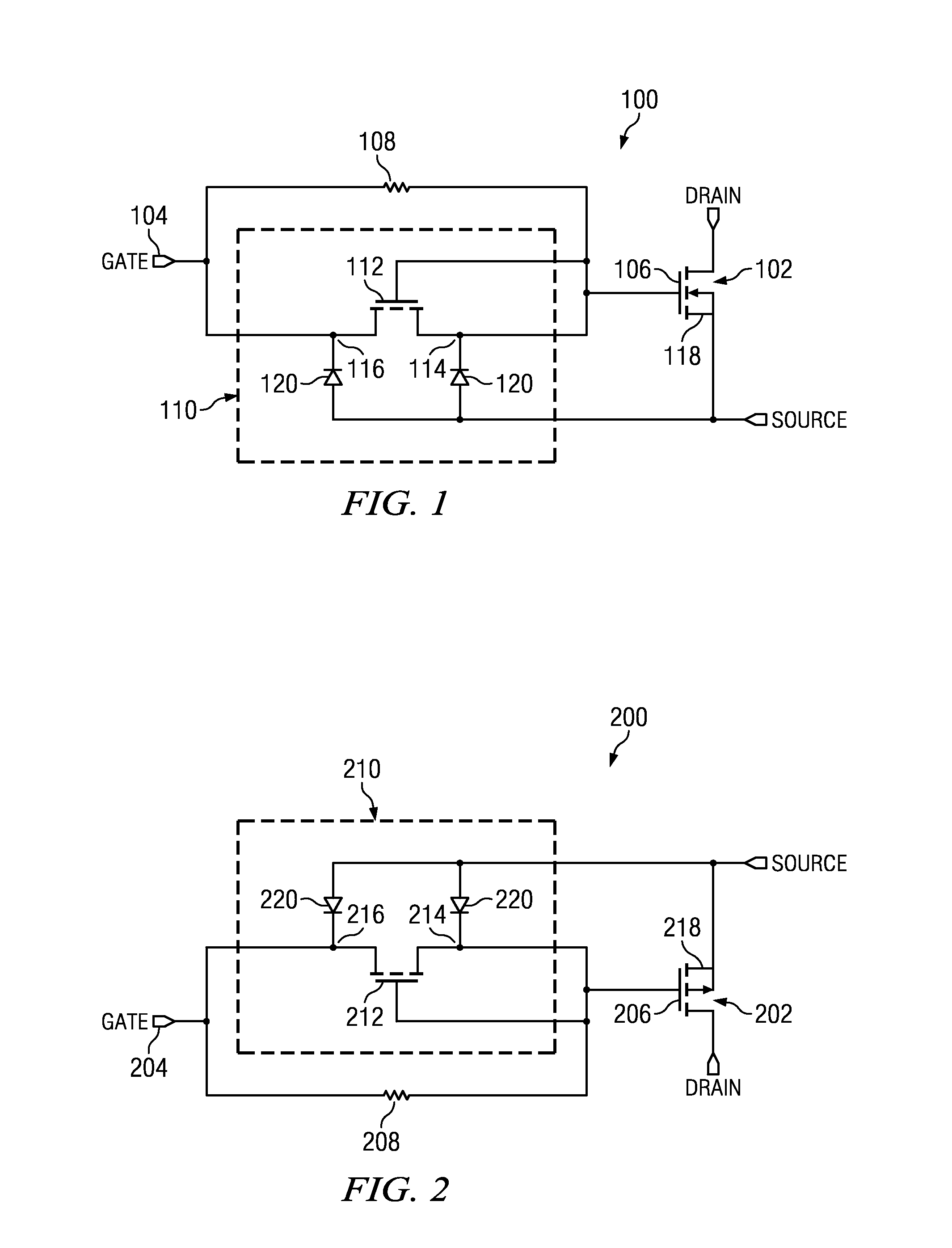

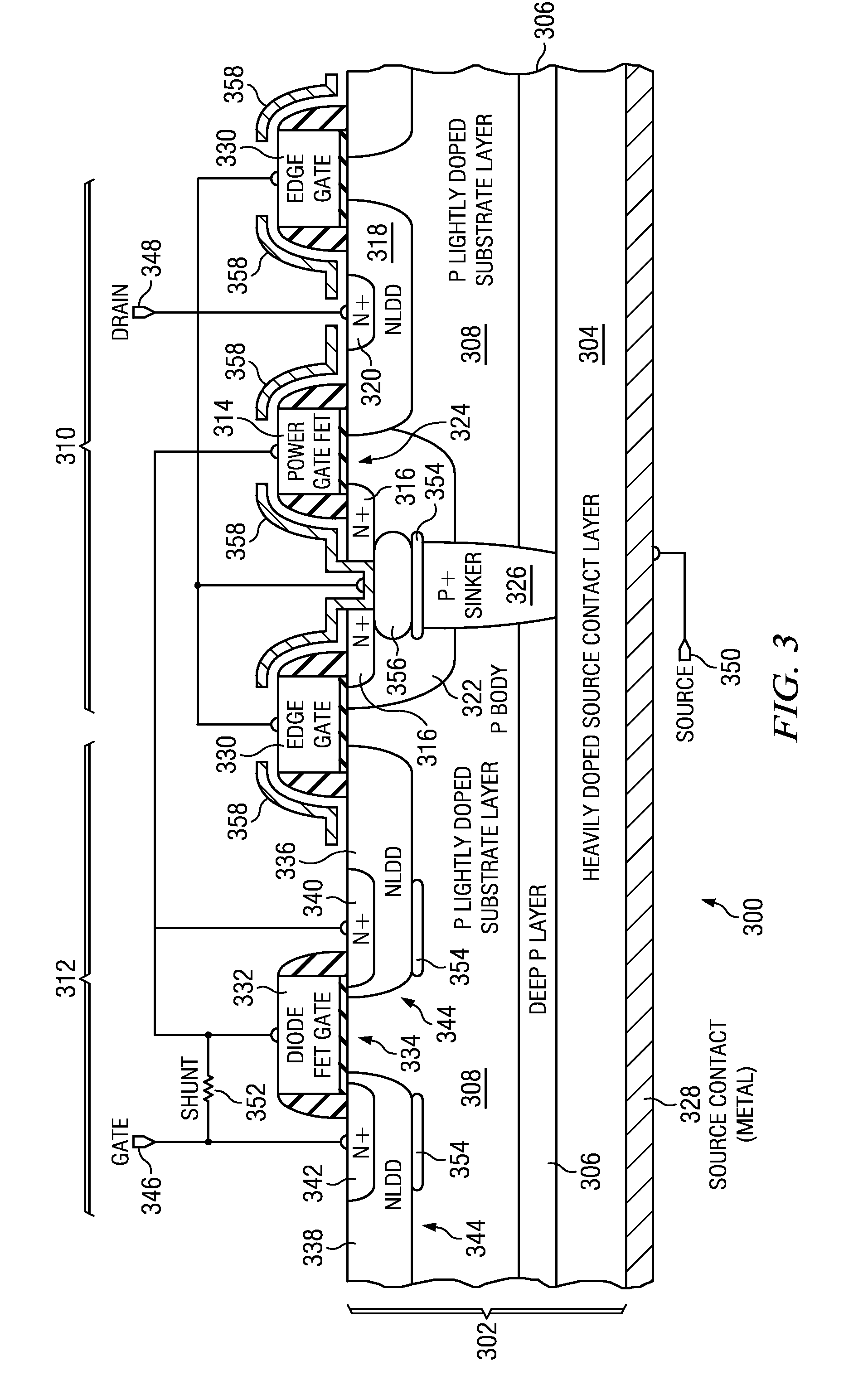

ActiveUS20130009253A1Low efficiencyRinging can be suppressedTransistorSolid-state devicesDevice materialEngineering

A power MOSFET is formed in a semiconductor device with a parallel combination of a shunt resistor and a diode-connected MOSFET between a gate input node of the semiconductor device and a gate of the power MOSFET. A gate of the diode-connected MOSFET is connected to the gate of the power MOSFET. Source and drain nodes of the diode-connected MOSFET are connected to a source node of the power MOSFET through diodes. The drain node of the diode-connected MOSFET is connected to the gate input node of the semiconductor device. The source node of the diode-connected MOSFET is connected to the gate of the power MOSFET. The power MOSFET and the diode-connected MOSFET are integrated into the substrate of the semiconductor device so that the diode-connected MOSFET source and drain nodes are electrically isolated from the power MOSFET source node through a pn junction.

Owner:TEXAS INSTR INC

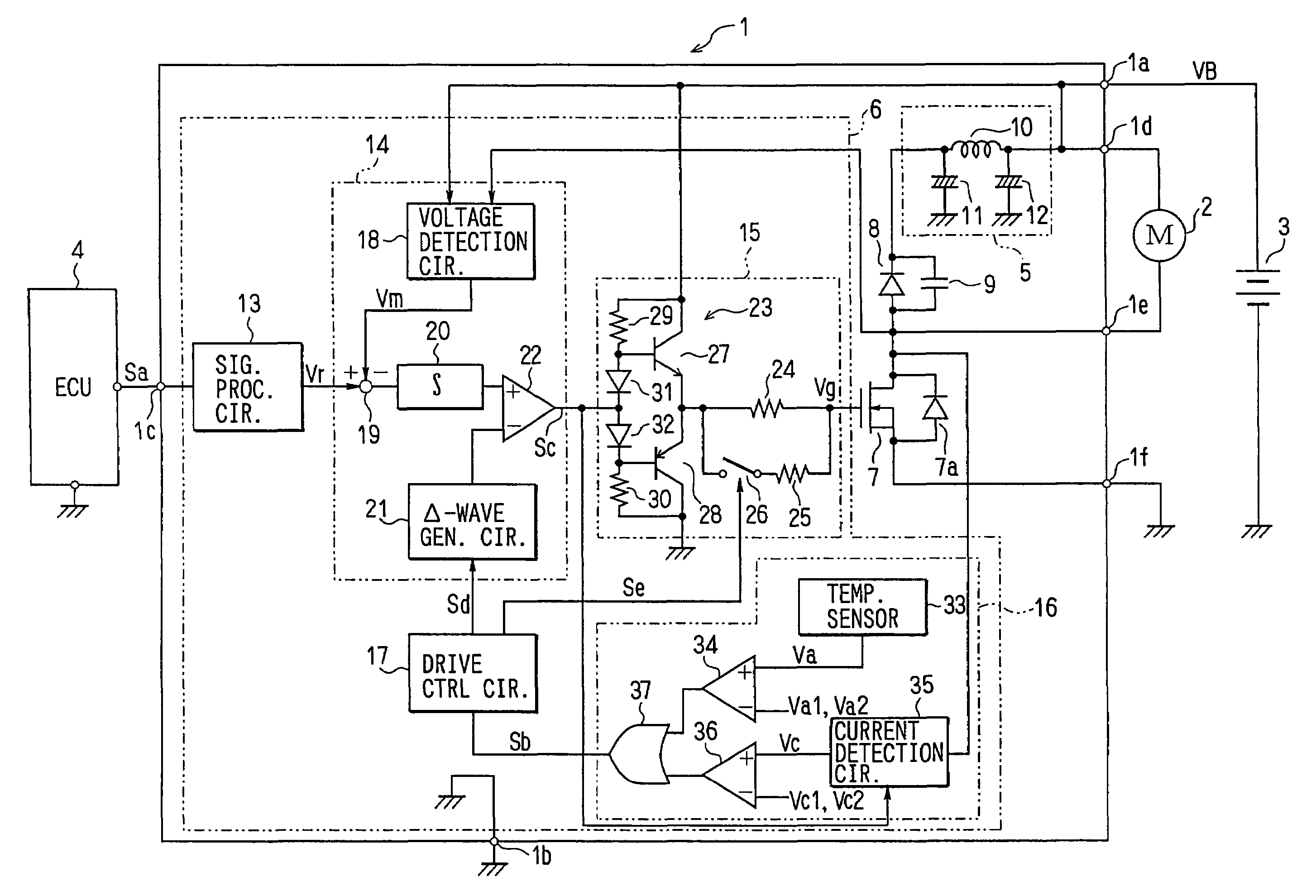

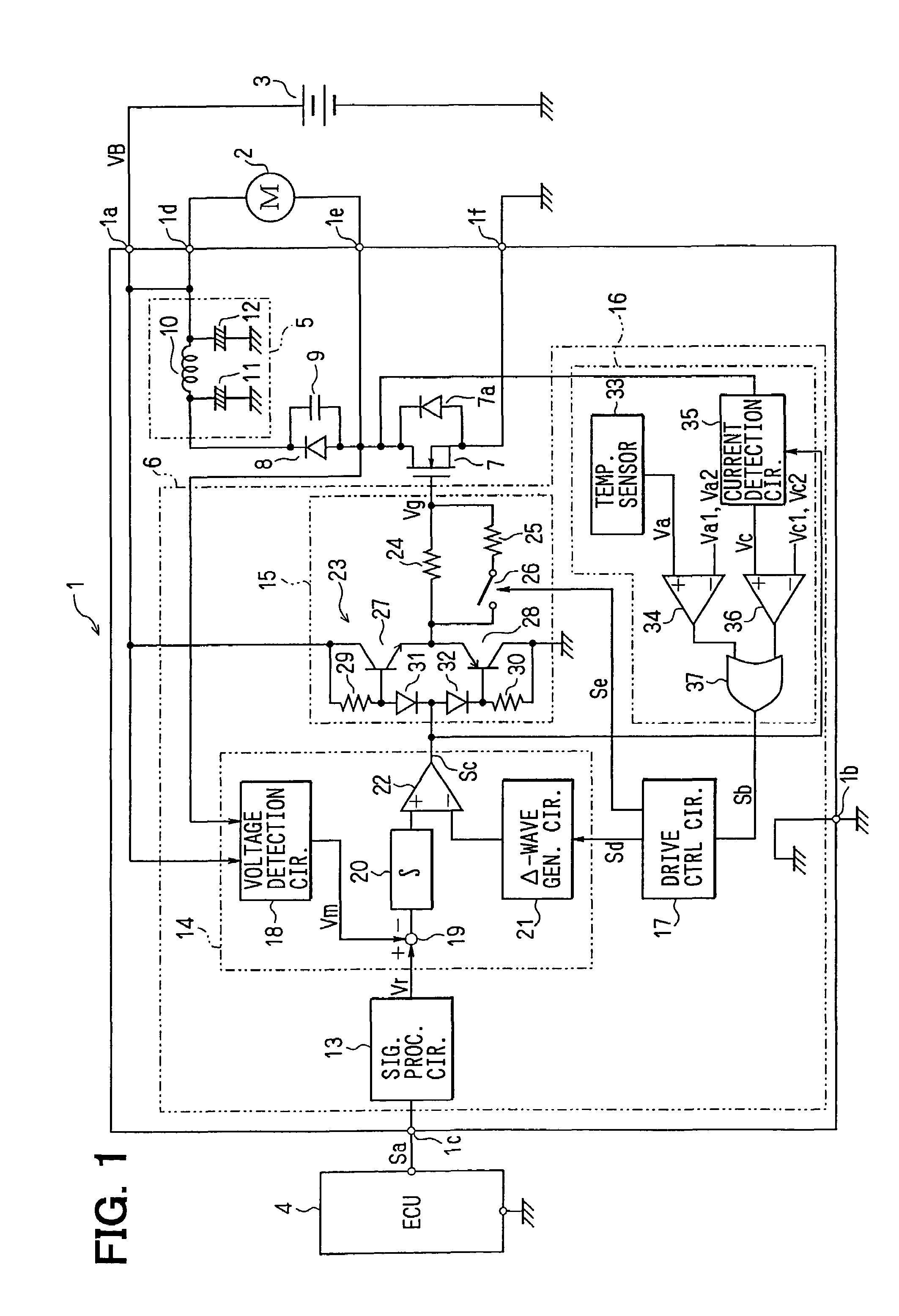

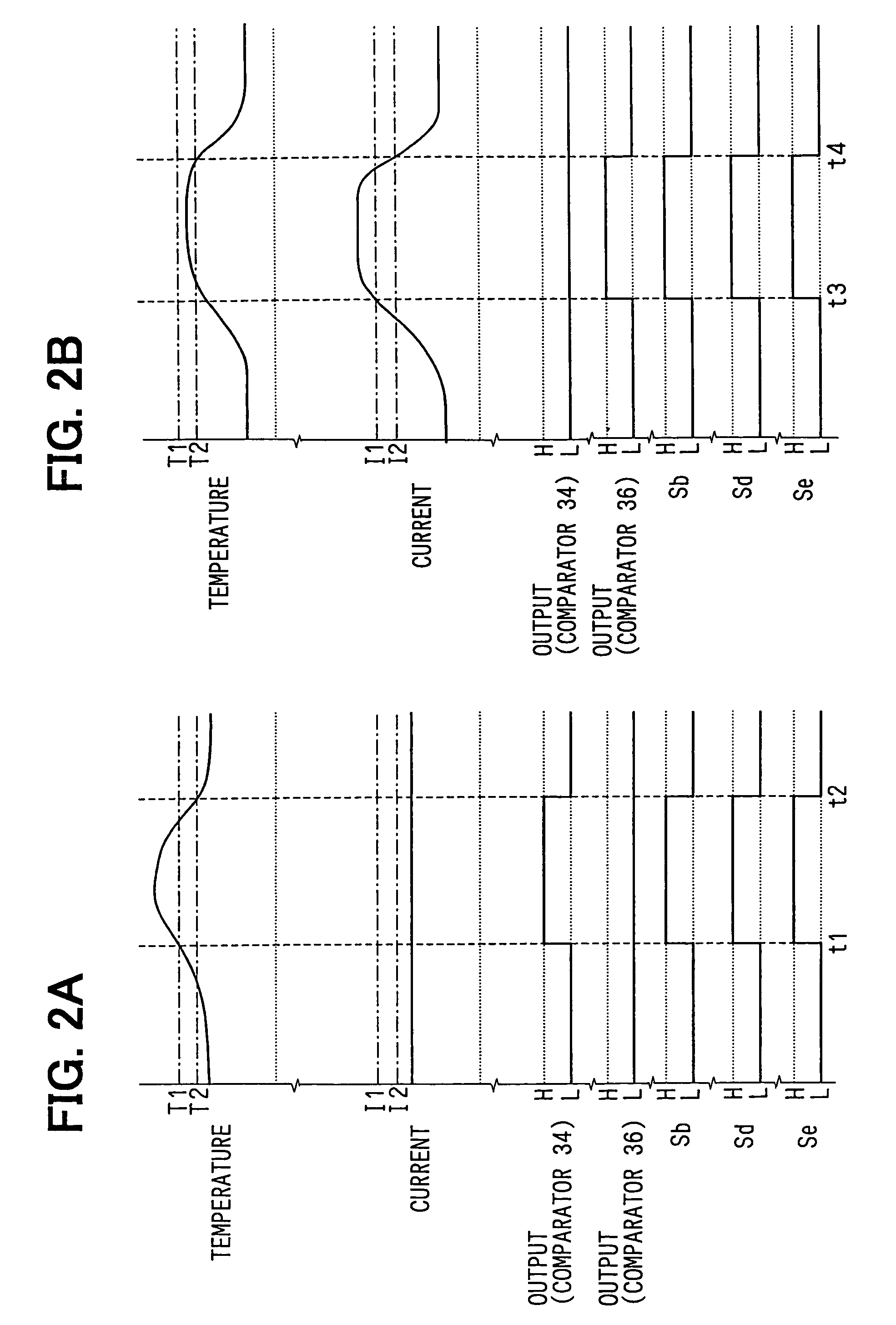

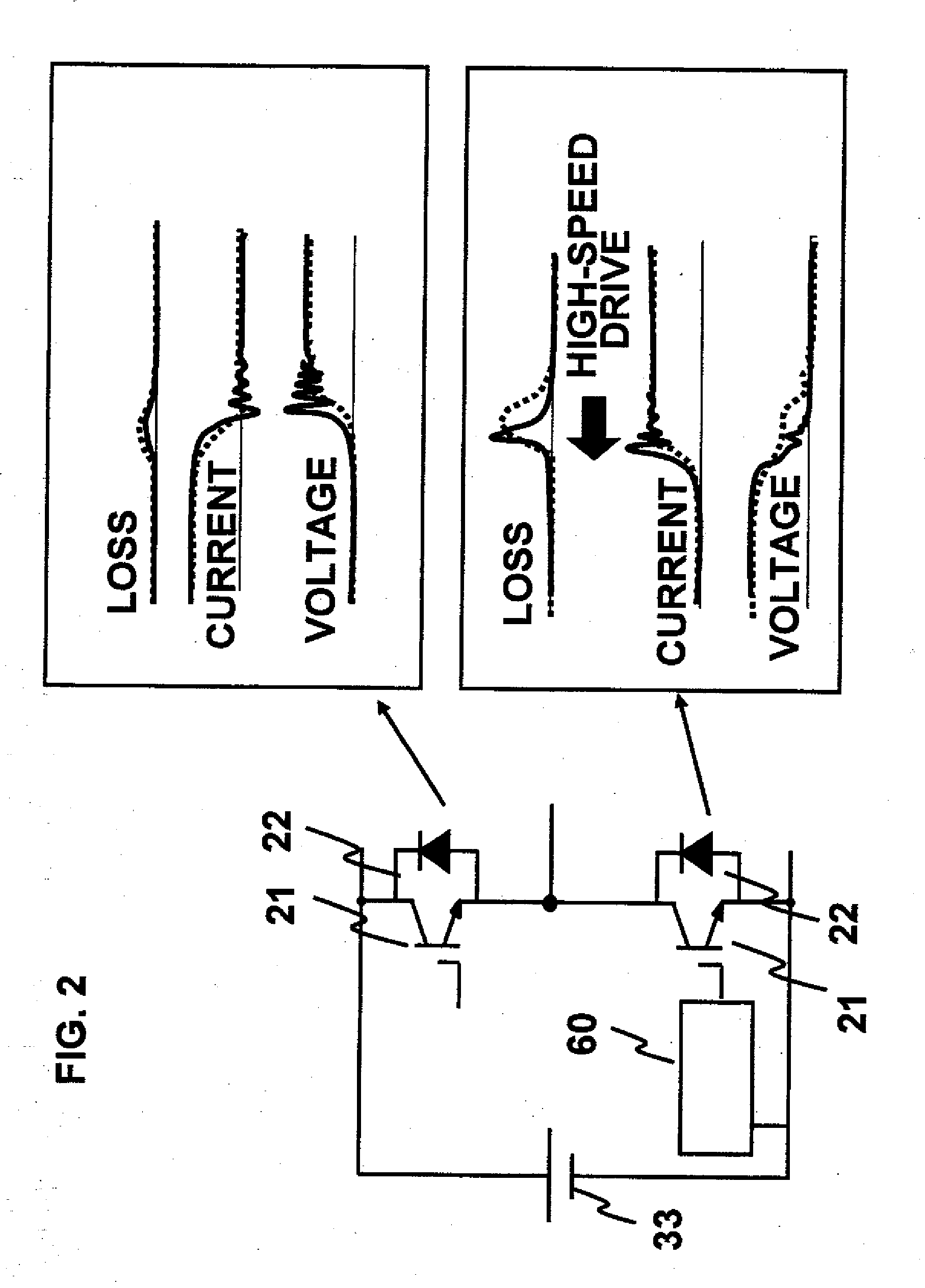

Motor driving device

InactiveUS7038415B2Reduce switchingReduce lossesTemperatue controlEmergency protective circuit arrangementsMotor driveSwitching signal

A temperature sensor (33) detects the temperature of a MOS transistor (7), and a current detecting circuit (35) detects current flowing in the MOS transistor (7). When the voltage corresponding to the detected temperature or the voltage corresponding to the detected current is increased to a threshold value or more, an overheat state detecting signal and further switching signal is set to a high level. As a result, a switch circuit in a driving circuit (17) is turned on, and the gate resistance value becomes the parallel value of a resistor (25), and the PWM frequency in the PWM control circuit is lowered, whereby the switching loss of the MOS transistor (7) can be reduced under the state that the motor (2) is rotated.

Owner:DENSO CORP

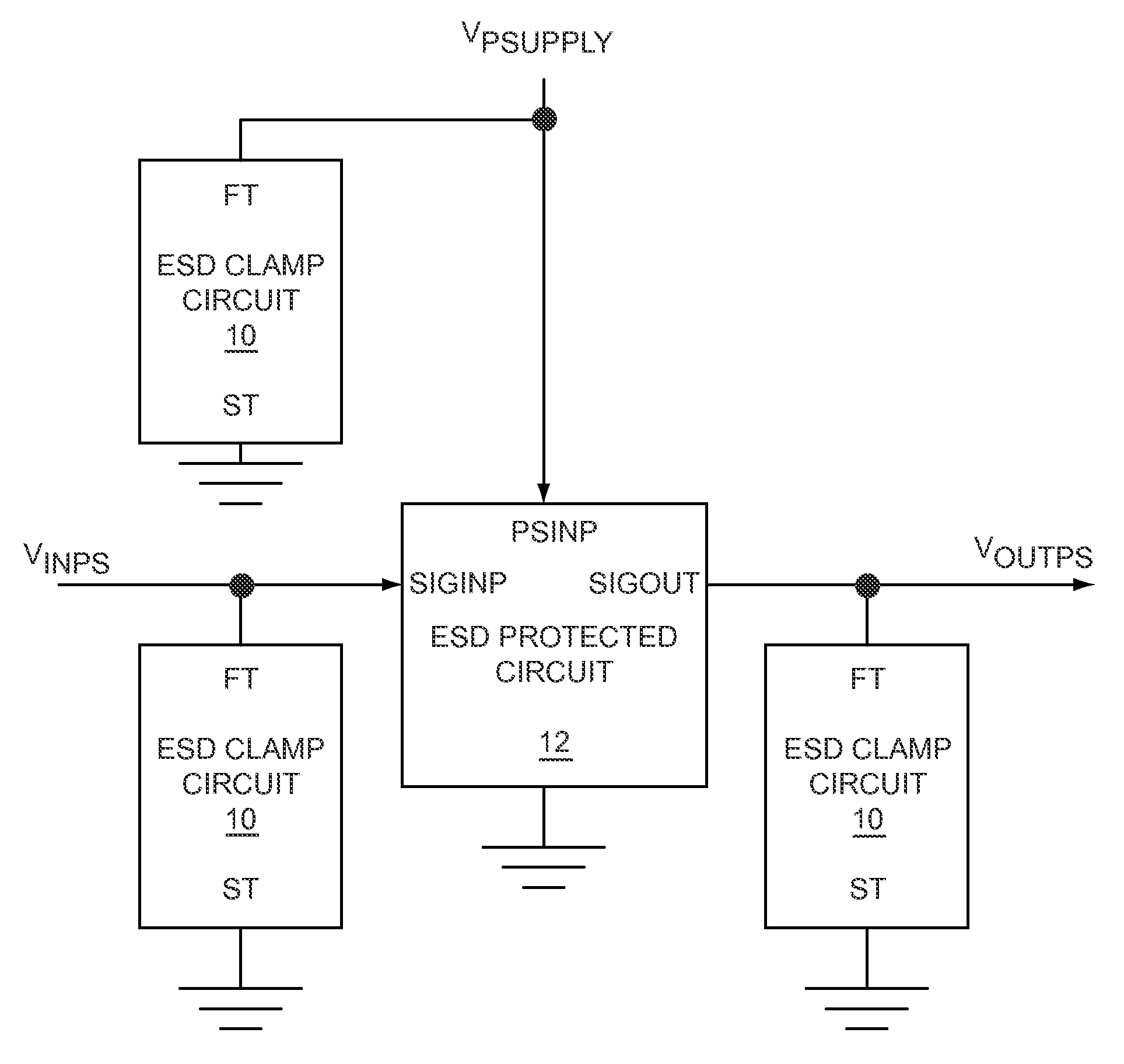

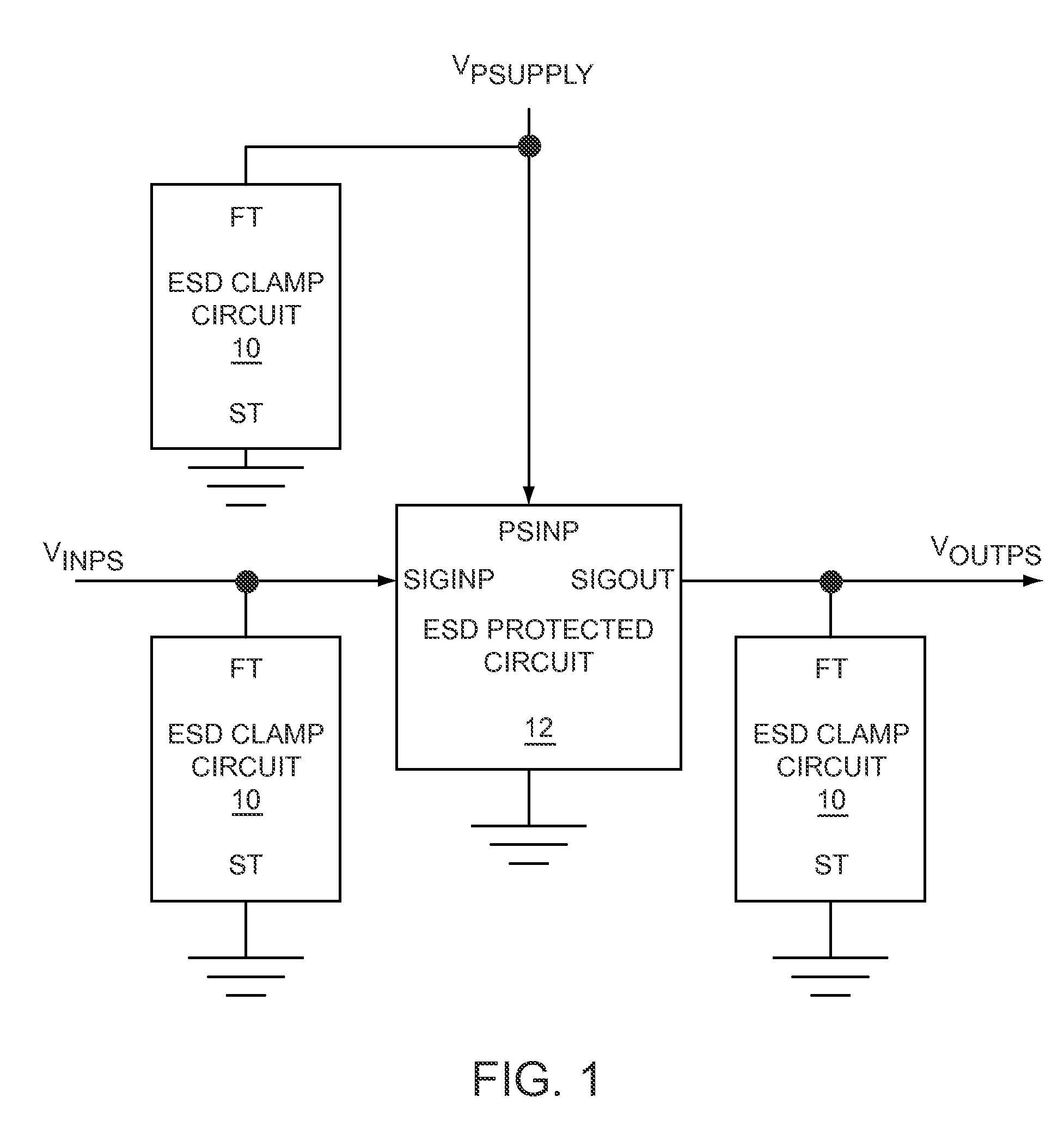

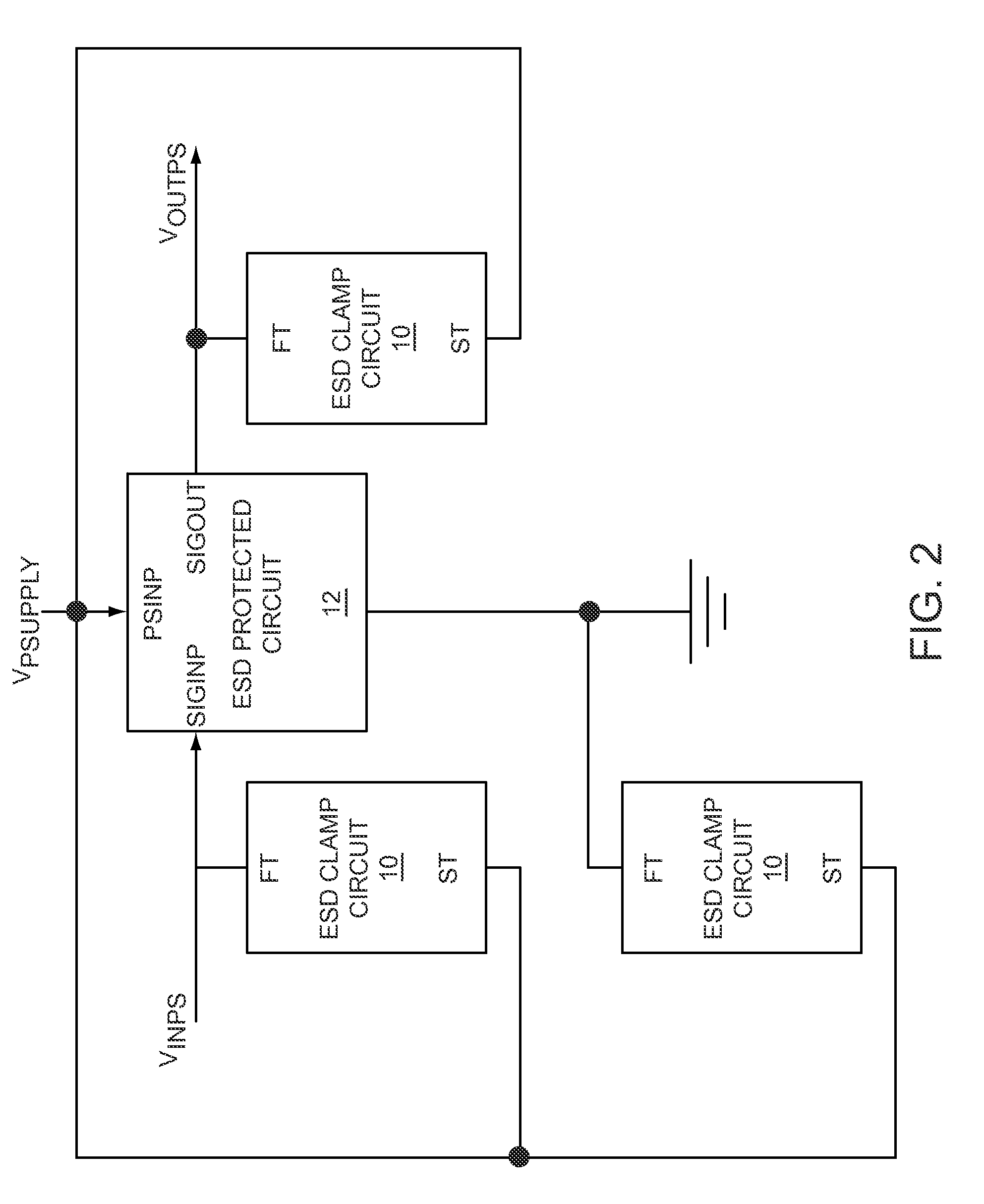

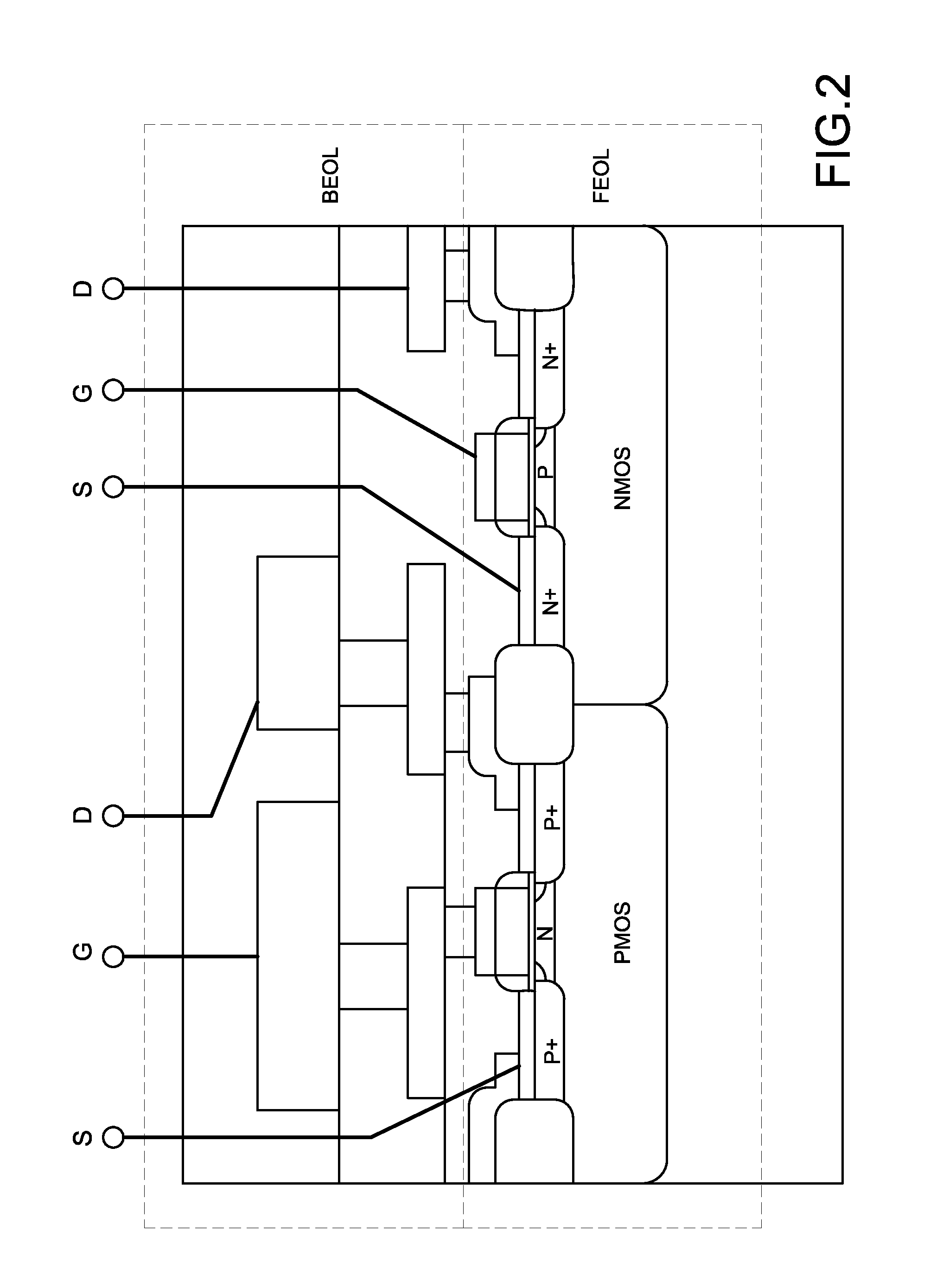

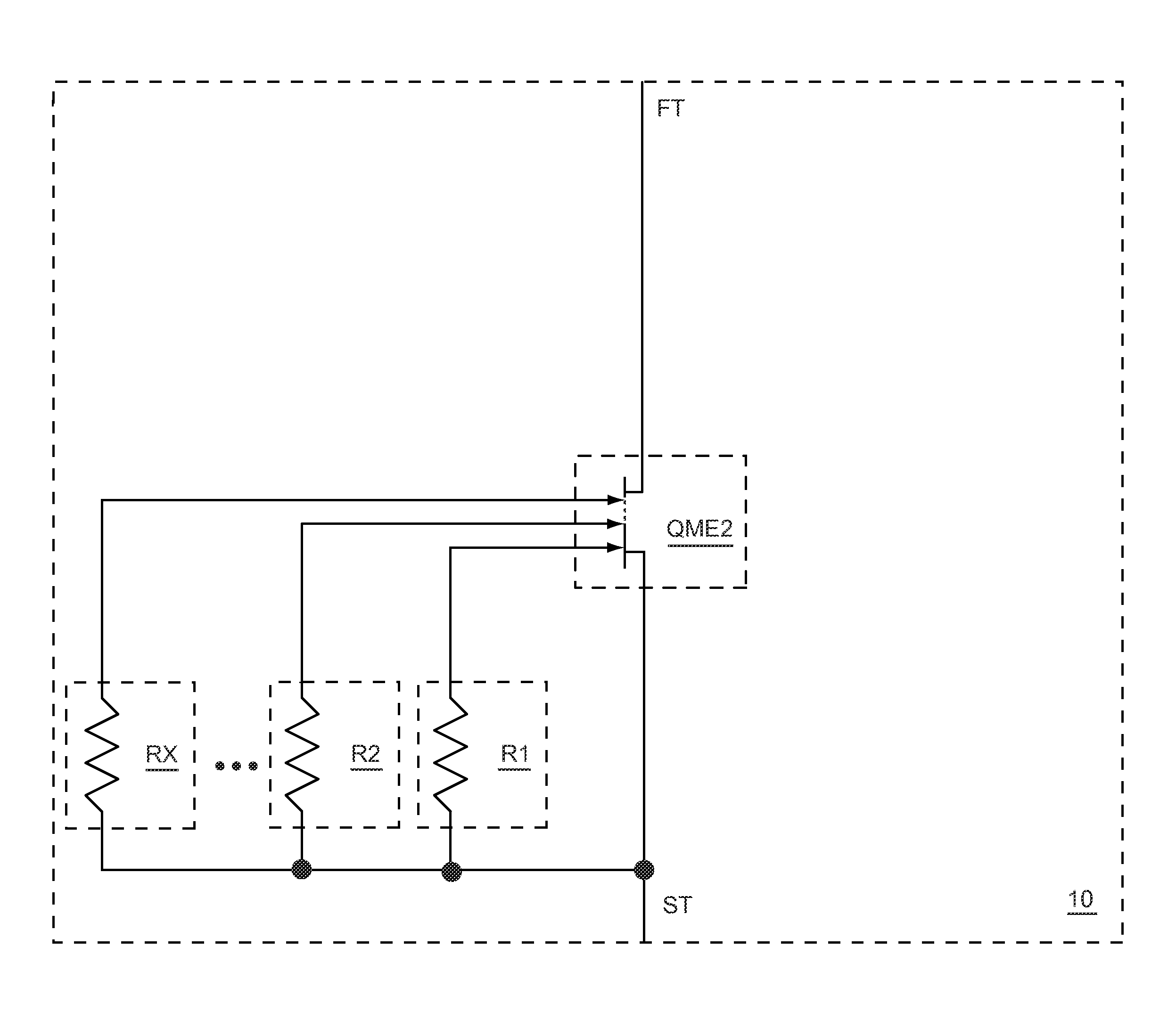

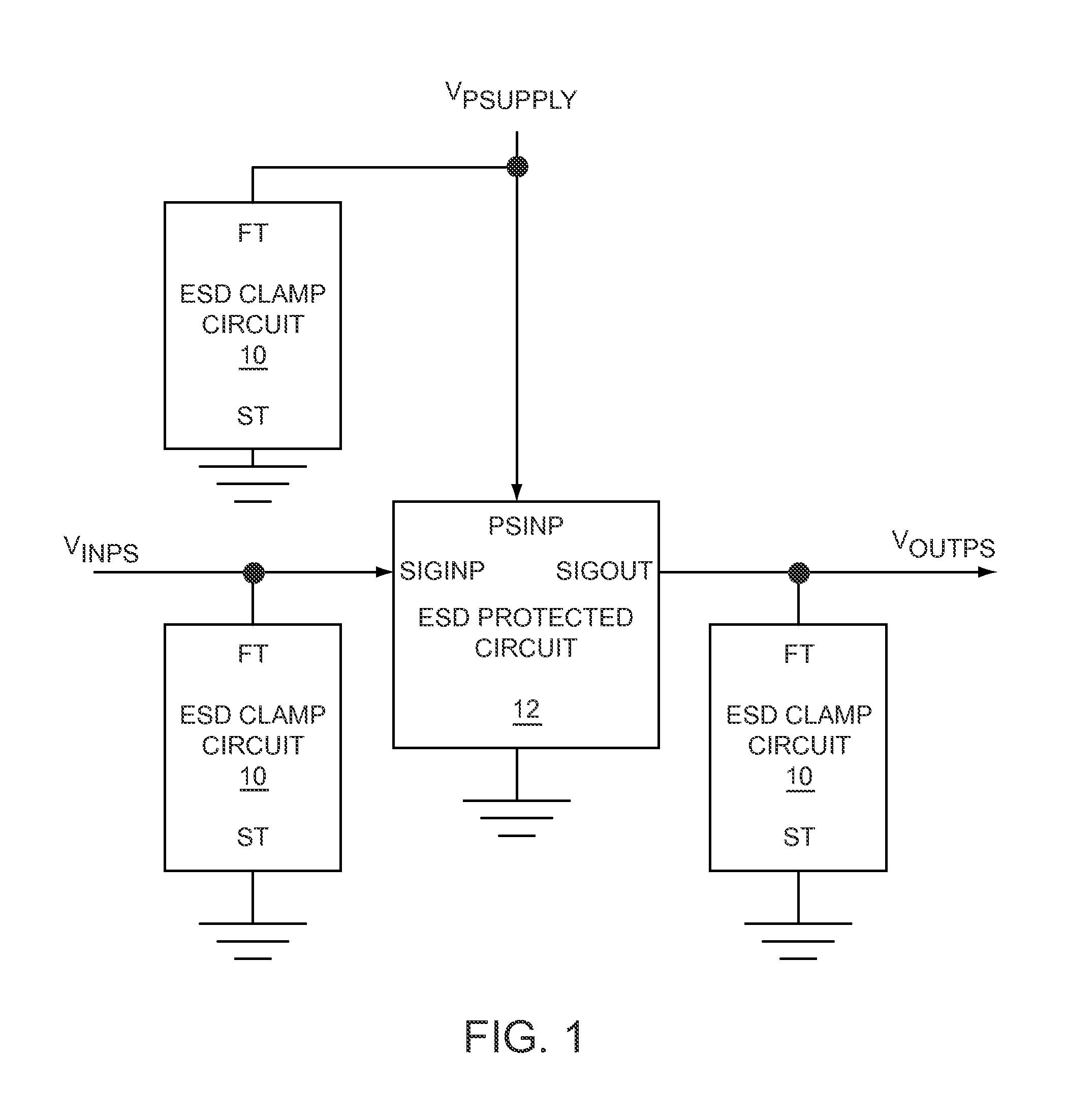

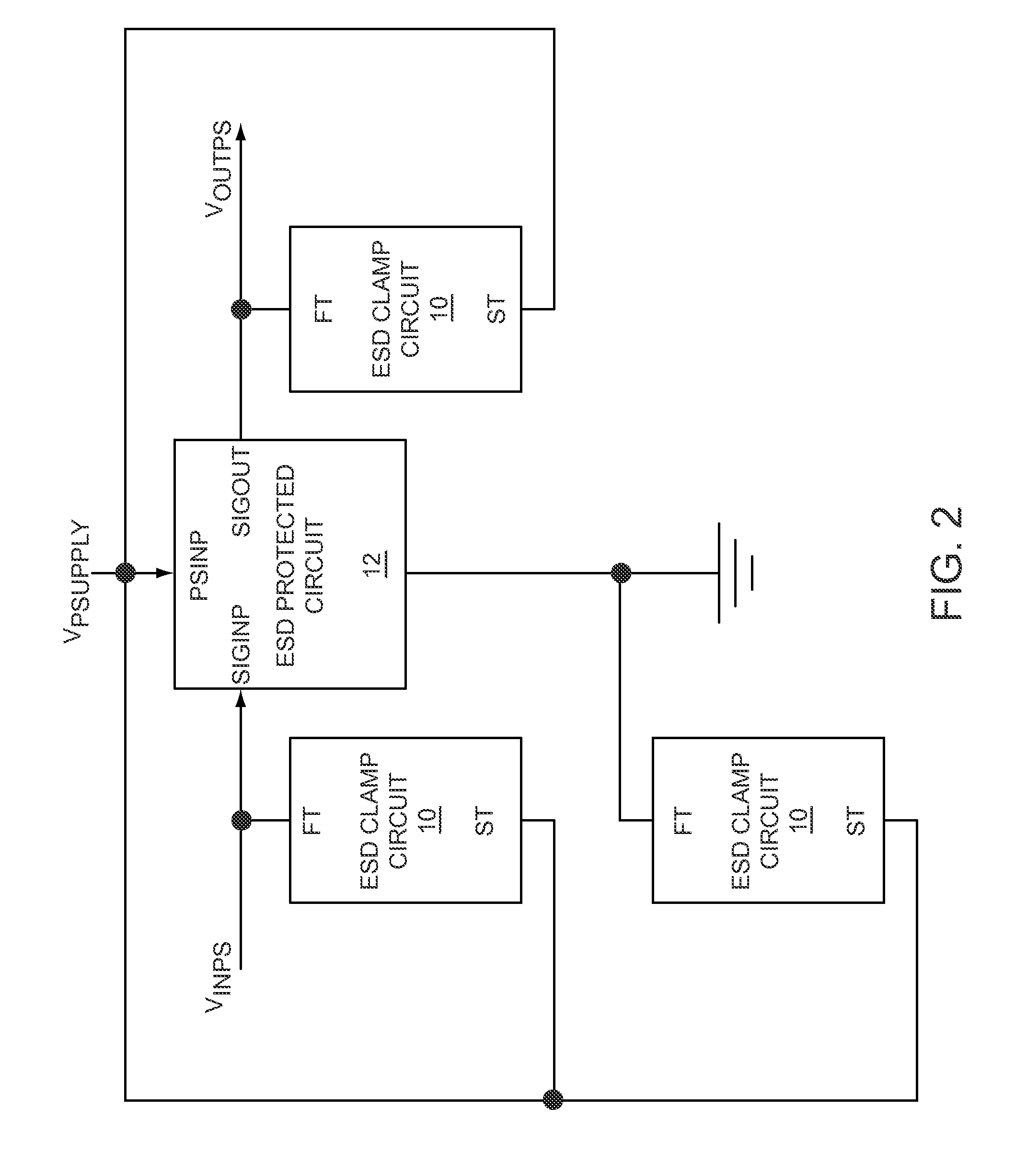

Depletion-mode field effect transistor based electrostatic discharge protection circuit

InactiveUS7881029B1Minimize parasitic capacitanceMaximize linearityAntennas earthing switches associationAmplifier protection circuit arrangementsLevel shiftingEngineering

The present invention relates to an electrostatic discharge (ESD) clamp circuit that is used to protect other circuitry from high voltage ESD events. The ESD clamp circuit may include a field effect transistor (FET) element as a clamping element, which is triggered by using a drain-to-gate capacitance and a drain-to-gate resistance of the FET element and a resistive element as a voltage divider to divide down an ESD voltage to provide a triggering gate voltage of the FET element. In its simplest embodiment, the ESD clamp circuit includes only an FET element, a resistive element, a source-coupled level shifting diode, and a reverse protection diode. Therefore, the ESD clamp circuit may be small compared to other ESD protection circuits. The simplicity of the ESD clamp circuit may minimize parasitic capacitances, thereby maximizing linearity of the ESD clamp circuit over a wide frequency range.

Owner:QORVO US INC

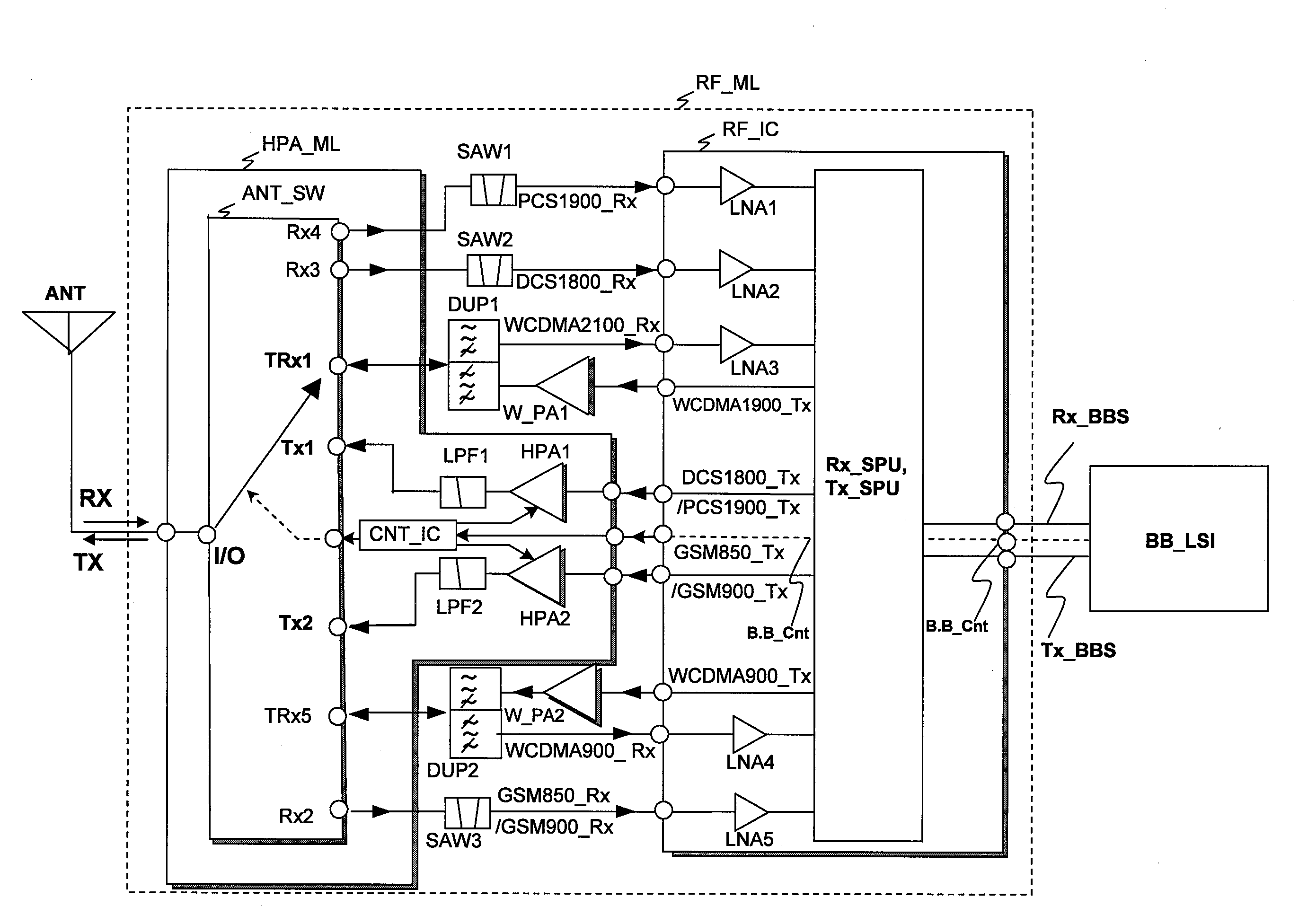

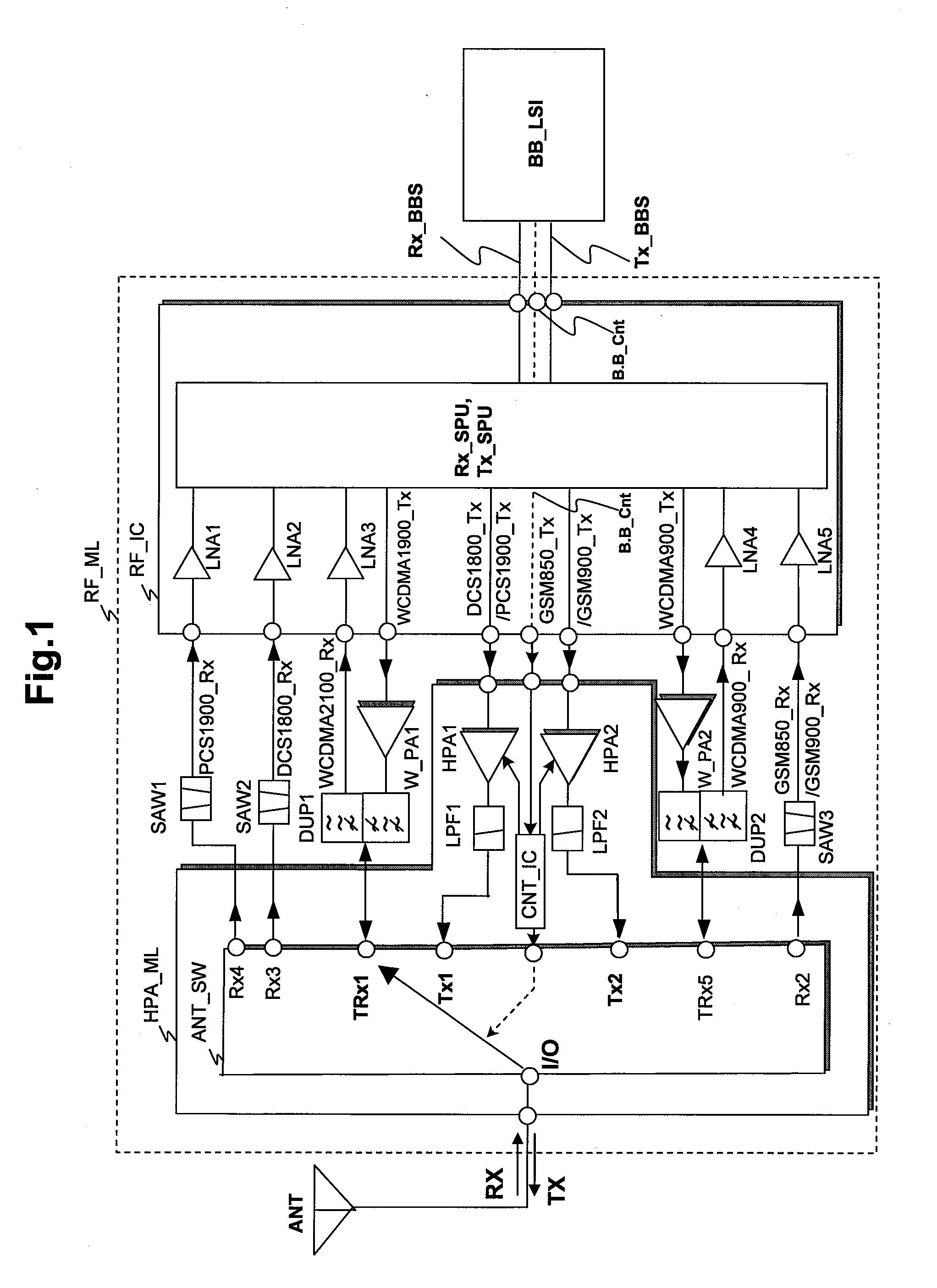

Semiconductor integrated circuit, RF module using the same, and radio communication terminal device using the same

InactiveUS20100069020A1Harmonic reductionProlong lifePulse automatic controlElectronic switchingTerminal equipmentRF module

One high-frequency switch Qm supplied with transmit and receive signals to ON, and another high-frequency switch Qn supplied with a signal of another system to OFF are controlled. In the other high-frequency switch Qn, to set V-I characteristics of near-I / O gate resistances Rg1n-Rg3n of a near-I / O FET Qn1 near to a common input / output terminal I / O connected with an antenna are set to be higher in linearity than V-I characteristics of middle-portion gate resistances Rg3n and Rg4n of middle-portion FETs Qn3 and Qn4. Thus, even in case that an uneven RF leak signal is supplied to near-I / O gate resistances Rg1n-Rg3n, and middle-portion gate resistances Rg3n and Rg4n, the distortion of current flowing through the near-I / O gate resistances Rg1n-Rg3n near to the input / output terminal I / O can be reduced.

Owner:RENESAS ELECTRONICS CORP

Selective growth of a work-function metal in a replacement metal gate of a semiconductor device

InactiveUS20150108577A1Improves fill-in of metal materialLower gate resistanceTransistorSolid-state devicesMetallic materialsField-effect transistor

Approaches for forming a replacement metal gate (RMG) of a semiconductor device, are disclosed. Specifically provided is a p-channel field effect transistor (p-FET) and an n-channel field effect transistor (n-FET) formed over a substrate, the p-FET and the n-FET each having a recess formed therein, a high-k layer and a barrier layer formed within each recess, a work-function metal (WFM) selectively grown within the recess of the n-FET, wherein the high-k layer, barrier layer, and WFM are each recessed to a desired height within the recesses, and a metal material (e.g., Tungsten) formed within each recess. By providing a WFM chamfer earlier in the process, the risk of mask materials filling into each gate recess is reduced. Furthermore, the selective WFM growth improves fill-in of the metal material, which lowers gate resistance in the device.

Owner:GLOBALFOUNDRIES INC

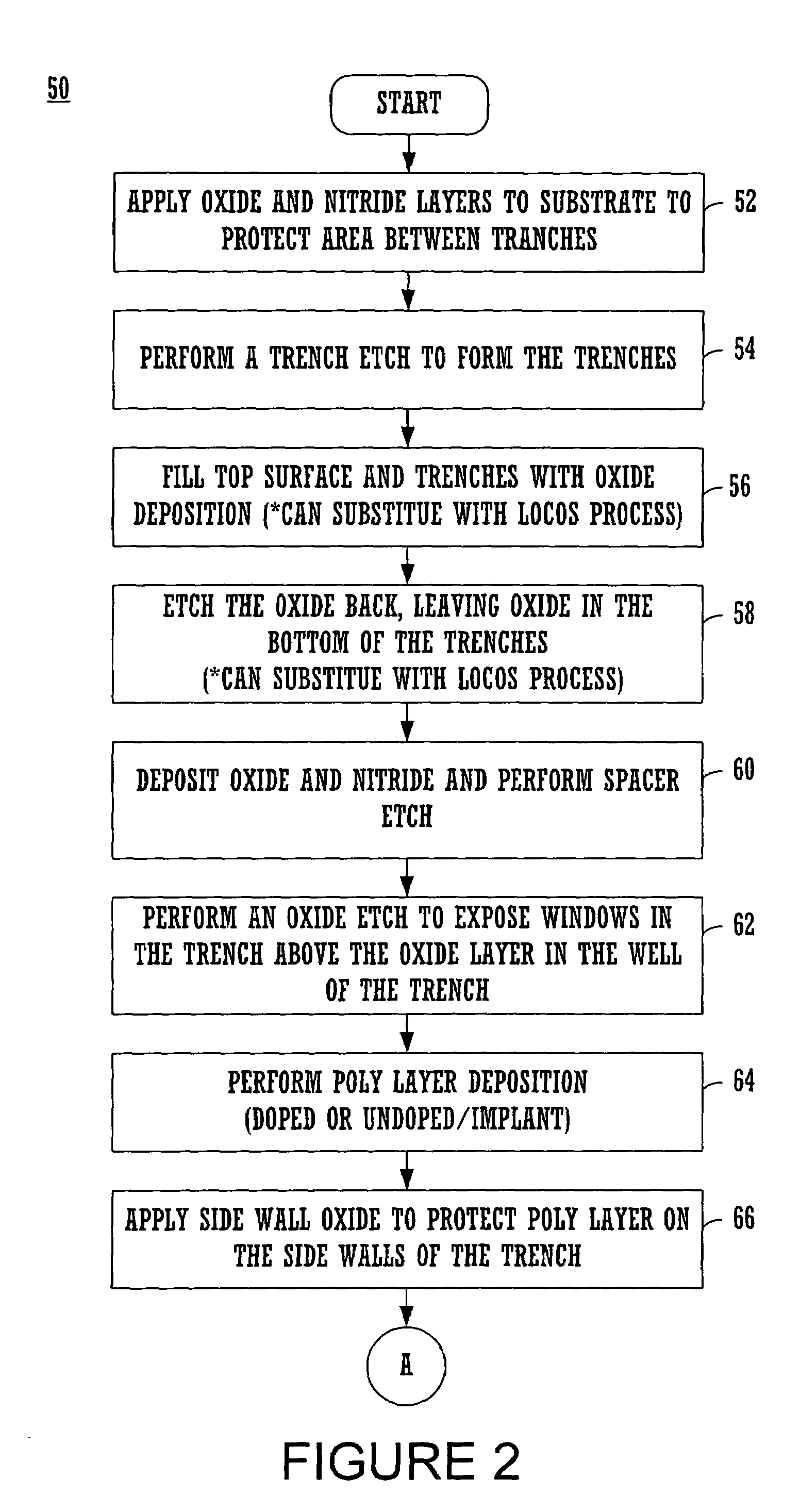

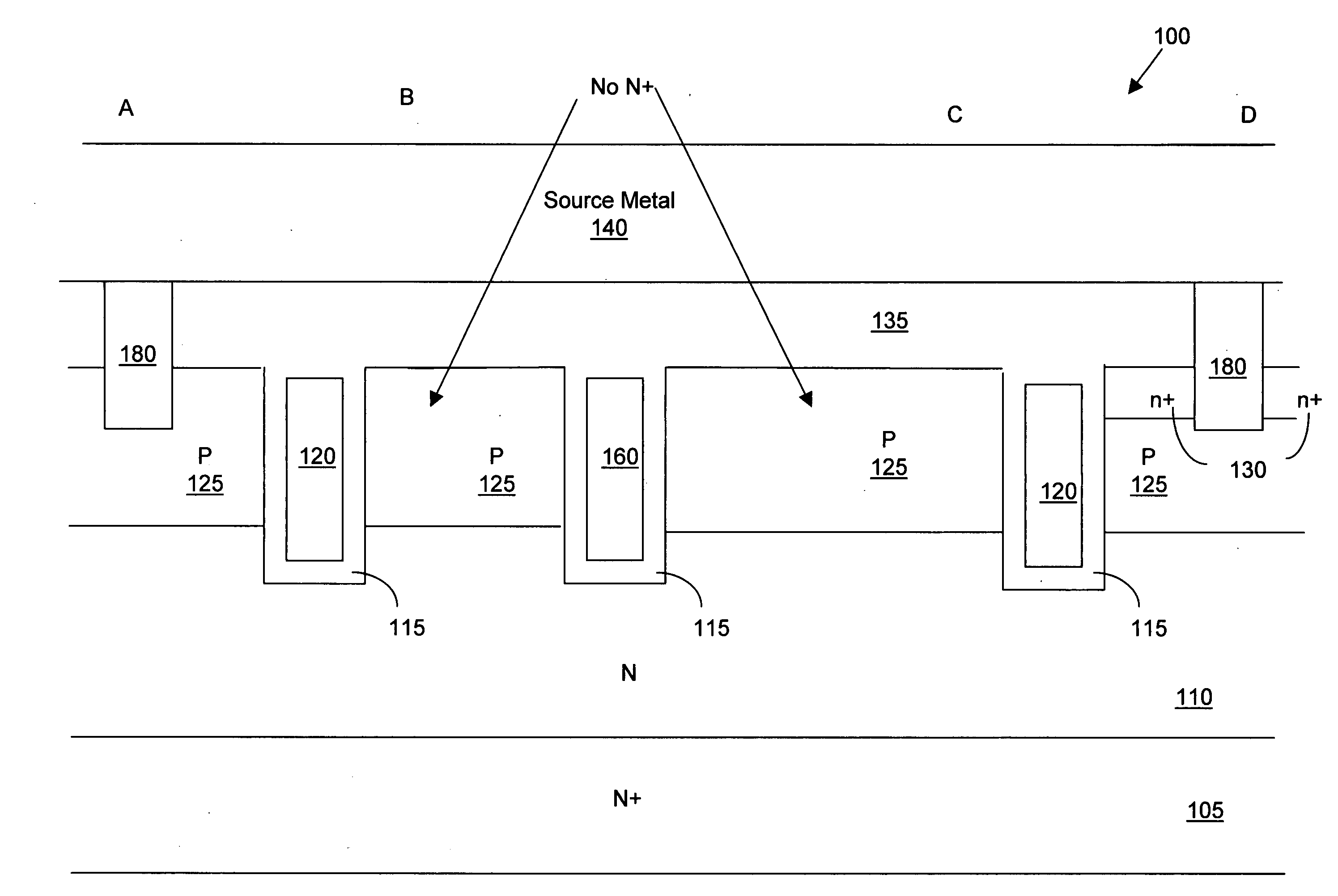

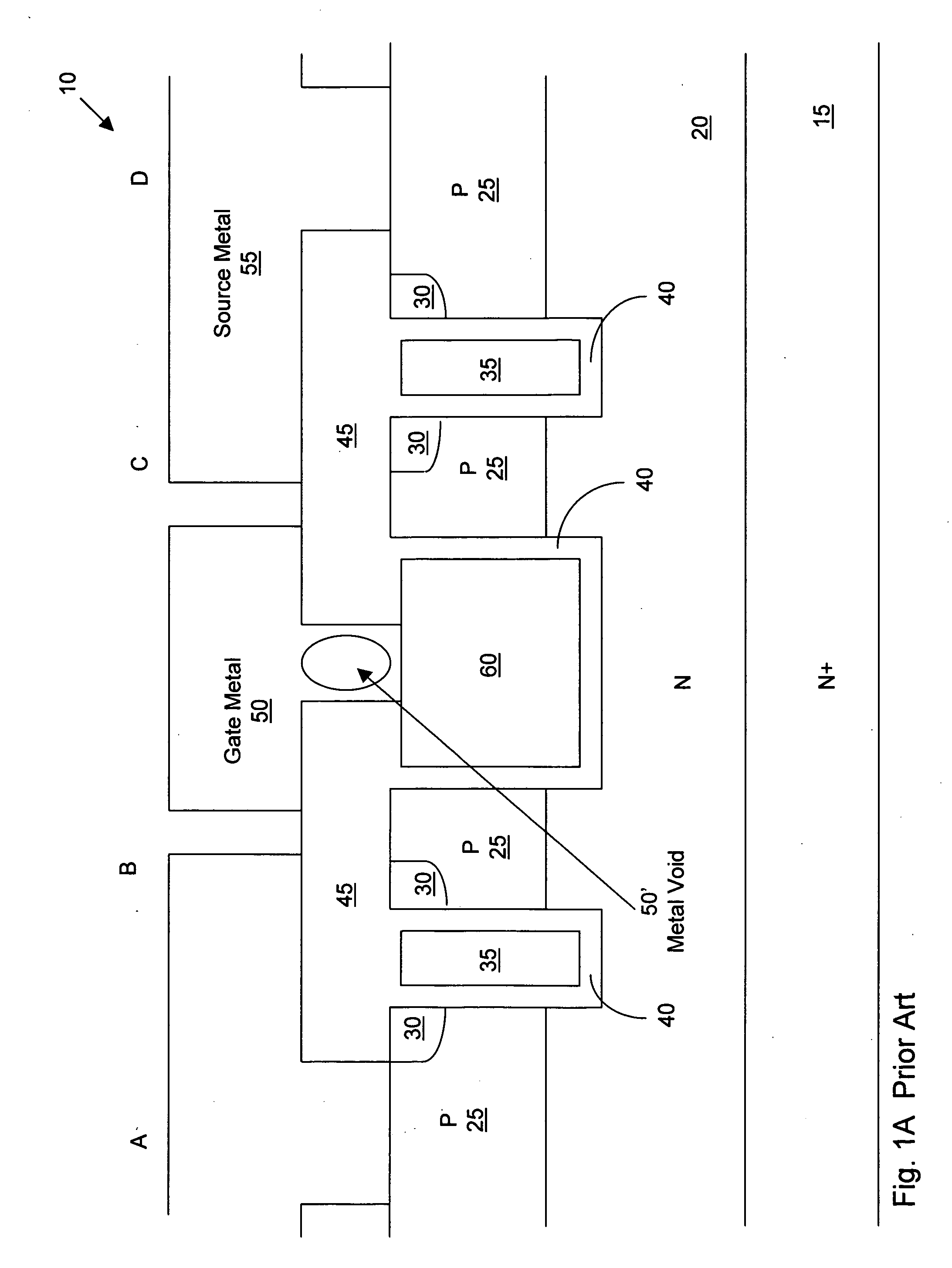

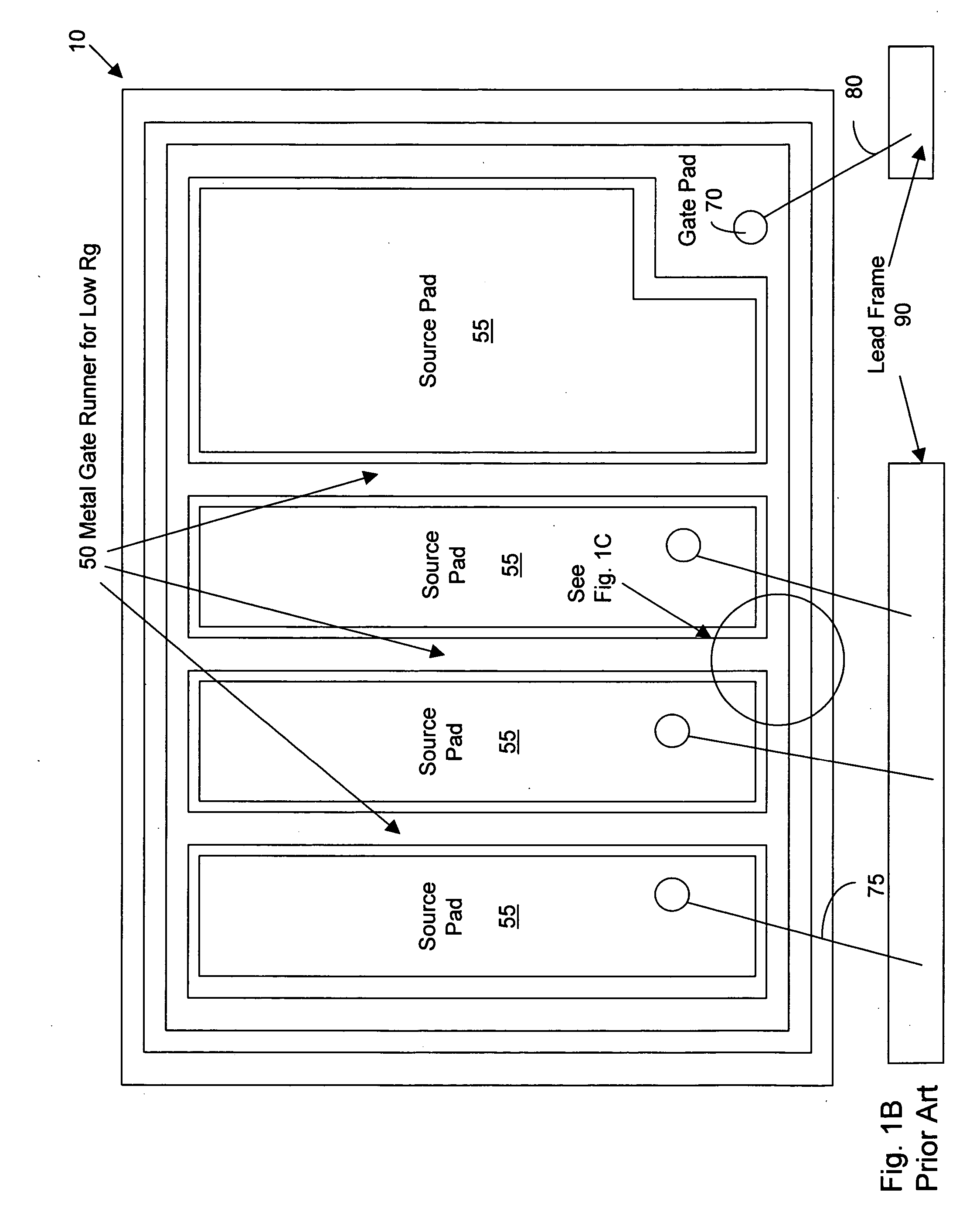

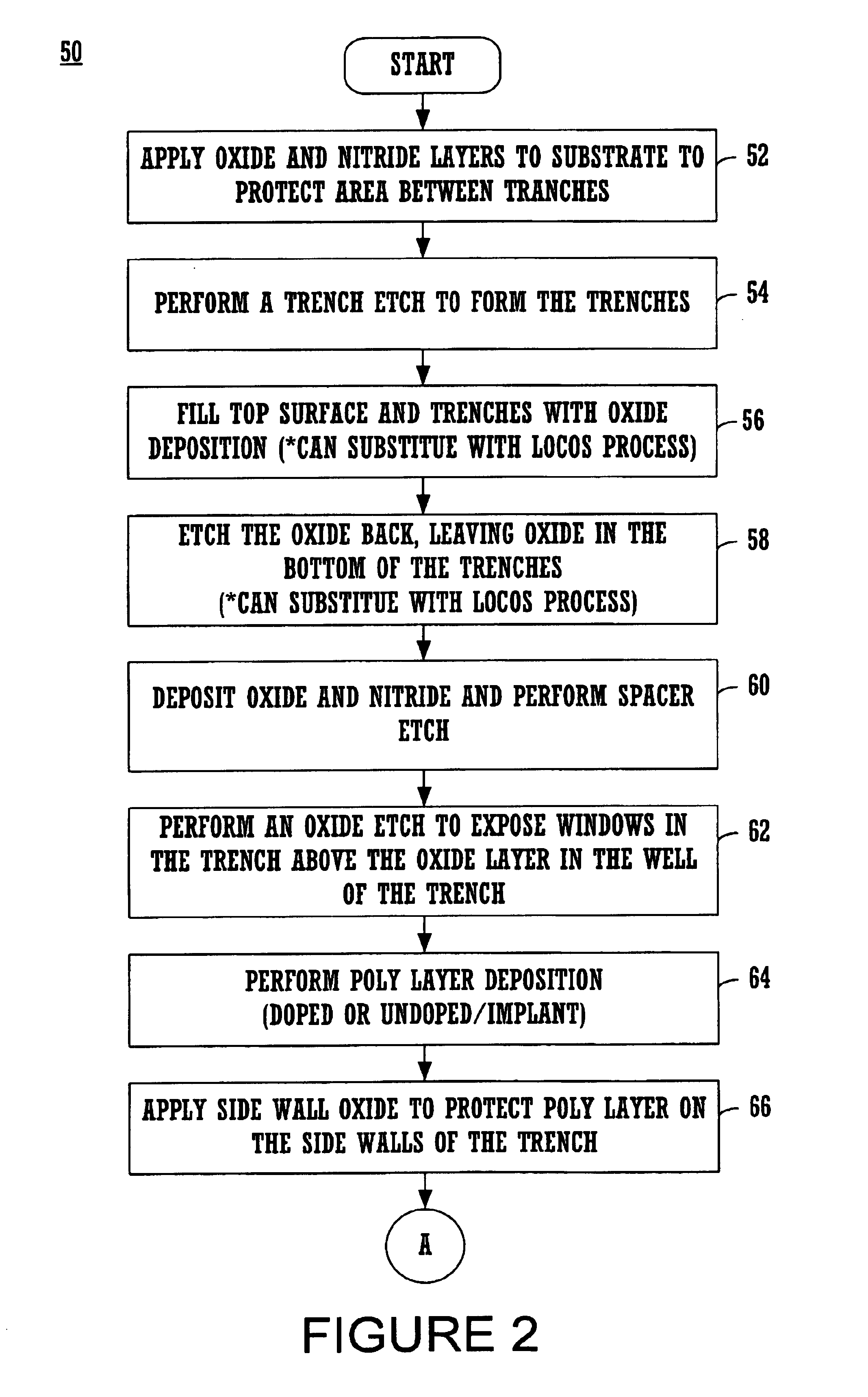

Gate contact and runners for high density trench MOSFET

InactiveUS20060273390A1Lower gate resistanceReduce source-body resistanceSolid-state devicesSemiconductor devicesTrench mosfetHigh density

A trenched metal oxide semiconductor field effect transistor (MOSFET) cell that includes a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The MOSFET cell further includes a buried trench-poly gate runner electrically contacting to a trench gate of the trenched MOSFET. The buried trench-poly gate runner for functioning as a gate runner to increase gate transmission area and a contact area to a gate contact metal for reducing a gate resistance.

Owner:M MOS SEMICON

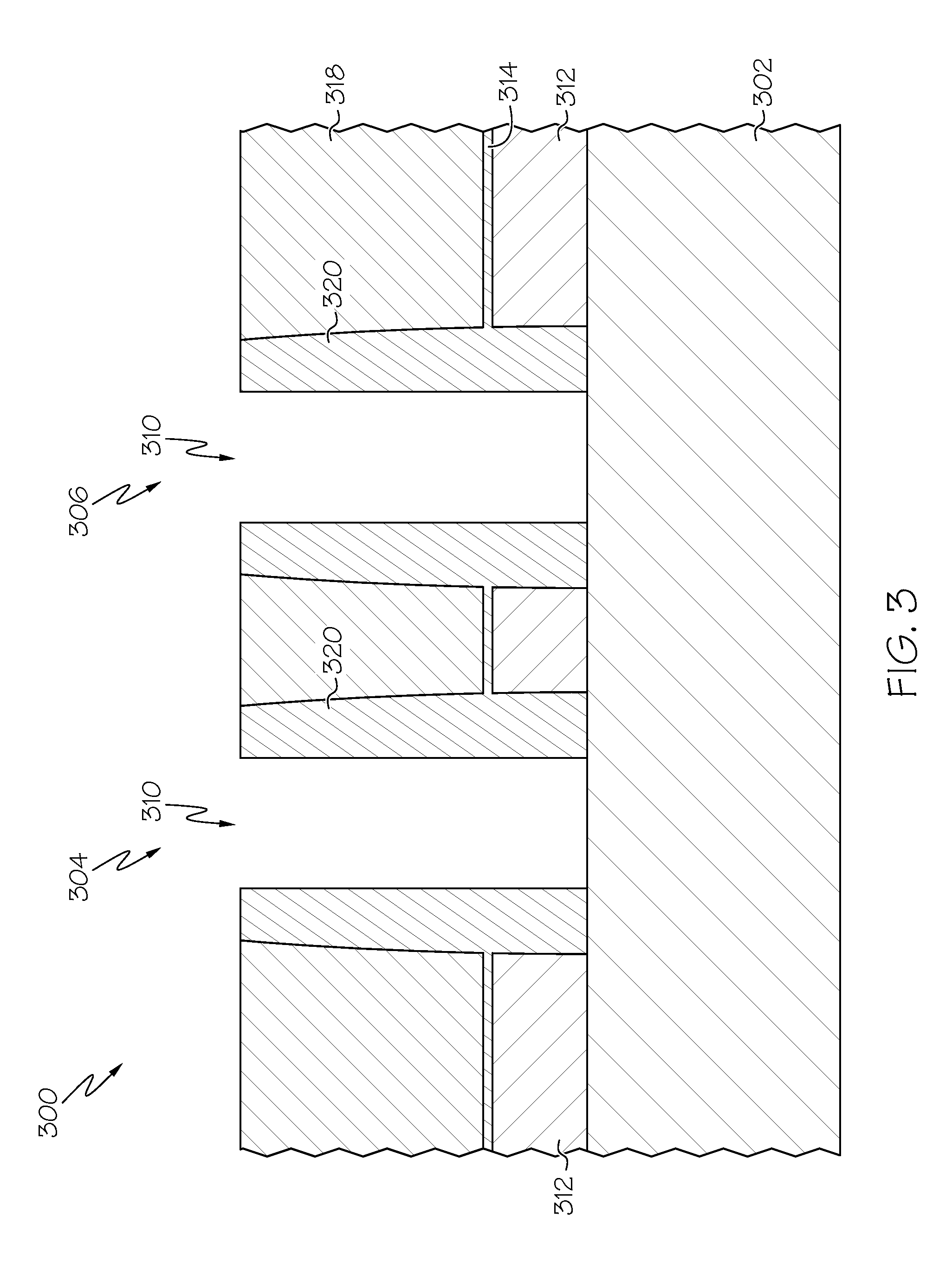

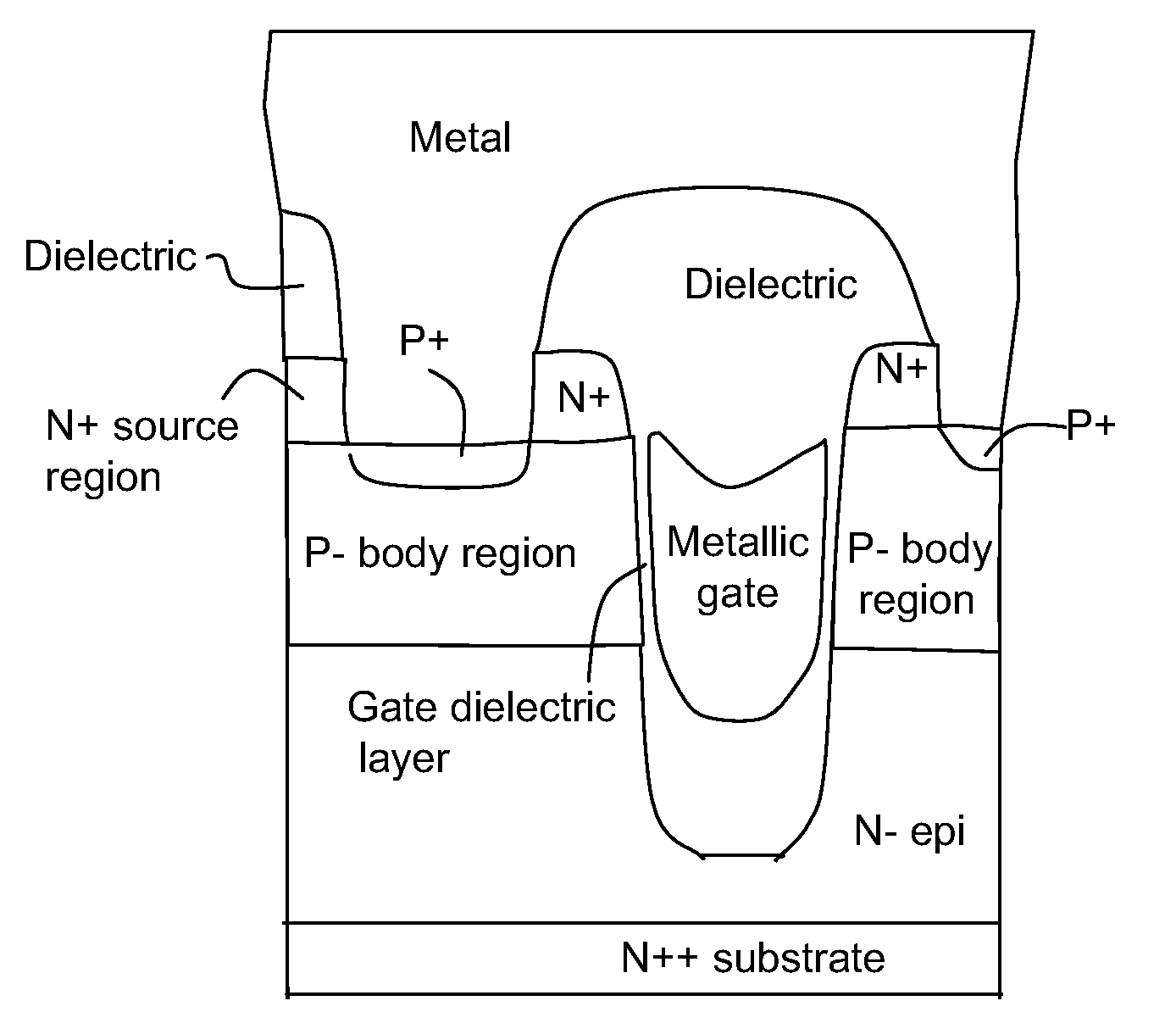

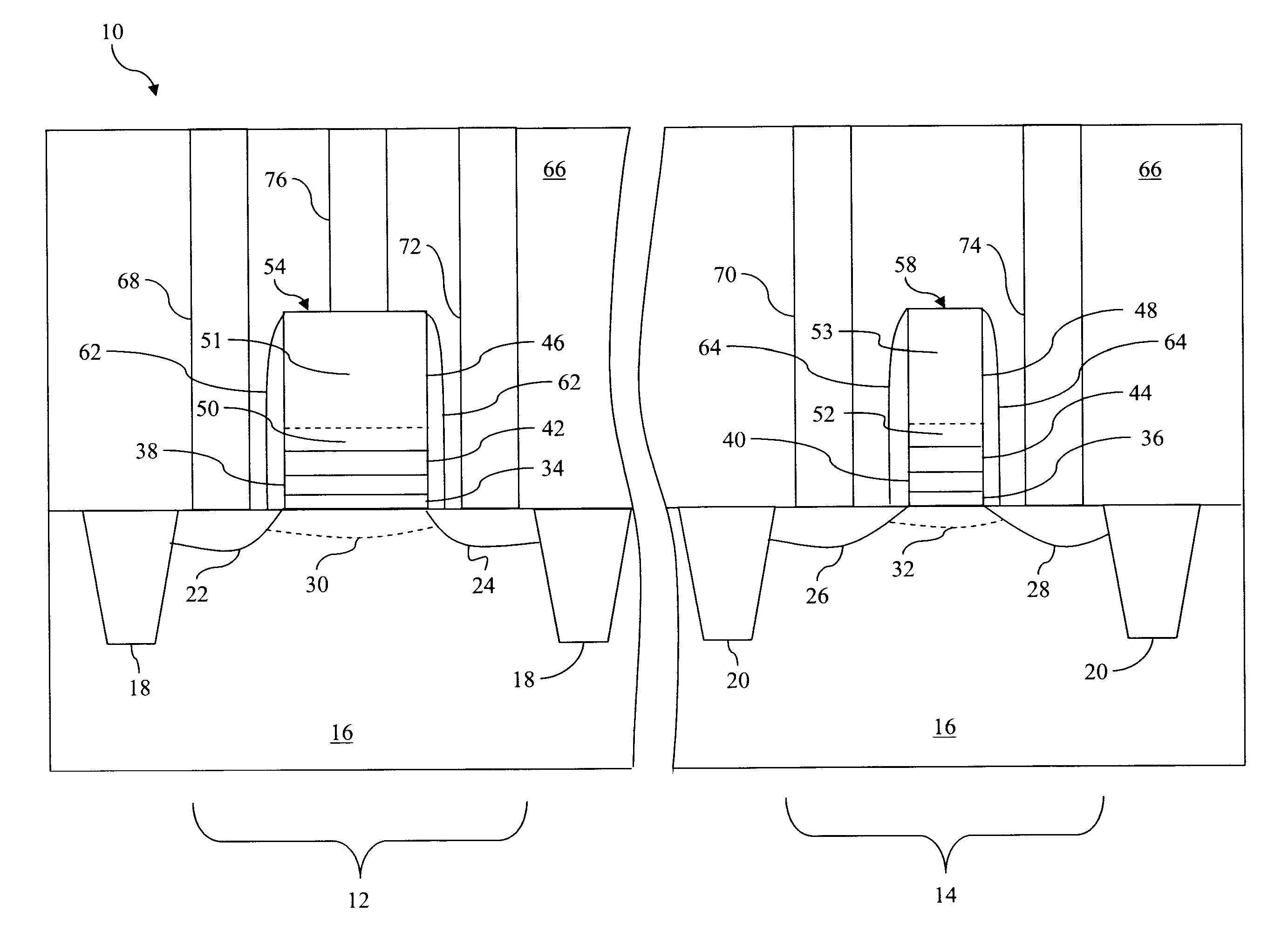

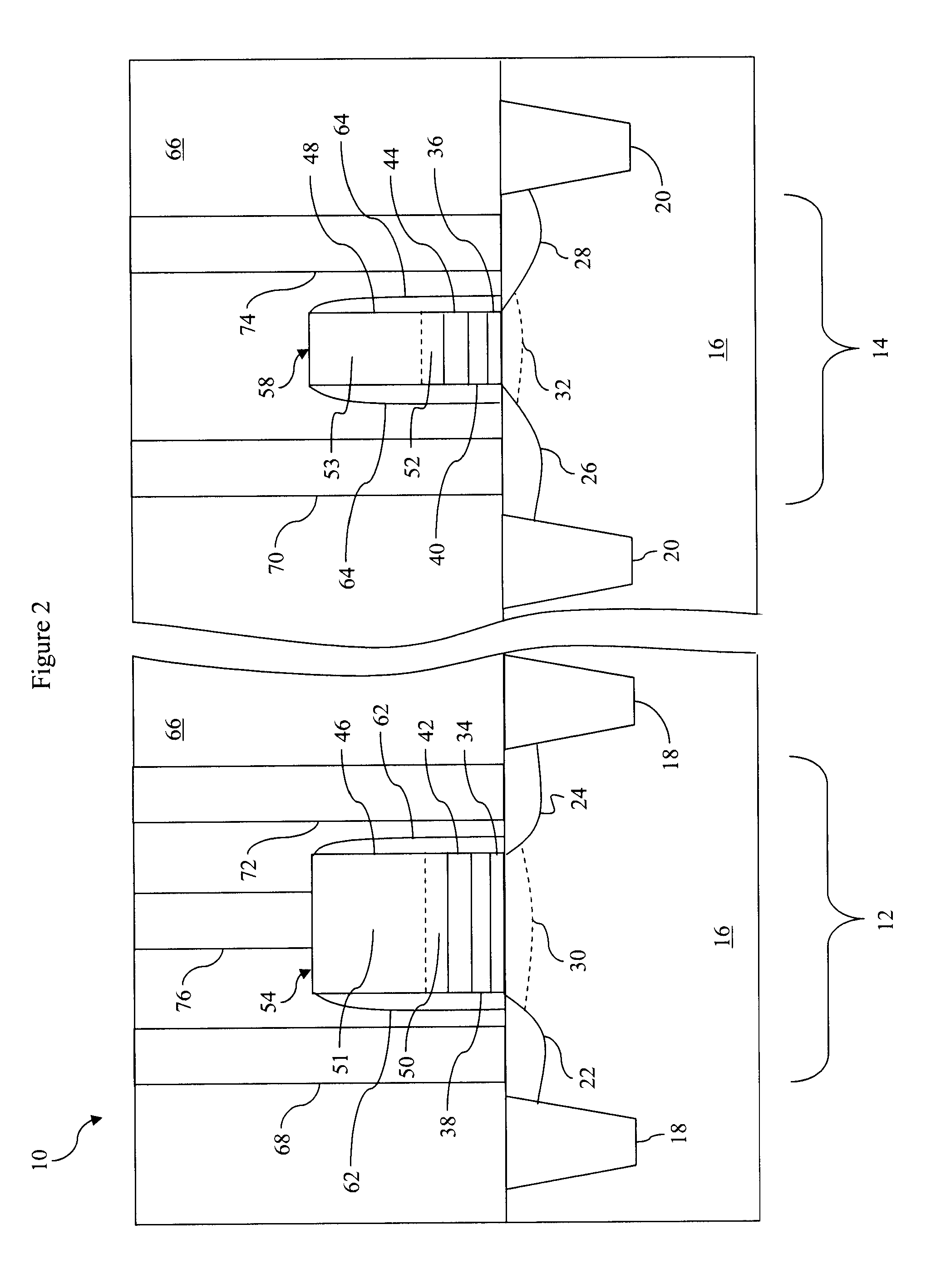

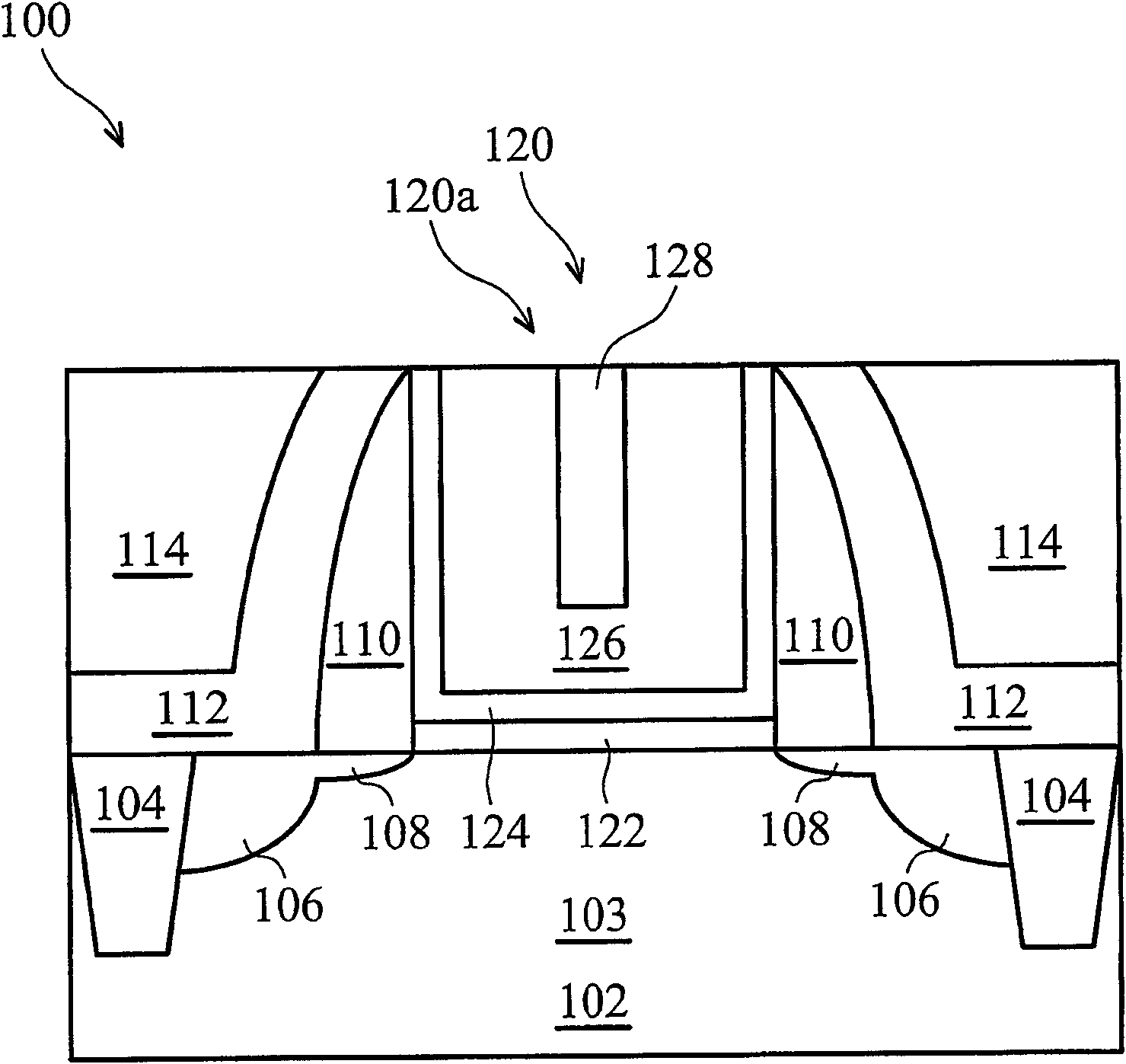

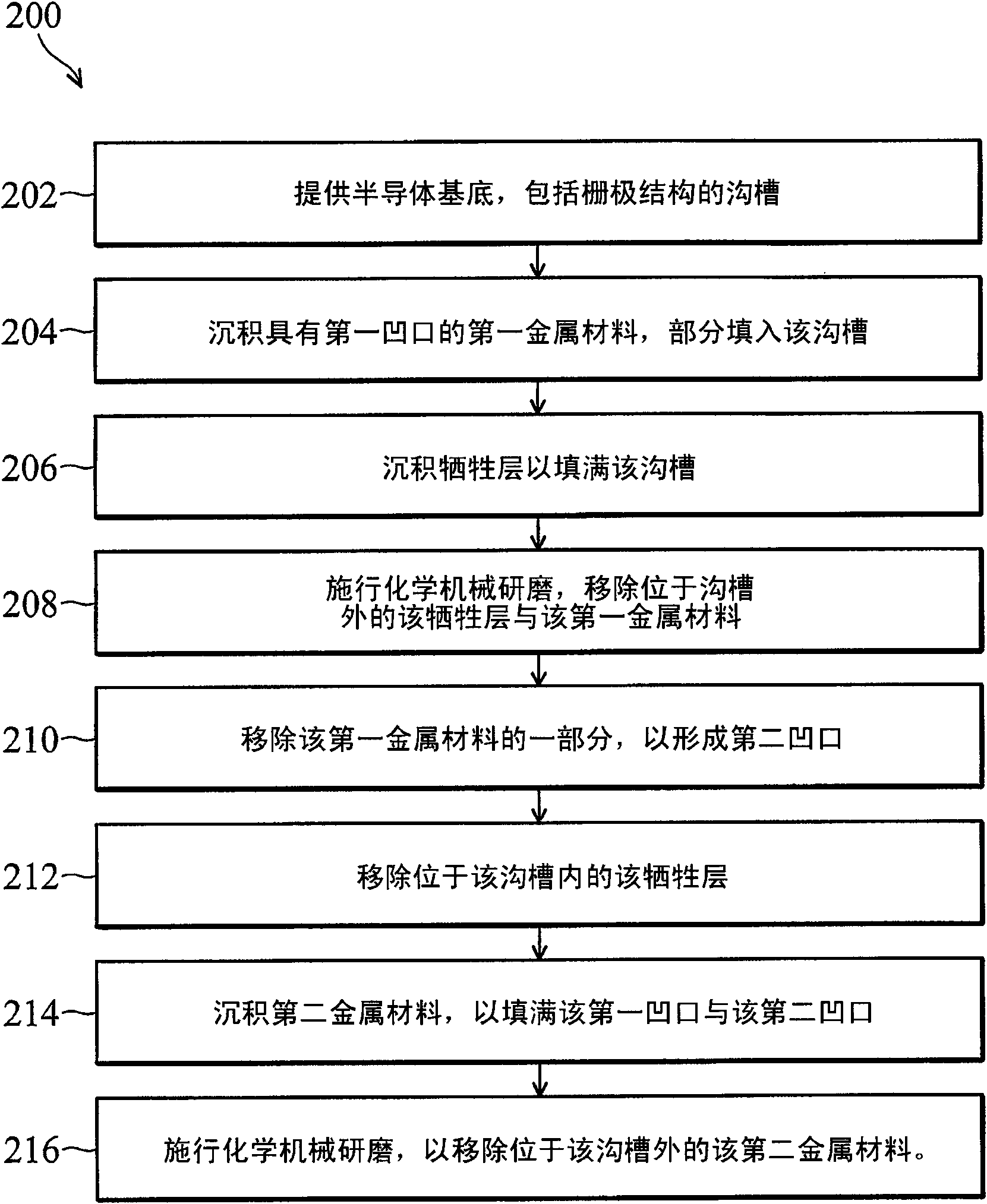

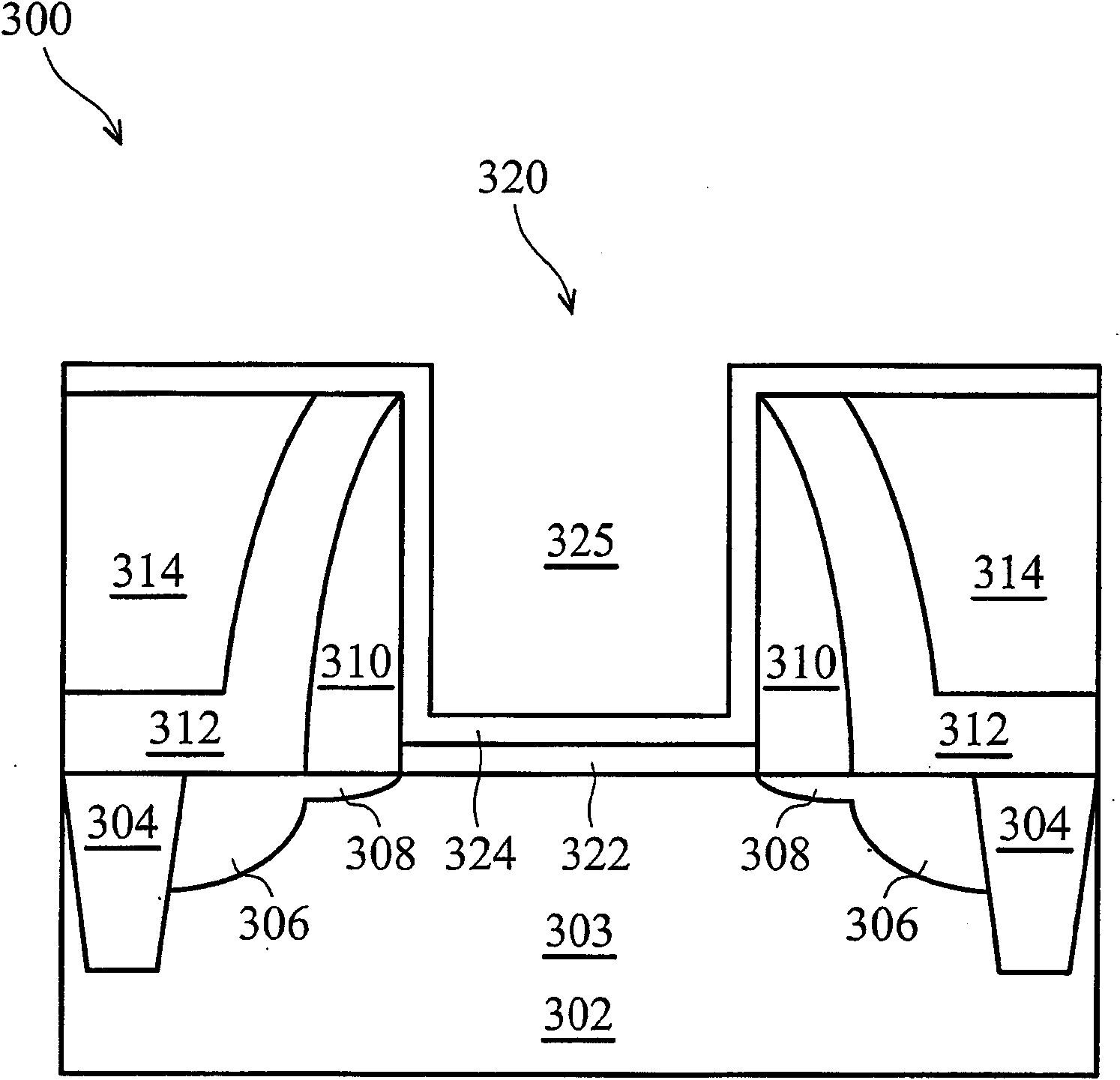

Structure and Method for Forming Trench Gate Transistors with Low Gate Resistance

InactiveUS20100013009A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricMetallic materials

A field effect transistor includes body regions of a first conductivity type over a semiconductor region of a second conductivity type such that the body regions form p-n junctions with the semiconductor region. Trenches extend through the body region and terminate within the semiconductor region. Source regions of the second conductivity type extend over the body regions adjacent the trenches such that the source regions form p-n junctions with the body regions. A gate dielectric layer lines sidewalls of each trench. A metal liner lines the gate dielectric layer in each trench. A gate electrode comprising metallic material is disposed in each trench.

Owner:SEMICON COMPONENTS IND LLC

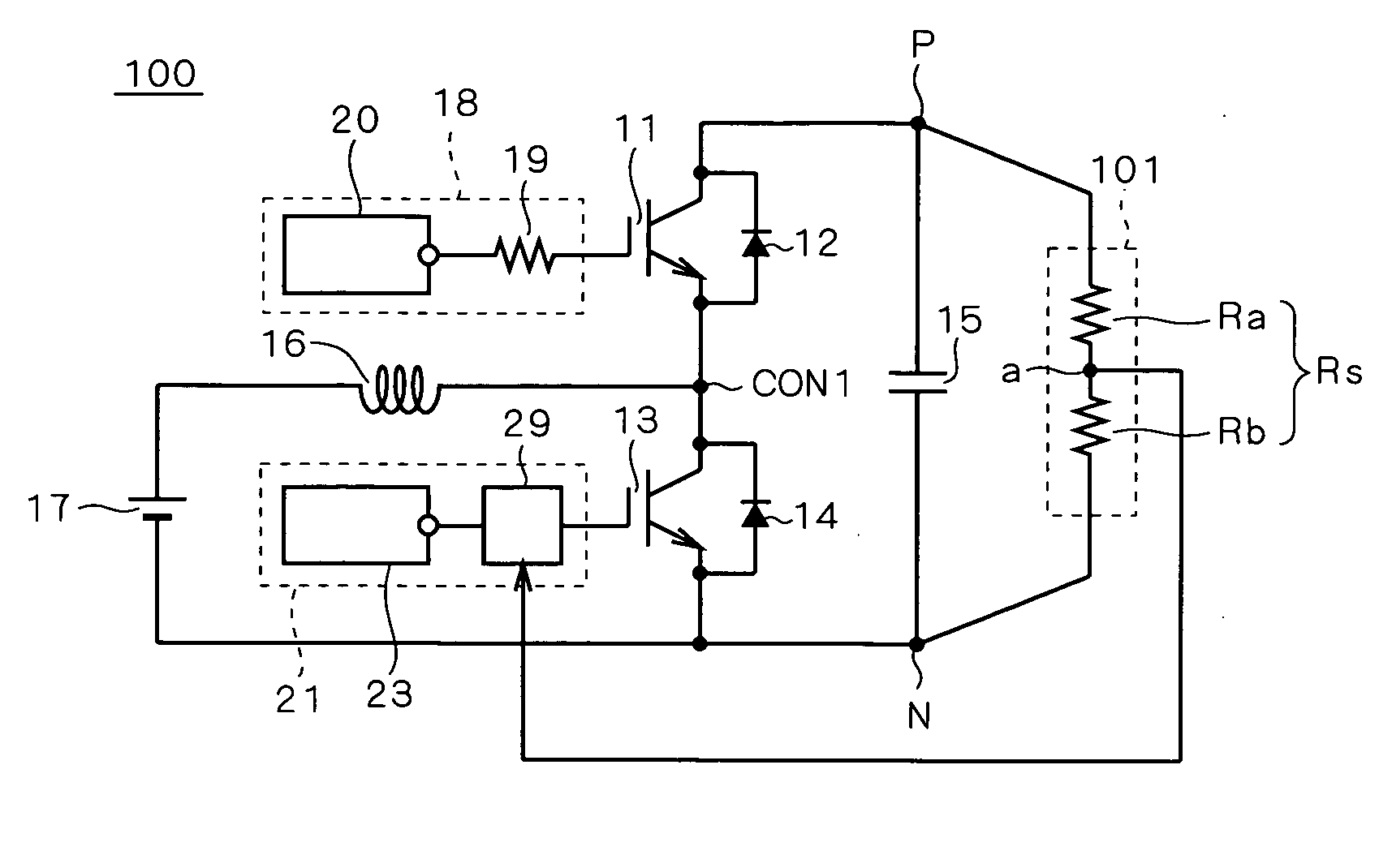

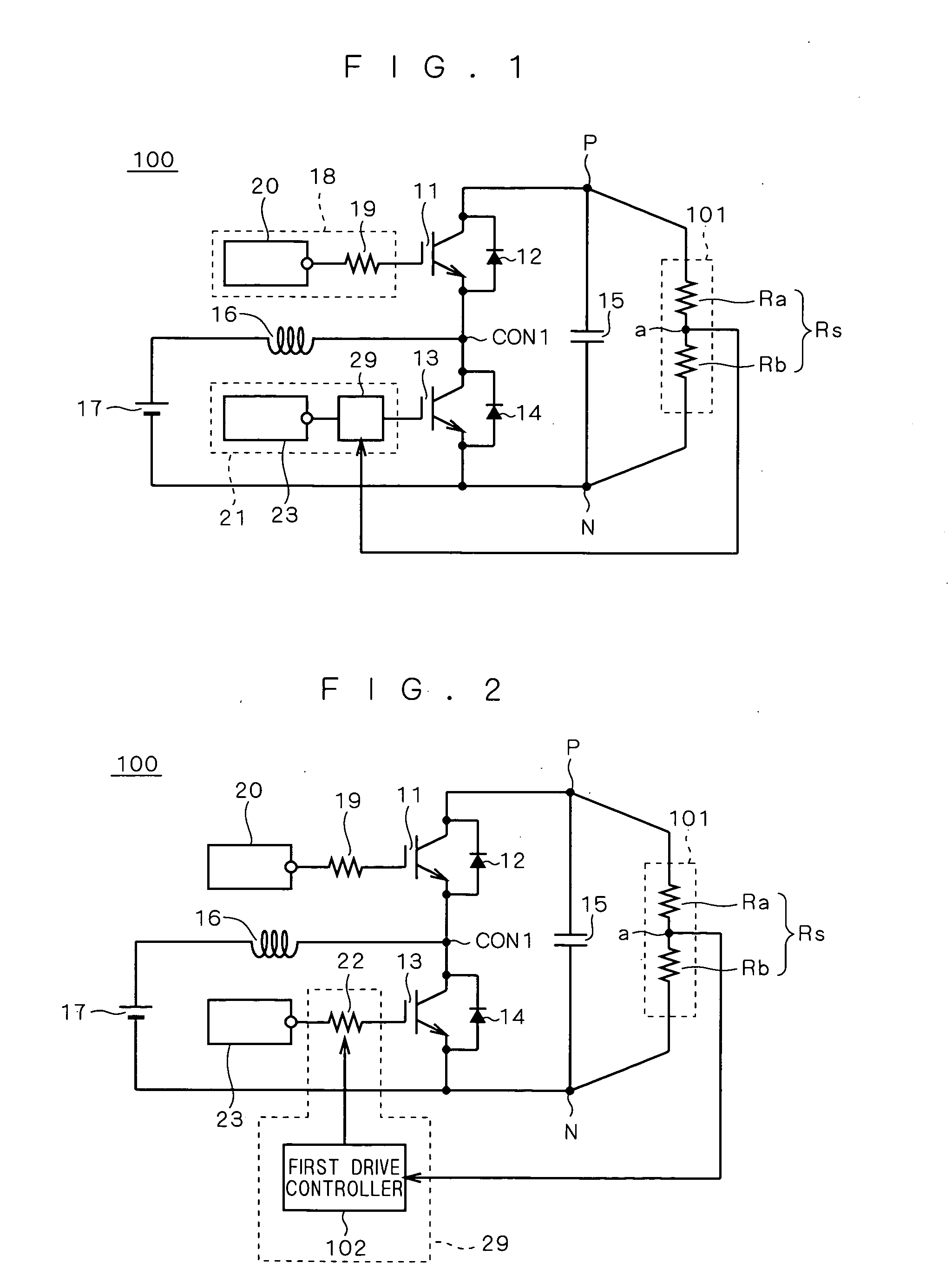

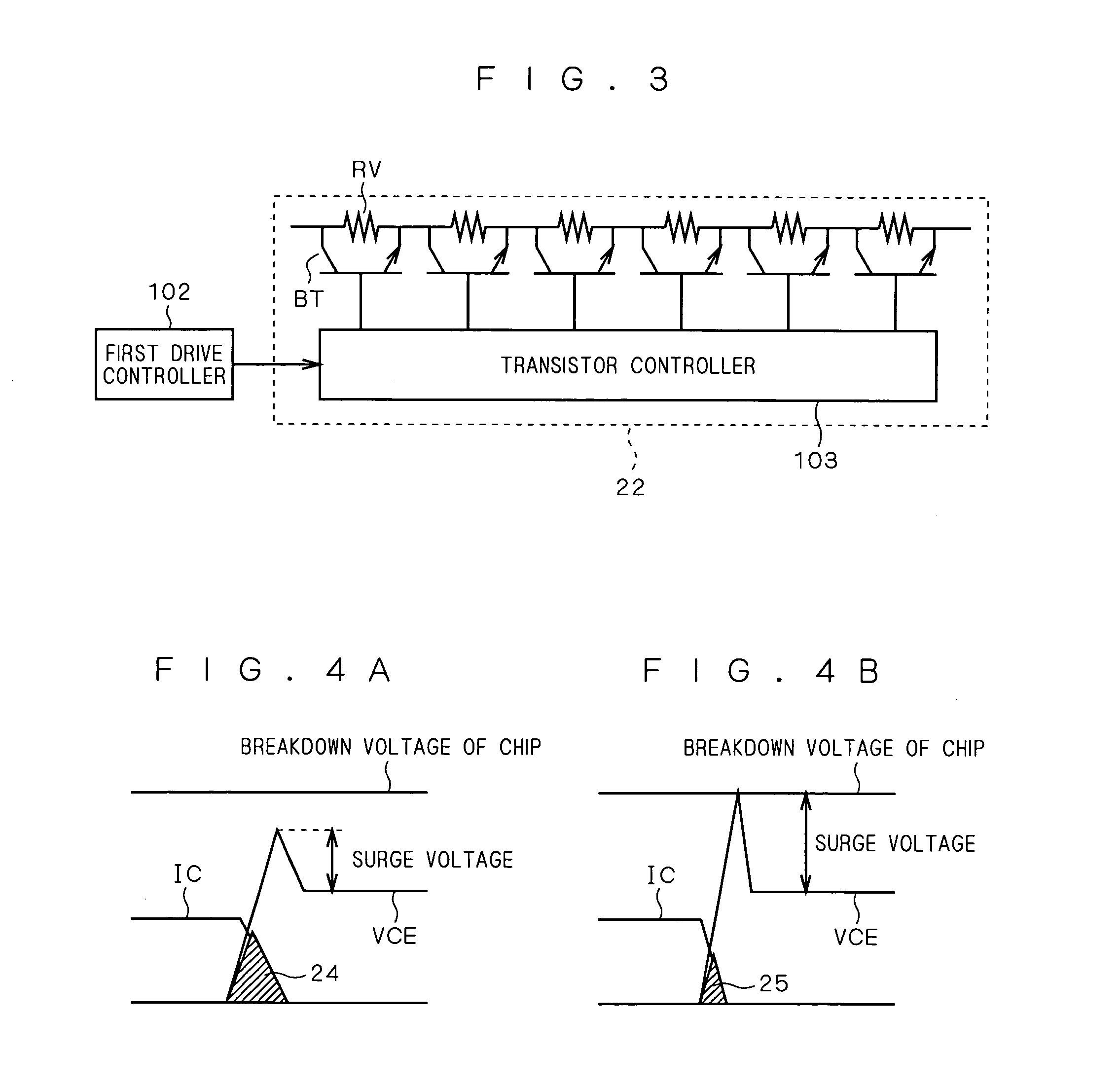

Booster and motor controller

ActiveUS20050146295A1Reduce switching lossesLess switching lossSynchronous motors startersAC motor controlControl signalEngineering

A voltage sensor (101) is connected to output terminals (P, N) of a booster. The voltage sensor (101) detects a boosted voltage, and outputs the detected voltage to a first drive controller (102). The first drive controller (102) outputs a control signal to a variable resistor (22) indicating a gate resistance obtained on the basis of the boosted voltage. The variable resistor (22) is controlled to have the specified gate resistance in response to the received control signal.

Owner:MITSUBISHI ELECTRIC CORP

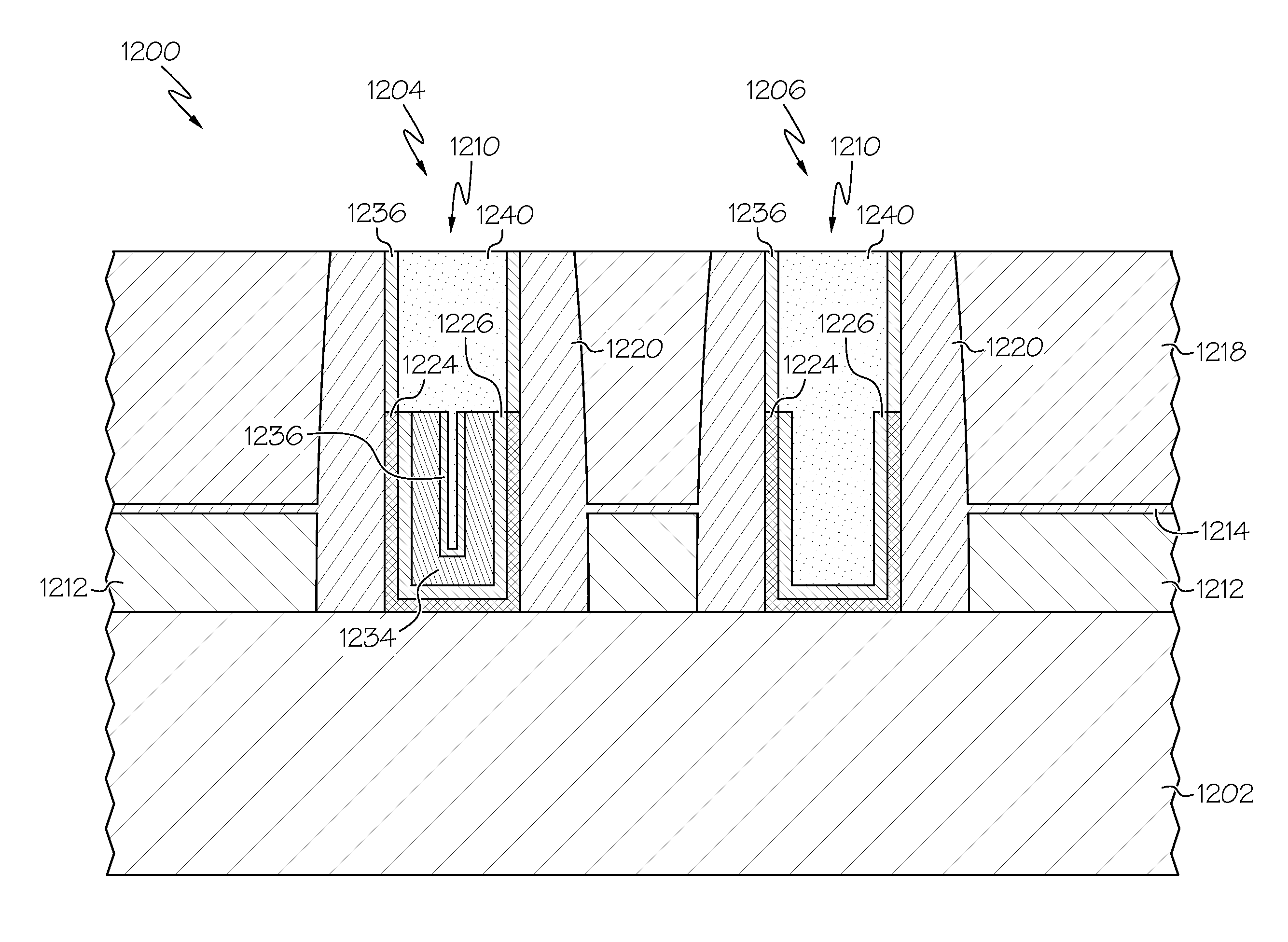

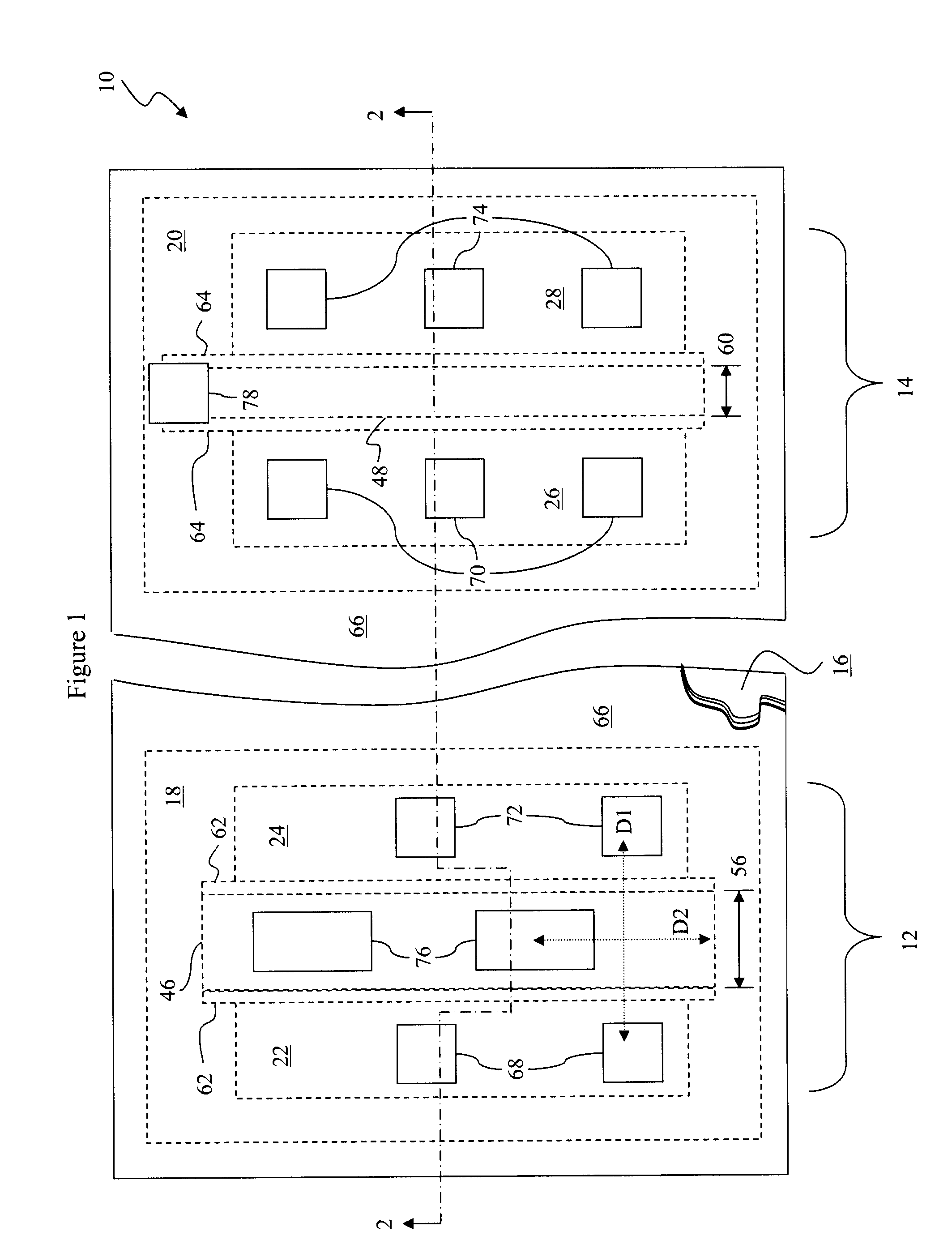

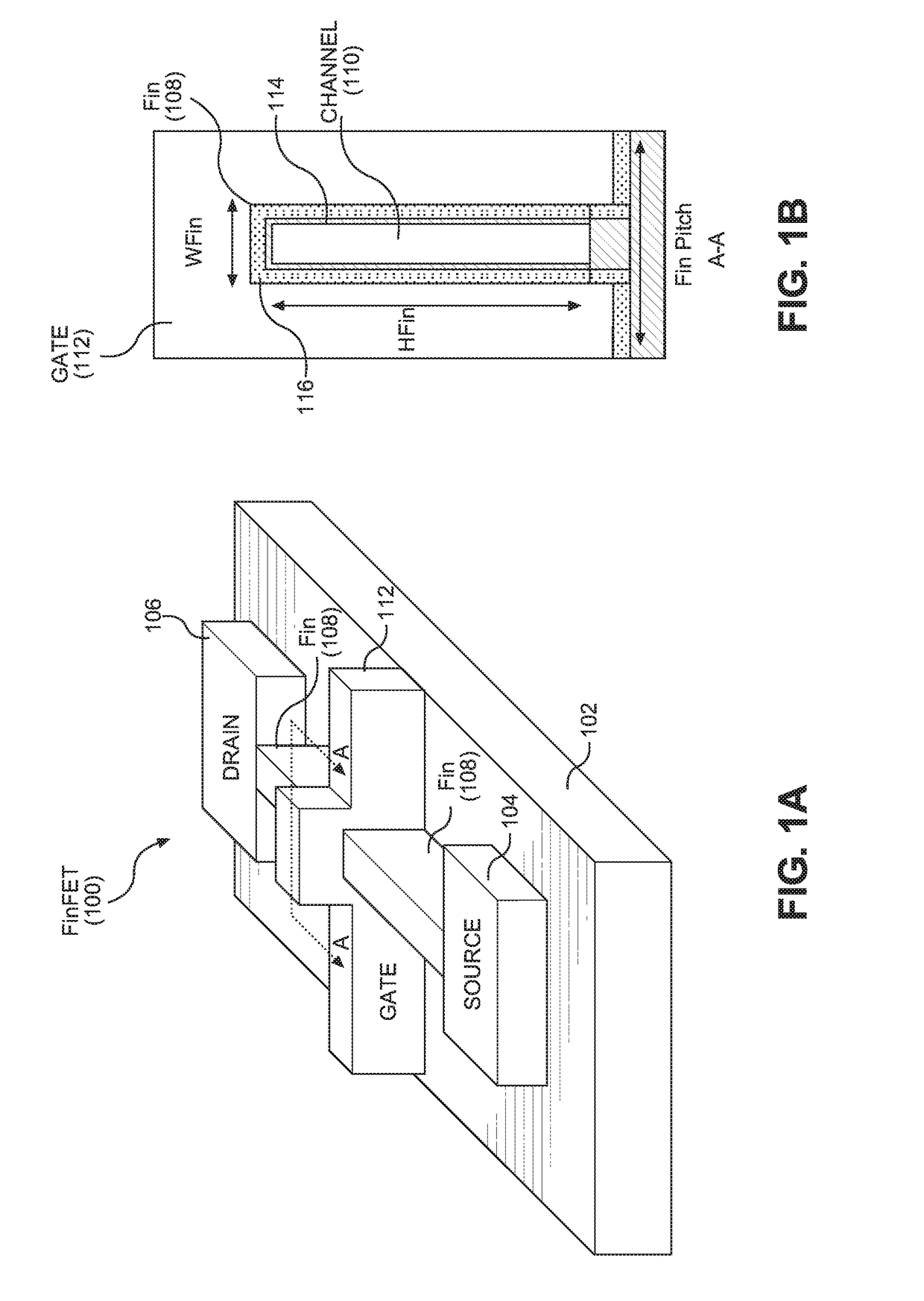

Method and apparatus for reducing gate resistance

An apparatus has a semiconductor device that includes: a semiconductor substrate having a channel region, a high-k dielectric layer disposed at least partly over the channel region, a gate electrode disposed over the dielectric layer and disposed at least partly over the channel region, wherein the gate electrode is made substantially of metal, and a gate contact engaging the gate electrode at a location over the channel region. A different aspect involves a method for making a semiconductor device that includes: providing a semiconductor substrate having a channel region, forming a high-k dielectric layer at least partly over the channel region, forming a gate electrode over the dielectric layer and at least partly over the channel region, the gate electrode being made substantially of metal, and forming a gate contact that engages the gate electrode at a location over the channel region.

Owner:TAIWAN SEMICON MFG CO LTD

Metal gate structure of a field effect transistor and field effect transistor

InactiveCN102104061ALow Gate ResistanceReduce RC delaySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceMetallic materials

The invention relates to integrated circuit fabrication, and more particularly to a Field Effect Transistor with a low resistance metal gate electrode. An exemplary structure for a gate electrode for a Field Effect Transistor comprises a lower portion formed of a first metal material having a recess and a first resistance; and an upper portion formed of a second metal material having a protrusion and a second resistance, wherein the protrusion extends into the recess, wherein the second resistance is lower than the first resistance. The metal gate electrode provided in the invention has a low gate resistance value, so can reduce the capacitance-resistance delay of circuit and improve the performance an apparatus.

Owner:TAIWAN SEMICON MFG CO LTD

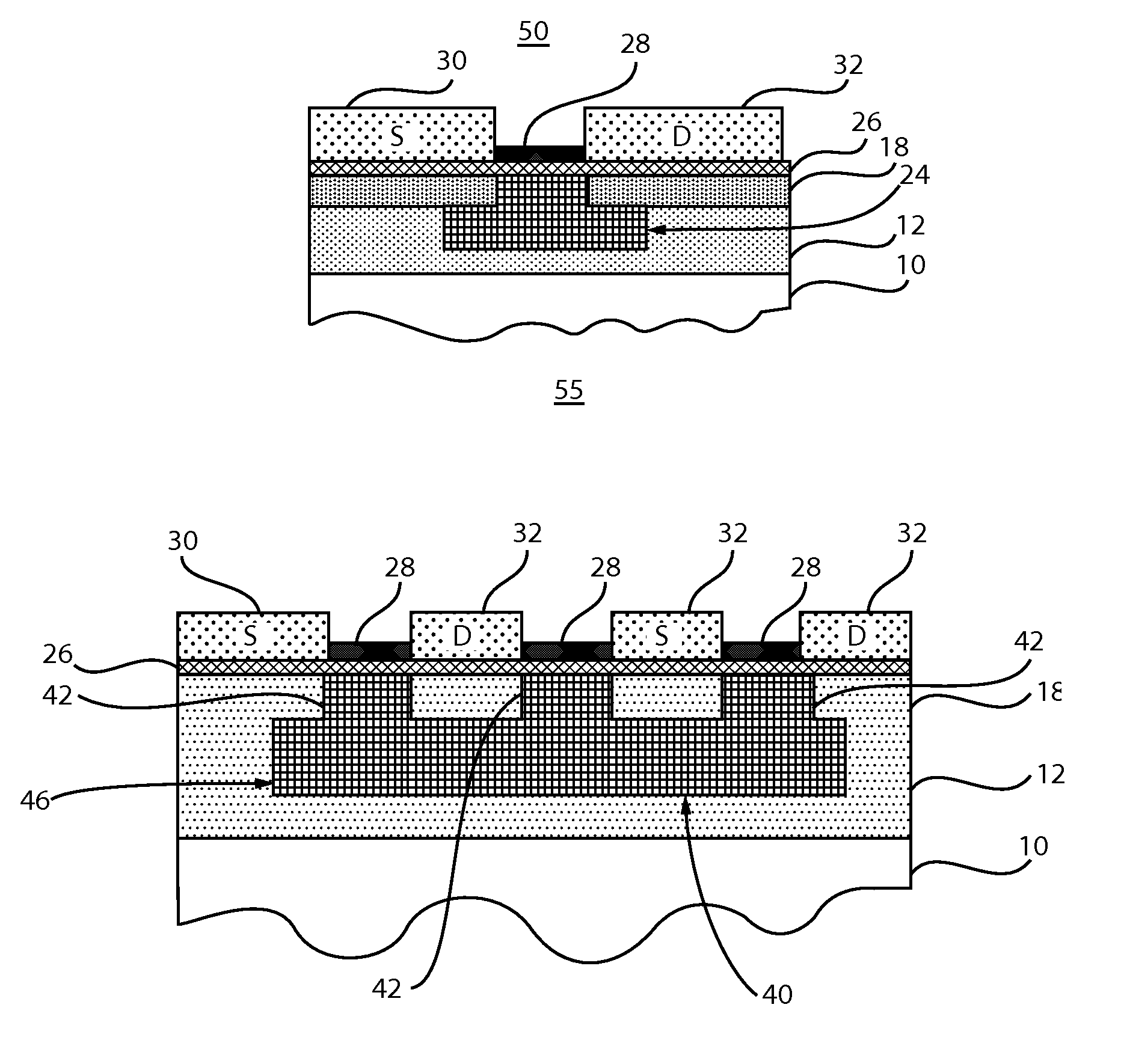

Transistor device with reduced gate resistance

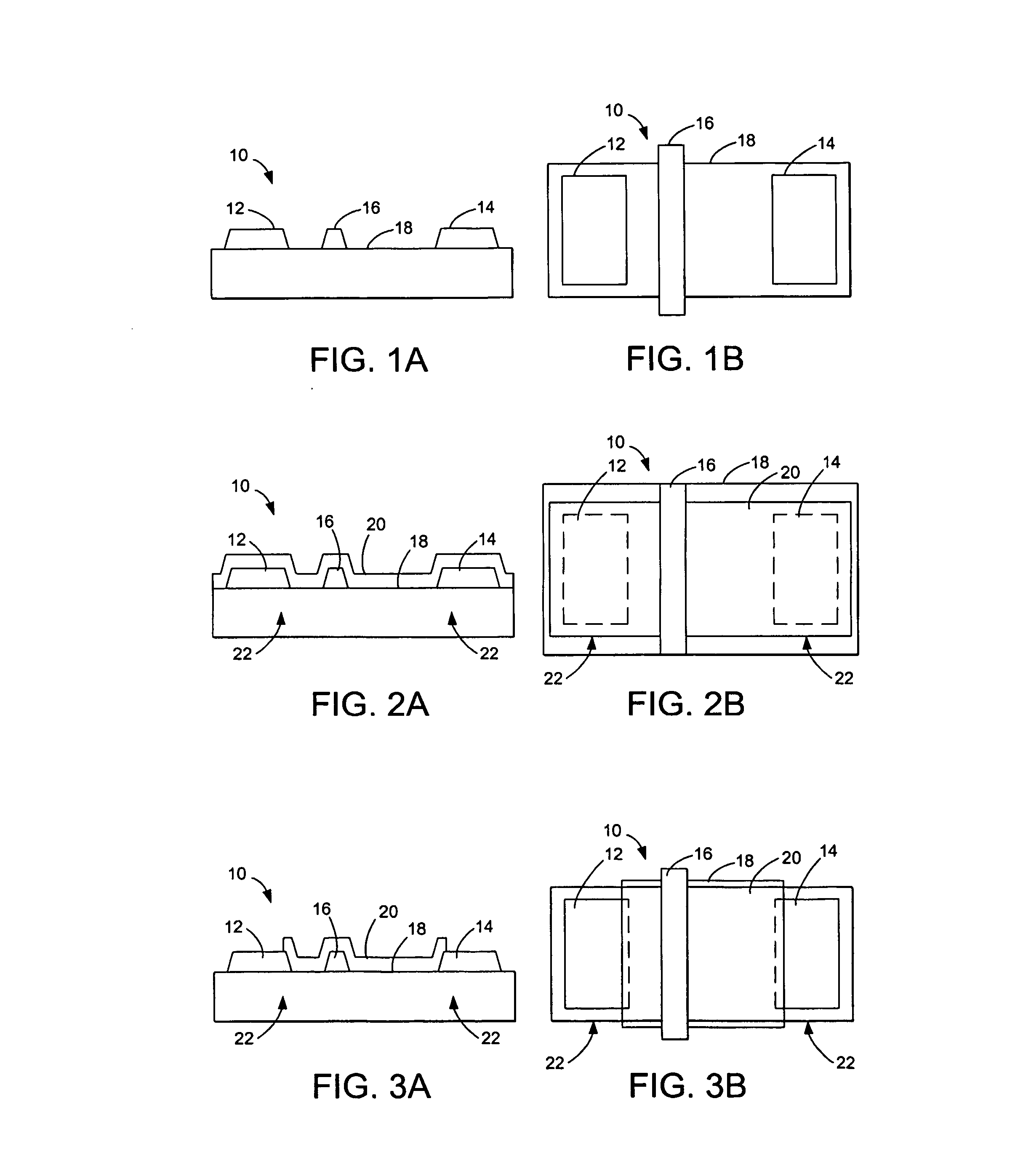

A device with reduced gate resistance includes a gate structure having a first conductive portion and a second conductive portion formed in electrical contact with the first conductive portion and extending laterally beyond the first conductive portion. The gate structure is embedded in a dielectric material and has a gate dielectric on the first conductive portion. A channel layer is provided over the first conductive portion. Source and drain electrodes are formed on opposite end portions of a channel region of the channel layer. Methods for forming a device with reduced gate resistance are also provided.

Owner:INT BUSINESS MASCH CORP

Fabrication of single or multiple gate field plates

ActiveUS20070059873A1Strict controlMaximum performanceSolid-state devicesSemiconductor/solid-state device manufacturingDielectricField effect

A process for fabricating single or multiple gate field plates using consecutive steps of dielectric material deposition / growth, dielectric material etch and metal evaporation on the surface of a field effect transistors. This fabrication process permits a tight control on the field plate operation since dielectric material deposition / growth is typically a well controllable process. Moreover, the dielectric material deposited on the device surface does not need to be removed from the device intrinsic regions: this essentially enables the realization of field-plated devices without the need of low-damage dielectric material dry / wet etches. Using multiple gate field plates also reduces gate resistance by multiple connections, thus improving performances of large periphery and / or sub-micron gate devices.

Owner:RGT UNIV OF CALIFORNIA +1

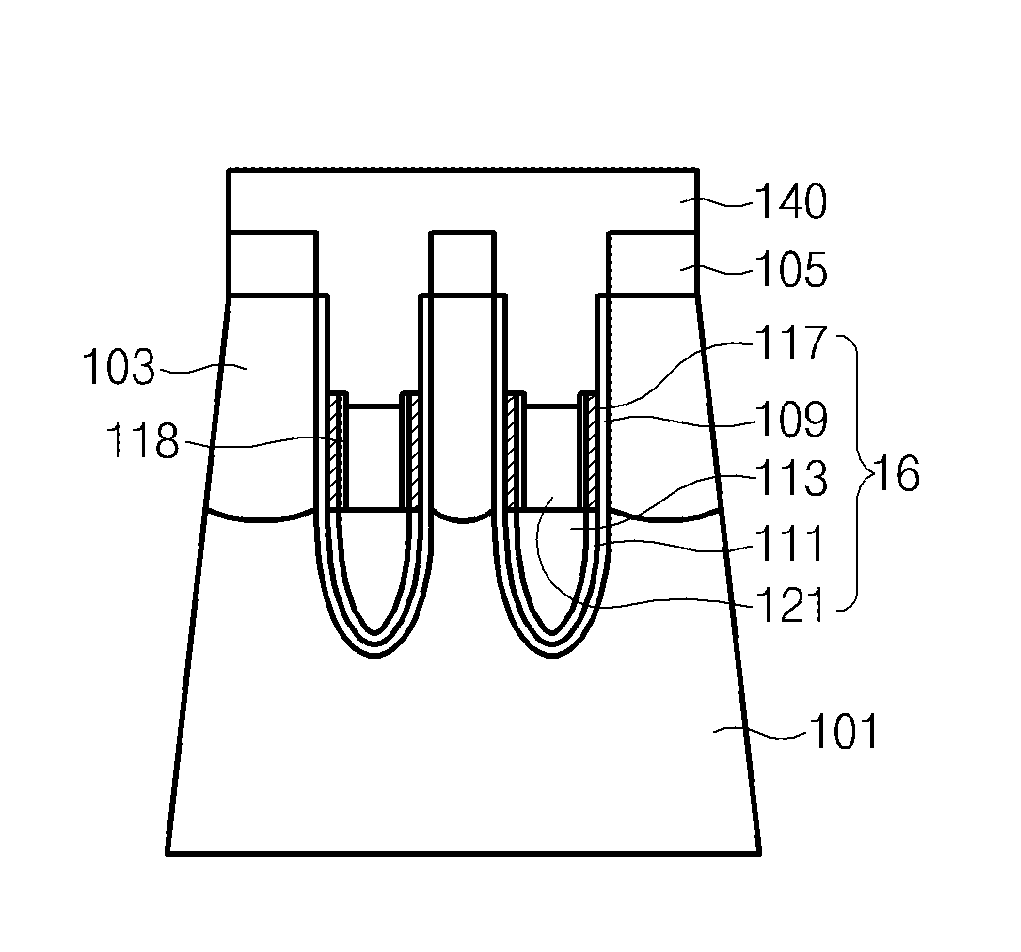

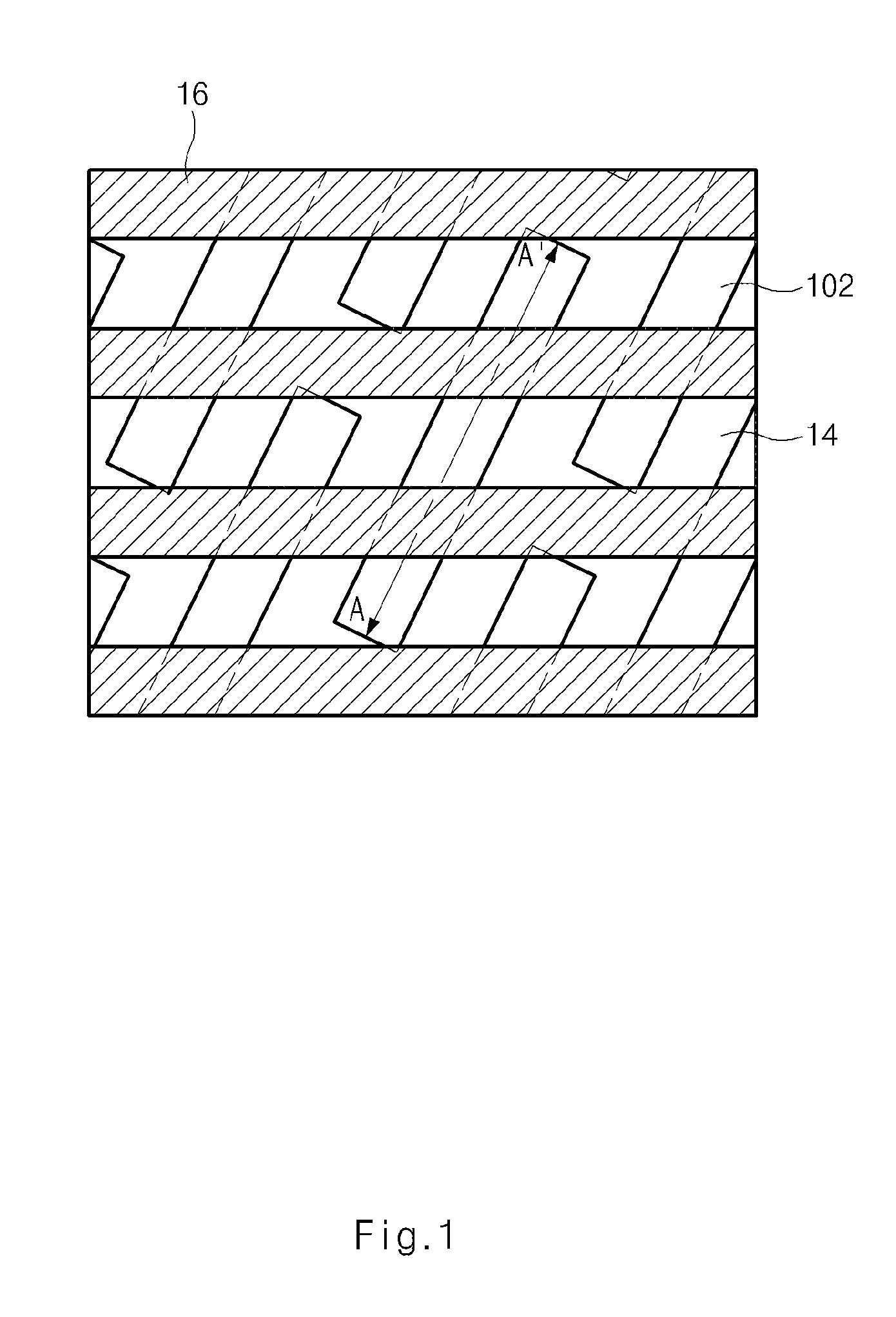

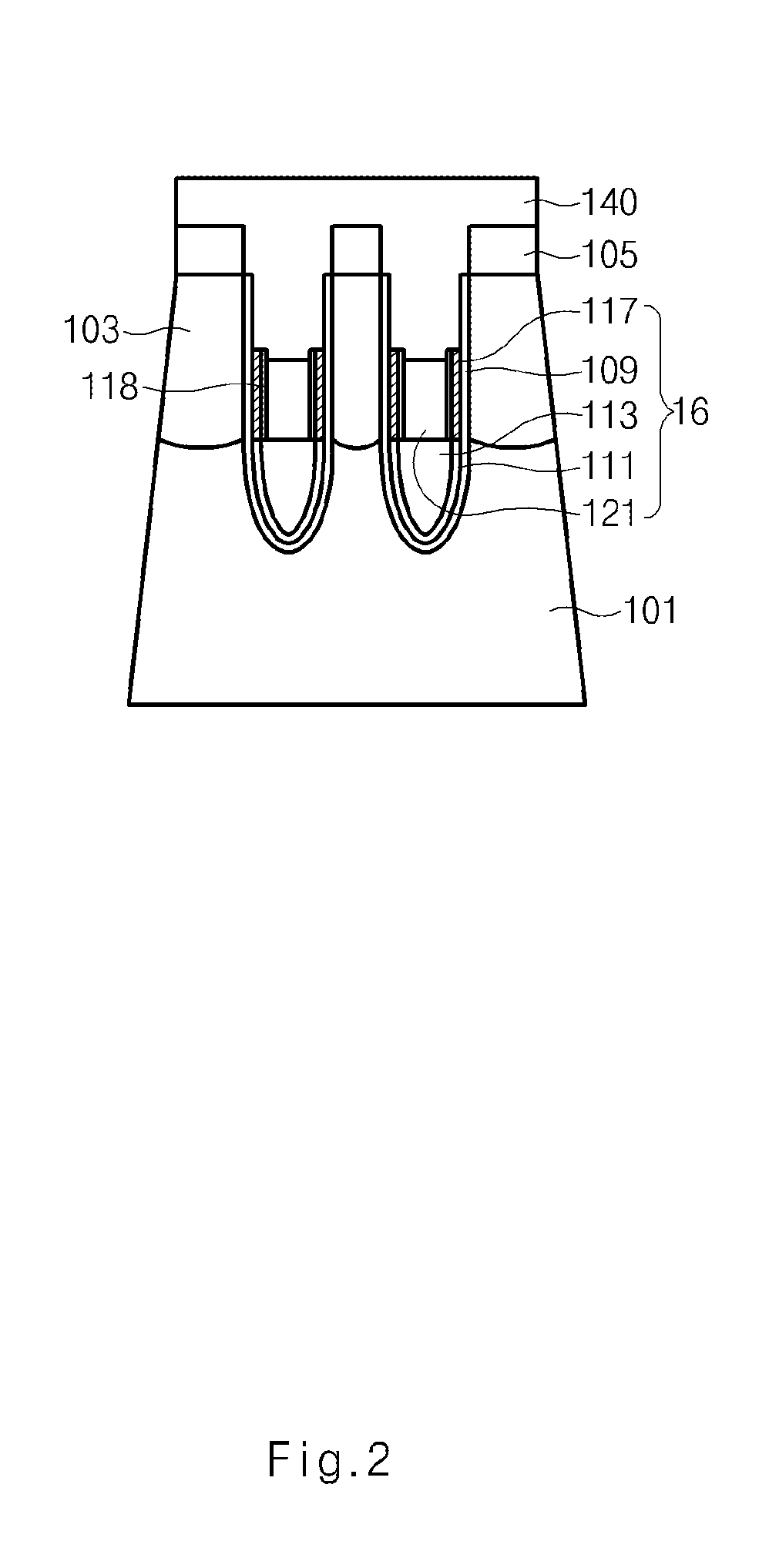

Semiconductor device and method of fabricating the same

ActiveUS20140061781A1Lower gate resistanceImprove GIDLSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

A semiconductor device and a method for manufacturing the same are capable of improving GIDL in a buried gate, and preventing degradation of device characteristics and reliability due to reduction in gate resistance. The semiconductor device may include: junction regions formed at both sidewalls of a trench formed in a semiconductor substrate; a first gate electrode formed in a lower portion of the trench; a second gate electrode formed on at least one inner sidewall of the trench which overlaps one of the junction regions on the first gate electrode; and a third gate electrode formed on one side of the second gate electrode on the first gate electrode.

Owner:SK HYNIX INC

Ultra-thin SOI MOSFET method and structure

InactiveUS7060546B2Minimize gate resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETLithographic artist

Owner:GLOBALFOUNDRIES INC

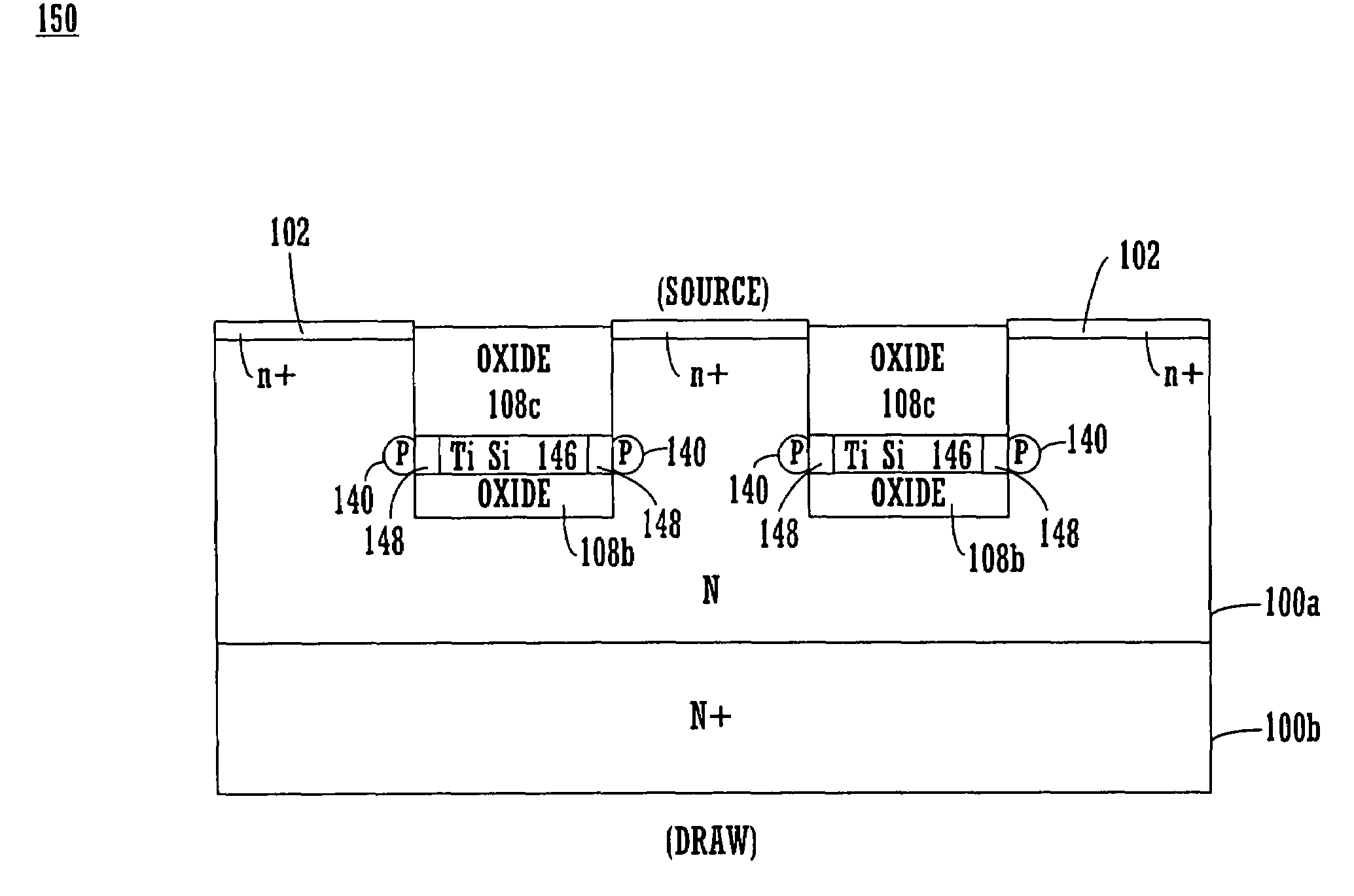

JFET and MESFET structures for low voltage, high current and high frequency applications

InactiveUS6921932B1Easy to controlLower junction capacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceLow voltage

JFET and MESFET structures, and processes of making same, for low voltage, high current and high frequency applications. The structures may be used in normally-on (e.g., depletion mode) or normally-off modes. The structures include an oxide layer positioned under the gate region which effectively reduces the junction capacitance (gate to drain) of the structure. For normally off modes, the structures reduce gate current at Vg in forward bias. In one embodiment, a silicide is positioned in part of the gate to reduce gate resistance. The structures are also characterized in that they have a thin gate due to the dipping of the spacer oxide, which can be below 1000 angstroms and this results in fast switching speeds for high frequency applications.

Owner:POWER INTEGRATIONS INC

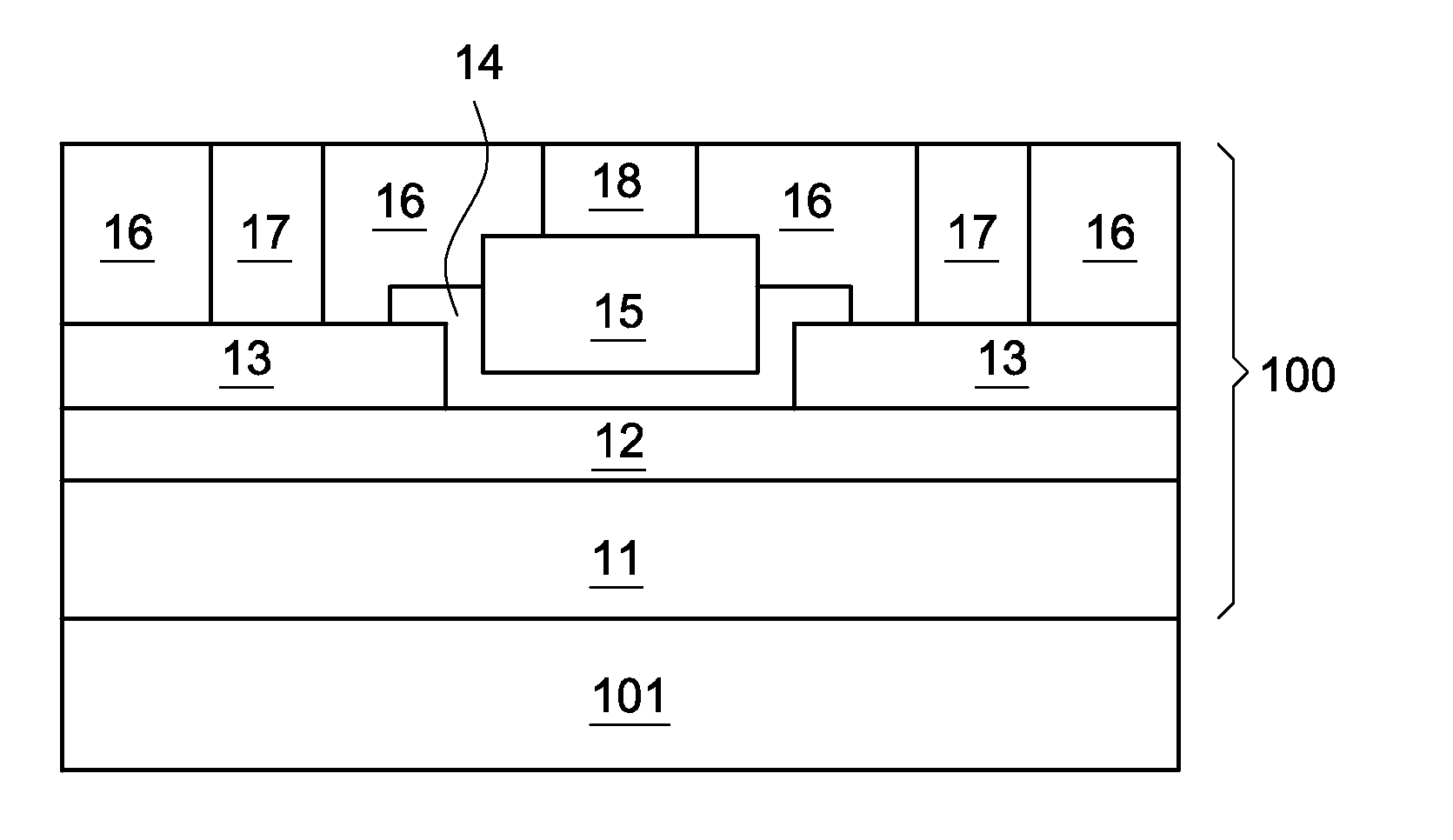

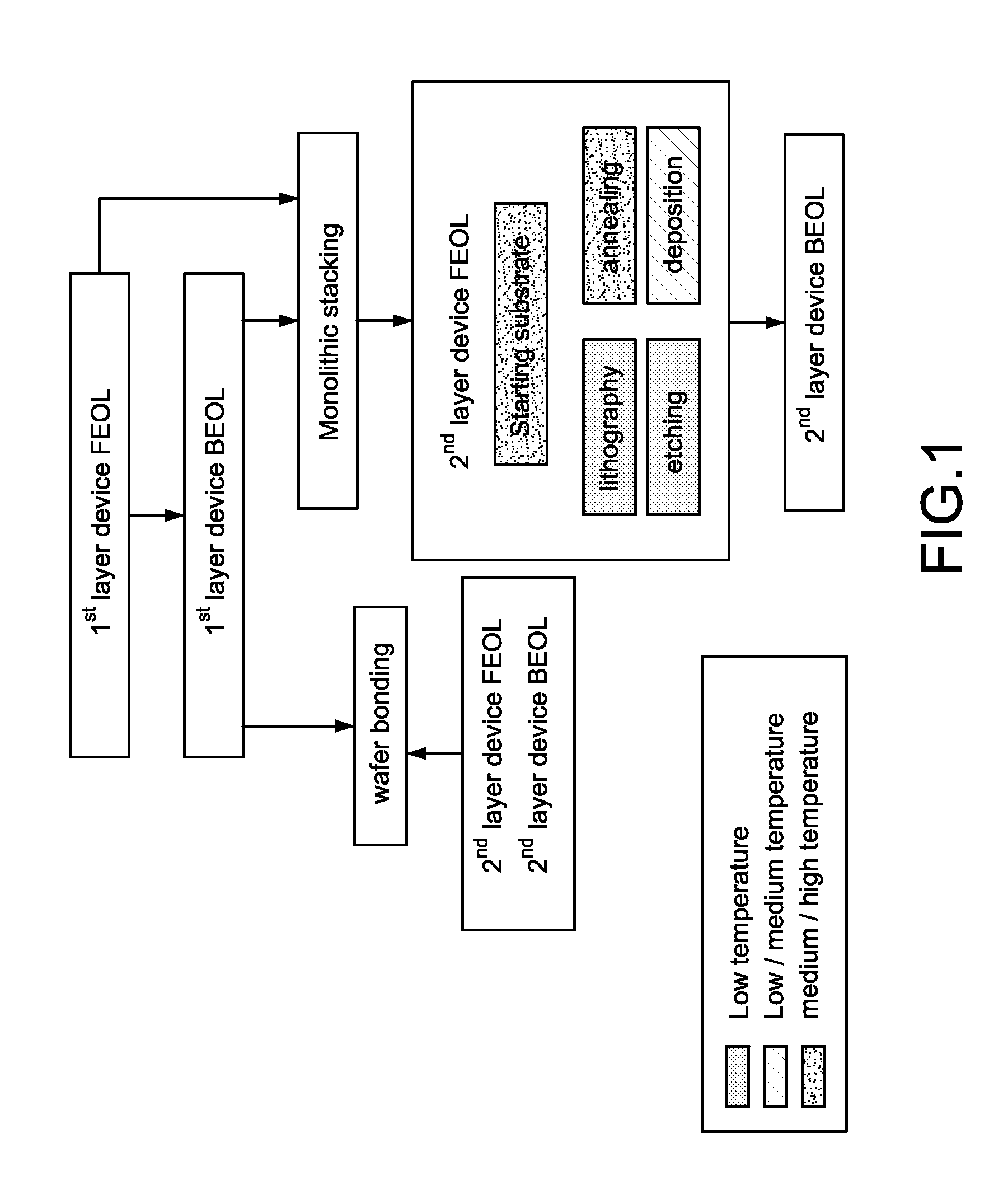

Electrical switch using gated resistor structures and three-dimensional integrated circuits using the same

ActiveUS20120056258A1Low thermal budgetImprove interconnect densityTransistorSolid-state devicesElectrical resistance and conductanceIsolation layer

An electrical switch using a gated resistor structure includes an isolation layer, a doped silicon layer arranged on the isolation layer and having a recessed portion with reduced thickness, the doped silicon layer having a predetermined doping type and a predetermined doping profile; a gate layer arranged corresponding to the recessed portion. The recessed portion in the doped silicon layer has such thickness that a channel defined under the gate can be fully depleted to form a high resistivity region. The recessed channel gated resistor structure can be advantageously used to achieve high interconnect density with low thermal budget for 3D integration.

Owner:CHEN SHU LU

Enhancement-mode field effect transistor based electrostatic discharge protection circuit

ActiveUS7881030B1Maximize linearityMinimizes parasitic capacitanceAntennas earthing switches associationAmplifier protection circuit arrangementsParasitic capacitanceGate voltage

The present invention relates to an electrostatic discharge (ESD) clamp circuit that is used to protect other circuitry from high voltage ESD events. The ESD clamp circuit may include a field effect transistor (FET) element as a clamping element, which is triggered by using a drain-to-gate capacitance, a drain-to-gate resistance, or both of the FET element, and a resistive element as a voltage divider to divide down an ESD voltage to provide a triggering gate voltage of the FET element. In its simplest embodiment, the ESD clamp circuit includes only an FET element and a resistive element. Therefore, the single FET element ESD clamp circuit may be small compared to other ESD protection circuits. The simplicity of the ESD clamp circuit may minimize parasitic capacitances, thereby maximizing linearity of the ESD clamp circuit over a wide frequency range.

Owner:QORVO US INC

Transistor device with reduced gate resistance

InactiveUS20130082242A1Solid-state devicesSemiconductor/solid-state device manufacturingGate dielectricEngineering

A device with reduced gate resistance includes a gate structure having a first conductive portion and a second conductive portion formed in electrical contact with the first conductive portion and extending laterally beyond the first conductive portion. The gate structure is embedded in a dielectric material and has a gate dielectric on the first conductive portion. A channel layer is provided over the first conductive portion. Source and drain electrodes are formed on opposite end portions of a channel region of the channel layer. Methods for forming a device with reduced gate resistance are also provided.

Owner:IBM CORP

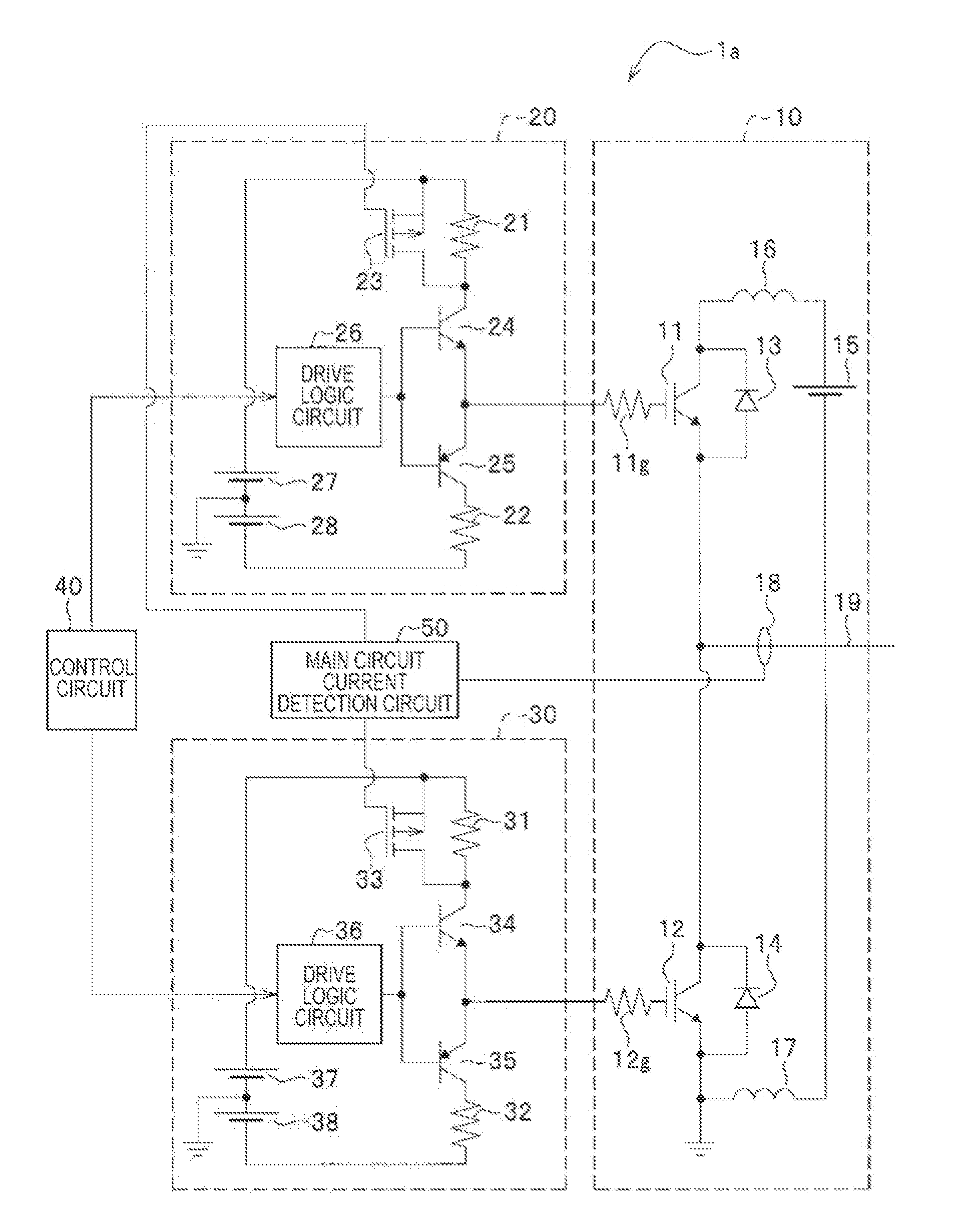

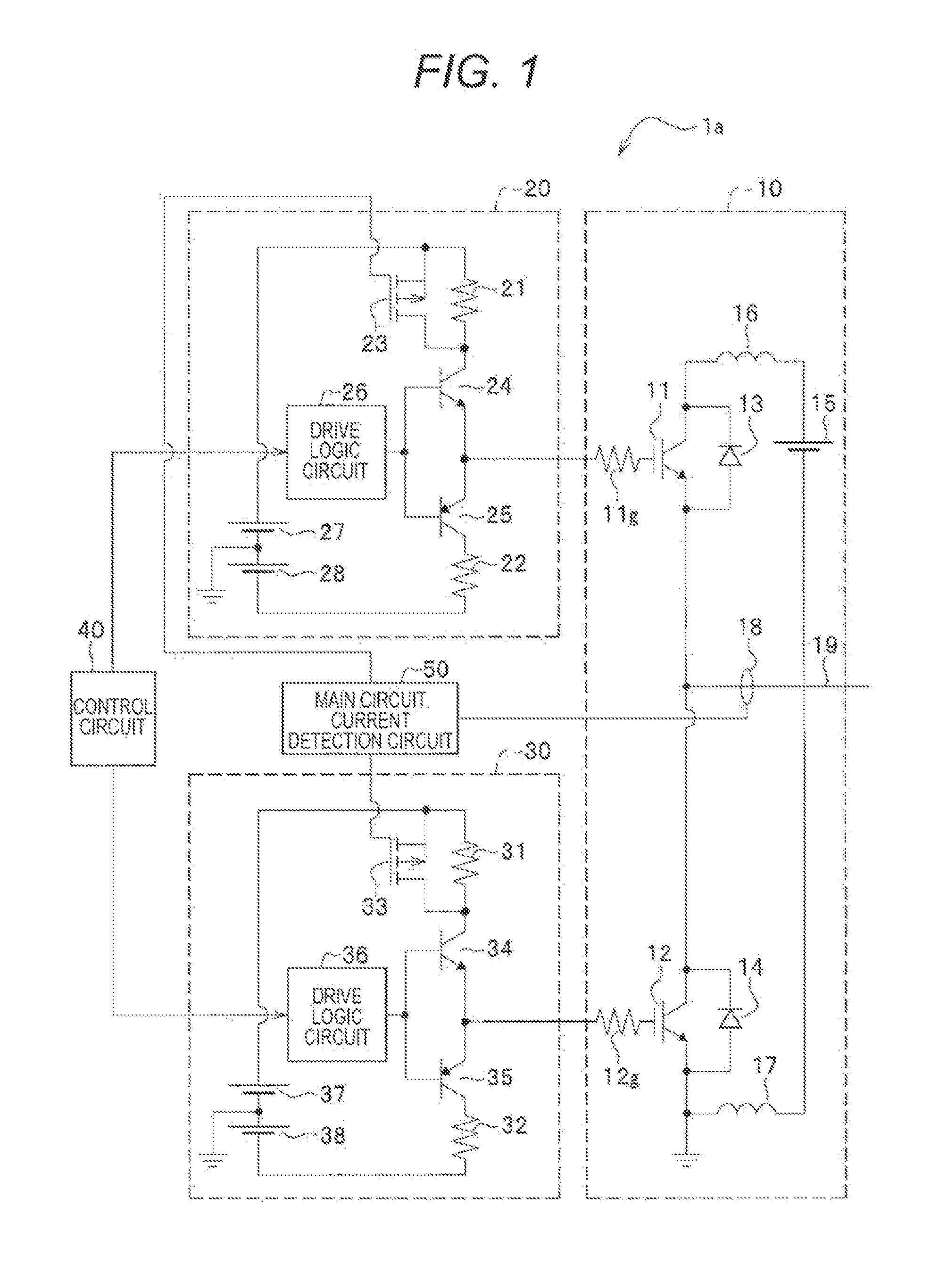

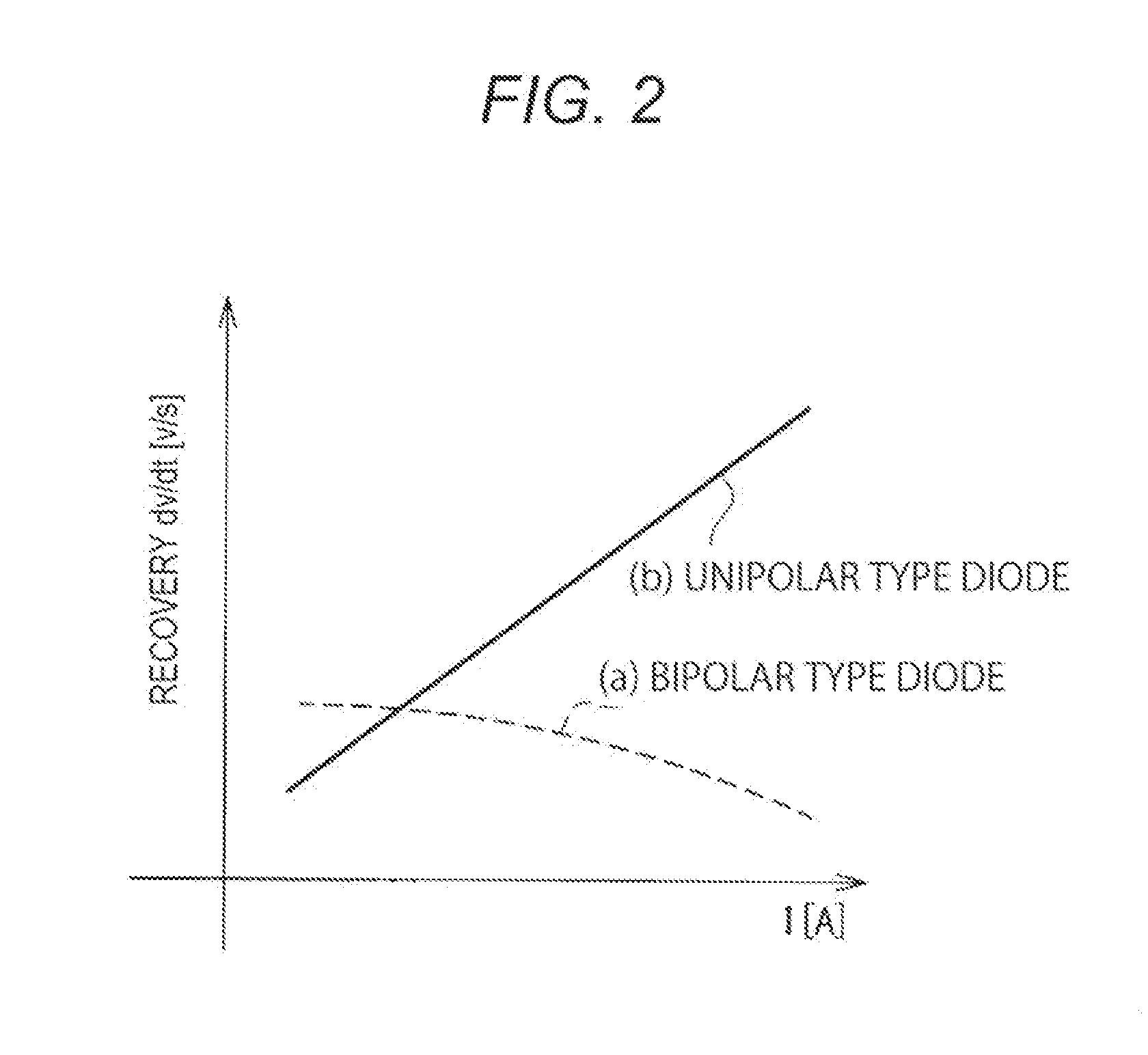

Inverter Device

InactiveUS20140334214A1Suppress ringingEfficient power electronics conversionAc-dc conversionPower inverterElectrical resistance and conductance

In a switching circuit in which a power semiconductor switching element and a unipolar type diode are connected in parallel, the noise due to ringing is reduced. When the main circuit current flowing is equal to or less than a predetermined value, an Si-IGBT is switched and driven by a gate resistance. In this case, when the main circuit current detected is equal to or more than a threshold value, a main circuit current detection circuit changes a gate resistance switching pMOS from ON state to OFF state. Accordingly, the Si-IGBT operates with a summation of a gate resistance and a gate resistor. More specifically, a gate resistance value of a gate drive circuit of the Si-IGBT increases. Therefore, dv / dt of the collector-emitter voltage of the Si-IGBT, i.e., the recovery dv / dt of the unipolar type diode, is small, and therefore, the noise due to ringing can be reduced.

Owner:HITACHI LTD

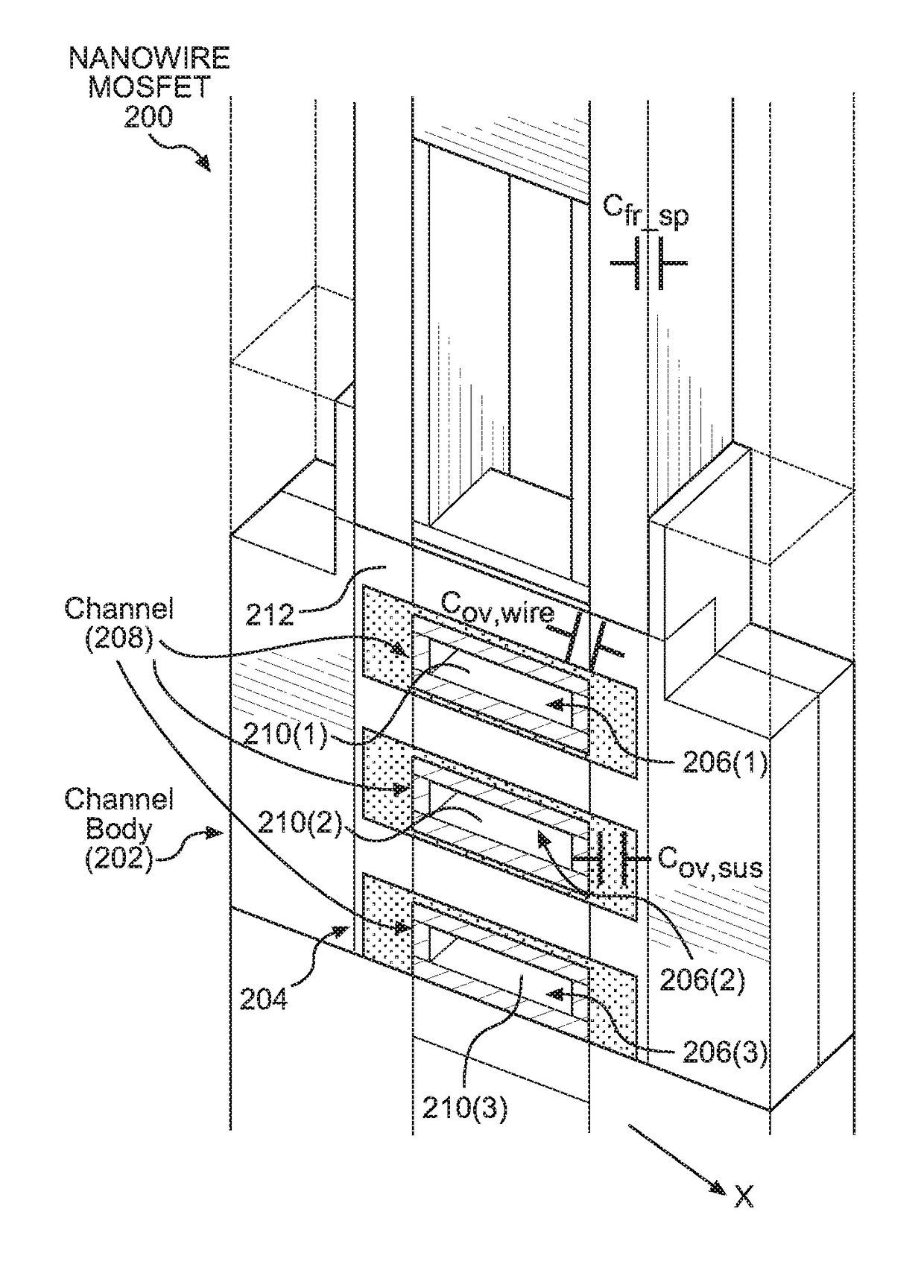

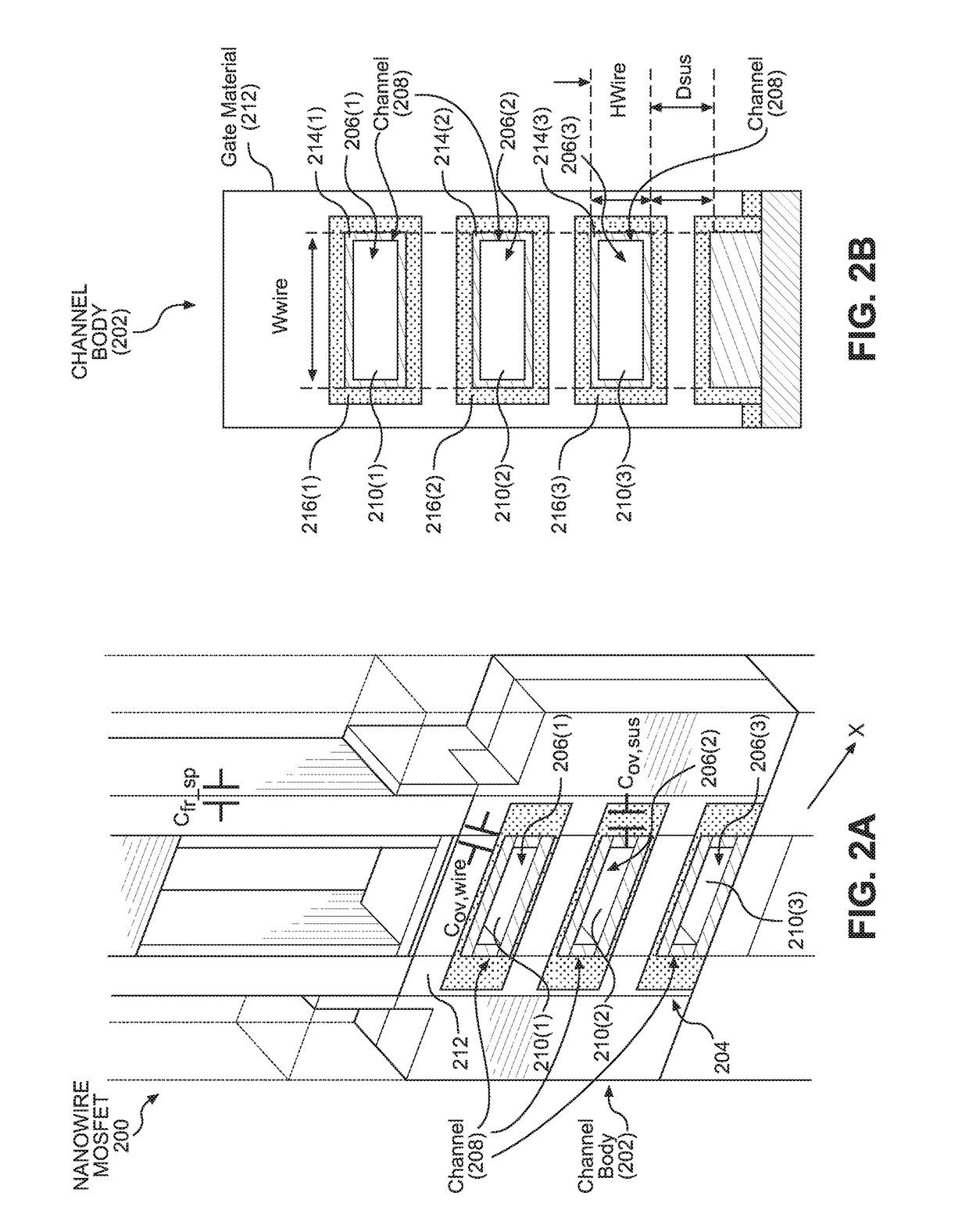

NANOWIRE METAL-OXIDE SEMICONDUCTOR (MOS) FIELD-EFFECT TRANSISTORS (FETs) (MOSFETs) EMPLOYING A NANOWIRE CHANNEL STRUCTURE EMPLOYING RECESSED CONDUCTIVE STRUCTURES FOR CONDUCTIVELY COUPLING NANOWIRE STRUCTURES

InactiveUS20170207313A1Increase widthIncrease channel current densitySemiconductor devicesMOSFETNanowire

Nanowire metal-oxide semiconductor (MOS) Field-Effect Transistors (FETs) (MOSFETs) employing a nanowire channel structure employing recessed conductive structures for conductively coupling nanowire structures are disclosed. Conductive structures are disposed between adjacent nanowire structures to conductively couple nanowire structures. Providing conductive structures in the nanowire channel structure increases the average cross-sectional area of nanowire structures, as compared to a similar nanowire channel structure not employing conductive structures, thus increasing effective channel width and drive strength for a given channel structure height. The precision of a gate material filling process is also eased, because gate material does not have to be disposed in areas between adjacent nanowire structures occupied by conductive structures. The conductive structure width can also be recessed with regard to width of nanowire structures in the nanowire channel structure to allow for a thicker metal gate to lower the gate resistance, while providing excellent electrostatic gate control of the channel.

Owner:QUALCOMM INC

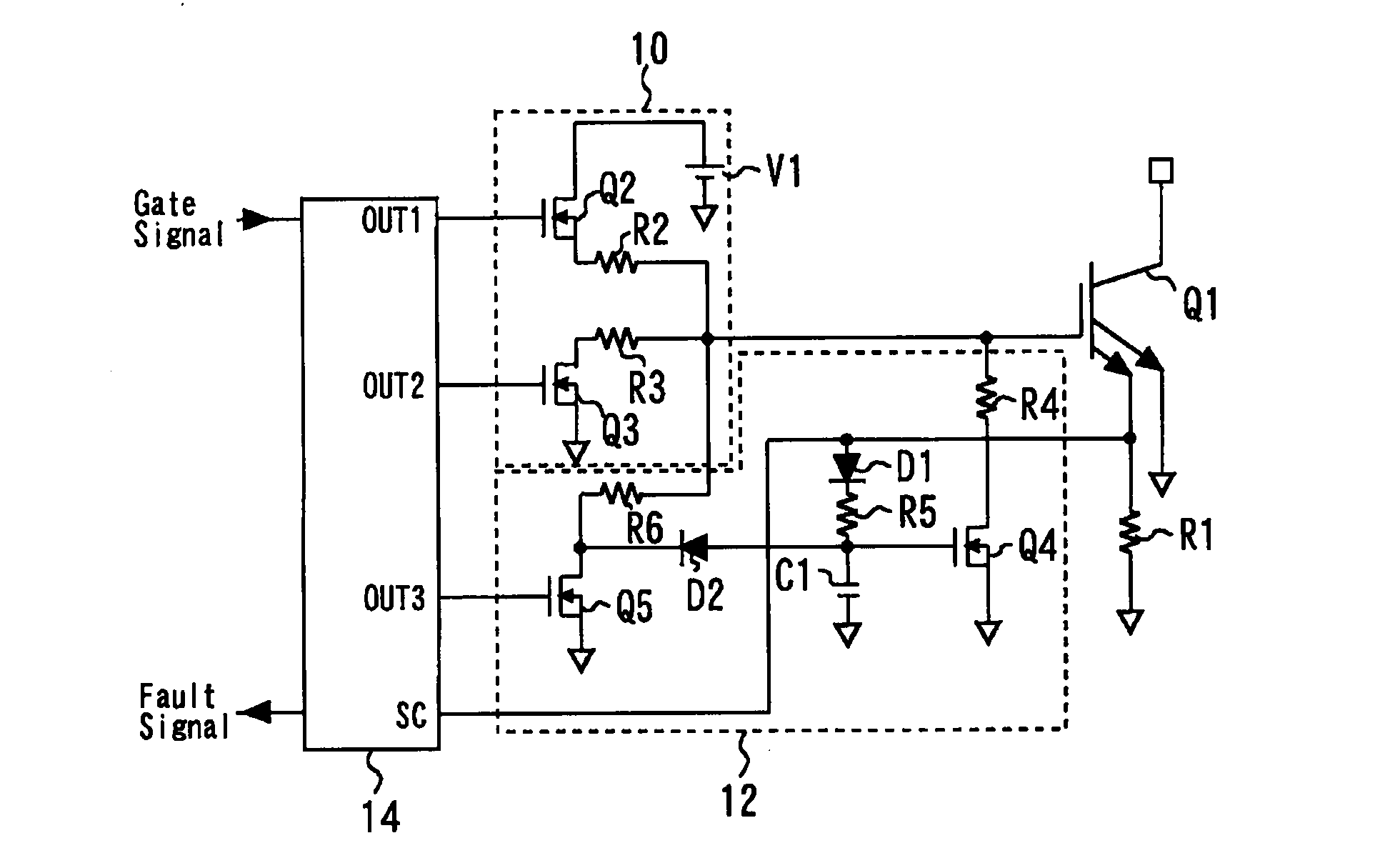

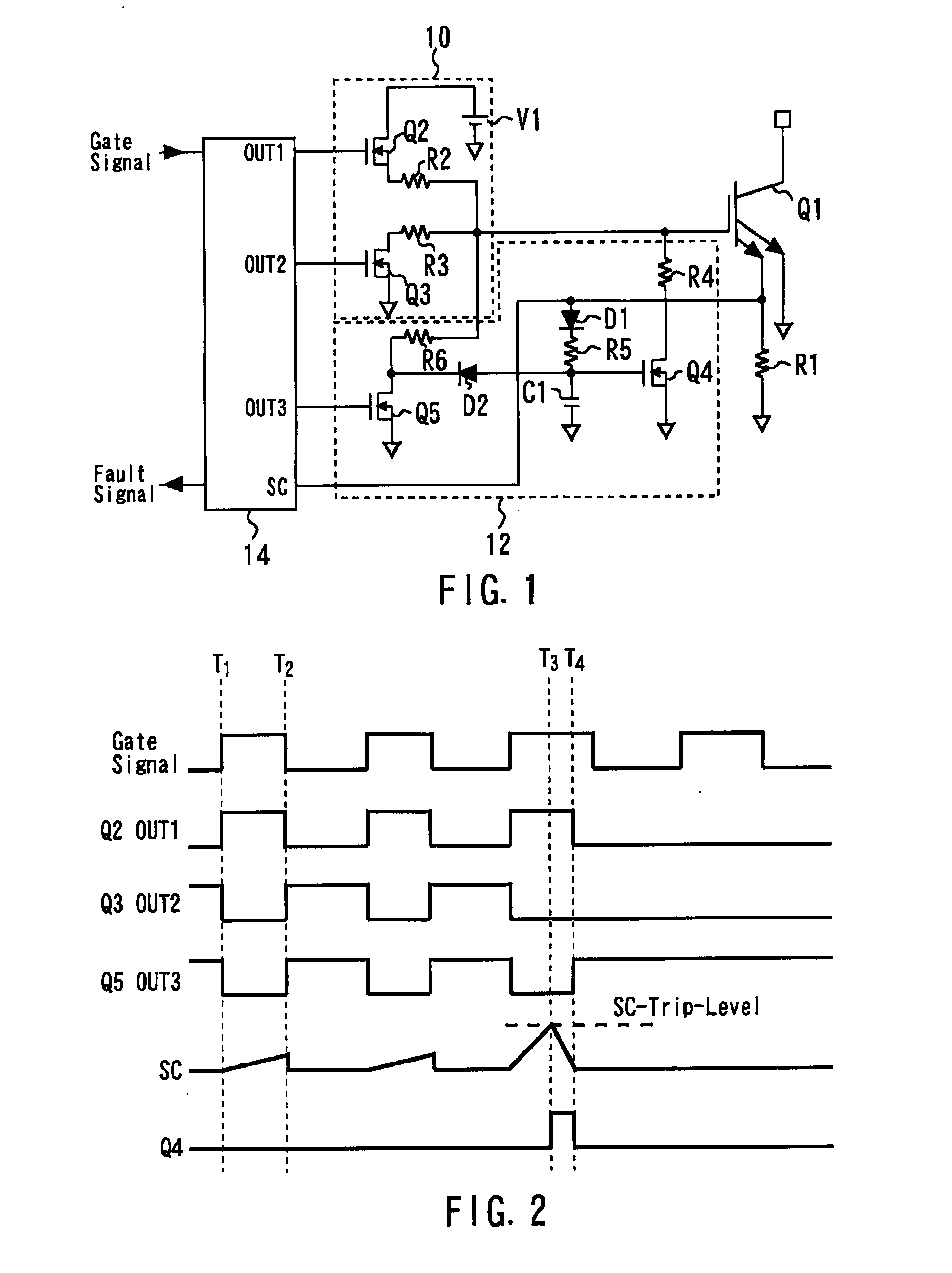

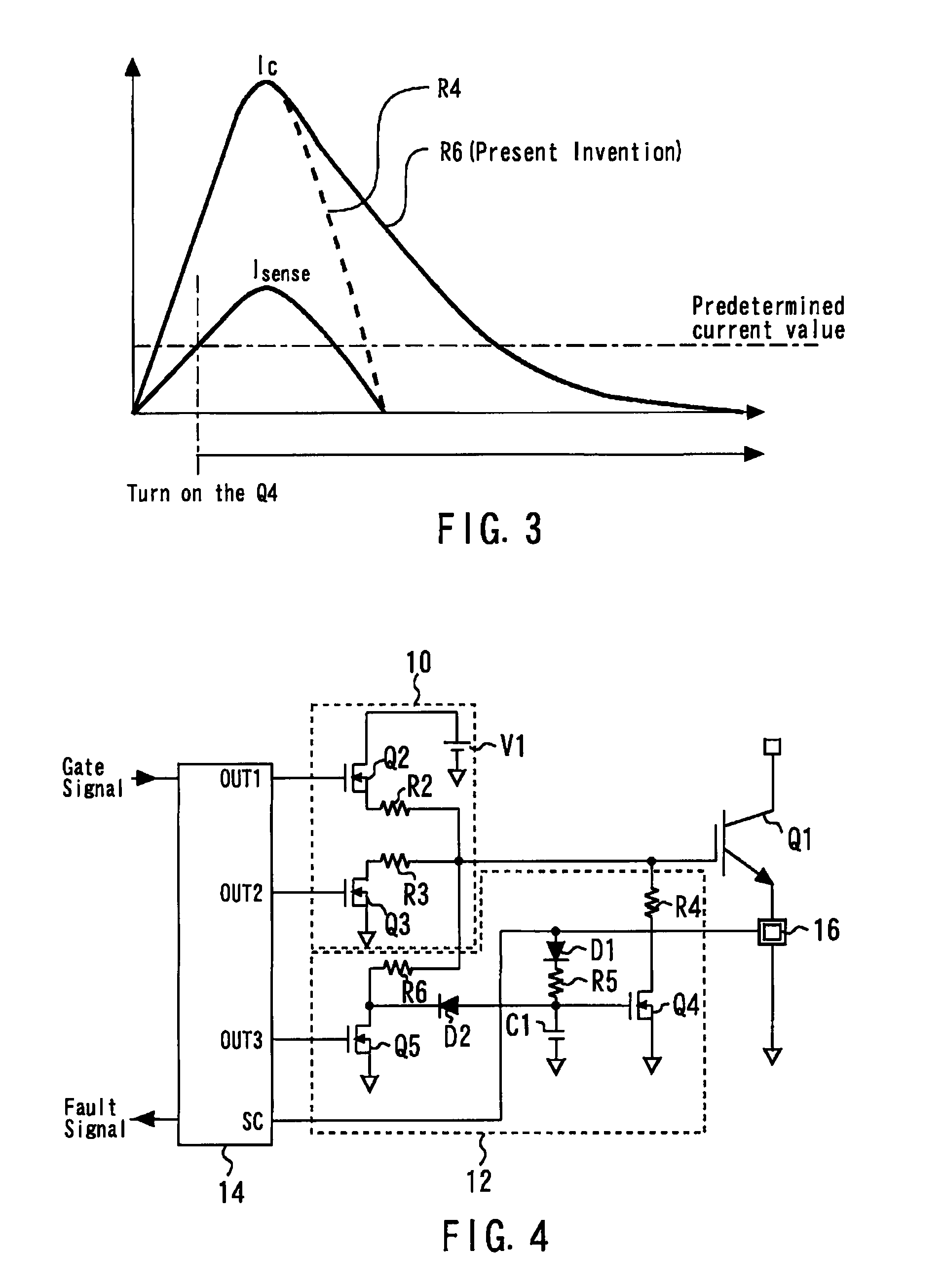

Gate circuit

ActiveUS20120229942A1More flowRate of decrease is very slowElectronic switchingEmergency protective arrangements for limiting excess voltage/currentHigh resistancePower flow

A gate circuit includes a gate resistive element connected at one end to the gate of a power device, an on-switching device connected between a power supply and the other end of the gate resistive element, a first resistive element whose connection to the gate is controlled by a first switching device, a second resistive element whose connection to the gate is controlled by a second switching device, and having a higher resistance value than the first resistive element, excessive current suppression means for turning on the first switching device just when the current in the power device reaches a predetermined value, and turn-off delay means for, after the excessive current suppression means turns on the first switching device, turning off the on-switching device and the first switching device and turning on the second switching device to turn off the power device.

Owner:MITSUBISHI ELECTRIC CORP

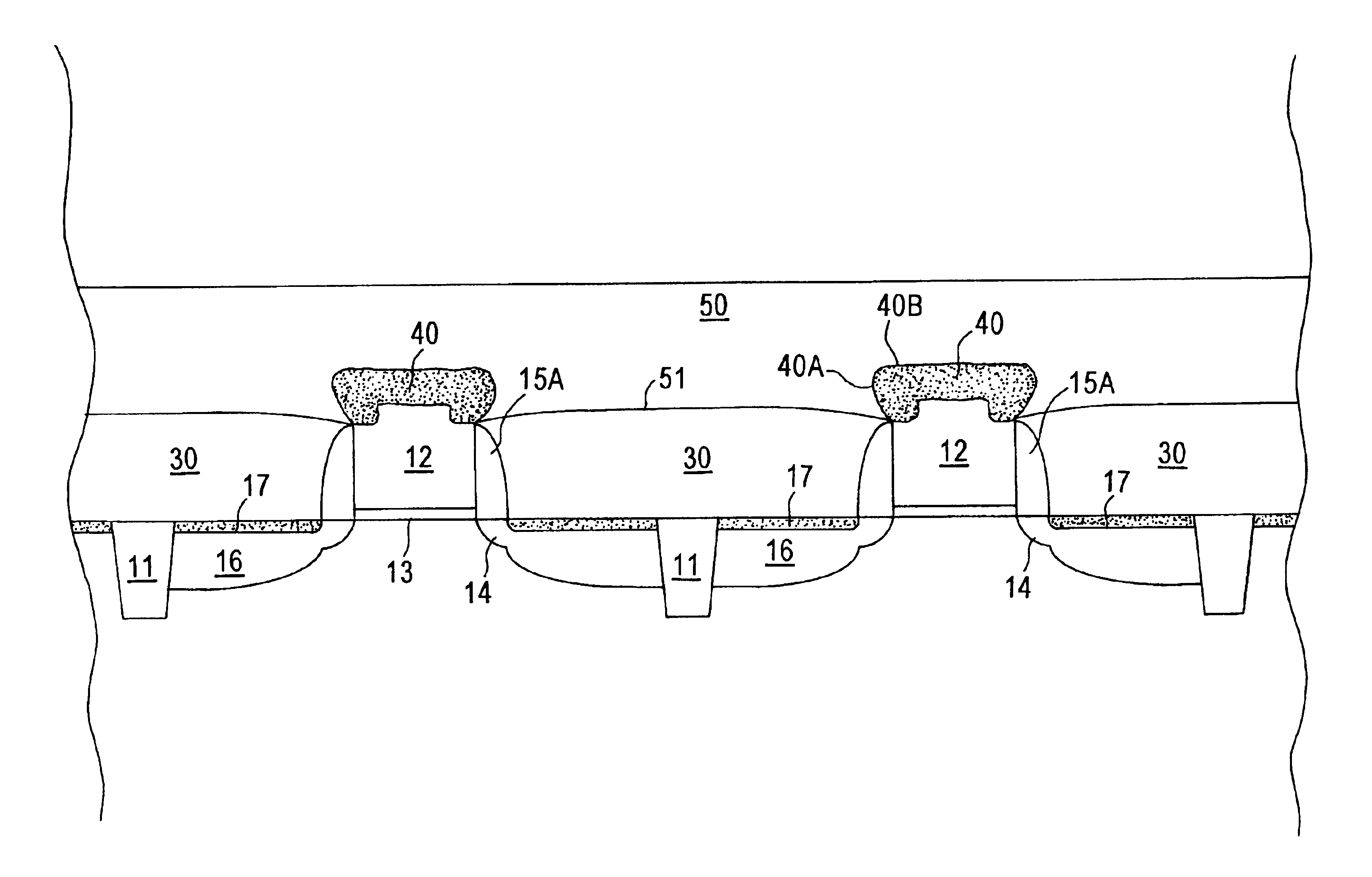

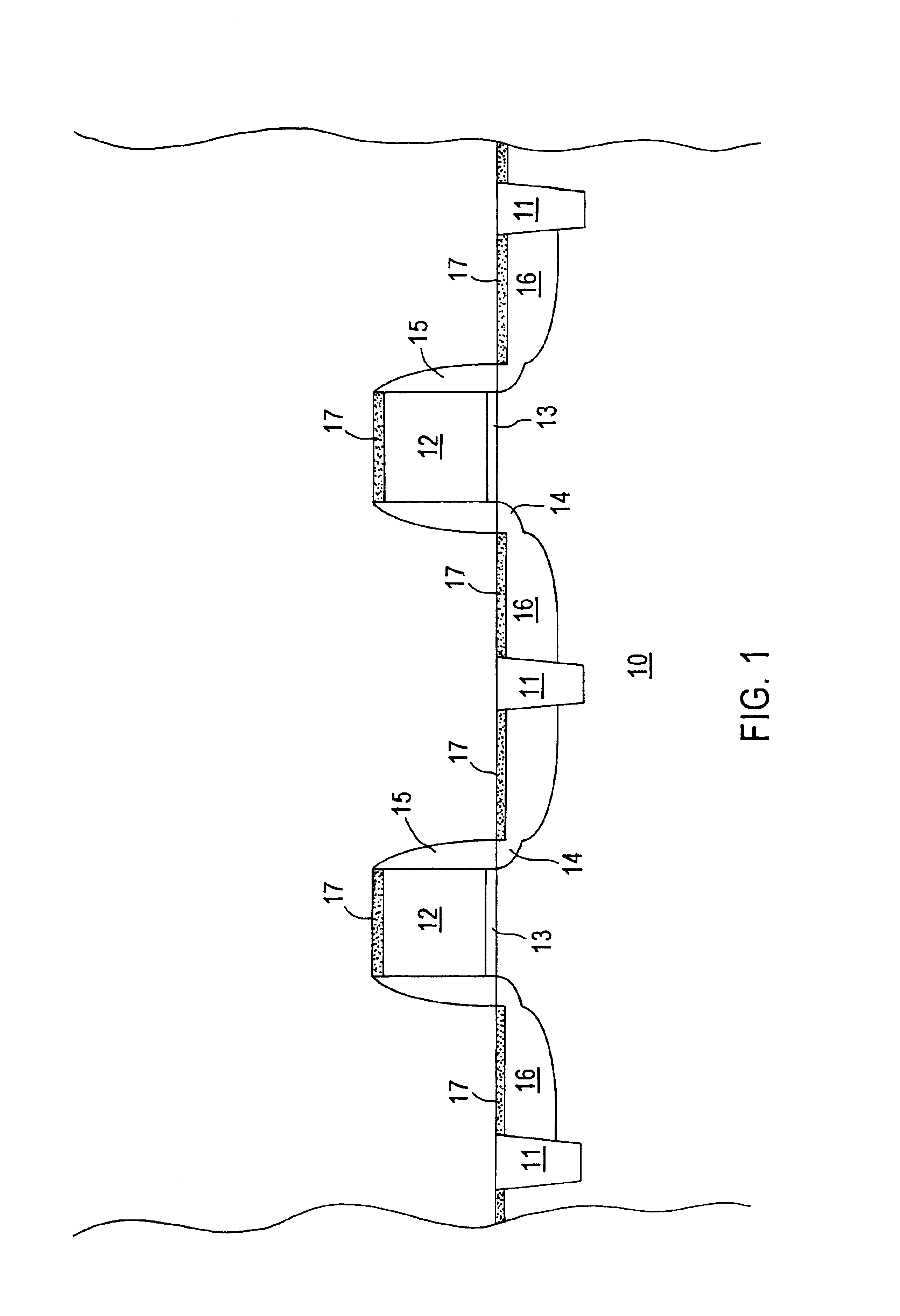

Transistor having reduced gate resistance and enhanced stress transfer efficiency and method of forming the same

InactiveUS20090001479A1High carrier mobilityImprove controllabilityTransistorSemiconductor/solid-state device manufacturingEngineeringTransfer mechanism

By removing an upper portion of a complex spacer structure, such as a triple spacer structure, an upper surface of an intermediate spacer element may be exposed, thereby enabling the removal of the outermost spacer and a material reduction of the intermediate spacer in a well-controllable common etch process. Consequently, sidewall portions of the gate electrode may be efficiently exposed for a subsequent silicidation process, while the residual reduced spacer provides sufficient process margins. Thereafter, highly stressed material may be deposited, thereby providing an enhanced stress transfer mechanism.

Owner:ADVANCED MICRO DEVICES INC

Drive circuit of semiconductor device

InactiveUS20100265746A1Reduce power lossLoss and noiseAc-dc conversionElectronic switchingPower semiconductor deviceEngineering

The invention provides a switching circuit of a power semiconductor device having connected in parallel SiC diodes with a small recovery current, capable of significantly reducing turn-on loss and recovery loss without increasing the noise in the MHz band, and contributing to reducing the loss and noise of inverters. The present invention provides a switching circuit and an inverter circuit of a power semiconductor device comprising a module combining Si-IGBT and SiC diodes, wherein an on-gate resistance is set smaller than an off-gate resistance.

Owner:HITACHI LTD