Tunneling transistor structure and manufacturing method thereof

A technique for tunneling transistors and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, diodes, semiconductor devices, etc., and can solve problems such as increasing the tunneling area and not increasing the on-state current of the device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention.

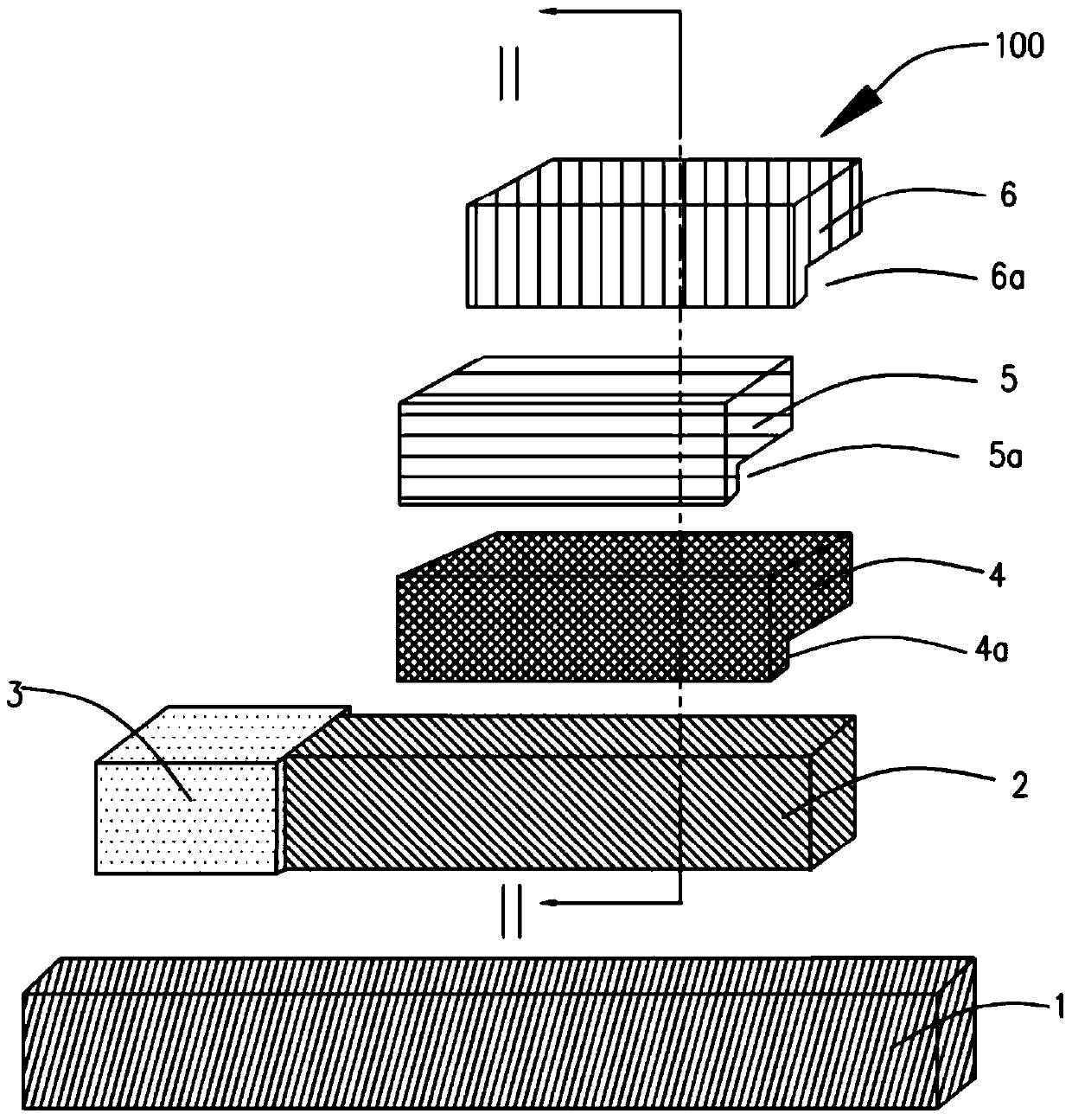

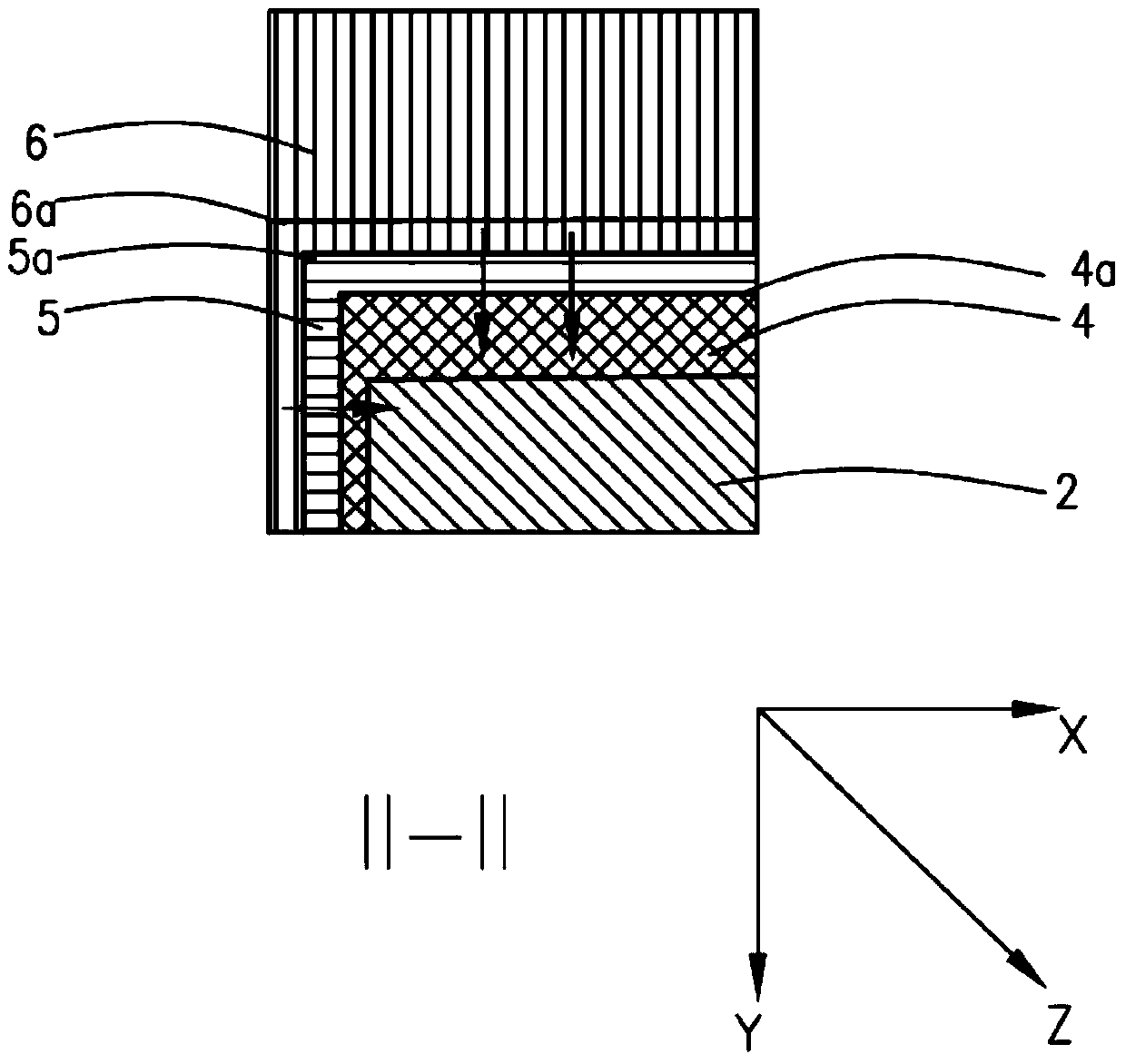

[0051] Please also refer to Figure 1 to Figure 2, is a tunneling transistor structure 100 provided in Embodiment 1 of the present invention, which includes a substrate 1, a silicon strip 2, a drain region 3, a source region 4, a gate dielectric layer 5, and a gate 6, and the silicon strip 2 is formed on one surface of the substrate 1, and the drain region 3 is formed on one side of the silicon strip 2. The source region 4 , the gate dielectric layer 5 and the gate 6 are sequentially stacked and formed on the silicon strip 2 . The source region 4 is not in contact with the drain region 3, and a first groove 4a is provided on the surface of the source region 4 facing the silicon strip 2, and the silicon strip 2 is partially housed in the first groove 4a. Inside the groove 4a....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More