Doped-free l-shaped tunneling field-effect transistor and its preparation method

A tunneling field effect, non-doped technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increasing device static power consumption, device damage, high cost, etc., and achieve a simple manufacturing process. Ease of implementation, suppression of bipolar effects, and reduction of implementation costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0034] Embodiment 1, manufacturing an undoped L-shaped tunneling field effect transistor whose gate is gallium metal with a work function of 4.2eV.

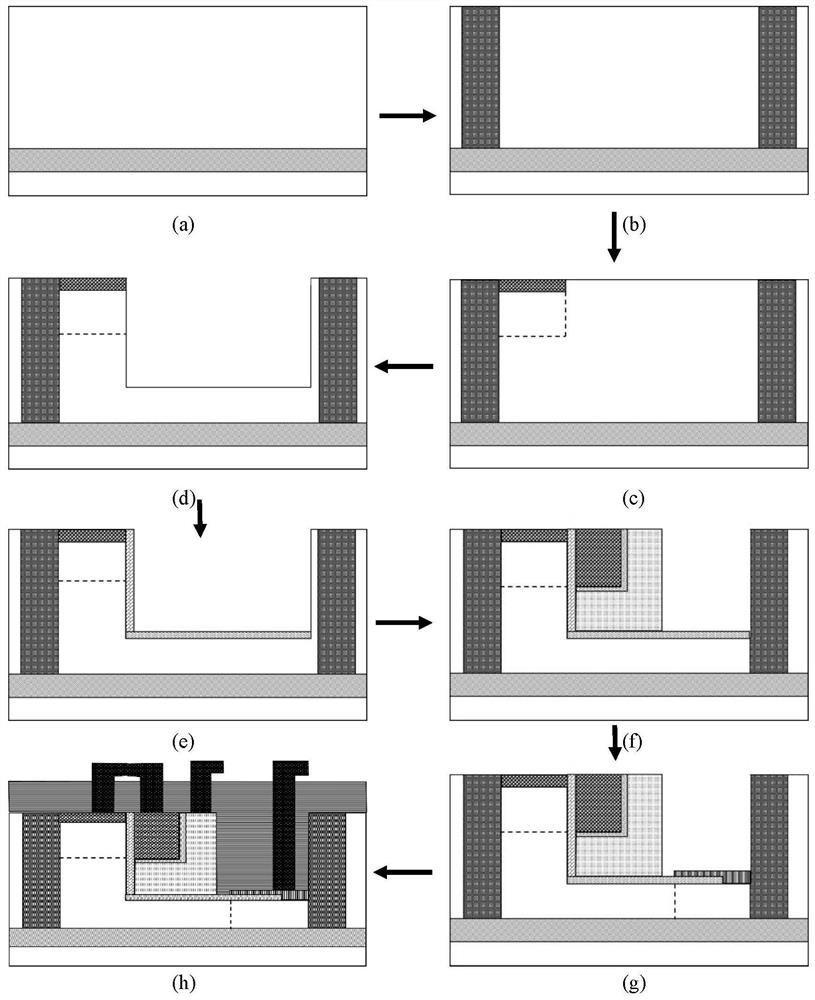

[0035] Step 1, make SOI substrate, such as image 3 (a).

[0036] 1a) Dry oxygen oxidation on the prepared bottom initial silicon wafer to generate SiO with a thickness of 10nm 2 Oxide buried layer;

[0037] 1b) Growing silicon with a thickness of 15 nm on the buried oxide layer as an epitaxial layer by an epitaxial growth process to form an SOI substrate.

[0038] Step 2, etching on both sides of the epitaxial silicon to form isolation grooves, such as image 3 (b).

[0039] 2a) Deposit SiO with a thickness of 2nm on the surface of epitaxial silicon 2 As a bottom oxide layer, then deposit Si with a thickness of 15nm on the surface of the layer 3 N 4 as a protective layer;

[0040] 2b) Using a photolithography machine, using a photolithography process on Si 3 N 4 A shallow trench isolation pattern is formed on the prote...

Embodiment 2

[0078] Embodiment 2, manufacturing an undoped L-shaped tunneling field effect transistor whose gate is tungsten metal with a work function of 4.5eV.

[0079] Step 1, making SOI substrate, such as image 3 (a).

[0080] 1.1) Dry oxygen oxidation on the prepared bottom initial silicon wafer to generate SiO with a thickness of 13nm 2 Oxide buried layer;

[0081] 1.2) An SOI substrate is formed by growing silicon with a thickness of 14 nm on the buried oxide layer as an epitaxial layer through an epitaxial growth process.

[0082] Step 2, etching on both sides of the epitaxial silicon to form isolation grooves, such as image 3 (b).

[0083] 2.1) Deposit SiO with a thickness of 4nm on the surface of epitaxial silicon 2 As a bottom oxide layer, then deposit Si with a thickness of 12nm on the surface of the layer 3 N 4 as a protective layer;

[0084] 2.2) Using a photolithography machine, using a photolithography process on Si 3 N 4 A shallow trench isolation pattern is fo...

Embodiment 3

[0122] Embodiment 3, manufacturing an undoped L-shaped tunneling field effect transistor whose gate is copper metal with a work function of 4.7eV.

[0123] The first step is to make the SOI substrate, such as image 3 (a).

[0124] First, dry oxygen oxidation is performed on the prepared bottom initial silicon wafer to produce SiO with a thickness of 15nm 2 An oxide buried layer; and then grow silicon with a thickness of 13nm on the oxide buried layer as an epitaxial layer through an epitaxial growth process to form an SOI substrate.

[0125] The second step is to etch and form isolation grooves on both sides of the epitaxial silicon, such as image 3 (b).

[0126] First, deposit SiO with a thickness of 5 nm on the surface of epitaxial silicon 2 As a bottom oxide layer, then deposit Si with a thickness of 10nm on the surface of the layer 3 N 4 As a protective layer; then use a photolithography machine, using photolithography process on Si 3 N 4 Form a shallow trench is...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electron work function | aaaaa | aaaaa |

| electron work function | aaaaa | aaaaa |

| electron work function | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More