Patents

Literature

217results about How to "Manufacturing process compatible" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

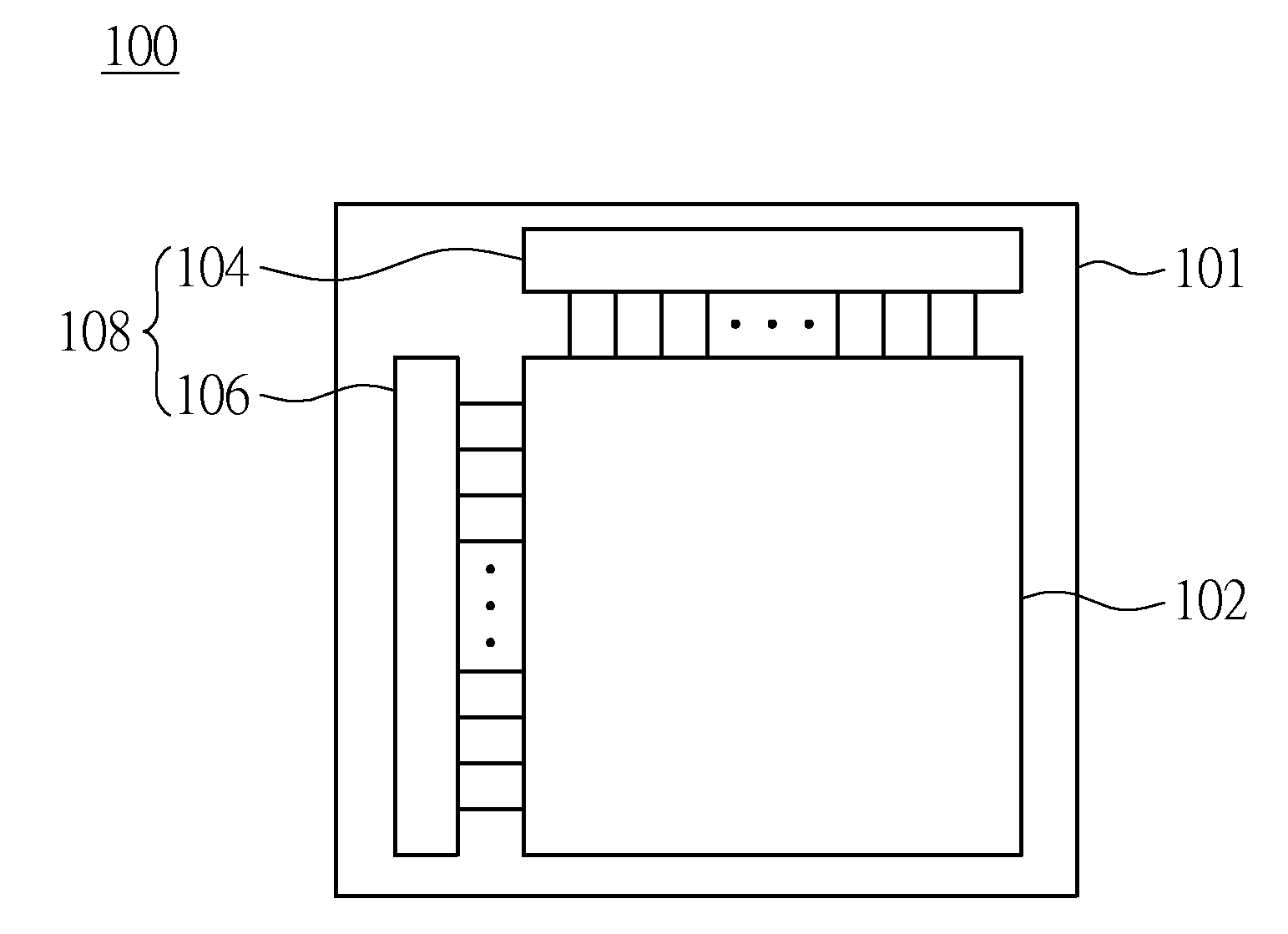

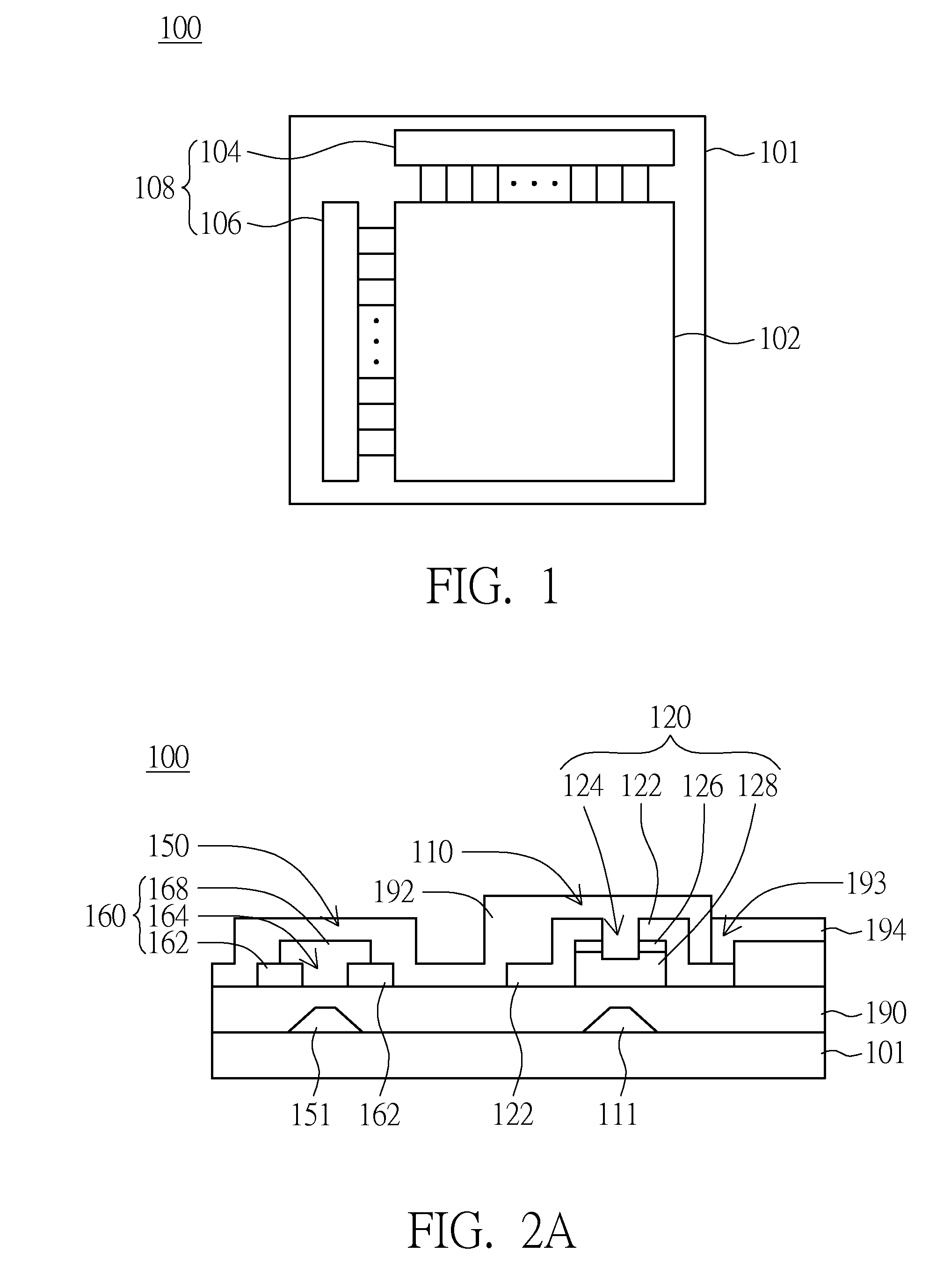

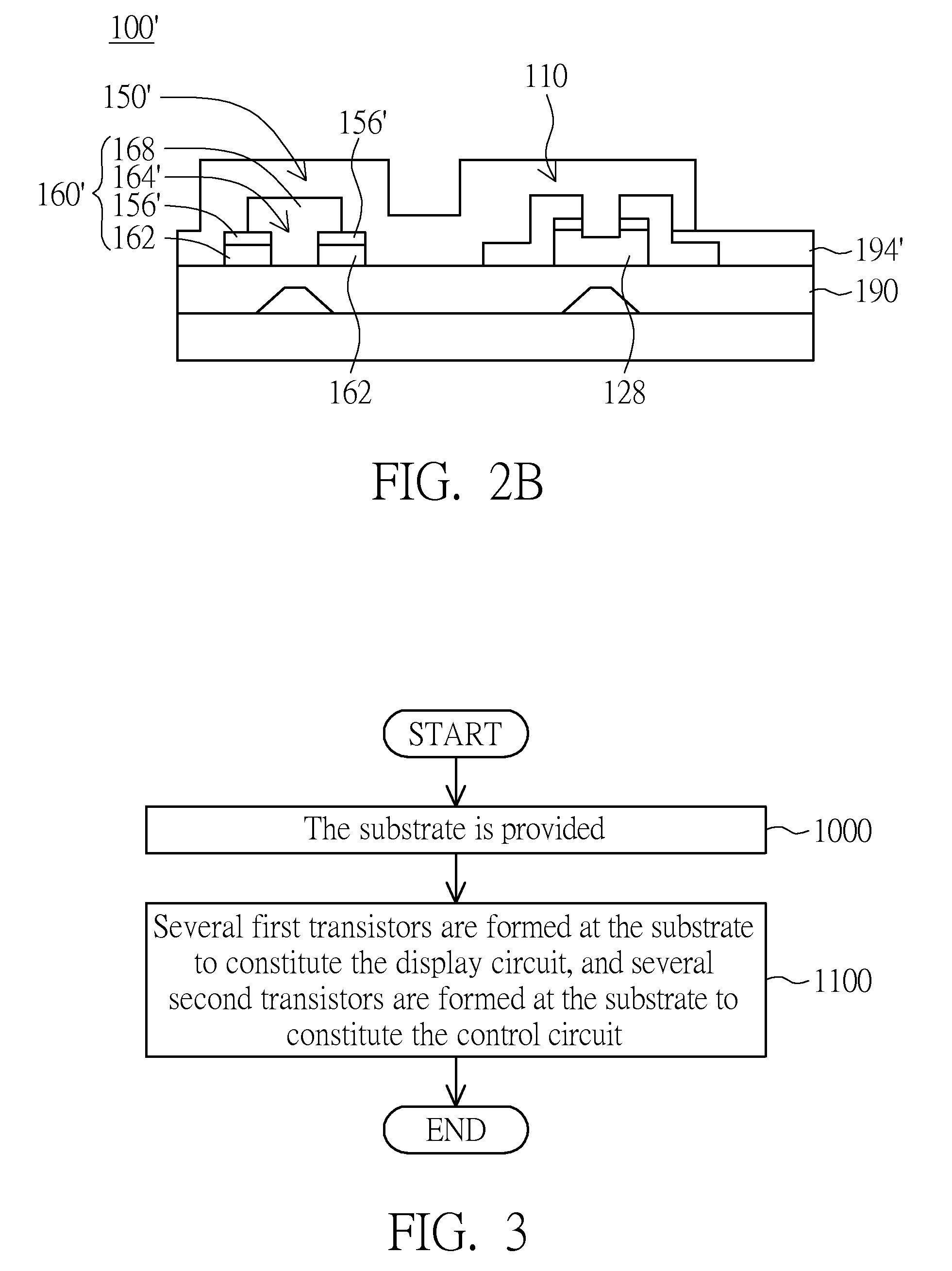

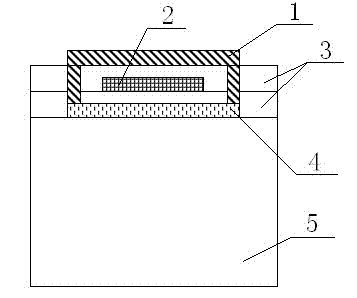

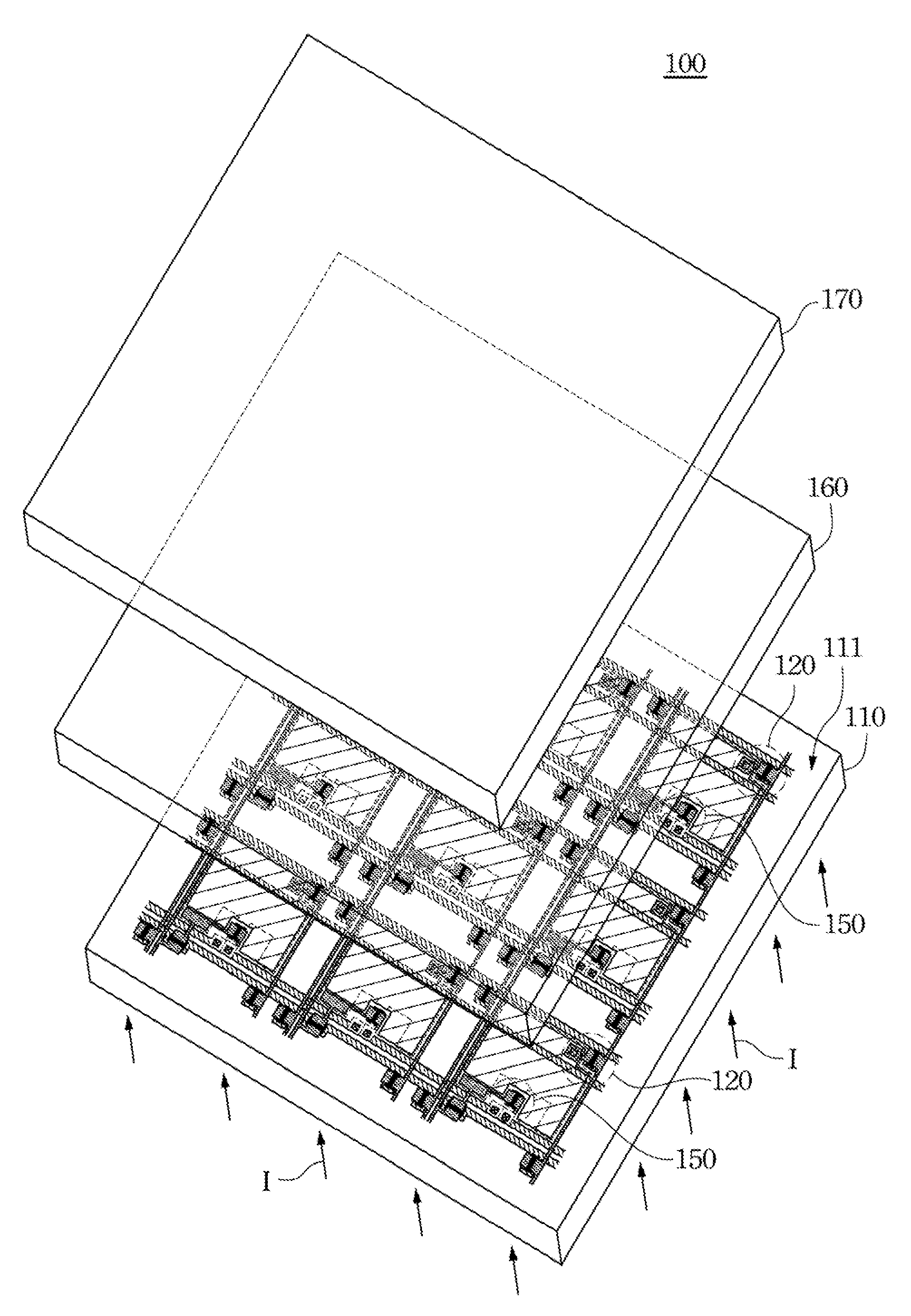

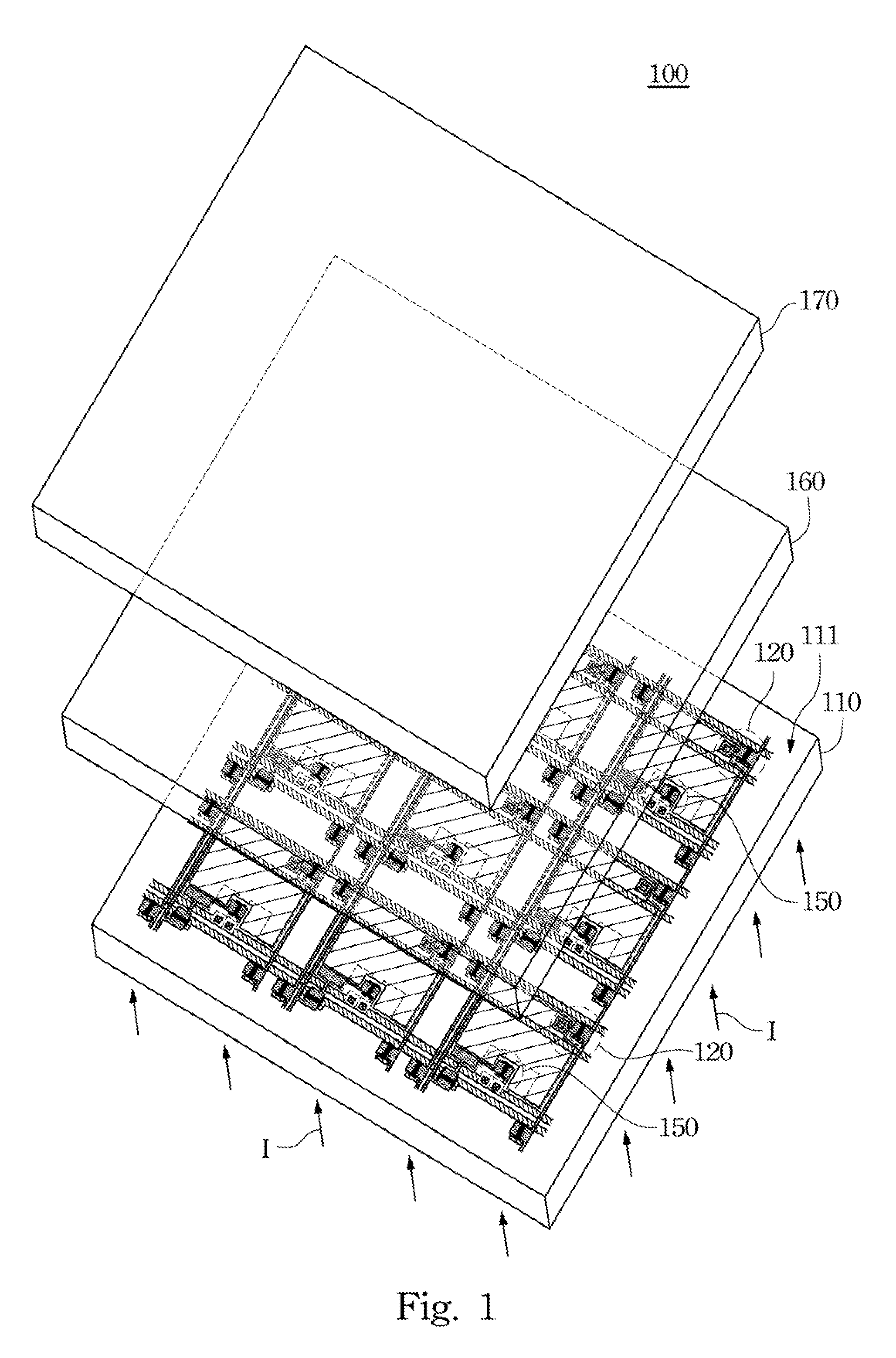

Panel structure and manufacturing method thereof

InactiveUS20090114918A1High electron mobilityManufacturing process compatibleTransistorSolid-state devicesDisplay deviceEngineering

A panel structure and a manufacturing method thereof are provided. The panel structure is disposed in a display device. The panel structure includes a substrate, several first transistors and second transistors. The substrate has a display circuit and a control circuit. The first transistors are disposed at the display circuit of the substrate. Each of the first transistors has a first active layer. The second transistors are disposed at the control circuit of the substrate. Each of the second transistors has a second active layer. The materials of at least one of the first active layer and the second active layer include ZnO.

Owner:WINTEK CORP

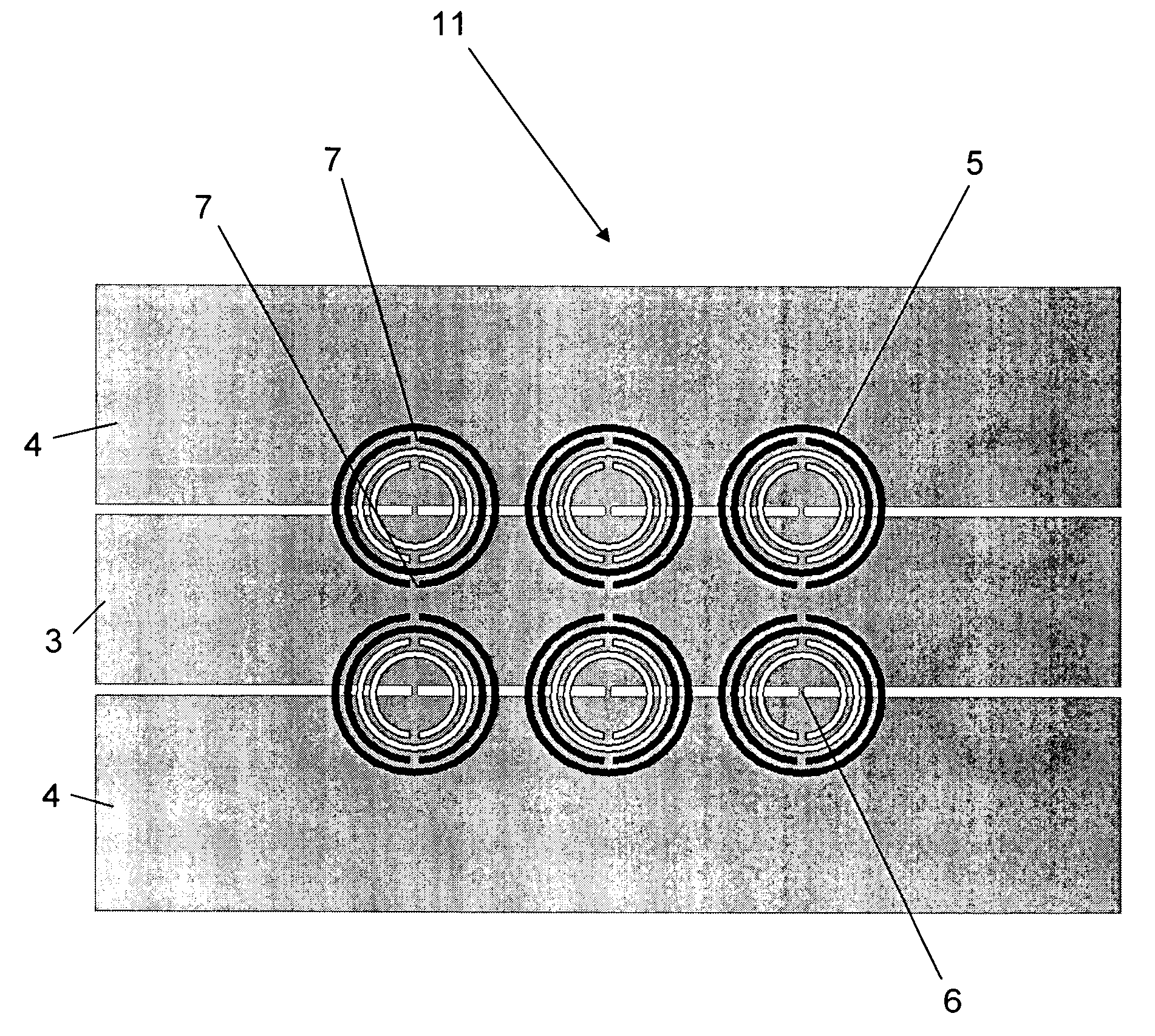

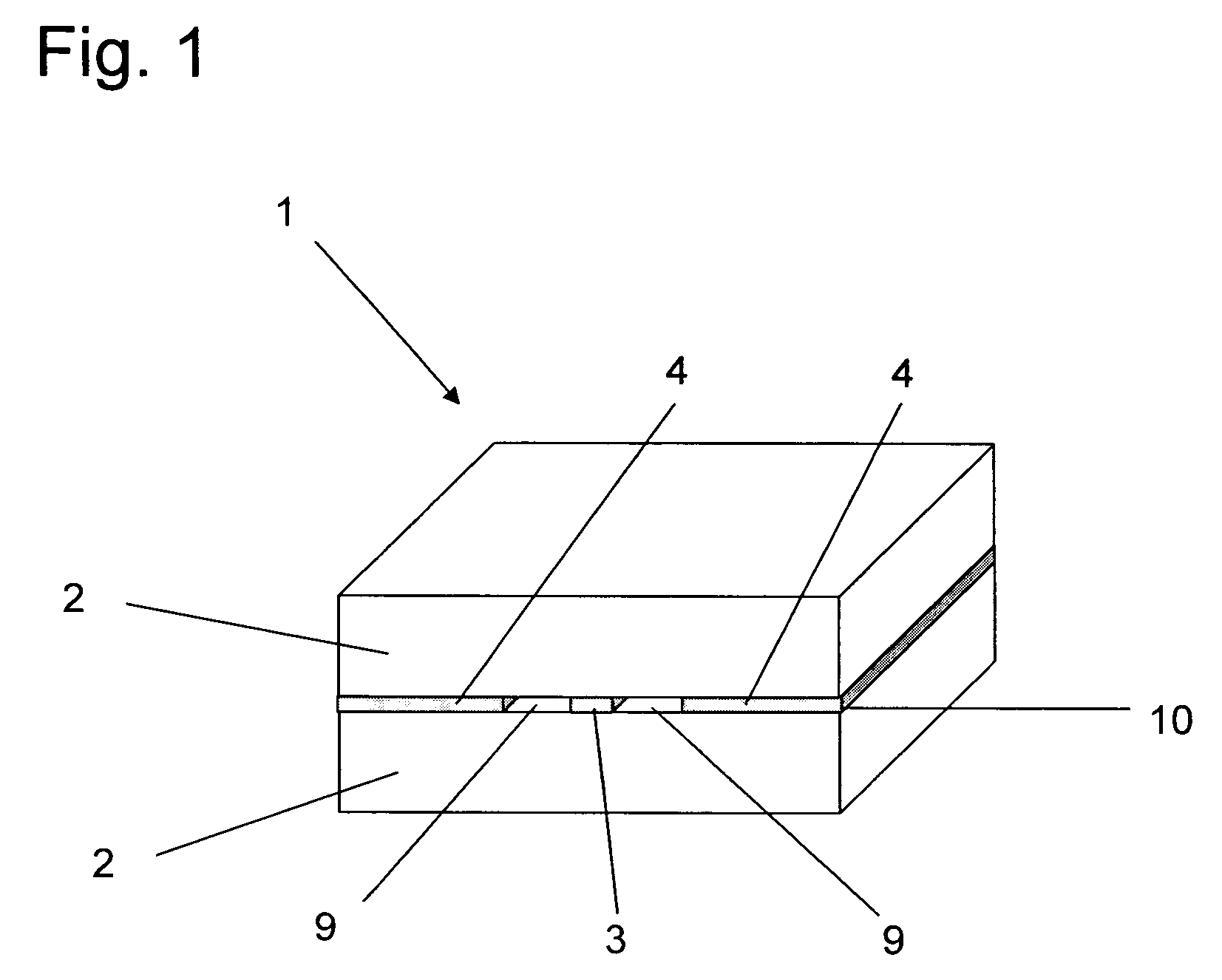

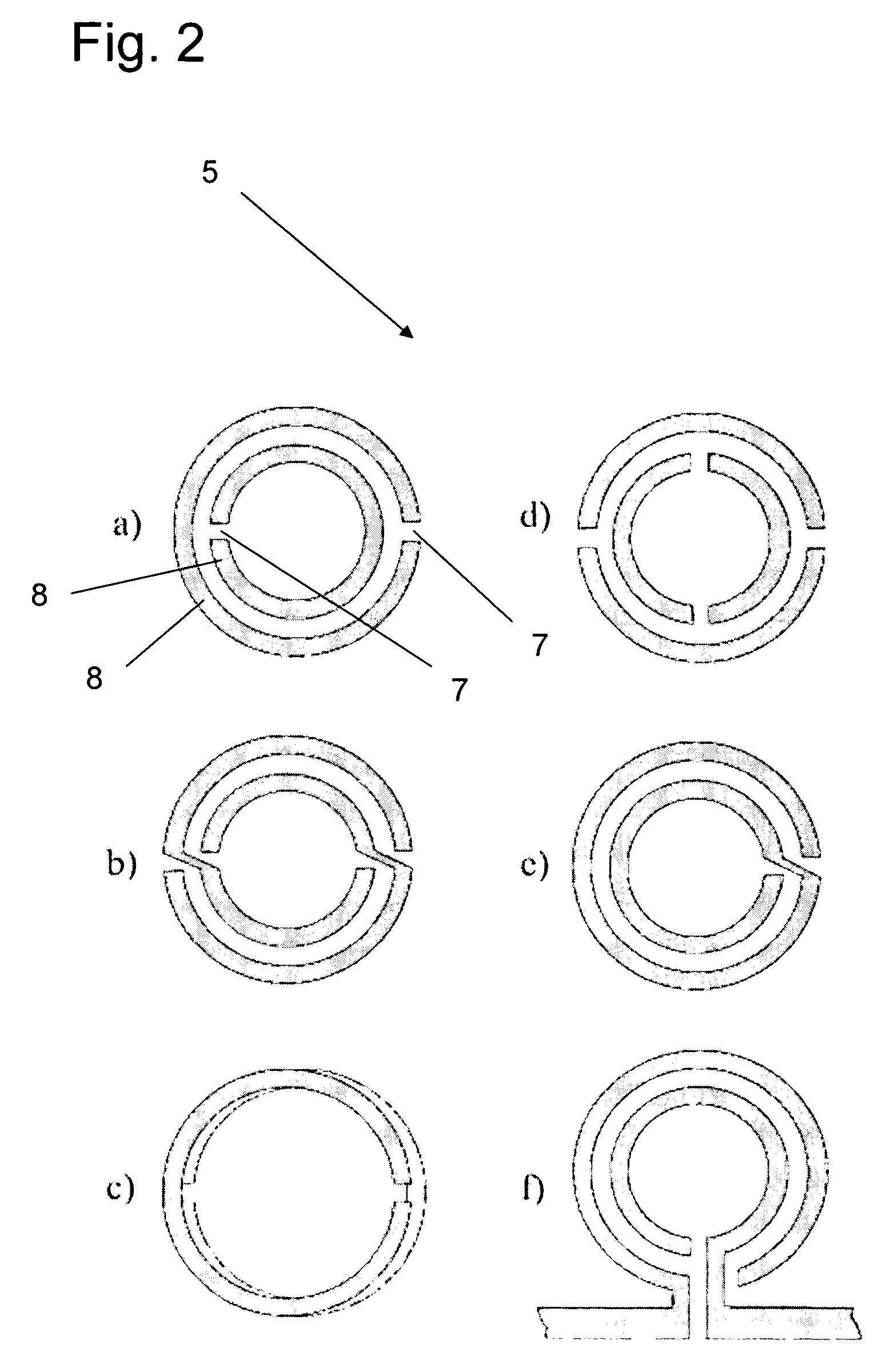

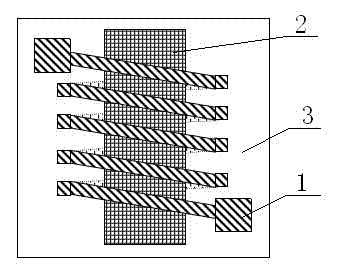

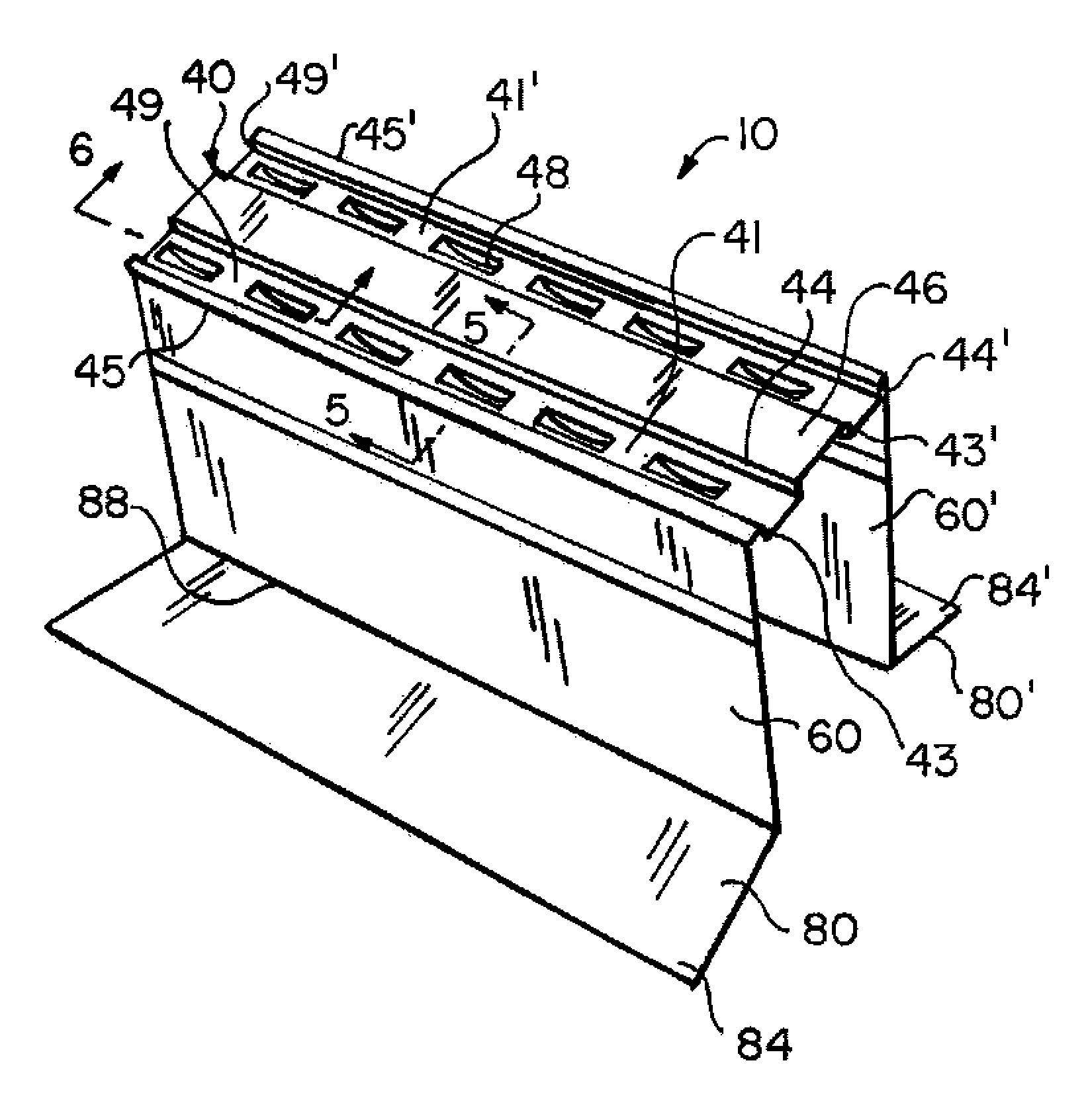

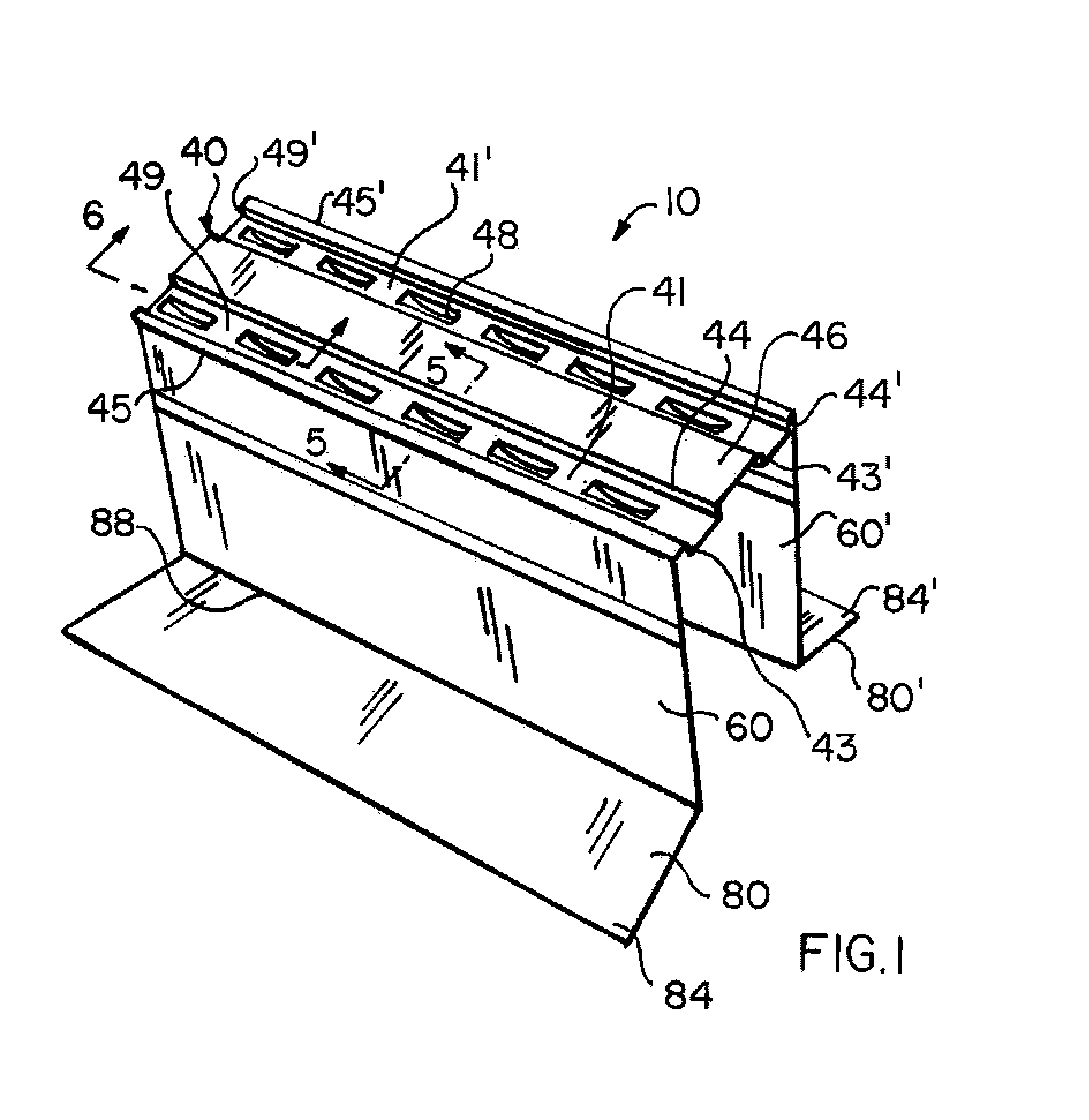

Filters and antennas for microwaves and millimetre waves, based on open-loop resonators and planar transmission lines

InactiveUS20070024399A1Good level of directivityGood level of polarisationResonatorsLoop antennasElectrical conductorDielectric substrate

Filter for microwaves and millimetER waves, characterised in that it comprises a planar transmission medium (1) that it includes a conductor strip (3), metallic ground plane (4) and dielectric substrate (2) and in that it includes at least one split rings resonator (5a, 5b, 5c, 5d, 5e and 5f)

Owner:AUTONOMOUS UNIVERSITY OF BARCELONA

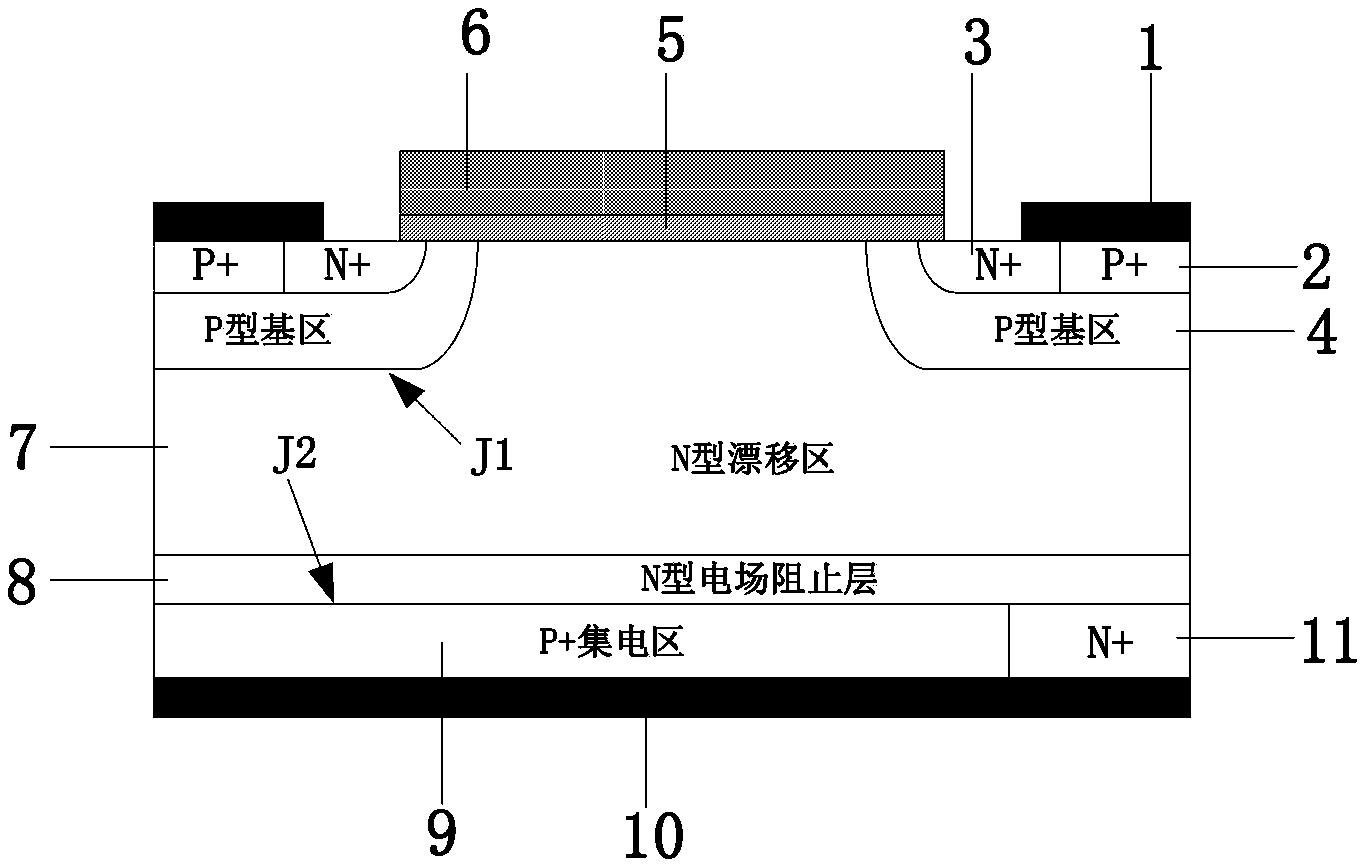

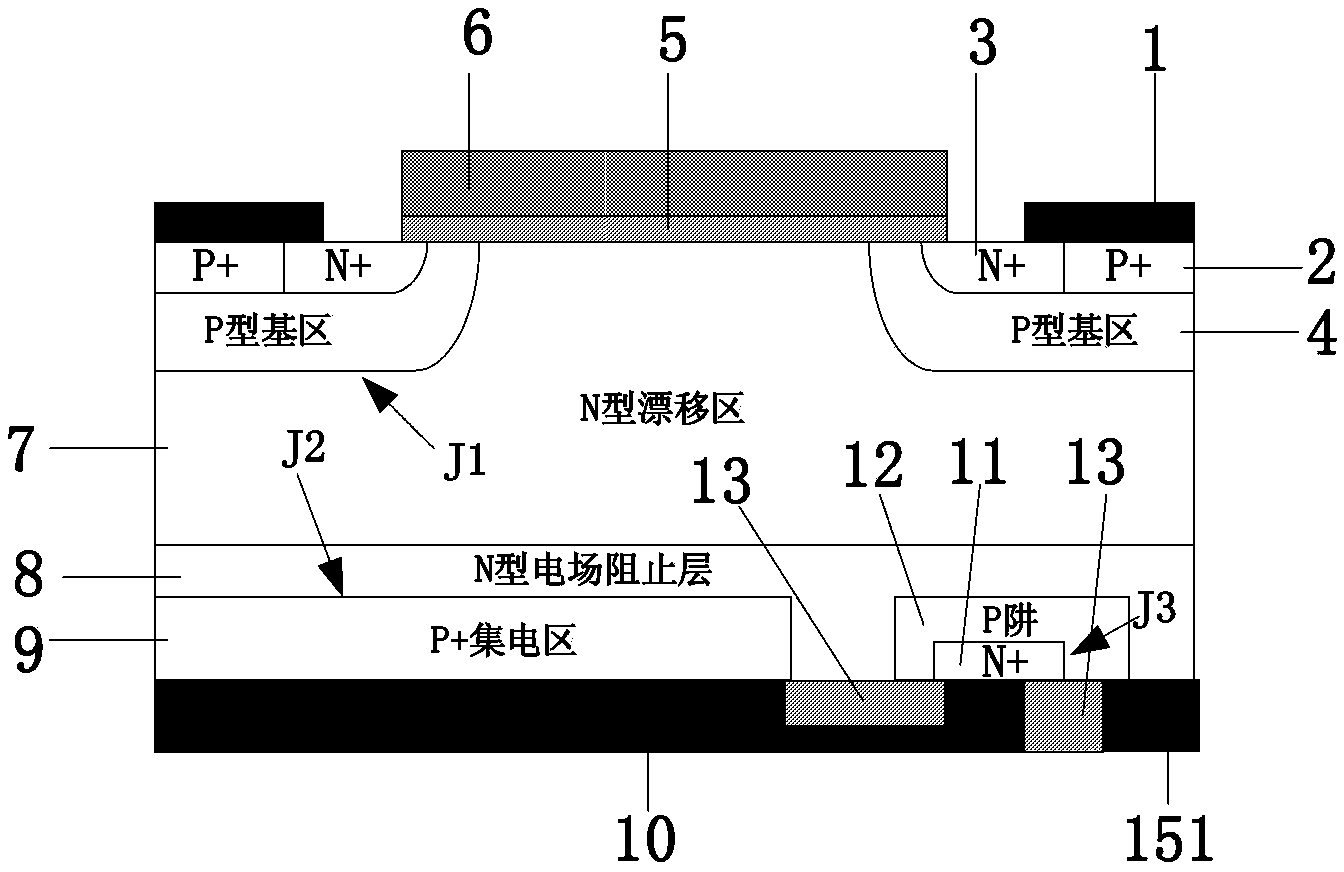

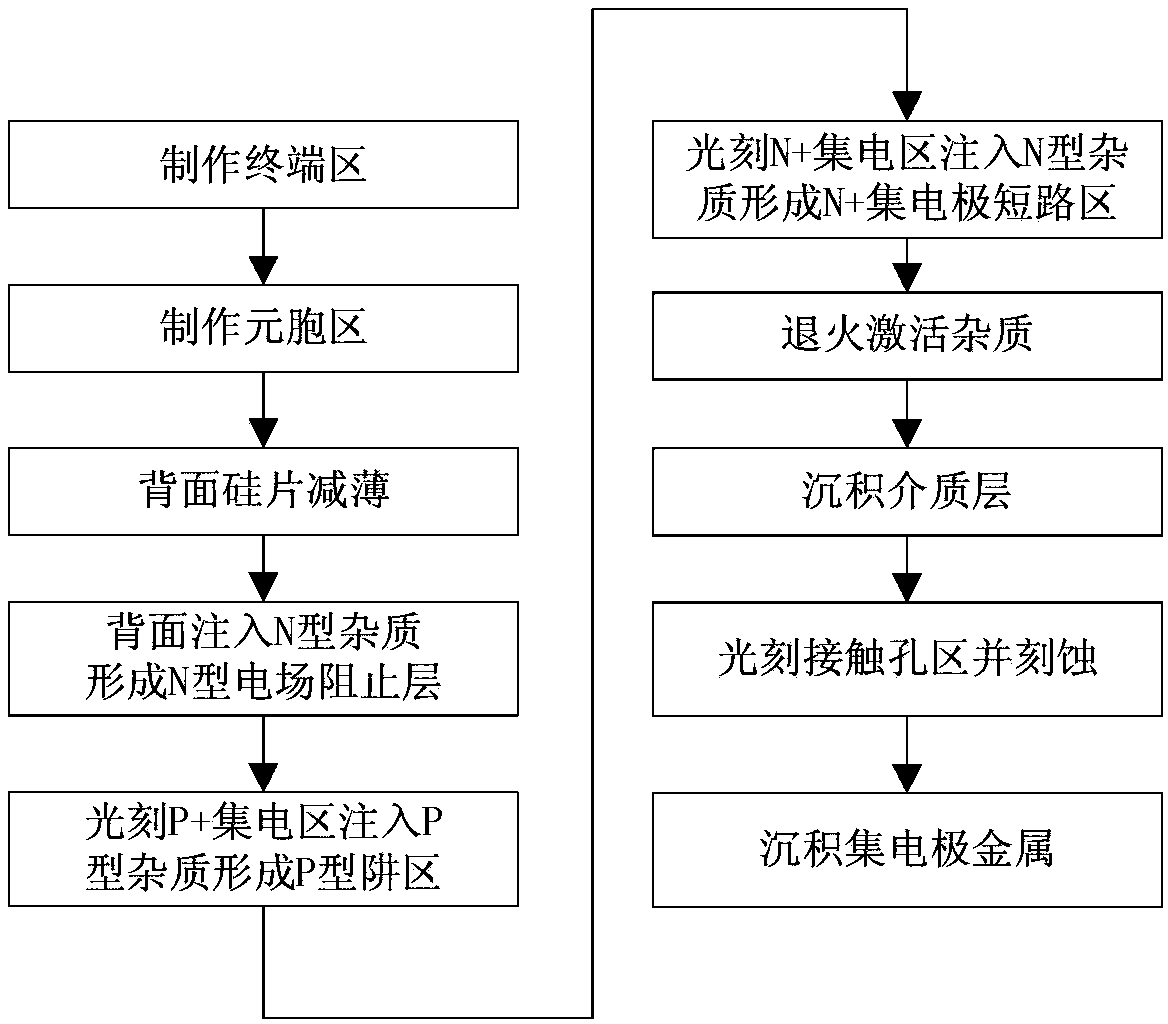

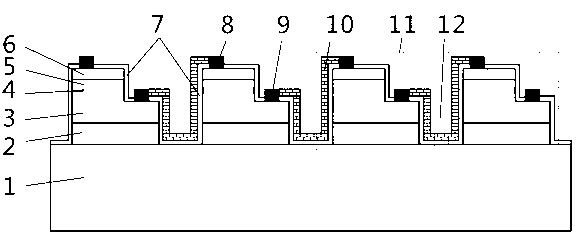

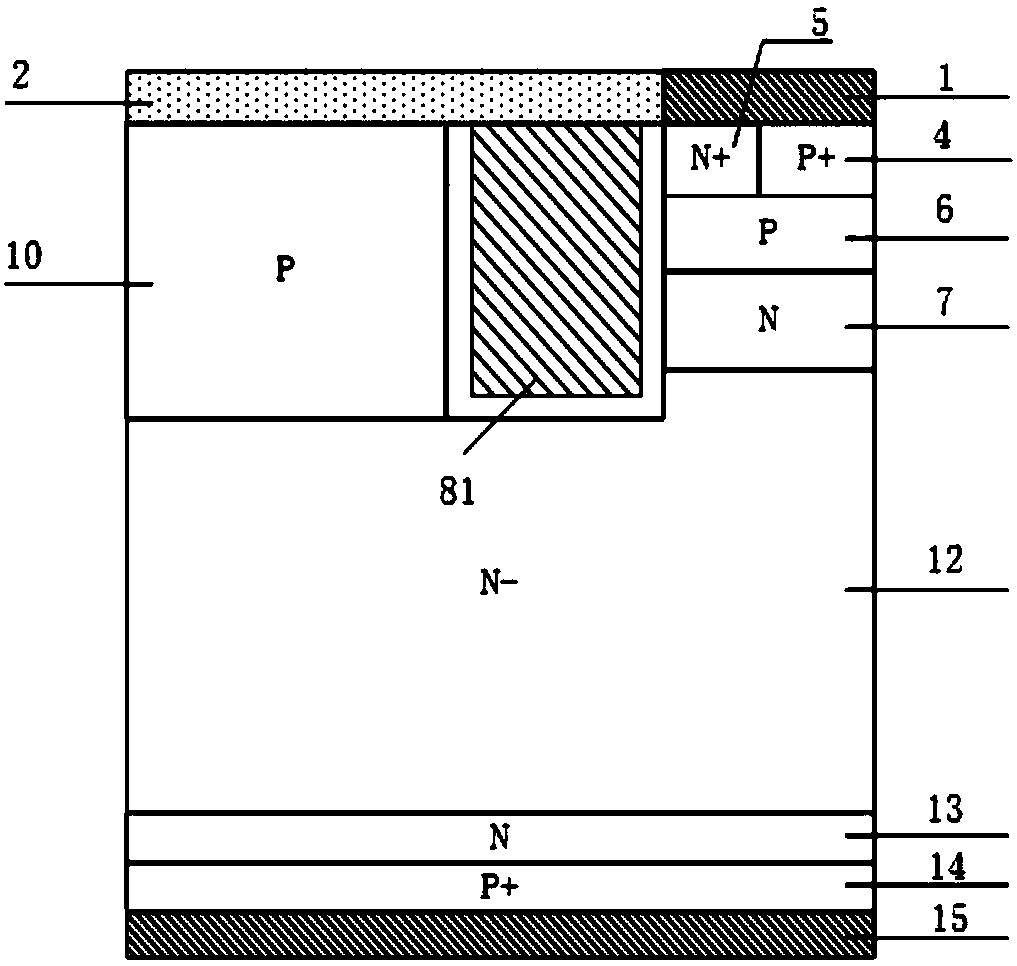

Reverse conducting (RC)-insulated gate bipolar transistor (IGBT) device and manufacturing method thereof

InactiveCN103383958AImprove reliabilityNo Snapback phenomenonSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringElectric field

A reverse conducting (RC)-insulated gate bipolar transistor (IGBT) device and a manufacturing method thereof belong to the technical field of power semi-conductor devices. On the basis of a traditional RC-IGBT device structure, a P-type well region 12 is introduced between an N+ collector short circuit area 11 and an N type electric field preventing layer 8, and the N type electric field preventing layer 8 and the P-type well region 12 are insulated from a metal collector 10 by adopting an isolation medium 13. On the basis of traditional RC-IGBT device characteristics, the device can fully eliminate an intrinsic Snap back phenomenon of a traditional RC-IGBT during connection in the positive direction and has a similar loss characteristic as the traditional RC-IGBT. The RC-IGBT device and the manufacturing method are applicable to the field of semi-conductor power devices from small power to large power and power integrated circuits.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

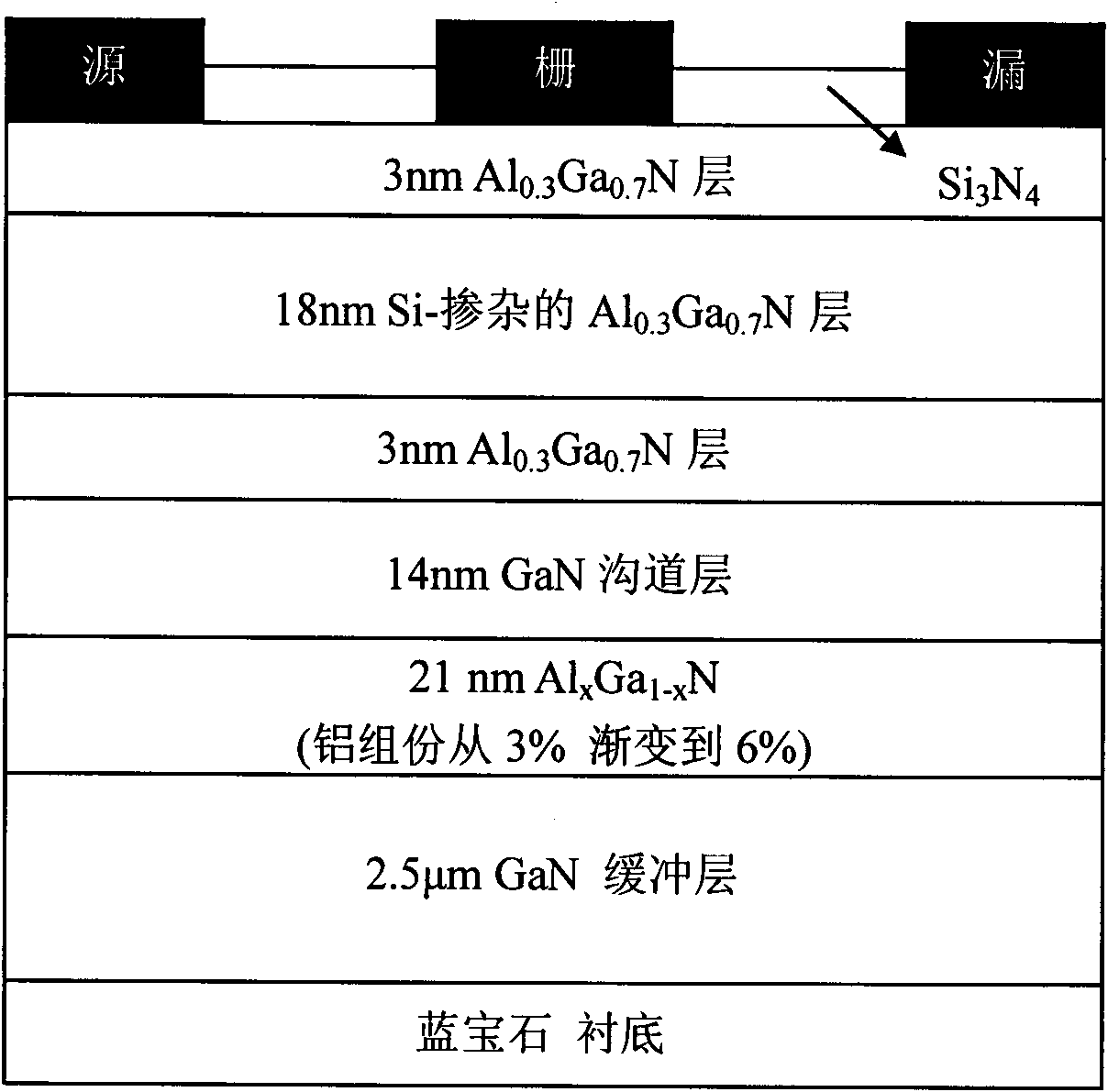

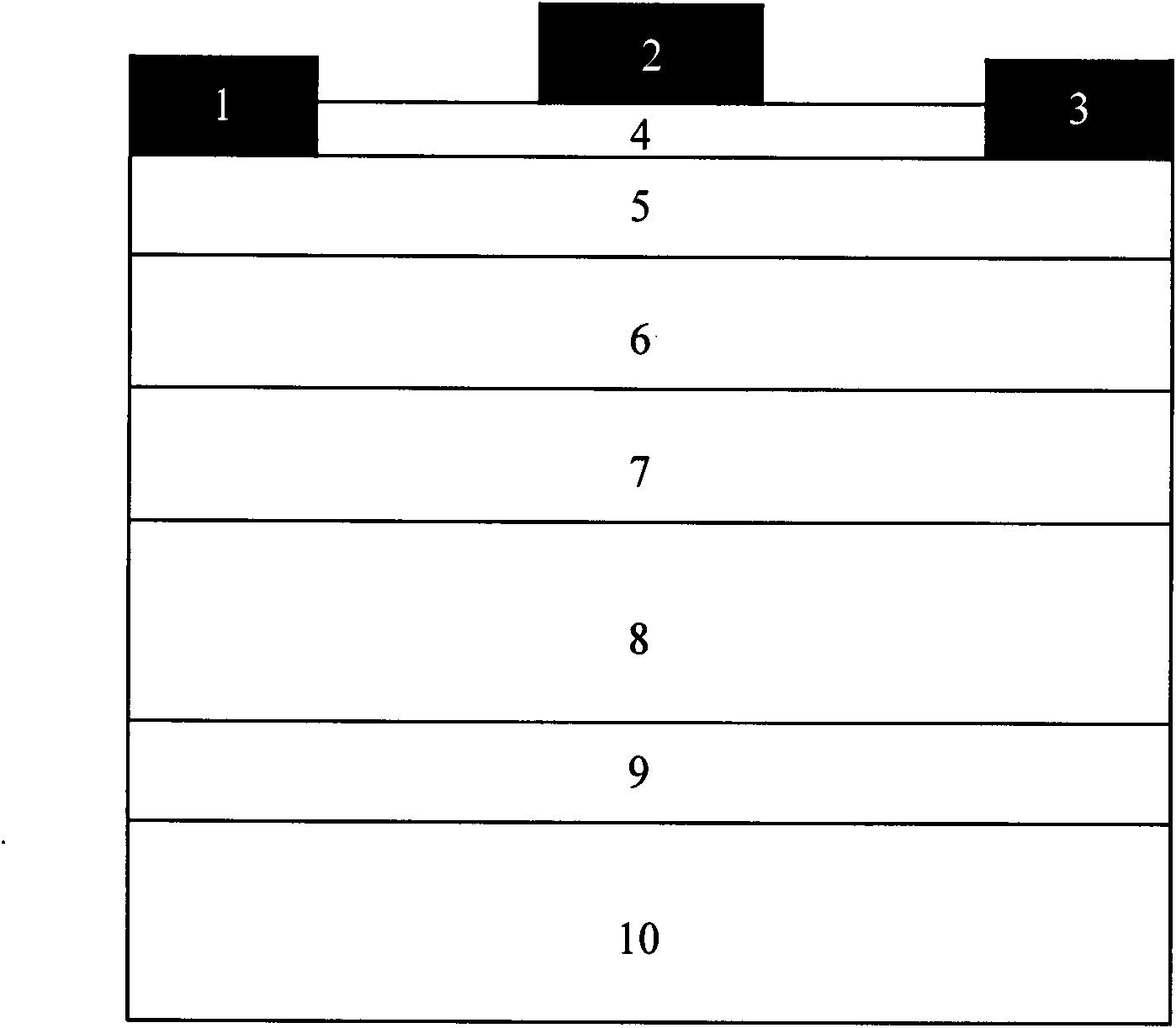

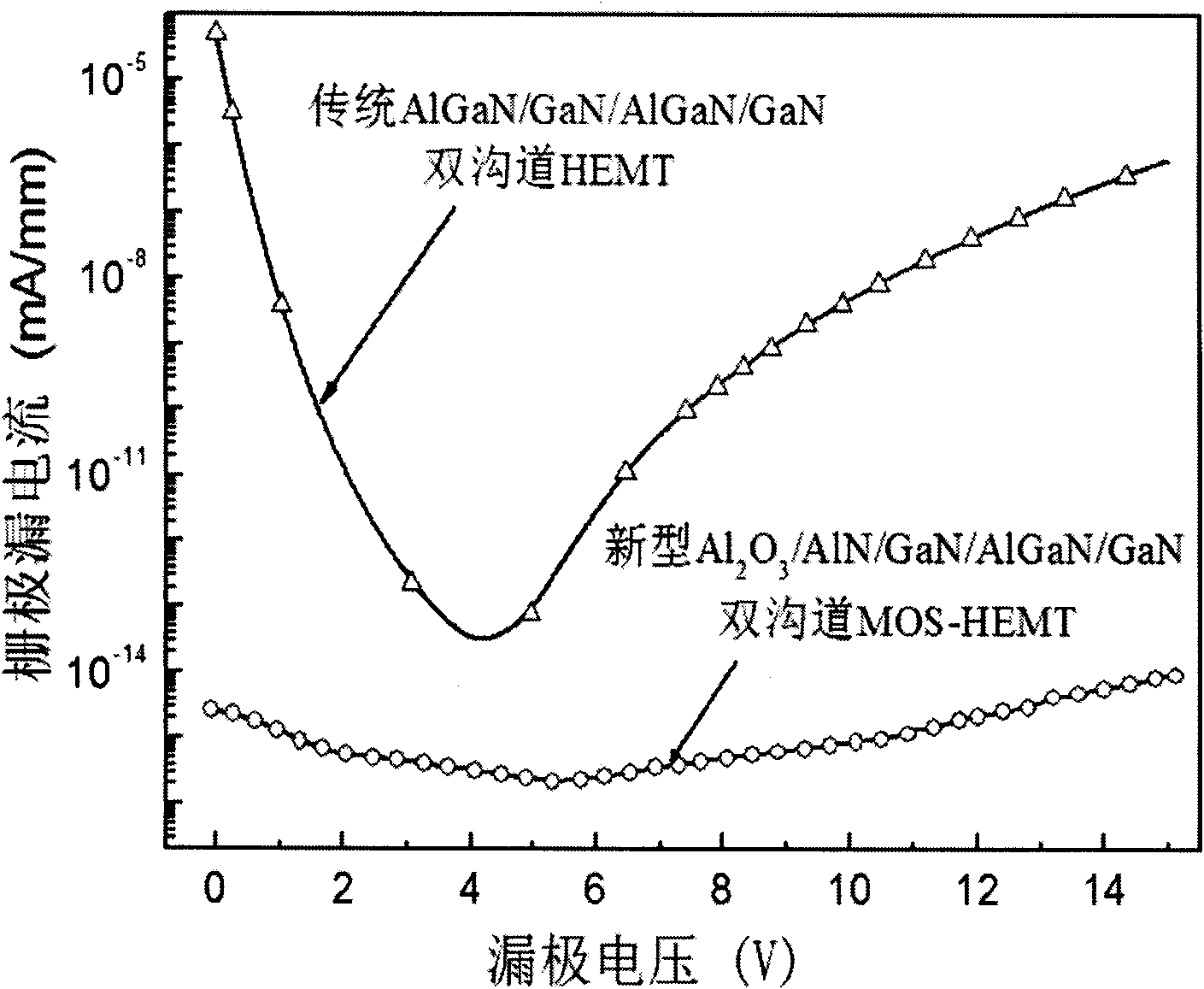

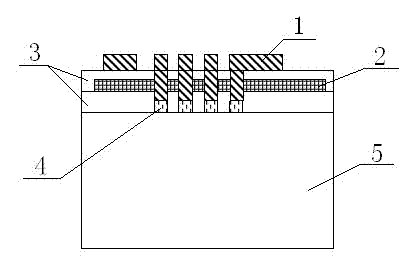

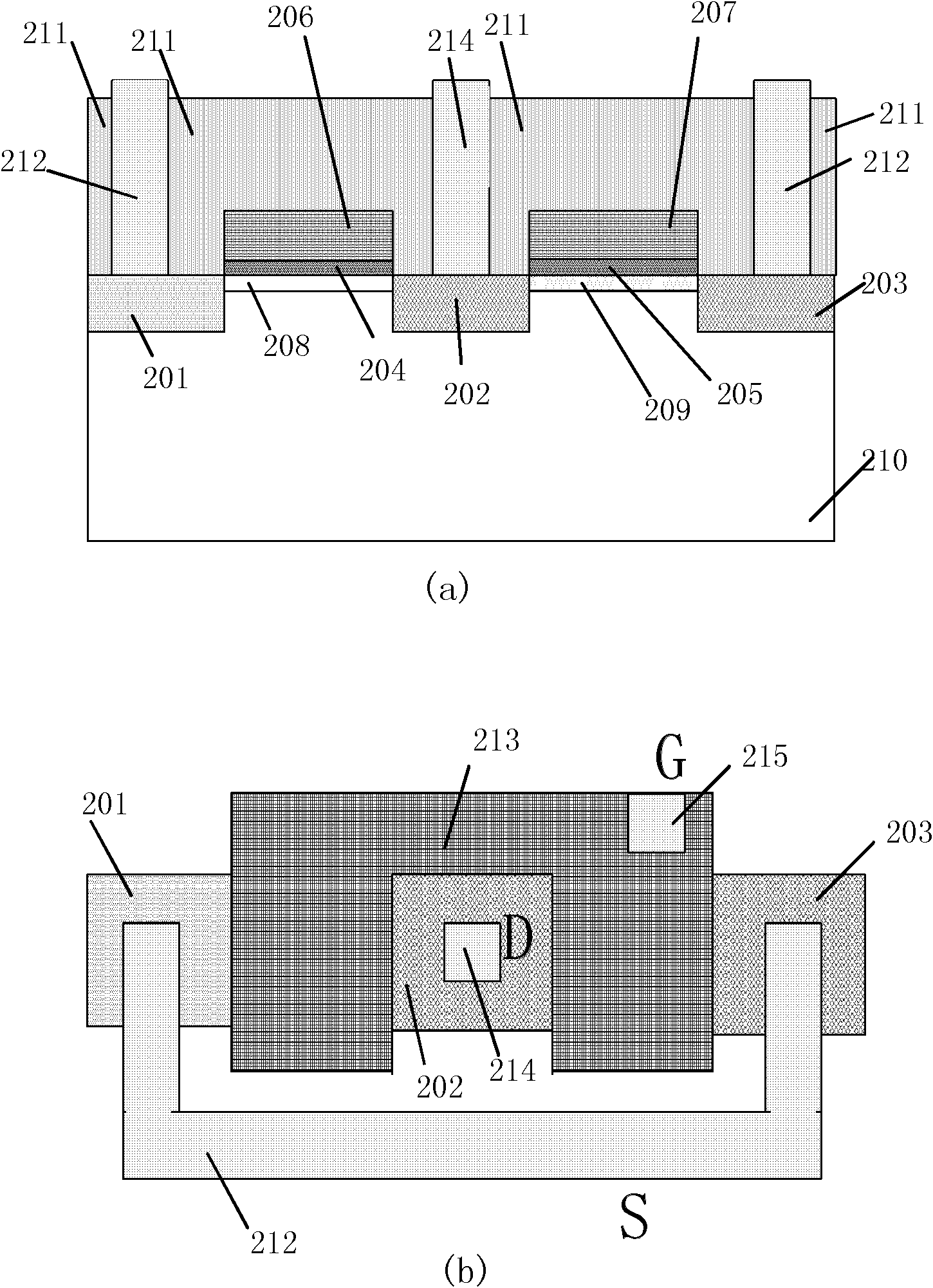

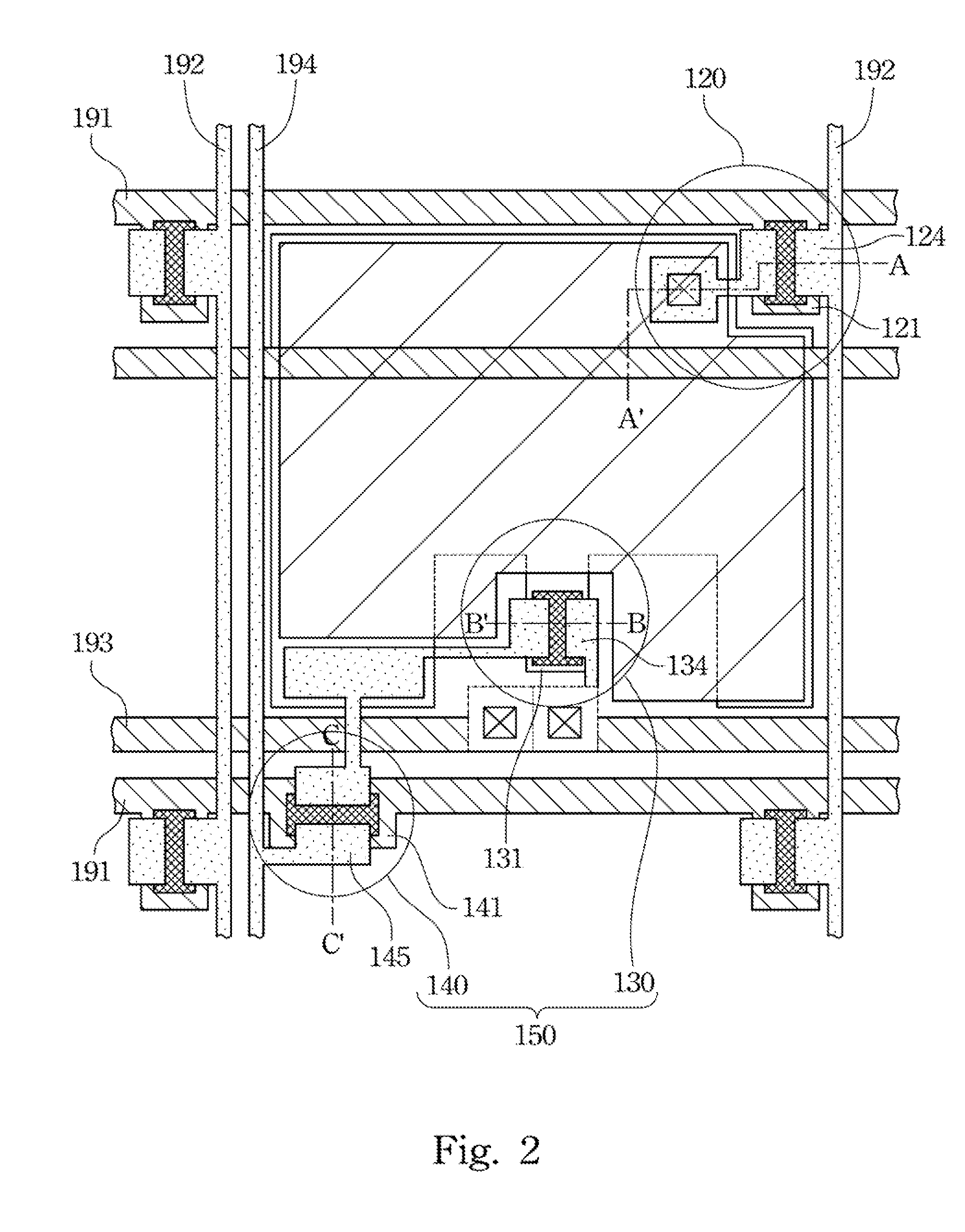

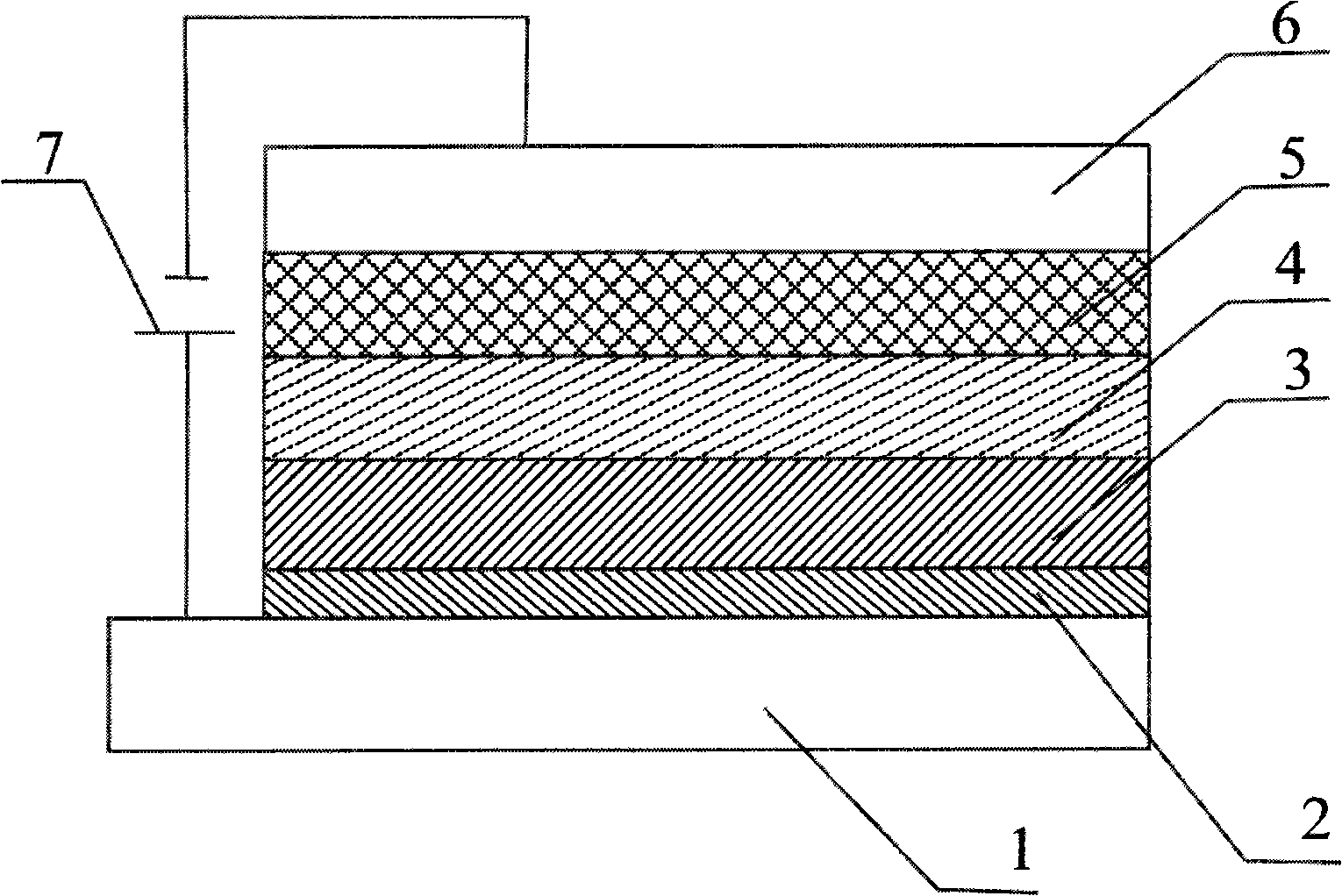

Double-channel MOS-HEMT (Metal Oxide Semiconductor-High Electron Mobility Transistor) device and manufacturing method

InactiveCN101916773AAddressing Excessive Threshold Voltage and Gate LeakageIncrease saturation drain current and output powerSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsOxide semiconductor

The invention discloses an Al2O3 / AlN / GaN / AlGaN / GaN double-channel MOS-HEMT (Metal Oxide Semiconductor-High Electron Mobility Transistor) device and a manufacturing method. The double-channel MOS-HEMT device comprises a GaN nucleating layer 9, a GaN buffer layer 8, an AlGaN lower barrier layer 7, a GaN channel layer 6, an AlN upper barrier layer 5, an Al2O3 gate dielectric layer 4, a source electrode 1, a drain electrode 3 and a gate electrode 2, wherein the GaN nucleating layer 9, the GaN buffer layer 8, the AlGaN lower barrier layer 7, the GaN channel layer 6 and the AlN upper barrier layer 5 are formed on a sapphire substrate 10 in sequence, the Al2O3 gate dielectric layer 4, the source electrode 1 and thea drain electrode 3 are formed on the AlN upper barrier layer 5, and the gate electrode 2 is formed on the Al2O3 gate dielectric layer 4. The invention is characterized in that an AlN material with good heat conductivity and greater forbidden band width is used as the upper barrier layer, so that the self heating effect of the device is reduced, and the threshold voltage of the device in a depletion mode is reduced; a depth potential well made from AlN and GaN is used for suppressing the hot electron effect under high voltage, so that the current collapse effect of the device is reduced; the strong polarization feature of the AlN material is used to increase the electron concentration in the channel and increase the saturation current and the output power of the device; and the Al2O3 material deposited by using the atomic layer deposition process is used as the gate dielectric layer, so that the leakage current of the gate electrode is reduced, and the breakdown voltage of the device is increased.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

Composite passivated anti-reflection film used for crystalline silicon solar battery and preparation method thereof

InactiveCN102157570AImprove anti-reflection effectImprove passivation effectFinal product manufactureChemical vapor deposition coatingElectrical batteryEngineering

The invention discloses a composite passivated anti-reflection film used for a crystalline silicon solar battery and a preparation method thereof. The composite passivated anti-reflection film consists of a silicon oxide (SiO2) layer, an amorphous alumina (a-Al2O3) layer and an amorphous silicon nitride (a-Si1-xNx) layer which are arranged on the emitter on a light receiving surface of the crystalline silicon solar battery in turn. The preparation method comprises the following steps of: preparing an a-Al2O3 layer on the emitter on the light receiving surface of the crystalline silicon solar battery by a plasma enhanced chemical vapor deposition (PECVD) process or an atomic layer deposition (ALD) process; forming the SiO2 layer between the emitter layer and the a-Al2O3 layer by an annealing process; and preparing the a-Si1-xNx layer on the a-Al2O3 layer by the PECVD process. The composite passivated anti-reflection film has the advantages that: the a-Si1-xNx anti-reflection film has a good anti-reflection effect; the a-Al2O3 / SiO2 composite passivated film has double effects of chemical passivation and field passivation and has a good passivation effect; the a-Si1-xNx / a-Al2O3 / Si2O composite passivated anti-reflection film has high thermal stability and is compatible with a subsequent battery preparation process; and the anti-ultraviolet (UV) performance is high.

Owner:上海太阳能电池研究与发展中心

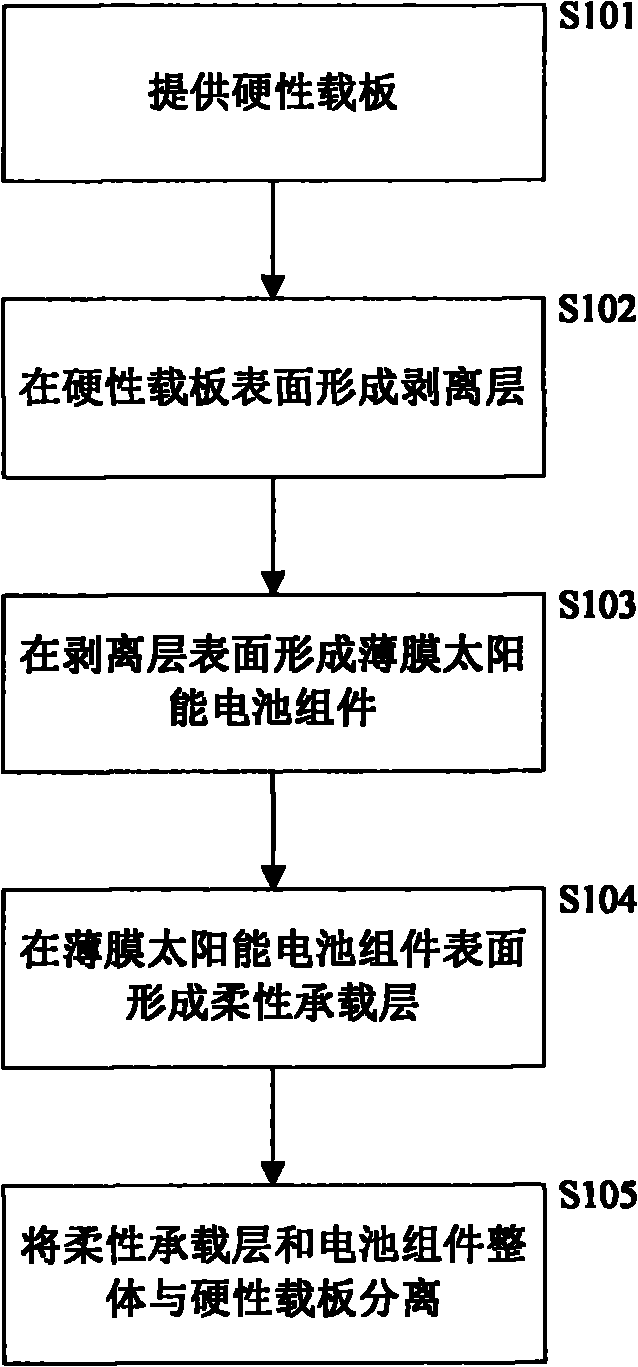

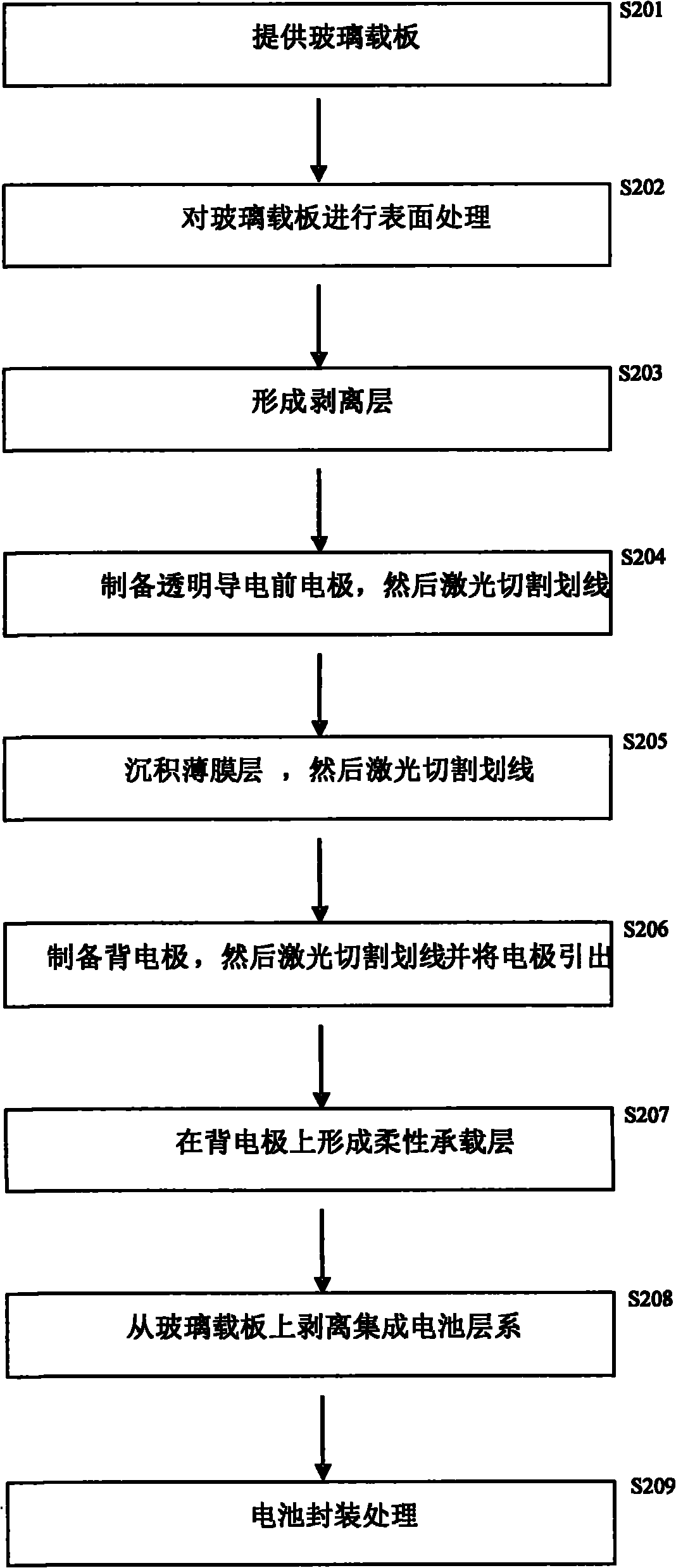

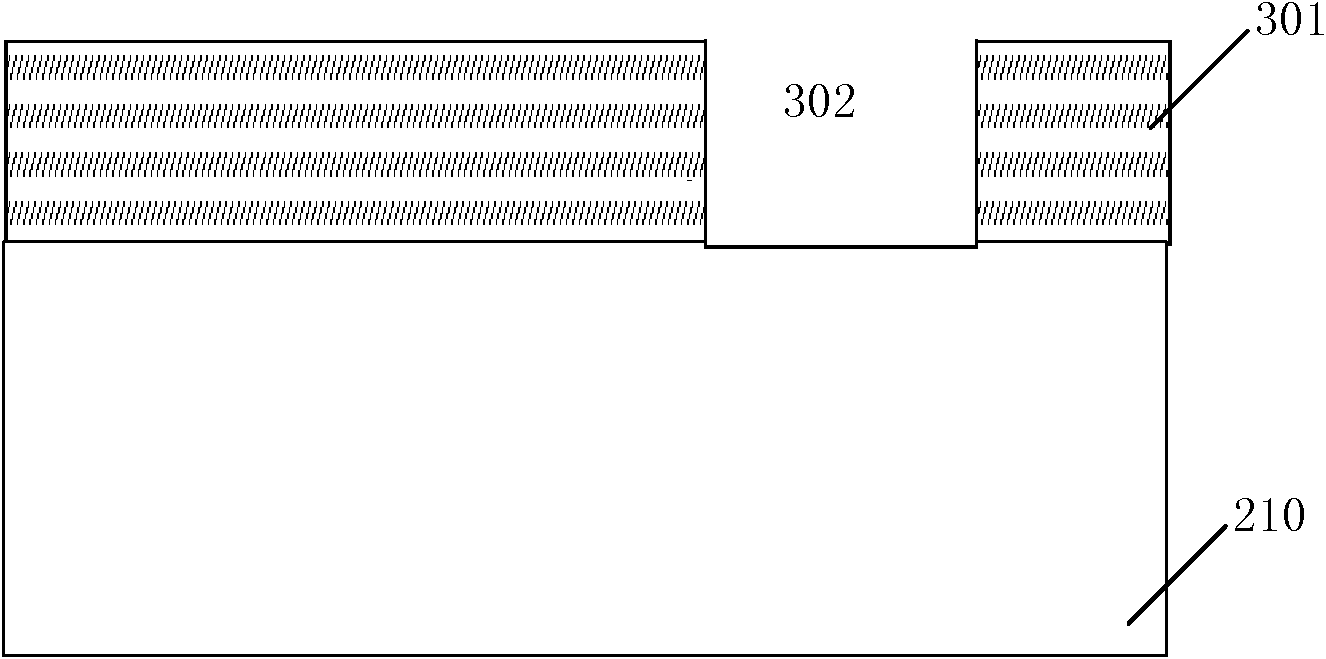

Flexible thin film solar cell and manufacturing method thereof

InactiveCN101964398AImprove conversion efficiencyManufacturing process compatibleFinal product manufactureSolid-state devicesEngineeringThin film solar cell

The invention discloses a flexible thin film solar cell and a manufacturing method thereof, wherein the manufacturing method comprises the following steps: providing a hard support plate; forming a stripping layer on the surface of the hard support plate; forming a thin film solar cell layer series on the surface of the stripping layer; forming a flexible support layer on the surface of the thin film solar cell layer series; and separating the flexible support layer and the whole thin film solar cell layer series from the hard support plate. In the invention, the flexible thin film solar cell can be manufactured directly on the surface of the hard support plate such as glass without depending on traditional flexible substrates which are high in requirements for physical and chemical characteristics and high in expense and without the complicated flexible thin film solar cell manufacturing process of firstly adhering the flexible substrate on the surface of the hard support plate and then carrying out thin film deposition, therefore, the method of the invention is a revolutionary method for directly manufacturing a large-area and internal cascade flexible thin film solar cell on the hard support plate.

Owner:BEIJING JINGCHENG BOYANG OPTOELECTRONICS EQUIPCO

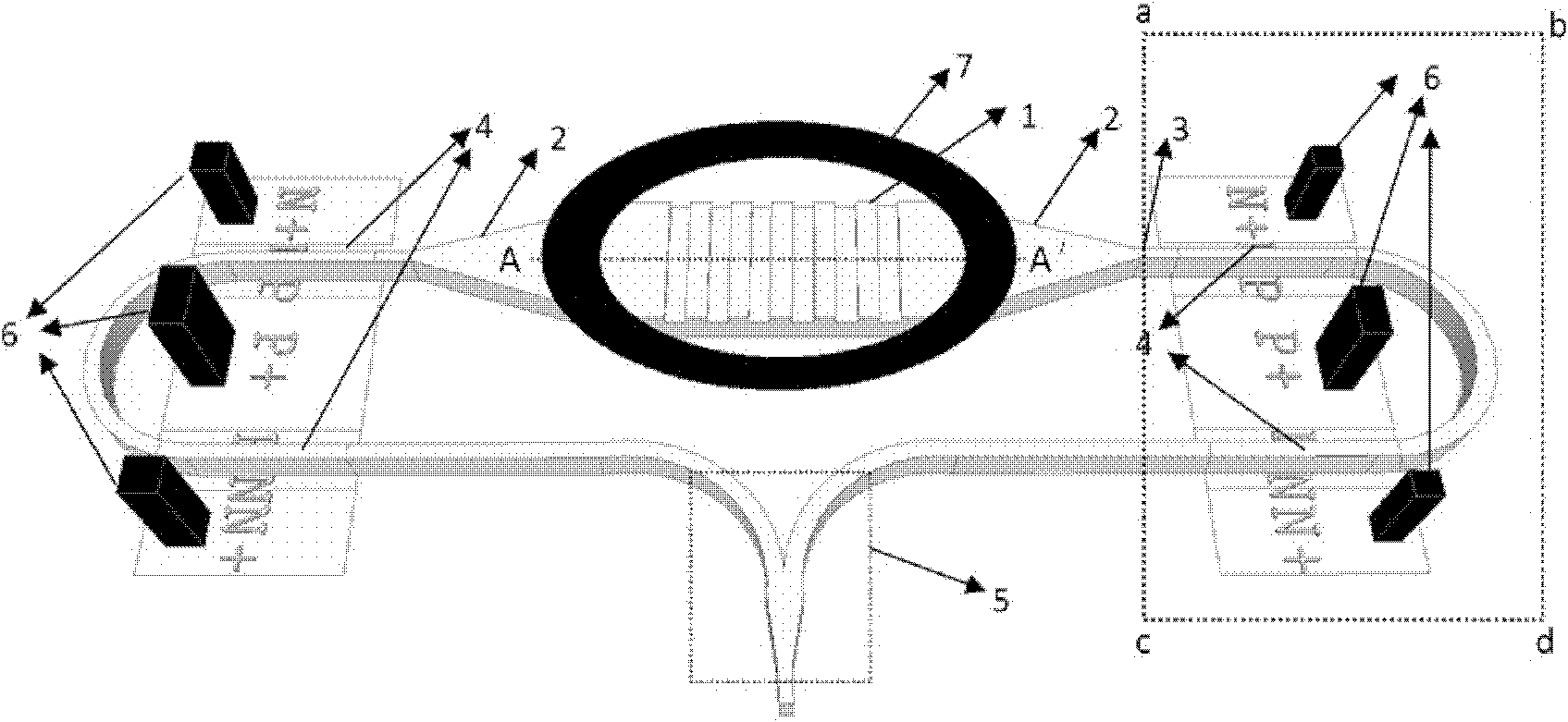

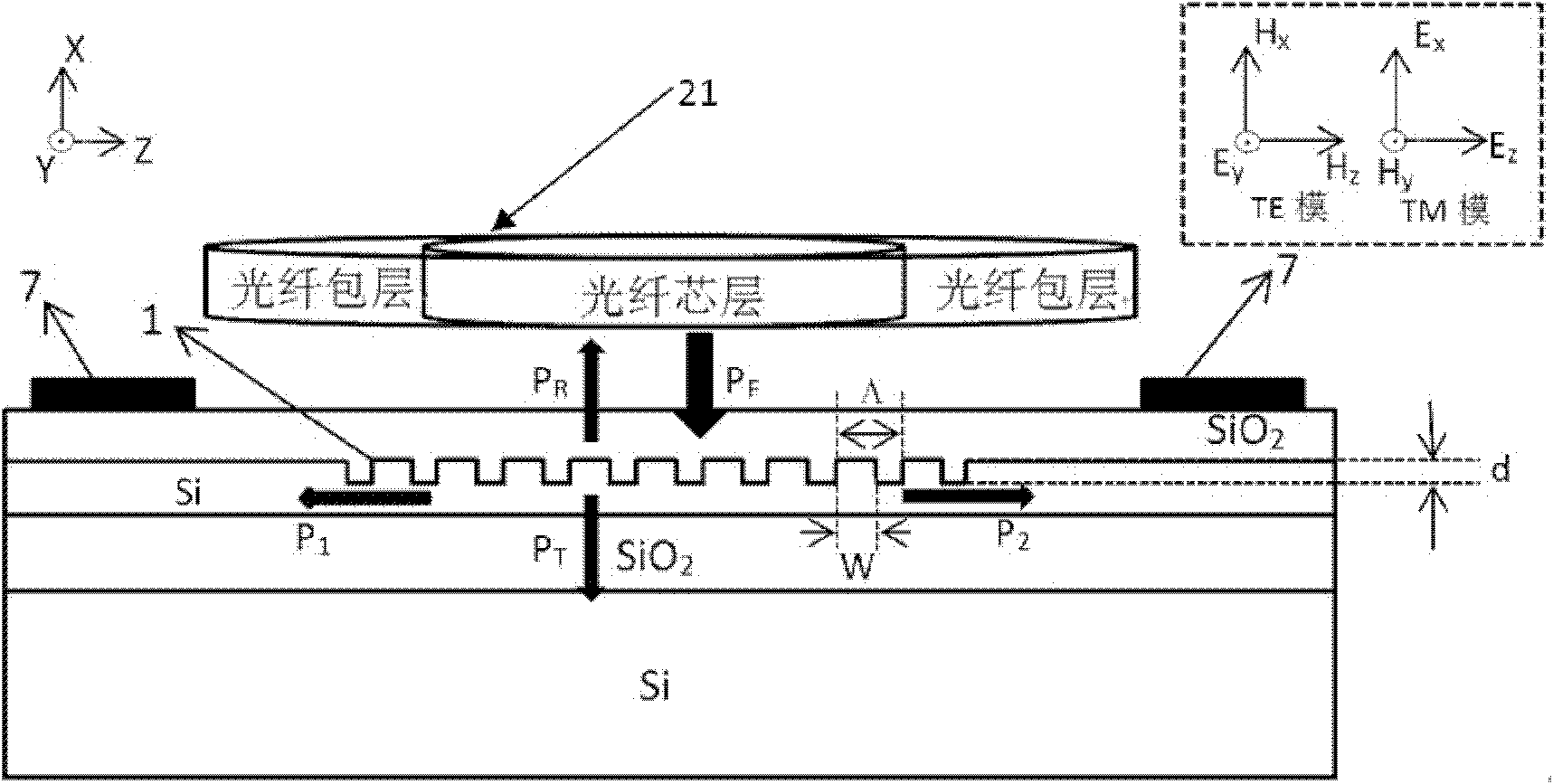

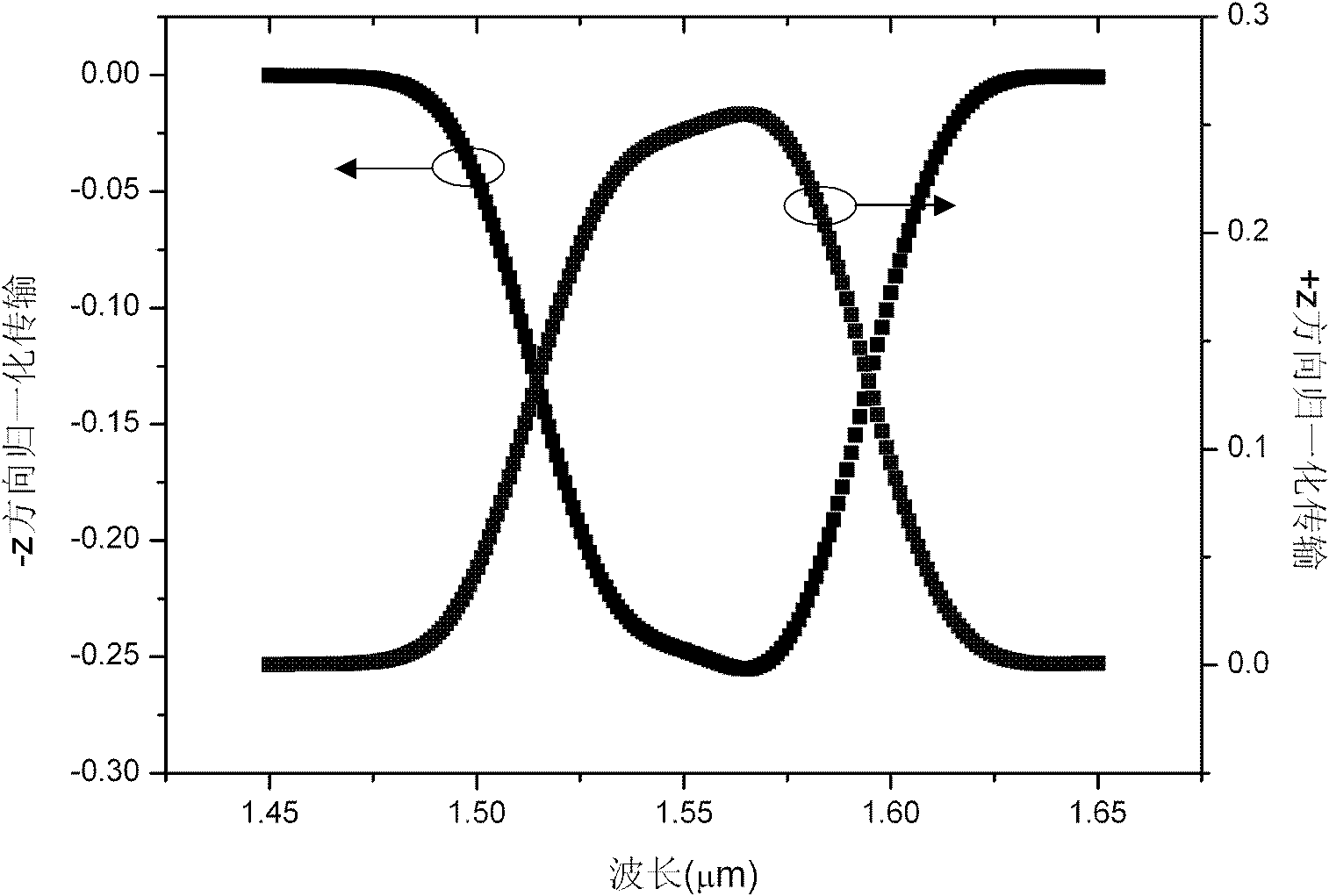

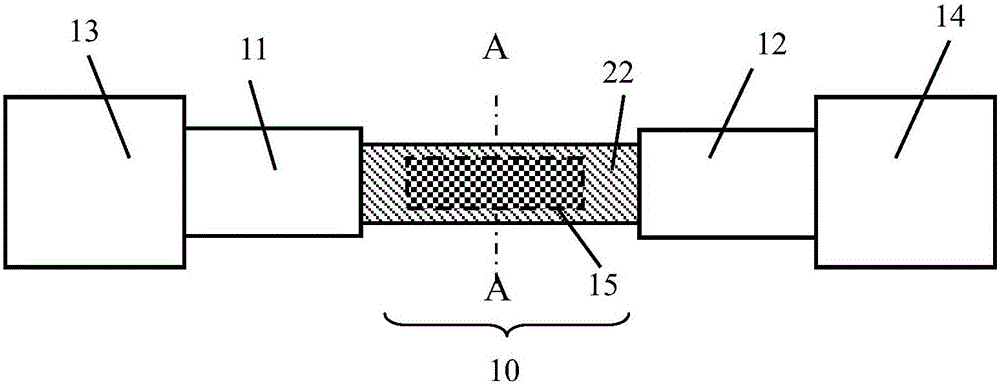

SOI (silicon on insulator) based electrooptical modulator based on symmetrical and vertical grating coupling

ActiveCN102540505AIntegration of coupling and modulation functionsEasy alignmentNon-linear opticsGratingCoplanar waveguide

The invention discloses an SOI (silicon on insulator) based electrooptical modulator based on symmetrical and vertical grating coupling, which comprises a symmetrical and vertical coupling grating, a 3-d B optical beam splitter, two mode converters, two optical phase shift arms, an optical beam combiner, two coplanar waveguide wave traveling electrodes and an annular metal alignment mark, wherein the 3-d B optical beam splitter acts as an interface of the SOI based electrooptical modulator and a single mode fiber or an input end of a coupler and the SOI based electrooptical modulator; the two mode converters act as the connection of a wide wave guide of the symmetrical and vertical coupling grating and a single mode ridge-shaped waveguide; each optical phase shift arm consists of the single mode ridge-shaped waveguide and an electric structure embedded into the single mode ridge-shaped waveguide; the optical beam combiner is used for combining the light in the two optical phase shift arms which are divided by the symmetrical and vertical coupling grating into one beam, thus phase modulation of light is converted into intensity modulation; the coplanar waveguide wave traveling electrodes are respectively positioned on the two optical phase shift arms, form electric contact with the electric structure in the optical phase shift arms, and are used for the loading and transmission of radio frequency / micro wave electrical modulation signals; and the annular metal alignment mark is positioned around the symmetrical and vertical coupling grating, and is used for the alignment of the optical fiber in an optical grating test.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

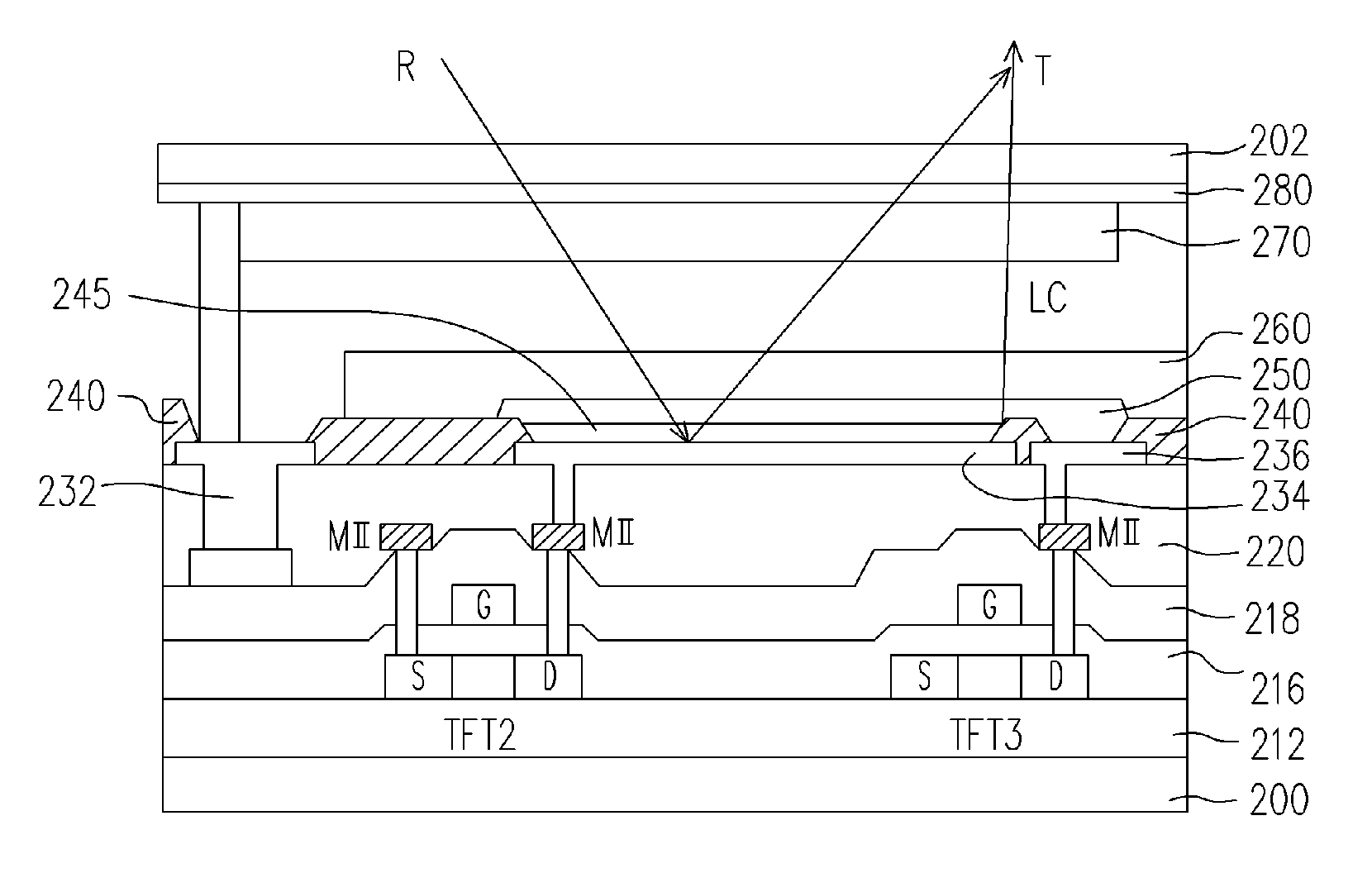

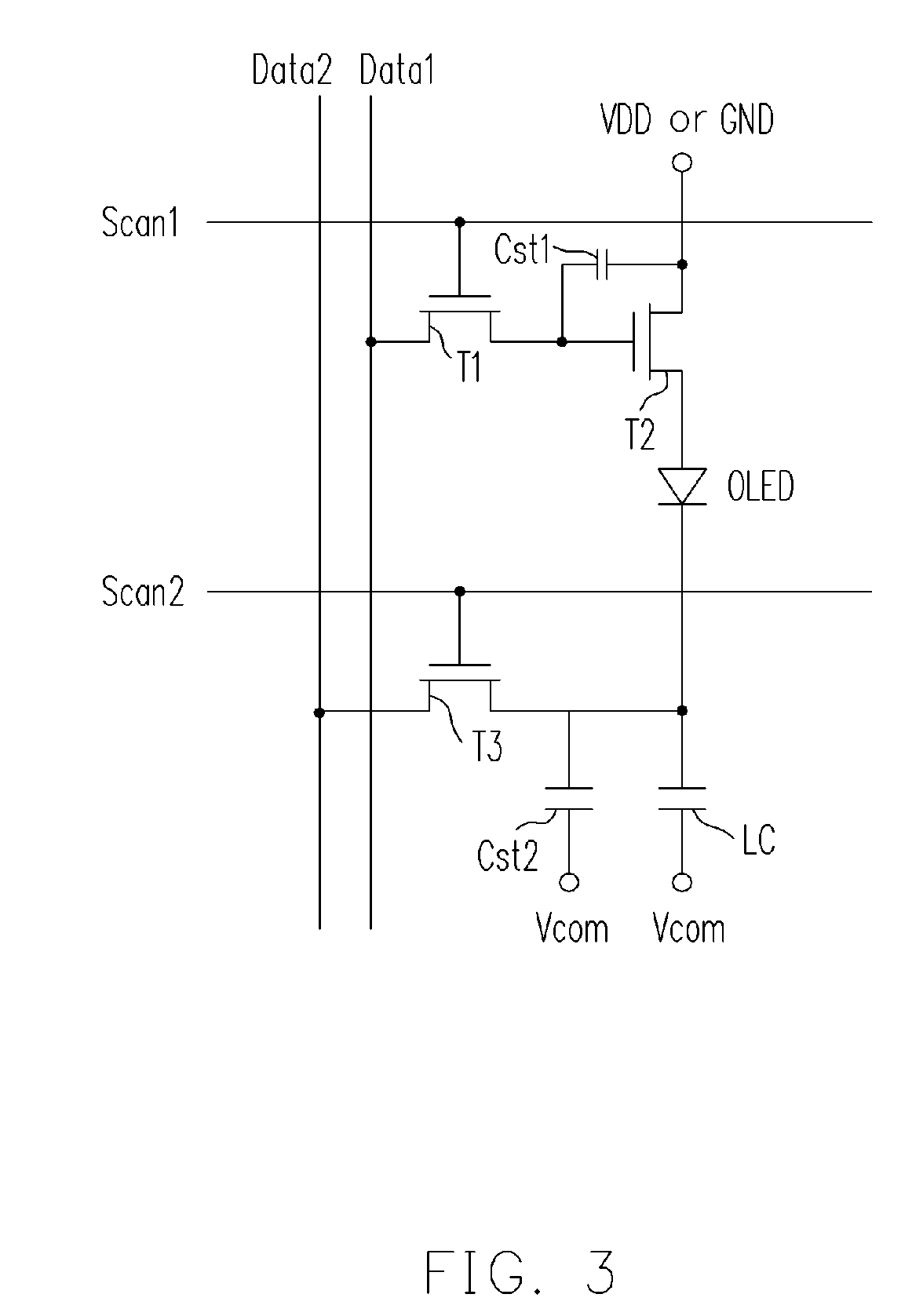

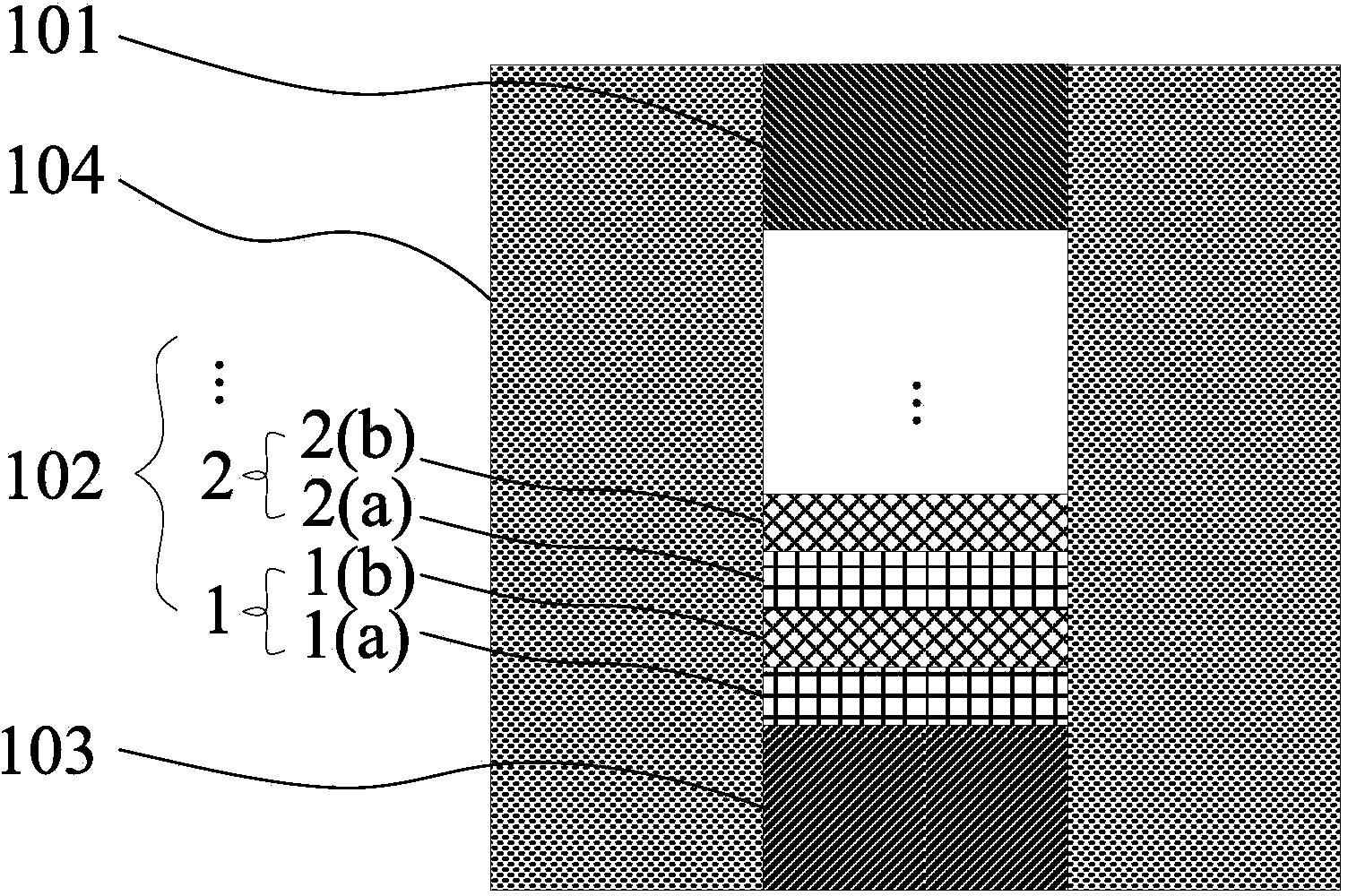

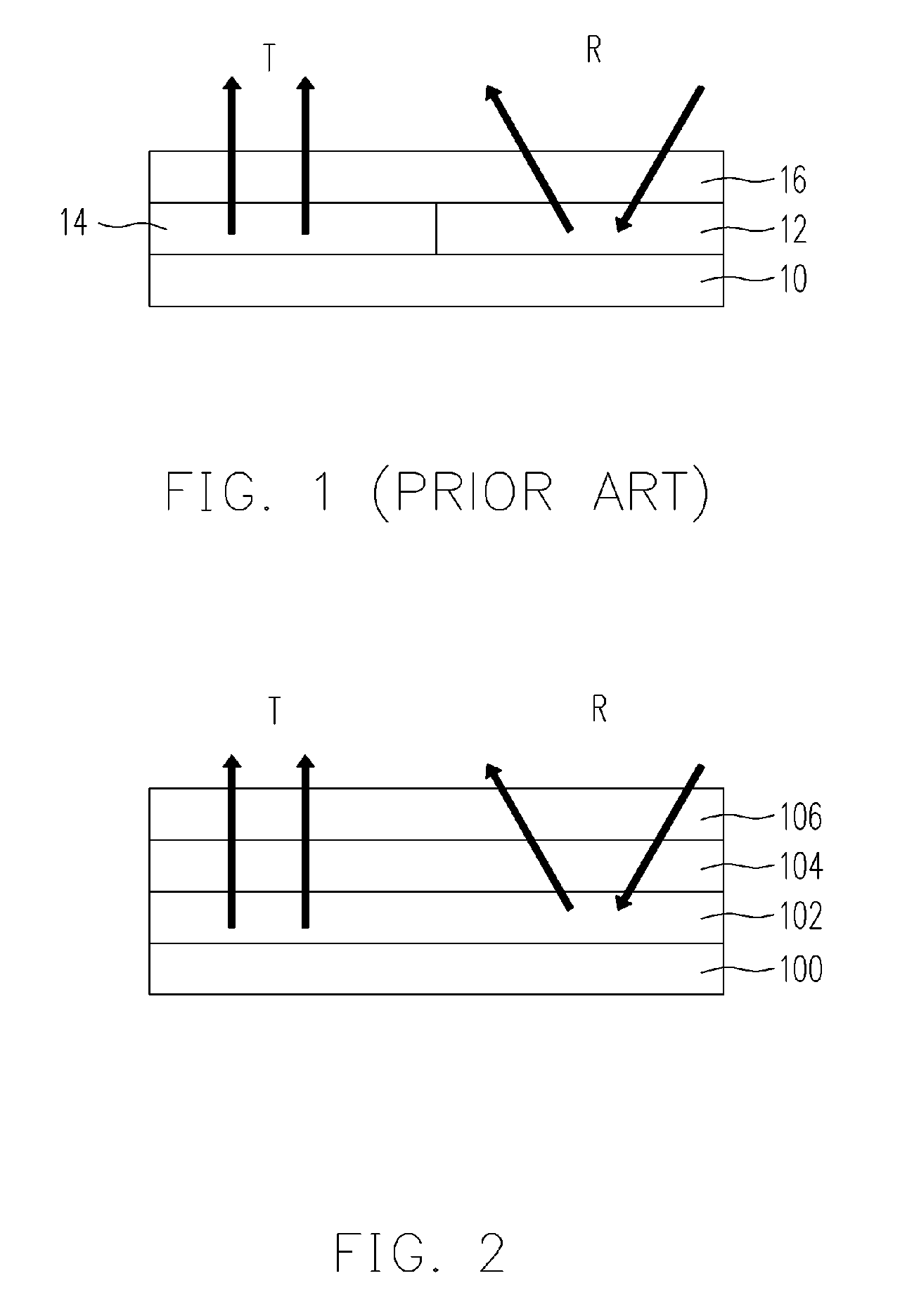

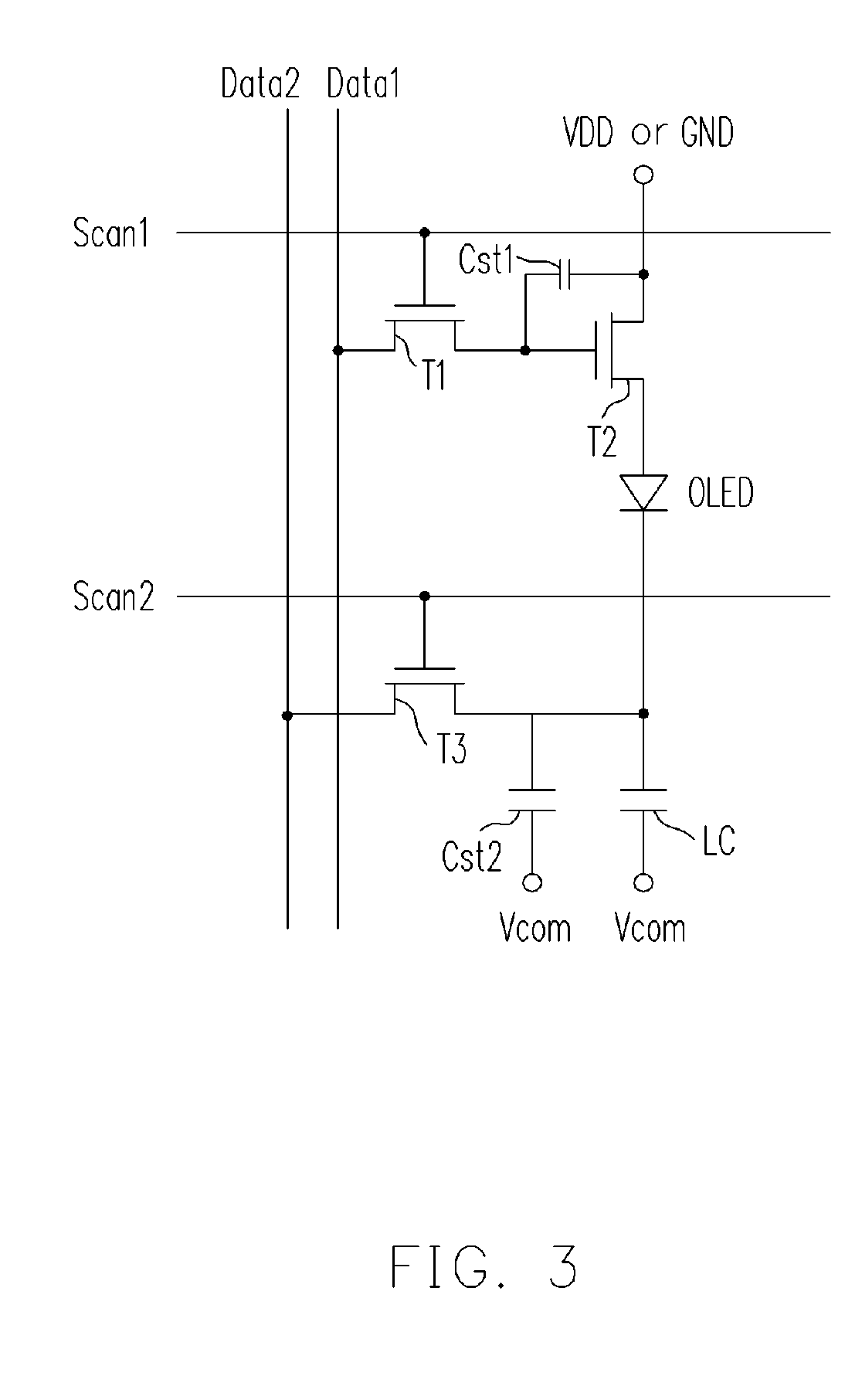

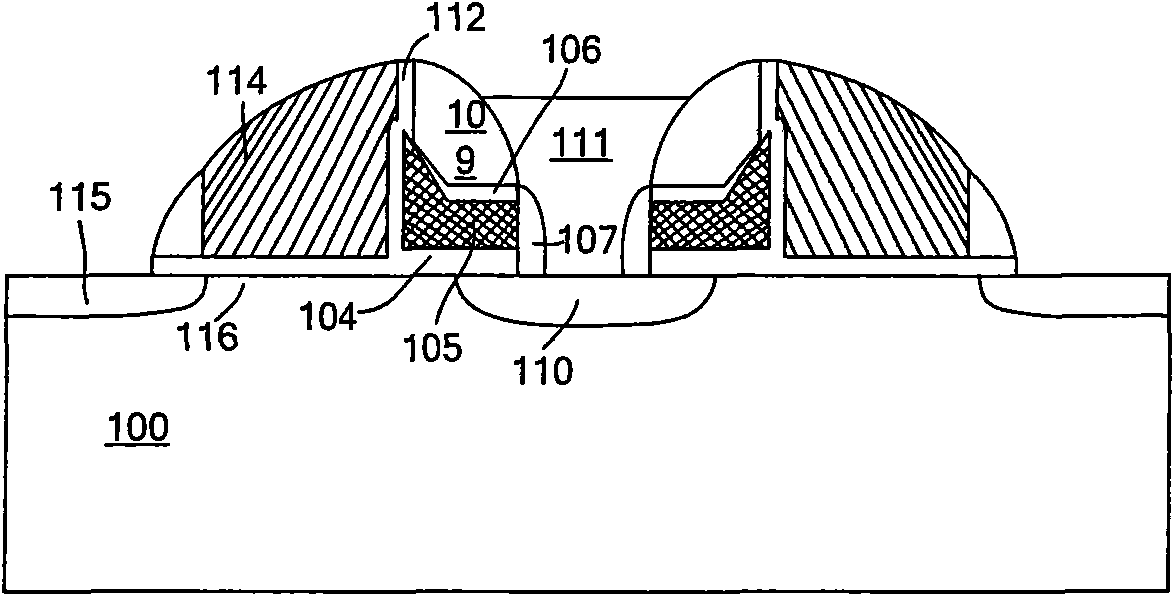

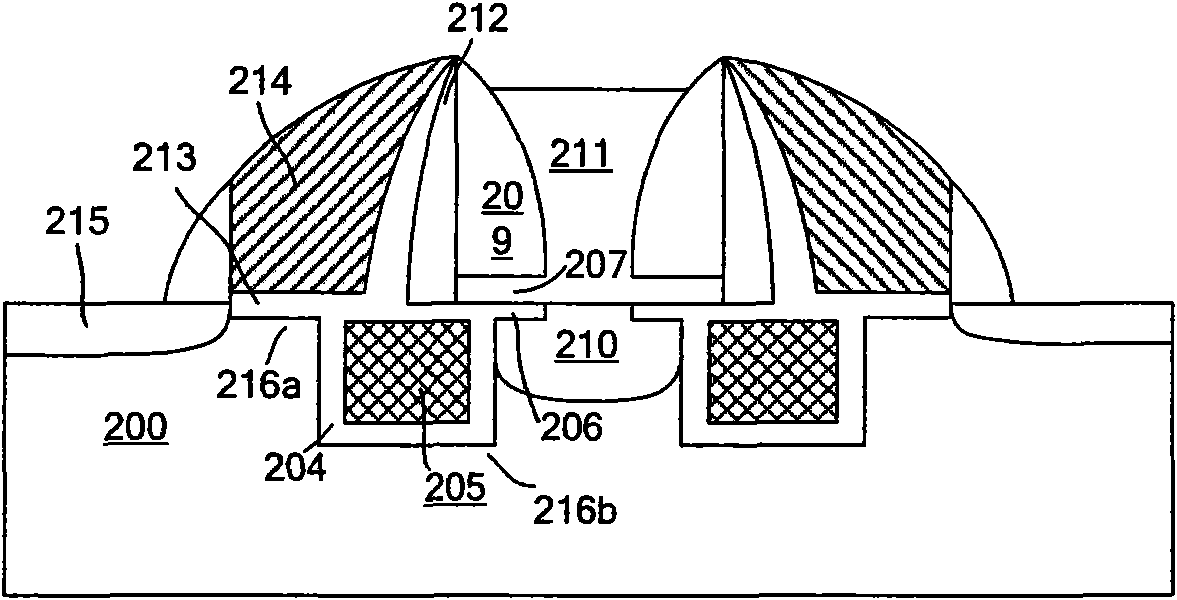

Vertical pixel structures for emi-flective display and methods for making the same

InactiveUS20070032000A1High apertureImprove energy savingStatic indicating devicesSolid-state devicesDisplay deviceComputer science

A vertical pixel structure for emi-flective display and a method thereof are provided. The vertical pixel structure has a substrate, a emitting pixel unit arranged on the substrate and a reflective pixel unit arranged on the emitting pixel unit. By using the vertical pixel structure the aperture of the display can be increased, and the power consumption can be reduced as well.

Owner:IND TECH RES INST

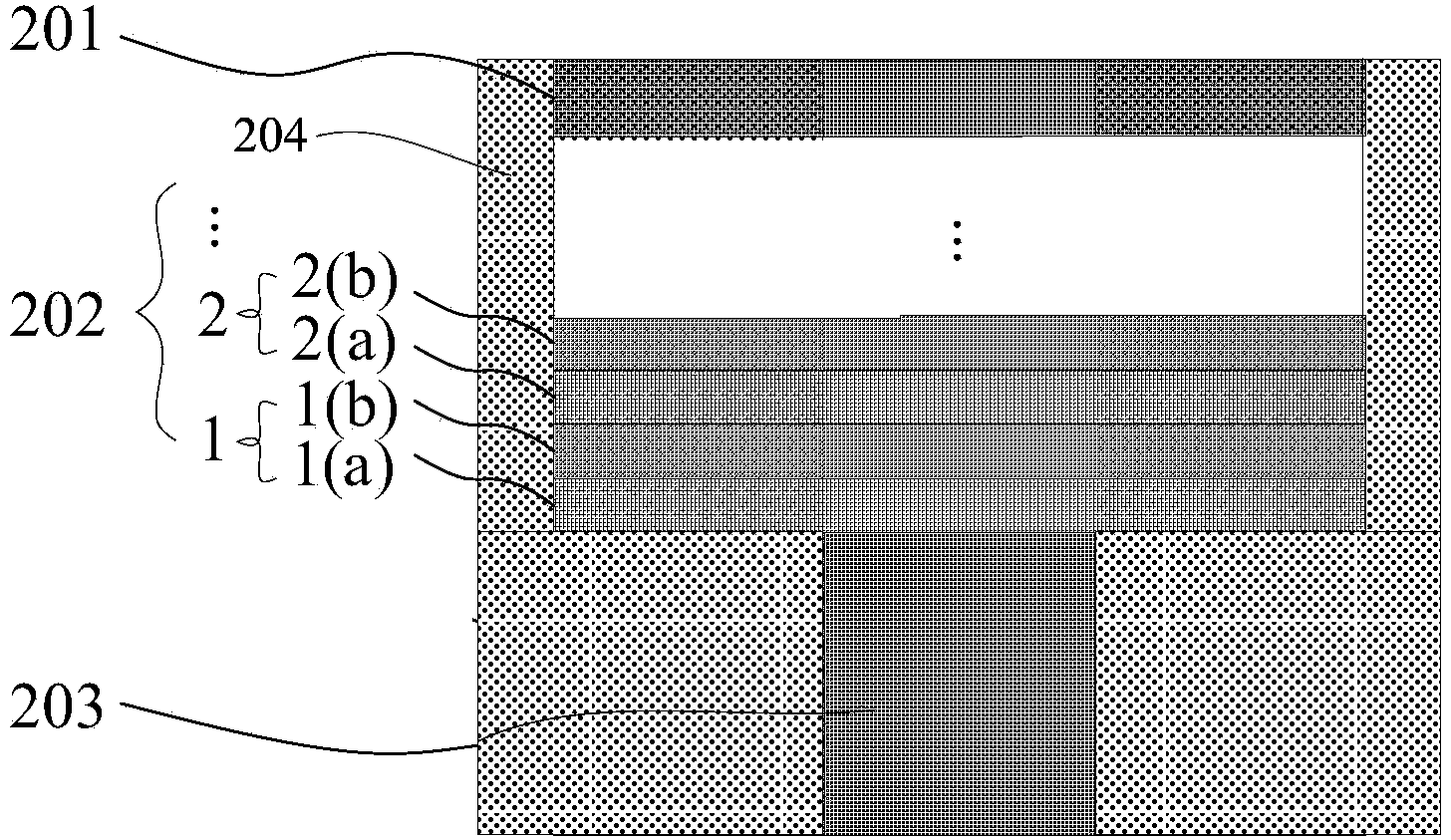

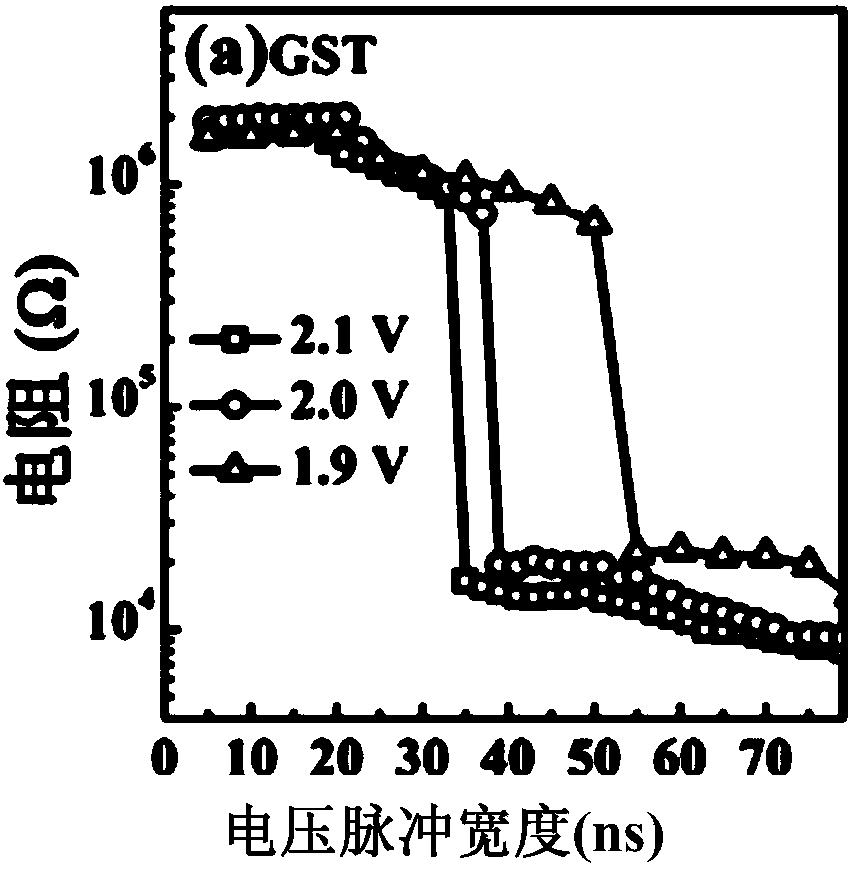

Phase change memory unit and method for manufacturing phase change memory unit

InactiveCN103794723AManufacturing process compatibleReduce power consumptionElectrical apparatusPhase-change memoryMedia layer

The invention provides a phase change memory unit and a method for manufacturing the phase change memory unit. A memory medium layer of the phase change memory unit is a superlattice thin film structure which is composed of an Sb[x]Te[1-x] layer and a Ti[y]Te[1-y] layer, and then a stable layered (Sb[x]Te[1-x])-(Ti[y]Te[1-y]) phase change material is obtained, wherein 0.4<=x<=0.8, 0.33<=y<=0.56, the thickness of the Sb[x]Te[1-x] layer is between 1 nm and 10 nm, and the thickness of the Ti[y]Te[1-y] layer is between 1 nm and 10 nm. The phase-change mechanism of the superlattice (Sb[x]Te[1-x])-(Ti[y]Te[1-y]) phase change material manufactured with the method is completely different from that of a traditional Ge-Sb-Te phase change material, and thus an obtained phase change memory device has the advantages of being lower in power consumption, higher in phase change speed, higher in retentivity, longer in service life and the like.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

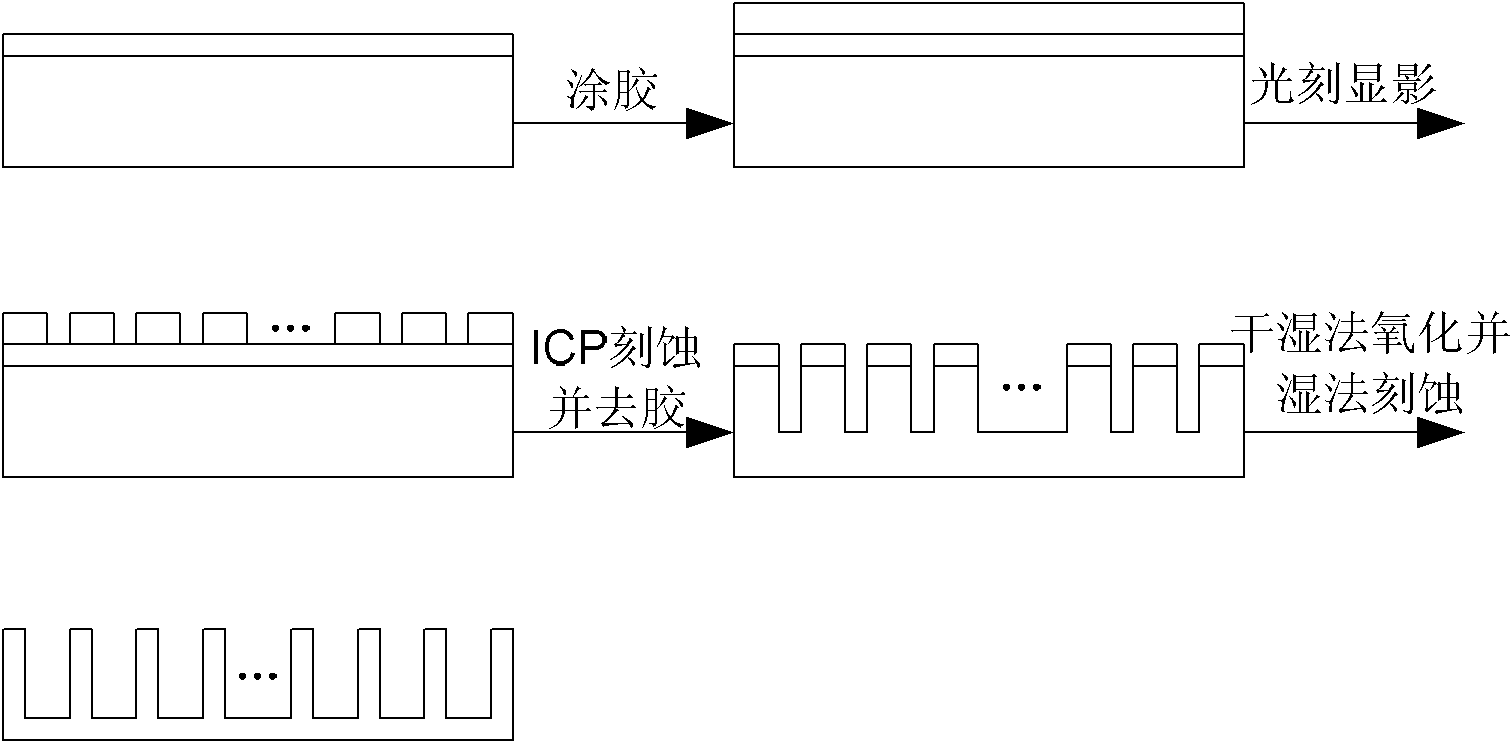

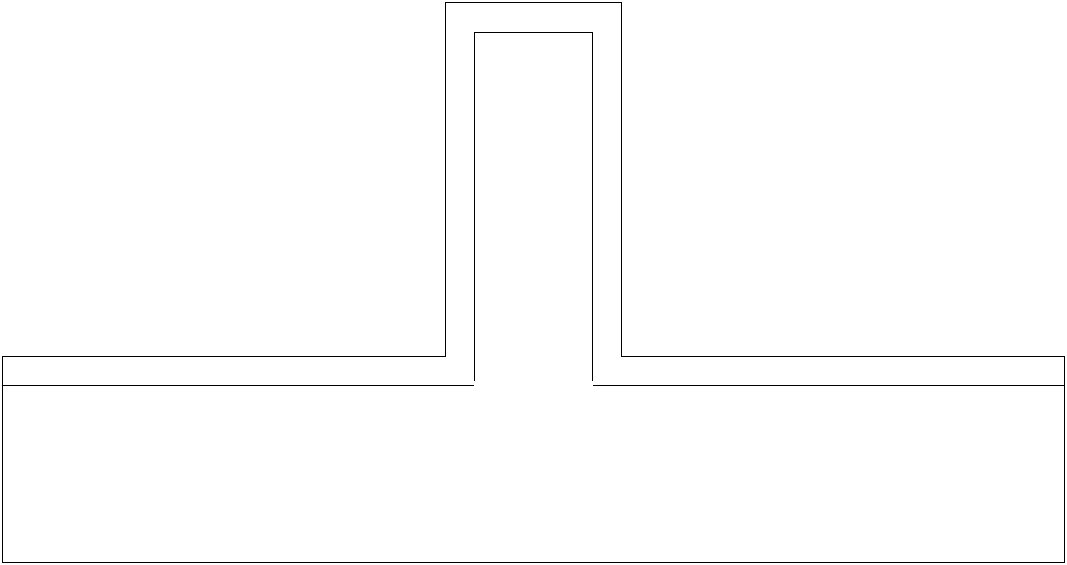

Preparation method of silicon nano-wire field-effect transistor

InactiveCN102214586AEasy to controlSmooth and steep etch effectSemiconductor/solid-state device manufacturingNanotechnologySilicon nanowiresField effect

The invention relates to the field of microelectronic apparatus manufacture, and discloses a top-down preparation method of a vertical silicon nano-wire gate field-effect transistor. The vertical silicon nano-wire gate field-effect transistor includes a semiconductor substrate, a nano-wire channel region vertically arranged on the semiconductor substrate and an annular grid conductive layer arranged out of the channel. The nano-wire channel region is provided with an active conductive layer; the upper part is doped with n impurity to serve as a source end n area; the semiconductor substrate contacting with the bottom of the drain conductive layer is doped with n impurity to serve as a drain end n area; and a non-symmetrical Halo-doped structure p+ region is added between the source end and the channel. The method for preparing the vertical silicon nano-wire gate field-effect transistor can well control the consistency of the position and size of the nano-wire, thus simplifying the manufacture process and reducing the manufacture cost.

Owner:XI AN JIAOTONG UNIV

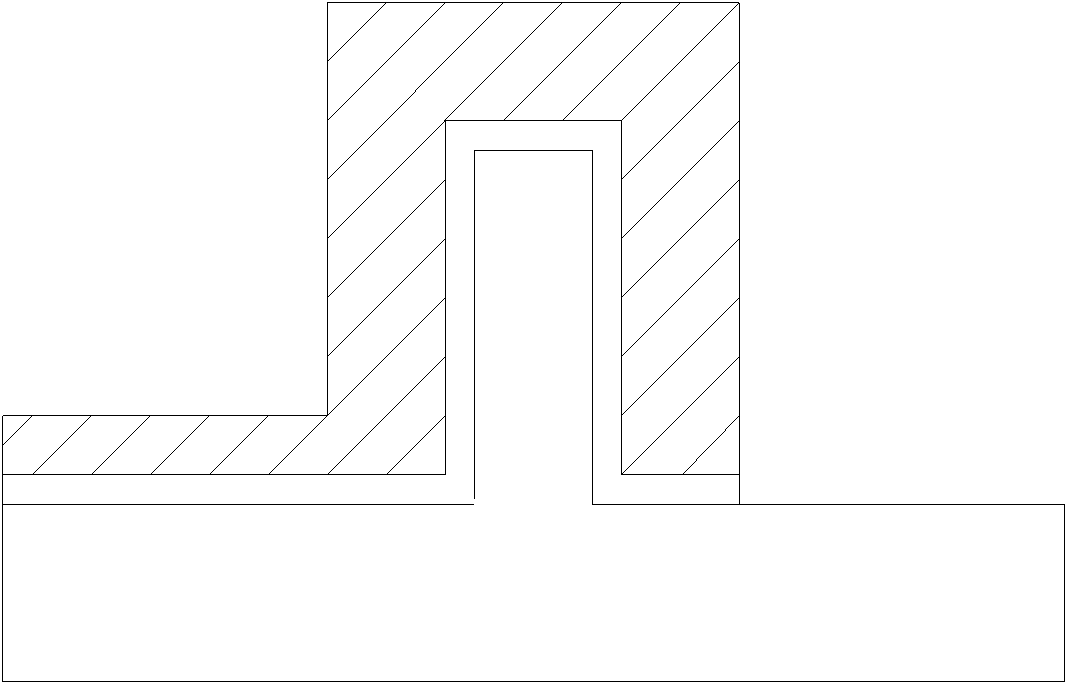

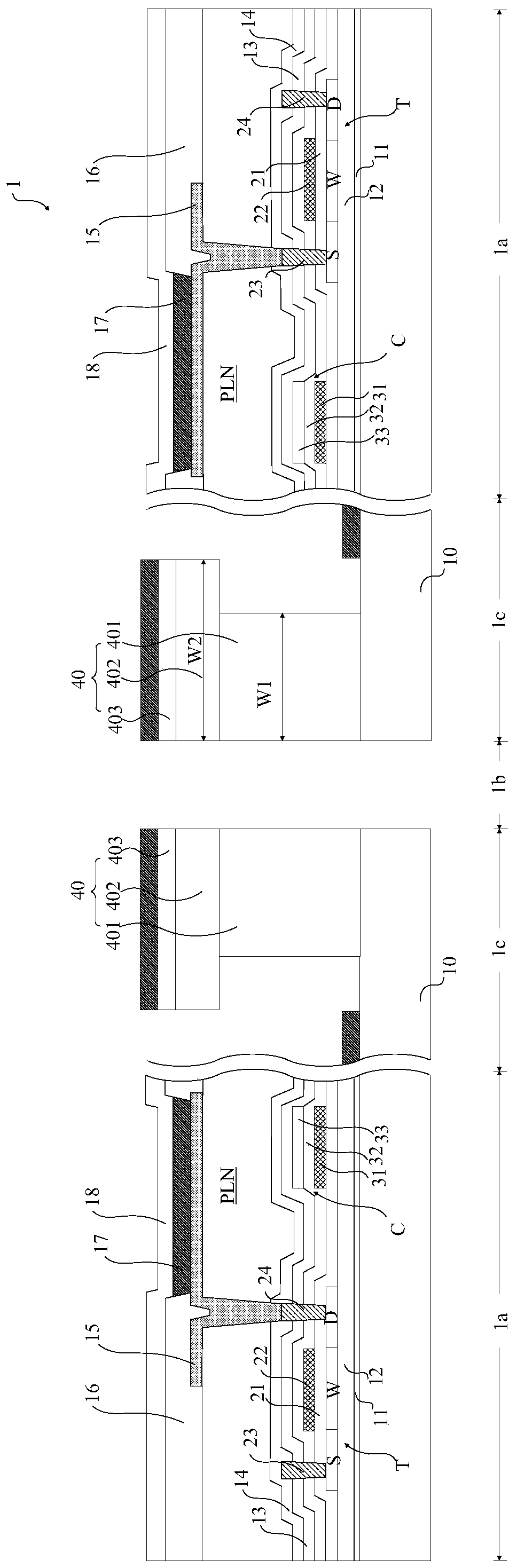

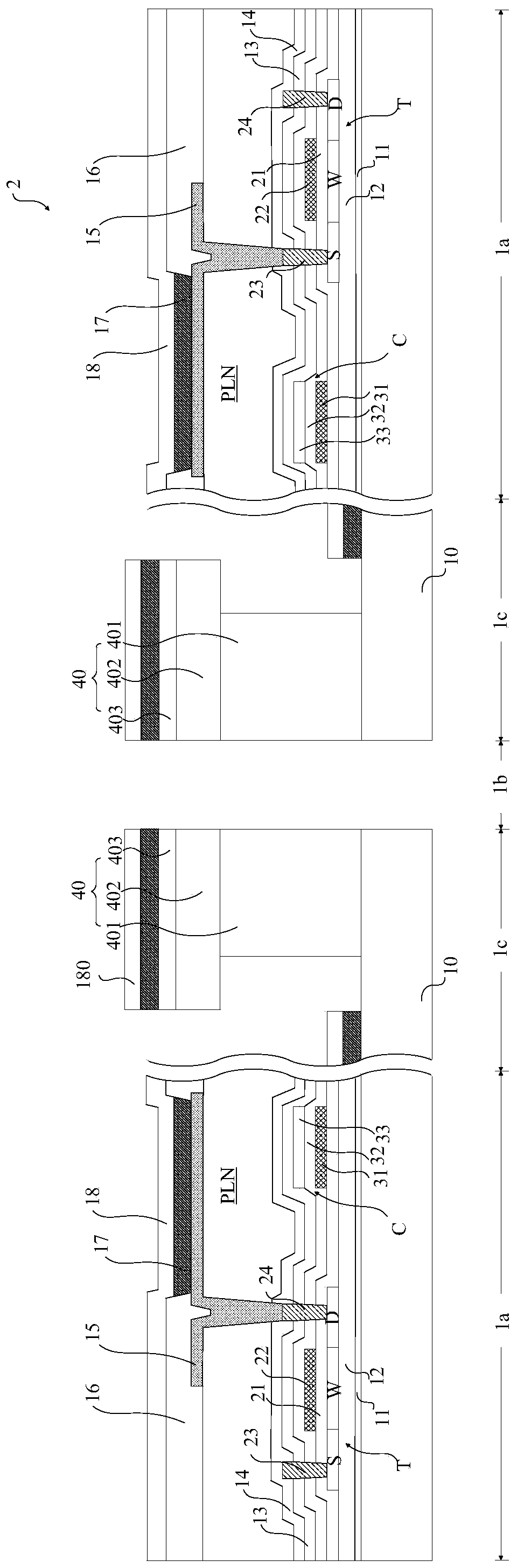

Display device and display substrate thereof

PendingCN110416282AGood partitionImprove pass rateSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOxygen

The invention provides a display device and a display substrate thereof. The display substrate comprises a display area, a porose area, and a partition area between the display area and the porose area. The partition area is provided with at least one partition ring surrounding the porose area, and is used for partitioning an organic light-emitting material layer. The partition ring comprises at least a support portion and a partition portion. The partition portion is provided with a tensile stress layer used for applying tensile stress to the partition portion. When the organic light-emittingmaterial layer is vapor-deposited, partial section of the partition portion in the partition ring is suspended. The partitioning effect on the organic light-emitting material layer is good, and external water and oxygen can be prevented from entering the display area from the opening. In addition, the partition portion can automatically block the organic light-emitting material layer. The use oflaser burning to remove the organic light-emitting material layer around the porose area is avoided. A hot process is omitted. The spacing between the porose area and the display area is shortened. The border of the porose area is reduced. Third, the tensile stress layer can apply tensile stress to the partition portion to prevent the suspended partition portion from collapsing and falling off. The partitioning performance of the partition portion is reliable.

Owner:YUNGU GUAN TECH CO LTD

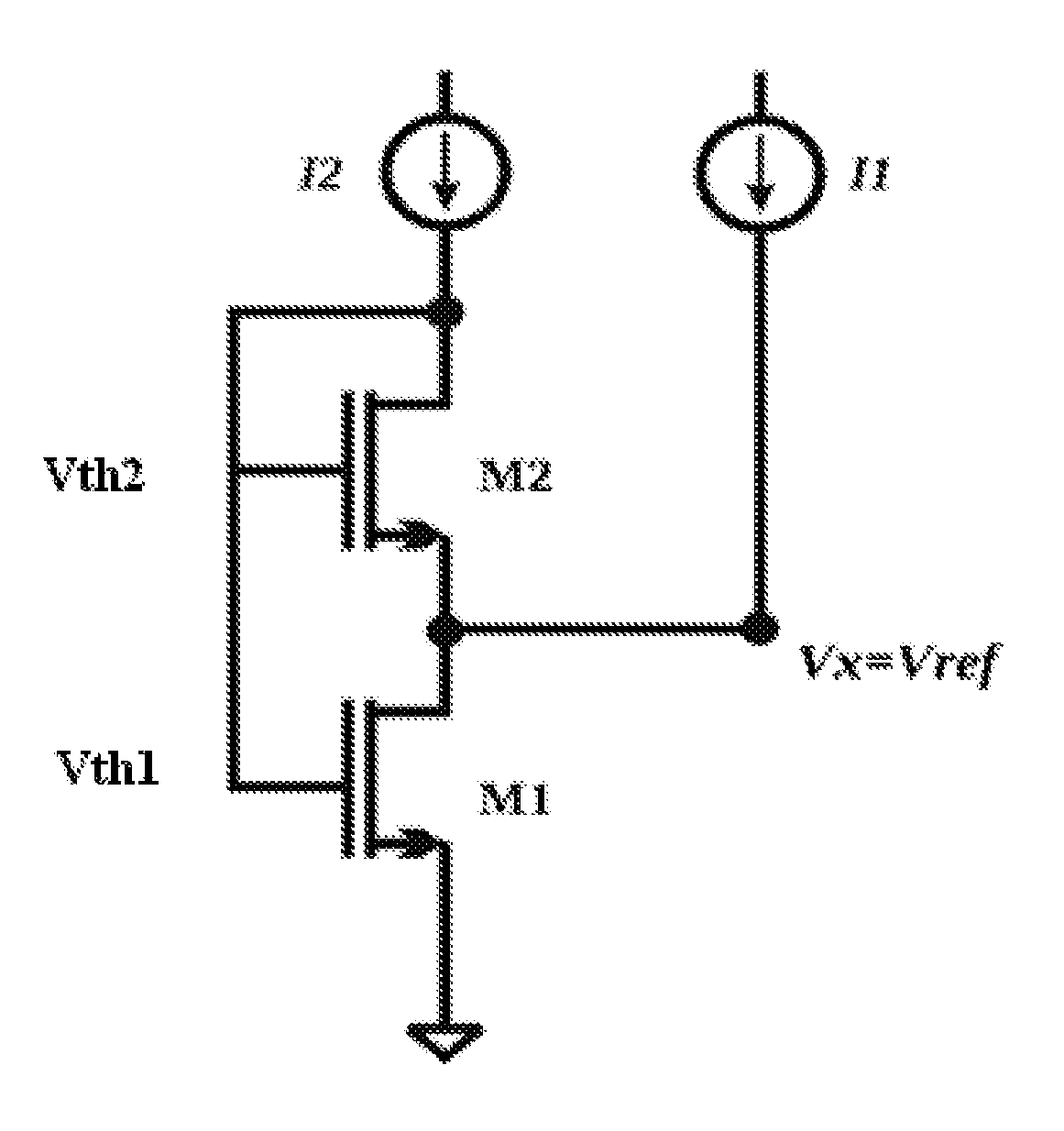

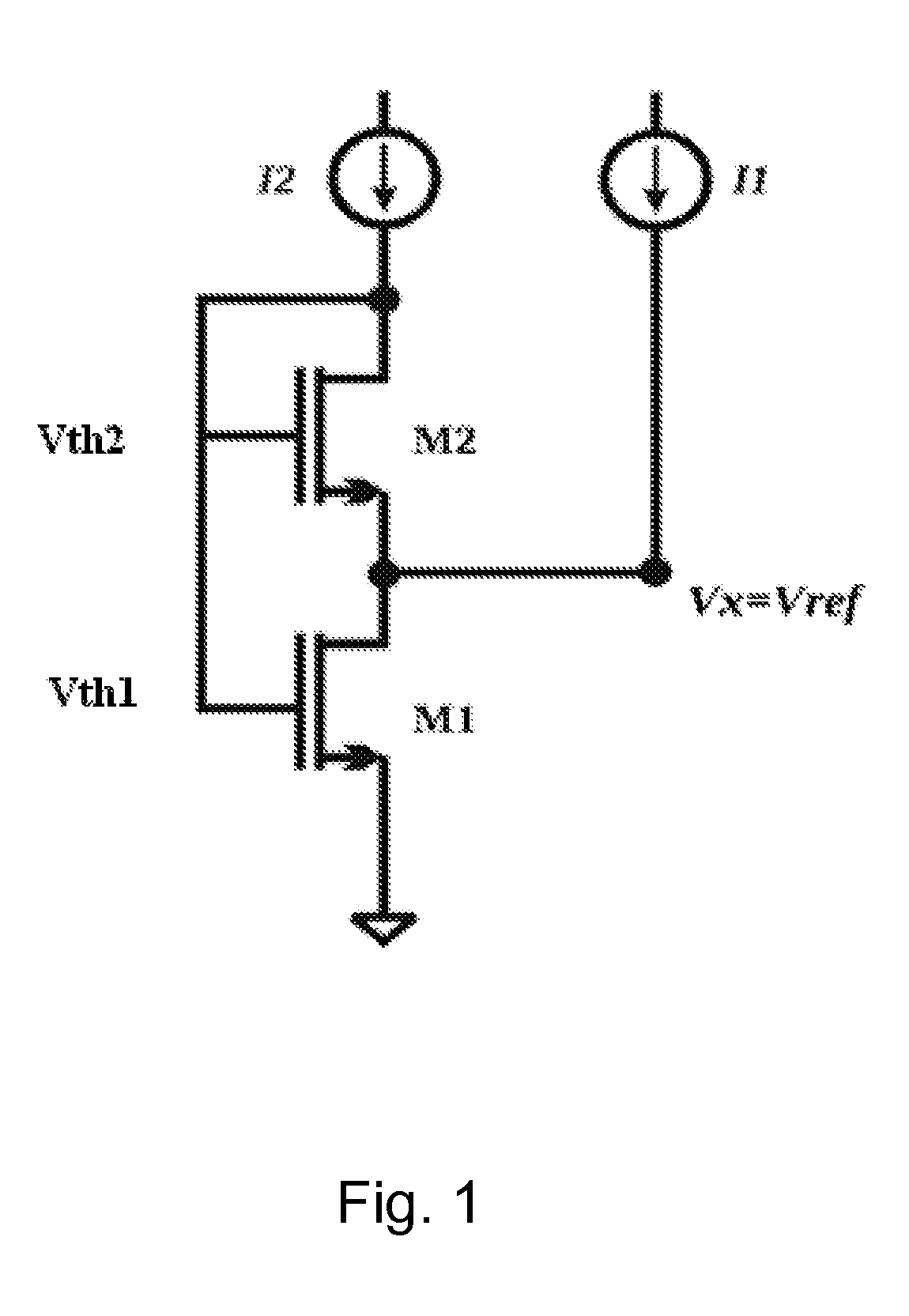

Temperature-Compensated Reference Voltage System With Very Low Power Consumption Based On An SCM Structure With Transistors Of Different Threshold Voltages

ActiveUS20150234401A1Eliminate inconvenienceReduce power consumptionElectric variable regulationCMOSPower flow

A simple SCM (Self Cascode MOSFET) structure to generate a sub-1V reference voltage in the SCM intermediate node. The structure requires only 2 transistors to create a temperature-compensated reference voltage. When sized correctly, the transistors in the SCM will operate both at weak, moderate or strong inversion, and in the saturation region or saturation and triode regions, providing good correspondence and low part to part variation. The following proposal innovates by operating with supply voltages on a broad variation range, from 3.6V through below 1V (sub-1V operation), with bias currents in the range of tens of nA (nano Amperes) and temperature variation smaller than ±1% from −40° C. through 85° C. This is an extremely low cost implementation (in terms of area and complexity), compatible with standard CMOS manufacturing processes, and very robust (in terms of fab-to-fab transference, technology mapping, and also well controlled part-to-part variation).

Owner:CENT NACIONAL DE TECHA ELECTRONICSA AVANCADA

Manufacturing method for soft magnetic core spiral micro-inductor

ActiveCN102789967AIncrease inductanceHigh quality factorSemiconductor/solid-state device manufacturingInductances/transformers/magnets manufactureManufacturing technologyInductor

The invention relates to a manufacturing method for a soft magnetic core spiral micro-inductor, which is characterized by integrating a NiFe-AlOx soft magnetic core spiral micro-inductor and comprising the following steps: 1) preparing lower-layer metal of an inductor; 2) preparing a first benzo-cyclobutene BCB dielectric layer; 3) preparing a NiFe-AlOx film; 4) preparing a second benzo-cyclobutene BCB dielectric layer; 5) preparing a benzo-cyclobutene BCB dielectric through hole; and 6) preparing upper-layer metal of the inductor. The manufacturing method has the advantages that the soft magnetic core spiral micro-inductor for an RF / MMIC (Radio Frequency / Monolithic Microwave Integrated Circuit) is prepared by integrating a soft magnetic material with an MMIC micro-inductor. Compared with the micro-inductor free from the magnetic core, the soft magnetic core spiral micro-inductor has the advantages: (1) the inductance volume is greatly increased; (2) the quality factor is certainly increased; and (3) the whole technology is compatible with the manufacturing technology of a GaAs and GaN MMIC.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

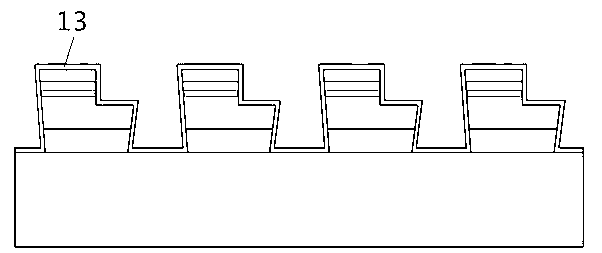

Method for bridging electrodes of LED light-emitting units isolated by deep trenches

InactiveCN103236475AImprove yieldReduce moisture absorption performanceSolid-state devicesSemiconductor devicesEngineeringUnit structure

The invention provides a method for bridging electrodes of LED light-emitting units isolated by deep trenches. The method is specifically implemented for large LED chips with a plurality of light-emitting units isolated by deep trenches. The method includes steps of depositing first passivation layers; performing spin-coating for liquid insulating materials to fill the liquid insulating materials in the isolation trenches among the light-emitting units and forming a flat film on the surface of a chip; curing the liquid insulating materials at a high temperature; etching the film formed by the insulating materials so as to expose the passivation layers on surfaces of the light-emitting units and enabling surfaces, which are positioned at the isolation trenches, of the insulating materials to be flush with surfaces of the passivation layers; depositing second passivation layers to seal parts, which are positioned at the isolation trenches, of the insulating materials in the passivation layers; and etching the passivation layers and manufacturing electrode grooves; depositing metal, manufacturing the electrodes by a lift-off technology and manufacturing connecting bridges of the electrodes on upper surfaces of the passivation layers. The method has the advantages the electrode bridging yield is increased, and the method is applicable to light-emitting unit structures with rectangular, regularly trapezoidal or reversely trapezoidal cross sections, and is particularly applicable to isolation trenches with high depth-to-width ratios.

Owner:SOUTH CHINA UNIV OF TECH

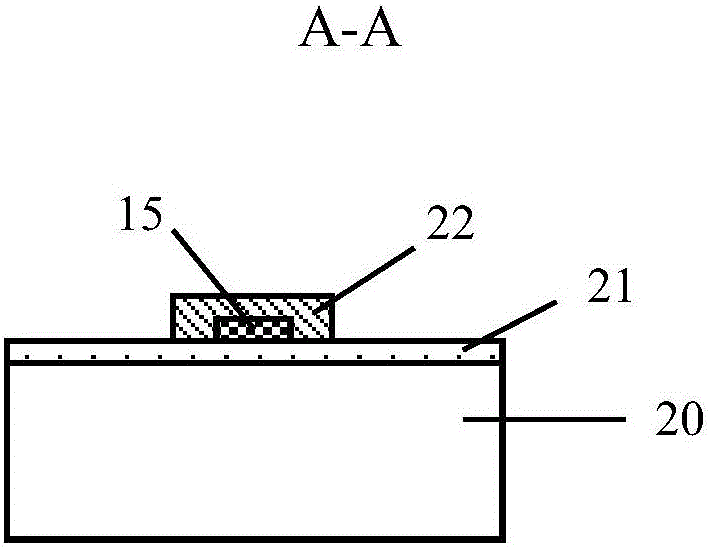

Non-refrigerated infrared detection focal plane device

InactiveCN102226721AImprove infrared absorptionImprove detection efficiencyPyrometry using electric radation detectorsPiezoelectric/electrostrictive devicesResonant cavityBridge deck

The invention, which belongs to the technical field of the non-refrigerated infrared detection, relates to a non-refrigerated infrared detection focal plane device. The device comprises a substrate structure, a support structure, and a bridge deck structure. The bridge deck structure is supported on a substrate by bridge legs and bridge piers, an infrared resonant cavity is formed between an infrared absorbed layer film and a reflecting layer. And a thermo-sensitive layer film is on a surface of the infrared absorbed layer film outside the infrared resonant cavity. According to the invention, a customary thinking employed in the invention of a present device structure is broken through; a position relation of the infrared absorbed layer film and the thermo-sensitive layer film within the bridge deck structure is inversed, so that the thermo-sensitive layer film is arranged on the surface of the infrared absorbed layer film outside the infrared resonant cavity, and thus an infrared absorptivity of the infrared detection focal plane device is increased; and therefore, a detection efficiency of the non-refrigerated infrared detection focal plane device is further improved. Furthermore, an anti-reflection film is not required by the device, so that the device structure is simplified to some extent and device cost is also reduced appropriately.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

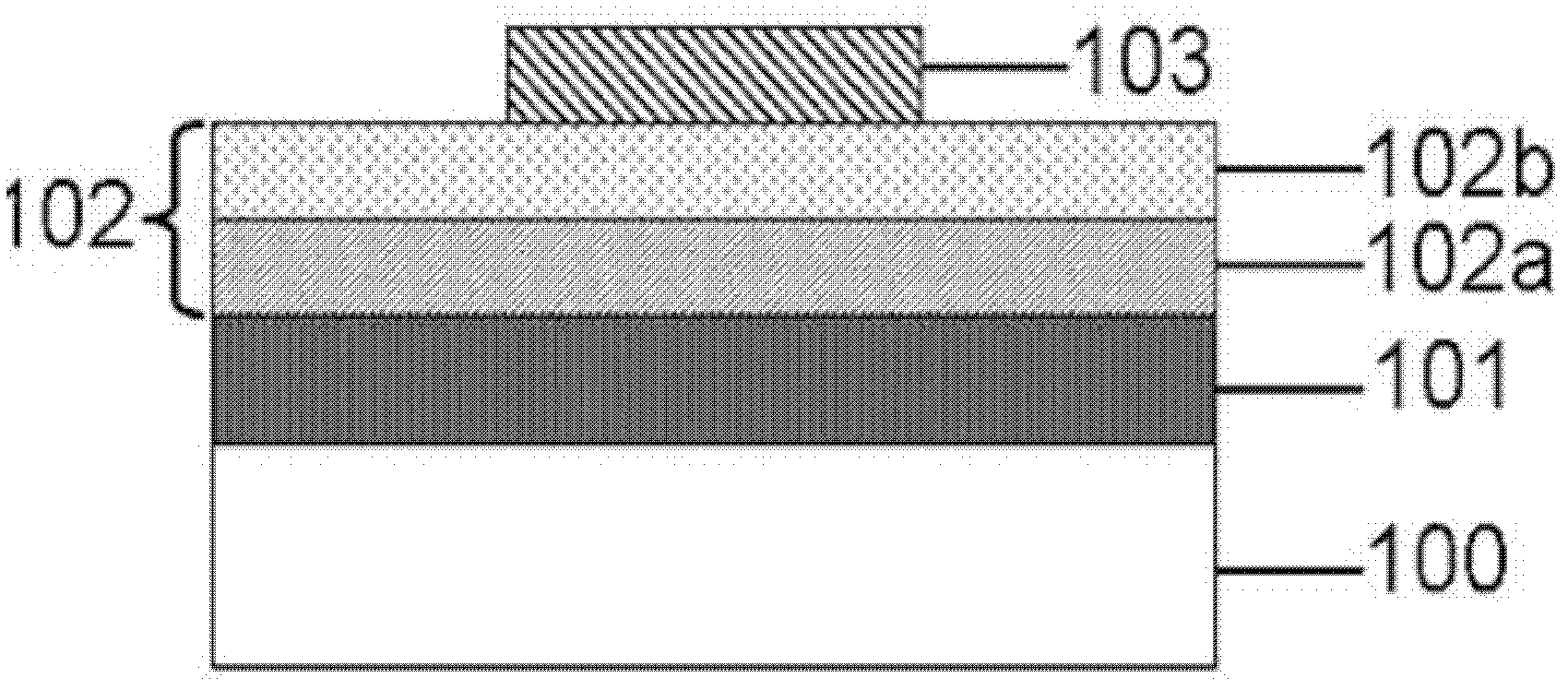

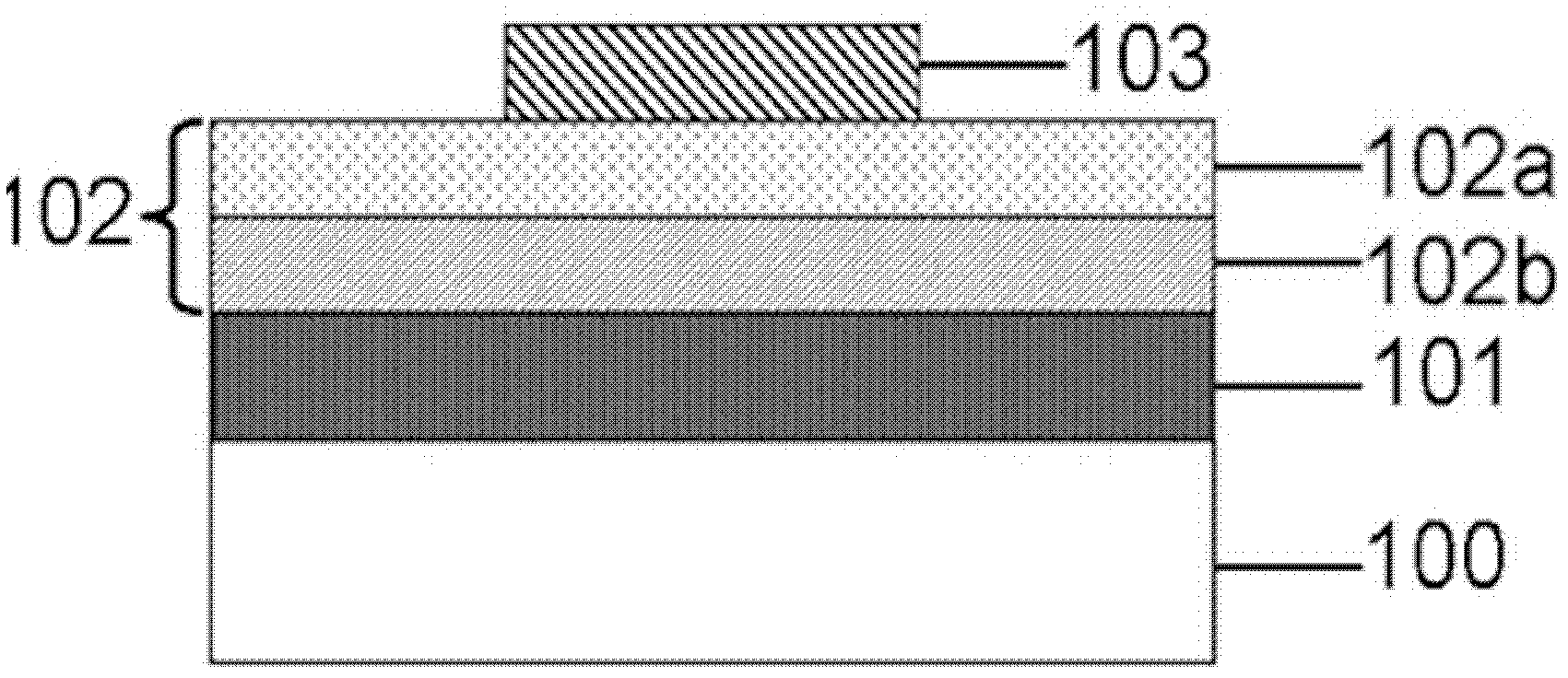

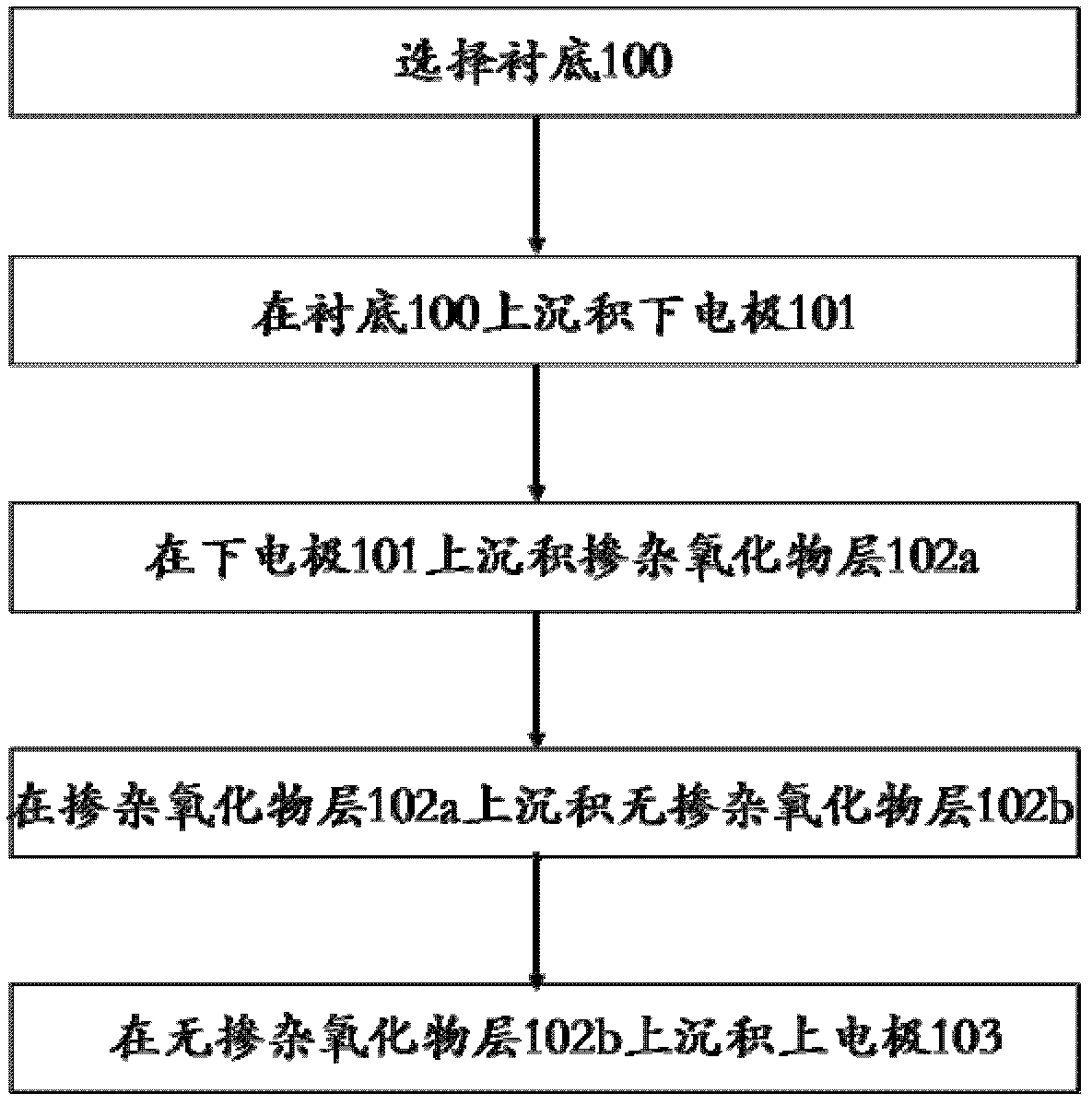

Memristor device and manufacturing method thereof

InactiveCN102931346AImplement storageEasy to prepareElectrical apparatusCMOSManufacturing technology

The invention discloses a memristor device and a manufacturing method thereof. The memristor device comprises a substrate, a lower electrode formed above the substrate, a memory storage layer formed above the lower electrode and an upper electrode formed above the memory storage layer, wherein the memory storage layer comprises two layers of oxide materials with different oxygen contents. The method for manufacturing the memristor device comprises the following steps of: growing a conducting material on the substrate as the lower electrode; growing the memory storage layer on the lower electrode, wherein the memory storage layer comprises two layers of oxide materials, and the oxygen contents of the two layers of oxide materials are different; and growing a conducting material on the memory storage layer as the upper electrode. The manufacturing method provided by the invention is simple, and the manufacturing technology is compatible with the traditional CMOS (Complementary Metal Oxide Semiconductors) technology and has certain application prospect in the field of memories.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Tunneling field effect transistor and preparation method thereof

ActiveCN102201450AManufacturing process compatibleIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorPhysics

The invention discloses a tunneling field effect transistor and a preparation method thereof. The transistor comprises: a semiconductor substrate, a first channel region and a second channel region, a first gate stack zone, a second gate stack zone, a first source zone, a leakage zone, a second source zone a third insulating layer and a source electrode S, wherein the first conducting layer in the first gate stack zone is connected with the second conducting layer of the second gate stack outside the channel region to form a interdigital grid; the electrodes of the first source zone and second source zone, the drain electrode in the leakage zone and the gate electrode G on the interdigital grid are formed in the third insulating layer. According to the invention, the work current of the tunneling field effect device provided in the invention is a tunneling current and the work current is a current of an MOS (Metal-Oxide-Semiconductor) field effect transistor. The driving current is substantially improved. Meanwhile, the manufacture technology is compatible with the tradition technology and the area is saved, because the interdigital structure is adopted and the first source zone plays a role in substrate lead-out.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

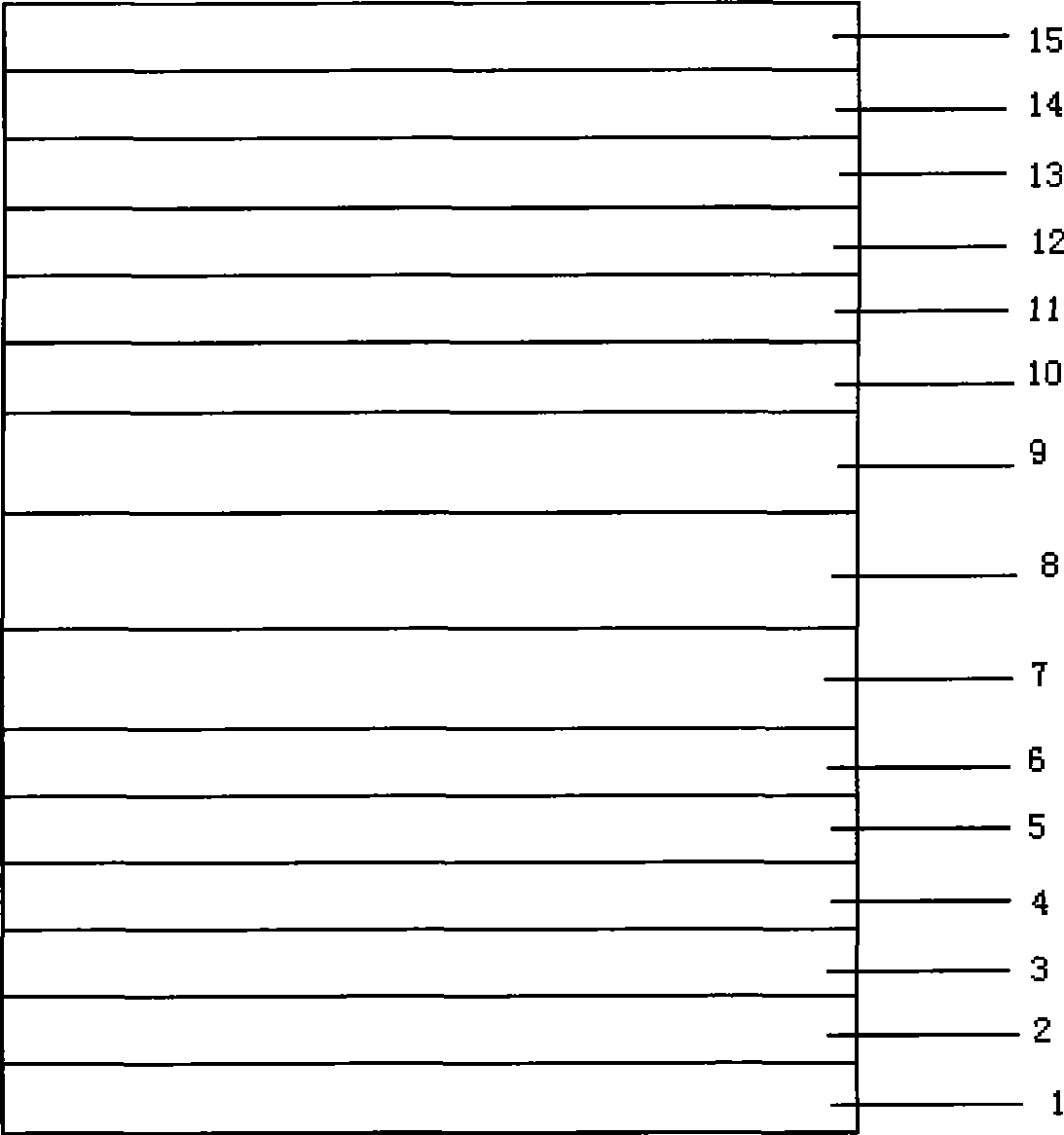

Three-junction solar cell

InactiveCN101499493ABroad absorption spectrumHigh currentPhotovoltaic energy generationSemiconductor devicesSemiconductor materialsQuantum well

The invention provides a solar cell which comprises a quantum well structure; the cell structure comprises from bottom to top a back electrode, a bottom cell consisting of a p-typed germanium substrate and an n-typed germanium epitaxial layer, an n-typed GaAs layer transition layer, a lower tunneling junction, a middle cell consisting of a p-typed GaAs layer, the quantum well structure and an n-typed GaAs layer, an upper tunneling junction, a top cell consisting of a p-typed GaInP layer and an n-typed GaInP layer, an anti-reflection film and an upper electrode, wherein, the quantum well structure is divided into a quantum well layer which is made by three to five clusters of semiconductor materials and a barrier layer; and the solar cell can extend the absorption spectra of the middle cell, improve the current matching among three sub-cells, and enhance the conversion efficiency of the cell.

Owner:SOUTHEAST UNIV +1

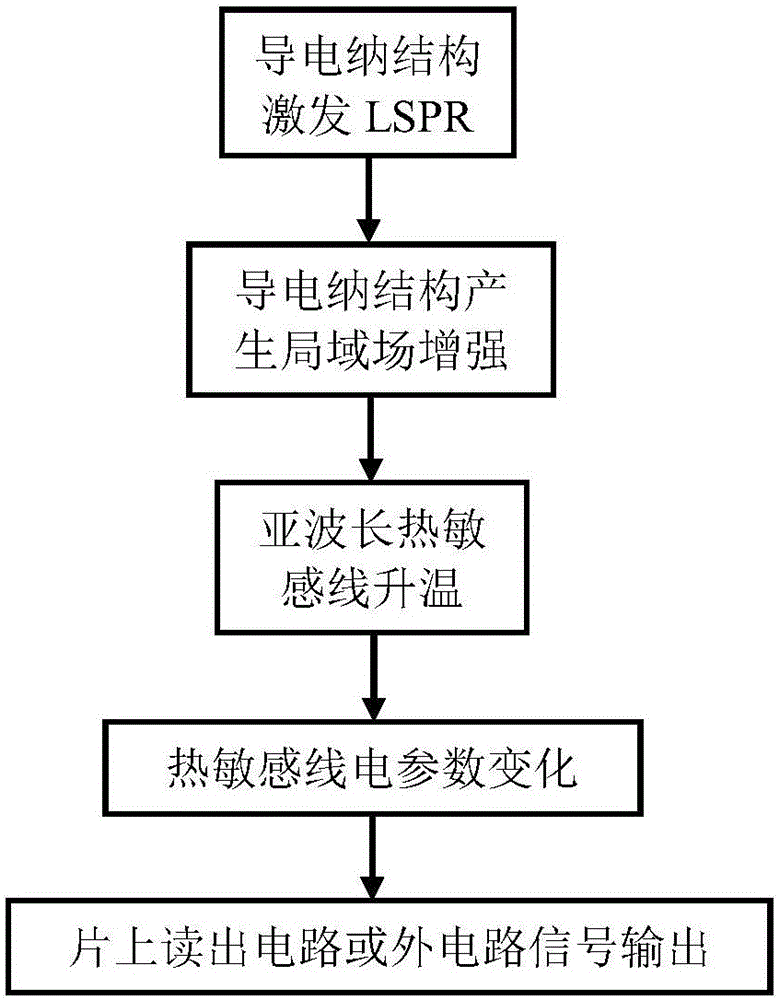

Short wave optical thermal detector and focal plane array device thereof

ActiveCN105977335ASimple structureStructural parameter optimizationSolid-state devicesRadiation controlled devicesElectromagnetic radiationFocal Plane Arrays

The invention discloses a short wave optical thermal detector and a focal plane array device thereof. The short wave optical thermal detector includes an electrode, an electric contact, a photo-thermal detection structure and a substrate. Two ends of the electrode are connected with the electric contact and the photo-thermal detection structure respectively. The photo-thermal detection structure includes heat reactive lines and conducting Na particles capable of generating local surface Plasmon resonance. When electromagnetic radiation of a specific wavelength acts on the conducting Na particles, local surface Plasmon resonance is generated, os that hot spots are formed. Therefore, temperature rise of the heat reactive lines is caused and electric parameter change is caused, and detection of specific electromagnetic radiation by the detector is realized. Through adjusting geometric parameters of the conducting Na particles and combining the conducting Na particles of different parameters, selective spectrum radiation detection and multi-waveband radiation detection are realized. The optical thermal detector provided by the invention is simple in structure and the low cost short wave optical (ultraviolet, visible light and near infrared) waveband detector and the focal plane array device thereof are realized.

Owner:WUHAN IND INST FOR OPTOELECTRONICS

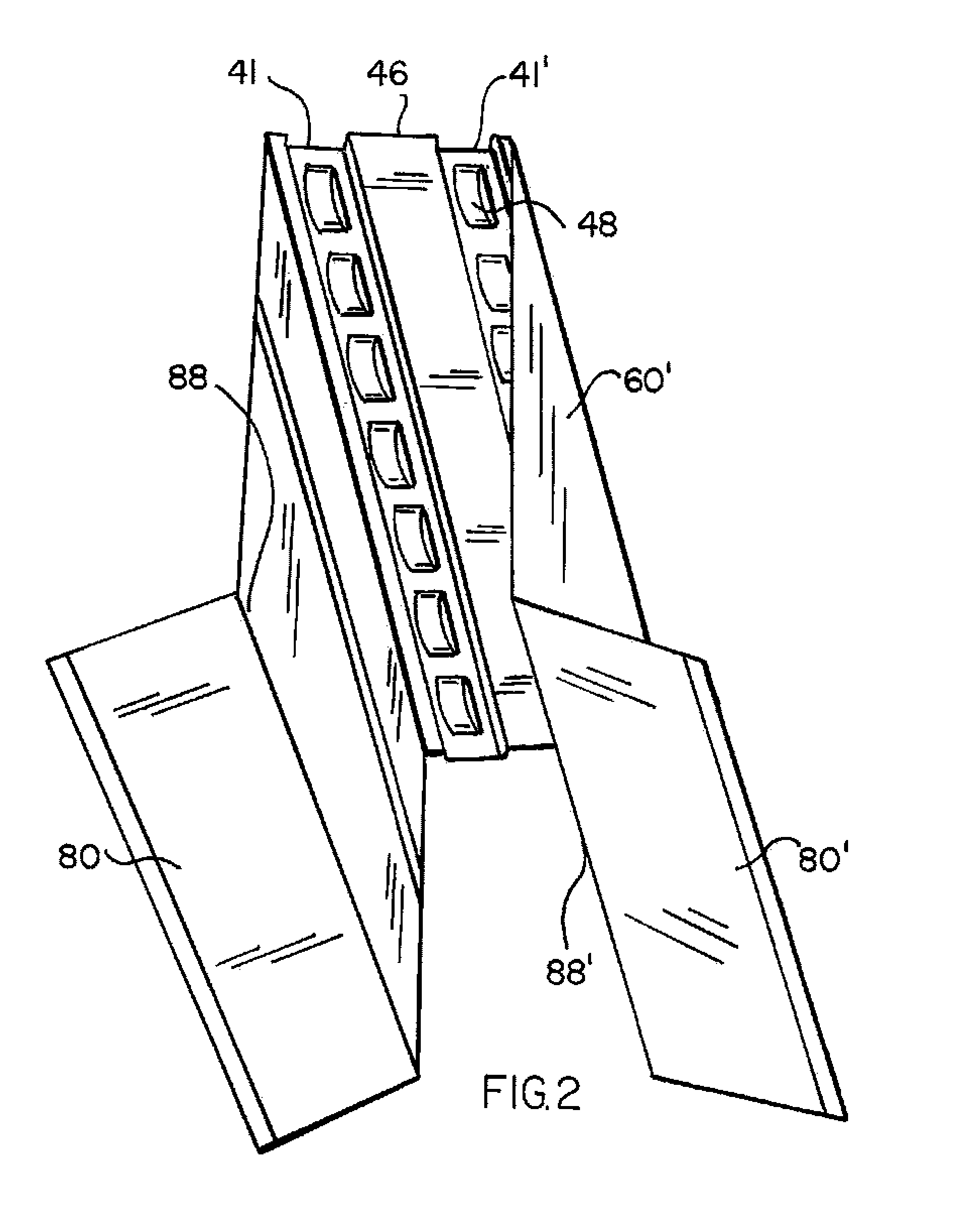

Roof hip and ridge anchor device (CIP)

ActiveUS7774990B1Manufacturing process compatibleMaximize contact areaRailway roofsBuilding roofsAdhesiveEngineering

A device for roof structures having a ridge or hip defined by the planes of two roof decks, disposed at an angle with respect to each other defining a longitudinal joint. A longitudinally extending cover with at least one coextensive channel defined by a bottom, two spacer walls and two lateral walls are mounted over the ridge or hip. The channel(s) increases the effective contact area to enhance the gripping action of the adhesive compound. From the longitudinal bends of the cover wall extend two perpendicularly extending walls with distal ends that continue with longitudinally coextensive flanges. The longitudinal flanges extend at an angle to be cooperatively and rigidly mounted over the roof decks with mechanical fasteners. An adhesive compound is positioned in the channel and over the cover. The adhesive is pressed so that part of it passes through and is lodged within the connected depressed slots positioned along the bottom, spacer and / or lateral walls that define the channel thereby creating a mechanical anchorage with the device. Tile accessories are placed over the cover and in contact with the adhesive compound to secure them to the device.

Owner:EAST COAST METALS

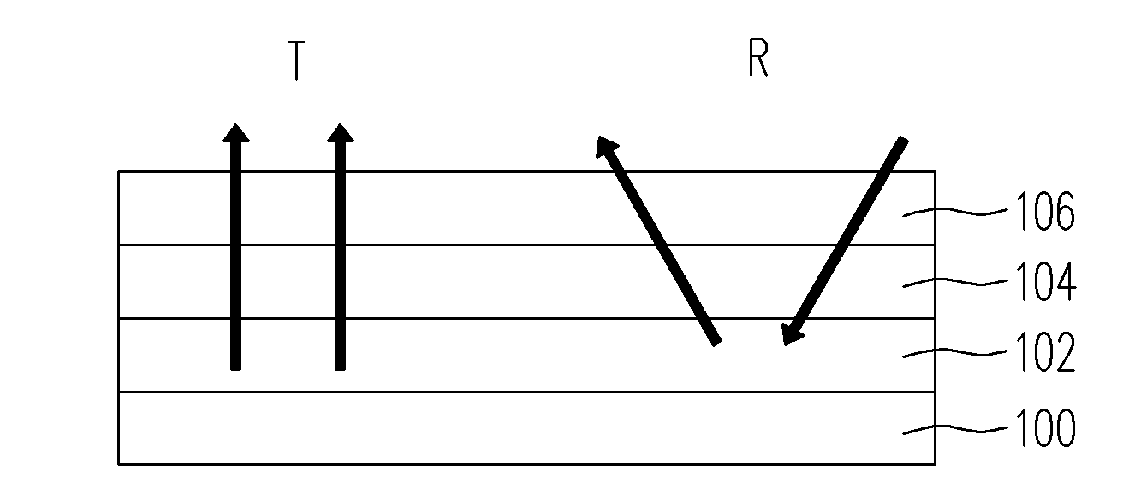

Vertical pixel structures for emi-flective display and methods for making the same

InactiveUS20070030571A1High apertureImprove energy savingStatic indicating devicesSolid-state devicesDisplay deviceComputer science

A vertical pixel structure for emi-flective display and a method thereof are provided. The vertical pixel structure has a substrate, a emitting pixel unit arranged on the substrate and a reflective pixel unit arranged on the emitting pixel unit. By using the vertical pixel structure the aperture of the display can be increased, and the power consumption can be reduced as well.

Owner:IND TECH RES INST

Reflective touch display panel and manufacturing method thereof

InactiveUS20110254808A1Reduce sensitivityHigh sensitivitySolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceLight sensing

A reflective touch display panel and a manufacturing method thereof are provided. An incident light enters the display panel through a front substrate thereof. A plurality of pixel structures and a plurality of light sensing devices are disposed on an inner surface of the front substrate. The light sensing device includes a light sensing transistor having a transparent gate electrode. The manufacturing method for the reflective touch display panel includes the following steps. A first patterned transparent conductive layer, including the transparent gate electrode and a capacitance lower electrode, is formed on the front substrate. A first patterned conductive layer, a dielectric layer, a patterned semi-conductive layer, a second patterned conductive layer and a second patterned transparent conductive layer are sequentially formed on the front substrate to respectively form the light sensing device and the pixel structure. A reflective material layer and a back substrate are. assembled on the front substrate to complete the reflective touch display panel.

Owner:AU OPTRONICS CORP

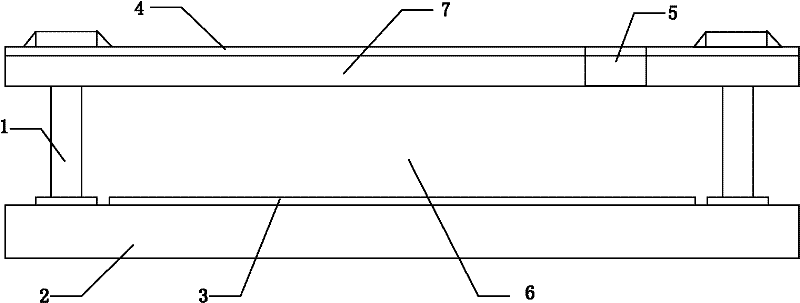

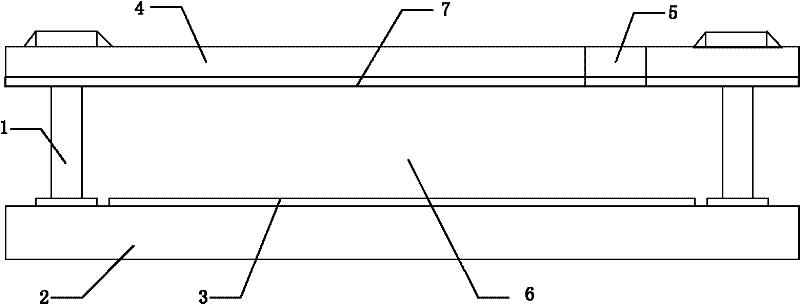

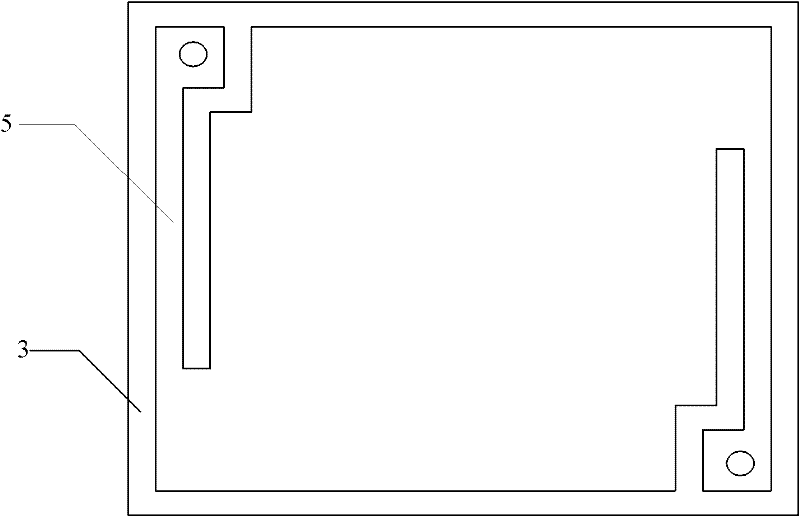

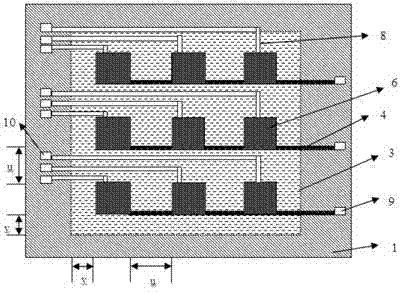

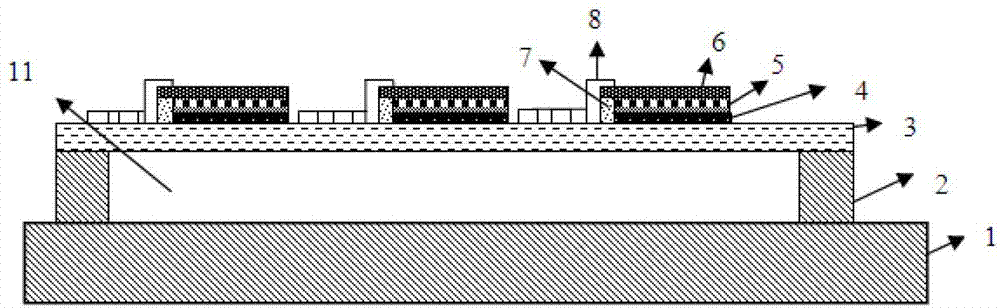

Non-refrigerating film infrared focal plane array detector structure and production method thereof

InactiveCN103117287AImprove thermoelectric performanceManufacturing process compatiblePyrometry using electric radation detectorsRadiation controlled devicesLead electrodeFocal Plane Arrays

A non-refrigerating film infrared focal plane array detector structure comprises a first substrate provided with reading circuits, and a second substrate provided with thermal isolation microbridge arrays and sensitive element arrays. The first substrate and the second substrate are integrally bonded. The etched second substrate serves as a pier for each thermal isolation microbridge unit in the thermal isolation microbridge arrays, and a support layer tightly attached to the top of the pier serves as a deck. The deck of each thermal isolation microbridge unit is provided with one sensitive element array. Each sensitive element array is electrically connected with the corresponding reading circuit of the first substrate through a lead electrode. A production method of the non-refrigerating film infrared focal plane array detector structure includes: preparing a pattern on a bonding surface of the first substrate, preparing the support layer, preparing the sensitive element arrays, protecting the front side of the second substrate, preparing the thermal isolation microbridge arrays, bonding the first substrate and the second substrate, removing a front protective layer of the second substrate, and connecting electrodes of the sensitive element electrode reading circuits.

Owner:SICHUAN UNIV

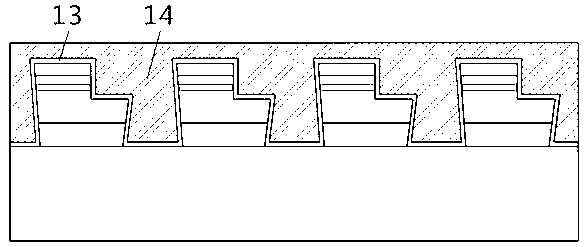

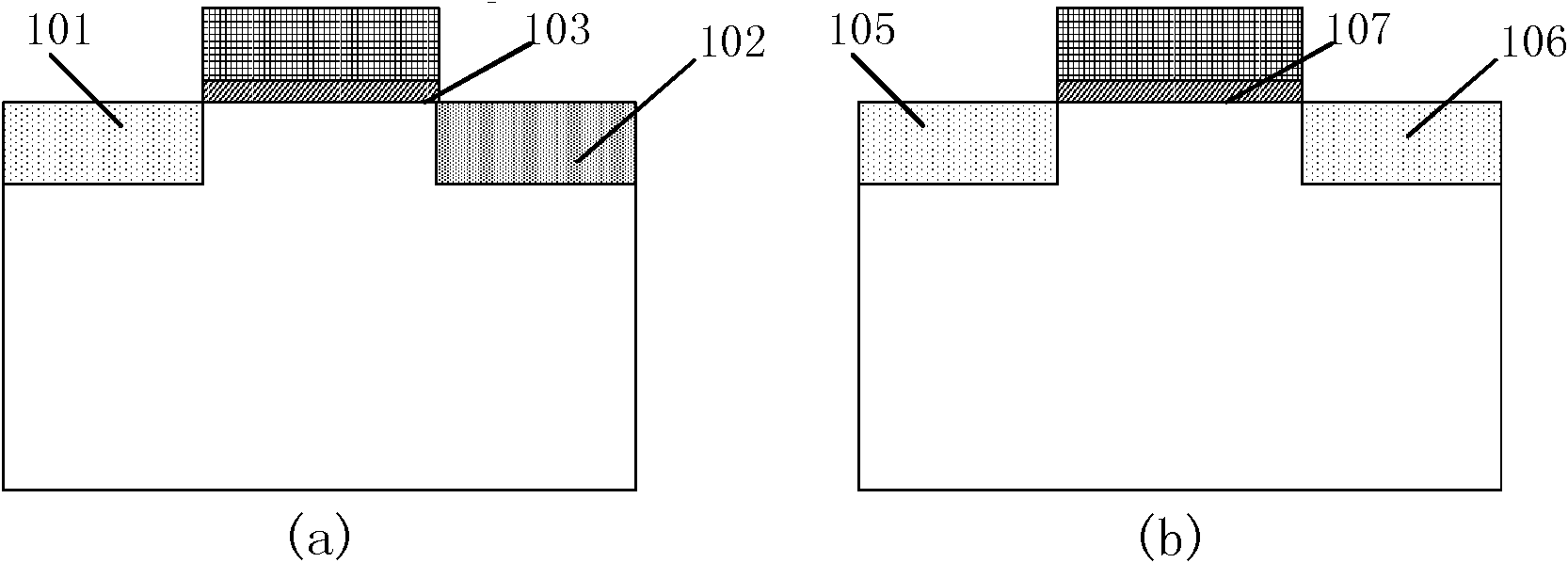

Separated grid type embedded layer float grid nonvolatile storage unit and manufacturing method thereof

ActiveCN101667581AManufacturing process compatibleIncrease distanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringMedia layer

The invention relates to a separated grid type embedded layer float grid nonvolatile storage unit and a manufacturing method thereof. The storage unit comprises a semiconductor substrate, a source region, a drain region, a channel region, a float grid, a source electrode and a control grid. The float grid is below first insulated medium layers and fully embedded in the semiconductor substrate, a second insulated medium layer between the float grid and the semiconductor substrate is connected with the first insulated medium layers and fully enclosures the float grid. The float and the second insulated medium layer are positioned between the source region and the drain region, the second insulated medium layer is far from one side of the drain region and contacted with the source region, thechannel region comprises a first channel region which is arranged between the drain region and the second insulated medium layer along the surface of the semiconductor substrate and a second channelalong the surface of the second insulated medium layer to the source region, and first insulated medium layers are arranged between the float grid and the control grid as well as between the float grid and the source electrode, a part protruding levelly at the bottom of the source electrode is positioned above the first insulated medium layer, and a covering part is arranged in the direction vertical to the surface of the semiconductor substrate.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Method for producing organic electroluminescence device

InactiveCN101540379AGood film-forming propertiesGood dispersion systemSolid-state devicesSemiconductor/solid-state device manufacturingHole injection layerLED display

The invention discloses a method for producing an organic electroluminescence device. The method comprises the followings steps: frirstly, conducting polymer or conducting polymer nano-particle composite materials are formed on the anode of a device, and are used as the hole injection layers of the device; and secondly, other functional layers and membrane electrodes of the device are produced. The conducting polymers in the hole injection layers include conducting polymers and nano-particles thereof, and the device has the characteristics of high electrical conductivity and good membrane planeness. The method can not only be used for producing the organic electroluminescence device with the advantages of high luminous efficiency and long service life, but also can be applied to the fields of backlights, luminance light panels, and the like for color LED display.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

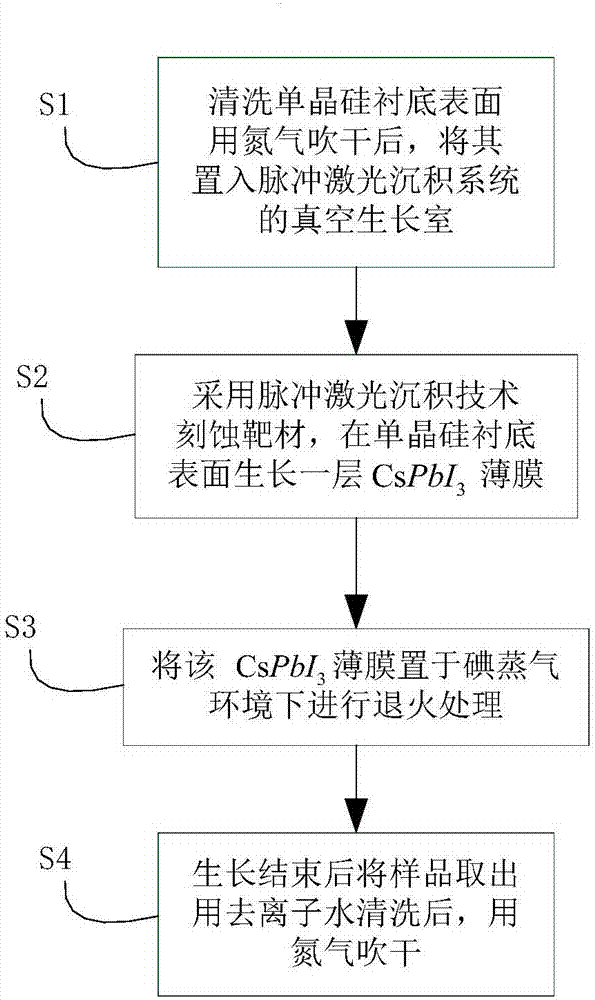

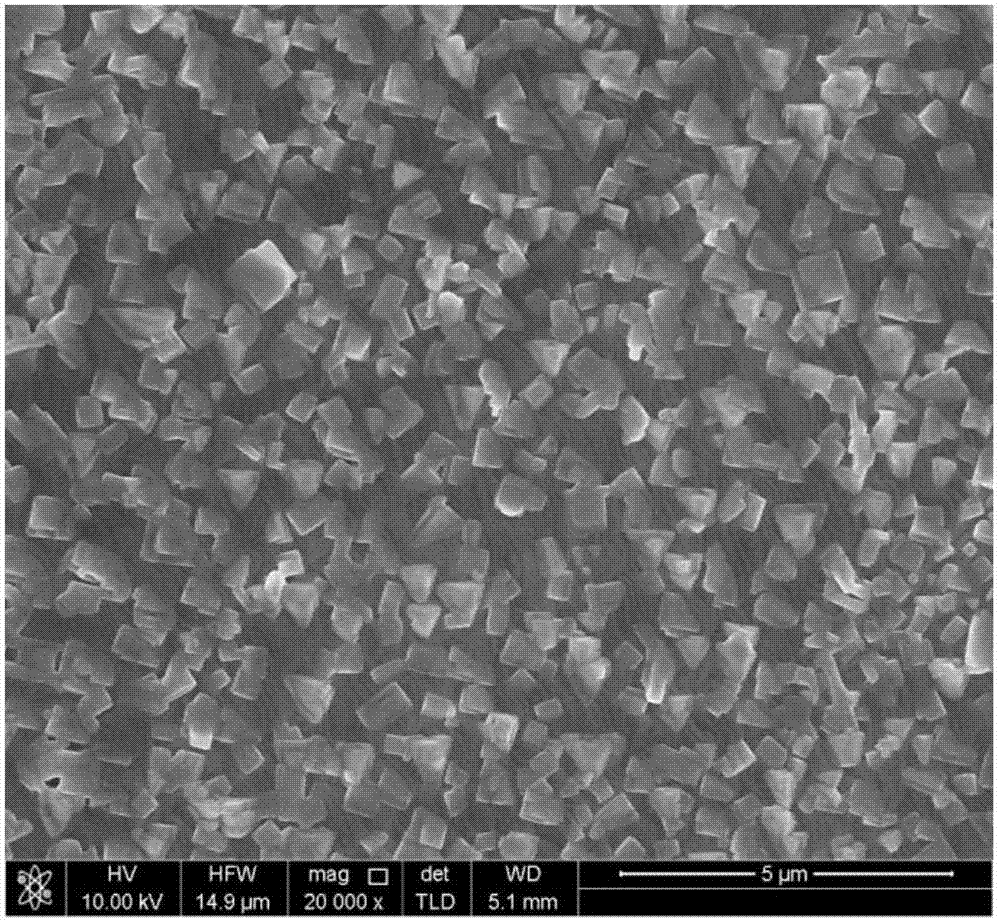

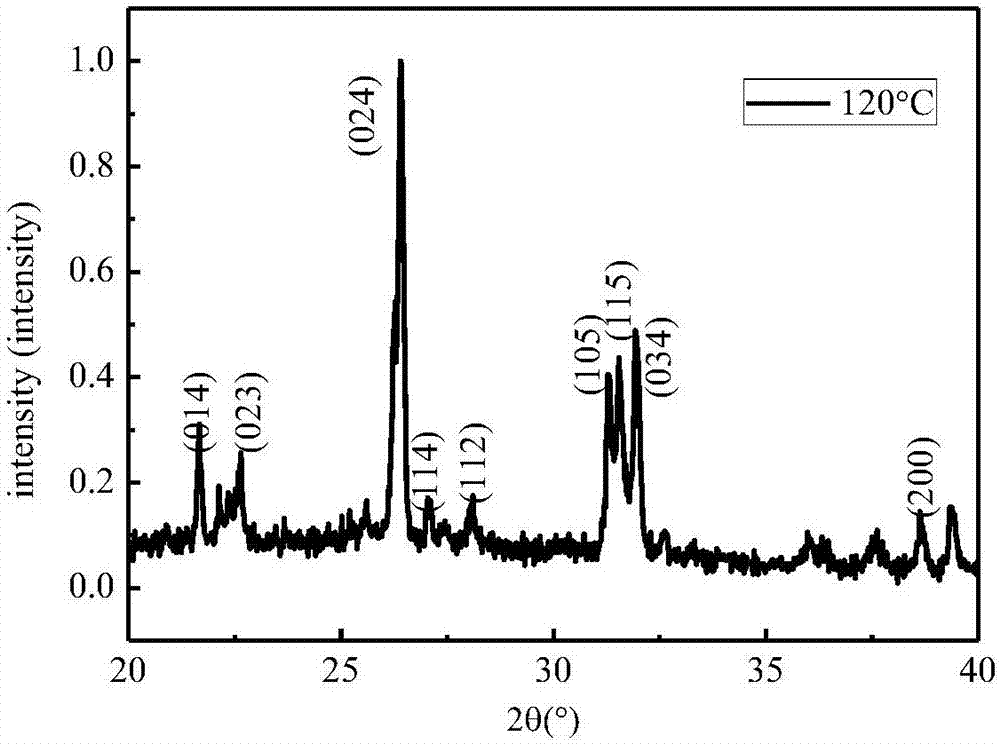

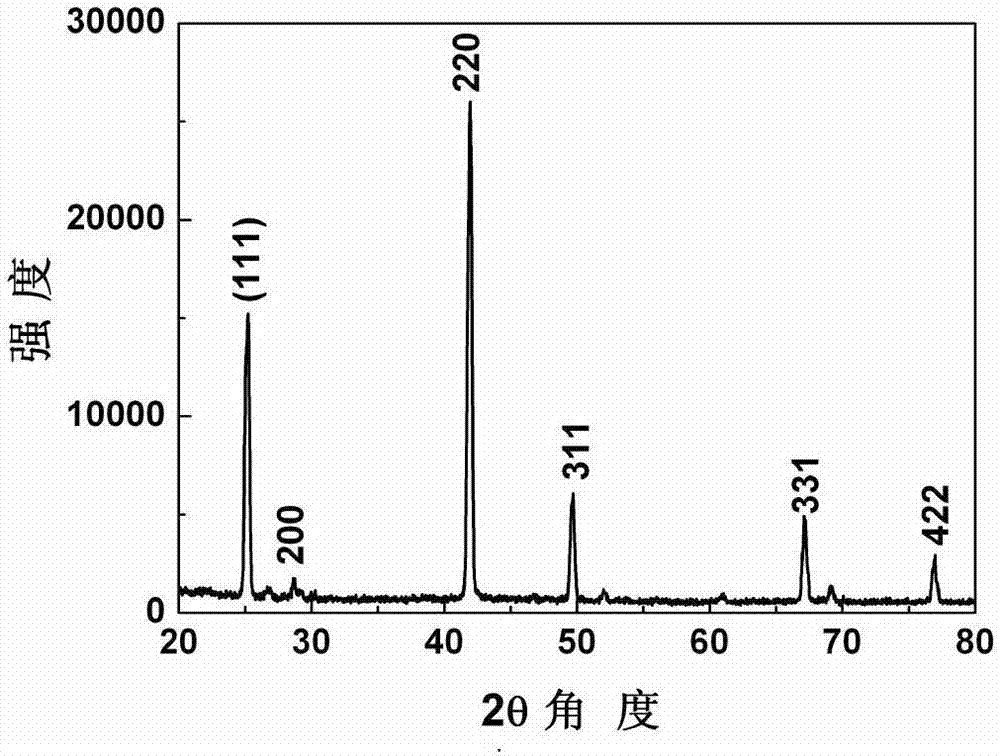

Preparation method of CsPbI3 thin film

InactiveCN107881472AHave a technical effectEasy to prepareVacuum evaporation coatingSputtering coatingReaction temperatureNitrogen

The invention provides a preparation method of a CsPbI3 thin film. The preparation method includes the following steps that the surface of a monocrystalline silicon substrate is cleaned, and the monocrystalline silicon substrate is placed in a vacuum growth room of a pulse laser deposition system after the surface is blown to be dry through nitrogen; a target material is etched through the pulse laser deposition technology, and a layer of CsPbI3 thin film grows on the surface of monocrystalline silicon; the CsPbI3 thin film is placed under an iodine steam environment to be subjected to annealing treatment, and in other words, the CsPbI3 thin film is recrystallized under the iodine steam environment; and a sample is taken out after growth ends, is cleaned with deionized water and is blown to be dry through nitrogen. The preparation method is simple, the reaction temperature is low, the reaction time is short, cost is low, and the preparation method is suitable for industrialized production; and the large-area uniform and compact CsPbI3 thin film high in crystallization quality and excellent in photoelectric property can be obtained, and application of the CsPbI3 thin film to the field of photoelectric devices such as luminescent materials and solar cells is met.

Owner:LUDONG UNIVERSITY

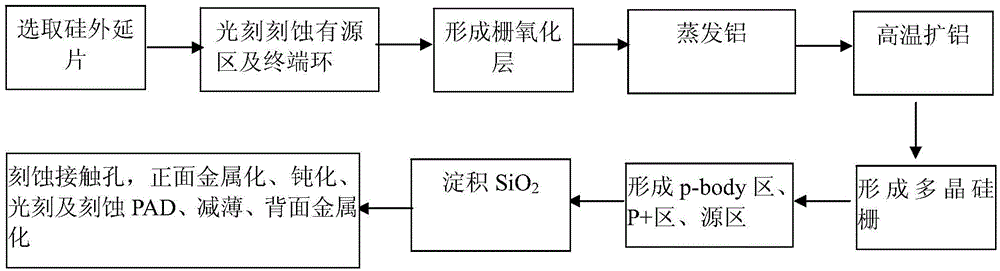

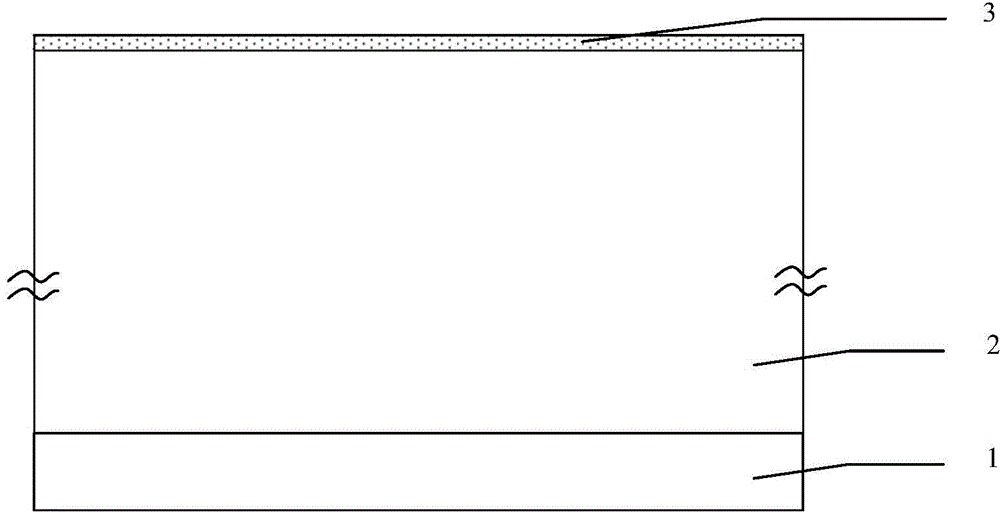

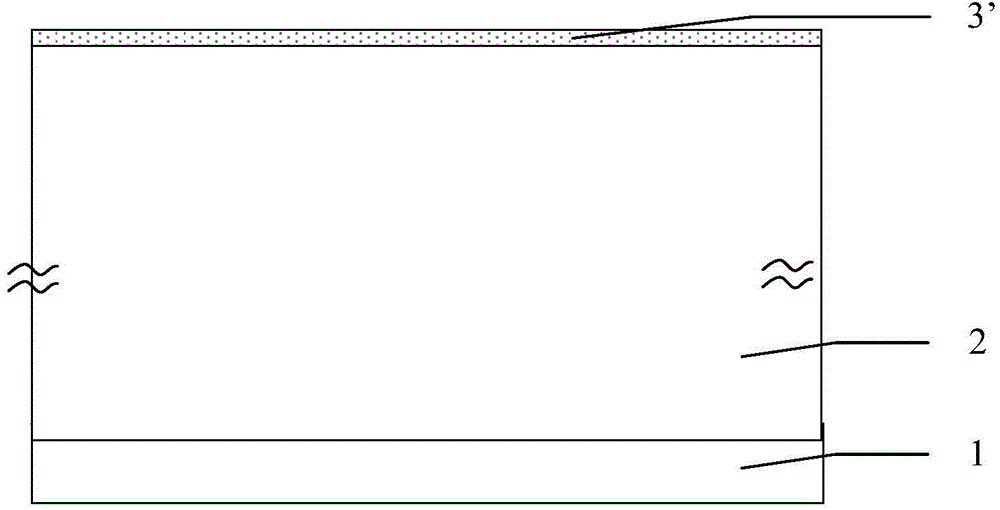

Manufacture method of VDMOS device with irradiation resistance

ActiveCN104576398ASimple processManufacturing process compatibleSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate oxide

The invention discloses a manufacture method of a VDMOS device with irradiation resistance. The manufacture method of the VDMOS device is characterized by forming a gate oxide layer, evaporating aluminum on the gate oxide layer, and then diffusing aluminum at high temperature to form a gate medium of an Si-O-Al structure. Positive charges accumulated in the gate medium can be reduced when the VDMOS device is irradiated; the resistance to total dose irradiation of the device is improved; meanwhile, compared with the conventional silicon dioxide gate medium, the gate medium of the Si-O-Al structure is higher in dielectric constant; the resistance to single event gate rupture of the device can be improved. The manufacture method can be used for effectively overcoming the contradiction of requirements on the thickness of the resistance to total dose irradiation and the single event gate rupture and optimizing the resistance to total dose irradiation and the single event gate rupture at the same time; the process is simple; the resistance to the irradiation of the VDMOS device is improved.

Owner:BEIJING MXTRONICS CORP +1

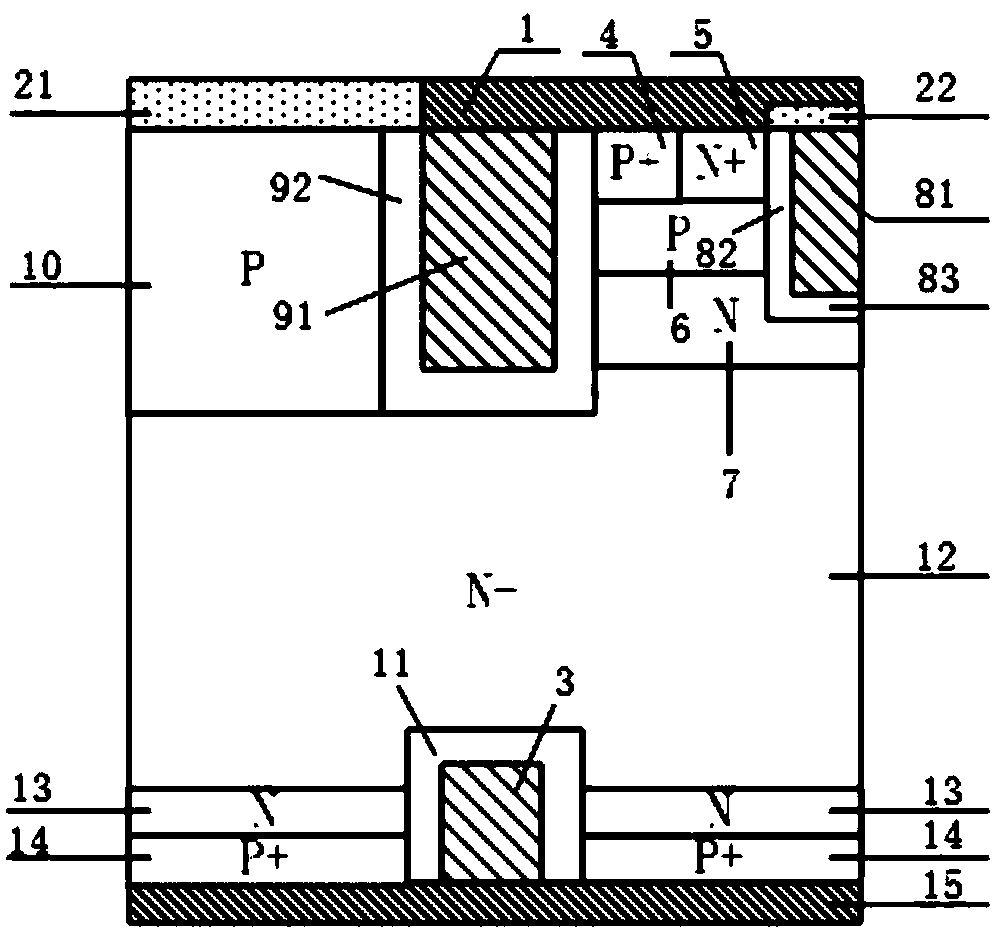

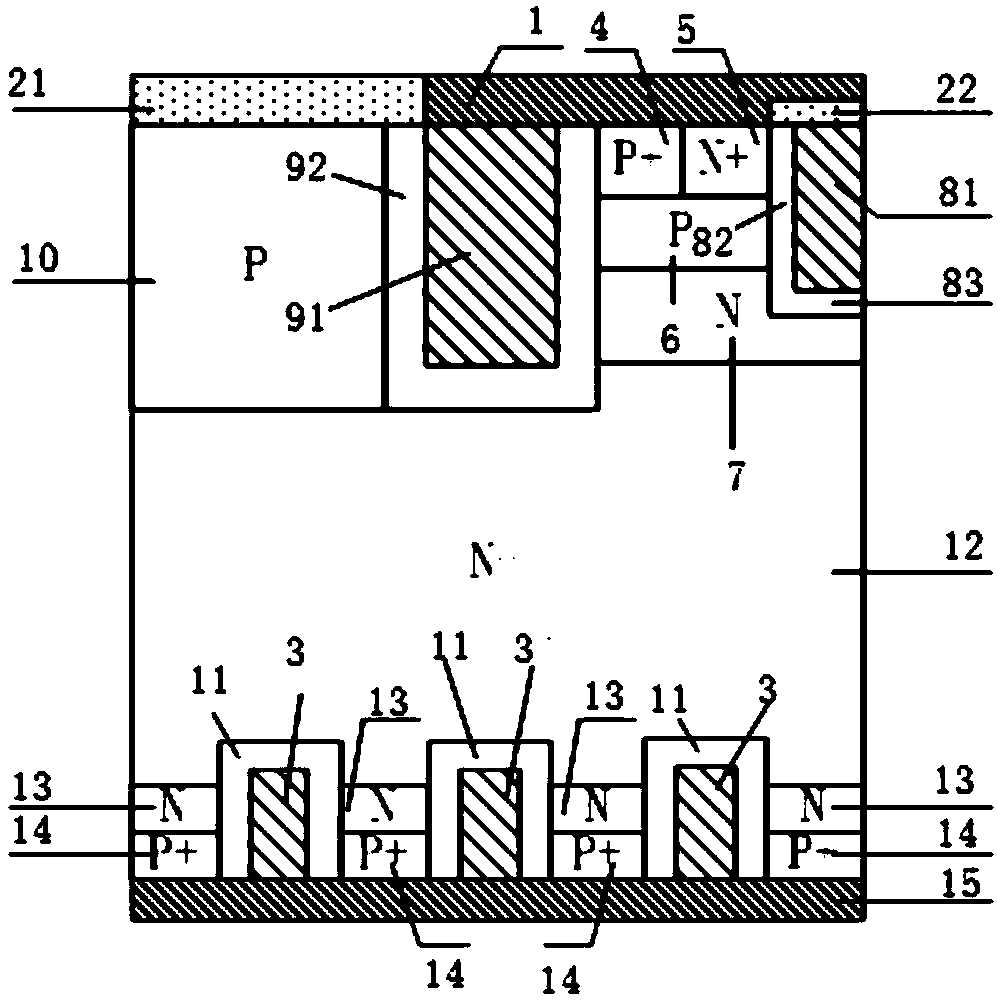

Reverse blocking type IGBT and manufacturing method therefor

InactiveCN107799588AImprove reverse breakdown voltageFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

The invention discloses a reverse blocking type IGBT and a manufacturing method therefor, and belongs to the technical field of a semiconductor power device. By introducing trench emitter and trench collector structures, the reverse breakdown voltage of a device is improved without influencing the threshold voltage and switch-on of an IGBT device; the overall gate capacitance is lowered, the switching speed of the device is improved, the switching loss and driving power consumption of the device are lowered, and the compromising relation between forward switch-on voltage drop and switch-off loss of the conventional CSTBT structure is improved; the problems of current, voltage oscillation and EMI in the device starting dynamic process can be avoided, and device reliability is improved; theelectric field concentration effect at the bottom of the trench is improved, the forward breakdown voltage of the device is improved, and reliability of the device is further improved; and the currentcarrier enhancement effect at the emitter end of the device is further improved, the current carrier concentration distribution in a drift region can be improved, and compromising between forward switch-on voltage drop and switch-off loss can be further improved. The manufacturing method disclosed in the invention is compatible with the existing manufacturing process of a CSTBT device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

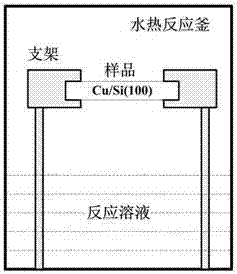

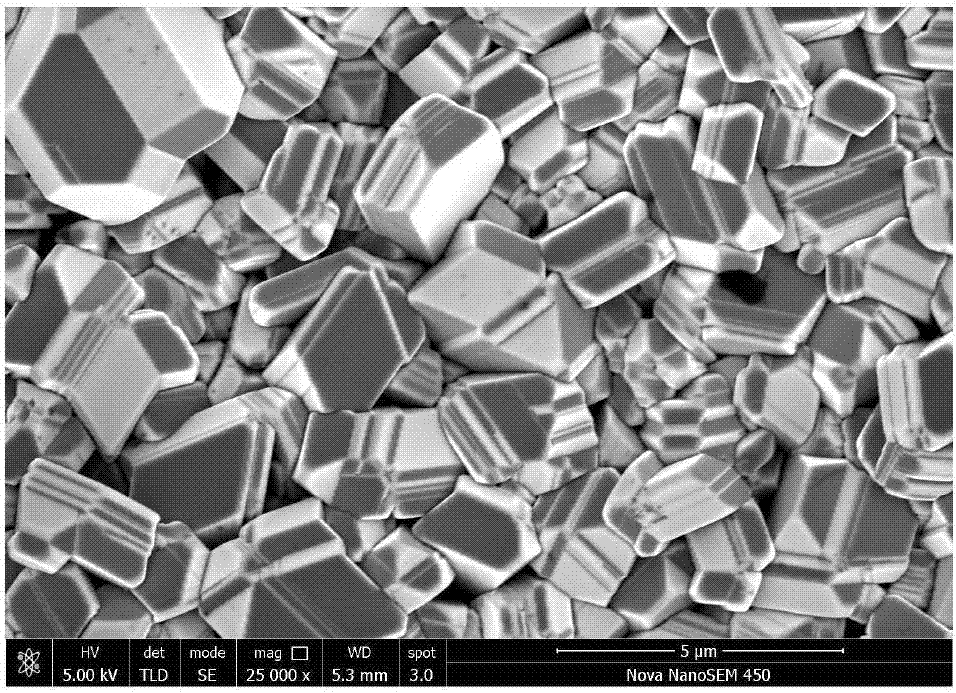

Preparation method of CuI nanostructure

InactiveCN107083532AManufacturing process compatibleImprove crystal qualityVacuum evaporation coatingSputtering coatingEvaporationHigh pressure

The invention relates to a method for preparing a CuI nanostructure, comprising the following steps: cleaning the surface of a single crystal silicon substrate, and putting it into a vacuum growth chamber of an electron beam evaporation device; growing on the surface of a single crystal silicon by electron beam evaporation A layer of copper film; the obtained silicon-based copper film is suspended in the reactor, placed horizontally above the solution, and the precursor solution in the reactor is CuCl 2 , a mixed aqueous solution of polyvinylpyrrolidone and KI; seal the reactor and place it in a blast drying oven for hydrothermal reaction at 120-200°C; after the reaction, take out the sample, wash it, and dry it. For the first time, the present invention uses Cu film and iodine vapor evaporated by hydrothermal synthesis as reaction raw materials to prepare large-area and uniform CuI nanomaterials under low temperature and high pressure conditions, and the preparation process is compatible with the preparation process of optoelectronic devices.

Owner:LUDONG UNIVERSITY

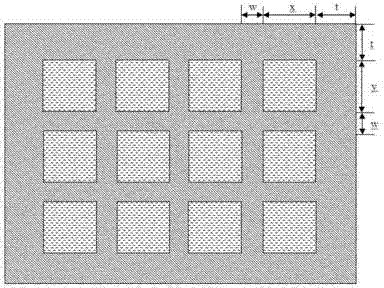

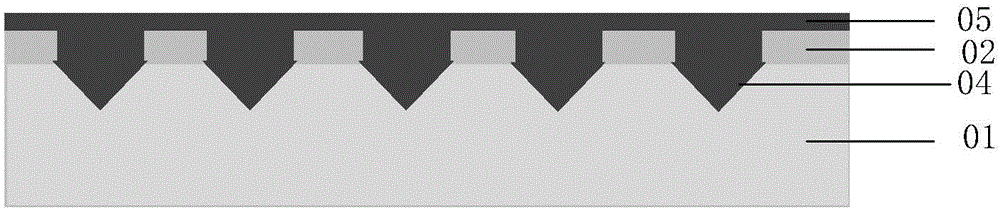

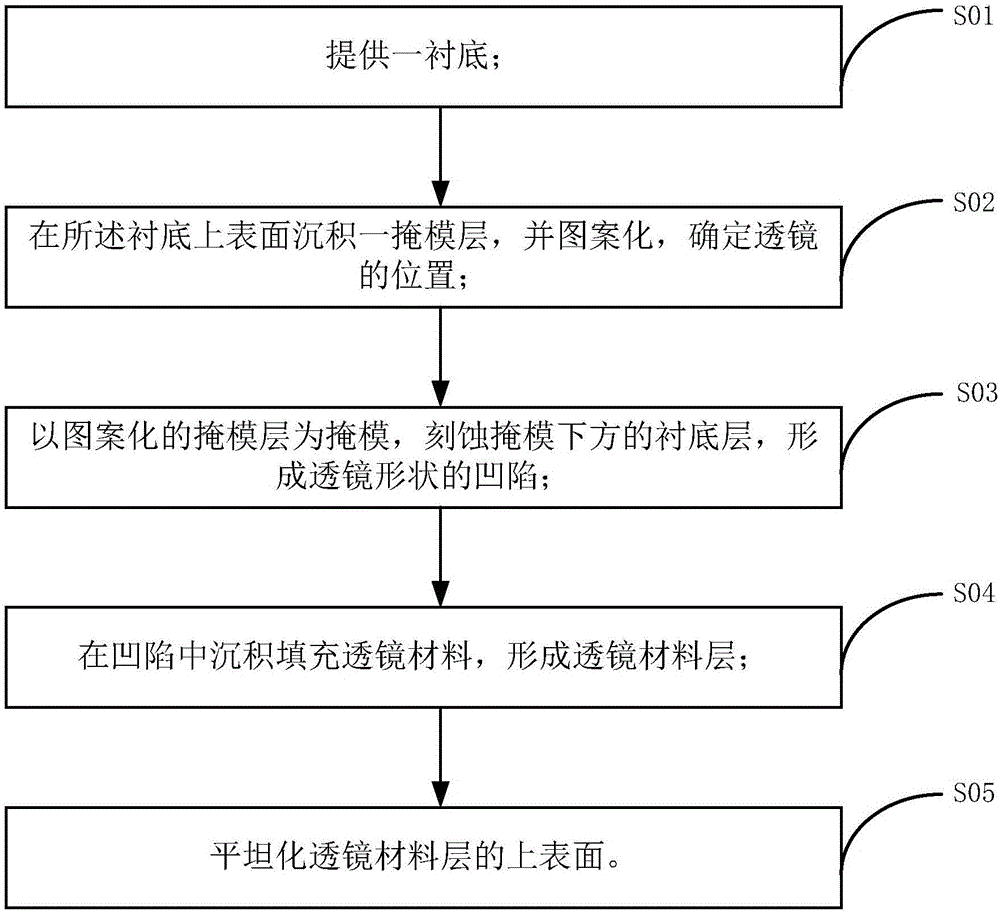

Structure and method for forming optical splitting lens

ActiveCN106597583APromote formationManufacturing process compatibleSolid-state devicesRadiation controlled devicesIntegrated circuit manufacturingUltraviolet lights

The present invention provides a structure for forming an optical splitting lens. Through changing the material of a lens material layer and the shape of a lens, the light splitting characteristics of different light wave ranges can be obtained, and the requirement from ultraviolet light to infrared light is satisfied. The invention also provides a method for forming an optical splitting lens, through forming different recesses with lens shapes by using crystal orientation etching in a substrate and depositing lens materials in the recesses to form lenses, various optical splitting lenses can be formed conveniently, and the method can be fully compatible with an existing integrated circuit manufacturing process.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT