Patents

Literature

35 results about "Technology mapping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

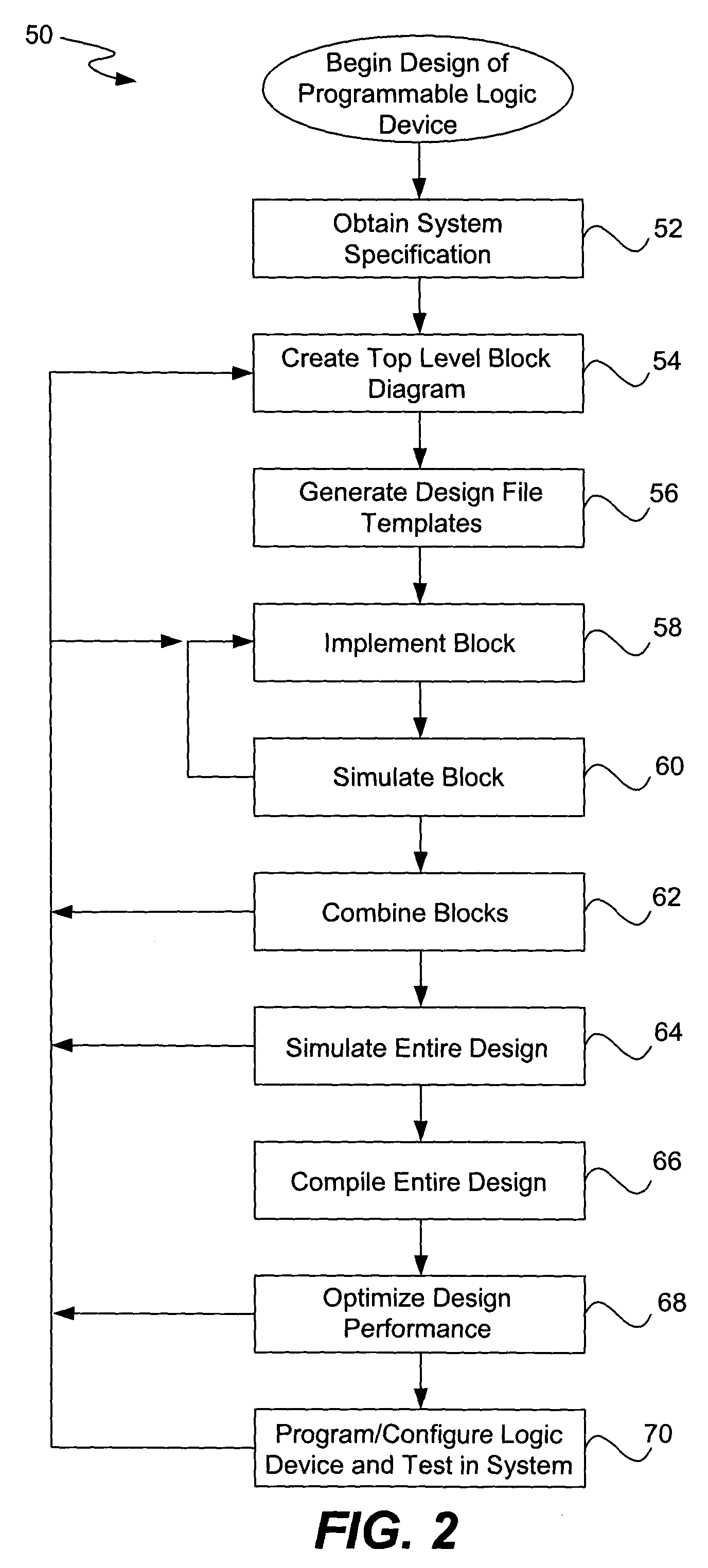

Method for delay-optimizing technology mapping of digital logic

InactiveUS6470486B1CAD circuit designSoftware simulation/interpretation/emulationTheoretical computer scienceArrival time

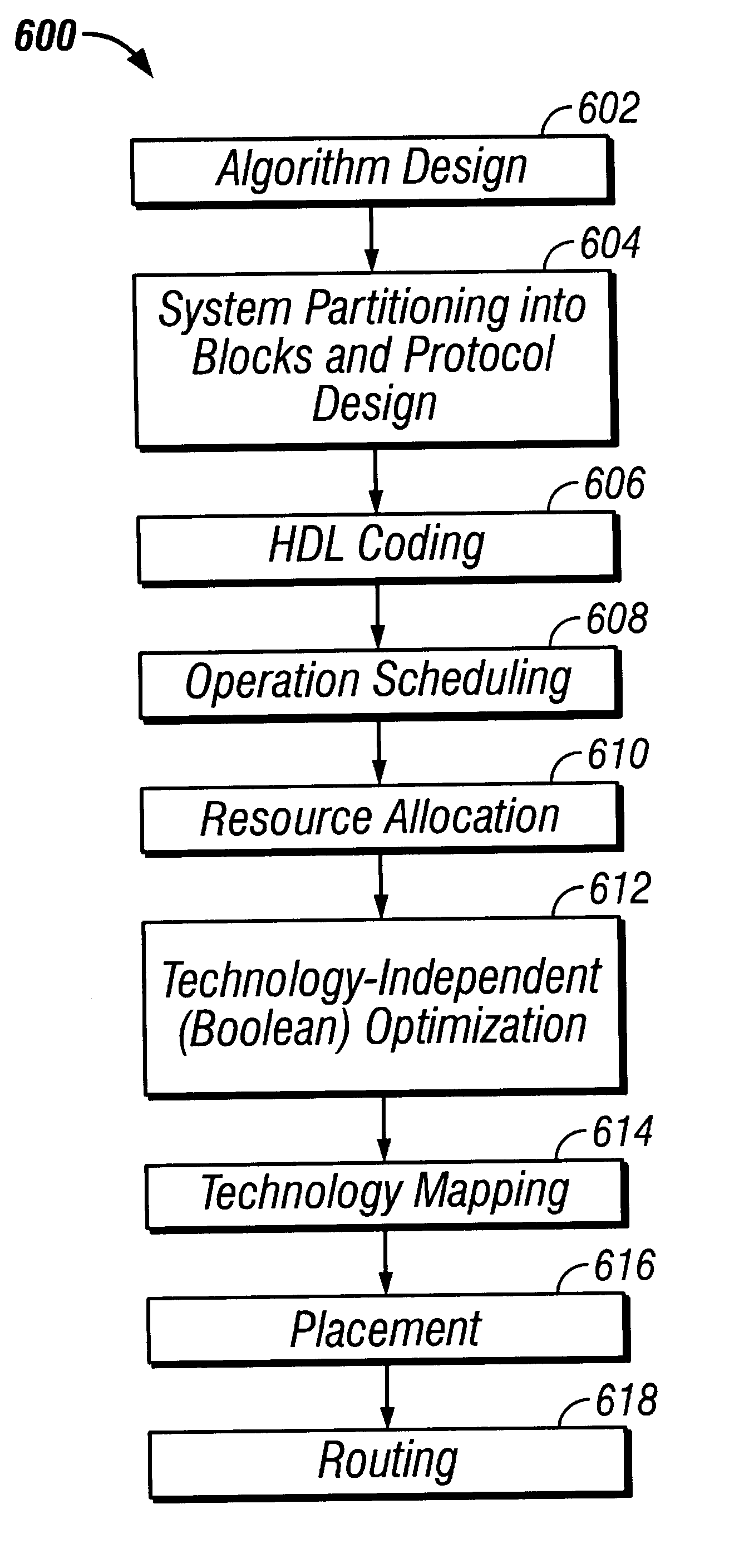

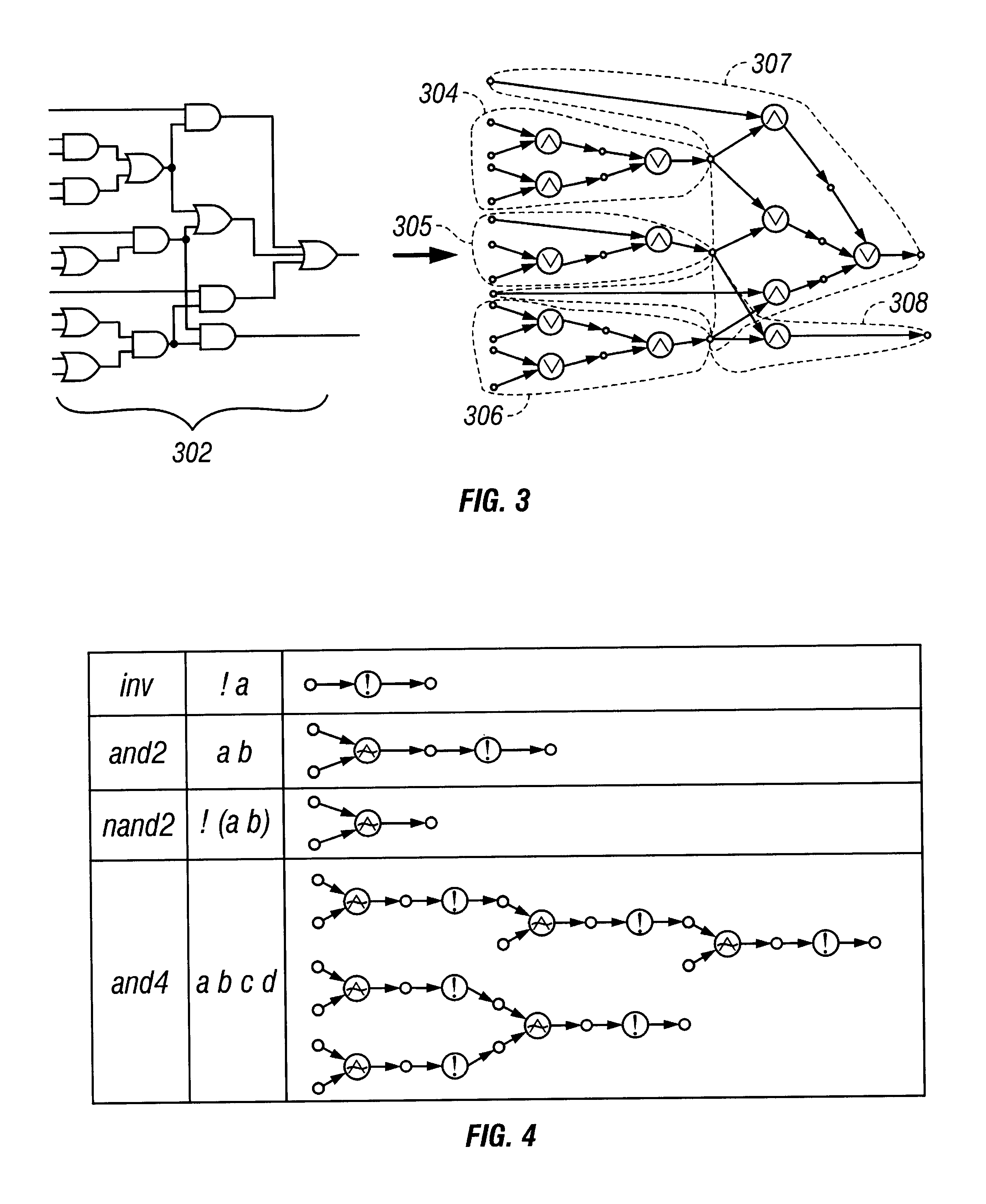

A delay-optimizing technology-mapping process for an electronic design automation system selects the best combination of library devices to use in a forward and a backward sweep of circuit trees representing a design. A technology selection process in an electronic design automation-system comprises the steps of partitioning an original circuit design into a set of corresponding logic trees. Then, ordering the set of corresponding logic trees into an ordered linear list such that each tree-T that drives another ordered tree precedes the other ordered tree, and such that each ordered tree that drives the tree-T precedes the tree-T. Next, sweeping forward in the ordered linear list while computing a set of Pareto-optimal load / arrival curves for each of a plurality of net nodes that match a technology-library element. And, sweeping backward in the ordered linear list while using the set of Pareto-optimal load / arrival curves for each of the net nodes and a capacitive load to select a best one of the technology-library elements with a shortest signal arrival time. Wherein, only those net nodes that correspond to gate inputs are considered, and any capacitive loads are predetermined.

Owner:CADENCE DESIGN SYST INC

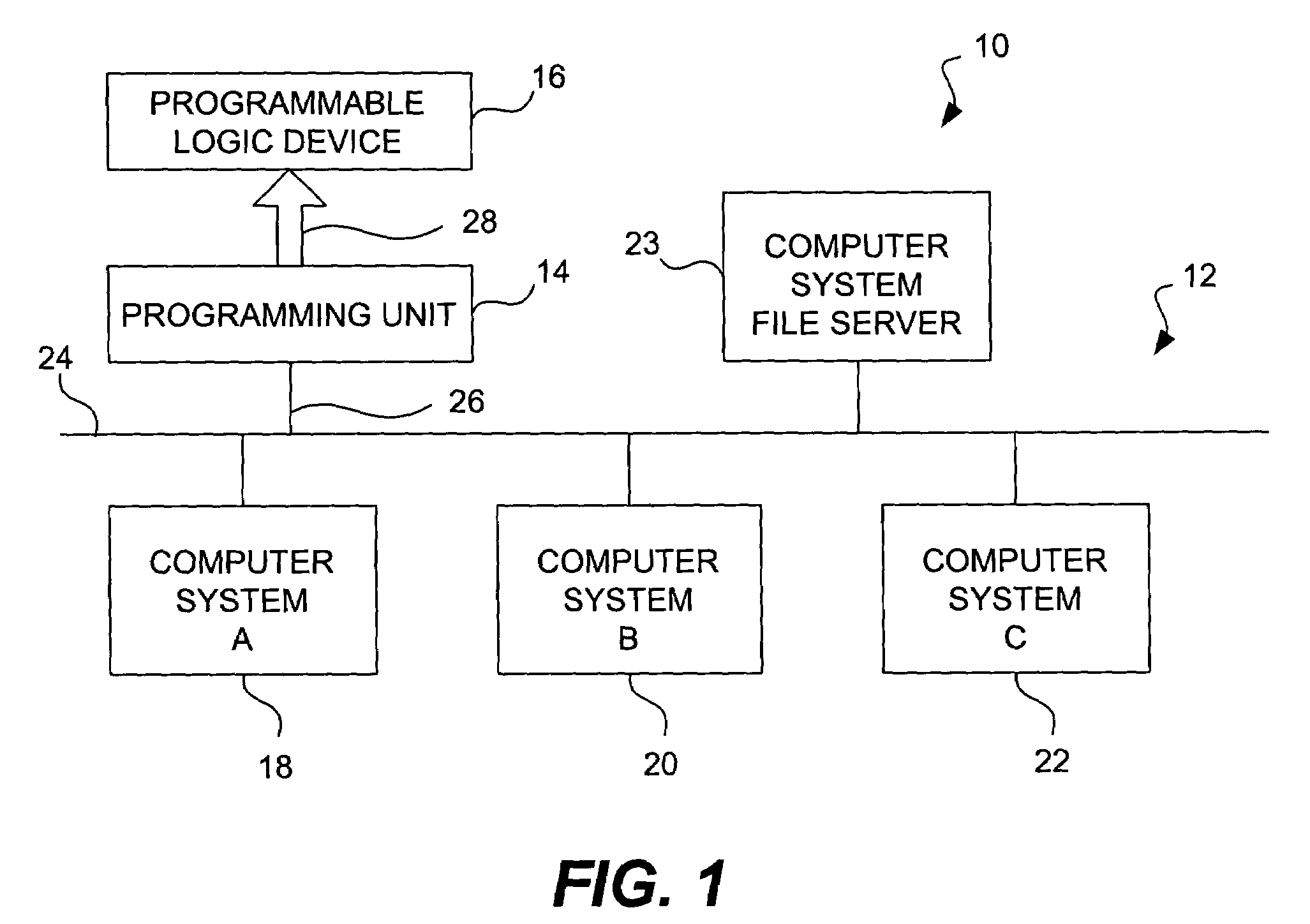

Chip debugging using incremental recompilation

InactiveUS7076751B1Save precious timeCAD circuit designSoftware simulation/interpretation/emulationIncremental compilerSignal of interest

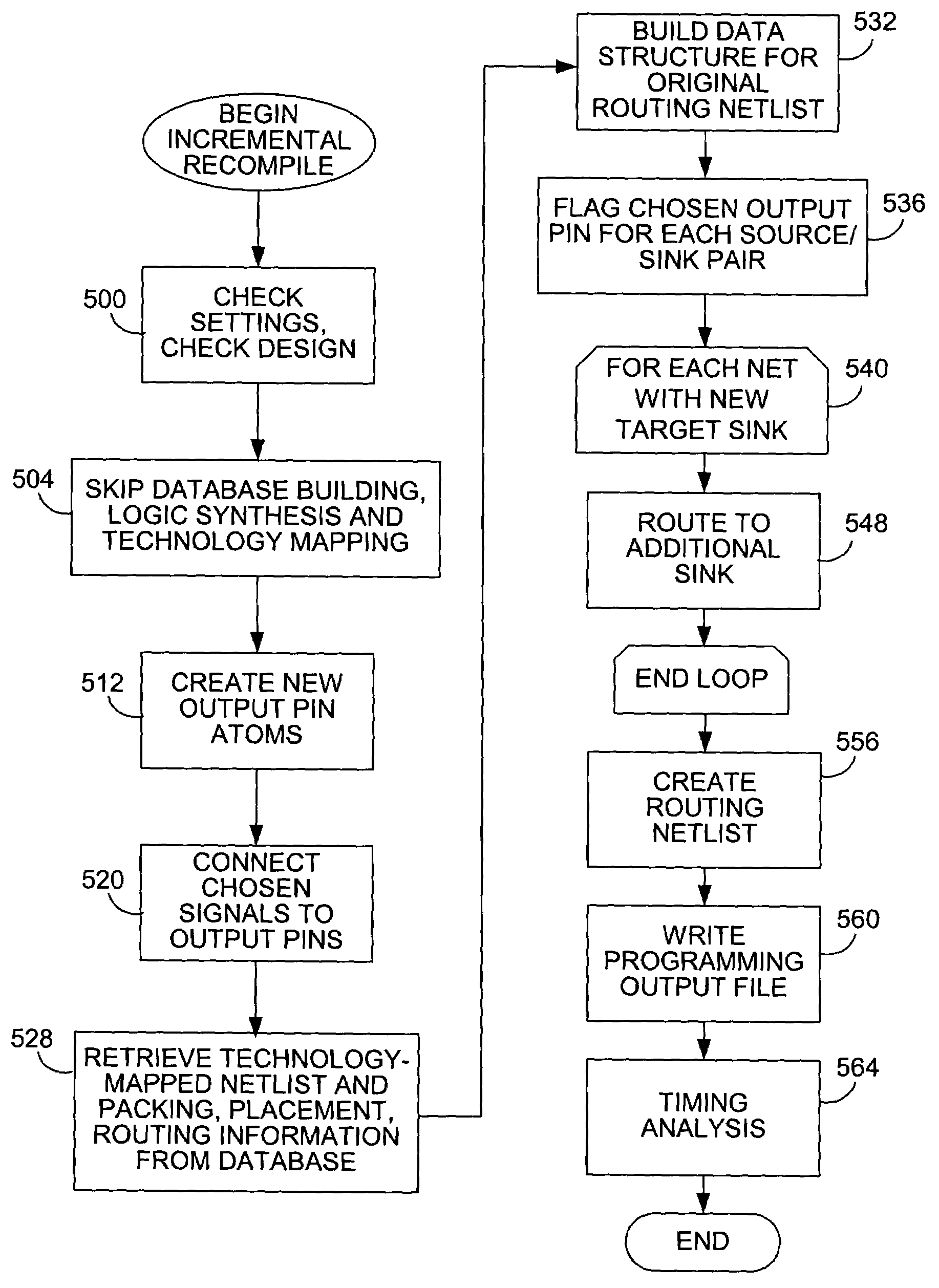

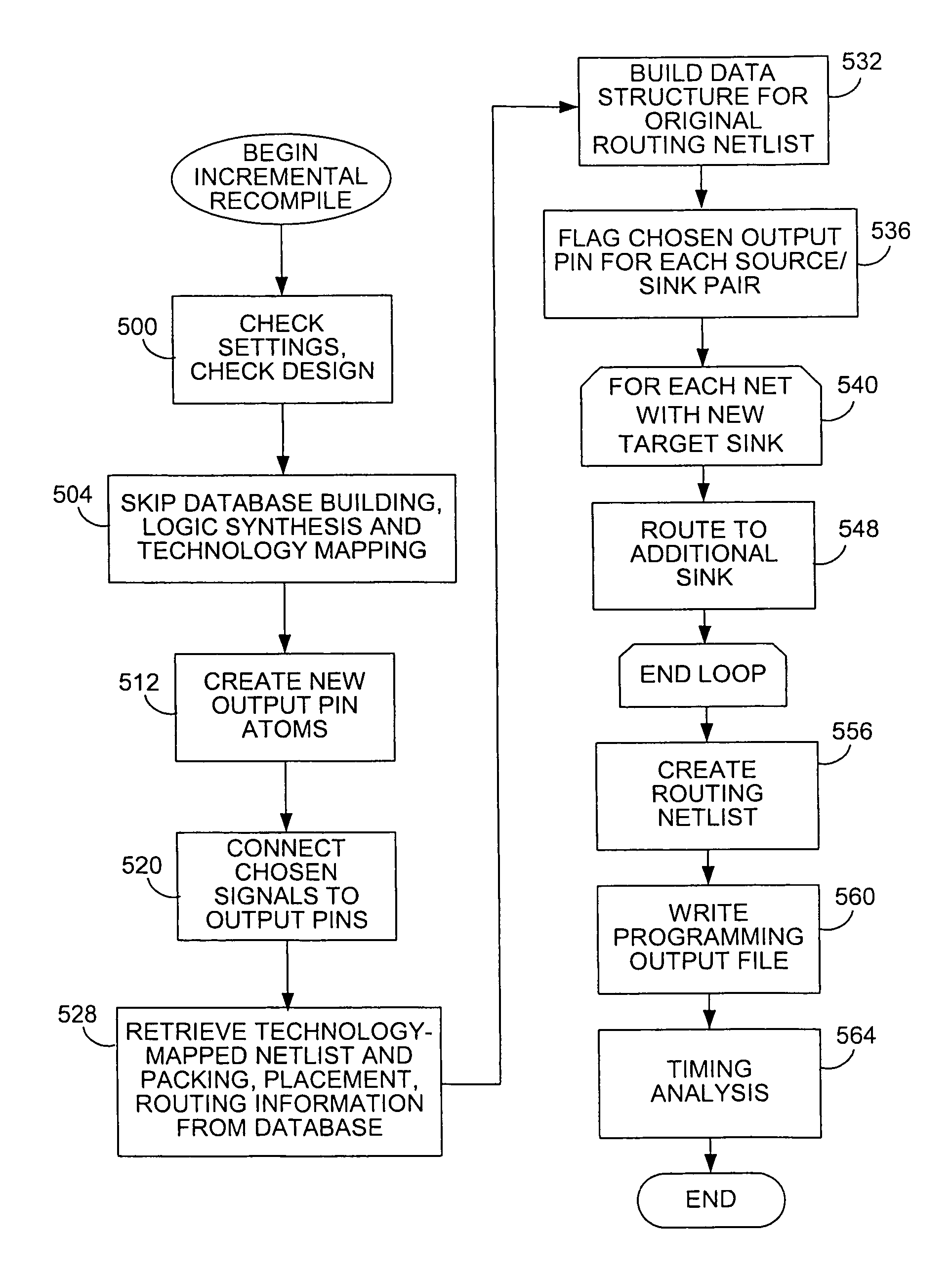

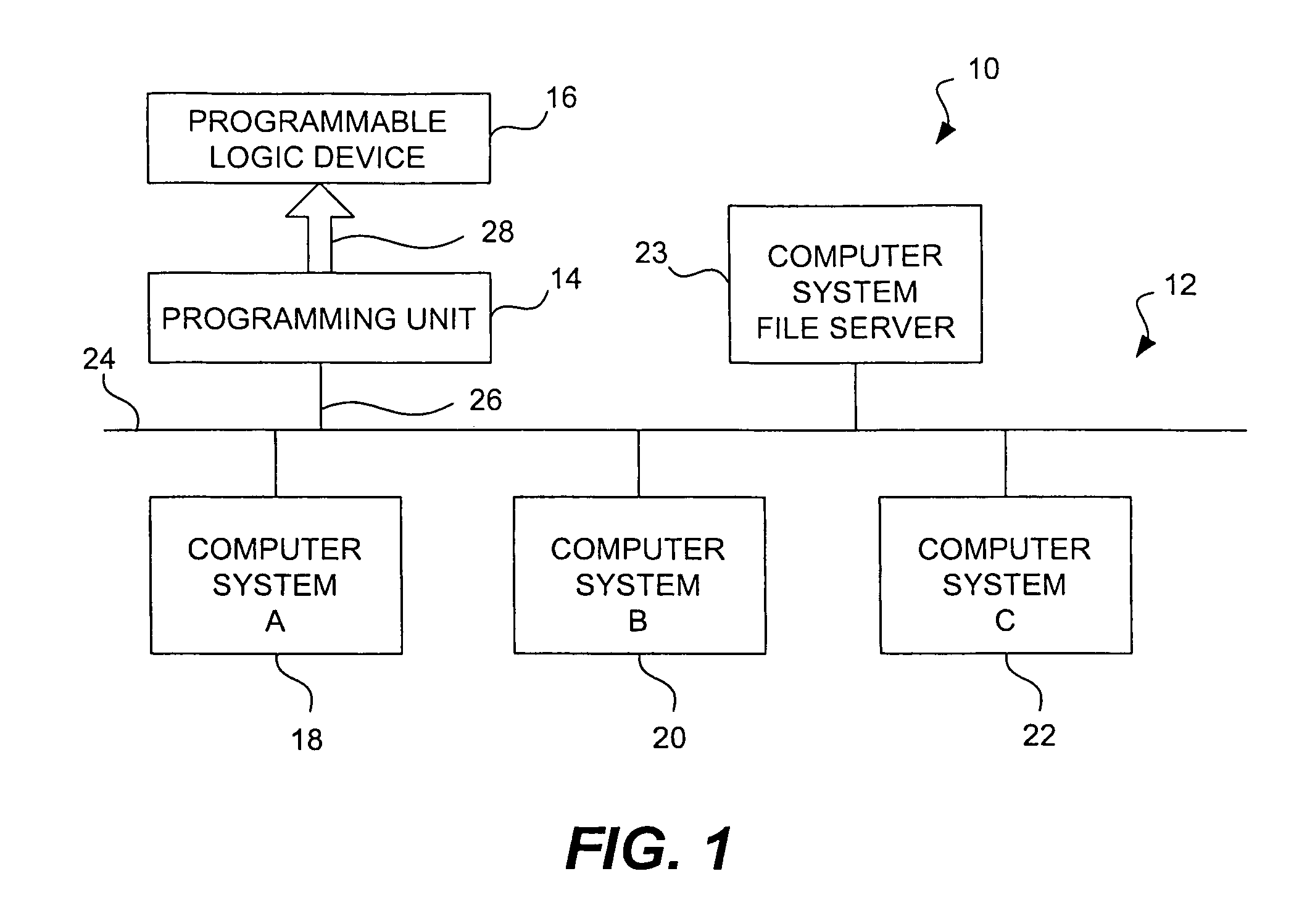

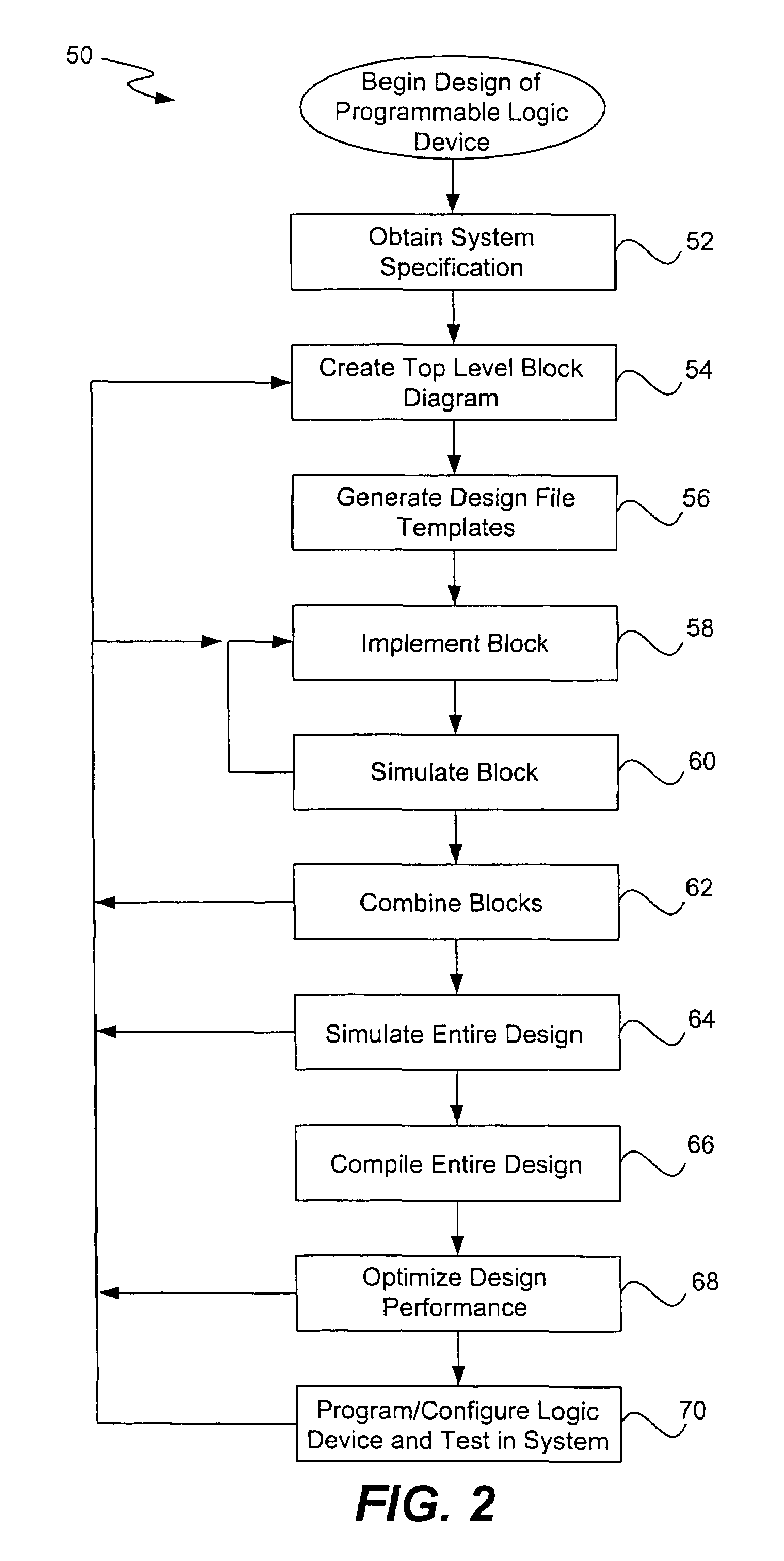

While debugging, a user chooses an incremental recompile. Internal signals of interest are selected and output pins are optionally reserved. An incremental recompile of the compiled design includes compiling a routing from each internal signal to an output pin. The technology-mapped netlist and placing and routing information corresponding to an original compiled design are saved into a database during full compilation. During debugging, an incremental compiler retrieves this information to build the original routing netlist. The database building, logic synthesis and technology mapping stages may be skipped. New connections are added, fitted to the device, and then the final routing netlist is output into a programming output file (POF) in a form suitable for programming the PLD. The user views the internal signals at the output pins chosen. The user may iterate through this process many times in order to debug the PLD. The debugging assignments may be deleted.

Owner:ALTERA CORP

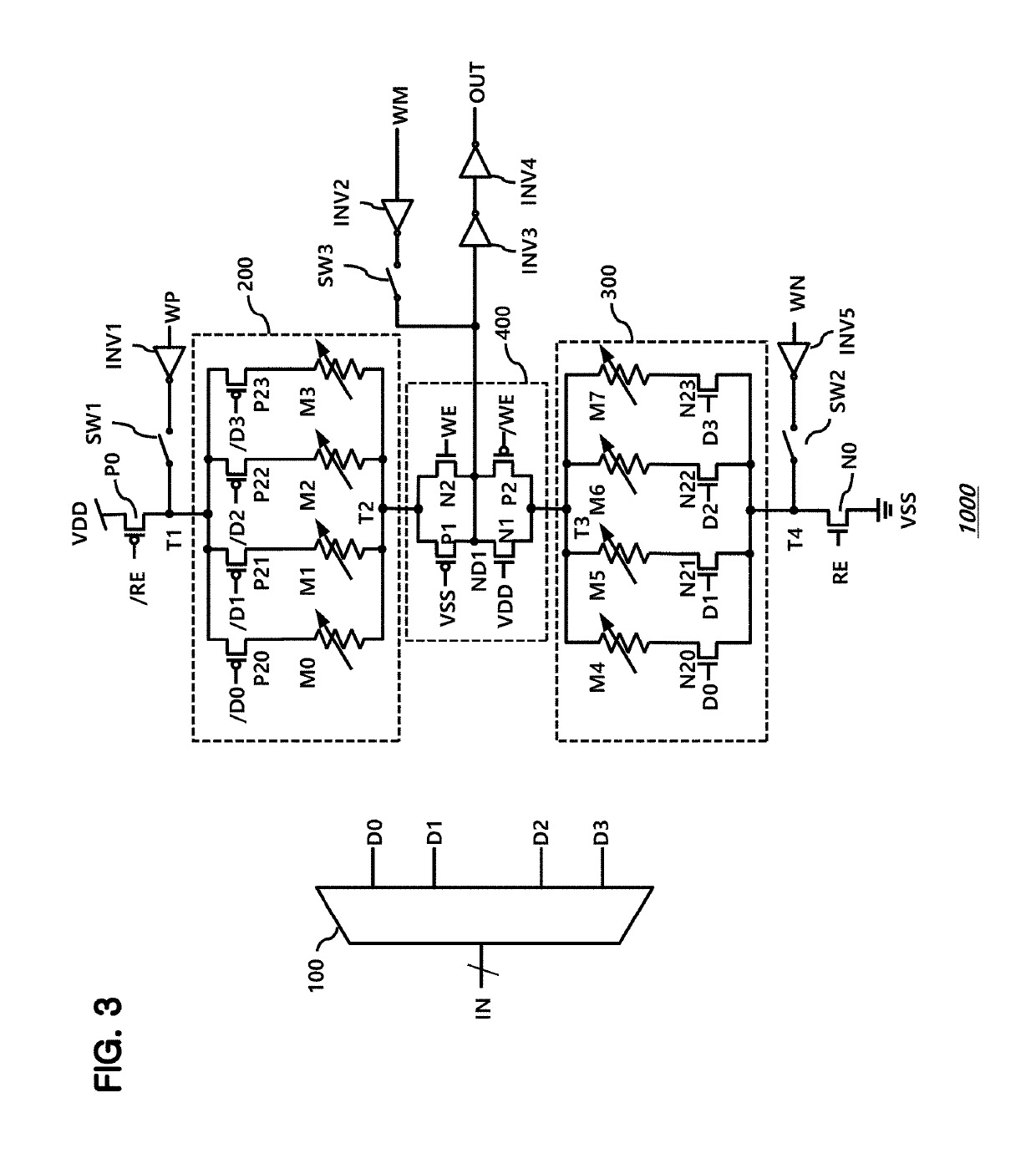

Look up table including magnetic element, FPGA including the look up table, and technology mapping method of the FPGA

ActiveUS10419001B2Power reduction in field effect transistorsLogic circuits characterised by logic functionEngineeringElectrical and Electronics engineering

Owner:SK HYNIX INC +1

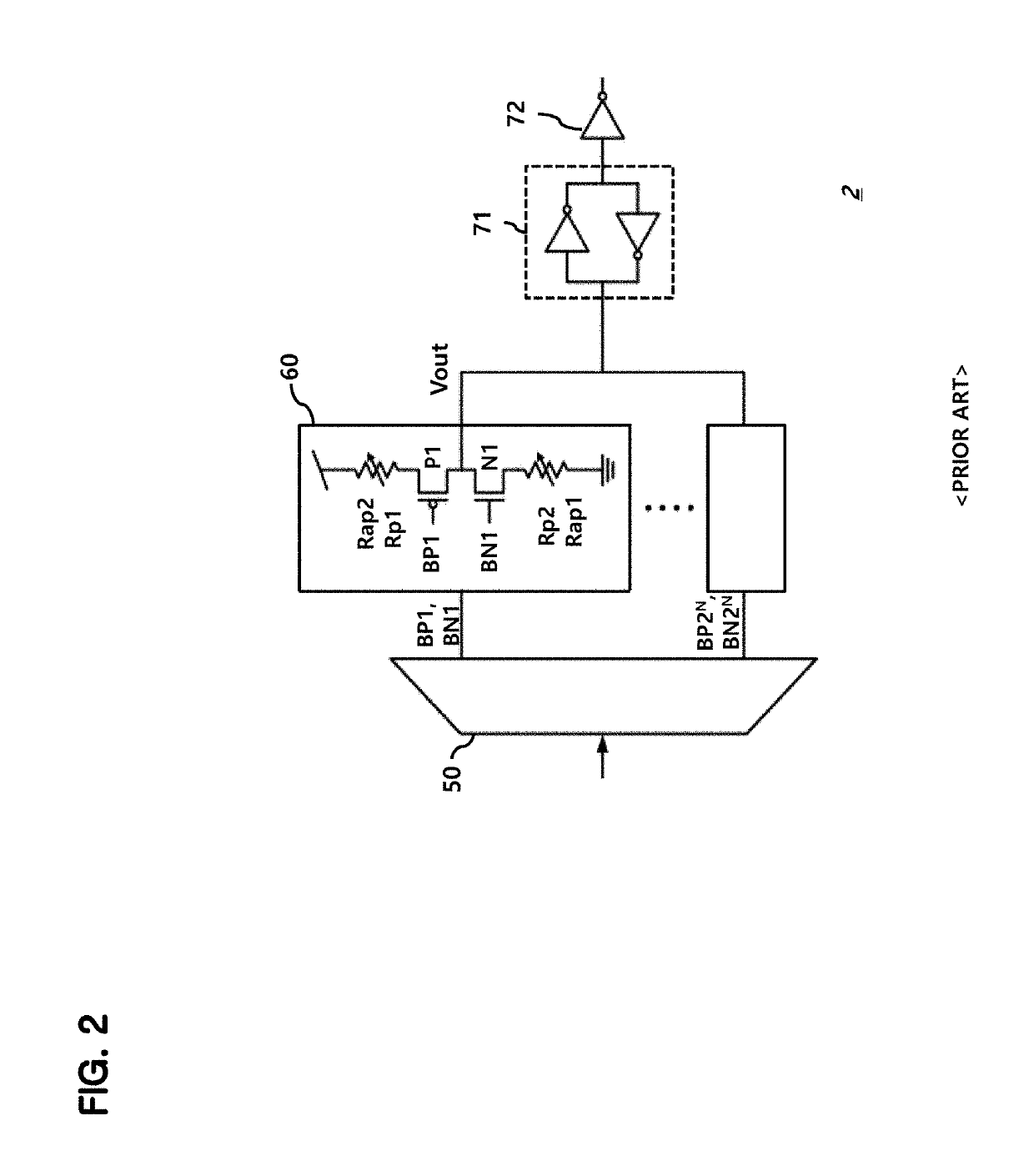

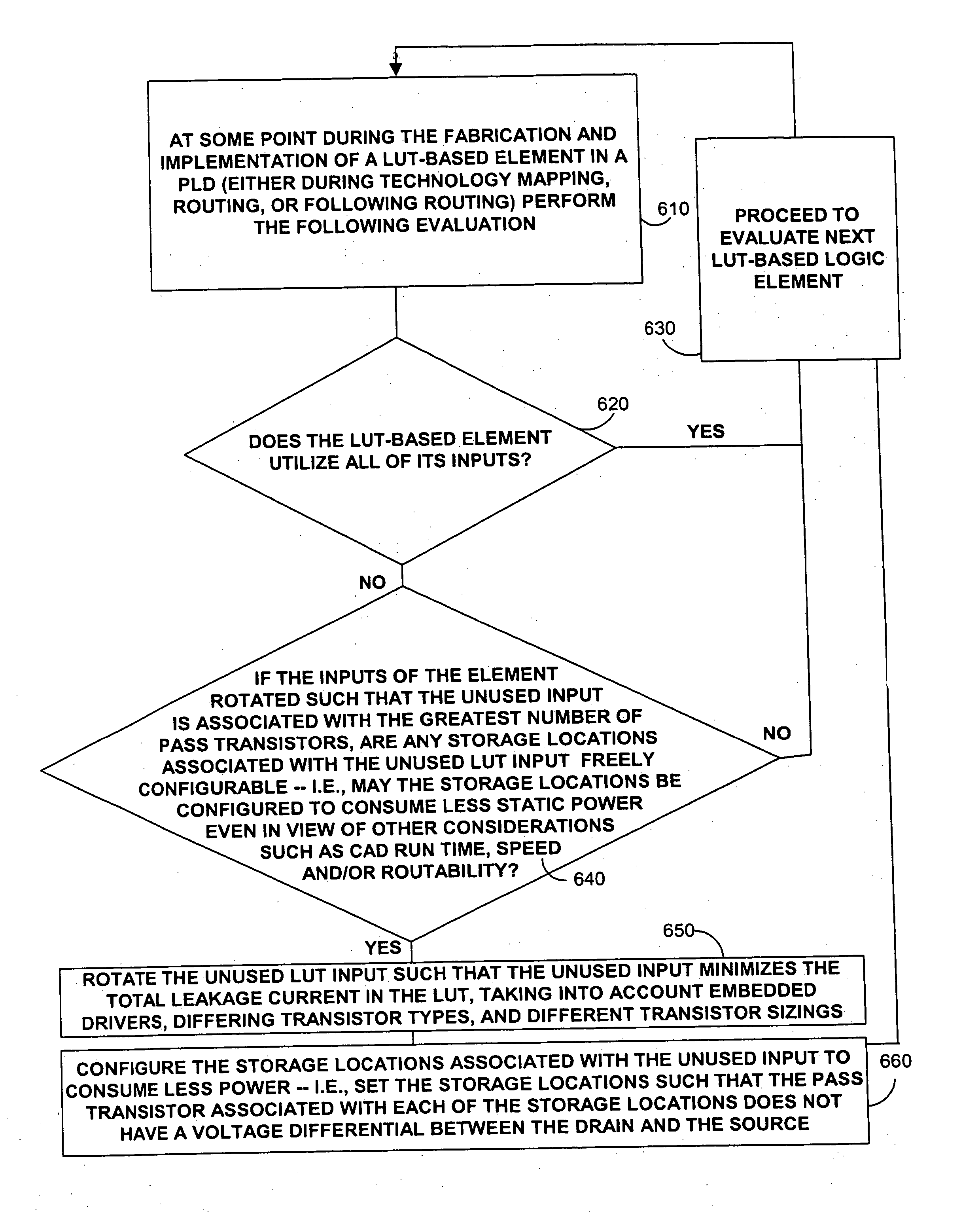

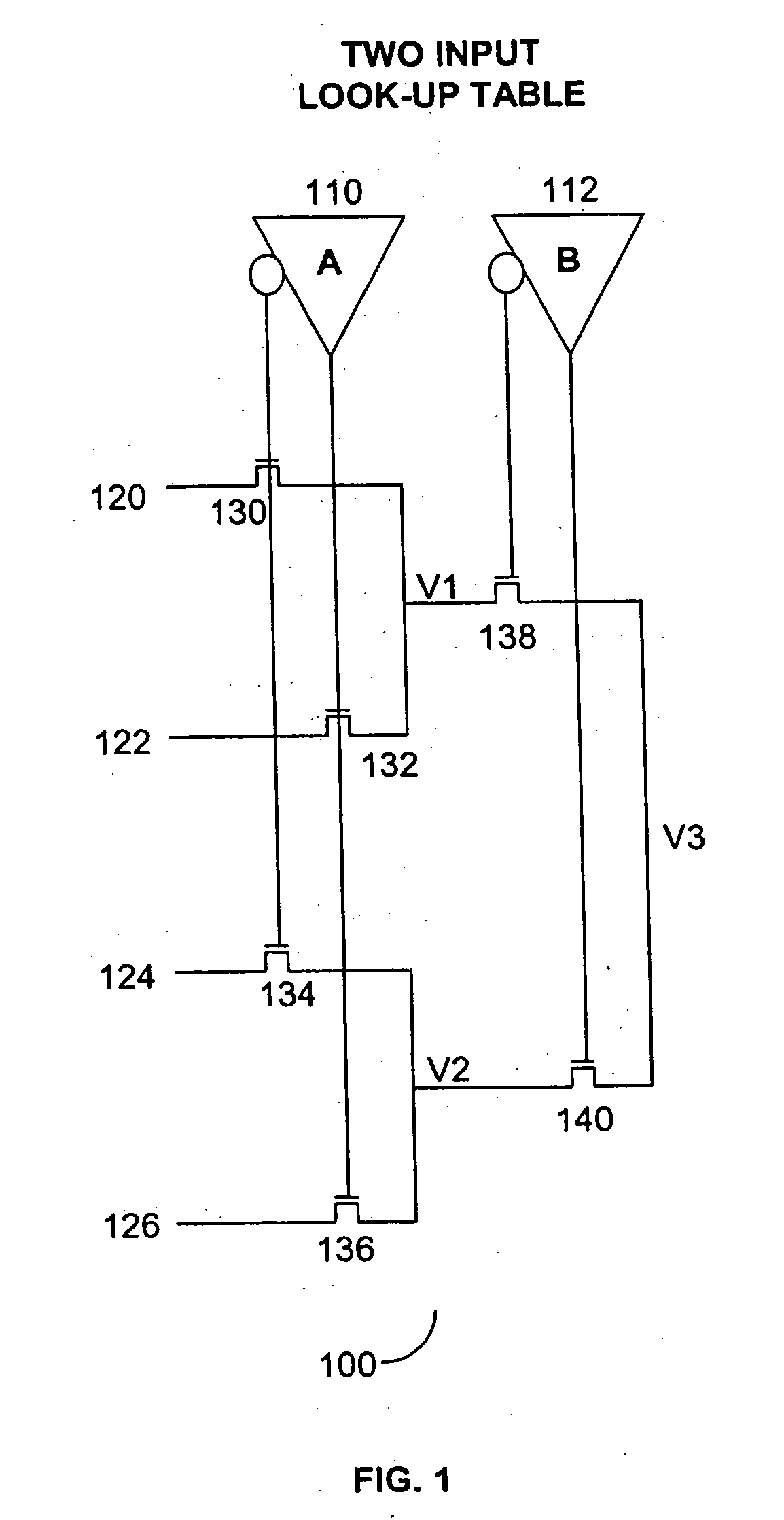

Systems and methods for reducing static and total power consumption in a programmable logic device

InactiveUS7188266B1Consumes less powerMaintaining level of functionalityVolume/mass flow measurementPower supply for data processingProgrammable logic deviceEngineering

A method and system for reducing power consumption in a programmable logic device (PLD) is provided. The power consumption may be reduced by preferably continually considering power consumption as a factor in circuit design during the technology mapping, routing, and period following routing of the programmable logic device.

Owner:ALTERA CORP

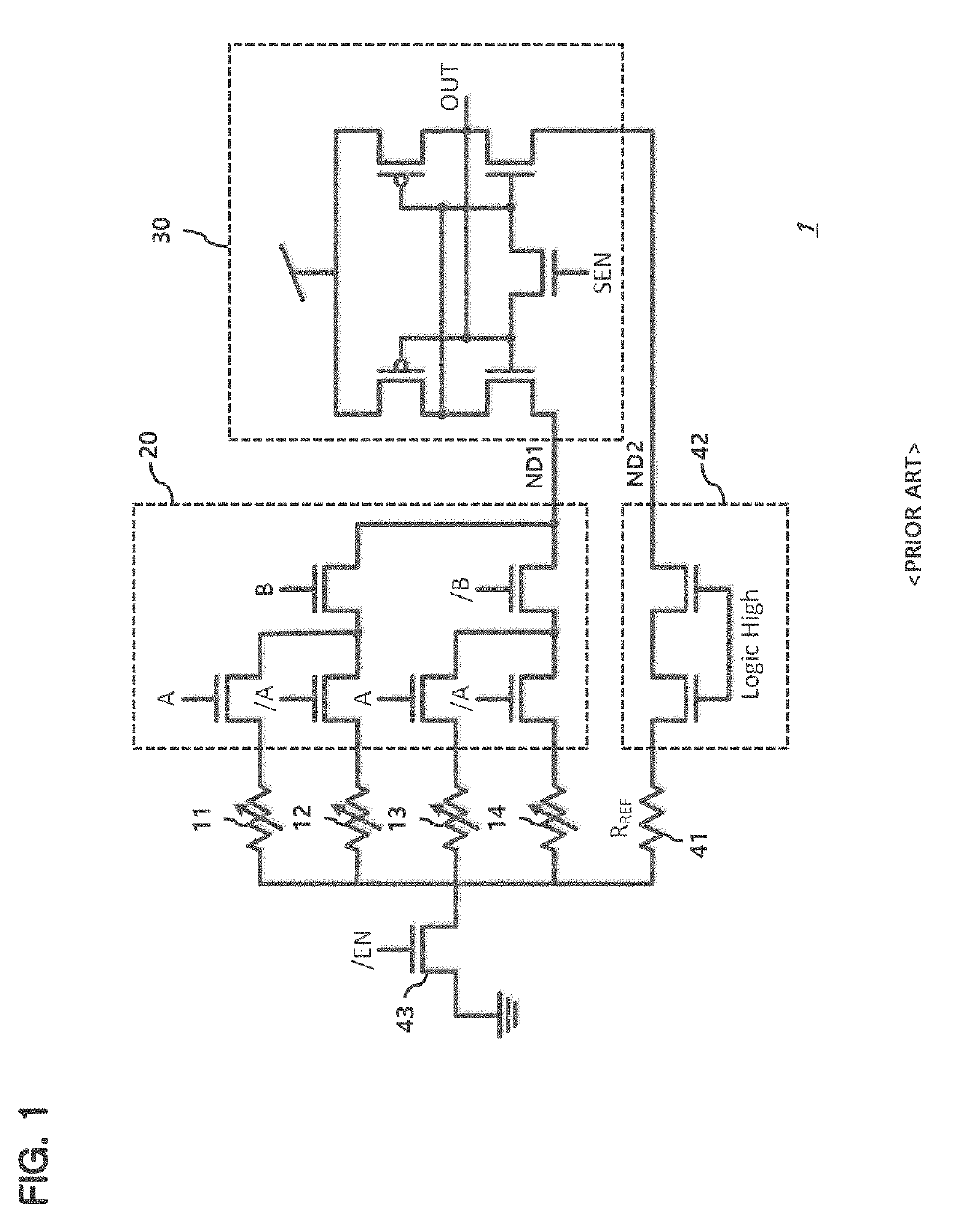

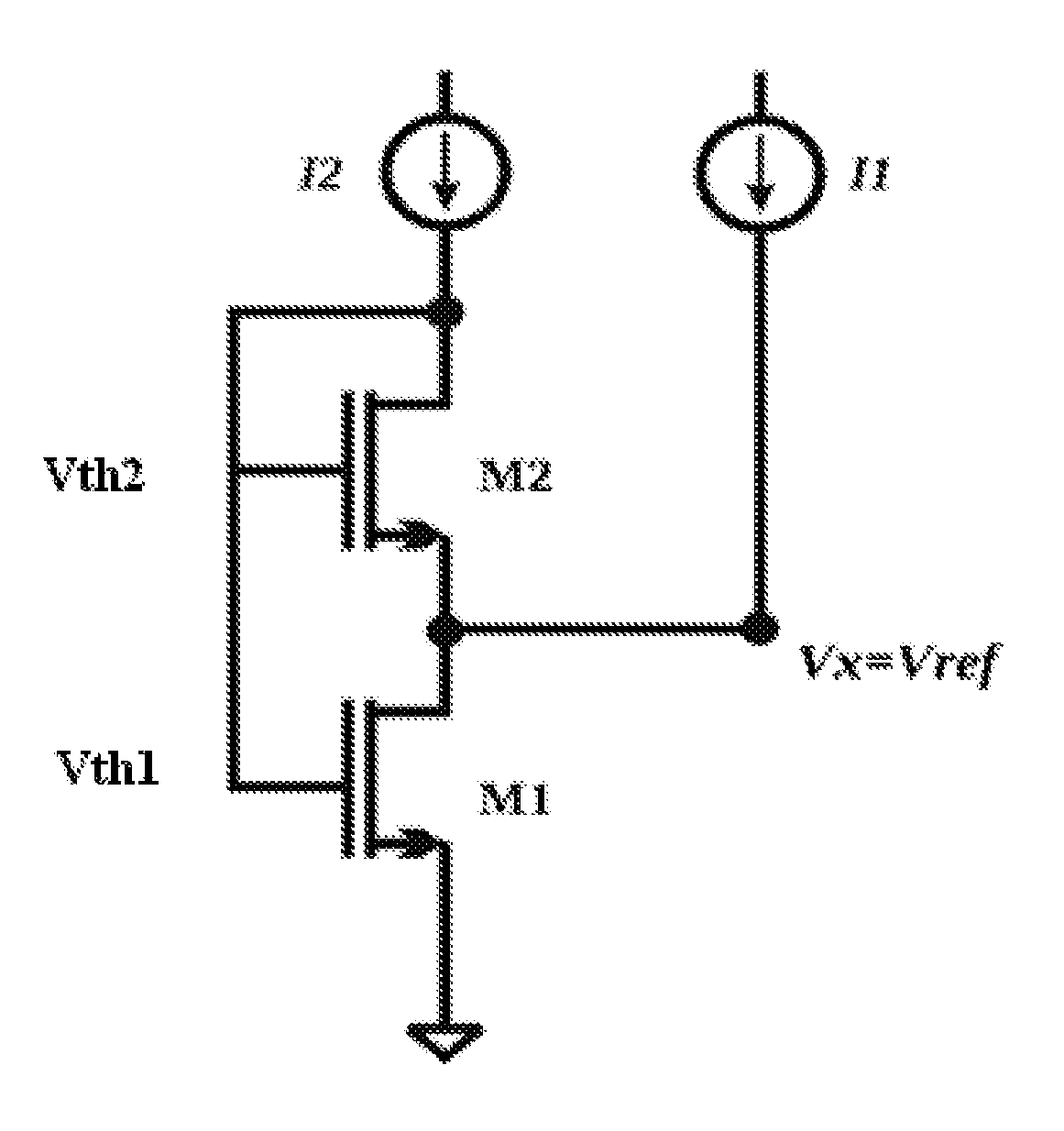

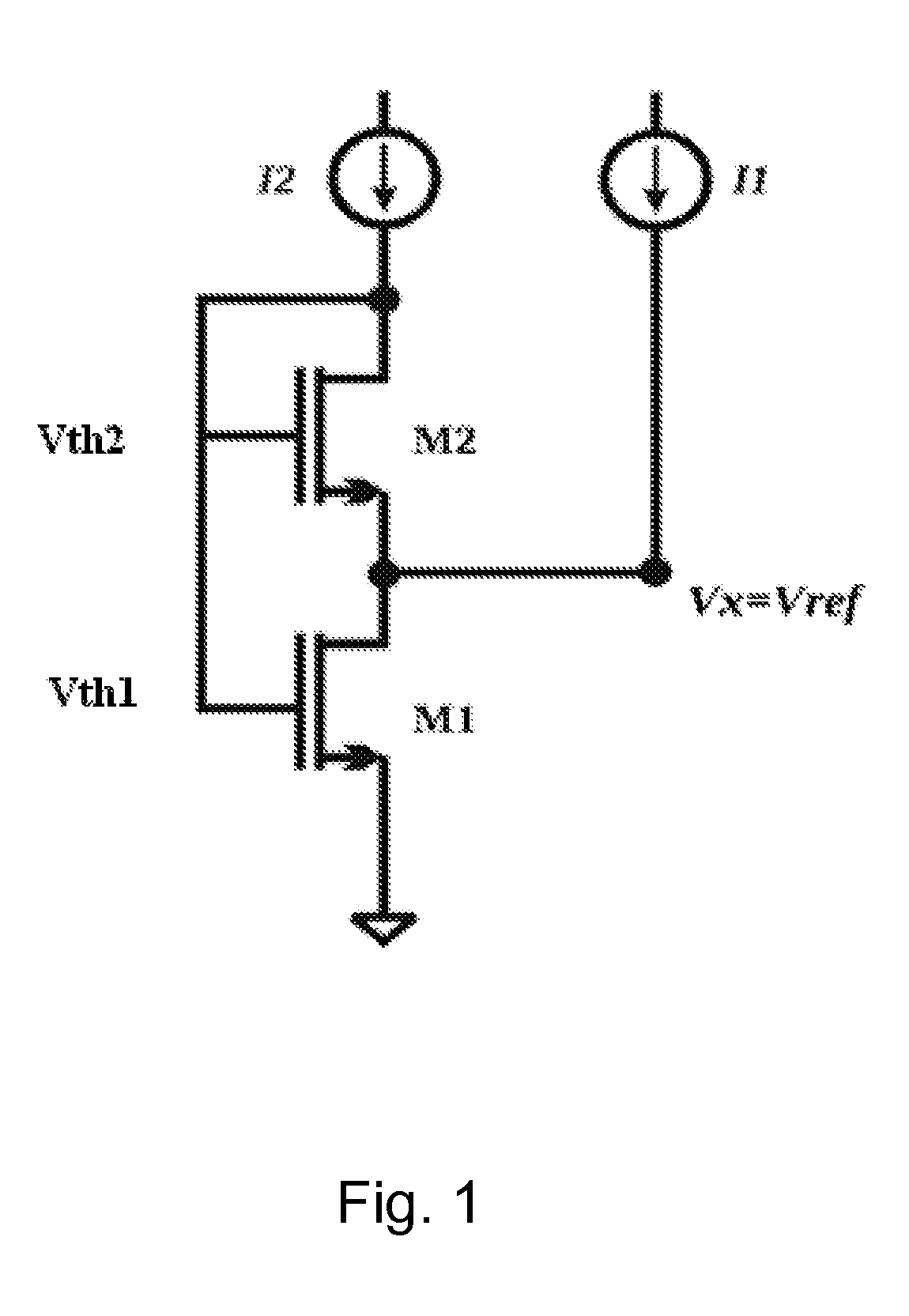

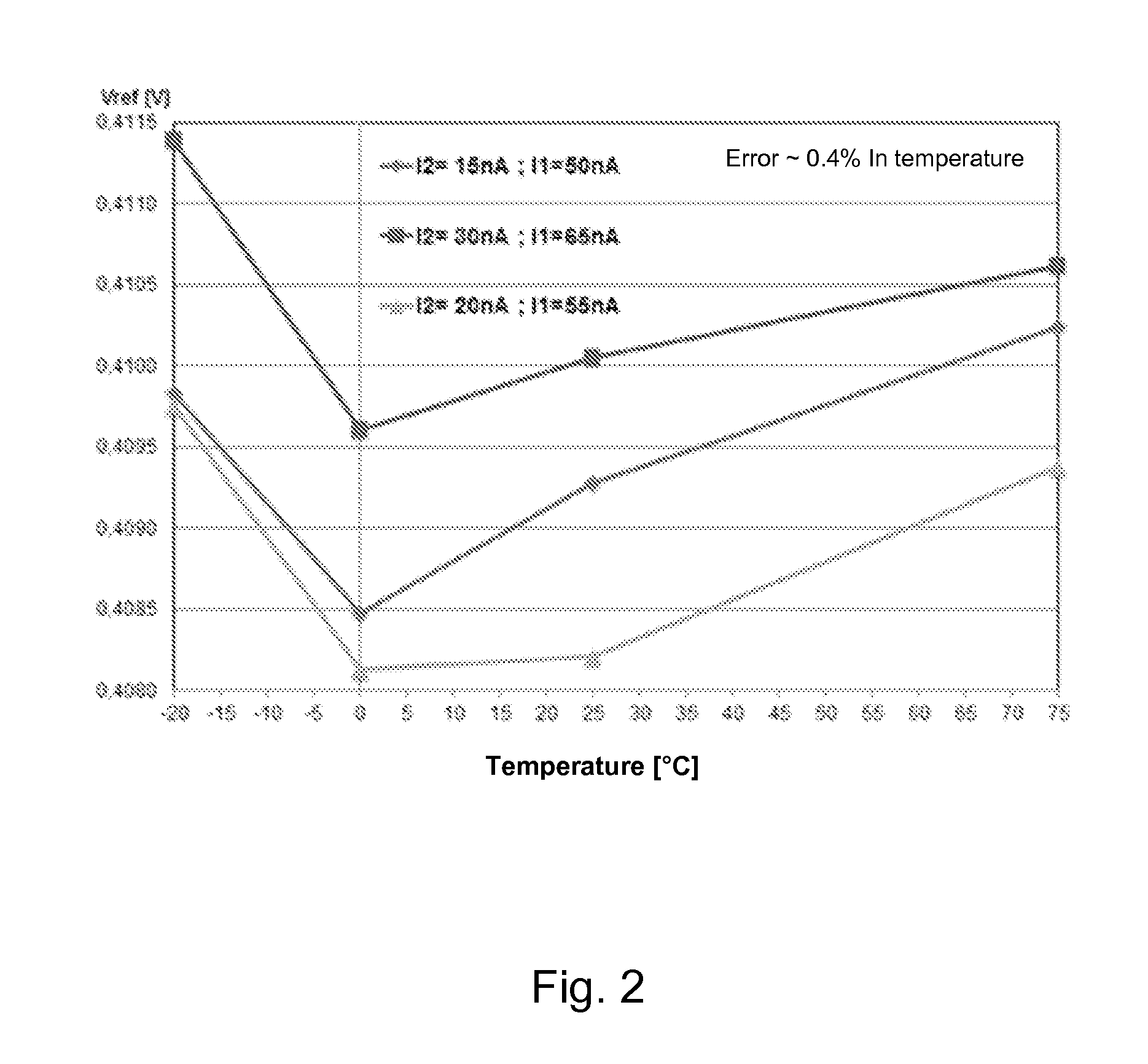

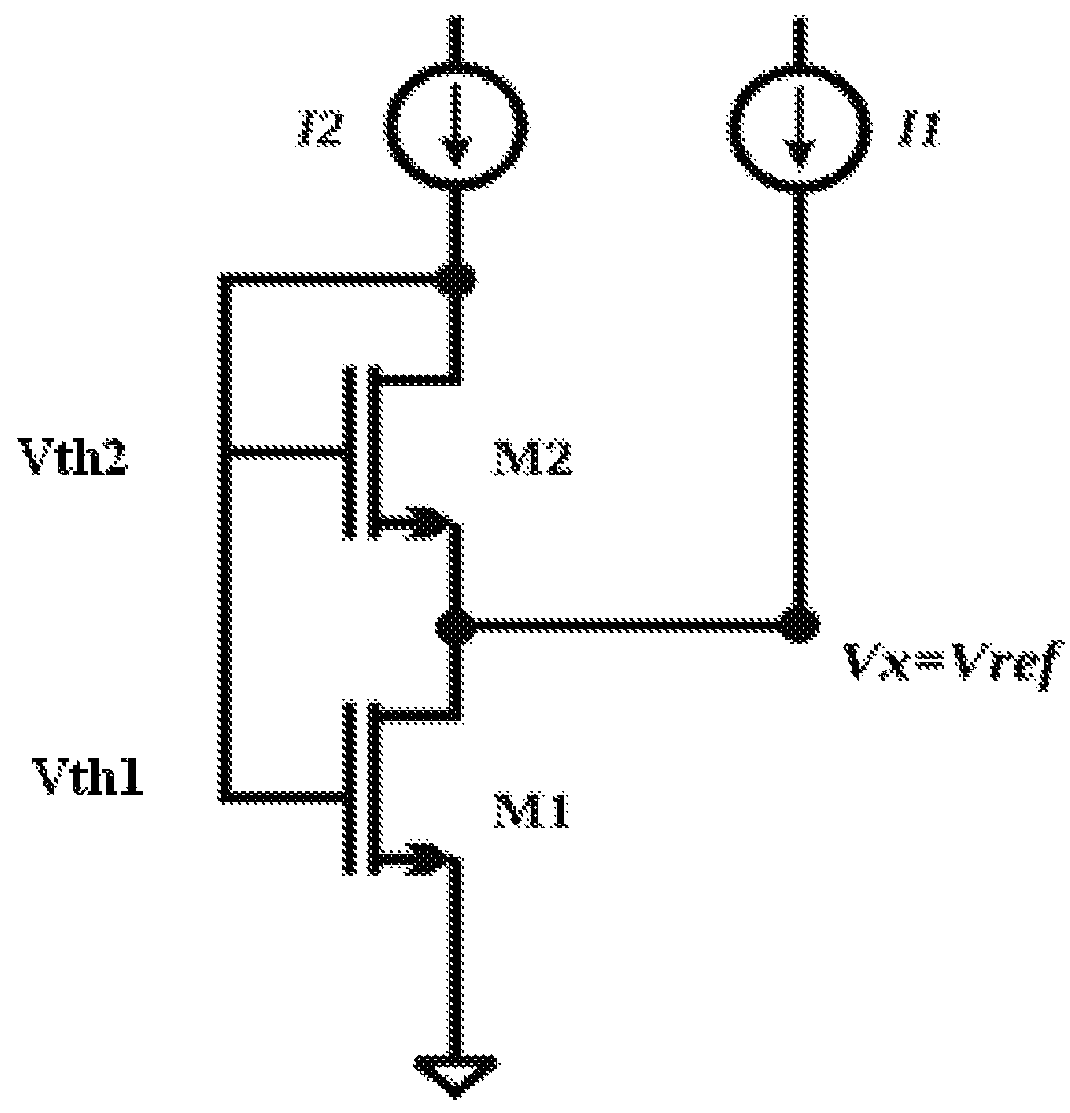

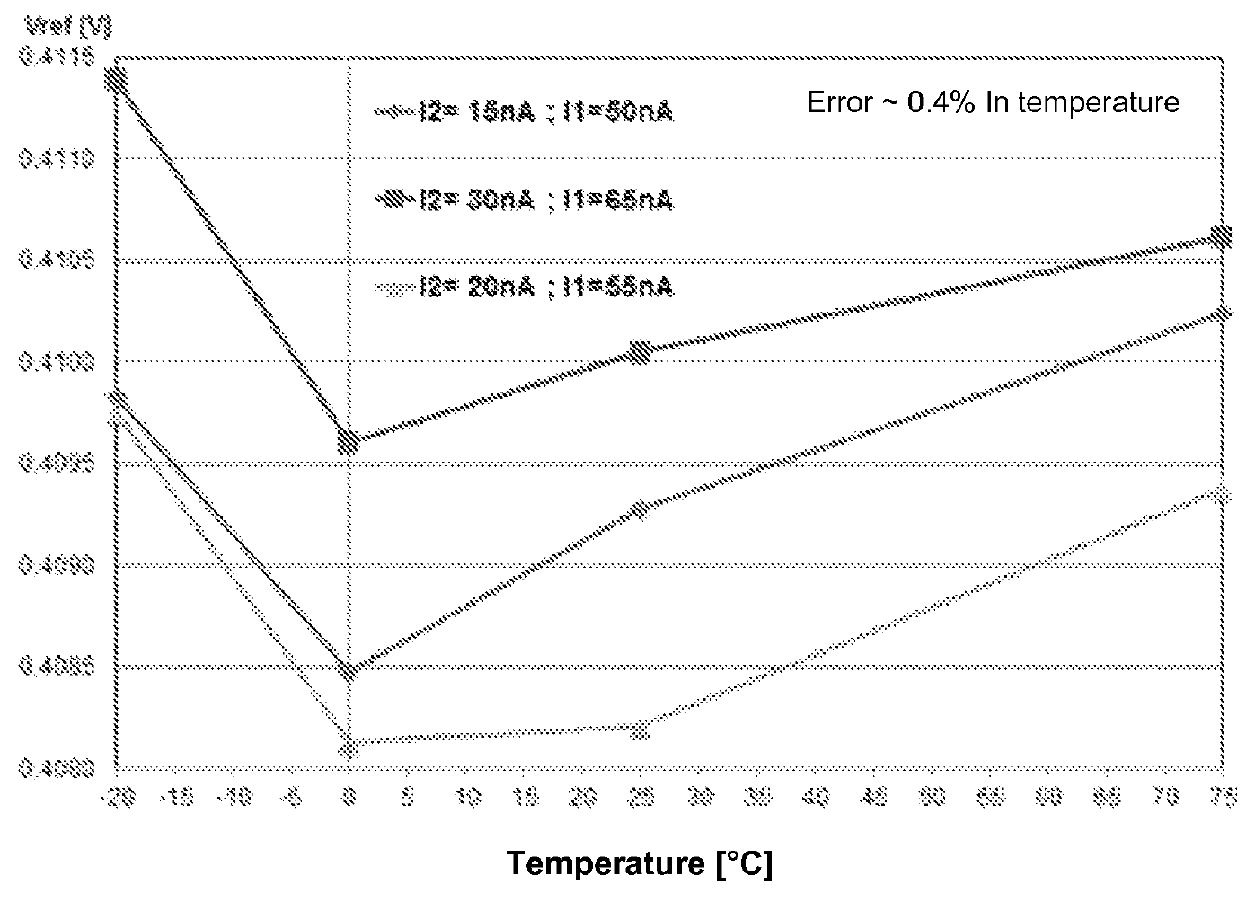

Temperature-Compensated Reference Voltage System With Very Low Power Consumption Based On An SCM Structure With Transistors Of Different Threshold Voltages

ActiveUS20150234401A1Eliminate inconvenienceReduce power consumptionElectric variable regulationCMOSPower flow

A simple SCM (Self Cascode MOSFET) structure to generate a sub-1V reference voltage in the SCM intermediate node. The structure requires only 2 transistors to create a temperature-compensated reference voltage. When sized correctly, the transistors in the SCM will operate both at weak, moderate or strong inversion, and in the saturation region or saturation and triode regions, providing good correspondence and low part to part variation. The following proposal innovates by operating with supply voltages on a broad variation range, from 3.6V through below 1V (sub-1V operation), with bias currents in the range of tens of nA (nano Amperes) and temperature variation smaller than ±1% from −40° C. through 85° C. This is an extremely low cost implementation (in terms of area and complexity), compatible with standard CMOS manufacturing processes, and very robust (in terms of fab-to-fab transference, technology mapping, and also well controlled part-to-part variation).

Owner:CENT NACIONAL DE TECHA ELECTRONICSA AVANCADA

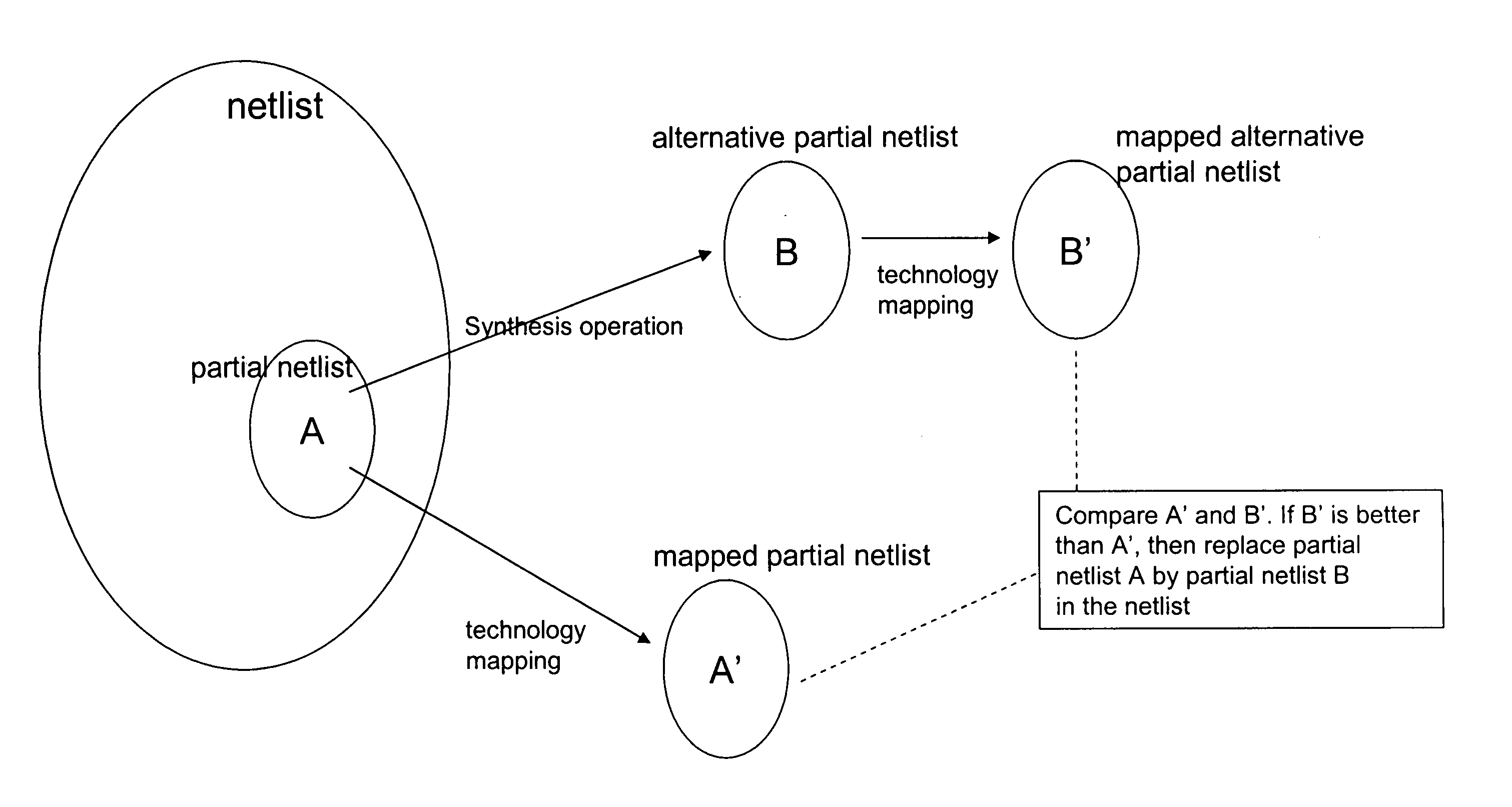

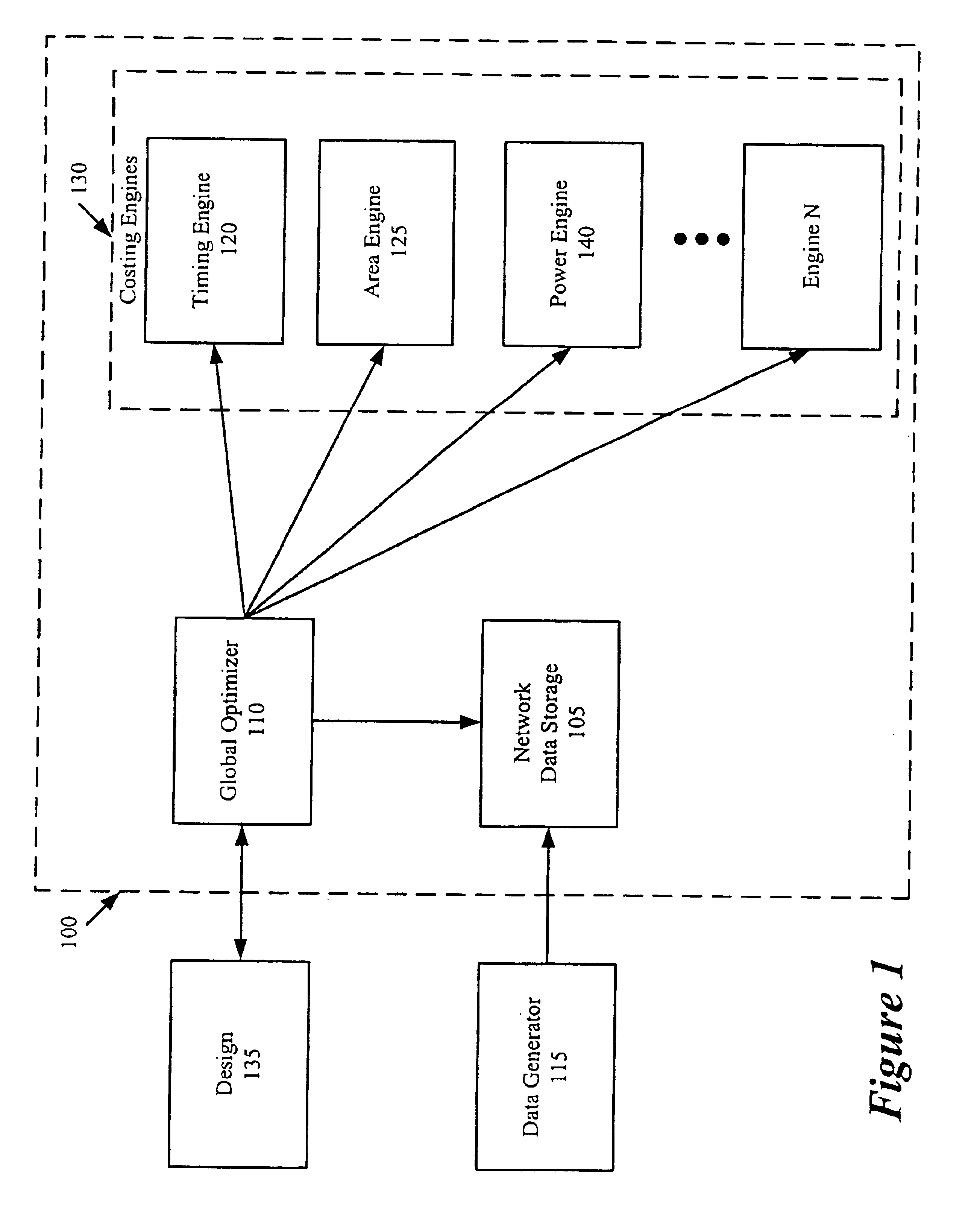

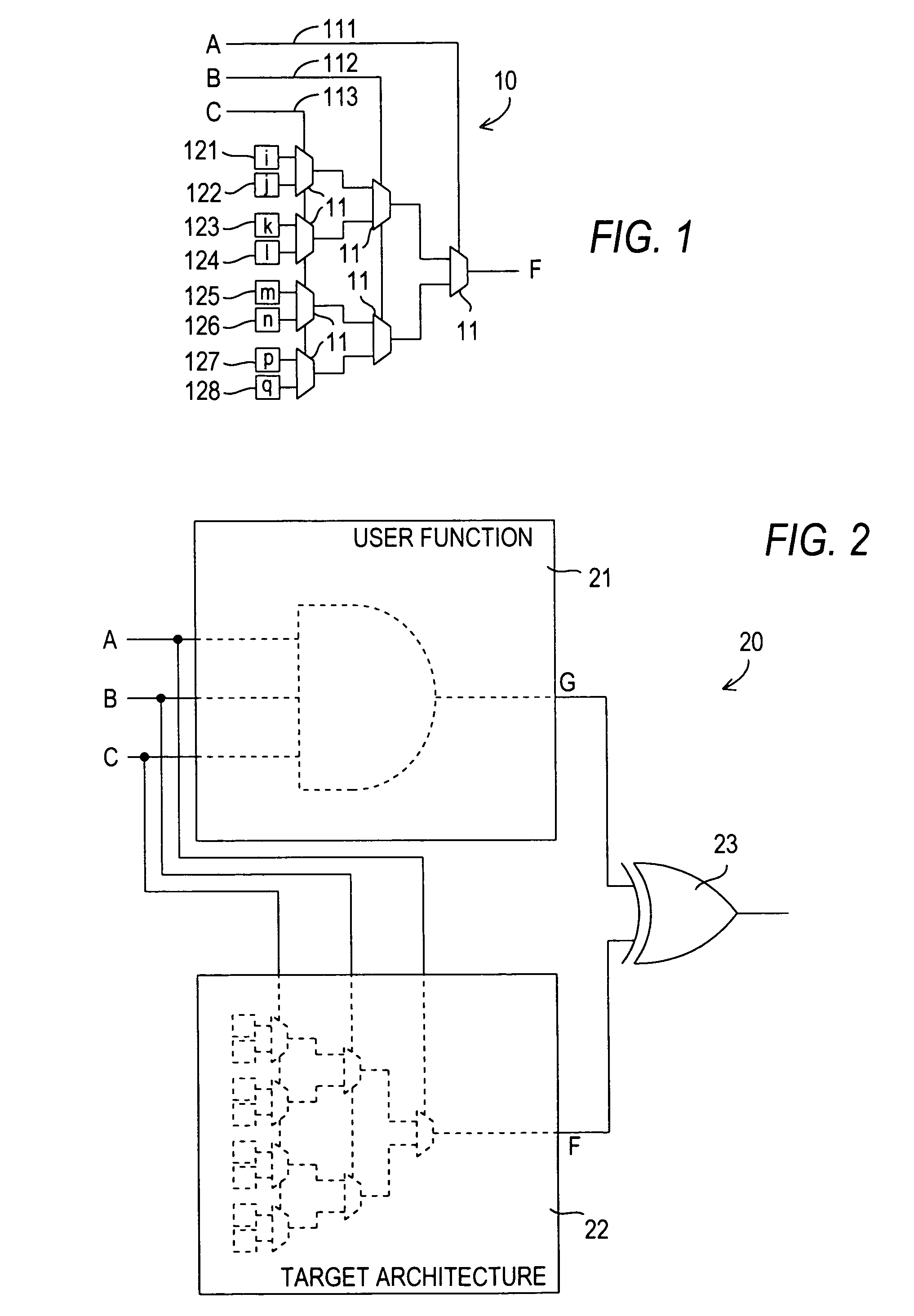

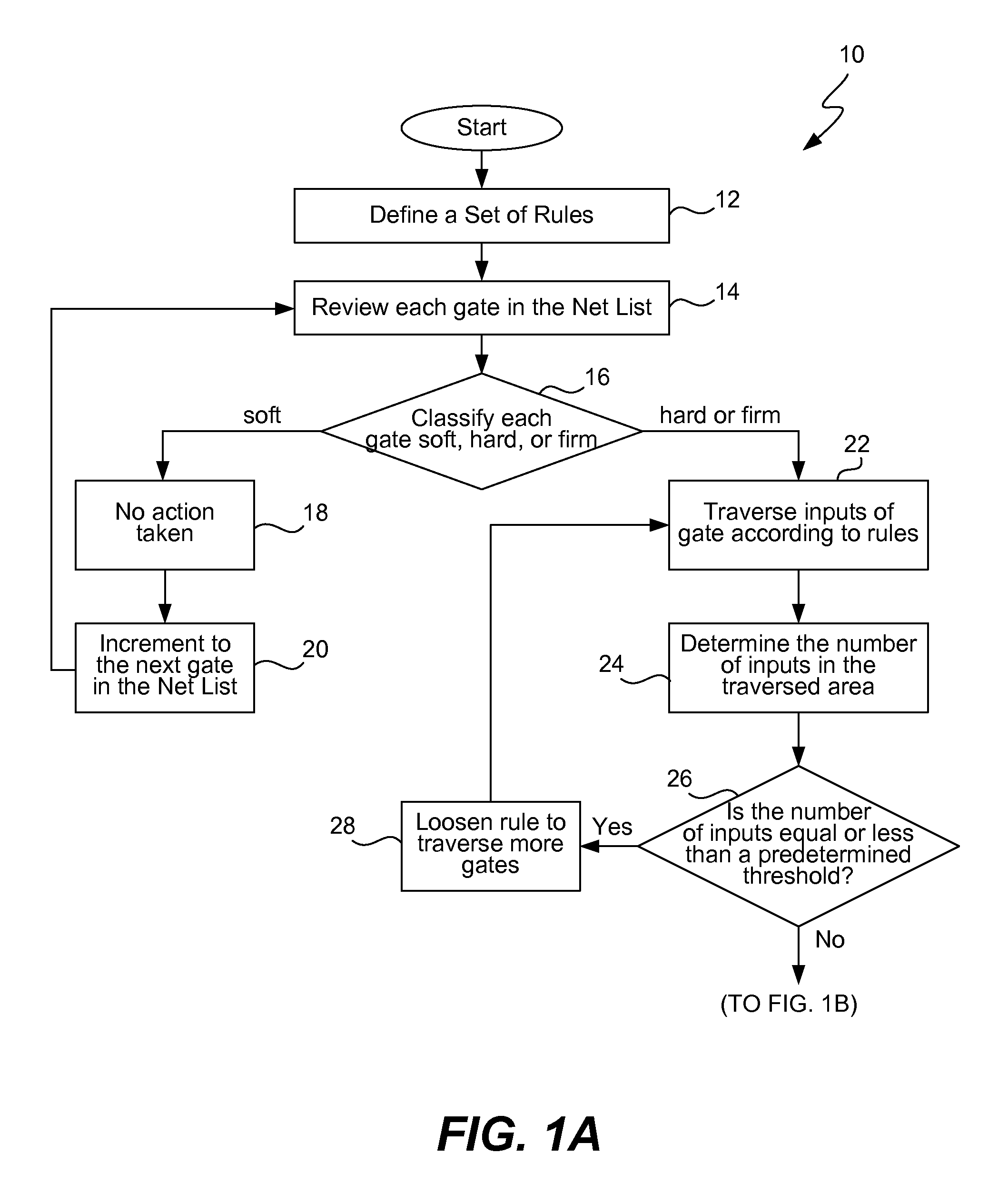

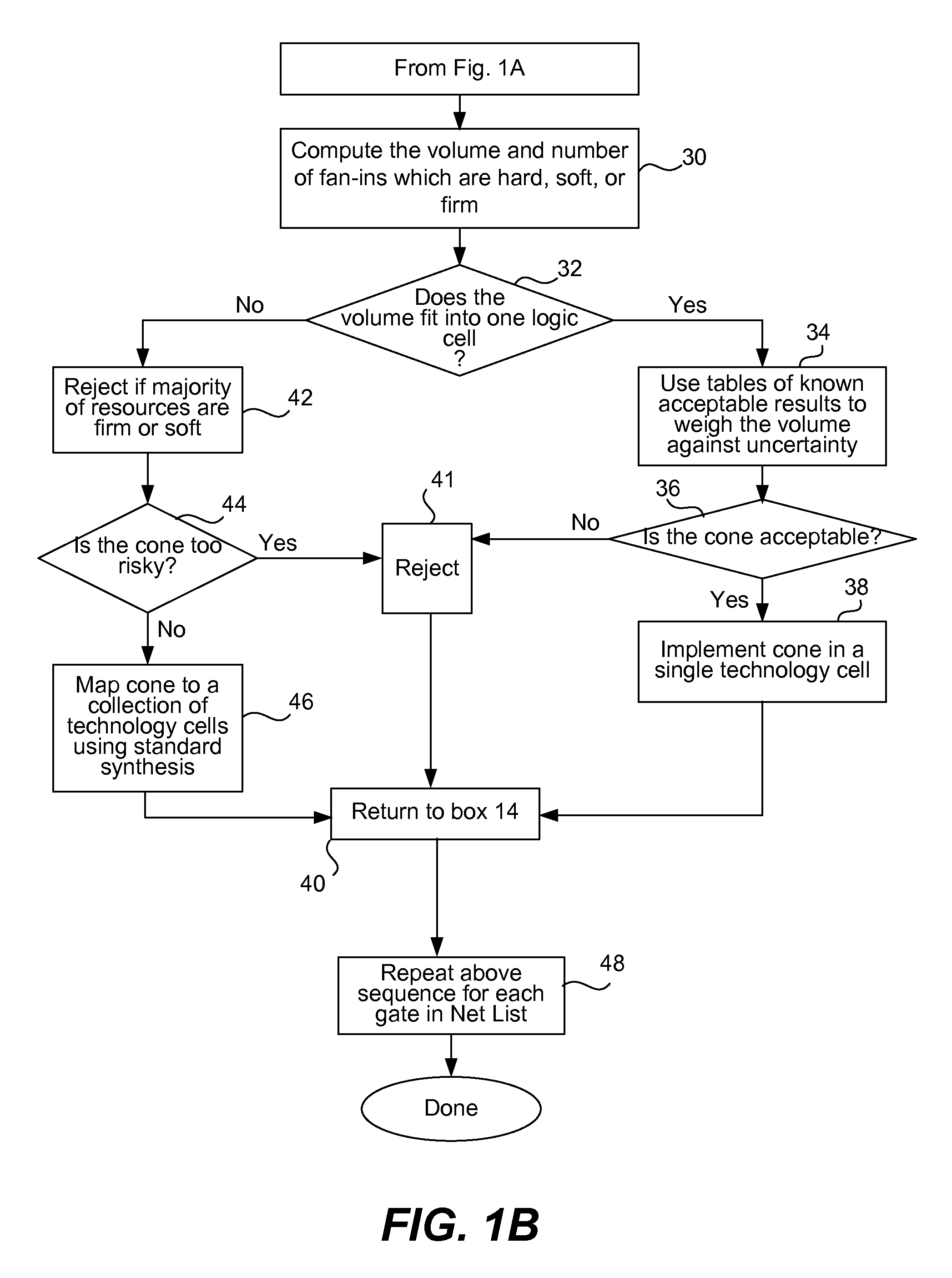

Estimating quality during early synthesis

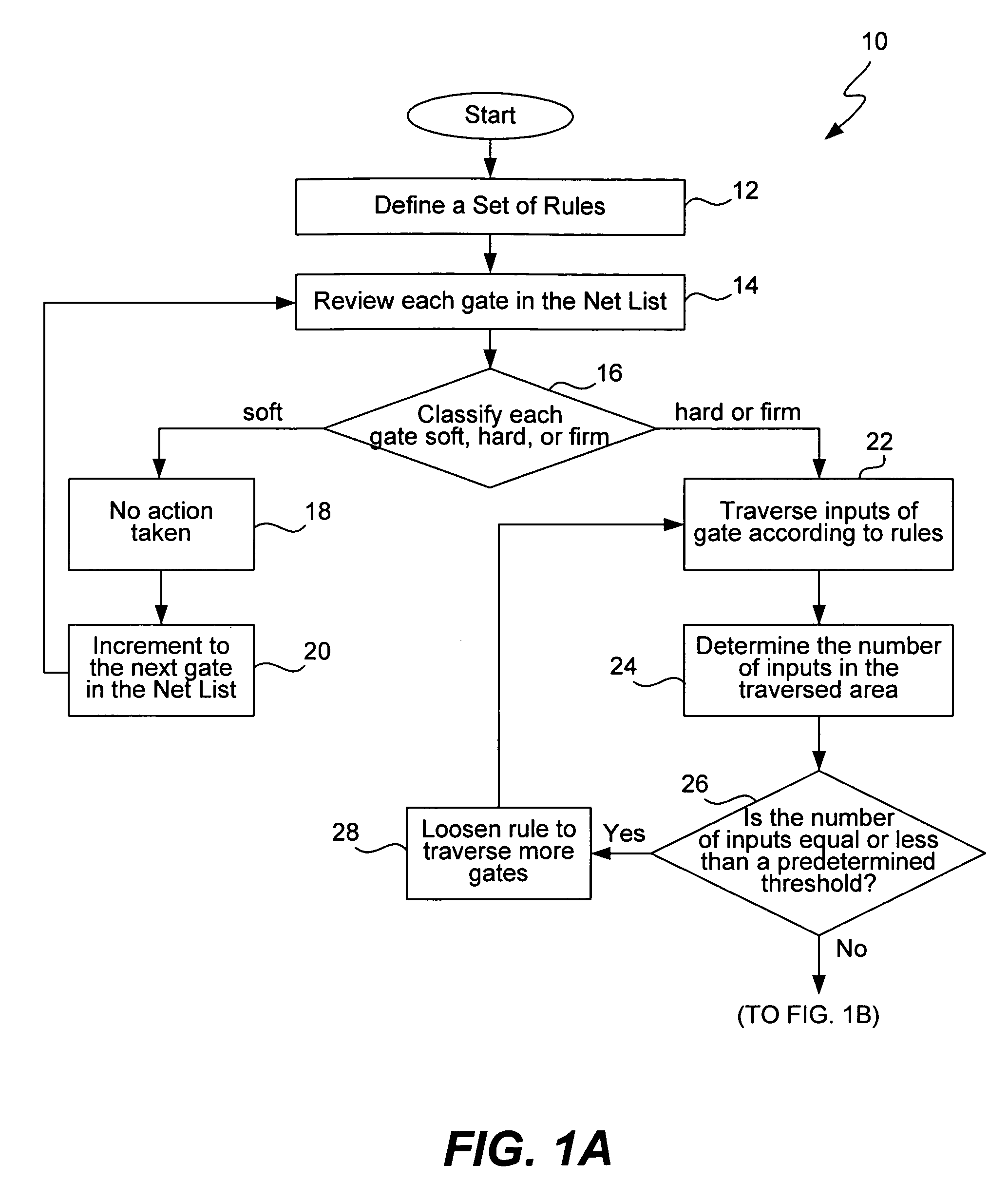

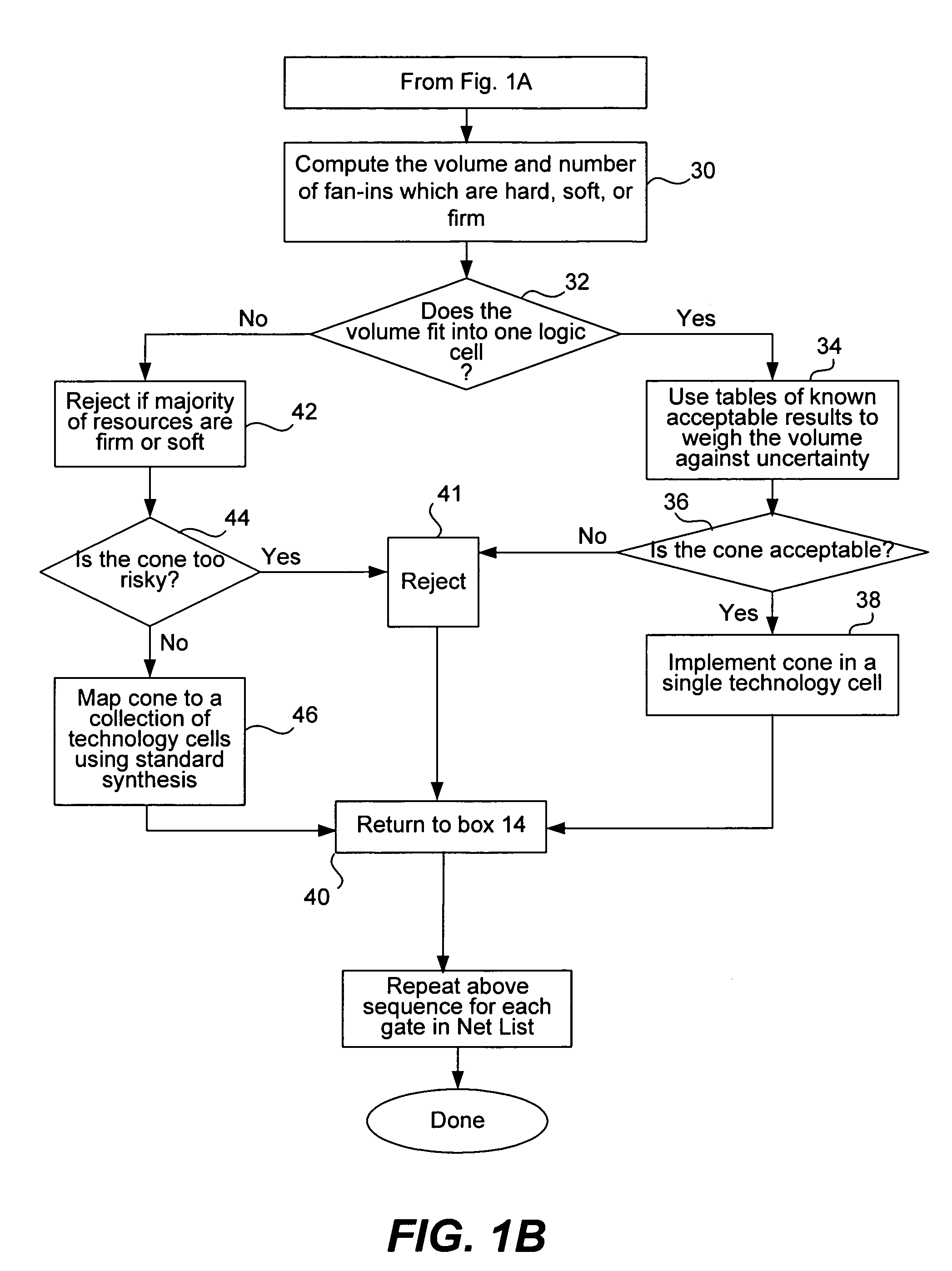

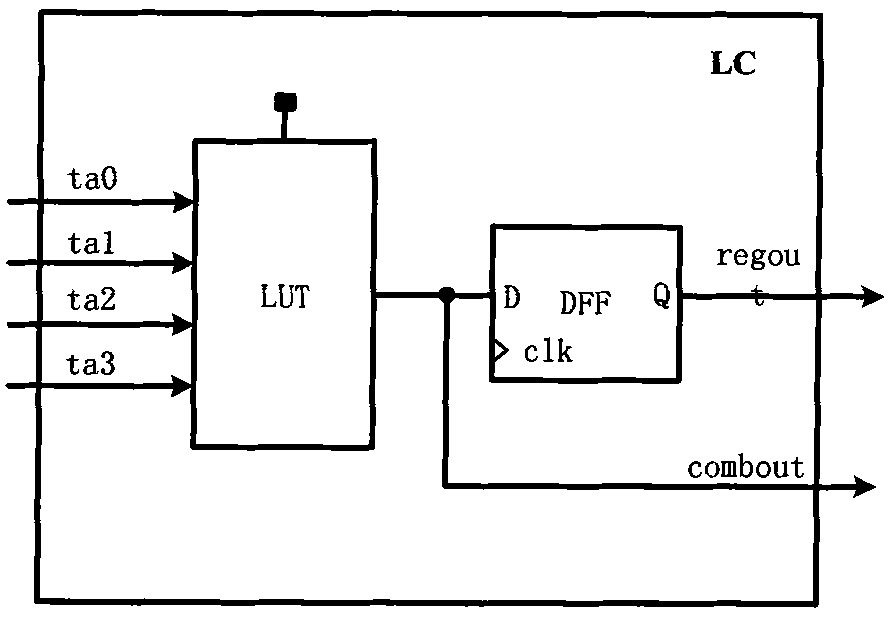

InactiveUS7171633B1Improve accuracyImproving minimizationComputer aided designSoftware simulation/interpretation/emulationLogic cellTheoretical computer science

A computer aided system includes a method of improving the accuracy, optimization, and minimization for the synthesis and mapping of logical functions into the logical structures of a target technology, such as the logic cells (e.g., look-up tables) of a programmable logic integrated circuit. In a specific implementation, the invention incorporates late-stage synthesis operations, such as found during a technology mapping operation, into earlier stage synthesis procedures. These late-stage synthesis operations are used to provide better estimates of delay and area of a final compiled design in order to guide optimization operations.

Owner:ALTERA CORP

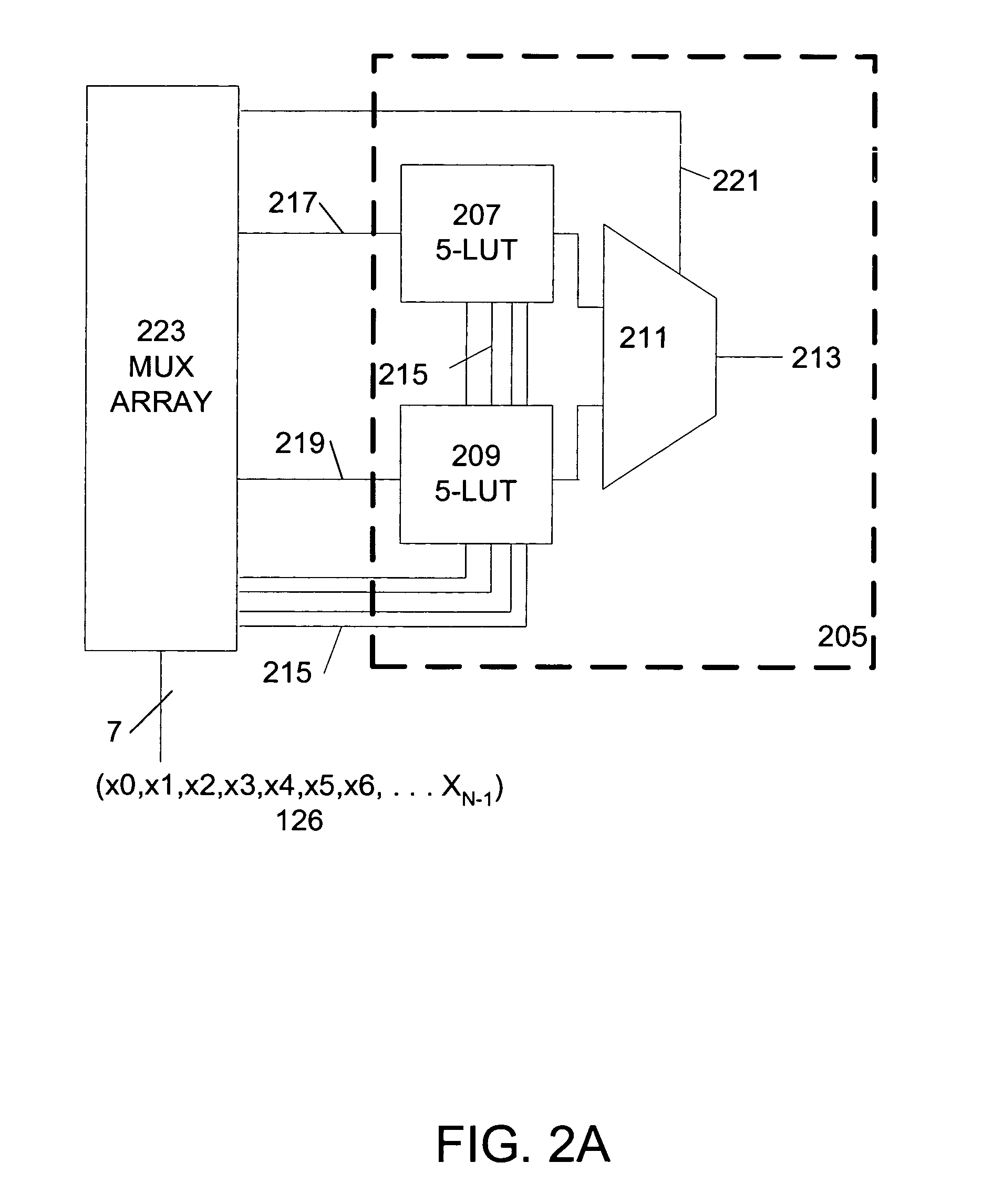

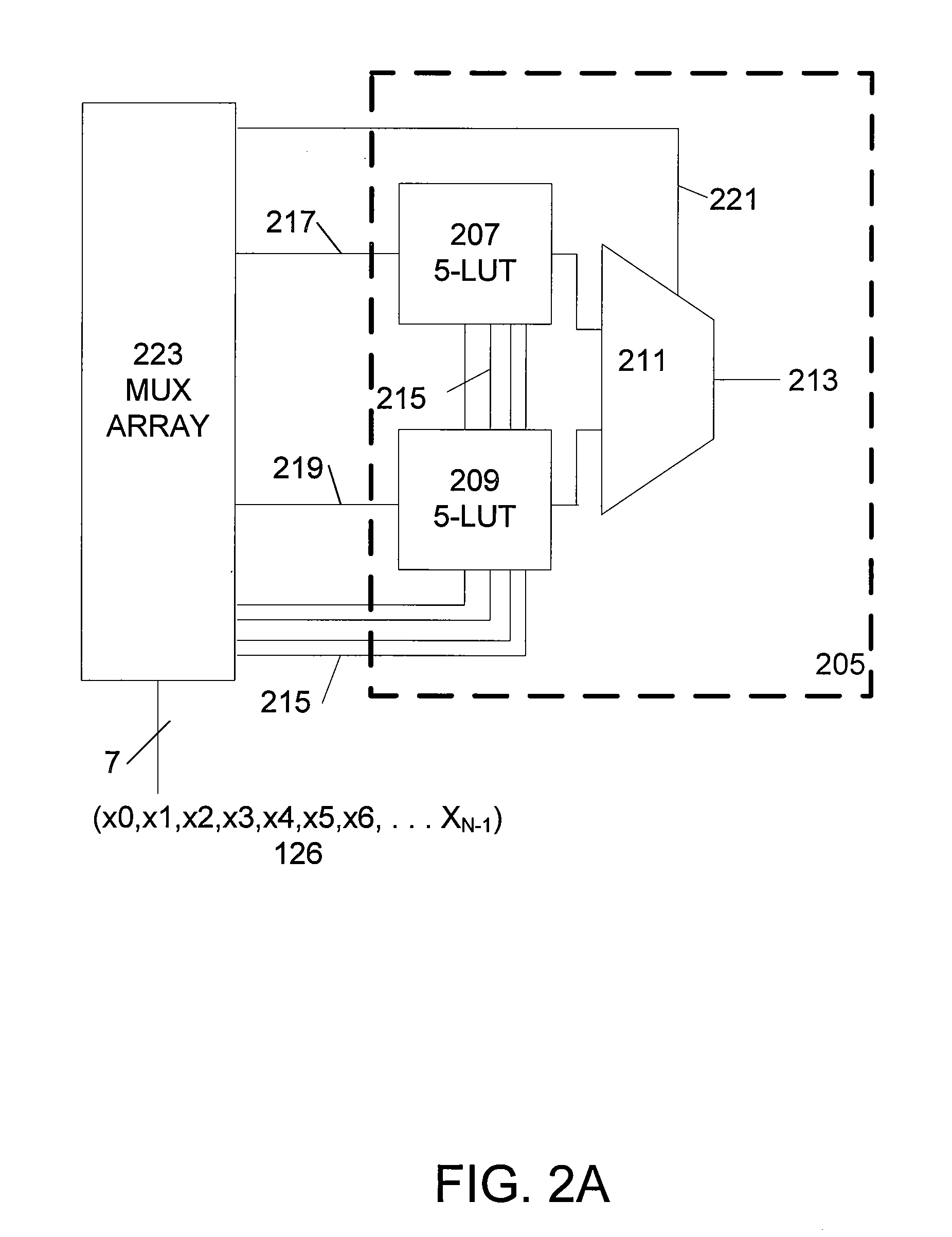

Technology mapping technique for fracturable logic elements

InactiveUS7100141B1Minimizes circuit areaReduce circuit areaCAD circuit designSoftware simulation/interpretation/emulationComputer Aided DesignProgrammable logic device

Owner:ALTERA CORP

Chip debugging using incremental recompilation

While debugging, a user chooses an incremental recompile. Internal signals of interest are selected and output pins are optionally reserved. An incremental recompile of the compiled design includes compiling a routing from each internal signal to an output pin. The technology-mapped netlist and placing and routing information corresponding to an original compiled design are saved into a database during full compilation. During debugging, an incremental compiler retrieves this information to build the original routing netlist. The database building, logic synthesis and technology mapping stages may be skipped. New connections are added, fitted to the device, and then the final routing netlist is output into a programming output file (POF) in a form suitable for programming the PLD. The user views the internal signals at the output pins chosen. The user may iterate through this process many times in order to debug the PLD. The debugging assignments may be deleted.

Owner:ALTERA CORP

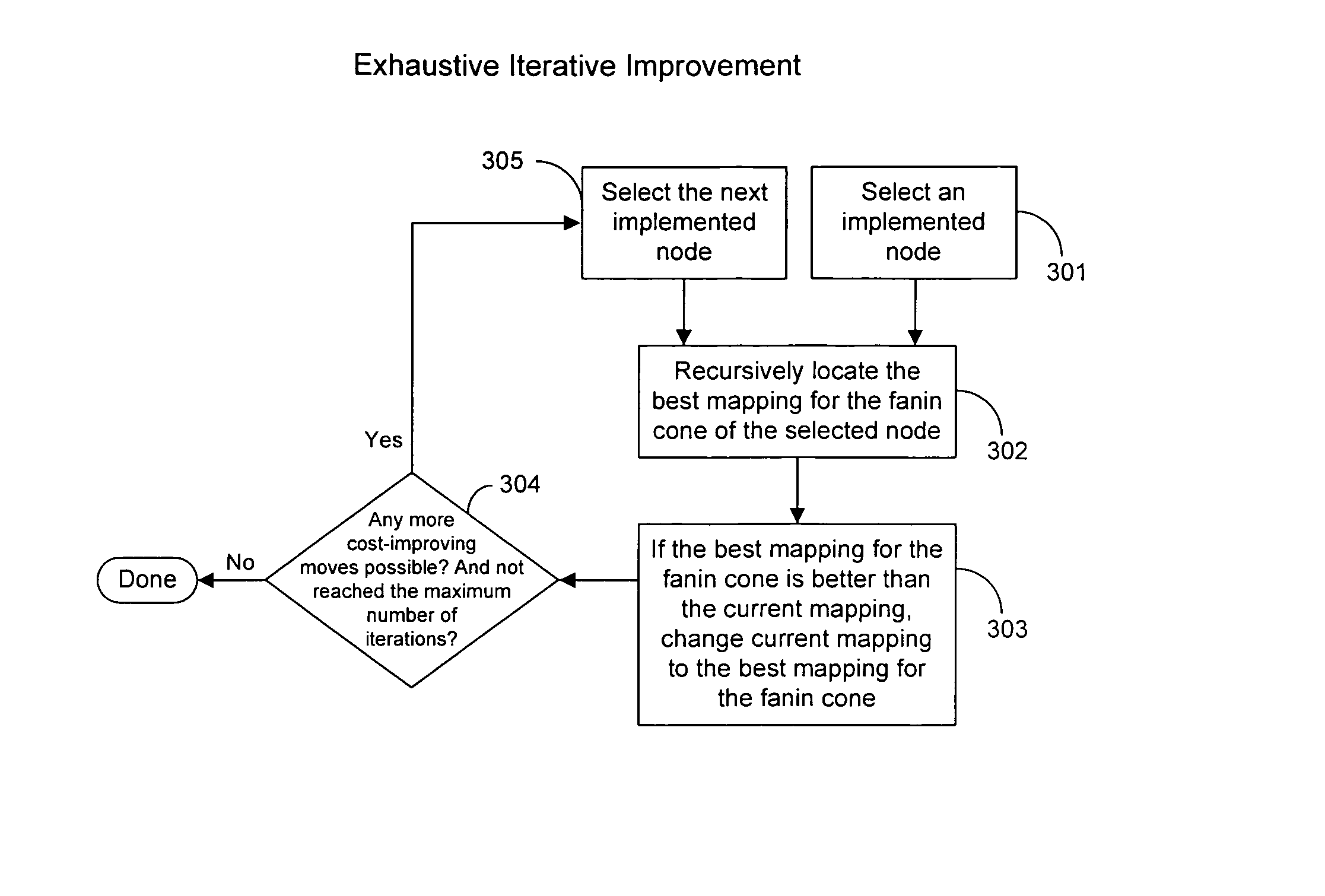

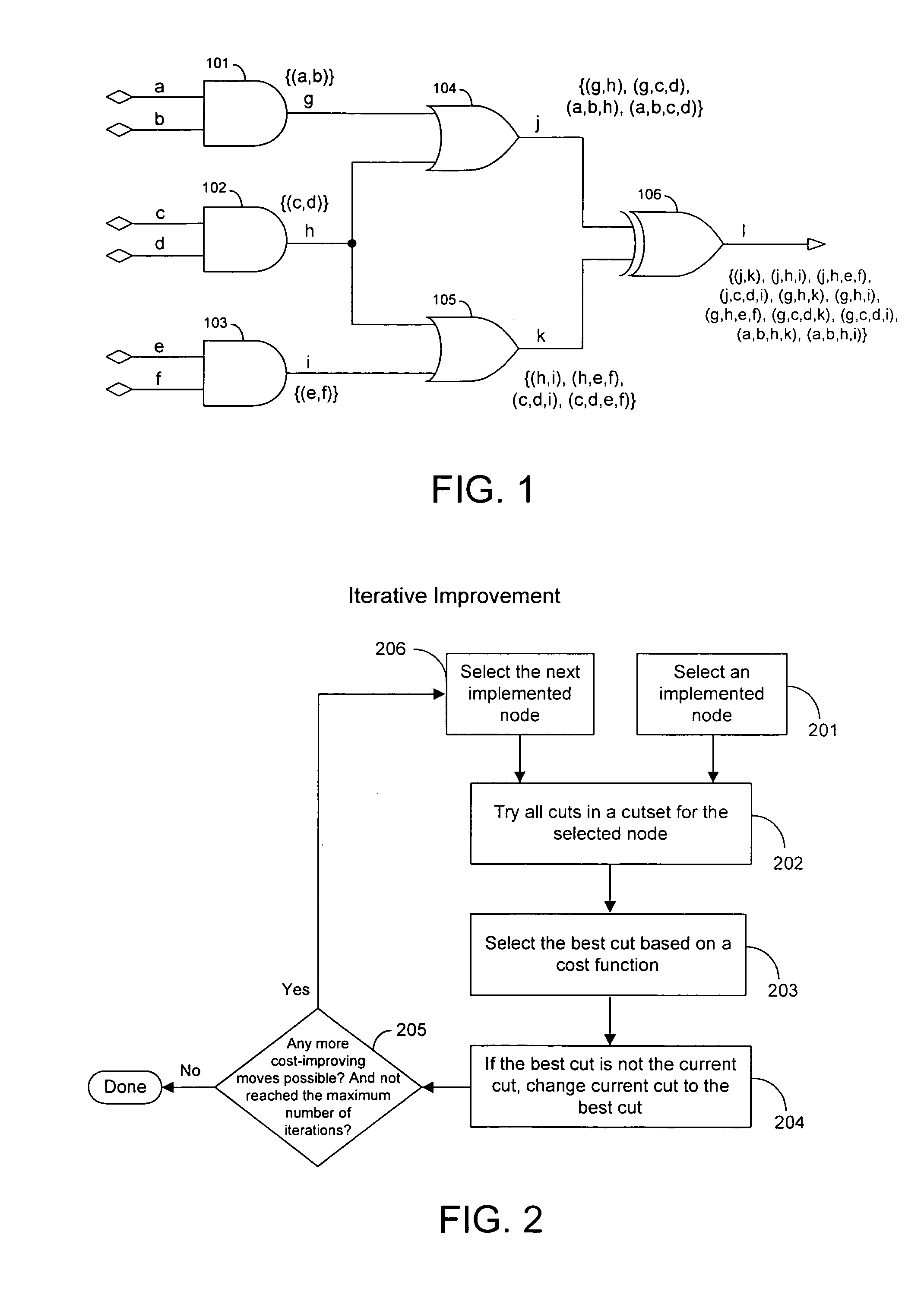

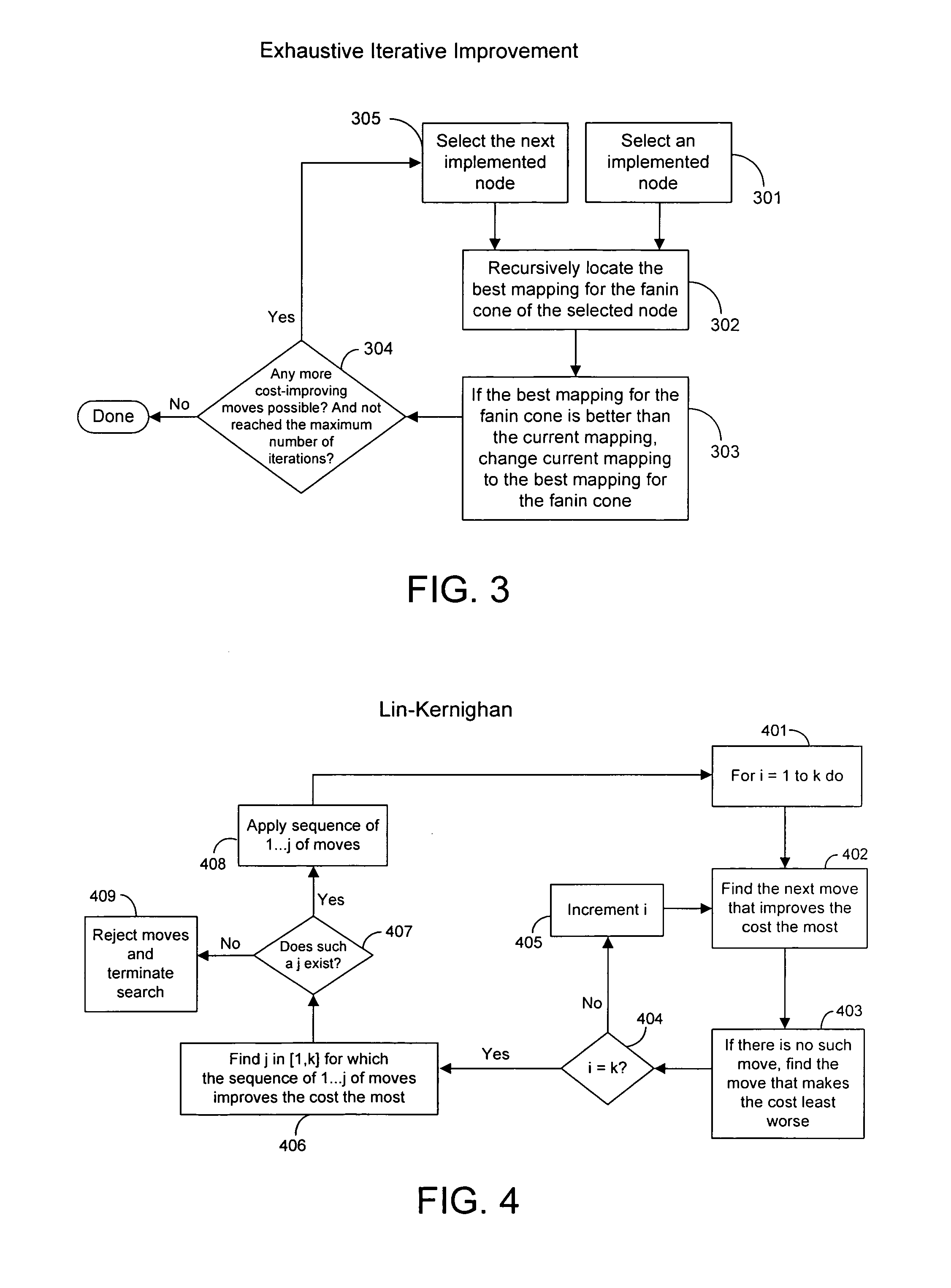

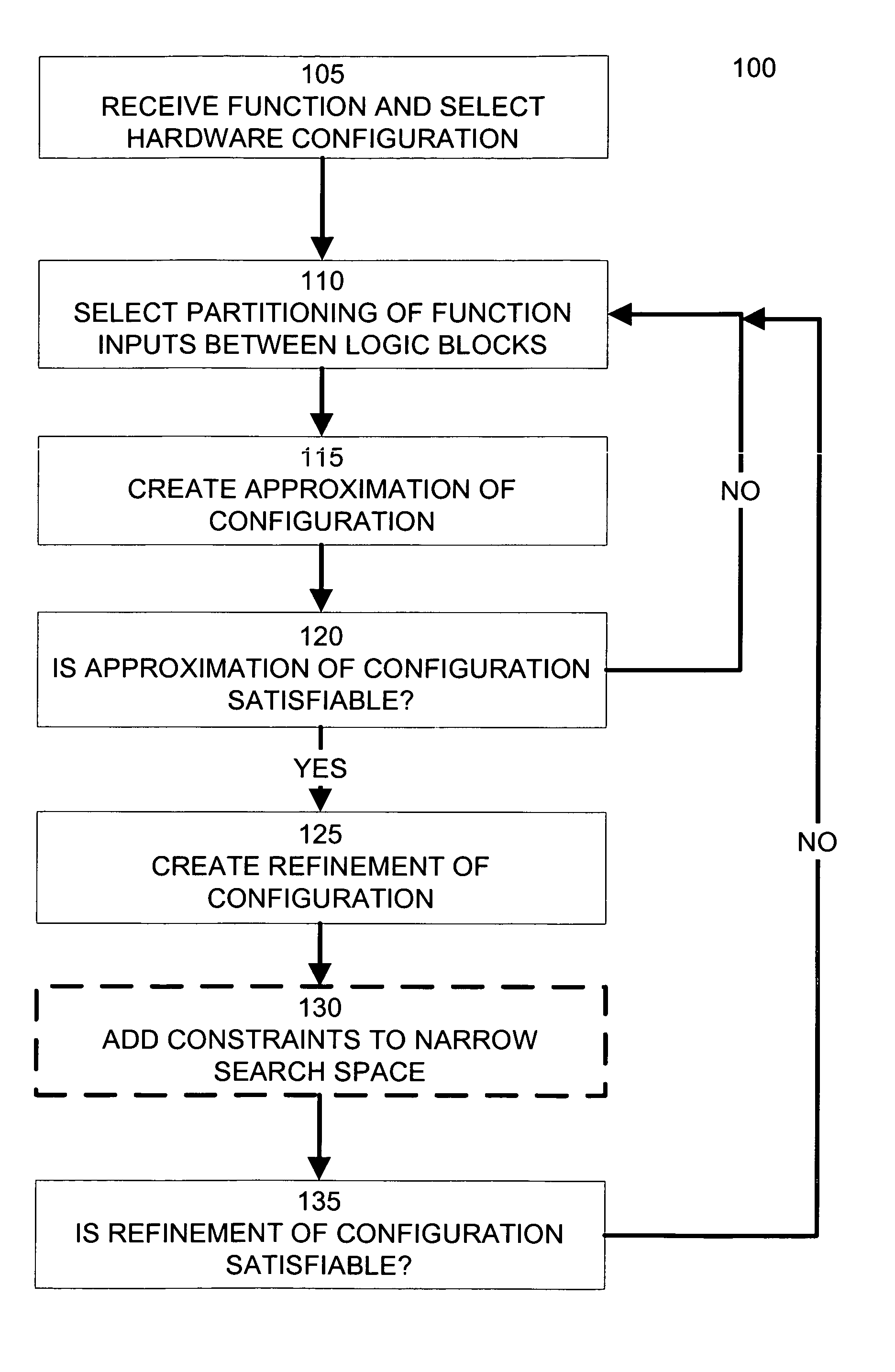

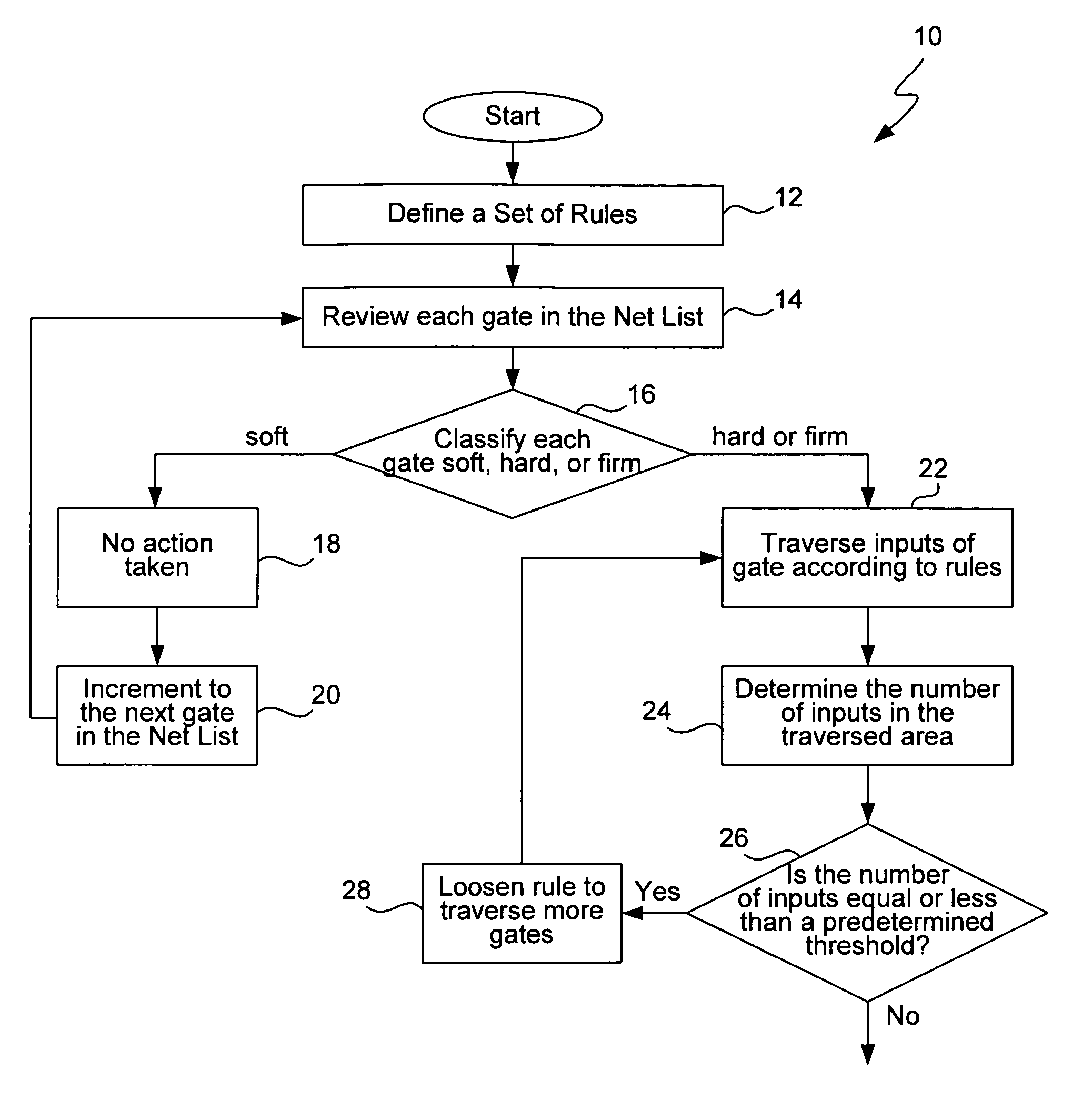

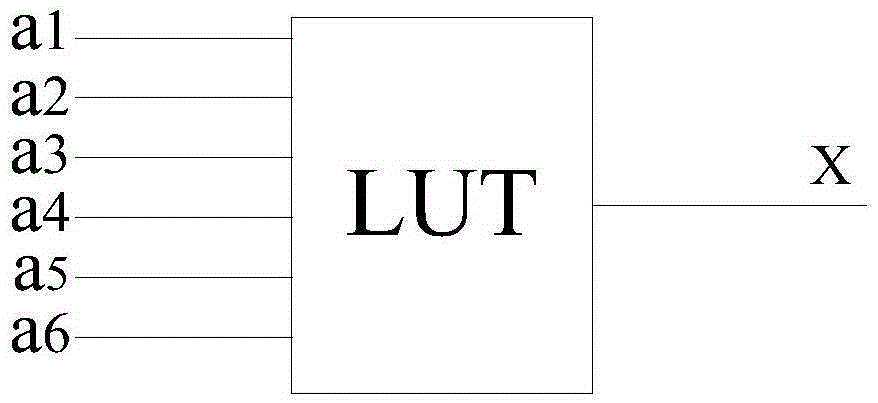

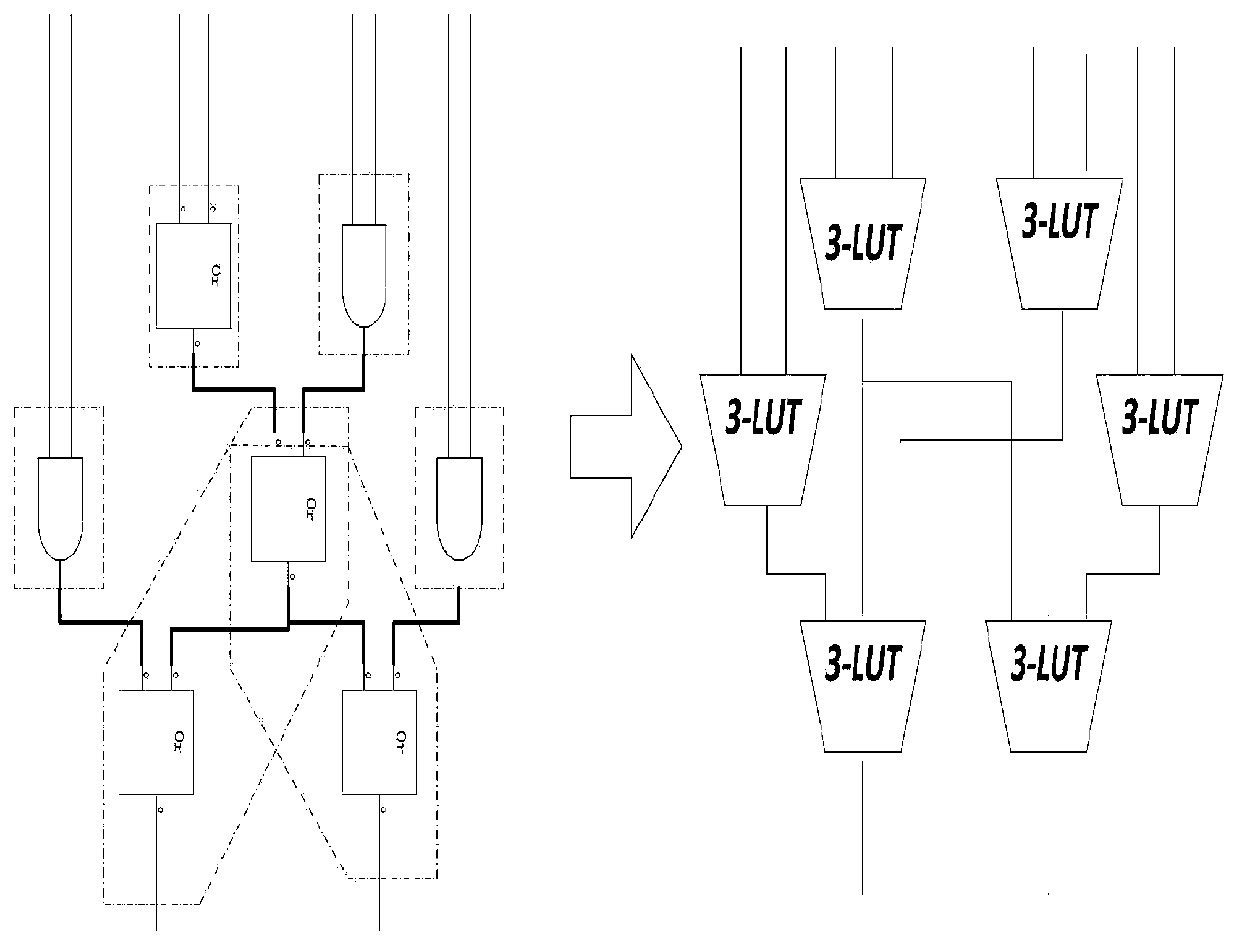

Local searching techniques for technology mapping

InactiveUS7418690B1Increase costCAD circuit designSpecial data processing applicationsLookup tableLogic gate

Local searches are provided for improving technology mapping for programmable logic integrated circuits. A local search algorithm is applied to a solution for mapping logic gates in a netlist to lookup tables (LUTs) on a programmable logic IC. The local search algorithm applies a series of local moves to the solution. At each move, a small change to the LUT mapping is proposed, and the change in cost for that LUT mapping change is computed. If the cost is improved, the change is accepted and the LUT mapping is replaced by the changed LUT mapping. Otherwise, the change in solution is either rejected, or accepted with a probability that depends on the cost change. The cost function can be chosen to represent one or more features of the LUT mapping, such as area, speed, power consumption, or a combination thereof.

Owner:ALTERA CORP

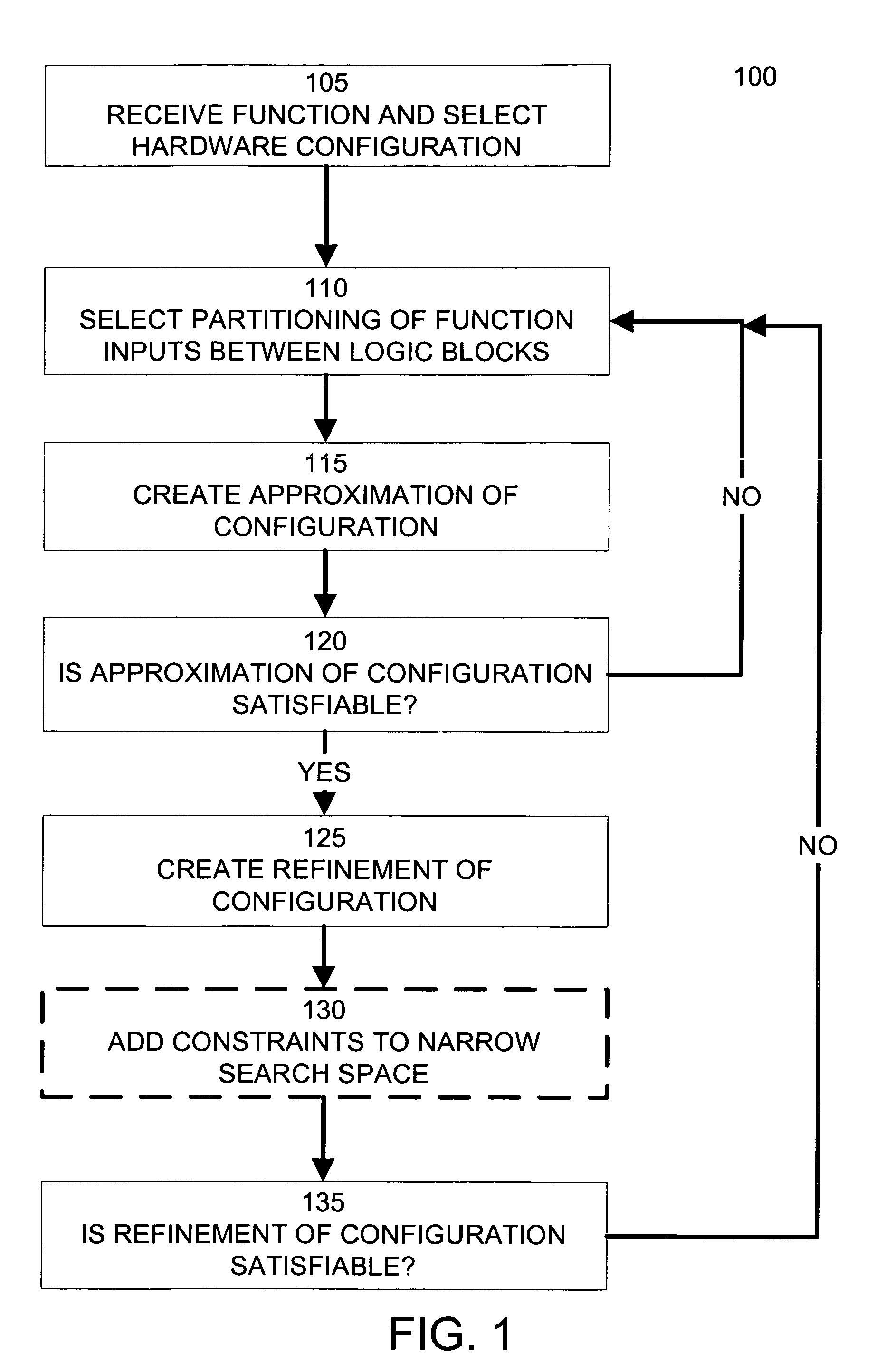

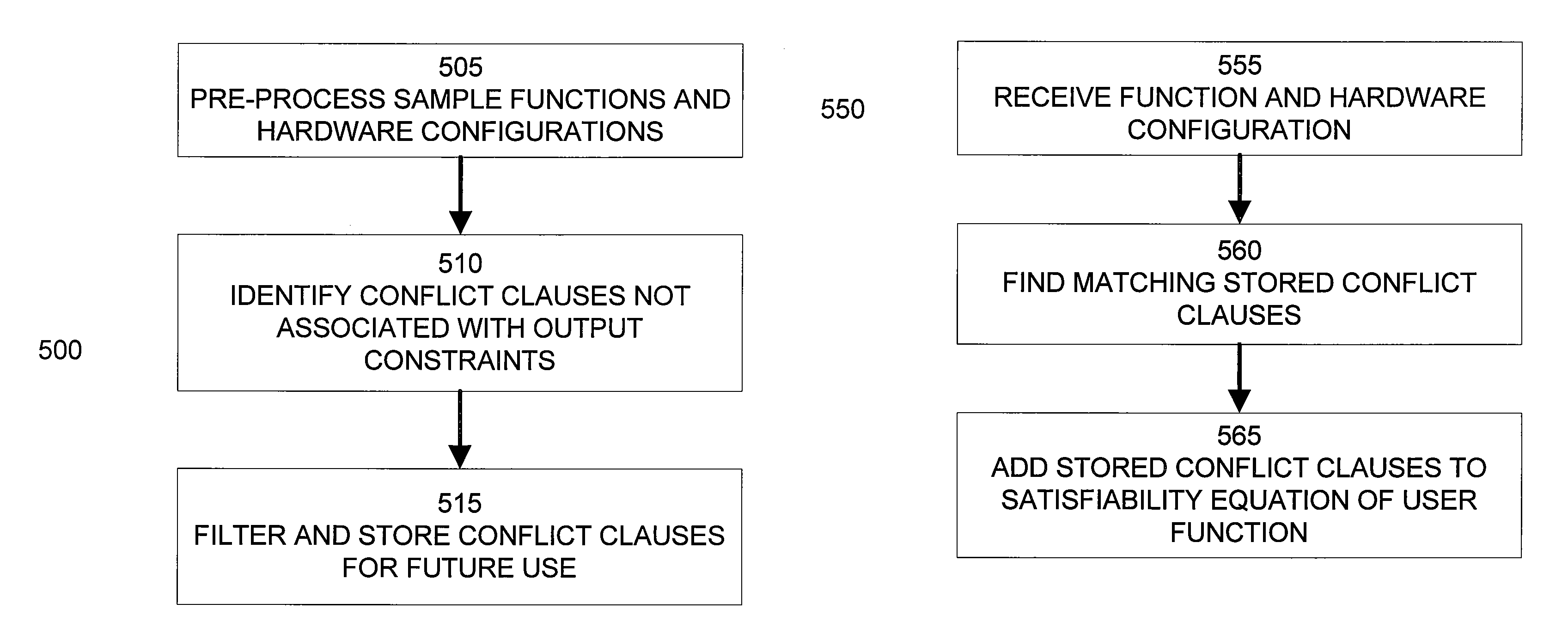

SAT-based technology mapping framework

InactiveUS7386828B1Narrow down the search spaceEfficiently determinedComputer aided designSoftware simulation/interpretation/emulationTheoretical computer scienceAnalysis sample

Owner:ALTERA CORP

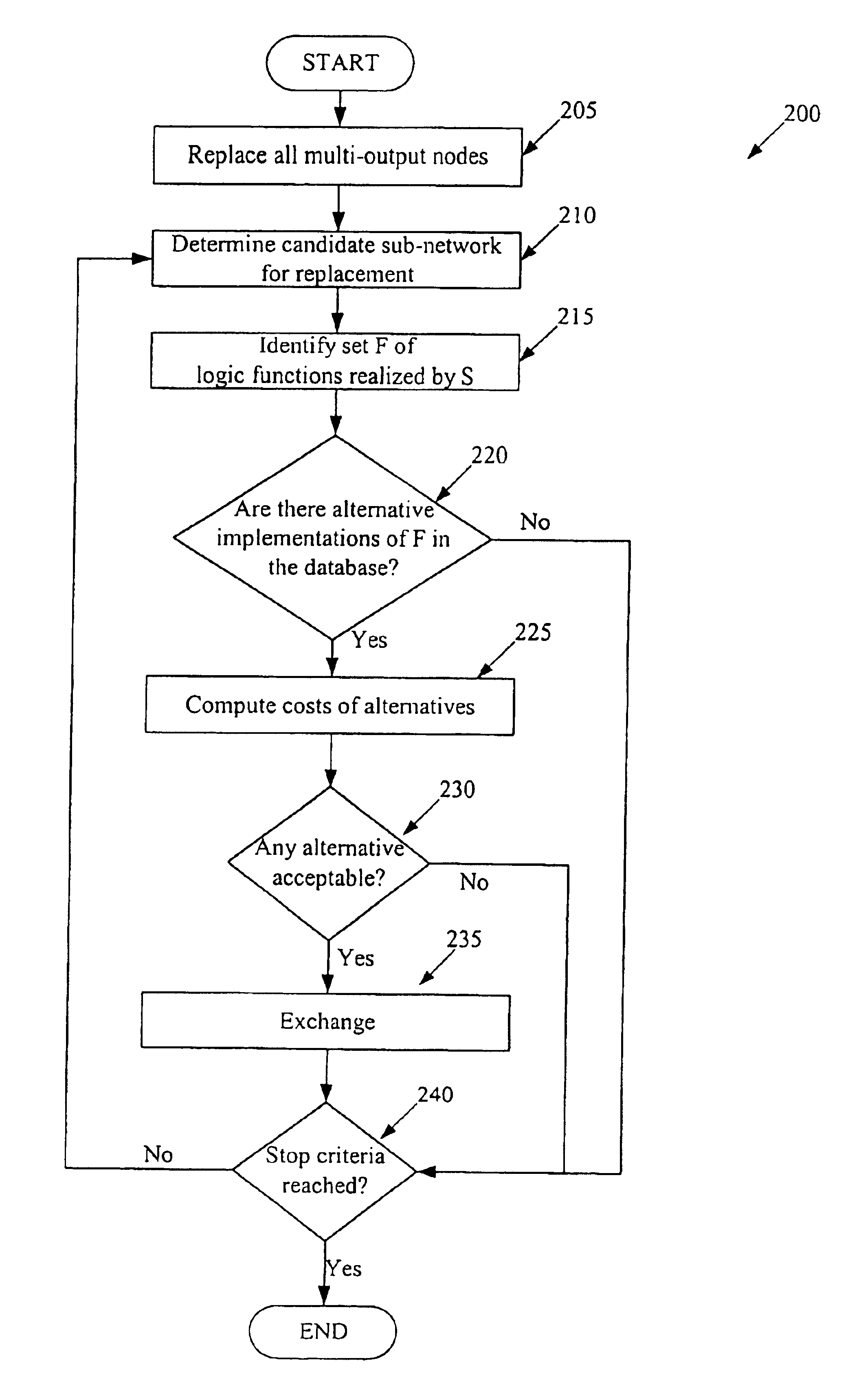

Method and apparatus for performing technology mapping

InactiveUS6854097B2Computer aided designSpecial data processing applicationsStructure recognitionTheoretical computer science

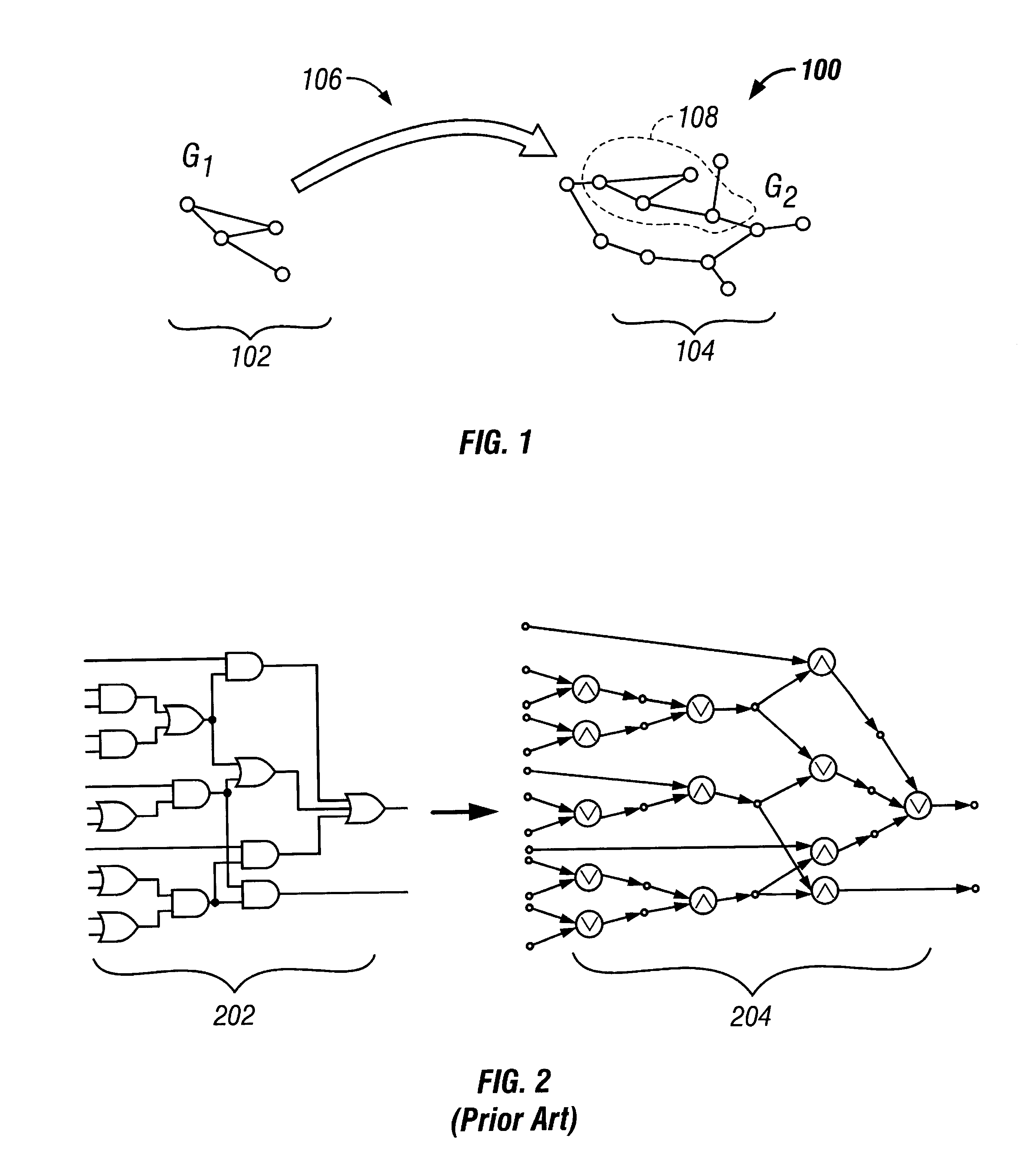

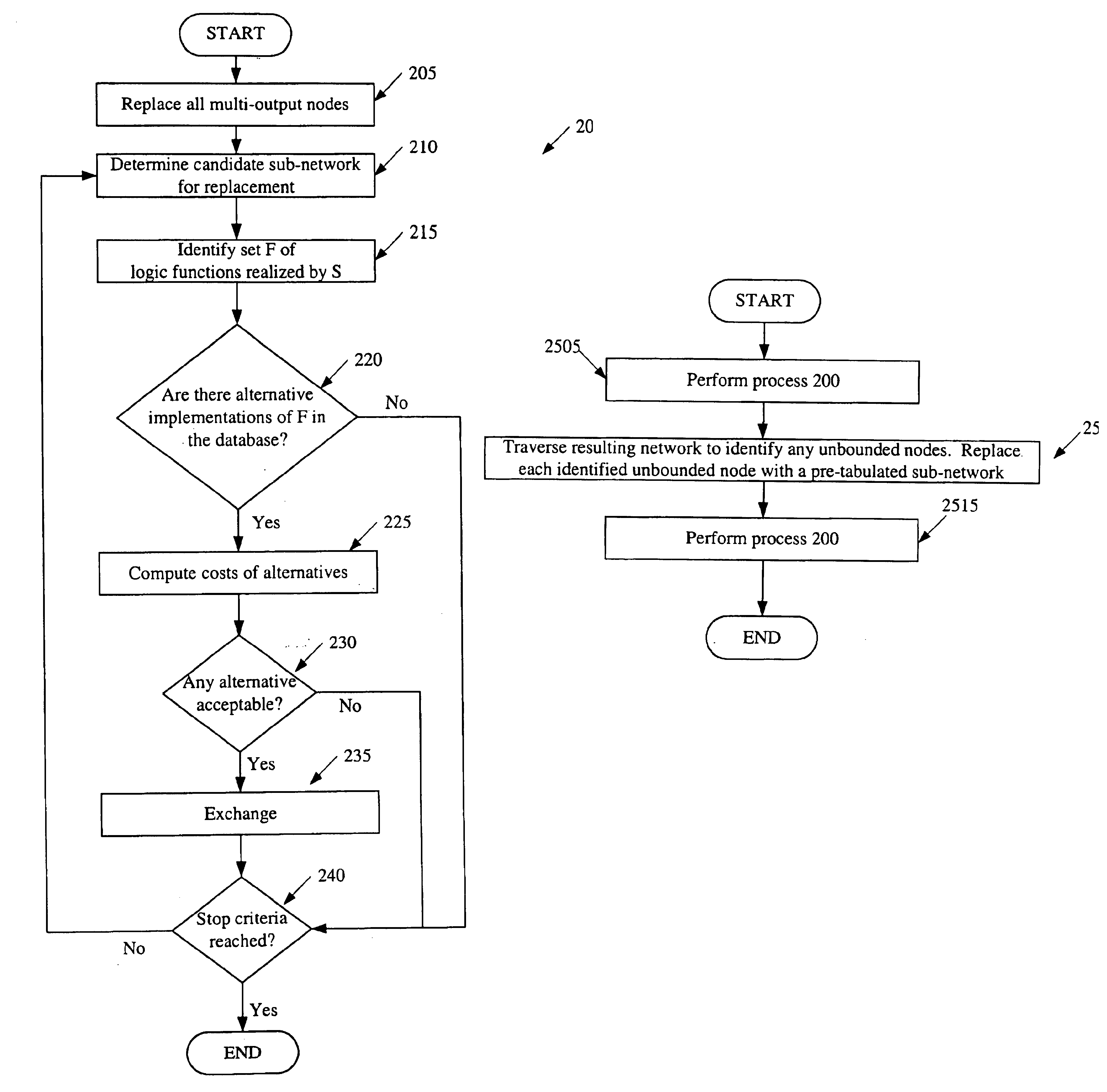

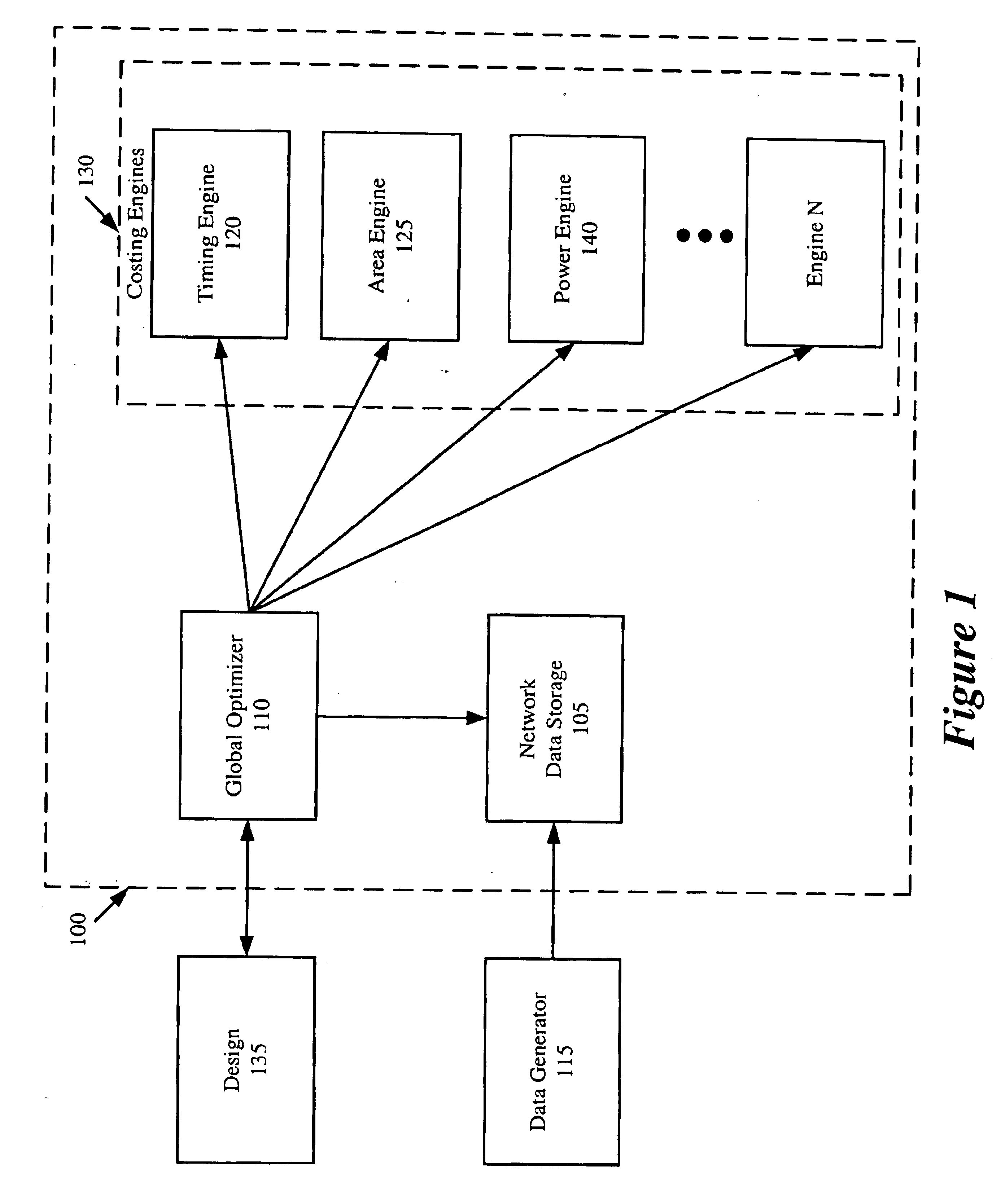

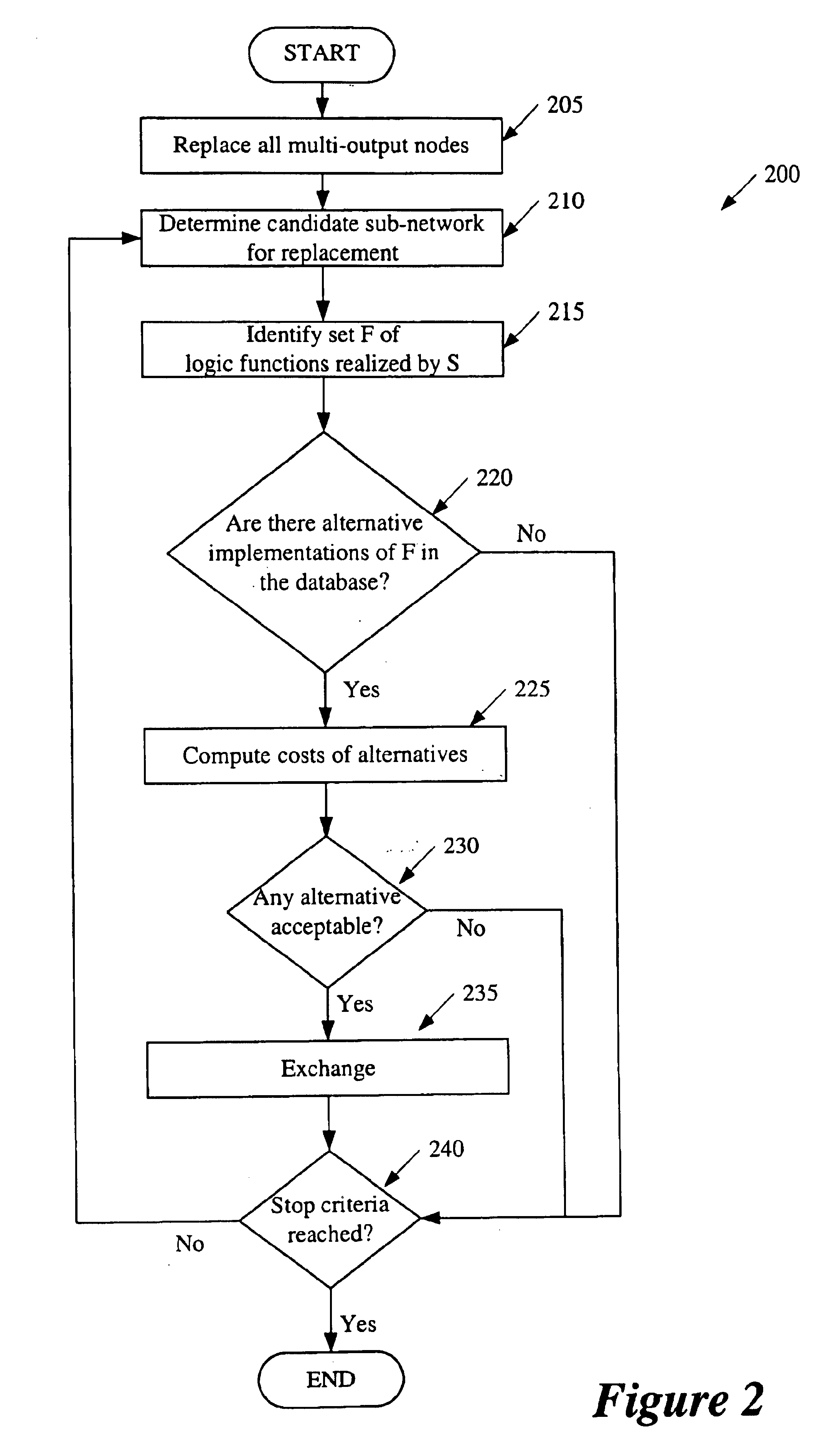

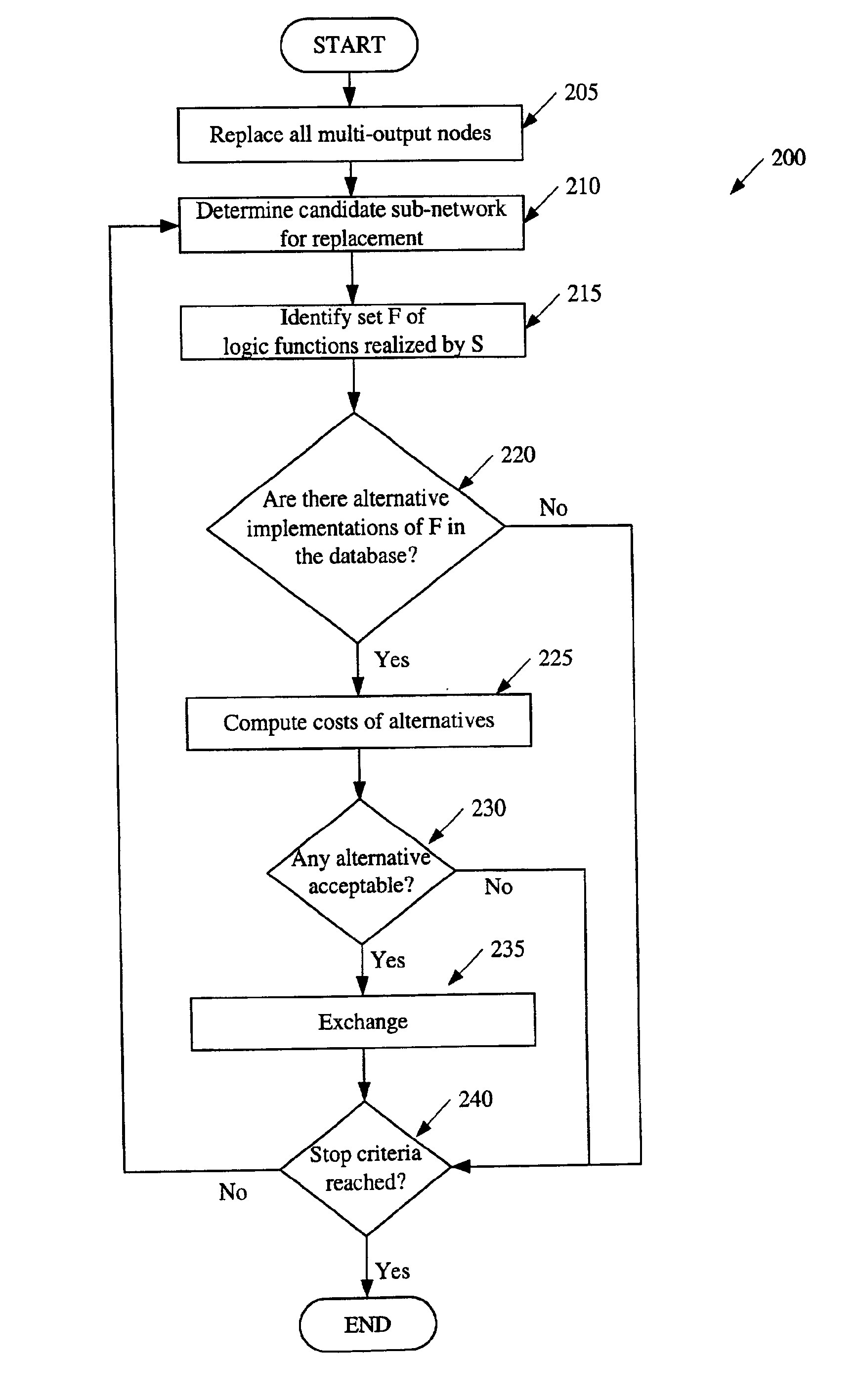

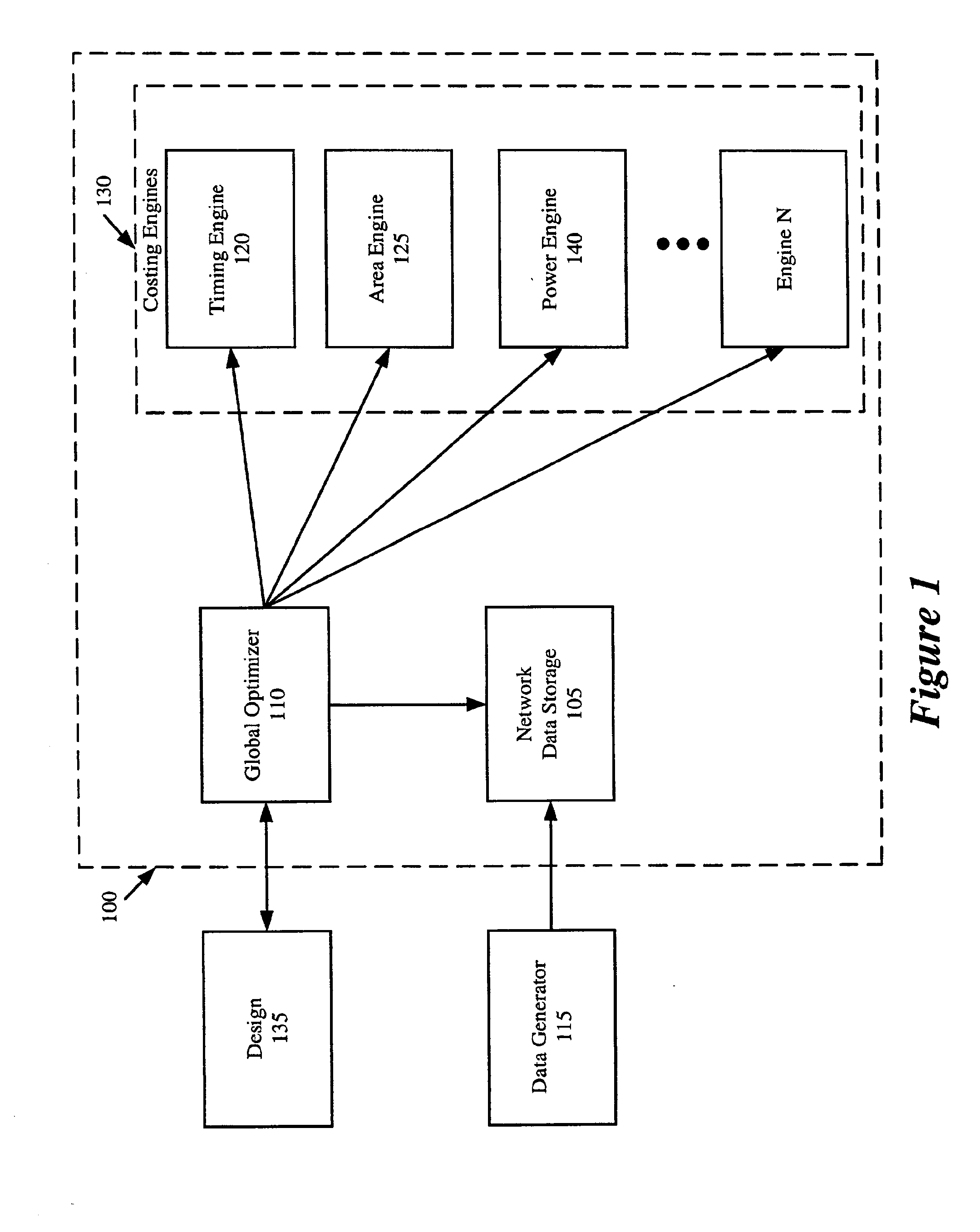

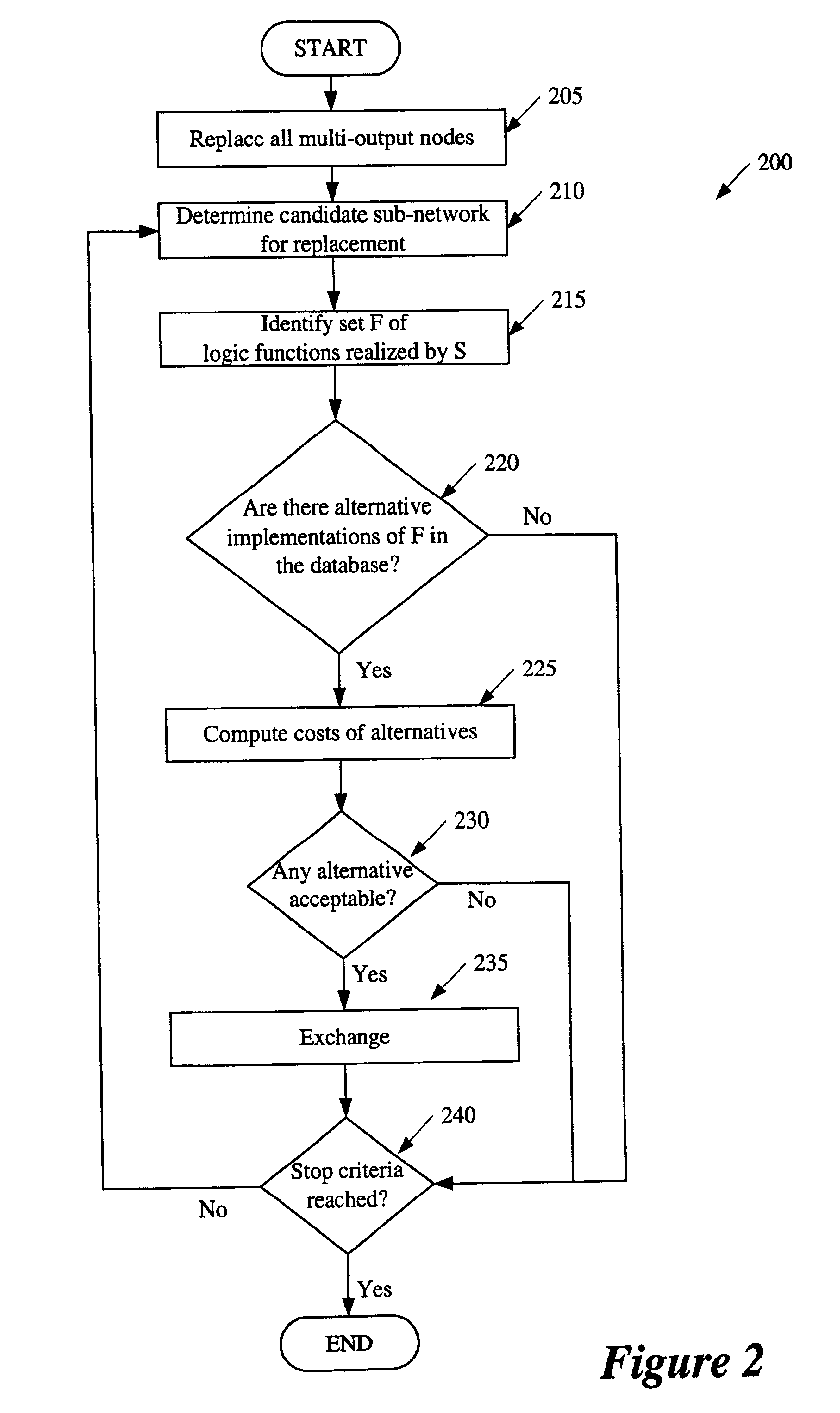

Some embodiments of the invention provide a method for pre-tabulating sub-networks. This method (1) generates a sub-network that performs a function, (2) generates a parameter based on this function, and (3) stores the sub-network in a storage structure based on the generated parameter. In some embodiments, the generated sub-network has several circuit elements. Also, in some embodiments, the generated sub-network performs a set of two or more functions. Some embodiments store each generated sub-network in an encoded manner. Some embodiments provide a method for producing a circuit description of a design. This method (1) selects a candidate sub-network from the design, (2) identifies an output function performed by the sub-network, (3) based on the identified output function, identifies a replacement sub-network from a storage structure that stores replacement sub-networks, and (4) replaces the selected candidate sub-network with the identified replacement sub-network in certain conditions. In some embodiments, this method is performed to map a design to a particular technology library. Some embodiments provide a data storage structure that stores a plurality of sub-networks based on parameters derived from the output functions of the sub-networks.

Owner:CADENCE DESIGN SYST INC

Method and apparatus for performing technology mapping

InactiveUS6848086B2Computer aided designSoftware simulation/interpretation/emulationStructure recognitionTheoretical computer science

Some embodiments of the invention provide a method for pre-tabulating sub-networks. This method (1) generates a sub-network that performs a function, (2) generates a parameter based on this function, and (3) stores the sub-network in a storage structure based on the generated parameter. In some embodiments, the generated sub-network has several circuit elements. Also, in some embodiments, the generated sub-network performs a set of two or more functions. Some embodiments store each generated sub-network in an encoded manner. Some embodiments provide a method for producing a circuit description of a design. This method (1) selects a candidate sub-network from the design, (2) identifies an output function performed by the sub-network, (3) based on the identified output function, identifies a replacement sub-network from a storage structure that stores replacement sub-networks, and (4) replaces the selected candidate sub-network with the identified replacement sub-network in certain conditions. In some embodiments, this method is performed to map a design to a particular technology library. Some embodiments provide a data storage structure that stores a plurality of sub-networks based on parameters derived from the output functions of the sub-networks.

Owner:CADENCE DESIGN SYST INC

Method and apparatus for performing technology mapping

InactiveUS6990650B2Program controlComputer aided designStructure recognitionTheoretical computer science

Some embodiments of the invention provide a method for pre-tabulating sub-networks. This method (1) generates a sub-network that performs a function, (2) generates a parameter based on this function, and (3) stores the sub-network in a storage structure based on the generated parameter. In some embodiments, the generated sub-network has several circuit elements. Also, in some embodiments, the generated sub-network performs a set of two or more functions. Some embodiments store each generated sub-network in an encoded manner. Some embodiments provide a method for producing a circuit description of a design. This method (1) selects a candidate sub-network from the design, (2) identifies an output function performed by the sub-network, (3) based on the identified output function, identifies a replacement sub-network from a storage structure that stores replacement sub-networks, and (4) replaces the selected candidate sub-network with the identified replacement sub-network in certain conditions. In some embodiments, this method is performed to map a design to a particular technology library. Some embodiments provide a data storage structure that stores a plurality of sub-networks based on parameters derived from the output functions of the sub-networks.

Owner:CADENCE DESIGN SYST INC

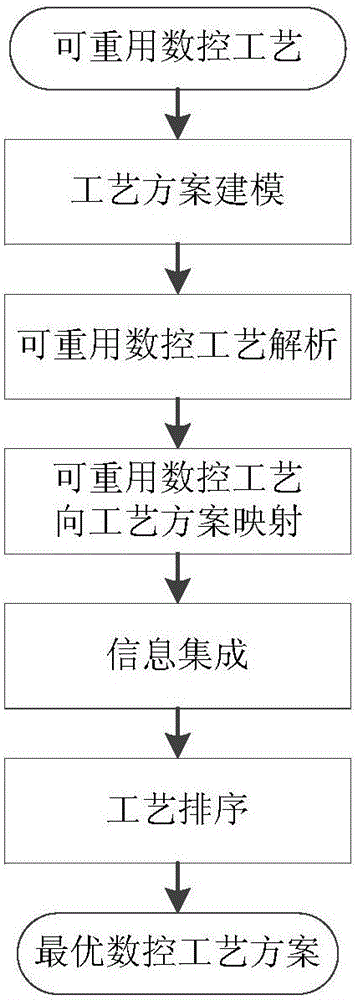

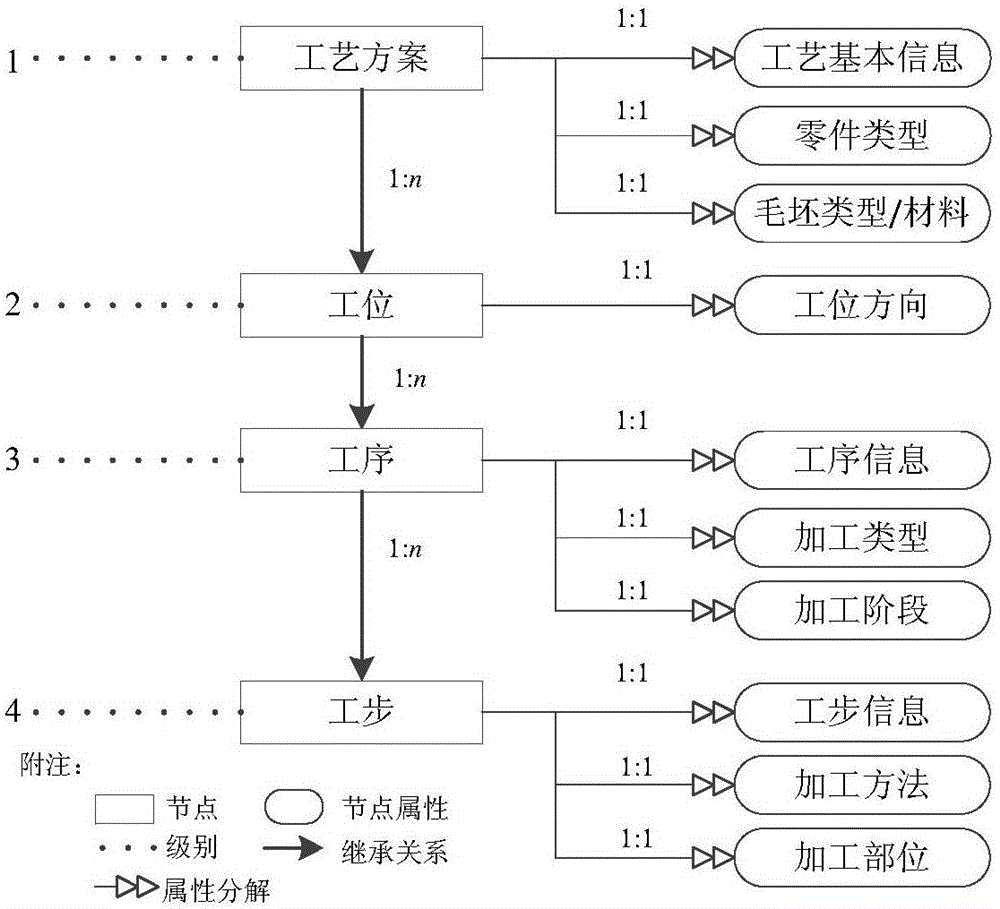

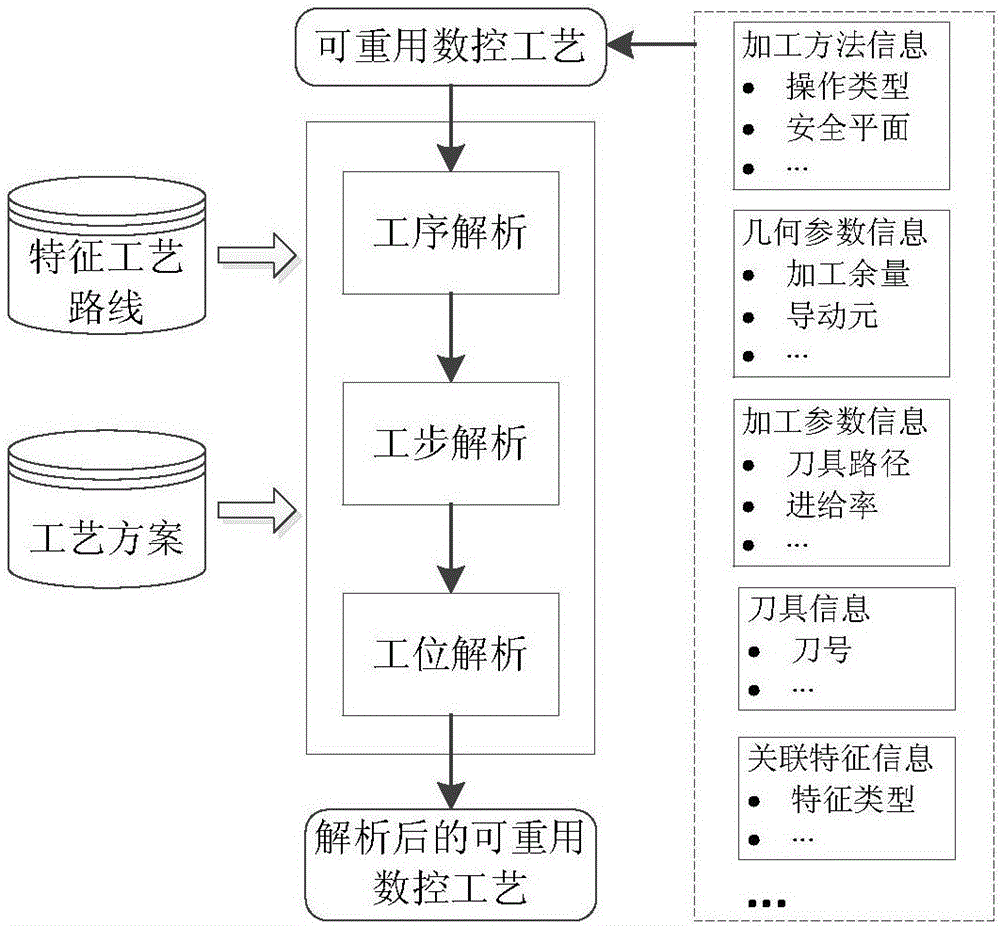

Reusable numerical control technology mapping method for technology scheme

ActiveCN106843153AImprove practicalityQuick editProgramme controlComputer controlStructured modelNumerical control

Owner:NORTHWESTERN POLYTECHNICAL UNIV

Temperature-compensated reference voltage system with very low power consumption based on an SCM structure with transistors of different threshold voltages

ActiveUS9383760B2Reduce power consumptionImprove accuracyElectric variable regulationCMOSEngineering

A simple SCM (Self Cascode MOSFET) structure to generate a sub-1V reference voltage in the SCM intermediate node. The structure requires only 2 transistors to create a temperature-compensated reference voltage. When sized correctly, the transistors in the SCM will operate both at weak, moderate or strong inversion, and in the saturation region or saturation and triode regions, providing good correspondence and low part to part variation. The following proposal innovates by operating with supply voltages on a broad variation range, from 3.6V through below 1V (sub-1V operation), with bias currents in the range of tens of nA (nano Amperes) and temperature variation smaller than ±1% from −40° C. through 85° C. This is an extremely low cost implementation (in terms of area and complexity), compatible with standard CMOS manufacturing processes, and very robust (in terms of fab-to-fab transference, technology mapping, and also well controlled part-to-part variation).

Owner:CENT NACIONAL DE TECHA ELECTRONICSA AVANCADA

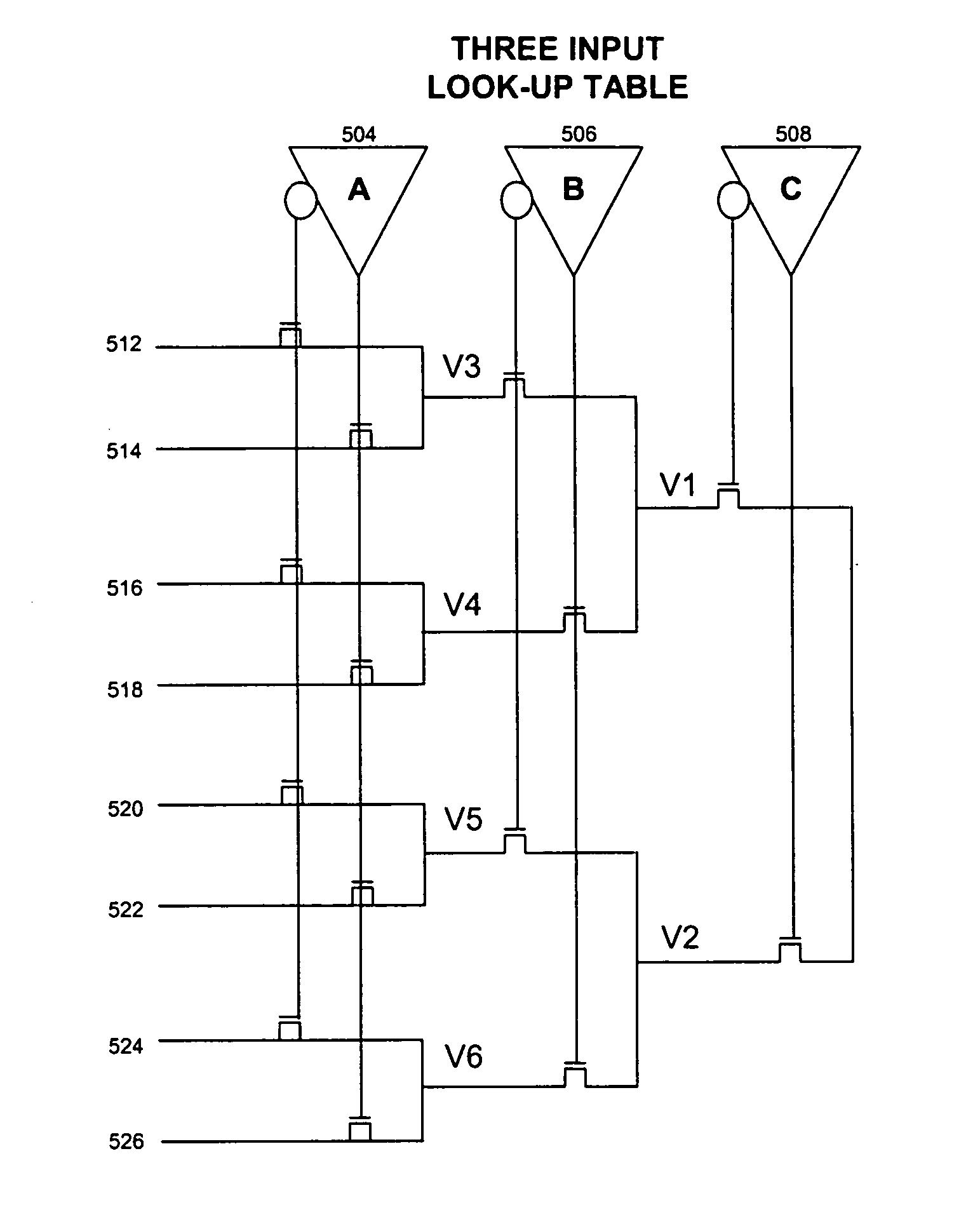

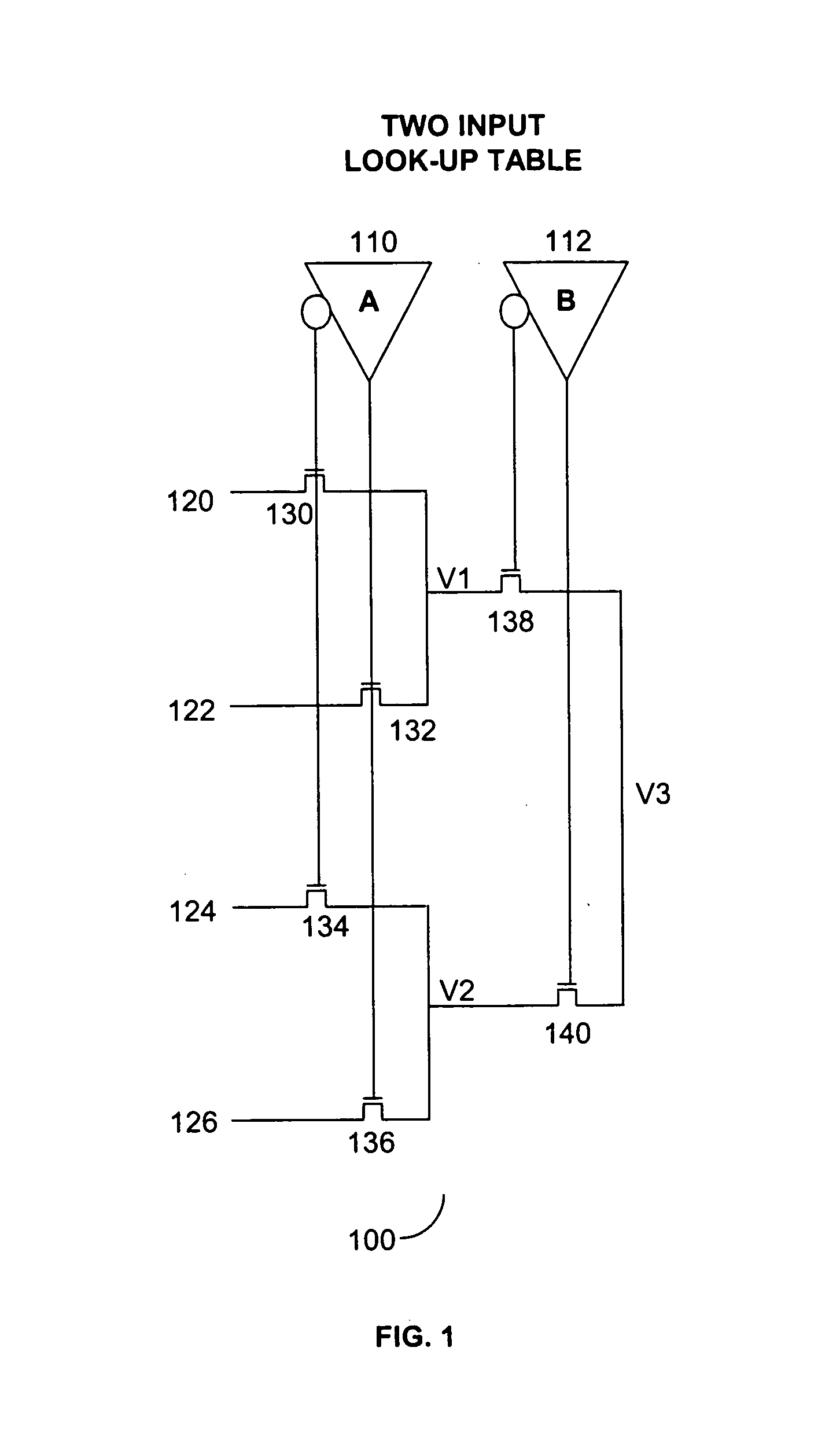

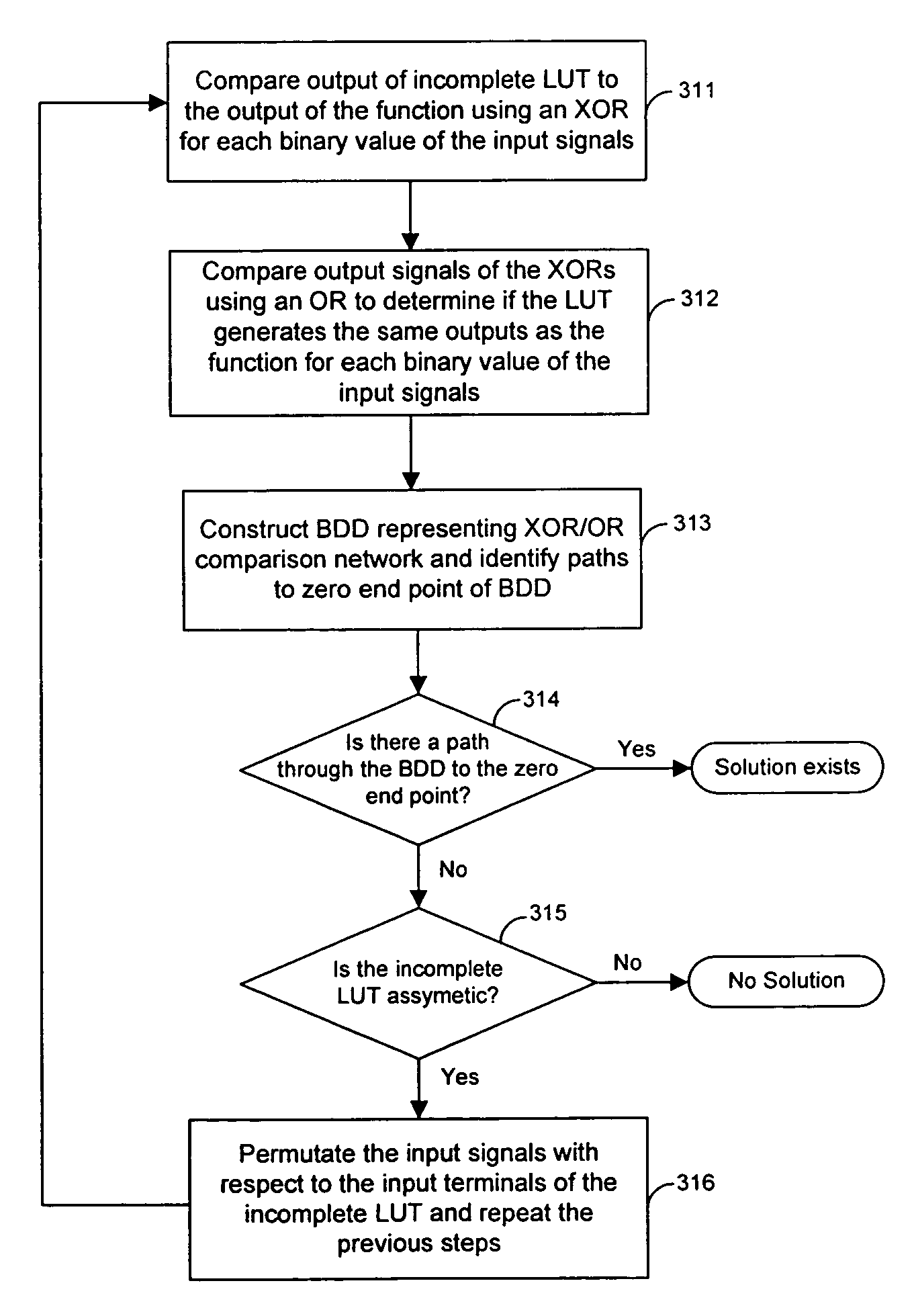

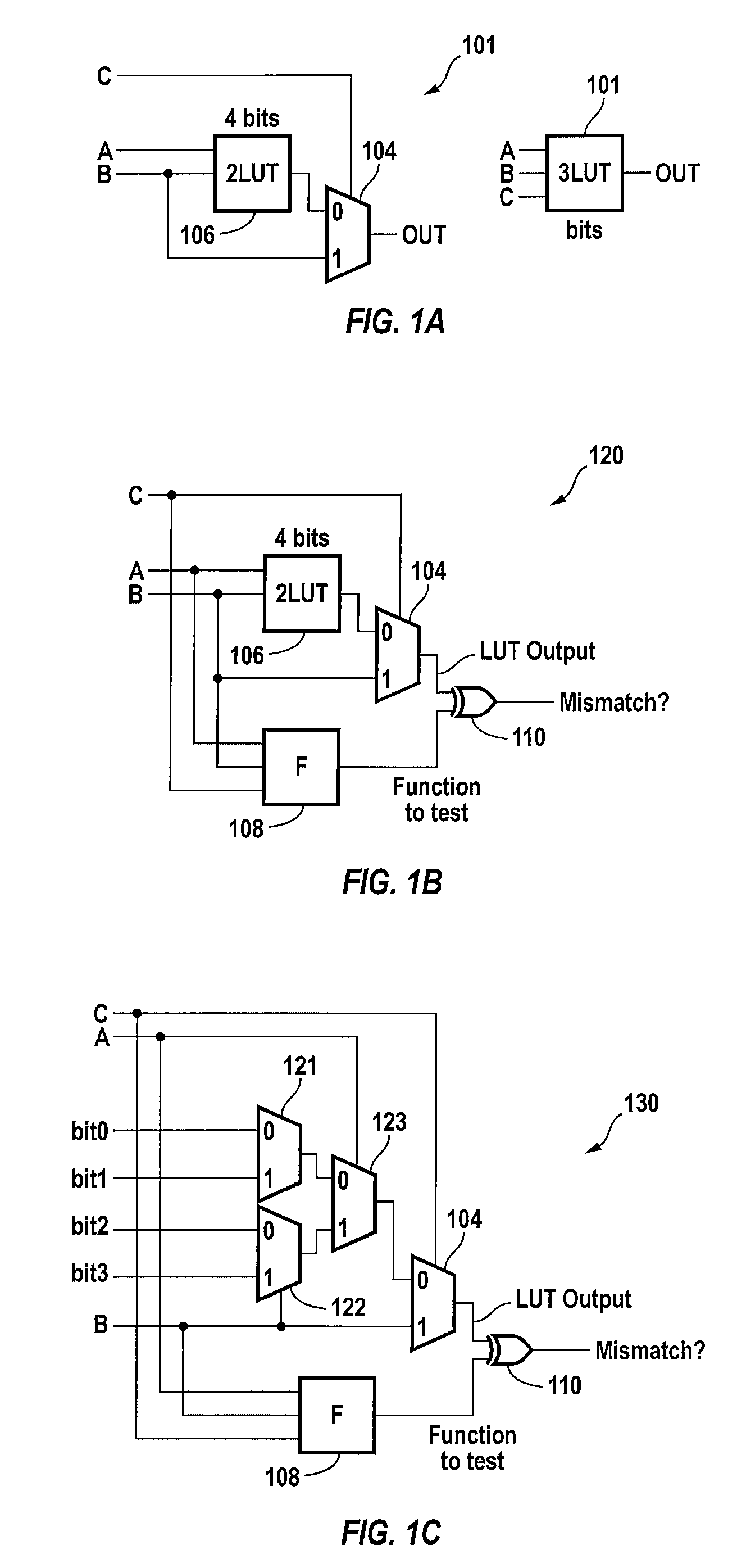

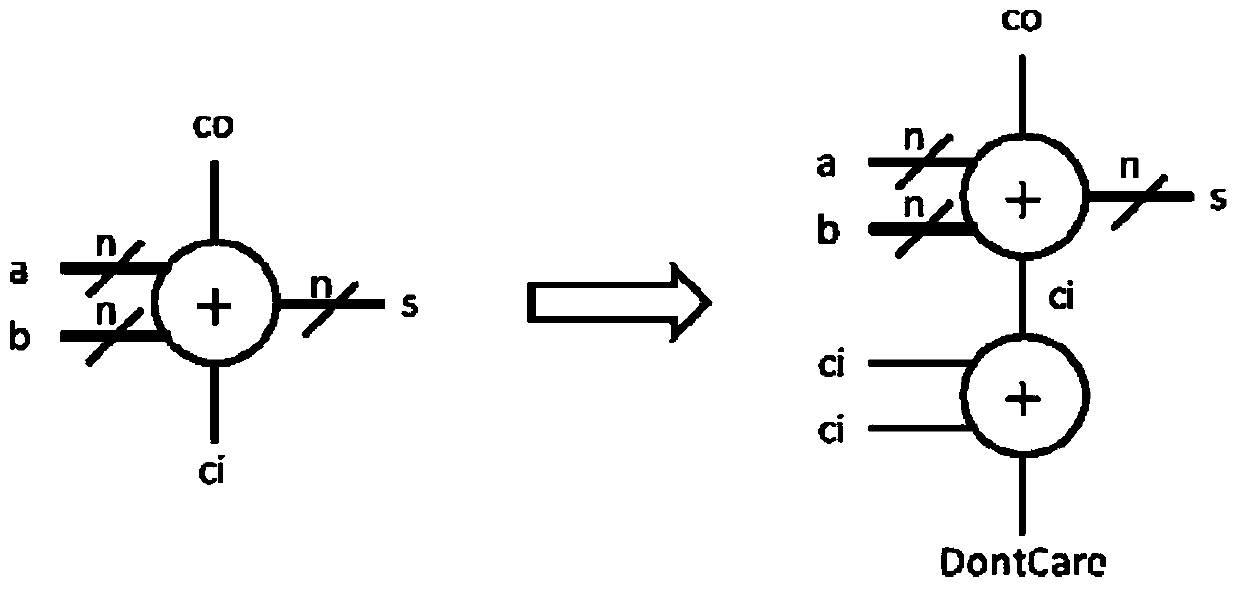

Technology mapping techniques for incomplete lookup tables

Technology mapping techniques for determining whether a function can be implemented using an incomplete lookup table (LUT) are provided. For example, the output of a function is compared to the output of an incomplete LUT for each binary value of the function's input signals and for each binary value of the bits stored in the incomplete LUT. For a LUT that is functionally asymmetric, the process can be repeated for multiple permutations of the input signals with respect to the input terminals of the LUT. As another example, the user function is converted into a network of multiplexers and complete LUTs, which are analyzed to determine if an incomplete LUT can implement the function. As another example, a truth table is constructed for a function. The truth table variables are then tested one by one as candidates for each input position using co-factoring and dependency checking.

Owner:ALTERA CORP

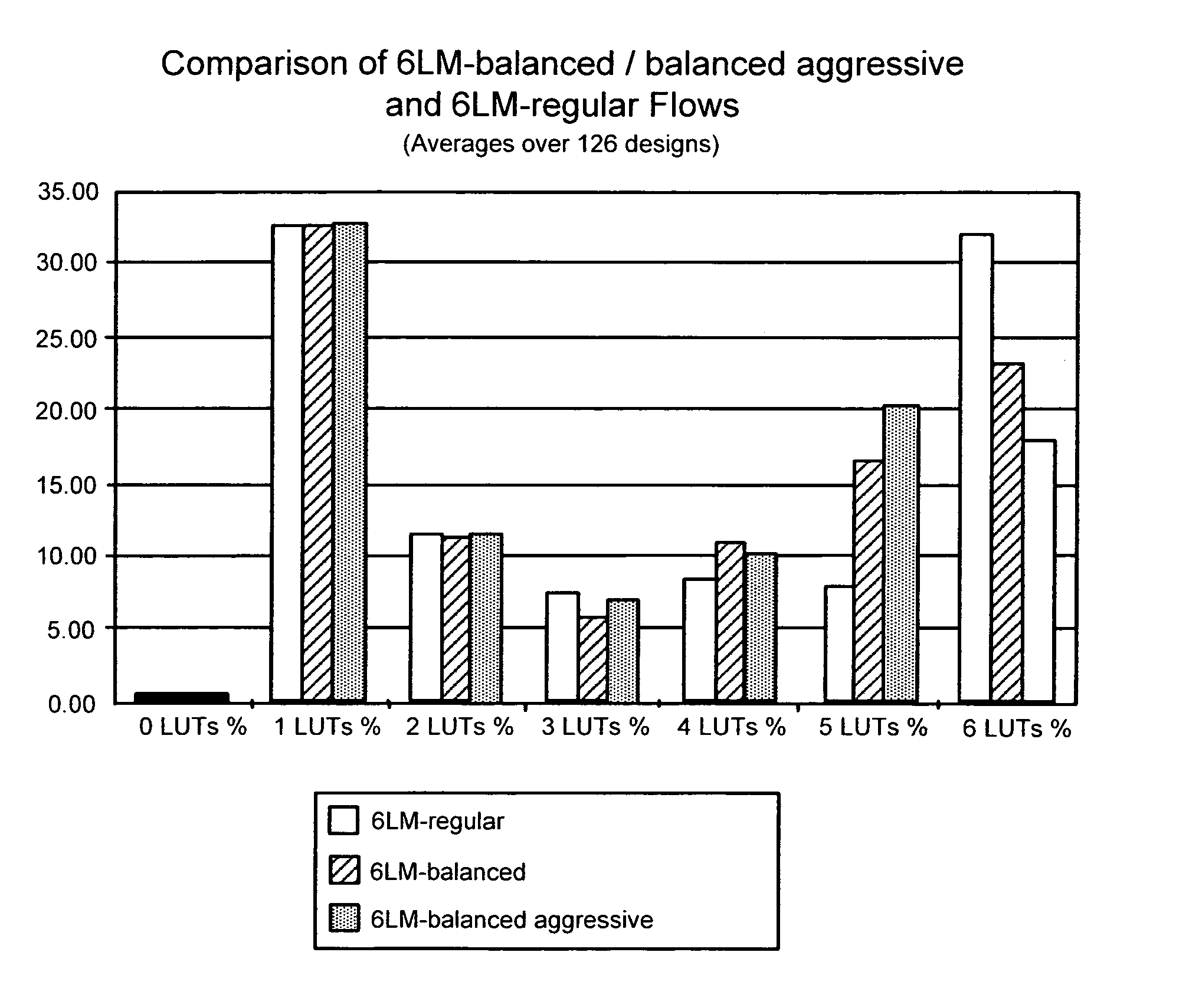

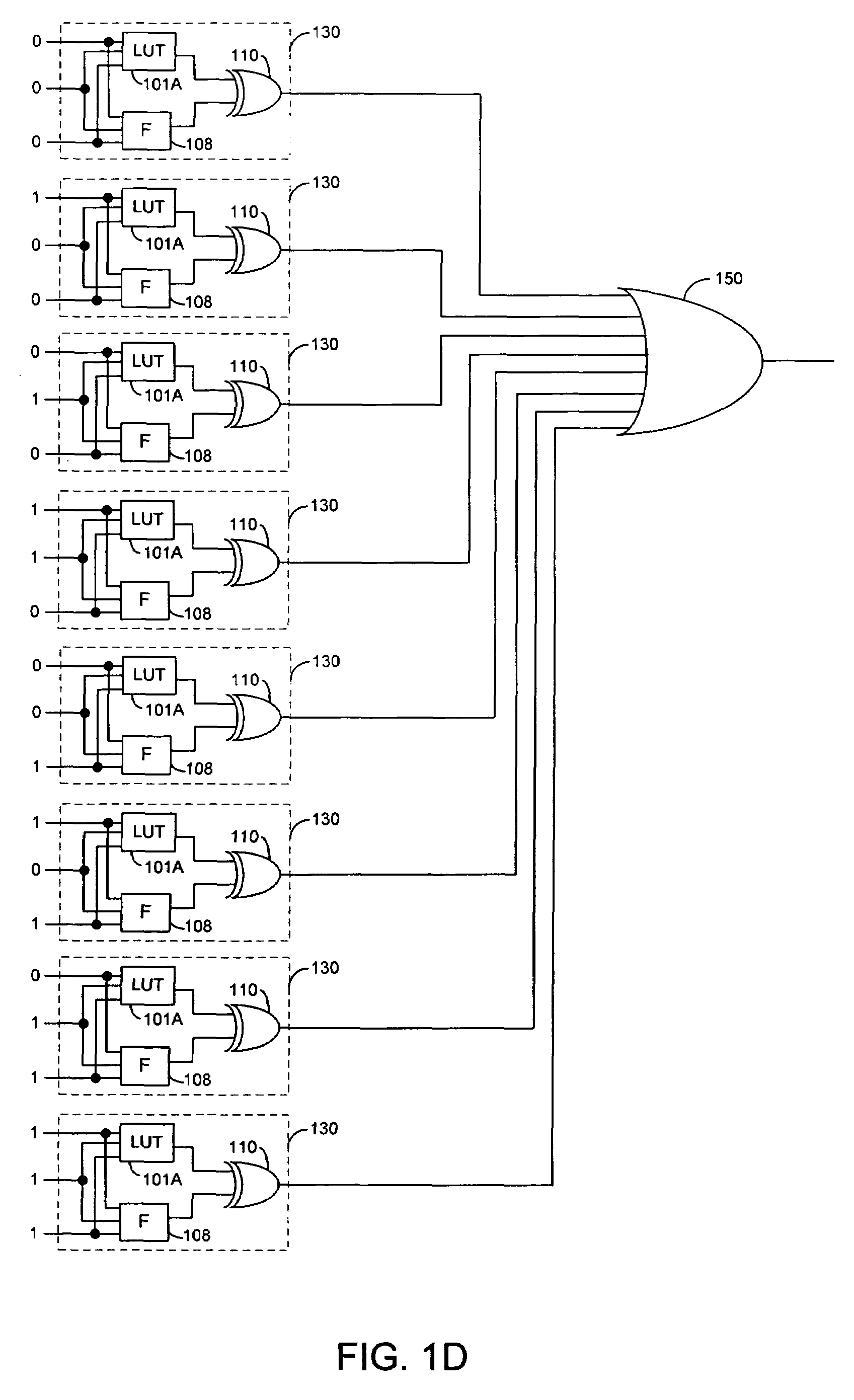

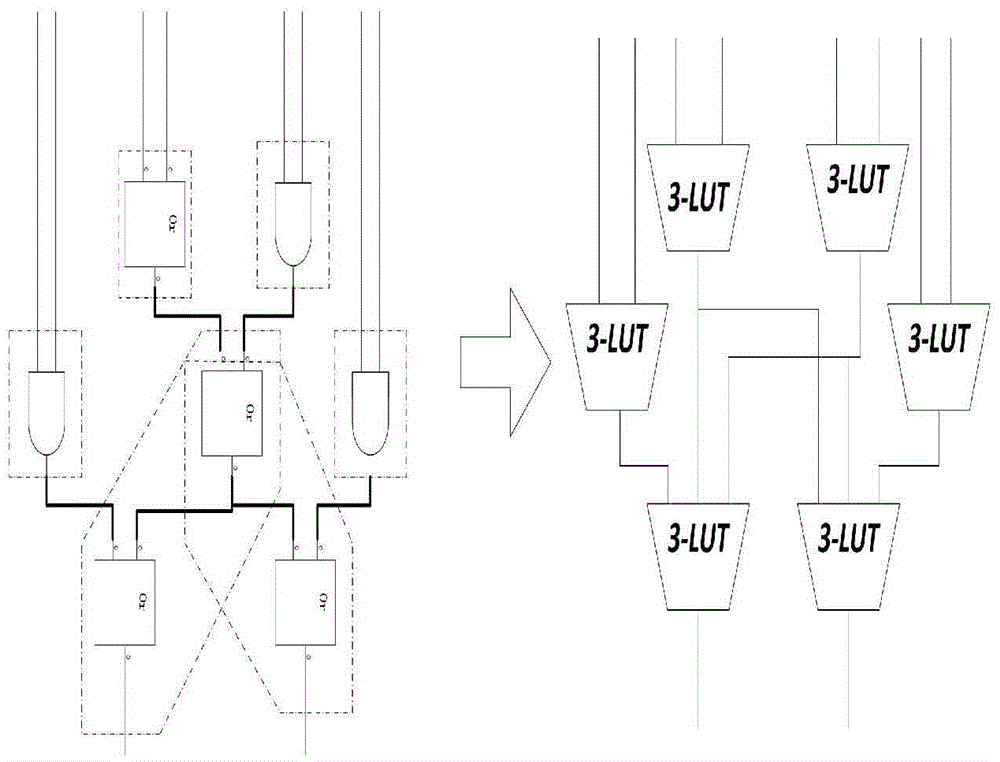

Efficient FPGA technology mapping algorithm

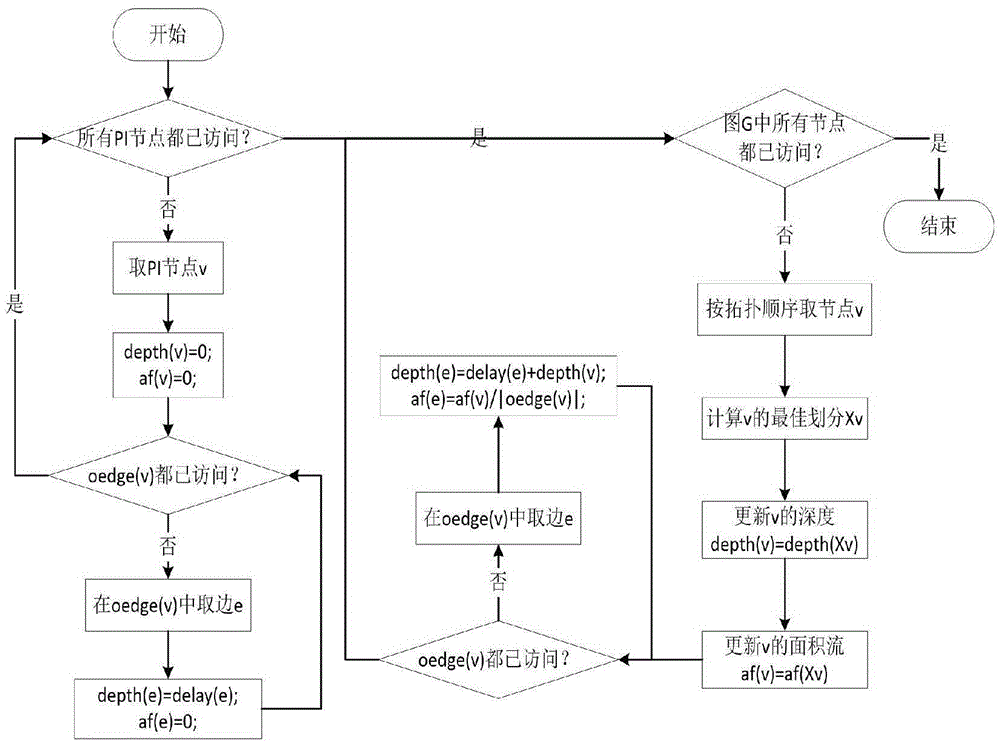

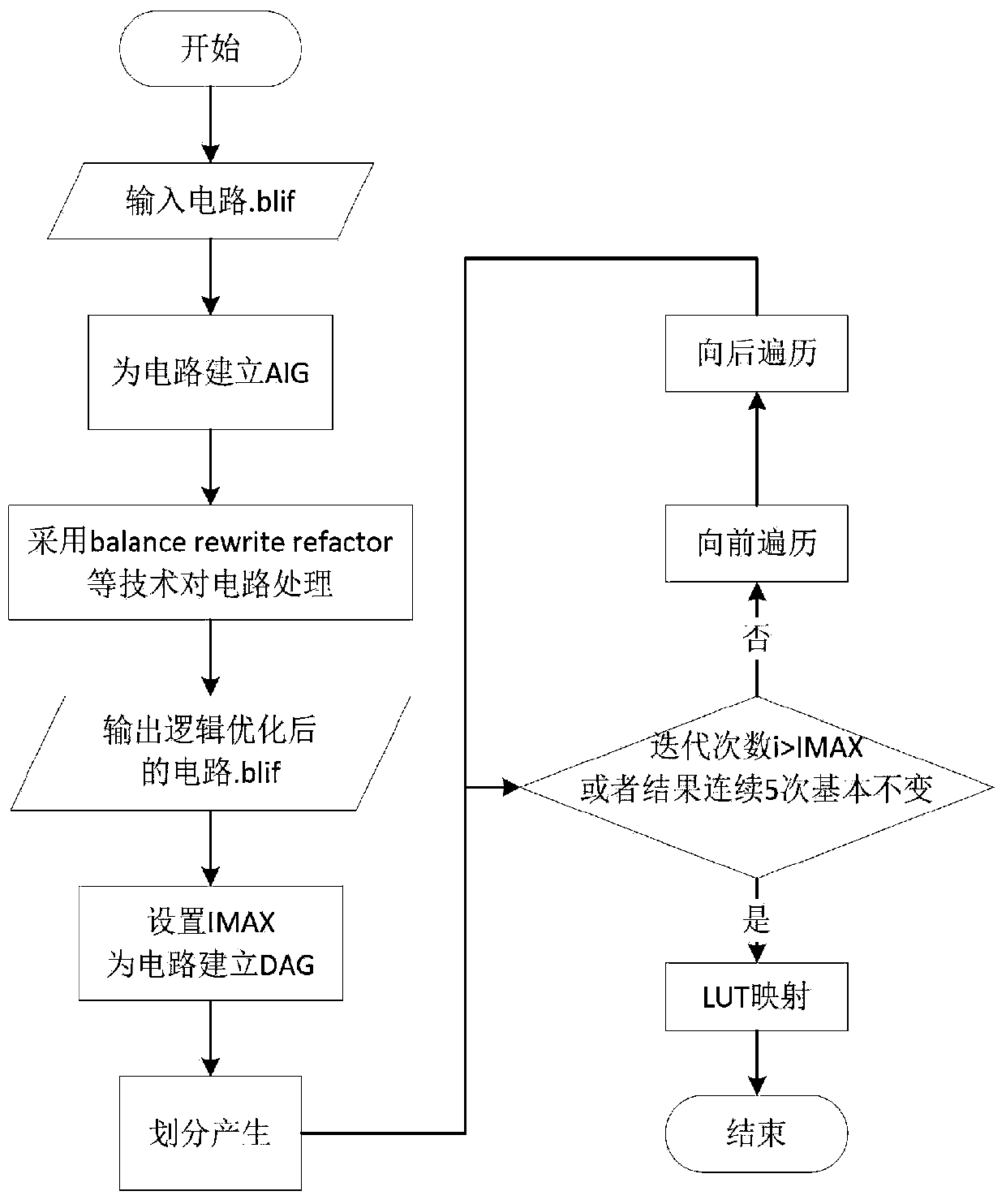

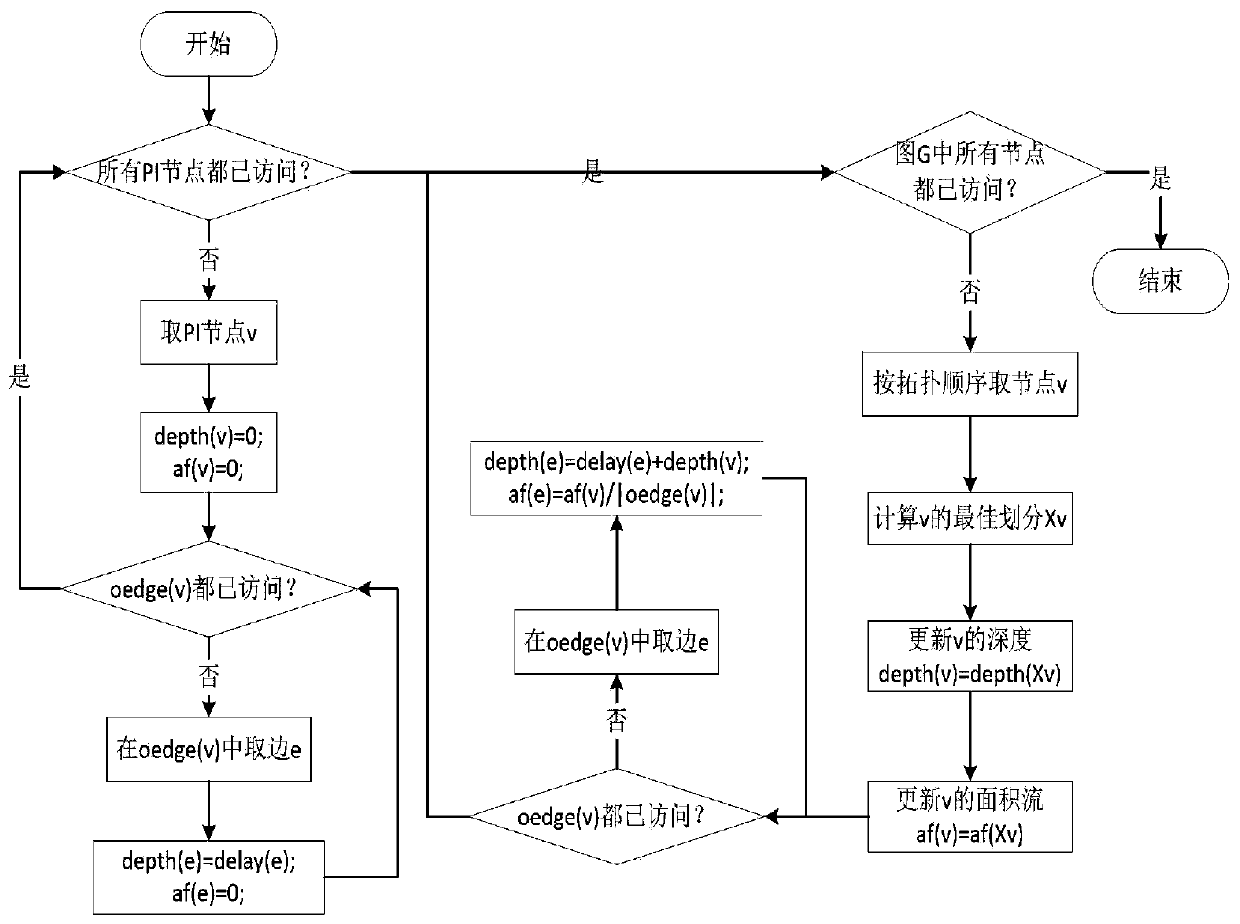

ActiveCN105488285AOptimizing the Efficiency of MappingReduce iterative processSpecial data processing applicationsDynamic planningLogic optimization

The invention discloses an efficient FPGA technology mapping algorithm. Technical mapping is divided into logic optimization and structural optimization. The logic optimization part adopts an AIG model and technologies of balance, rewrite, refactor and the like to optimize a circuit. The structural optimization part adopts a DAG model and comprises three steps of partition generation, partition selection and LUT mapping. For the partition generation, a dynamic planning thought is adopted for quickly generating all k- feasible partitions for each node. For the partition selection, a partition set with a characteristic that a time delay and an area are optimized at the same time is finally selected through multi-time forward traversal and backward traversal iteration based on an iterative heuristic thought with an adaptively changeable iterative frequency. Meanwhile, a node area stream calculation formula is corrected and the randomness of the partition selection is improved. Through the LUT mapping, partition combination generated by the partition selection is mapped into an LUT network.

Owner:XIDIAN UNIV

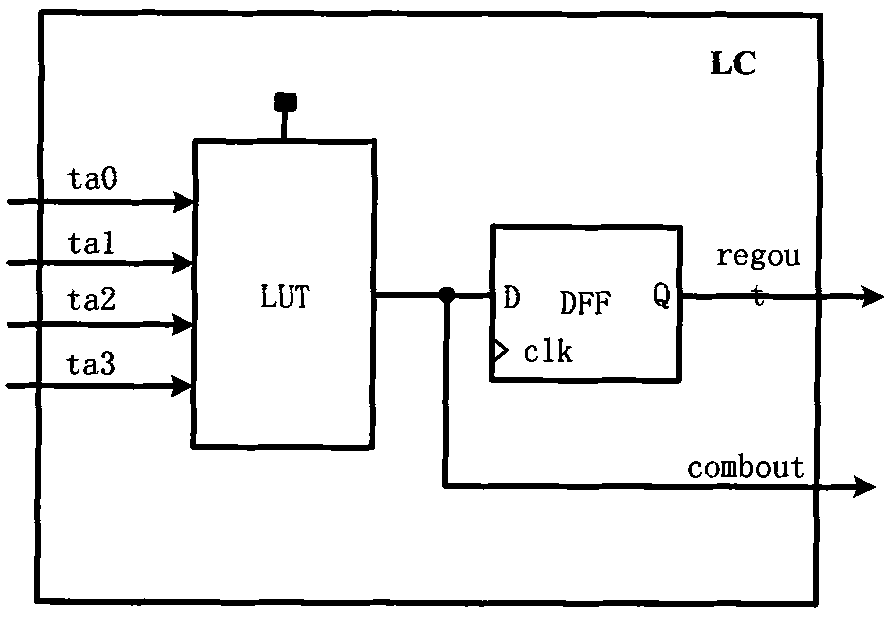

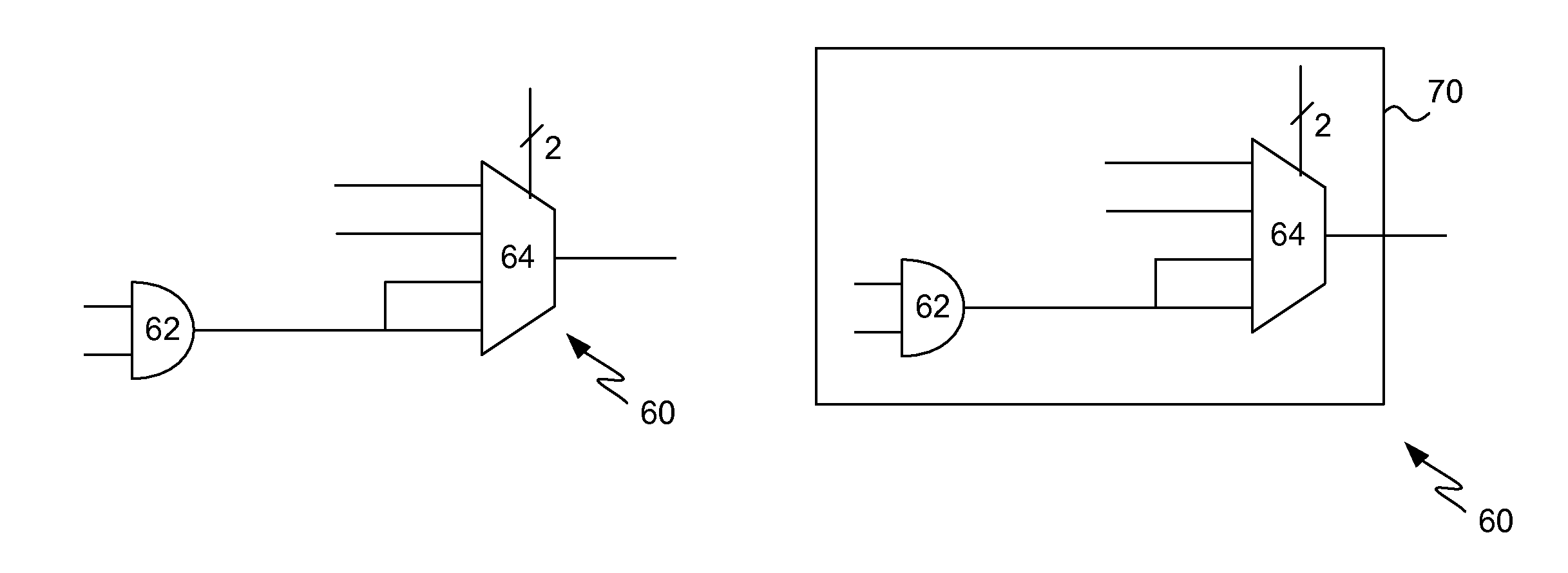

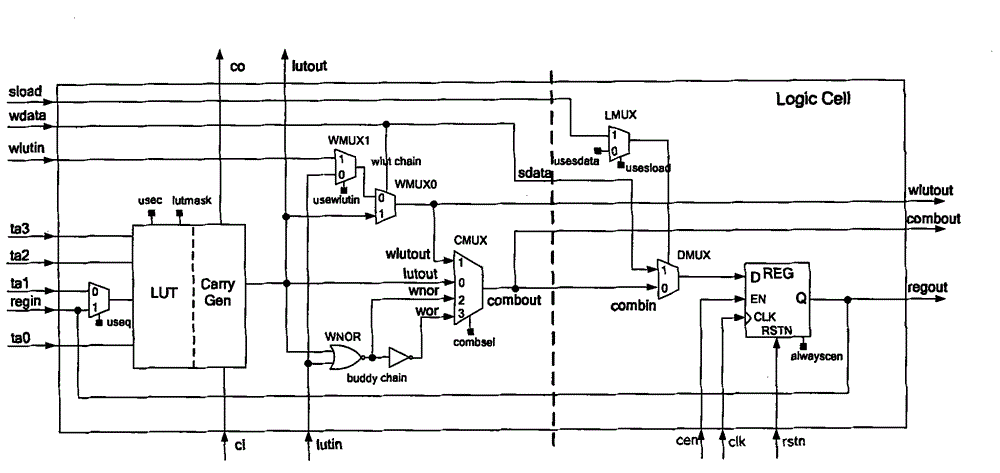

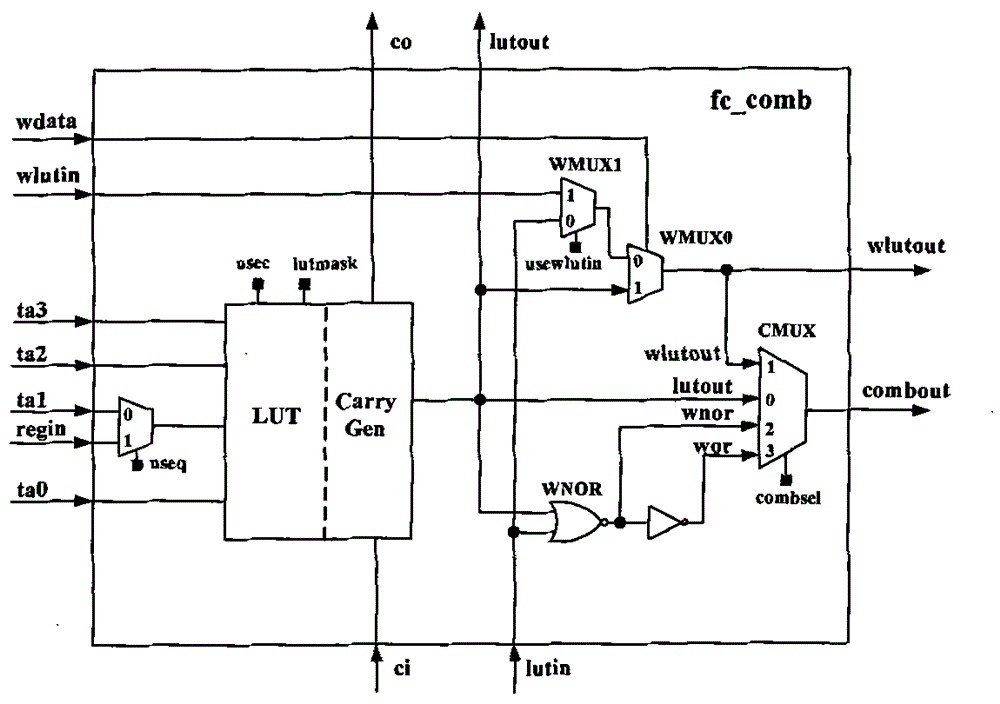

Technology mapping method for integrated circuits for improved logic cells

InactiveCN102375905AImprove performanceSimple designSpecial data processing applicationsComputer architectureLogic cell

The invention relates to a technology mapping method for integrated circuits for improved logic cells, which comprises the following steps of: firstly, decomposing a universal combinational logic circuit into circuits consisting of input logic cells 2; then, taking the input logic cell 2 as a node, partitioning the node based on an improved logic cell, and finding out all partitions of the node; taking a partition corresponding to the maximum ratio of the number of nodes covered by each partition PGCN(Propagate Gate Cover Number) to the number of actually-used improved logic cells PRUN(Propagate Resource Usage Number) as the optimal partition; and finally, converting the optimal partition into a corresponding improved logic cell. By using the method provided by the invention, through fully using the structural advantages of the improved logic cells, an improved circuit is more efficient on area and time. The method provided by the invention can be widely applied to technology mapping of integrated circuits.

Owner:AGATE LOGIC BEIJING

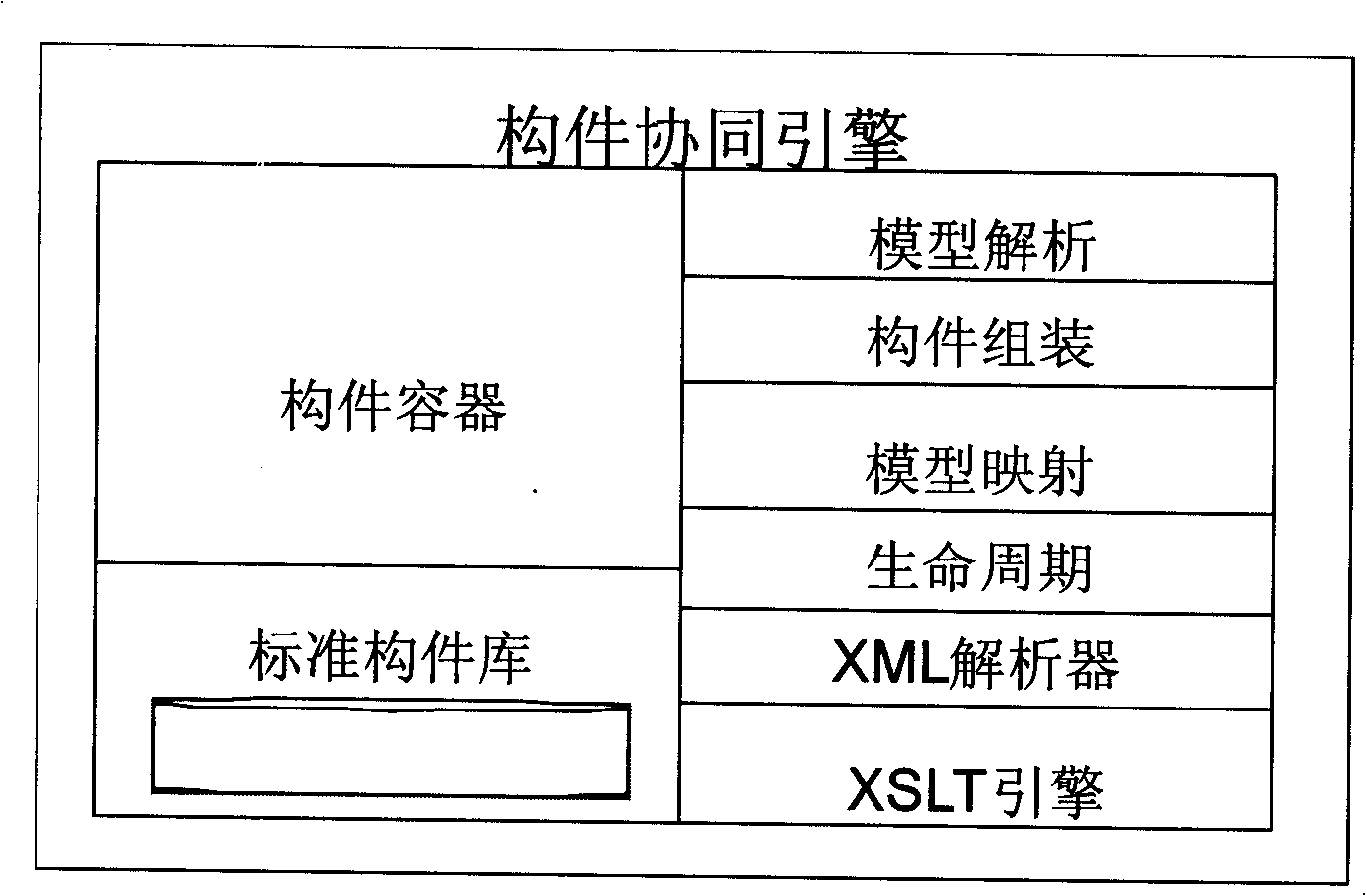

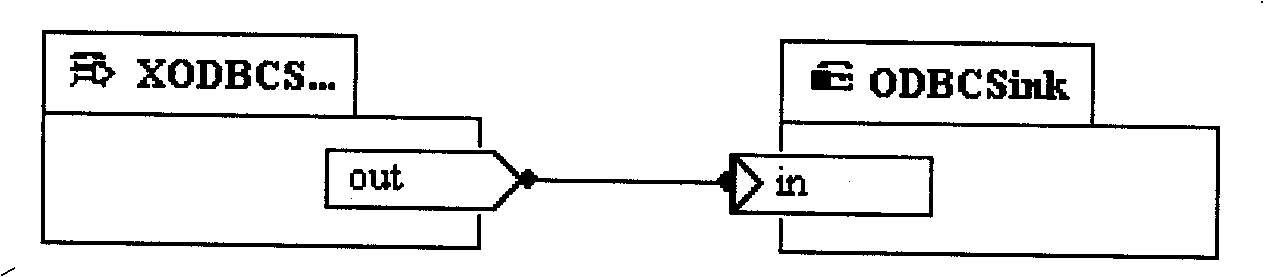

Component synergism engine

InactiveCN101256485AAchieve zero programmingSimplify the difficulty of application integrationSpecific program execution arrangementsIntegratorXSLT

The invention relates to the field of component dynamic loading, component corporative work and component running management filed, specifically to a component corporative engine. The component corporative engine comprises a model parser, a component fittingshop, a model mapping, life cycle management, a XML parser, a XSLT engine, a component container and a component library. The invention has the advantages that because of the automatic technology mapping ability of the component corporative engine, designers can design architecture level application integration by directly using a visual integrator, focuses on business level modeling, in no need of putting energy into technological implementation, therefore the difficulty of application integration is greatly simplified.

Owner:SHANDONG CVIC SOFTWARE ENG

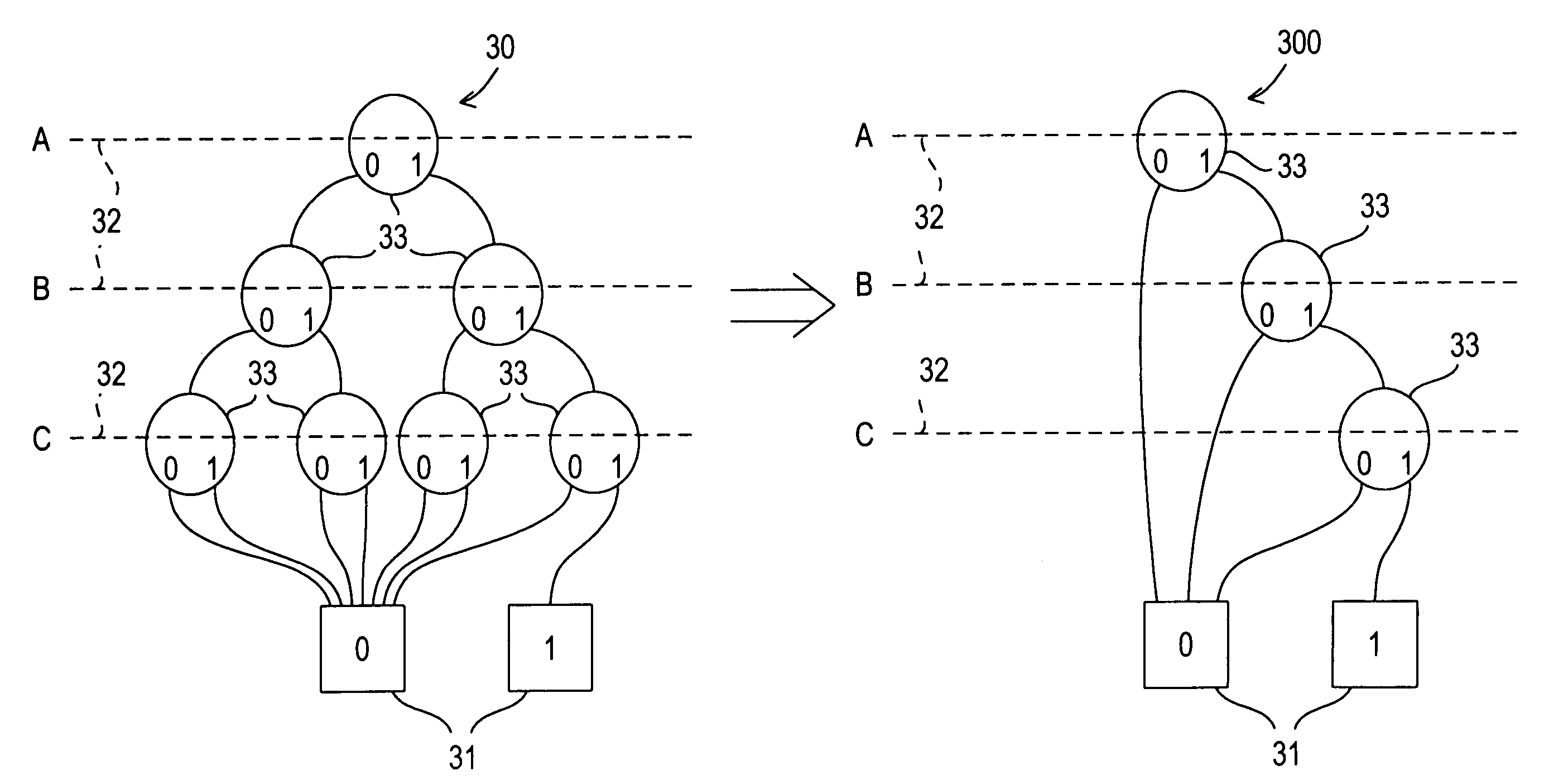

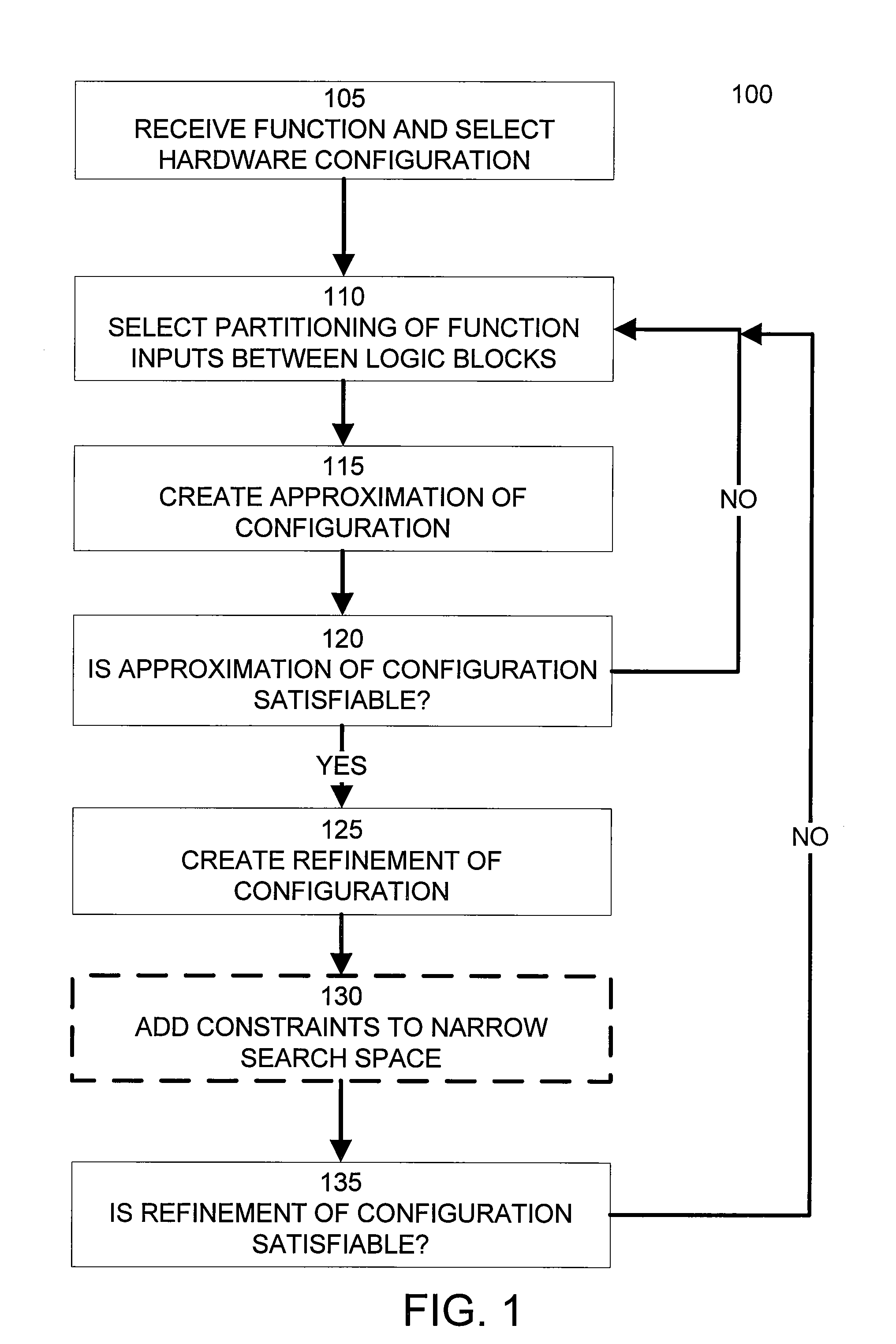

Technology mapping for programming and design of a programmable logic device by equating logic expressions

InactiveUS7360196B1More efficientReduce decreaseCAD circuit designSoftware simulation/interpretation/emulationBinary decision diagramProgrammable logic device

A programmable logic device (“PLD”) architecture and a user logic design are modeled logically to find an efficient programming solution for the user logic design on the PLD architecture. The logical models are converted to equations—e.g., by representing them as binary decision diagrams which can be modeled and manipulated mathematically with commercially available tools. The equations can be solved for the programming or configuration variables. Similarly, an efficient programmable logic device architecture for implementing one or more of a given set of logic functions can be found by mapping each function in the set of functions onto a generic architecture and solving for the configuration variables. By comparing the results for all functions, one can reduce the generic architecture to an efficient architecture for that set of functions by eliminating structures from the generic architecture whose configuration bits are the same for all solutions.

Owner:ALTERA CORP

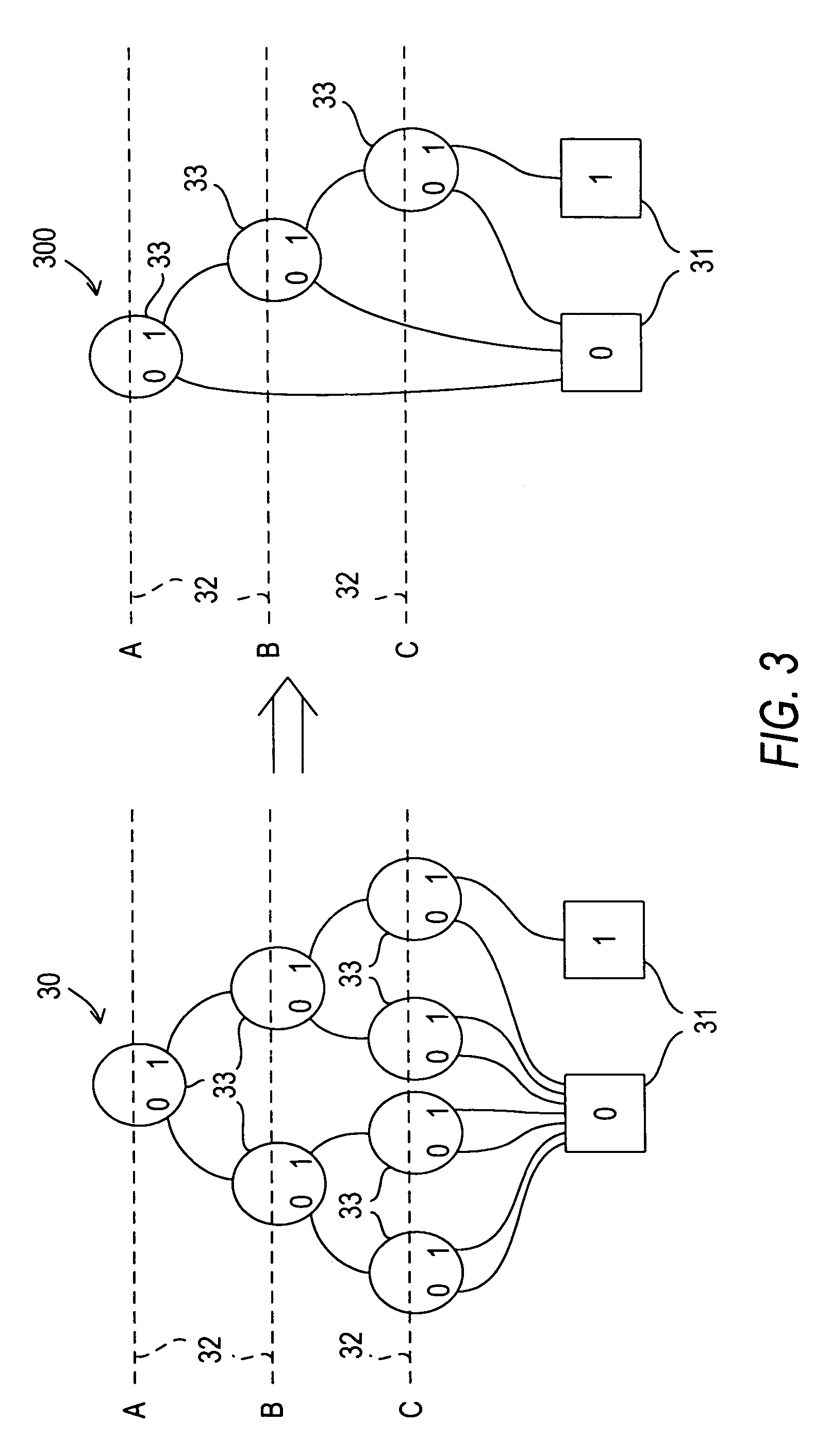

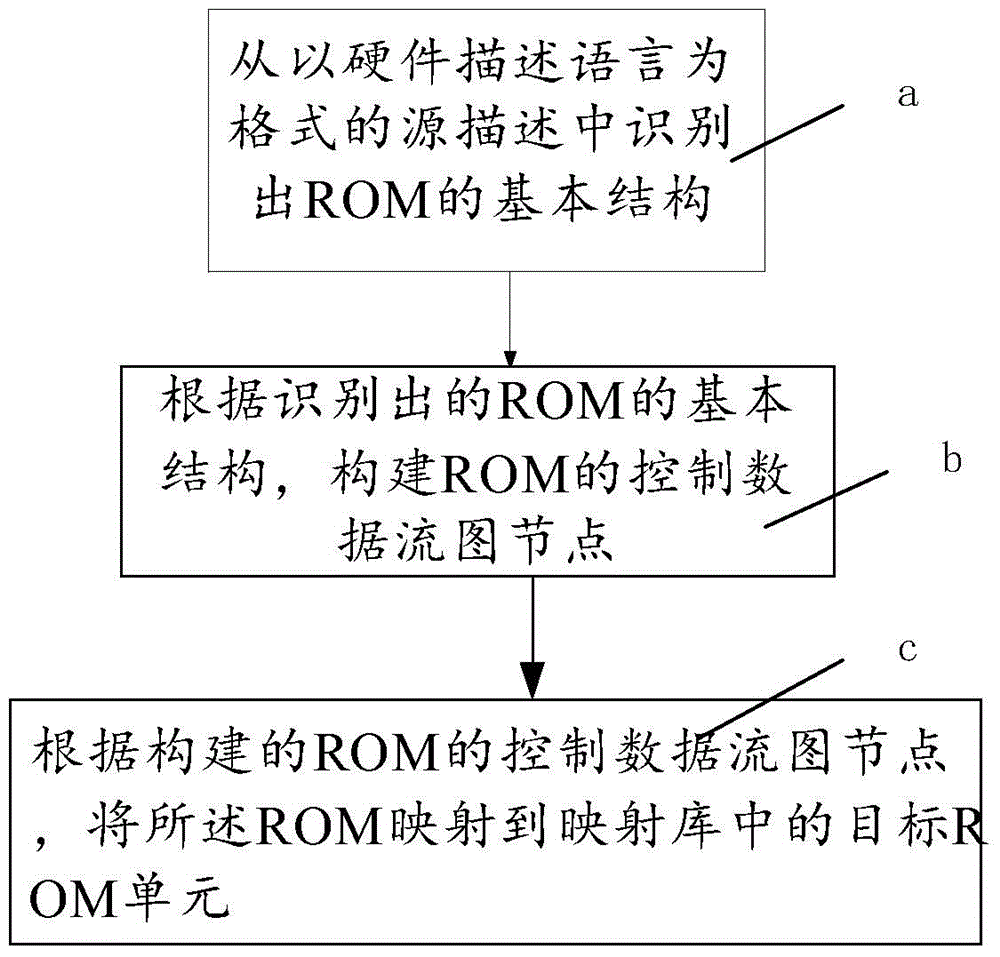

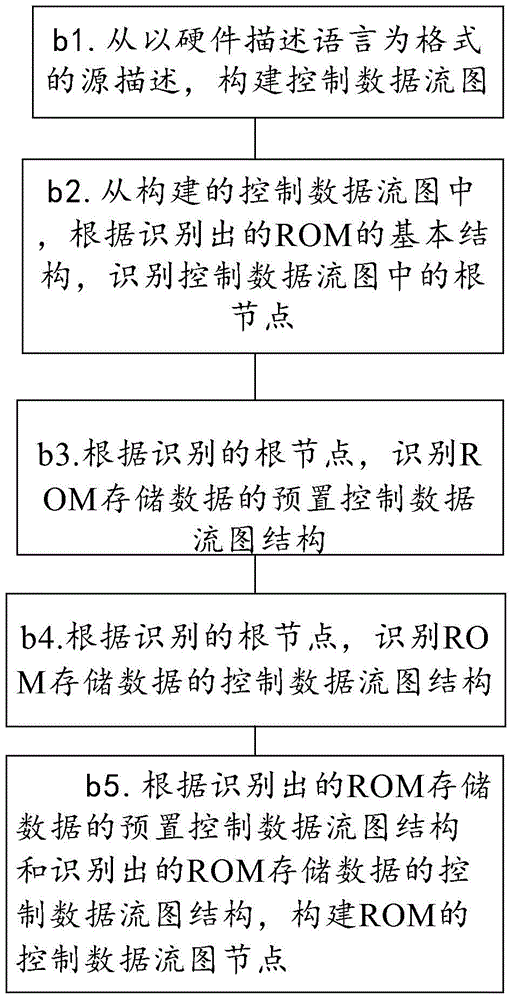

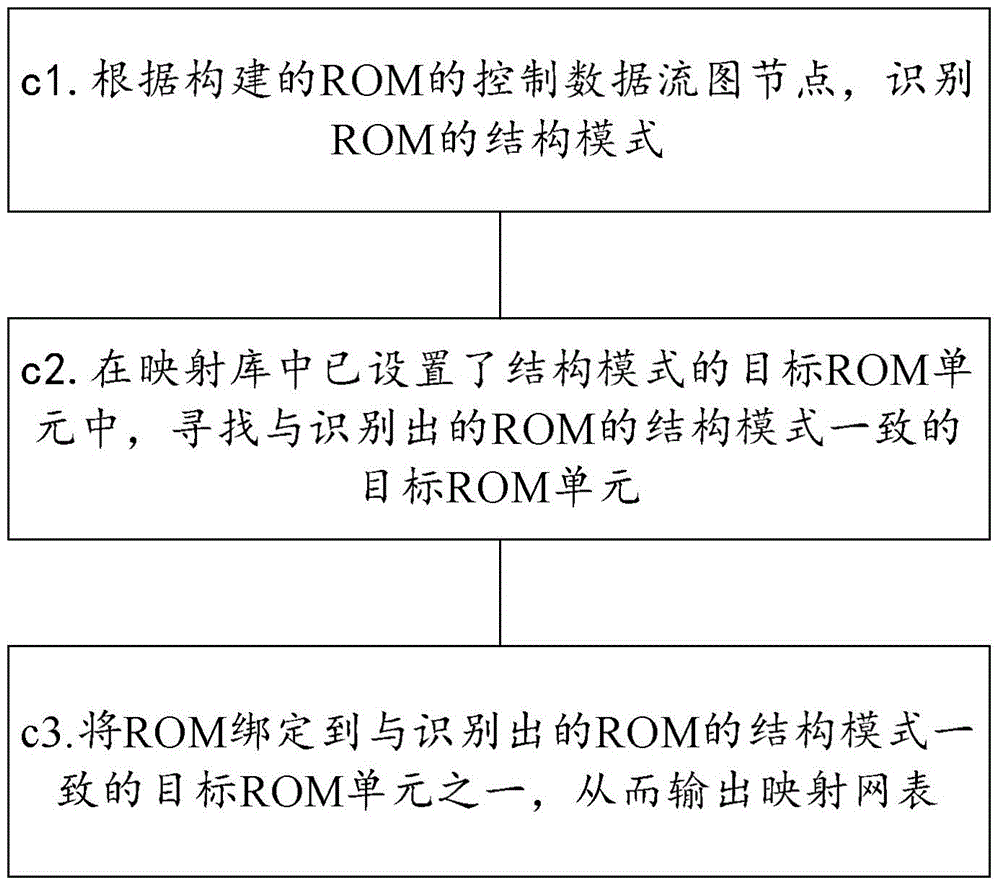

Processing method of ROM (Read-Only-Memory) technology mapping

ActiveCN104361171AMapping implementationSpecial data processing applicationsGraph NodeRead-only memory

The invention provides a processing method of ROM (Read-Only-Memory) technology mapping. The method comprises the following steps: identifying the basic structure of an ROM from source description in which a hardware description language is taken as a format; constructing a control data flow graph node of the ROM according to the identified basic structure of the ROM; mapping the ROM to a target ROM unit in a mapping library according to the constructed control data flow graph node of the ROM. According to the method, mapping from behavioral level ROM description to an ROM target process library in FPGA (Field-Programmable Gate Array) RTL (Register-Transfer-Level) synthesis is realized through ROM identification and mapping, the processed ROM is implemented on an ROM macro unit of an FPGA, and the same effect as a Synplify synthesis tool is achieved.

Owner:SOI MICRO CO LTD

SAT-based technology mapping framework

InactiveUS7725871B1Computer aided designSpecial data processing applicationsTheoretical computer scienceAnalysis sample

Owner:ALTERA CORP

Method for early logic mapping during FPGA synthesis

InactiveUS7543265B1Increase powerIncrease the areaCAD circuit designSpecial data processing applicationsTheoretical computer sciencePredictability

Programming software defining an algorithm that provides improved power, area and frequency predictability of a logic design early in the synthesis flow process, prior to Technology Mapping, without degrading the power, speed or area of the design implementation for PLDs. The method of the algorithm involves performing a high level synthesis of the logic to generate a netlist, performing a multilevel synthesis on the netlist to generate a gate implementation of the netlist; and performing technology mapping on the gate implementation to map the gate implementation to actual resources on the target device. During the high level synthesis of the logic into the netlist, technology mapping is performed on a selected portion of the logic to improve the predictability of the power, area and / or frequency of the logic design without substantially degrading the performance of the power, area and frequency of the logic design.

Owner:ALTERA CORP

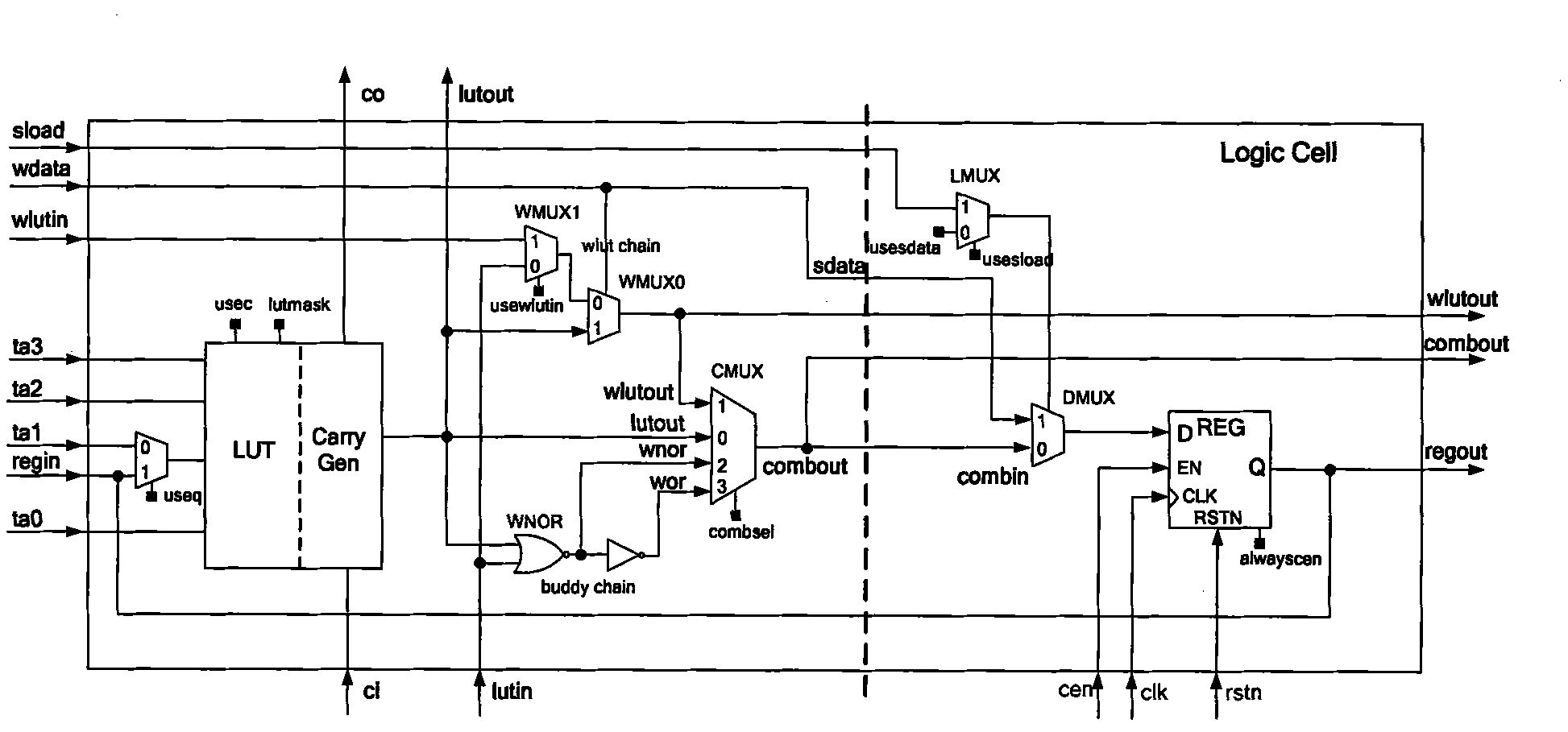

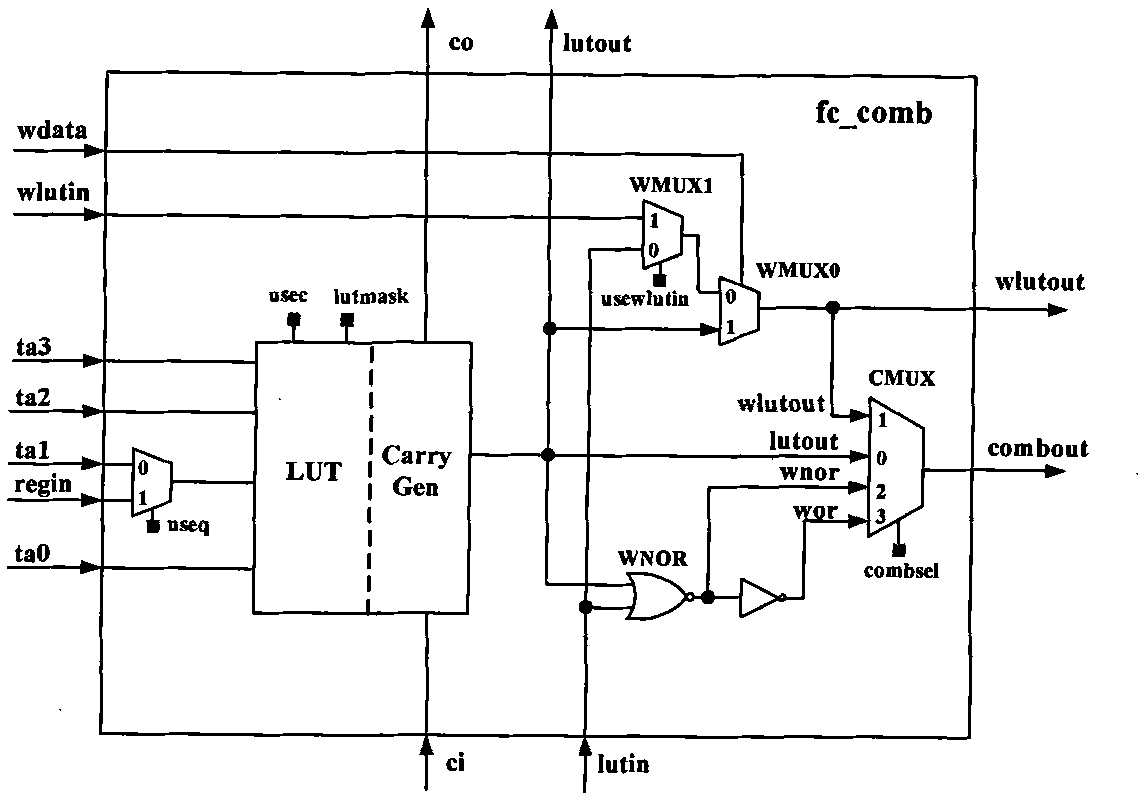

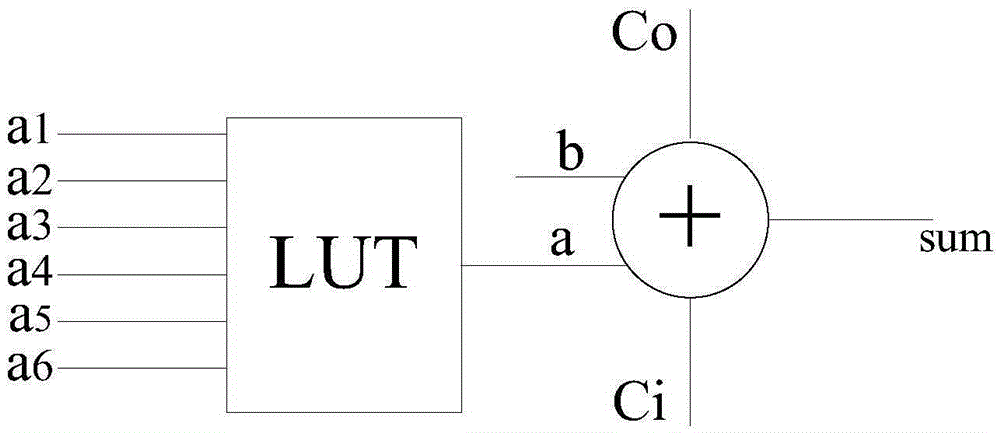

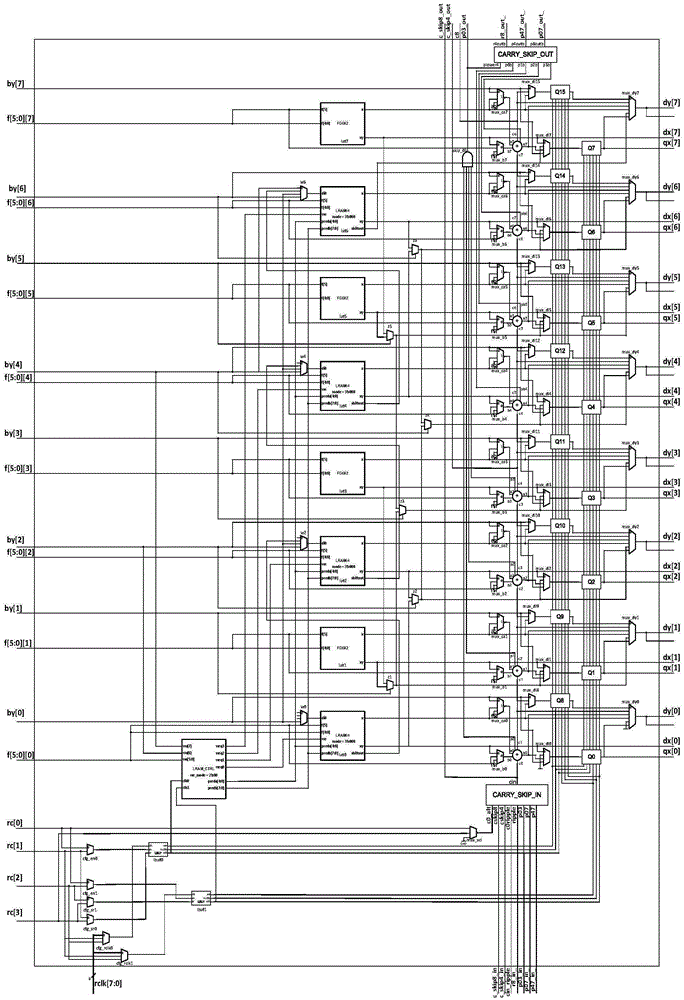

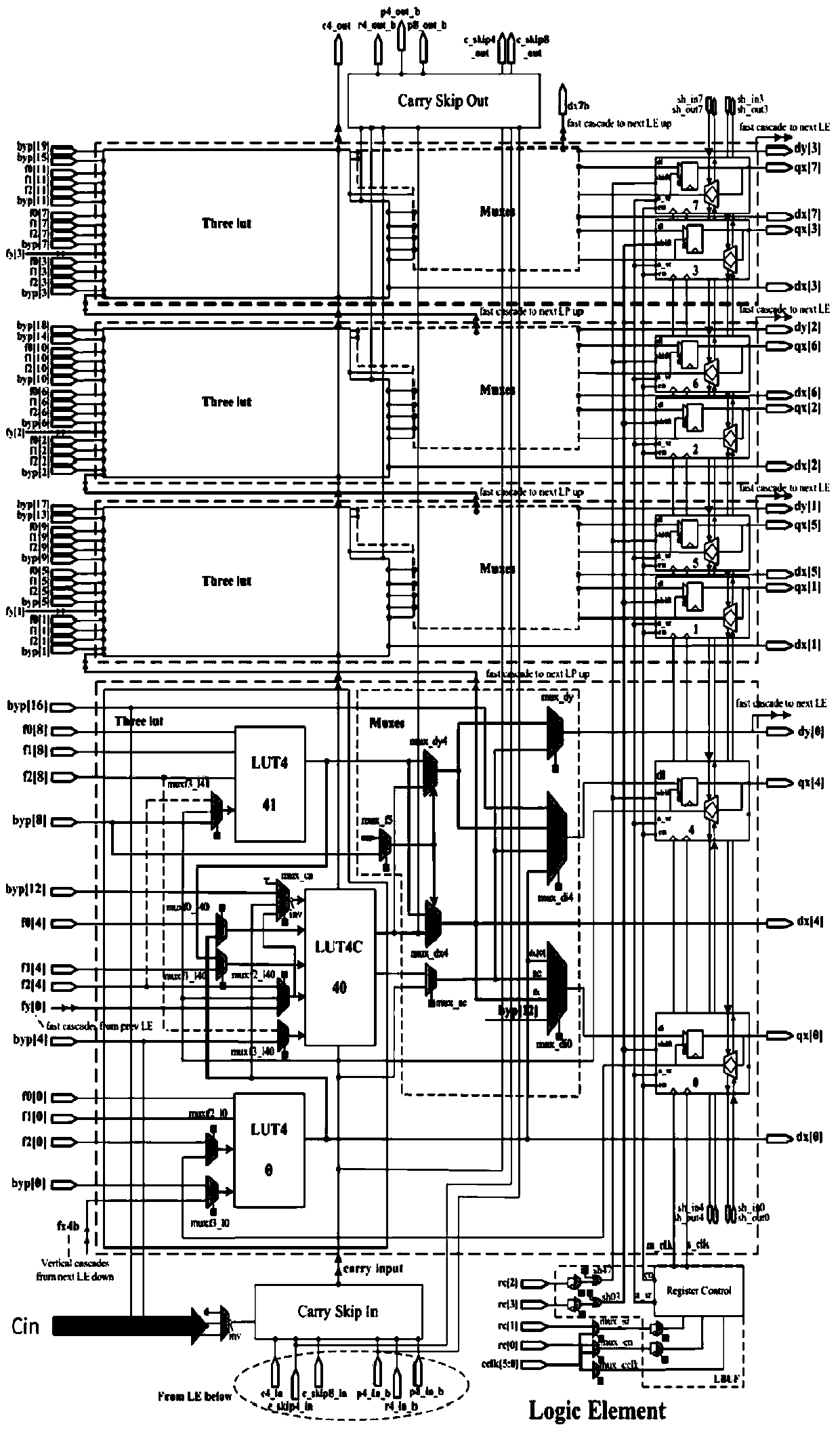

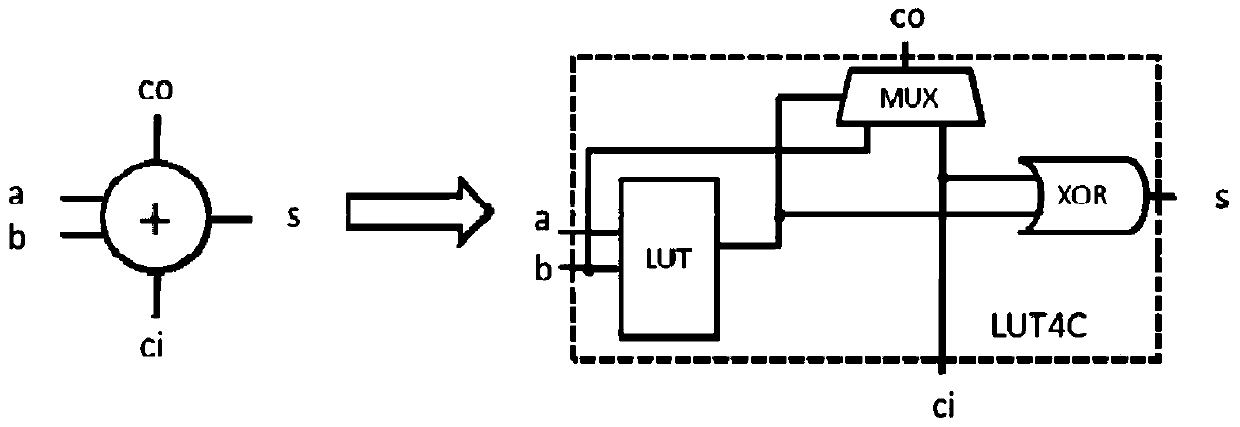

Technology mapping method by utilizing carry chain

ActiveCN106649905ALower latencySave logic resourcesCAD circuit designEnergy efficient computingLogical elementMulti input

The invention relates to a technology mapping method by utilizing a carry chain. According to the method, an FPGA comprises multiple logical units, and one logical unit comprises multiple logical pieces; the output end of a multi-input lookup table in a logical piece LP on a logical element LE of the FPGA is connected to the input end of a second addend of a first summator; one bit signal is input to the carry input end of the first summator and one bit signal is input to the input end of a first addend; a carry output signal is output through the carry output end of the first addend. According to the technology mapping method by utilizing the carry chain, by utilizing the technology mapping method which combines the lookup table and the addend, technology mapping with a long width and / or logic is achieved, chip logical resources can be saved, and time delaying of achieving the logic can be sharply reduced at the same time.

Owner:CAPITAL MICROELECTRONICS

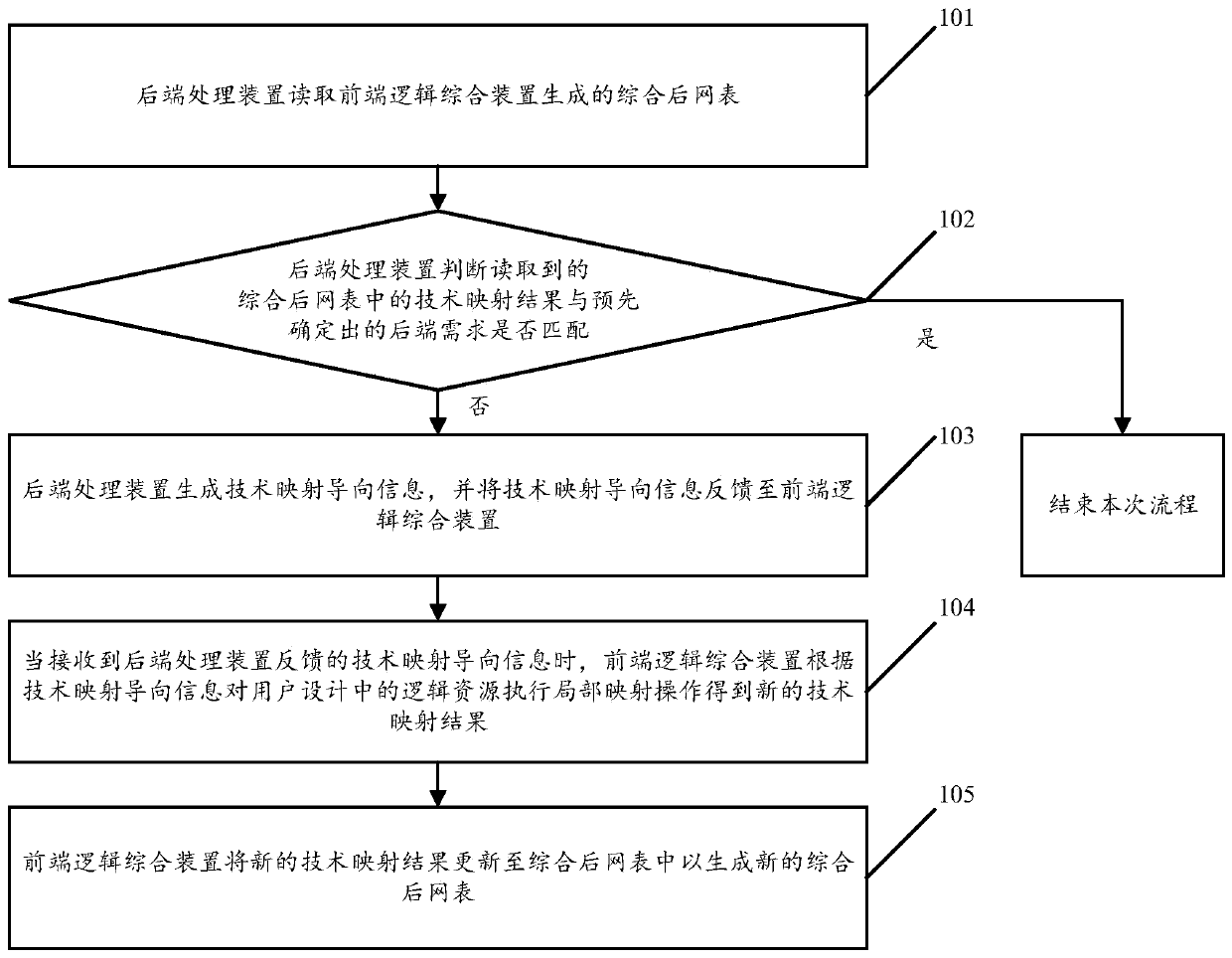

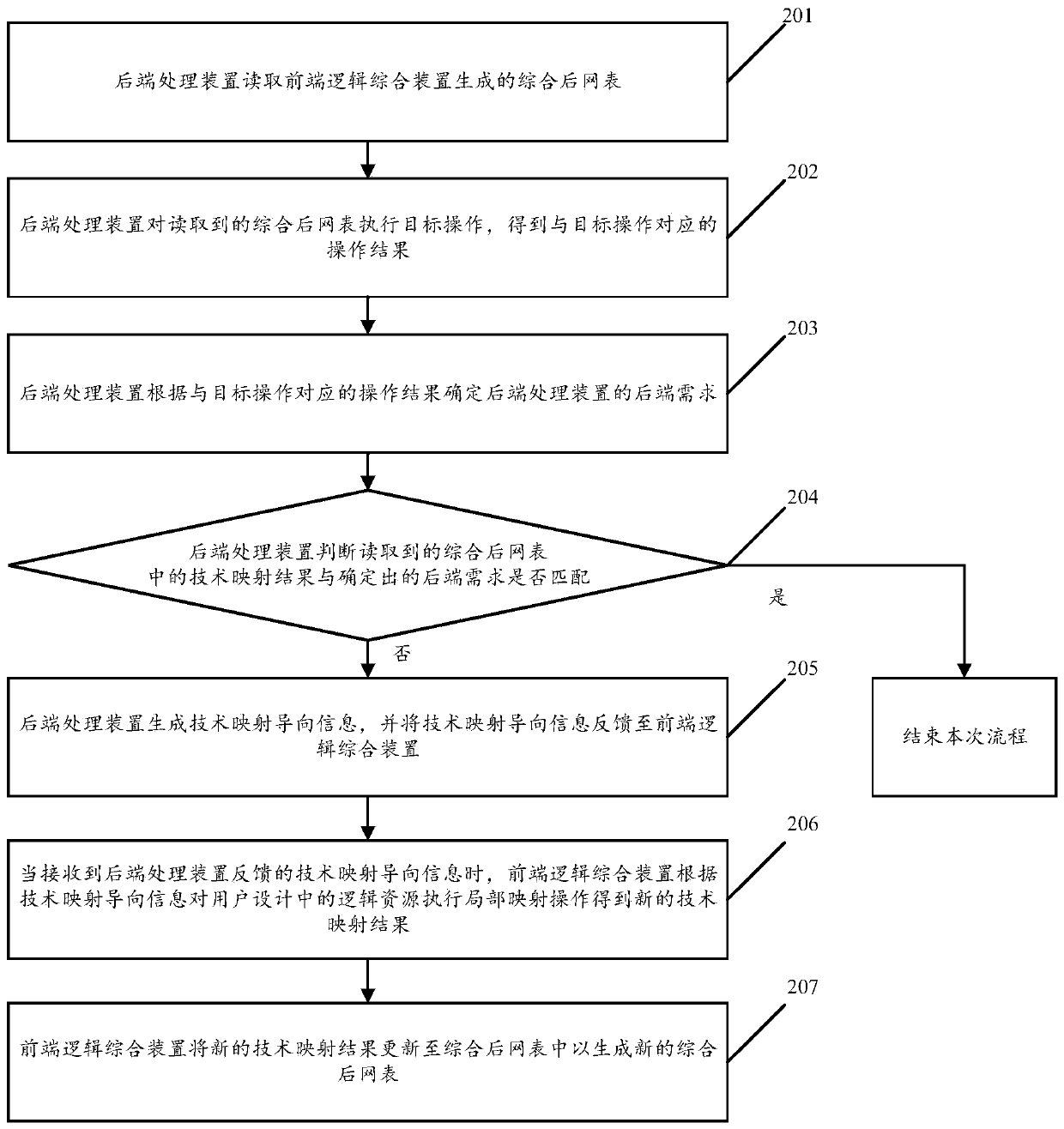

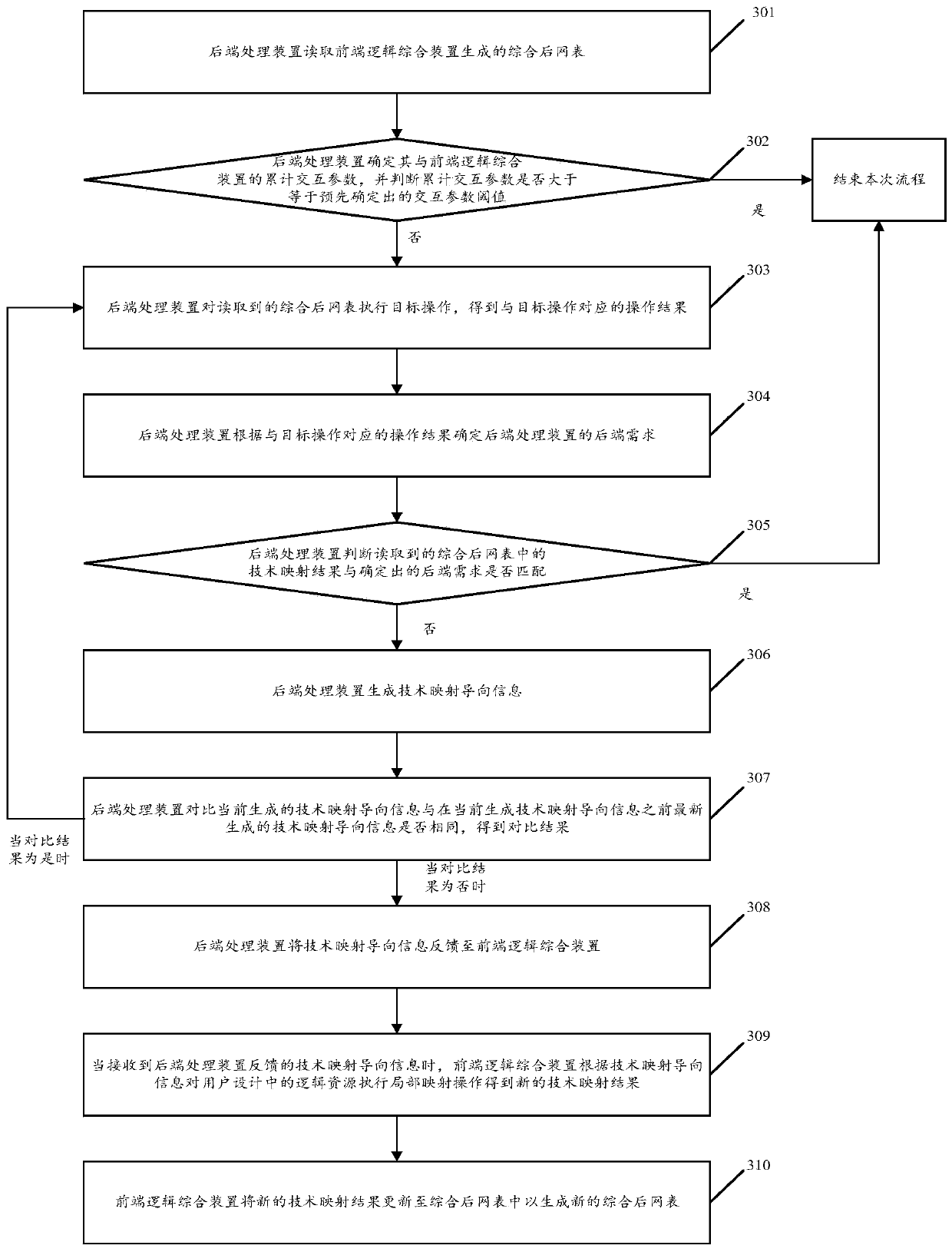

Technical mapping control method, device and system based on rear-end requirements

ActiveCN111144056AQuality improvementImprove matchComputer aided designSpecial data processing applicationsControl engineeringLogisim

The invention discloses a technical mapping control method, device and system based on rear-end requirements. The method comprises the steps that a rear-end processing device reads a comprehensive rear netlist generated by a front-end logic comprehensive device and judges whether a technical mapping result in the comprehensive rear netlist is matched with the rear-end requirements or not; when thejudgment result is no, technical mapping guide information is generated and fed back to the front-end logic synthesis device; when the technical mapping guide information fed back by the back-end processing device is received, the front-end logic comprehensive device executes local mapping operation on logic resources in user design according to the technical mapping guide information to obtain anew technical mapping result and updates the new technical mapping result to the comprehensive rear netlist to generate a new comprehensive rear netlist, and the comprehensive rear netlist generatedby the front-end logic comprehensive device is used for being provided for the rear-end processing device. Visibly, by implementing the method and the device, accurate guide information can be provided for technical mapping according to the back-end requirements, the quality of the mapping result is improved, and the matching degree of the mapping result and the back-end requirements can be further improved.

Owner:GOWIN SEMICON CORP LTD

Early logic mapper during FPGA synthesis

ActiveUS8166436B1CAD circuit designSpecial data processing applicationsTheoretical computer sciencePredictability

Programming software defining an algorithm that provides improved power, area and frequency predictability of a logic design early in the synthesis flow process, prior to Technology Mapping, without degrading the power, speed or area of the design implementation for PLDs. The method of the algorithm involves performing a high level synthesis of the logic design to generate a netlist, performing a multilevel synthesis on the netlist to generate a gate implementation of the netlist, and performing technology mapping on the gate implementation to map the gate implementation to actual resources on the target device. During the high level synthesis of the logic design into the netlist, technology mapping is performed on a selected portion of the logic design.

Owner:ALTERA CORP

A high-efficiency fpga technology mapping method

ActiveCN105488285BReduce iterative processIterative reduction where the number of iterations can be adaptively changedComputer aided designSpecial data processing applicationsDynamic planningLogic optimization

The invention discloses an efficient FPGA technology mapping algorithm. Technical mapping is divided into logic optimization and structural optimization. The logic optimization part adopts an AIG model and technologies of balance, rewrite, refactor and the like to optimize a circuit. The structural optimization part adopts a DAG model and comprises three steps of partition generation, partition selection and LUT mapping. For the partition generation, a dynamic planning thought is adopted for quickly generating all k- feasible partitions for each node. For the partition selection, a partition set with a characteristic that a time delay and an area are optimized at the same time is finally selected through multi-time forward traversal and backward traversal iteration based on an iterative heuristic thought with an adaptively changeable iterative frequency. Meanwhile, a node area stream calculation formula is corrected and the randomness of the partition selection is improved. Through the LUT mapping, partition combination generated by the partition selection is mapped into an LUT network.

Owner:XIDIAN UNIV

Technology Mapping Method of Adder with Optimum Layout Structure Based on FPGA

ActiveCN105589981BOptimize structure layoutSpecial data processing applicationsLogical elementFpga architecture

The invention relates to an FPGA-based summator technology mapping method for optimizing a layout structure. The method comprises the following steps: inputting a carry input signal of a first summator at each of two input ends of an LUT4C with a carry chain in one logic portion (LP) of one logical element (LE) of the FPGA; carrying out an logical operation on the two input carry input signals by the LUT4C and then outputting a sum and a first carry output signal; and connecting the first carry output signal to a carry input end of the first summator. Through using one LUT4C to generate a carry input signal of the lowest order, the starting position of the carry chain is not restricted by FPGA architecture any longer and can lie in any carry element of the LE, thus optimizing the layout structure and size of a chip.

Owner:CAPITAL MICROELECTRONICS

Systems and methods for reducing static and total power consumption in a programmable logic device

InactiveUS20070101175A1Consumes less powerMaintaining level of functionalityVolume/mass flow measurementPower supply for data processingProgrammable logic deviceTime segment

Owner:ALTERA CORP

Technology mapping method for integrated circuits for improved logic cells

InactiveCN102375905BImprove performanceSimple designSpecial data processing applicationsComputer architectureLogic cell

The invention relates to a technology mapping method for integrated circuits for improved logic cells, which comprises the following steps of: firstly, decomposing a universal combinational logic circuit into circuits consisting of input logic cells 2; then, taking the input logic cell 2 as a node, partitioning the node based on an improved logic cell, and finding out all partitions of the node; taking a partition corresponding to the maximum ratio of the number of nodes covered by each partition PGCN(Propagate Gate Cover Number) to the number of actually-used improved logic cells PRUN(Propagate Resource Usage Number) as the optimal partition; and finally, converting the optimal partition into a corresponding improved logic cell. By using the method provided by the invention, through fully using the structural advantages of the improved logic cells, an improved circuit is more efficient on area and time. The method provided by the invention can be widely applied to technology mapping of integrated circuits.

Owner:AGATE LOGIC BEIJING