Technology mapping method for integrated circuits for improved logic cells

A technology of process mapping and logic unit, applied in the field of process mapping, to achieve the effect of reducing difficulty, good area and excellent performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

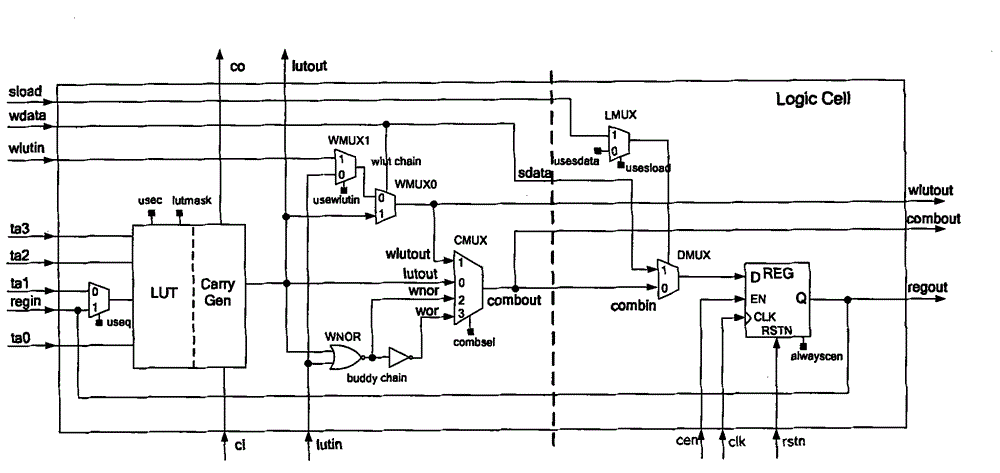

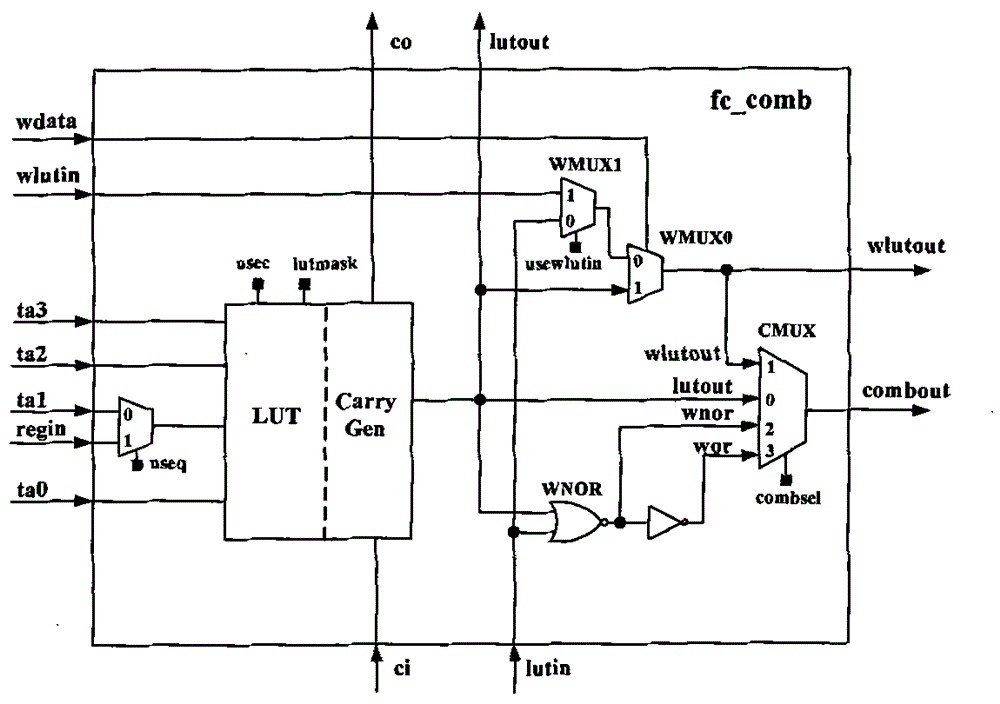

[0034] Figure 10 It is an integrated circuit process mapping flowchart for an improved logic unit according to an embodiment of the present invention.

[0035] In an integrated circuit, the circuits in the initial logic netlist are general logic circuits that have nothing to do with physical devices. The general logic circuits include two types, one is general sequential logic circuits, and the other is general combinational logic circuits. Step 101 described below is to map the general sequential logic circuit into a specific function register fc_reg, and step 102, step 103, and step 104 are to map the general combinatorial logic circuit into a combinatorial improved logic unit fc_comb. Therefore, step 101 can be before step 102, or after step 104, or anywhere between step 102 and step 104.

[0036] In step 101, according to the initial logic netlist, its general sequential logic circuit is mapped to the corresponding synchronous circuit fc_reg in register form, including m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More