A high-efficiency fpga technology mapping method

A mapping method and technology technology, applied in the computer field, can solve the problems of time-consuming technology mapping and unclear quality optimization of technology mapping, and achieve the effects of improving efficiency, reducing iterations, and optimizing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0070] The present invention will be further described below in conjunction with the accompanying drawings. It should be noted that this embodiment is based on the technical solution, and provides detailed implementation and specific operation process, but the protection scope of the present invention is not limited to the present invention. Example.

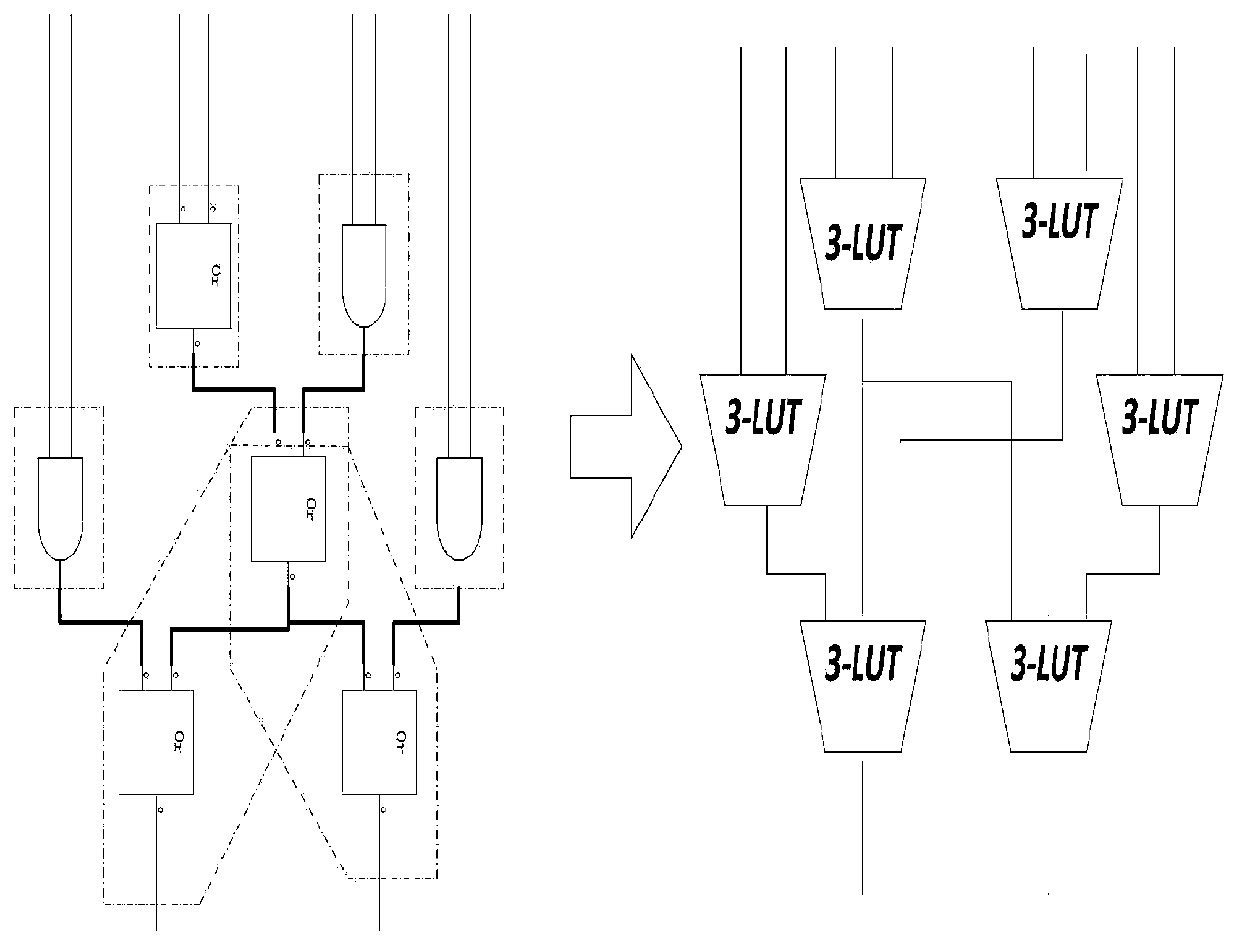

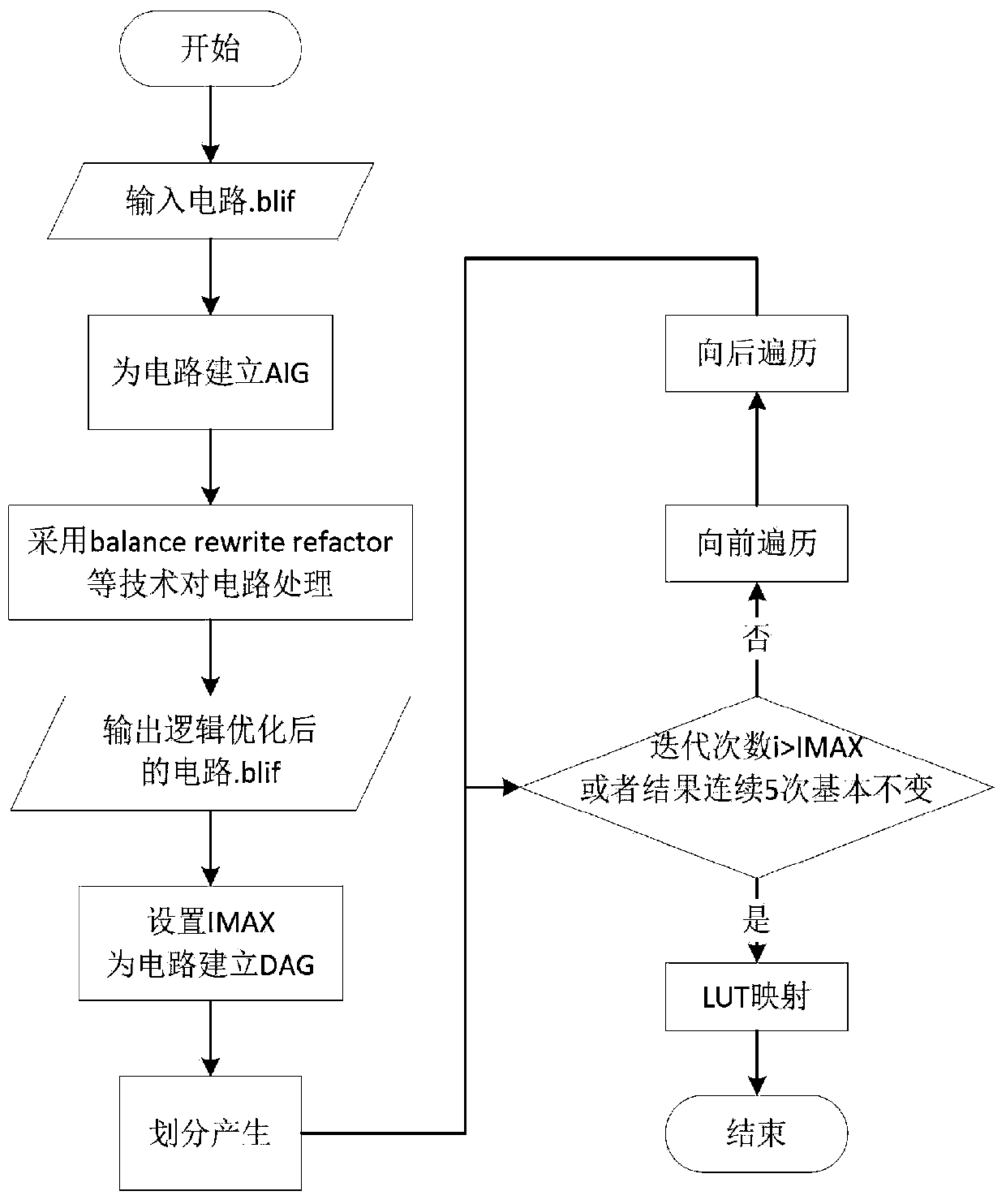

[0071] like figure 2 As shown, a high-efficiency FPGA technology mapping algorithm includes the following steps:

[0072] S1 logic optimization:

[0073] 1.1) Initialization: create an AIG diagram for the circuit;

[0074] 1.2) Decompose and optimize the AIG diagram obtained in step 1.1), obtain two input circuits and output;

[0075] S2 structure optimization:

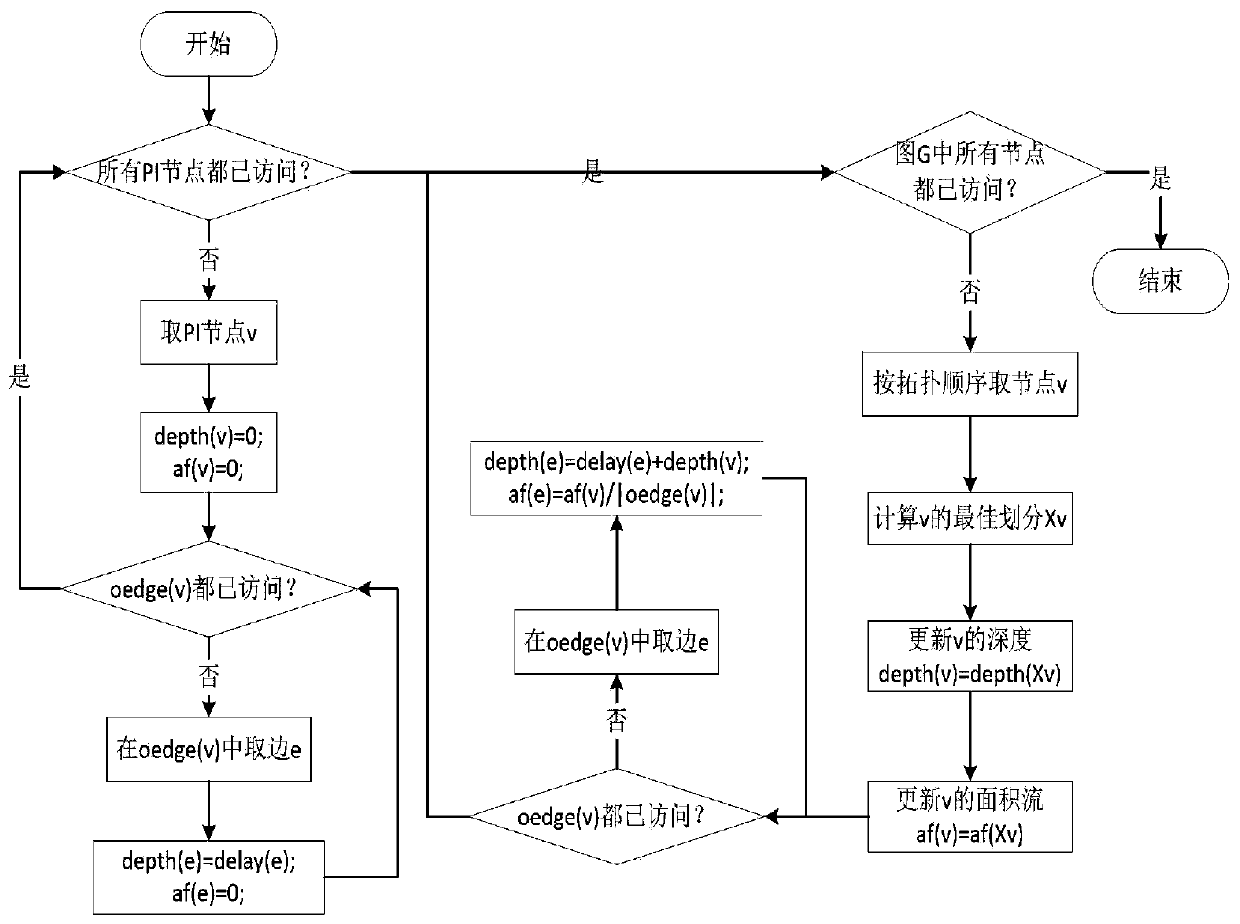

[0076] 2.1) Establish a DAG graph G for the circuit obtained after the logic optimization of step S1, and set the maximum number of iterations IMAX and the maximum number M of continuous execution results;

[0077] 2.2) Generate all k-feasible partitions for each ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More