Patents

Literature

93 results about "Logic optimization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

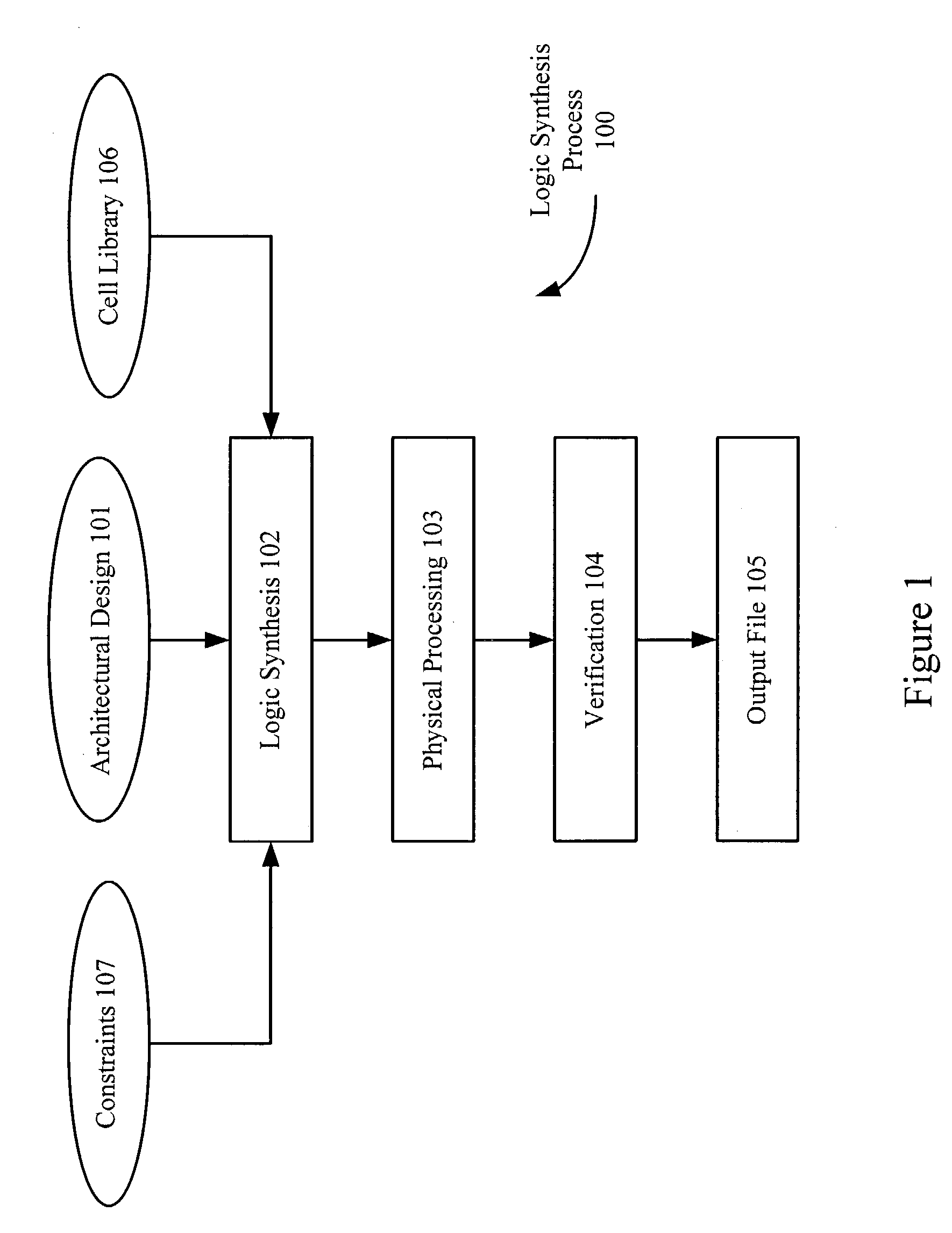

Logic optimization, a part of logic synthesis in electronics, is the process of finding an equivalent representation of the specified logic circuit under one or more specified constraints. Generally the circuit is constrained to minimum chip area meeting a prespecified delay.

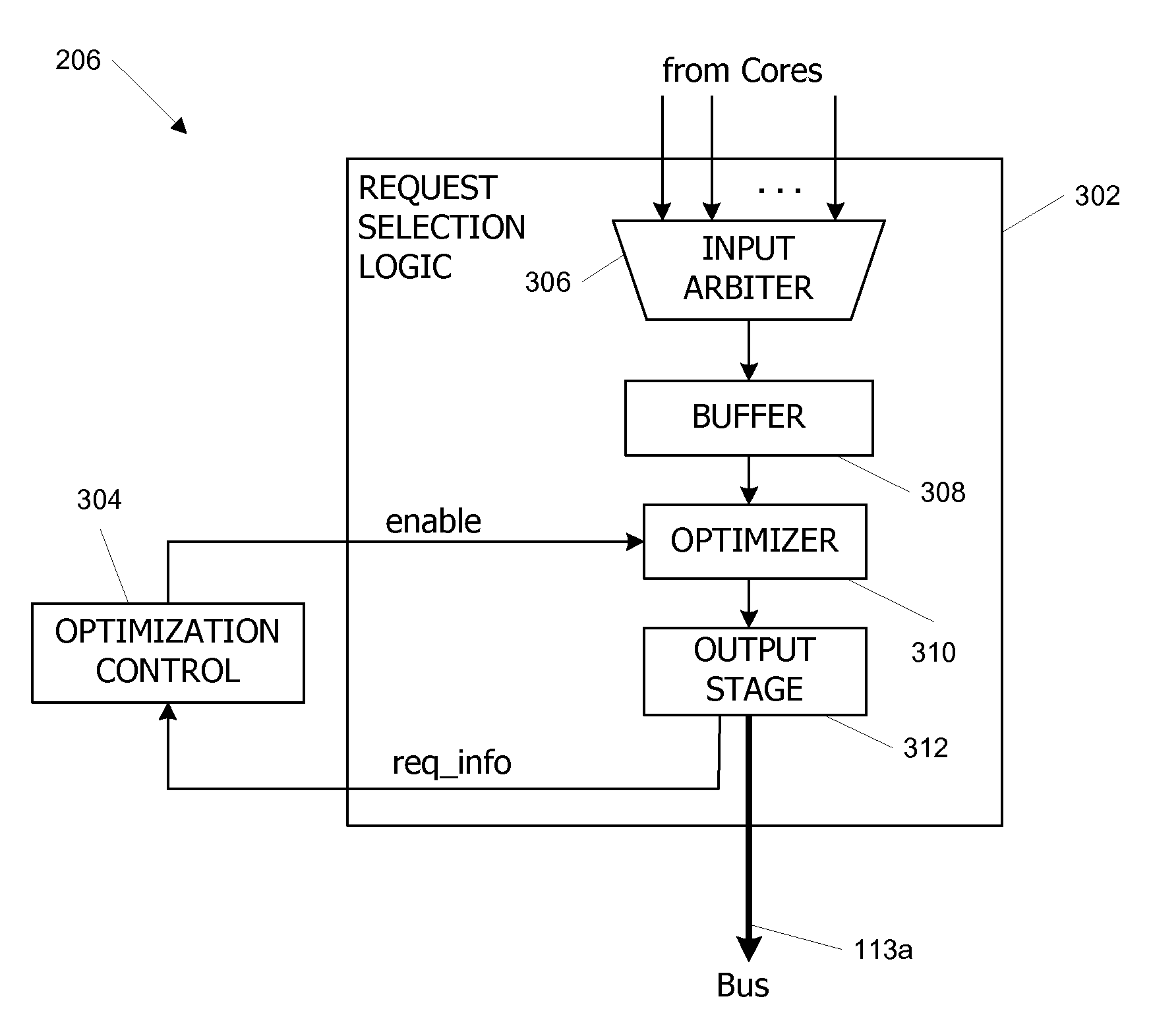

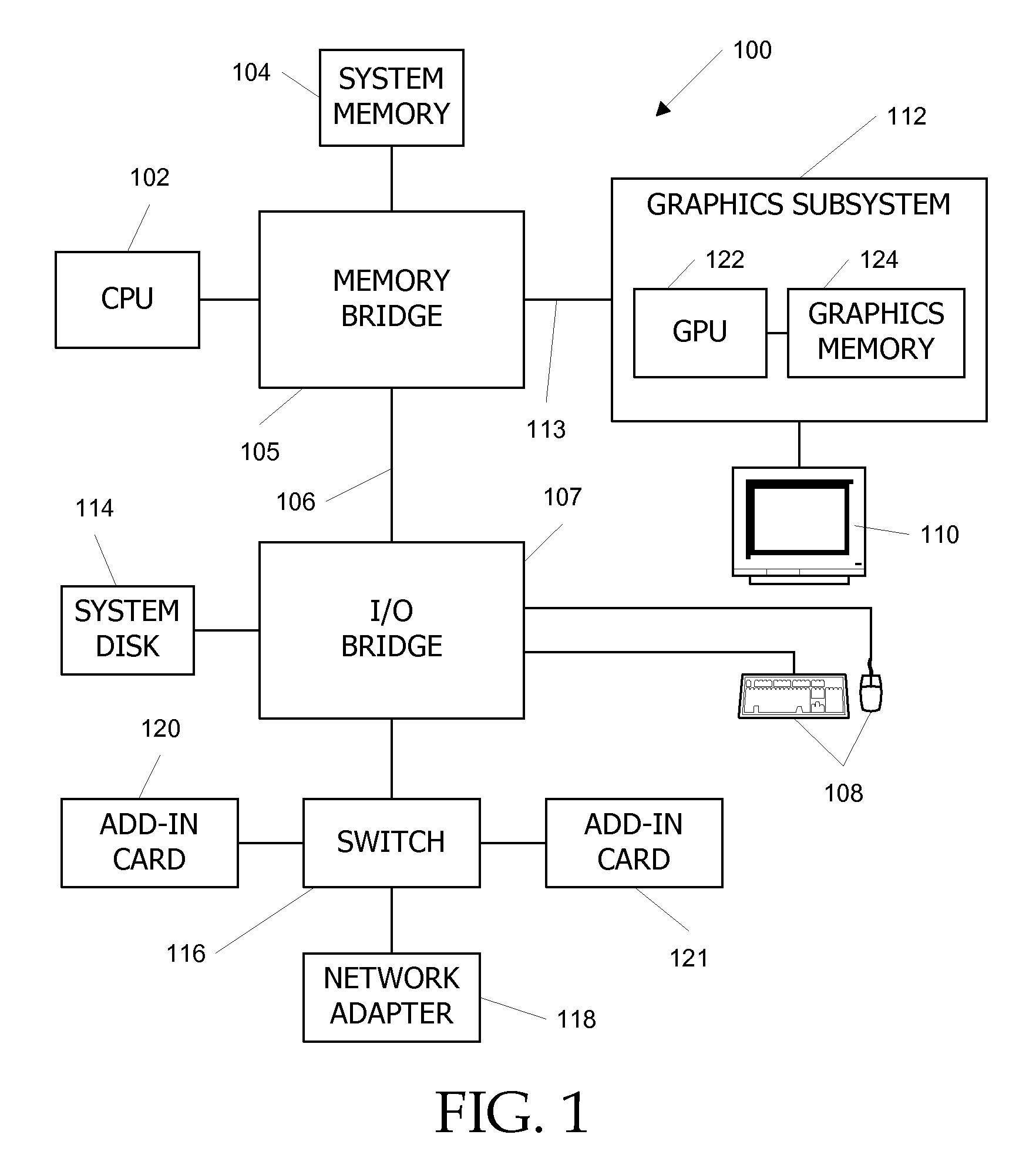

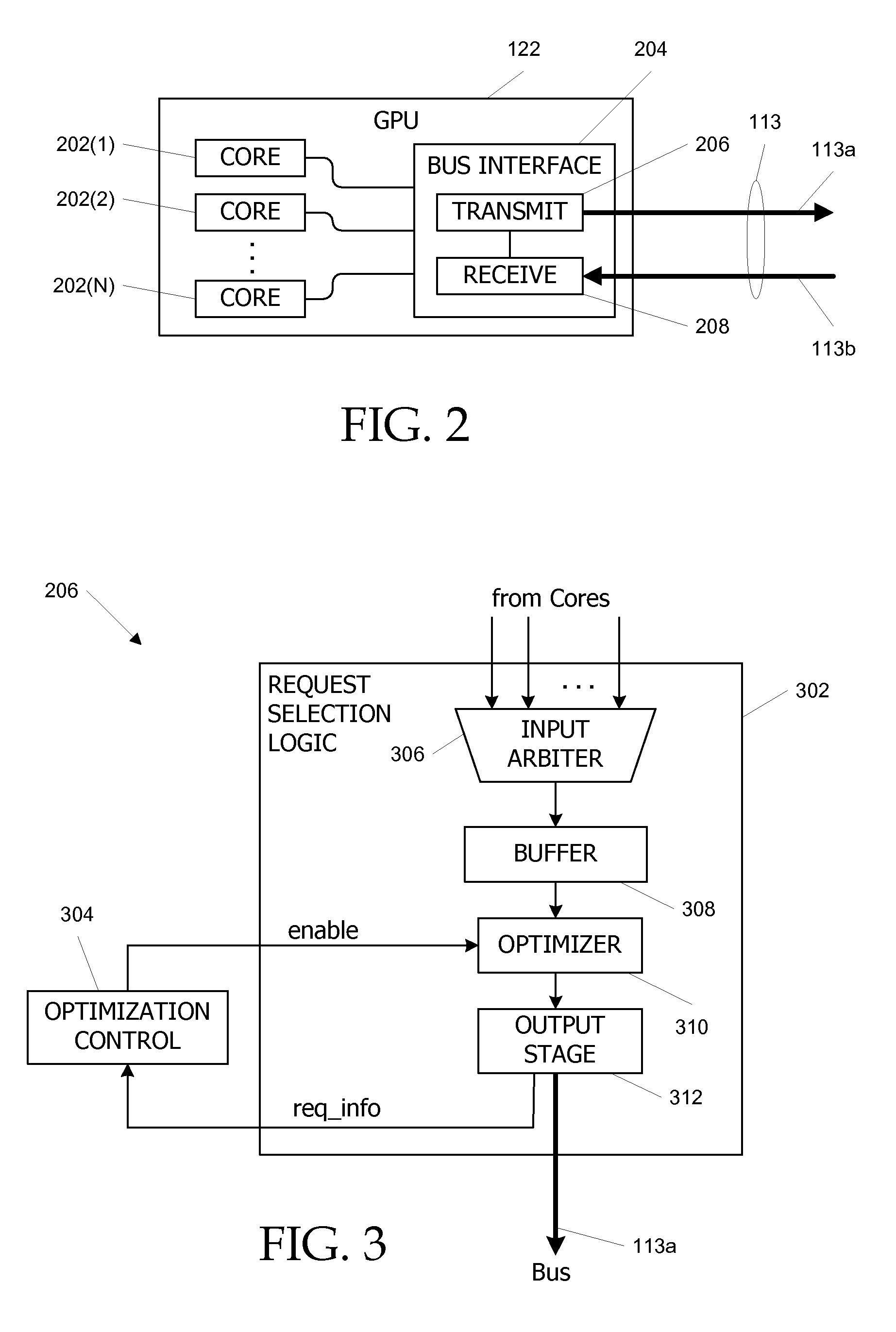

Control device for data stream optimizations in a link interface

Optimization logic that optimizes a stream of requests being transmitted onto a link by a link interface unit can be enabled or disabled based on a performance metric that represents a measure of the degree to which a response to a request is likely to be slowed due to congestion, propagation delays, or other bottlenecks in the system. For example, the performance metric can be based on a measured level of link activity due to requests from the transmitting device and / or a prediction as to behavior (e.g., access time) of the target device that receives the stream of requests. The control logic advantageously does not require extra signals to be carried on the bus.

Owner:NVIDIA CORP

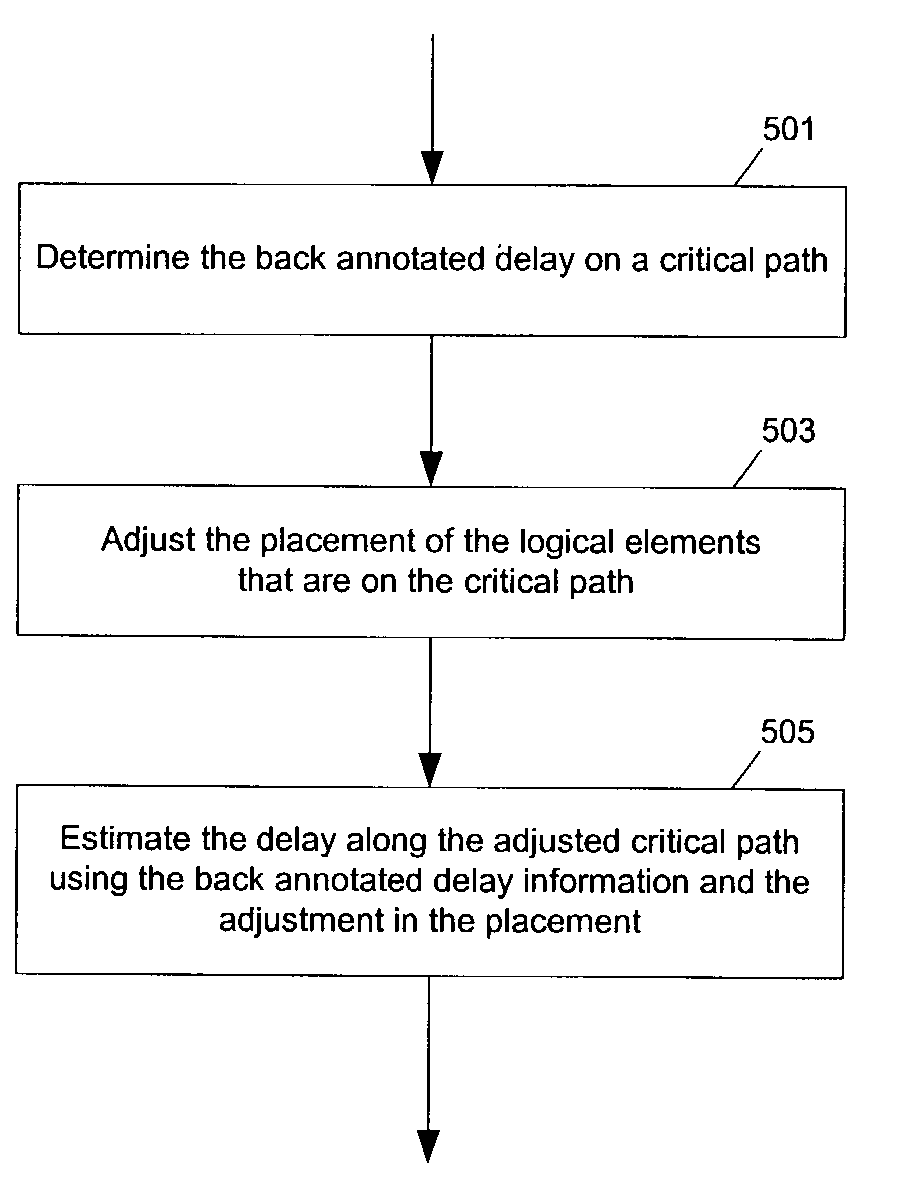

Method and apparatus to estimate delay for logic circuit optimization

InactiveUS6973632B1CAD circuit designSoftware simulation/interpretation/emulationLogic optimizationLogic circuitry

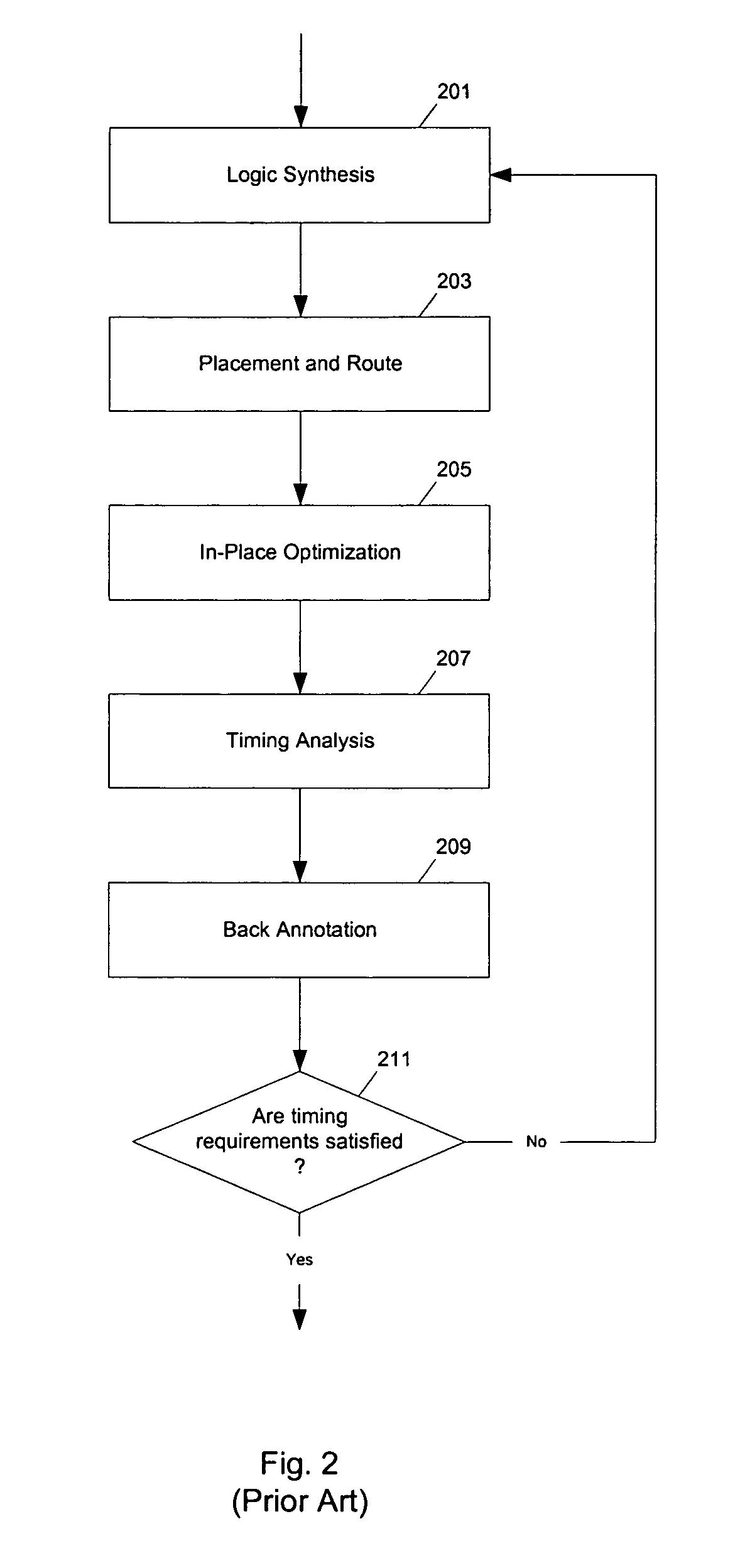

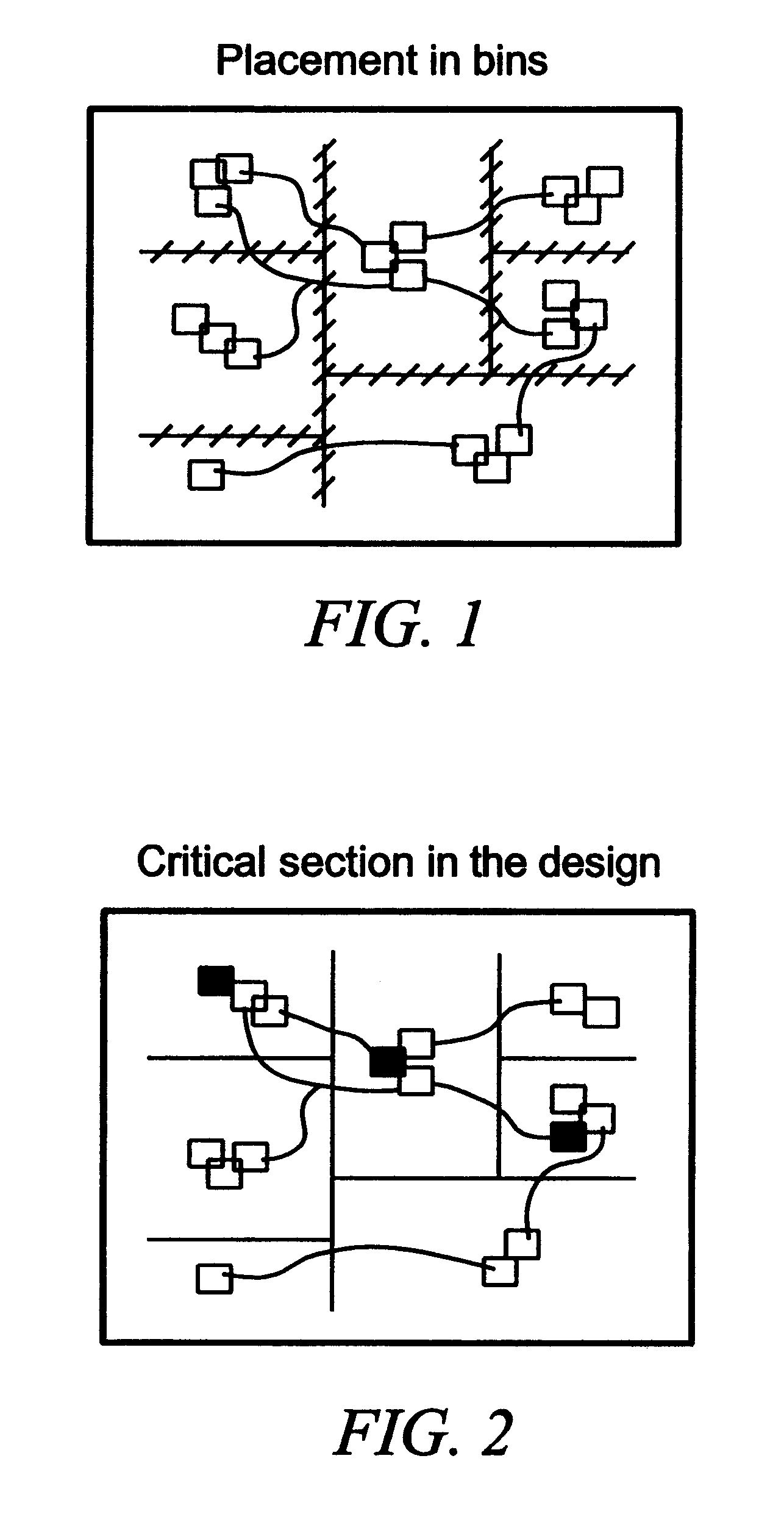

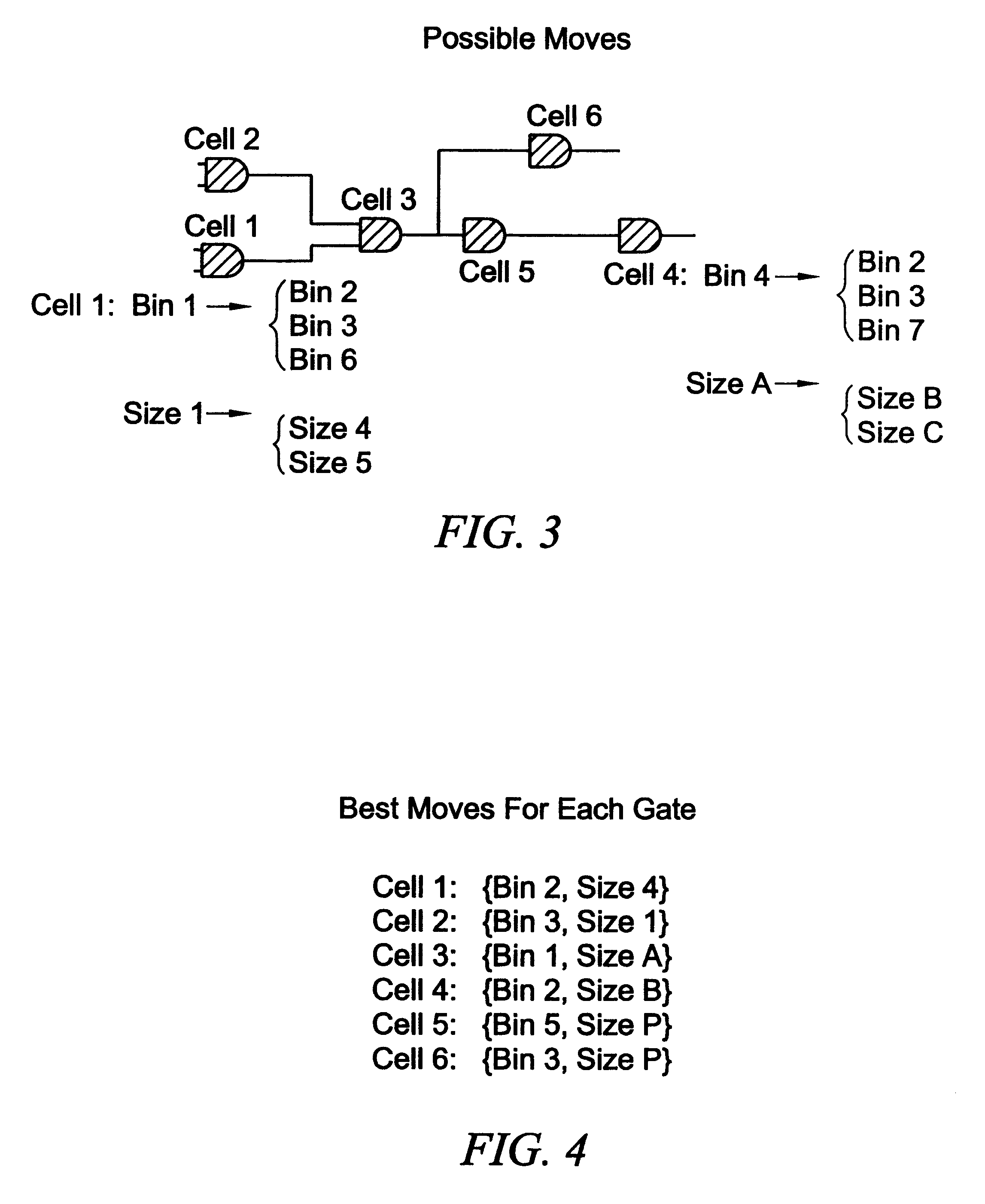

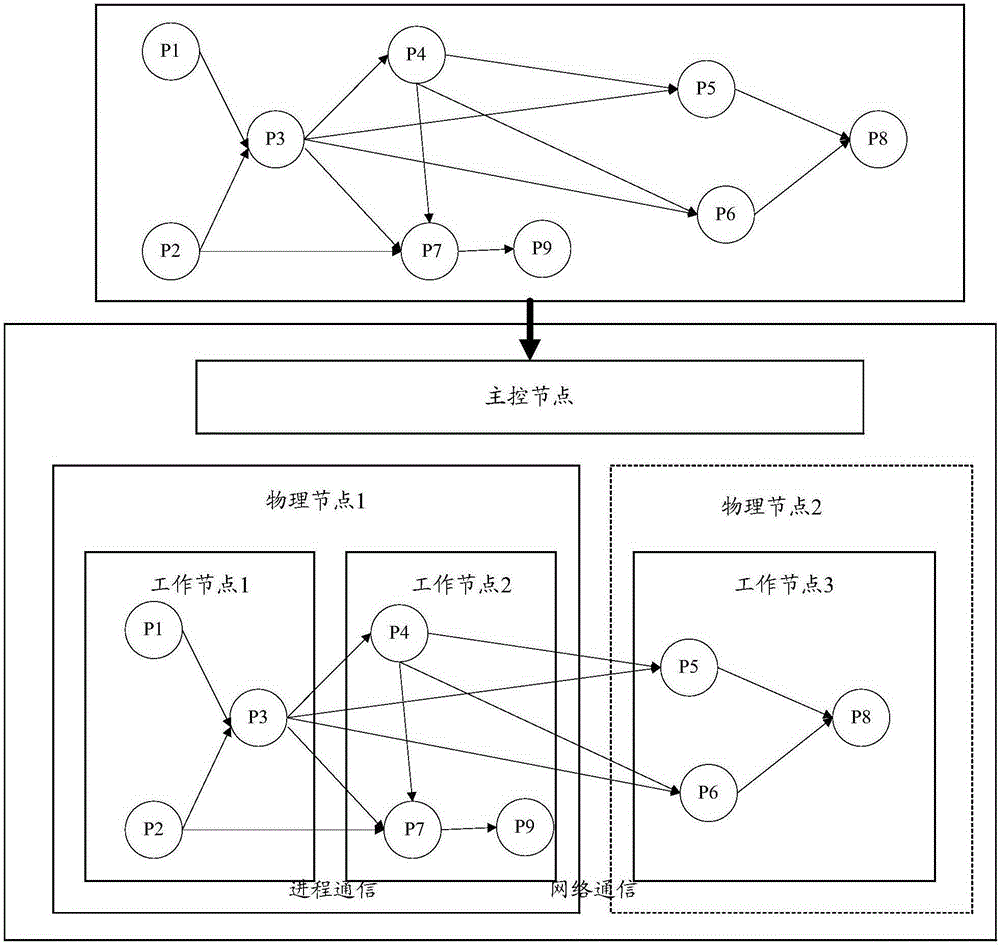

Methods and apparatuses to estimate delay for logic circuit optimization using back annotated placement and delay data. In one aspect of the invention, a method to design a logic circuit, the method includes: modifying a first path that is back annotated with first placement information and first delay information to generate a second path; and calculating a signal delay on the second path from second placement information for the second path, the first placement information and the first delay information (or, computing an adjustment to the first delay information from second placement information for the second path and the first placement information). In one example according to this aspect, the first placement information and the first delay information are back annotated from a timing analysis based on placing and routing at least the first path. An actual route is determined from the first placement information in calculating the signal delay.

Owner:SYNOPSYS INC

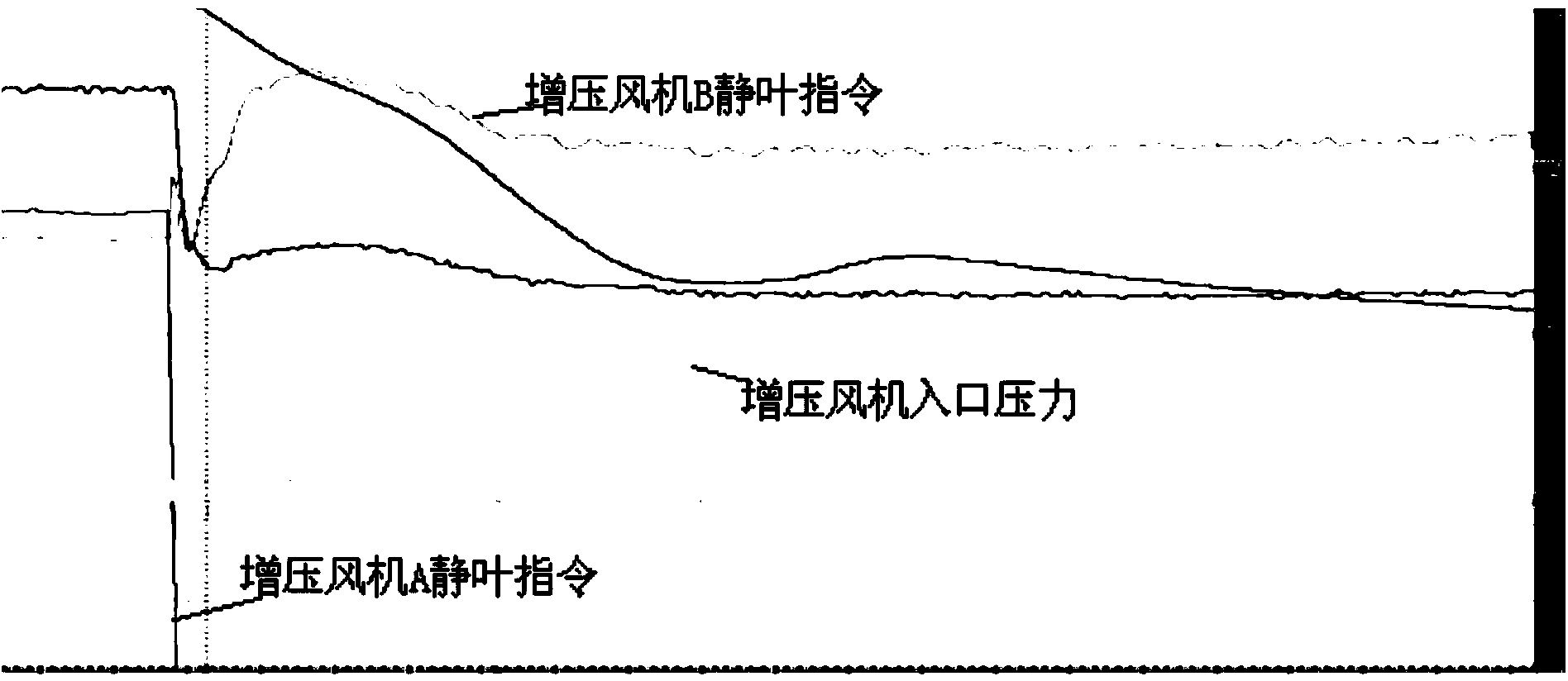

Induced draught fan and boost fan combined control method for large thermal generator set

InactiveCN104033410AGuaranteed uptimeStable and optimized operationPump controlNon-positive displacement fluid enginesLogic optimizationEngineering

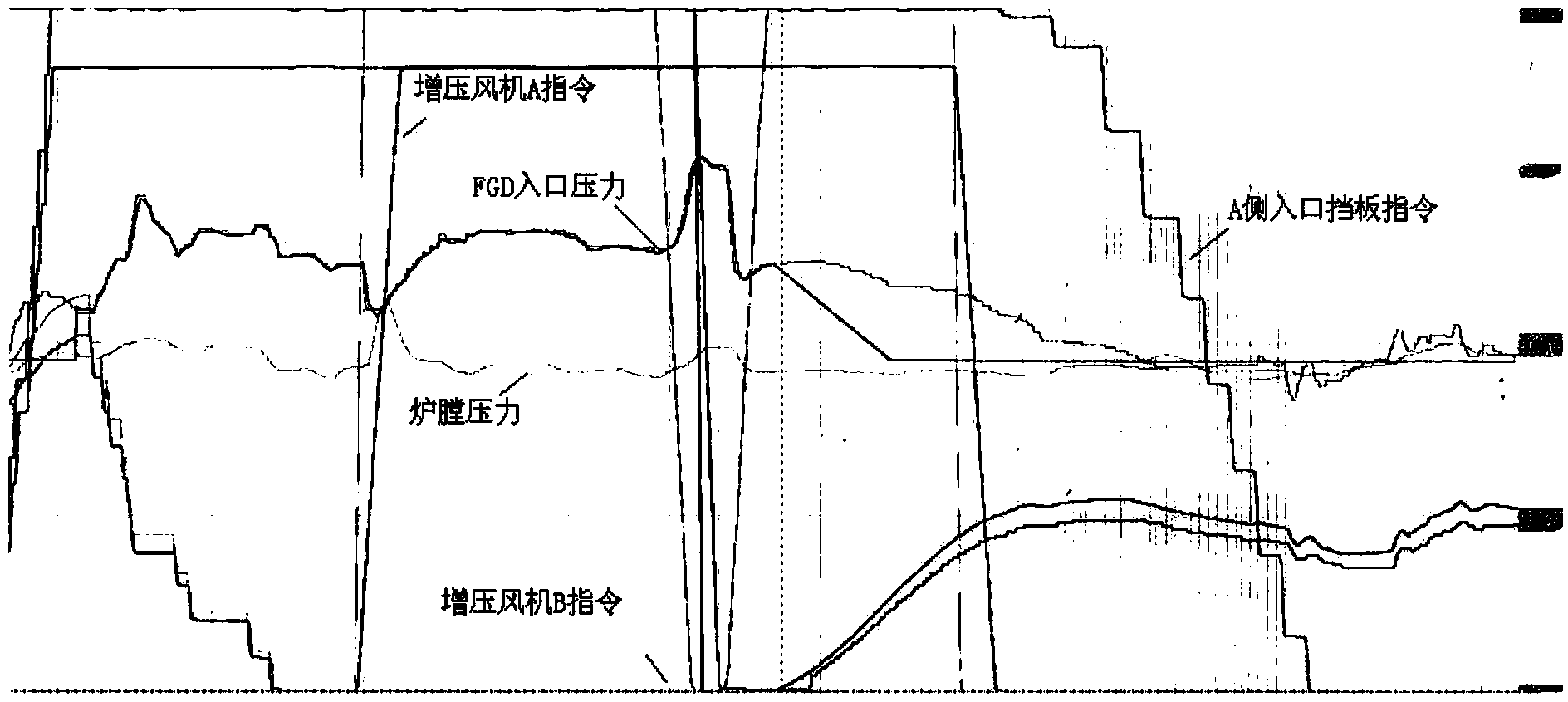

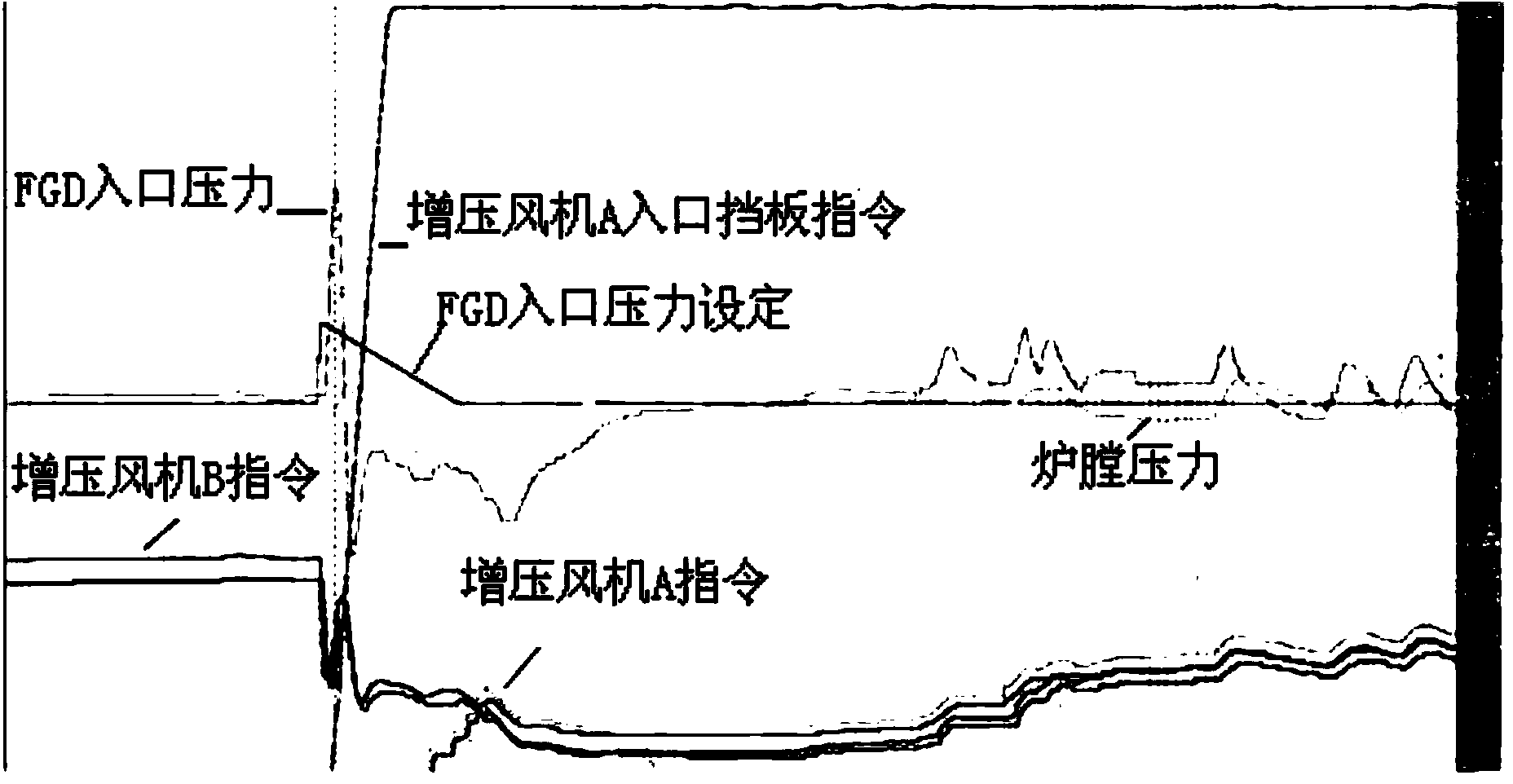

The invention discloses an induced draught fan and boost fan combined control method for a large thermal generator set. The thermal generator set comprises at least two induced draught fans and at least two boost fans. The control method includes the following portions, namely, stripping protection logic optimization of the induced draught fans and the boost fans, sequential control start step sequence optimization of the induced draught fans and the boost fans, the steps of the induced draught fan and boost fan combined control method in the normal running process, and the steps of the induced draught fan and boost fan combined control method under the abnormal working condition. By means of the method, the influences on pressure at the inlet of the FGD can be reduced when the boost fans are started; working condition changes can be responded to in time in the running process of the set; running of the set can be ensured by conducting adjustment in time through the RB method and other methods under the accident working condition; when device safety is influenced, interlocked stripping of the induced draught fans and the boost fans can be achieved, and the method has great significance in safe, stable and optimized running of the set.

Owner:STATE GRID CORP OF CHINA +1

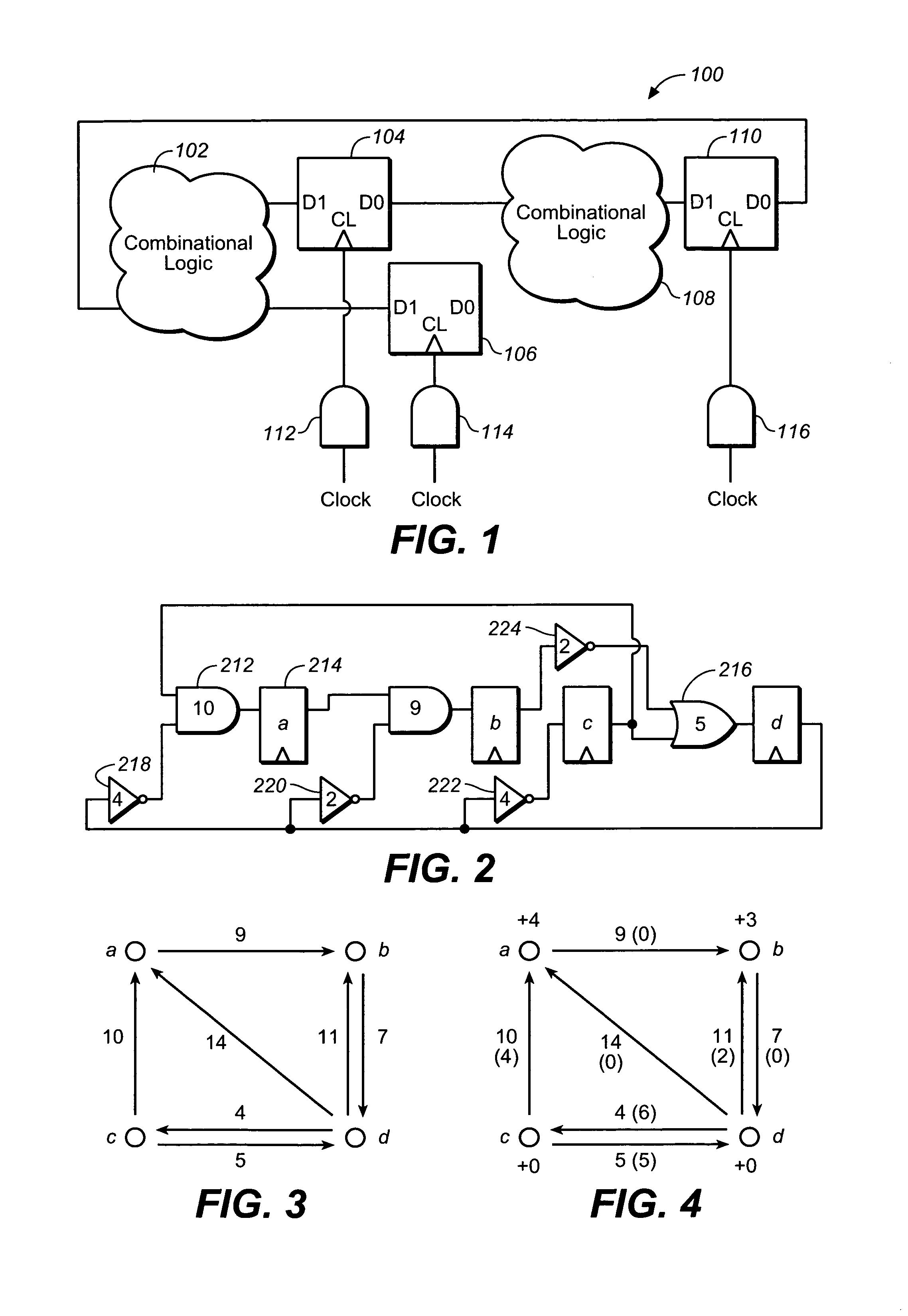

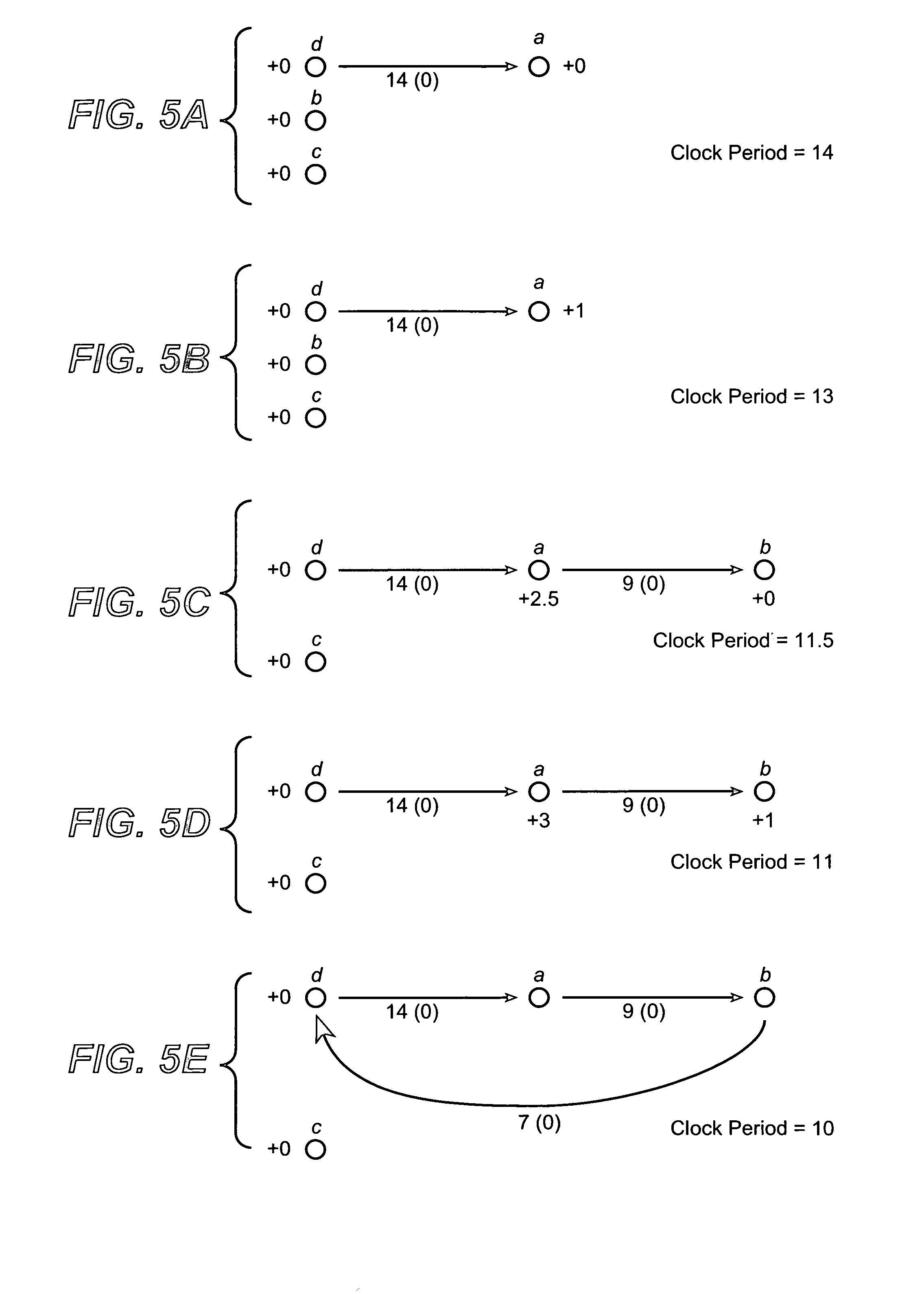

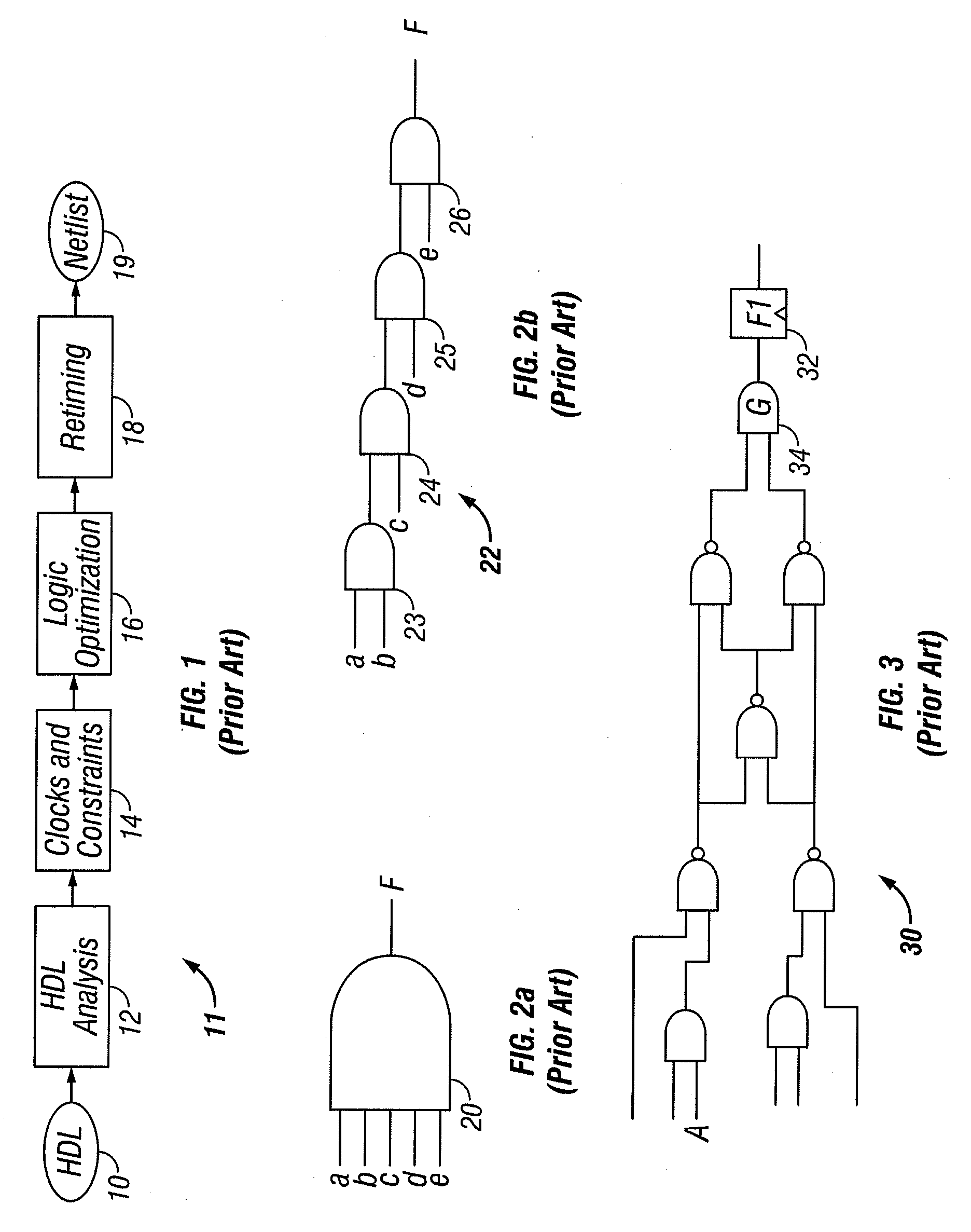

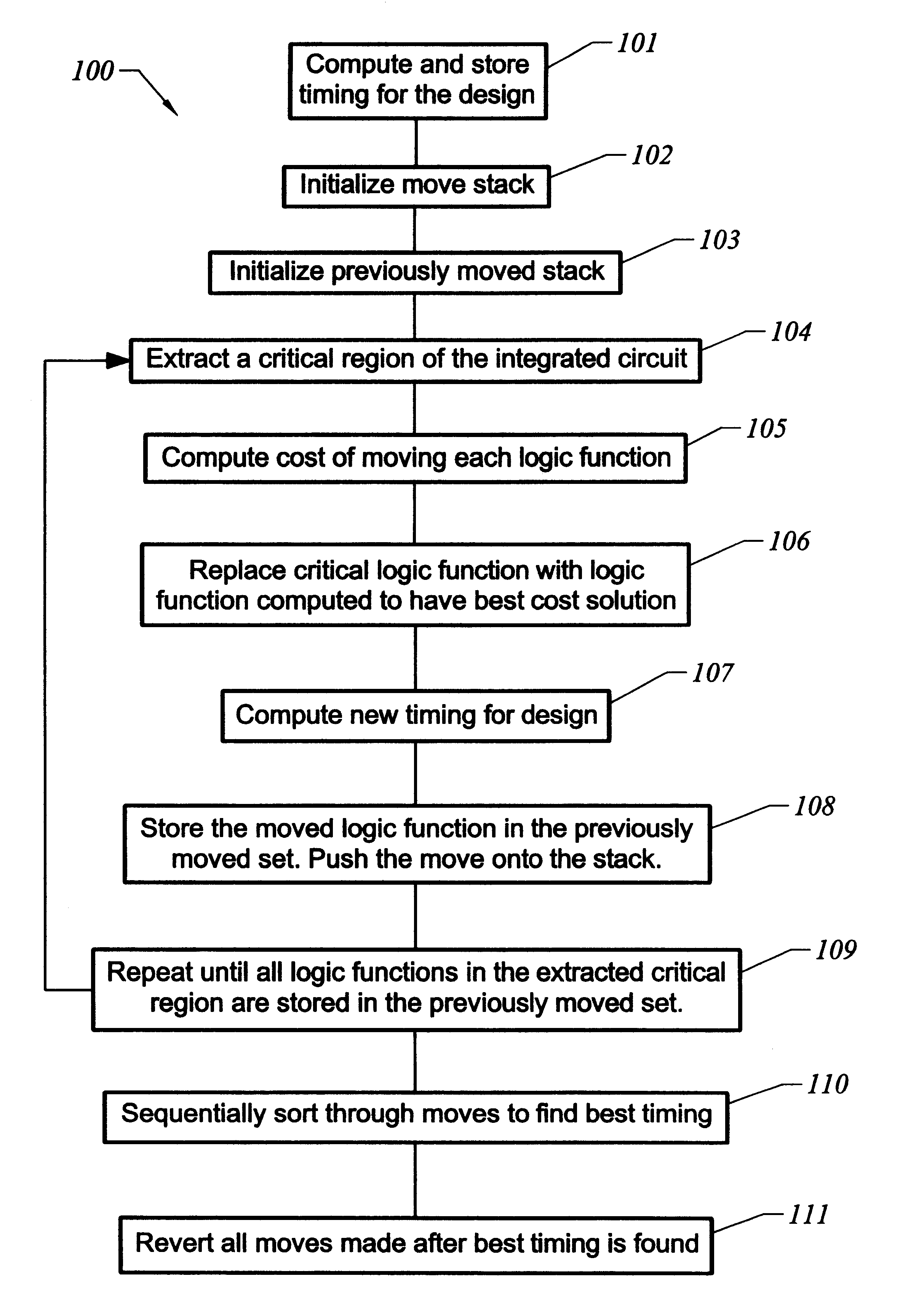

Optimization of combinational logic synthesis through clock latency scheduling

InactiveUS7559040B1Optimize circuit designSimple designComputer aided designSoftware simulation/interpretation/emulationLogic optimizationProcessor register

In optimizing a design of an integrated circuit, an iteration of a logic optimization process is performed that at least partially optimizes a circuit design such that there is slack remaining in one or more combinational logic paths in the circuit design following the iteration. A clock latency scheduling process is performed that respectively distributes the remaining slack of one or more respective combinational logic paths in the circuit design across respective registers in the circuit design. Another iteration of the logic optimization process is performed that uses at least a portion of the distributed slack to further optimize the circuit design.

Owner:CADENCE DESIGN SYST INC

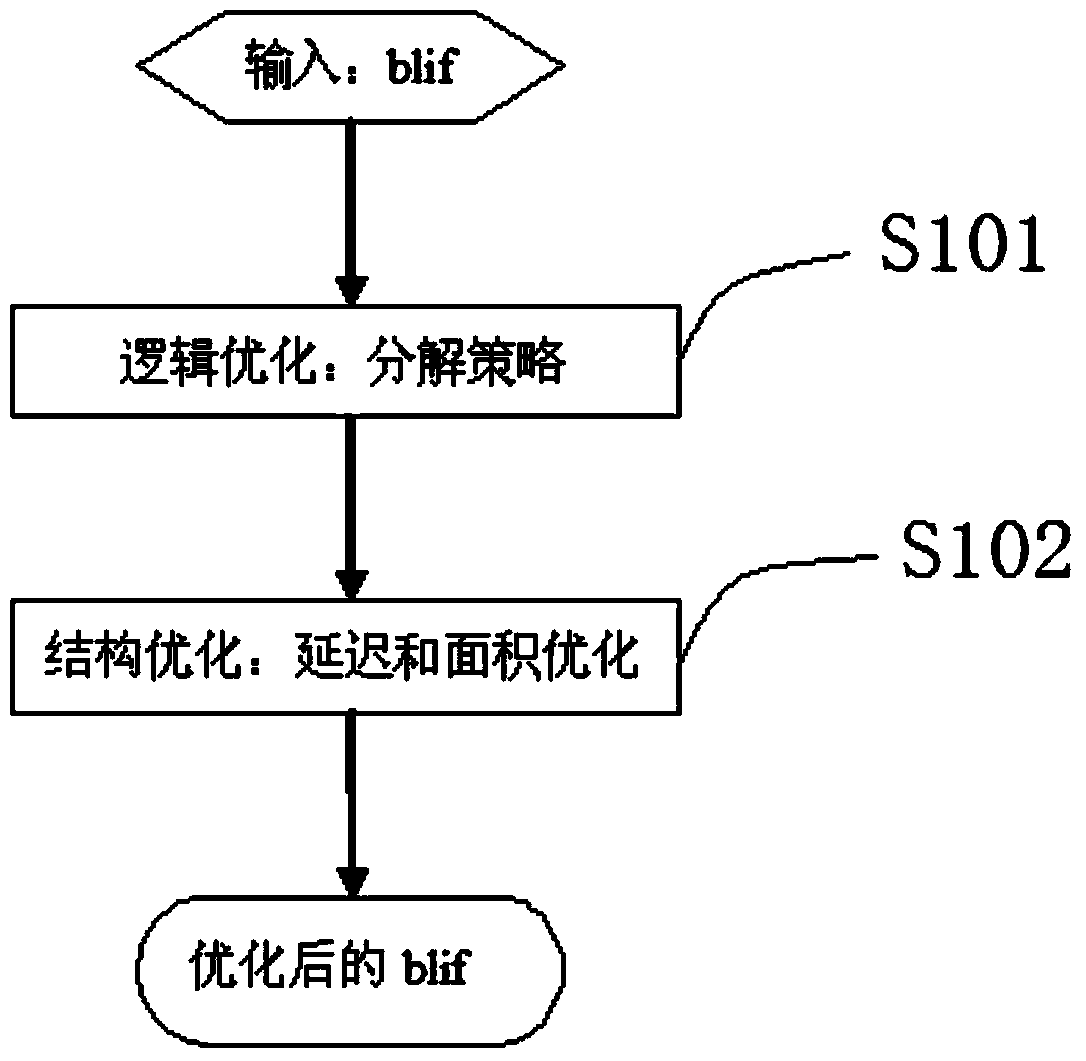

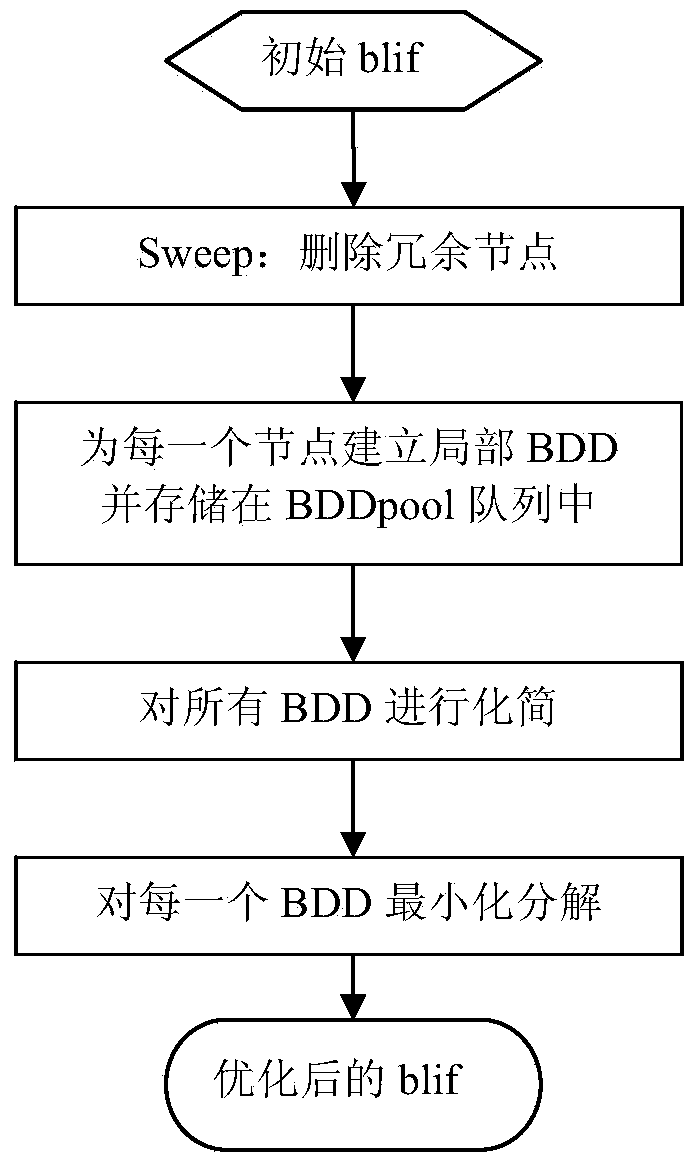

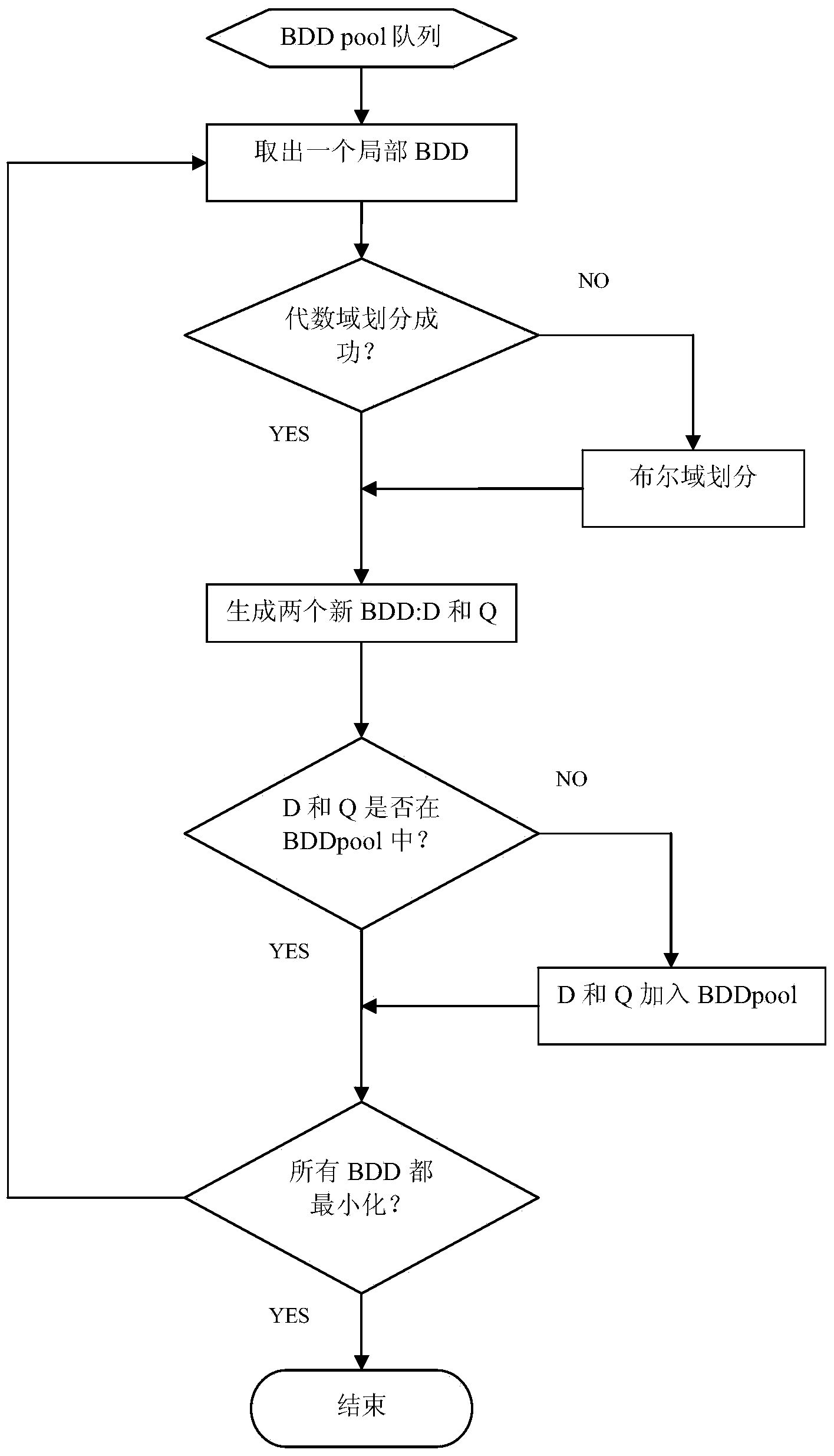

Local minimization ROBDD (reduced ordered binary decision diagram) and area delay optimization based process mapping method

ActiveCN103885771AReduce areaLower latencySpecific program execution arrangementsNODALLogic optimization

The invention discloses a local minimization ROBDD (reduced ordered binary decision diagram) and area delay optimization based process mapping method. The process mapping method includes: generating partial optional partitions through domain nodes of the ROBDD, and loosening node delay on non-critical paths to optimize area. For a logical optimization part, shared data structure of a minimization Local ROBDD is adopted, circuit decomposition efficiency is improved by the aid of domain nodes and operation of the ROBDD, and waste of time and memory due to the fact that all the optional partitions are enumerated is avoided; for a structure optimization part, the idea that a classical algorithm Flowmap is used for delay tag minimization of the nodes of a circuit is improved, min-height min-cost coverage is performed in critical paths, and min-cost coverage is performed in the non-critical paths. The shortcomings of mutual restriction of inefficiency as well as delay with the area of all the generated optional partitions are overcome, requirements of a field-programmable device chip on input number of LUTs (look up table) are met, and the objectives of circuit area and delay optimization can be achieved.

Owner:XIDIAN UNIV

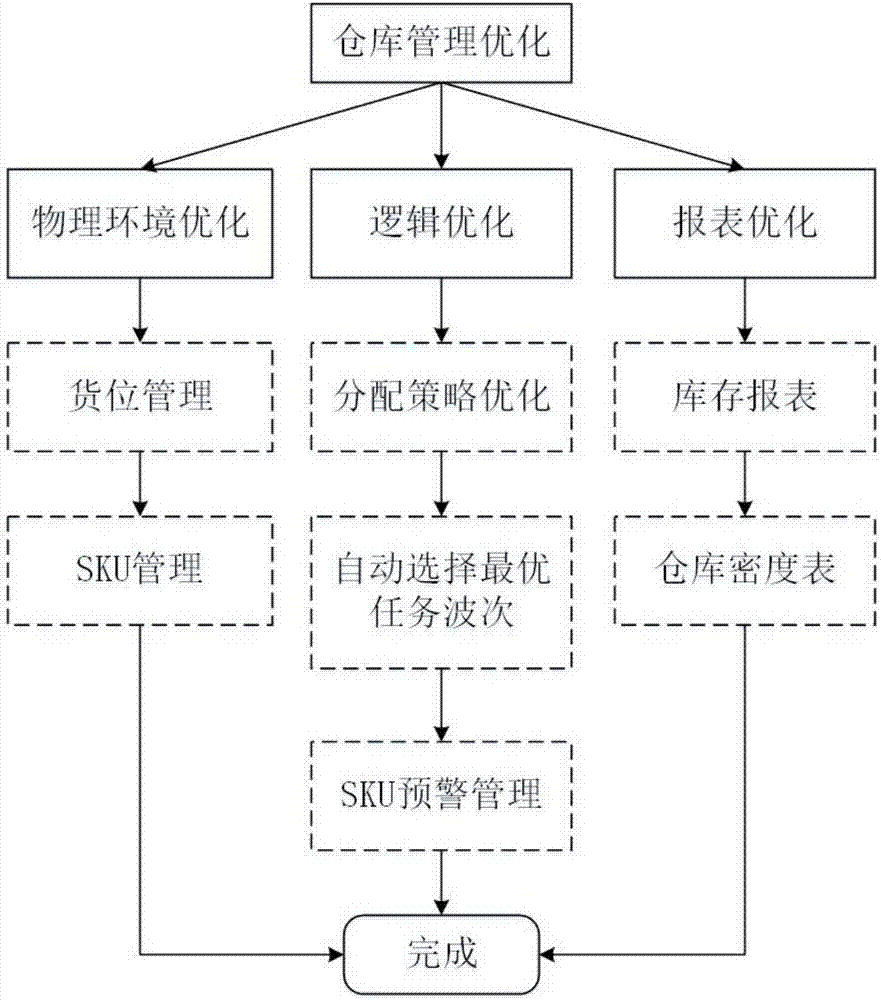

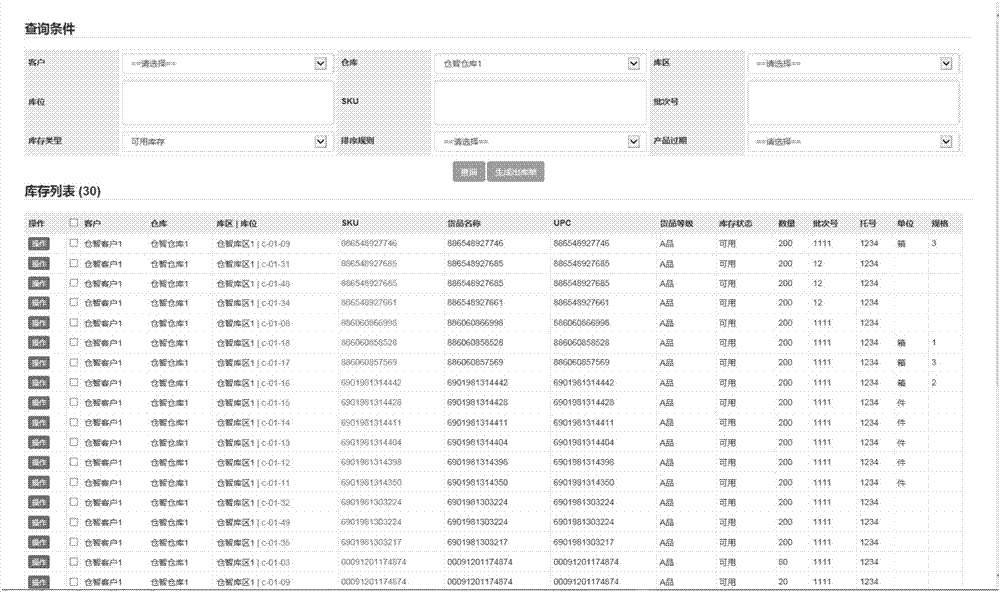

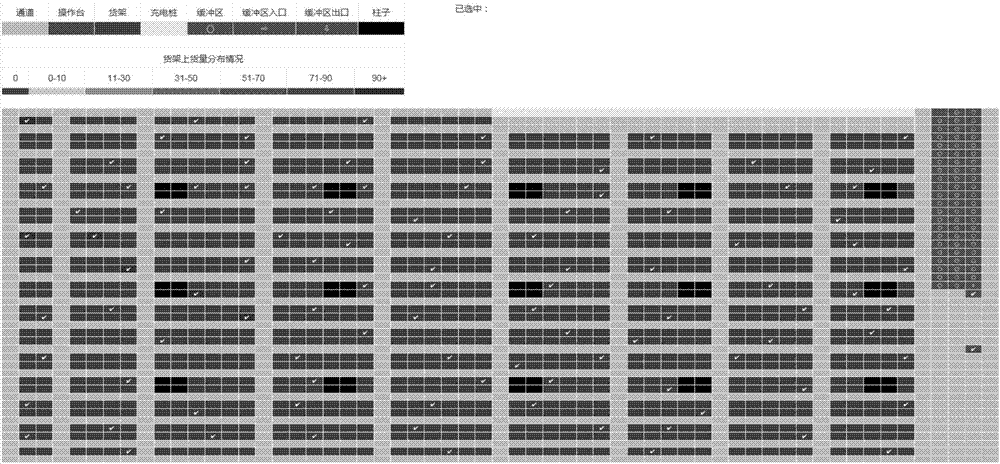

Store management optimization method

The invention discloses a store management optimization method. The store management optimization method comprises the steps of: optimizing the physical environment of cargoes and logistics at first, then, logically optimizing optimized information according to requirements of customers, and finally, making store information into a report to perform report optimization, wherein the physical environment optimization content includes cargo management and SKU logistics management; the logic optimization content includes distribution strategy optimization, automatic selection of an optimal task wave order and SKU forewarning management; and the report optimization content includes an inventory report and a store density table. The invention provides the store management optimization method, which integrates cargo allocation, distribution and loading strategy, transport capacity resource, logistics network and task wave order logistics management optimization algorithms into a whole, and can realize seamless joint with a logistics supply chain information system.

Owner:仓智(上海)智能科技有限公司

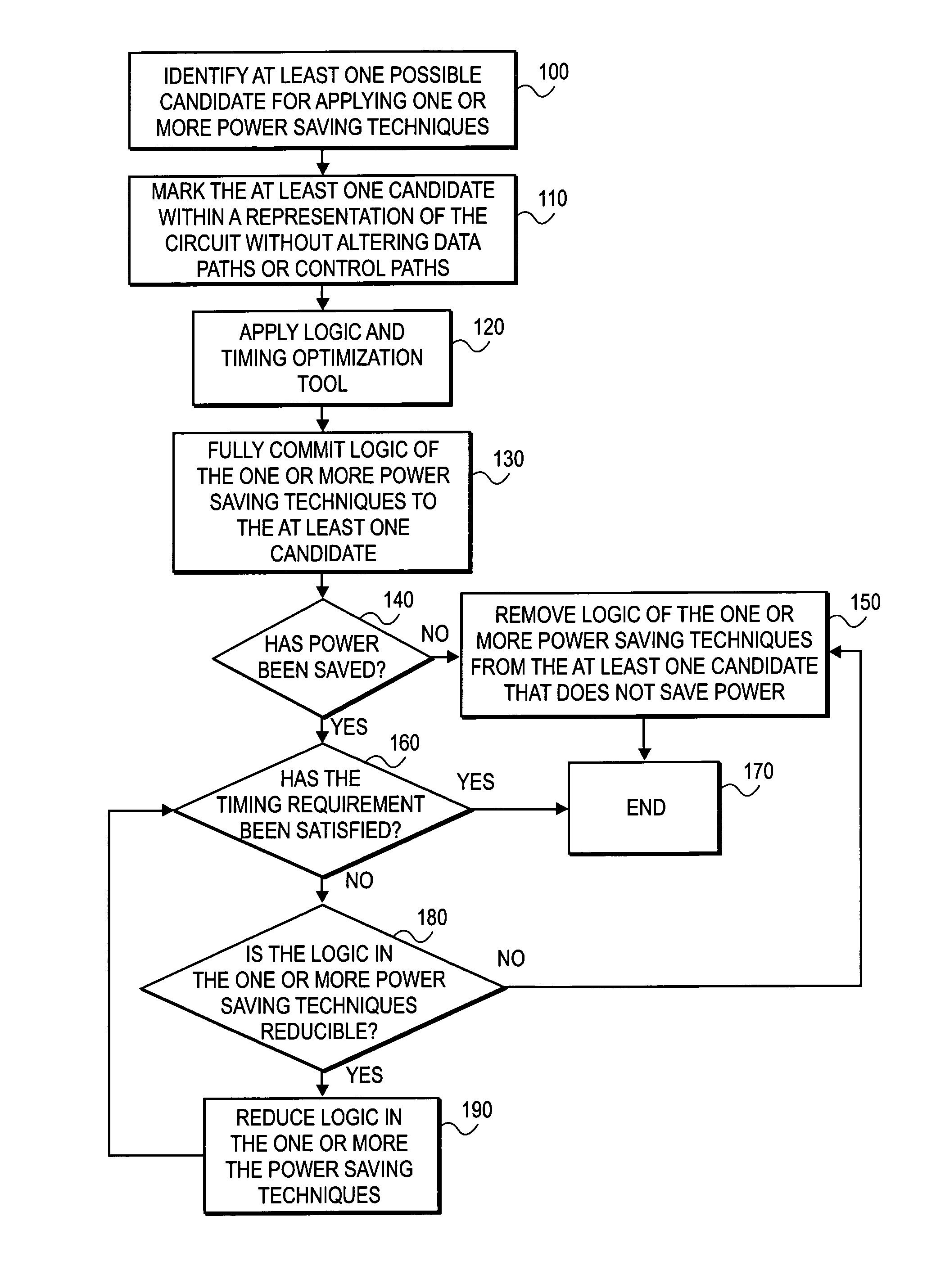

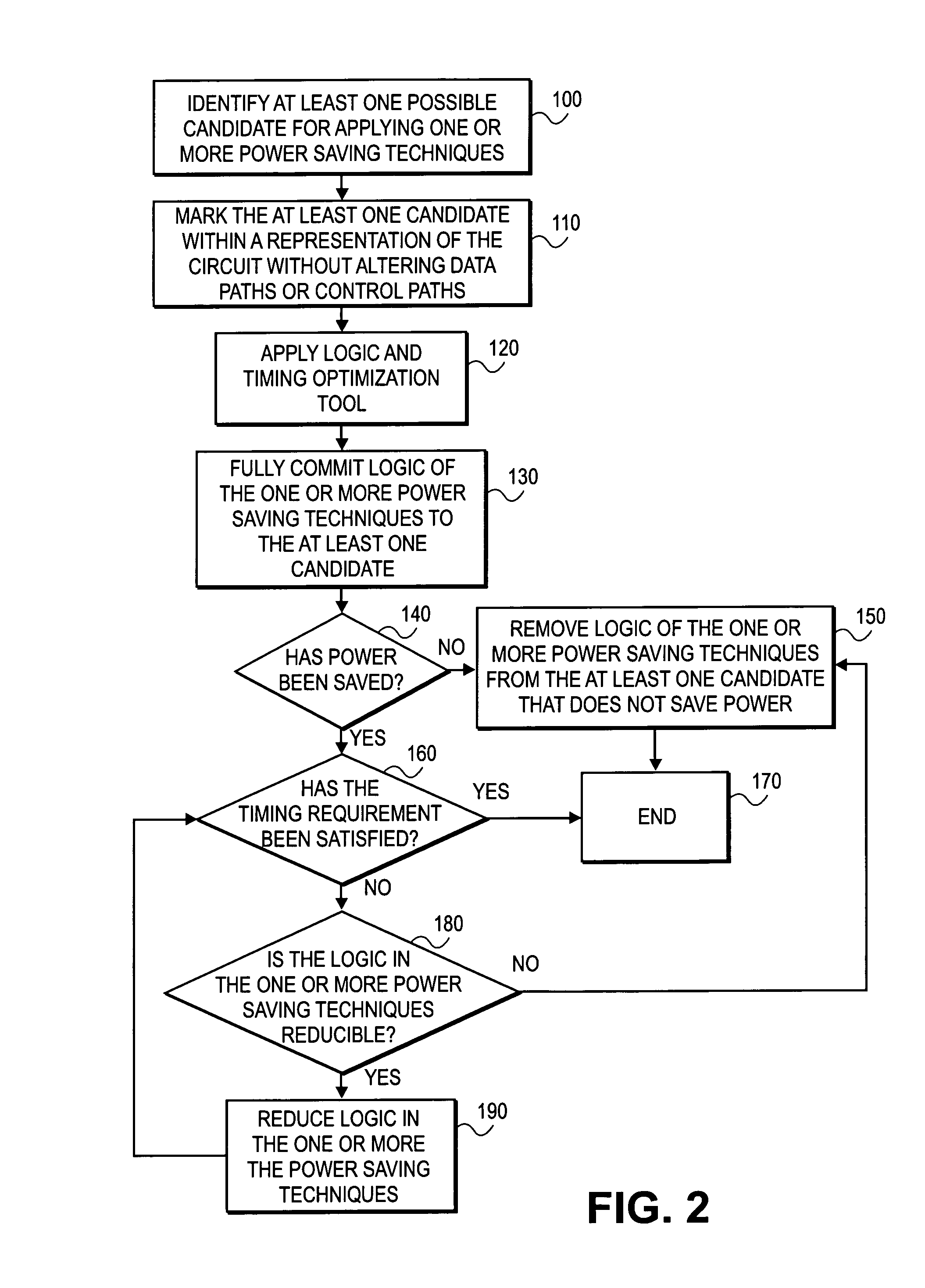

Method and mechanism for RTL power optimization

ActiveUS7007247B1Save substantial amount of powerIncrease powerComputer programmed simultaneously with data introductionCAD circuit designLogic optimizationMicroelectronic circuits

The present invention provides a method and mechanism for optimizing the power consumption of a micro-electronic circuit. According to an embodiment, when optimizing the power consumption of a micro-electronic circuit, one or more candidates for applying one or more optimization techniques may be identified. Then, the one or more candidates may be marked with the one or more optimization techniques within the micro-electronic circuit without altering the data and / or control paths of the circuit. Then, after timing and logic optimization, each power saving technique applied to the one or more candidates may be evaluated to determine whether the technique saves power and / or satisfies the timing requirement of the circuit. Further, each power saving technique applied to the one or more candidates may be evaluated to determine whether the technique is reducible, and if so, then the technique may be reduced to determine whether such reduction improves the circuit's timing.

Owner:CADENCE DESIGN SYST INC

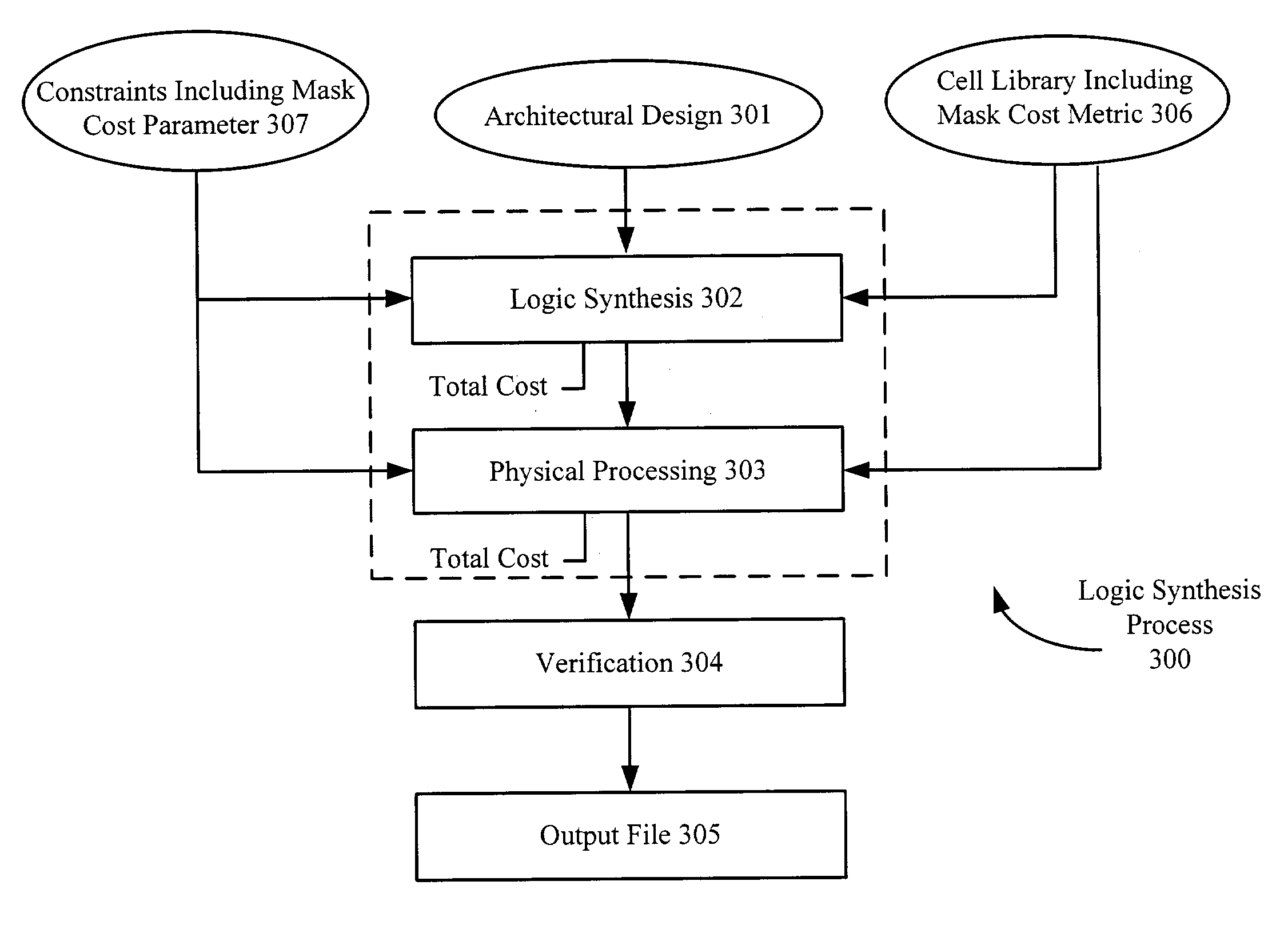

Mask cost driven logic optimization and synthesis

InactiveUS20040210856A1CAD circuit designSpecial data processing applicationsLogic optimizationEngineering

The cost of making a mask set cost has been dramatically increasing due to demand for very small device sizes as well as higher chip complexity. Thus, users would like to minimize the total mask costs. Current logic synthesis tools can create mask designs based on IC characteristics, e.g. speed, area, and power consumption. Therefore, a method of providing a mask design that can be optimized for cost is described. This method includes accessing cells from a library, wherein each cell includes a mask cost metric. Additionally, the weightings of one or more parameters in a constraints listing can be determined. Of importance, at least one parameter relates to mask cost. At this point, logic synthesis can be performed on the design using both the cells and the constraints listing. Advantageously, the resulting synthesized design can be optimized for mask cost.

Owner:SYNOPSYS INC

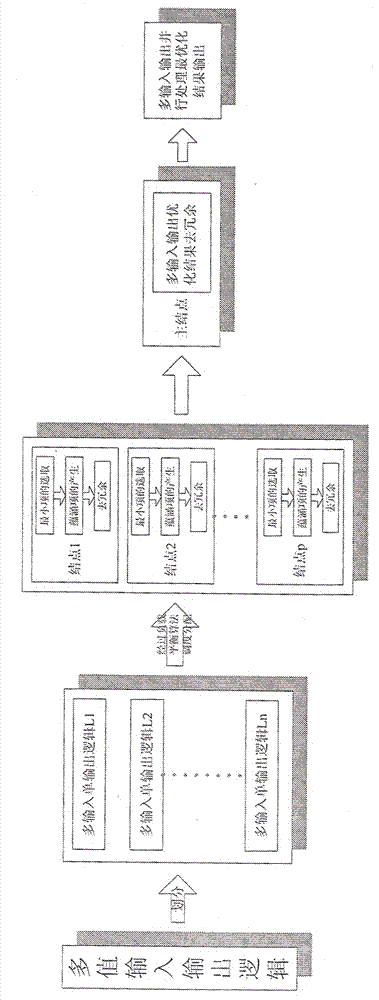

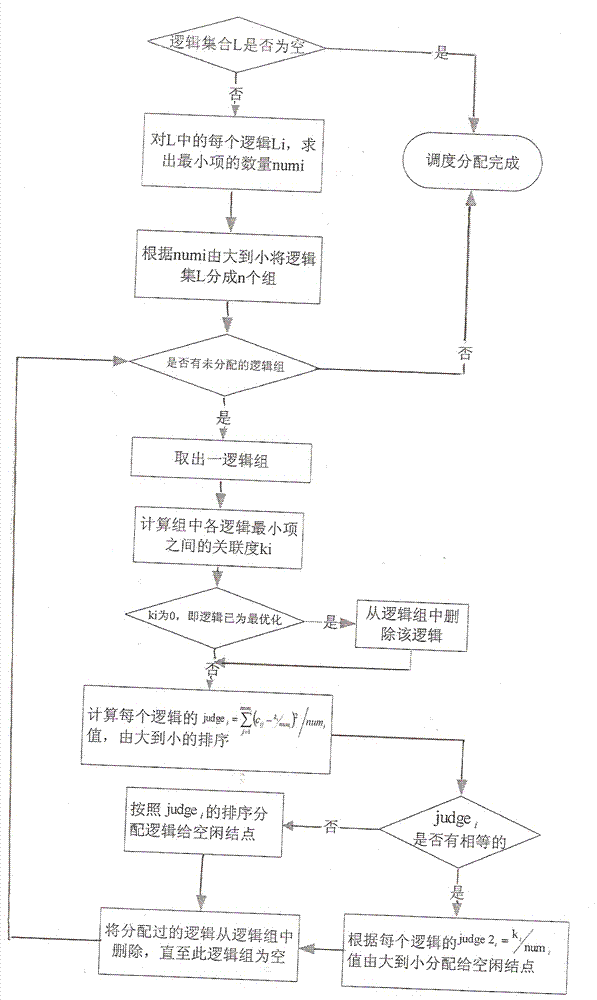

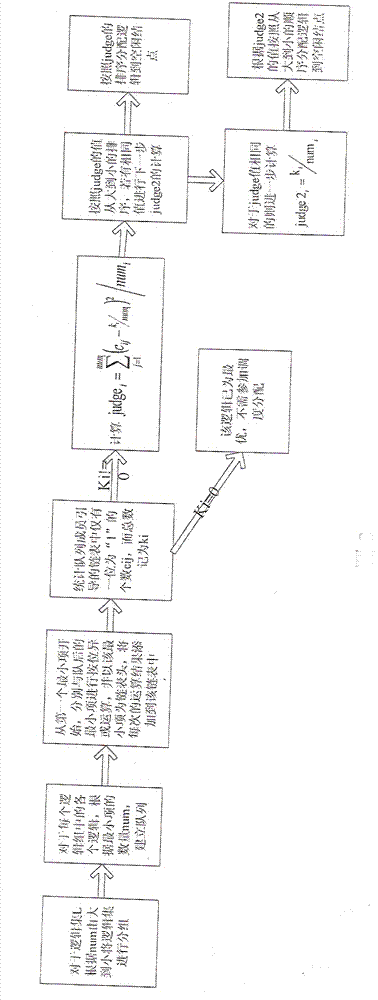

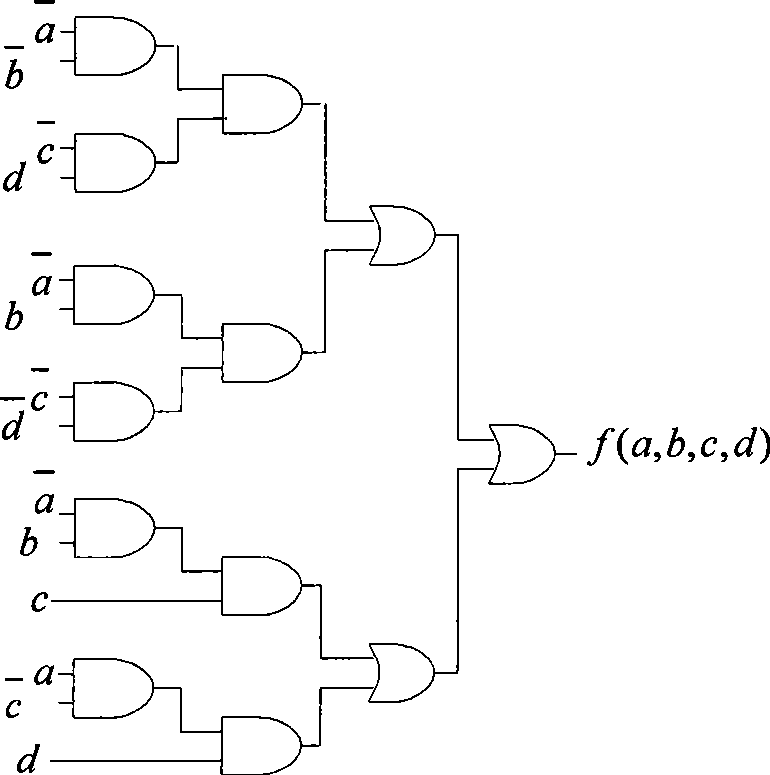

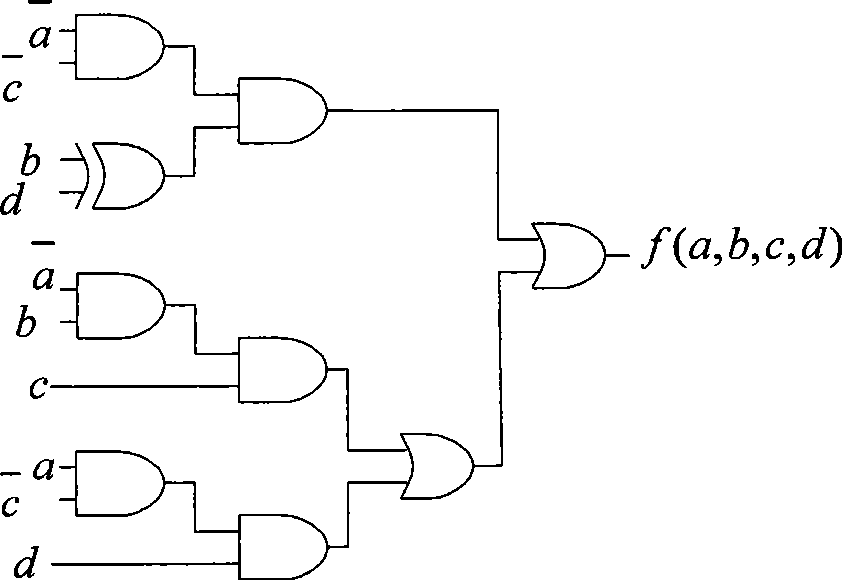

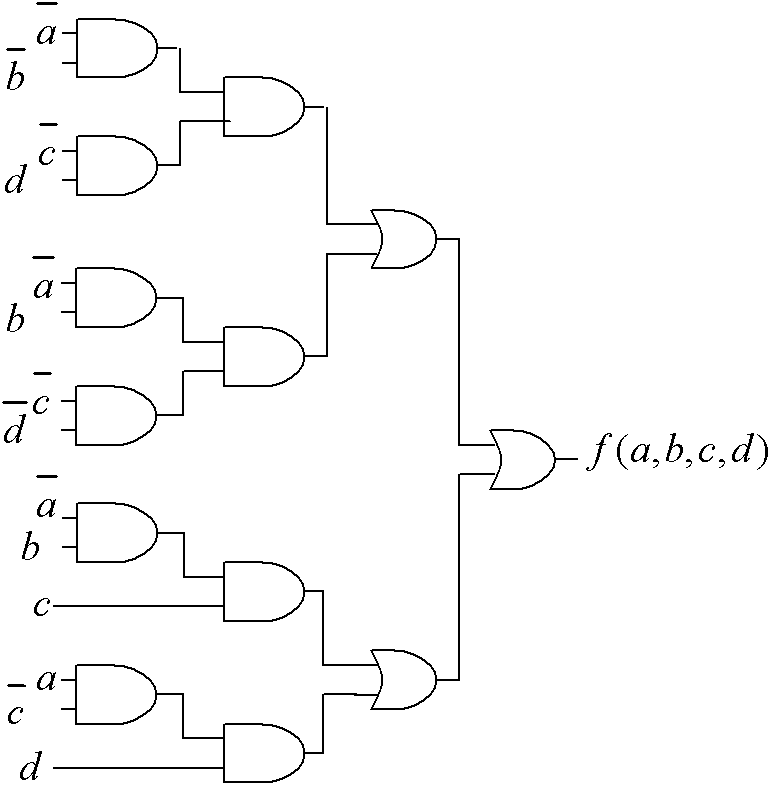

Logic optimizing and parallel processing method of integrated circuit

ActiveCN103034758AImprove processing efficiencyReduce parallel processing timeSpecial data processing applicationsComputer architectureLogic optimization

The invention discloses a logic optimizing and parallel processing method of an integrated circuit. The parallel processing has a function in the logic optimizing that a multiple input and multiple output logic matrix is divided into a plurality of multiple input and single output logic matrixes, and then the multiple input and single output logic matrixes are dispatched to processing nodes to realize optimizing and processing; the optimizing and the processing combine the scale of a logic in the logic optimizing process and the combining probability of implication items in the logic, so as to form a parallel processing dispatching algorithm; the dispatching process of the logic optimizing and the parallel processing is divided into sections, and the inside of each section follows the logic with longer priority dispatching and processing time; and a distribution strategy is adopted in the logic optimizing and parallel processing of the integrated circuit. The logic optimizing and parallel processing method has the advantage that according to the number of the implication items in a logic function of the integrated circuit and the correlation degree of the implication items, the processing efficiency of the logic optimizing of the integrated circuit can be improved.

Owner:江苏博沃汽车电子系统有限公司

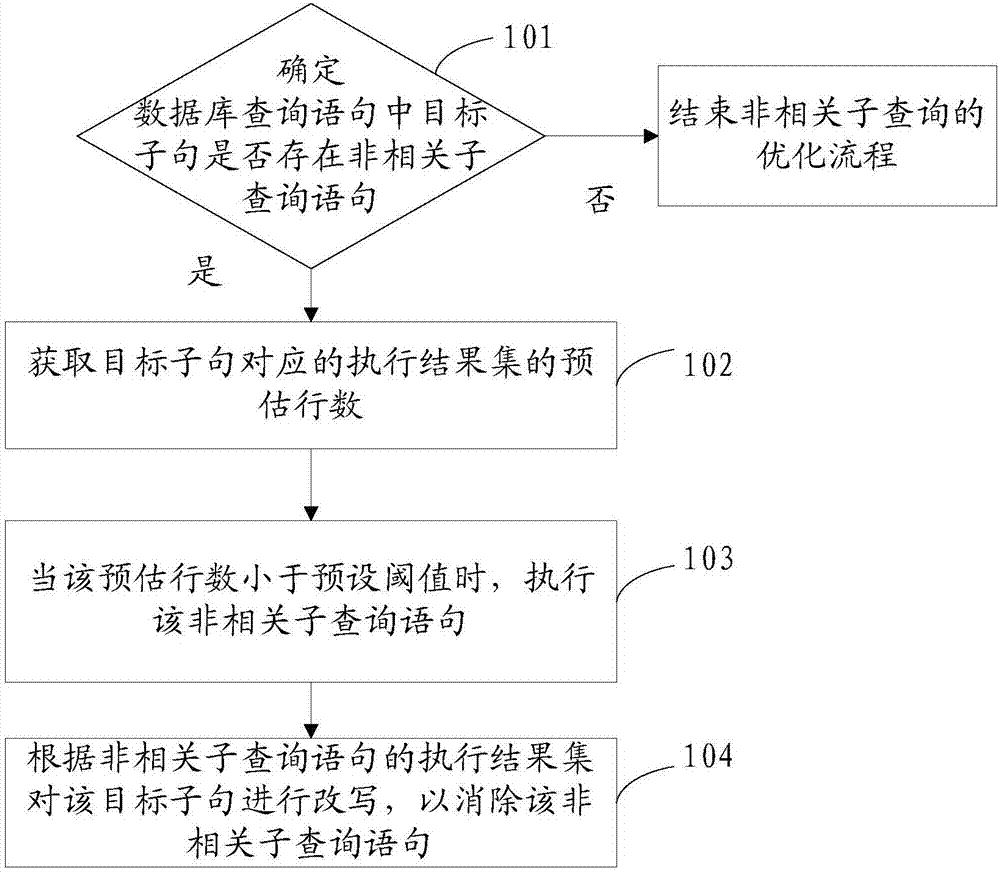

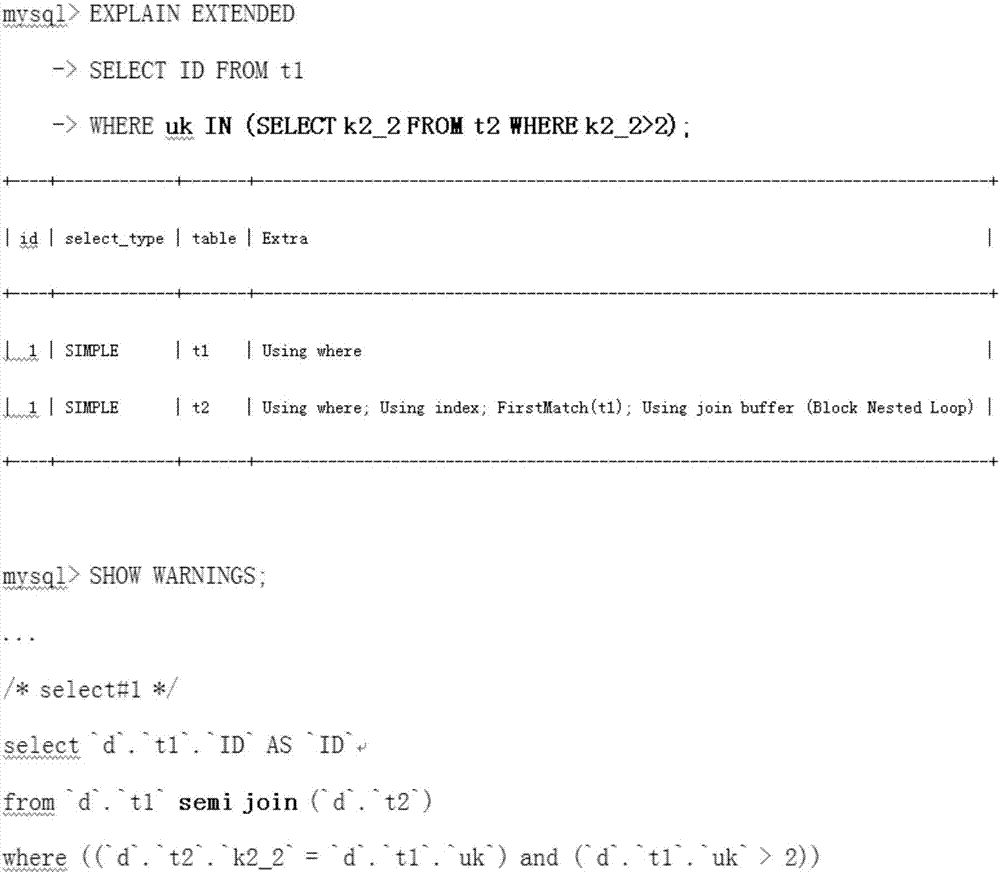

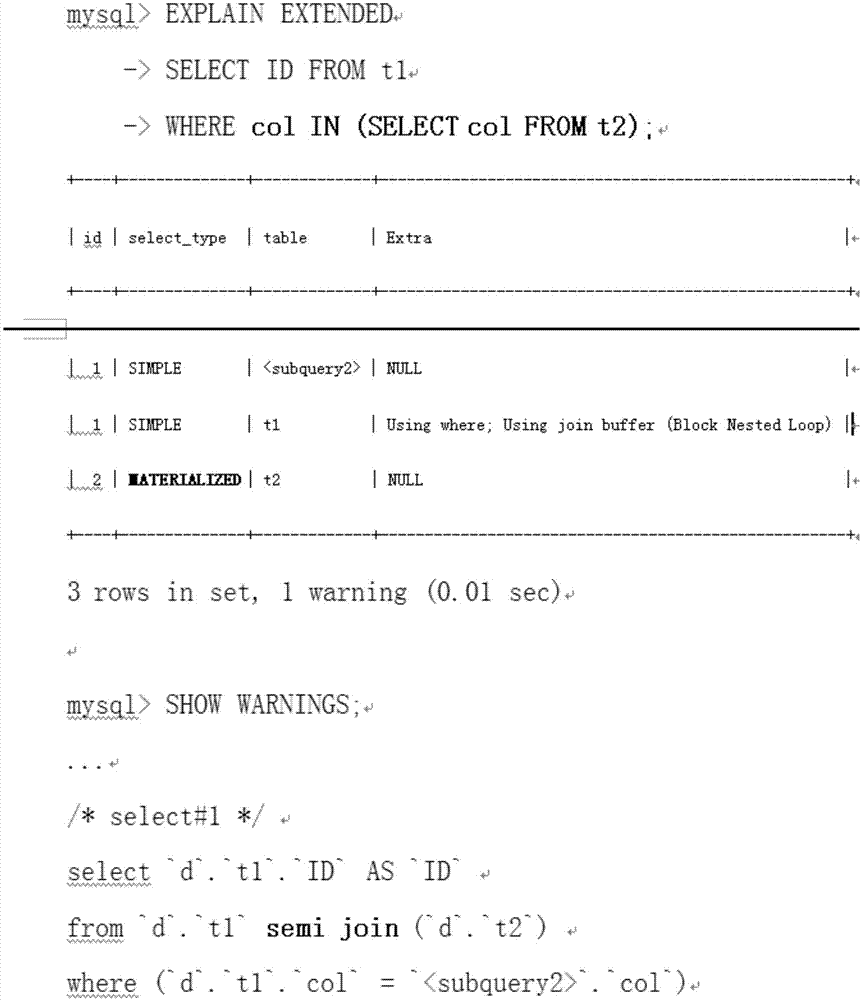

Optimization method and device of non-correlator inquiry

ActiveCN107315790AReduced execution timeImprove execution efficiencySpecial data processing applicationsLogic optimizationAlgorithm

The embodiment of the invention discloses an optimization method and device of non-correlator inquiry. According to the embodiment, whether a non-correlator inquiry sentence exists in a target sub sentence in a database inquiry sentence or not is determined; if the non-correlator inquiry sentence exists, the estimated row number of an execution result set corresponding to the target sub sentence is obtained; when the estimated row number is smaller than a preset threshold value, the non-correlator inquiry sentence is executed to obtain the execution result set; and the target sub sentence is modified according to the execution result set so as to eliminate the non-correlator inquiry sentence. By using the scheme, the non-correlator inquiry sentence can be executed in advance before the sentence execution stage such as in the logic optimization stage; the located target sub sentence of the non-correlator inquiry sentence is modified according to the execution result so as to eliminate the non-correlator inquiry, so that the relevant inquiry and access on any non-correlator inquiry sentence are not needed in the subsequent sentence execution stage; and the execution efficiency of the database inquiry sentence with the non-correlator inquiry can be improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

Methods for automatically generating assertions

ActiveUS7926020B1Detecting faulty computer hardwareCAD circuit designLogic optimizationTheoretical computer science

One embodiment of the present invention provides a method that automatically generates assertions of a hardware design. The method includes accessing a trace and a set of predicates of the hardware design. Then, the trace is projected over the set of predicates to generate a second trace. Then, a new set of states of the second trace is computed and the result is represented as a logical formula. The formula is reduced by logic optimization techniques. And finally, a set of logical consequences of the logic formula is produced and each logical consequence is enumerated as an assertion.

Owner:SYNOPSYS INC

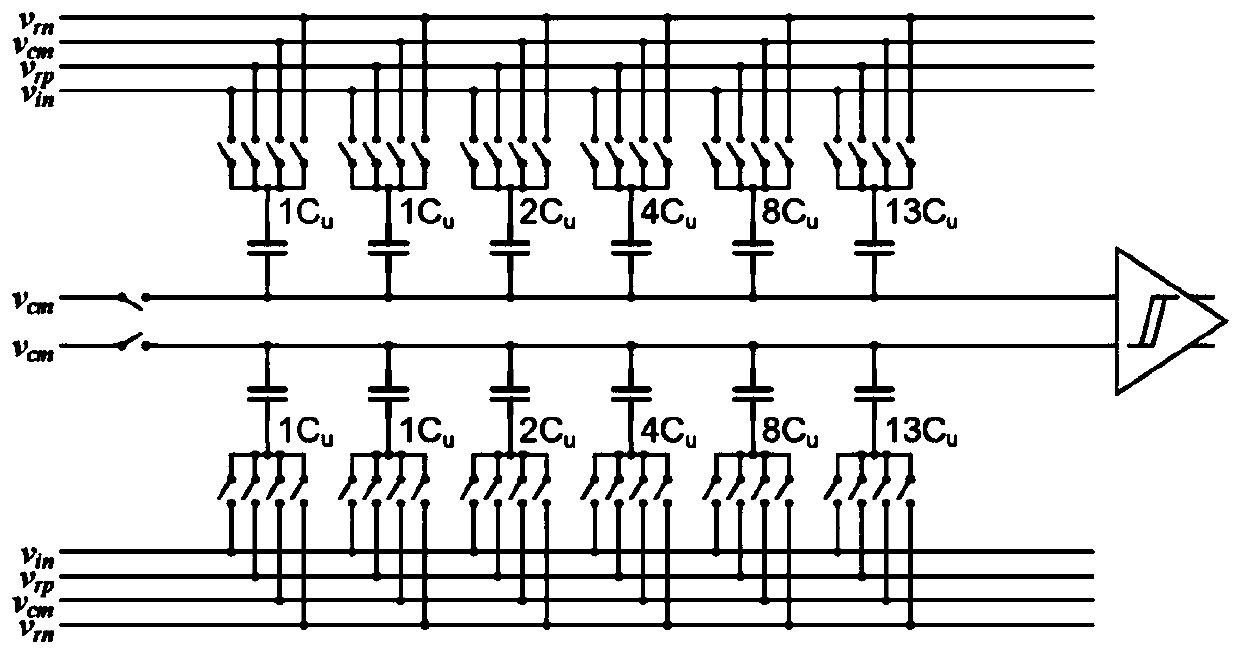

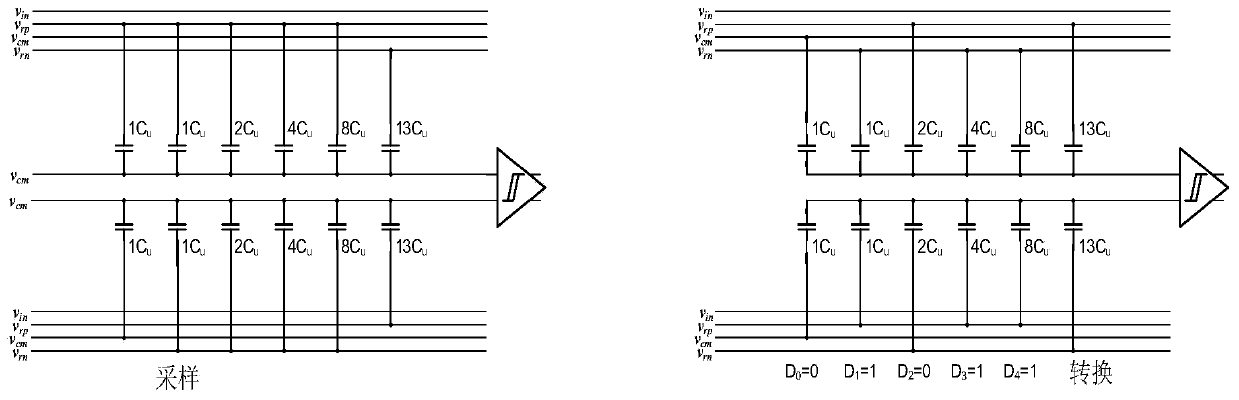

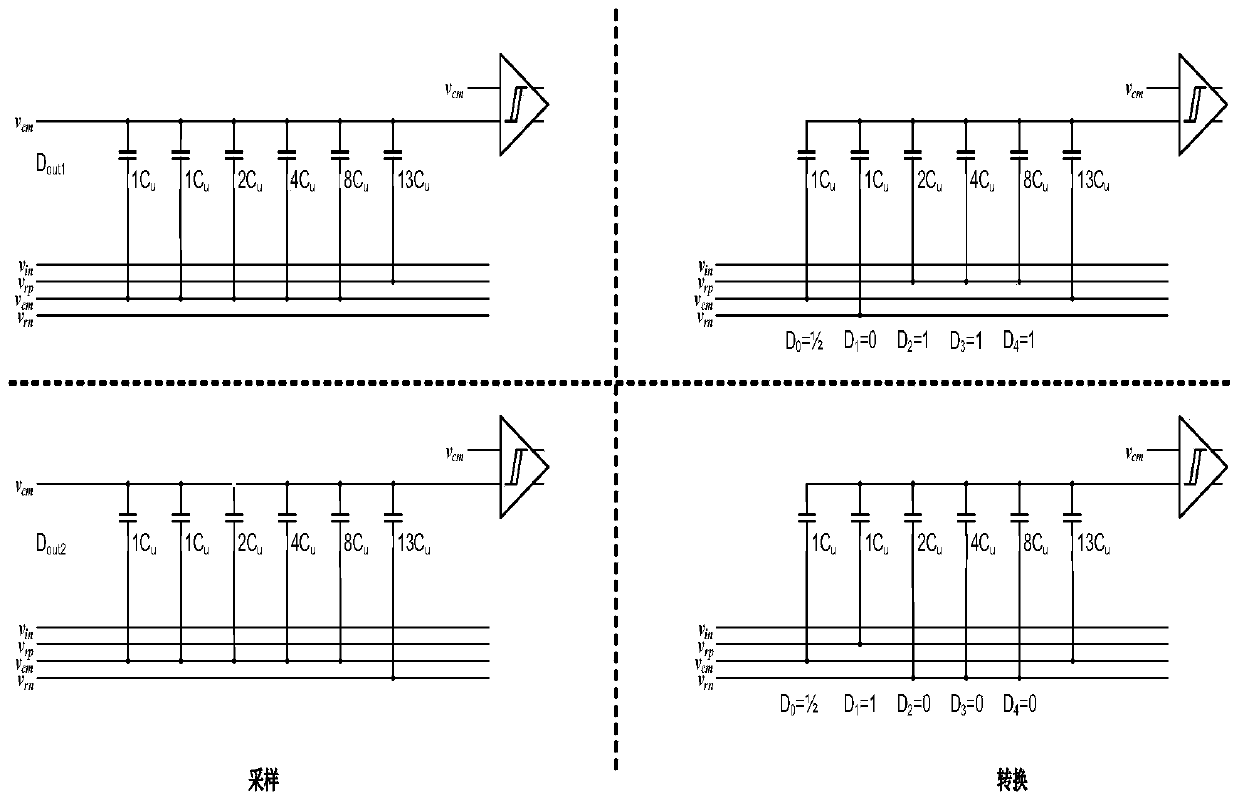

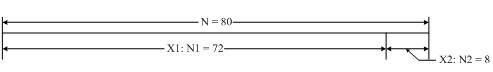

Weight calibration method of non-binary successive approximation type analog-digital converter

ActiveCN110086468AImprove conversion accuracySimplify digital logicElectric signal transmission systemsAnalogue/digital conversion calibration/testingCapacitanceLogic optimization

The invention discloses a weight calibration method for a non-binary successive approximation type analog-digital converter, the non-binary successive approximation type analog-digital converter comprises a capacitor array and a virtual capacitor C0, the capacitor array comprises n capacitors, and n capacitor values from the largest to the smallest are Cn, Cn-1, Cn-2, Cn-3 toC1, and C1 is equal toC. According to the weight calibration calculation method of the mth capacitor, the redundant weight Rm of the mth capacitor is larger than 0, and the mth capacitor refers to the mth capacitor with the capacitance value from low to high in the capacitor array. The invention provides a weight calibration method for the non-binary successive approximation type analog-to-digital converter. Sequential control logic optimization is carried out on sampling and conversion process so that the digital logic of the calibration algorithm is simplified, only the accumulation average process is carried out. Meanwhile, the method has a faster operation result, and only one quantization error is introduced when noise is small.

Owner:CHENGDU LIGHT COLLECTOR TECH

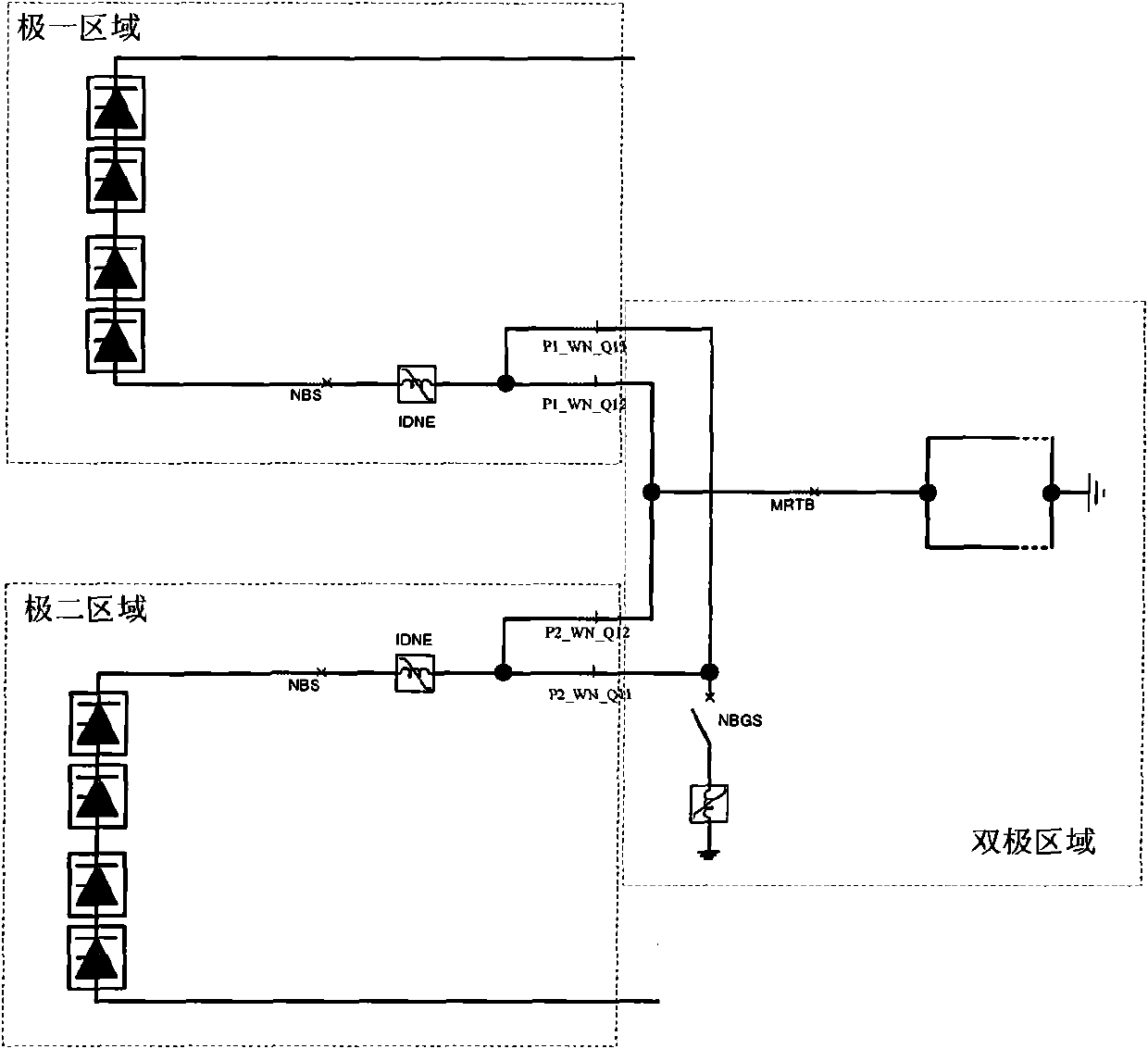

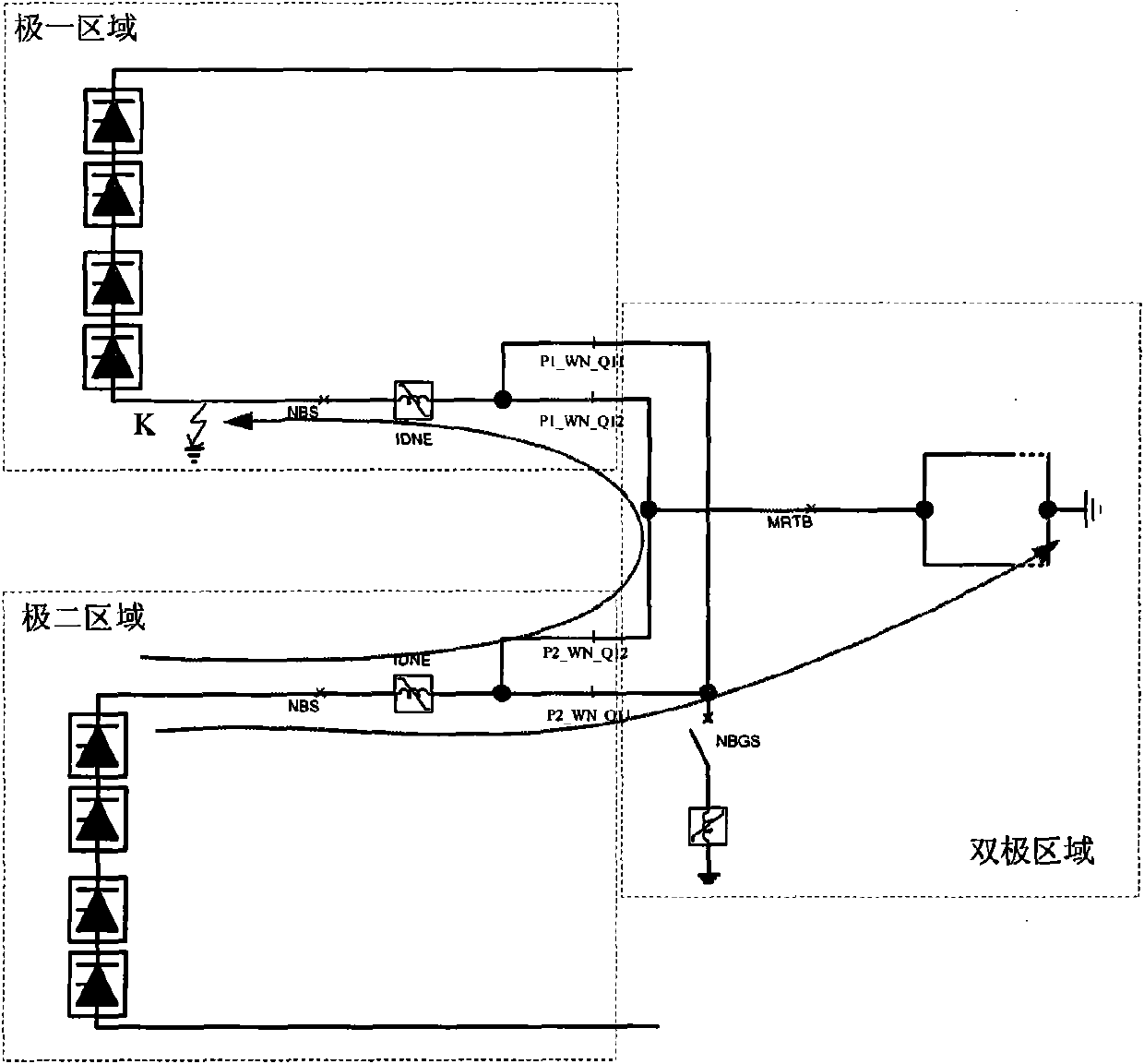

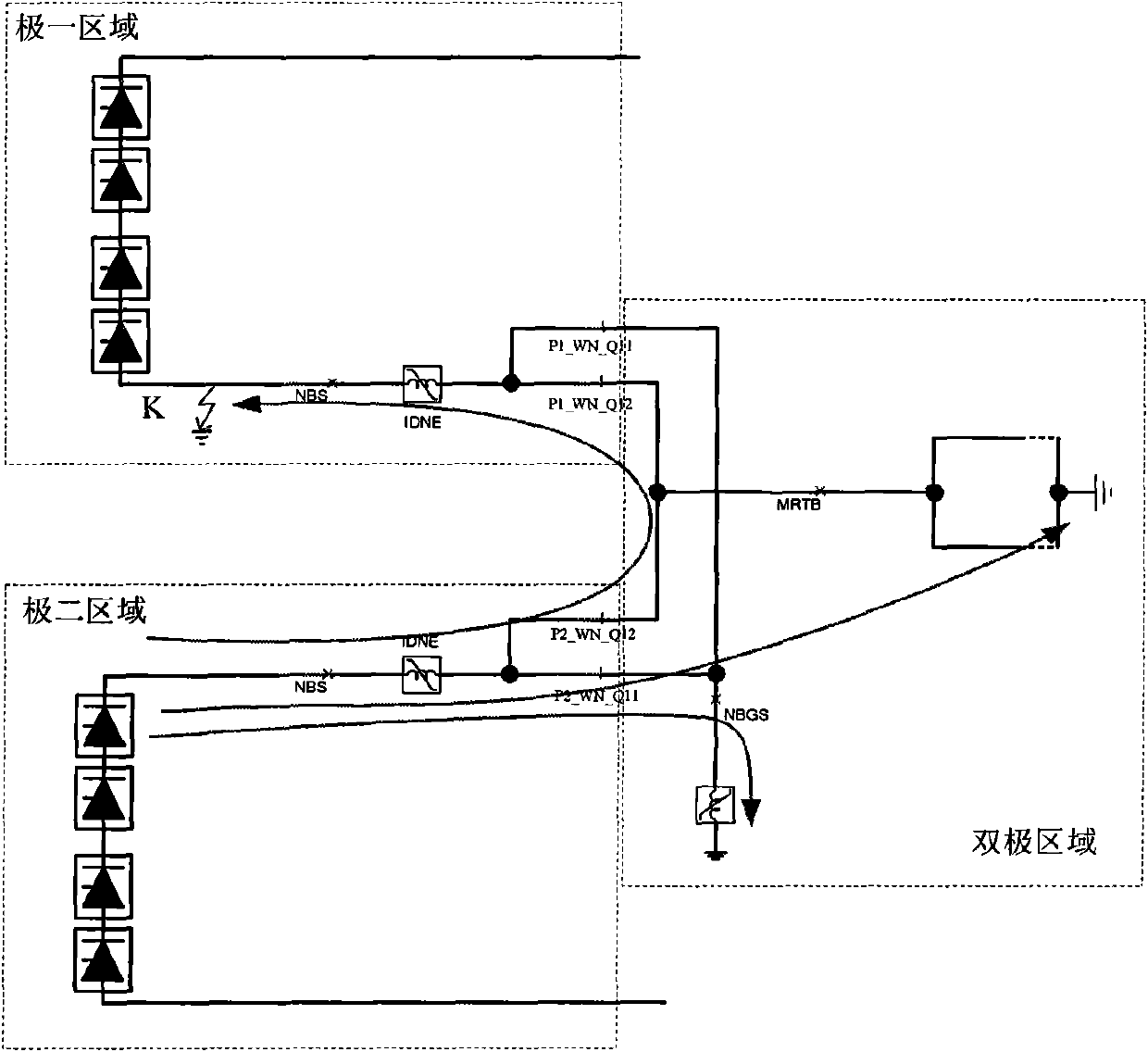

Method for carrying out failure protection and logic optimization on UHVDC (Ultra-High Voltage Direct Current) neutral bus switch

The invention discloses a method for carrying out failure protection and logic optimization on a UHVDC (Ultra-High Voltage Direct Current) neutral bus switch. In the operating process of double poles, once the neutral bus switch of a failure pole fails, firstly the operation of detecting whether a basis pole isolation signal exists is carried out, the operation is completed if the basis pole isolation signal does not exist, and the following steps are carried out if the basis pole isolation signal exists: 1, sending a command to make the neutral bus switch coincided and locked; 2, switching off an instation neutral bus earthed switch; 3, separating an isolation switch near the neutral bus switch of the failure pole; and 4, after the isolation switch is separated and is in place, switching off the instation earthed switch. After the processing method is adopted, when the neutral bus switch fails, the failure pole can still be isolated, so that the operation stoppage of the double poles is effectively avoided.

Owner:NR ELECTRIC CO LTD +1

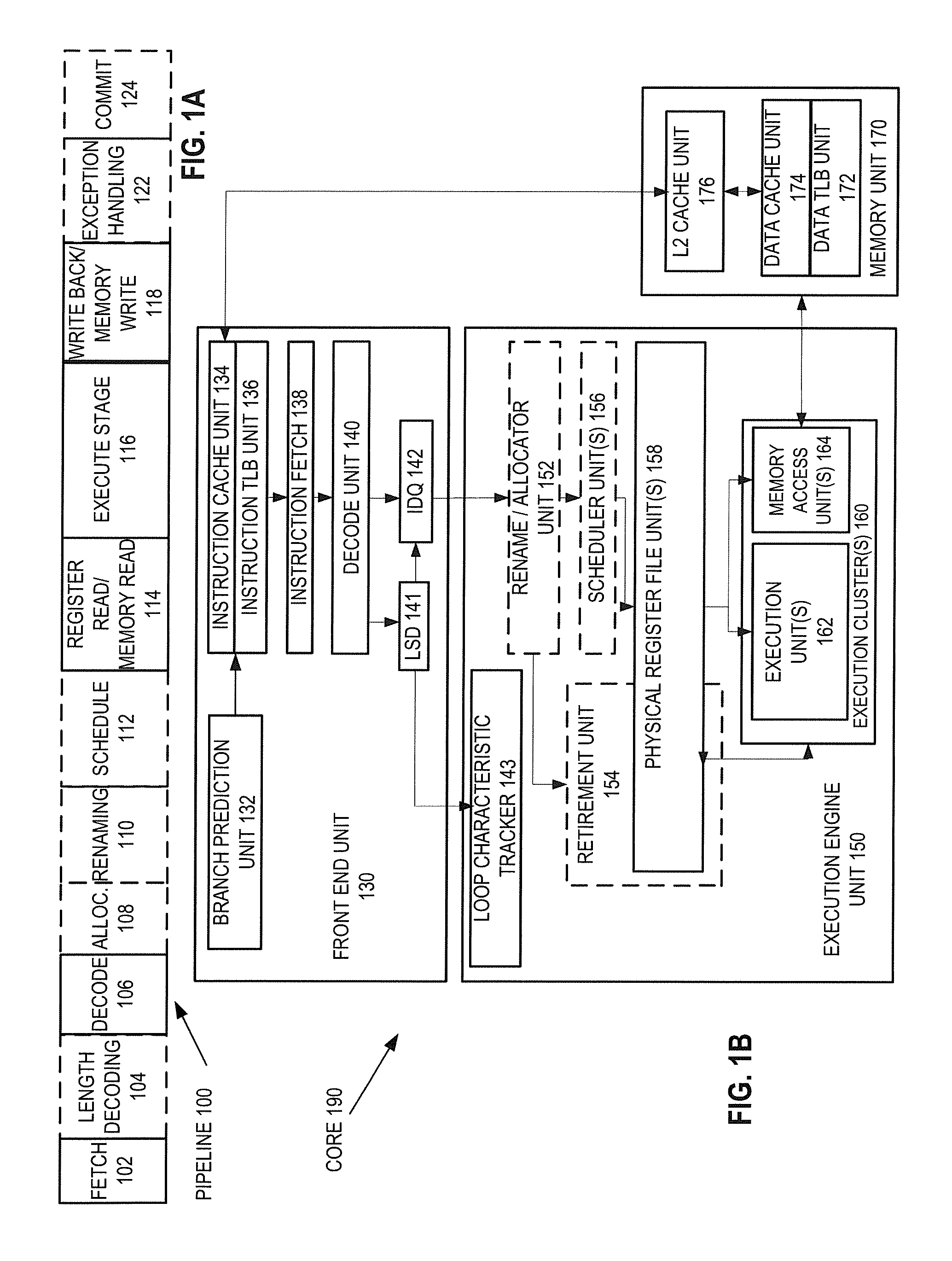

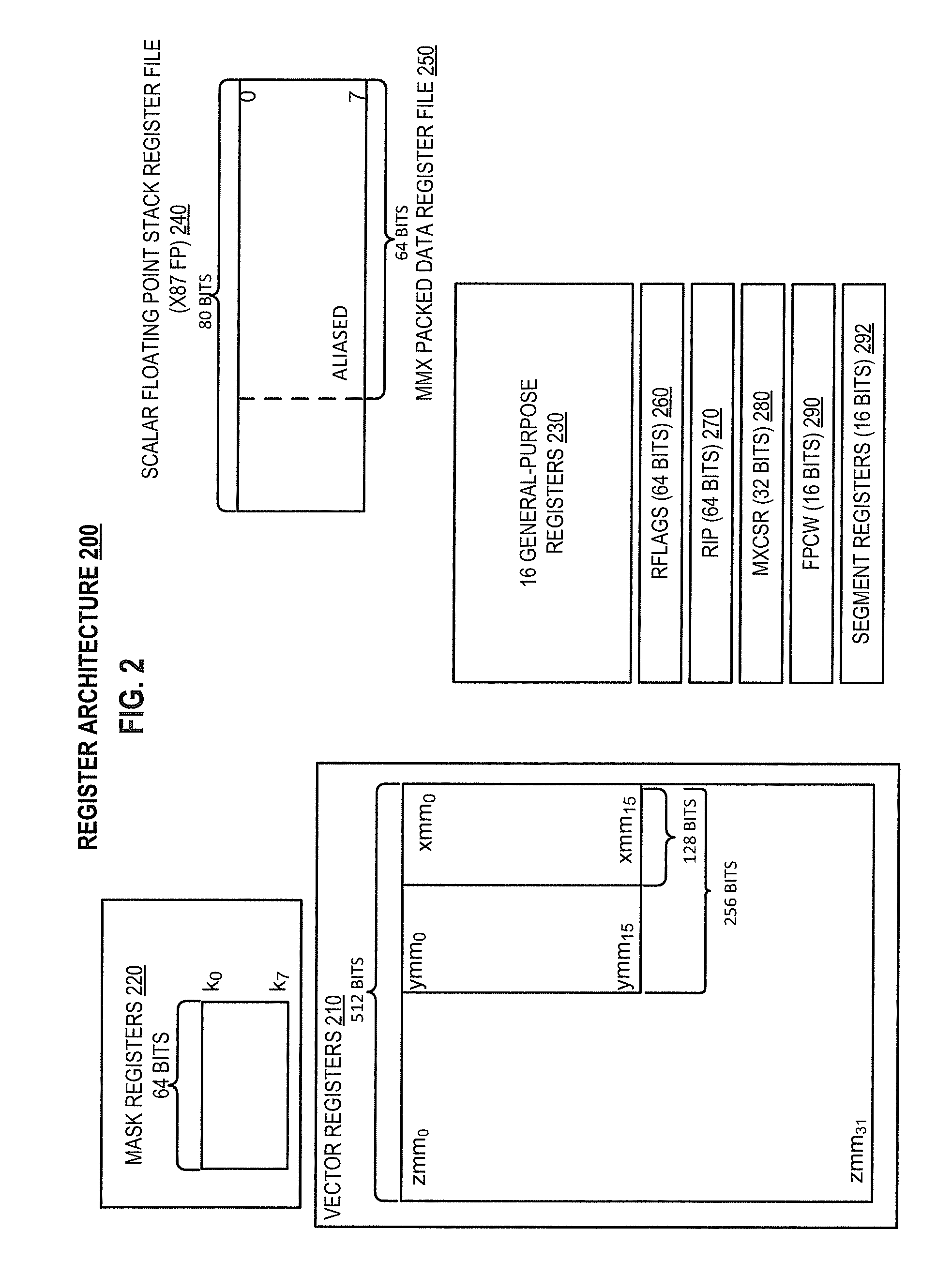

Enhanced loop streaming detector to drive logic optimization

ActiveUS20140189306A1Digital data processing detailsDigital computer detailsMicro-operationLogic optimization

An enhanced loop streaming detection mechanism is provided in a processor to reduce power consumption. The processor includes a decoder to decode instructions in a loop into micro-operations, and a loop streaming detector to detect the presence of the loop in the micro-operations. The processor also includes a loop characteristic tracker unit to identify hardware components downstream from the decoder that are not to be used by the micro-operations in the loop, and to disable the identified hardware components. The processor also includes execution circuitry to execute the micro-operations in the loop with the identified hardware components disabled.

Owner:INTEL CORP

Method for reducing area of digital logic circuit

InactiveCN101488745AReduce areaLogic circuits using elementary logic circuit componentsLogic optimizationTheoretical computer science

The invention discloses a method for reducing the area of a digital logical circuit; a specific product term is generated and added in an optimized function by using characteristics of exclusive OR operation 1 OR 1=0; as the new product term is added, original logically nonadjacent product terms become logically adjacent due to the inserting of added items so as to realize logic optimization; the advantages are as follows: two product terms do not constitute an OR expression right now but an added item p is firstly generated after the two product terms are judged to have a broad hamming distance of 2, and then whether the added item p is fit for simplification of function is judged by a corresponding evaluation method. As the complexity of the logic function is closely related with the complexity of the corresponding digital circuit, simple logic function always corresponds to smaller circuit area, thereby achieving the purpose of reducing the area of digital logic circuit by a method for simplifying the logic function.

Owner:NINGBO UNIV

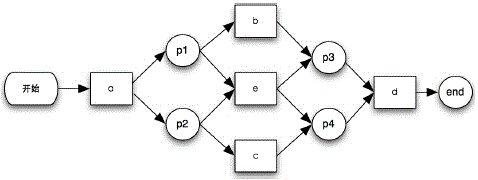

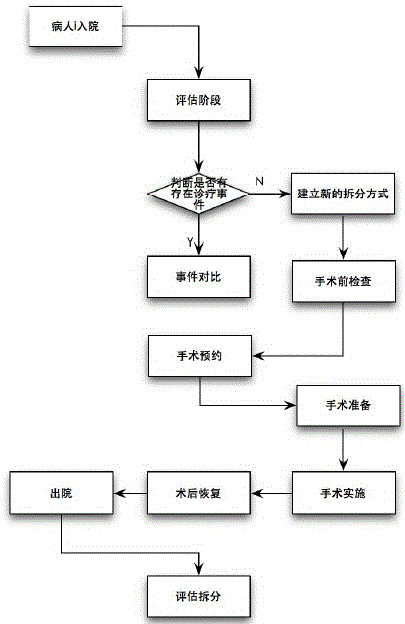

Process mining method based on single-disease treatment process

InactiveCN105005709AAccurate flowShorter hospital staySpecial data processing applicationsLogic optimizationAlgorithm

The invention provides a process mining method based on a single-disease treatment process. According to the method, a series of logic optimization algorithms such as association rules, a genetic algorithm, an EM (expectation maximum) algorithm and the like are used for determining a core even item of a treatment process, then case samples are used for connecting scattered points occurring on a treatment path for drawing, a treatment path diagram is obtained through a connected graph after historical case sample drawing, then each event node on the treatment path diagram is expanded, a complete treatment event item set is formed, and the cost interval for each treatment event item set is estimated and a treatment event sequence of the whole treatment process is given; the mined treatment event sequence is subjected to rationality verification and evaluation, and the path is disassembled effectively.

Owner:赵蒙海

Method for reducing area of digital logic circuit

InactiveCN102185606AReduce areaLogic circuits using elementary logic circuit componentsLogic optimizationTheoretical computer science

The invention discloses a method for reducing area of a digital logic circuit. By utilizing the characteristic of xor operation, a specified product term is generated and added into the optimized function; owning to the adding of the new product term, the original product term with nonadjacent logics becomes logically adjacent owning to the interposing of the product term, thus realizing logic optimization; the method has the advantages that after the existence of two product terms with the generalized hamming distance of 2 is judged, the two product terms do not form an xor expression immediately; a corresponding addition term is generated; and subsequently whether the addition term is suitable for function simplification is judged by a corresponding evaluation method. As the complexity of the logic function is related to the complexity of the corresponding digital circuit, the simple logic function always corresponds to a smaller circuit area; and the aim of reducing the area of digital logic circuit can be achieved by the method of simplifying logic function.

Owner:NINGBO UNIV

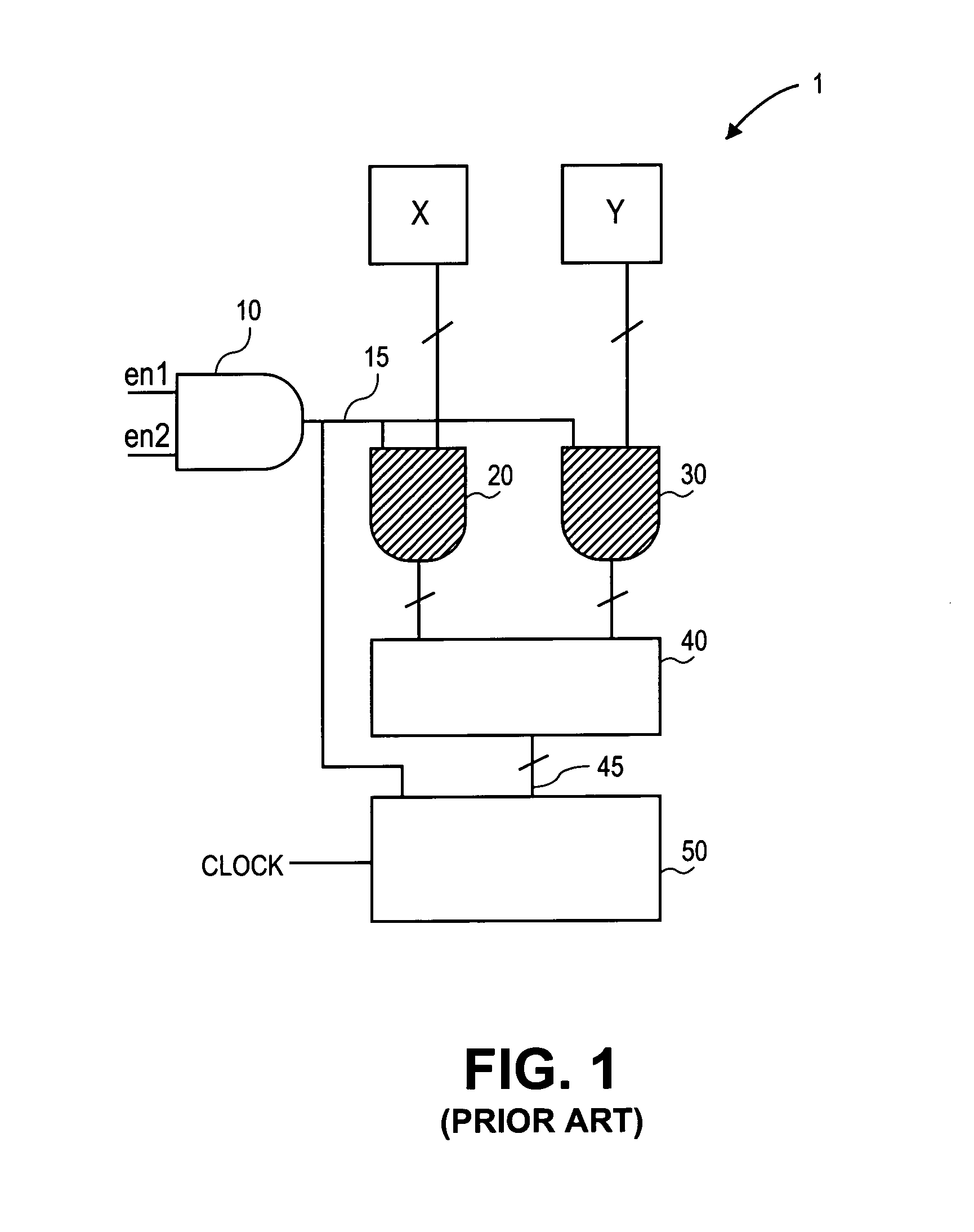

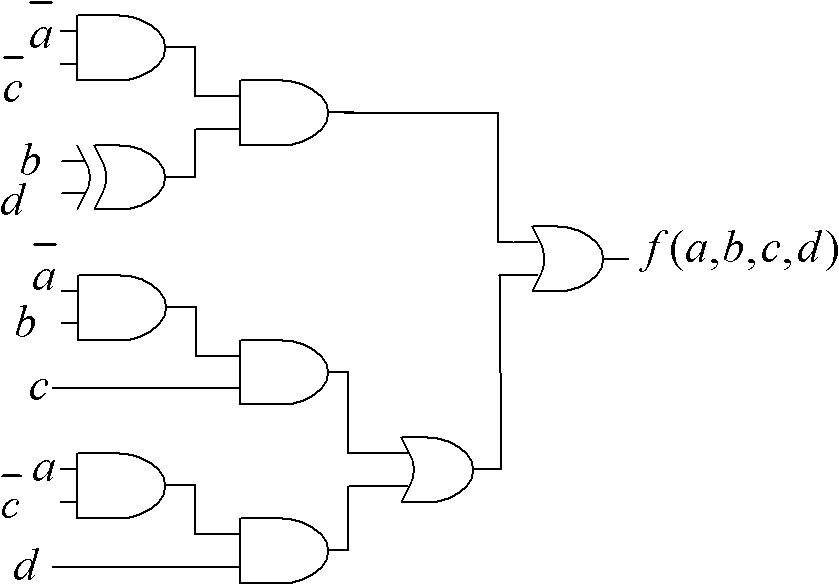

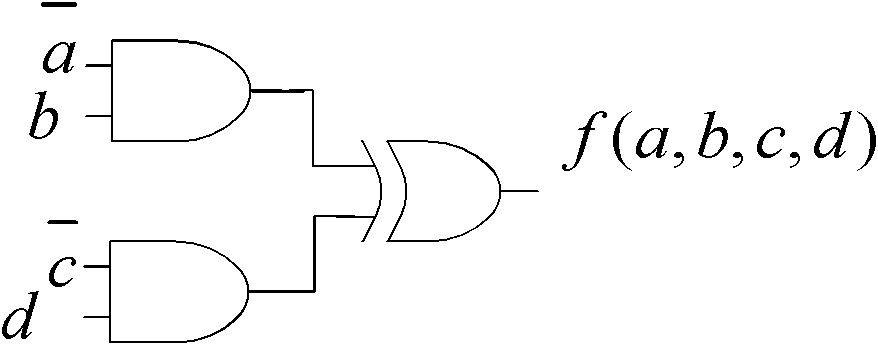

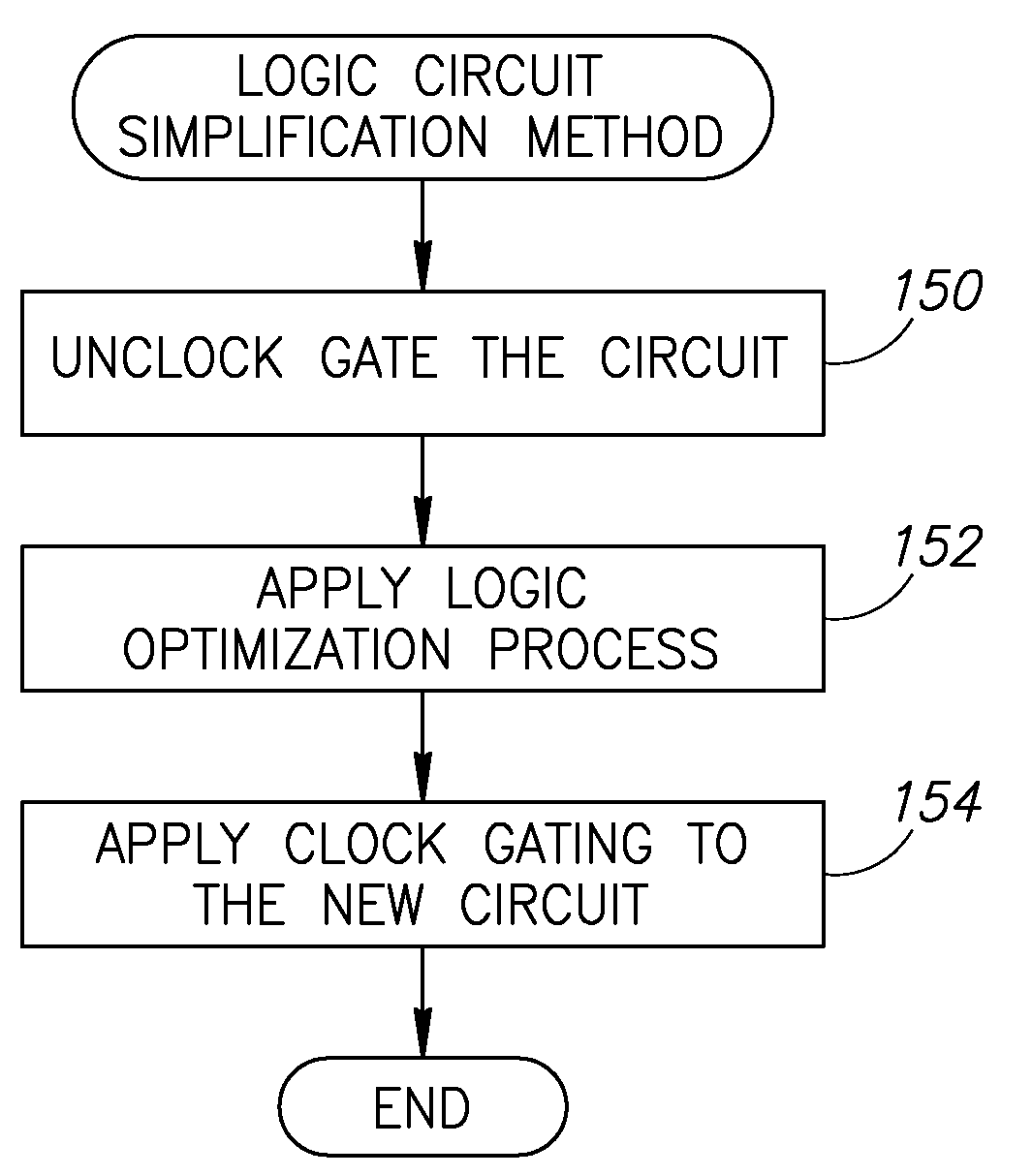

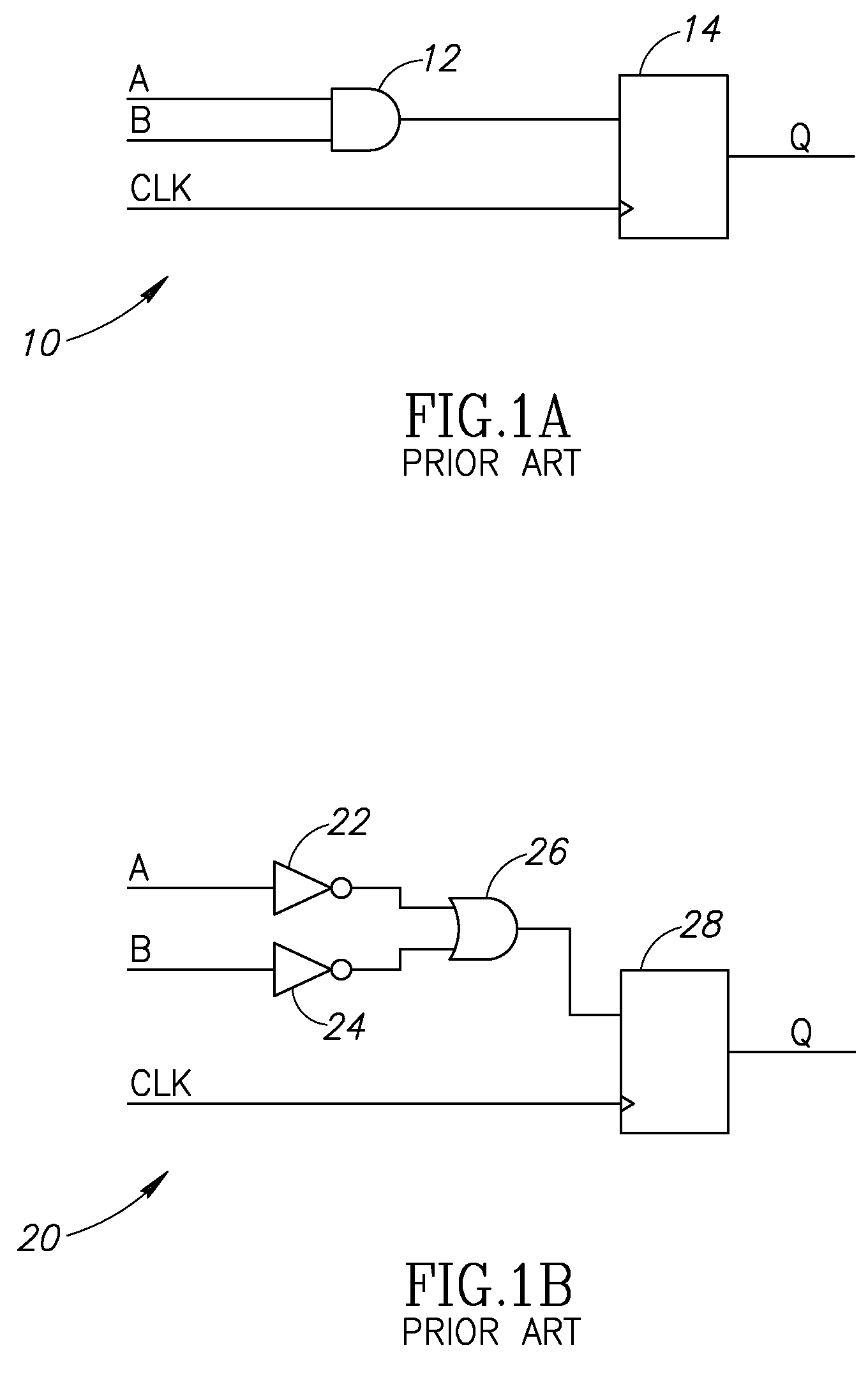

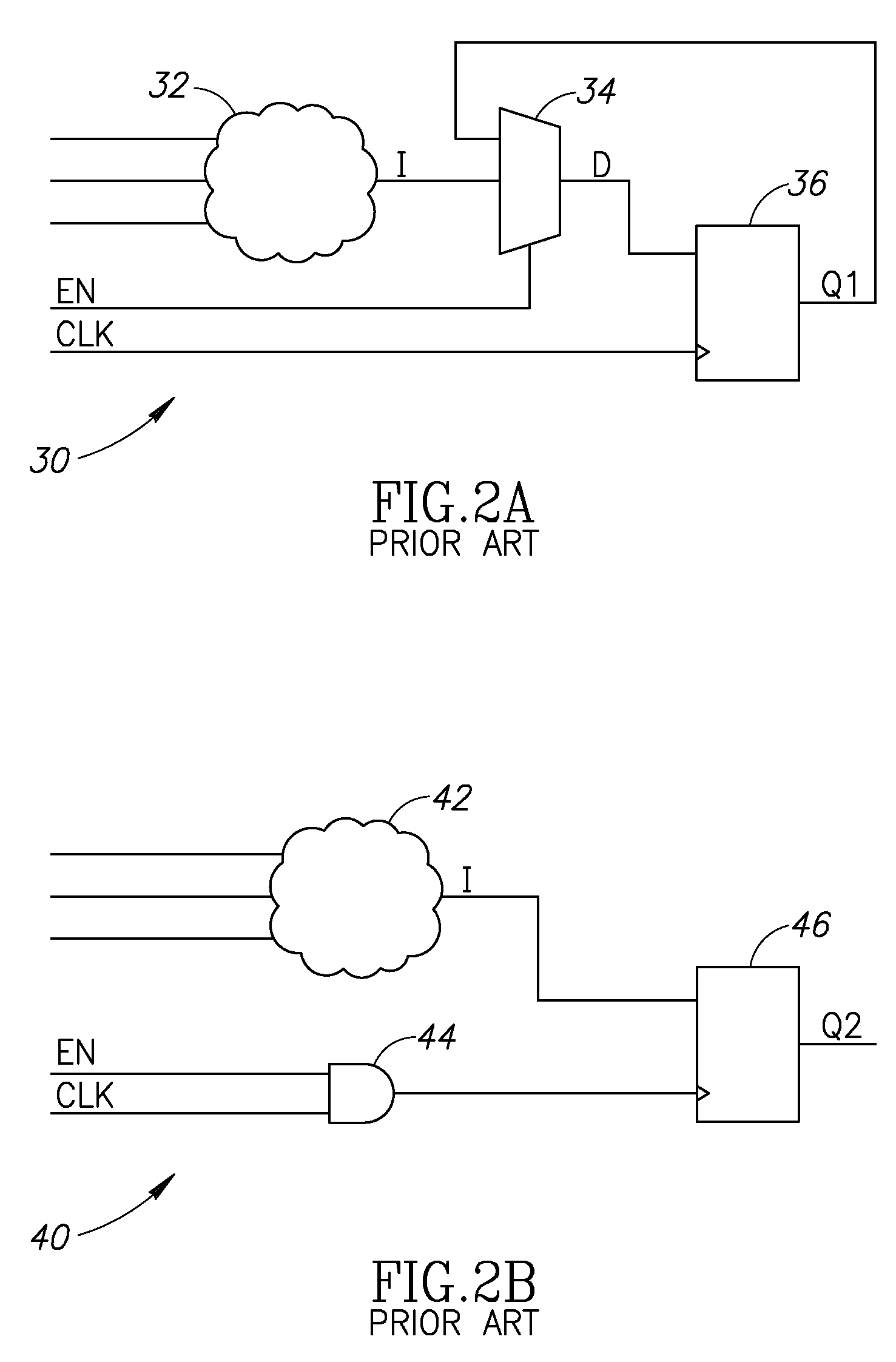

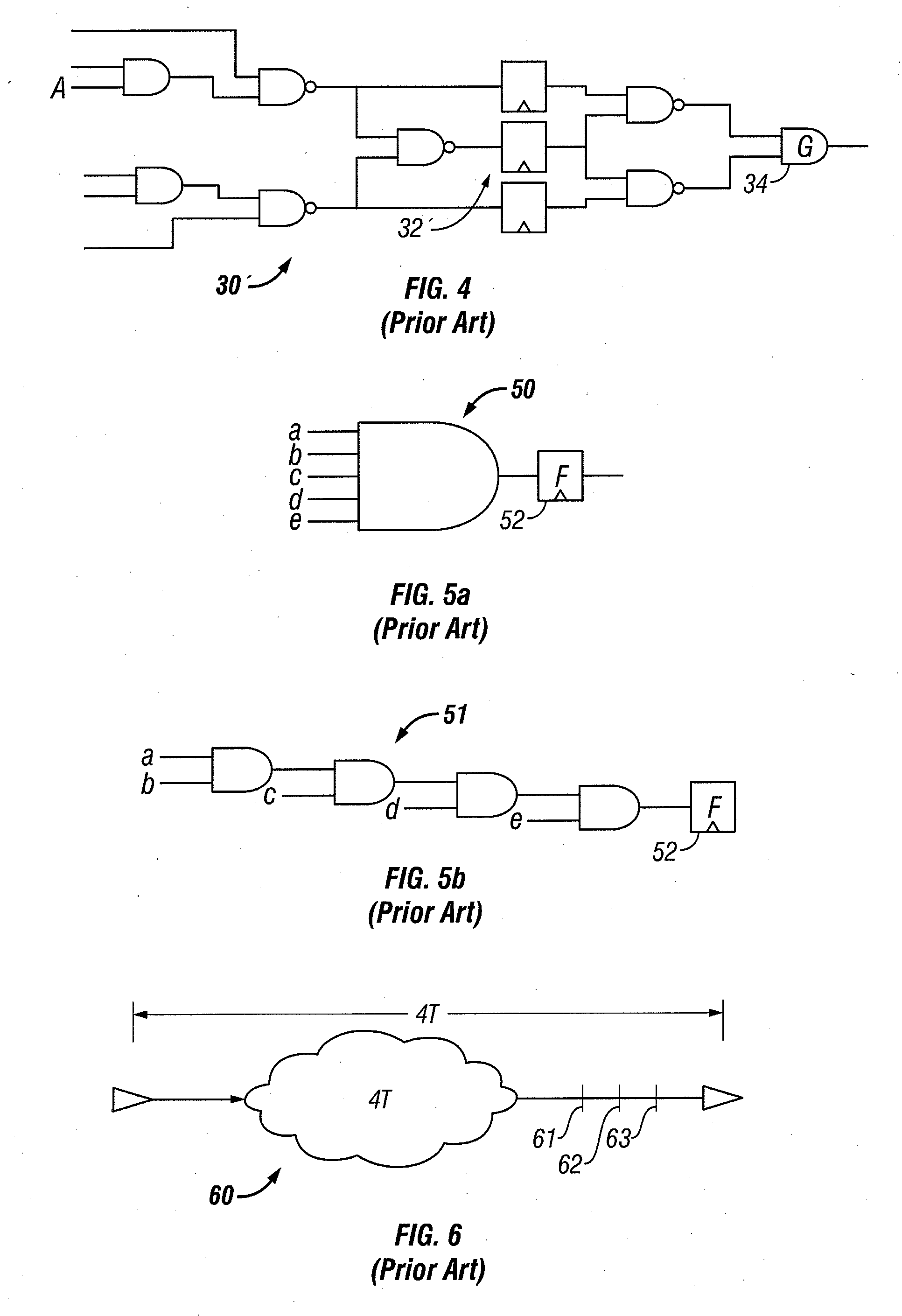

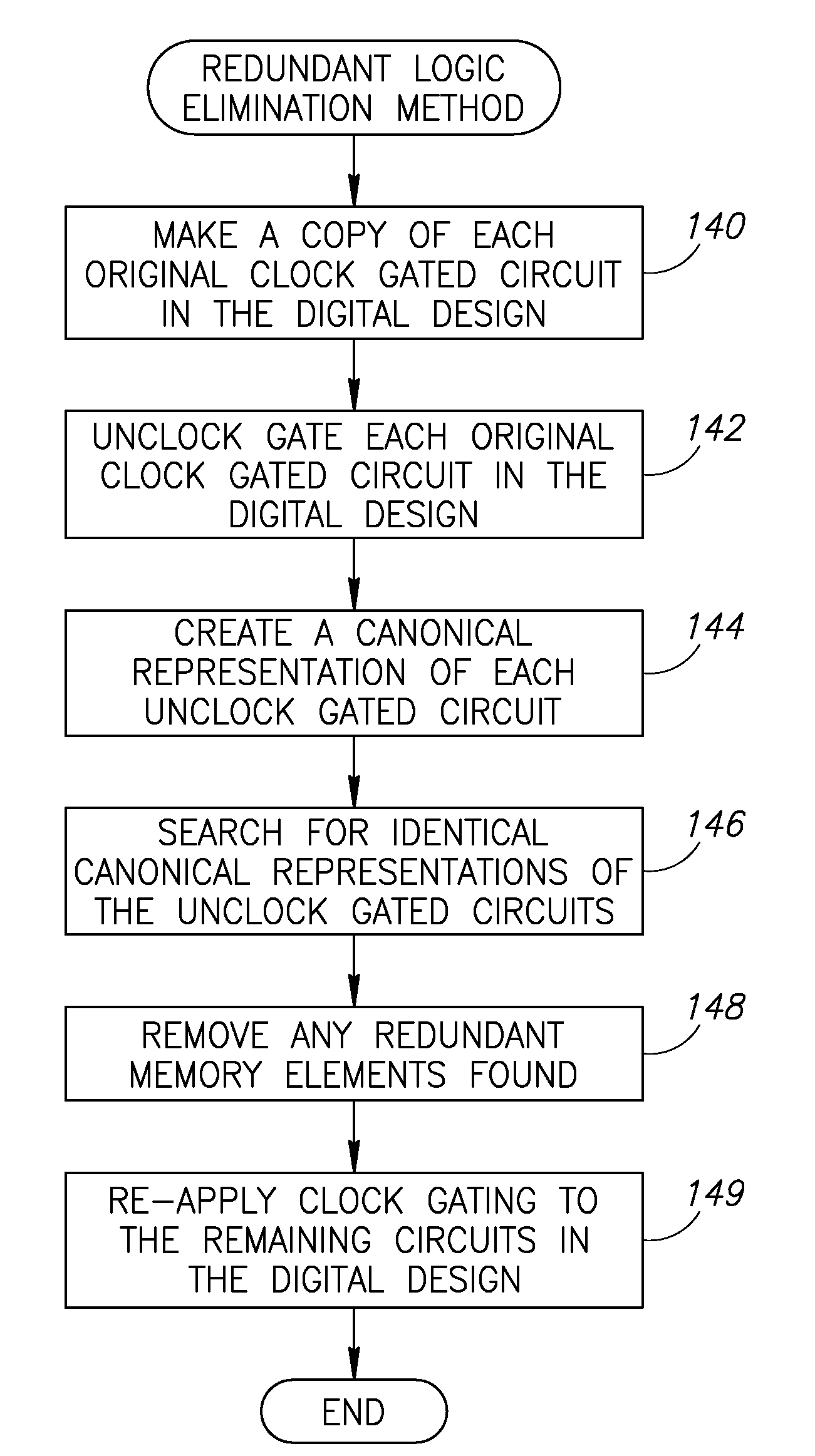

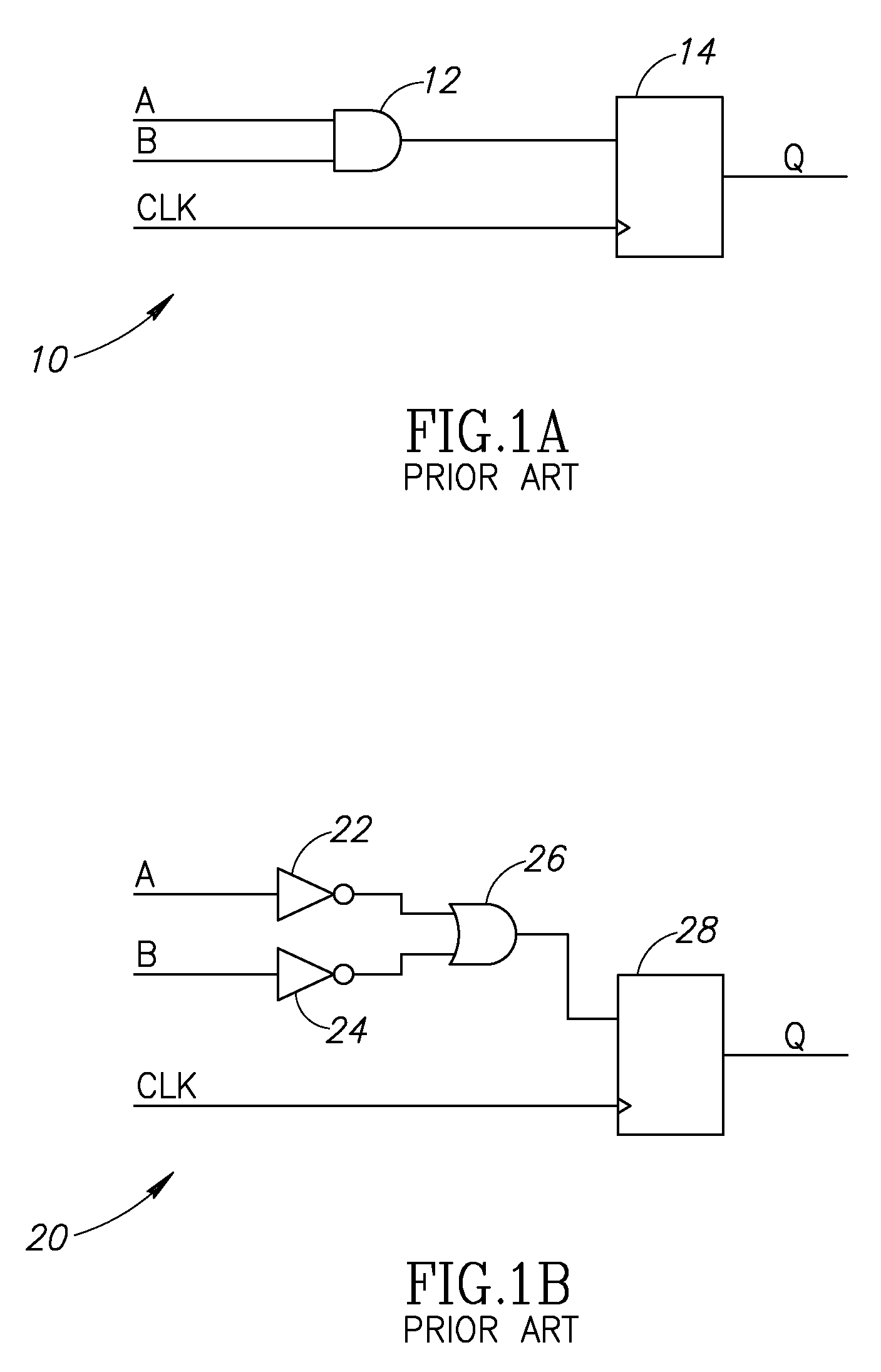

Circuit design optimization of integrated circuit based clock gated memory elements

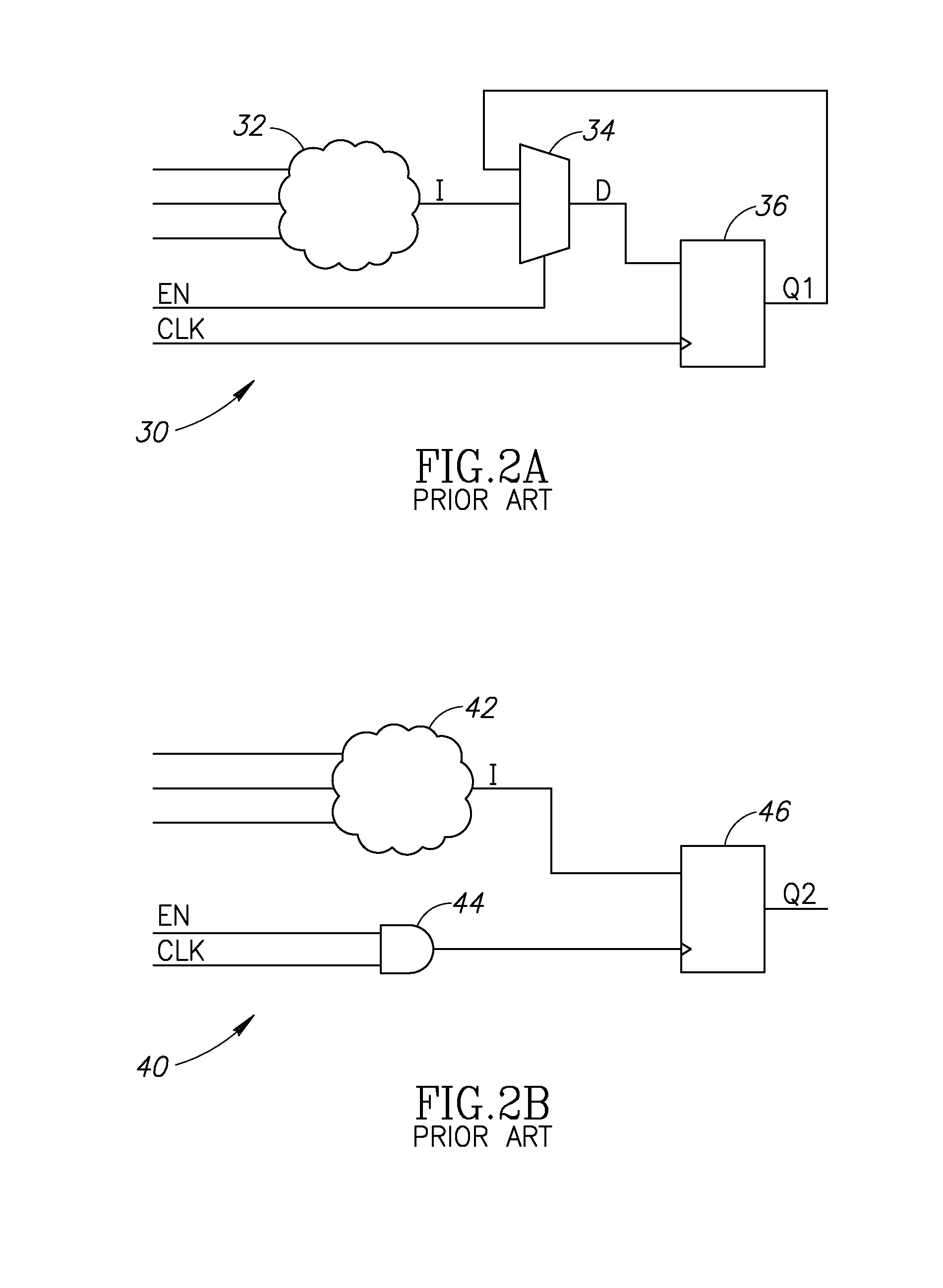

ActiveUS7676778B2Efficient designEliminate the problemCAD circuit designSoftware simulation/interpretation/emulationLogic optimizationIntegrated circuit layout

A novel method for optimizing the design of digital circuits containing clock gated memory elements. The method unclock gates memory elements by adding necessary feedback loops. Logic functions of memory element outputs in the circuit are viewed as a whole, rather than as separate functions for each input. Detection of duplicate unclock gated memory elements is then effected by identifying identical canonical representations of said unclock gated memory elements. Identified duplicate clock gated memory elements can then be eliminated from the original digital circuit. Further optimization can be accomplished by applying standard logic optimization algorithms to all unclock gated memory elements in said digital circuit. The resulting optimized circuit is clock gated and replaces the original clock gated circuit in said digital circuit.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

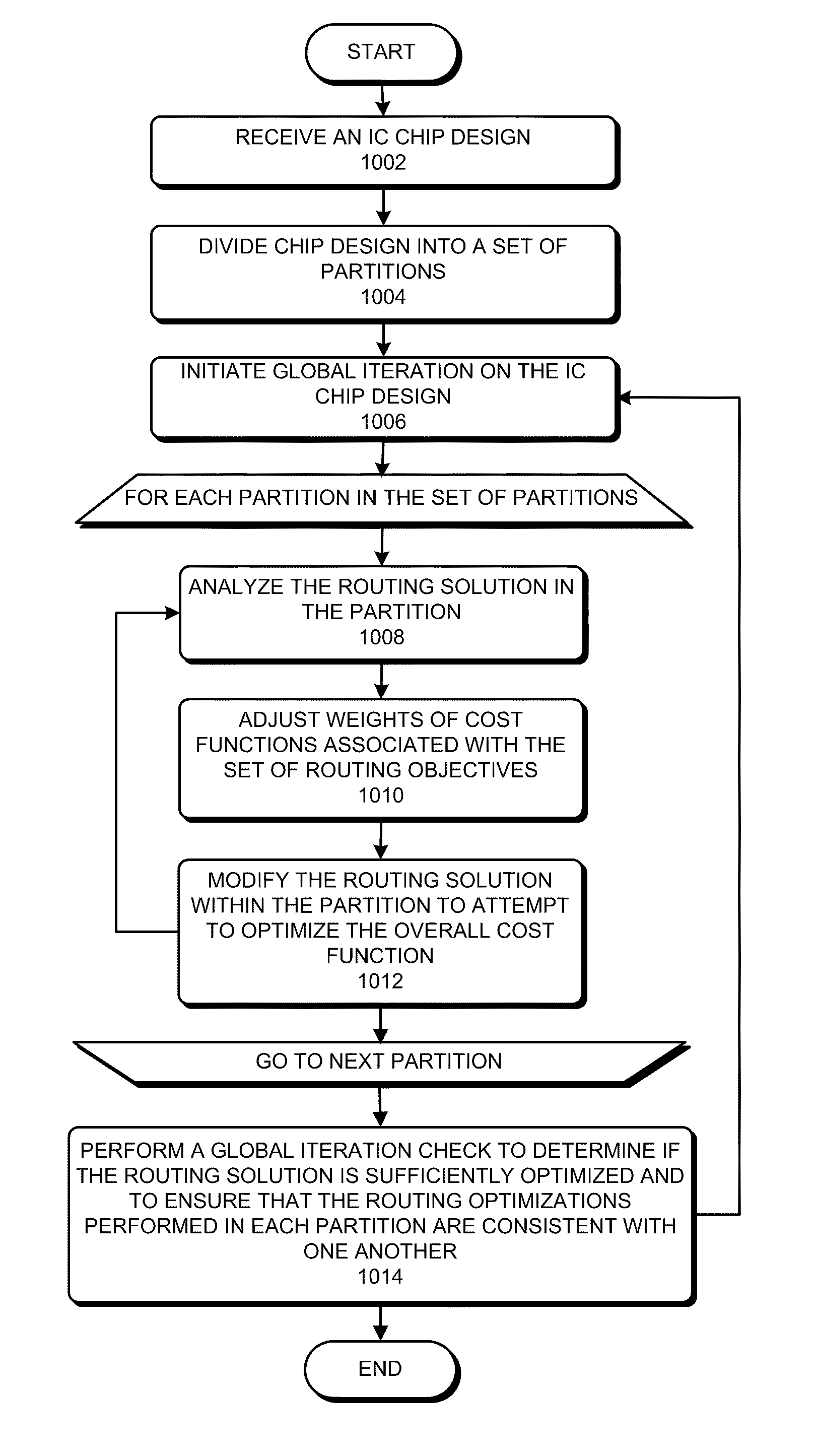

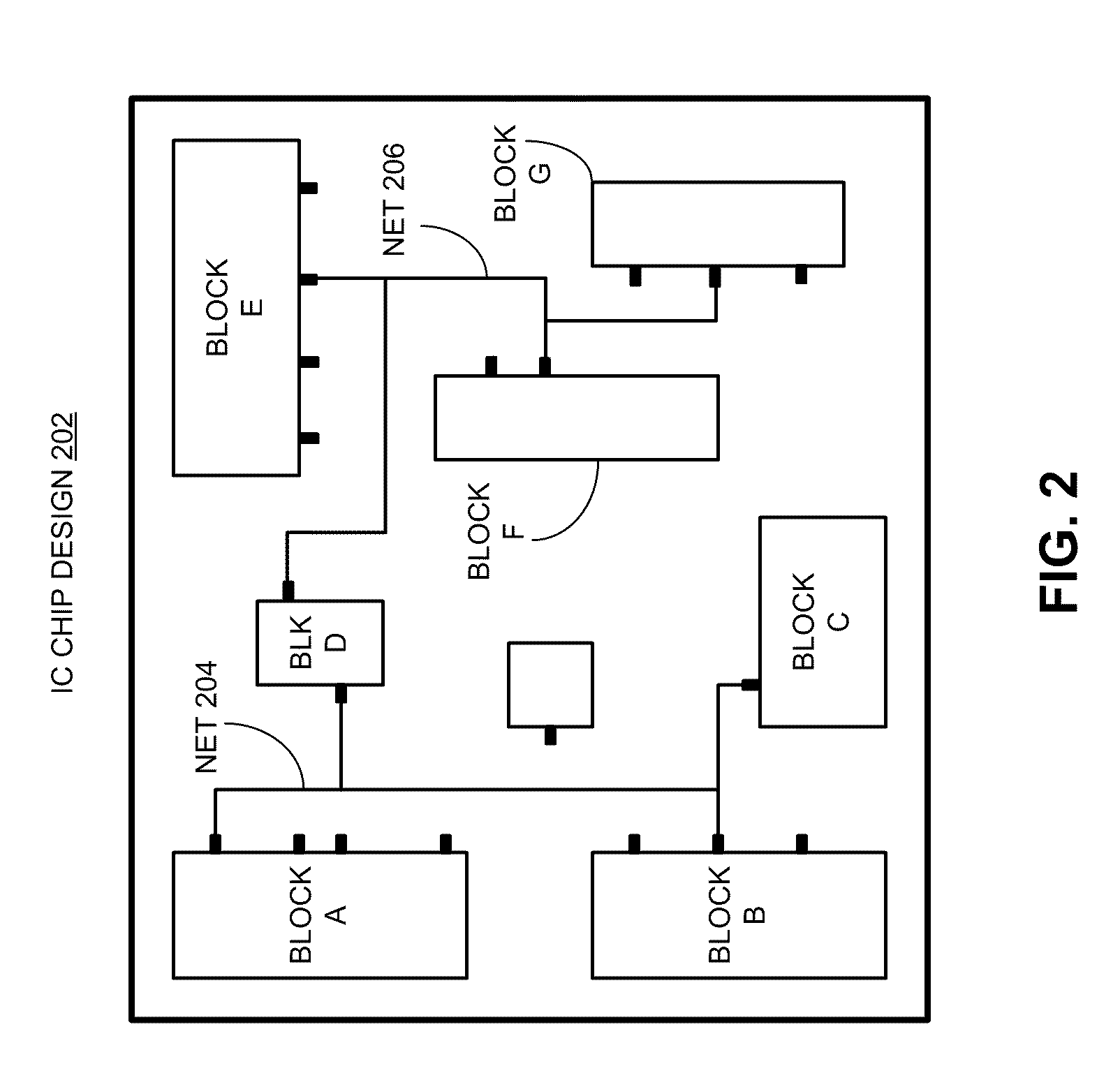

Method and apparatus for performing redundant via insertion during circuit design

ActiveUS20110055785A1Easy to insertIncrease in sizeCAD circuit designSoftware simulation/interpretation/emulationLogic optimizationEngineering

One embodiment of the present invention provides a system that concurrently performs redundant via insertion and timing optimization during routing of an integrated circuit (IC) chip design. During operation, the system performs an initial routing on the IC chip design to obtain a routing solution, which includes a set of vias. The system then performs a redundant-via-insertion operation on the routing solution, wherein the redundant-via-insertion operation attempts to modify a via within the set of vias into a redundant via. Next, the system performs a timing optimization on the routing solution by iteratively: (1) performing a timing analysis on the routing solution; (2) performing a logic optimization on the routing solution; and (3) performing an incremental routing adjustment on the routing solution, wherein the incremental routing adjustment adjusts the redundant vias.

Owner:SYNOPSYS INC

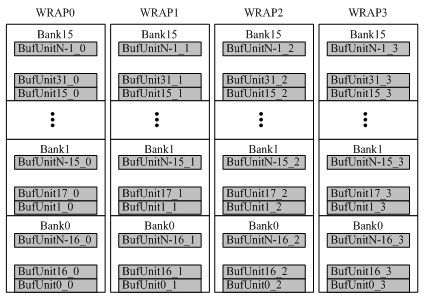

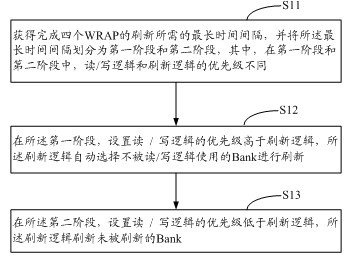

Dynamic random access memory (DRAM) and method for improving DRAM data access bandwidth

InactiveCN102436429AAvoid lossImplement random accessMemory adressing/allocation/relocationComputer architectureLogic optimization

The invention discloses a dynamic random access memory (DRAM) and a method for improving DRAM data access bandwidth. The method includes refreshing logic optimization, specifically includes the following steps: S11, obtaining a longest time interval which is required for completing refreshing of four web ready appliances protocols (WRAPs), dividing the longest time interval into a first stage and a second stage; S12, setting priority level of reading / writing logic to be higher than that of refreshing logic at the first stage, wherein the refreshing logic automatically selects Bank which is not used by the reading / writing logic to perform refreshing; and S13, setting the priority level of the reading / writing logic to be lower than that of the refreshing logic, wherein the refreshing logic refreshes the Bank which is not refreshed. Under the condition that the memory access clock frequency is not improved, the interface data bit width is not increased, and the logic design complexity is not increased, the DRAM and the method for improving the DRAM data access bandwidth improve interface data access bandwidth to the most extent, and meet requirements for data storage of integrated circuit (IC) design.

Owner:SUZHOU CENTEC COMM CO LTD

Method for generating optimized constraint systems for retimable digital designs

ActiveUS20090083685A1Low costDesirable propertyComputer aided designSoftware simulation/interpretation/emulationLogic optimizationDigital electronics

Owner:CADENCE DESIGN SYST INC

Circuit design optimization of integrated circuit based clock gated memory elements

ActiveUS20090013289A1Simple logicEfficient designCAD circuit designSoftware simulation/interpretation/emulationLogic optimizationIntegrated circuit layout

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

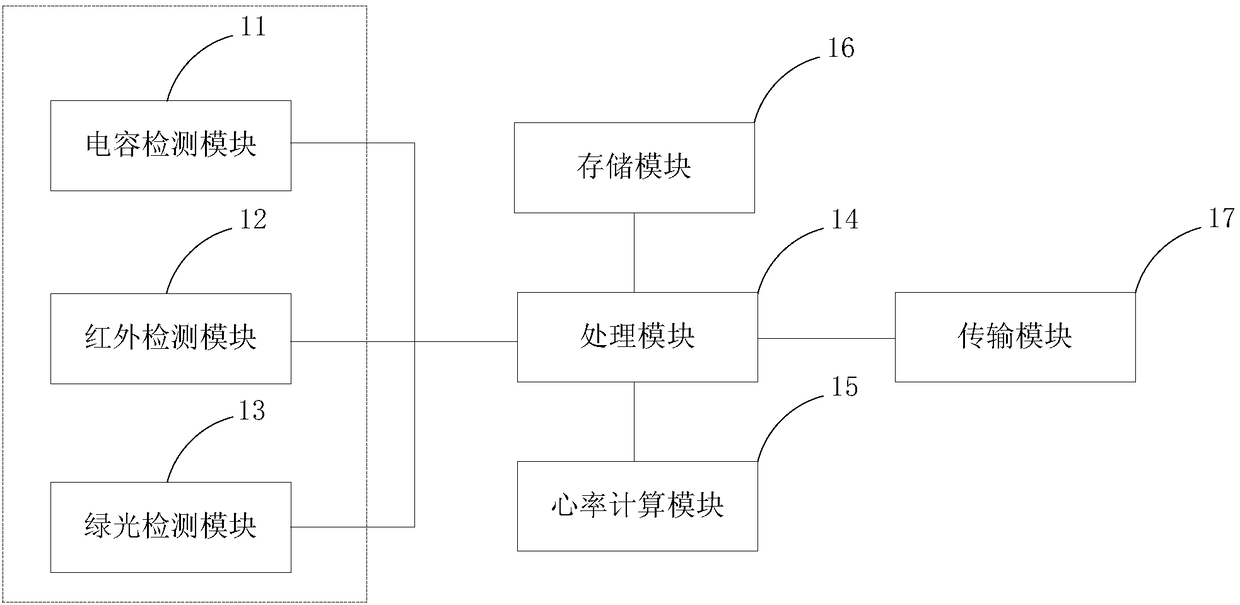

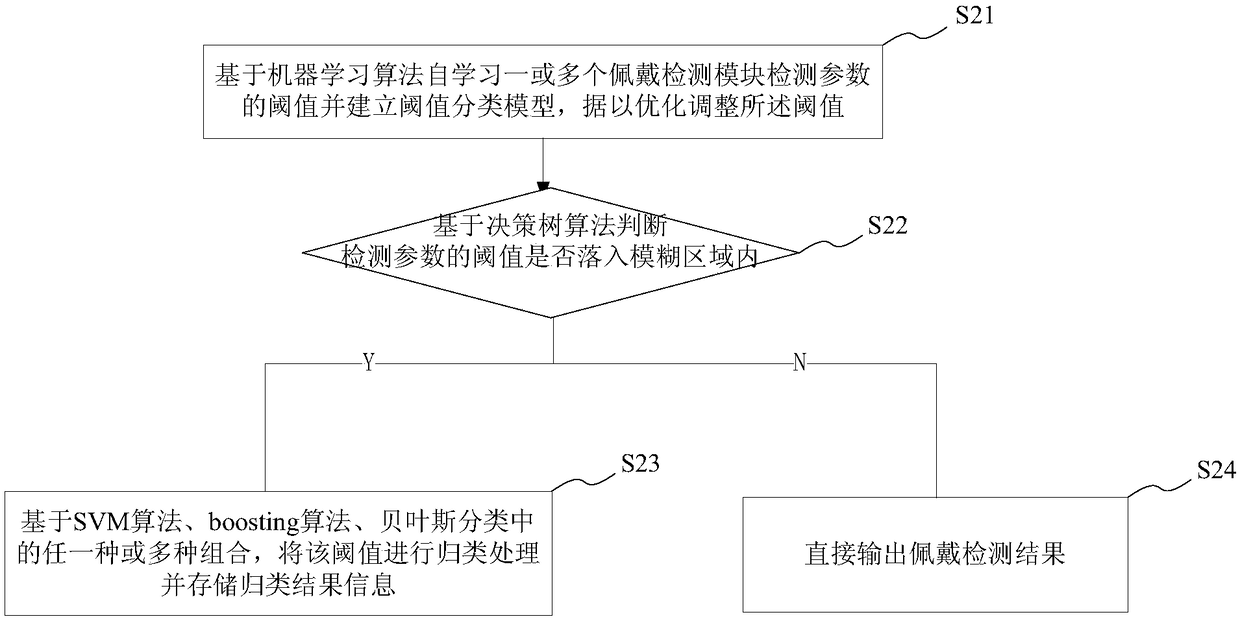

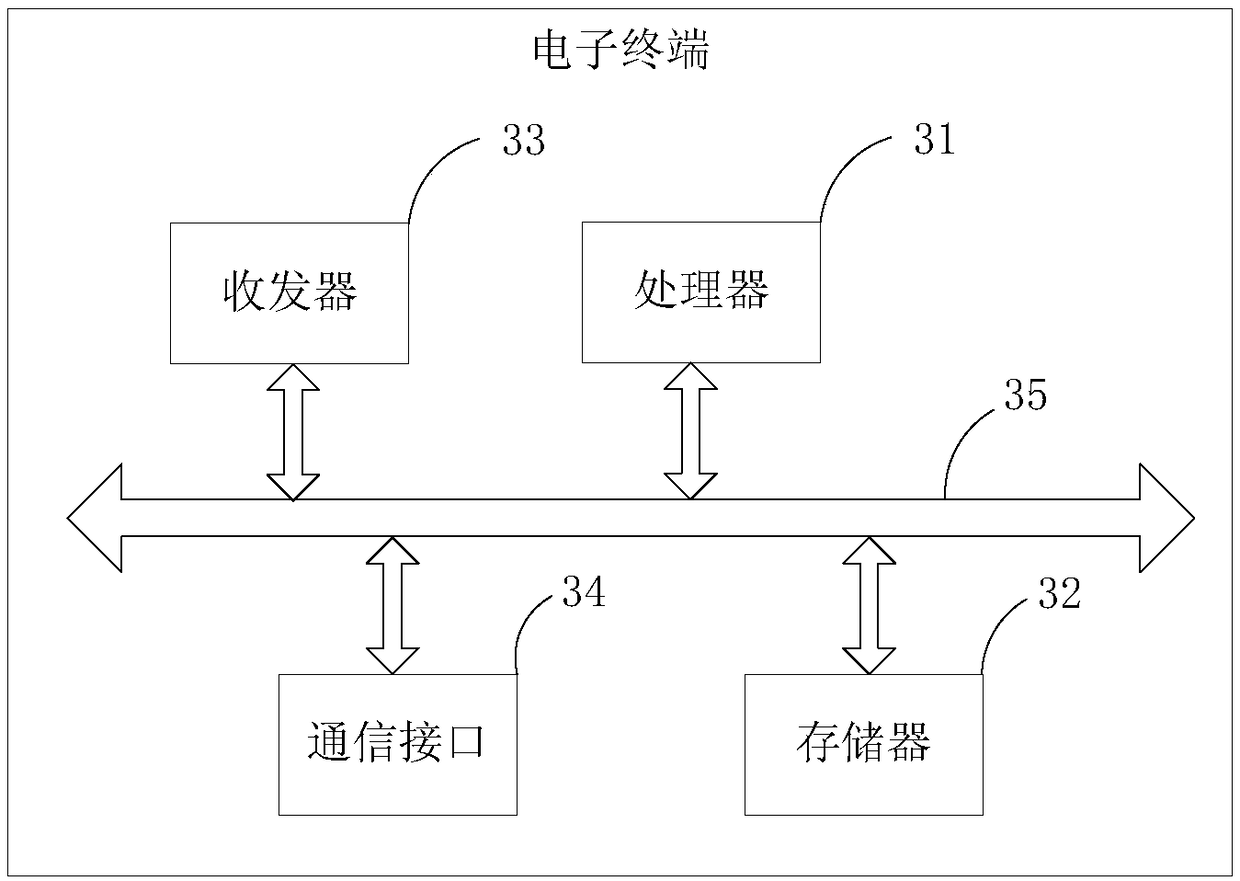

Wearing detection system and method, electronic terminal and computer readable storage medium

PendingCN108564179AImprove detection accuracyImprove and improve detection accuracyConverting sensor output electrically/magneticallyNeural learning methodsPattern recognitionLearning based

The invention provides a wearing detection system and method, an electronic terminal and a computer readable storage medium. The wearing detection system comprises one or more wearing detection modules and a processing module, wherein one or more wearing detection modules are used for judging whether wearable equipment is worn at the preset position or not according to threshold values of detection parameters; the processing module is in communication with all the wearing detection modules, so that the threshold values of the detection parameters is self learned based on the machine learning algorithm, a threshold-value classification model is established, and the threshold values are optimized and adjusted based on the threshold-value classification model. According to the wearing detection system and method, the electronic terminal and the computer readable storage medium, under the condition of effectively controlling the device hardware cost, correct judgment of wearing detection is furthest achieved through the multiple detection parameters, the machine learning software algorithm and the like and logic optimization; through self-learning, the wearing detection system is moresuitable for a user, conditions except for the non-human body or the non-user are furthest excluded, and data collected by the system is more valuably used for analyzing the physiological state and the healthy condition of the user.

Owner:上海翰临电子科技有限公司

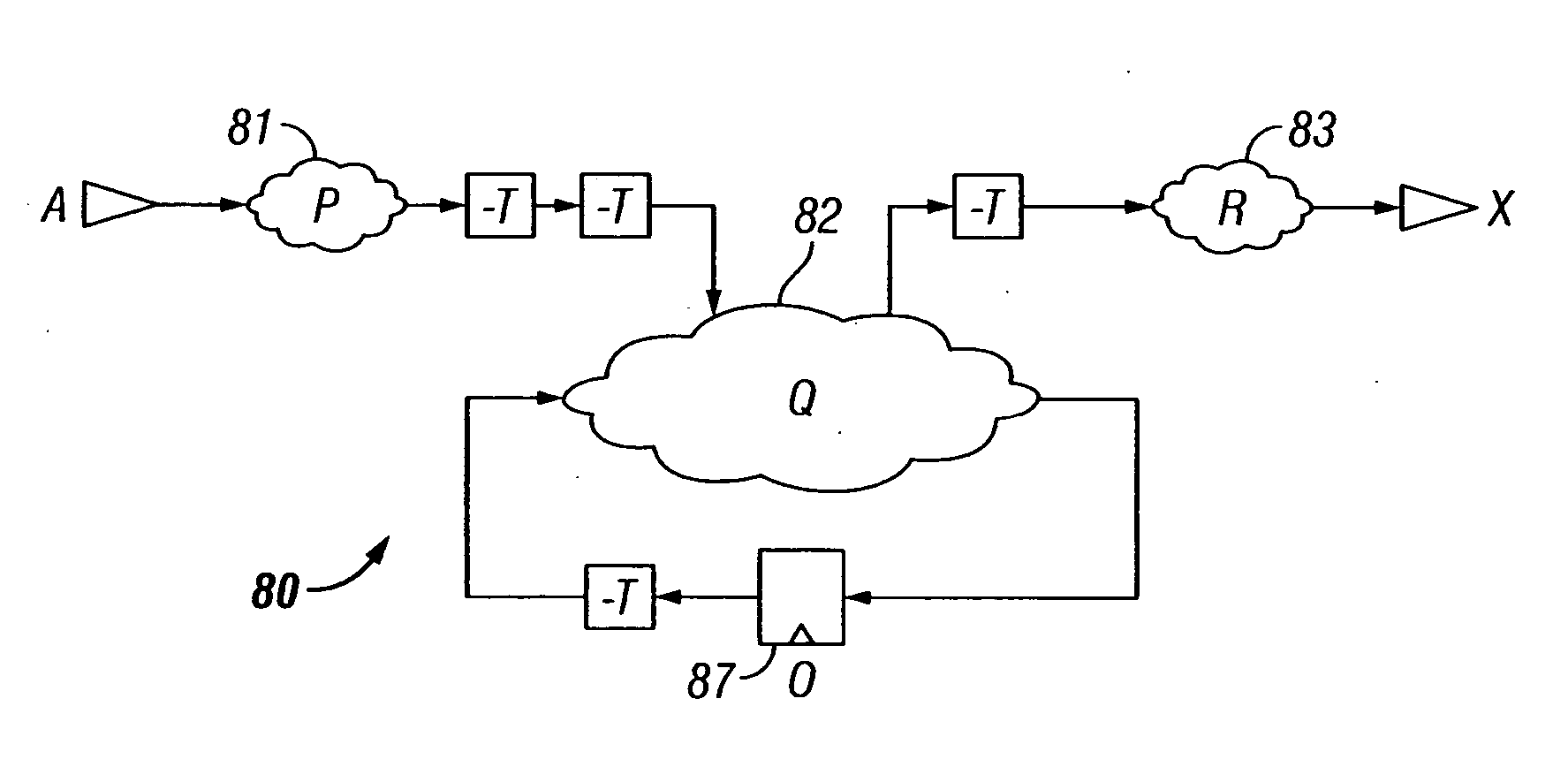

Method for generating optimized constraint systems for retimable digital designs

ActiveUS20050062496A1Reduce hardware costsDesirable propertyComputer aided designSoftware simulation/interpretation/emulationLogic optimizationDigital circuitry

A method for generating timing constraint systems, where the constrained object is a digital circuit., is provided, where the constraints are generated for the use of a digital logic optimization (synthesis) tool. The synthesis tool is used to optimize the circuit, under the applied constraints, so that the circuit exhibits certain desirable timing properties, while at the same time minimizing hardware cost and various other properties. The particular class of timing constraints generated by the disclosed invention is useful when the circuit is to be retimed after optimization. Typically, the joint use of the described invention and retiming results in improvements in the overall cost / performance tradeoff curve of the design. The invention comprises a method that comprises the following steps: (1) the flip-flops of the design are replaced with buffers having a negative delay whose magnitude is approximately the desired clock cycle time of the design; and (2) cycles in the design are broken using flip-flops having an infinite or quasi-infinite clock frequency. Following optimization by the synthesis tool, the temporary changes can be reverted, and retiming performed on the circuit.

Owner:CADENCE DESIGN SYST INC

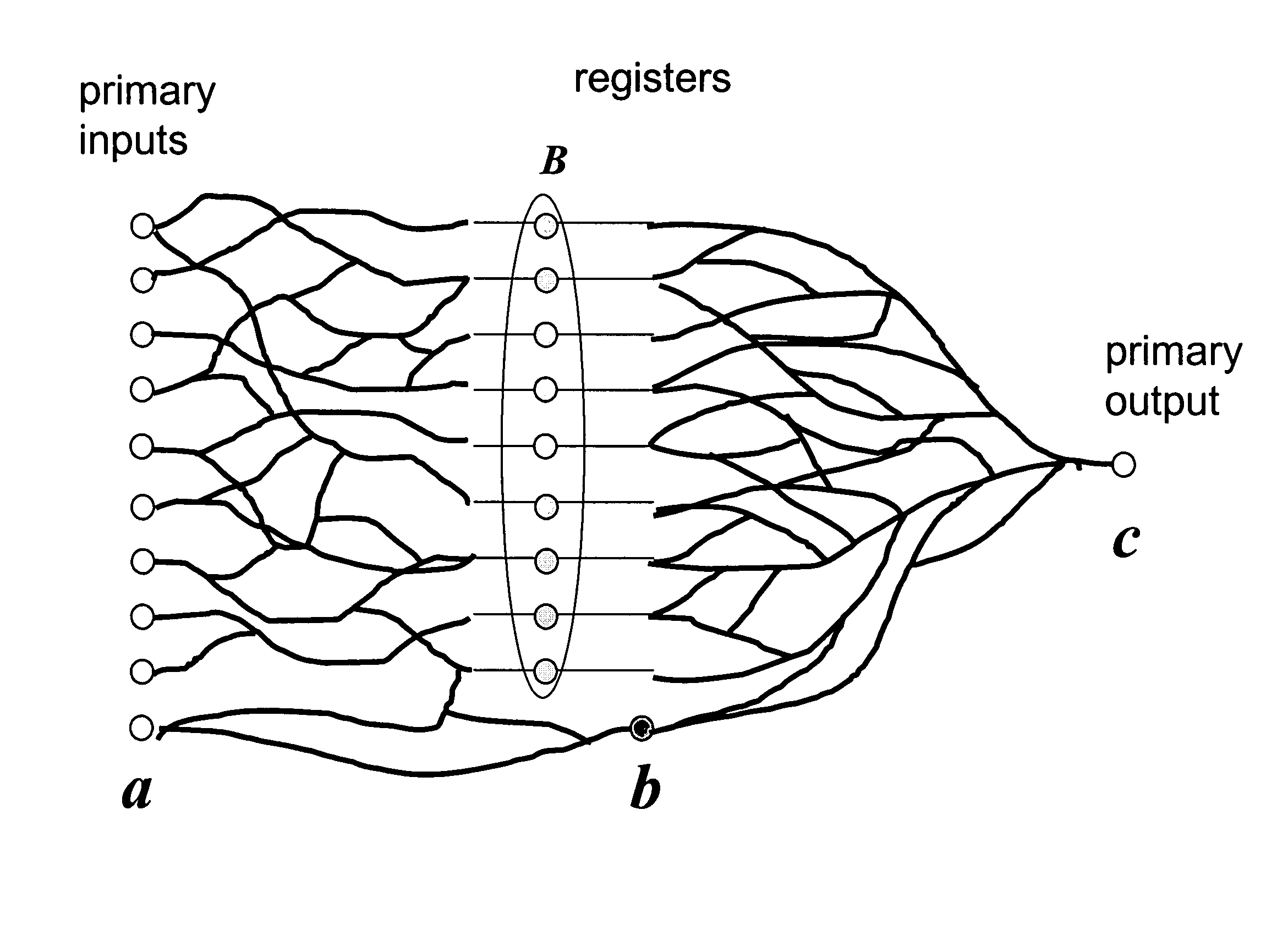

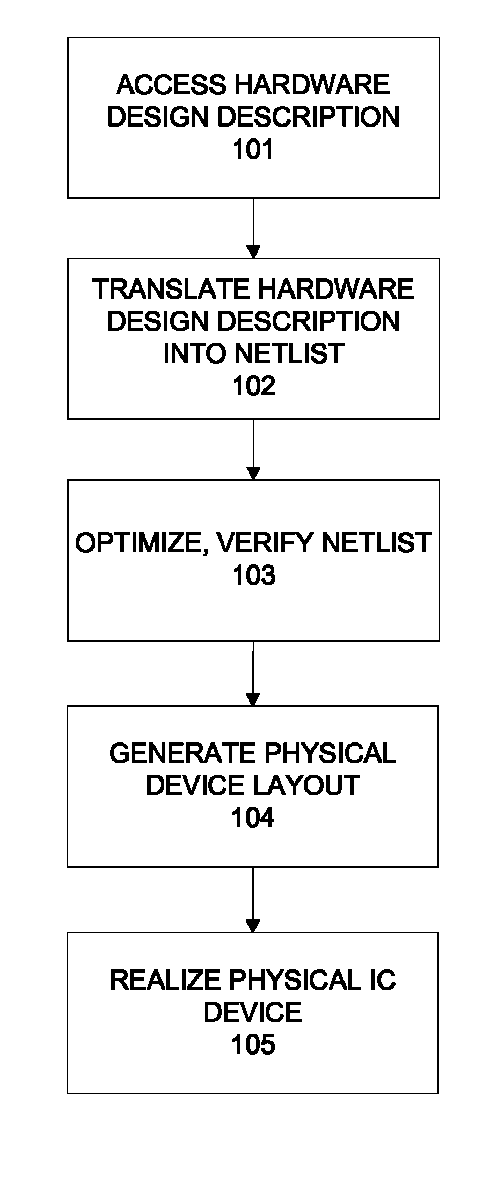

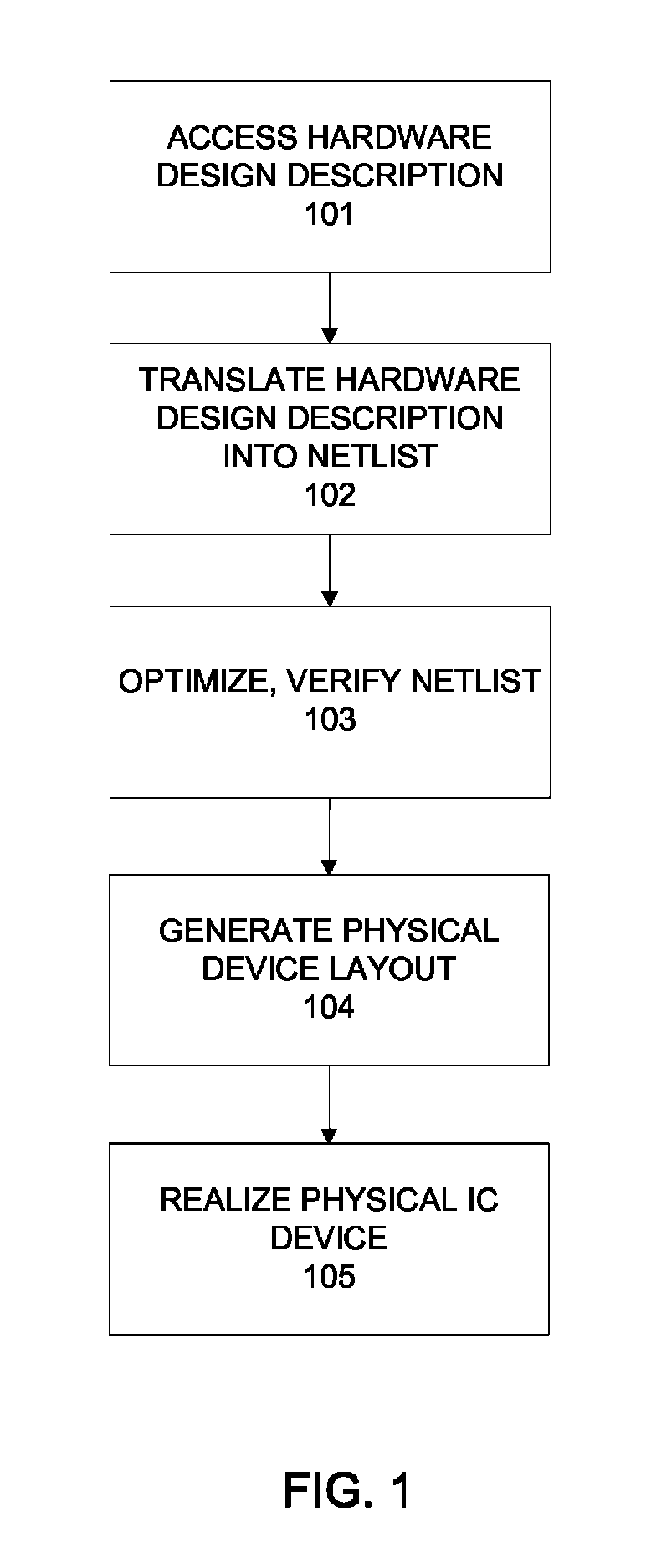

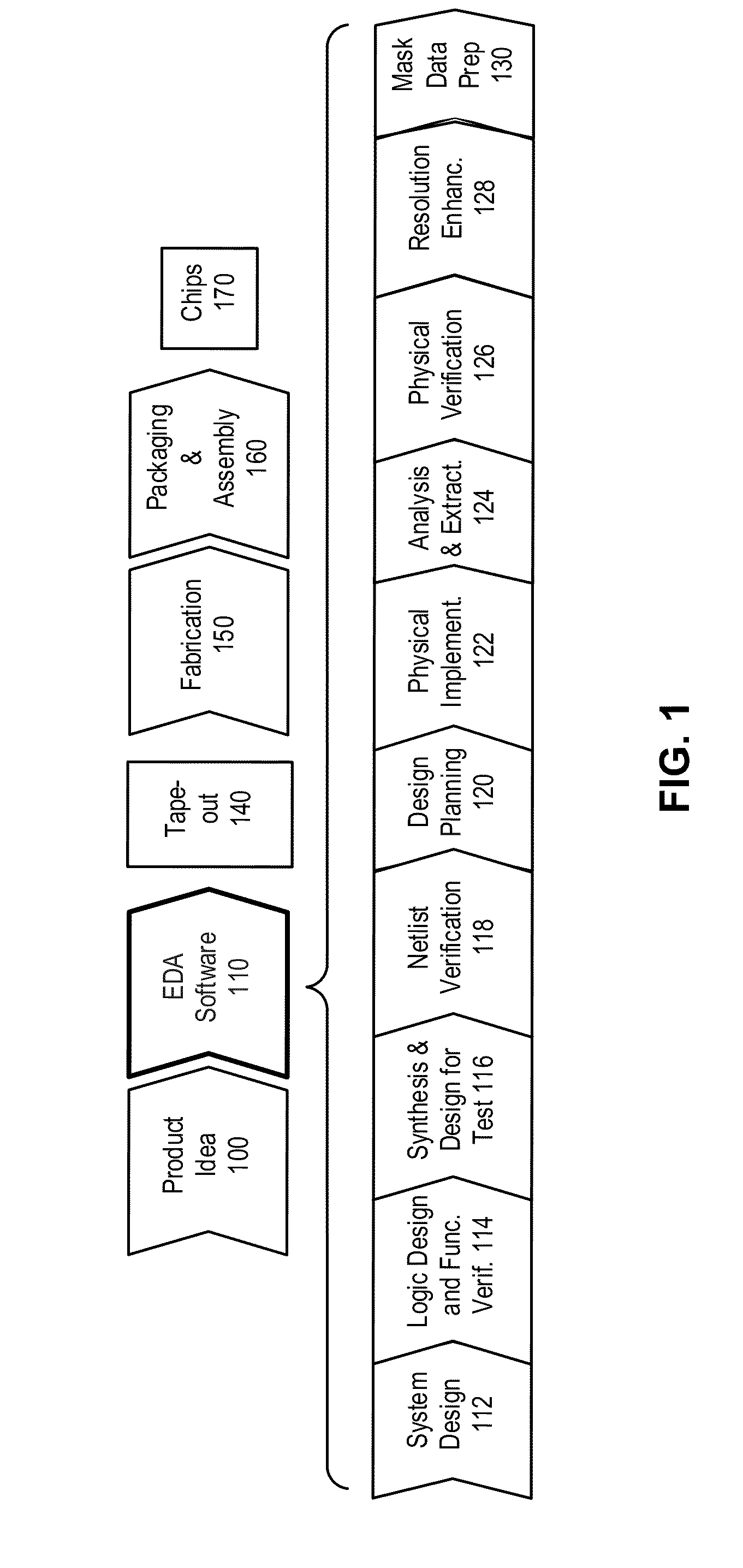

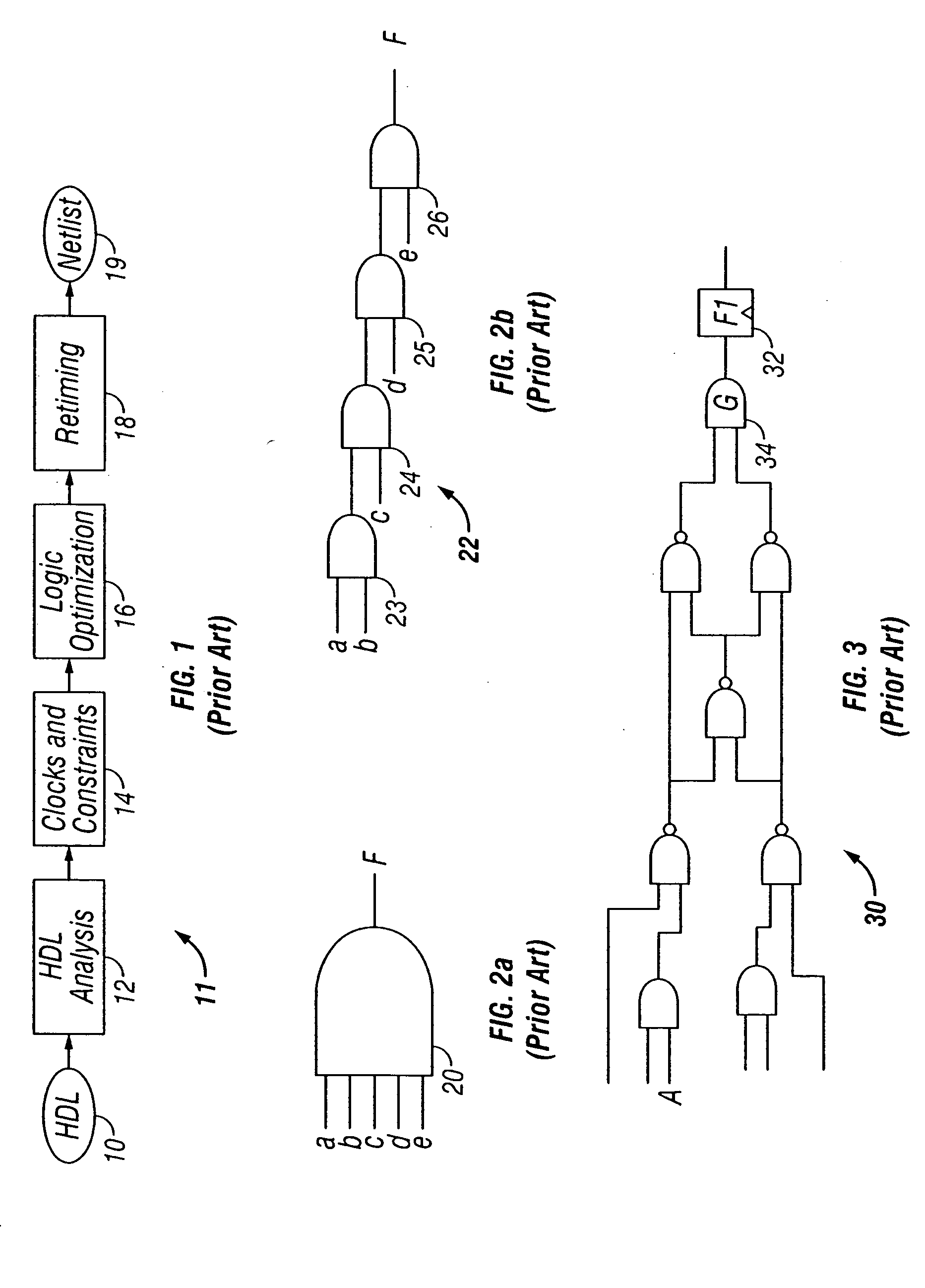

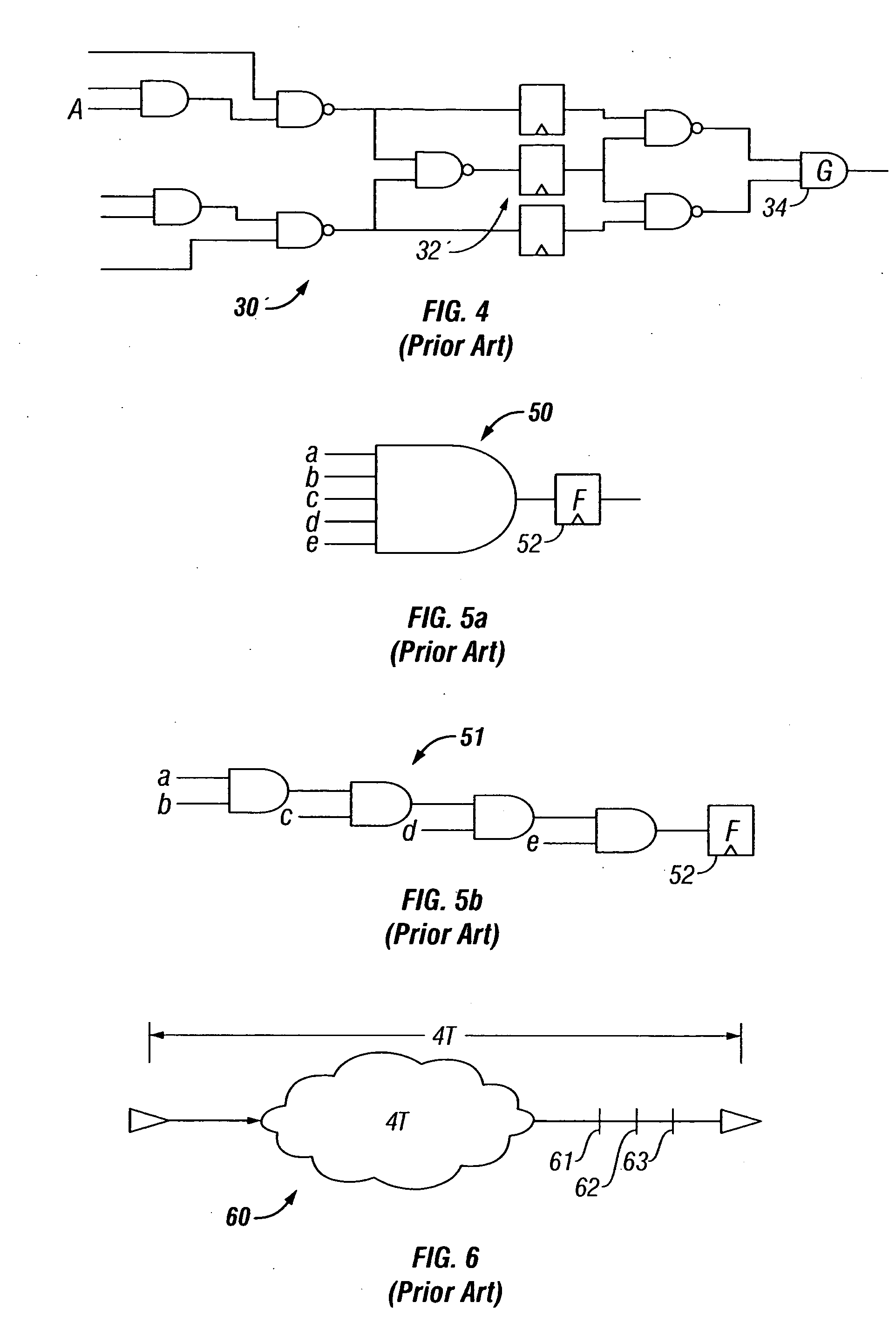

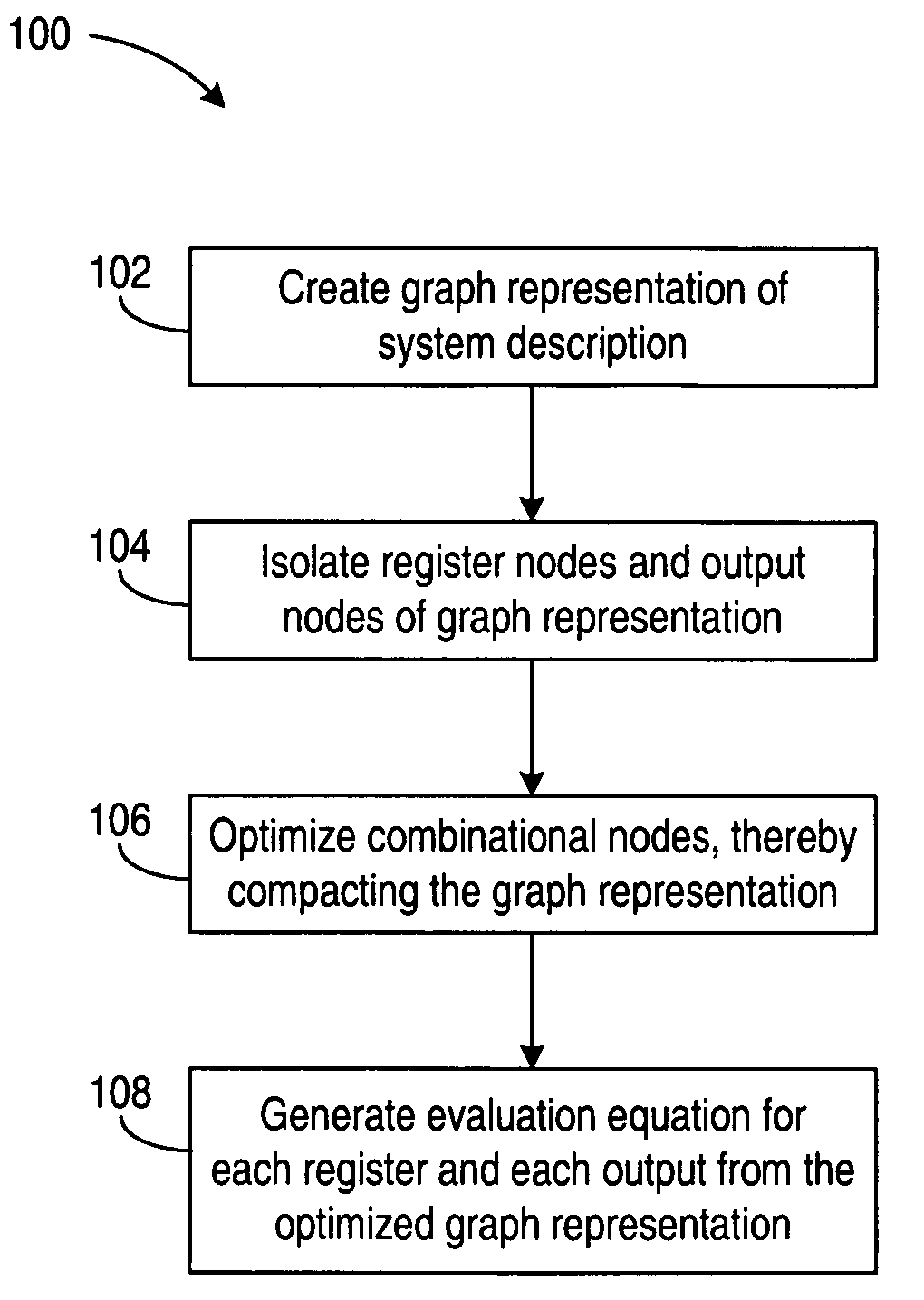

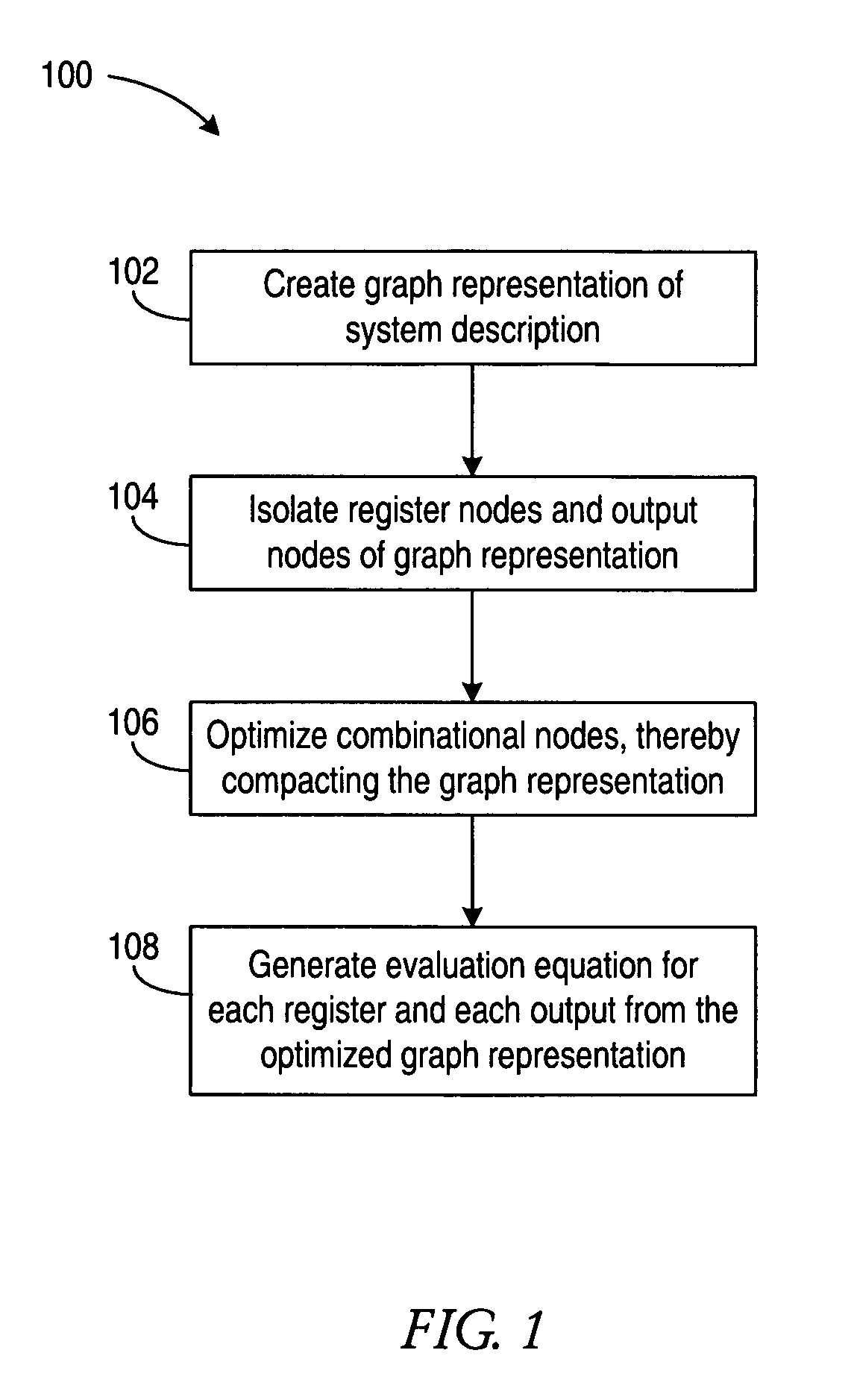

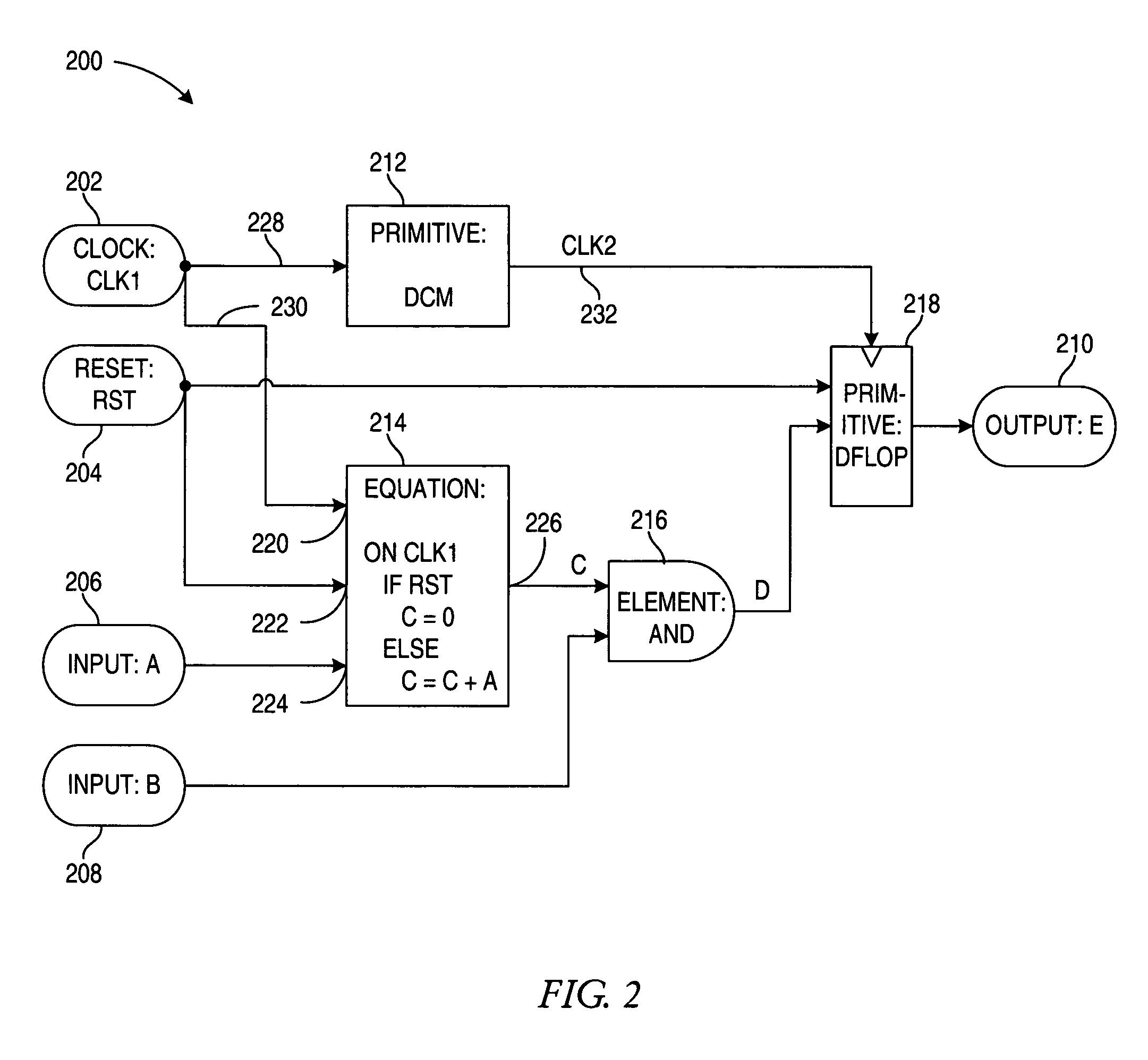

Generating fast logic simulation models for a PLD design description

ActiveUS7131091B1Simulation is accurateCAD circuit designSoftware simulation/interpretation/emulationGraphicsLogic optimization

Various approaches for generating a clock accurate simulation model from a circuit design description are disclosed. In one approach, a graph representation of the circuit design description is created. The graph representation includes nodes and edges. From the nodes in the graph representation, a plurality of register nodes are generated to correspond to respective register functions. Logic optimization is performed on nodes that represent combinational logic functions. For each register node and each output node, an evaluation equation is generated after performing logic optimization. For each clock cycle of a logic simulation, each evaluation equation is evaluated and produces an output value for the next clock cycle.

Owner:XILINX INC

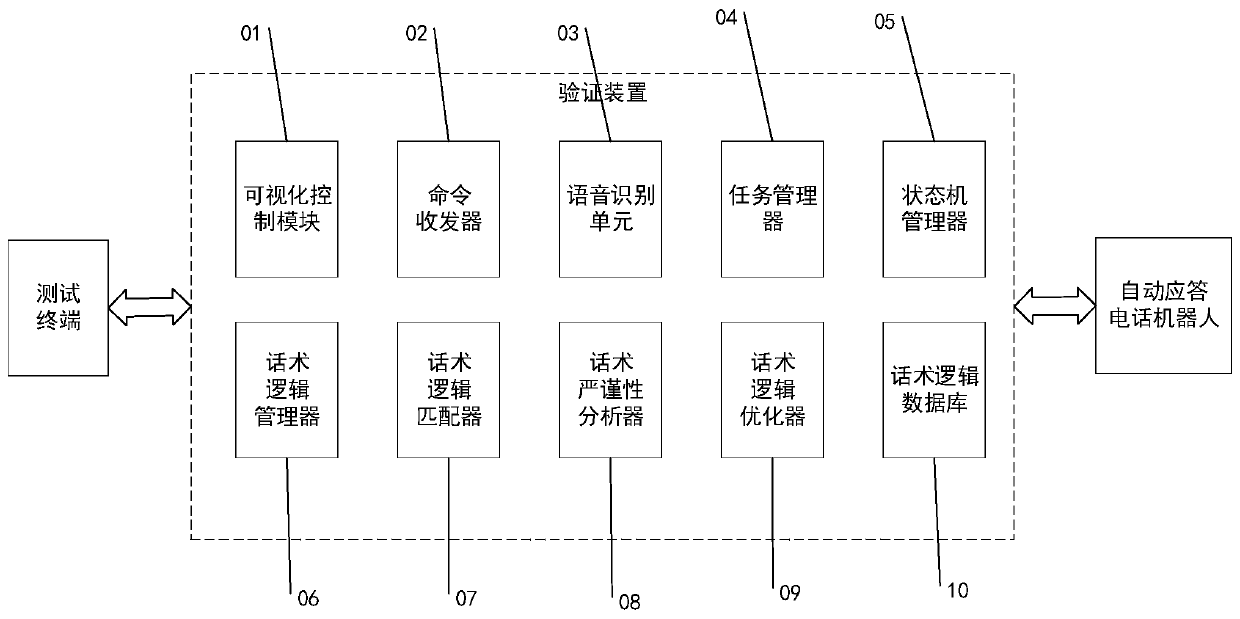

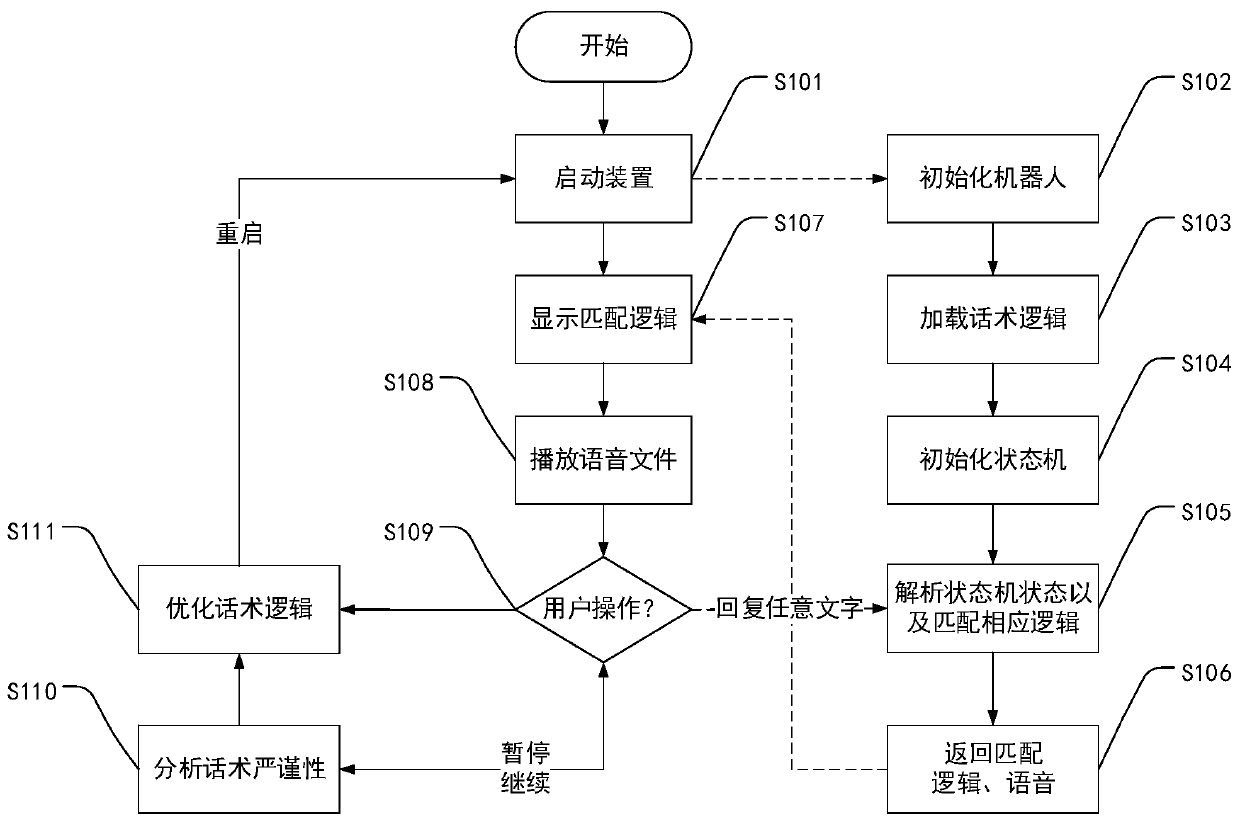

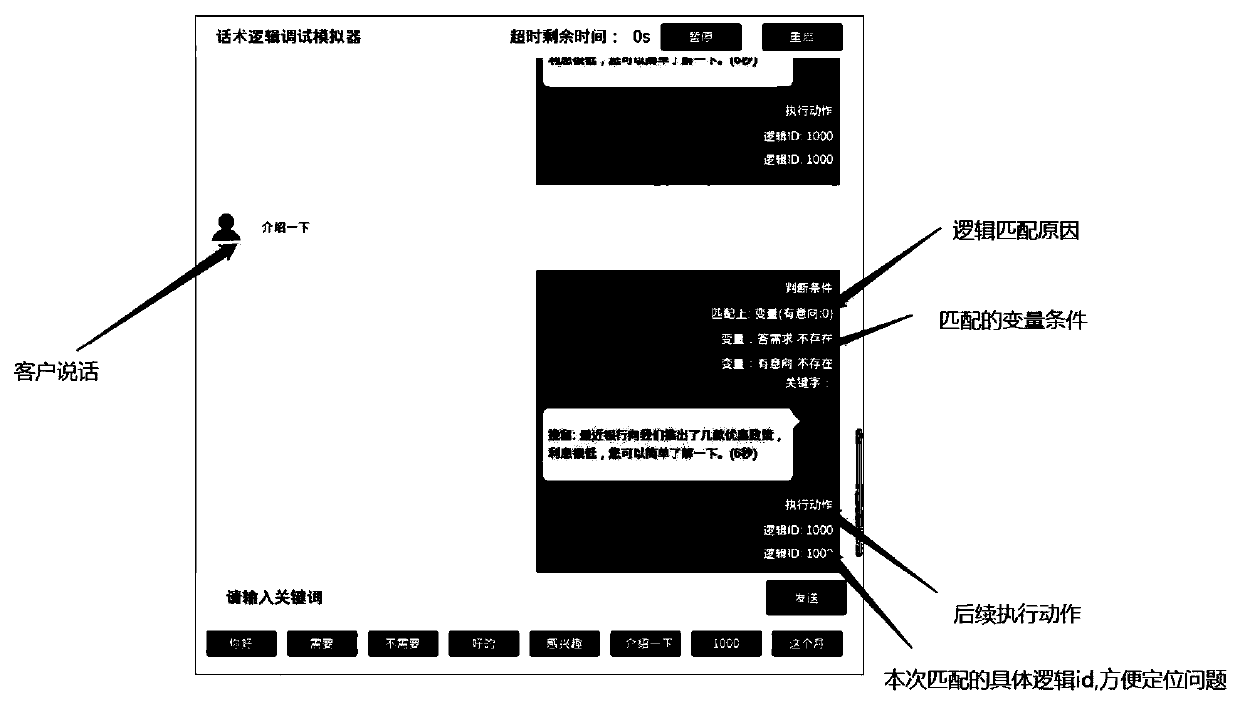

Device for verifying logical matching accuracy of automatic answering telephone robot answering speech

PendingCN109933477ARealize visualizationIncreased speed of match accuracy verificationLogical operation testingLogic optimizationTransceiver

The invention discloses a device for verifying logical matching accuracy of an automatic answering telephone robot answering speech. The device comprises a visual control module, a command transceiver, a voice recognition unit, a task manager, a state machine manager, a speech logic manager, a speech logic matcher, a speech preciseness analyzer, a speech logic optimizer and a speech logic database. Through the device provided by the invention, the test verification of the logic matching accuracy of the answering speech of the automatic answering telephone robot is realized, compared with manual verification, the verification speed and accuracy are improved, the consistency of the test verification is ensured, the verification process can be visually presented, and the cost of manual replayis also saved.

Owner:北京六行君通信息科技股份有限公司

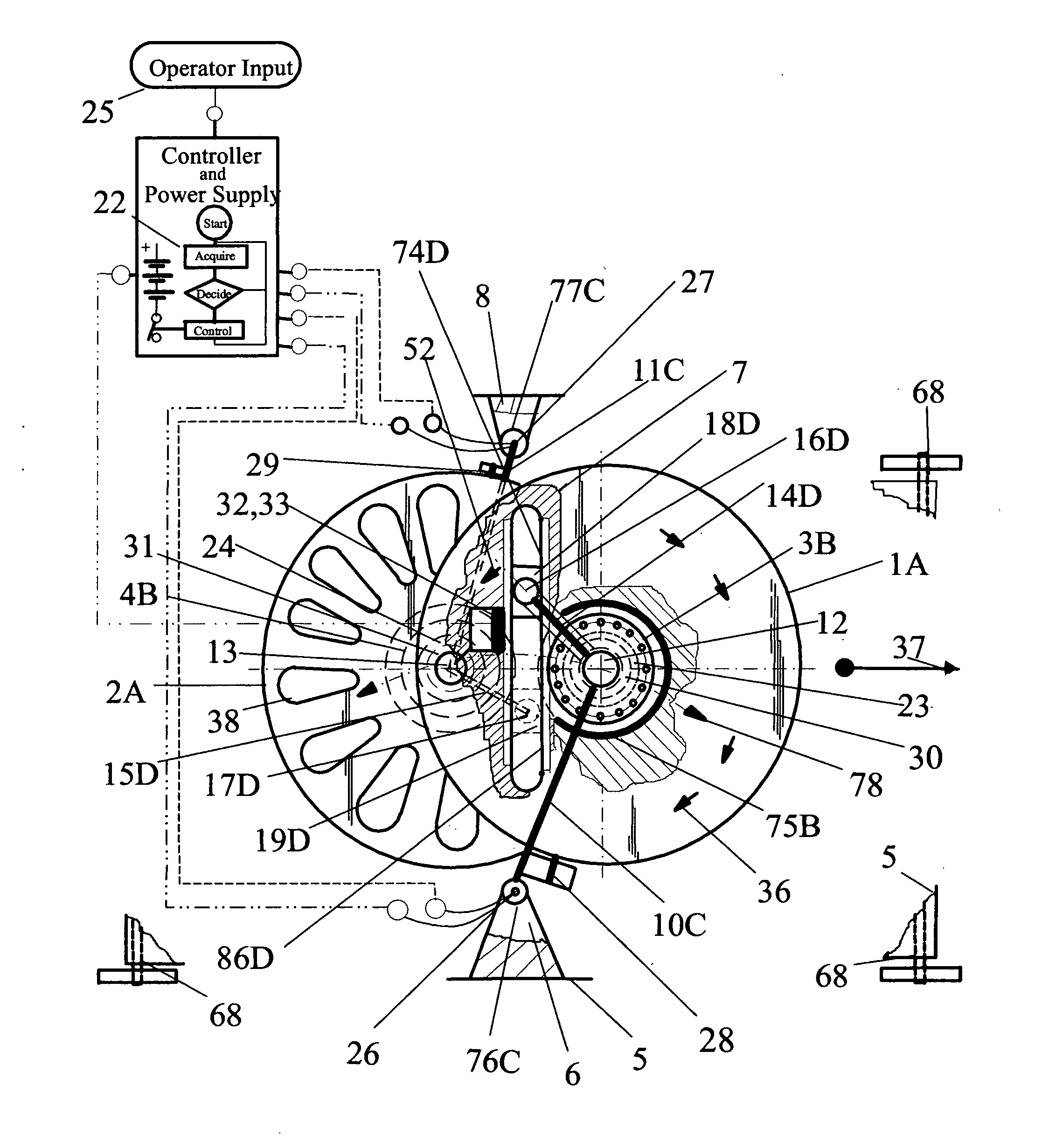

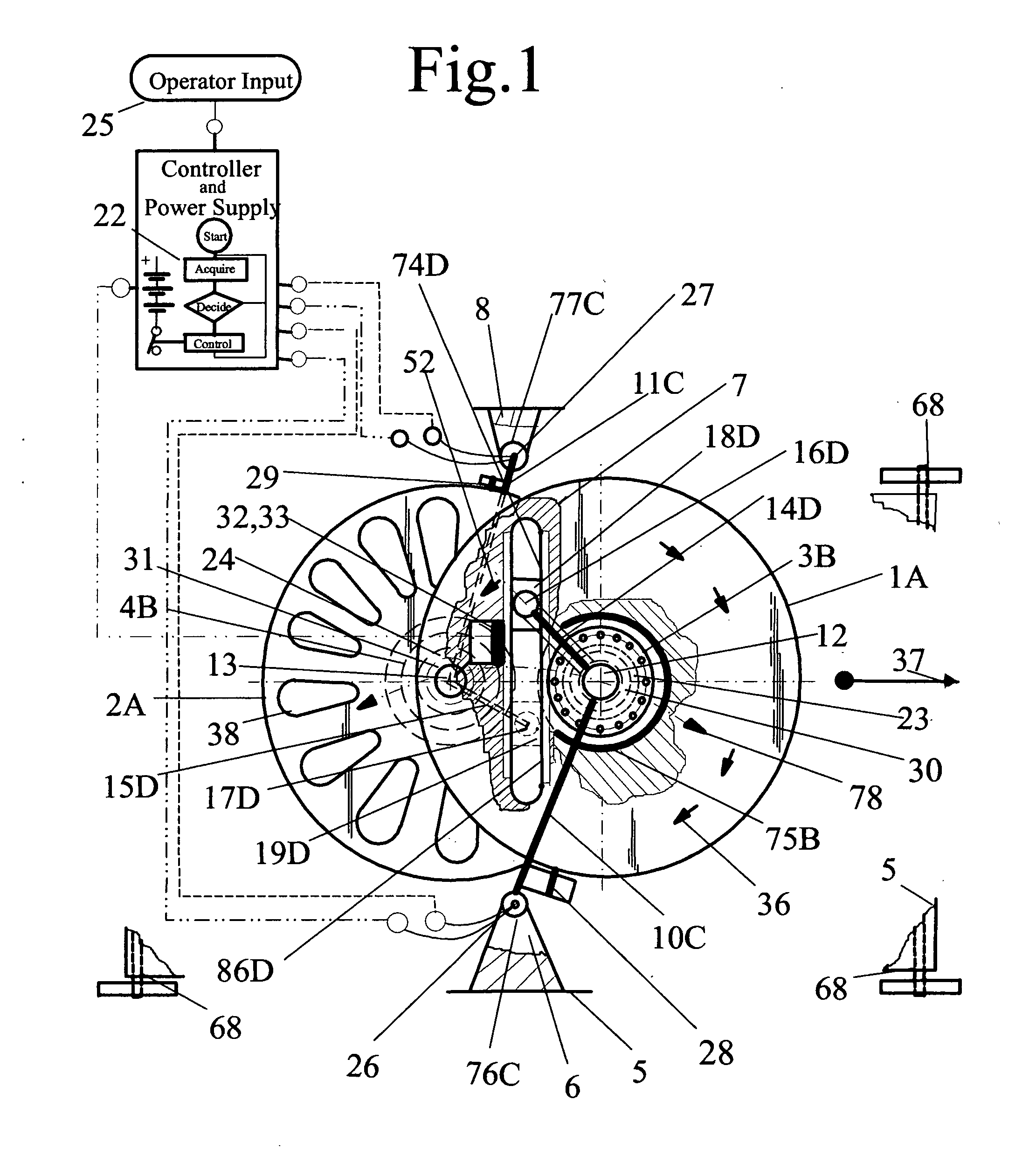

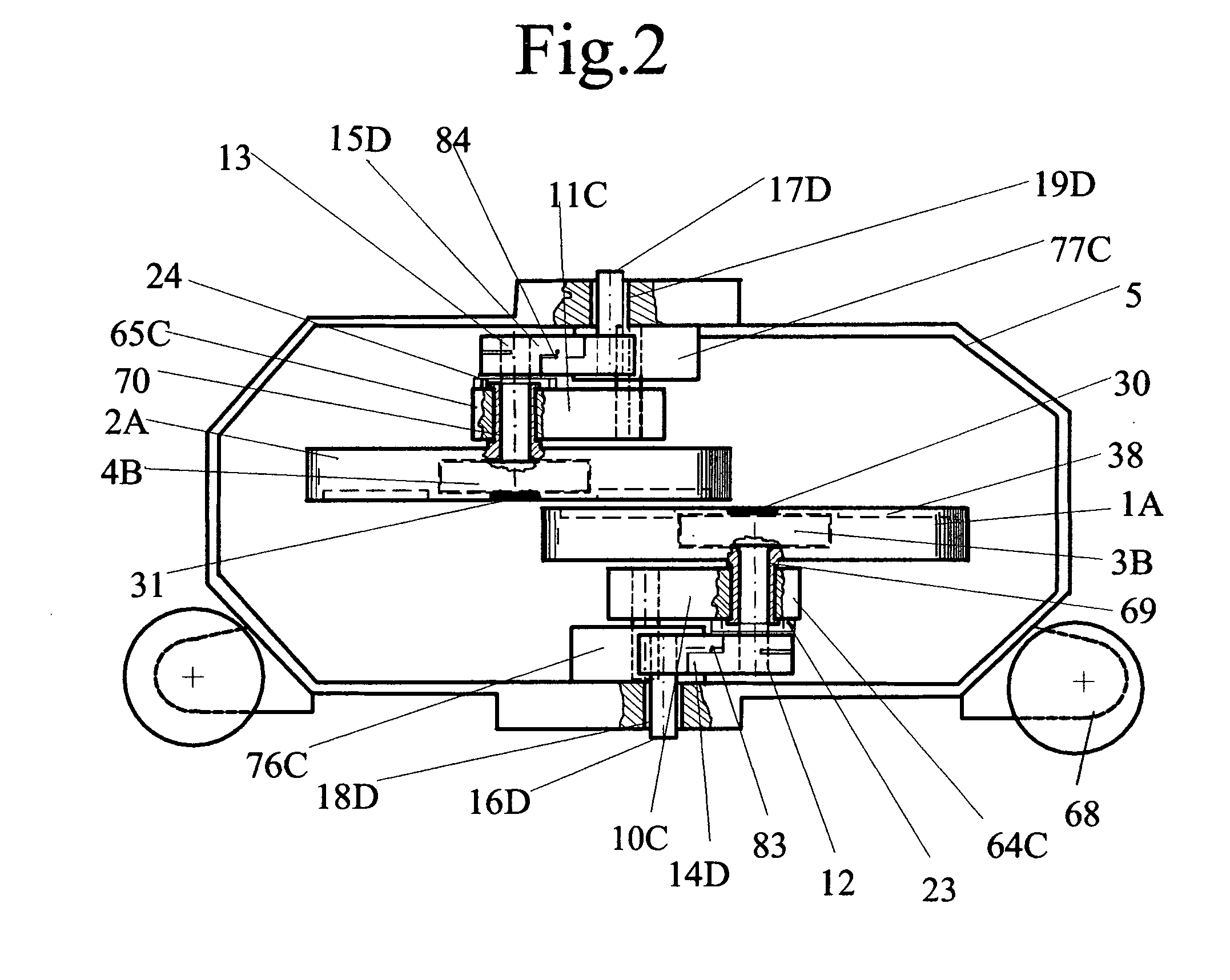

Method and device for self-contained inertial vehicular propulsion

Self-contained timely sequential inertial thrust drive pulses are generated by a tandem mechanical frequency modulated oscillator using the combined effort of linear and rotational inertial reluctance contained in the mass of paired flywheels. The flywheels are having parallel axial orientation with linear displaceable spacing, opposite free wheeling rotation and opposite alternate cyclic machine-logic optimized non-uniform reciprocal motion in union with vehicular travel direction. The combined effort of linear and rotational flywheel motion accomplishes the cyclic realignment of the flywheel motion into one timely gradient vector sum motivating thrust drive. A flywheel integral regenerative drive and rotor within each flywheel are used to obtain the cycle frequency modulation and non-uniform motions. The cyclic sum of all mutual reciprocal mass motion energy transactions represents a closed loop complex Cartesian grid motion with one self-contained superior centripetal inertial thrust drives pulse per each rotor cycle.

Owner:GUTSCHE GOTTFRIED J

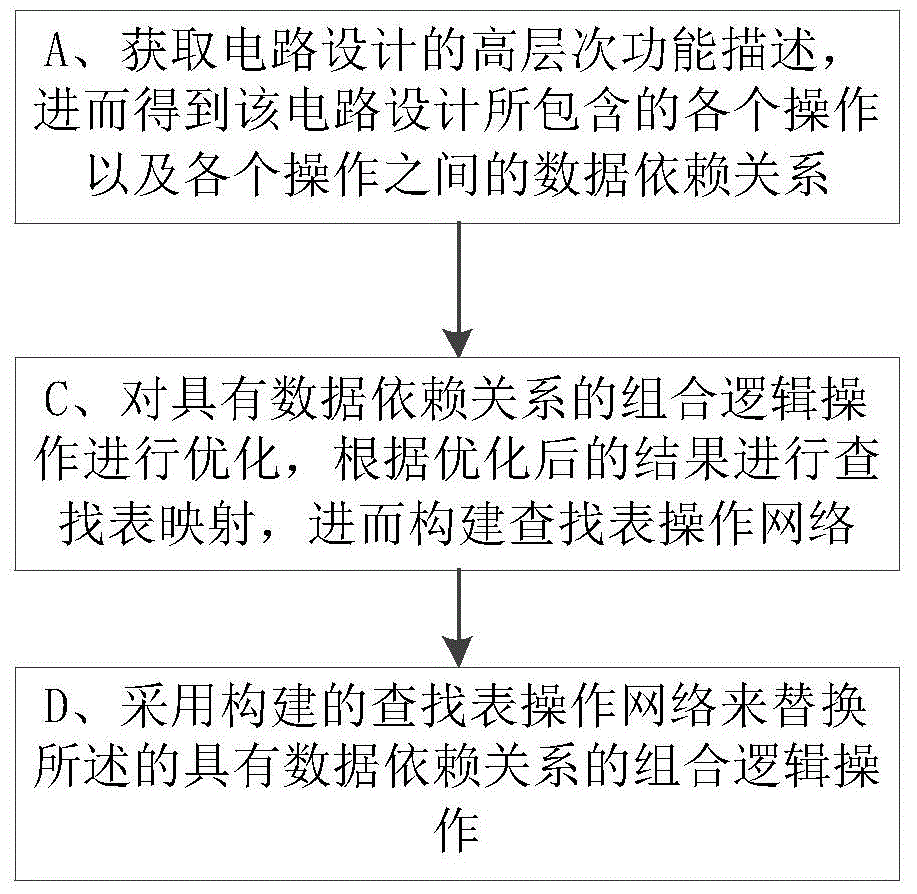

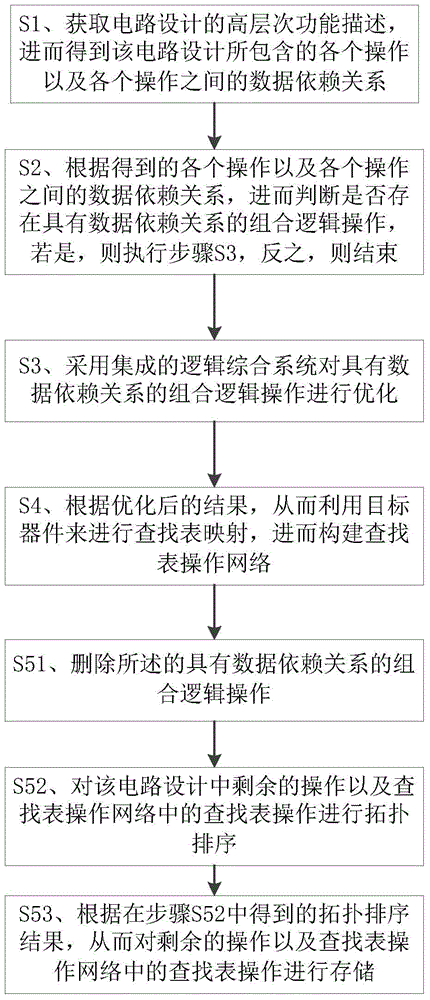

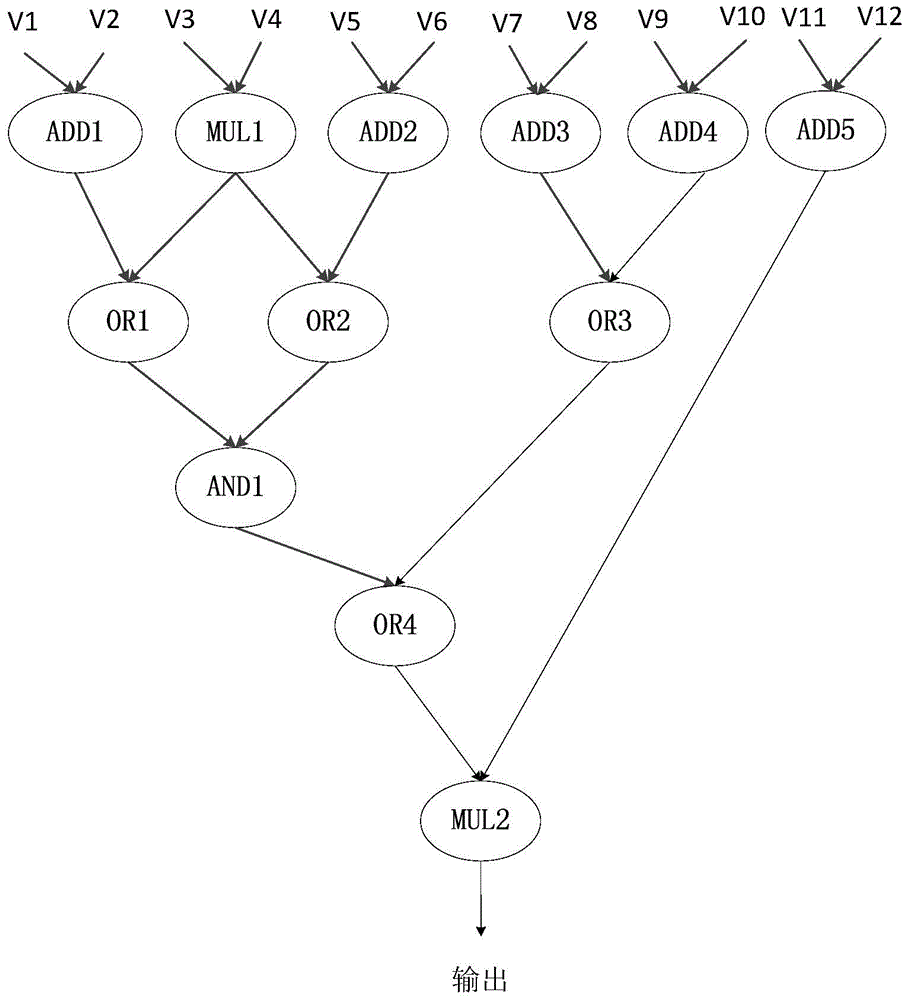

Combinational logic optimization method and system in high-level synthesis

ActiveCN104408232AExcellent build performanceReduce redundancySpecial data processing applicationsLogic optimizationTheoretical computer science

The invention discloses a combinational logic optimization method and system in high-level synthesis. The combinational logic optimization system in the high-level synthesis comprises an obtaining unit, a combinational logic optimization mapping unit and a reconstruction unit. The combinational logic optimization method in the high-level synthesis comprises the following steps of obtaining operations designed in a circuit and a data dependence relationship between the operations; optimizing the combinational logic operations having the data dependence relationship, performing lookup table mapping according to an optimized result, and accordingly constructing a lookup table operation network; replacing the combinational logic operations having the data dependence relationship with the lookup table operation network. The combinational logic optimization method and system in the high-level synthesis can optimize the designing combinational logic in a high-level synthesis stage, remove redundant combinational logic calculations, introduce bottom layer hardware information to the high-level synthesis by adding the lookup table operation, provide more accurate combinational logic time delay and resource expenditure information for a follow-up high-level synthesis step, are beneficial to improvement of performance of each high-level synthesis tool, and can be widely applied to the hardware design field.

Owner:SUN YAT SEN UNIV

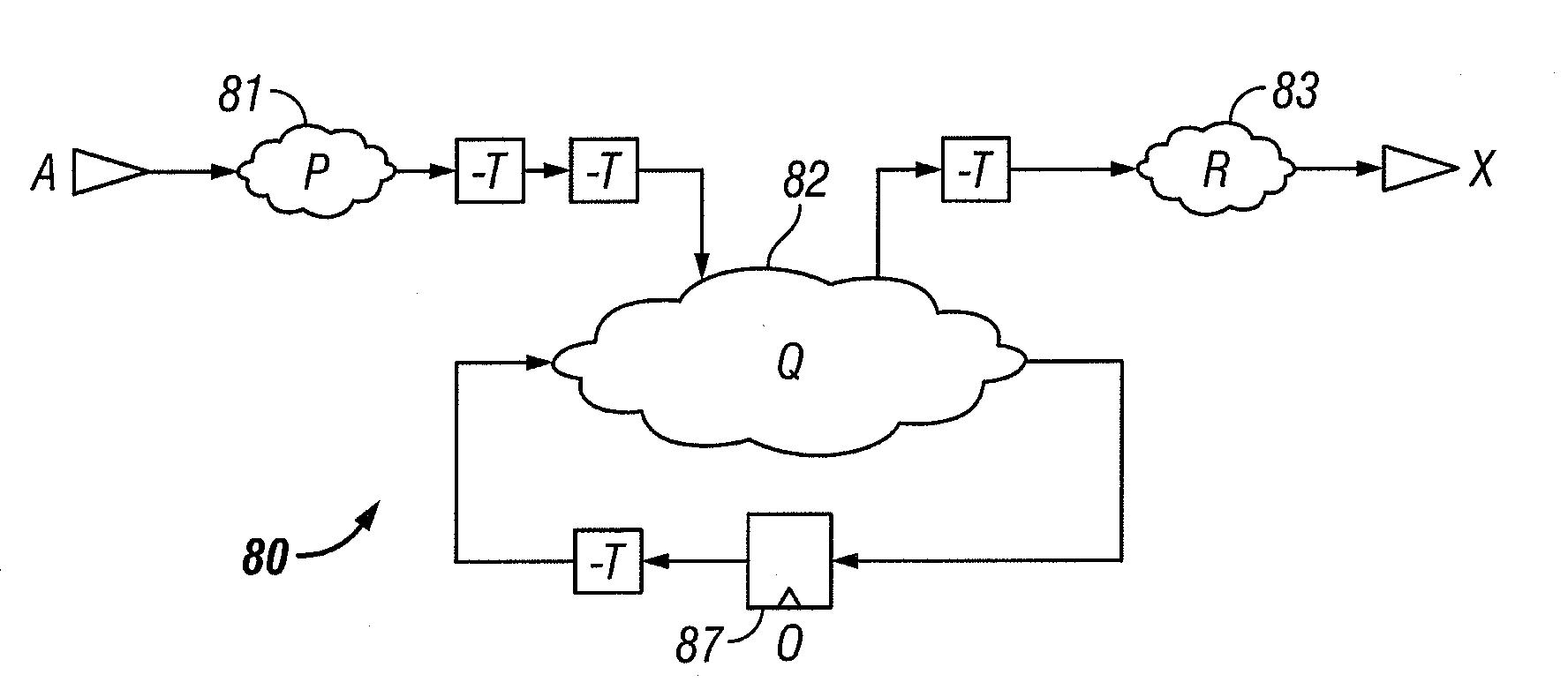

Method to optimize net lists using simultaneous placement and logic optimization

InactiveUS6523161B1Improve circuit performanceGood signalSemiconductor/solid-state device manufacturingComputer aided designLogic optimizationFunction optimization

Method to optimize net lists used in the design and fabrication of integrated circuits by using simultaneous placement optimization, logic function optimization and net buffering algorithms. Method simultaneously obtains a placement of logic functions, mapping of logic functions on to library elements and buffering of nets connecting the logic functions.

Owner:SYNOPSYS INC

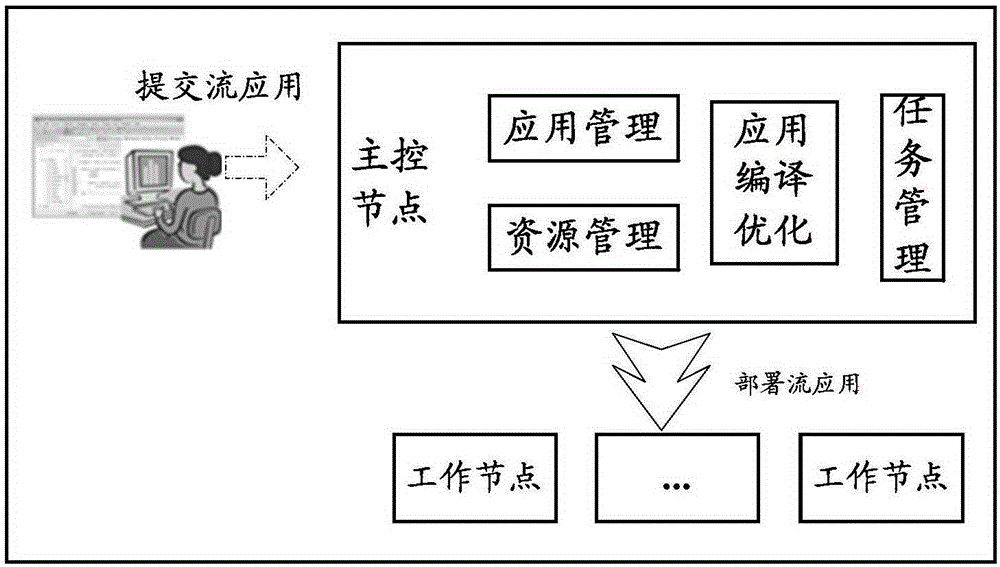

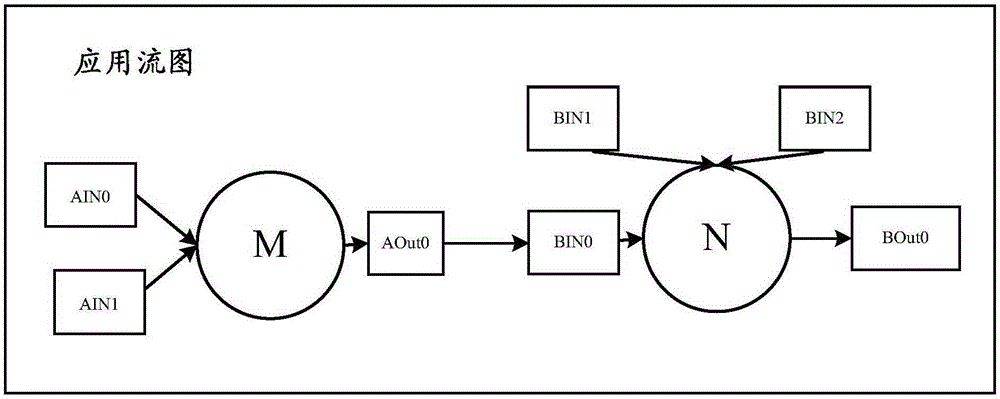

Stream application optimization method and apparatus

ActiveCN106547522AImprove computing powerSpecific program execution arrangementsData streamParallel computing

The invention discloses a stream application optimization method. The method comprises the steps of obtaining an application stream graph and an initial operator code of a to-be-optimized stream application, wherein the application stream graph comprises an operator, and the initial operator code is used for describing initial operation logic born by the operator; determining a data stream graph of the operator according to the initial operator code; determining a hotspot path in a plurality of paths of the data stream graph according to the data stream graph of the operator and the initial operation logic born by the operator, wherein each of the paths represents arithmetic logic, and the hotspot path is arithmetic logic of which a usage frequency meets a preset condition in the arithmetic operation process; and optimizing a local operator code corresponding to the hotspot path so as to obtain an optimized operator code. According to the stream application optimization method provided by an embodiment of the invention, the operator code can be automatically optimized, so that the usability and computing performance of the stream application are improved.

Owner:HUAWEI TECH CO LTD