Patents

Literature

107 results about "State logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A state logic control system is a programming method created for PLCs. A state logic control system uses a state transition diagram as a model of reality, thus using the fundamentals of finite-state machine theory as the basis of a programming language. State logic enables users to model the application they are trying to control by using a hierarchy that consists of Tasks, subdivided by States which are described by Statements.

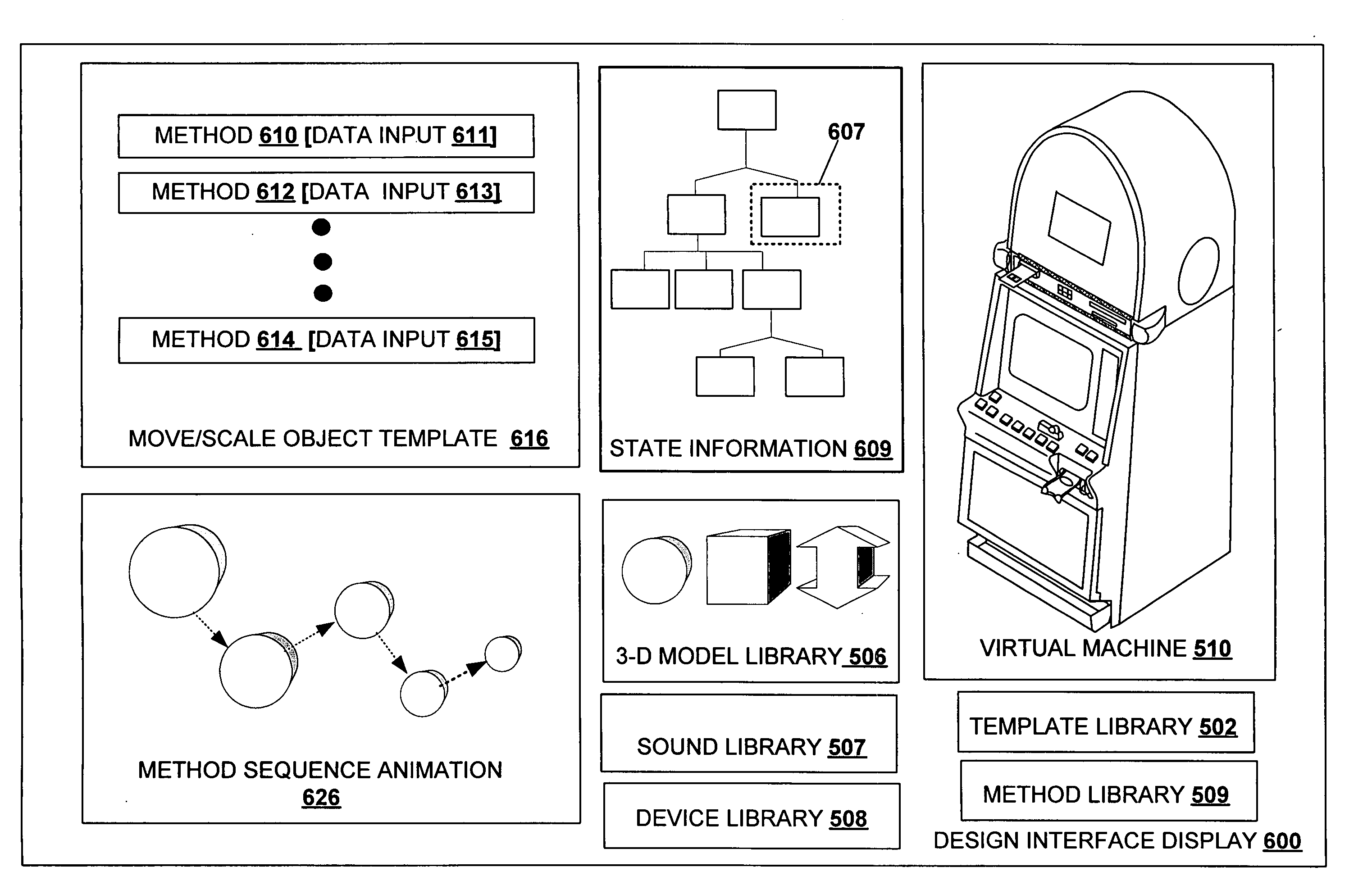

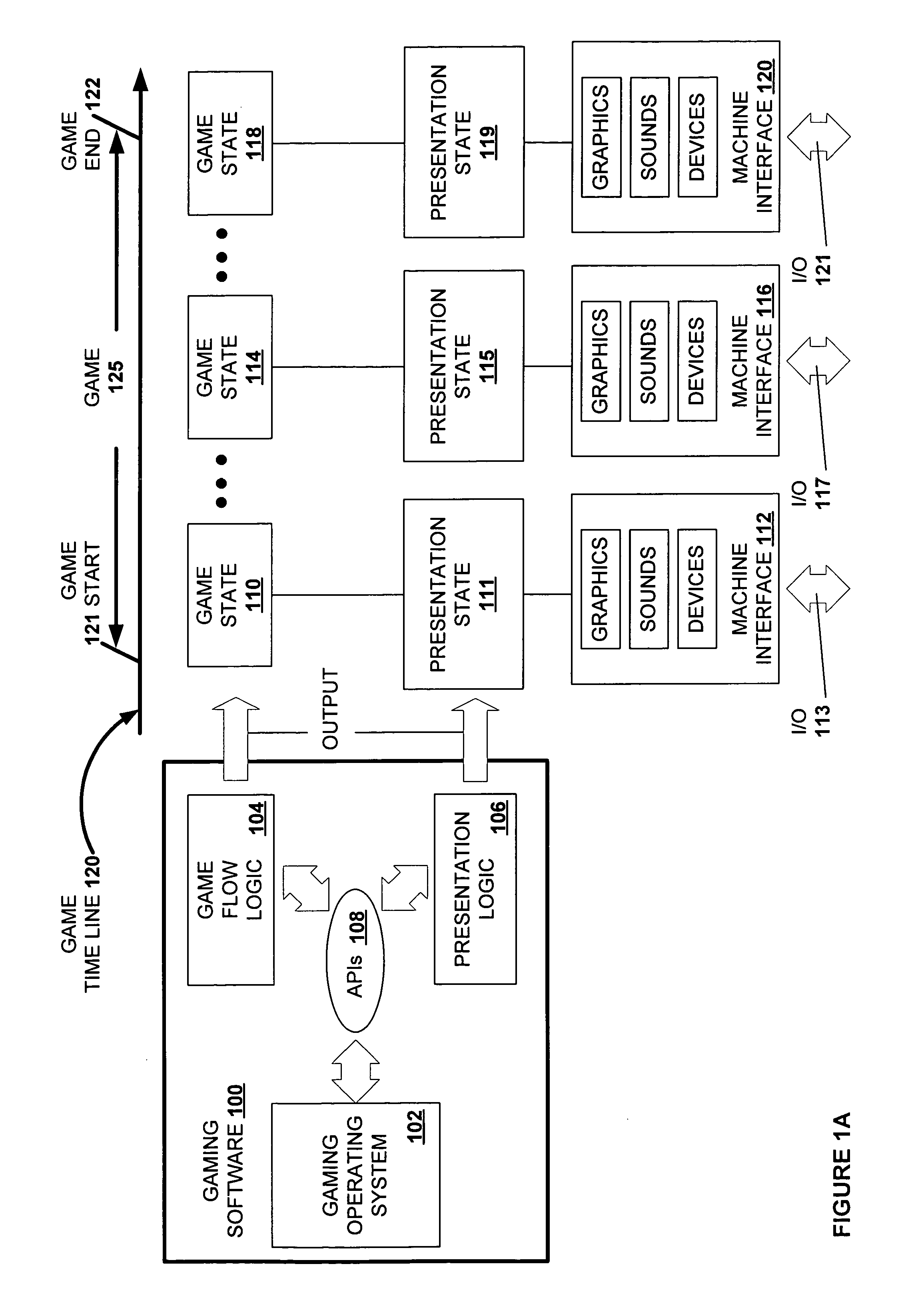

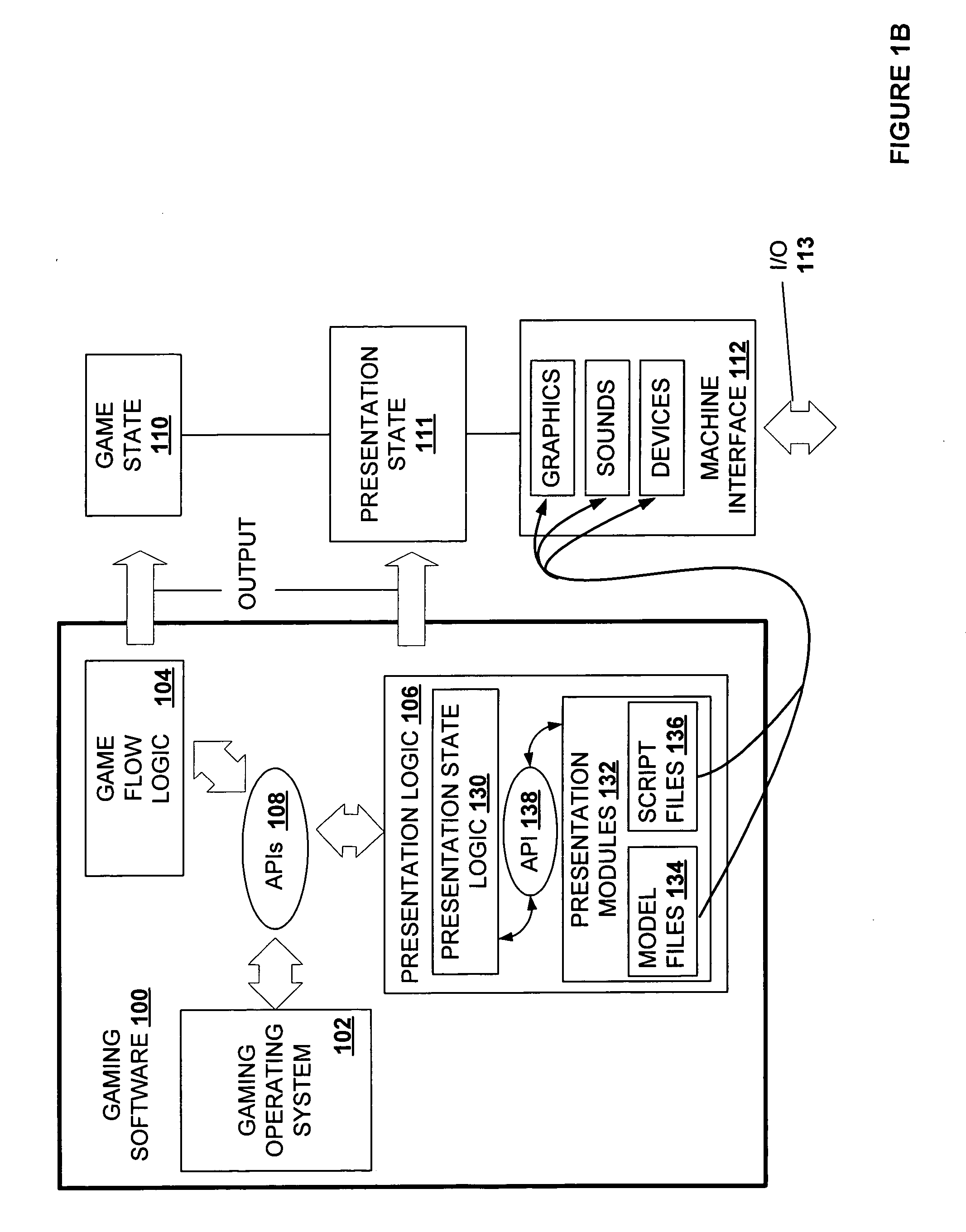

Decoupling of the graphical presentation of a game from the presentation logic

ActiveUS20050192092A1Apparatus for meter-controlled dispensingVideo gamesGraphicsSoftware architecture

Owner:IGT

Anti-tear protection for smart card transactions

InactiveUS6727802B2Avoid collisionShorten transaction timeMemory record carrier reading problemsUnauthorized memory use protectionInformation processingProduct system

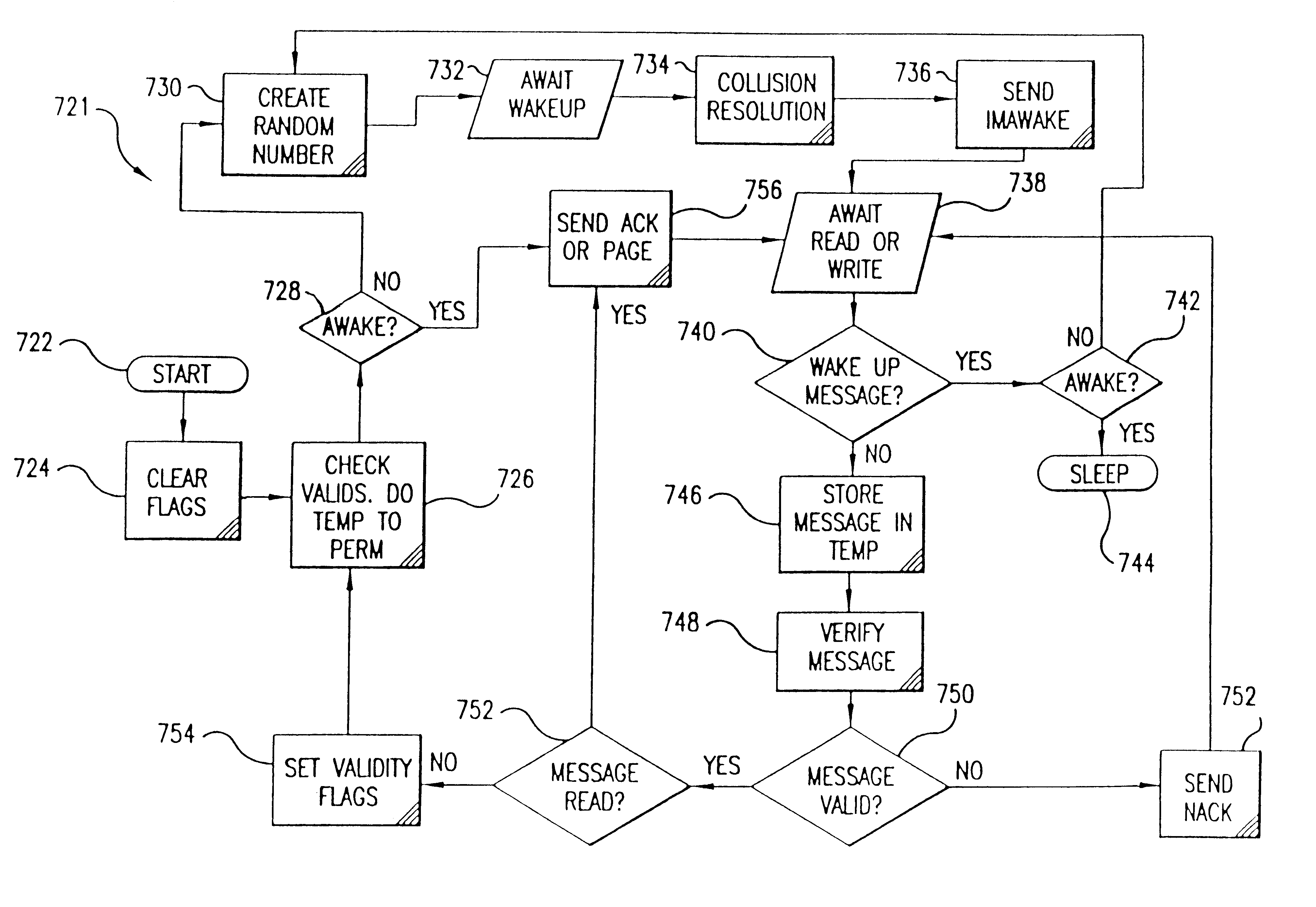

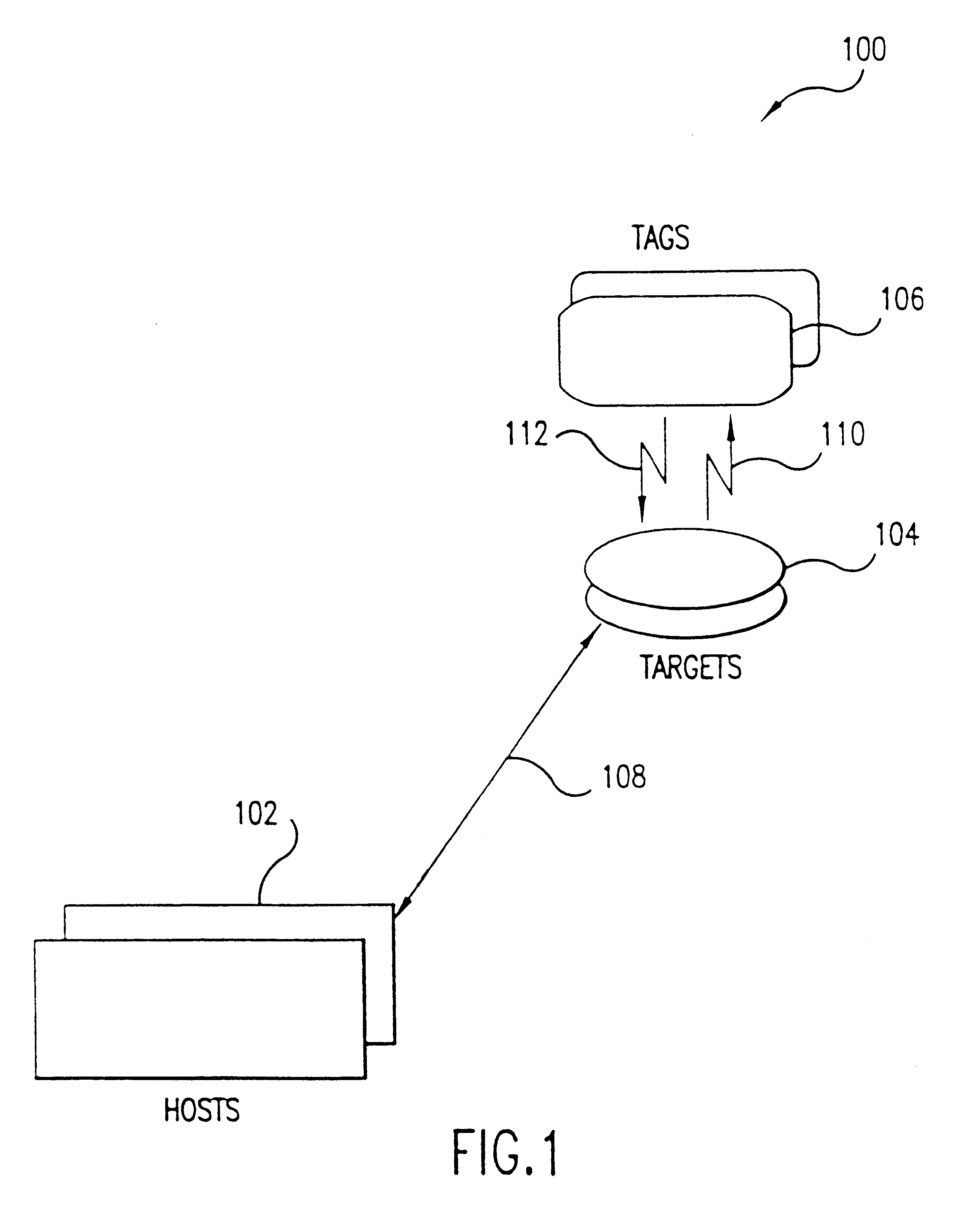

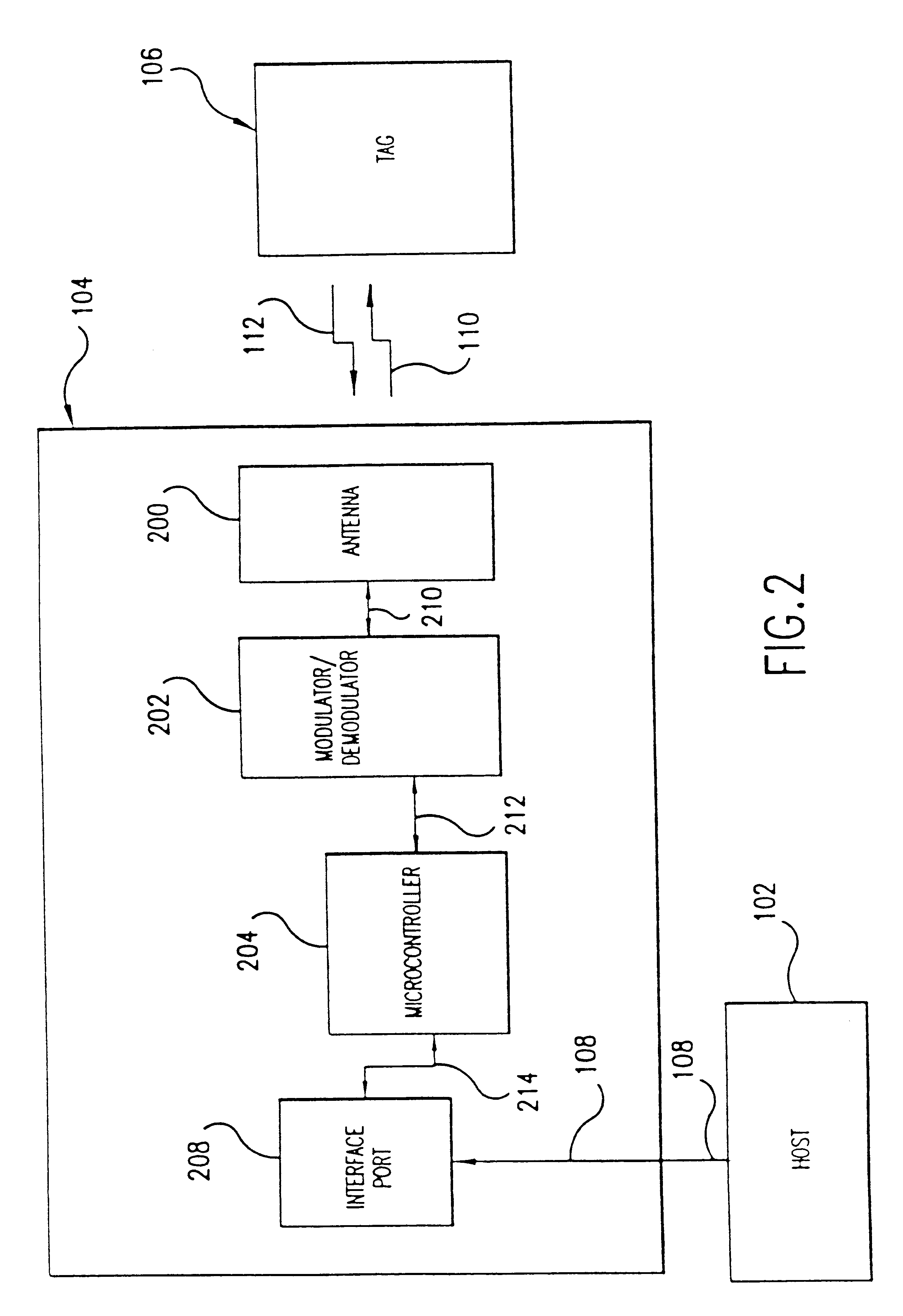

A fast data transfer collection system using message authentication and contactless RF proximity card technology in non-contact storage and retrieval applications. The system is generally comprised of Host computers (application computer systems), Target radio frequency (RF) terminals, and a plurality of portable Tags ("smart" or "proximity" cards). A Host provides specific application functionality to a Tag holder, with a high degree of protection from fraudulent use. A Target provides control of the RF antenna and resolves collisions between multiple Tags in the RF field. A Tag provides reliable, high speed, and well authenticated secure exchanges of data / information with the Host resulting from the use of a custom ASIC design incorporating unique analog and digital circuits, nonvolatile memory, and state logic. Each Tag engages in a transaction with the Target in which a sequence of message exchanges allow data to be read(written) from(to) the Tag. These exchanges establish the RF communication link, resolve communication collisions with other Tags, authenticate both parties in the transaction, rapidly and robustly relay information through the link, and ensure the integrity and incorruptibility of the transaction. The system architecture provides capabilities to ensure the integrity of the data transferred thus eliminating the major problem of corrupting data on the card and in the system. The architecture and protocol are designed to allow simple and efficient integration of the transaction product system into data / information processing installations.

Owner:KELLY GUY M +3

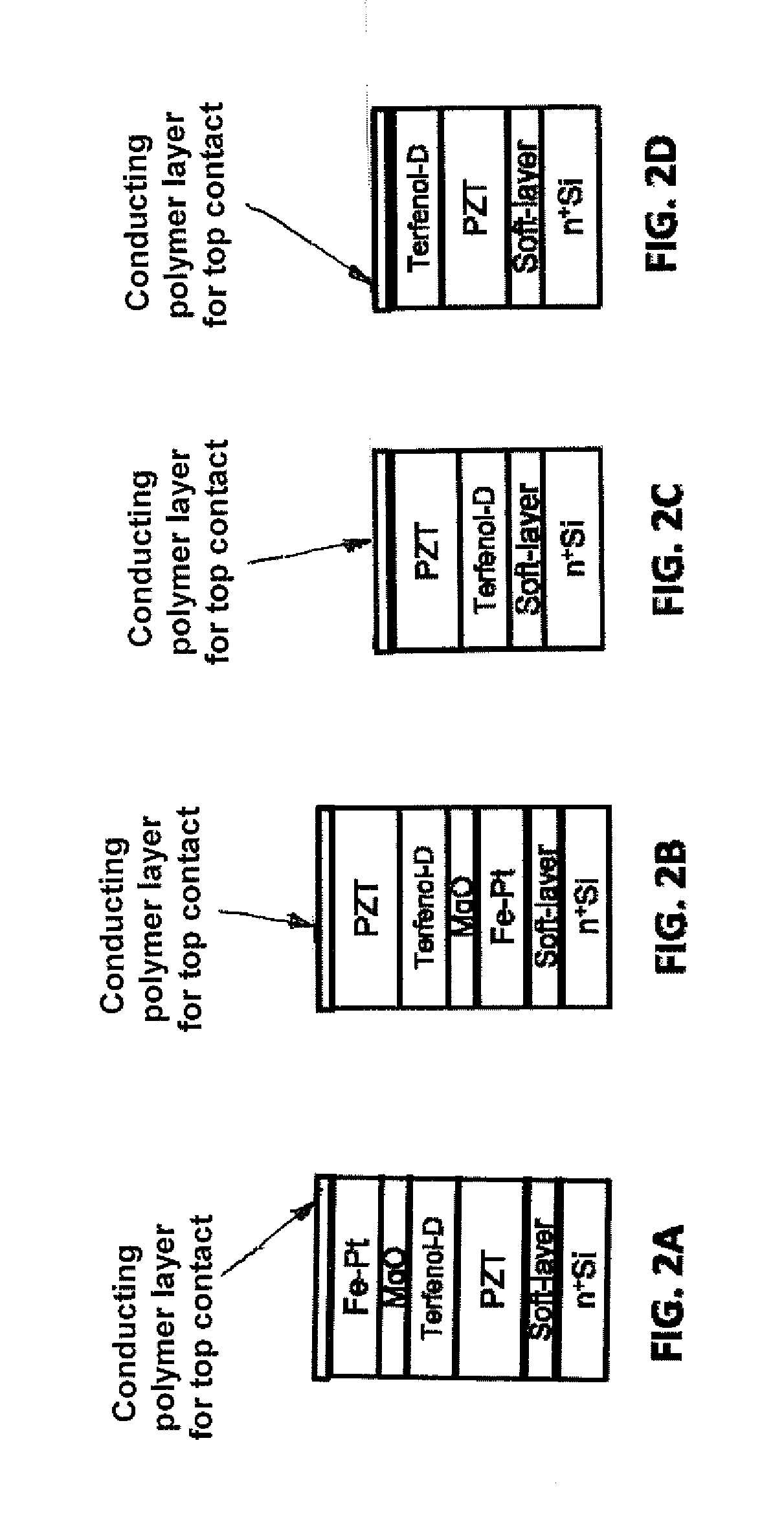

Planar Multiferroic/Magnetostrictive Nanostructures as Memory Elements, Two-Stage Logic Gates and Four-State Logic Elements for Information Processing

InactiveUS20120267735A1Energy efficiencyMinimize dipole momentSolid-state devicesSemiconductor/solid-state device manufacturingInformation processingNanomagnet

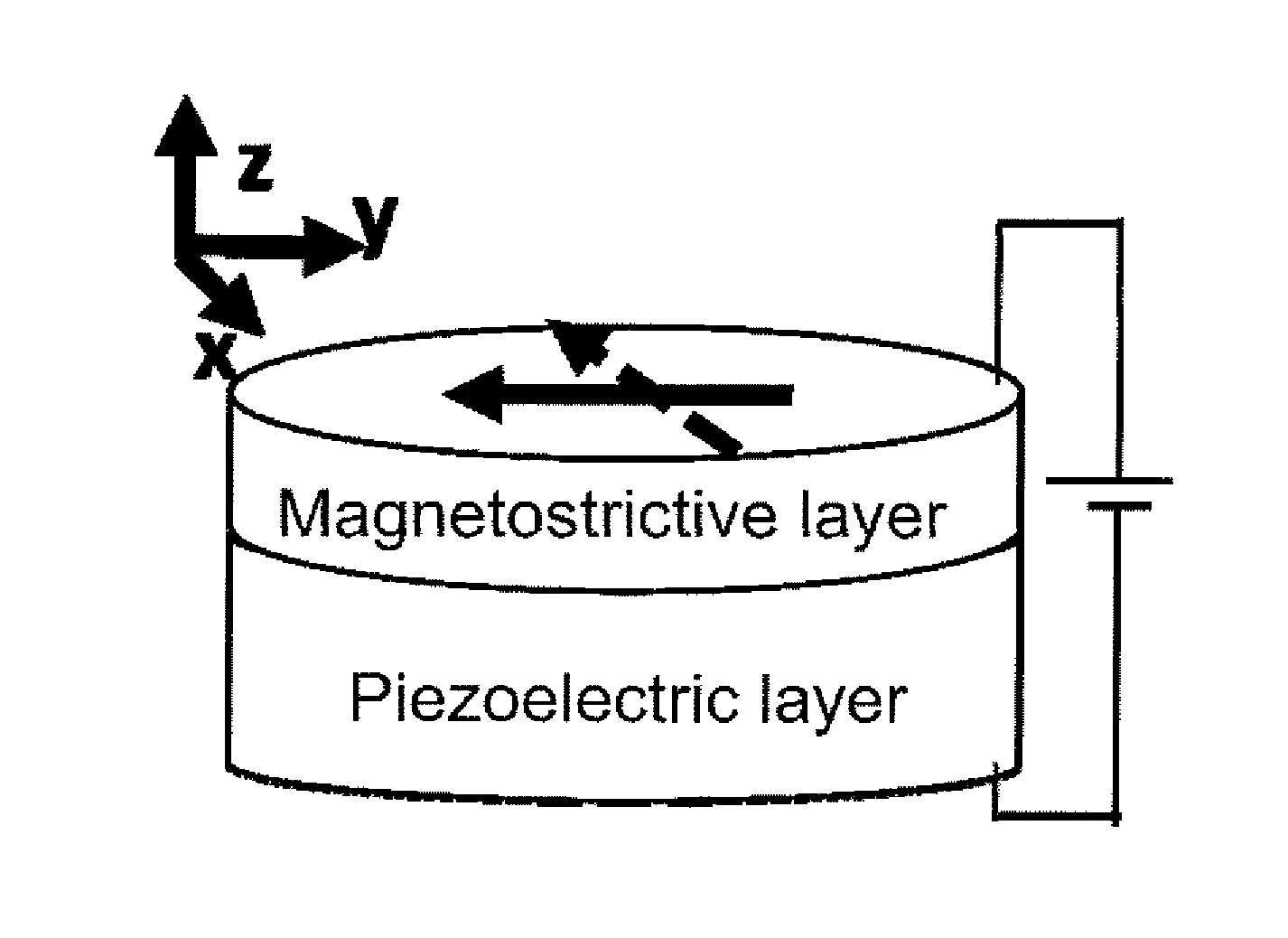

A magnetostrictive-piezoelectric multiferroic single- or multi-domain nanomagnet whose magnetization can be rotated through application of an electric field across the piezoelectric layer has a structure that can include either a shape-anisotropic mangnetostrictive nanomagnet with no magnetocrystalline anisotropy or a circular nanomagnet with biaxial magnetocrystalline anisotropy with dimensions of nominal diameter and thickness. This structure can be used to write and store binary bits encoded in the magnetization orientation, thereby functioning as a memory element, or perform both Boolean and non-Boolean computation, or be integrated with existing magnetic tunneling junction (MTJ) technology to perform a read operation by adding a barrier layer for the MTJ having a high coercivity to serve as the hard magnetic layer of the MTJ, and electrical contact layers of a soft material with small Young's modulus. Equivalently, mangnetostrictive nanomagnetic elements whose magnetization is rotated by strain transferred from the substrate that has acoustic waves propagating on the substrate can be used.

Owner:VIRGINIA COMMONWEALTH UNIV

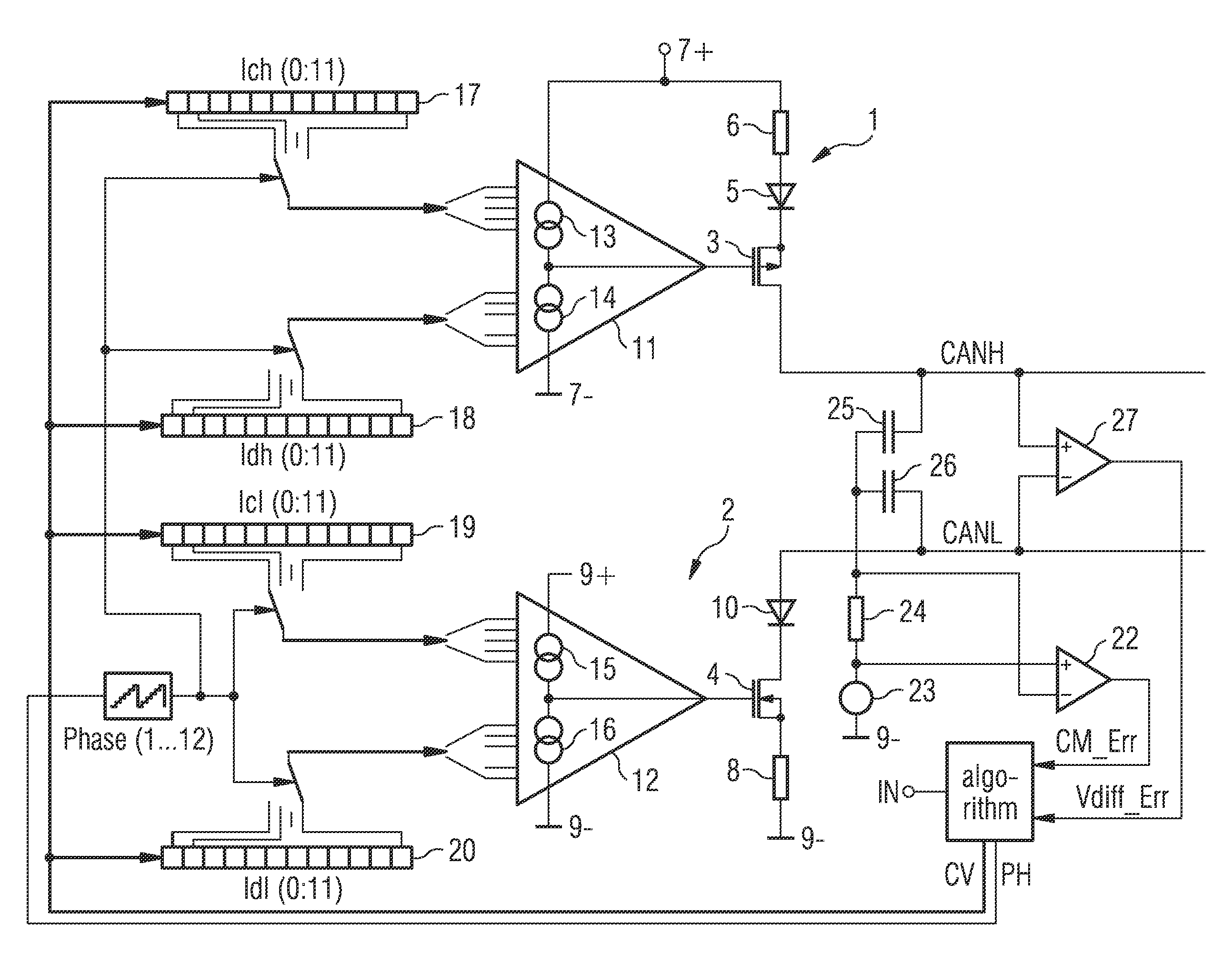

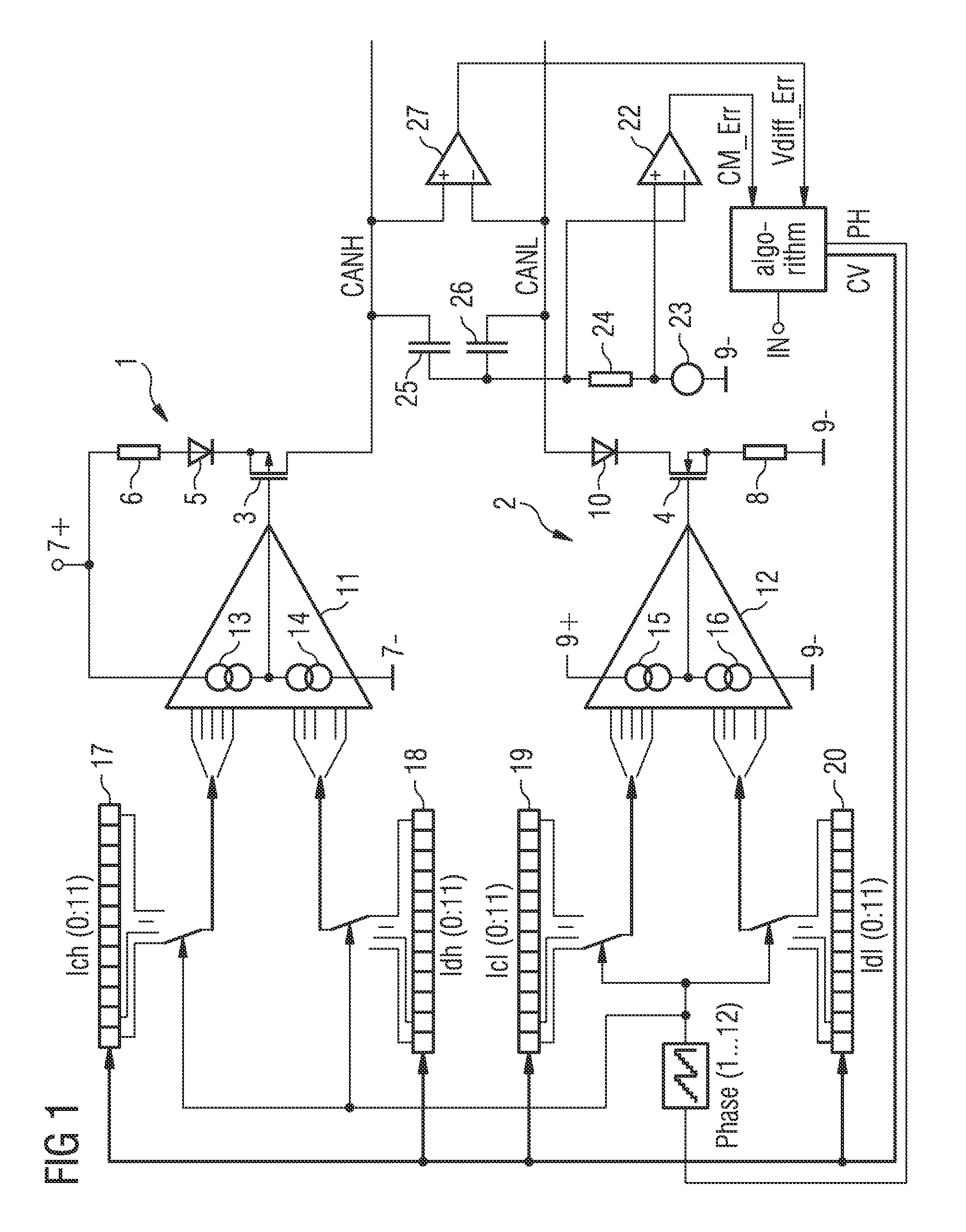

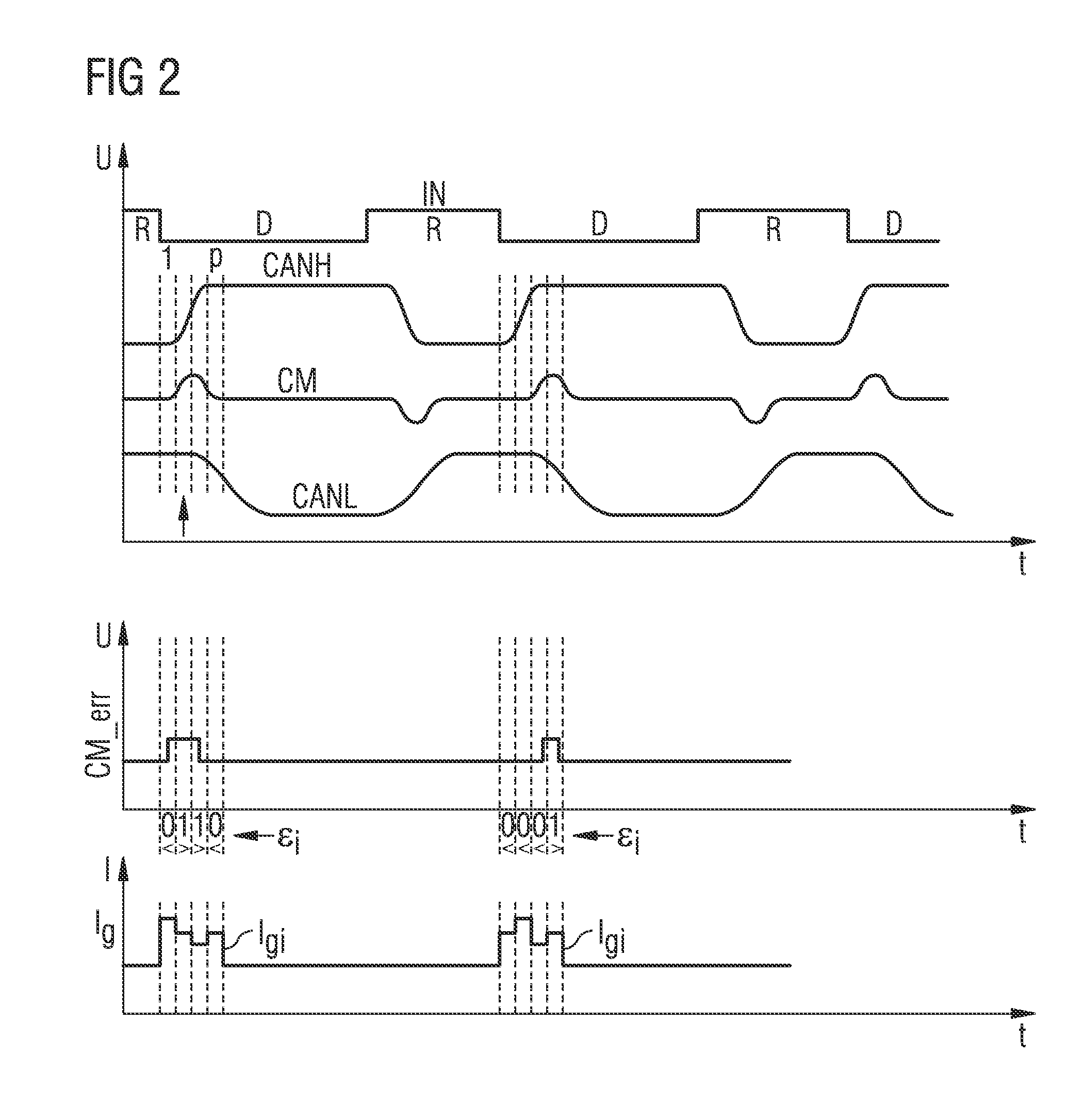

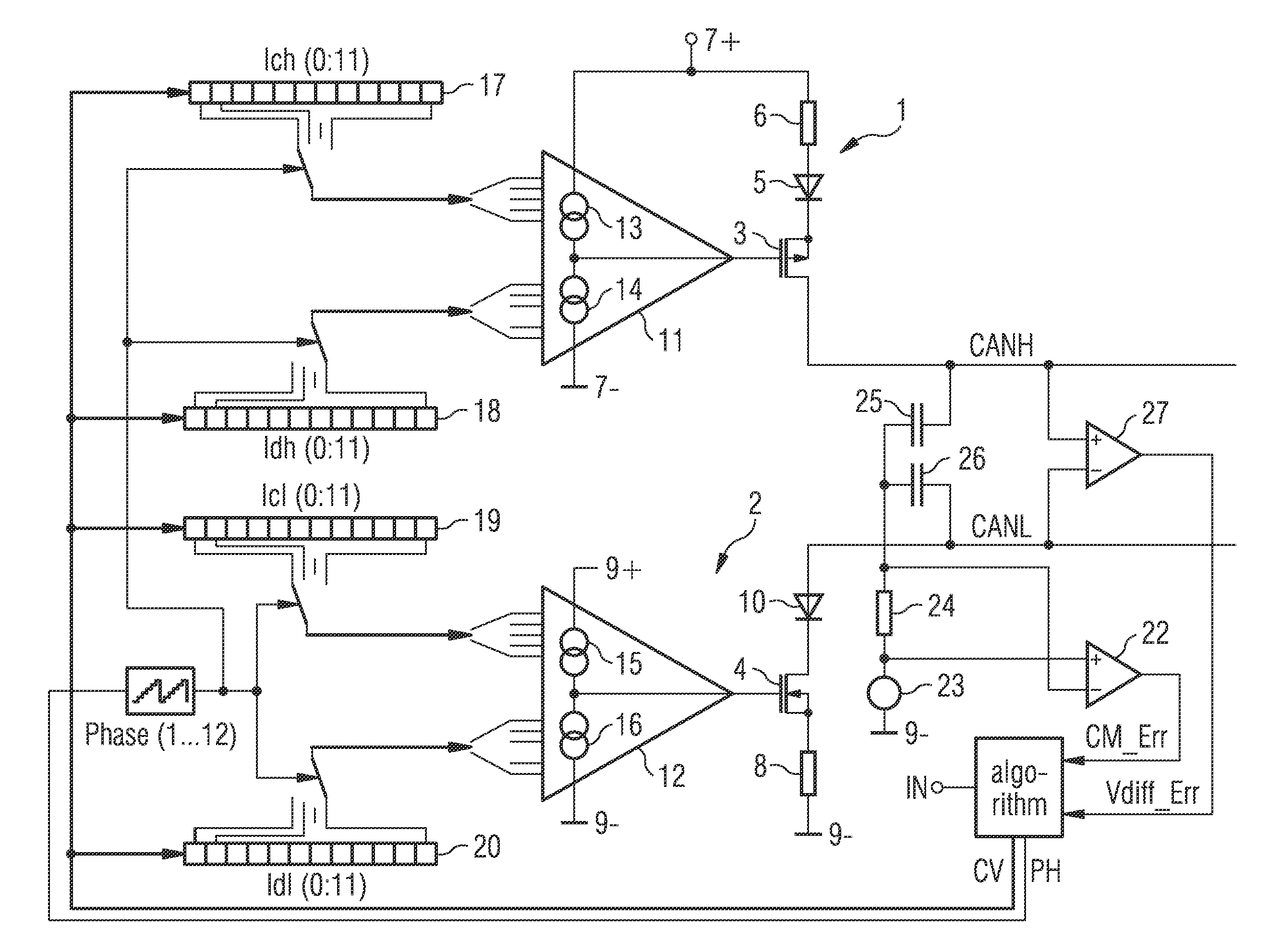

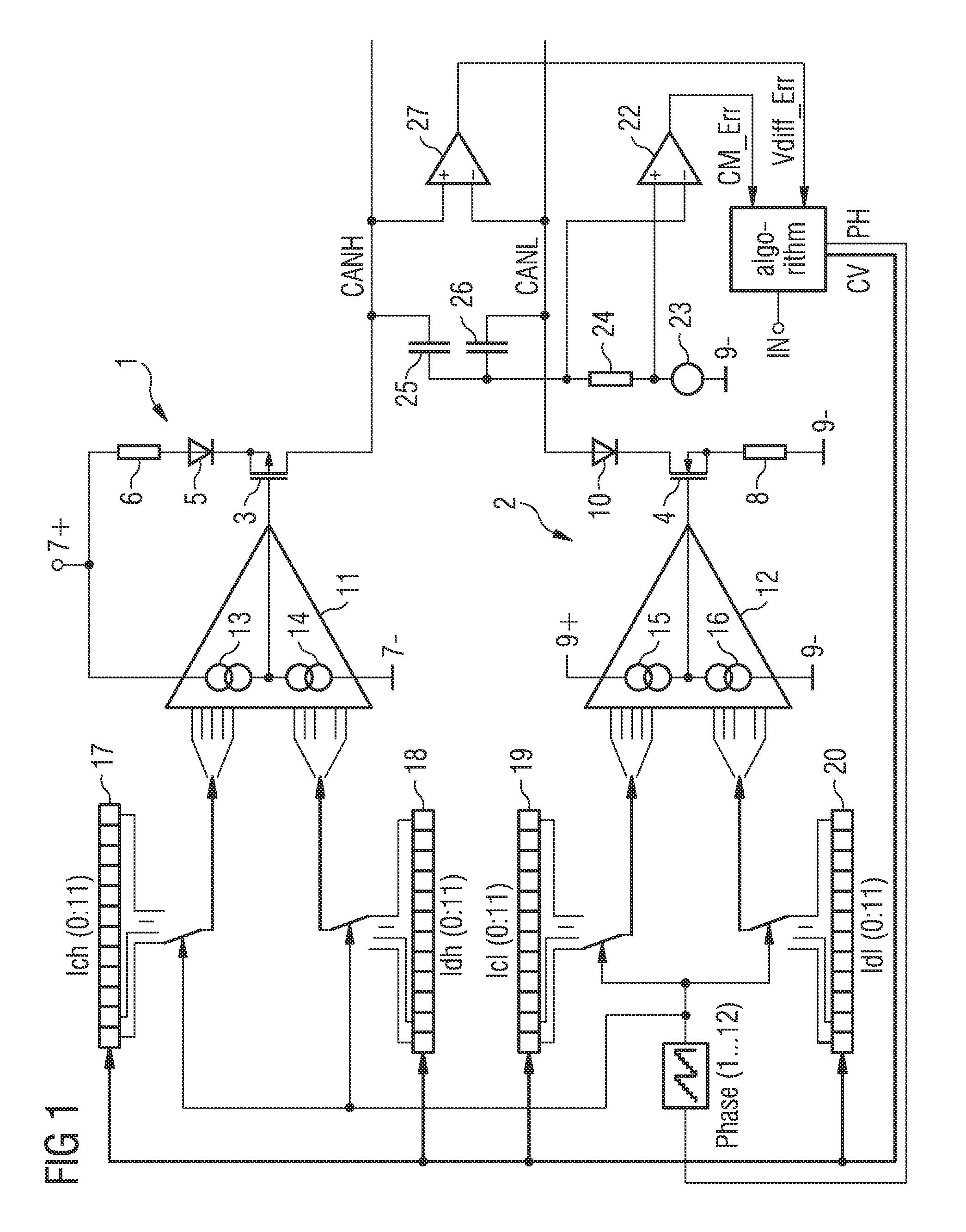

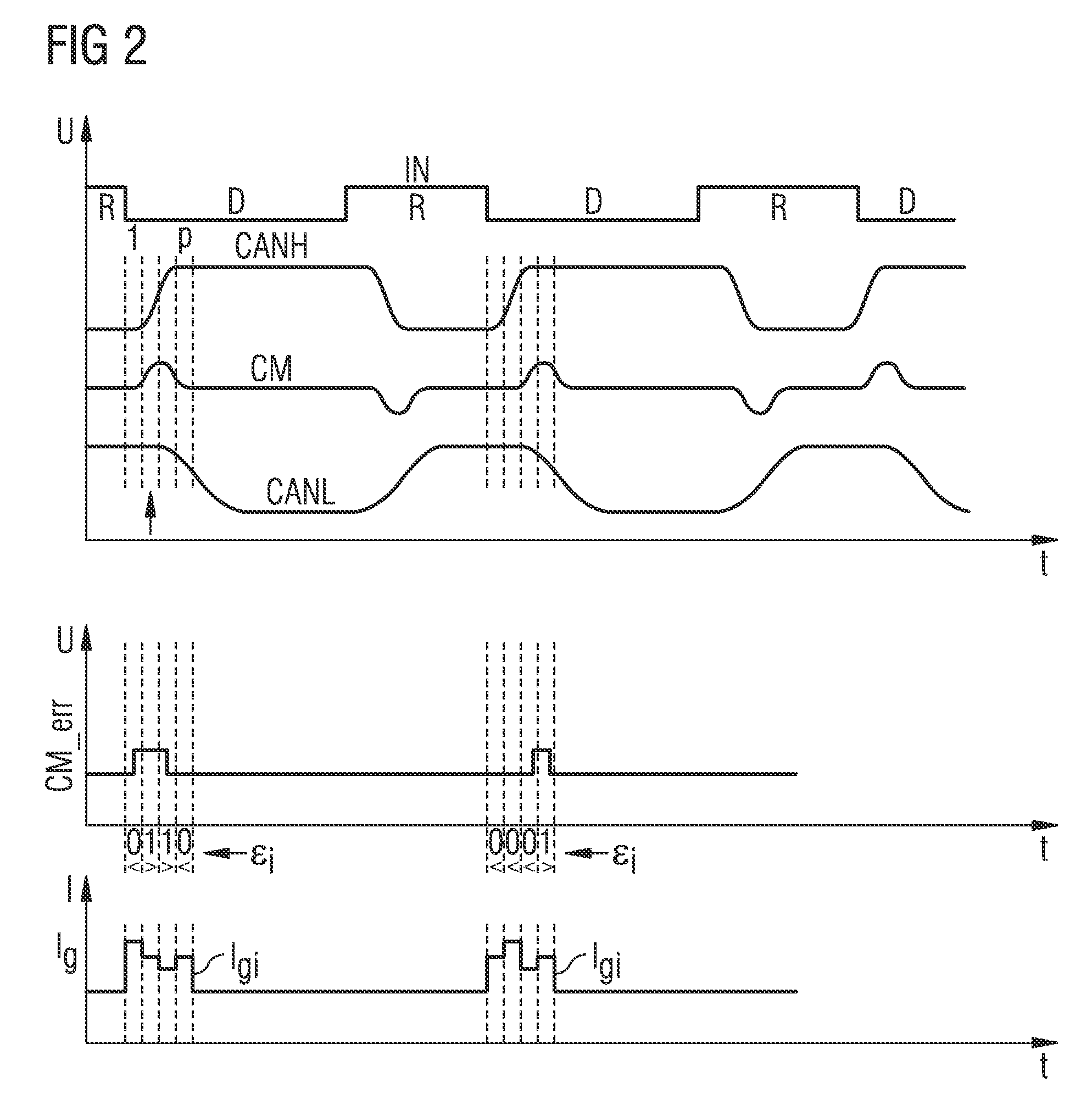

Driver Circuit for a Two-Wire Conductor and Method for Generating Two Output Currents for a Two-Wire Conductor

ActiveUS20100201399A1Reliability increasing modificationsTransmission control/equlisationDriver circuitState variation

A driver circuit and method for generating two complementary output currents from a two-state logic input signal at two outputs for connecting a two-wire conductor provide the following actions: generating from the input signal, an output signal at each output, the amperage of one of the output currents being adjustable by a control signal; analyzing each voltage materializing at the outputs; generating an error signal as a function of the output voltages within each of at least two time slots subsequent to a change in state of the input signal; caching the error signals or signals derived therefrom and adjusting, as a function of cached error signals or of the cached signals as a function thereof, the output current in corresponding time slots subsequent to a resulting change in state of the input signal.

Owner:INFINEON TECH AG

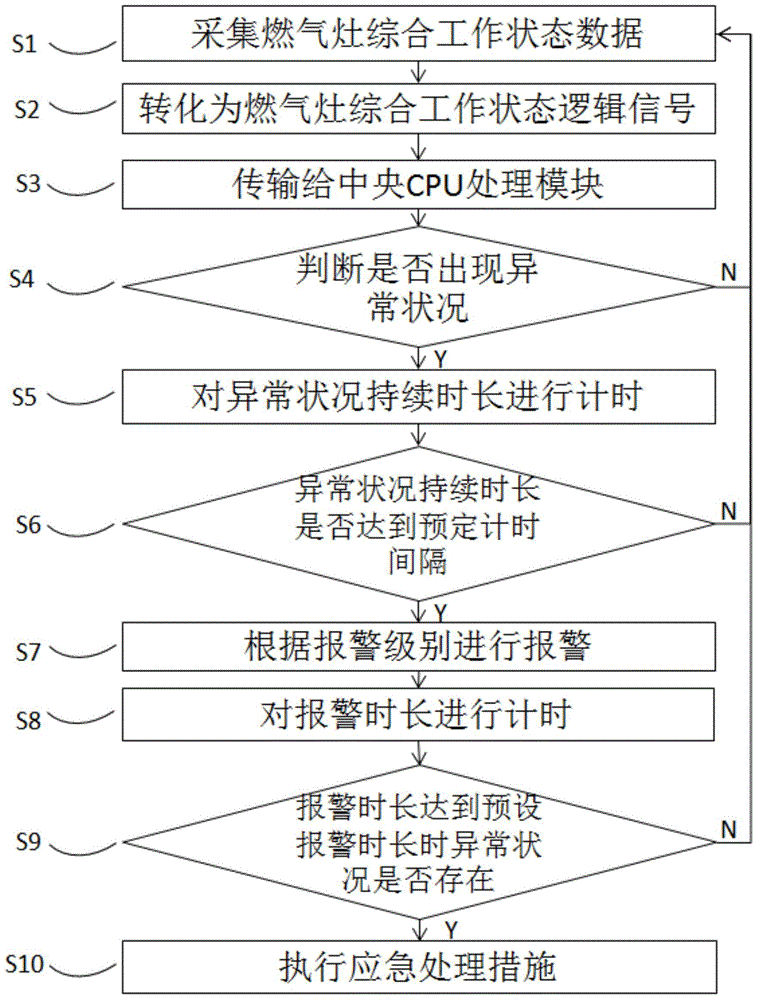

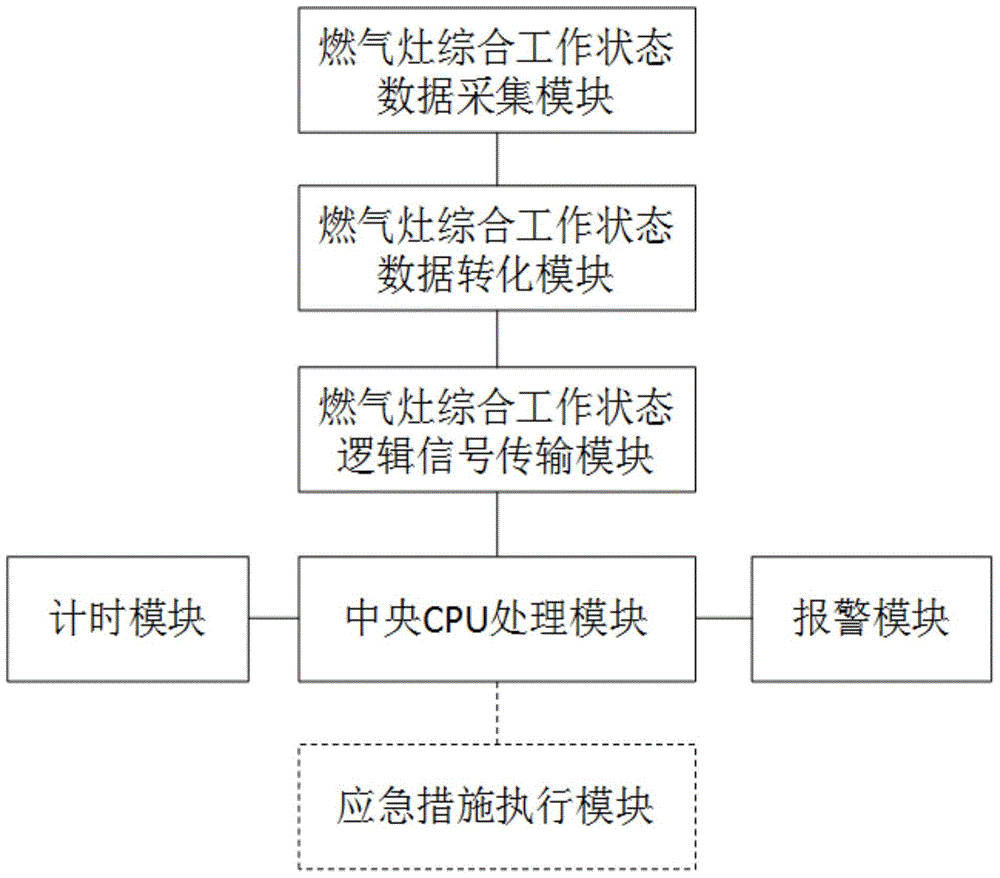

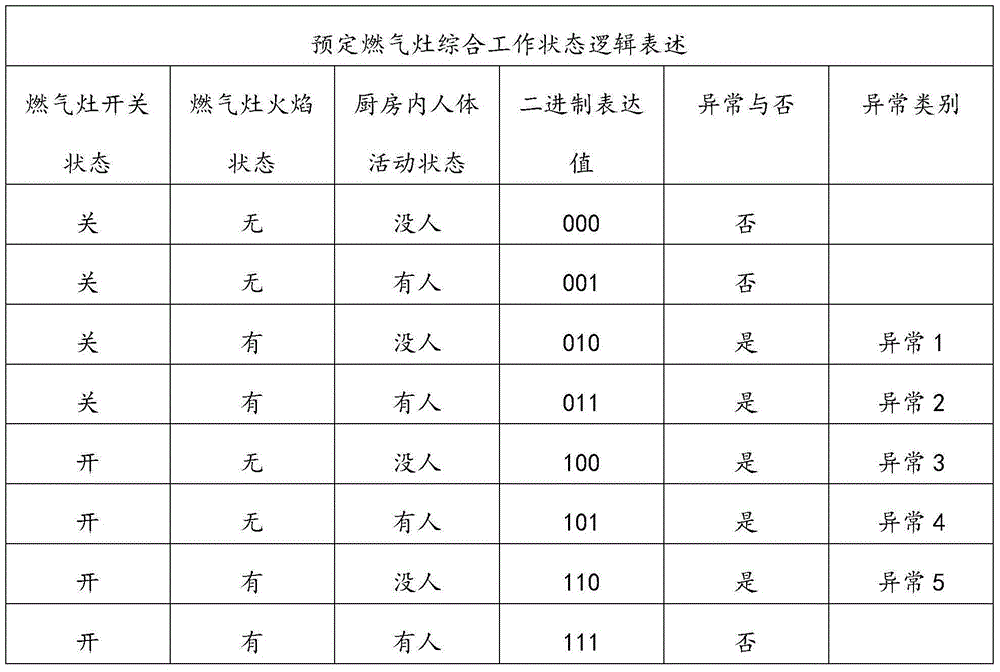

Method for carrying out safety monitoring and early warning on kitchen work environment and system

ActiveCN105045190AAvoid dangerAvoid safety accidentsProgramme controlComputer controlEarly warning systemProcess module

The present invention relates to a method for carrying out safety monitoring and early warning on a kitchen working environment and a system. The method comprises the following steps that gas stove integrated operating state data is collected and converted into a gas stove integrated operating state logic signal and is transmitted to a central CPU processing module, the central CPU processing module carries out abnormal condition judgment on the gas stove integrated operating state logic signal according to a predetermined gas stove integrated work state logic representation, if an abnormal condition is judged, the duration of the abnormal condition is counted, the central CPU processing module judges whether the duration of the abnormal condition reaches a predetermined timed interval, if so, the alarming is carried out according to an alarm level and the alarm duration is counted, the central CPU processing module judges whether the abnormal condition exists or not when the alarm duration reaches a predetermined alarm time duration, and if the abnormal condition still exists, emergency measures are implemented. According to the method and the system, the intelligent monitoring, classification process and multi-level warning of the kitchen working environment can be realized, and the safety performance is high.

Owner:烟台华绅智能科技有限公司

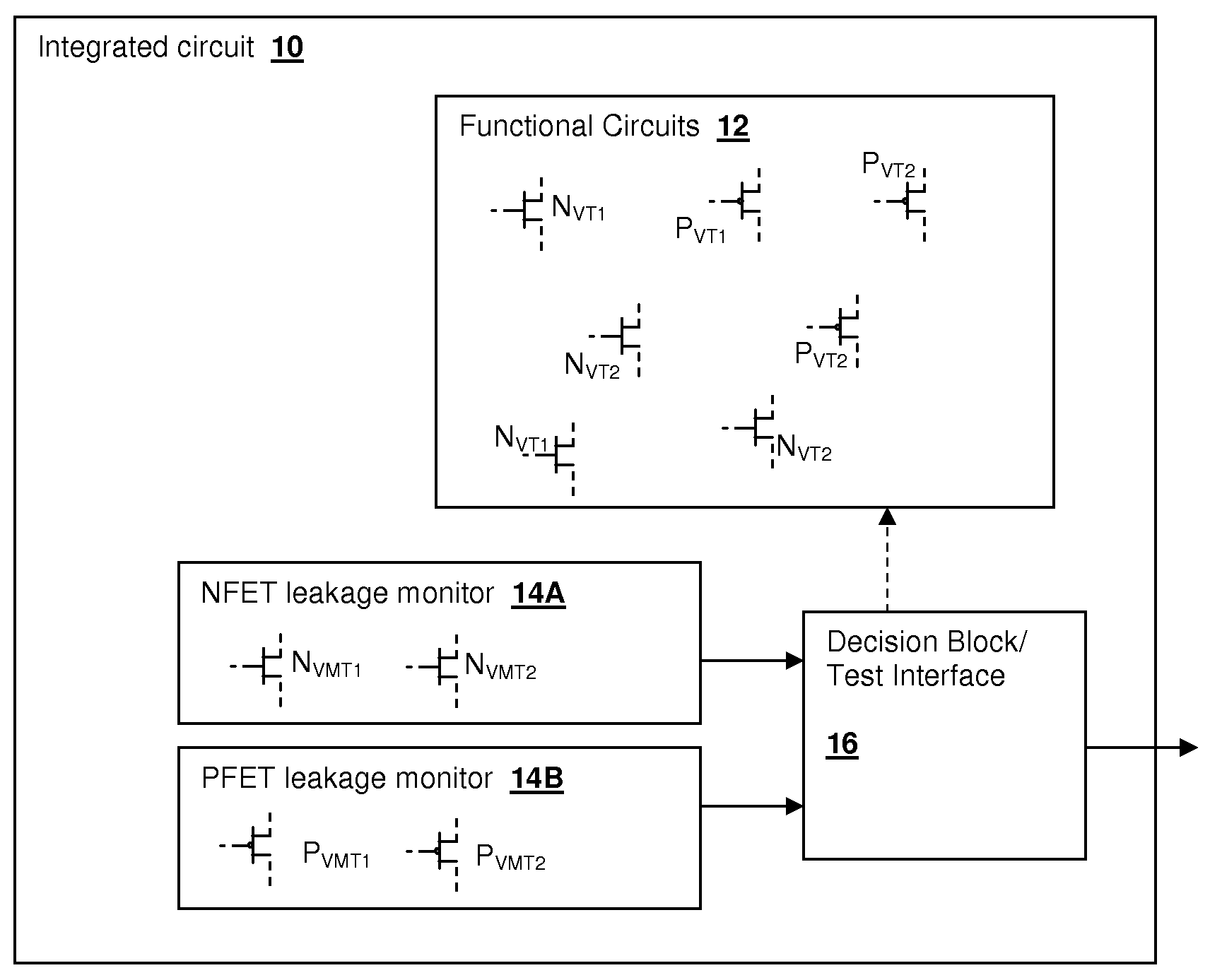

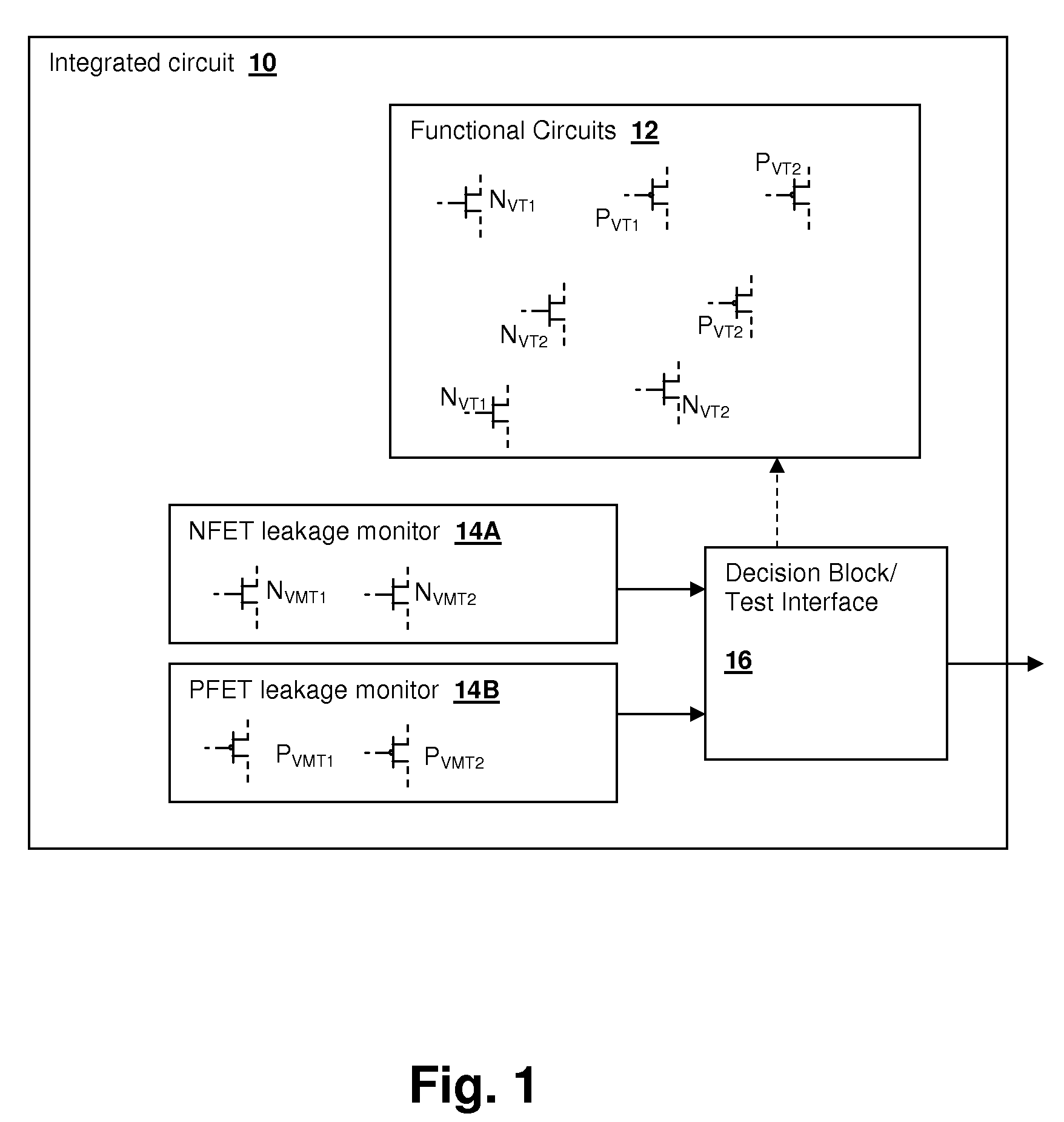

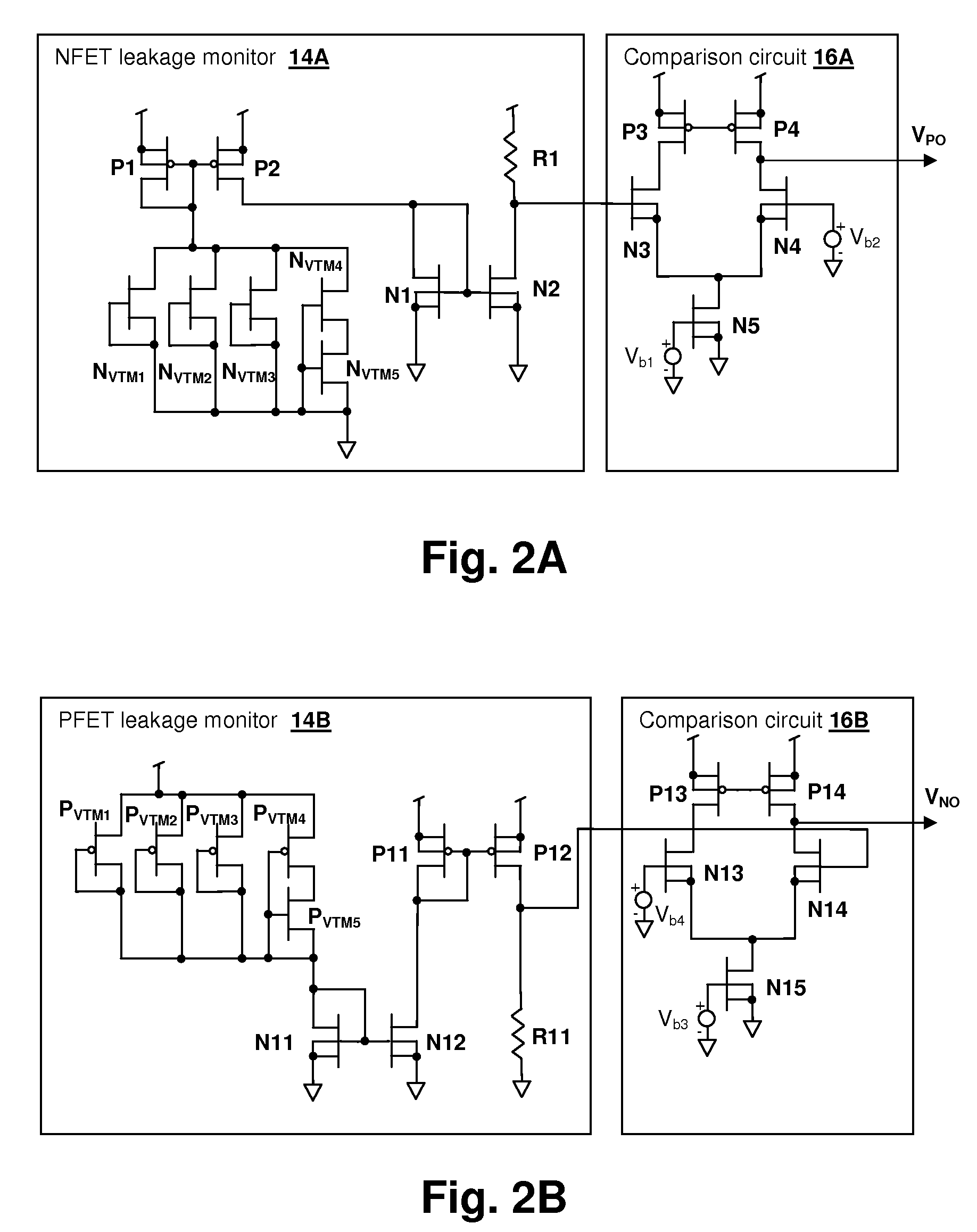

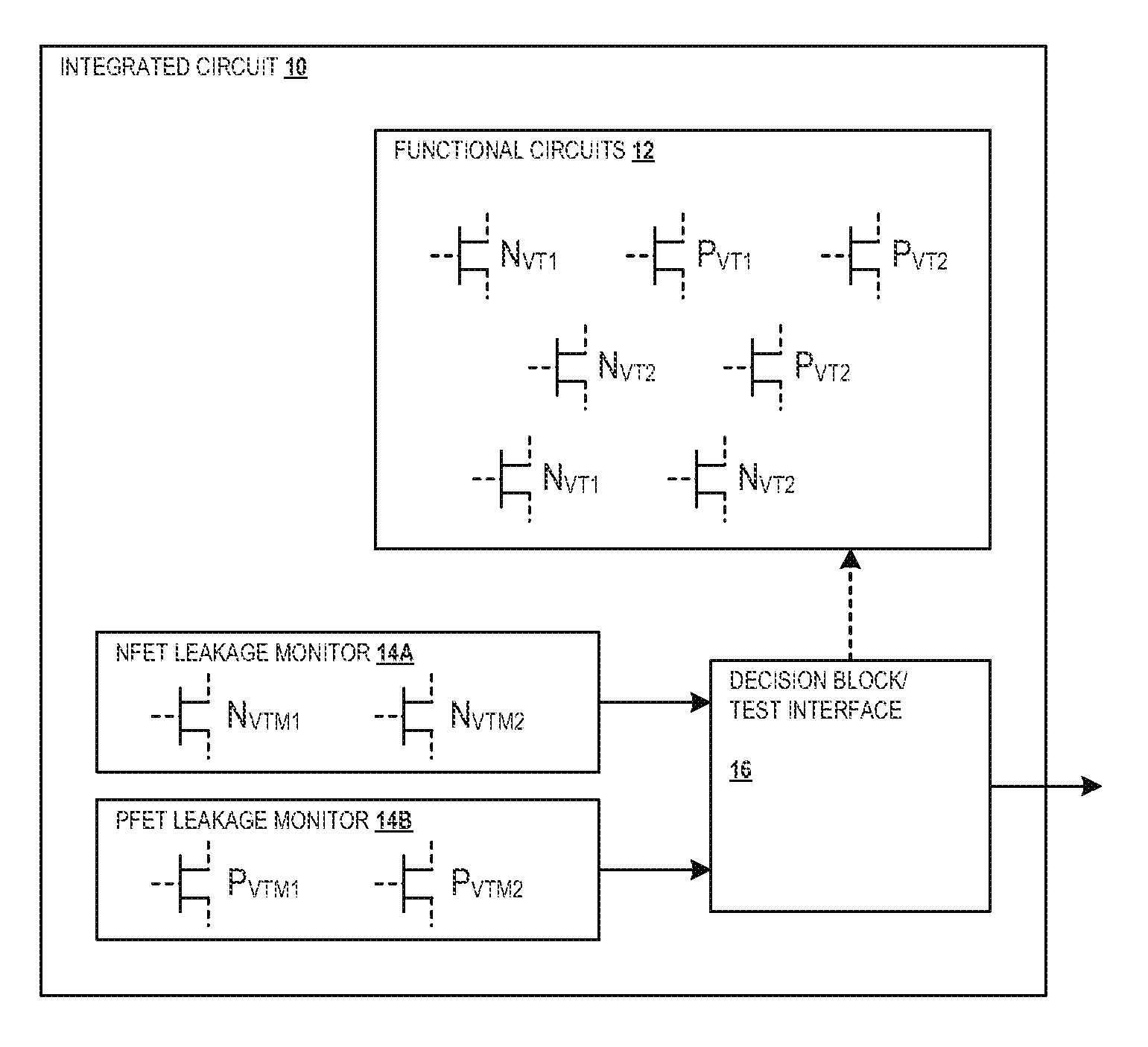

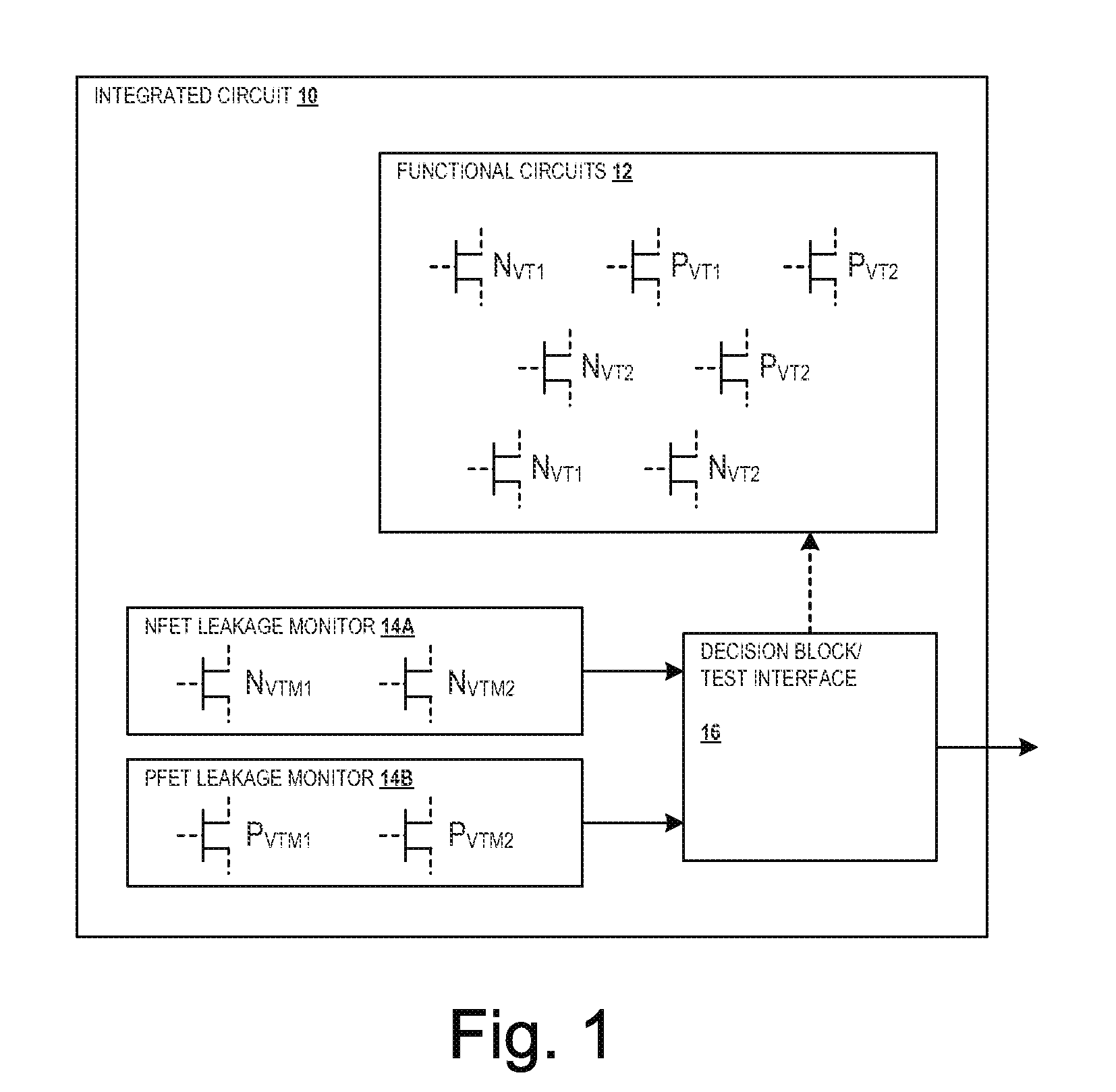

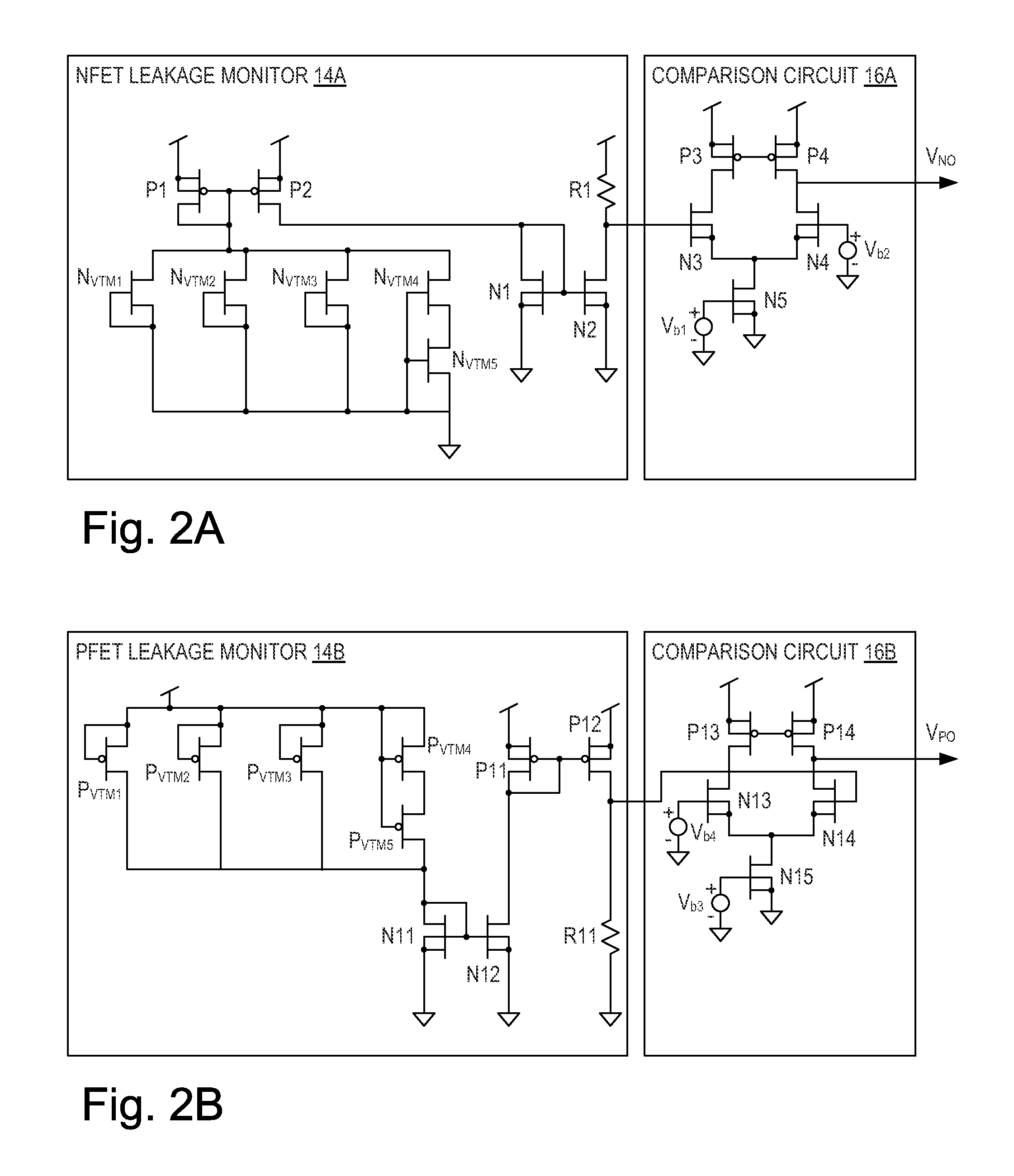

On-chip leakage current modeling and measurement circuit

ActiveUS20100257492A1Current/voltage measurementDetecting faulty computer hardwareControl circuitComparator

A leakage current monitor circuit provides an accurate statistically representative analog of true off-state leakage current in a digital circuit integrated on a die. At least one N-type transistor and at least one P-type transistor separate from the digital circuit are sized to represent the total area of the corresponding type transistors in the digital circuit. The gates of the N-type transistor and P-type transistors are set to voltages according to the corresponding off-state logic levels of the digital circuit. The N-type and P-type transistors form a portion of corresponding current mirror circuits, which can provide outputs to a leakage current monitor and / or a control circuit such as a comparator that determines when leakage current for the N-type or P-type devices has exceeded a threshold. The output of the measurement / control circuit can be used to determine a temperature of and / or control operation of the digital circuit or the system environment of the integrated circuit.

Owner:GLOBALFOUNDRIES US INC

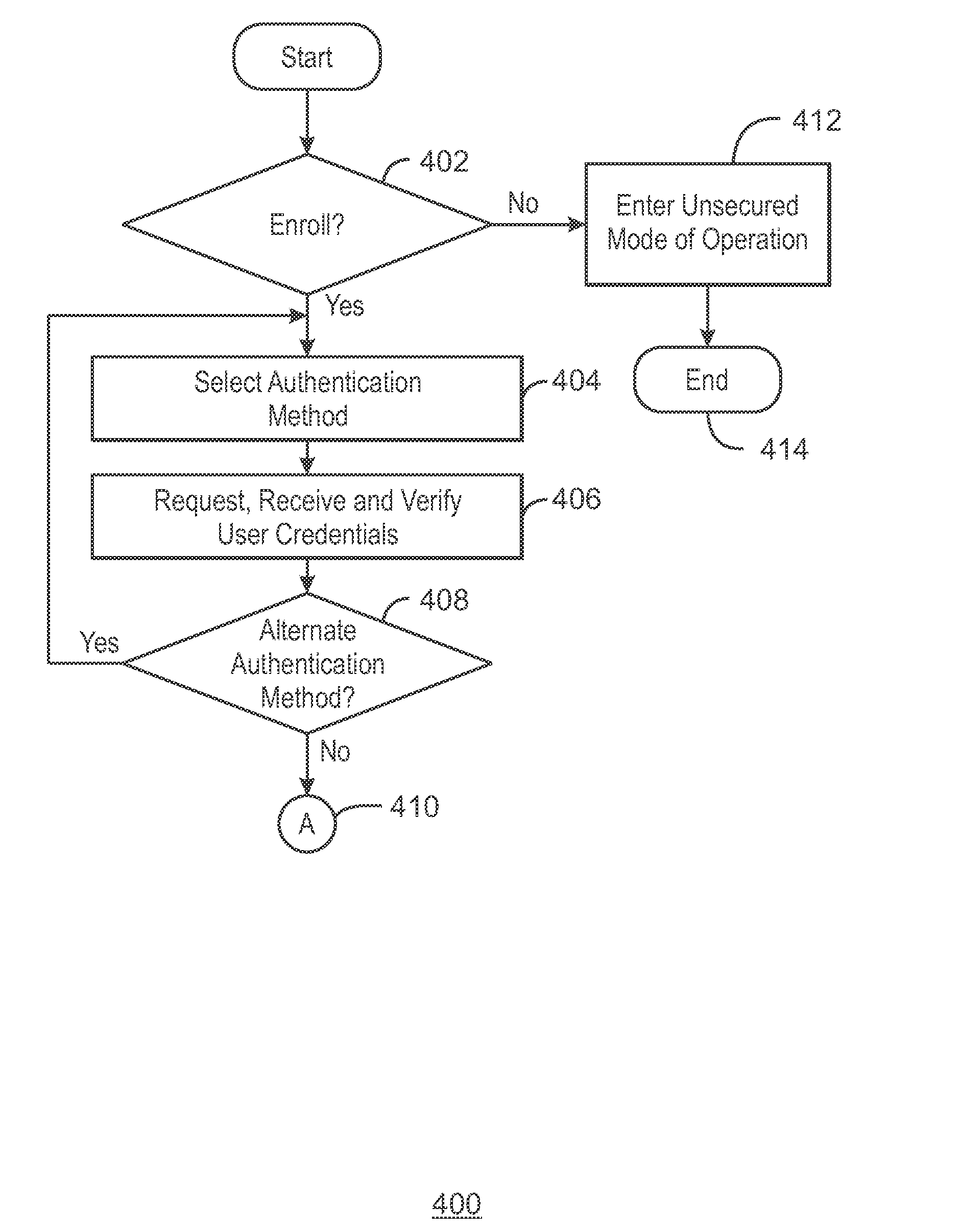

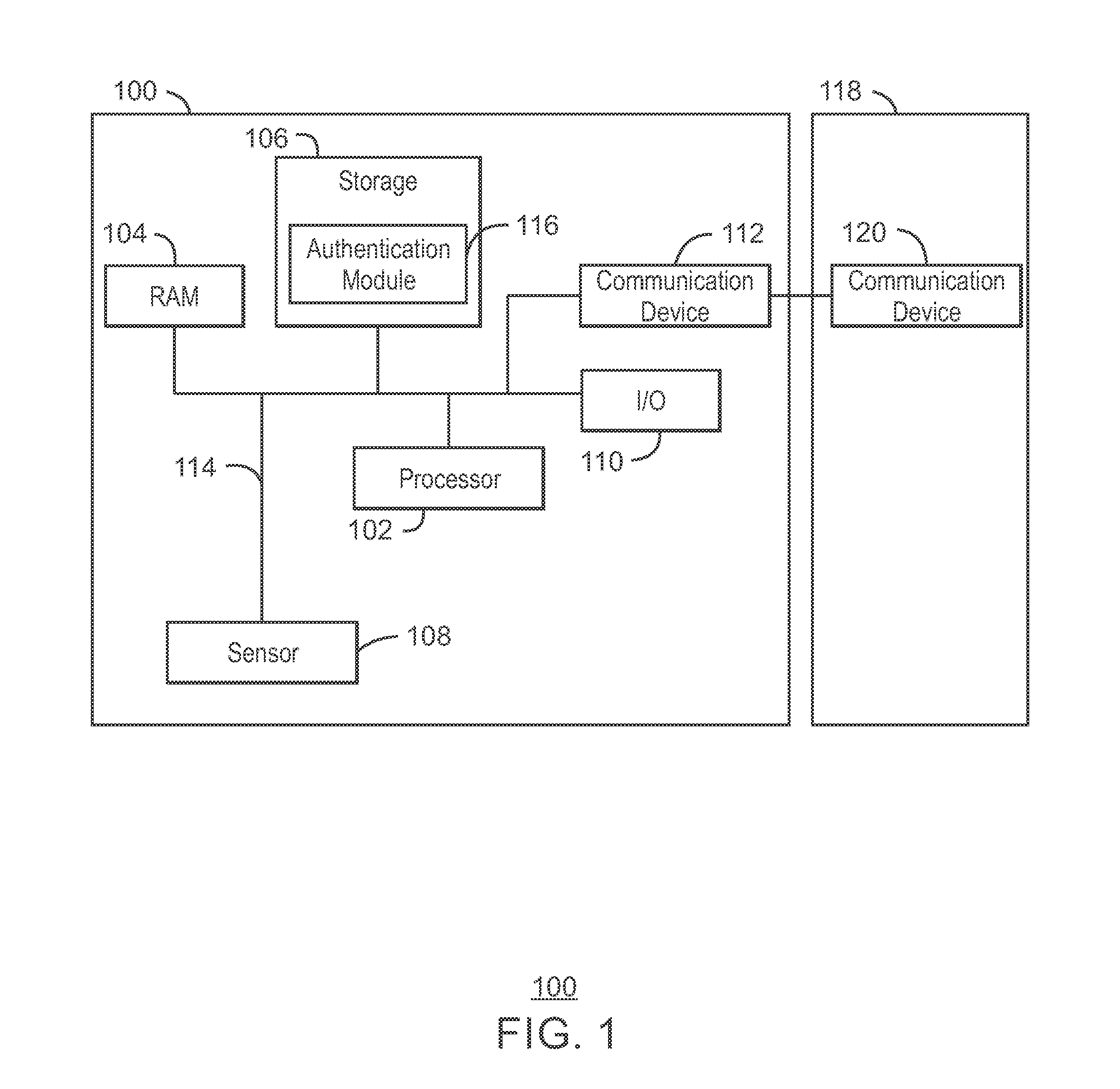

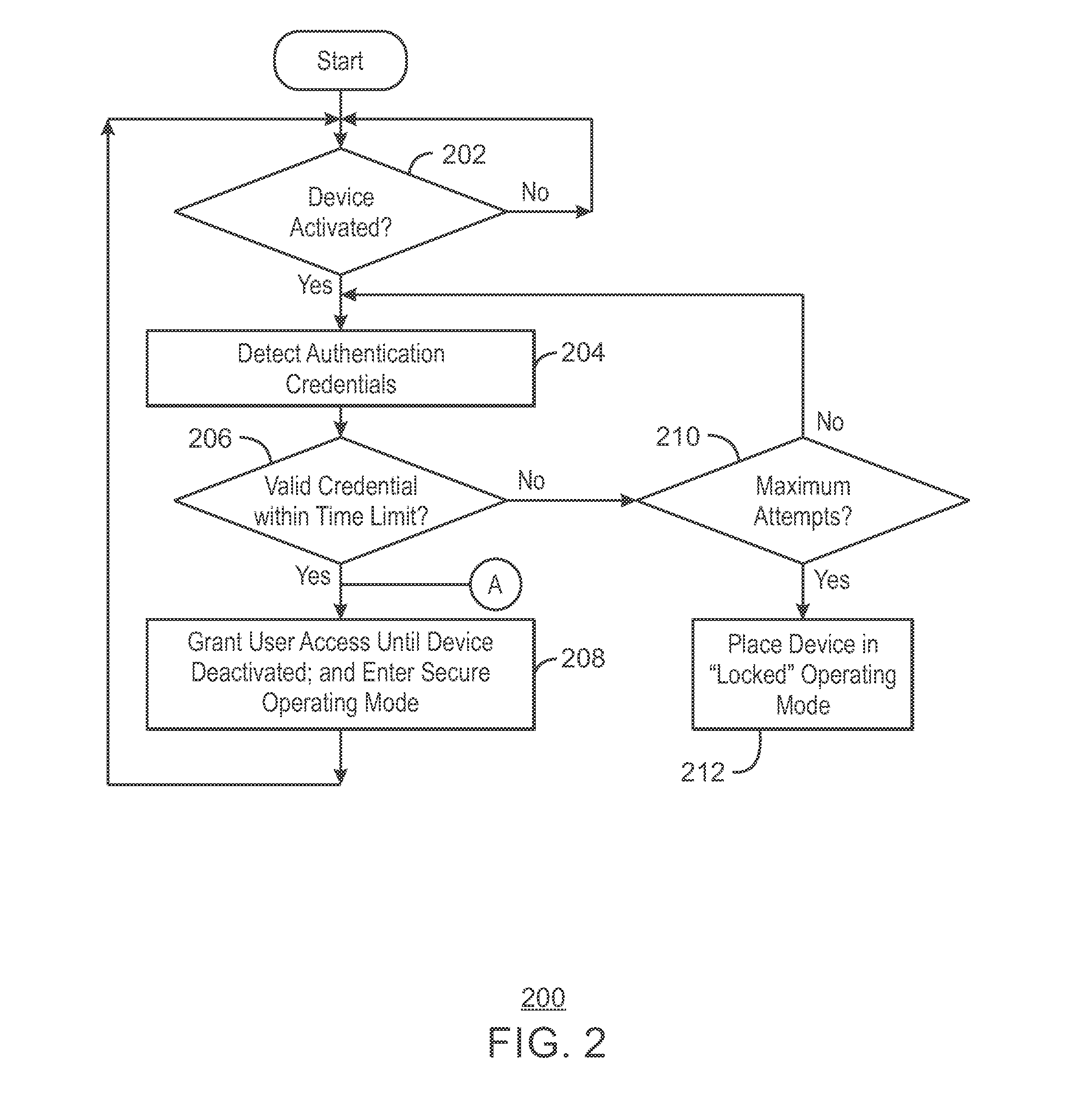

Authentication with an electronic device

InactiveUS20150186628A1Digital data processing detailsUnauthorized memory use protectionComputer hardwareUser authentication

Techniques for user authentication are described herein. In one example, an electronic device may include logic, at least partially implemented in hardware, that can determine that the electronic device has received sensor data, the sensor data indicating the electronic device is to enter an activation state and detect authentication credentials in response to determining that the electronic device is to enter the activation state. The logic can also determine whether the authentication credentials are valid and grant access to the electronic device if the authentication credentials are valid. Additionally, the logic can deactivate the electronic device in response to a change in the sensor data.

Owner:INTEL CORP

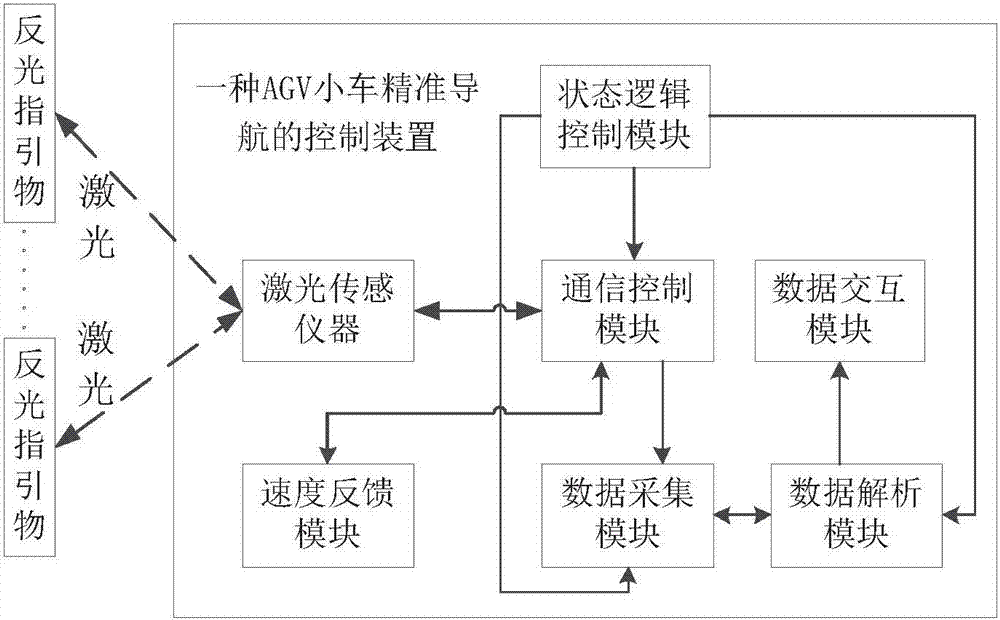

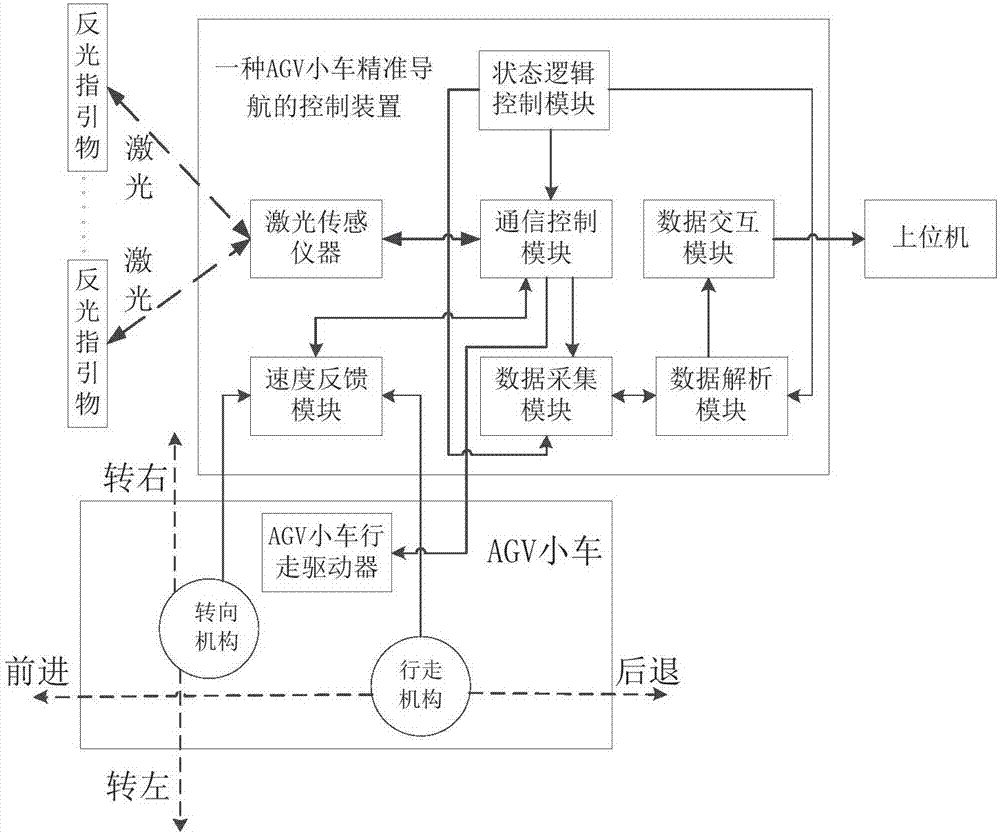

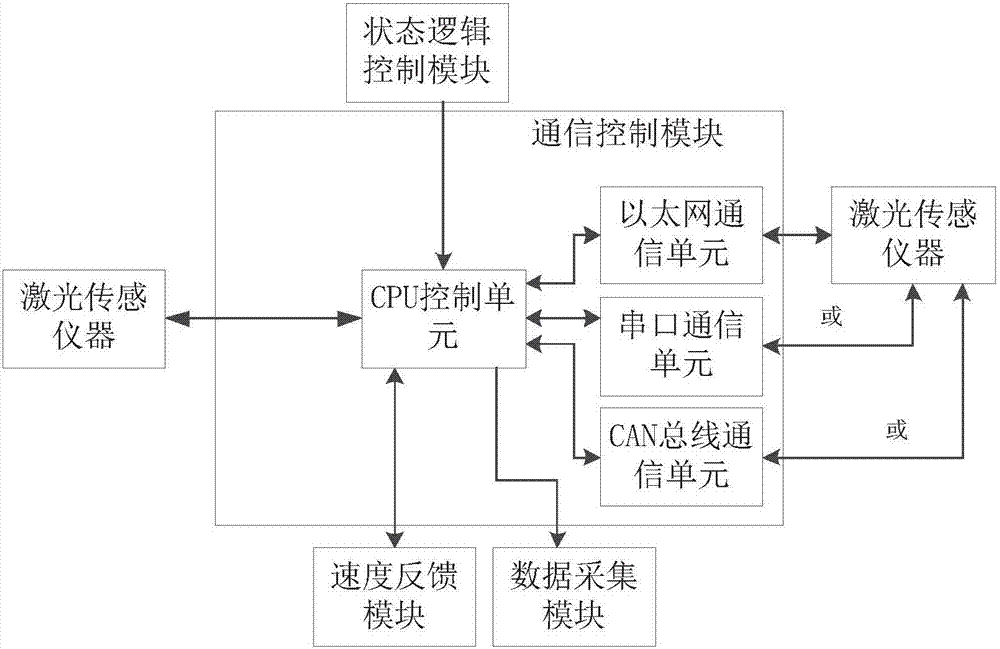

Control device, system and method for AGV accurate navigation

InactiveCN107168310AHigh precisionImprove intelligencePosition/course control in two dimensionsControl systemData acquisition

The invention discloses a control device for AGV accurate navigation, which comprises a communication control module, a laser sensing instrument, a speed feedback module, a data acquisition module, a data analysis module, a state logic control module and a data interaction module. The invention also discloses a control system for the AGV accurate navigation, which comprises the control device for the AGV accurate navigation, an upper computer and an AGV walking driver. The invention also discloses a control method for the AGV accurate navigation. The method comprises steps S1 to S7: S1, a system program enters a navigation mode; S2, position signals are acquired; S3, motion signals are acquired; S4, the position signals and the motion signals are processed; and S5, the accurate navigation information is deduced. Through the combination of a laser sensor, an encoder and a processing module and using control of an intelligent algorithm, the accuracy and the intelligence of AGV laser navigation can be improved.

Owner:GUANGZHOU JINGYUAN MECHANO ELECTRIC EQUIP

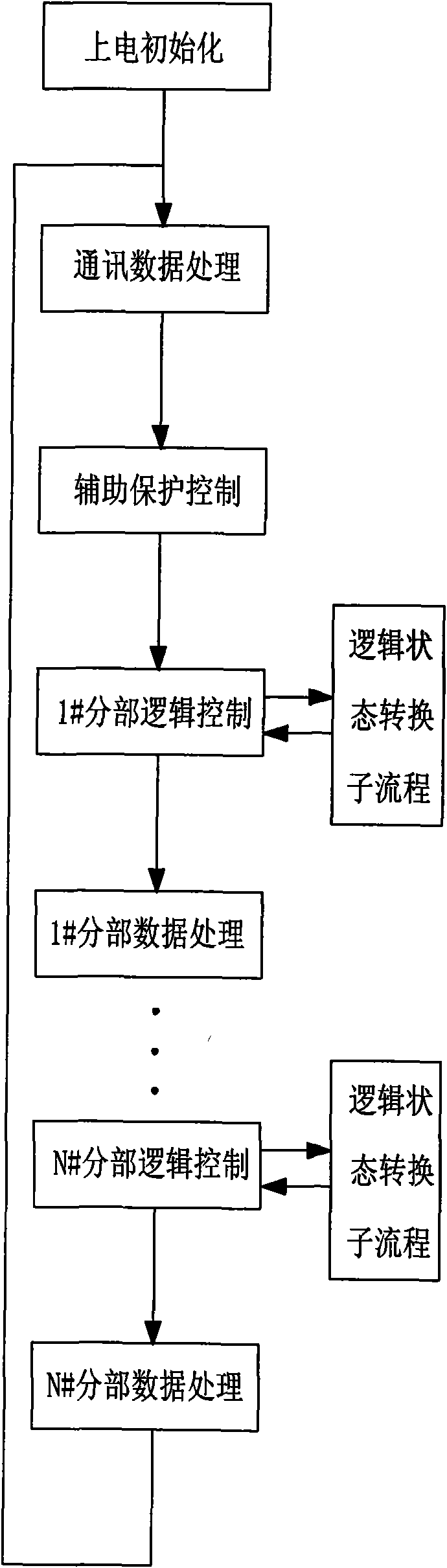

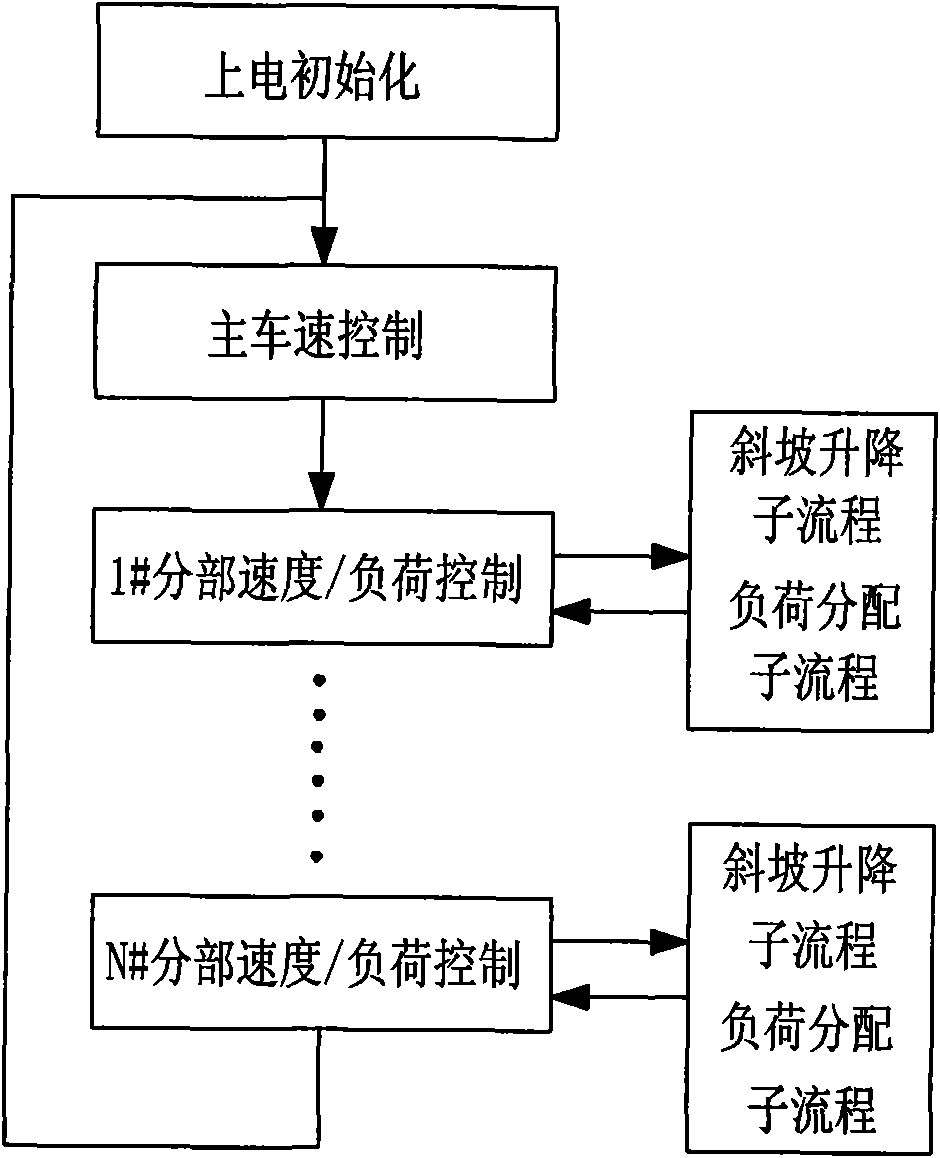

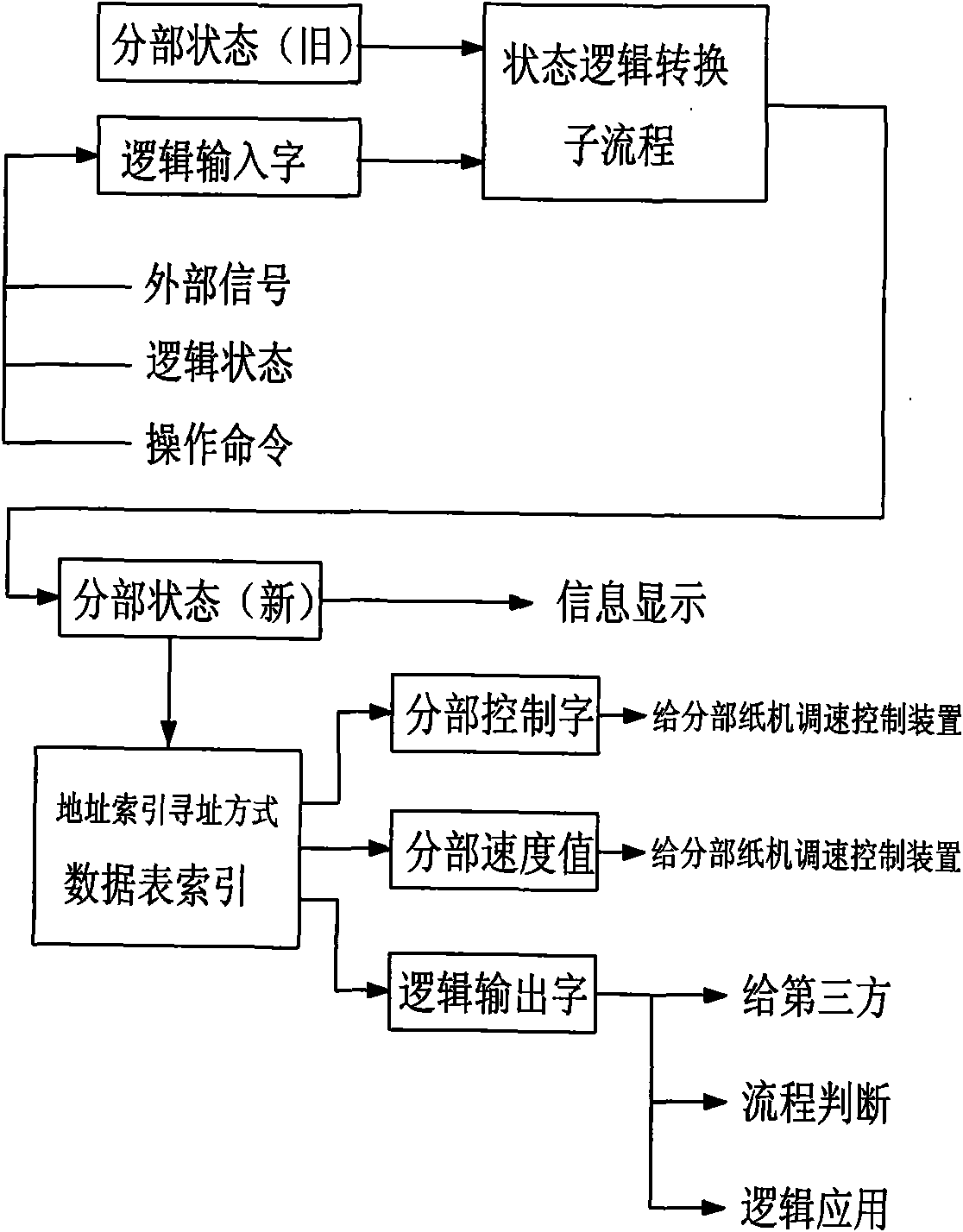

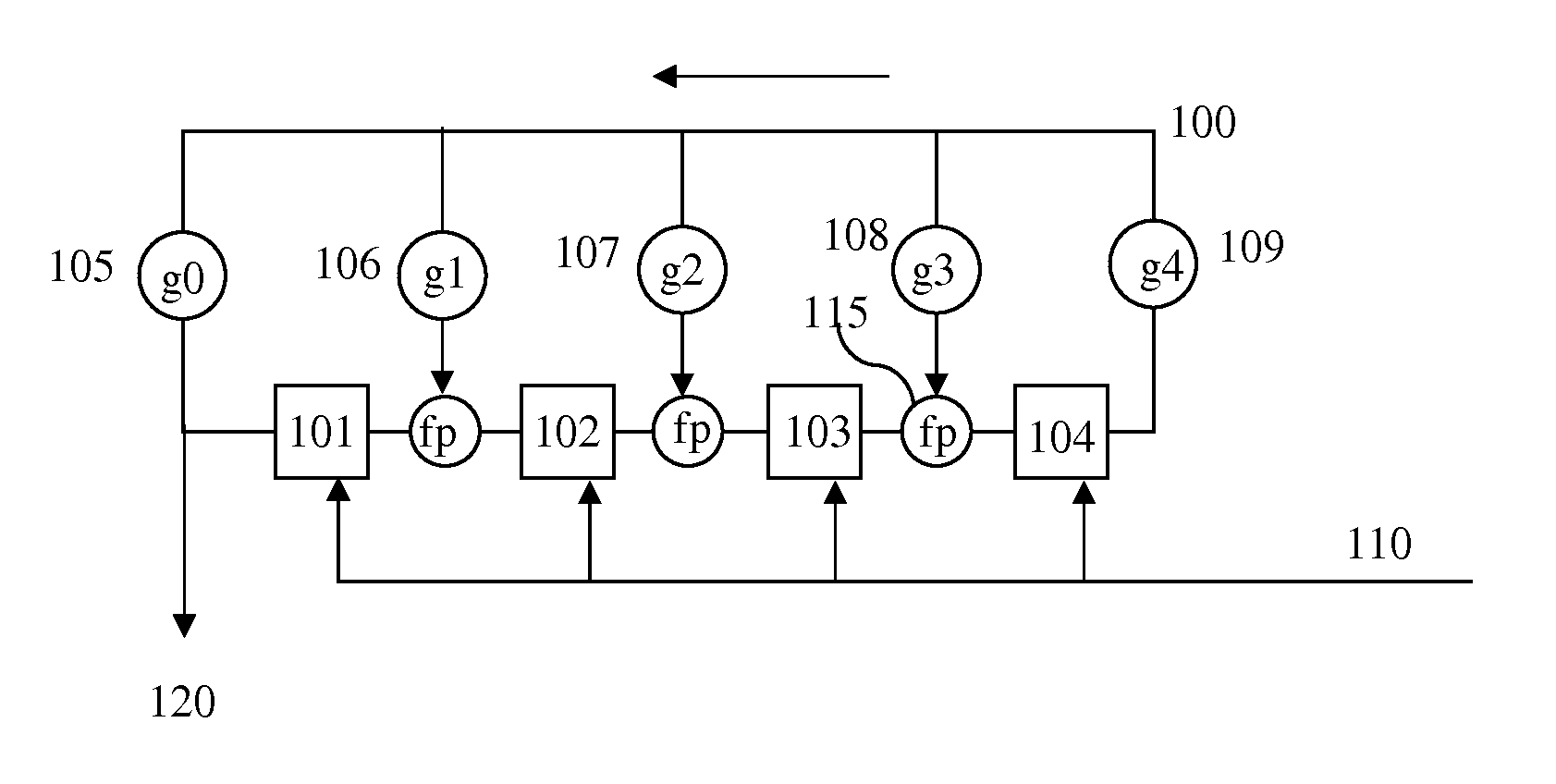

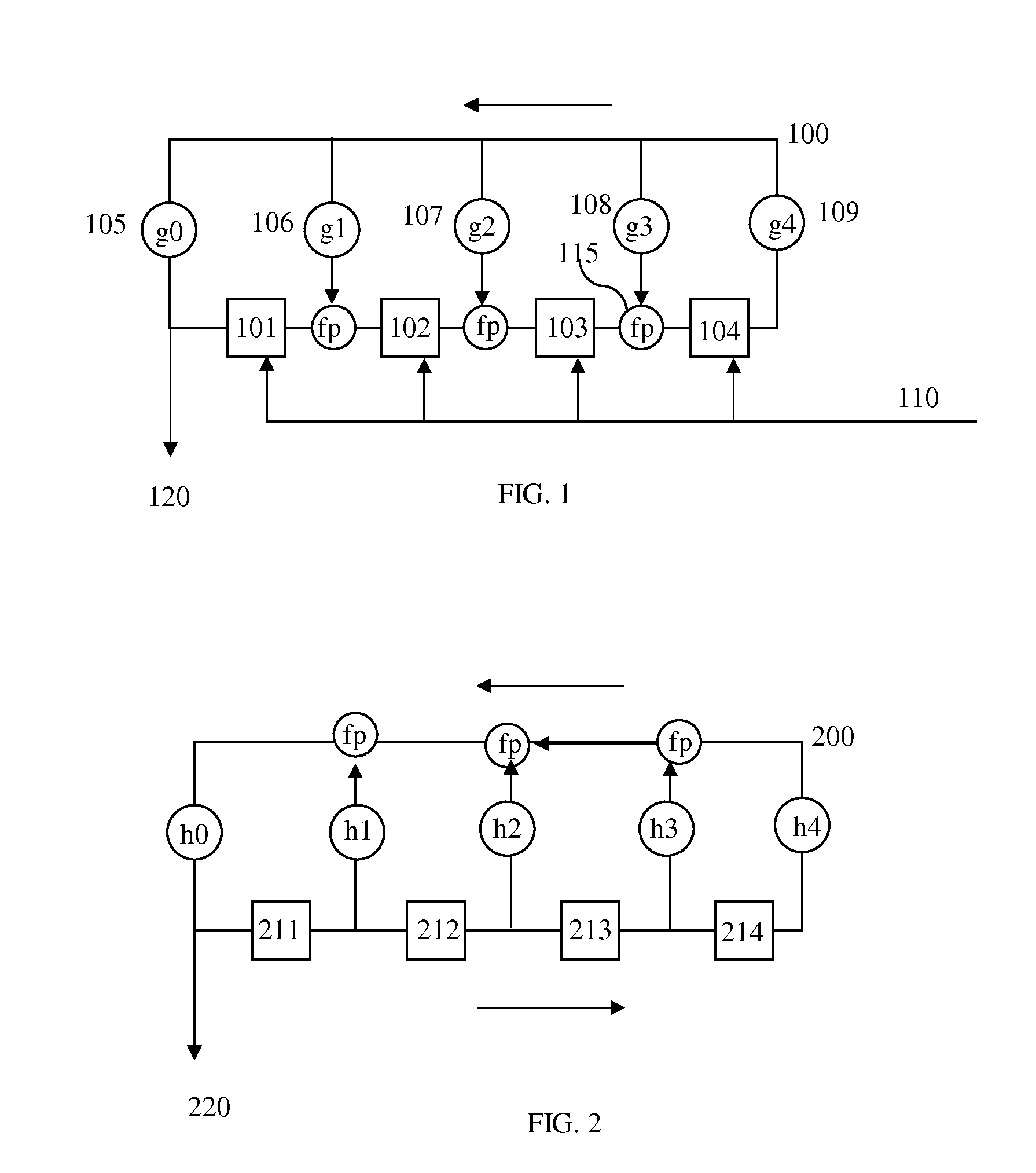

Method for controlling flow of transmission control system of paper machine

ActiveCN101560741AProcess parameters are accurate and reliableThe process parameters are finely adjusted to make the working speed of the paper machine reliableTotal factory controlProgramme control in sequence/logic controllersEngineeringData treatment

The invention discloses a method for controlling the flow of a transmission control system of a paper machine. In the method, a control system comprising a programmable control device PLC, a speed governing device and a field bus is used; the control operating flow of preparation, operation, creeping, shut-down, cleaning and fault treating functions, which is included in the transmission control system of the paper machine is modularized; according to the functions required to control by the transmission system of the paper machine, 10 to 50 subsection states are set, and the address indexed addressing mode is used for subsection state logic control of all subsections such as logic conversion, data treatment and speed / torque control switch; the PLC repeatedly controls the transmission system according to the steps of input sampling, program operation, output refreshing and under the support of a flow control module; and the speed governing device executes all functions according to the PLC output information transferred by the field bus. The method has the advantages of reliably and harmoniously controlling the operating speed, speed difference control, speed ratio adjustment and the like of the paper machine and facilitating the yield and the quality of the paper machine.

Owner:ZHEJIANG HUAZHANG TECH

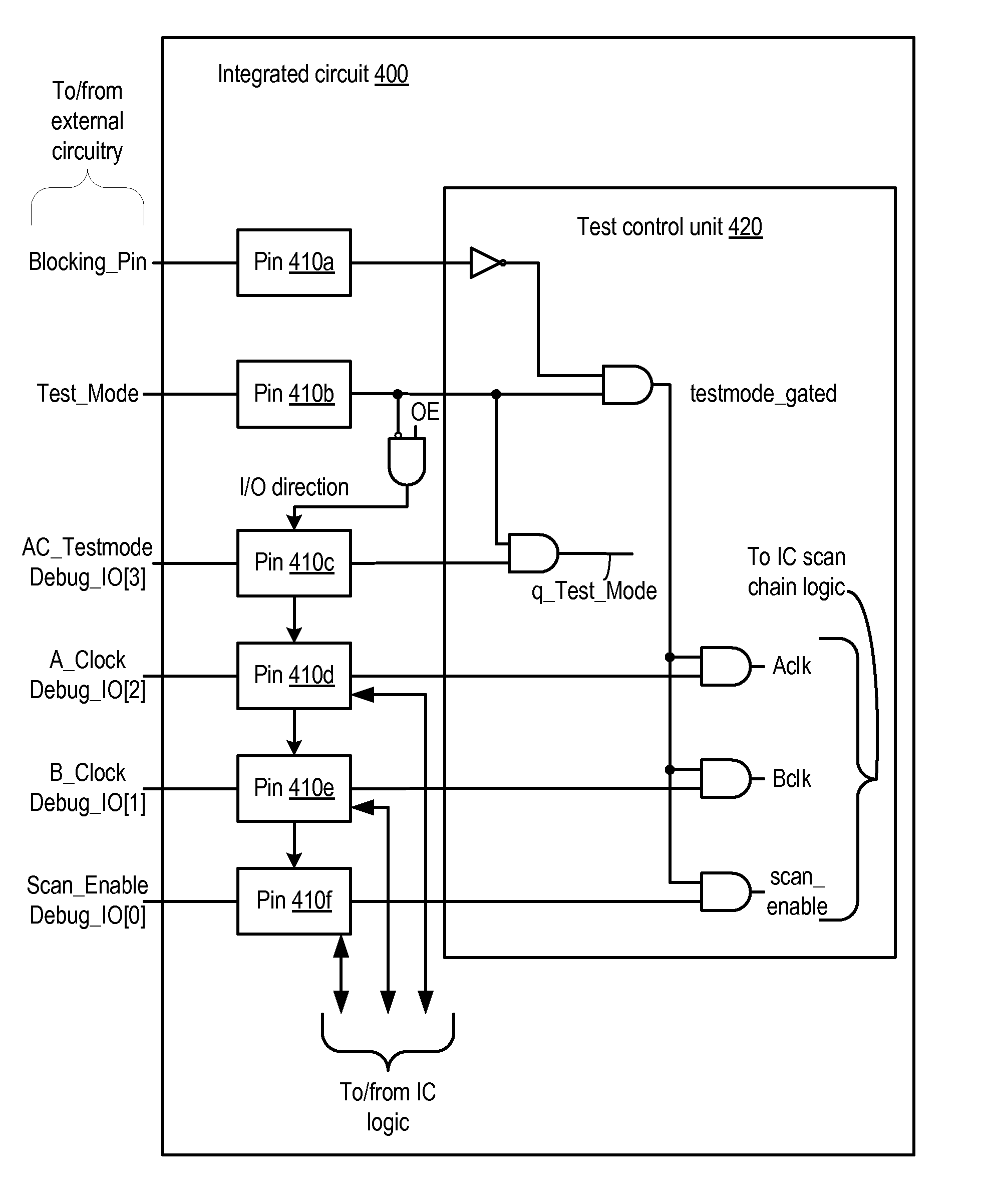

Integrated circuit with blocking pin to coordinate entry into test mode

An integrated circuit (IC) including a blocking pin. An IC may include state logic, a test control unit configured to coordinate access by external circuitry to operating state of the state logic during a test mode, and interface pins configured to couple the integrated circuit to the external circuitry. Shared interface pins may provide input signals to the test control unit during the test mode of operation and may perform distinct I / O functions during normal mode operation. A blocking interface pin, when asserted by external circuitry during normal mode operation, may force test signals derived from at least a portion of the shared interface pins by the test control unit into respective quiescent states, such that subsequent to assertion of the blocking pin, the integrated circuit is operable to enter the test mode of operation from the normal mode of operation without resetting operating state of the state logic.

Owner:ORACLE INT CORP

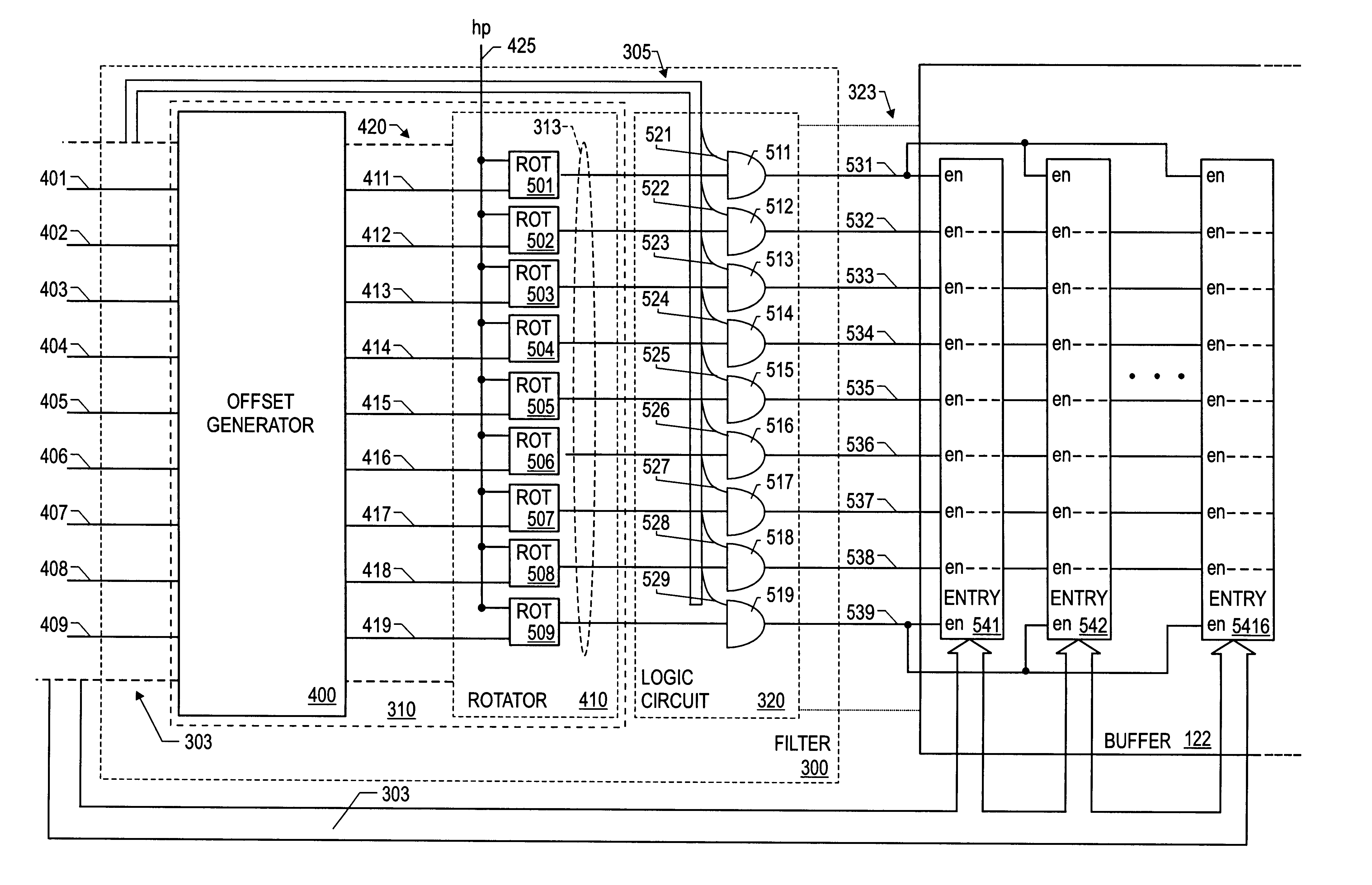

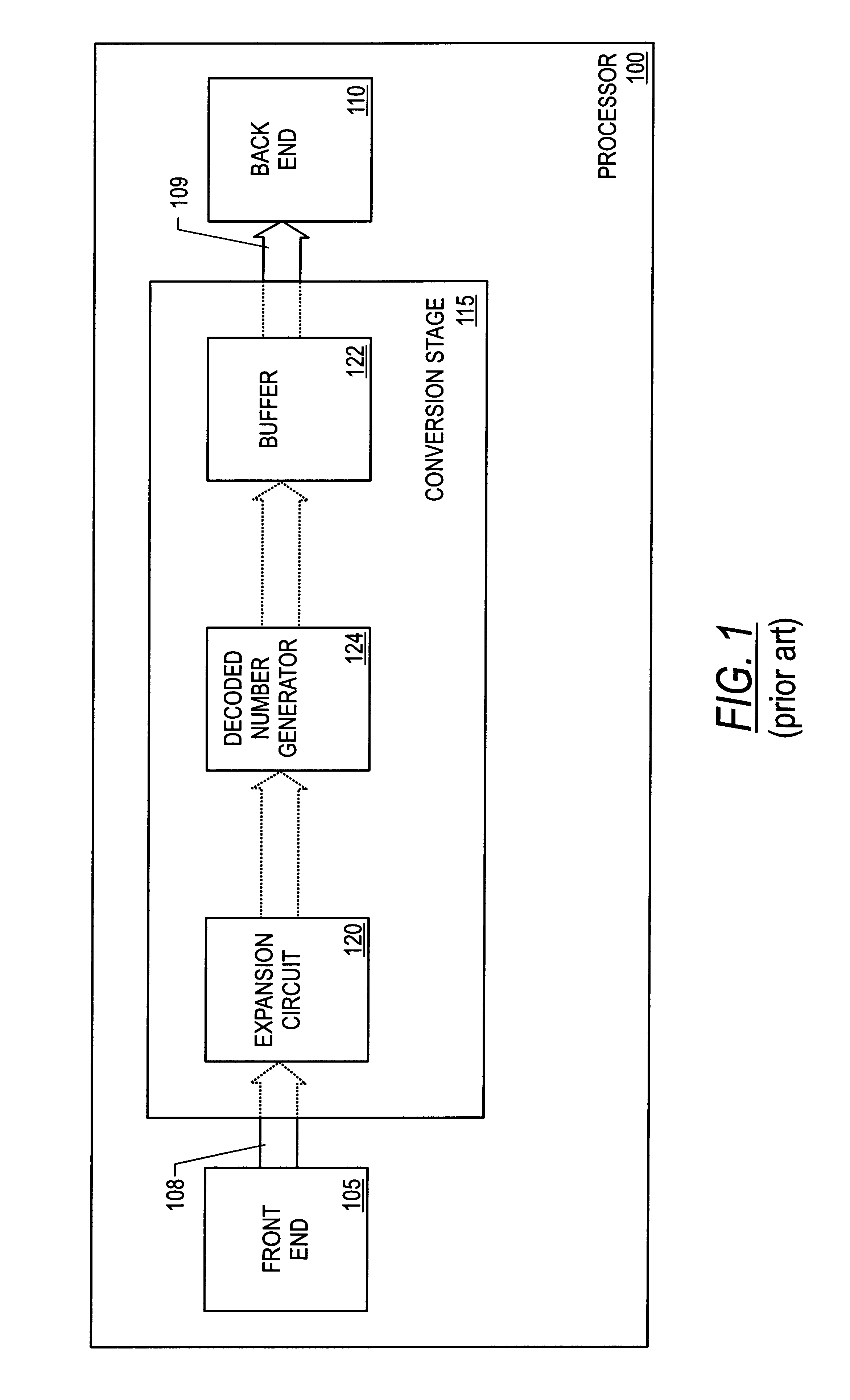

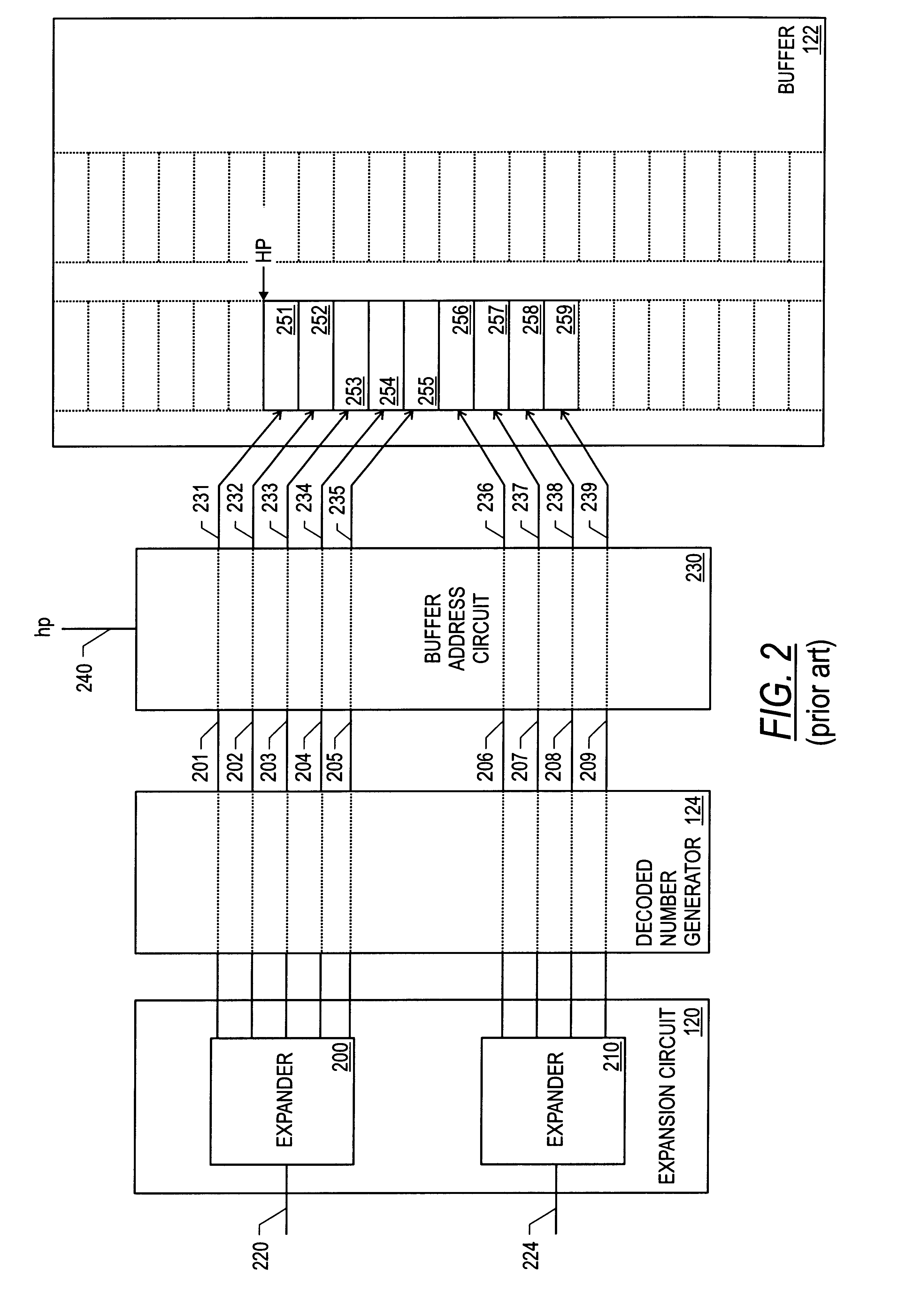

Method and apparatus for filtering valid information for downstream processing

InactiveUS6292882B1Runtime instruction translationGeneral purpose stored program computerMicro-operationDownstream processing

In one aspect, the invention includes an apparatus for filtering instructions within a digital system that eliminates the need to physically switch the valid instructions onto consecutive data lines of a buffer. The apparatus includes a filter for filtering instructions within a digital system. The filter includes an address generator capable of generating at least two addresses in response to receiving at least two micro-operations. The filter also includes a logic circuit coupled to the address generator. The logic circuit filters addresses corresponding to valid micro-operations in response to assessing the state of a portion of each of the micro-operations. In a second aspect, the invention includes a method for filtering instructions within a digital system that eliminates the need to physically switch the valid instructions onto consecutive data lines of a buffer. The method includes, generating at least two addresses in response to receiving at least two micro-operations. The method further includes filtering addresses corresponding to valid micro-operations in response to assessing the state of a portion of each of the micro-operations.

Owner:INTEL CORP

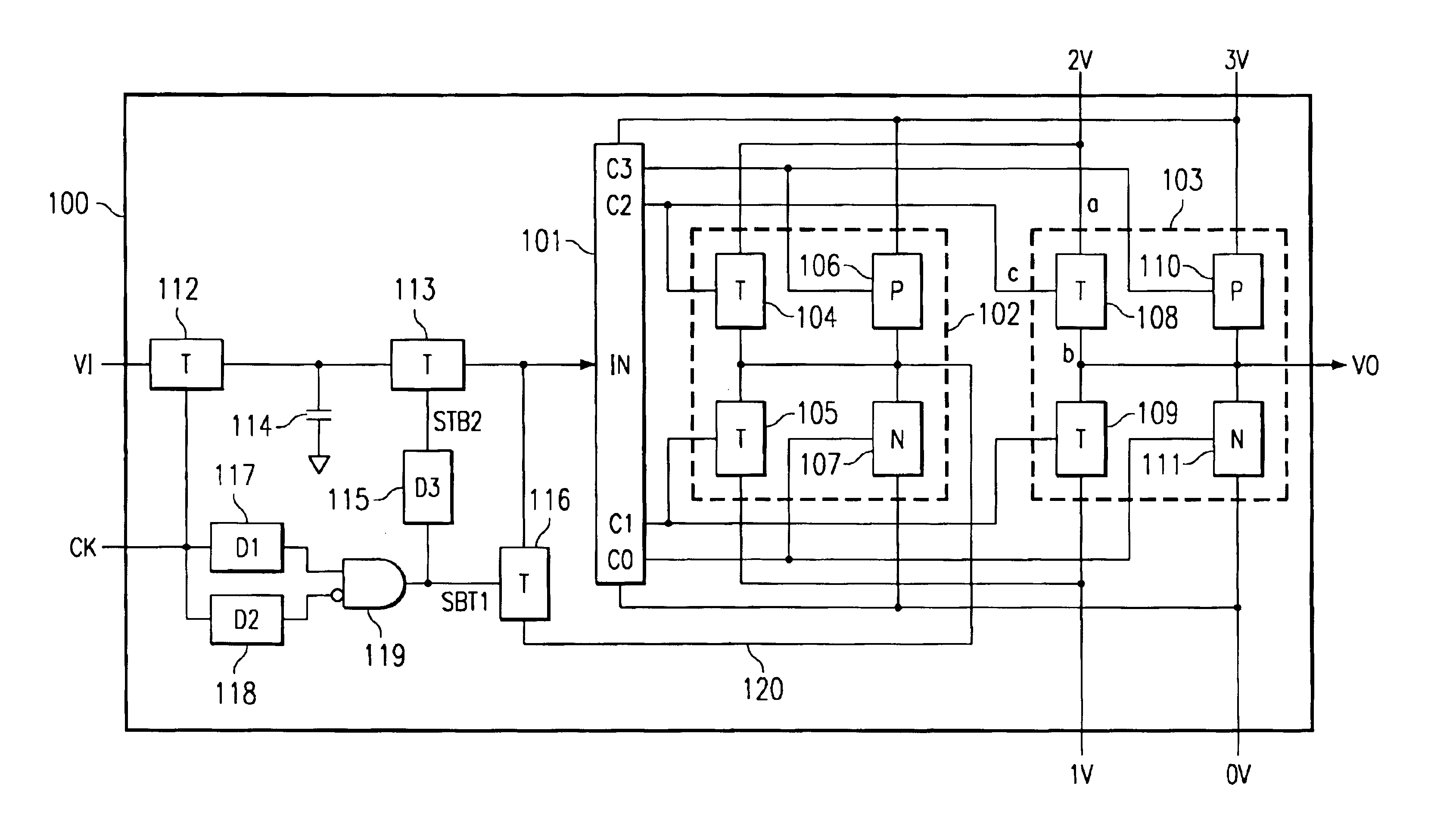

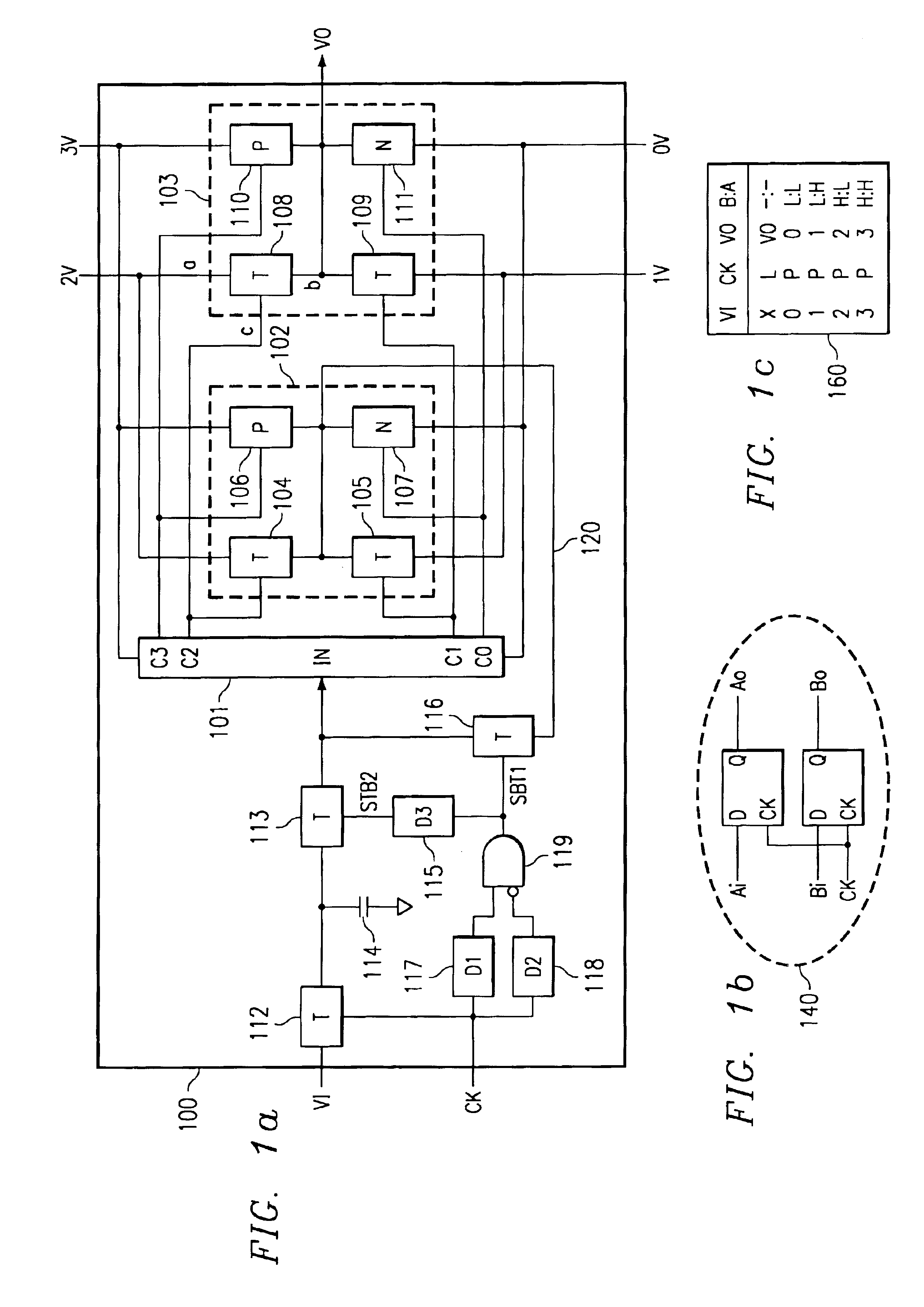

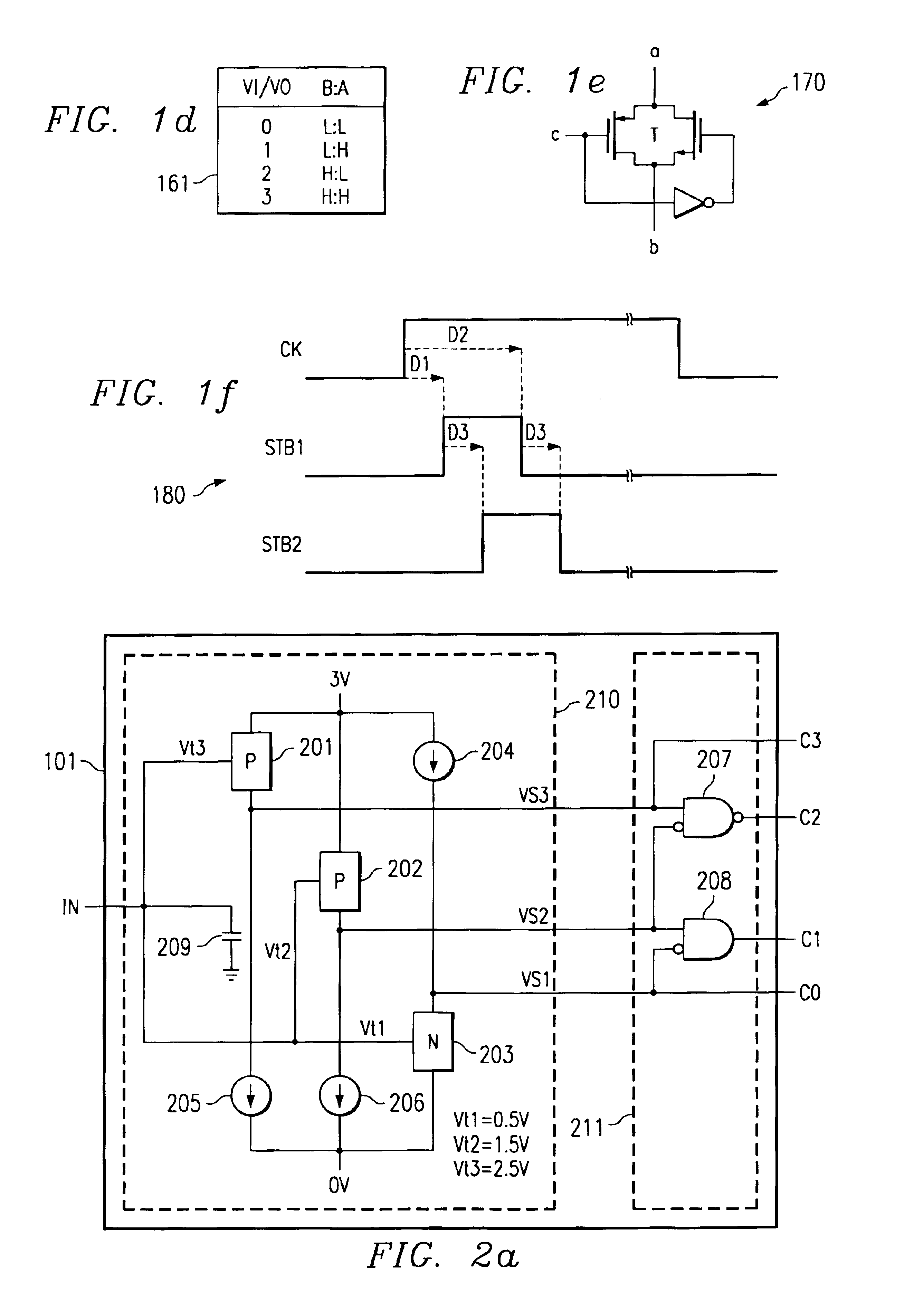

Quad state logic design methods, circuits, and systems

InactiveUS6963225B2Reduce wiring densityReduced wiring interconnectsLogic circuits characterised by logic functionMultistate logicHigh densityEngineering

Quad-state logic elements and quad-state memory elements are used to reduce the wiring density of integrated circuits. The resulting reduction in wiring interconnects between memories and logic elements results in higher speed, higher density, and lower power integrated circuit designs.

Owner:TEXAS INSTR INC

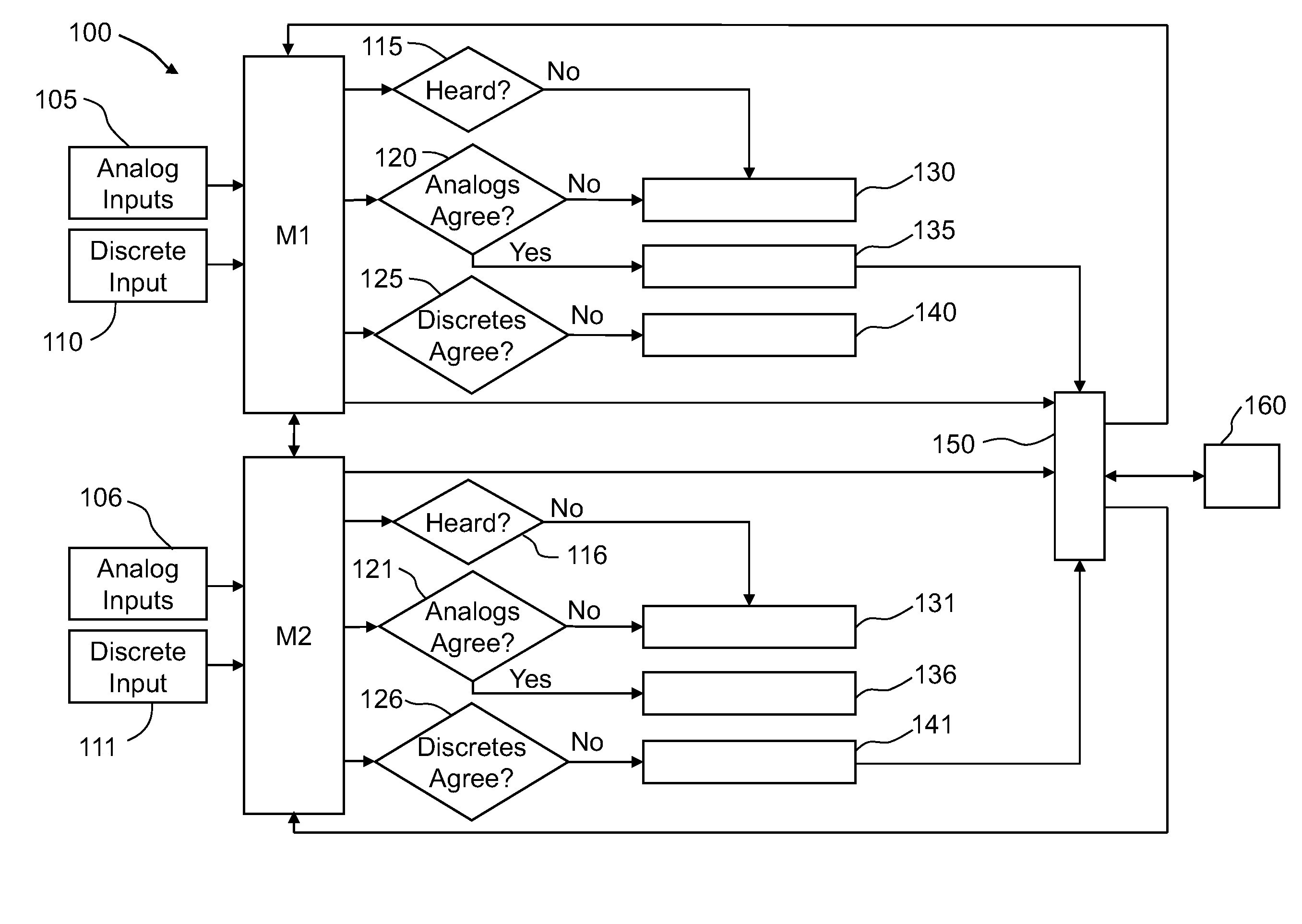

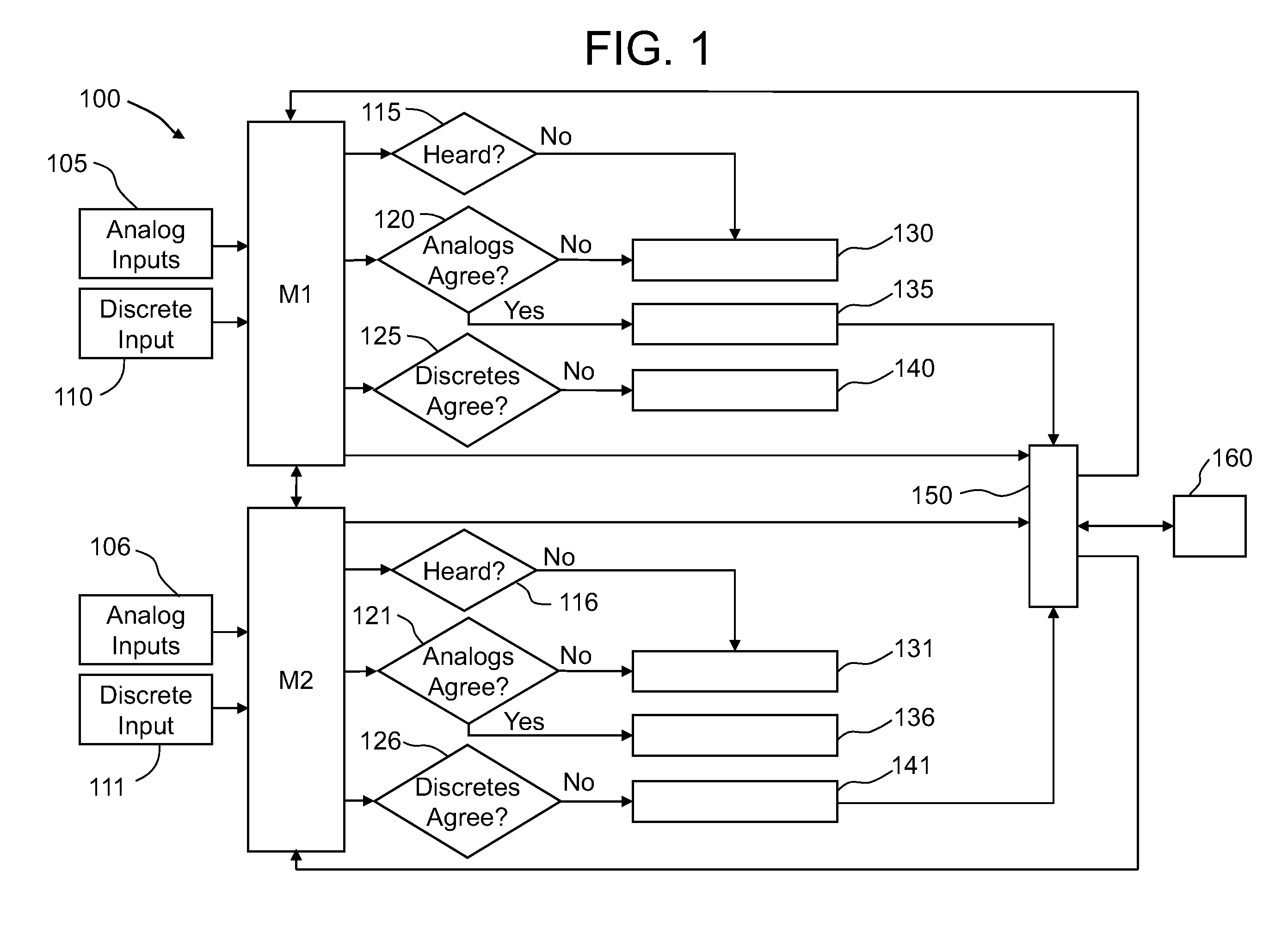

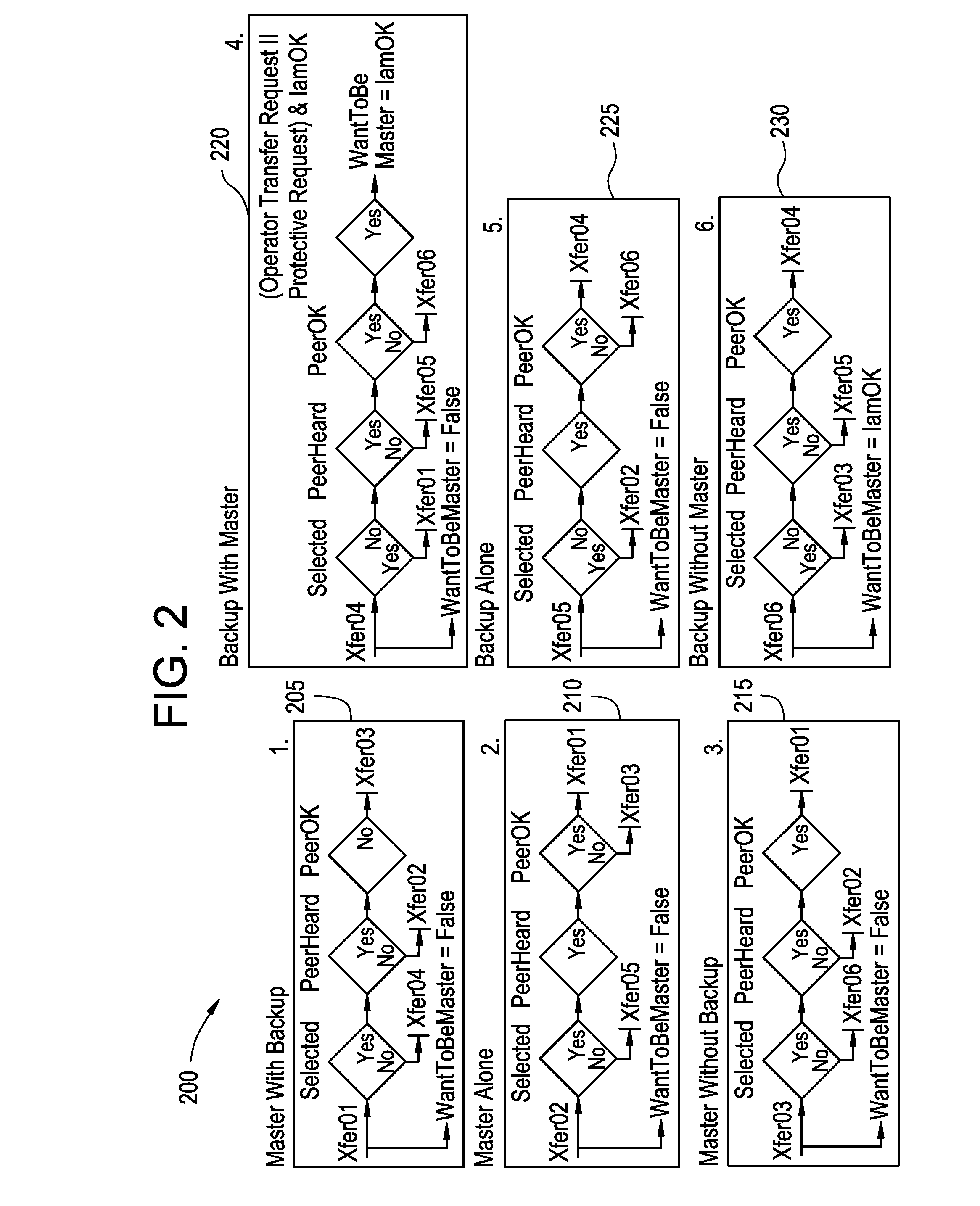

Generator regulating system and method with dual controllers

A regulating system can include a first controller configured to receive analog input and discrete input, a second controller communicatively coupled to the first controller, and configured to receive analog input and discrete input, a selector communicatively coupled to the first controller and second controller and configured to select either one of the first controller and the second controller as a master for the regulating system and state logic residing on each of the first controller and second controller to determine which of the first and second controller is the master.

Owner:GENERAL ELECTRIC CO

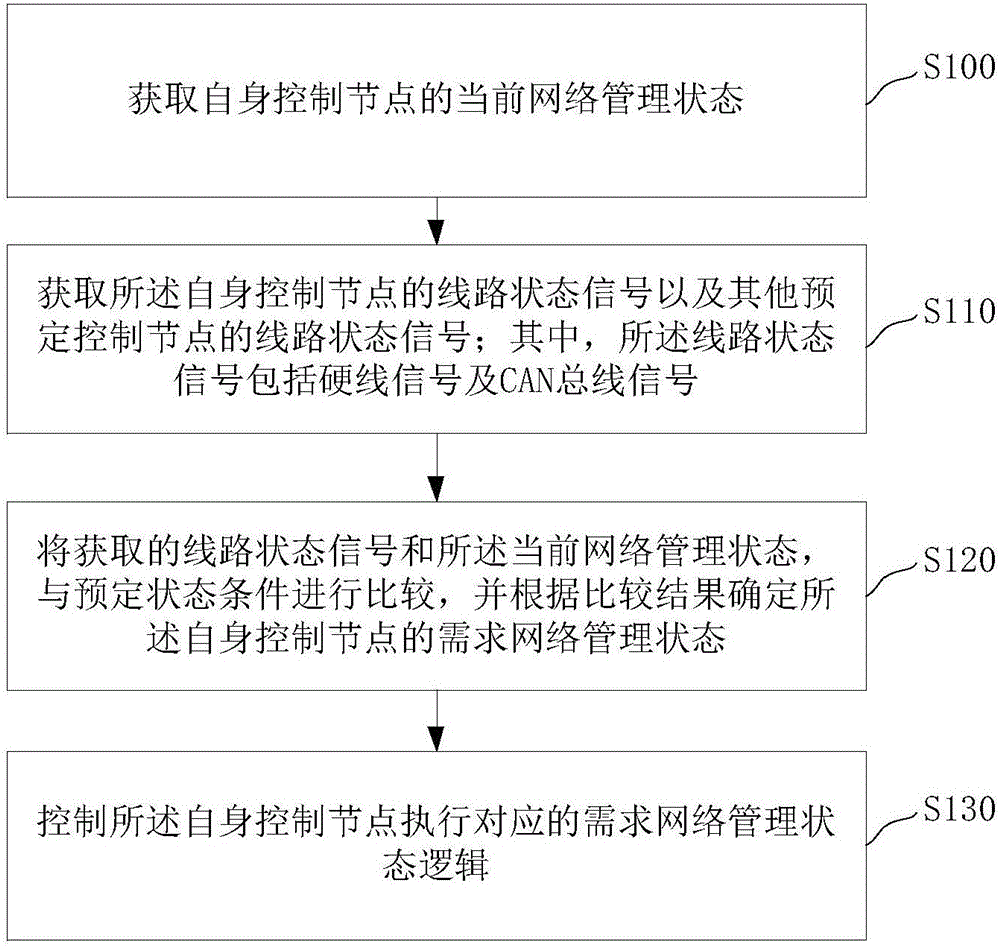

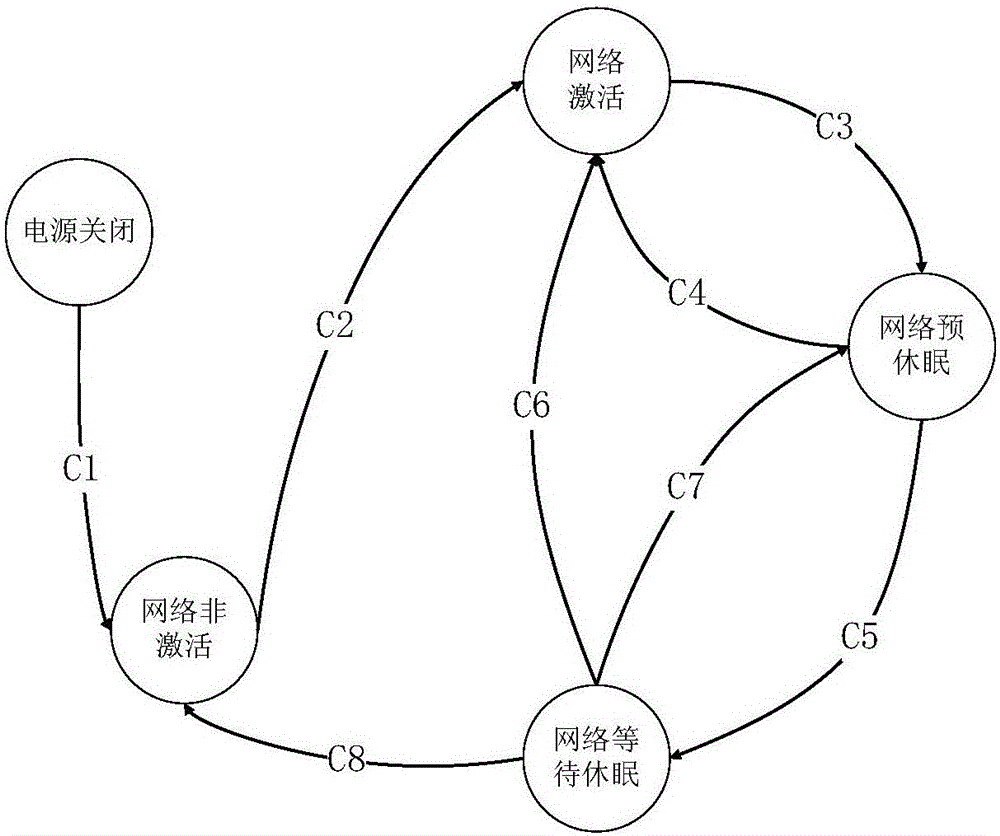

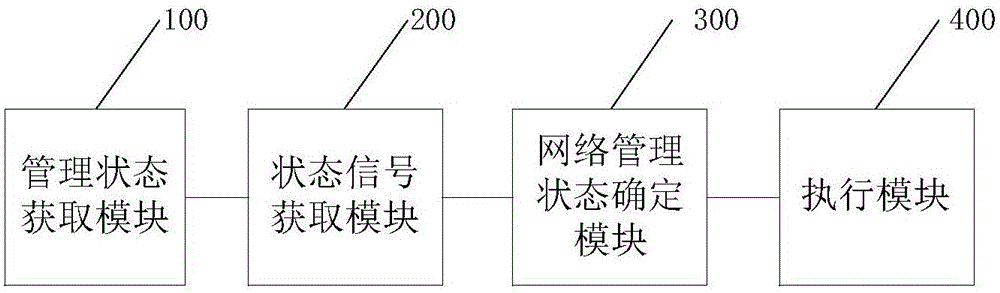

Vehicle network management method and system, and vehicle

The present invention discloses a vehicle network management method. The method comprises the steps of acquiring a current network management state of a self-control node; acquiring a line state signal of the self-control node and line state signals of other predetermined control nodes; comparing the obtained line state signals and the current network management state with a predetermined state condition, and determining a desired network management state of the self-control node according to a comparison result; and controlling the self-control node to execute corresponding desired network management state logic. According to the method, each control node automatically determines, according to obtained state information, the desired network management state of the control node and adjusting corresponding desired network management state, so that the control node can be in a low power consumption state when in a sleep mode, and the control node can be awaken timely when the control node is to work. The development limitation of the control node due to use of a logic ring is broken up. The present invention further discloses a vehicle network management system and a vehicle. The system and the vehicle have the above beneficial effects.

Owner:BEIQI FOTON MOTOR CO LTD

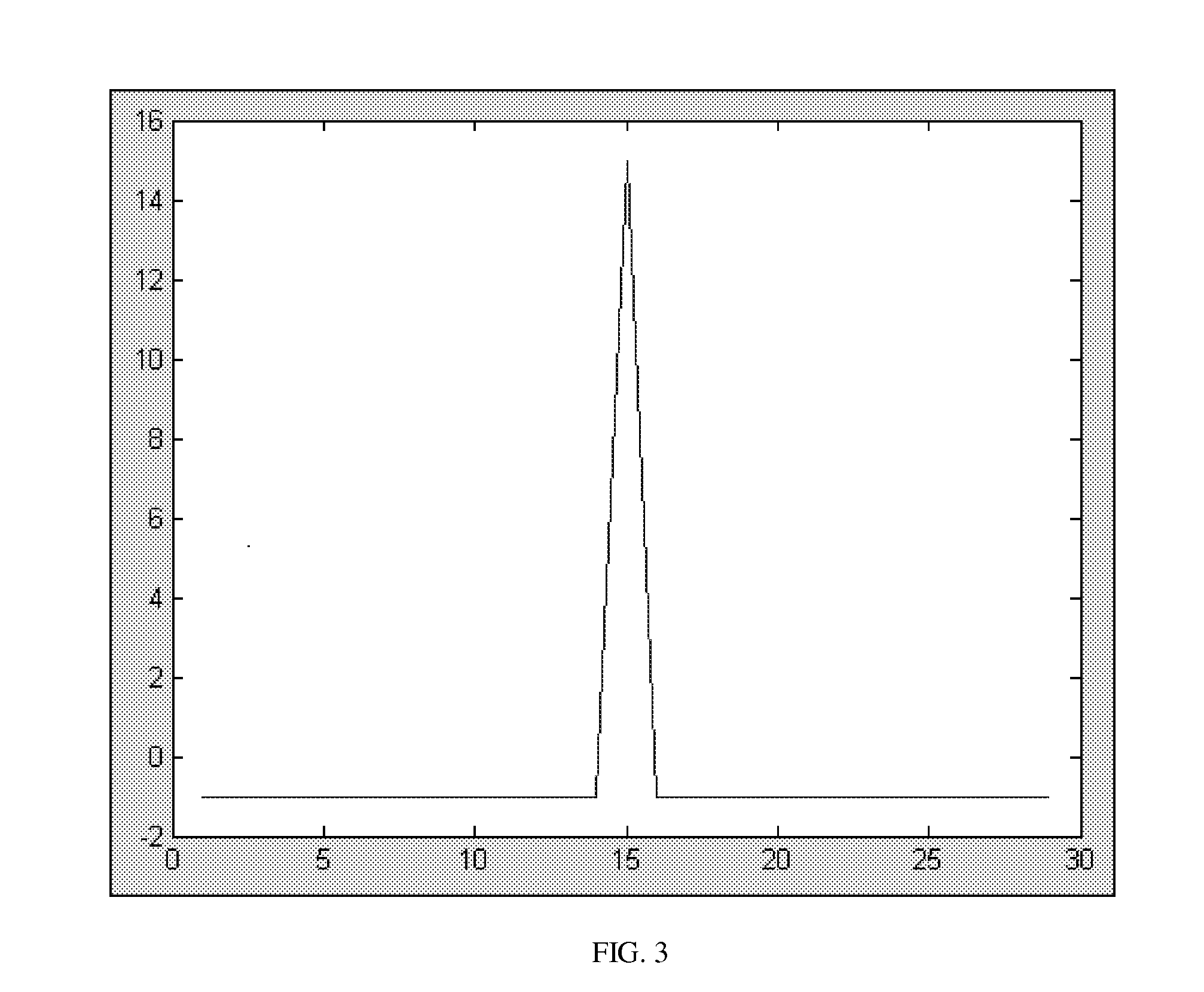

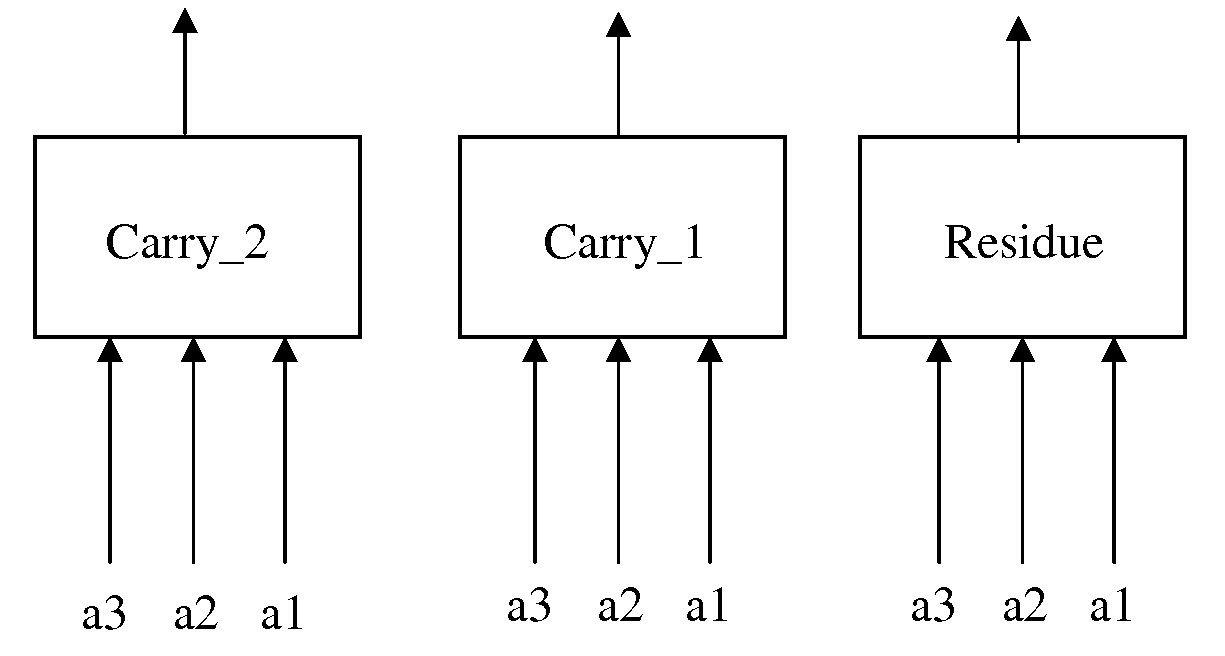

Methods and Systems for Determining Characteristics of a Sequence of n-state Symbols

InactiveUS20140032623A1Reduce the possibilityRandom number generatorsDigital function generatorsShift registerLength property

Maximum length properties of n-state sequences of n-state symbols with n=2 or n>2 are tested. Checkwords are generated from p consecutive n-state symbols in a sequence of n-state symbols which may overlap by (p−1) n-state symbols. If a sequence has np−1 n-state symbols in which 2 consecutive checkwords overlap in (p−1) n-state symbols and each checkword formed in the extended sequence is unique, then the sequence is a maximum length n-state sequence. An n-state feedback shift register based sequence generator with p n-state register elements is tested on the content of the shift register for np−1 cycles. If the shift register content is not repeated the sequence is maximum length. Generation of a sequence is stopped when the content repeats. Non-reversible n-state inverters and non-reversible n-state logic functions are applied to generate n-state sequences

Owner:TERNARYLOGIC

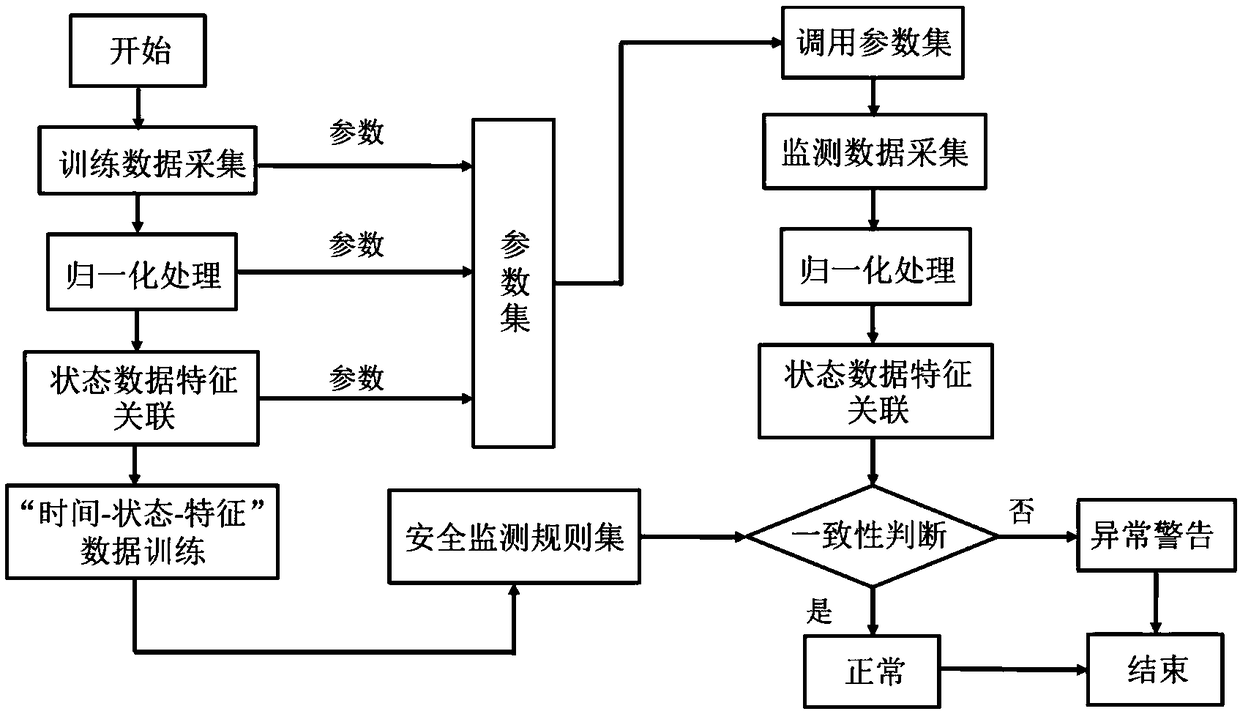

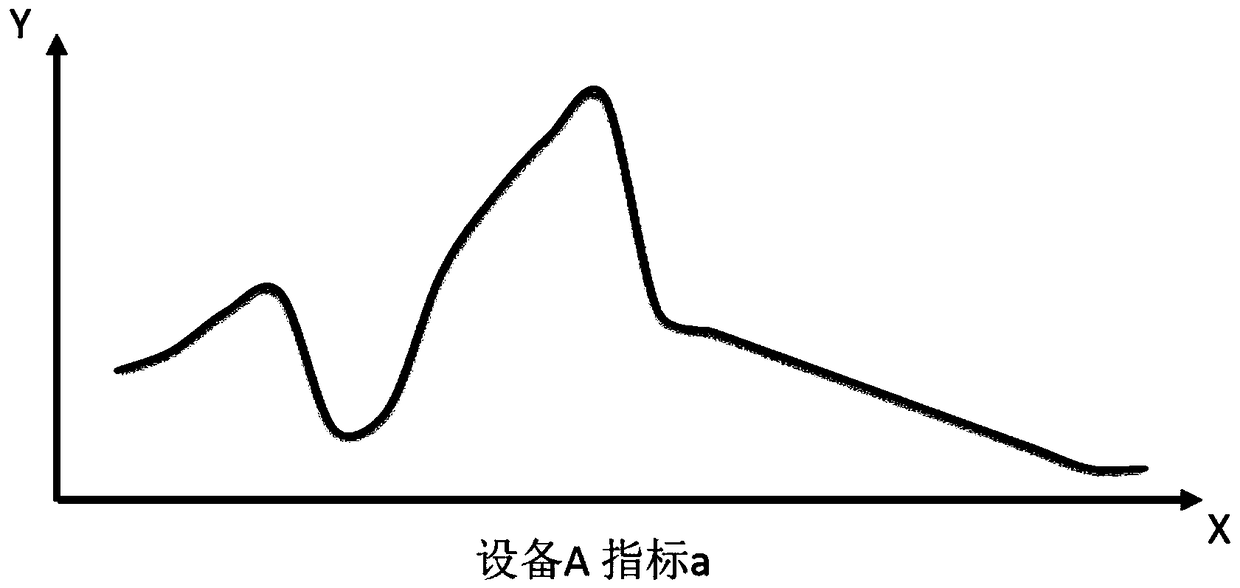

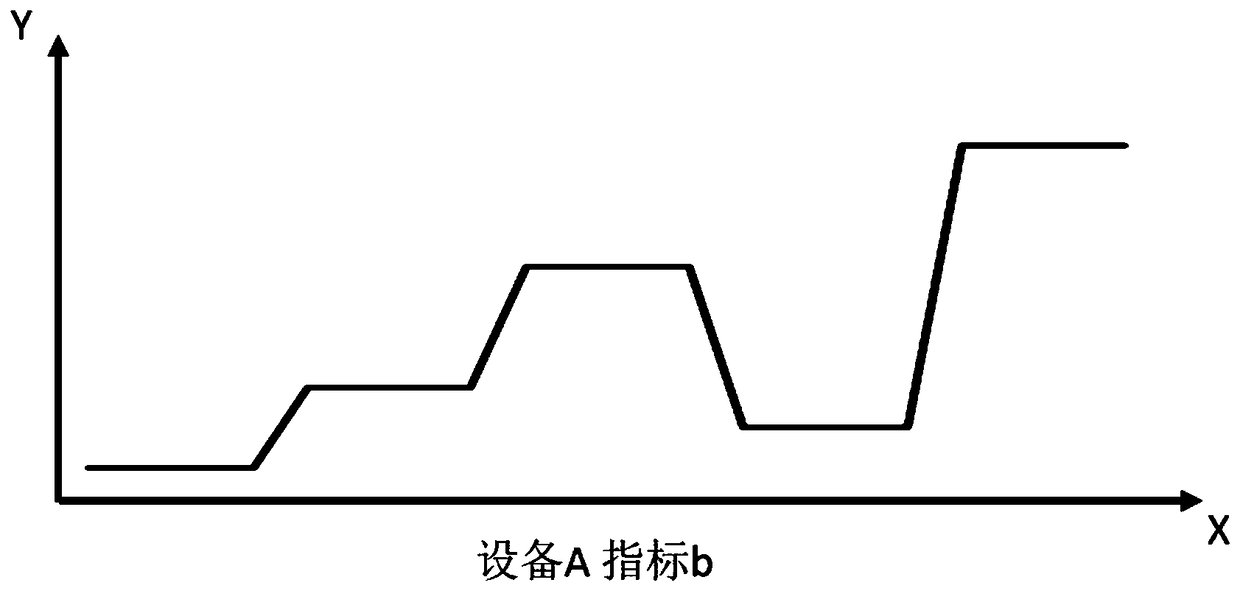

Safety monitoring method of electric power industrial control terminal based on service logic consistency

The invention discloses a safety monitoring method of electric power industrial control terminal based on service logic consistency, the invention aims at the safety problem of the electric power industrial control terminal equipment introduced by the diversified information in the 'Internet +' intelligent grid system, breaks through the existing attack detection method simply relying on the network space information, and puts forward a safety method of the electric power industrial control terminal based on the service logic consistency. By sampling the multi-modal data of physical world information and cyberspace information, normalized processing and temporal correlation, and through training, the safety monitoring set and parameter constraint set are obtained for safety monitoring andanomaly identification. From the business level, the method can effectively early-warn the state abnormality caused by equipment performance difference, equipment failure and hacker intrusion, and realize the 'time-state-service' trinity consistency safety monitoring of the electric power industrial control terminal based on equipment time logic, state logic and business logic.

Owner:HUANAN IND TECH RES INST OF ZHEJIANG UNIV

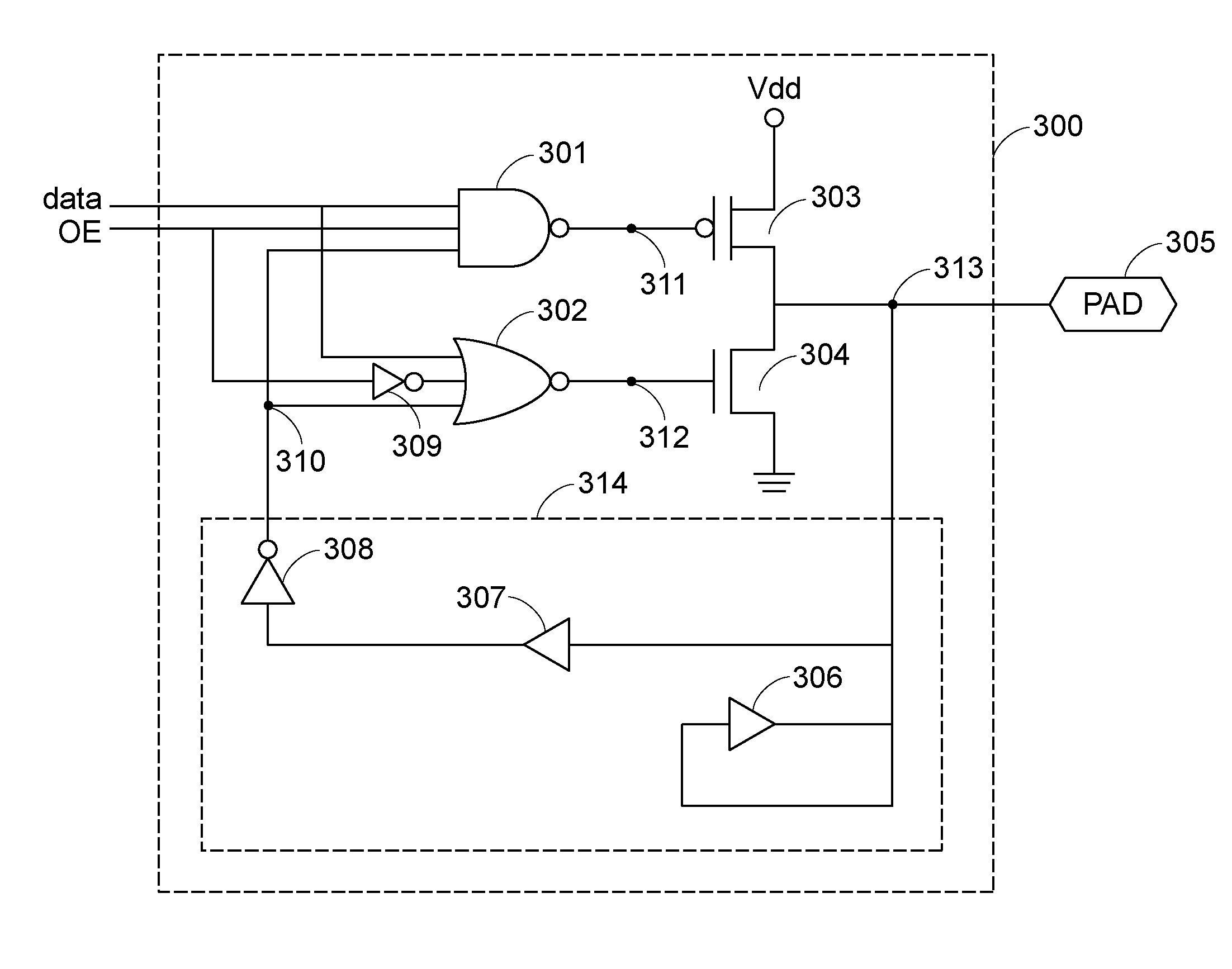

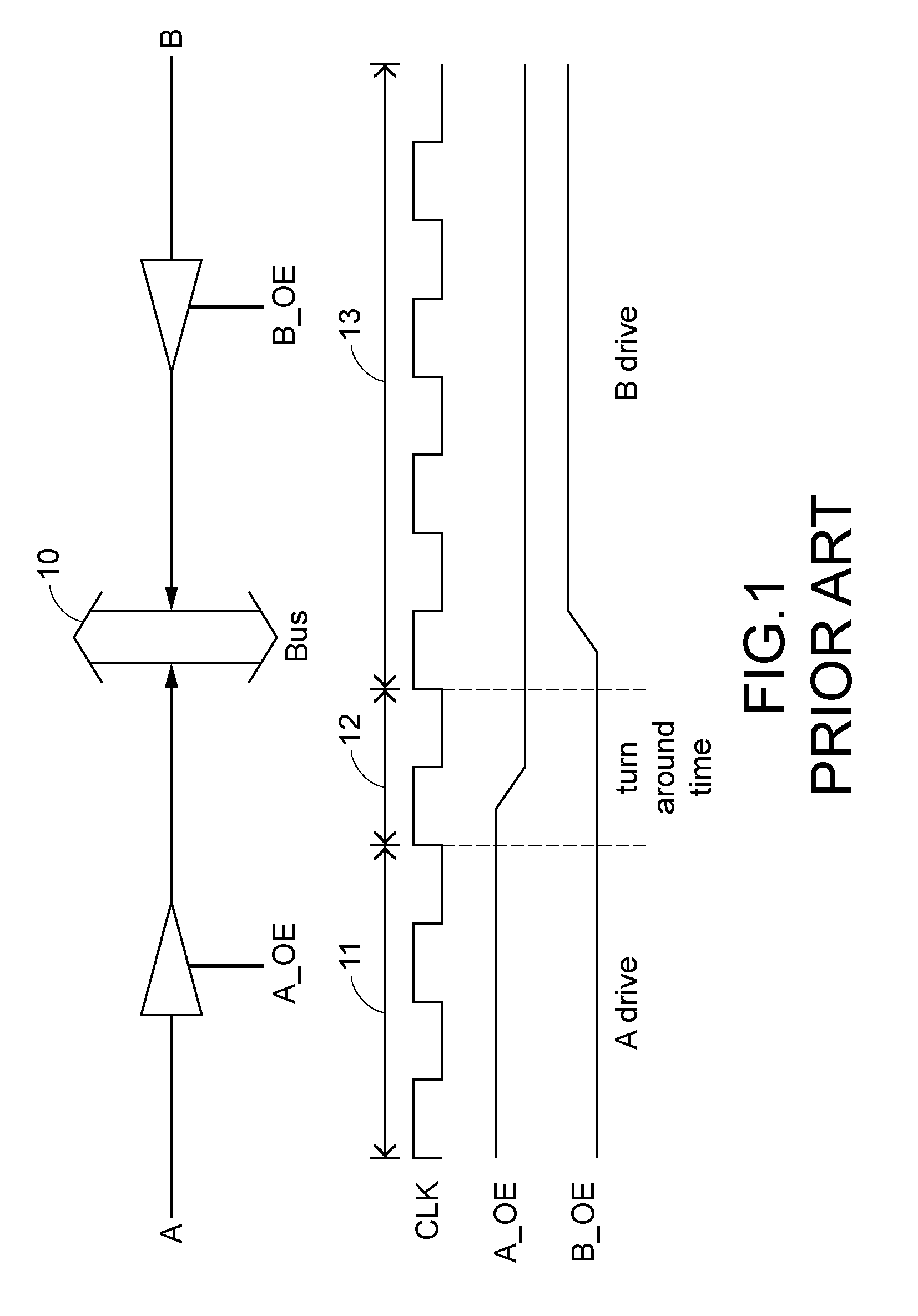

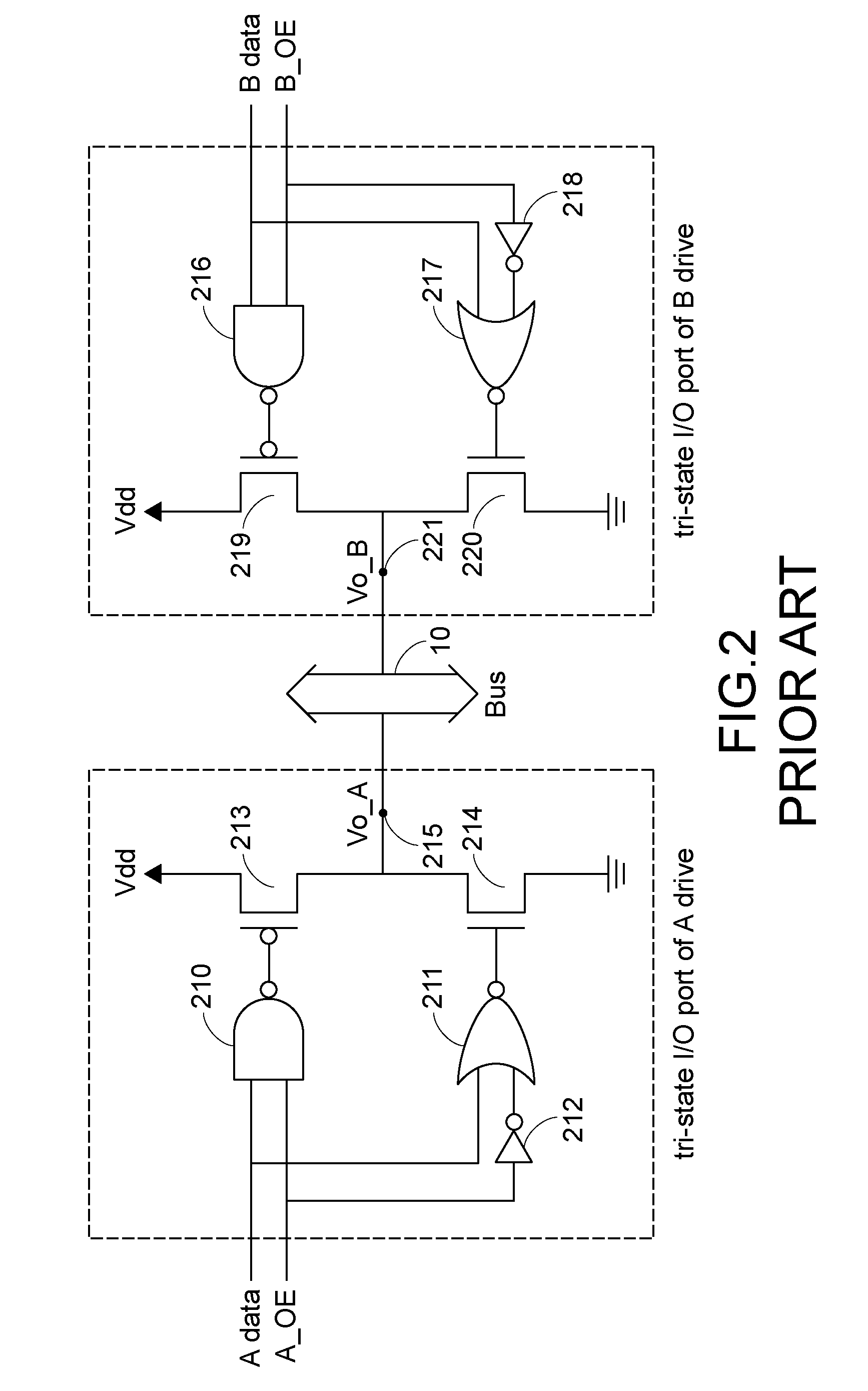

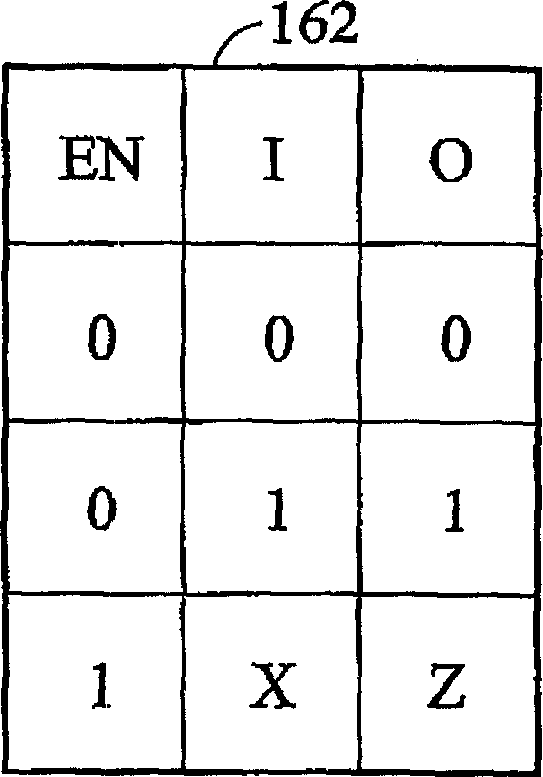

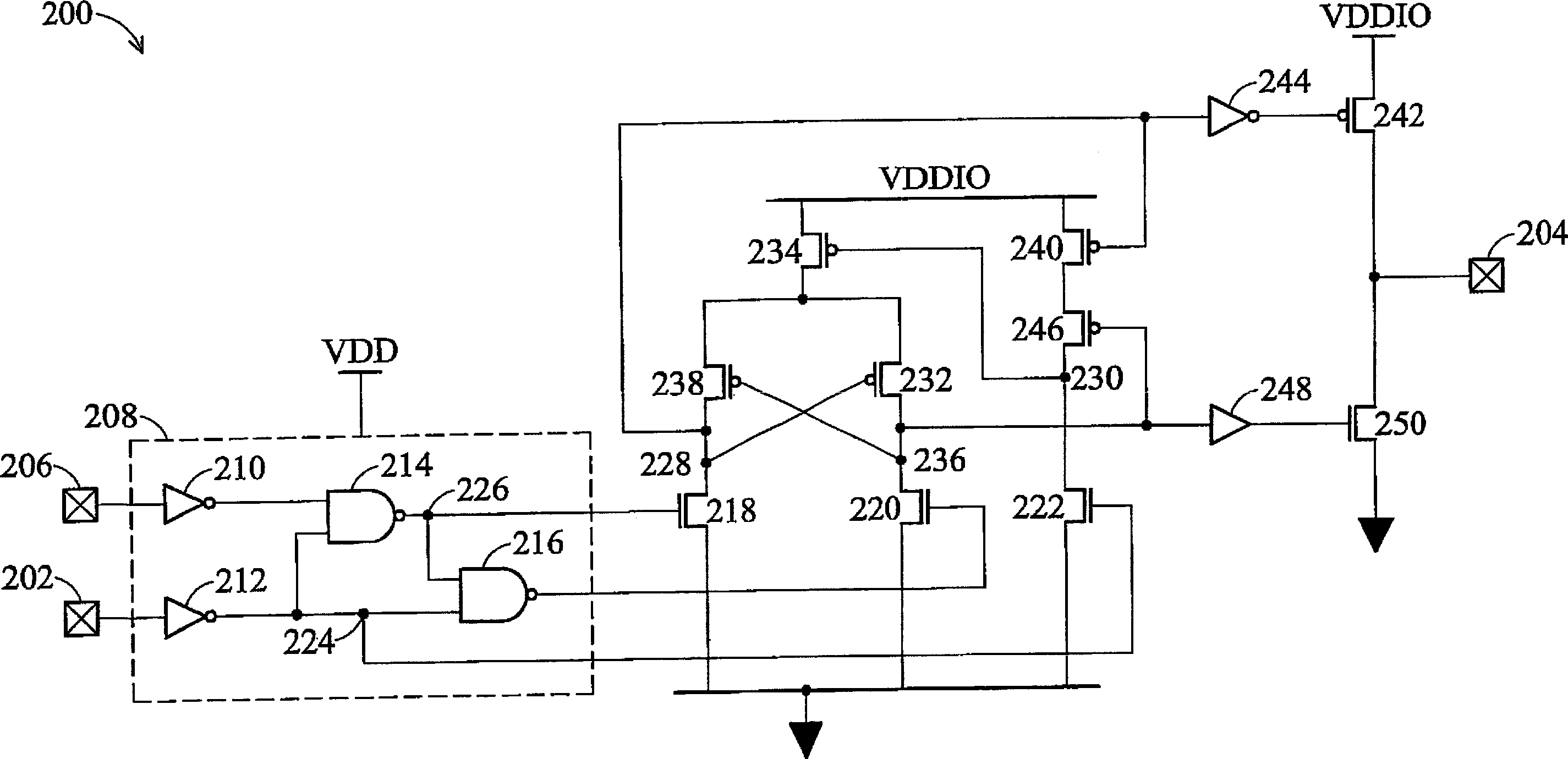

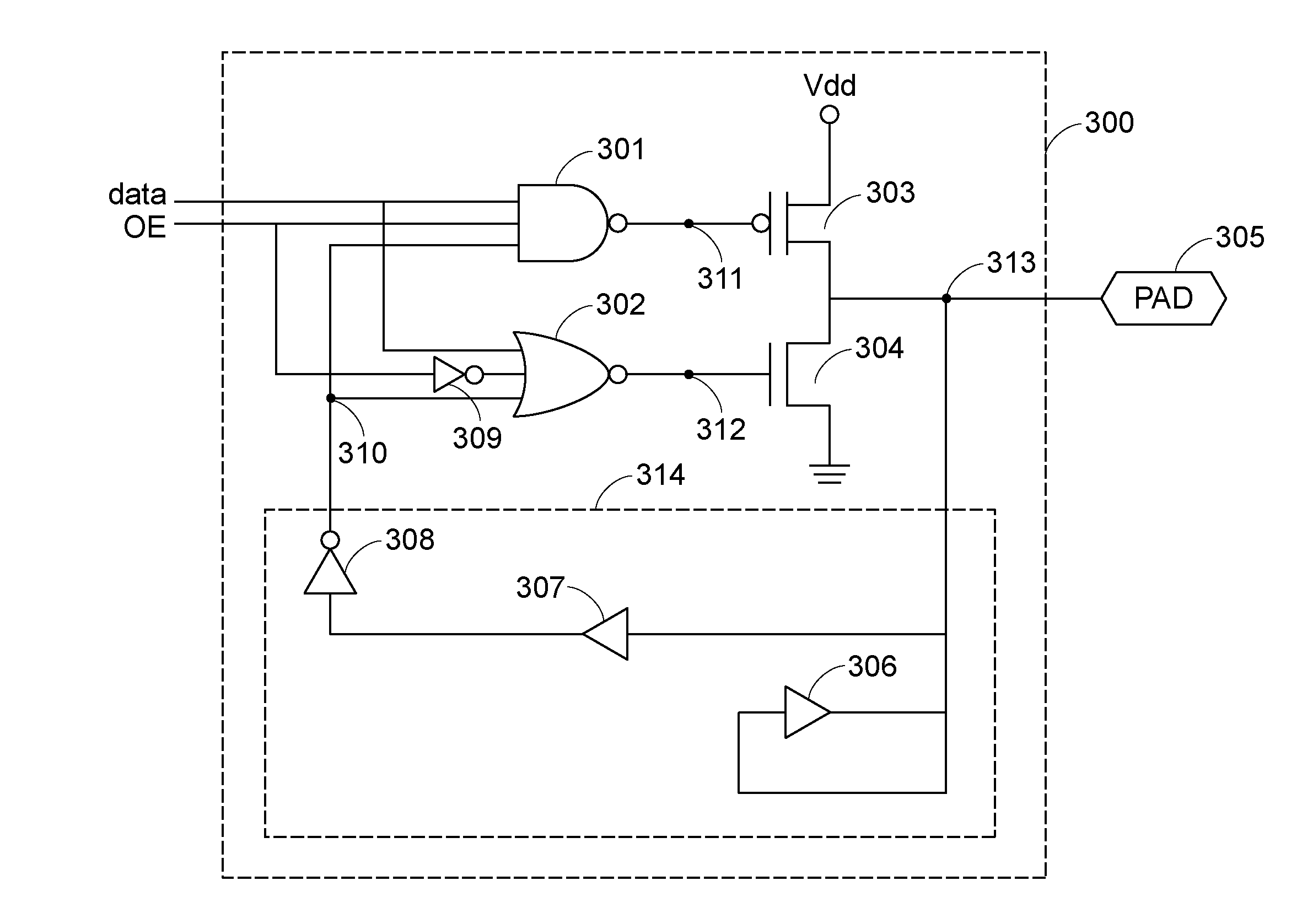

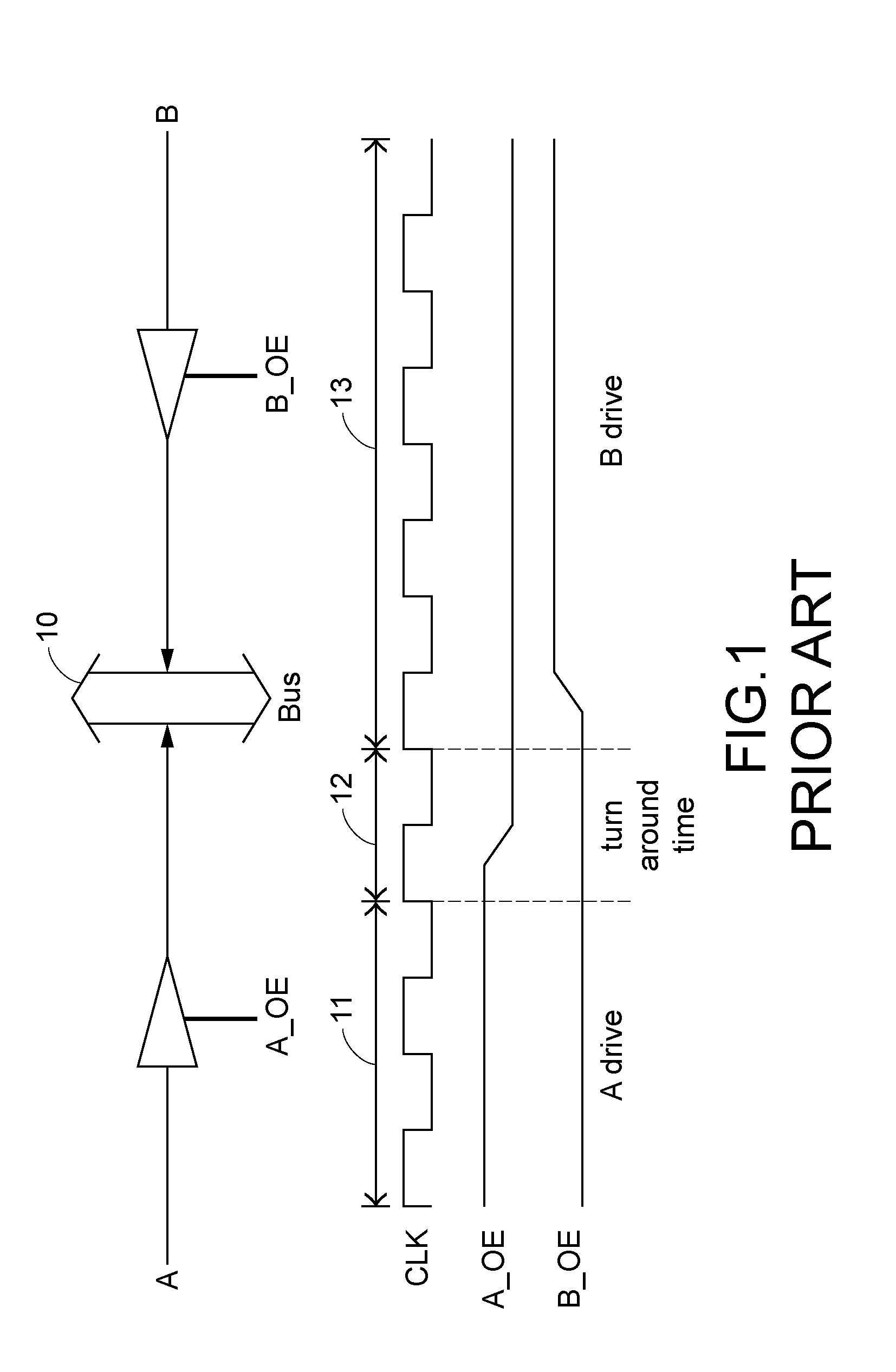

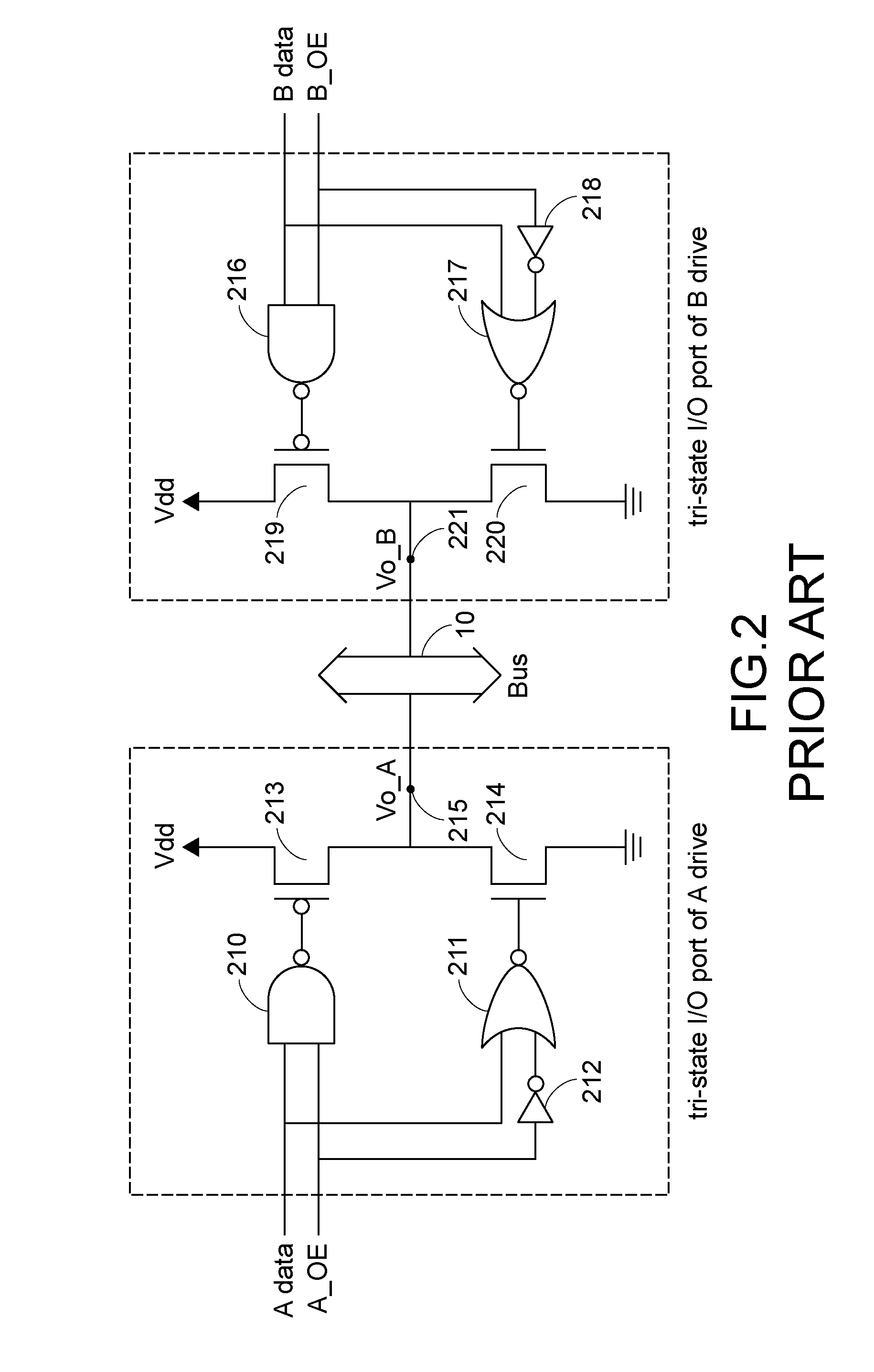

Tri-state I/O port

ActiveUS7863933B2Power downElectronic circuit testingElectric pulse generatorElectricityThree-state logic

The present invention discloses a tri-state I / O port. The tri-state I / O port comprises a tri-state logic block, a weak buffer and a delay block. The input terminals of the tri-state logic block are connected to data and OE (output enable) signals. When OE signal is enabled, the output terminal of the tri-state I / O block is pulled high when the data is high while the output terminal is pulled low when the data is low. The input terminal and the output terminal of the weak buffer are connected to the output terminal of the tri-state logic block. And the input terminal of the delay block is connected to the output terminal of the tri-state logic block while the output terminal of the delay block is fed back to the tri-state logic block. When the output terminal of the tri-state logic block is low to high / high to low, the weak buffer is active and maintains the output terminal of the tri-state logic block weak high / low while the delay block turns off the pull high / low function of the tri-state logic block.

Owner:RDC SEMICON CO LTD

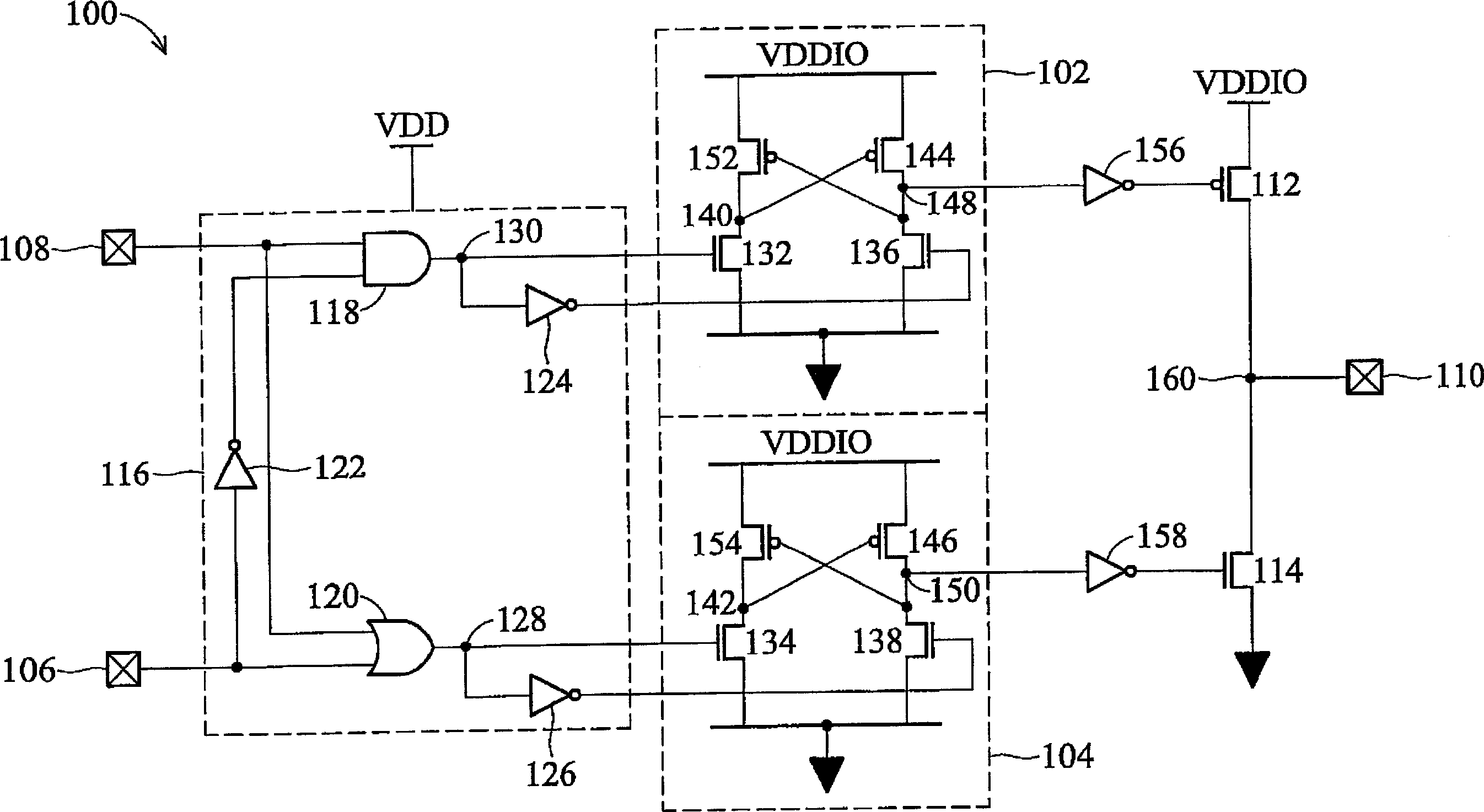

Dual-voltage three-state buffer circuit

ActiveCN1825767AReduce the configuration areaReduce switching energyPower reduction in field effect transistorsPower reduction by control/clock signalDriver circuitThree-state logic

A dual-voltage three-state buffer circuit controls a post driver circuit to operate in a three-state mode and includes a tri-state logic control module operated under a low supply voltage, a level shifter for receiving one or more inputs from the tri-state logic control module and operating with an output control circuit for controlling two differential outputs of the level shifter, and a post driver circuit driven by the two differential outputs of the level shifter, wherein the level shifter, the output control circuit, an the post driver circuit are operated under a high supply voltage, and wherein when the tri-state logic control module generates the inputs for putting the post driver circuit in a high impedance state, the output control circuit operates with the level shifter to turn off the PMOS and NMOS transistors of the post driver circuit while isolating the level shifter from a high supply voltage.

Owner:TAIWAN SEMICON MFG CO LTD

Integrated circuit with blocking pin to coordinate entry into test mode

An integrated circuit (IC) including a blocking pin. An IC may include state logic, a test control unit configured to coordinate access by external circuitry to operating state of the state logic during a test mode, and interface pins configured to couple the integrated circuit to the external circuitry. Shared interface pins may provide input signals to the test control unit during the test mode of operation and may perform distinct I / O functions during normal mode operation. A blocking interface pin, when asserted by external circuitry during normal mode operation, may force test signals derived from at least a portion of the shared interface pins by the test control unit into respective quiescent states, such that subsequent to assertion of the blocking pin, the integrated circuit is operable to enter the test mode of operation from the normal mode of operation without resetting operating state of the state logic.

Owner:ORACLE INT CORP

Driver circuit for a two-wire conductor and method for generating two output currents for a two-wire conductor

ActiveUS7888969B2Reliability increasing modificationsTransmission control/equlisationDriver circuitElectrical conductor

Owner:INFINEON TECH AG

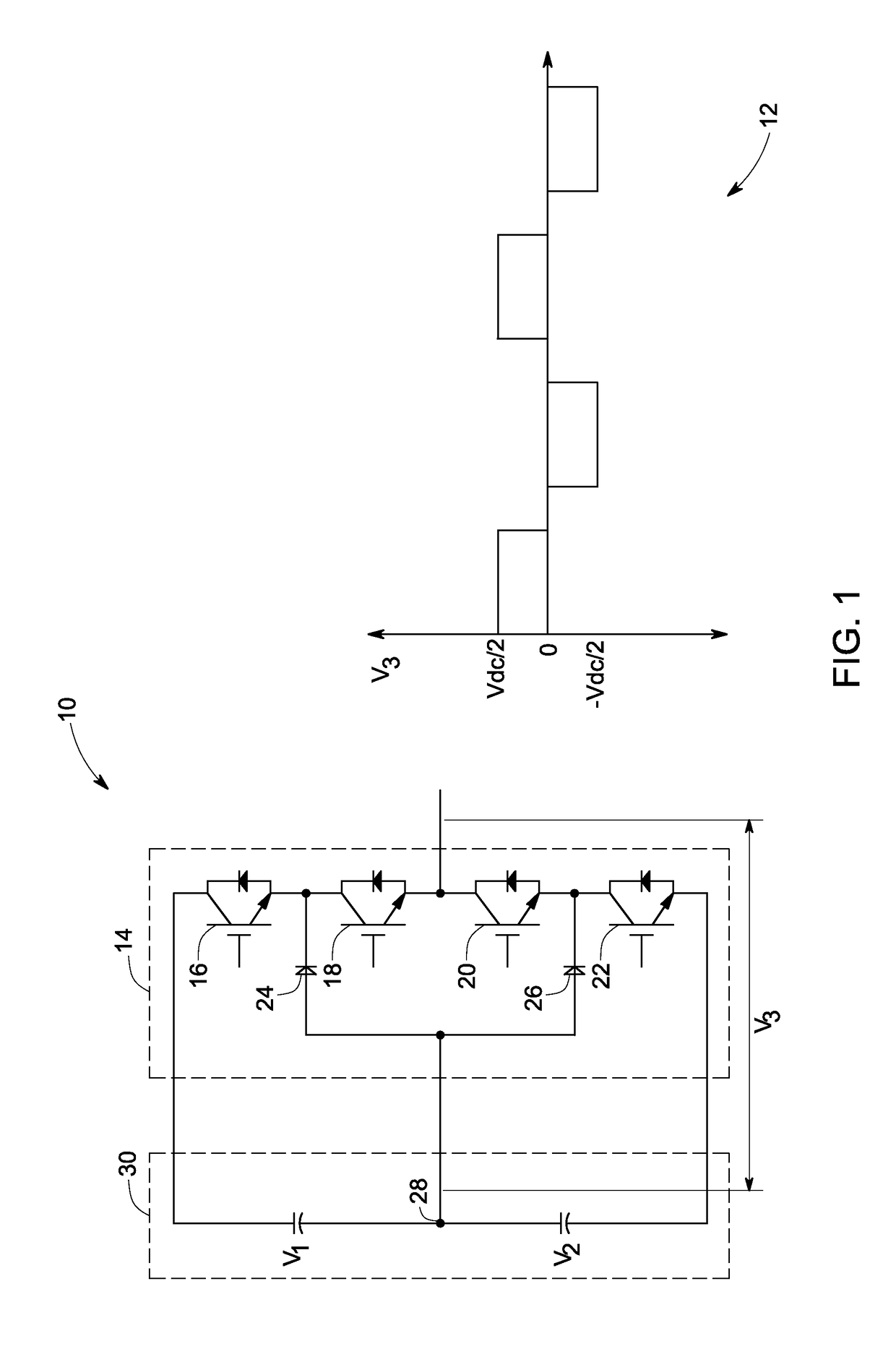

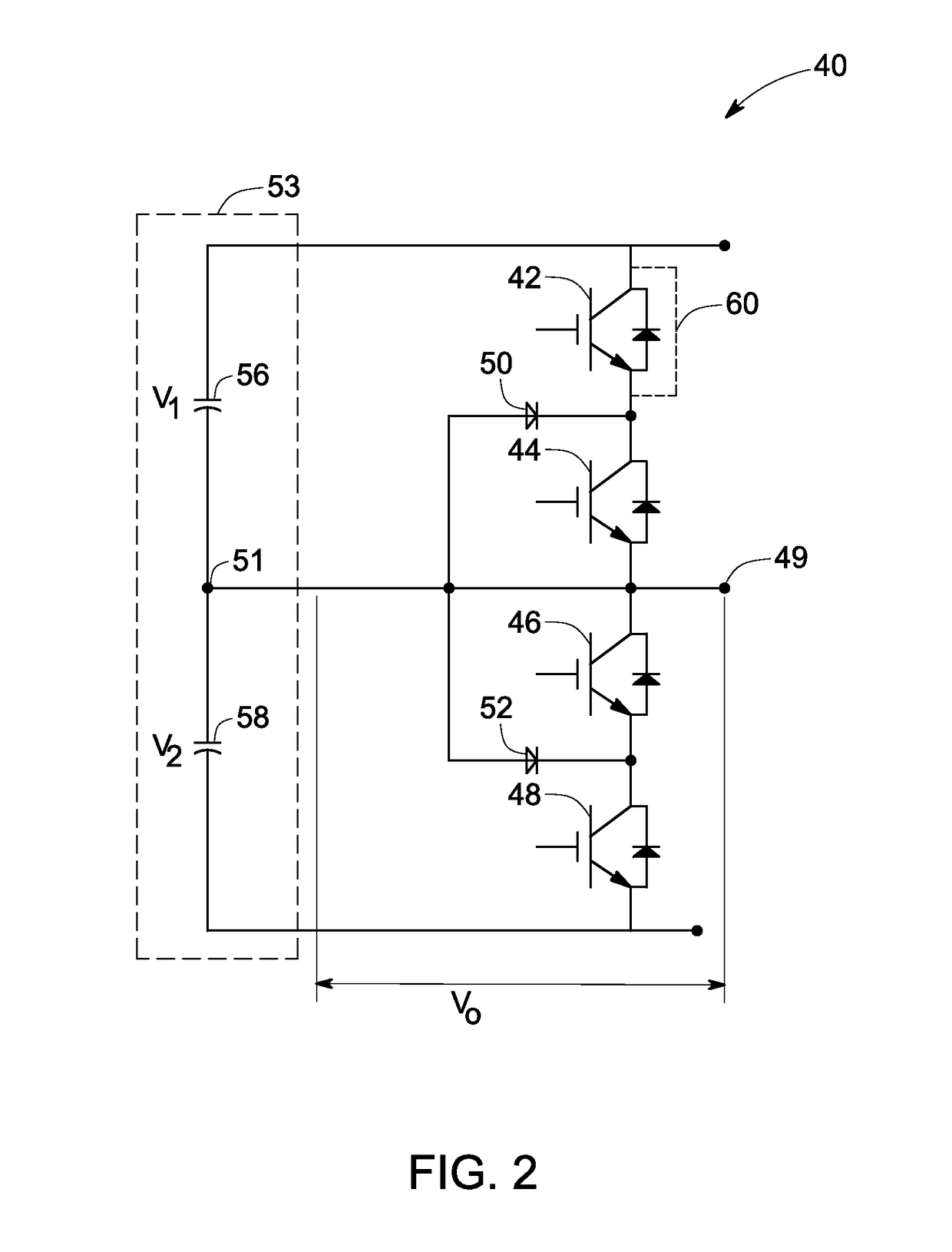

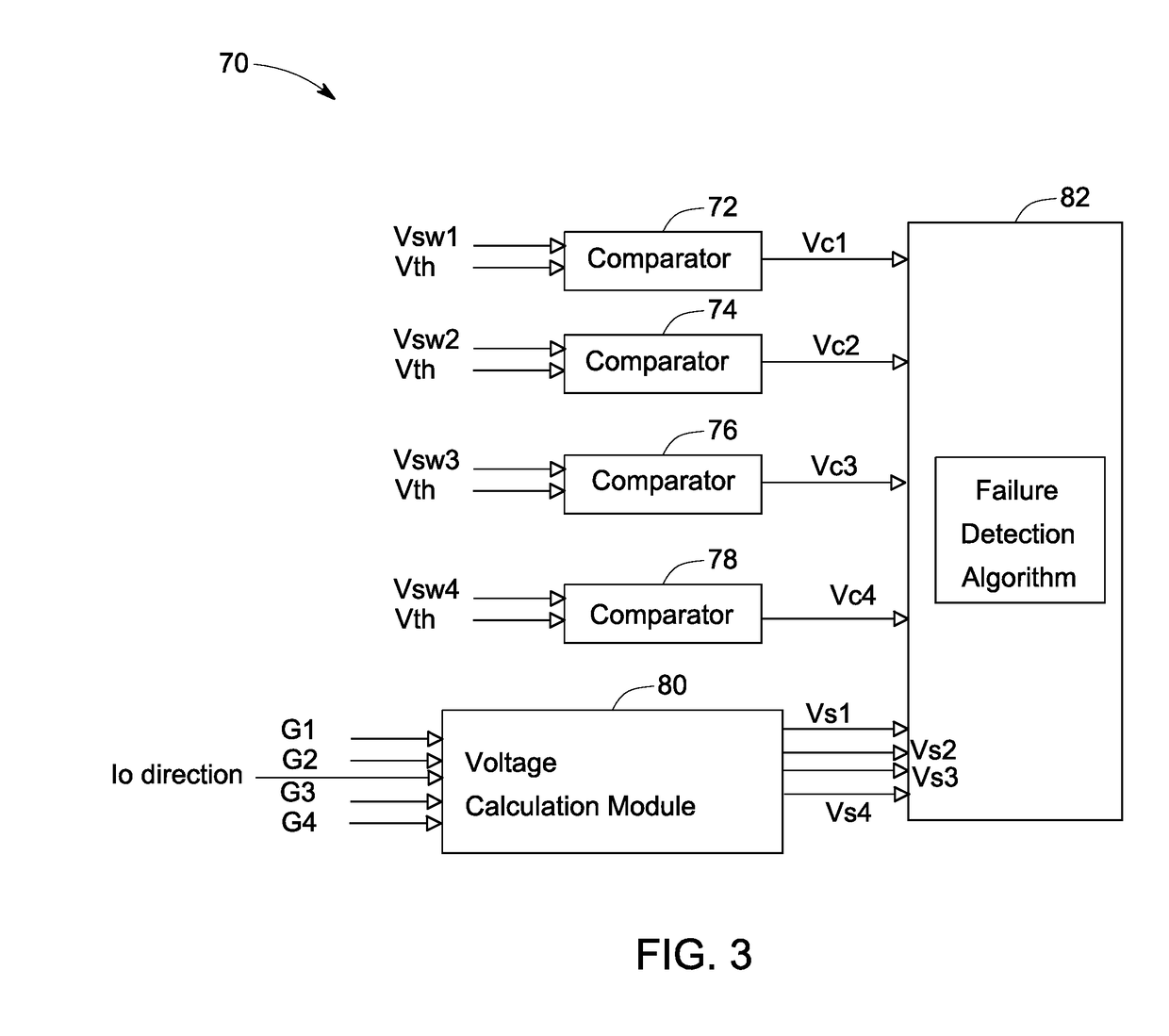

Switching device failure detection system and method for multilevel converters

A multilevel converter includes a plurality of phase legs each having at least two inner switching devices, at least two outer switching devices, at least two clamping diodes, a split DC link and a switching device failure detection circuit. The switching device failure detection circuit includes a logic module for each of the switching devices, a voltage calculation module and a failure detection algorithm. The logic module generates a blocking state logic signal by comparing a switching device voltage and a threshold reference voltage and the voltage calculation module determines an expected voltage blocking state for each of the switching devices based on the gate drive signals of the switching devices and an output current direction. The failure detection algorithm detects a failure condition in any of the switching devices based on the blocking state logic signals and the expected voltage blocking states of the switching devices.

Owner:GE INFRASTRUCTURE TECH INT LLC

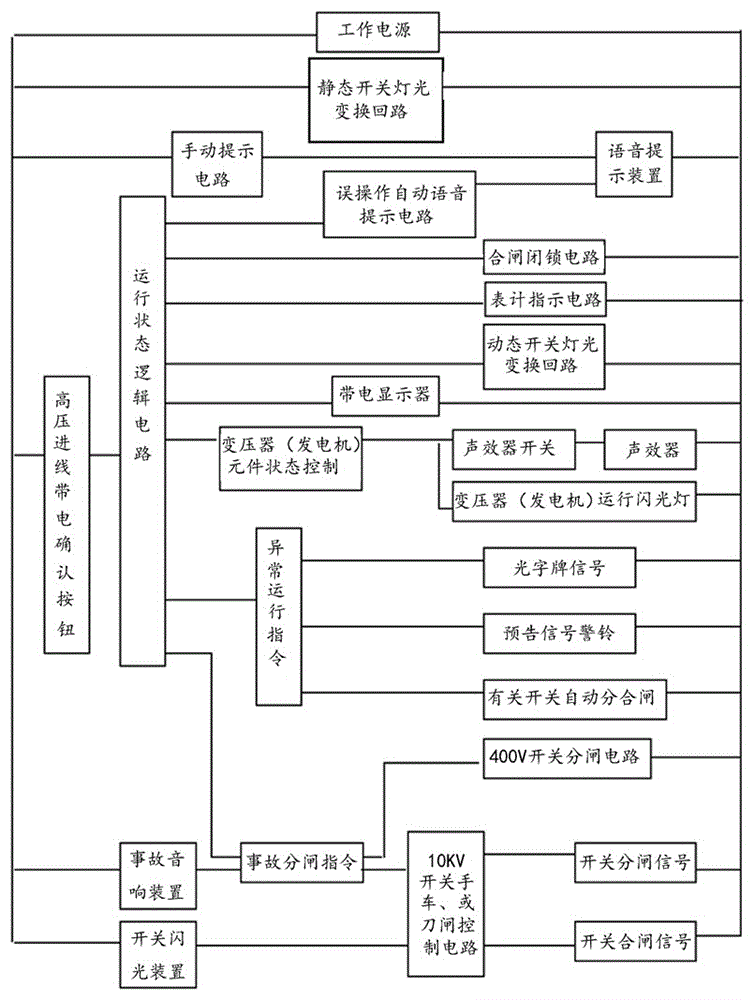

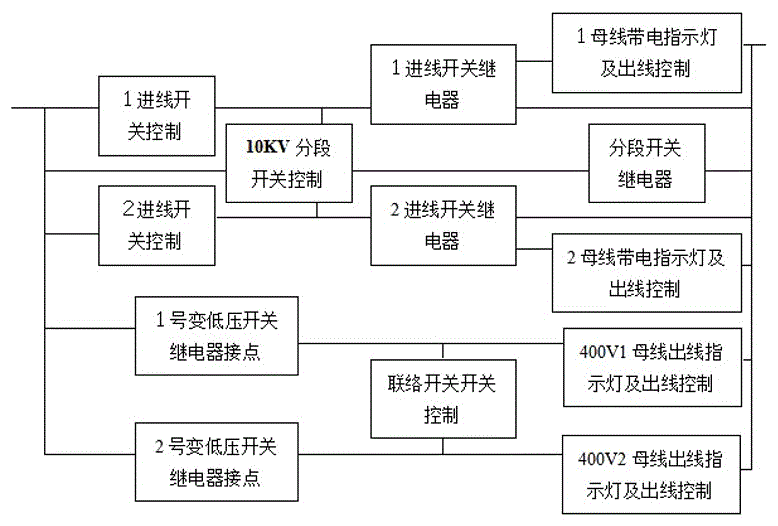

Transformation and distribution room simulation controller

ActiveCN105741653AImprove operational skillsHigh degree of simulationEducational modelsTransformerEconomic benefits

The invention discloses a transformation and distribution room simulation controller which comprises a high-voltage inlet wire live confirmation button, an operation state logic circuit, a transformer component state control module and a maloperation voice prompting module. According to the transformation and distribution room simulation controller, a master switch which is basically same with a transformation and distribution room, an instrument and a signal are utilized; accessing of high-voltage electrical equipment is not required; program operation, instrument and accident state and safety measure setting are realized through a light current logic circuit. An operation program which is similar with field high-voltage equipment is installed. The transformation and distribution room simulation controller has an advantage of high accident state simulation degree. The transformation and distribution room simulation controller is suitable for large-scale personnel training and can effectively and quickly improve operation skill of personnel and reduce or prevent electrical accidents and personal casualty accidents. Furthermore the transformation and distribution room simulation controller has high economic benefic and high economic benefit.

Owner:SHANDONG PINGAN ELECTRIC EQUIP CO LTD

On-chip leakage current modeling and measurement circuit

ActiveUS8214777B2Current/voltage measurementDetecting faulty computer hardwareEngineeringControl circuit

A leakage current monitor circuit provides an accurate statistically representative analog of true off-state leakage current in a digital circuit integrated on a die. At least one N-type transistor and at least one P-type transistor separate from the digital circuit are sized to represent the total area of the corresponding type transistors in the digital circuit. The gates of the N-type transistor and P-type transistors are set to voltages according to the corresponding off-state logic levels of the digital circuit. The N-type and P-type transistors form a portion of corresponding current mirror circuits, which can provide outputs to a leakage current monitor and / or a control circuit such as a comparator that determines when leakage current for the N-type or P-type devices has exceeded a threshold. The output of the measurement / control circuit can be used to determine a temperature of and / or control operation of the digital circuit or the system environment of the integrated circuit.

Owner:GLOBALFOUNDRIES US INC

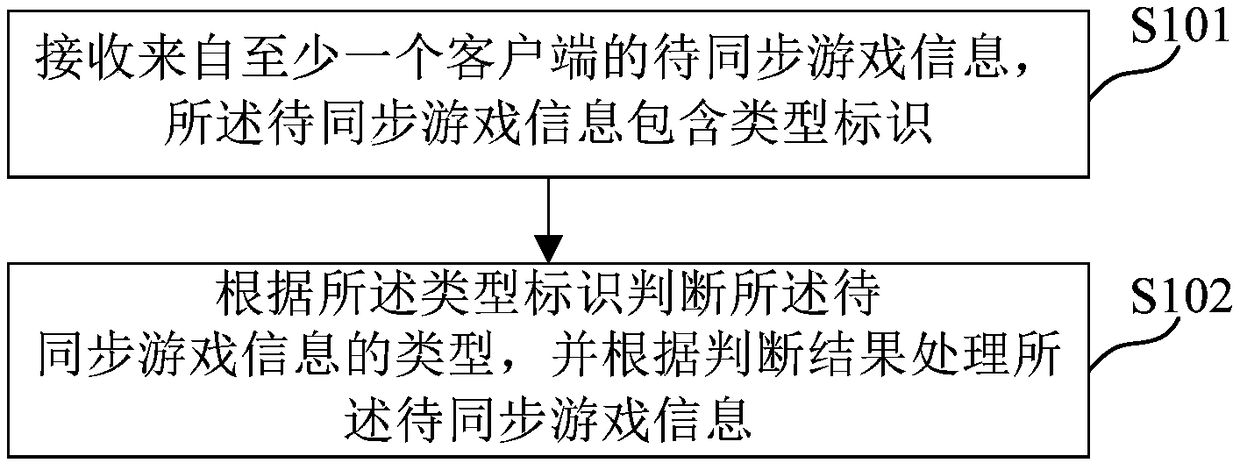

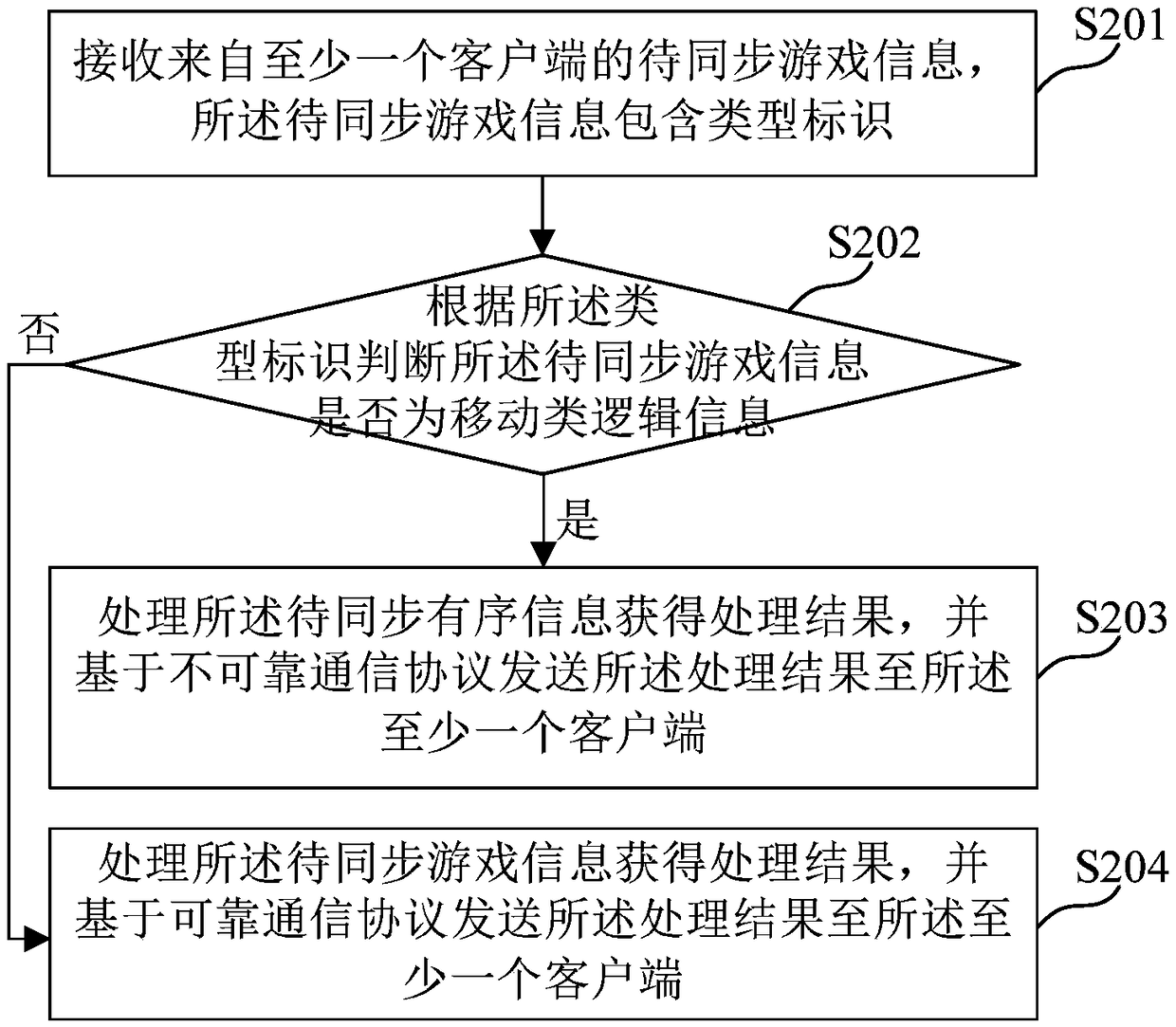

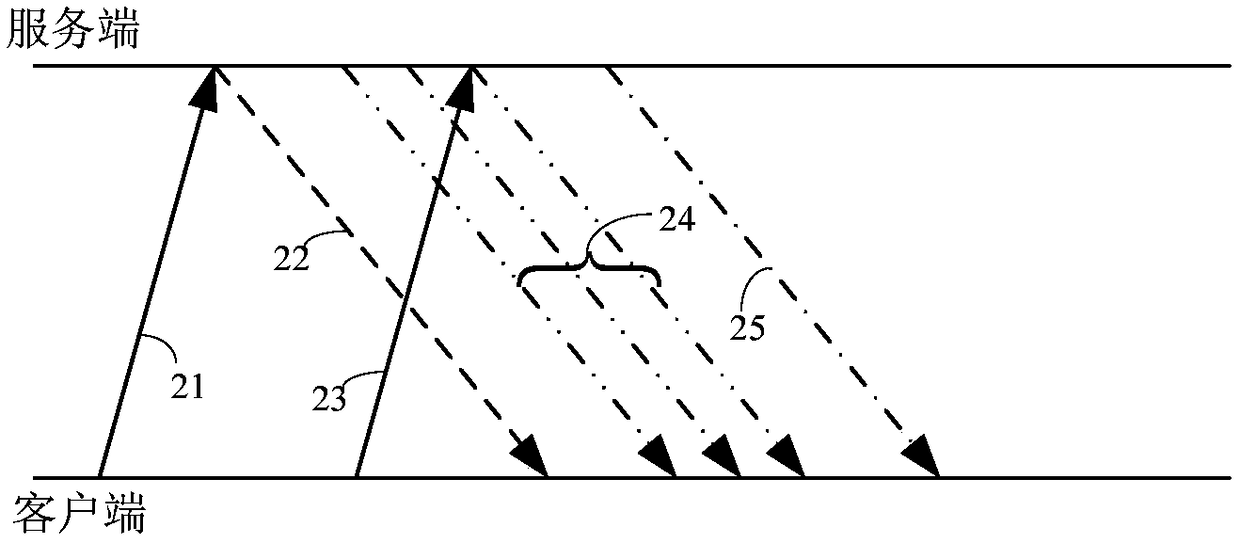

Synchronizing method of game information, server-side, client-side, medium and electronic device

ActiveCN109276883AAvoid delays in propagationAvoid missing questionsVideo gamesGame playerClient-side

The embodiment of the invention provides a synchronizing method of game information, a server-side, at least one client-side, a computer medium and an electronic device. The synchronizing method of game information comprises the following steps: receiving to-be-synchronized game information from the at least one client-side, wherein the to-be-synchronized game information comprises type identifiers; and judging the type of the to-be-synchronized game information according to the type identifiers, and processing the to-be-synchronized game information according to the judging result, so that synchronous display is carried out on the at least one client-side according to the to-be-synchronized game information. According to the technical scheme of the embodiment of the invention, the delay during the propagation process of the mobile logic information can be avoided, the moving smoothness of a virtual object in a game scene is improved, and the game experience of a game player is enhanced. Meanwhile, the problem of leak of the key information including the state logic information is avoided, and thus the game experience close to the reality is brought to the game player.

Owner:NETEASE (HANGZHOU) NETWORK CO LTD

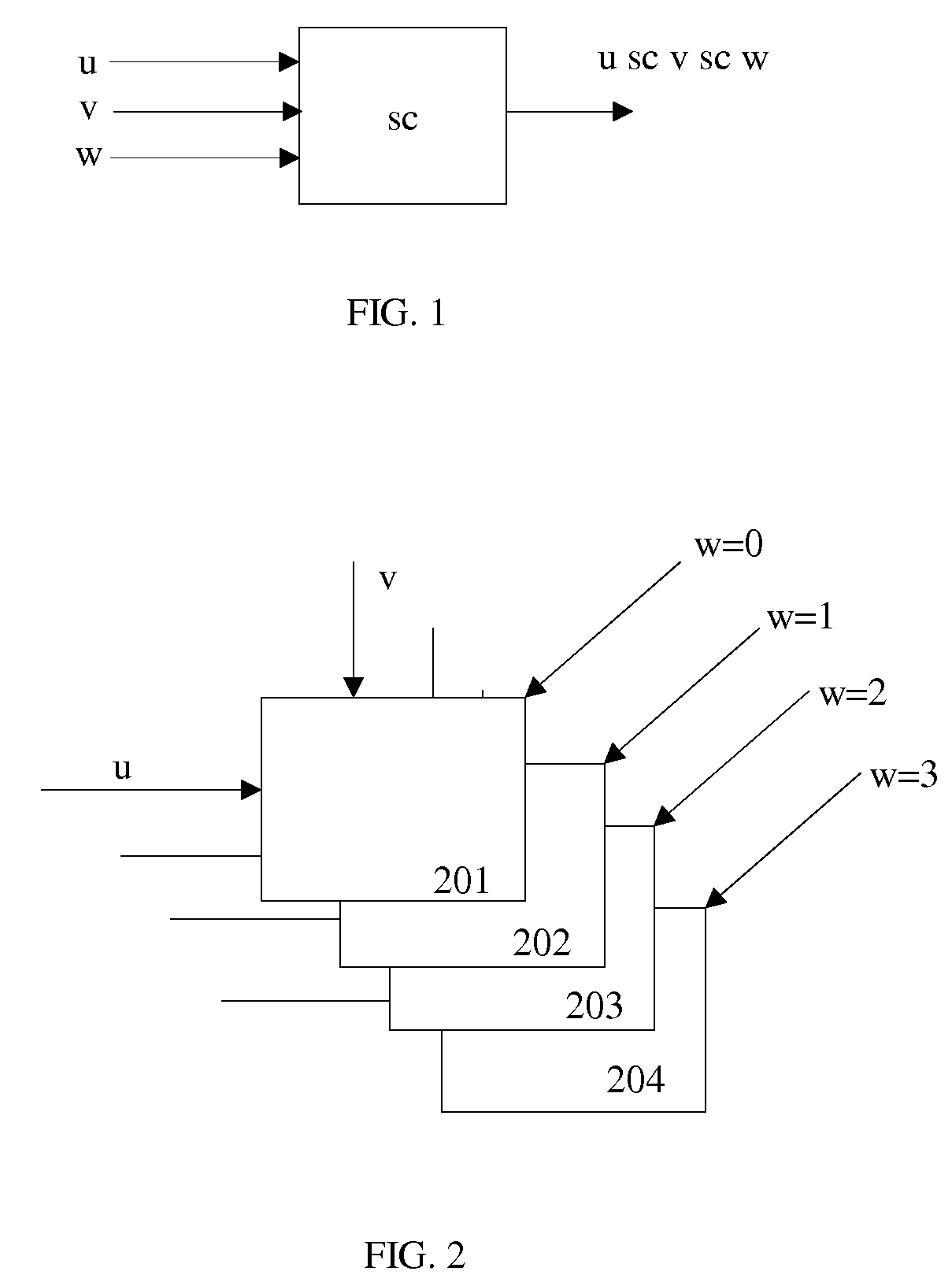

Multi-Input, Multi-State Switching Functions and Multiplications

InactiveUS20090077151A1Reduce component countReduce the possibilityComputation using non-contact making devicesMulti inputDigital signal processing

Methods to create an implementation for a multi-input n-state logic function with at least one inverter at an input by modifying the truth table according to the inverter into a reduced truth table are provided. Implementations of the reduced truth table by gates and inverters are also disclosed. Applying reduced truth tables in n-state multiplications are also provided. N-state multiplications may be used in filters, Digital Signal Processing or in Linear Feedback Shift Registers (LFSRs). Using implementations of reduced truth tables in n-state multiplications are disclosed.

Owner:LABLANS PETER

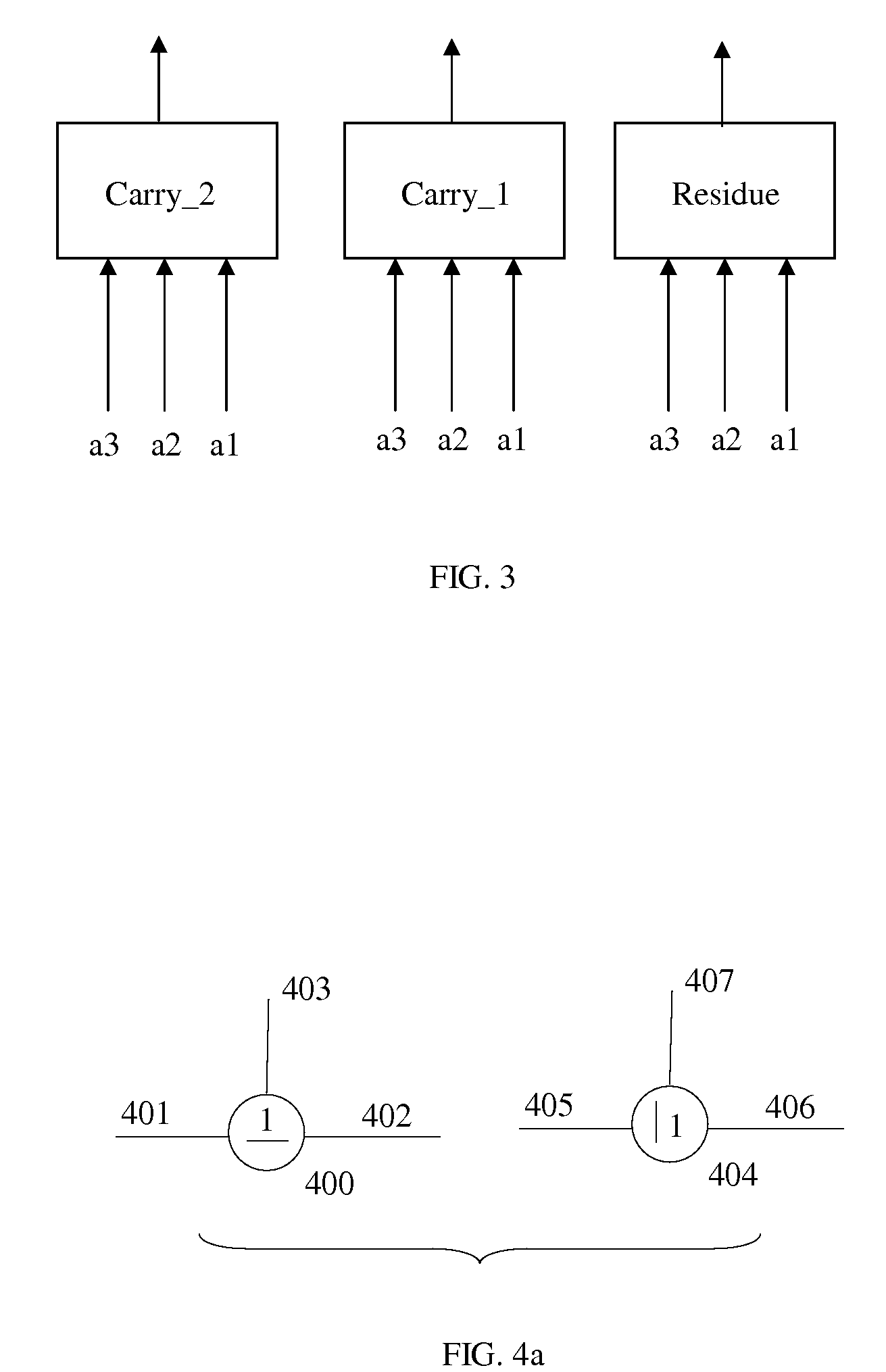

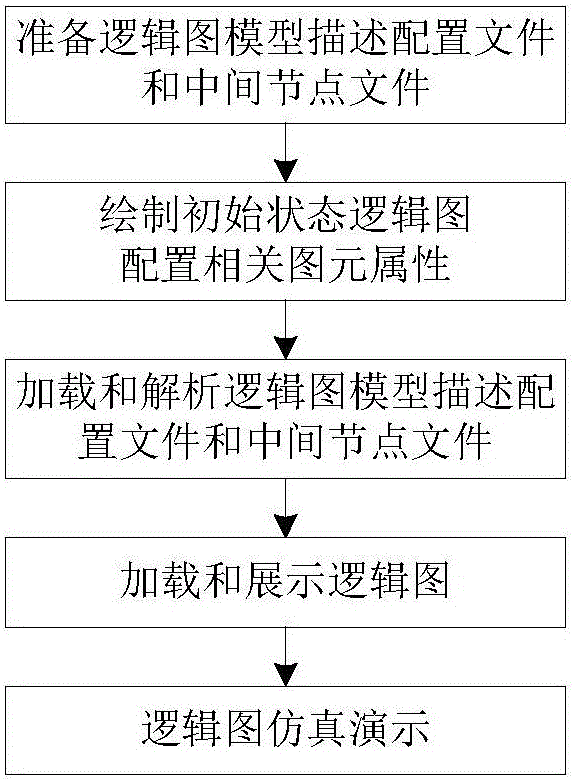

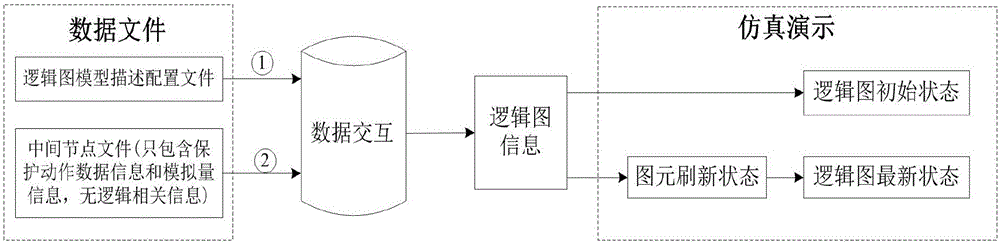

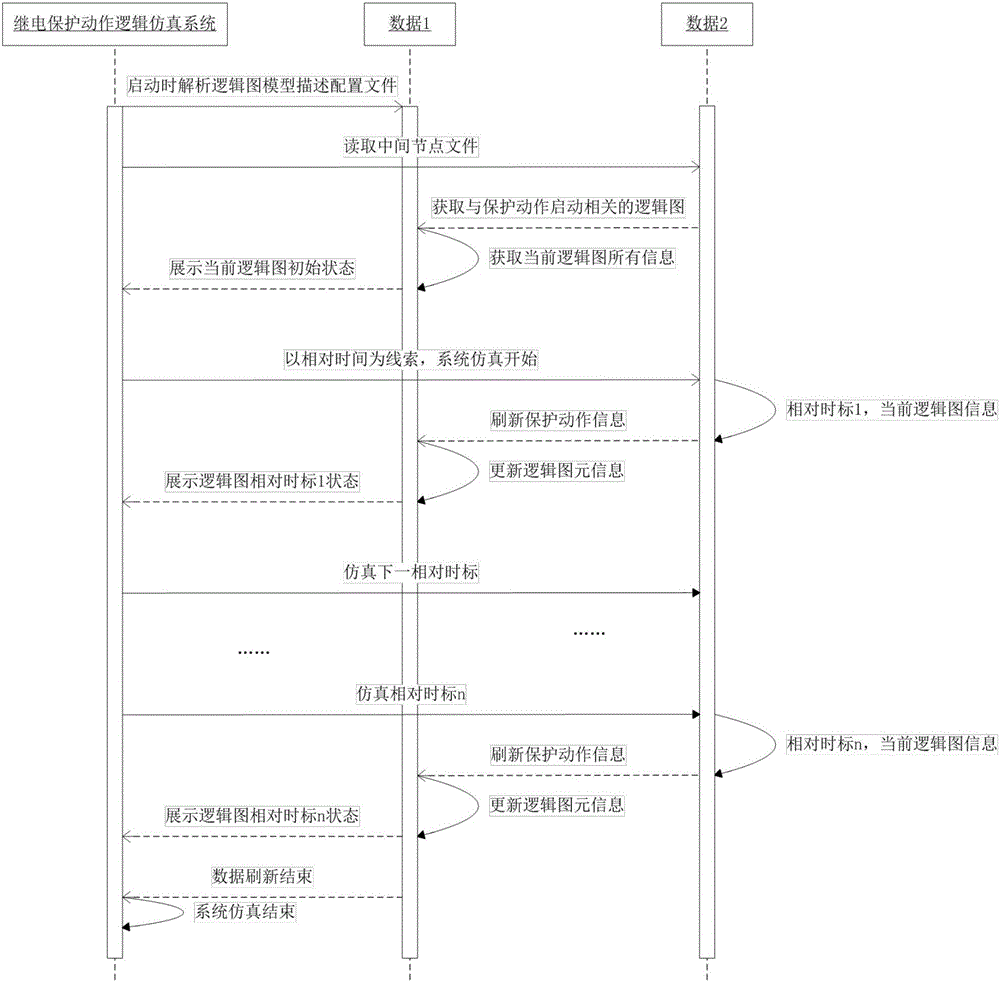

Relay protection action logic simulation realization method

InactiveCN105808831AIntegrity guaranteedGuaranteed real-timeData processing applicationsSpecial data processing applicationsCouplingMaintainability

The invention discloses a relay protection action logic simulation realization method. The method comprises the steps of preparing a logic graph model description configuration file and an intermediate node file; drawing an initial state logic graph and configuring related graphic element attributes; loading and analyzing the logic graph model description configuration file and the intermediate node file; loading and displaying the logic graph; and performing simulated demonstration on the logic graph. The method inherits object-oriented and modular design concepts, and has the advantages of high cohesion, low coupling, high maintainability and portability, and the like. Relay protection action logic simulation system software is developed based on the method described by the invention; and the simulation system software can simulate a protection action operation state of any fault type and fault point, and has the advantages of accuracy, intuitiveness, flexibility in use, high efficiency and the like.

Owner:INTEGRATED ELECTRONICS SYST LAB

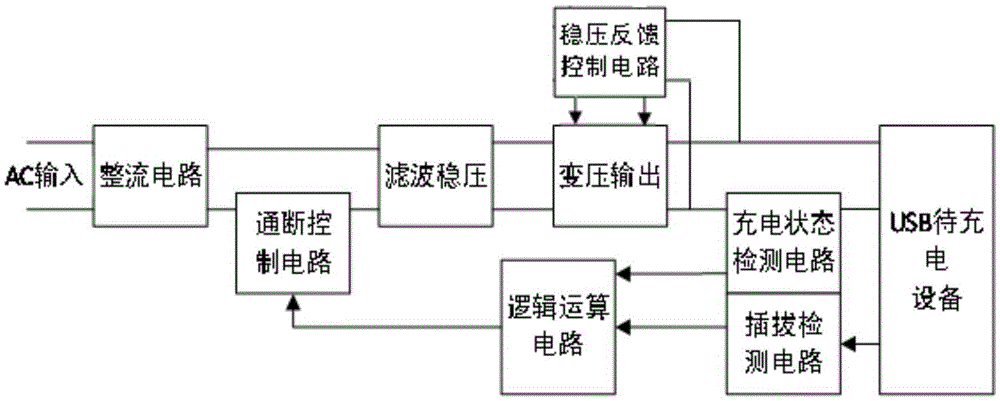

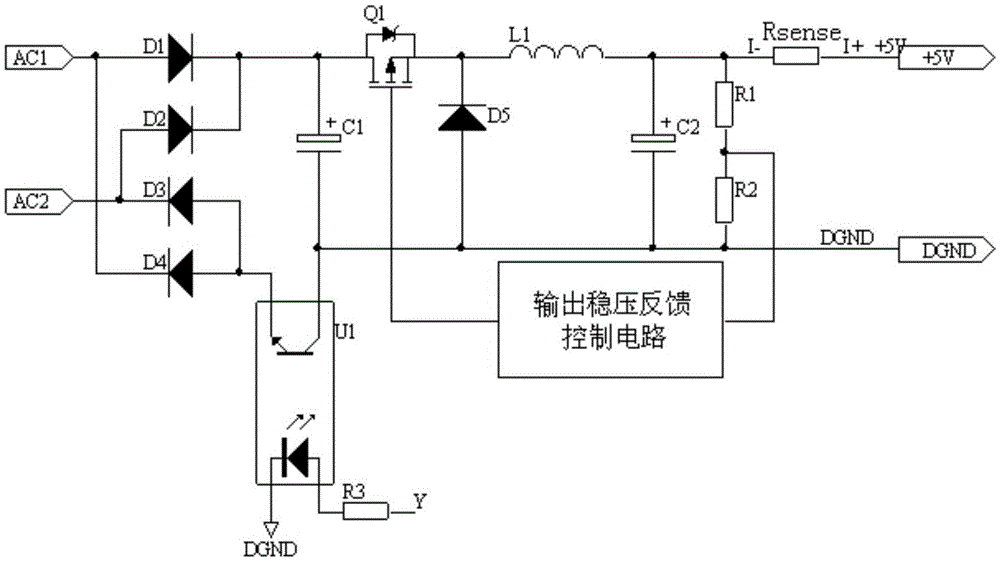

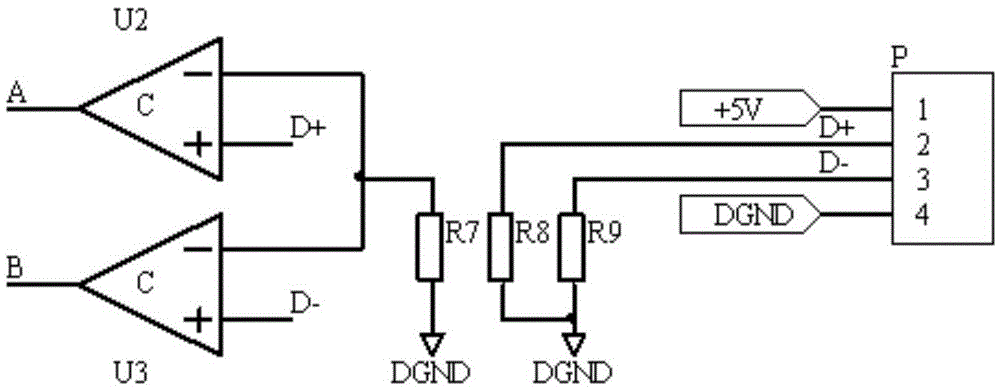

Intelligent charger with universal serial bus (USB) interface

InactiveCN105490361AIntelligent detection accessIntelligent detection and removalMobile unit charging stationsElectric powerElectricityControl signal

The invention relates to an intelligent charger with a universal serial bus (USB) interface. AC 220V current sequentially passes through a sorting circuit, a filtering voltage-stabilization circuit and a voltage transformation circuit and then is output to a USB device to be charged, the output end of the voltage transformation circuit is connected with a charging state detection circuit, a USB interface of the USB device to be charged is connected with a pull and plug detection circuit, the output ends of the charging state detection circuit and the pull and plug detection circuit are connected with a device comprehensive state logic operation circuit, the output end of the device comprehensive state logic operation circuit is connected with an on / off control circuit, the output end of the on / off control circuit is connected with the output end of a rectification circuit and can be used for switching on / off the input of a power supply, and the output end of the voltage transformation circuit is used for controlling duty cycle of a switching tube in the voltage transformation circuit according to a control signal output from a voltage-stabilization control circuit. By the intelligent charger, the access and the pull-out of a charging device are intelligently detected, power is automatically cut off from a source head after the device is pulled out, charging is automatically carried out after the device is inserted, and power is automatically cut off after the charging is full; and meanwhile, the intelligent charger has an overcurrent protection function, and the power supply is automatically cut off when overcurrent occurs so as to prevent an accident.

Owner:SHANGHAI INST OF TECH

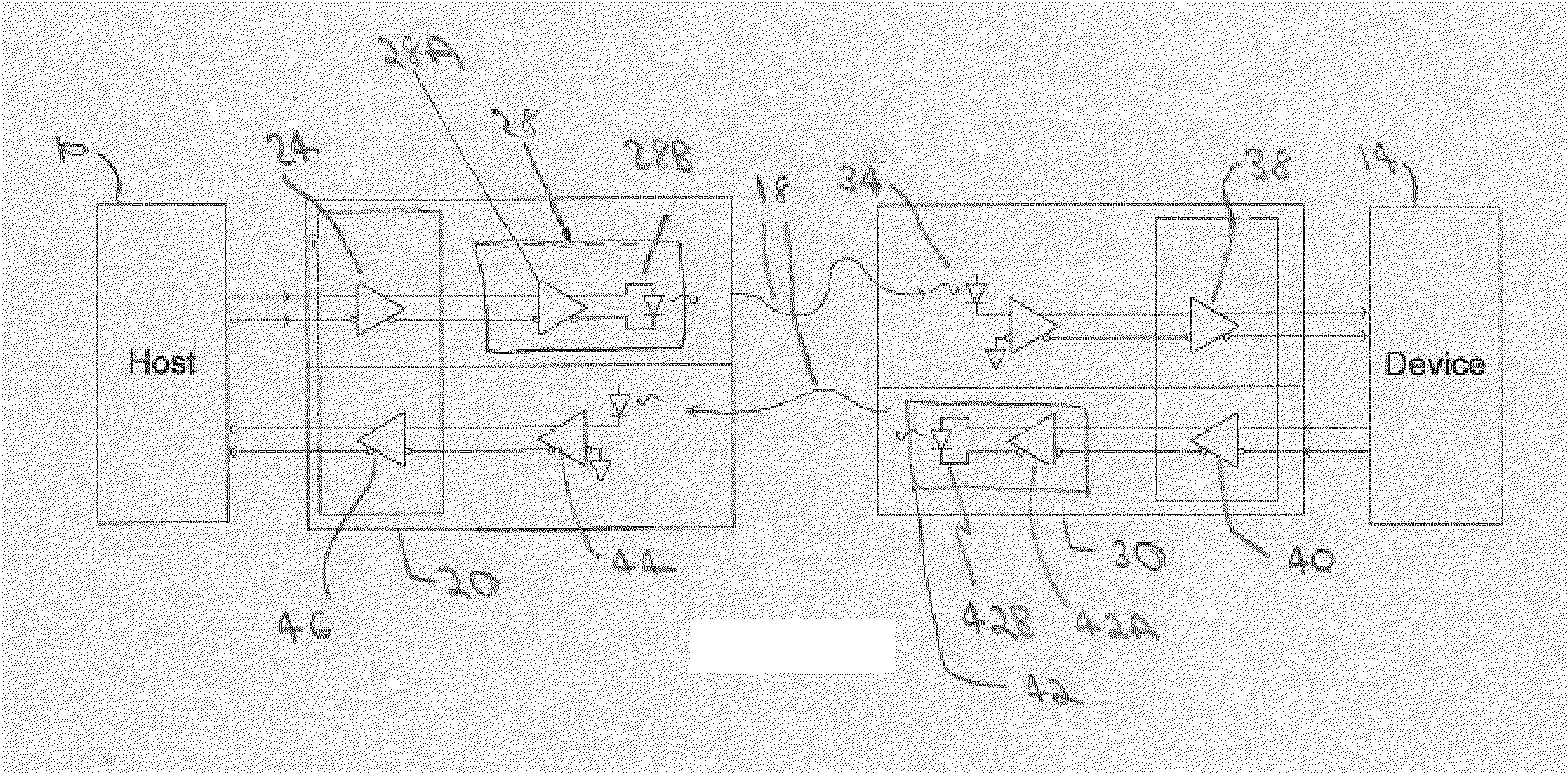

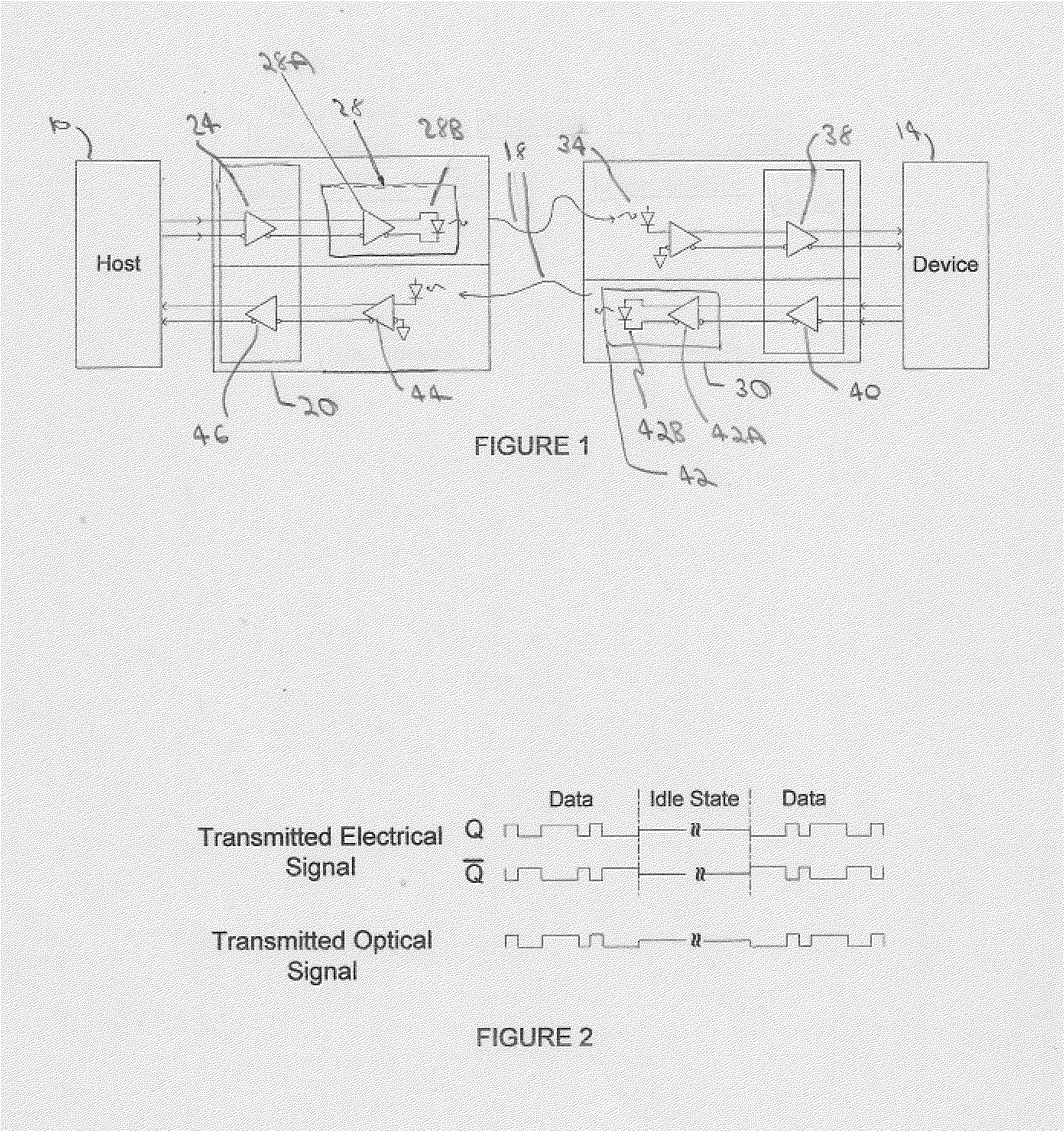

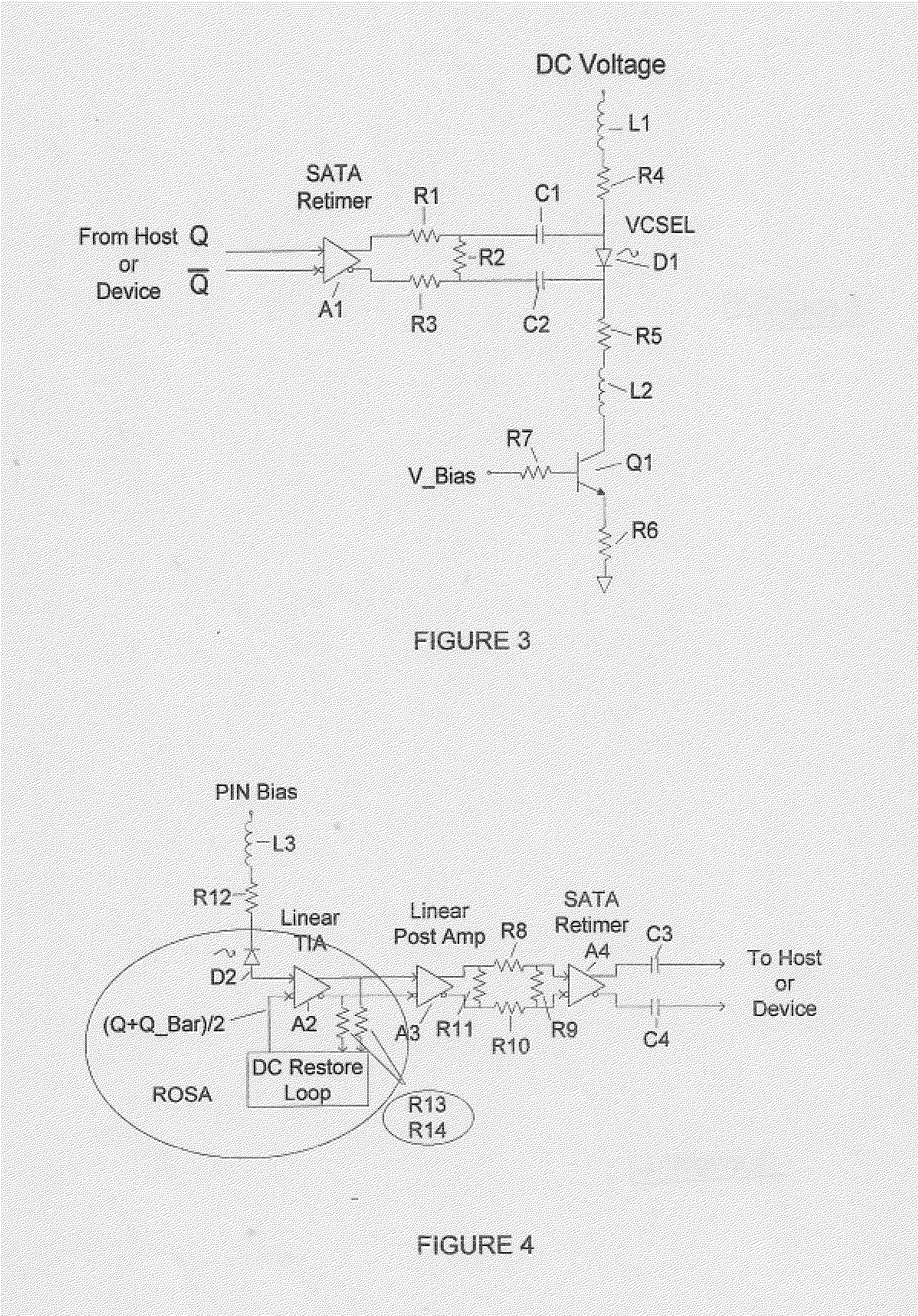

Device for sending and receiving SATA signals over an optical fiber link

A system for transmitting an optical signal between a host and a device according to a SATA protocol. The system comprises a transmitting-side converter for generating a logic one voltage value responsive to a data one value from an information source, for generating a logic zero voltage value responsive to a data zero value from the information source, for generating an idle state logic voltage value, wherein the idle state logic voltage value is (logic one voltage value+logic zero voltage value) / 2, the transmitting-side converter comprising only linear functions to preserve the idle state logic voltage value, and an electrical-to-optical converter for converting the logic one, logic zero and the idle state logic voltage values to an optical signal further comprising respective logic one, logic zero and idle state optical values and for supplying the optical signal to an optical communications medium.

Owner:WERNLUND JAMES V

Tri-state I/O port

ActiveUS20090150734A1Power downElectronic circuit testingElectric pulse generatorElectricityComputer architecture

The present invention discloses a tri-state I / O port. The tri-state I / O port comprises a tri-state logic block, a weak buffer and a delay block. The input terminals of the tri-state logic block are connected to data and OE (output enable) signals. When OE signal is enabled, the output terminal of the tri-state I / O block is pulled high when the data is high while the output terminal is pulled low when the data is low. The input terminal and the output terminal of the weak buffer are connected to the output terminal of the tri-state logic block. And the input terminal of the delay block is connected to the output terminal of the tri-state logic block while the output terminal of the delay block is fed back to the tri-state logic block. When the output terminal of the tri-state logic block is low to high / high to low, the weak buffer is active and maintains the output terminal of the tri-state logic block weak high / low while the delay block turns off the pull high / low function of the tri-state logic block.

Owner:RDC SEMICON CO LTD

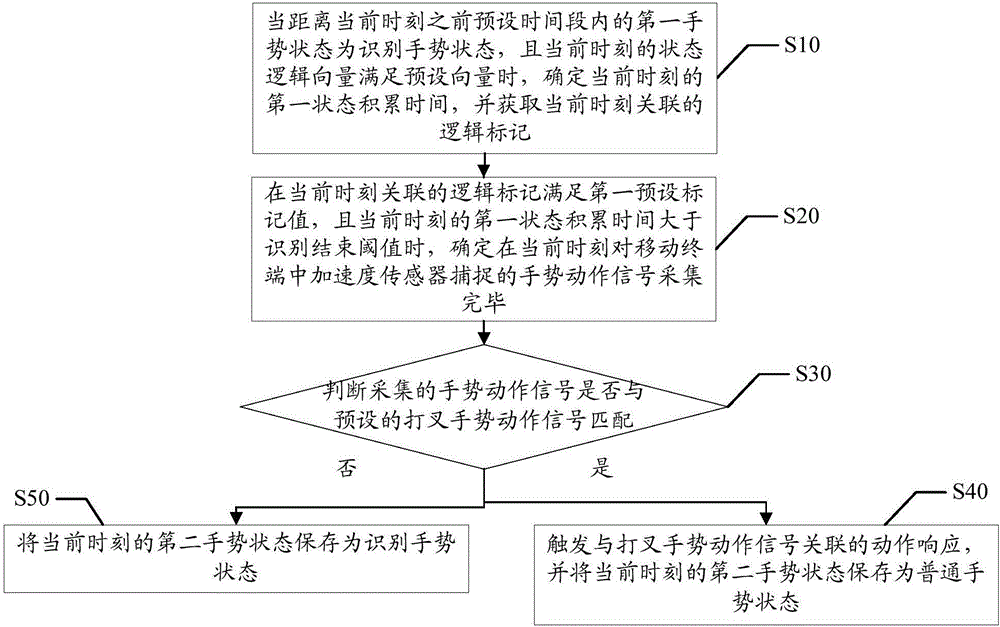

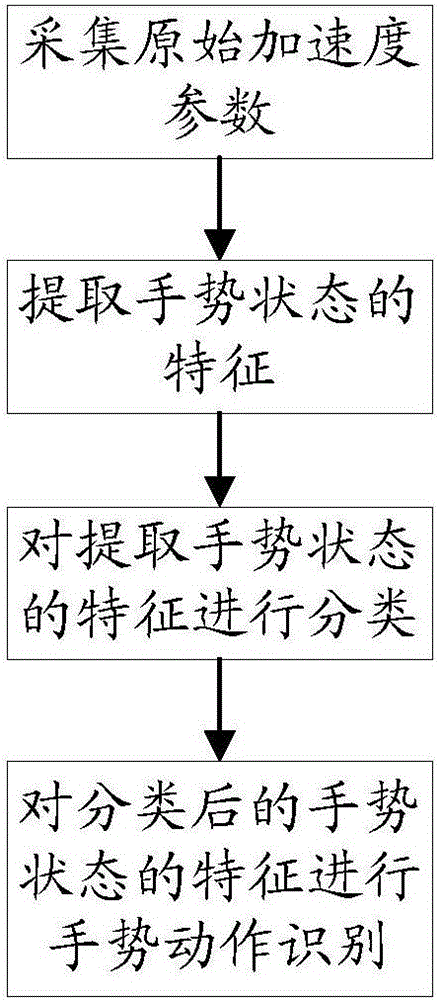

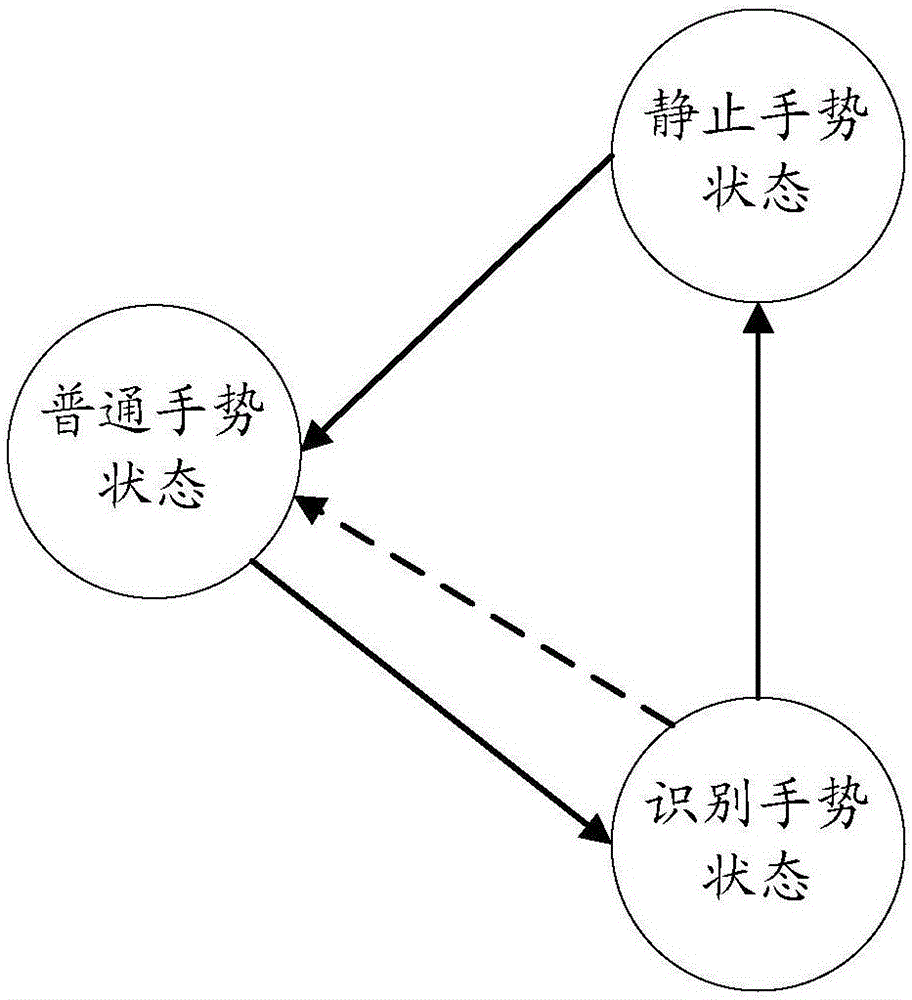

Gesture identification method and apparatus

ActiveCN106598231AImprove accuracyInput/output for user-computer interactionCharacter and pattern recognitionTime segmentHuman–computer interaction

The invention discloses a gesture identification method and apparatus. The method comprises the steps of determining first state accumulation time of a current moment when a first gesture state in a preset time segment before the current moment is a gesture identification state and a state logic vector of the current moment conforms to a preset vector, and obtaining a logic mark associated with the current moment; determining that the acquisition of a gesture action signal captured by an acceleration sensor in a mobile terminal is finished at the current moment when the logic mark associated with the current moment reaches a first preset mark value and the first state accumulation time of the current moment is longer than an identification termination threshold; judging whether the acquired gesture action signal is matched with a preset cross gesture action signal or not; if yes, triggering an action response associated with the cross gesture action signal, and storing a second gesture state of the current moment as a general gesture state; and if not, storing the second gesture state of the current moment as the gesture identification state. According to the gesture identification method and apparatus, the gesture identification accuracy is improved.

Owner:LAUNCH TECH CO LTD