Dual-voltage three-state buffer circuit

A three-state buffer, dual-voltage technology, applied in the direction of logic circuit, logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., can solve the excessive instability of inverter ratio and increase energy consumption Circuit layout area and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the above objects, features and advantages of the present invention more comprehensible, a preferred embodiment will be described in detail below together with the accompanying drawings.

[0035] The present invention proposes a dual-voltage tri-state buffer circuit with a tri-state level shifter, which can simplify circuit design. As such, the present invention reduces circuit layout area and reduces power consumption through dual voltage circuits.

[0036] The present invention will improve the design of dual voltage tri-state buffers.

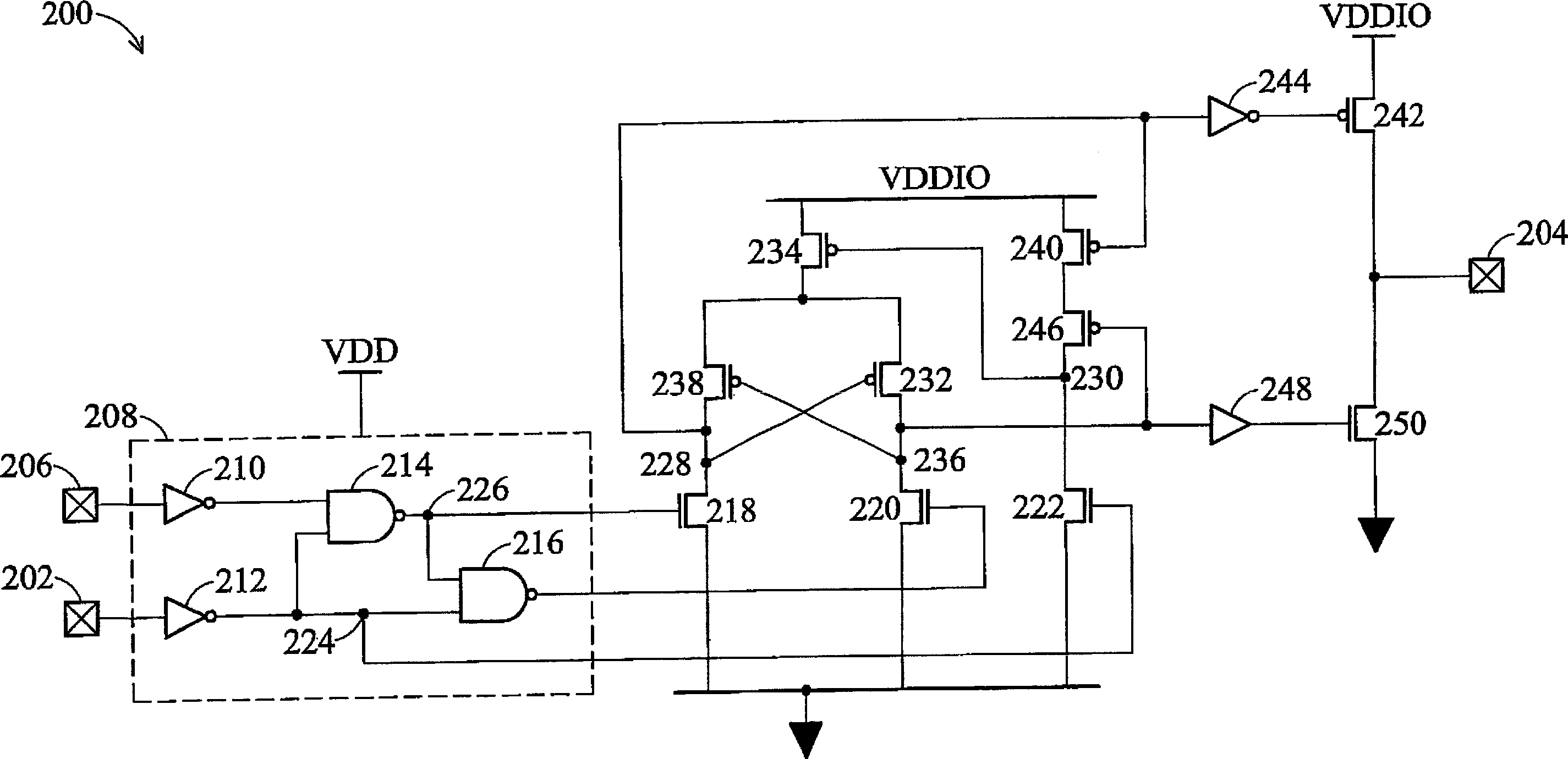

[0037] Figure 2A is a dual-voltage tri-state buffer circuit 200 according to the first embodiment of the present invention. Circuit 200 includes a level shifter and pull-up and pull-down switches.

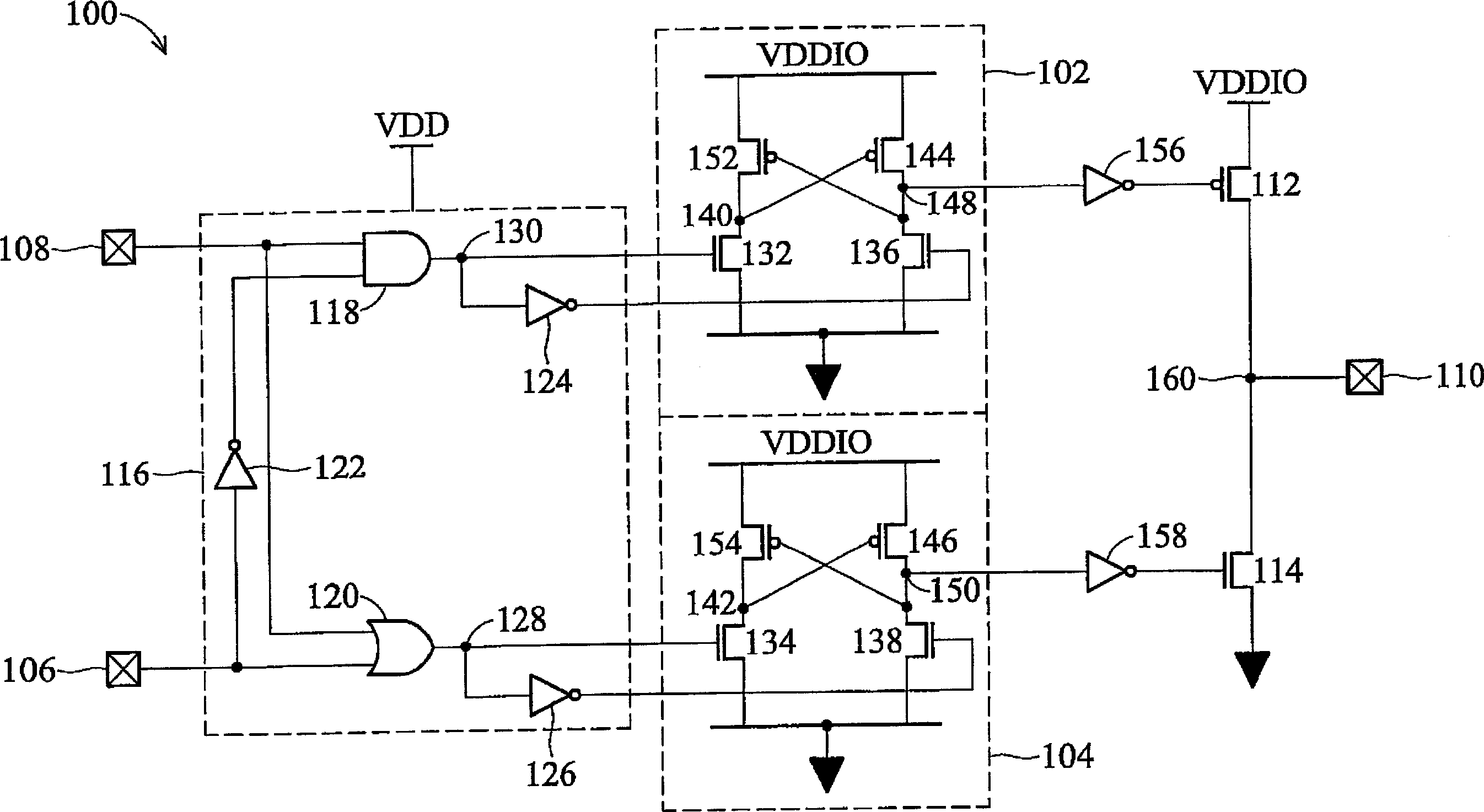

[0038] Like buffer 100, circuit 200 also switches between three different states and has two modes of operation: normal mode and tri-state mode. The normal mode occurs when the enable pin 202 is set to a low level, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More