Patents

Literature

353 results about "Addressing mode" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Addressing modes are an aspect of the instruction set architecture in most central processing unit (CPU) designs. The various addressing modes that are defined in a given instruction set architecture define how machine language instructions in that architecture identify the operand(s) of each instruction. An addressing mode specifies how to calculate the effective memory address of an operand by using information held in registers and/or constants contained within a machine instruction or elsewhere.

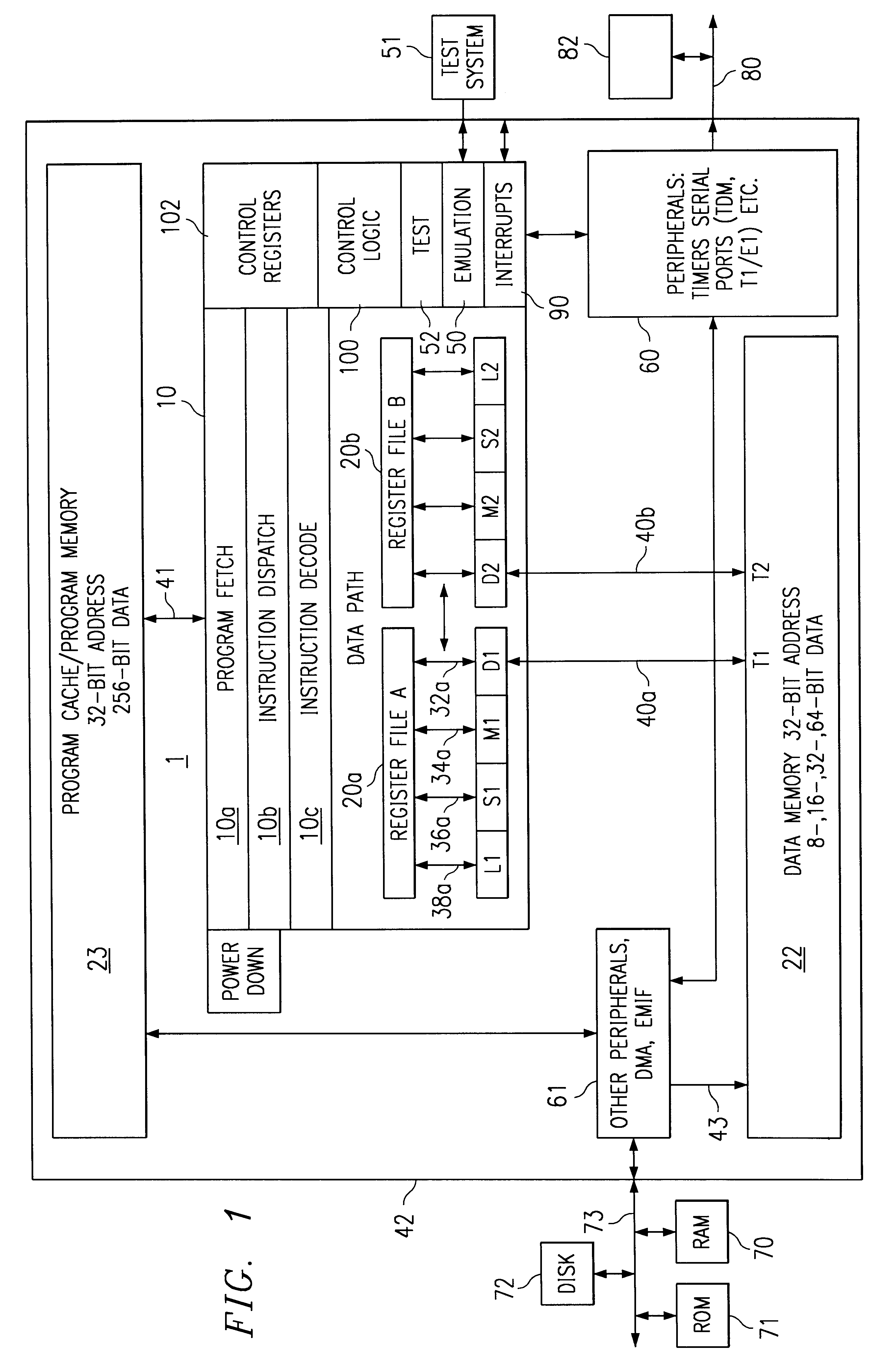

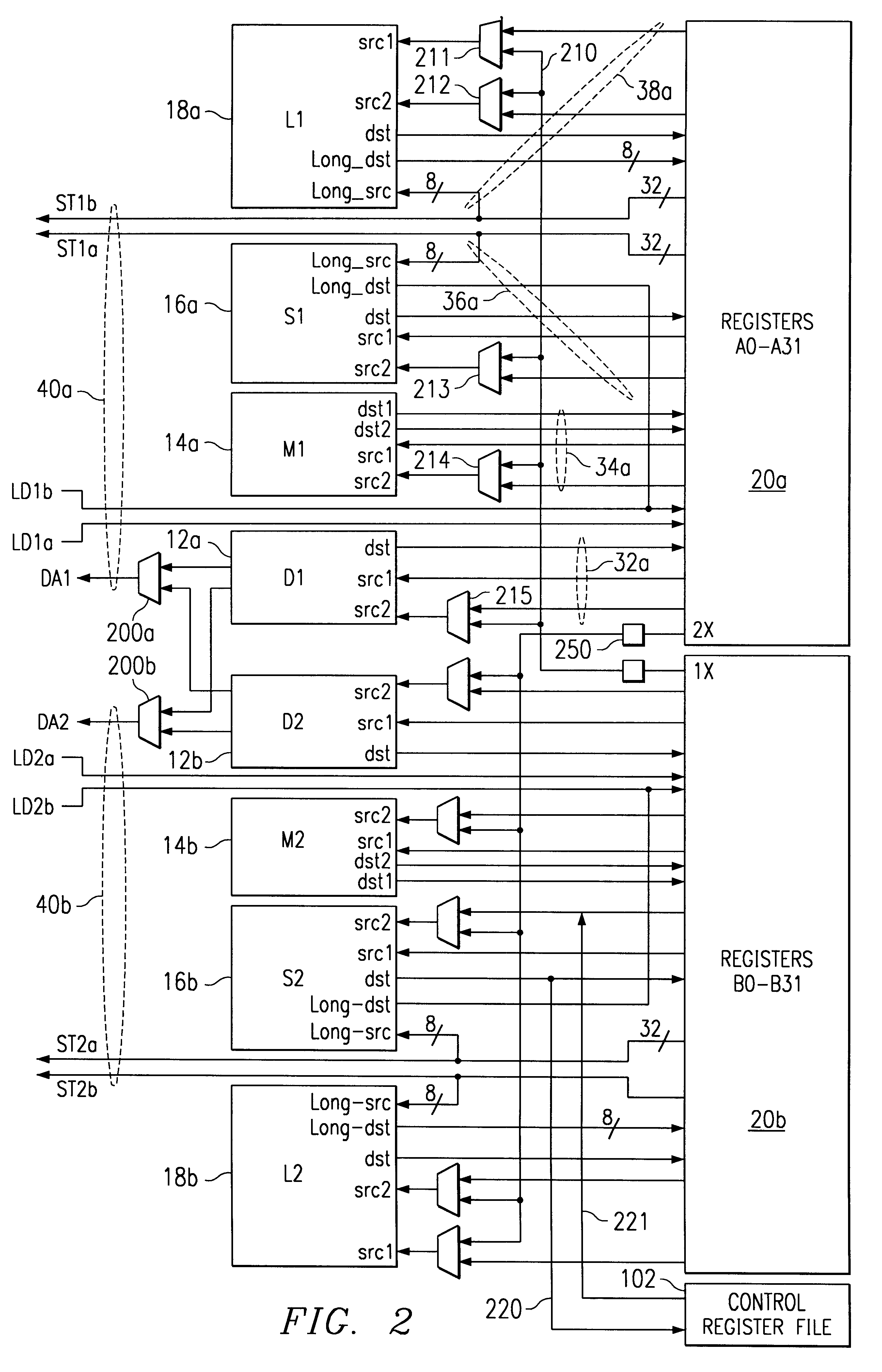

SIMD processor and addressing method

InactiveUS20060047937A1Without unduly consuming processor resourcesMemory adressing/allocation/relocationMicro-instruction address formationMemory addressProcessor register

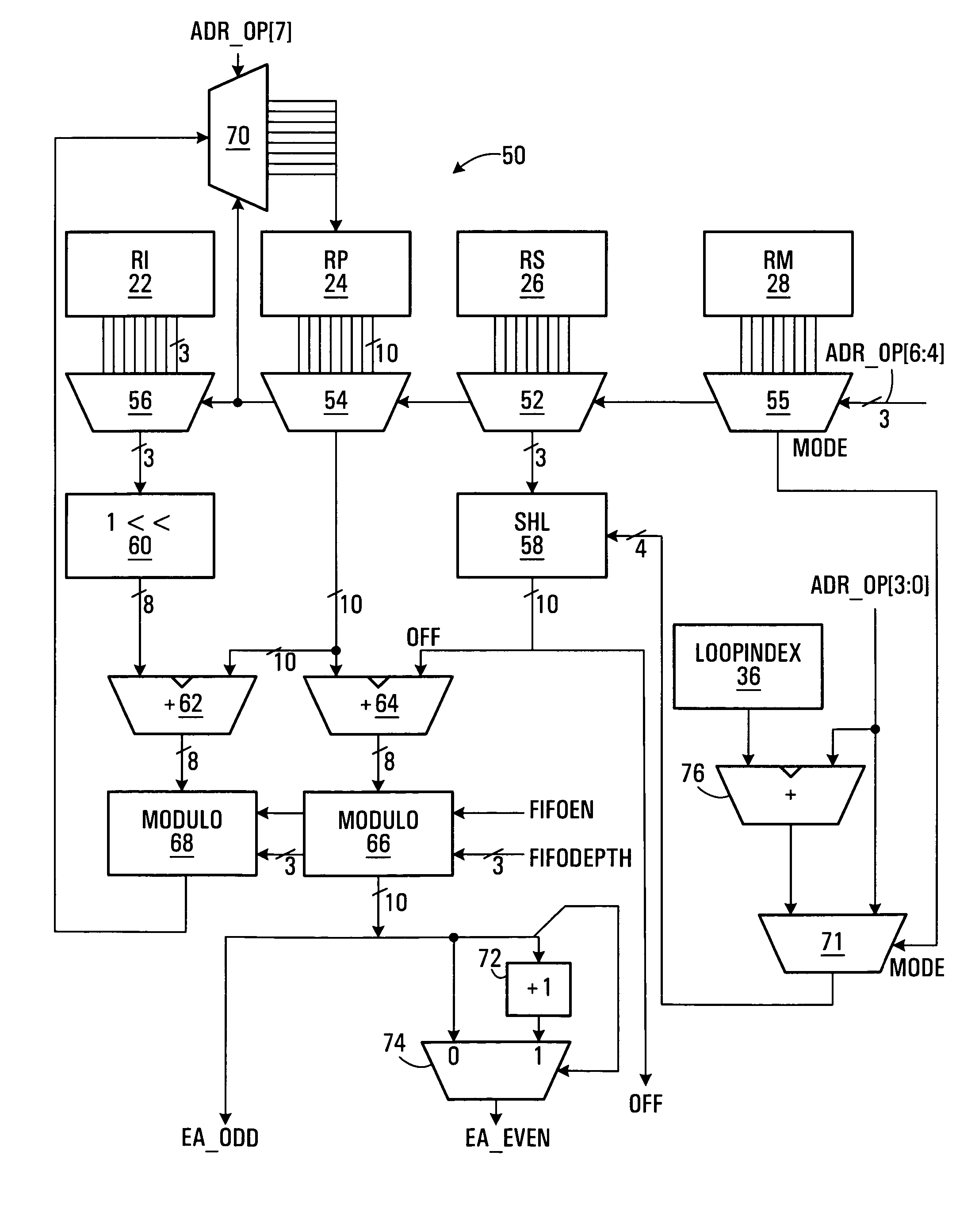

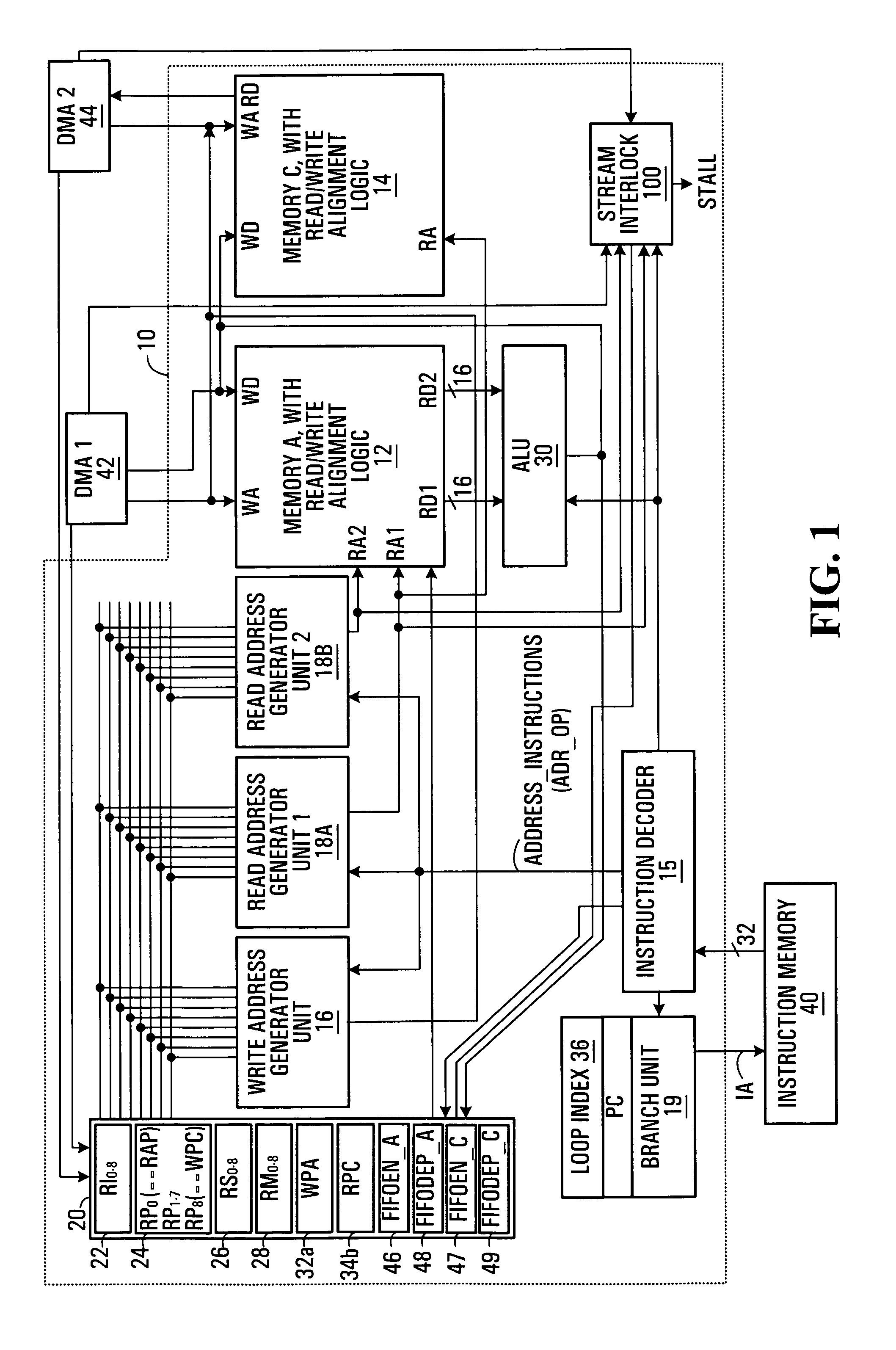

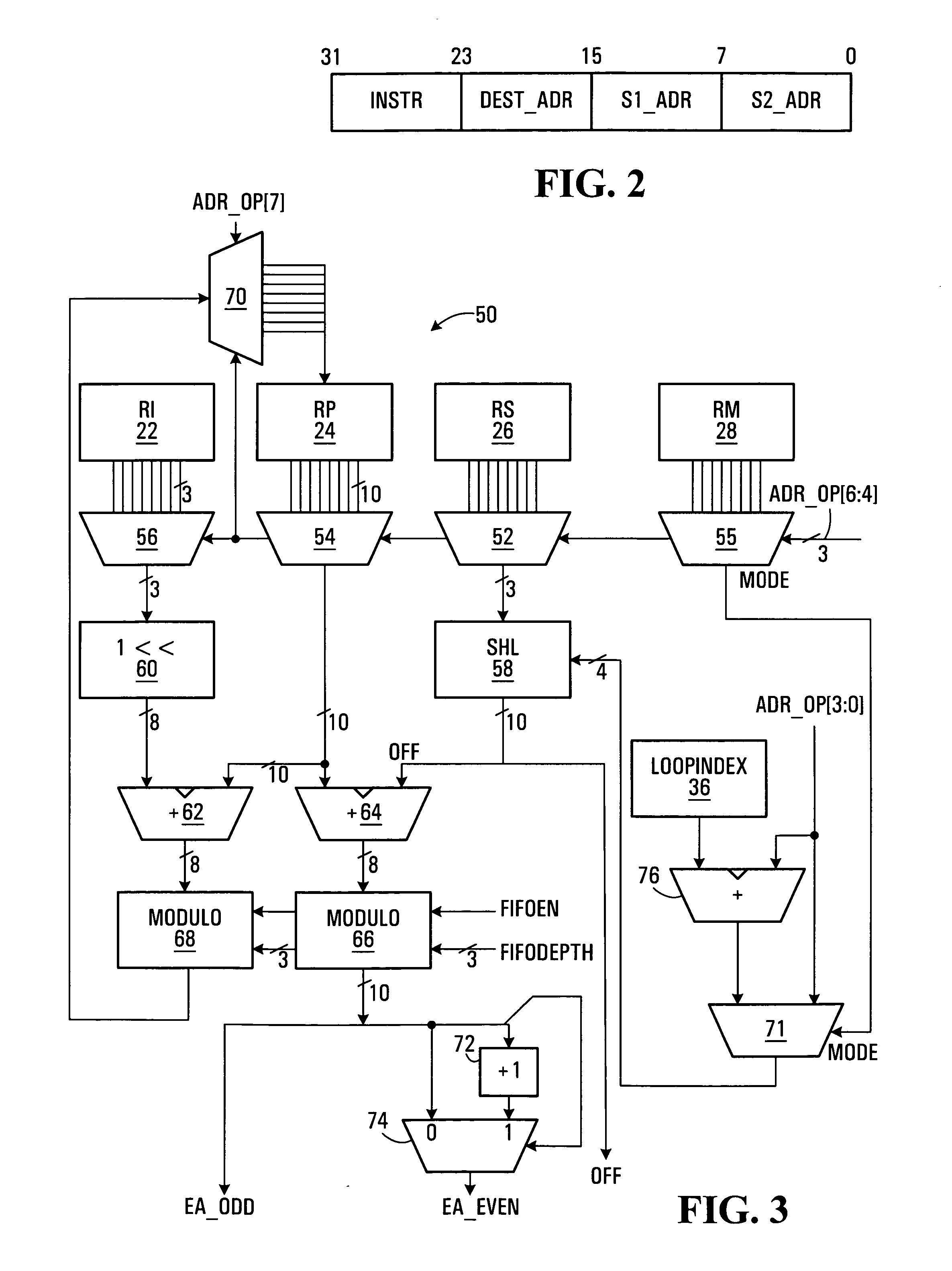

A single instruction, multiple data (SIMD) processor including a plurality of addressing register sets, used to flexibly calculate effective operand source and destination memory addresses is disclosed. Two or more address generators calculate effective addresses using the register sets. Each register set includes a pointer register, and a scale register. An address generator forms effective addresses from a selected register set's pointer register and scale register; and an offset. For example, the effective memory address may be formed by multiplying the scale value by an offset value and summing the pointer and the scale value multiplied by the offset value.

Owner:AVAGO TECH INT SALES PTE LTD

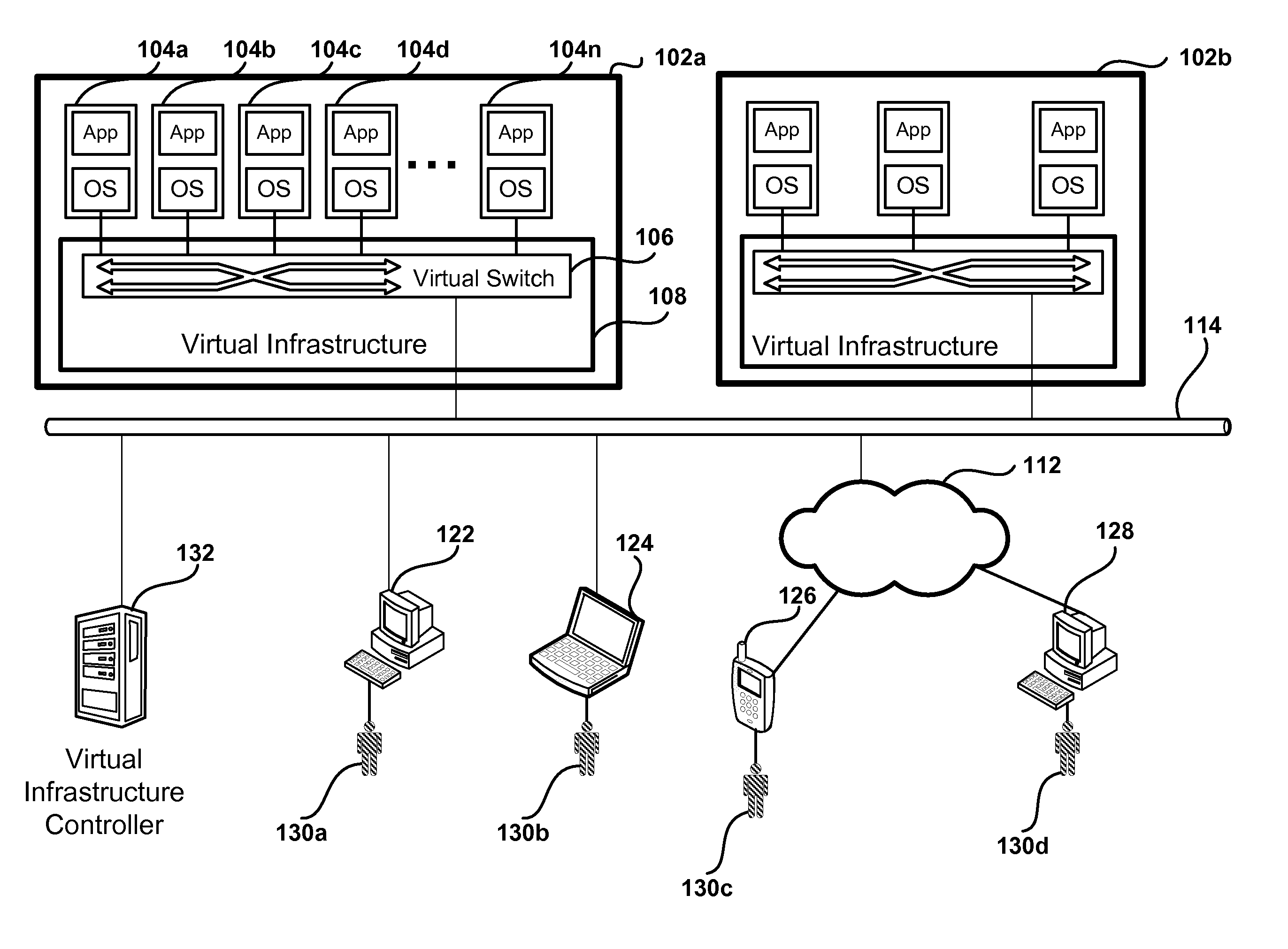

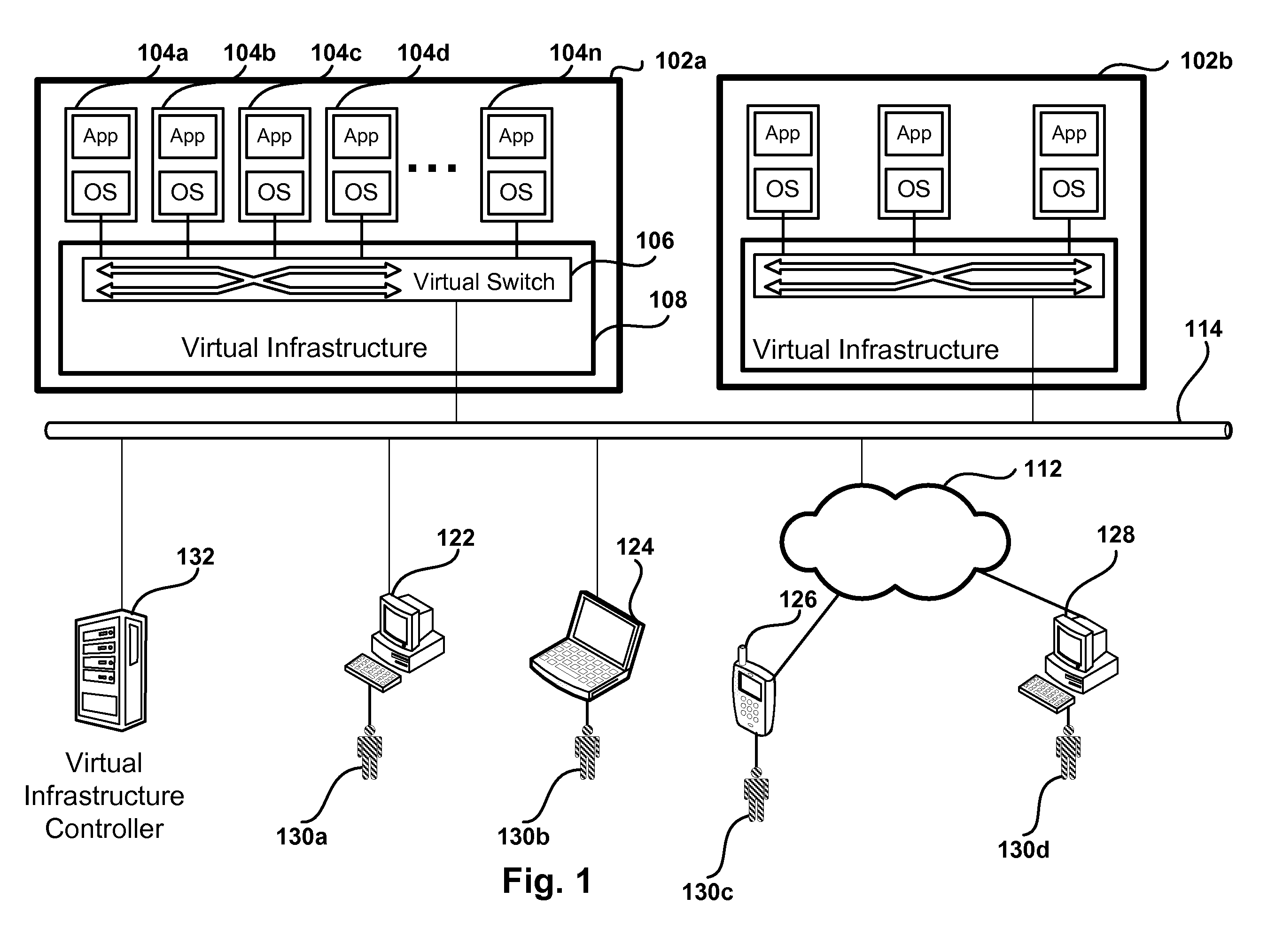

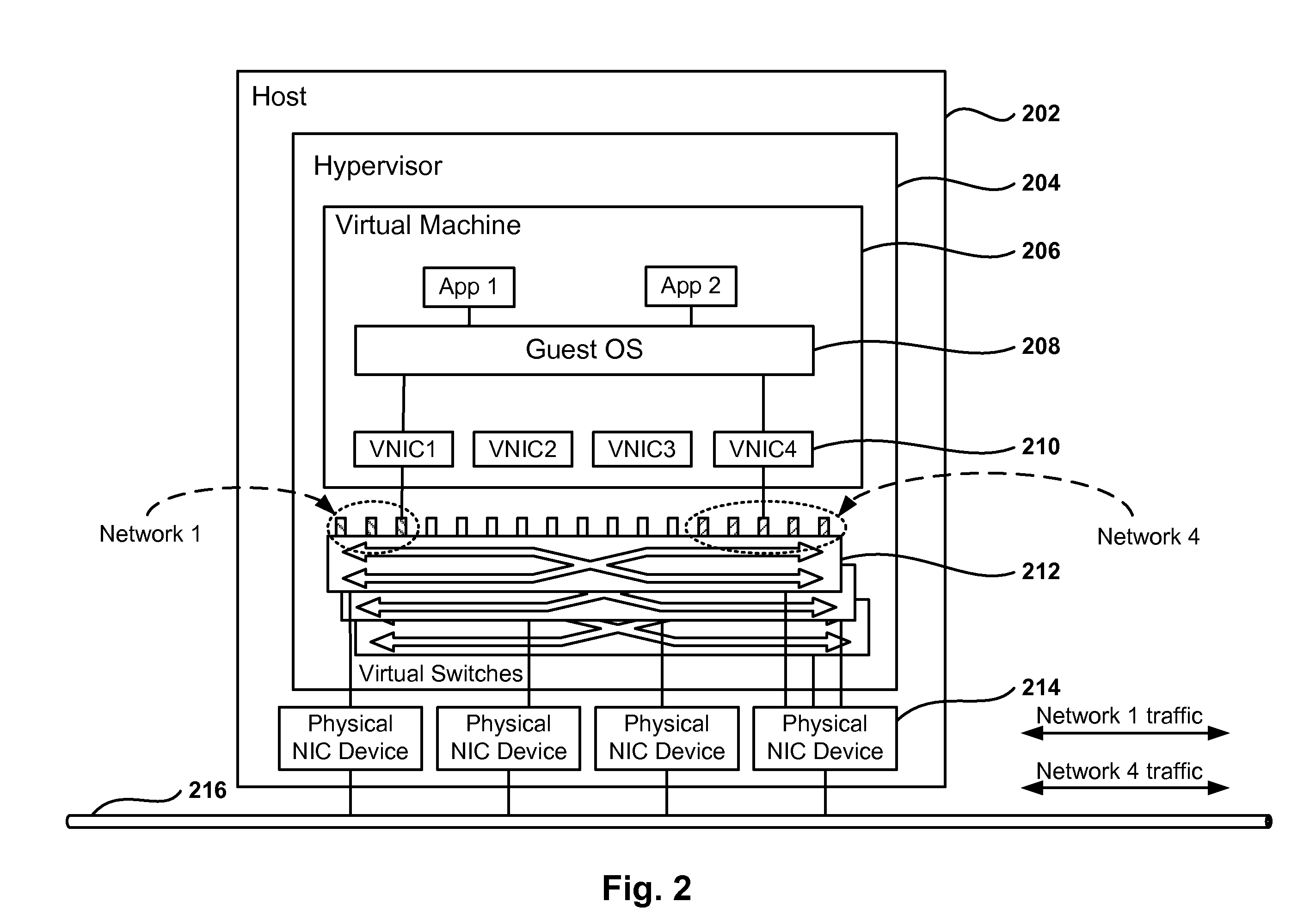

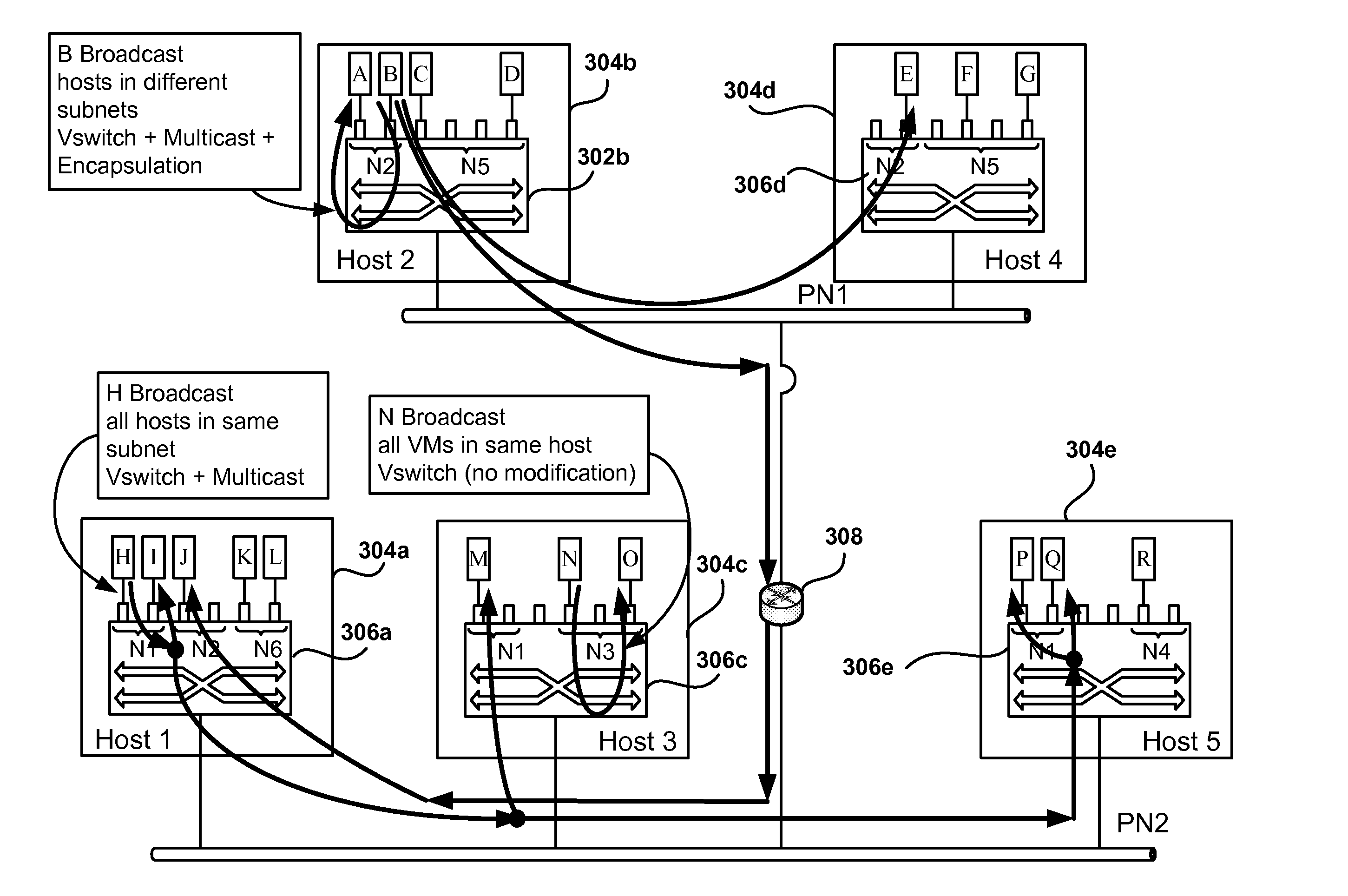

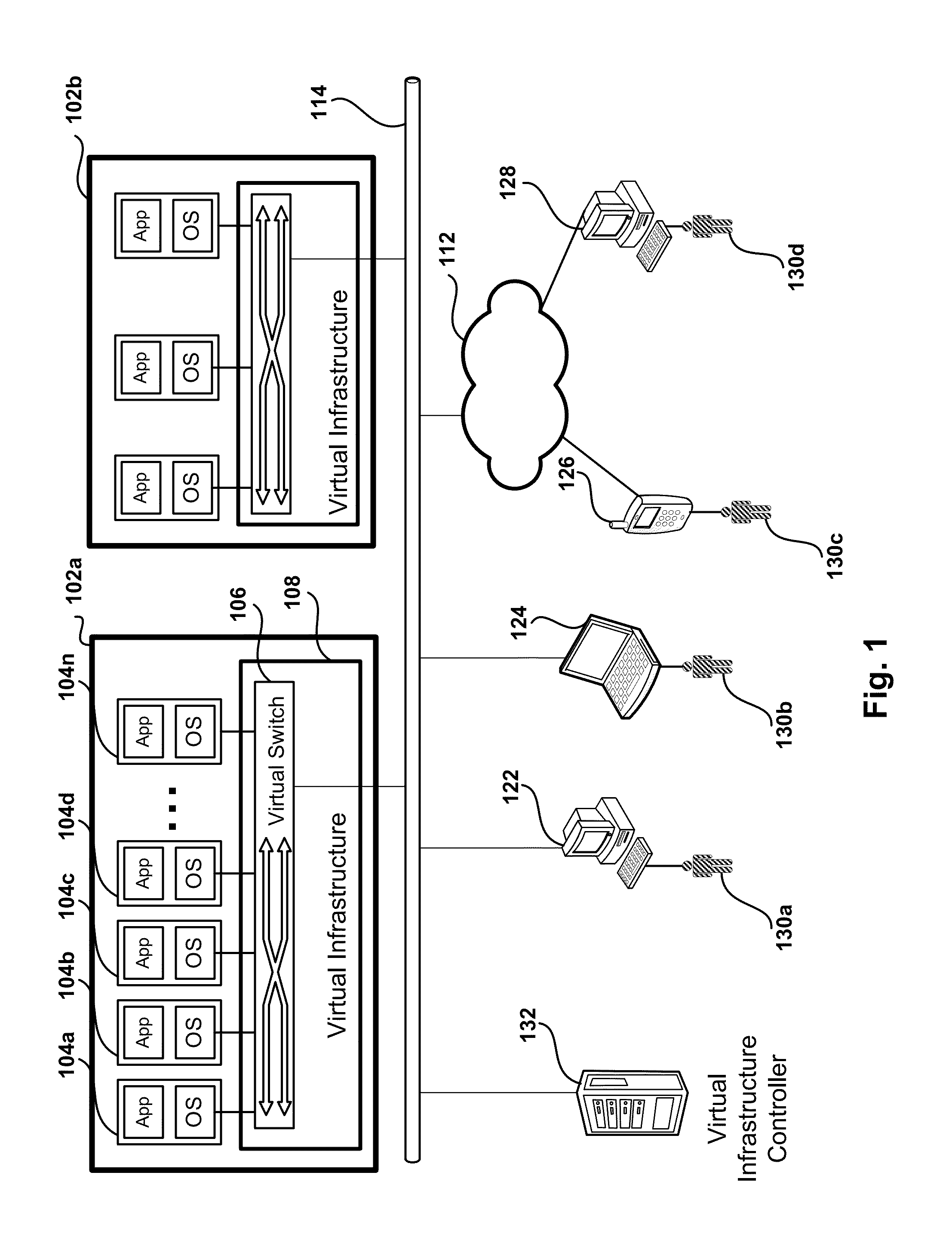

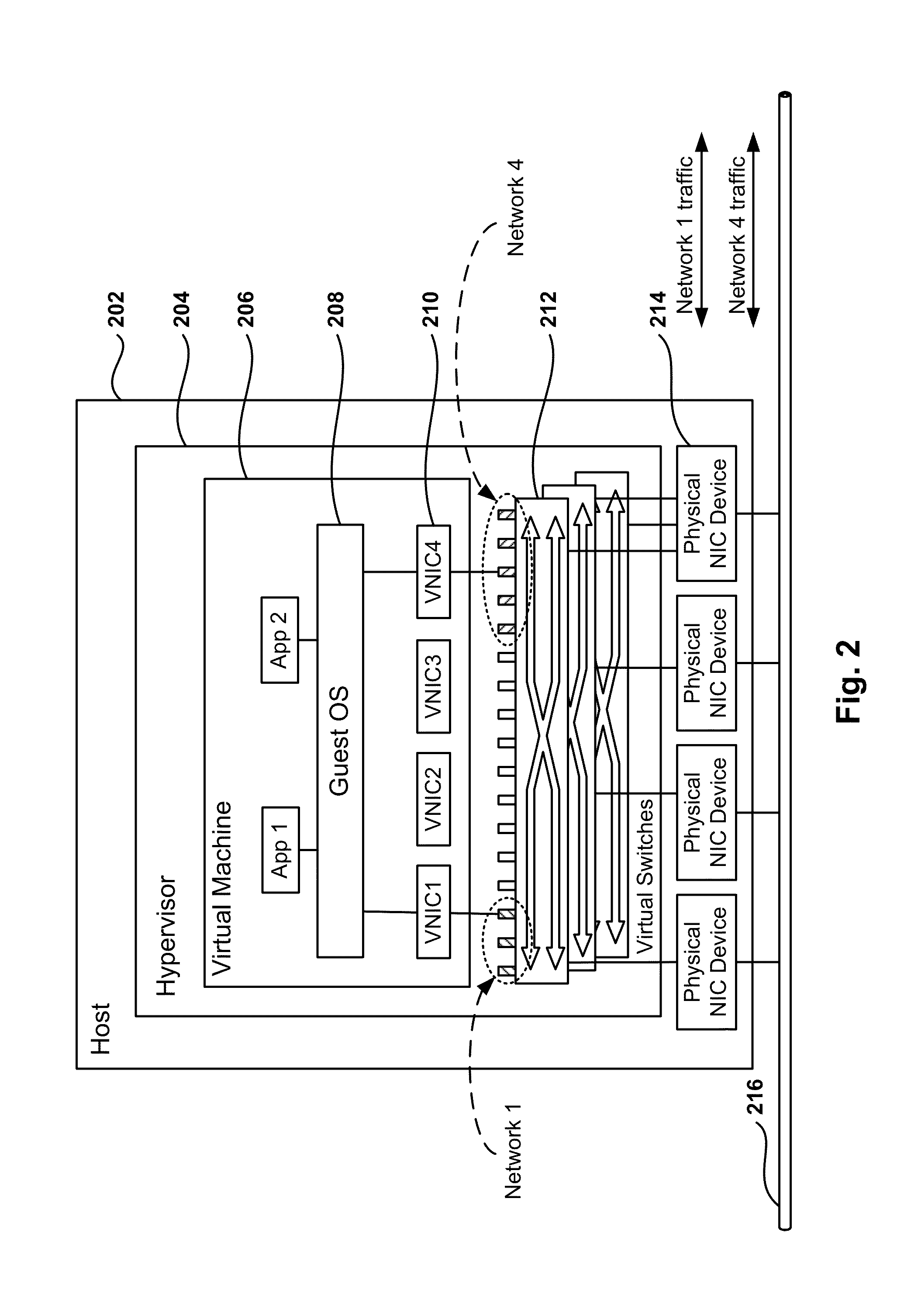

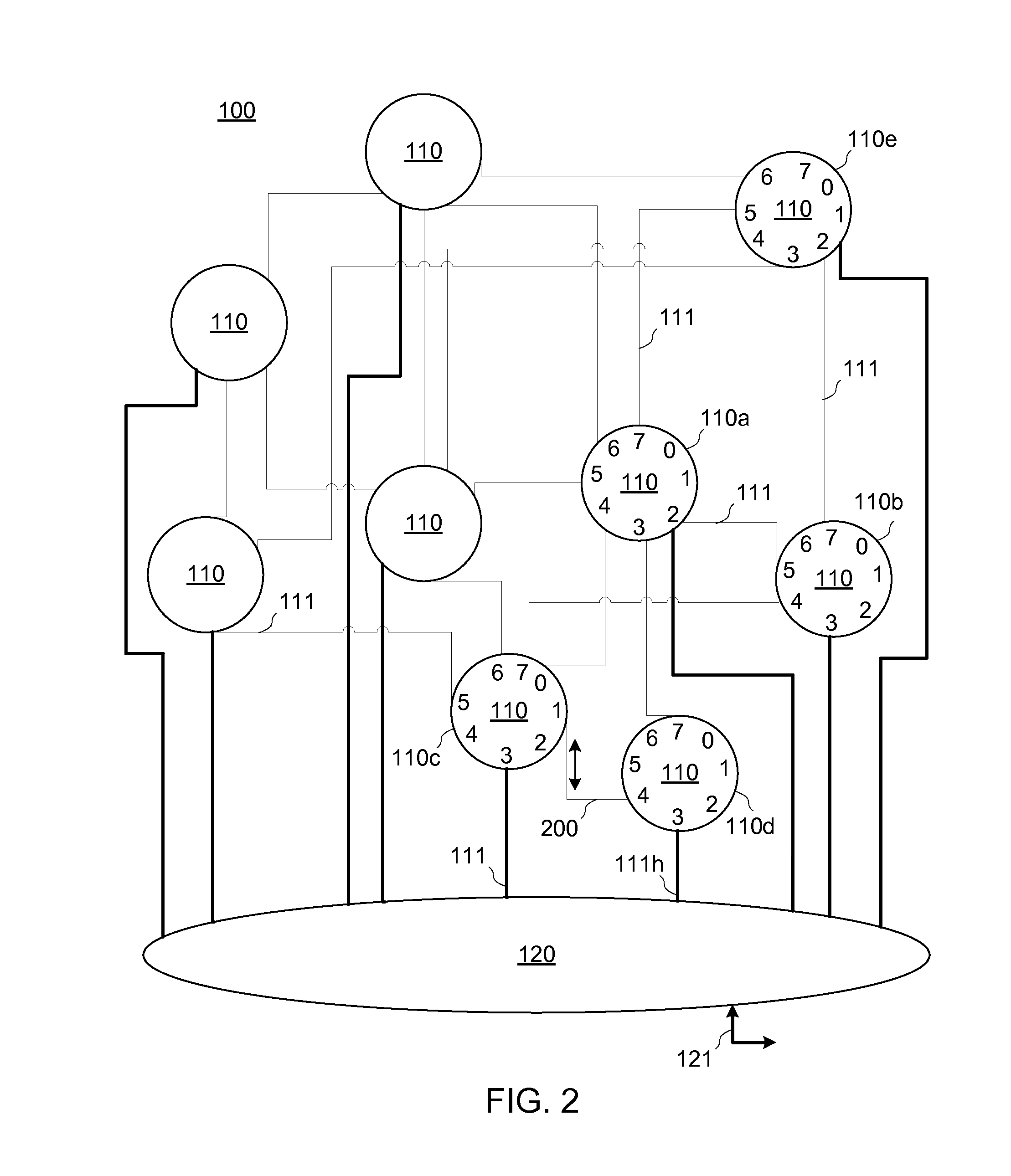

Private Allocated Networks Over Shared Communications Infrastructure

Methods and systems for implementing private allocated networks in a virtual infrastructure are presented. One method operation creates virtual switches in one or more hosts in the virtual infrastructure. Each port in the virtual switches is associated with a private allocated network (PAN) from a group of possible PANs. In one embodiment, one or more PANs share the same physical media for data transmission. The intranet traffic within each PAN is not visible to nodes that are not connected to the each PAN. In another operation, the method defines addressing mode tables for the intranet traffic within each PAN. The entries in the addressing mode tables define addressing functions for routing the intranet traffic between the virtual switches, and different types of addressing functions are supported by the virtual switches.

Owner:NICIRA

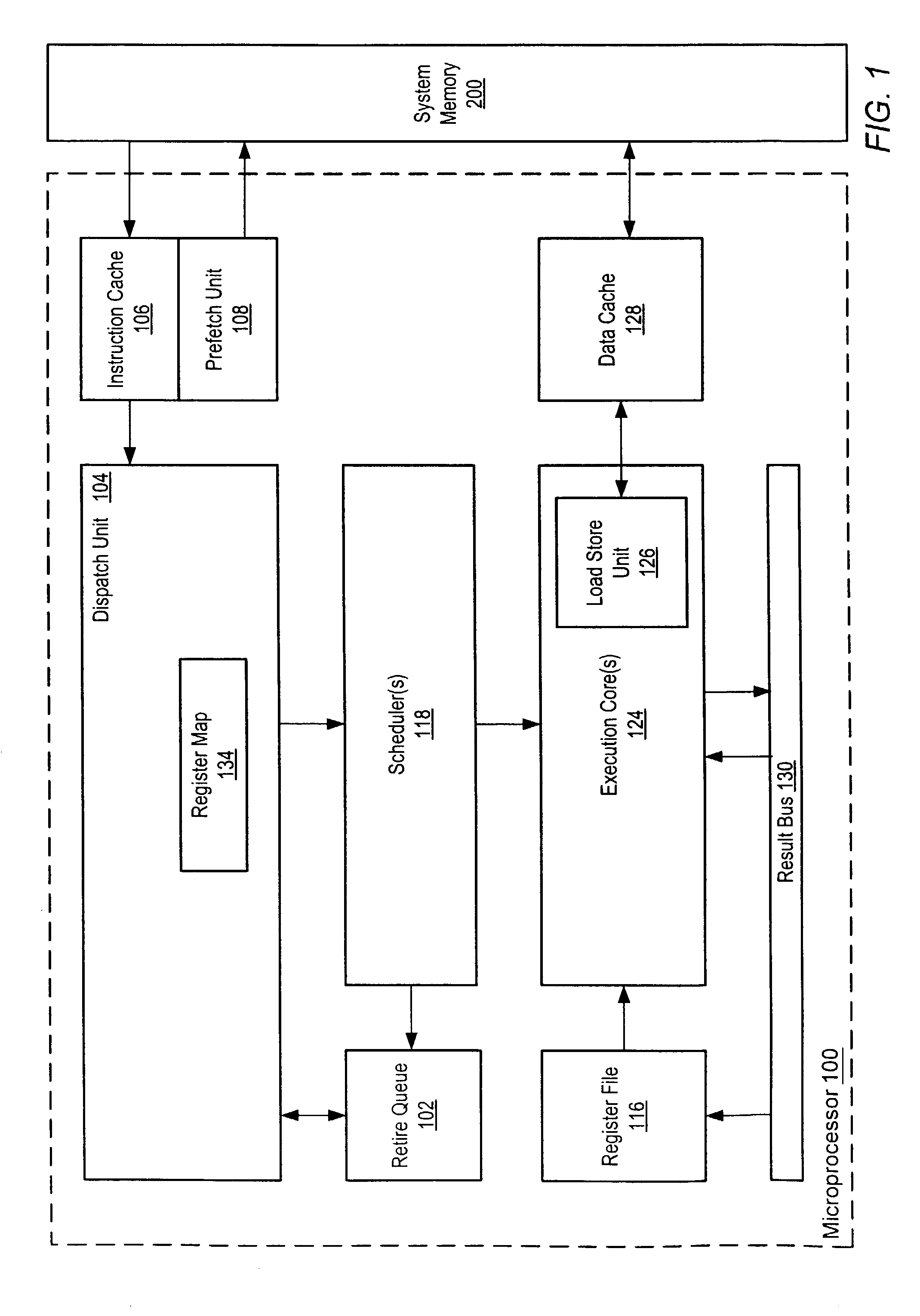

Microprocessors

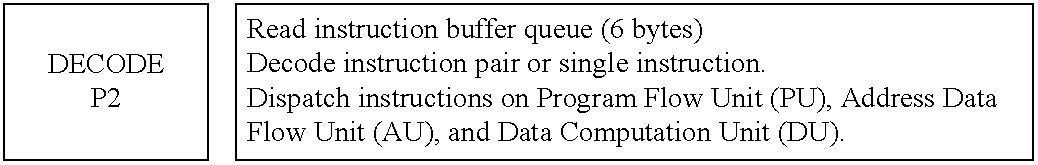

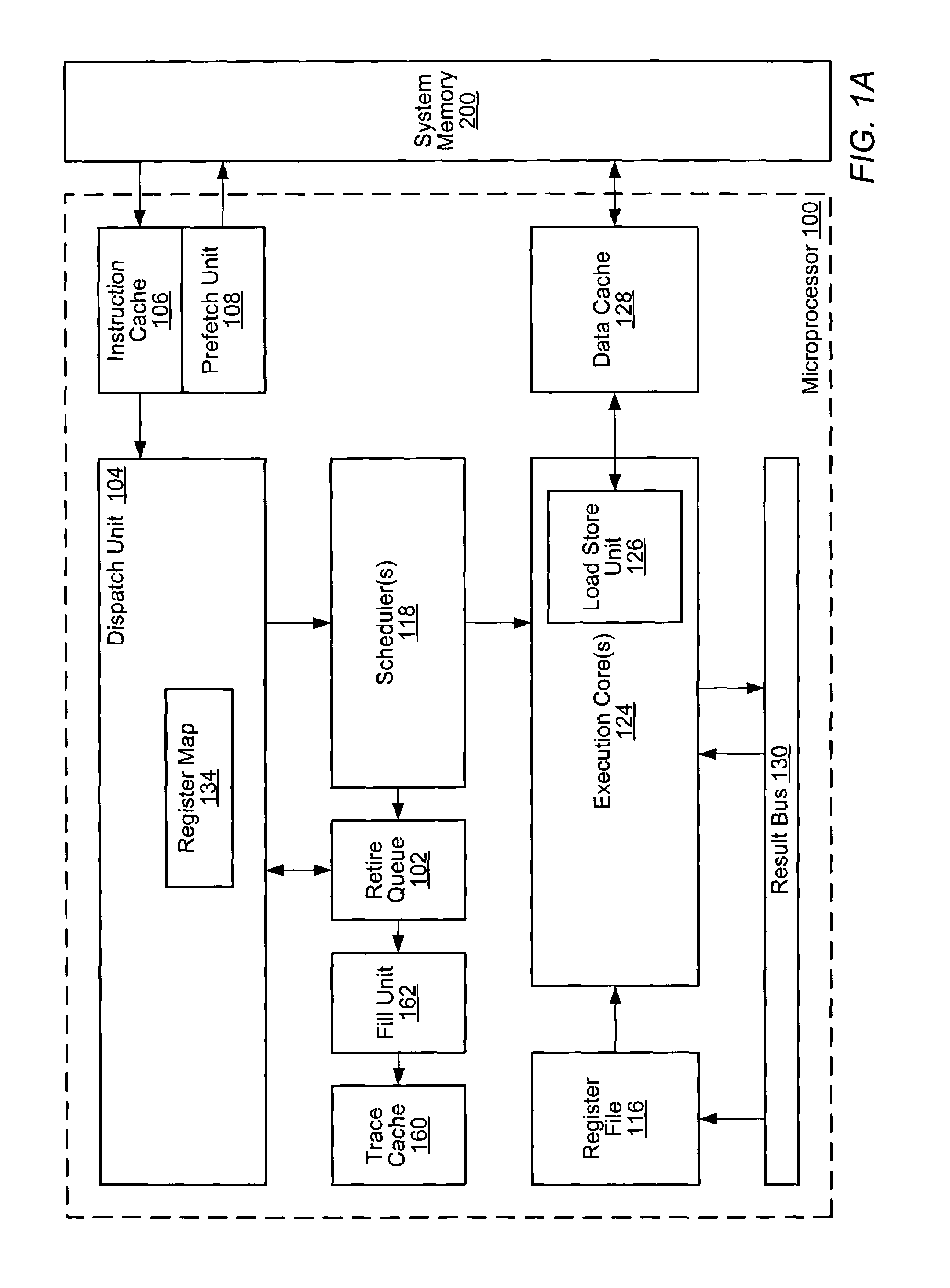

A processor (100) is provided that is a programmable fixed point digital signal processor (DSP) with variable instruction length, offering both high code density and easy programming. Architecture and instruction set are optimized for low power consumption and high efficiency execution of DSP algorithms, such as for wireless telephones, as well as pure control tasks. The processor includes an instruction buffer unit (106), a program flow control unit (108), an address / data flow unit (110), a data computation unit (112), and multiple interconnecting busses. Dual multiply-accumulate blocks improve processing performance. A memory interface unit (104) provides parallel access to data and instruction memories. The instruction buffer is operable to buffer single and compound instructions pending execution thereof. A decode mechanism is configured to decode instructions from the instruction buffer. The use of compound instructions enables effective use of the bandwidth available within the processor. A soft dual memory instruction can be compiled from separate first and second programmed memory instructions. Instructions can be conditionally executed or repeatedly executed. Bit field processing and various addressing modes, such as circular buffer addressing, further support execution of DSP algorithms. The processor includes a multistage execution pipeline with pipeline protection features. Various functional modules can be separately powered down to conserve power. The processor includes emulation and code debugging facilities with support for cache analysis.

Owner:TEXAS INSTR INC

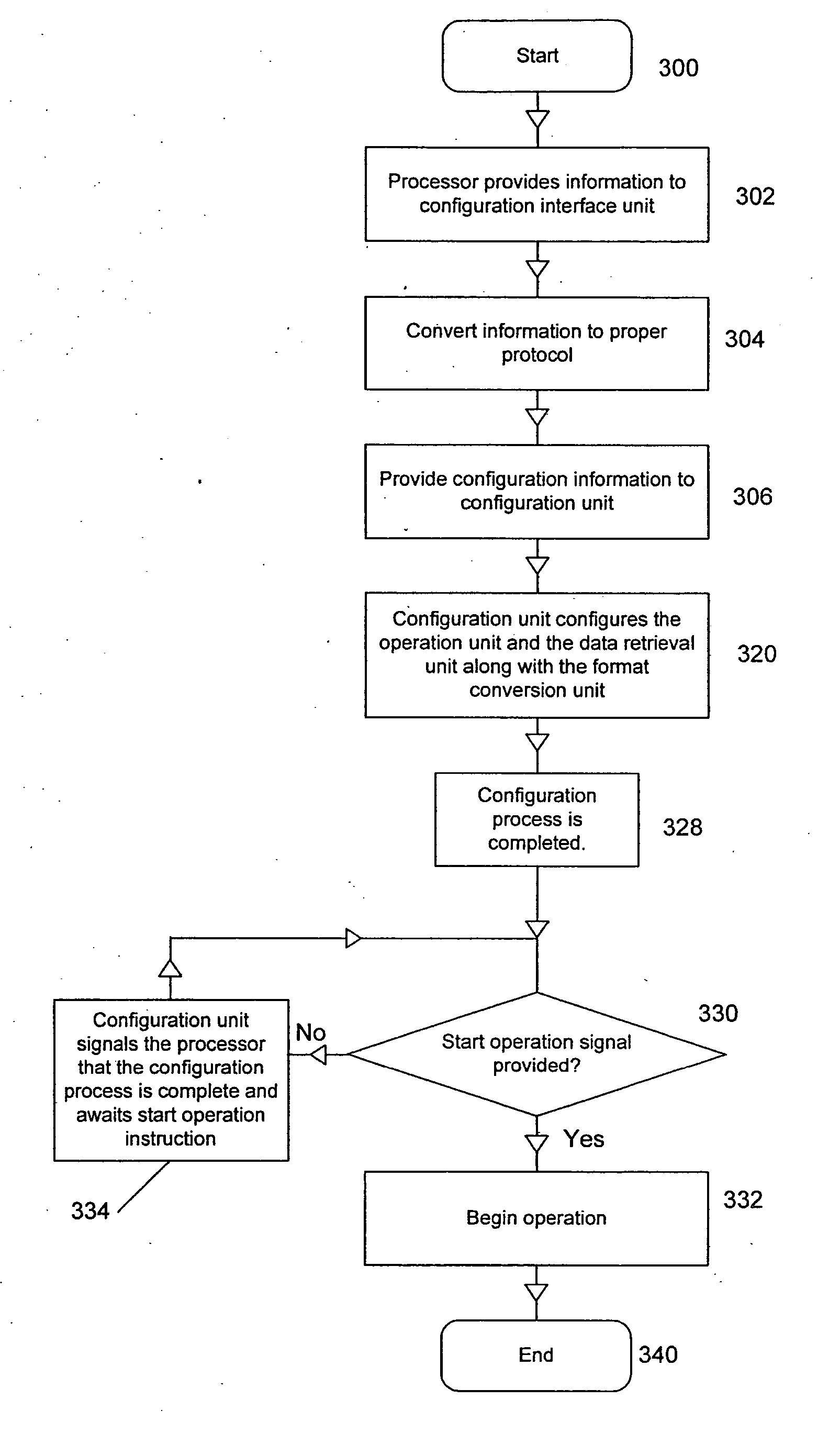

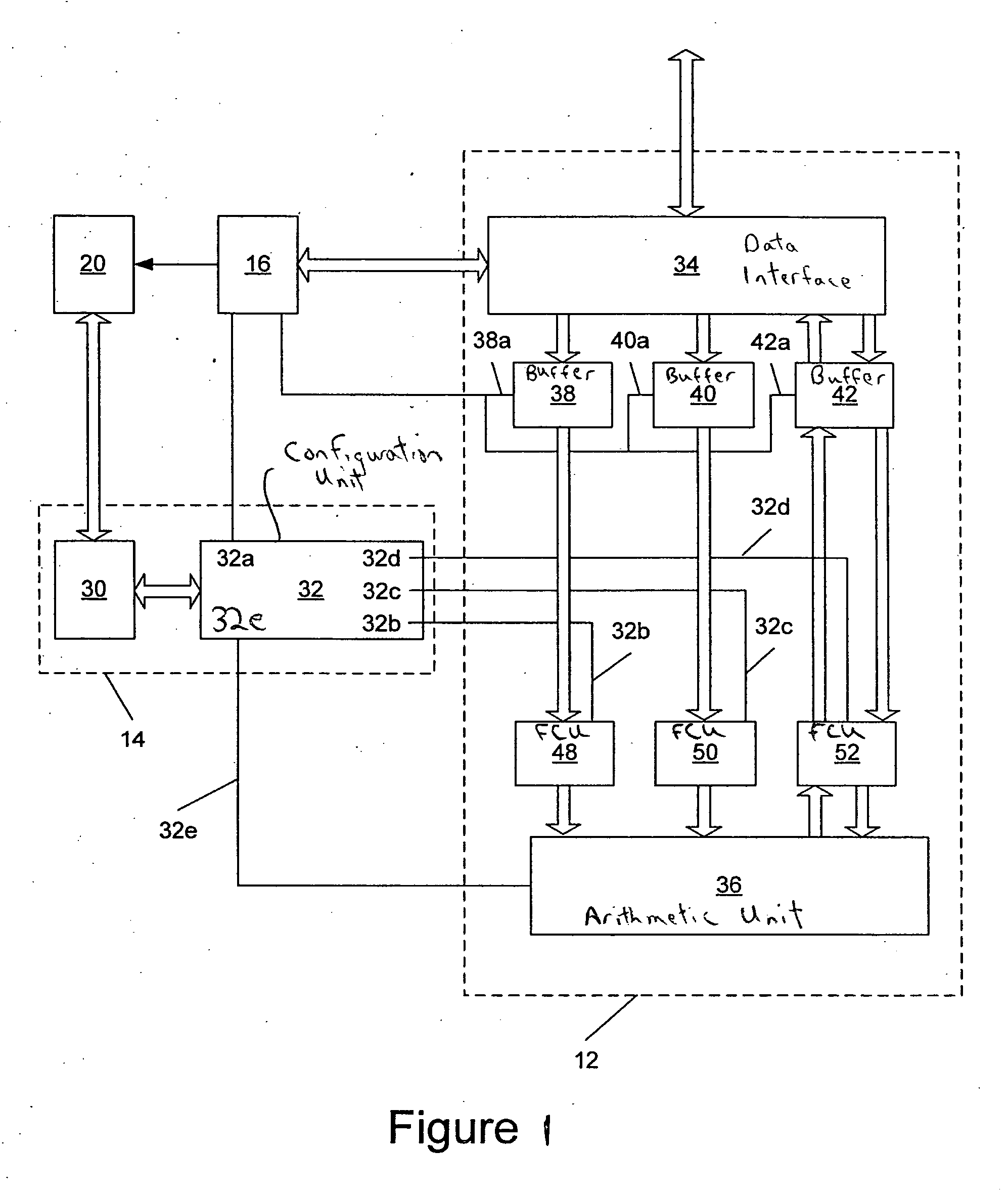

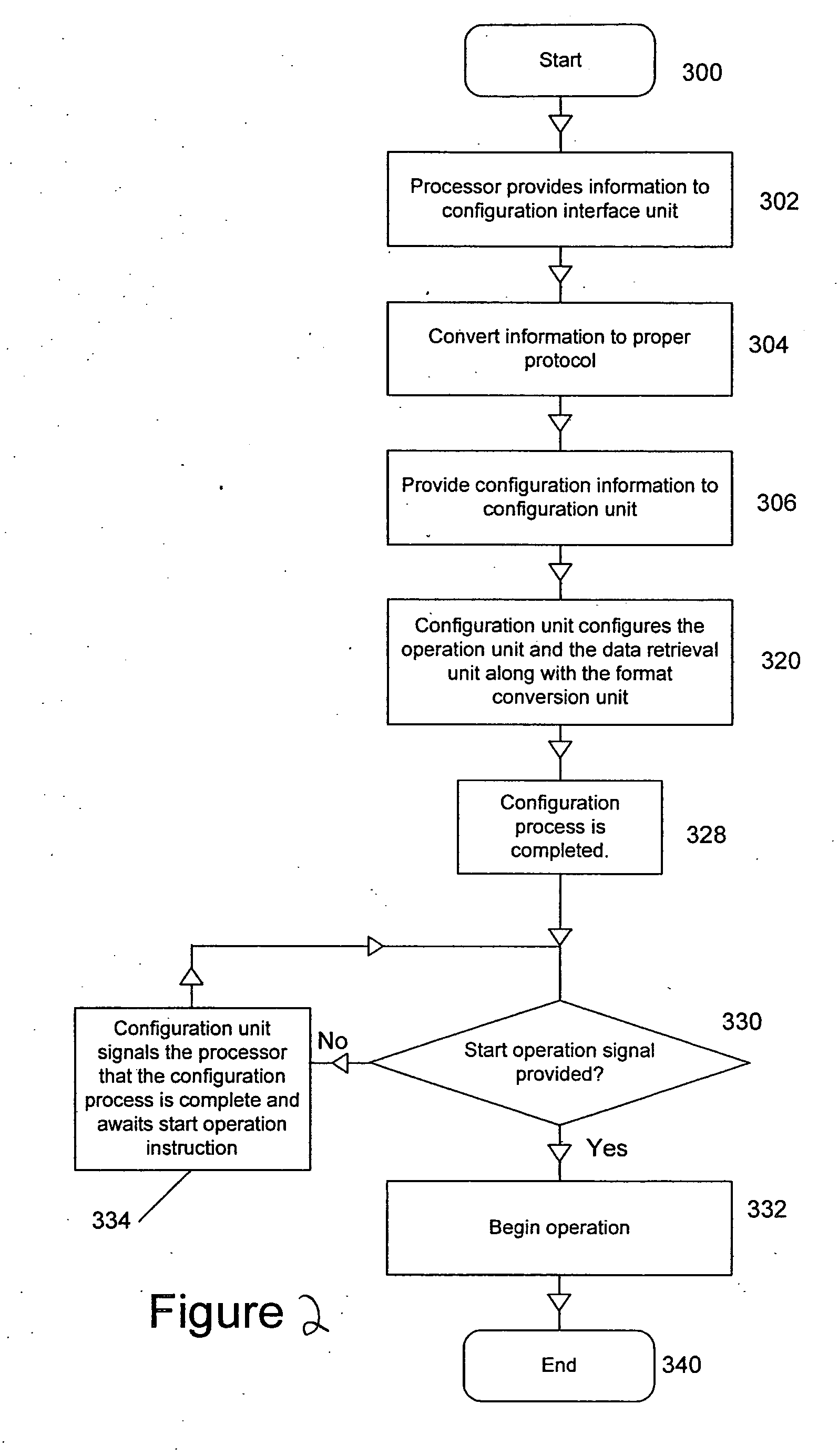

Configurable system for performing repetitive actions and method for configuring and operating same

ActiveUS20070078661A1Efficient executionHigh power consumptionSpeech analysisSpecial data processing applicationsData processing systemOperand

In some embodiments, a data processing system including an operation unit including circuitry configurable to perform any selected one of a number of operations on data (e.g., audio data) and a configuration unit configured to assert configuration information to configure the operation unit to perform the selected operation. When the operation includes matrix multiplication of a data vector and a matrix whose coefficients exhibit symmetry, the configuration information preferably includes bits that determine signs of all but magnitudes of only a subset of the coefficients. When the operation includes successive addition and subtraction operations on operand pairs, the configuration information preferably includes bits that configure the operation unit to operate in an alternating addition / subtraction mode to perform successive addition and subtraction operations on each pair of data values of a sequence of data value pairs. In some embodiments, the configuration information includes bits that configure the operation unit to operate in a non-consecutive (e.g., butterfly or bit-reversed) addressing mode to access memory locations having consecutive addresses in a predetermined non-consecutive sequence. Other aspects are audio encoders and decoders including any embodiment of, and configuration units and operation units for use in, any embodiment of the system, and methods performed during operation of any embodiment of the system or configuration or operation unit thereof.

Owner:NVIDIA CORP

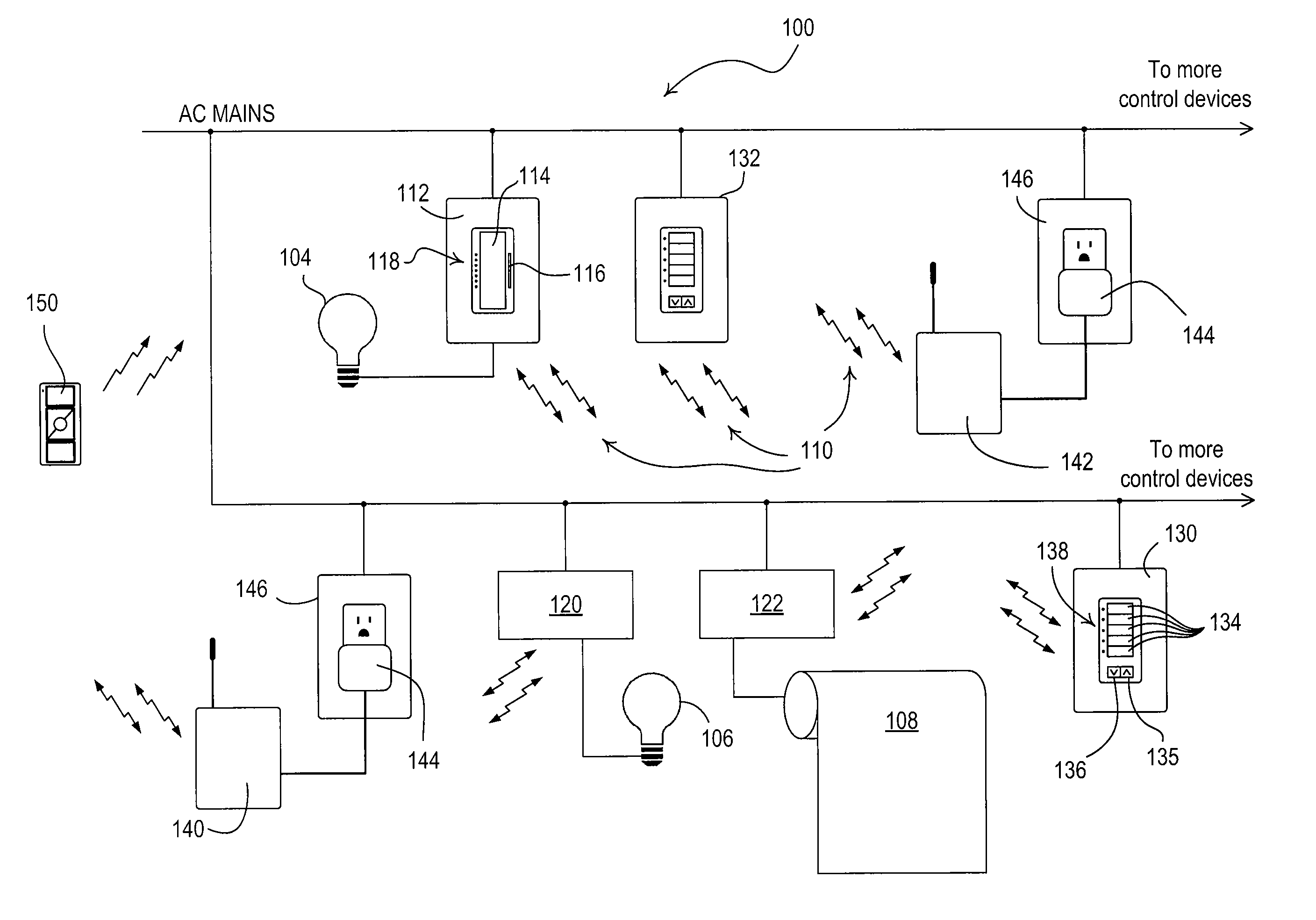

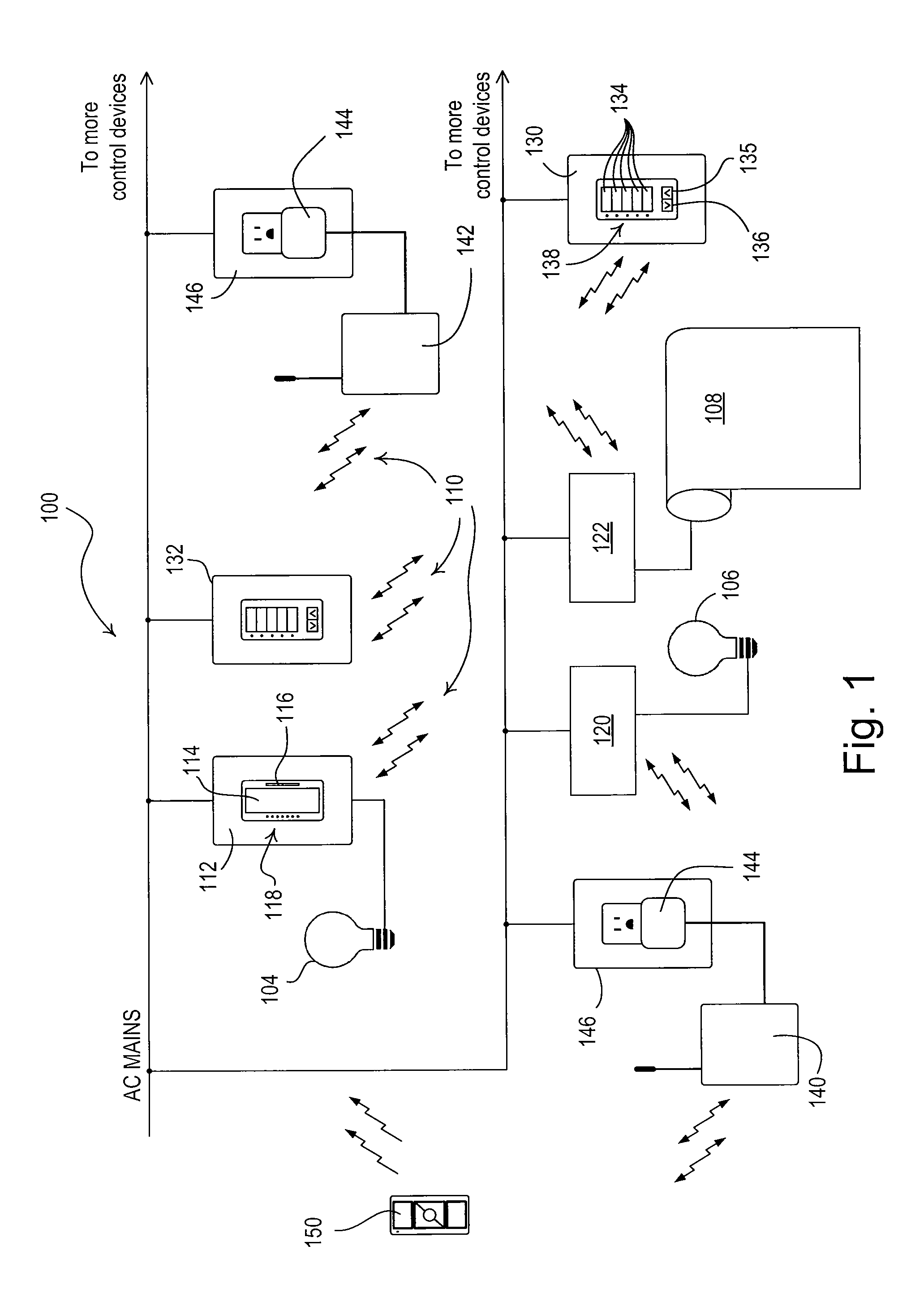

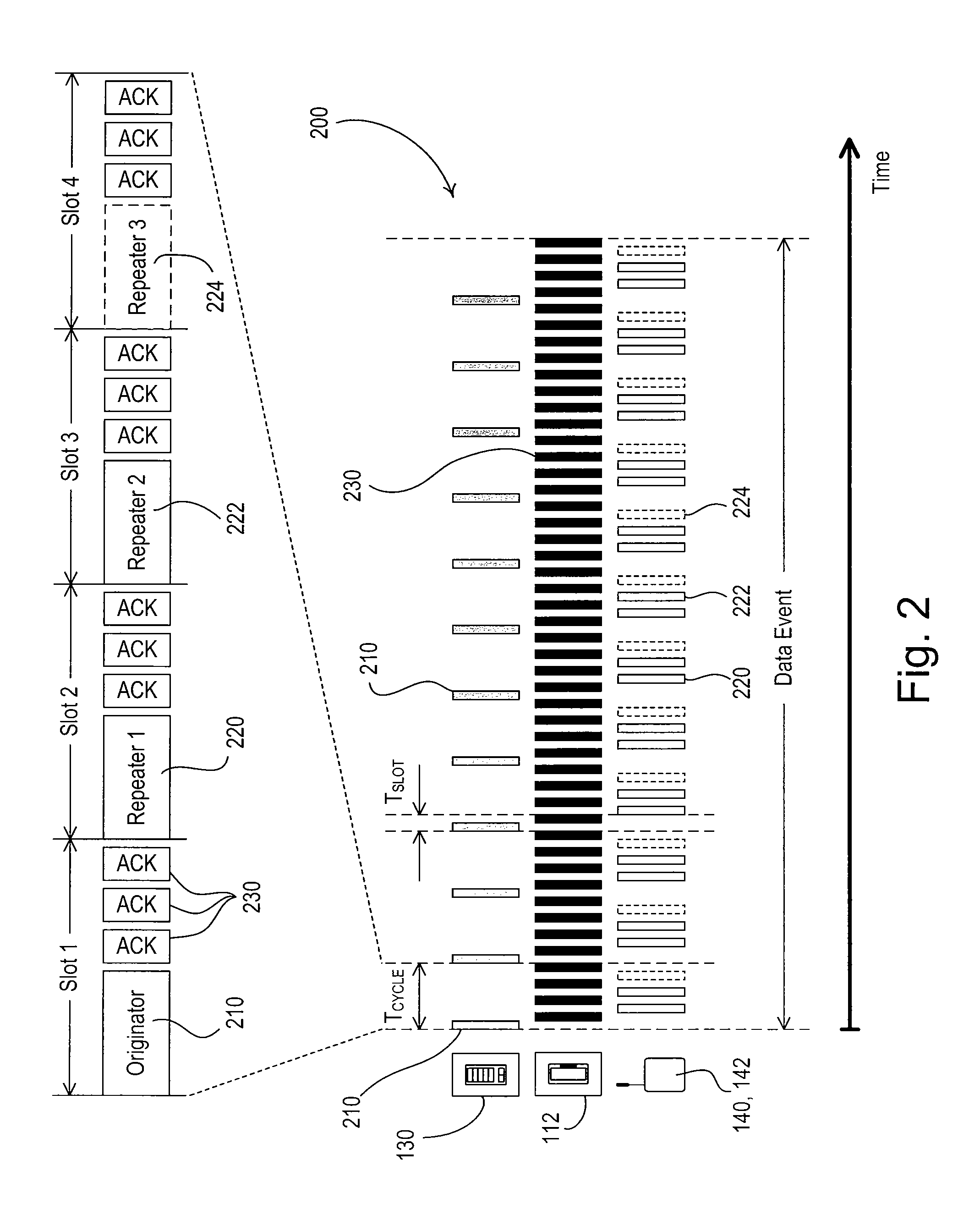

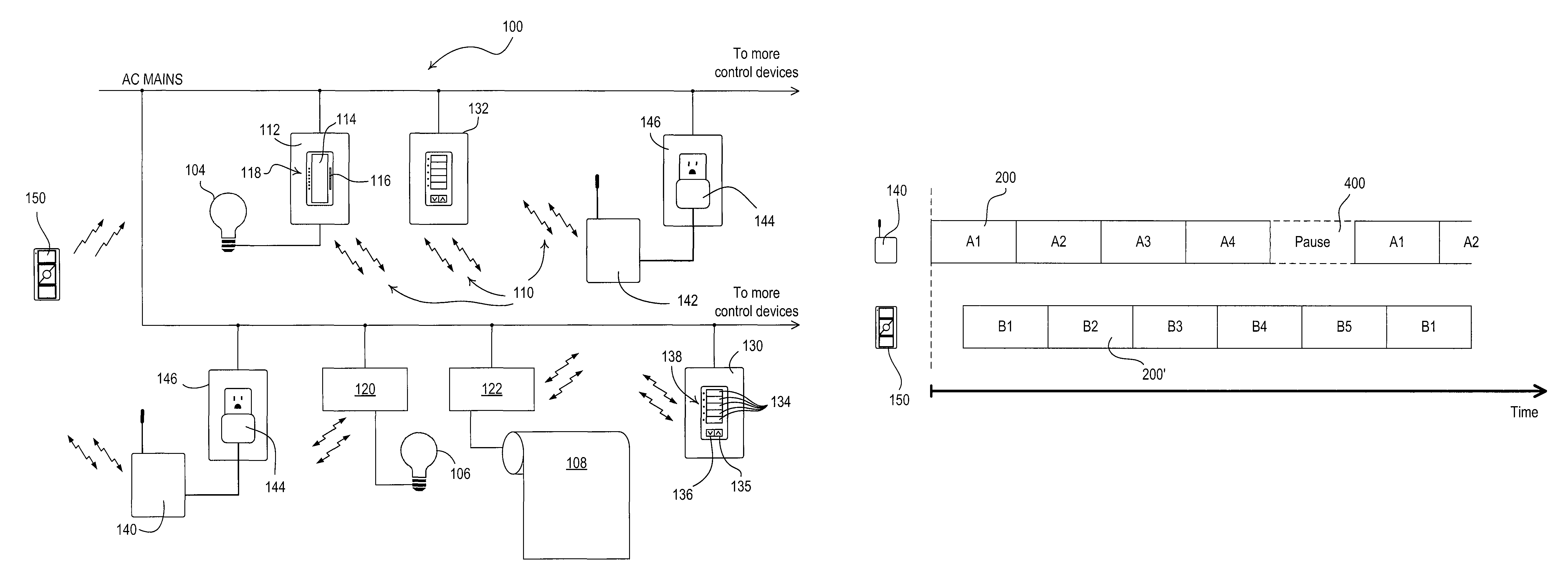

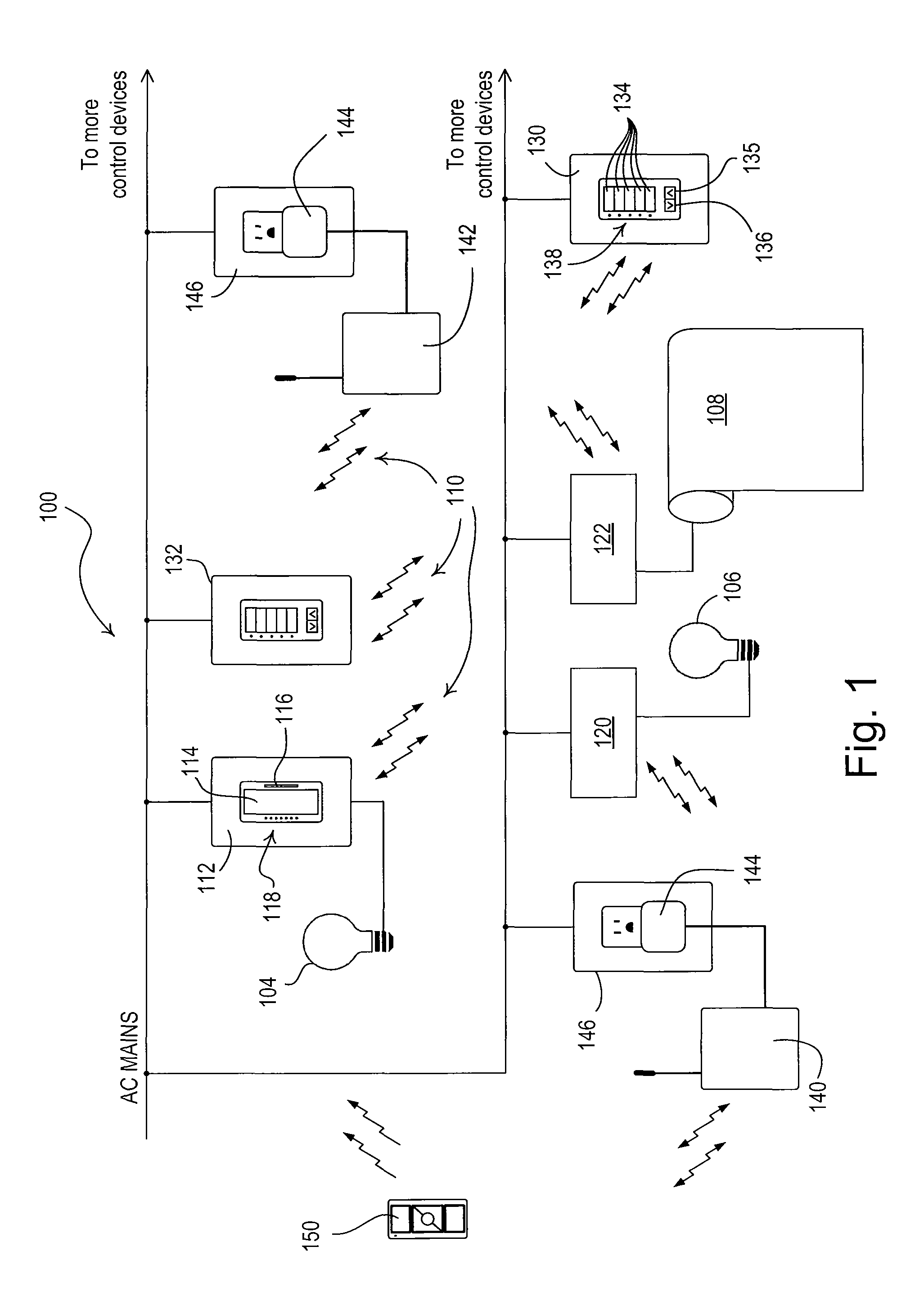

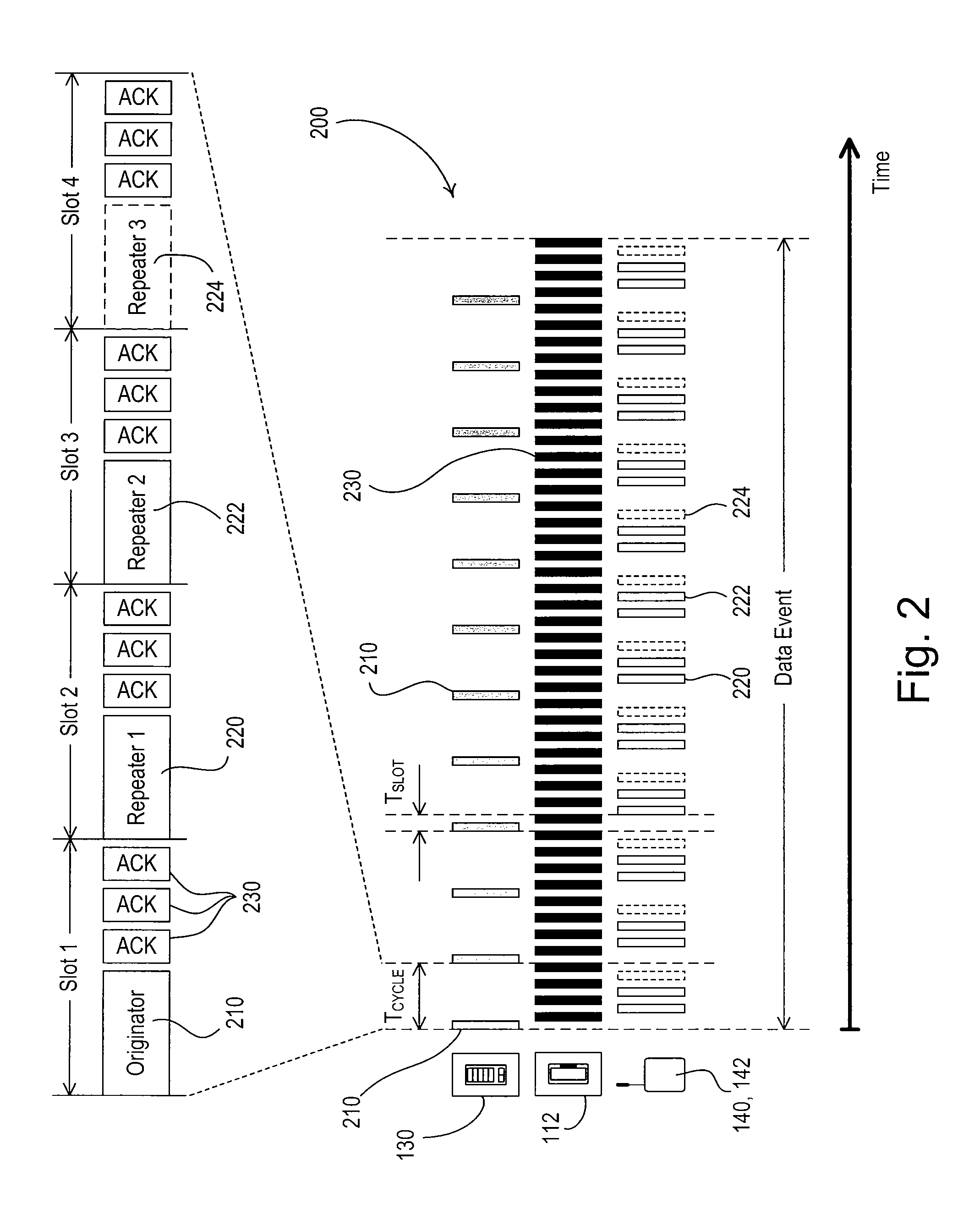

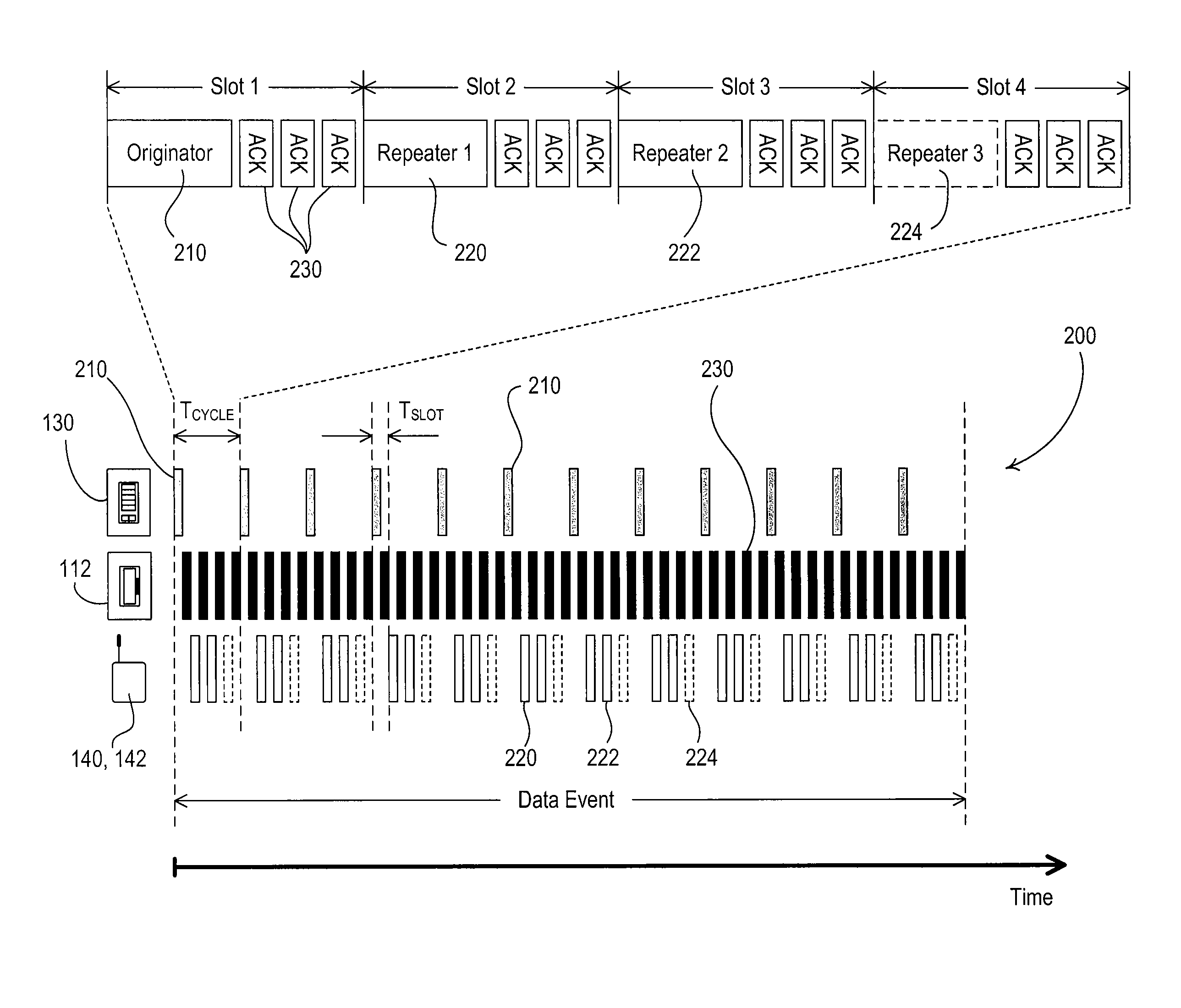

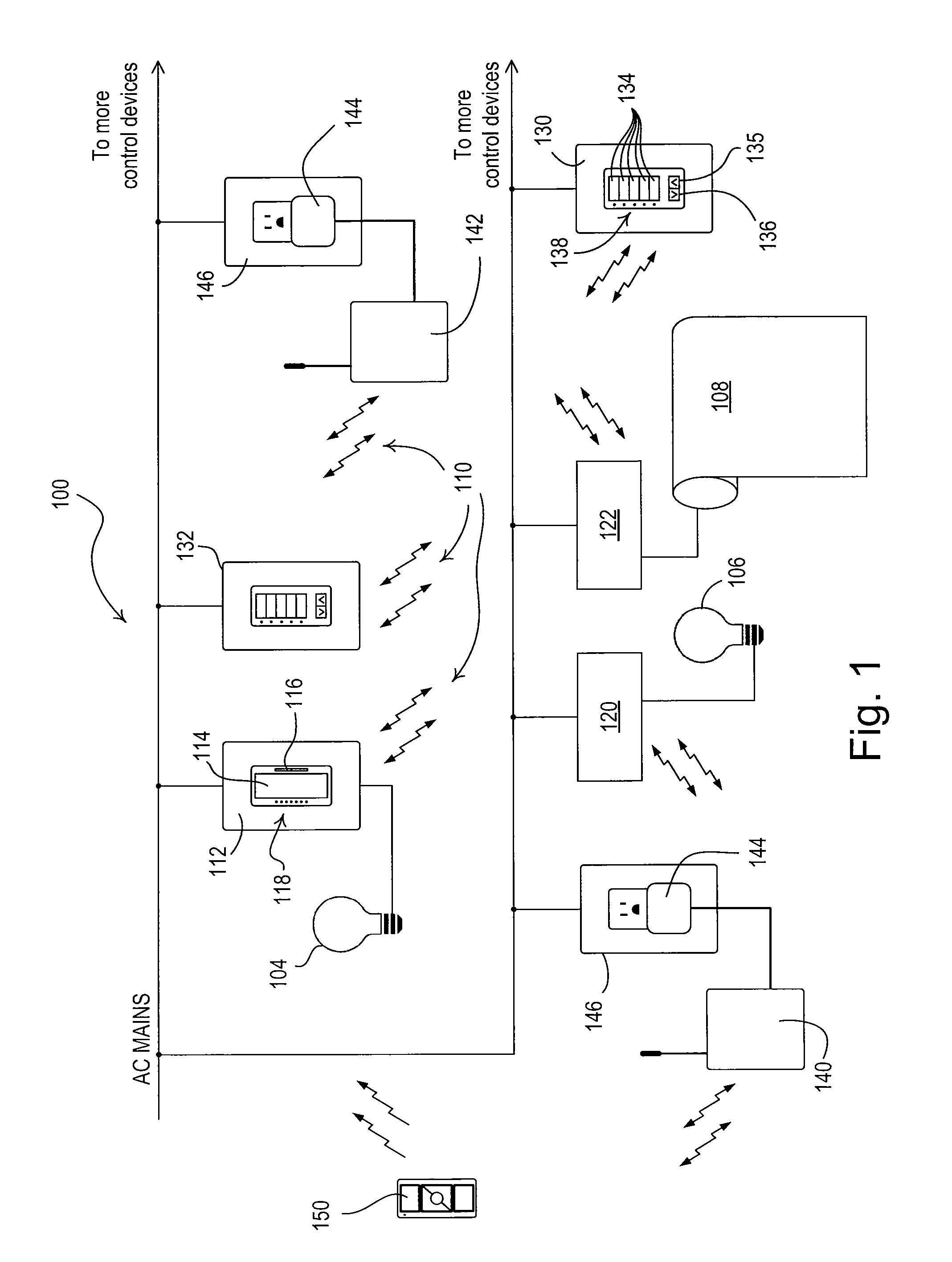

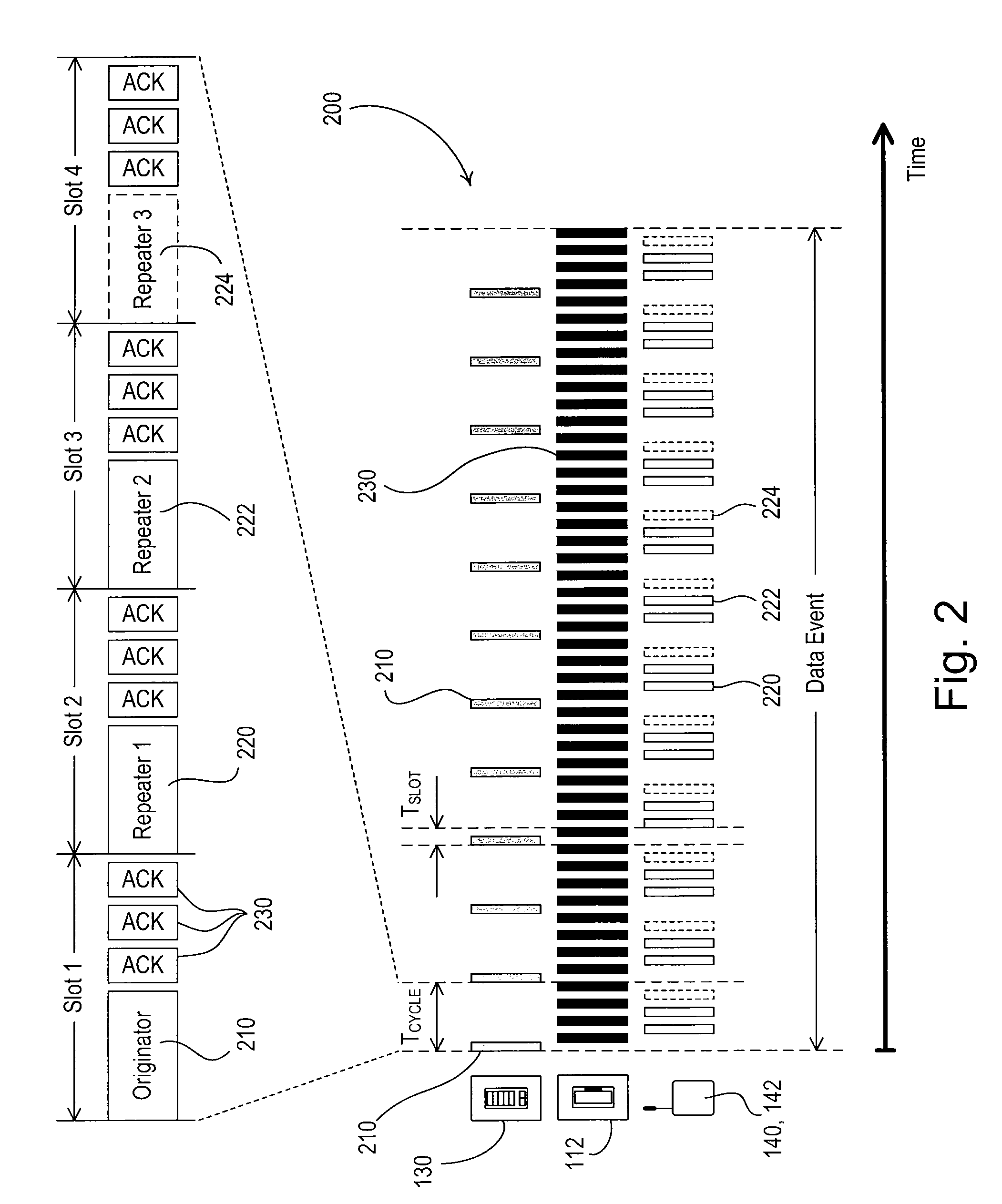

Method of configuring a two-way wireless load control system having one-way wireless remote control devices

ActiveUS20120056712A1Television system detailsElectric signal transmission systemsControl systemRadio frequency

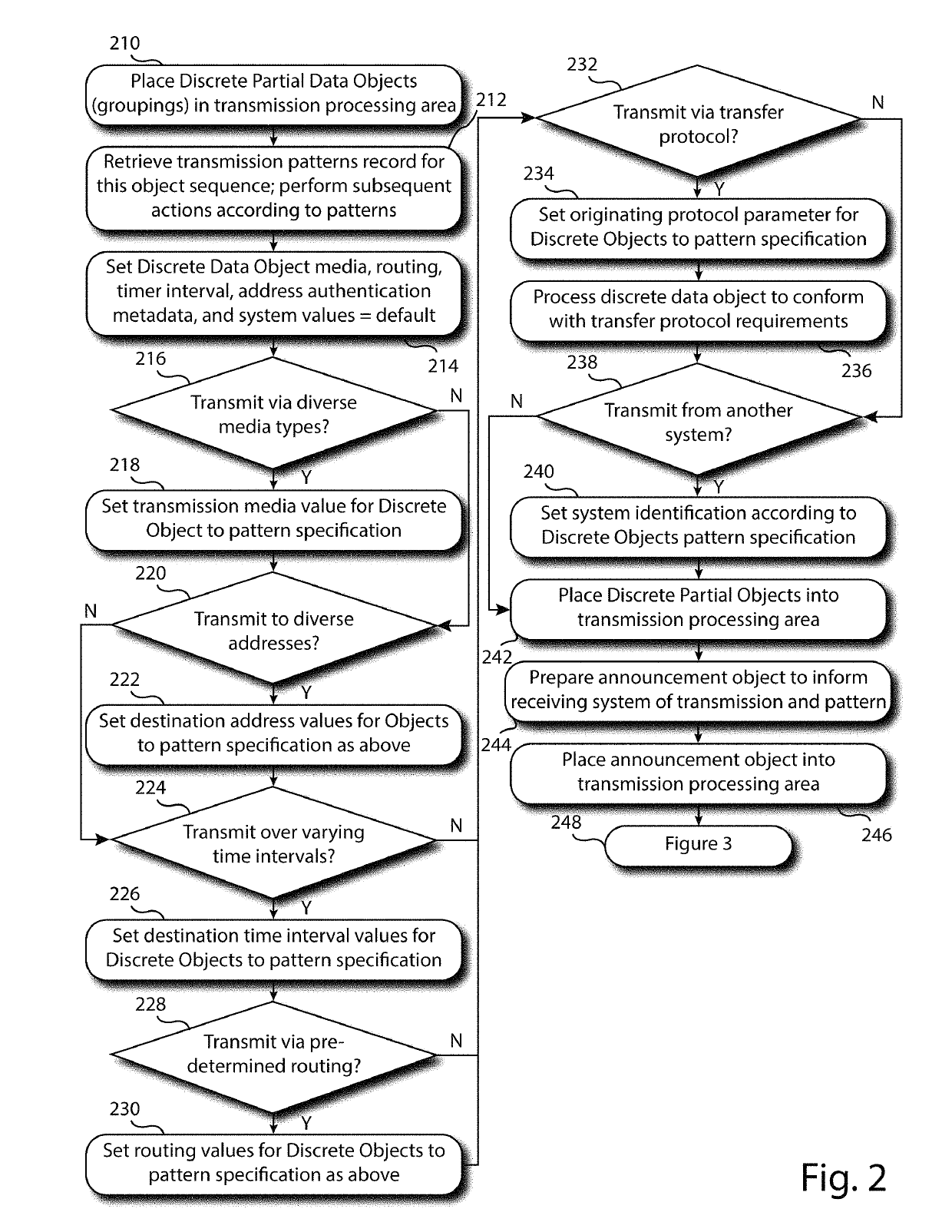

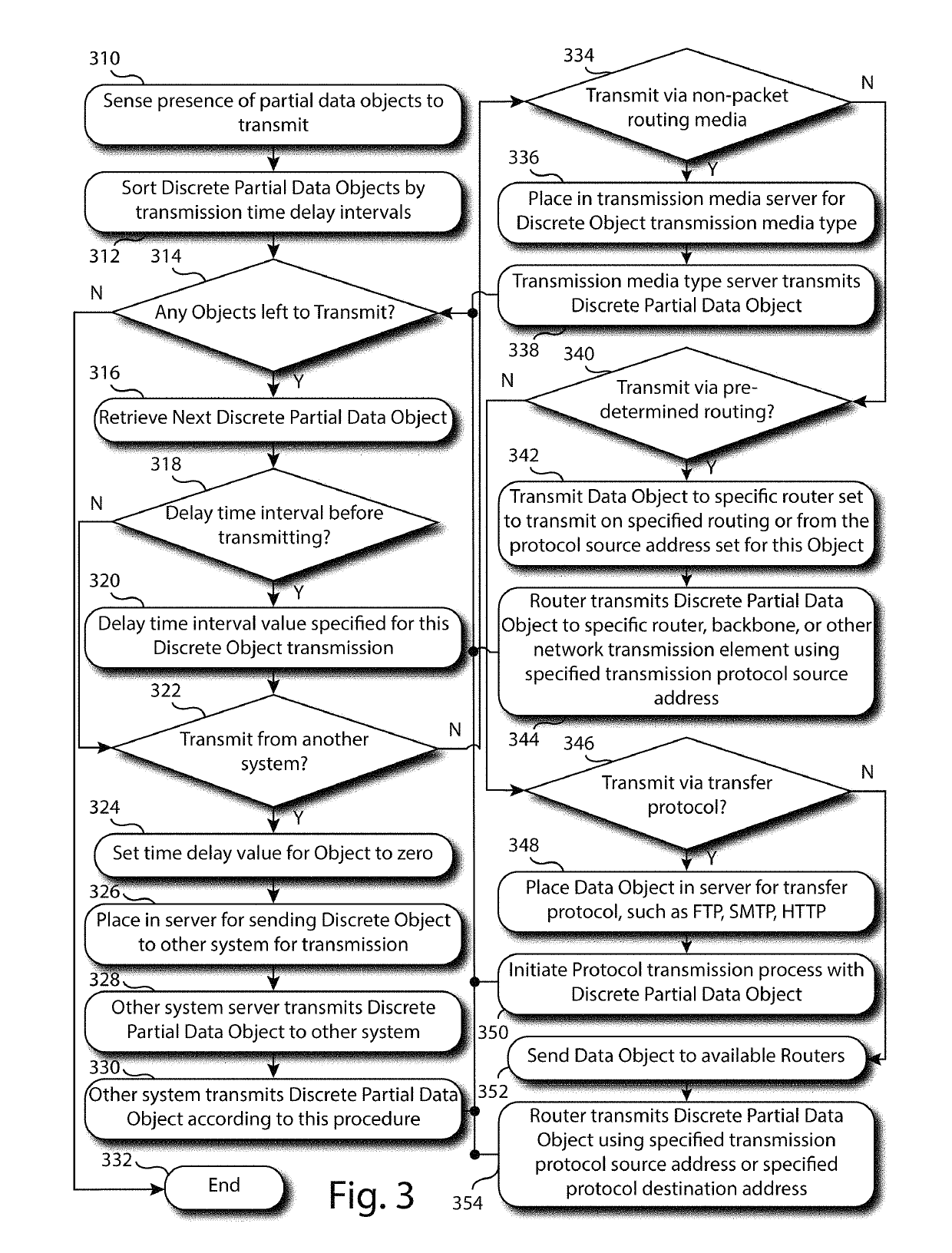

A radio-frequency (RF) load control system includes both two-way and one-way (e.g., transmit-only) remote control devices, and provides a simple, reliable process for configuring the one-way devices into the system. The one-way device may be programmed to operate at one of a predetermined number of radio frequencies as part of a frequency-selection procedure, during which, the one-way device transmits a test command to a signal repeater of the system. If the test command is transmitted at the same frequency as the repeater, the repeater emits an audible beep to inform the user that the remote control is transmitting at the appropriate frequency. To associate the two-way devices with the system, the signal repeater streams an “enter address mode” command. To allow the one-way device to be associated with the system, the signal repeater pauses the transmission of the enter address mode command to allow the one-way device to transmit an activation request message to the signal repeater.

Owner:LUTRON TECH CO LLC

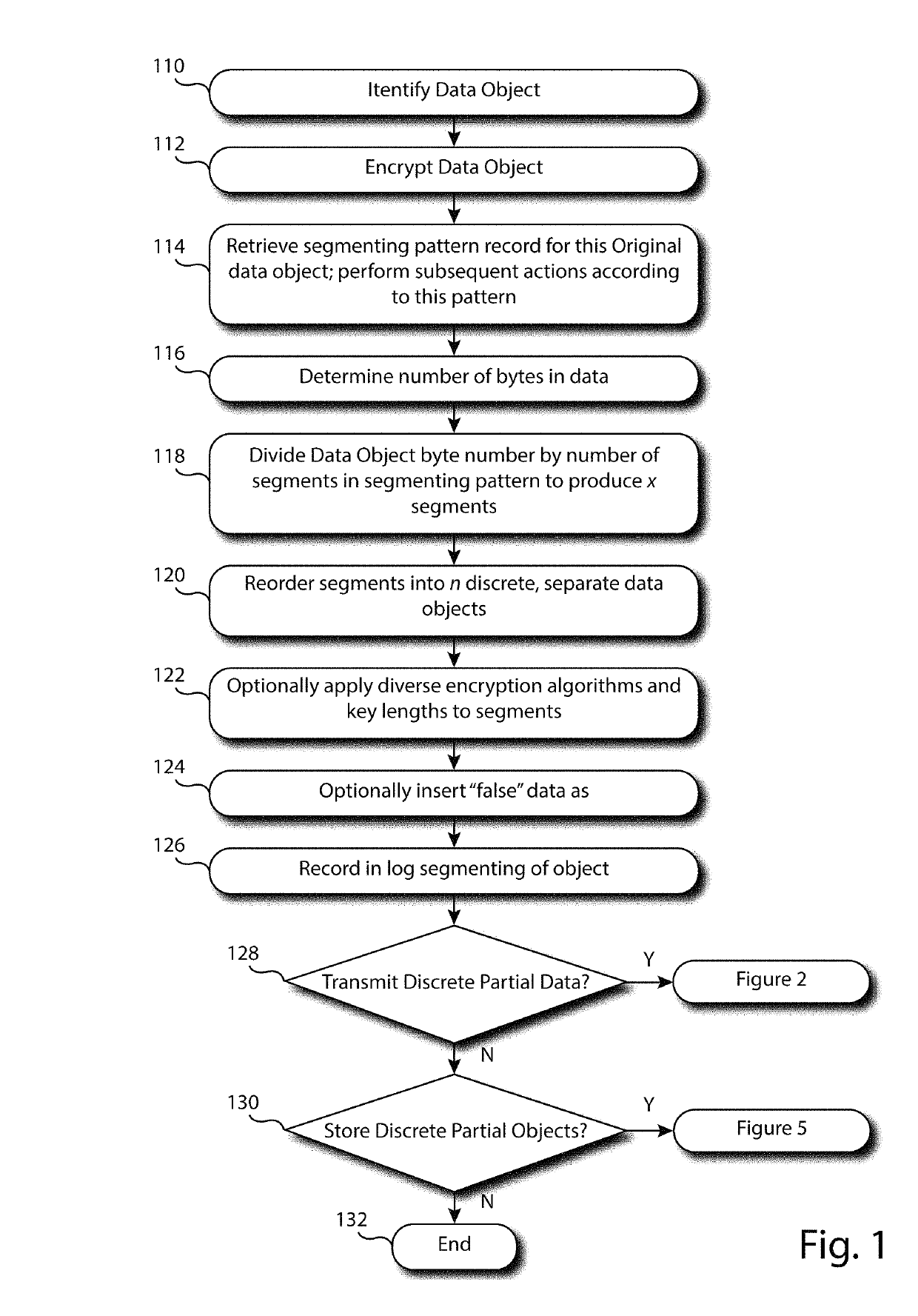

System and method for secure data transmission and storage

Owner:GRID7 LLC

Method of configuring a two-way wireless load control system having one-way wireless remote control devices

ActiveUS8598978B2Television system detailsElectric signal transmission systemsControl systemRadio frequency

Owner:LUTRON TECH CO LLC

Private allocated networks over shared communications infrastructure

Methods and systems for implementing private allocated networks in a virtual infrastructure are presented. One method operation creates virtual switches in one or more hosts in the virtual infrastructure. Each port in the virtual switches is associated with a private allocated network (PAN) from a group of possible PANs. In one embodiment, one or more PANs share the same physical media for data transmission. The intranet traffic within each PAN is not visible to nodes that are not connected to the each PAN. In another operation, the method defines addressing mode tables for the intranet traffic within each PAN. The entries in the addressing mode tables define addressing functions for routing the intranet traffic between the virtual switches, and different types of addressing functions are supported by the virtual switches.

Owner:NICIRA

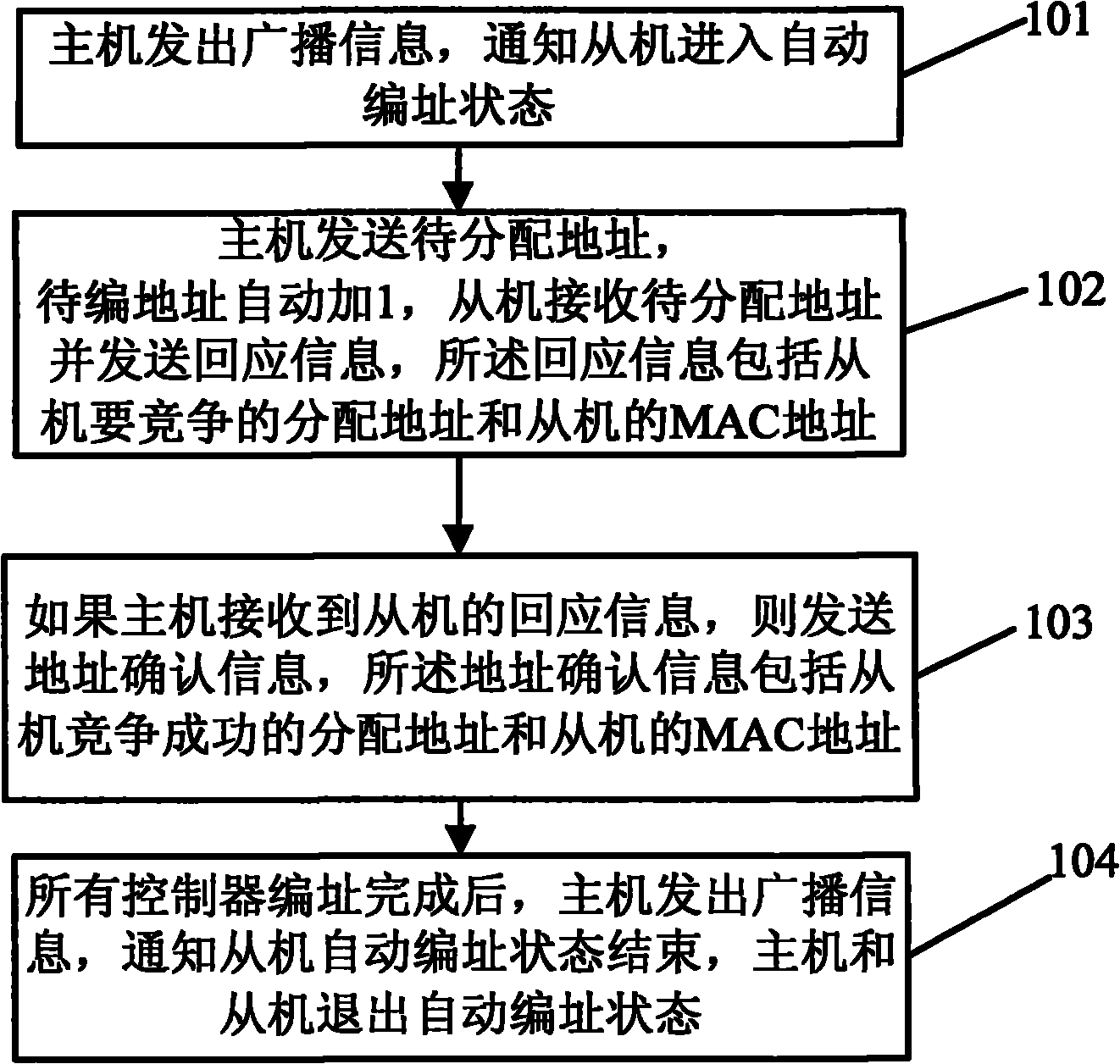

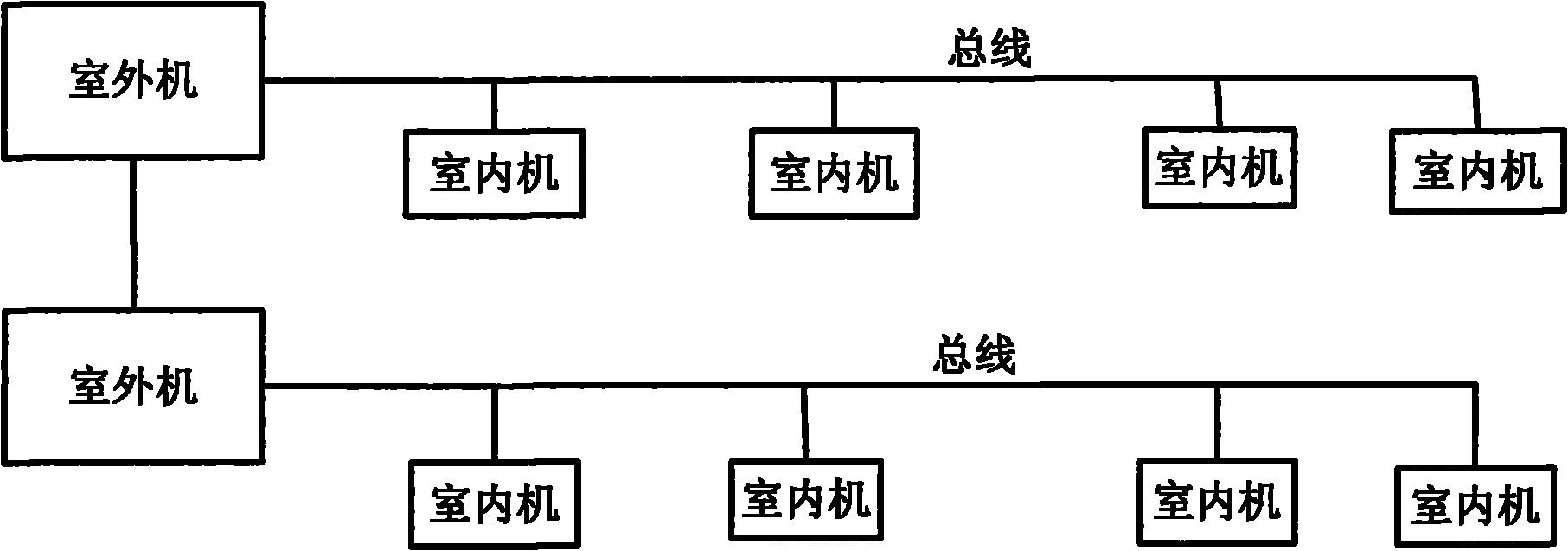

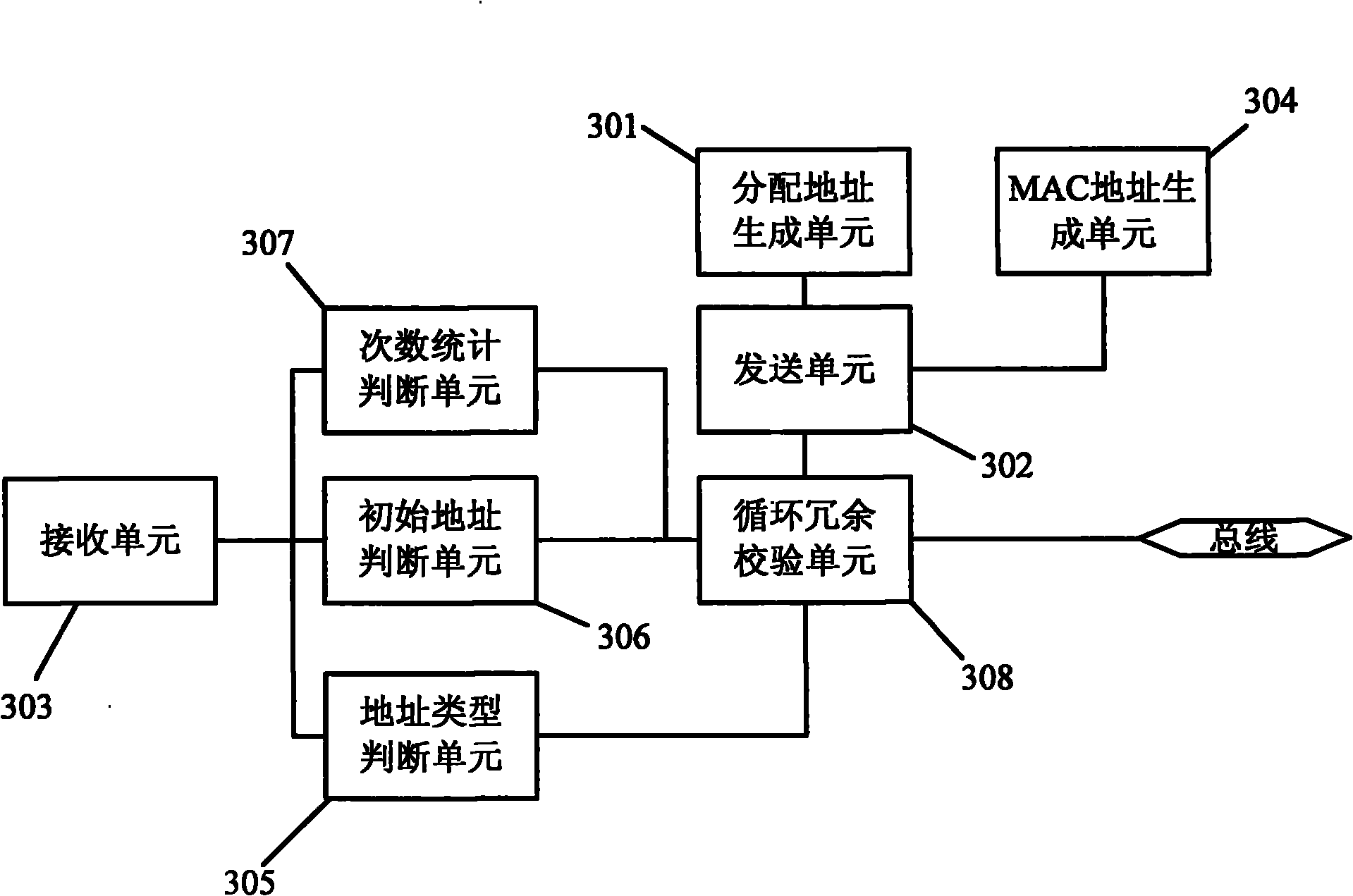

Automatic addressing method for air conditioning system and air conditioning controller

InactiveCN101852472AThe method of automatic addressing is simple and easyNot easy to make mistakesSpace heating and ventilation safety systemsLighting and heating apparatusEngineeringAir conditioning

The invention discloses an automatic addressing method for an air conditioning system. A first air conditioning serves as a master machine and the other air conditionings serve as slave machines. The method comprises the following steps that: the master machine sends broadcast information to notify the slave machines to enter an automatic addressing mode and the slave machines restore the addresses per se to initial addresses; the master machine transmits the addresses to be allocated, wherein the addresses to be allocated add one automatically, the slave machines receive the addresses to be allocated and transmit response information which comprises the allocated addresses to be competed by the slave machines and the MAC addresses of the slave machines; if receiving the response information from the slave machines, the master machine transmits the address acknowledgement information which comprises the allocated addresses successfully competed by the slave machines and the MAC addresses of the slave machines; and after the addressing of all controllers is finished, the master machine transmits the broadcast information to notify the slave machines to finish the automatic addressing state and the master machine and the slave machines quit the automatic addressing state. The air conditioning system can be simply and easily subjected to automatic addressing by the method without easy error. The invention also discloses an air conditioning controller.

Owner:欧威尔空调科技(中国)有限公司

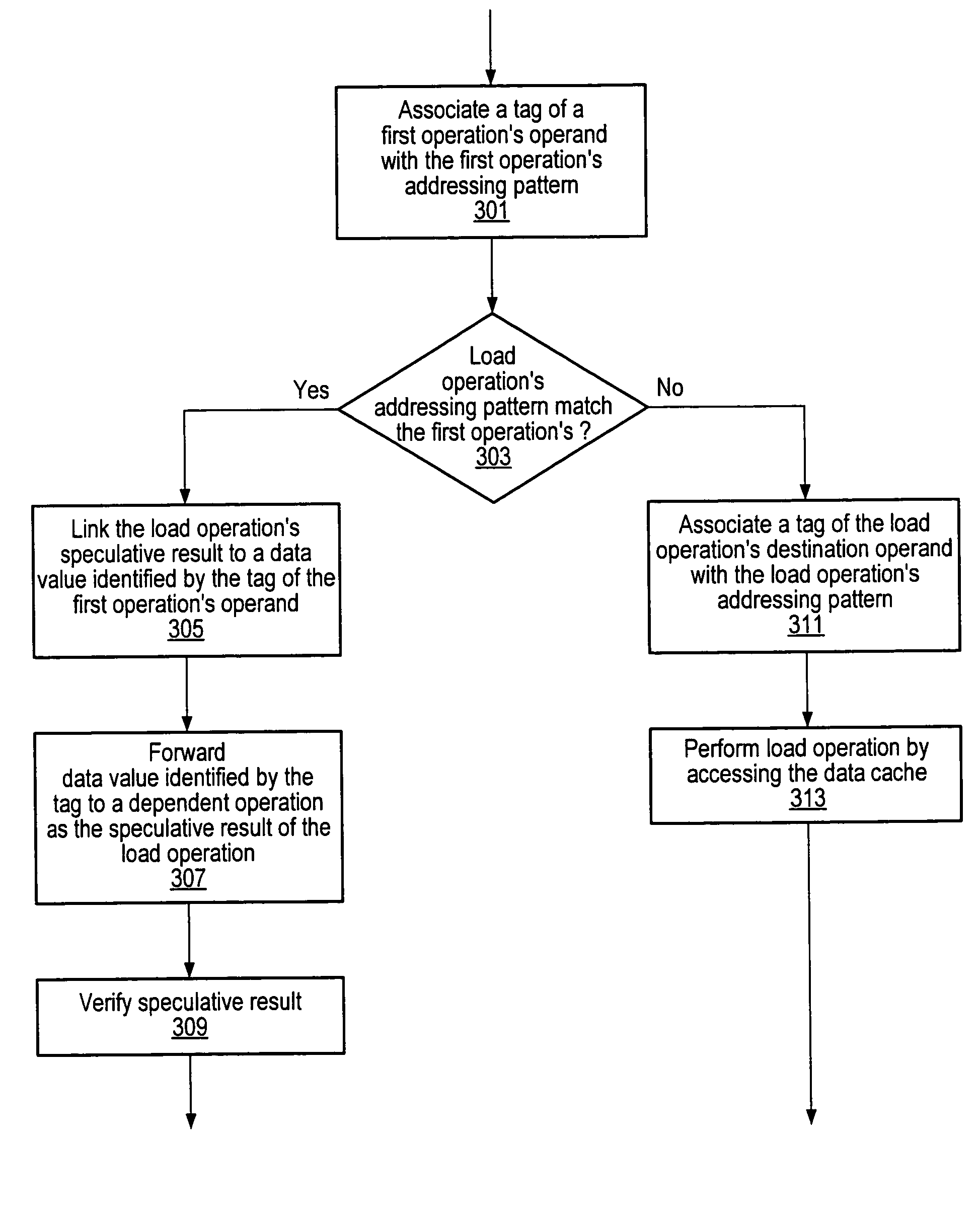

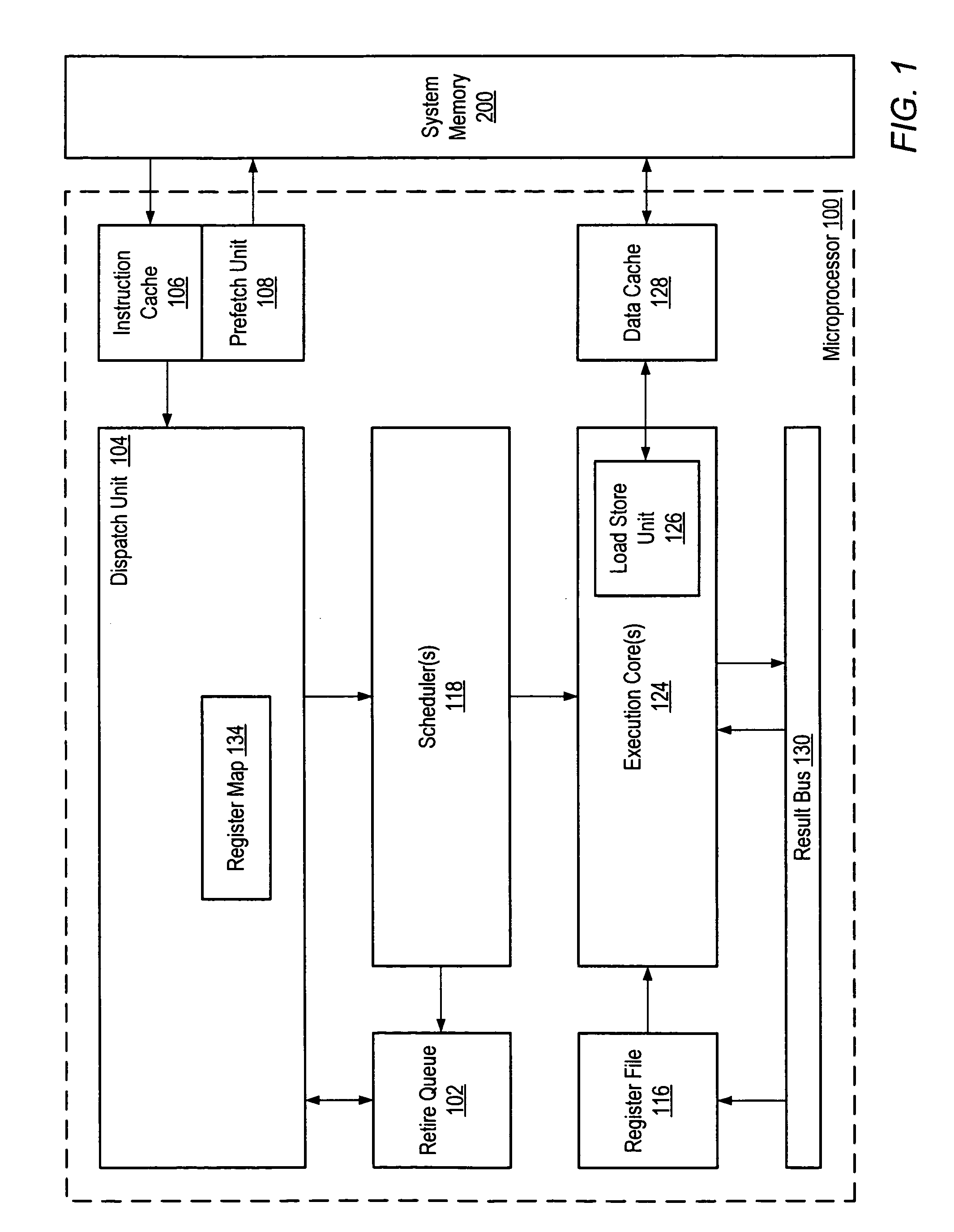

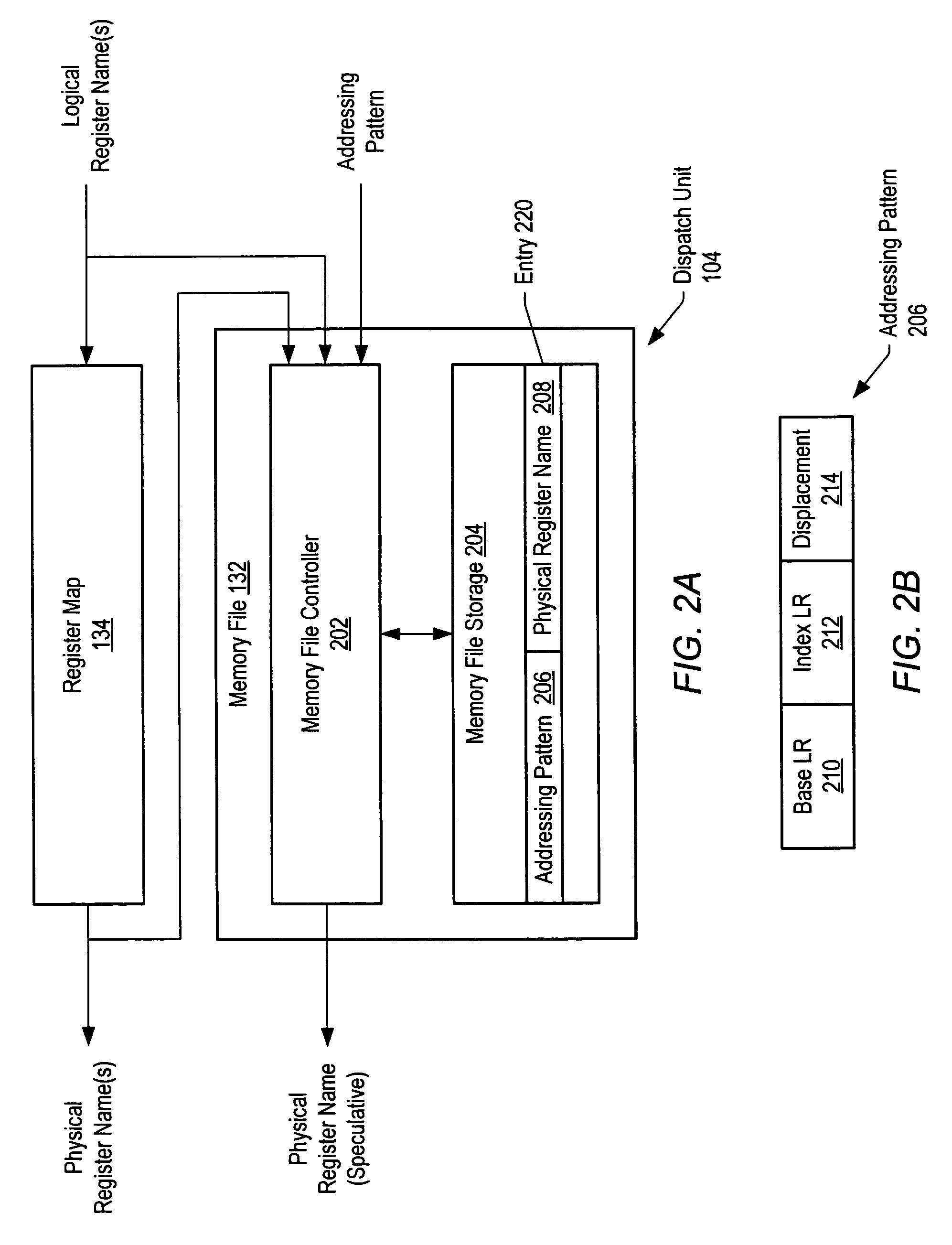

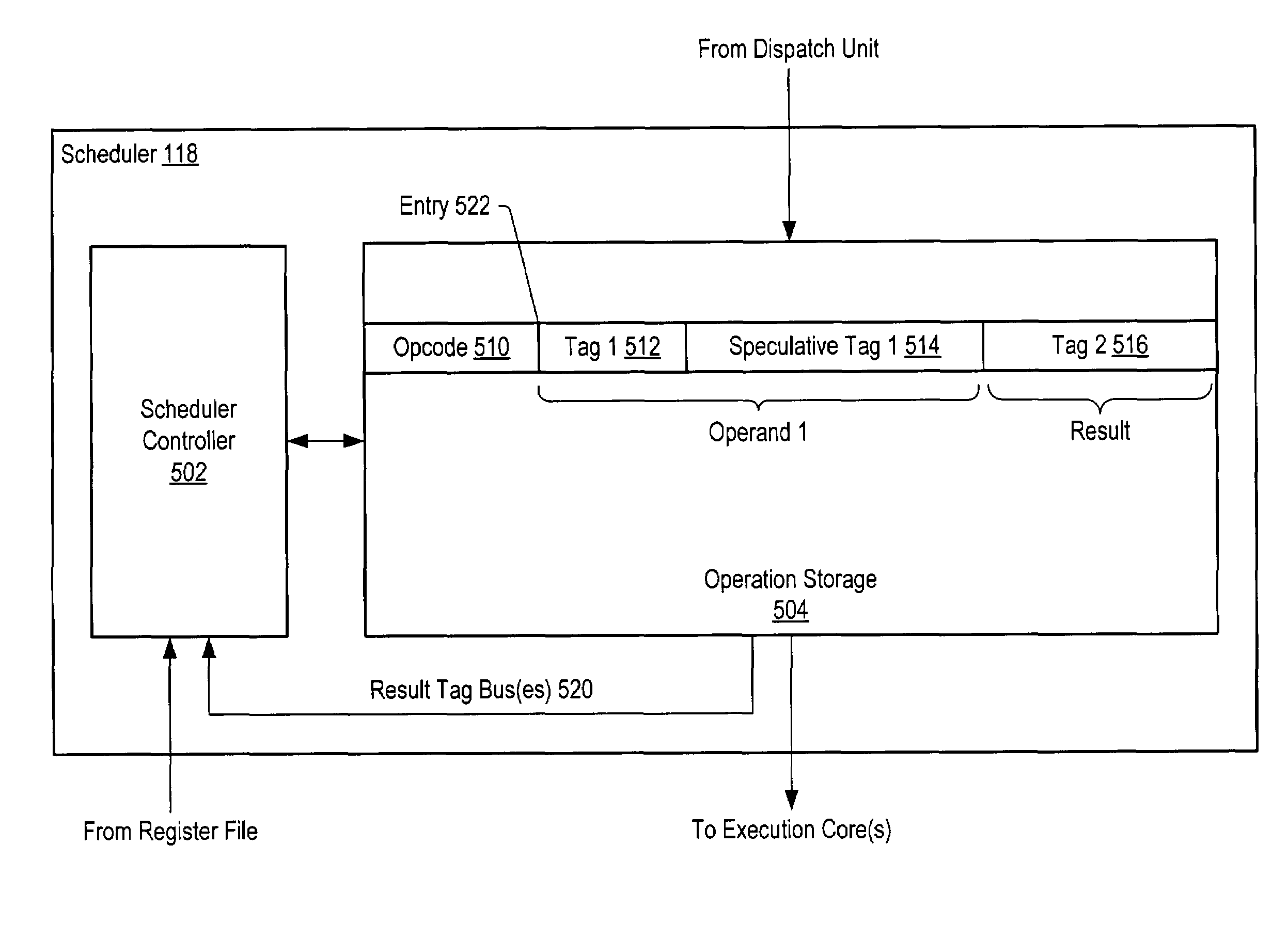

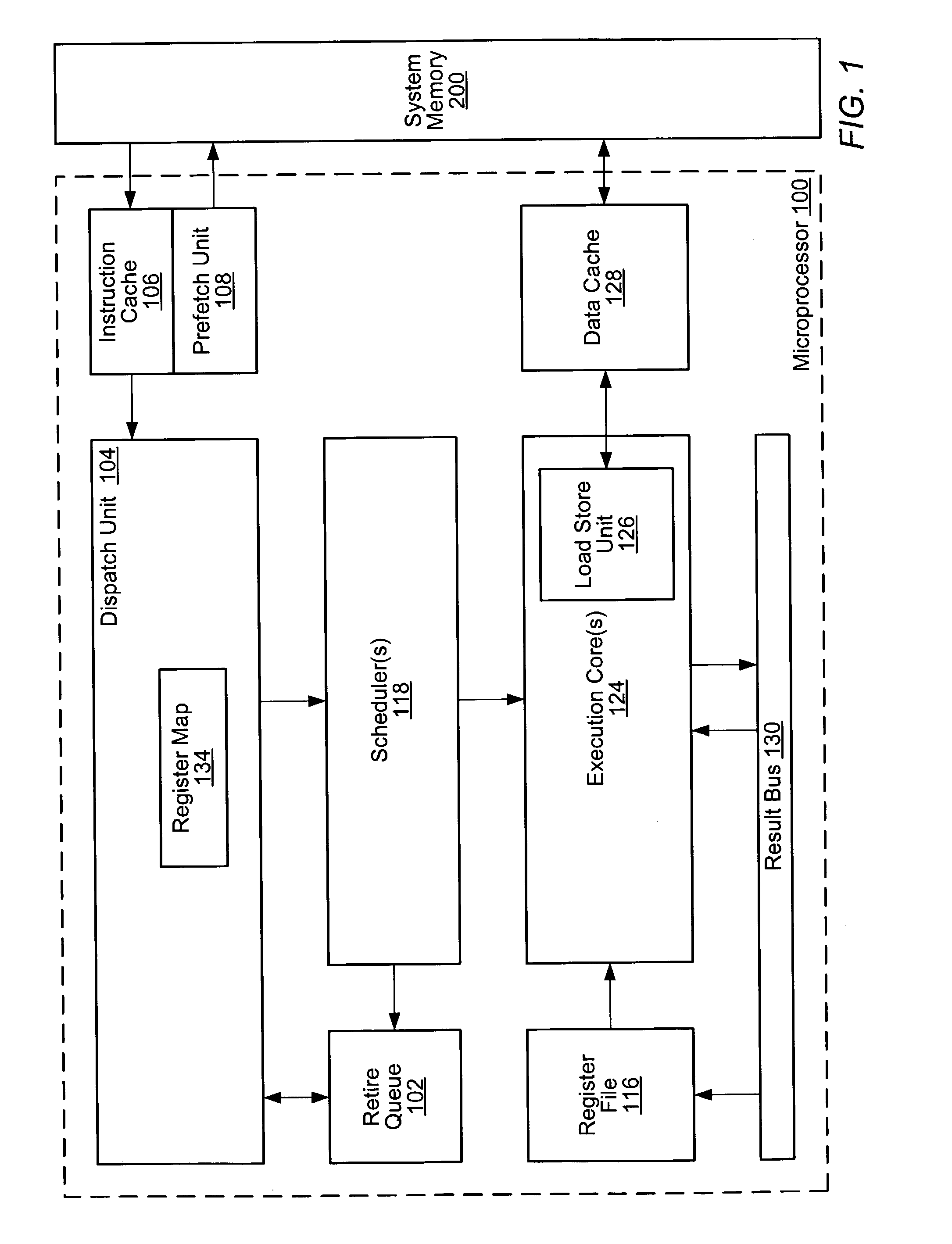

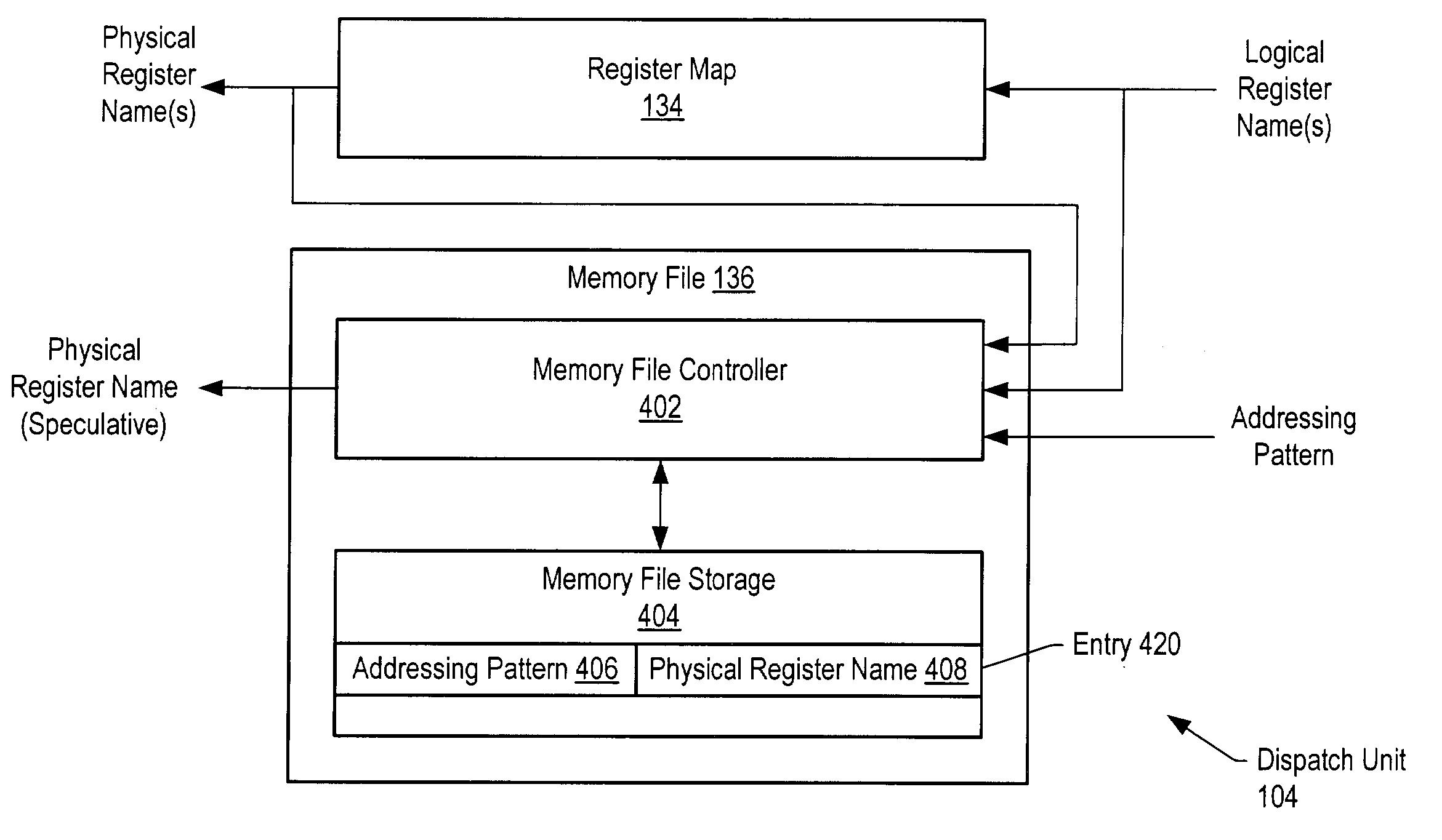

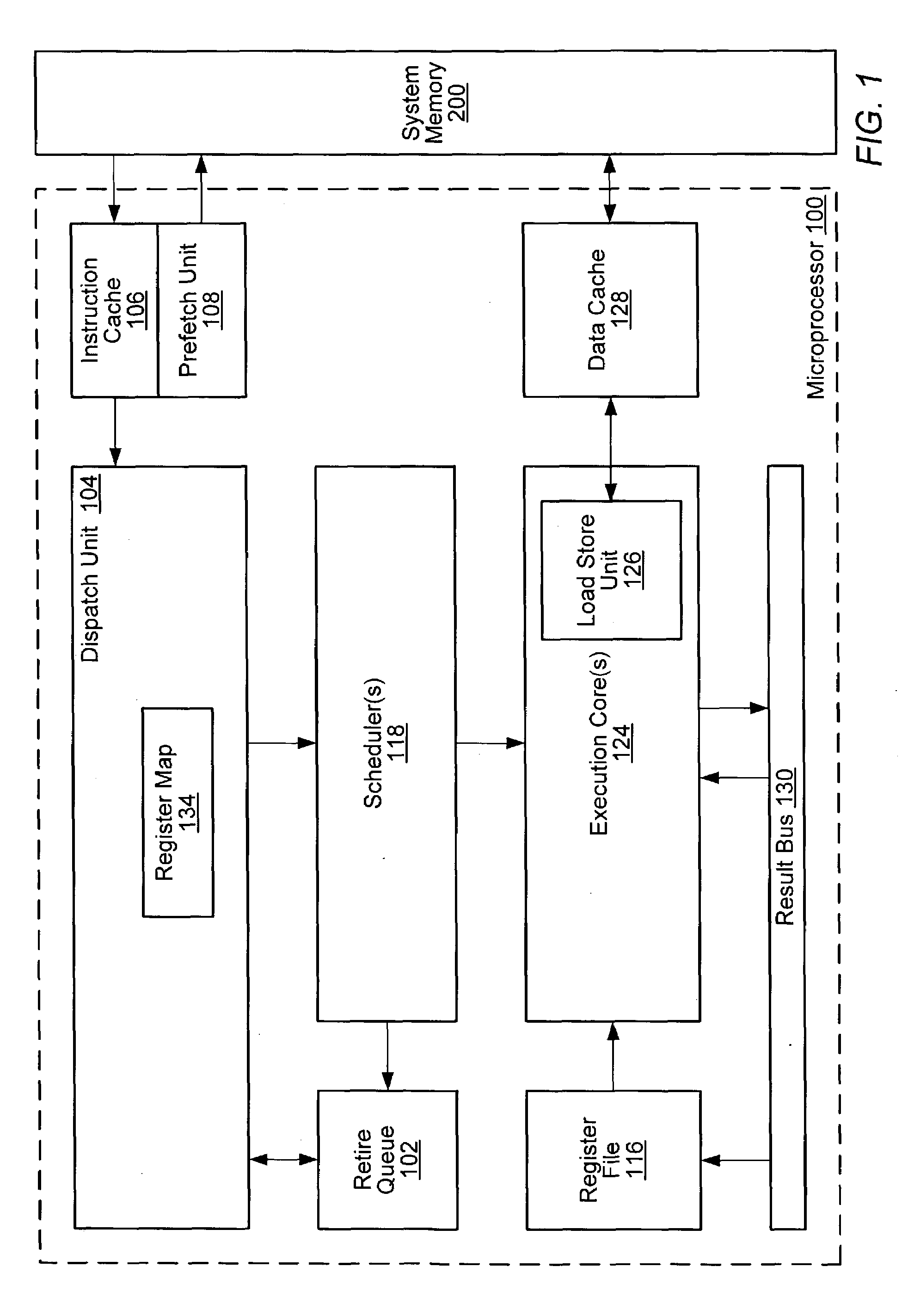

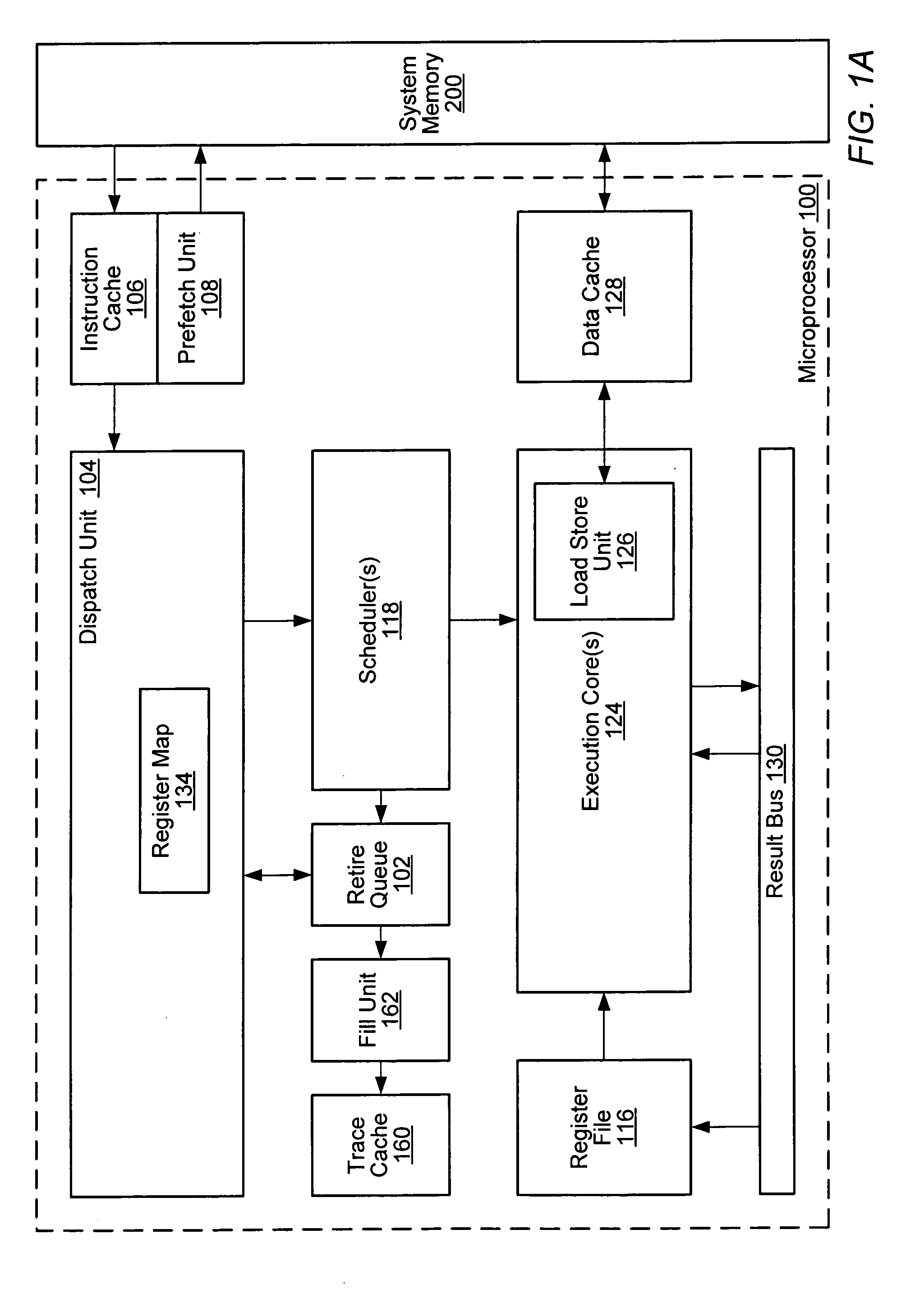

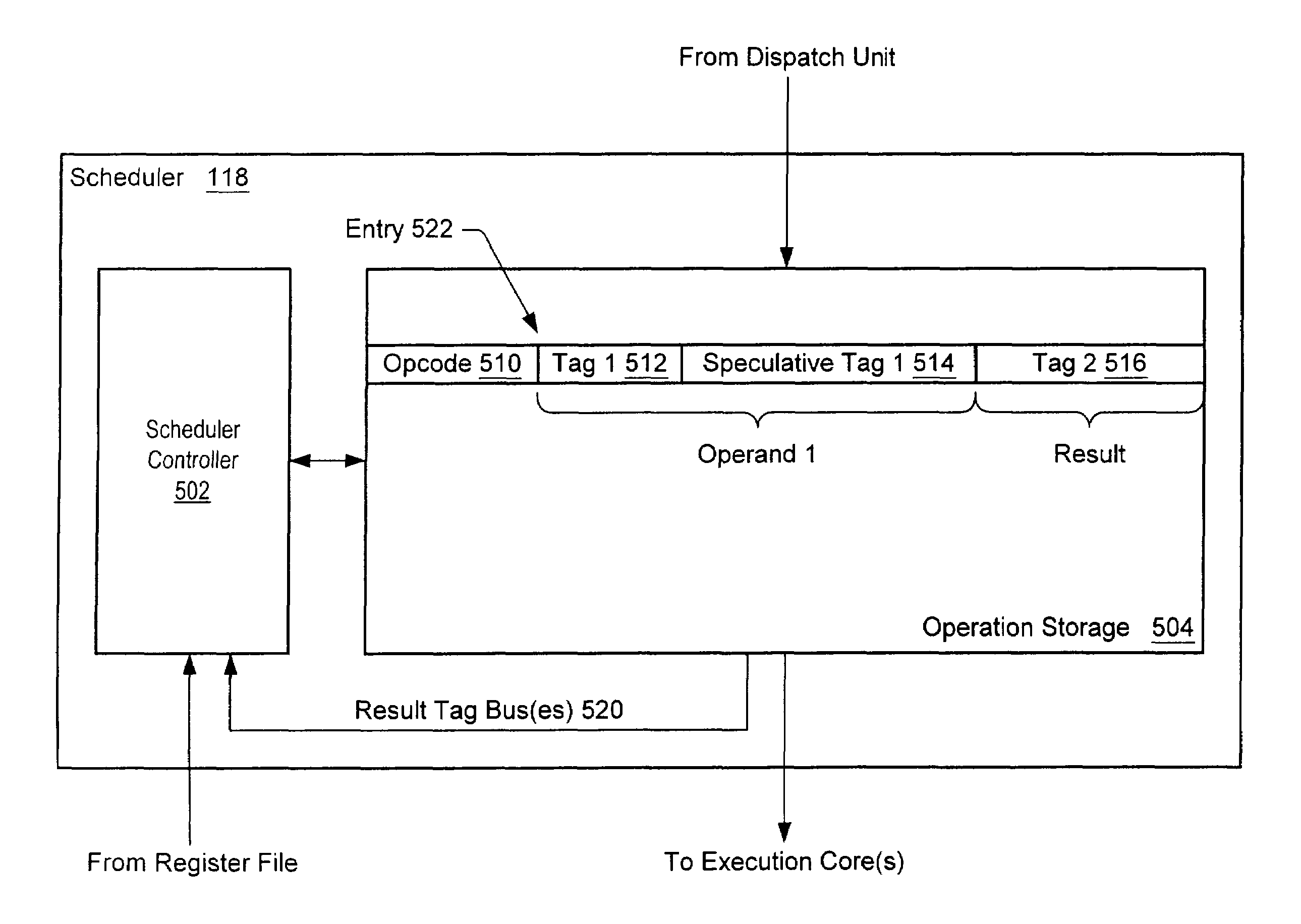

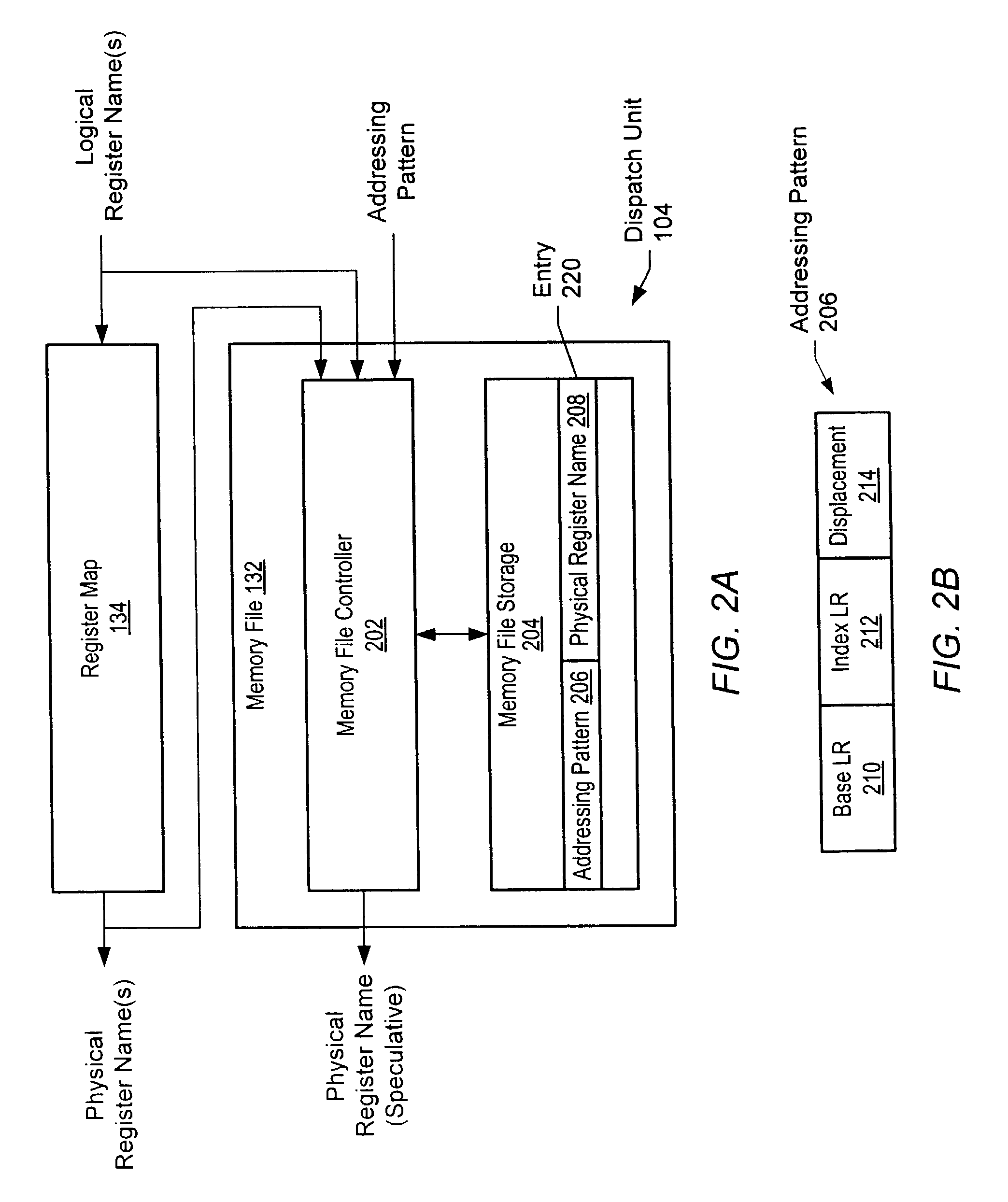

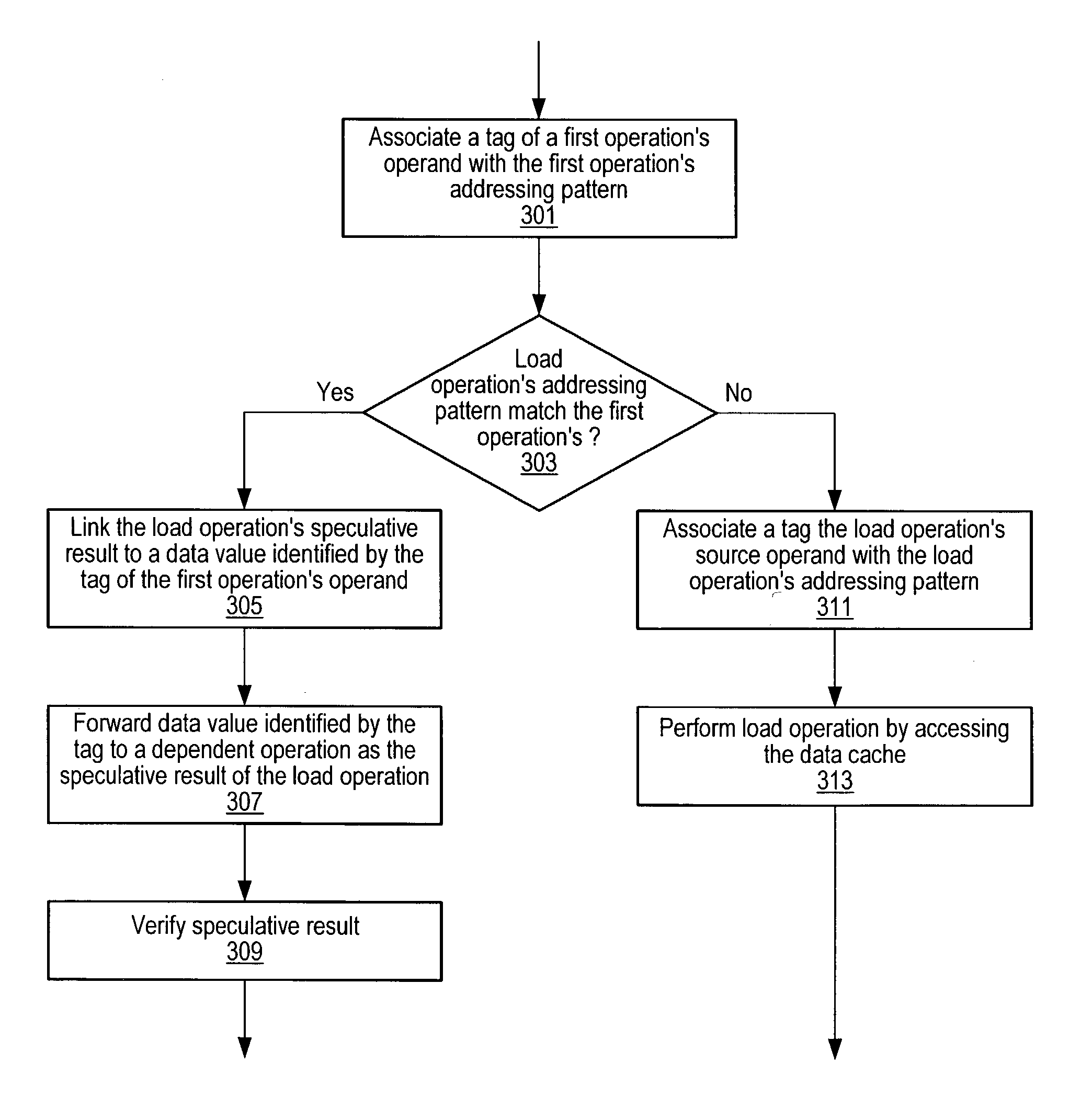

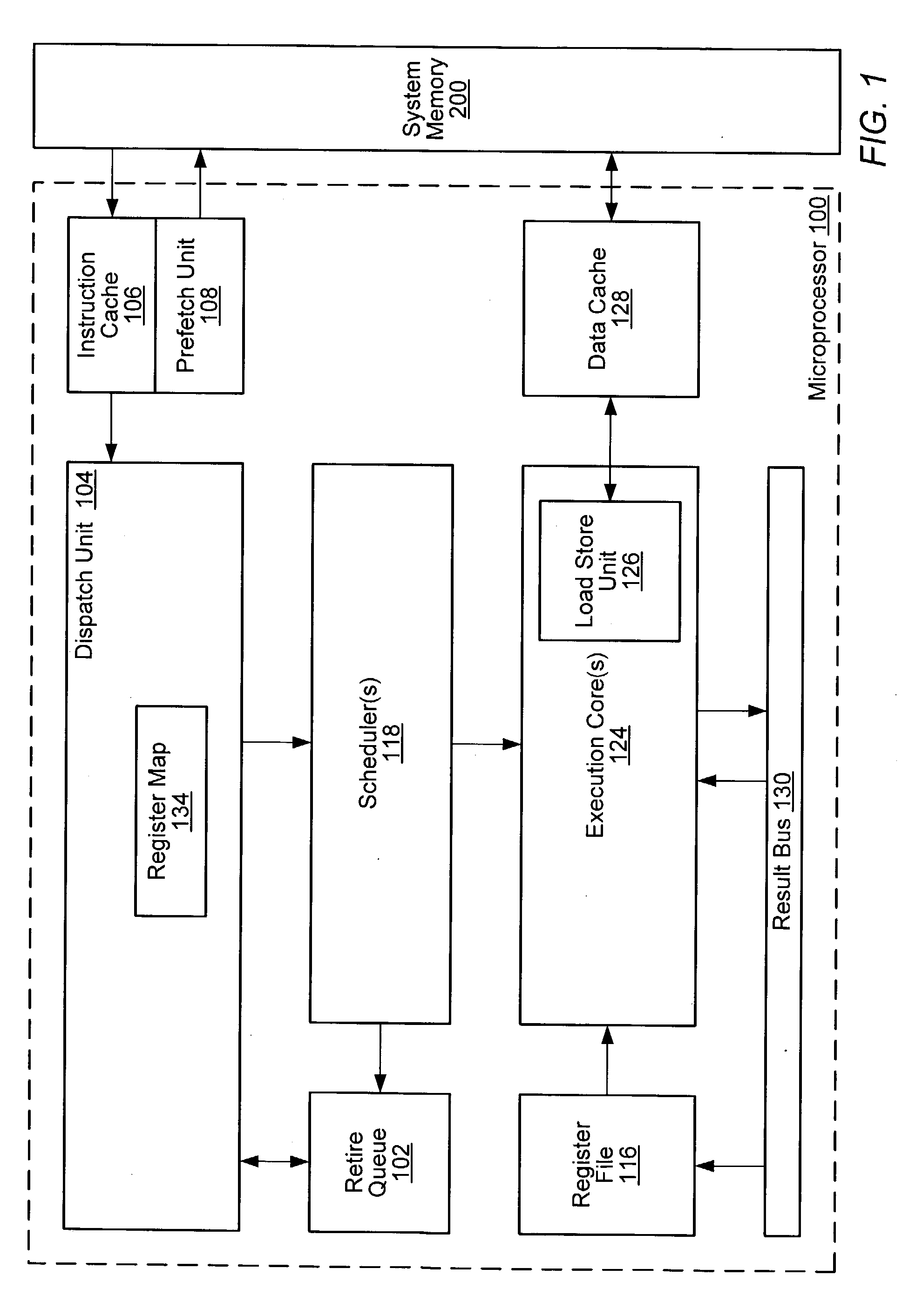

System and method for validating a memory file that links speculative results of load operations to register values

ActiveUS7263600B2Digital computer detailsConcurrent instruction executionProcessor registerData value

A system and method for linking speculative results of load operations to register values. A system includes a memory file including an entry configured to store a first addressing pattern and a first tag. The memory file is configured to compare the first addressing pattern to a second addressing pattern of a load operation, and to link a data value identified by the first tag to a speculative result of the load operation if there is a match. The system further includes an execution core coupled to the memory file and configured to access the speculative result when executing a second operation that is dependent on the load operation, and a load store unit coupled to the memory file and configured to verify the link between the data value and the speculative result of the load operation by performing a comparison between one or more addresses.

Owner:GLOBALFOUNDRIES U S INC

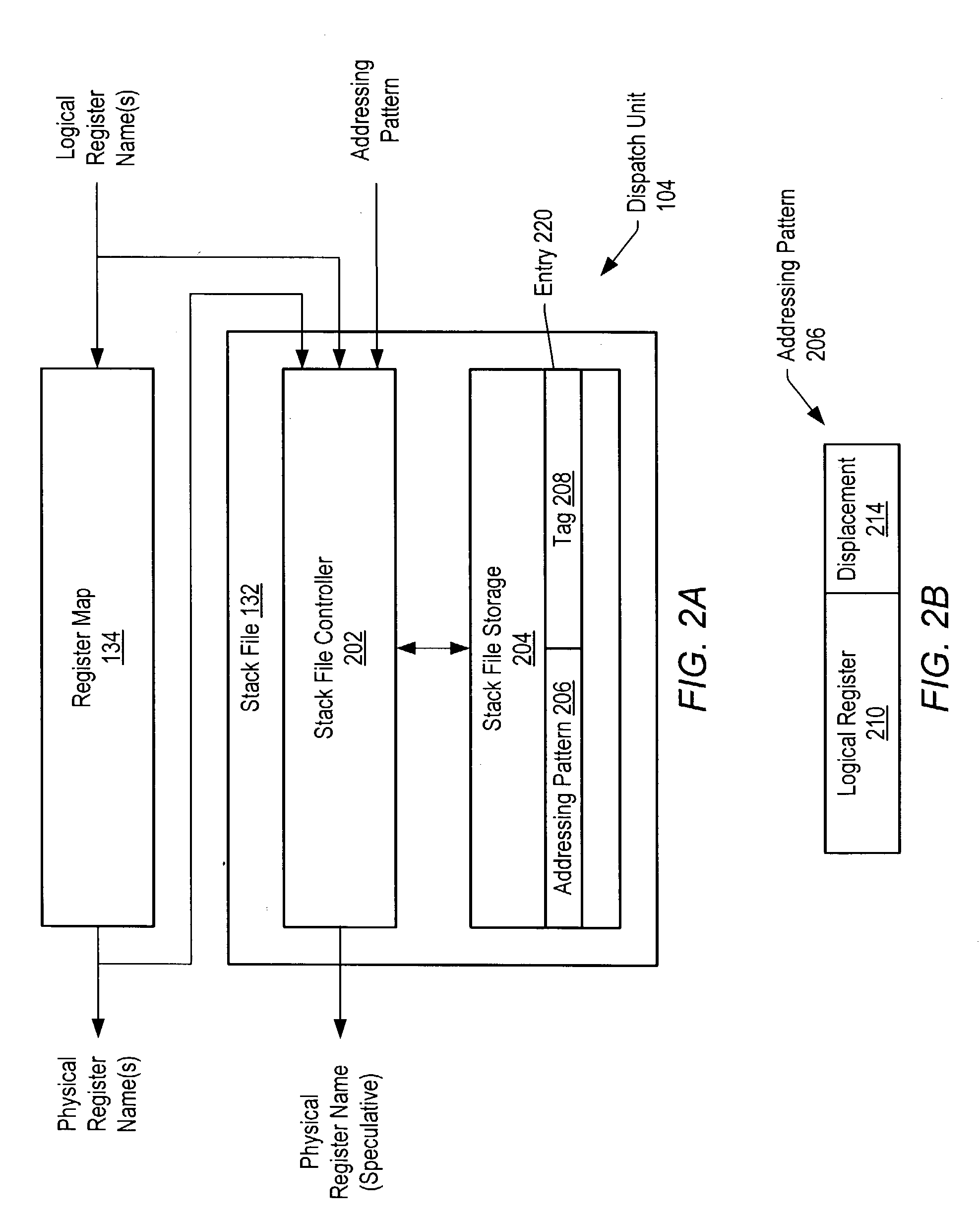

Data speculation based on stack-relative addressing patterns

A processor may include a stack file and an execution core. The stack file may include an entry configured to store an addressing pattern and a tag. The addressing pattern identifies a memory location within the stack area of memory. The stack file may be configured to link a data value identified by the tag stored in the entry to the speculative result of a memory operation if the addressing pattern of the memory operation matches the addressing pattern stored in the entry. The execution core may be configured to access the speculative result when executing another operation that is dependent on the memory operation.

Owner:ADVANCED MICRO DEVICES INC

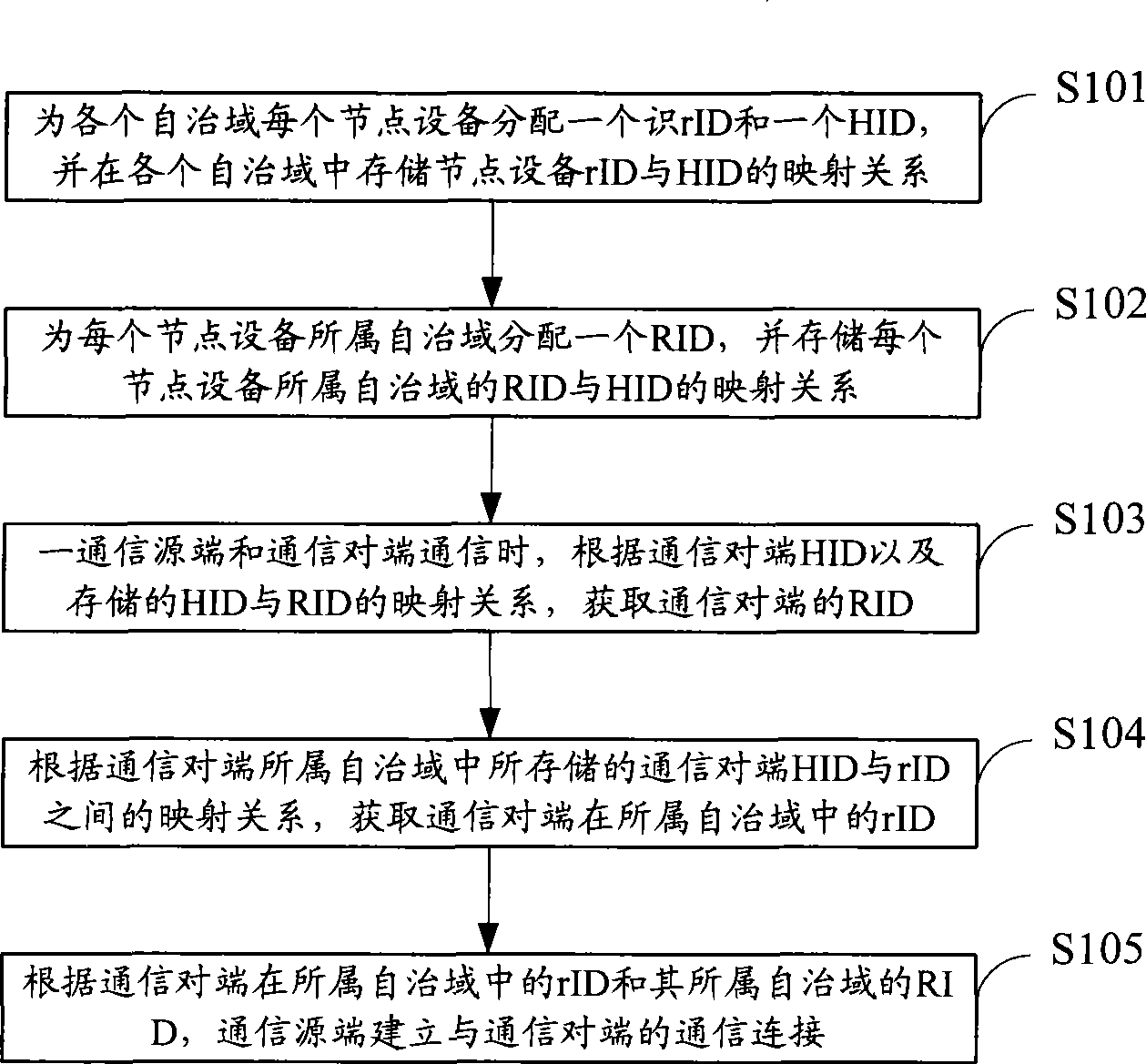

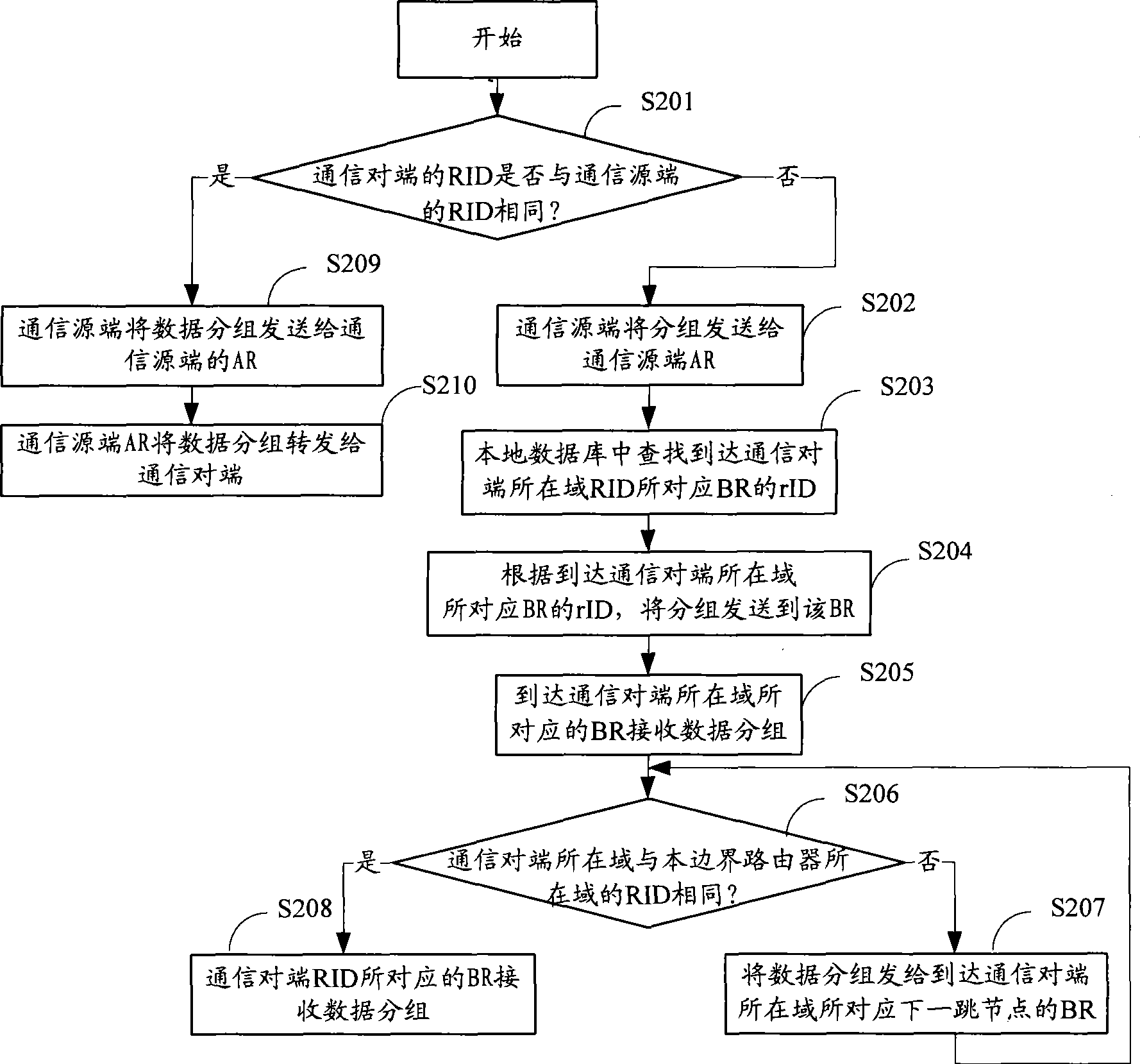

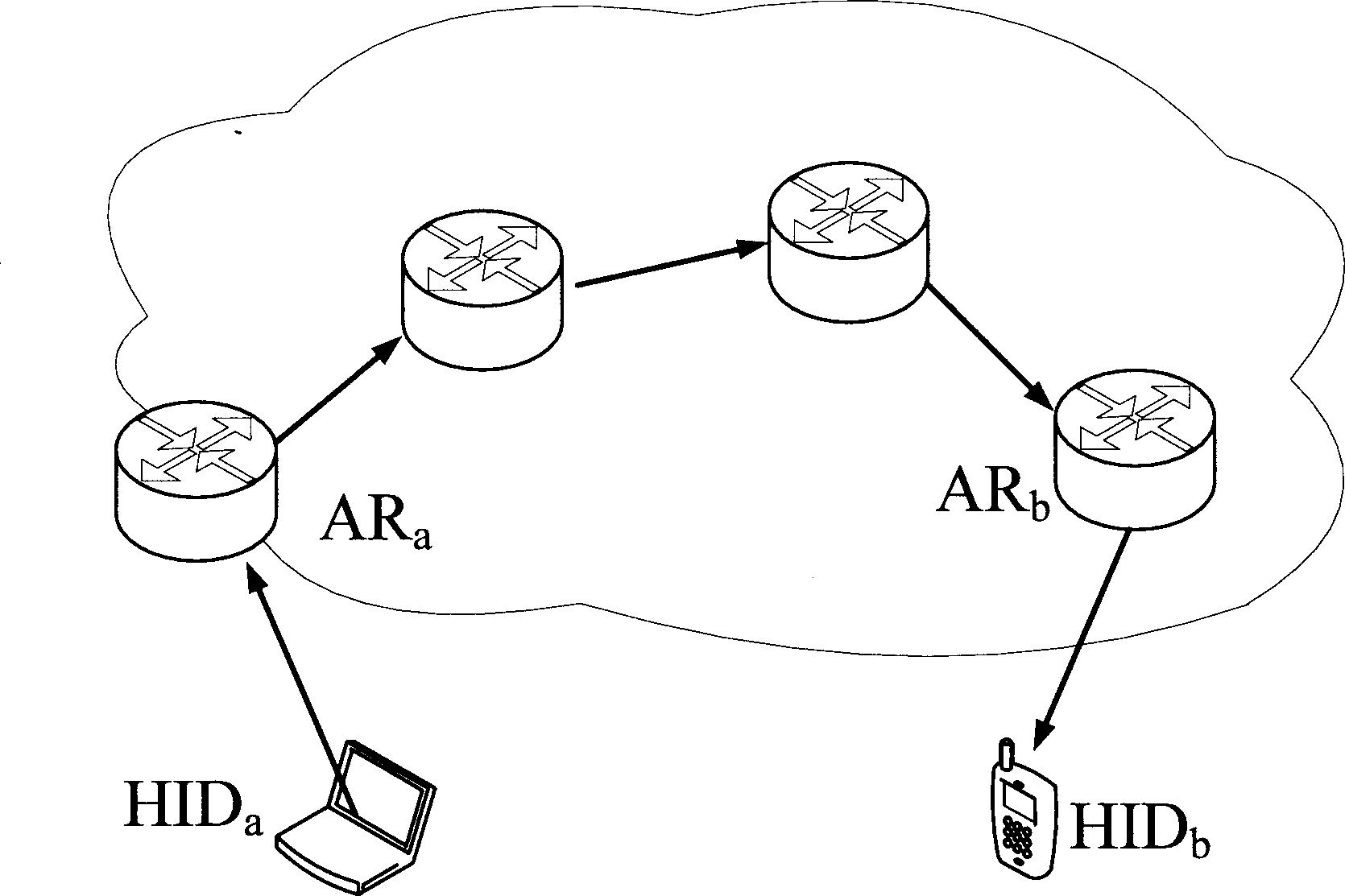

Intra-domain and inter-domain network interconnecting method and system thereof

InactiveCN101459698ARealize interconnectionData switching networksInterconnectionHeterogeneous network

The invention discloses a method for interconnecting networks in domains and between domains, which comprises the steps: distributing a RID to each autonomous domain, distributing a rID and an HID to each node device in each domain, storing the mapping relation between the HID and the RID, and between the HID and the rID of each node device, obtaining a communication end RID according to the HID on the communicating end and the stored mapping relation between the HID and the RID when a communication source end is communicated with the communication end, obtaining the rID of the communication end in the autonomous domain according to the mapping relation between the HID and the rID of the communication end, and building communication with the communication end by the communication source end according to the rID of the communication end in the domain and the RID of the communication end the domain. The invention also discloses a system for interconnecting networks in domains and between domains. The routing between the domains is independent from an addressed mode in the domain and details of a routing protocol through the method and the system, and integral interconnection of a heterogeneous network is implemented.

Owner:THE PLA INFORMATION ENG UNIV

Data speculation based on addressing patterns identifying dual-purpose register

InactiveUS7024537B2Memory adressing/allocation/relocationDigital computer detailsGeneral purposeProcessor register

Owner:GLOBALFOUNDRIES INC

System and method for linking speculative results of load operations to register values

InactiveUS7028166B2Digital computer detailsConcurrent instruction executionProcessor registerParallel computing

A system may include a memory file, which includes an entry configured to store a first addressing pattern and a first tag, and an execution core coupled to the memory file. The memory file may be configured to compare the first addressing pattern included in the entry to a second addressing pattern of a load operation. If the second addressing pattern matches the first addressing pattern stored in the entry, the memory file is configured to link a data value identified by the first tag to a speculative result of the load operation. The execution core is configured to access the speculative result when executing a second operation that is dependent on the load operation.

Owner:GLOBALFOUNDRIES INC

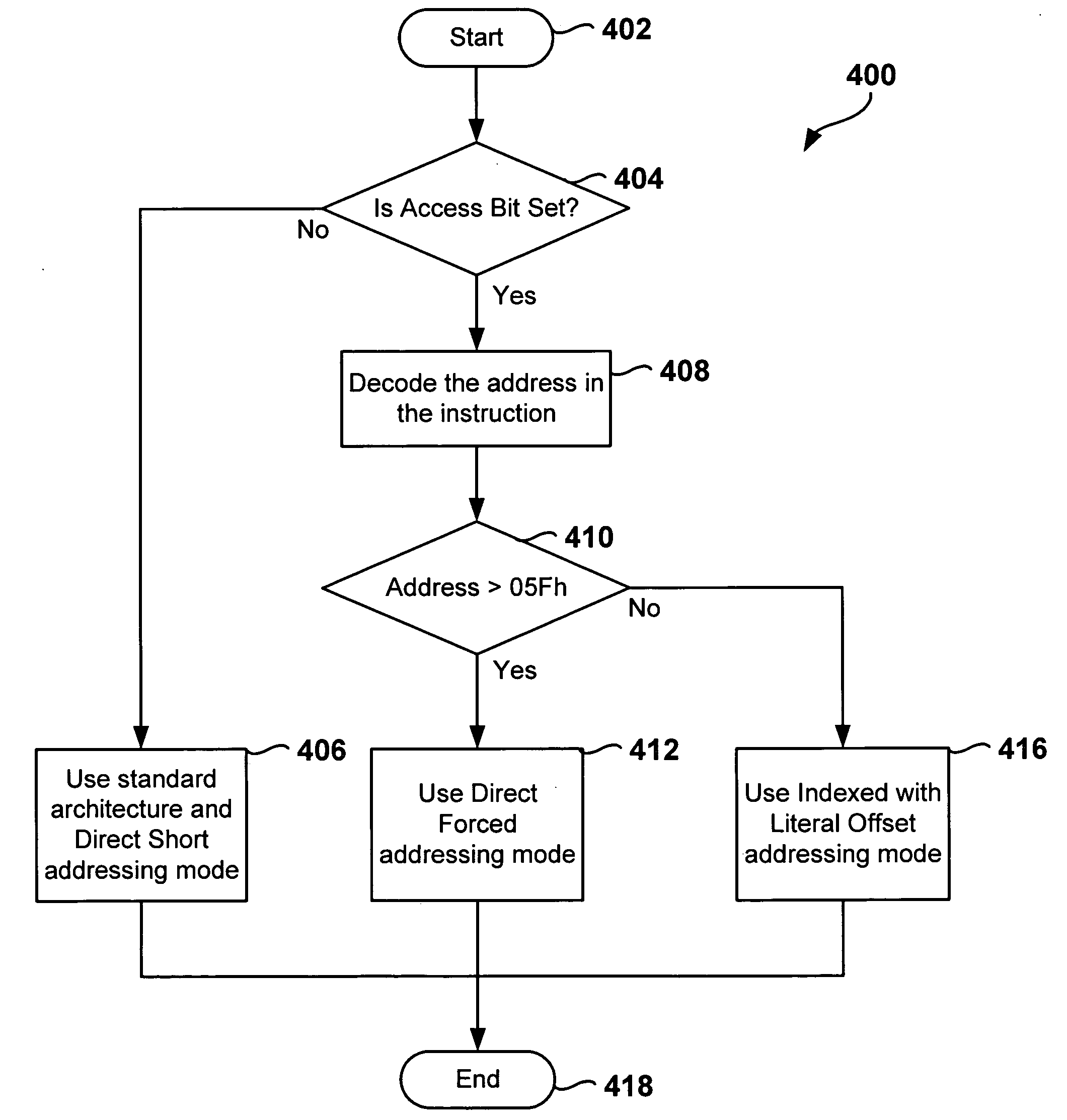

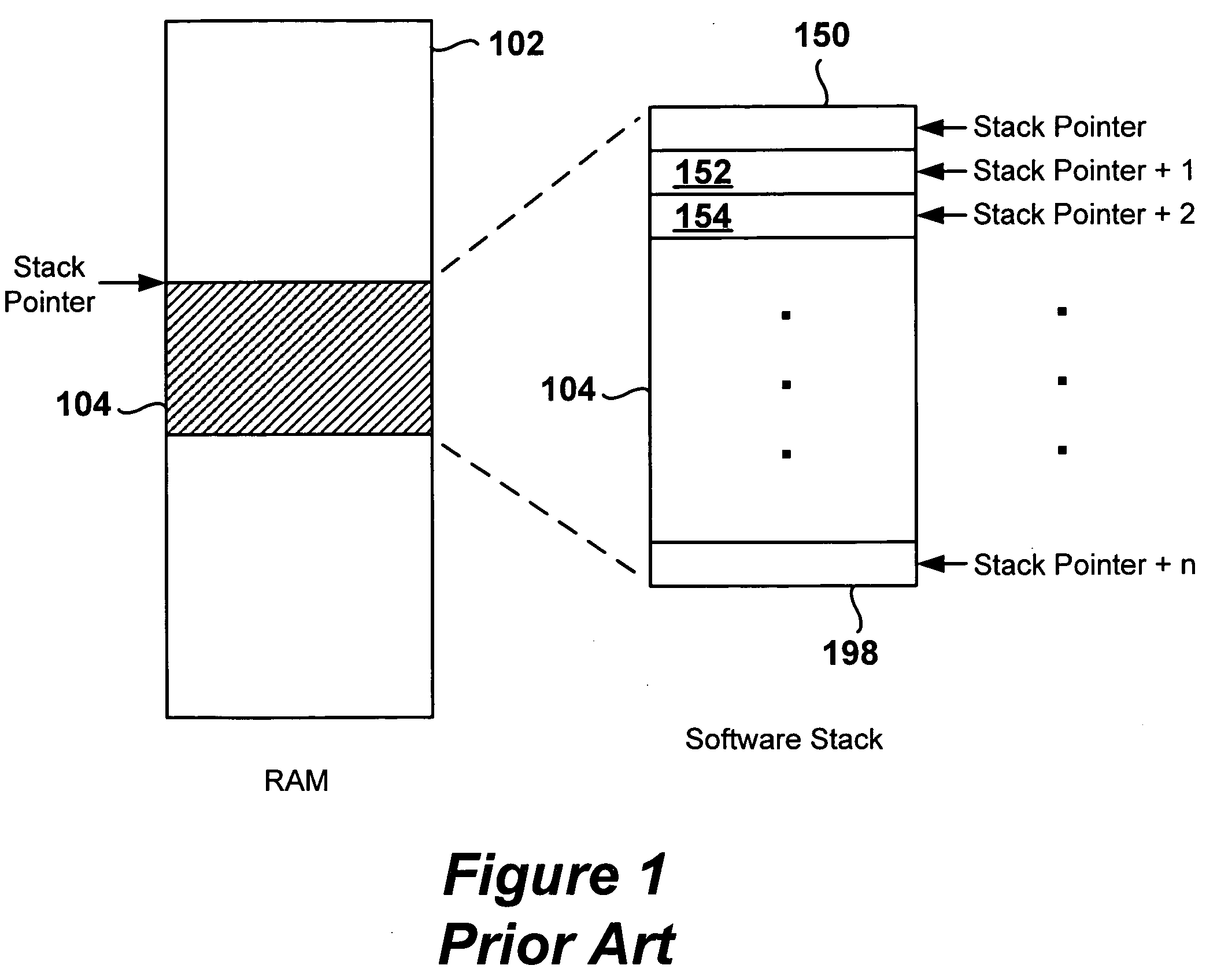

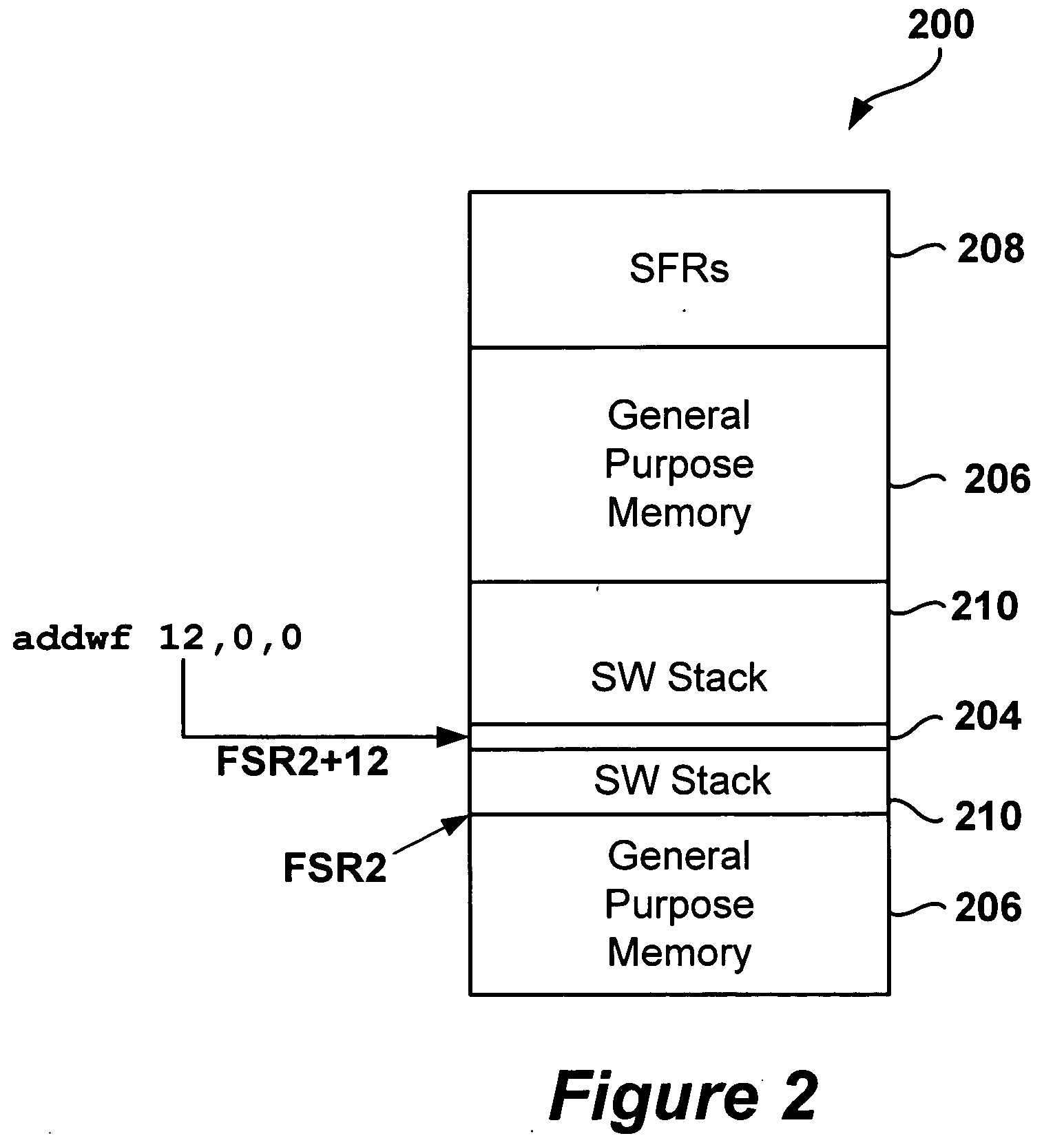

Method and system for fast access to stack memory

ActiveUS20050091471A1Memory adressing/allocation/relocationDigital computer detailsRandom access memoryCombined use

A method, system and apparatus are providing fast access to memory in a stack. The system and apparatus include an address bit, a stack pointer, and fast access random access memory (“RAM”). The method provides that, when a first address mode is used in conjunction with the address bit and the stack pointer, the location of the access RAM can be shifted in order to achieve an index of literal offset address mode.

Owner:MICROCHIP TECH INC

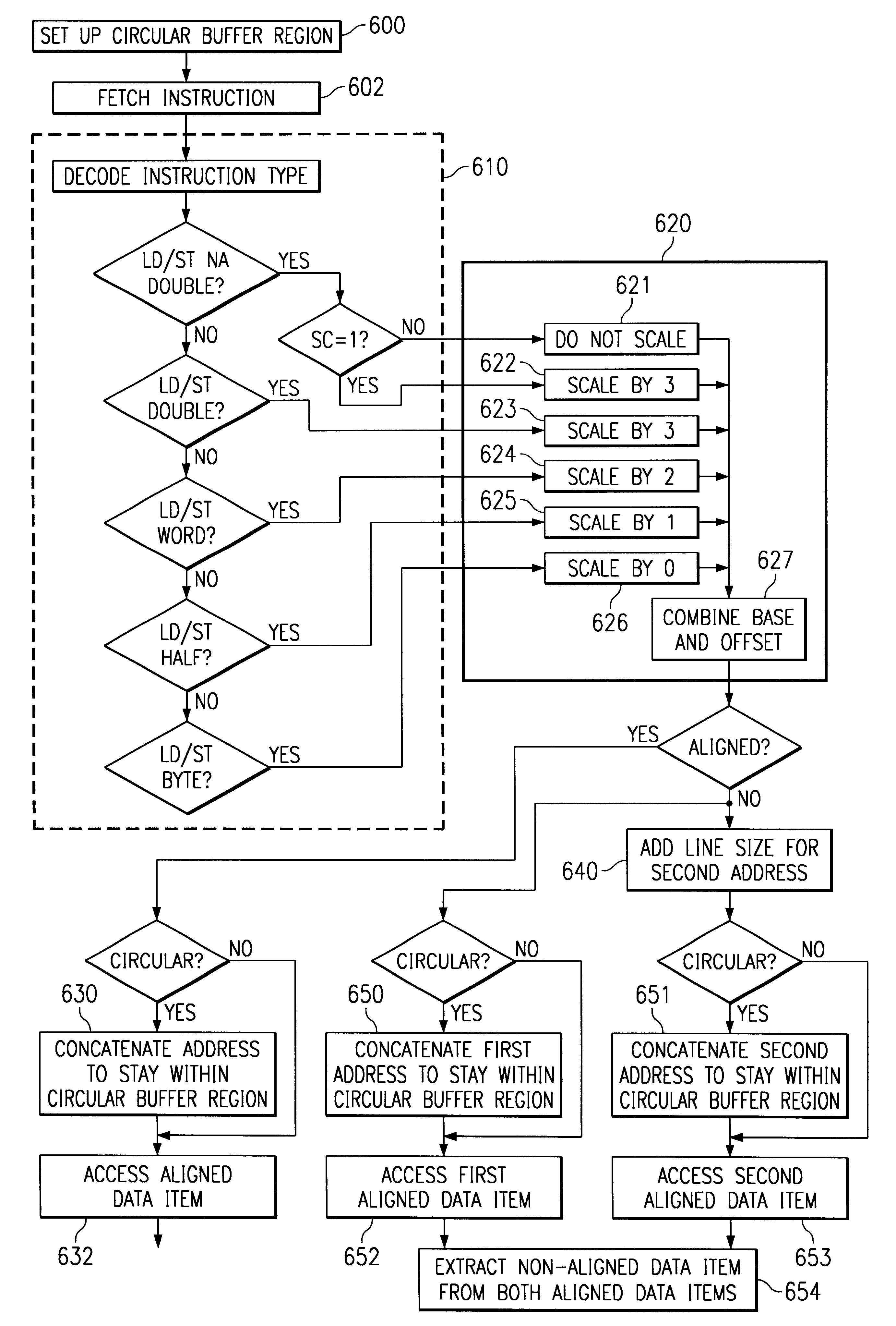

Microprocessor with non-aligned circular addressing

A data processing system having a central processing unit (CPU) with address generation circuitry for accessing a circular buffer region in a non-aligned manner is provided. The CPU has an instruction set architecture that is optimized for intensive numeric algorithm processing. The CPU has dual load / store units connected to dual memory ports of a memory controller. The CPU can execute two aligned data transfers each having a length of one byte, two bytes, four bytes, or eight bytes in parallel by executing two load / store instructions. The CPU can also execute a single non-aligned data transfer having a length of four bytes or eight bytes by executing a non-aligned load / store instruction that utilizes both memory ports. A data transfer address for each load / store instruction is formed by fetching the instruction (600), decoding the instruction (610) to determine instruction type, transfer data size, addressing mode and scaling selection. For a non-aligned instruction, after selectively scaling (620) an offset provided by the instruction and combining the selectively scaled offset with a base address value the resultant address is then augmented (640) by a line size associated with the instruction. For circular addressing mode, both the resultant address and the augmented address are bounded (650, 651) to stay within the circular buffer region and two aligned data items are accessed in parallel (652, 653) and a non-aligned data item is extracted (654) from the two aligned data items, such that the non-aligned data item wraps around the boundary of the circular buffer region.

Owner:TEXAS INSTR INC

Data speculation based on addressing patterns identifying dual-purpose register

InactiveUS20040143721A1Digital computer detailsConcurrent instruction executionGeneral purposeProcessor register

A system may include a memory file and an execution core. The memory file may include an entry configured to store an addressing pattern and a tag. If an addressing pattern of a memory operation matches the addressing pattern stored in the entry, the memory file may be configured to link a data value identified by the tag to a speculative result of the memory operation. The addressing pattern of the memory operation includes an identifier of a logical register, and the memory file may be configured to predict whether the logical register is being specified as a general purpose register or a stack frame pointer register in order to determine whether the addressing pattern of the memory operation matches the addressing pattern stored in the entry. The execution core may be configured to access the speculative result when executing another operation that is dependent on the memory operation.

Owner:GLOBALFOUNDRIES INC

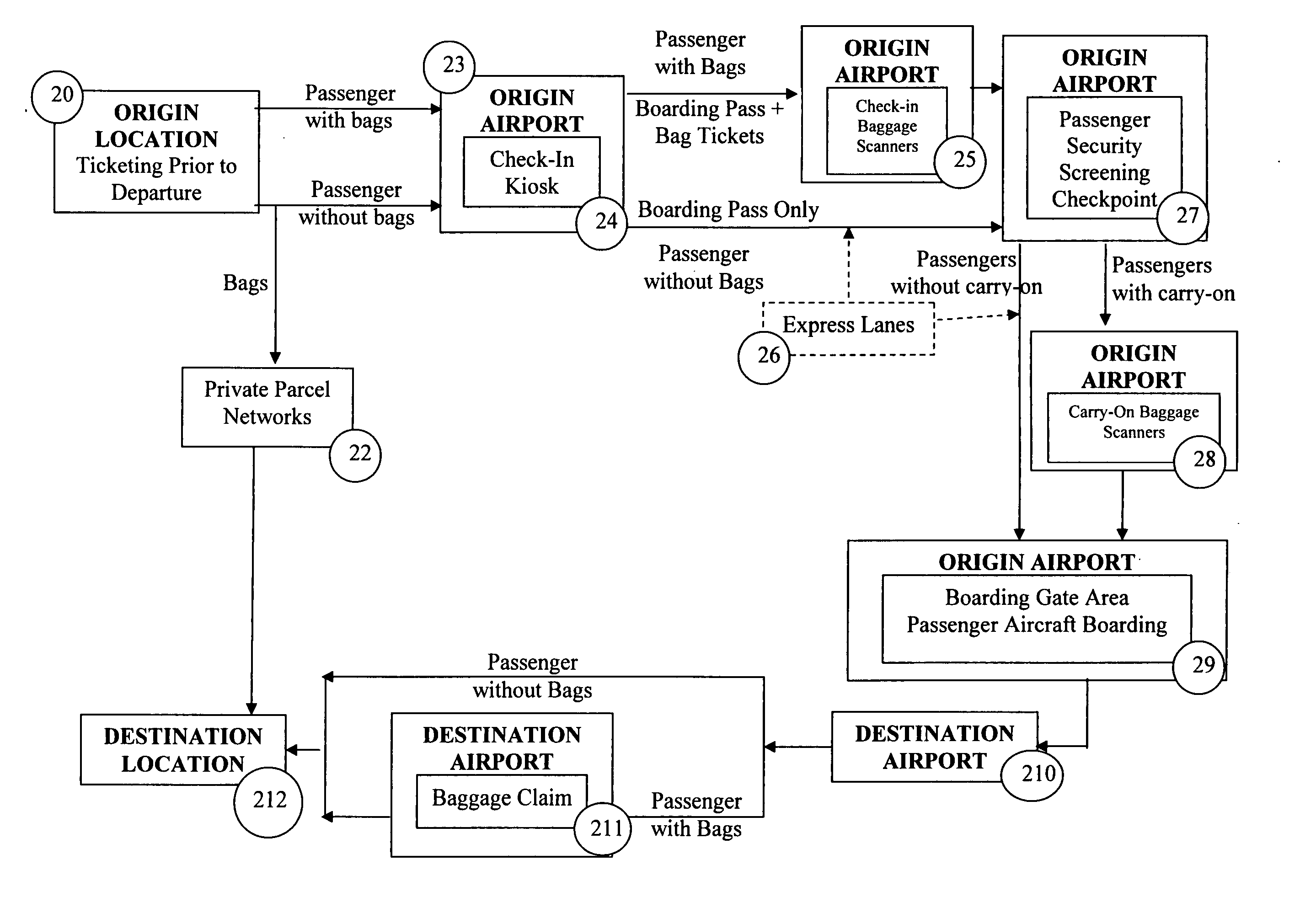

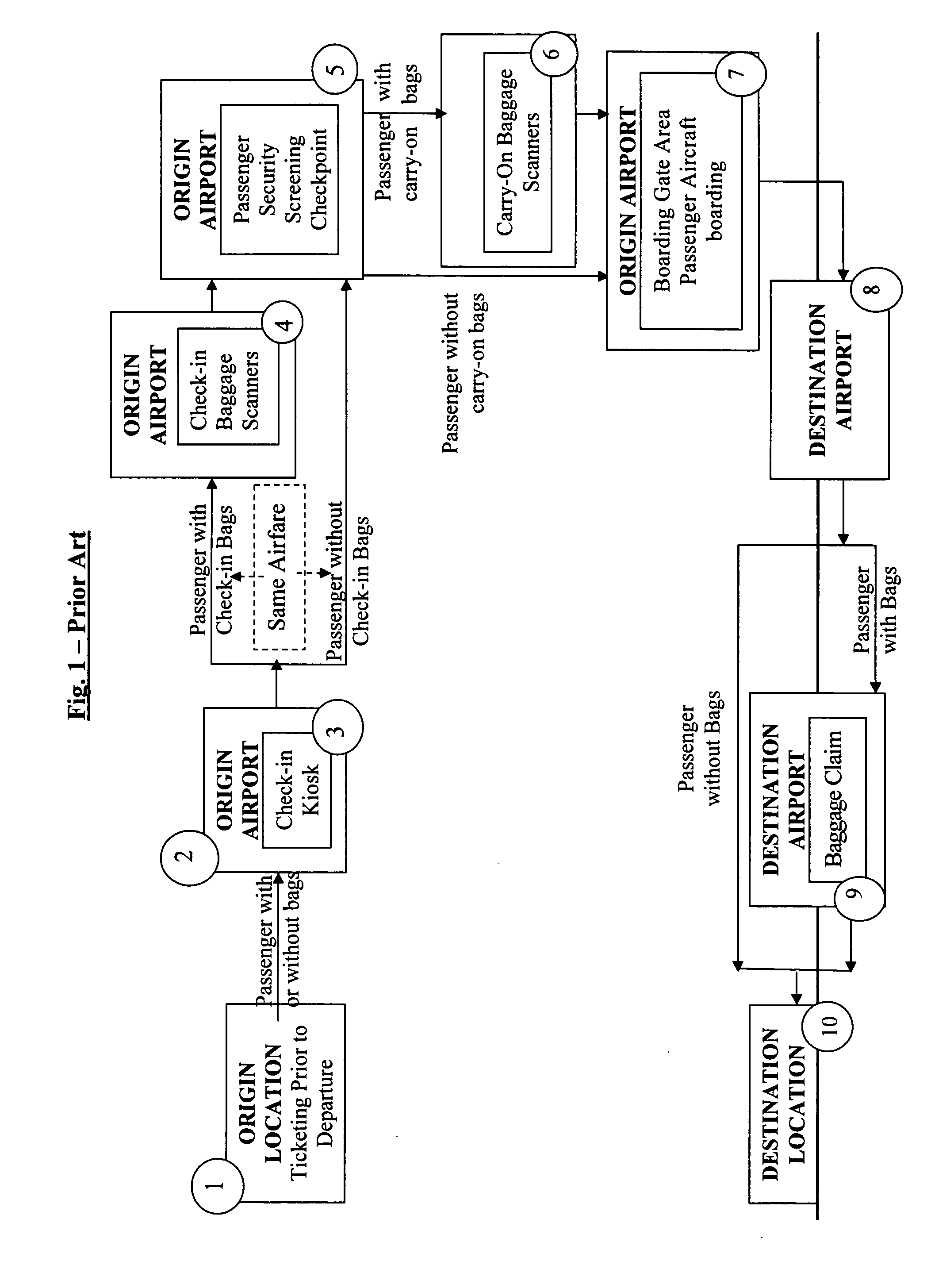

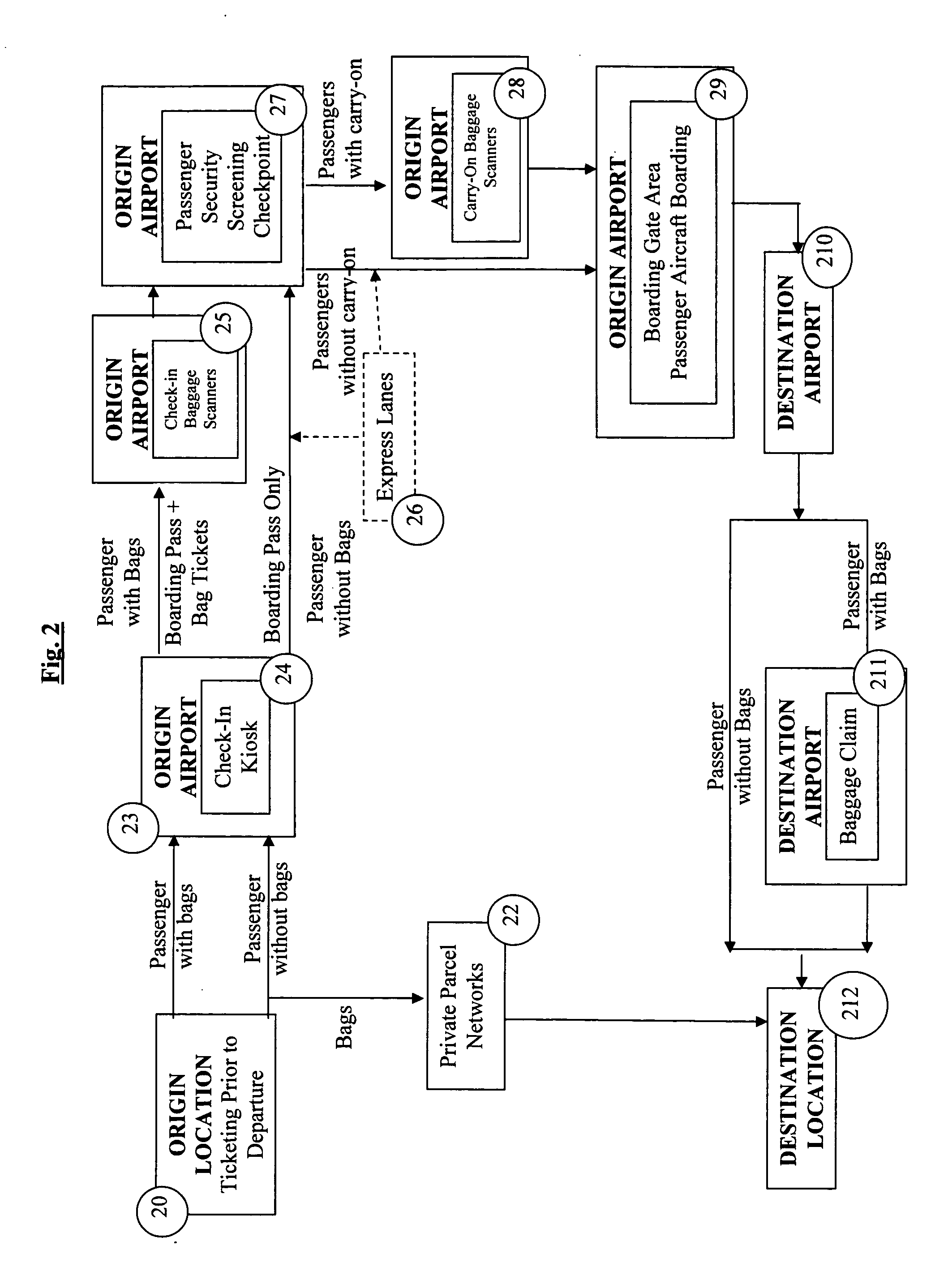

System and method for unbundling baggage costs from airfare prices

ActiveUS20050251430A1Encourage useImprove securityElectric signal transmission systemsDigital data processing detailsOnline bookingComputer science

A system and method is provided for categorizing airline passengers traveling with and without baggage and unbundling the baggage costs associated with the airfare to encourage separate parcel service use. In one embodiment, based on information from an online booking system, the traveler is allowed to choose from a variety of options addressing modes of baggage handling, and an online routine determines the associated costs for the options chosen, providing travel rates that vary from the typical base airfare.

Owner:JINDEL SATISH

Method of selecting a transmission frequency of a one-way wireless remote control device

InactiveUS20110050451A1Electric signal transmission systemsElectric controllersRemote controlControl system

A radio-frequency (RF) load control system includes both two-way and one-way (e.g., transmit-only) remote control devices, and provides a simple, reliable process for configuring the one-way devices into the system. The one-way device may be programmed to operate at one of a predetermined number of radio frequencies as part of a frequency-selection procedure, during which, the one-way device transmits a test command to a signal repeater of the system. If the test command is transmitted at the same frequency as the repeater, the repeater emits an audible beep to inform the user that the remote control is transmitting at the appropriate frequency. To associate the two-way devices with the system, the signal repeater streams an “enter address mode” command. To allow the one-way device to be associated with the system, the signal repeater pauses the transmission of the enter address mode command to allow the one-way device to transmit an activation request message to the signal repeater.

Owner:LUTRON TECH CO LLC

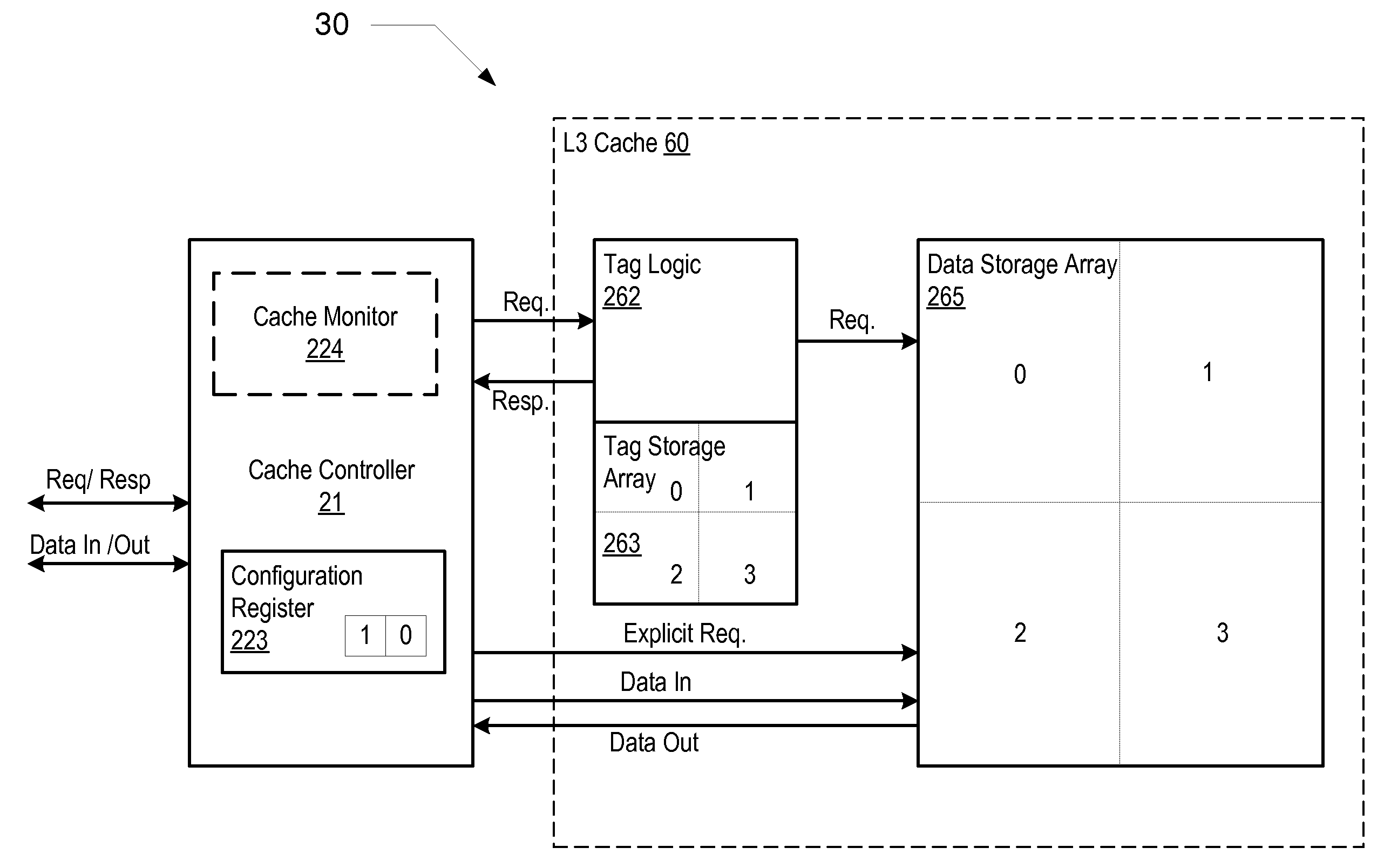

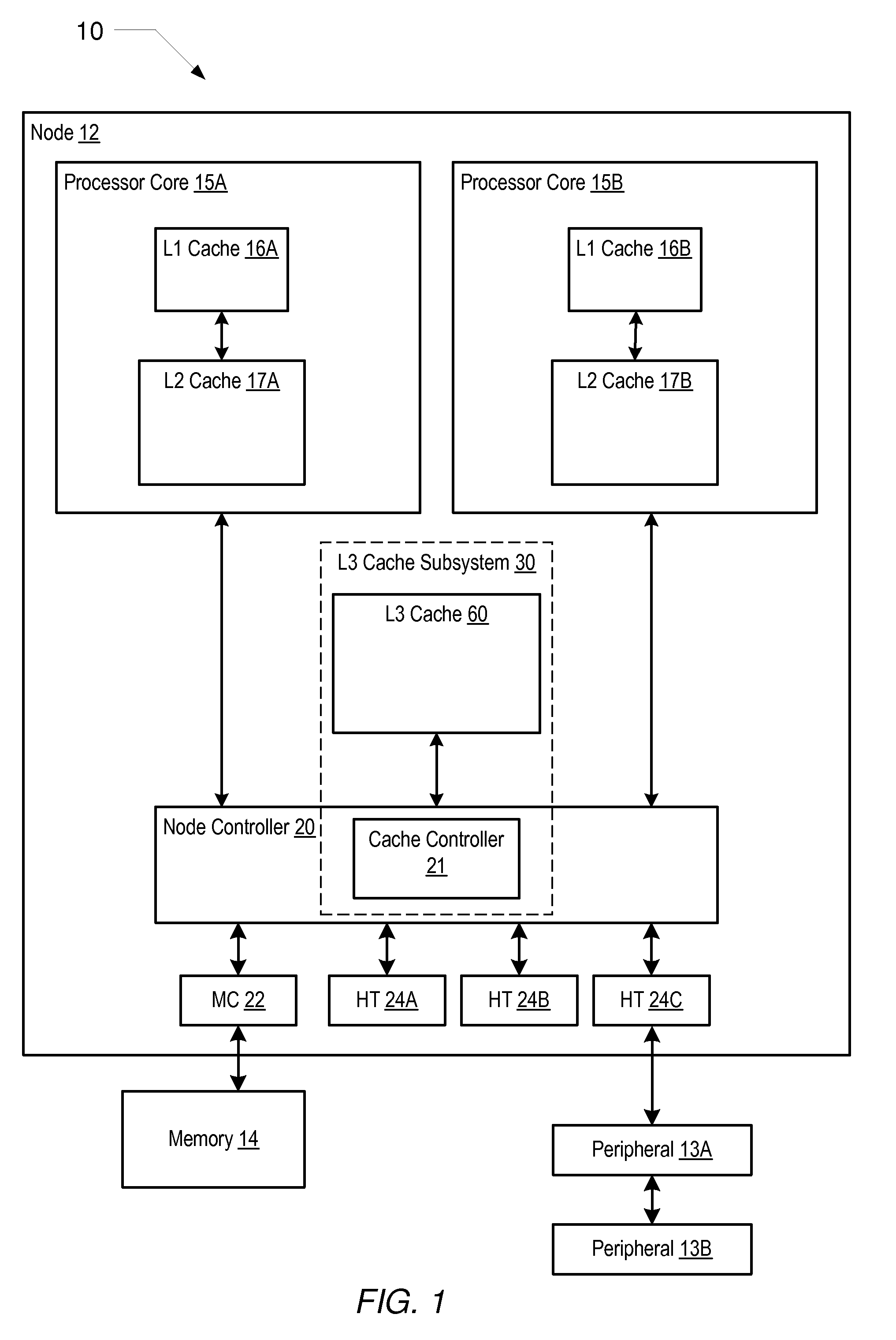

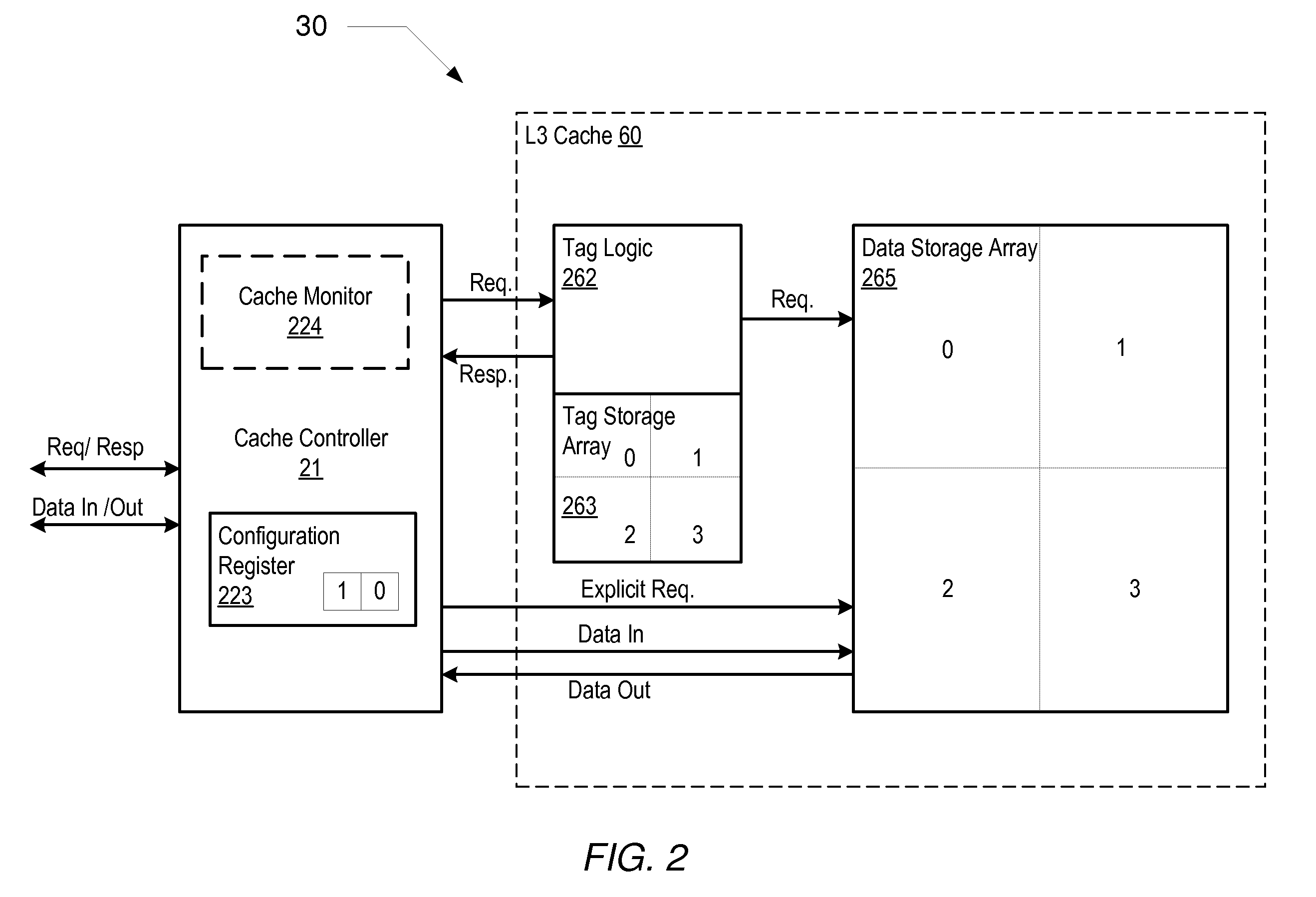

Cache memory having configurable associativity

InactiveUS20090006756A1Access be disabledMemory architecture accessing/allocationEnergy efficient ICTParallel computingData store

A processor cache memory subsystem includes a cache memory having a configurable associativity. The cache memory may operate in a fully associative addressing mode and a direct addressing mode with reduced associativity. The cache memory includes a data storage array including a plurality of independently accessible sub-blocks for storing blocks of data. For example each of the sub-blocks implements an n-way set associative cache. The cache memory subsystem also includes a cache controller that may programmably select a number of ways of associativity of the cache memory. When programmed to operate in the fully associative addressing mode, the cache controller may disable independent access to each of the independently accessible sub-blocks and enable concurrent tag lookup of all independently accessible sub-blocks, and when programmed to operate in the direct addressing mode, the cache controller may enable independent access to one or more subsets of the independently accessible sub-blocks.

Owner:GLOBALFOUNDRIES INC

Fixed length memory to memory arithmetic and architecture for a communications embedded processor system

InactiveUS7047396B1Fast pipeline processingImprove performanceInstruction analysisGeneral purpose stored program computerMemory processingComputer architecture

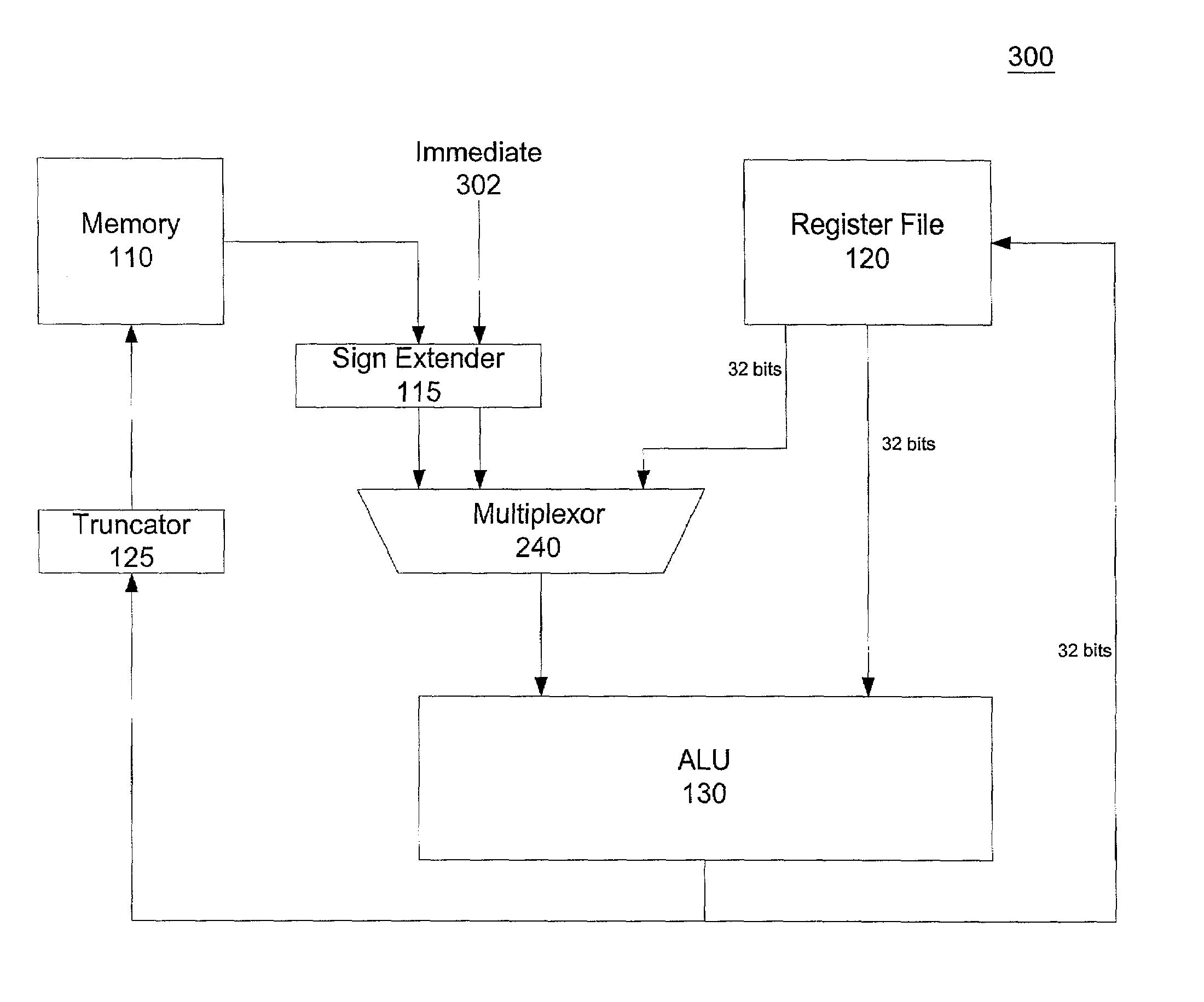

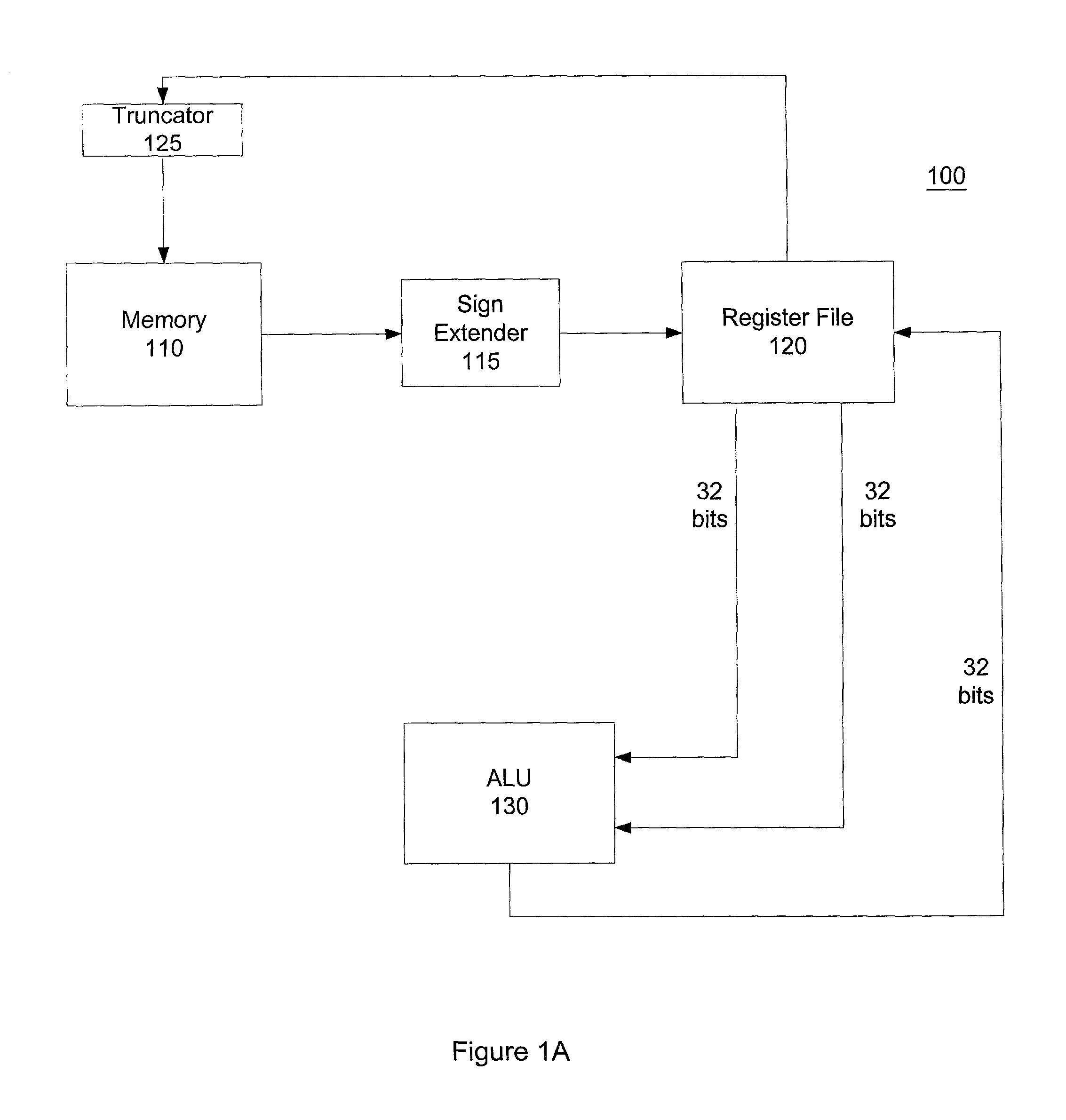

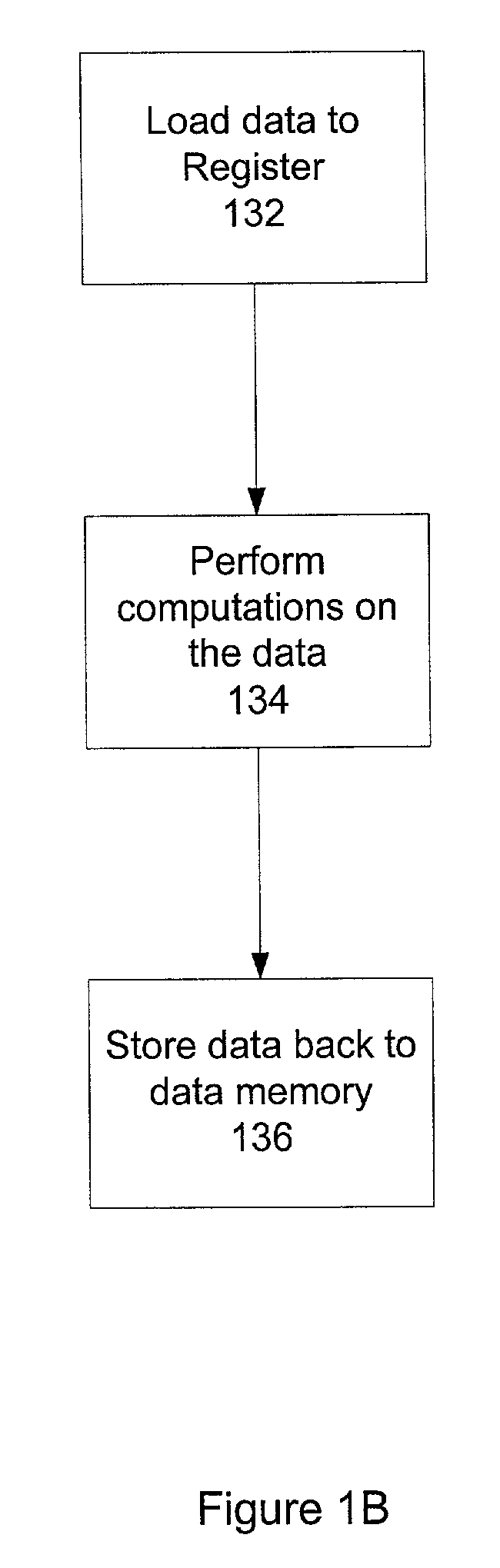

A method and system for fixed-length memory-to-memory processing of fixed-length instructions. Further, the present invention is a method and system for implementing a memory operand width independent of the ALU width. The arithmetic and register data are 32 bits, but the memory operand is variable in size. The size of the memory operand is specified by the instruction. Instructions in accordance with the present invention allow for multiple memory operands in a single fixed-length instruction. The instruction set is small and simple, so the implementation is lower cost than traditional processors. More addressing modes are provided for, thus creating a more efficient code. Semaphores are implemented using a single bit. Shift-and-merge instructions are used to access data across word boundaries.

Owner:MAYFIELD XI +8

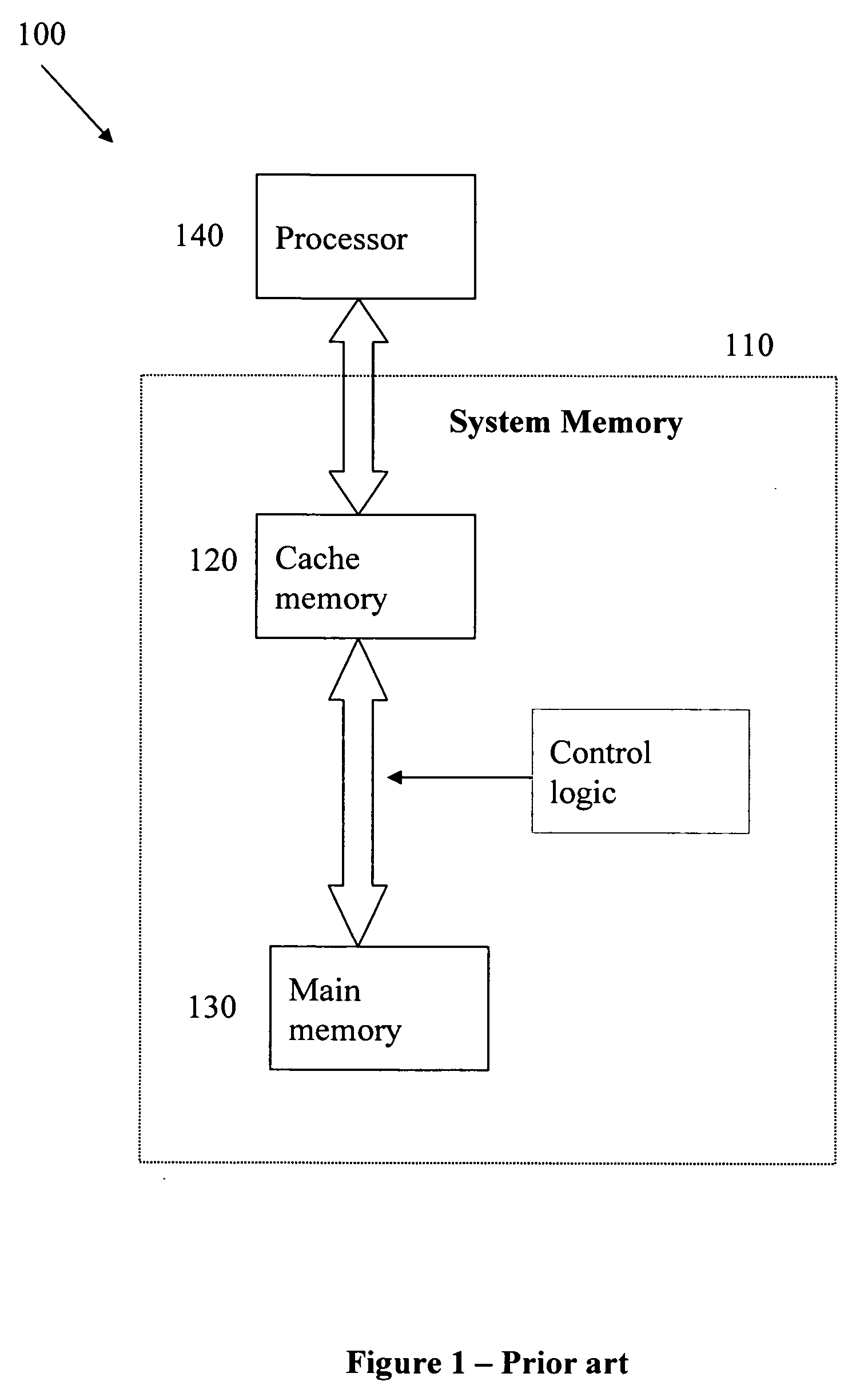

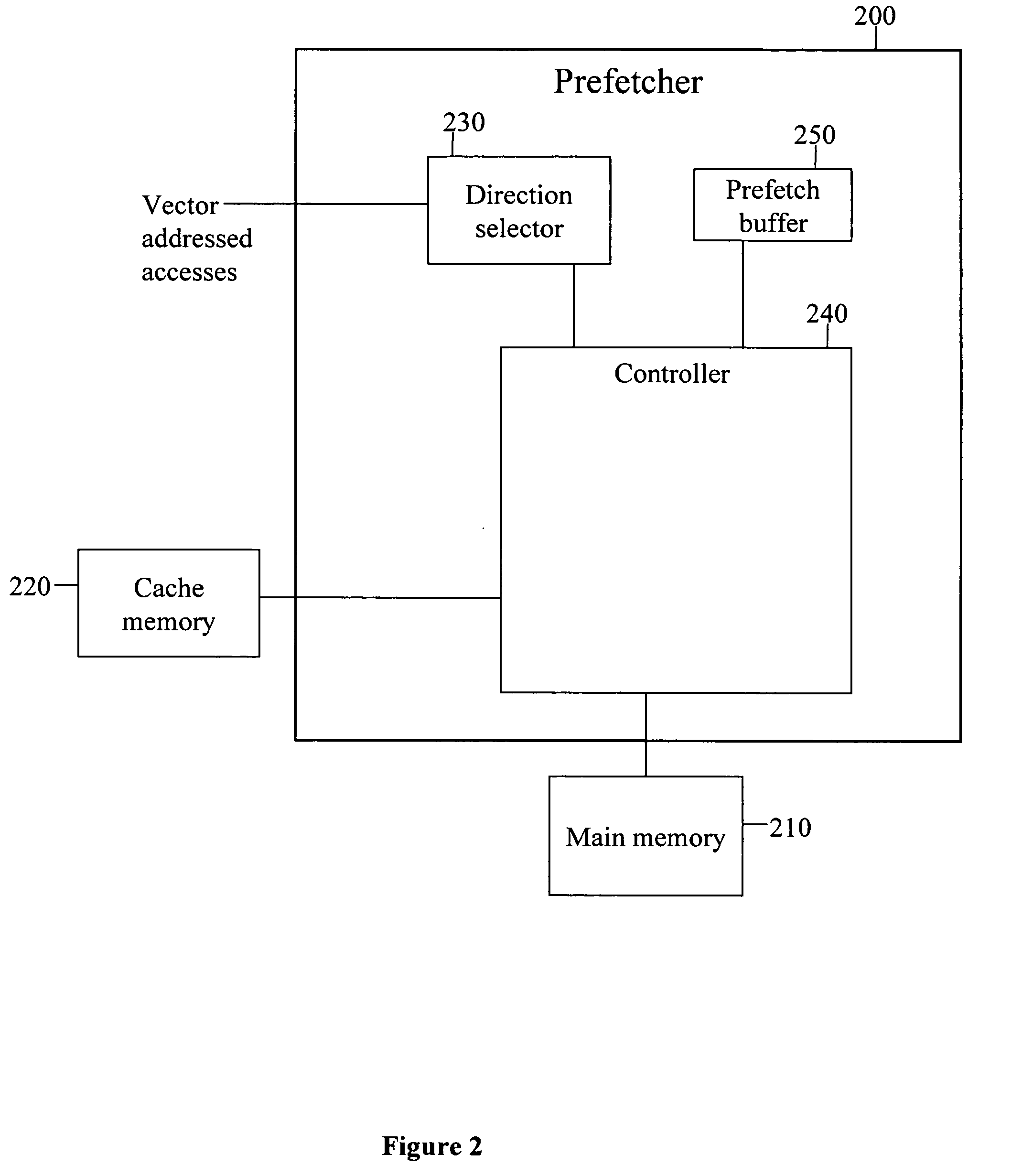

Cache memory prefetcher

InactiveUS20050198439A1Memory architecture accessing/allocationMemory adressing/allocation/relocationMemory addressParallel computing

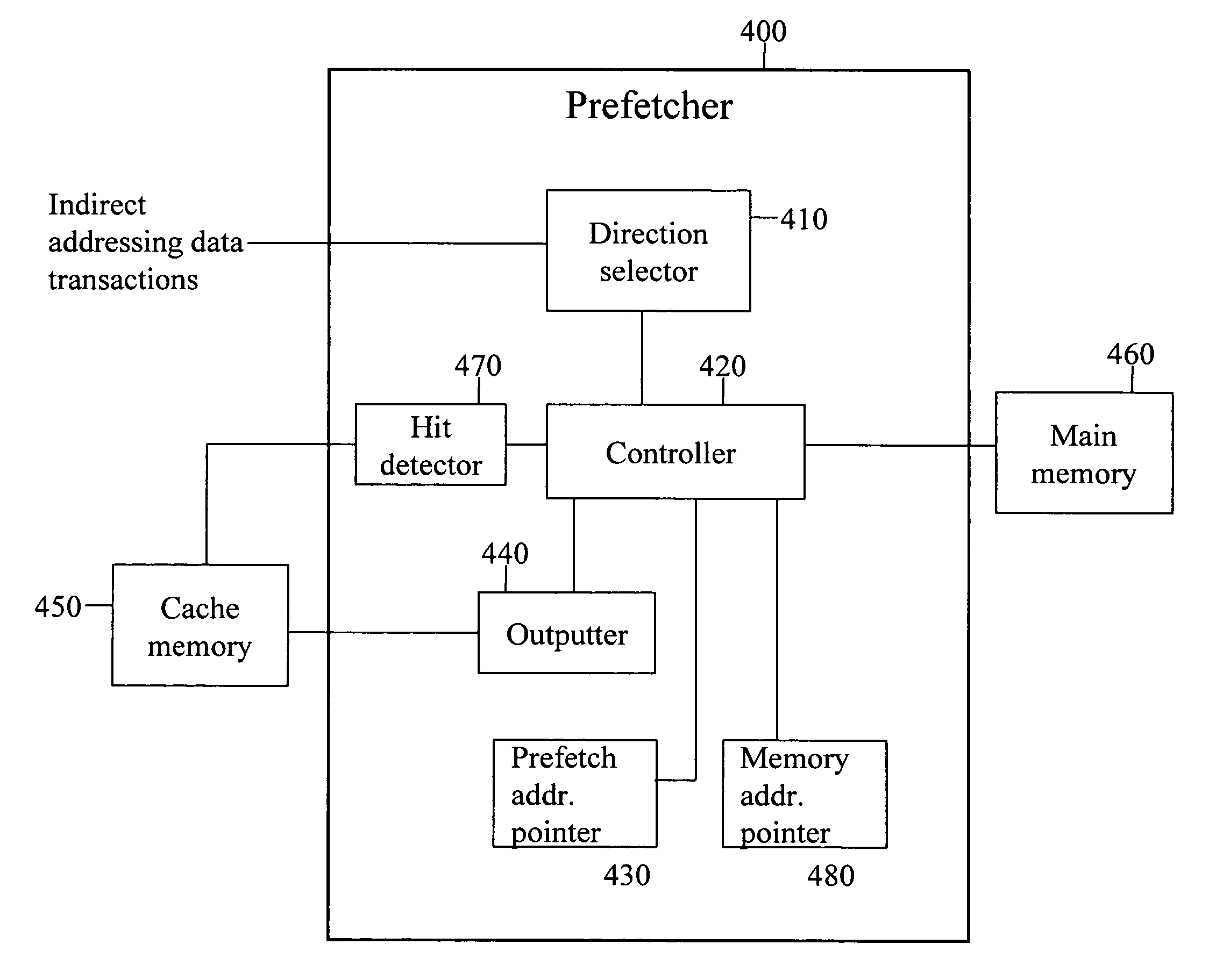

A prefetcher performs advance retrieval of data from a main memory, and places the retrieved data in an intermediate memory. The main memory is accessed by vector addressing, in which the vector access instruction includes a main memory address and a direction indicator. Main memory data is cached in an associated cache memory. The prefetcher contains a direction selector and a controller. The direction selector selects a direction of data access according to the direction indicator of a single data access transaction. The direction indicator is supplied by the processor accessing the main memory, and incorporates the processor's internal knowledge of the expected direction of future data accesses. The controller retrieves data items from the main memory, in the direction of access selected by the direction selector, and places the retrieved data items in the intermediate memory.

Owner:ANALOG DEVICES INC

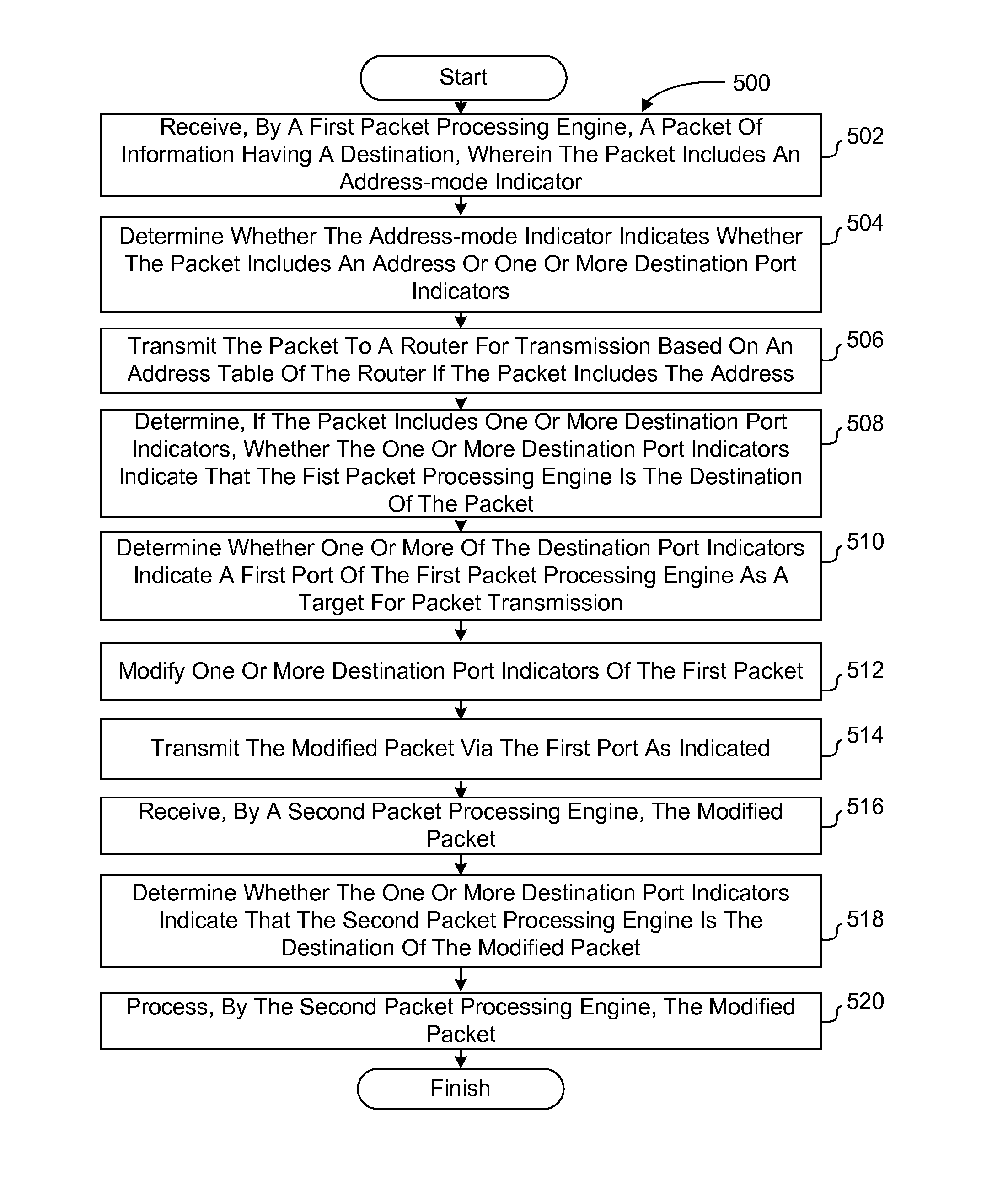

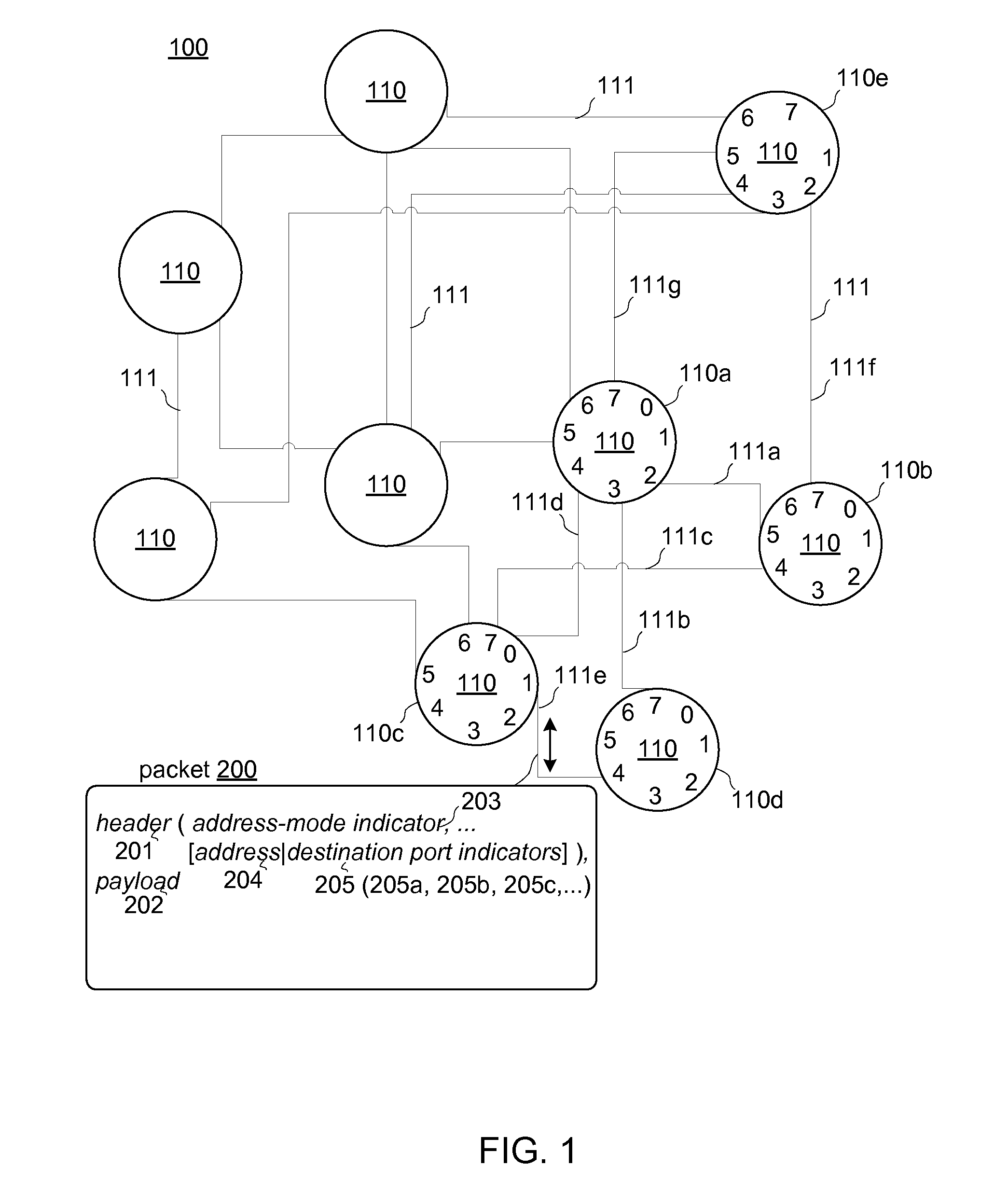

Systems and methods for packet routing

ActiveUS20140204943A1Efficient and simple and flexible and scalableData switching by path configurationOperation modePacket routing

Systems and methods to route packets of information within an integrated circuit, across one or more boards, racks, blades, and / or chassis, and / or across a connected network of packet processing engines include various modes of operation. Packets are routed to their destination, for example an individual packet processing engine. The packets of information include address-mode indicators, one or more destination port indicators, and / or (long-distance) addresses.

Owner:FRIDAY HARBOR LLC

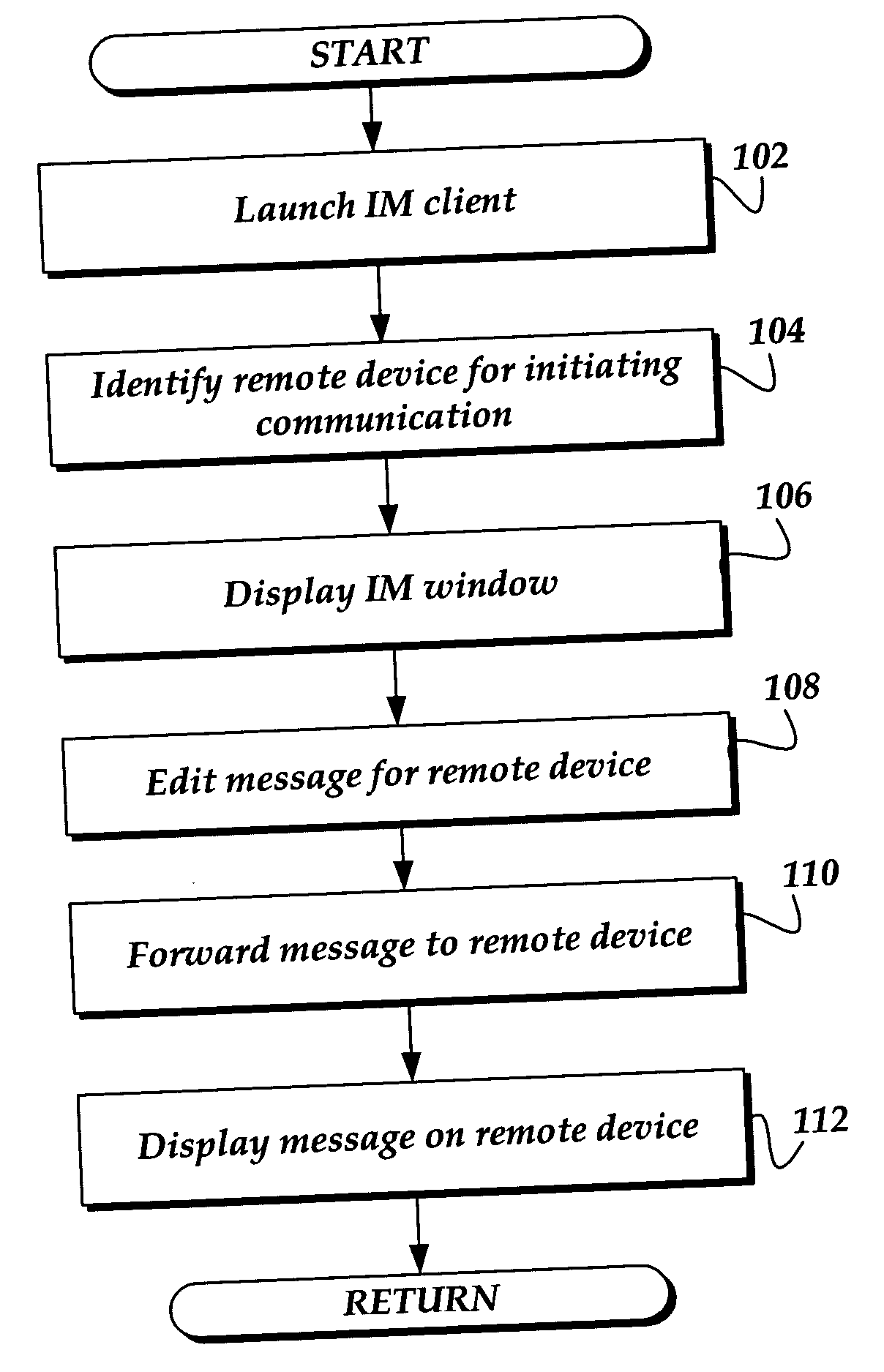

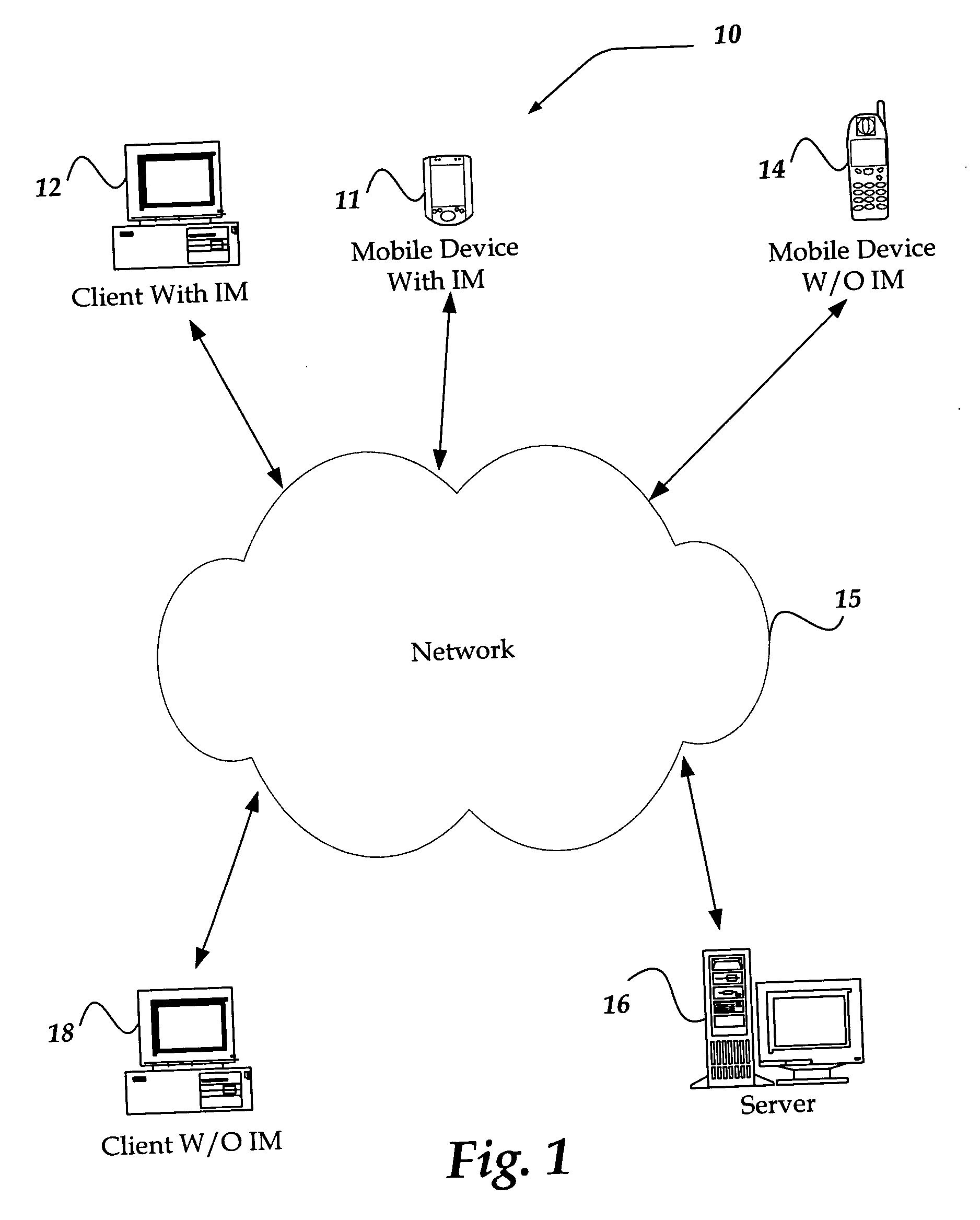

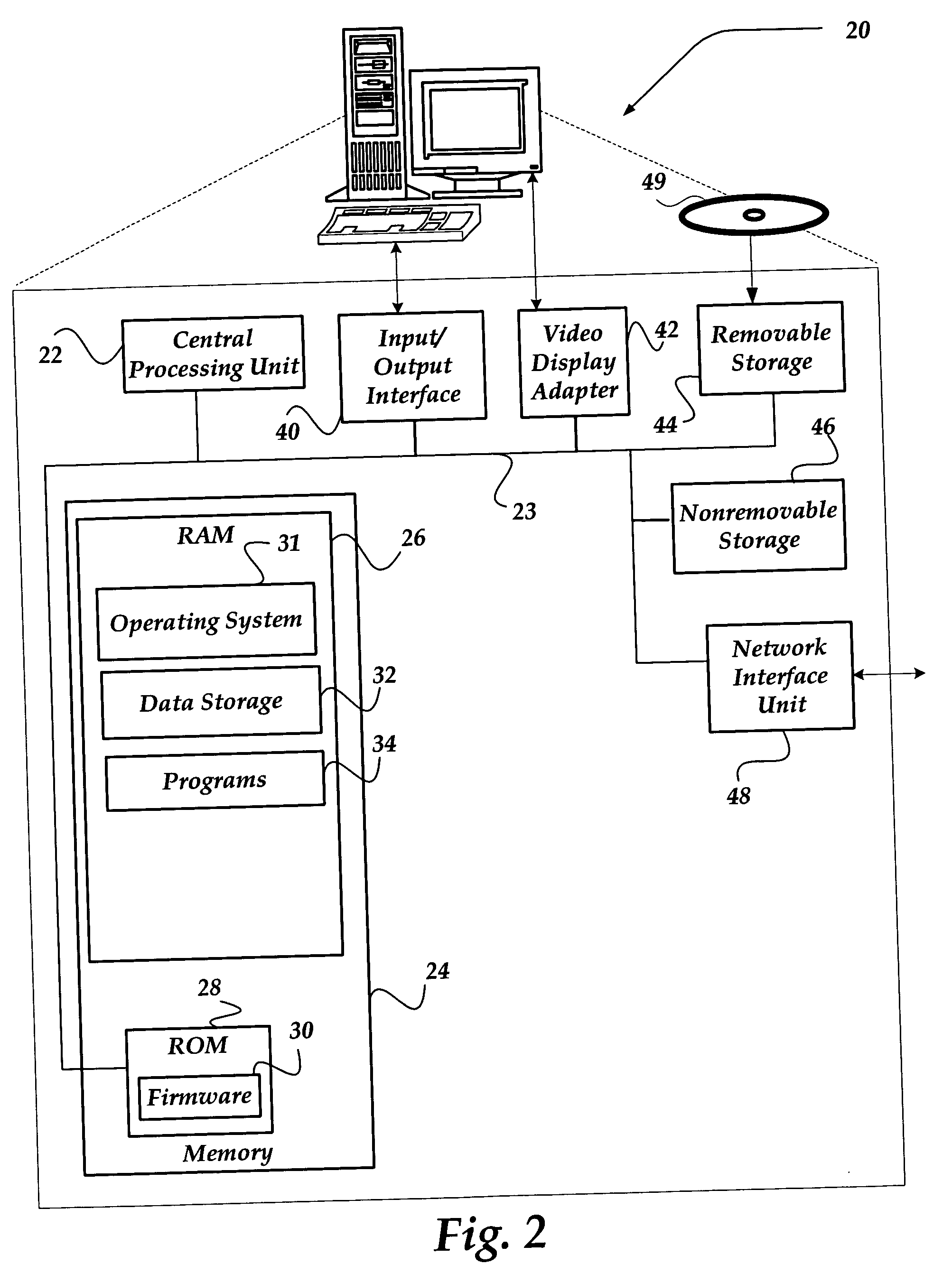

Establishing communication between a messaging client and a remote device

ActiveUS20070033255A1Automatic call-answering/message-recording/conversation-recordingMultiple digital computer combinationsCommunity associatedClient-side

A first device running a messaging application, such as an instant messaging (IM) application, engages in messaging communication with a remote device running a browsing application. The remote device user is not associated with the messaging network of the first device. The first device sends an instant message directed to the remote device. The remote device is addressed using a means other than the addressing means used in the IM community associated with the first device, such as the MSISDN number of the remote device. The message is processed so that it may be displayed on the remote device by way of the browsing application. The user of the remote device may reply to the message using the browsing application, in which case the reply message is processed and forwarded to the first device, where it is converted into the IM format for display within the IM application.

Owner:R2 SOLUTIONS

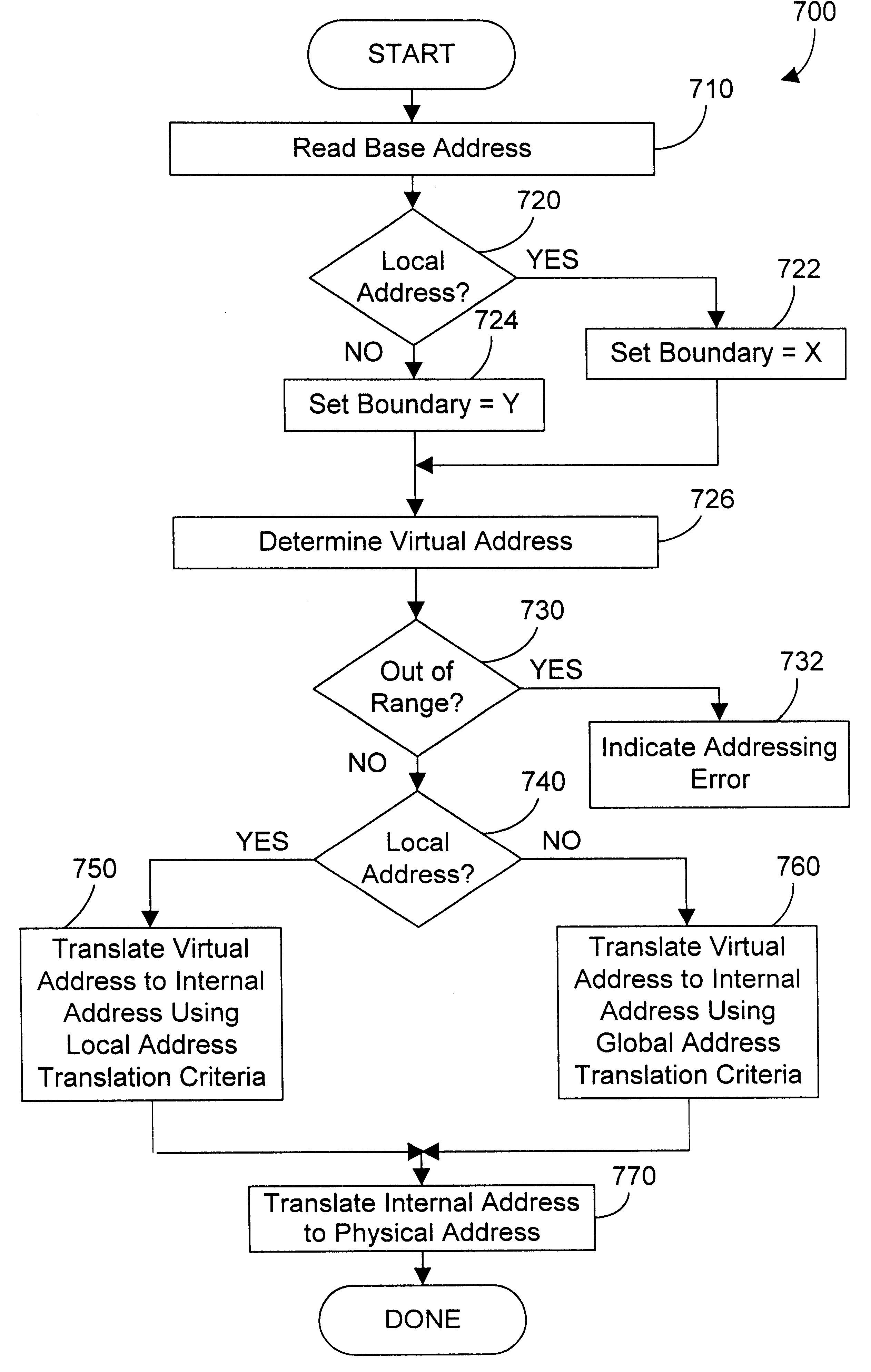

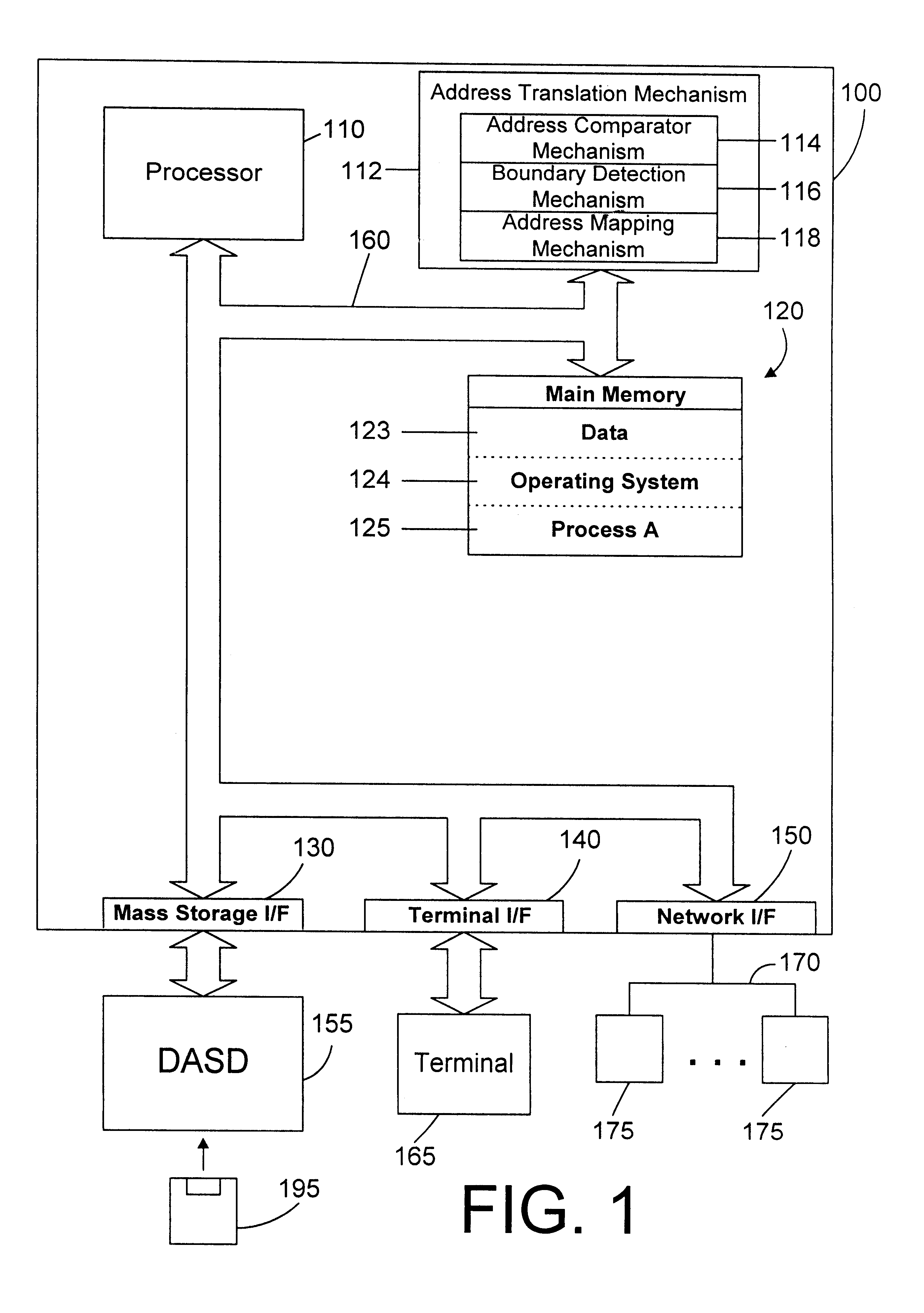

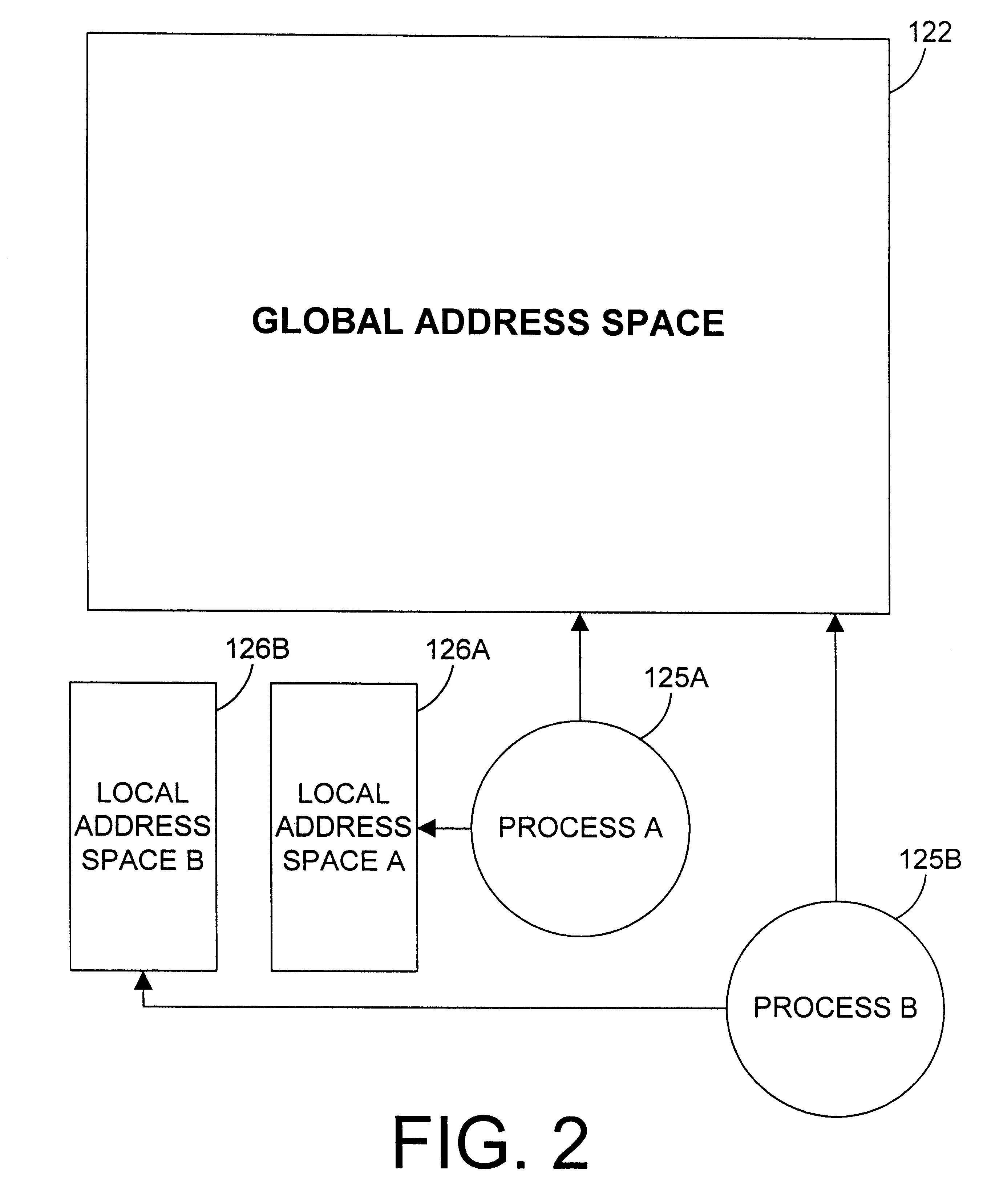

Apparatus and method for providing simultaneous local and global addressing with hardware address translation

InactiveUS6738889B2Good flexibilityMemory adressing/allocation/relocationDigital computer detailsGlobal address spaceParallel computing

An apparatus and method provide simultaneous local and global addressing capabilities. A global address space is defined that may be accessed by all processes. In addition, each process has a local address space that is local (and therefore available) only to that process. An address translation mechanism is implemented, preferably in hardware, to compare an address to defined addresses for local and global addressing and to detect when a virtual address computation result would go outside a boundary for the appropriate addressing scheme. The address translation mechanism maps a virtual address to a corresponding physical address, and uses different criteria depending on whether the address is local or global. The address translation mechanism allows an instruction to operate on both local and global addresses by determining at run-time which address space is referenced, and by performing the necessary translation and boundary checking for either global or local address space, whichever is accessed by the instruction. By providing both global and local addressing for the same instructions, the apparatus and method of the present invention provide great flexibility in addressing, allowing a computer program to benefit from the advantages of both addressing modes.

Owner:GOOGLE LLC

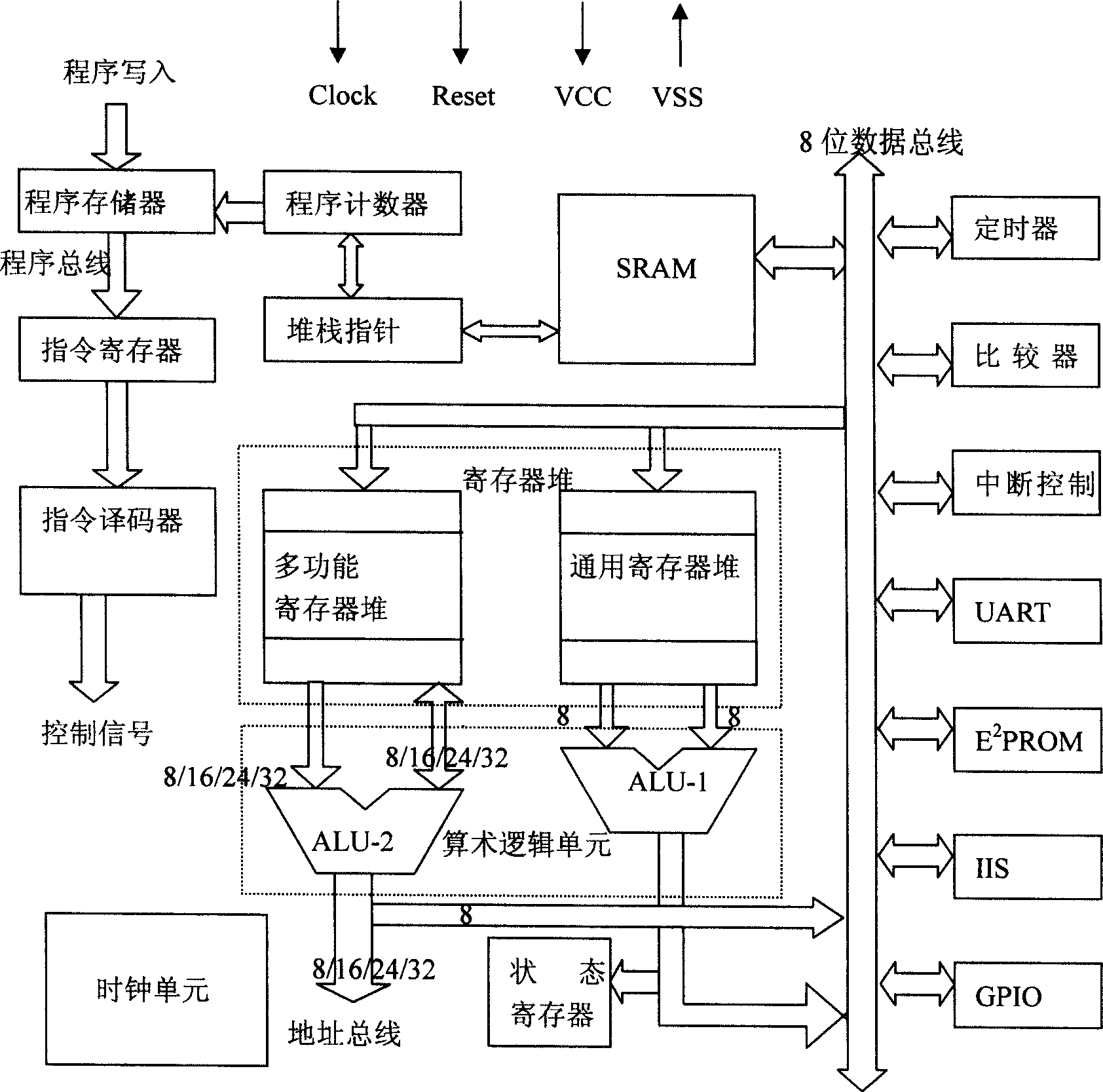

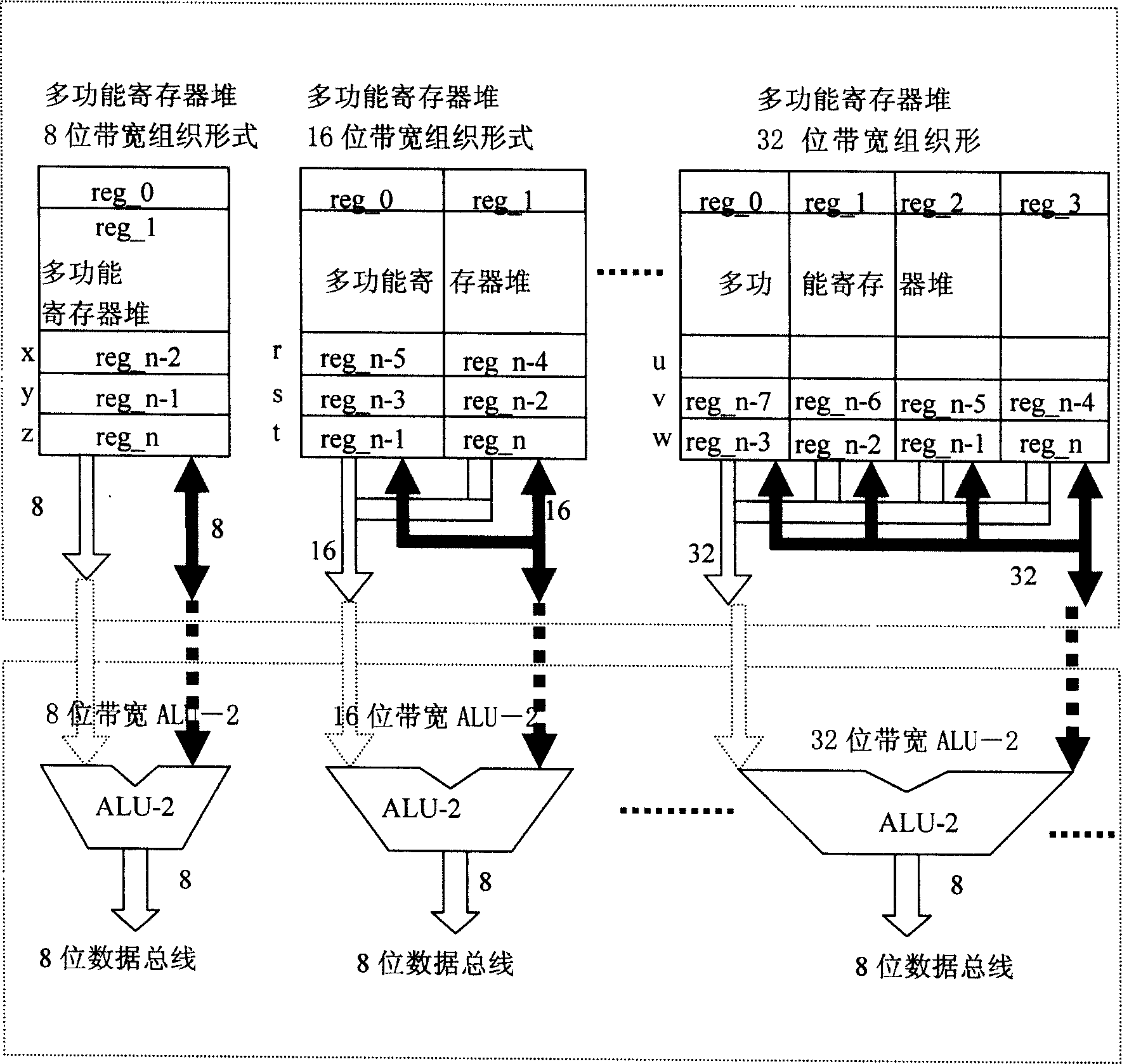

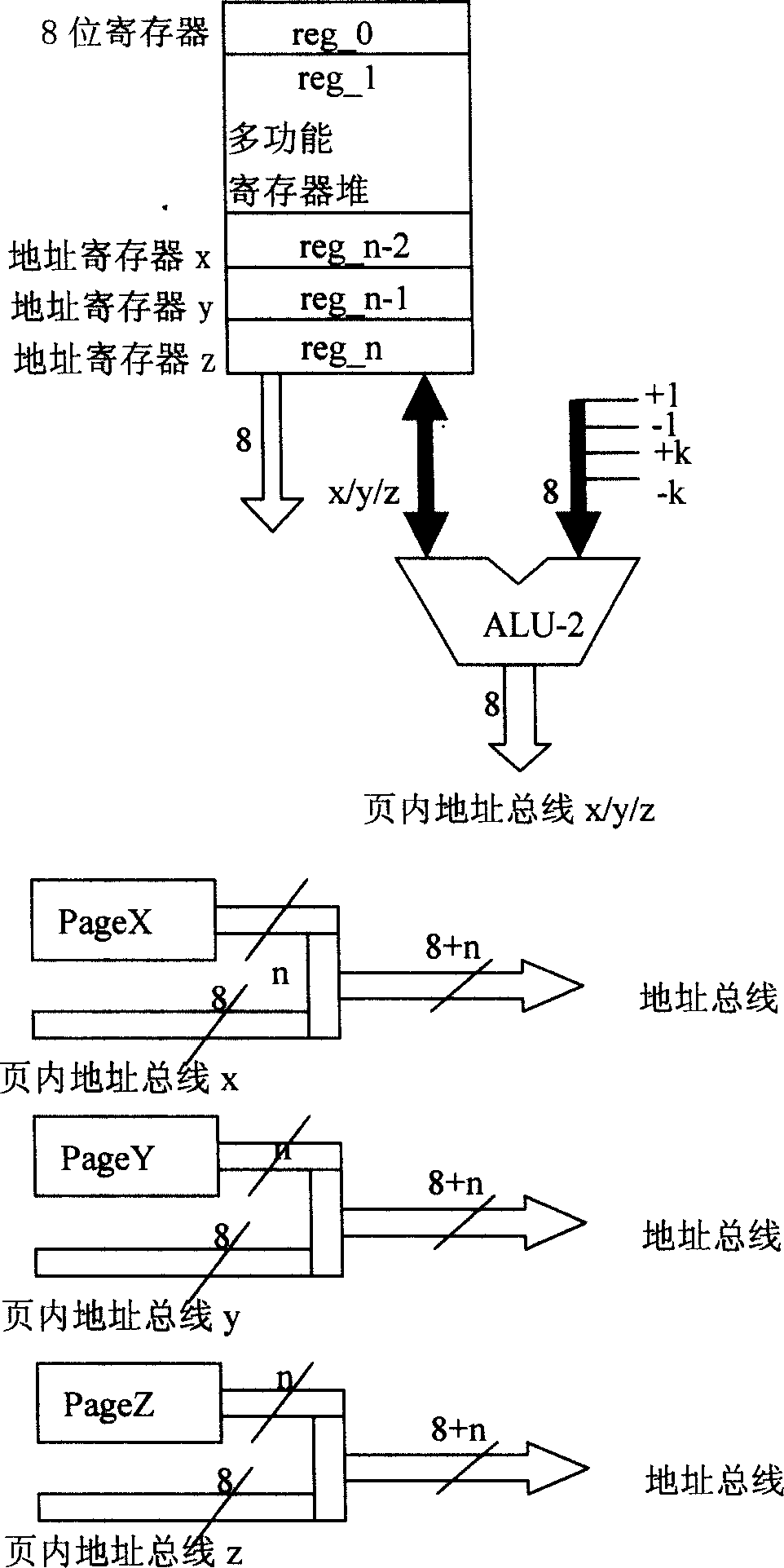

8-bit RISC microcontroller with double arithmetic logic units

InactiveCN1766834AMeet special application needsMeet application needsConcurrent instruction executionMemory systemsData spaceData treatment

The invention discloses a double arithmetic logic unit tamping instruction set 8 bit microcontroller. It adopts the current register pile and arithmetic logic unit ALU-1 of the 8 bit RISC structure and parallel connects with the multi-function register pile and arithmetic logic unit ALU-2, it arranges the bit holder and bit operating quoting device inside the order decoder of the initial RISC structure and the bite operator structure on the current arithmetic logic unit ALU-1, then it adds the operating function and the data processing function to the multi-byte data of the 8 bit microcontroller and provides the register address mode of the data space and amplifies the data address space by coupling the multi-function register pile and the arithmetic logic unit ALU-2.

Owner:XIDIAN UNIV

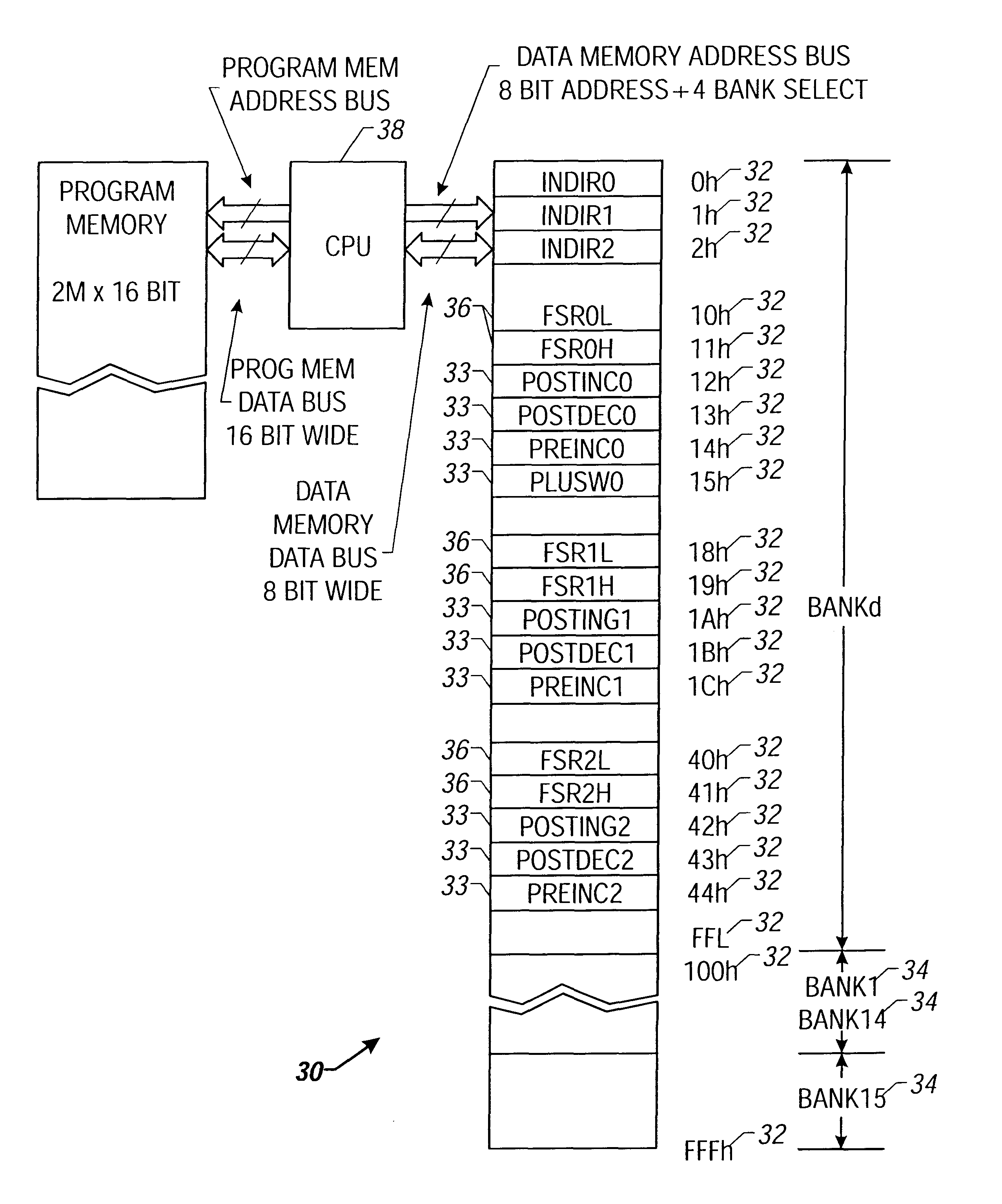

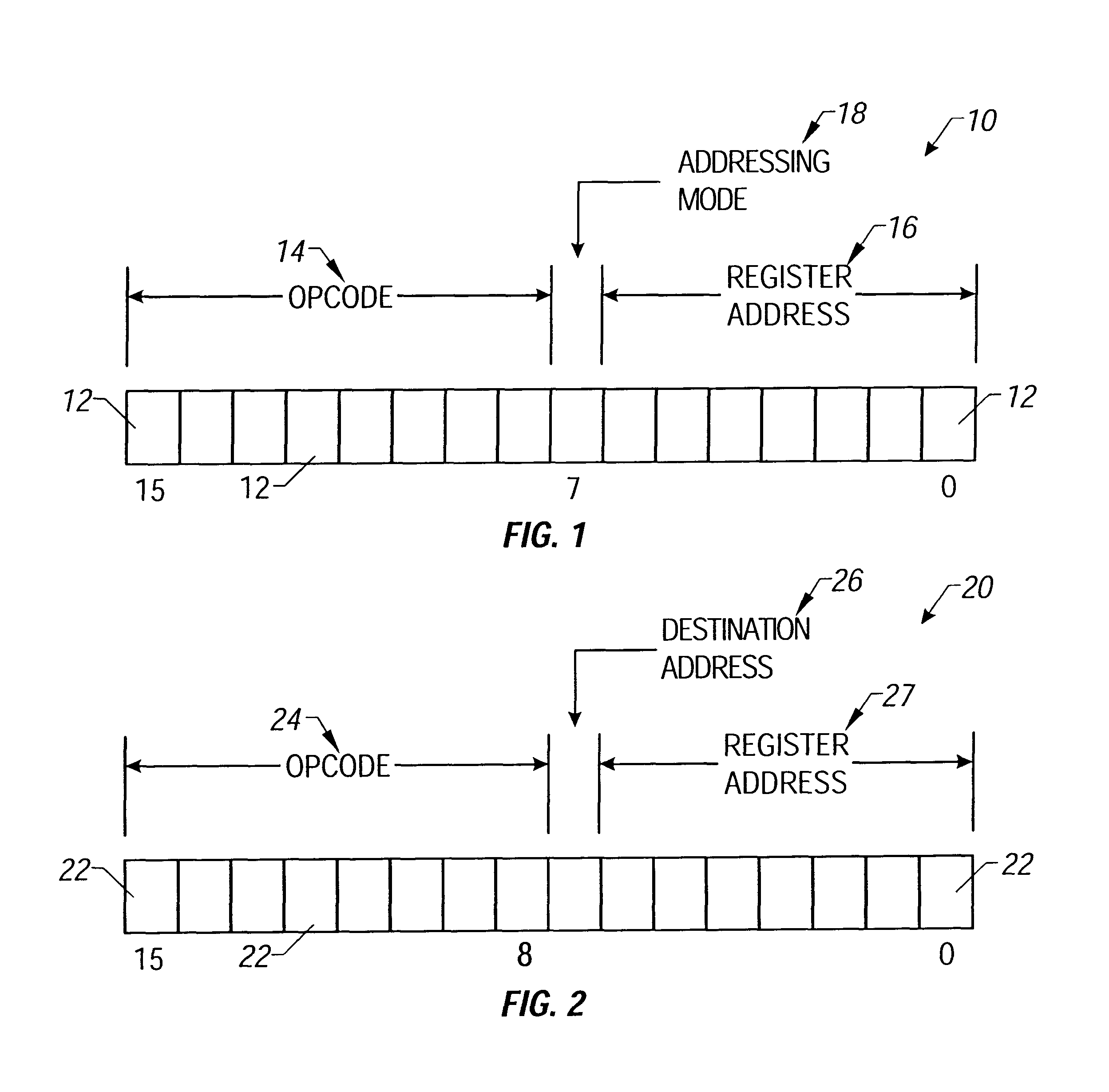

Processor architecture scheme which uses virtual address registers to implement different addressing modes and method therefor

InactiveUS6192463B1Instruction analysisGeneral purpose stored program computerPage address registerComputer architecture

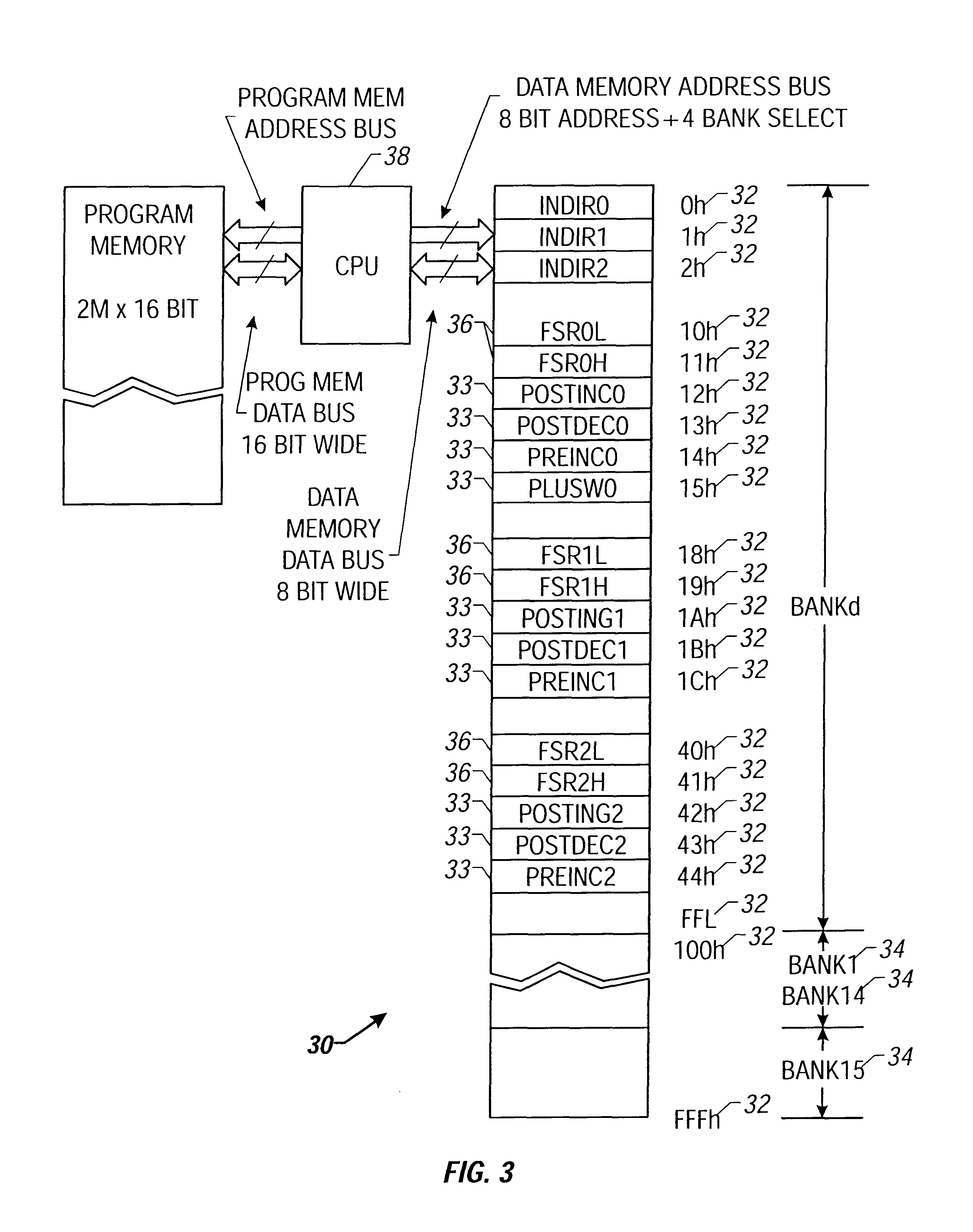

A processor architecture scheme which allows for encoding of multiple addressing modes through use of virtual register addresses in order to maximize number of directly addressable registers in the processor architecture scheme. A set of virtual address register locations associated with an indirect addressing pointer is reserved in memory. The number of virtual register address locations reserved is equal to a number of indirect addressing modes associated with the indirect addressing pointer. Each of the virtual register address locations initiates an indirect addressing mode to be used with the associated indirect addressing pointer when accessed.

Owner:MICROCHIP TECH INC

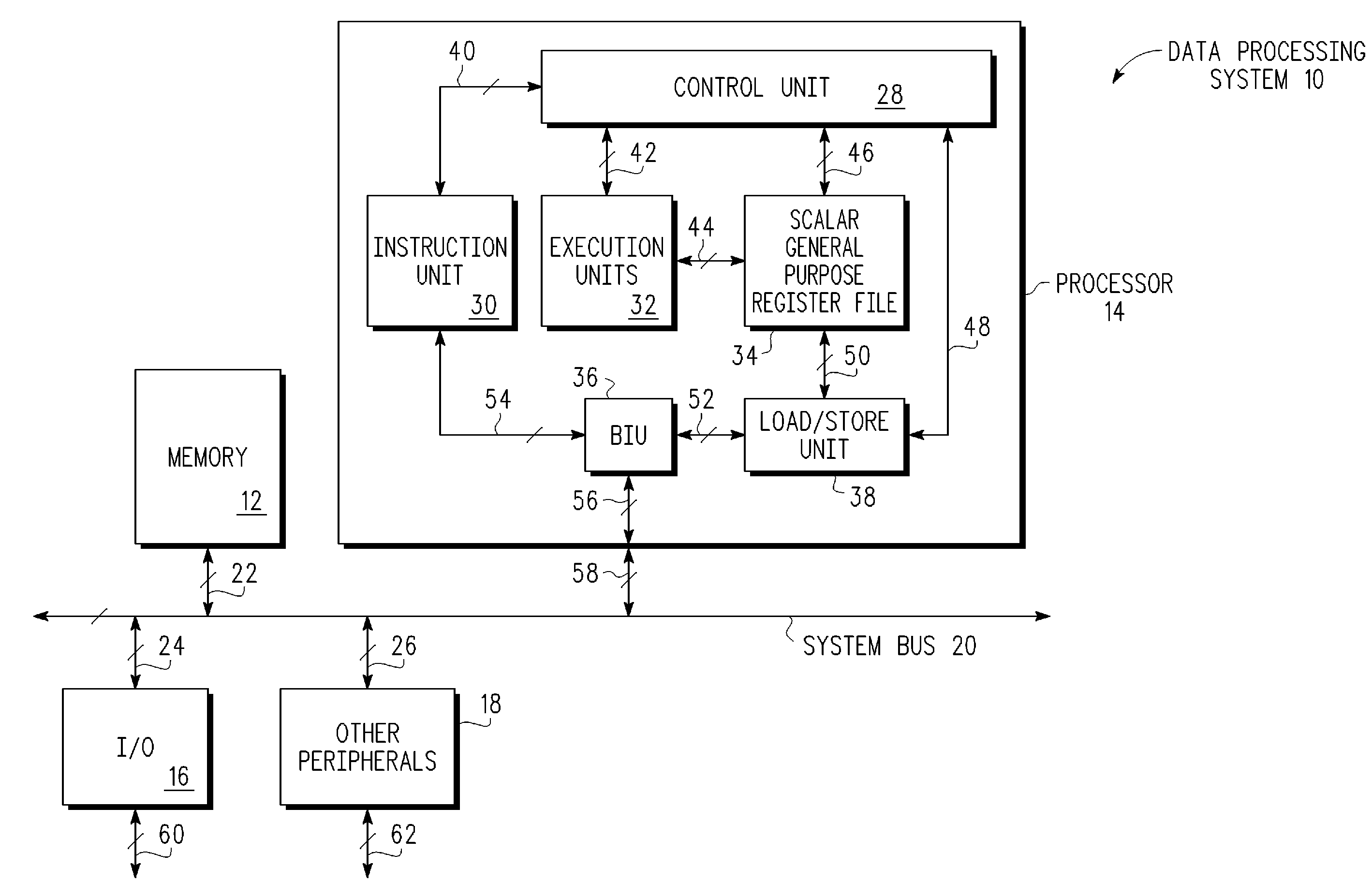

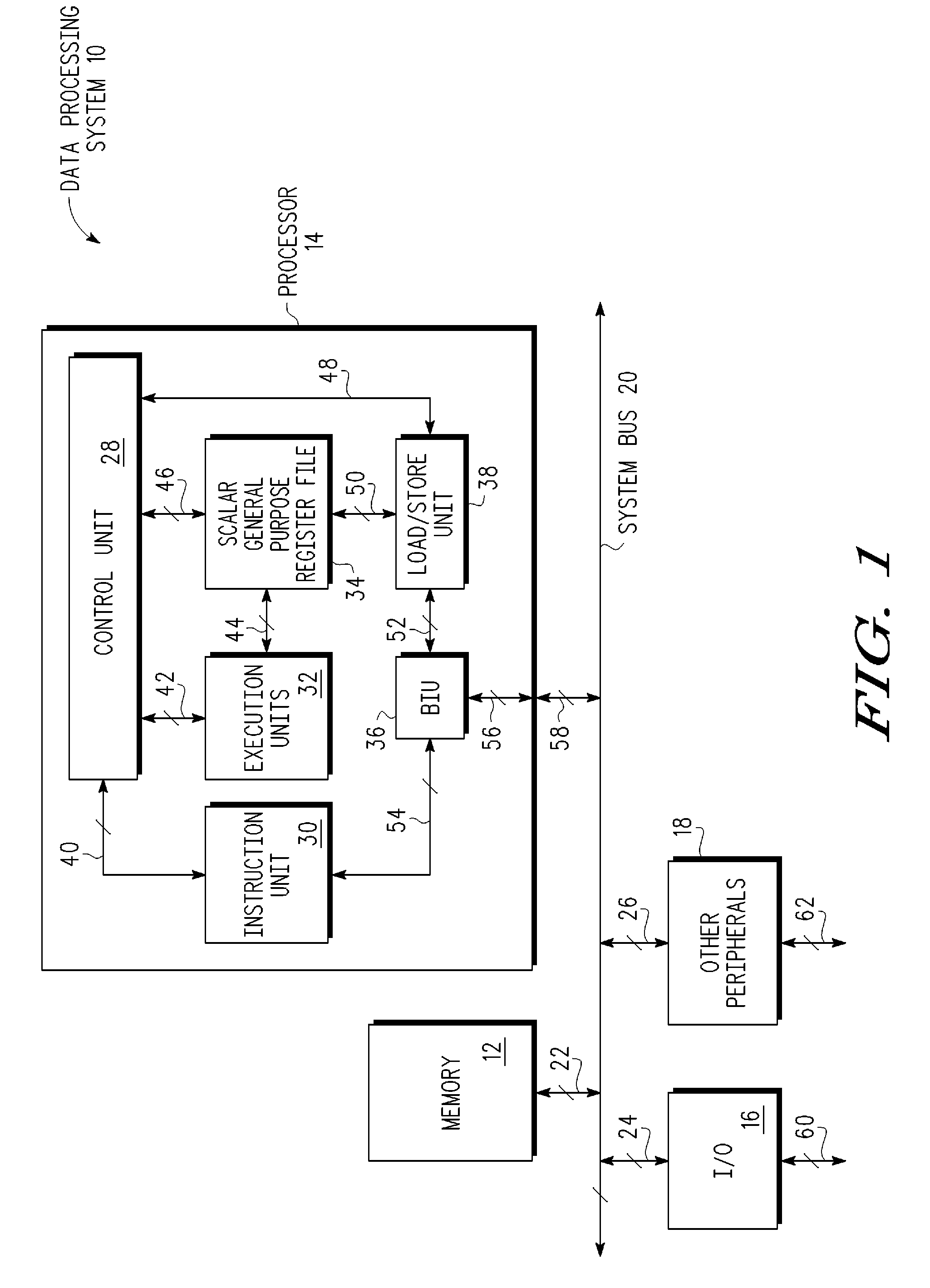

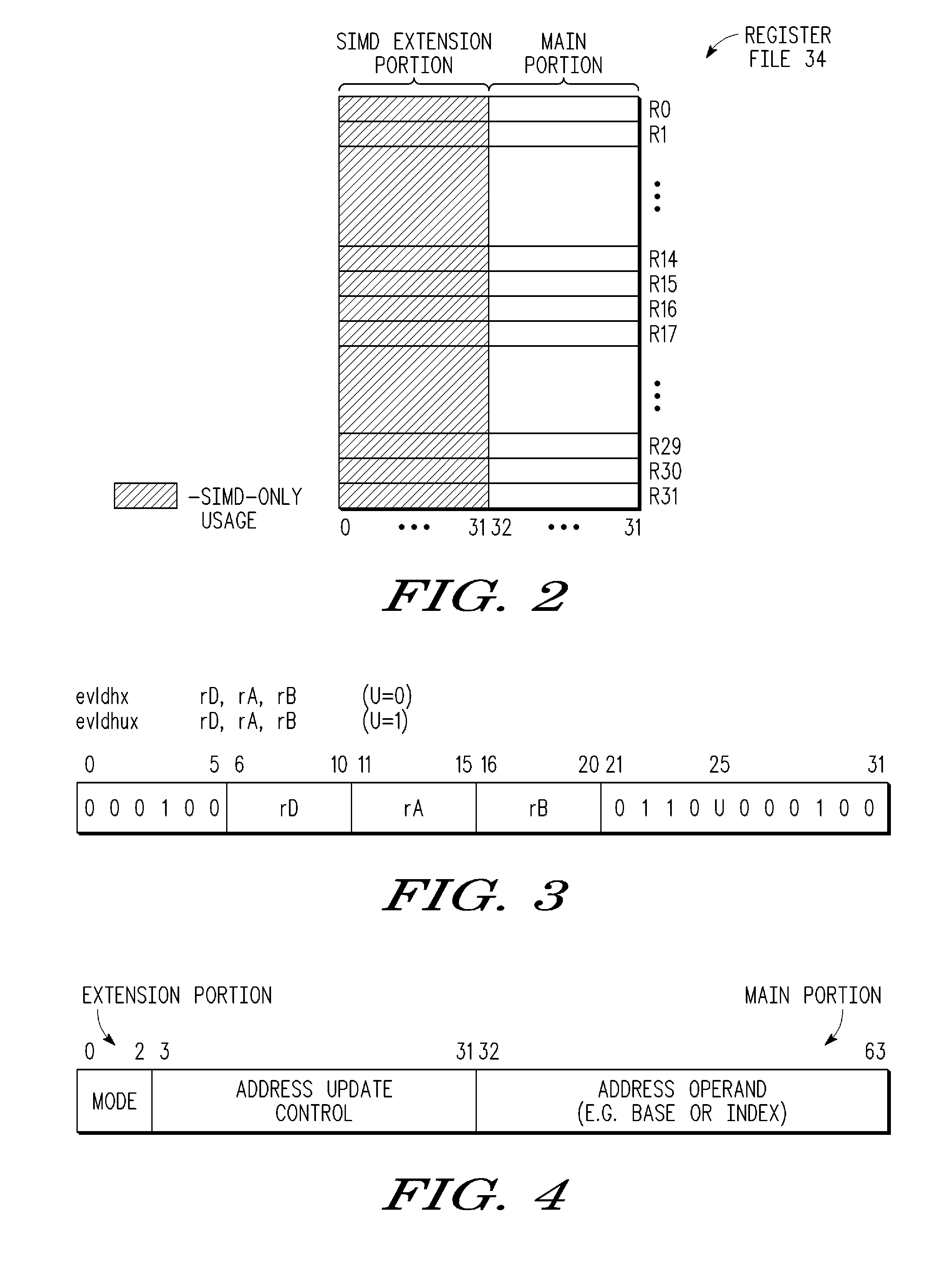

Provision of extended addressing modes in a single instruction multiple data (SIMD) data processor

ActiveUS20100042808A1Program control using stored programsInstruction analysisMemory addressProcessor register

Executing a first memory access instruction with update by an N-bit processor includes accessing at least one source register of a plurality of registers, wherein the accessing includes accessing a first register, wherein each register of the plurality of registers includes a main portion of N bits and an extension portion of M bits, wherein the main portion of the first register includes a first address operand. The execution of the first instruction further includes forming a memory access address using the first address operand; using the memory access address as an address for a memory access; producing an updated address operand; and writing the updated address operand to the main portion of the first register. The producing includes accessing an extension portion of a source register of the at least one source register to obtain modifying information and using the modifying information in the producing an updated address operand.

Owner:NXP USA INC

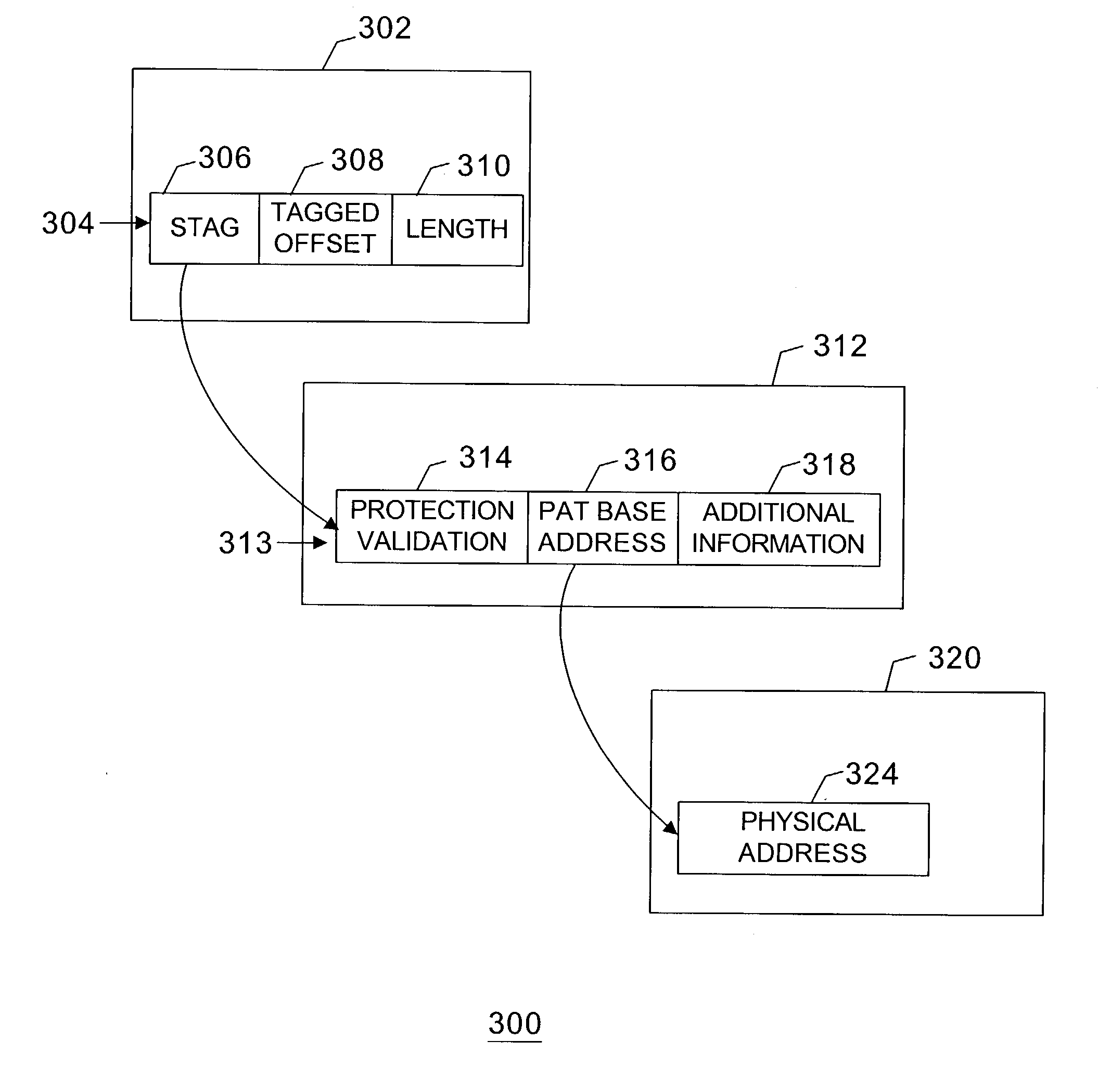

Physical mode addressing

InactiveUS20040193833A1Memory adressing/allocation/relocationMicro-instruction address formationOperating systemAddressing mode

The disclosed embodiments may relate to an address translation mechanism that may include a request that corresponds to a memory access operation. The request may include an address mode field. The address translation mechanism may also include an address field that may be used as a virtual address or a physical address depending on the contents of the address mode field.

Owner:HEWLETT PACKARD DEV CO LP

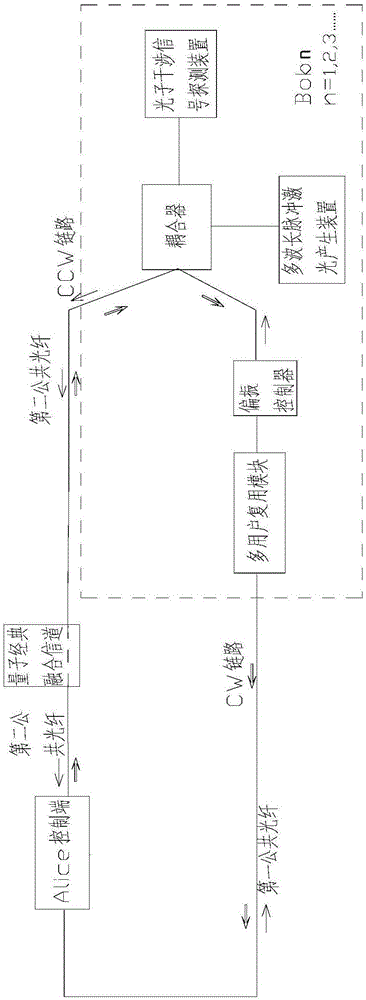

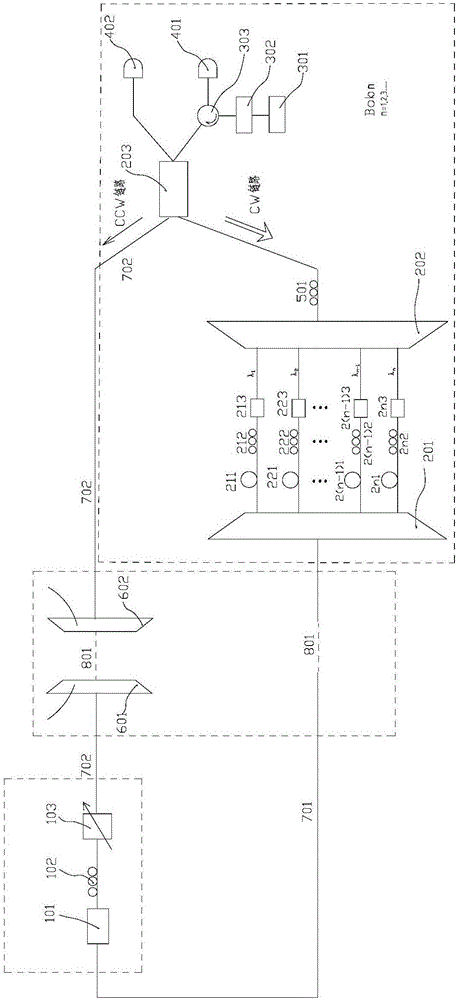

Multi-user QKD network system based on Sagnac ring, and secret key distribution method thereof

ActiveCN105049195AEasy to addEasy to deleteKey distribution for secure communicationPhotonic quantum communicationMulti wavelengthPhoton

The invention discloses a multi-user QKD network system based on a Sagnac ring, and a secret key distribution method thereof. The system comprises an Alice control end, a multiuser Bob client and a Sagnac annular pulse transmission link. The multiuser Bob client comprises a multi-wavelength pulse laser generation device, a photon interference signal detection device, a multiuser multiplexing module and a coupler; the Sagnac annular pulse transmission link comprises a CW link and a CCW link; and pulses generated by the multi-wavelength pulse laser generation device, after penetrating into the CW link and the CCW link through the coupler according to a proportion of 50:50, are merged and output from the coupler and then are transmitted to the photon interference signal detection device for detection. According to the invention, multiple users are multiplexed into the system through a wavelength division multiplexer / demultiplexer in a wavelength addressing mode, a phase coding mode is employed, the optical pulses are respectively modulated for loading information at the Alice end and the Bob end, the pulses are interfered at the coupler, the overall structure is simple, the photon utilization rate and the code rate are high, the transmission stability is good, and one-to-N multiuser transmission is realized.

Owner:GUANGDONG INCUBATOR TECH DEV CO LTD