Patents

Literature

30 results about "Page address register" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A page address register (PAR) contains the physical addresses of pages currently held in the main memory of a computer system. PARs are used in order to avoid excessive use of an address table in some operating systems. A PAR may check a page's number against all entries in the PAR simultaneously, allowing it to retrieve the pages physical address quickly. A PAR is used by a single process and is only used for pages which are frequently referenced (though these pages may change as the process's behaviour changes in accordance with the principle of locality). An example computer which made use of PARs is the Atlas.

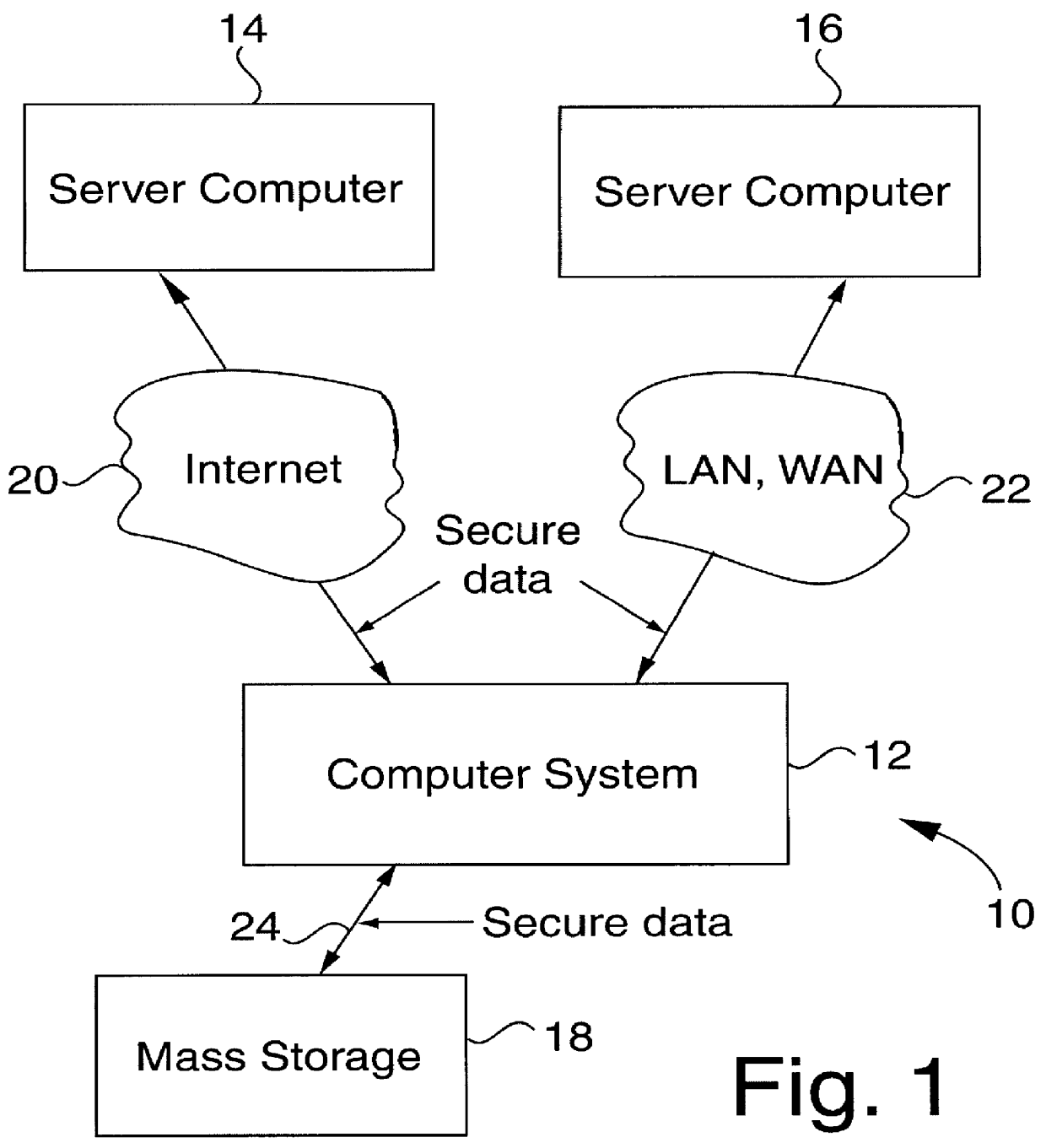

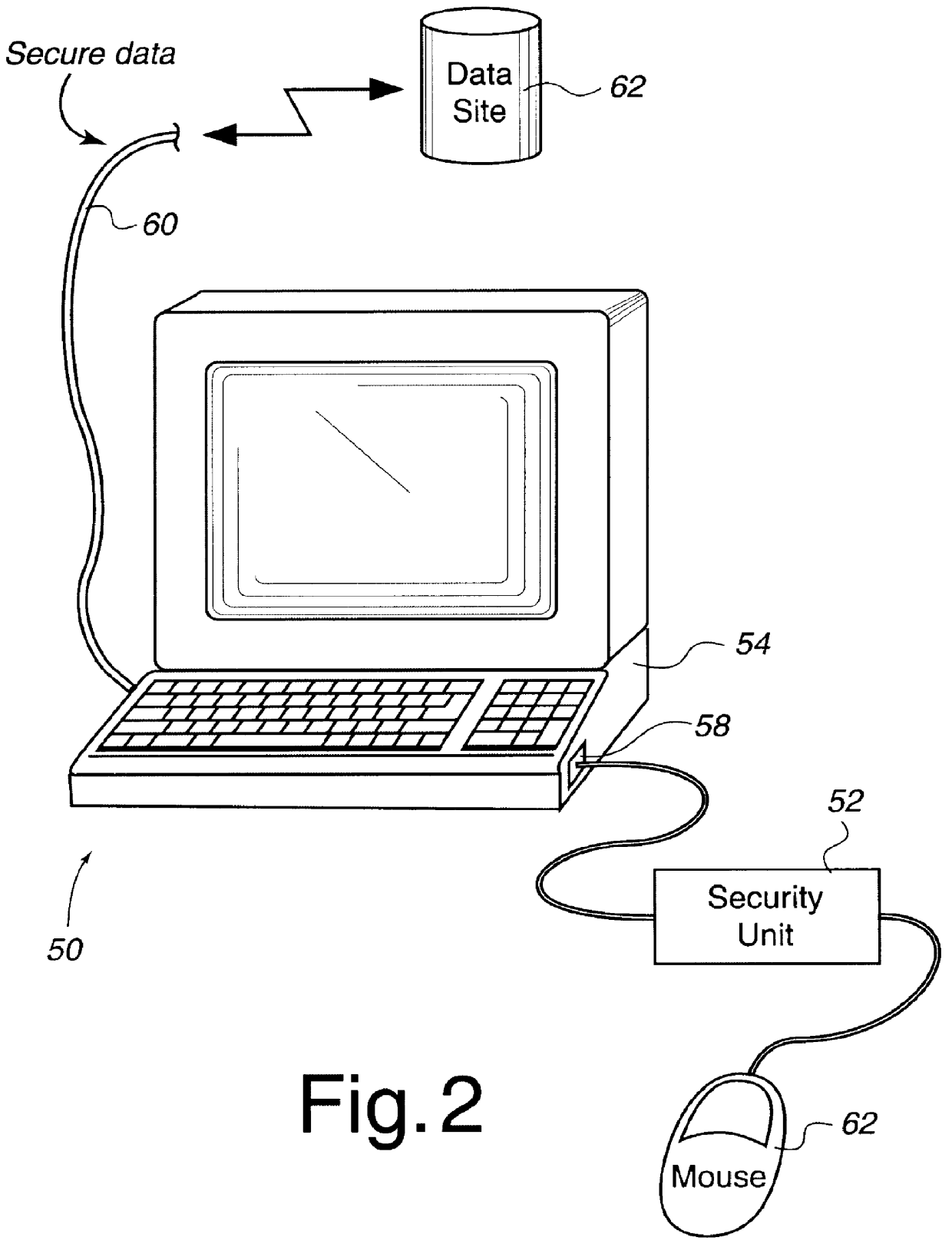

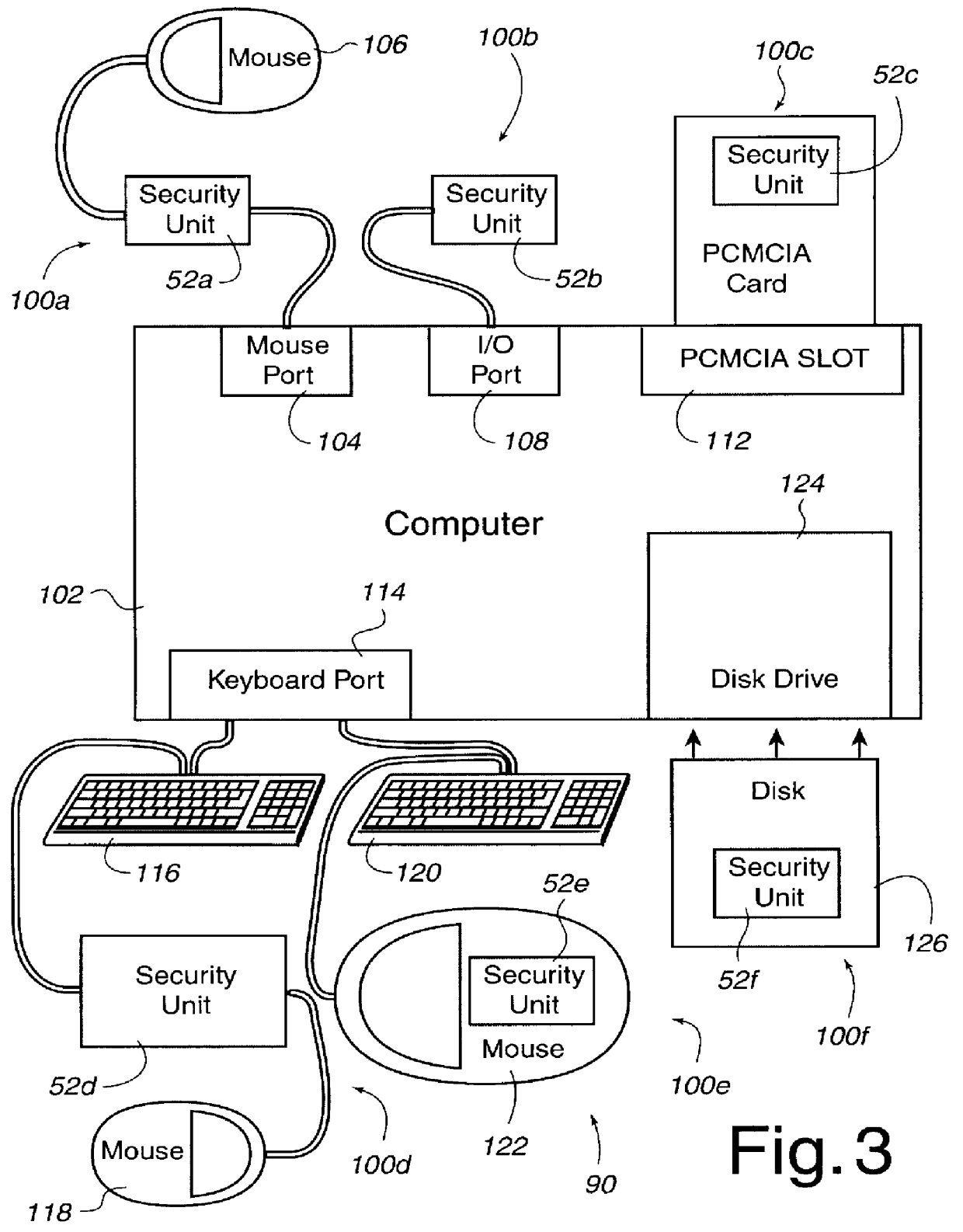

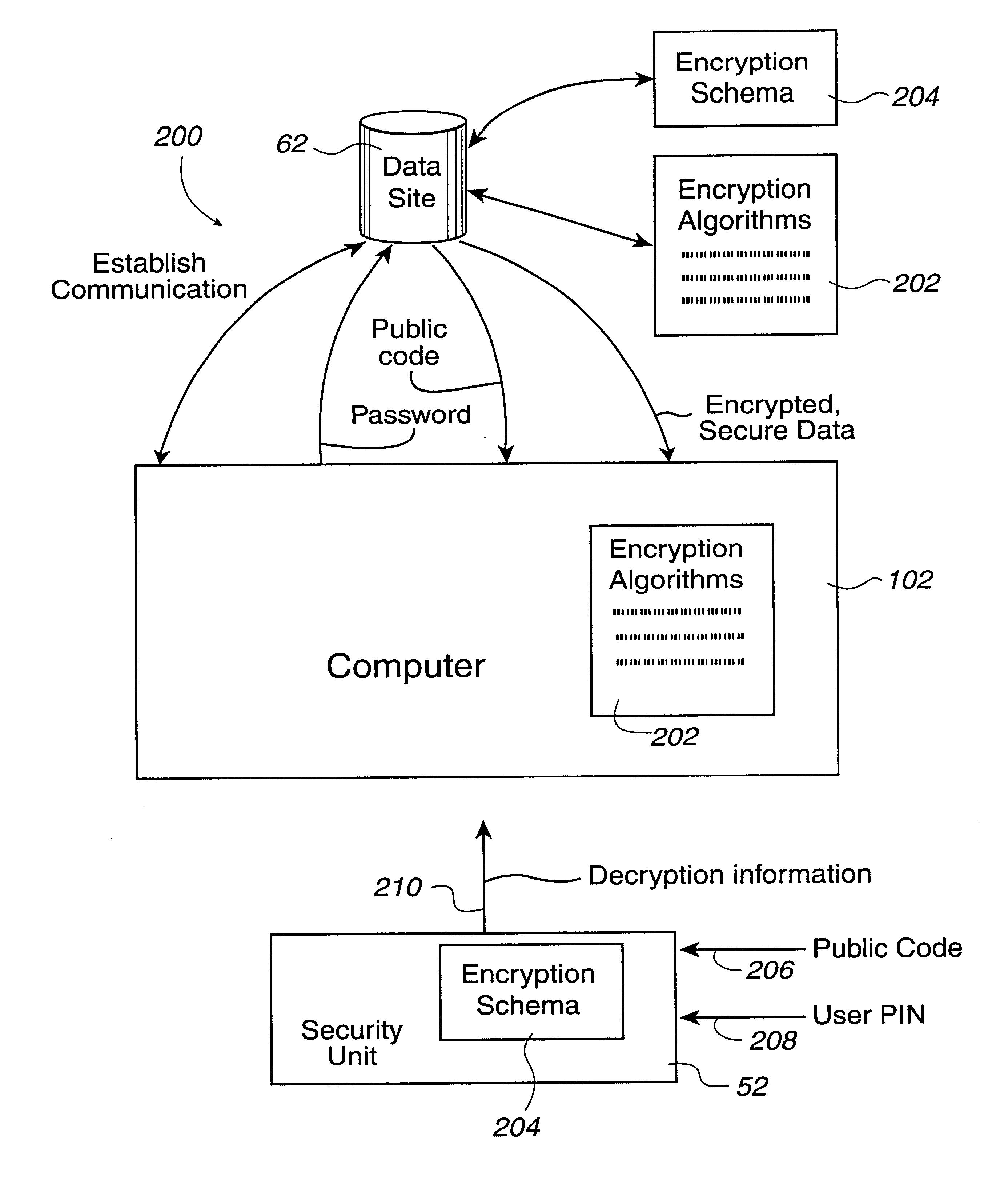

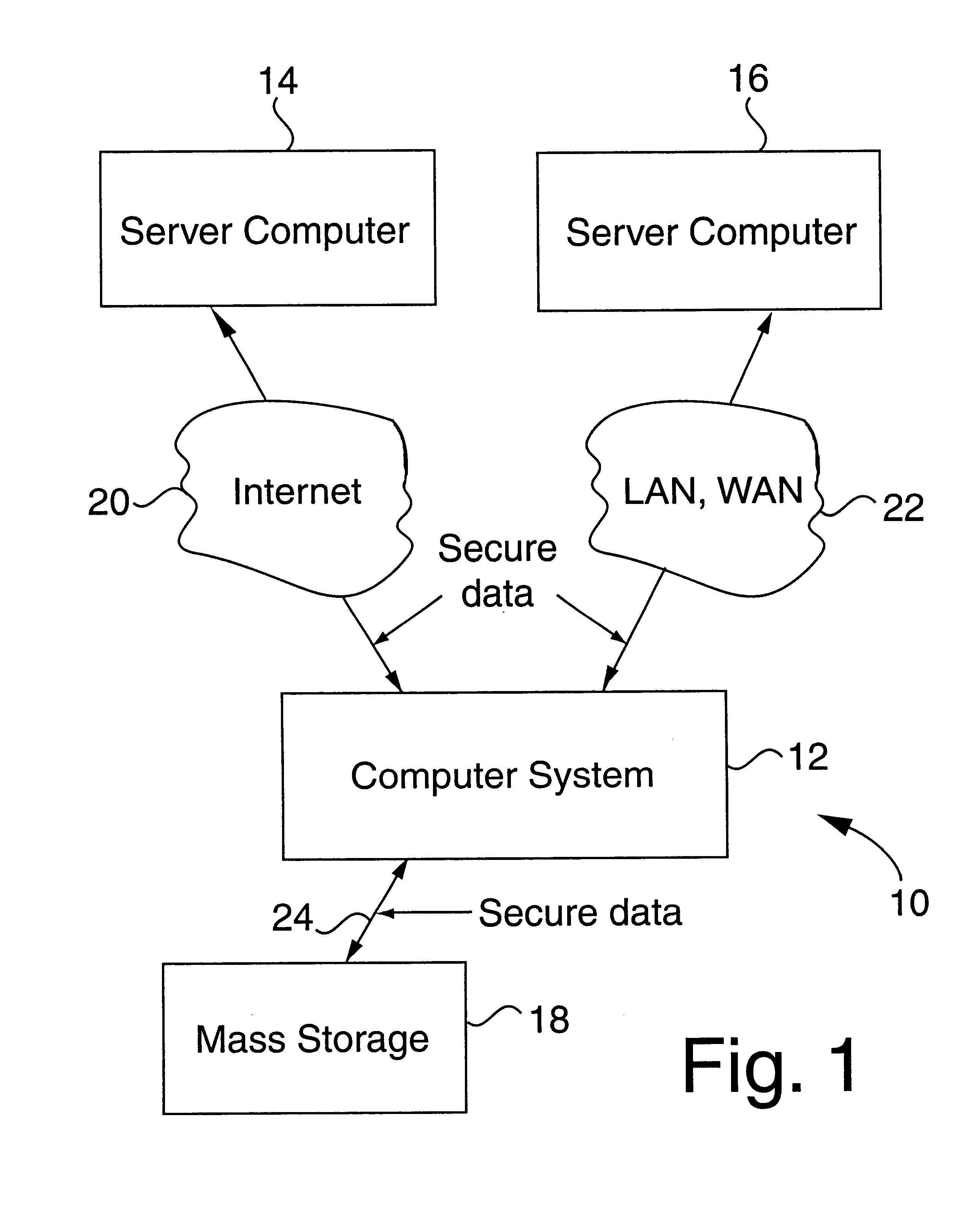

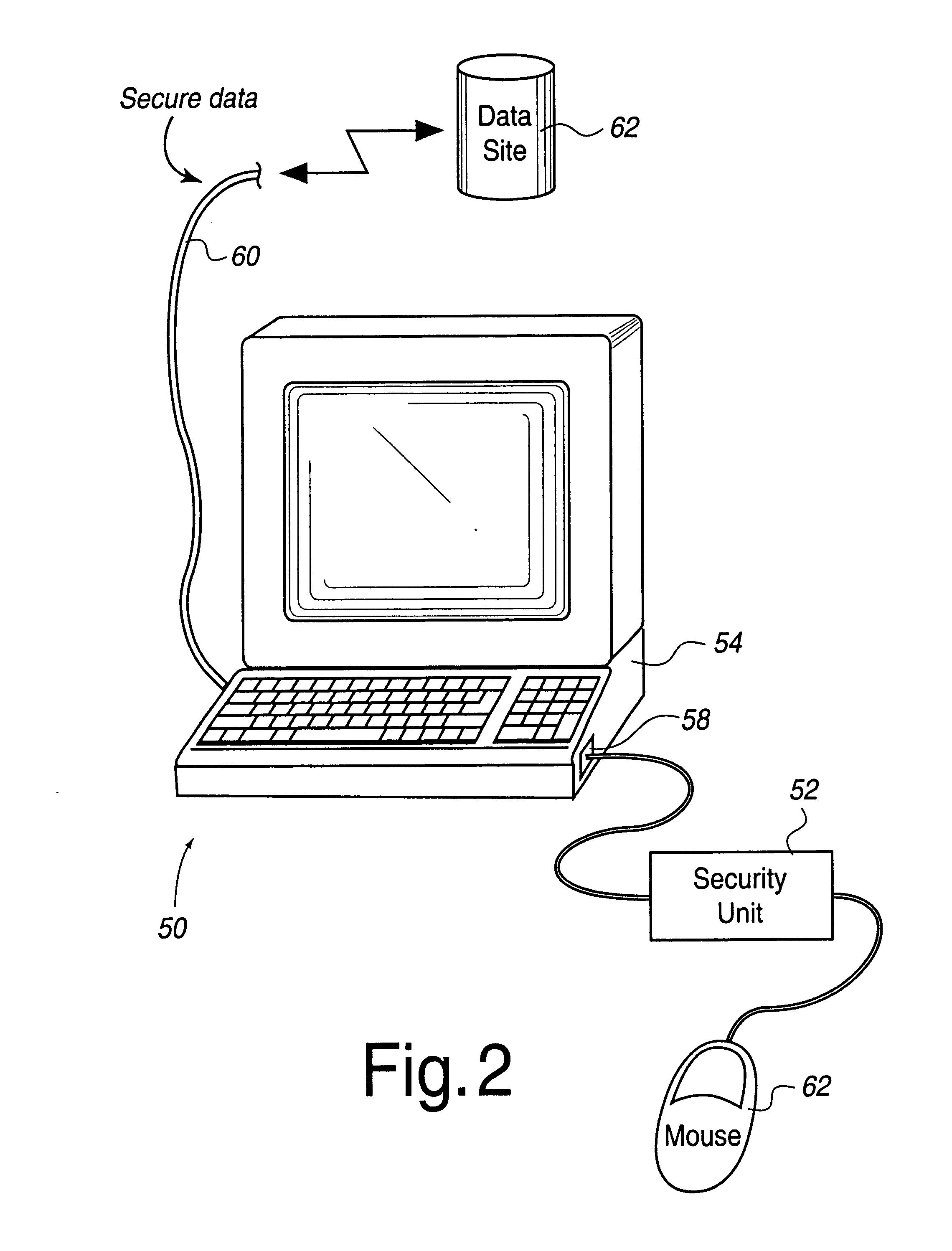

Security apparatus for data transmission with dynamic random encryption

InactiveUS6094486ASimple equipmentBuilt inexpensively and smallEqual length code transmitterDigital data processing detailsPage address registerShift register

A security apparatus including a number input device (302), an address register (312) responsive to the number input device, an encryption schema memory (316) addressable by the address register to produce an output code and a relative address code, and address incrementing logic (310) responsive the relative address code and operative to increment the address register. The apparatus also preferably includes a PIN register (304) coupled to the number input device, a public code register (306) coupled to the number input device, and merging logic (308) merging outputs of the PIN register and the public code register to be input to the address register. The apparatus also preferably includes an output shift register operative to shift out the output code of the encryption schema memory. The encryption schema memory can be read only memory, writeable memory, or both.

Owner:MARCHANT BRIAN E

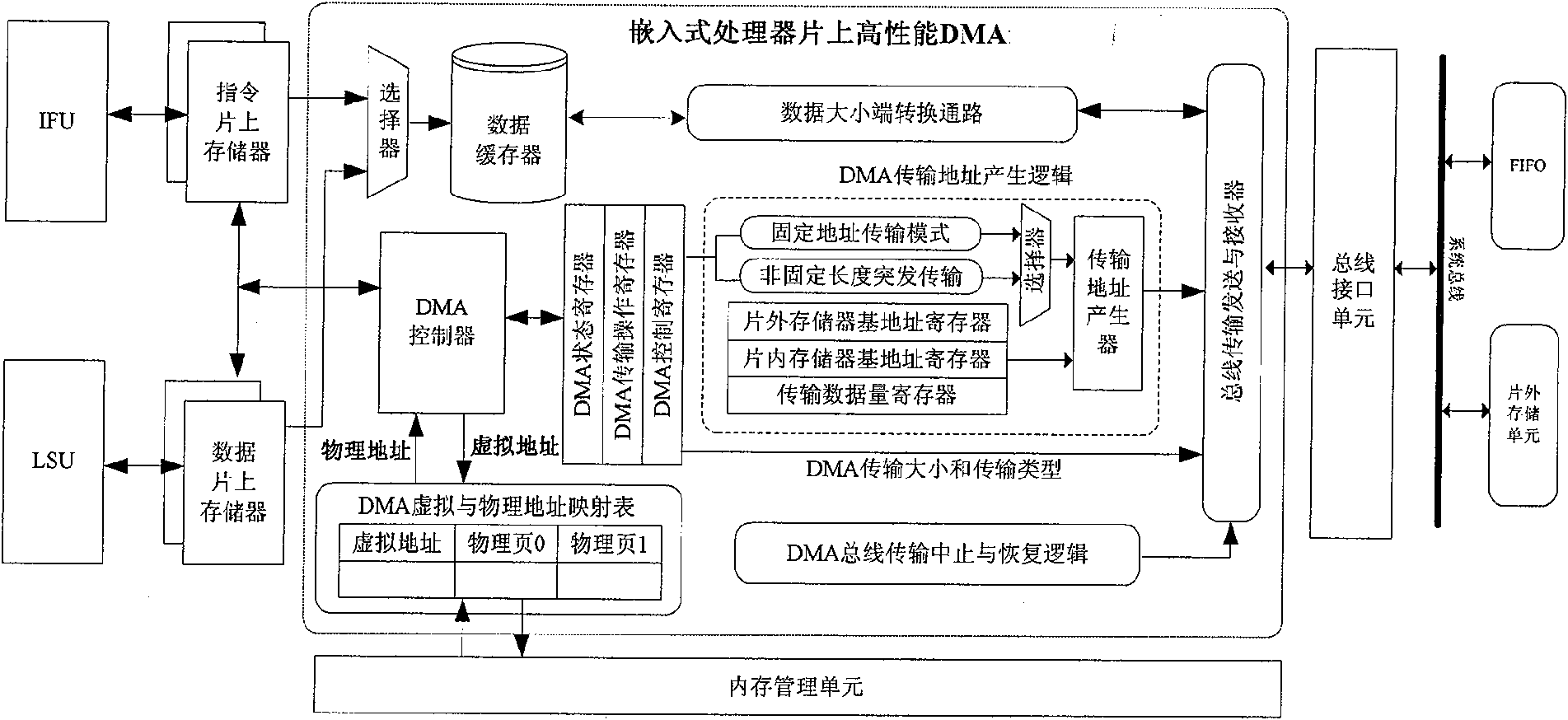

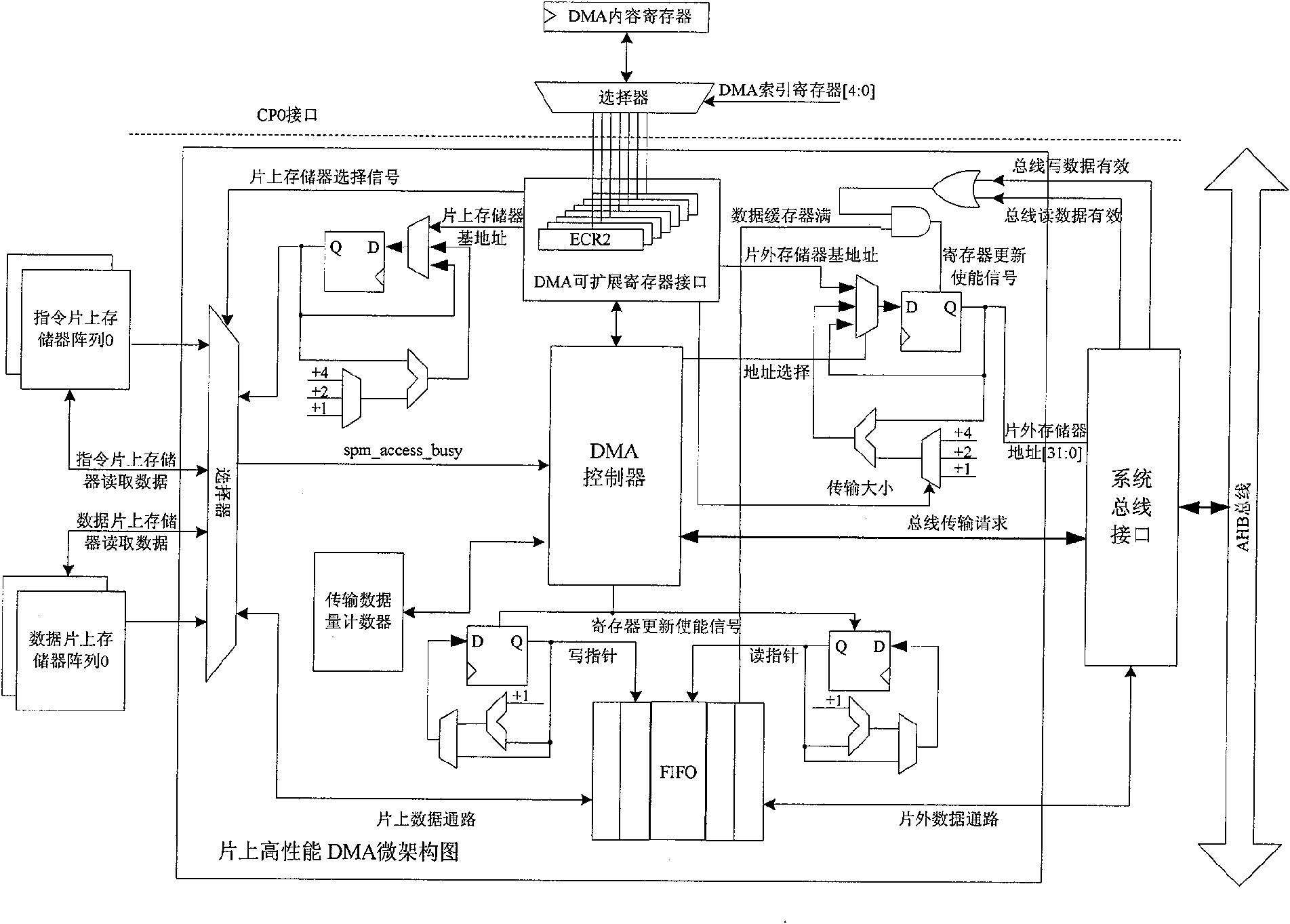

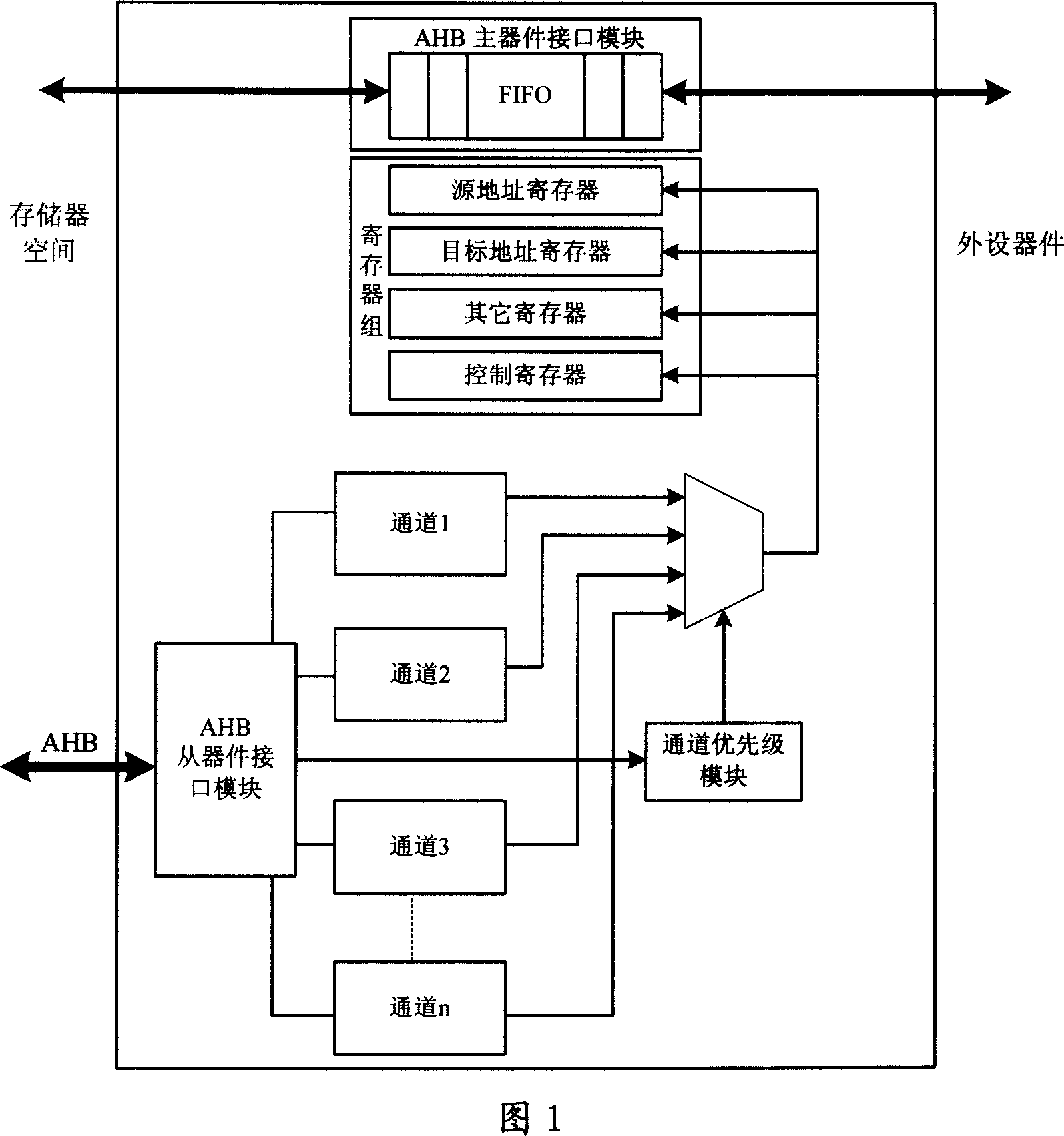

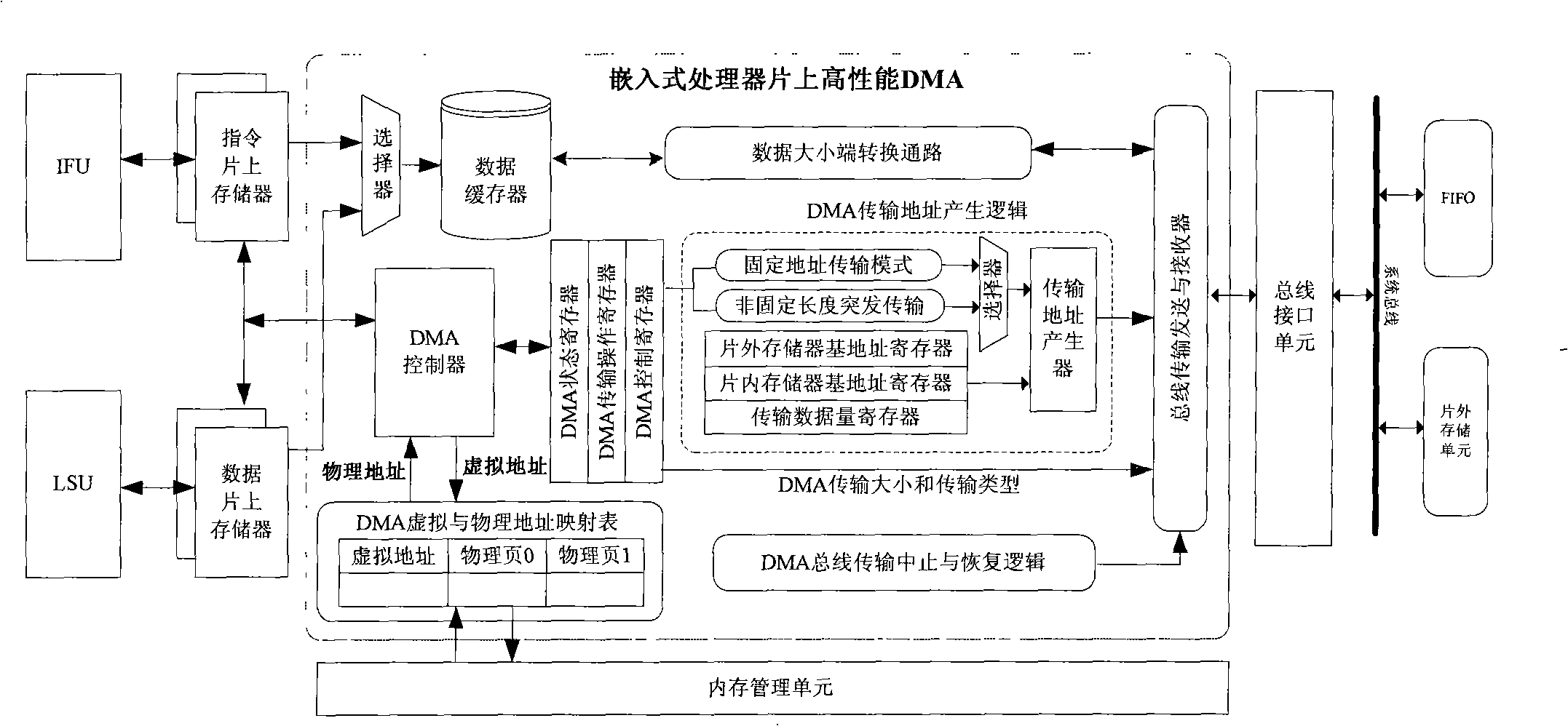

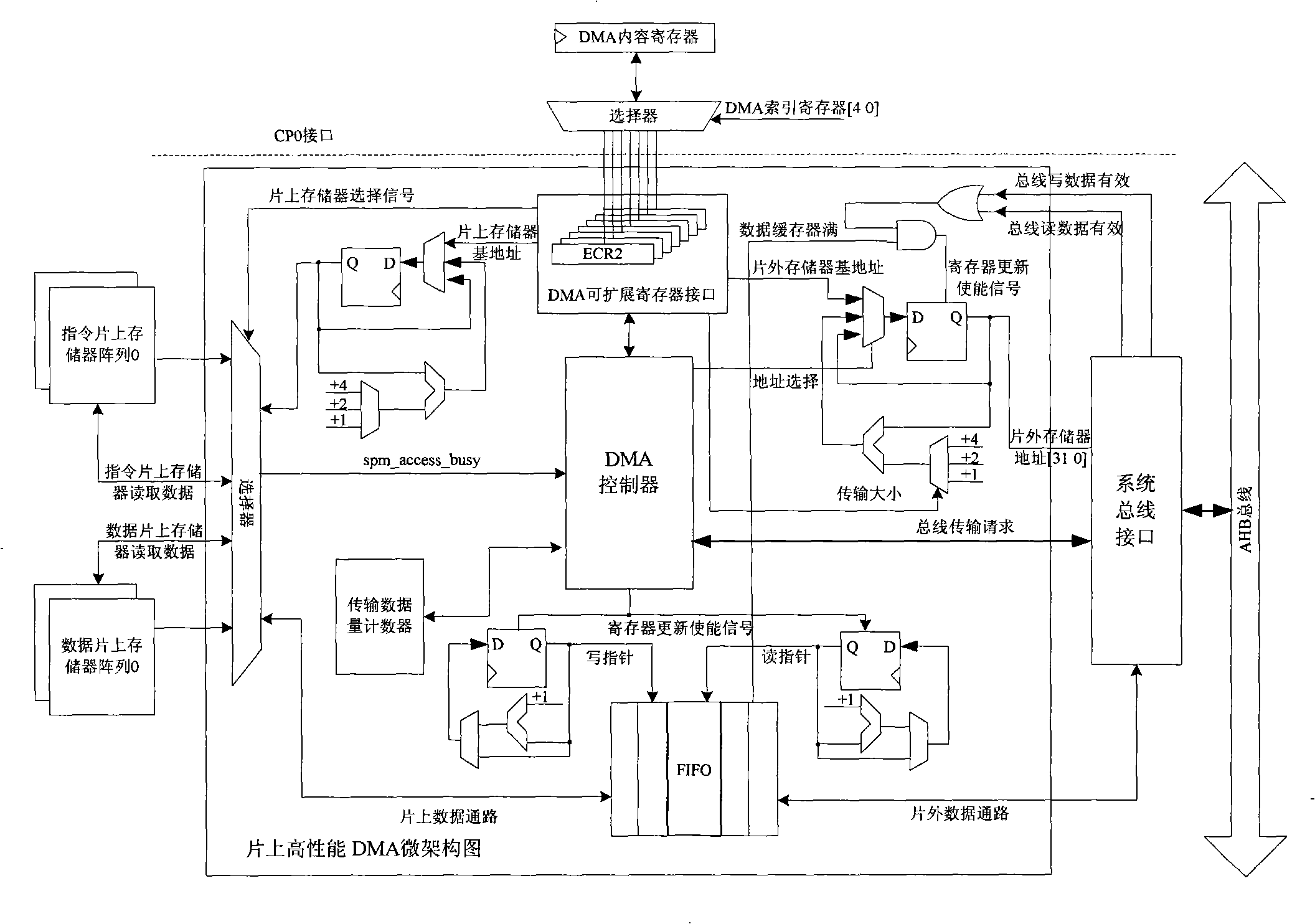

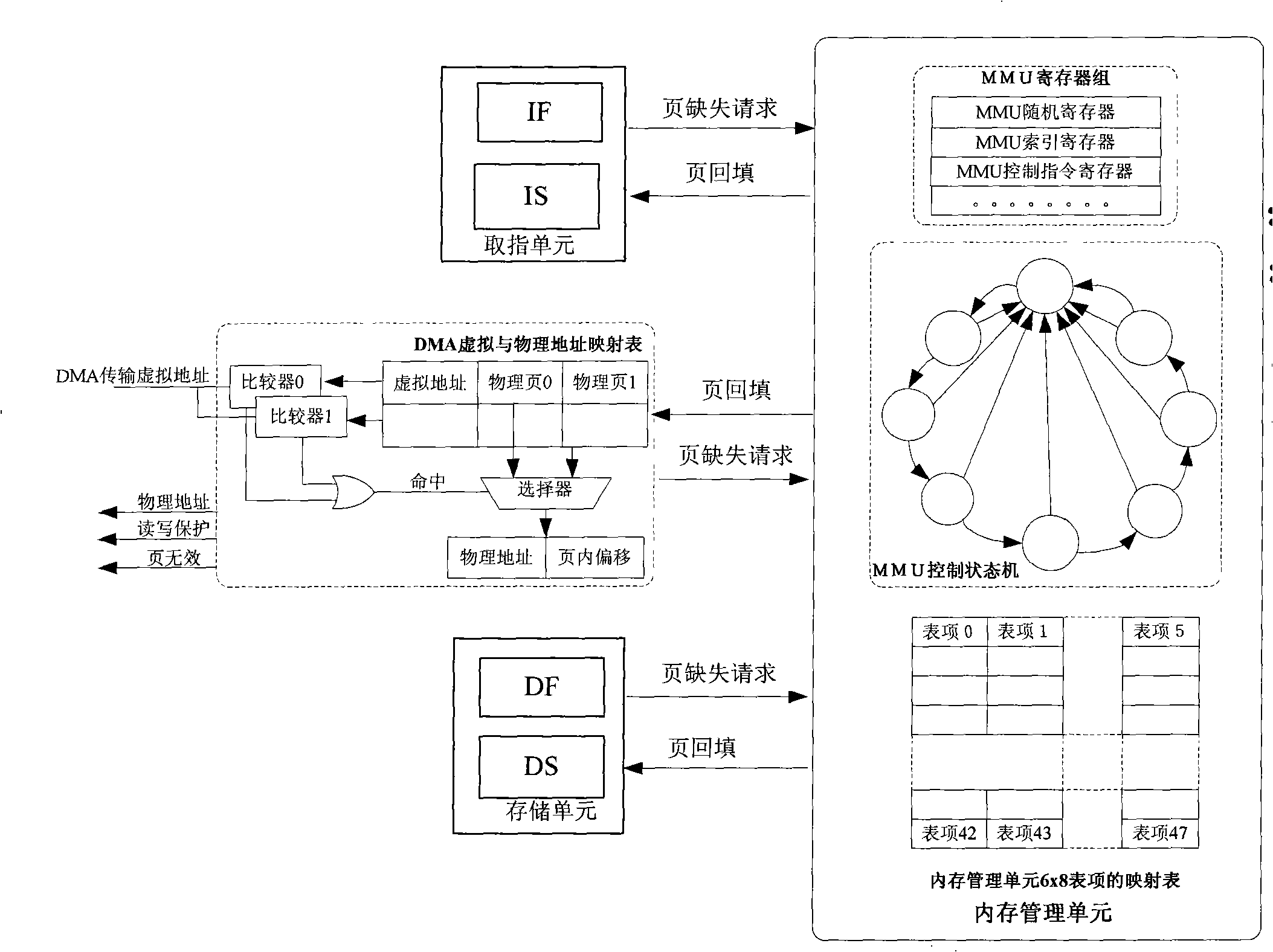

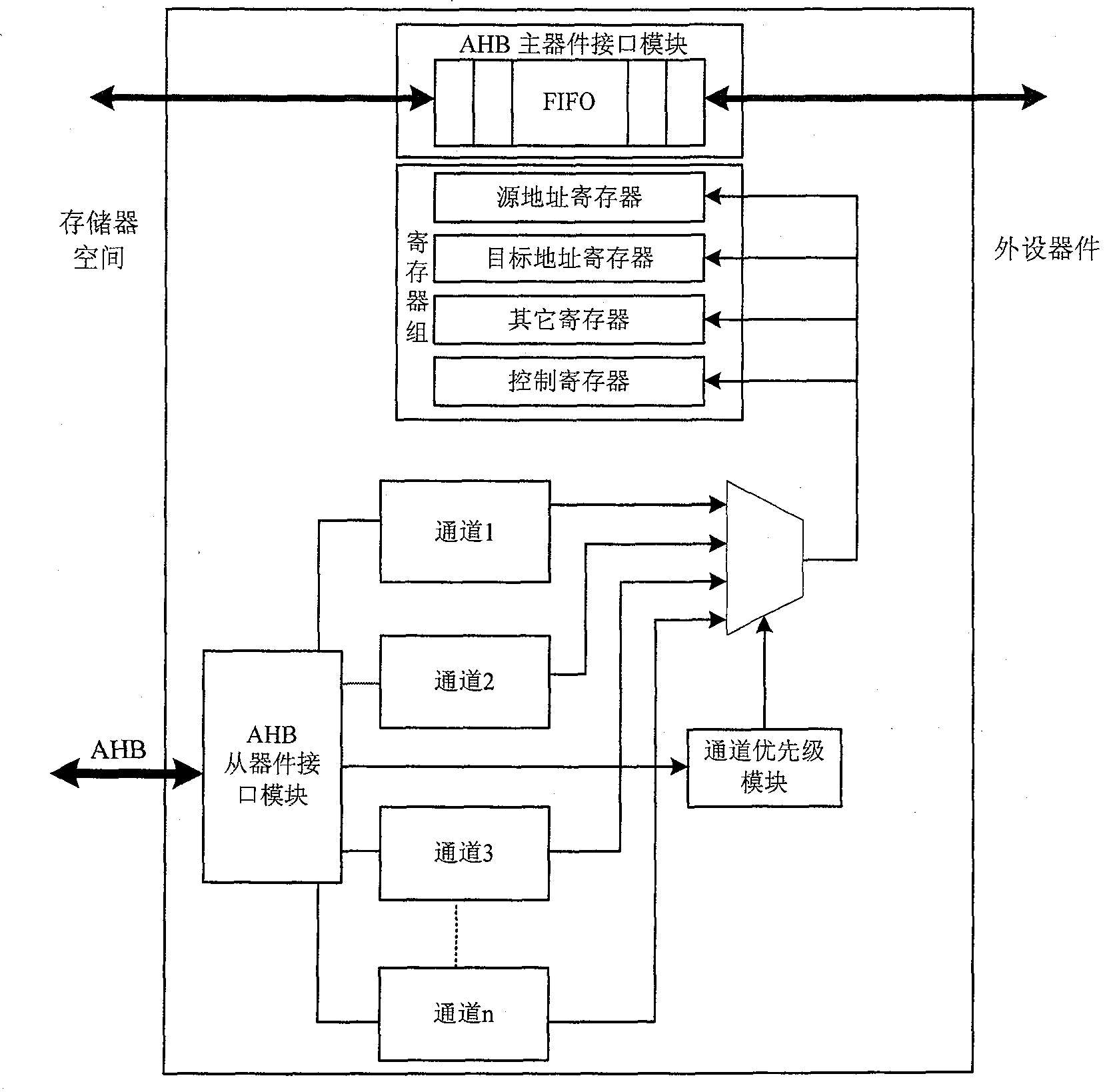

High performance DMA on embedded type processor chip

ActiveCN101556565AImprove performanceIncrease independenceElectric digital data processingPage address registerIp address

The invention relates to a high performance DMA on an embedded type processor chip. The high performance DMA comprises a data buffer used for caching the data read from an on-chip memory, the data sent to a bus interface unit, the data received from the bus interface unit, and the data written into the on-chip memory; a data big-endian and little-endian convertor; a DMA controller used for initializing a state register, a control register, an initial address register and a data size register; a DMA transmission address generating logic module used for automatically calculating the transmission address of the next data on an on-chip external memory and generating chip selection and read and write signals of the on-chip memory according to the on-chip address, and simultaneously updating a data size counter till the counter changes to zero; and a bus transmission transmitter and receiver. The high performance DMA has the advantages that the development difficulty is low, the cost of the hardware is low, the transplantation is convenient, the expansibility is flexible, the data transmission speed is high, and the performance of the processor is greatly enhanced.

Owner:C SKY MICROSYST CO LTD

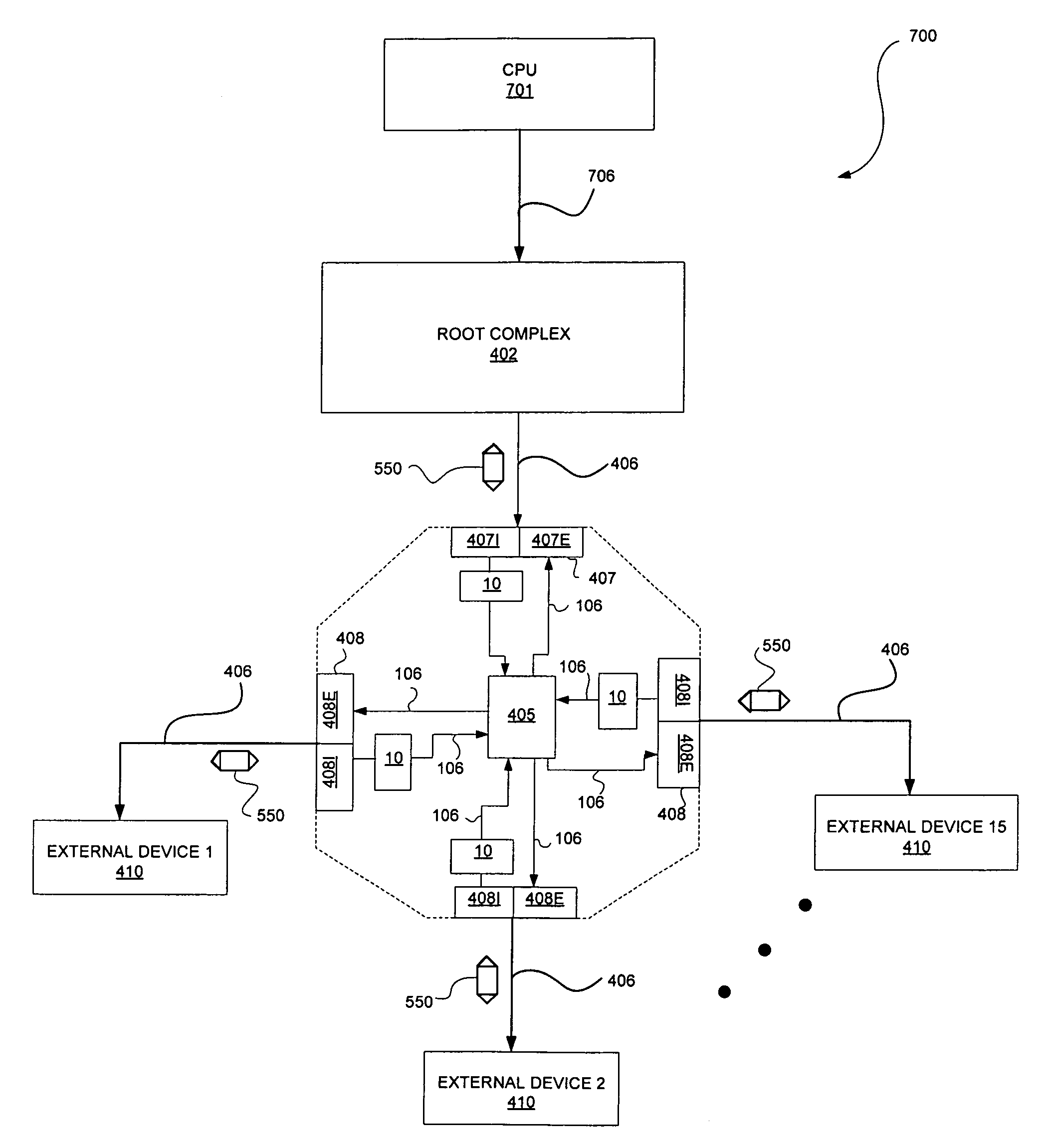

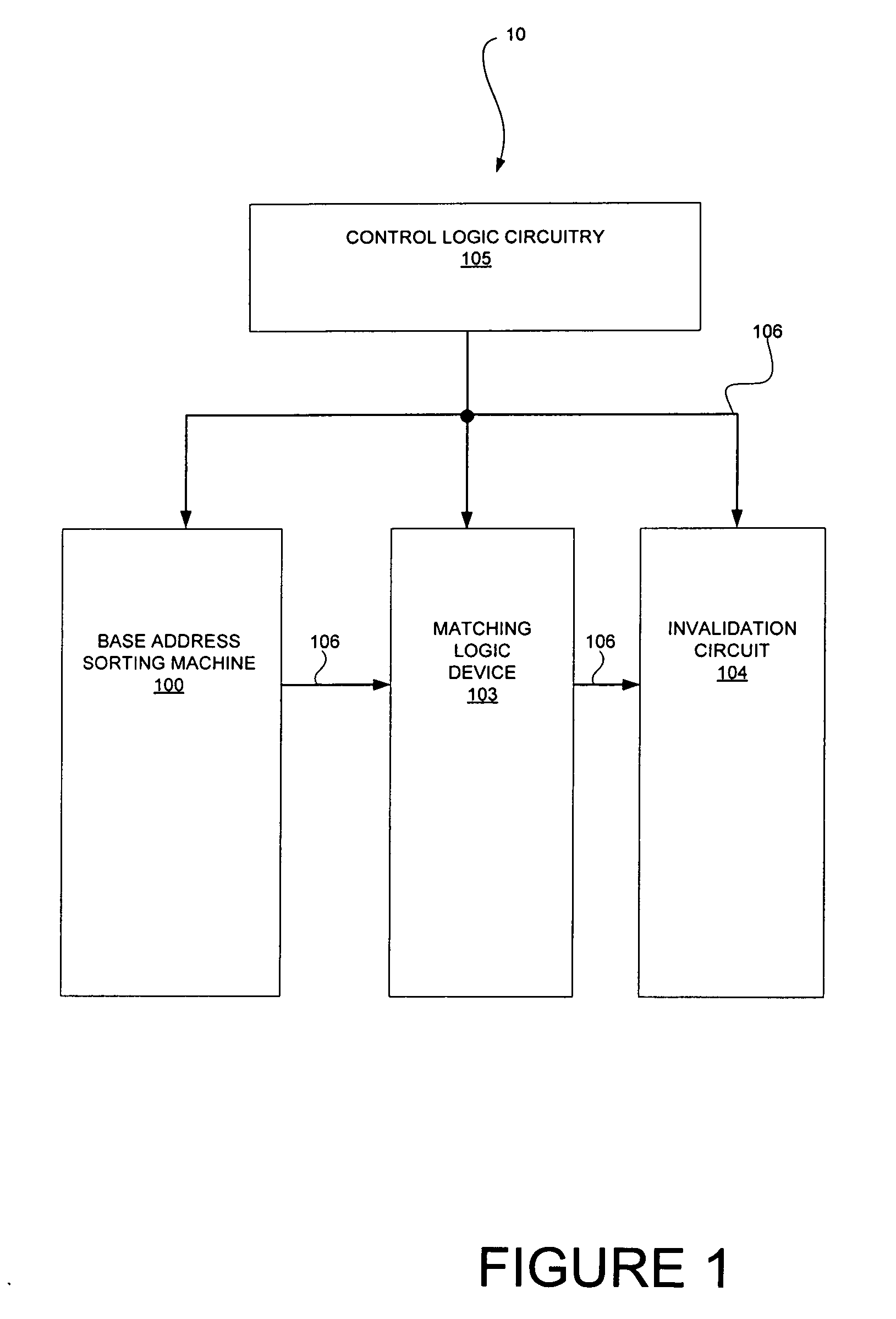

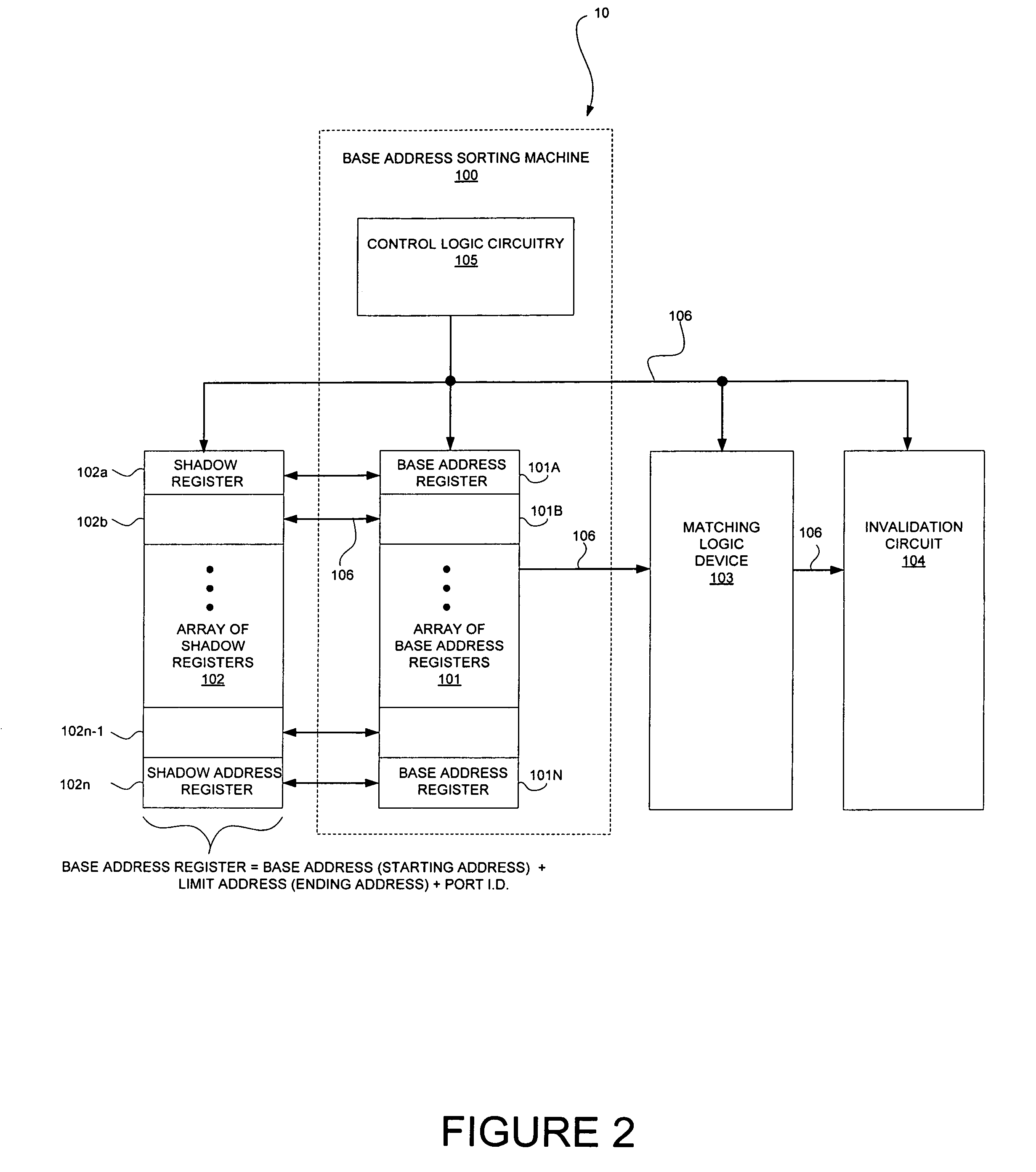

Method and device for base address sorting and entry into base address registers

ActiveUS7694025B1The process is fast and accurateGuaranteed ease of operationInput/output to shift register memoriesPage address registerArray data structure

A base address sorting device in a serial switch is disclosed which includes an array of shadow registers, each shadow register in the array being electrically coupled to a base address register, in an array of base address registers, each of the base address registers having a base address, and control logic circuitry electrically coupled to the array of shadow registers and to the array of base address registers with the control logic circuitry being operable, when it receives a configuration command, to implement a method, for reconfiguring the contents of the array of base address registers, including: inserting a new base address from the configuration command into a shadow register in the array of shadow registers, sorting the array of shadow registers into a predetermined order, and then copying the contents of the array of shadow registers into the array of base address registers.

Owner:MICROSEMI STORAGE SOLUTIONS US INC

Security apparatus for data transmission with dynamic random encryption

InactiveUS6236728B1Simple equipmentBuilt inexpensively and smallEqual length code transmitterDigital data processing detailsPage address registerShift register

A security apparatus including a number input device (302), an address register (312) responsive to the number input device, an encryption schema memory (316) addressable by the address register to produce an output code and a relative address code, and address incrementing logic (310) responsive the relative address code and operative to increment the address register. The apparatus also preferably includes a PIN register (304) coupled to the number input device, a public code register (306) coupled to the number input device, and merging logic (308) merging outputs of the PIN register and the public code register to be input to the address register. The apparatus also preferably includes an output shift register operative to shift out the output code of the encryption schema memory. The encryption schema memory can be read only memory, writeable memory, or both.

Owner:MARCHANT BRIAN E

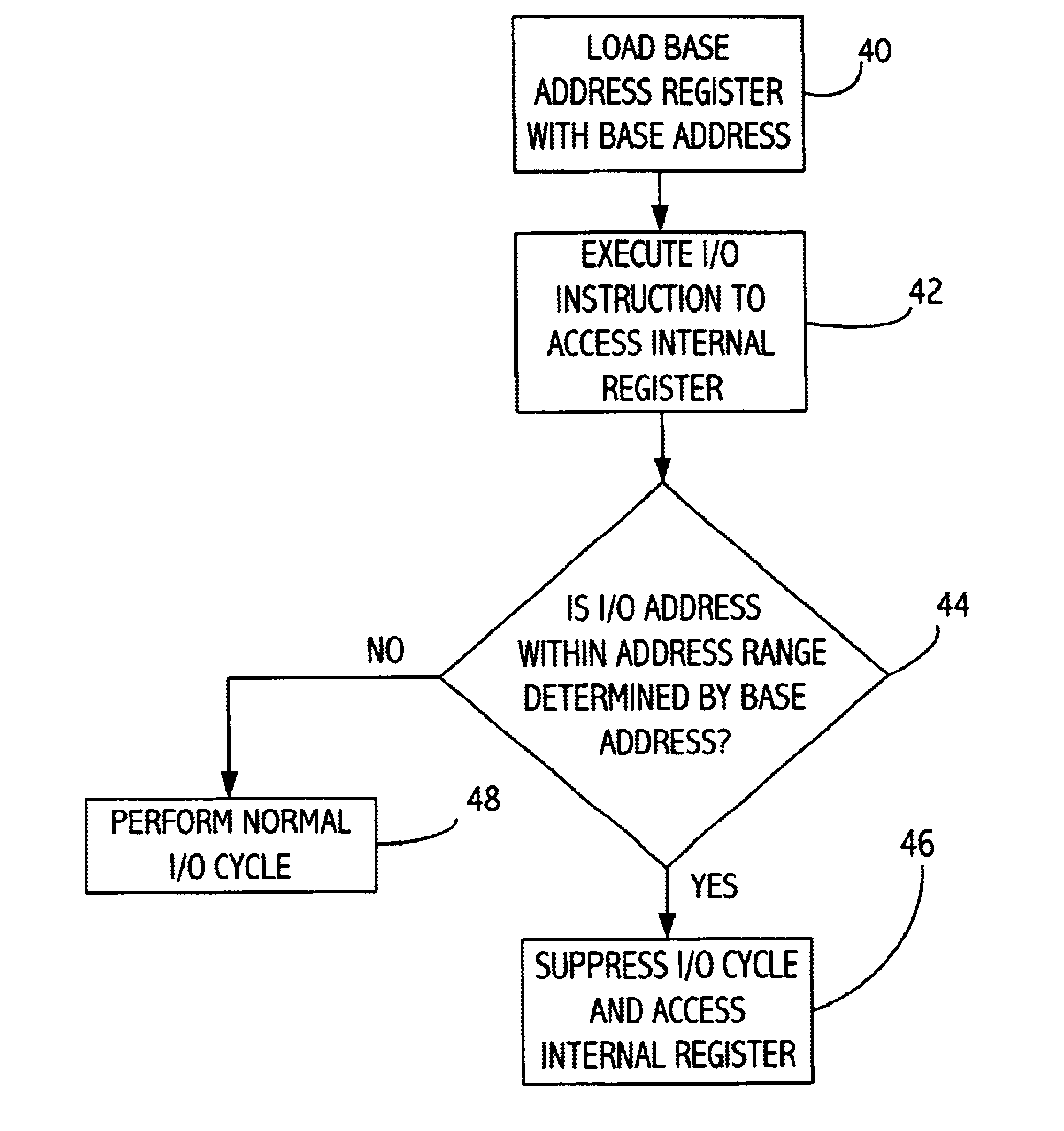

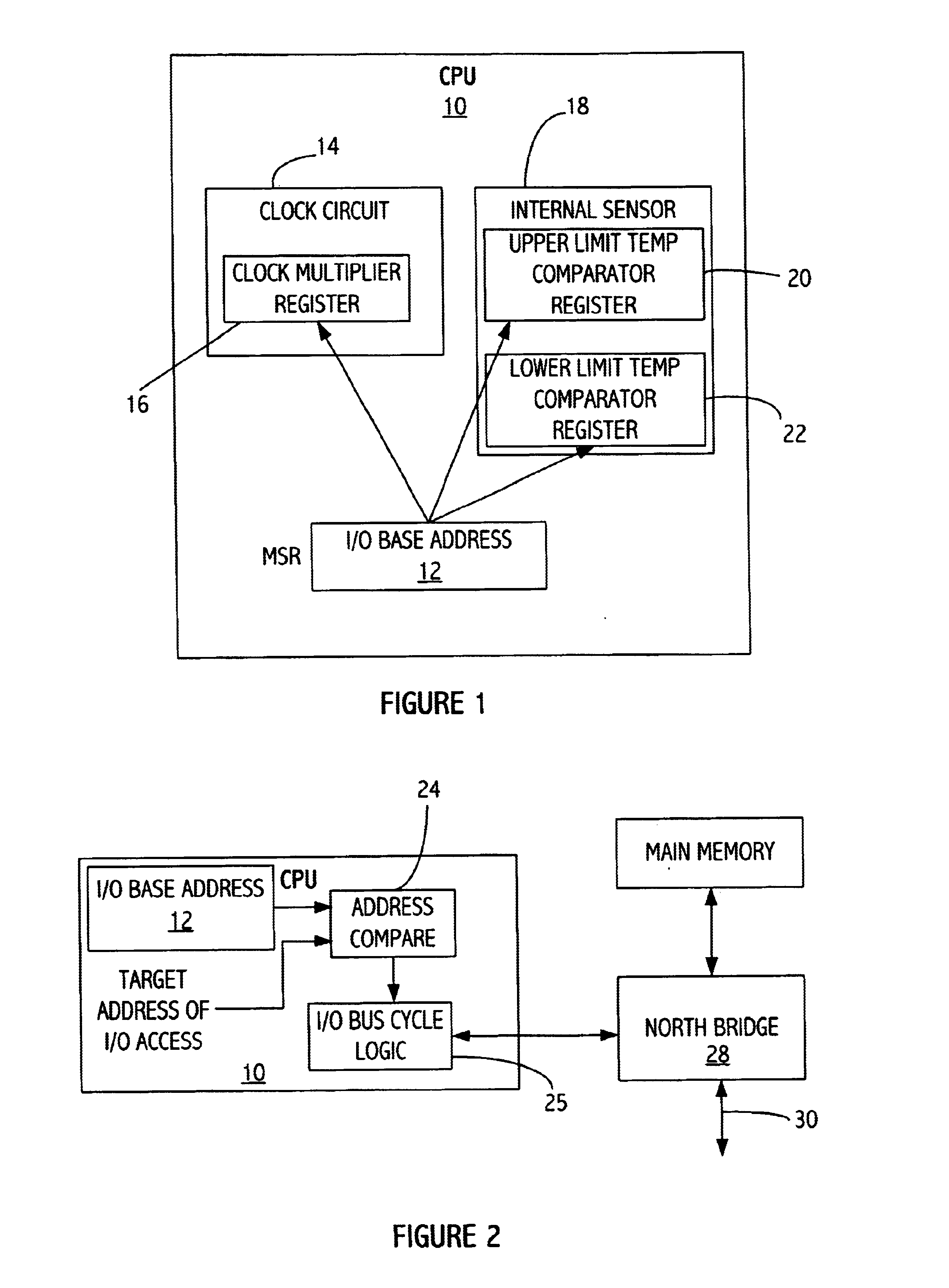

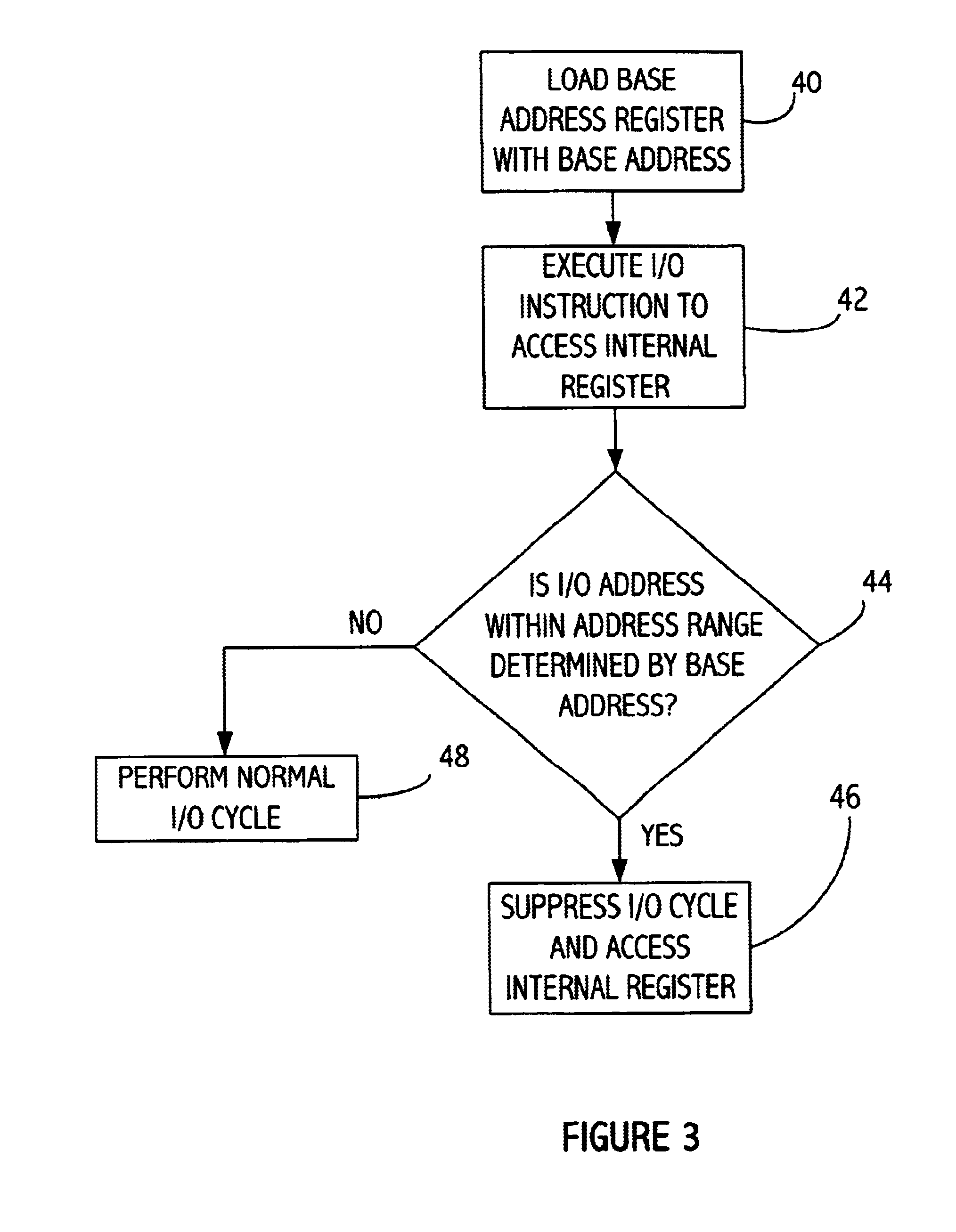

Using a model specific register as a base I/O address register for embedded I/O registers in a processor

InactiveUS6711673B1Memory adressing/allocation/relocationDigital computer detailsPage address registerProcessor register

A processor includes an input / output (I / O) register that is mapped into input / output (I / O) address space. The processor also includes a base address register that is loaded with a base address. The base address register may be a model specific register (MSR). The input / output register is accessed with an input / output instruction at an address determined according to the base address and an offset therefrom. The base address register may be accessible to software operating at a high privilege level and not accessible to software operating at a lower privilege level, while the I / O register is accessible to software operating at the lower privilege level. The processor determines when an I / O access is to the processor I / O register and accesses that I / O register without causing an input / output bus cycle that would otherwise occur.

Owner:GLOBALFOUNDRIES INC

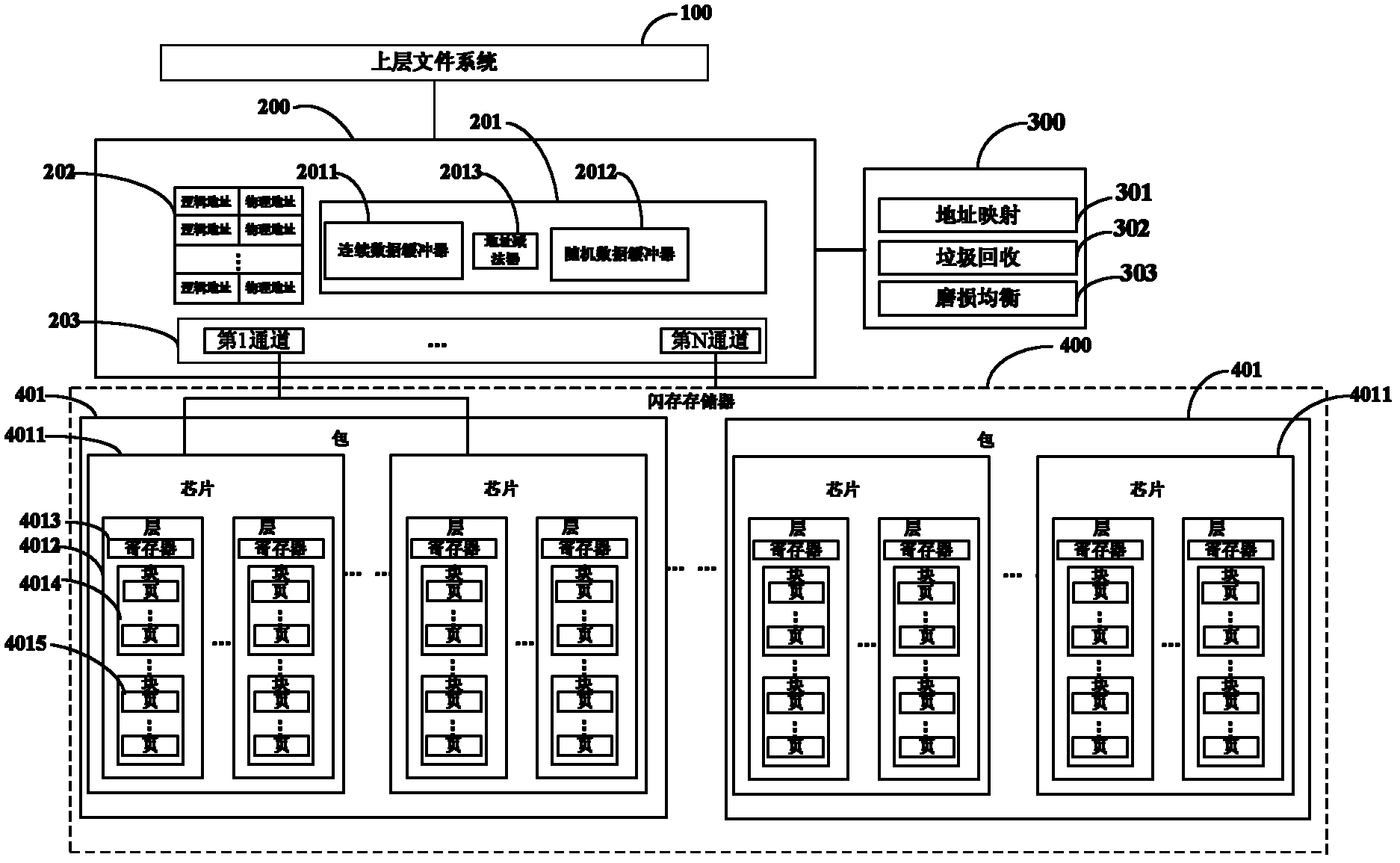

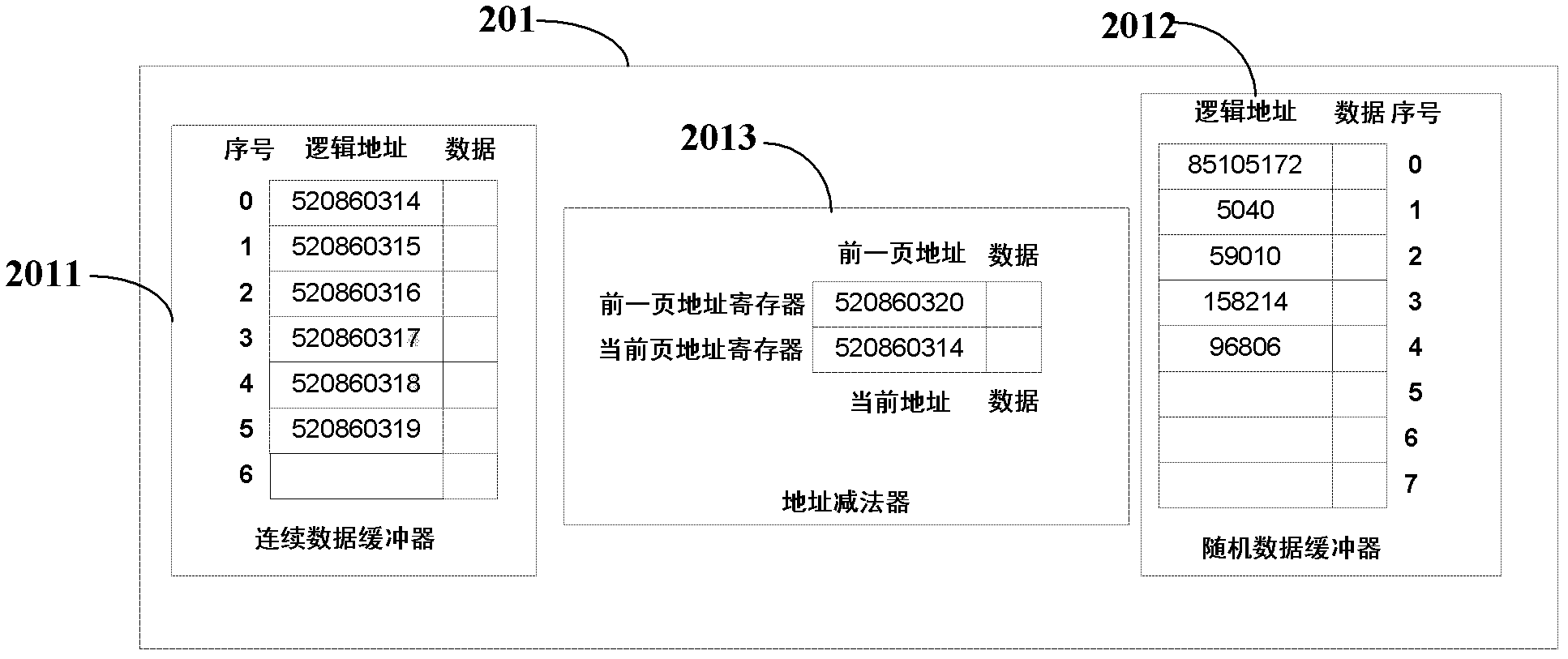

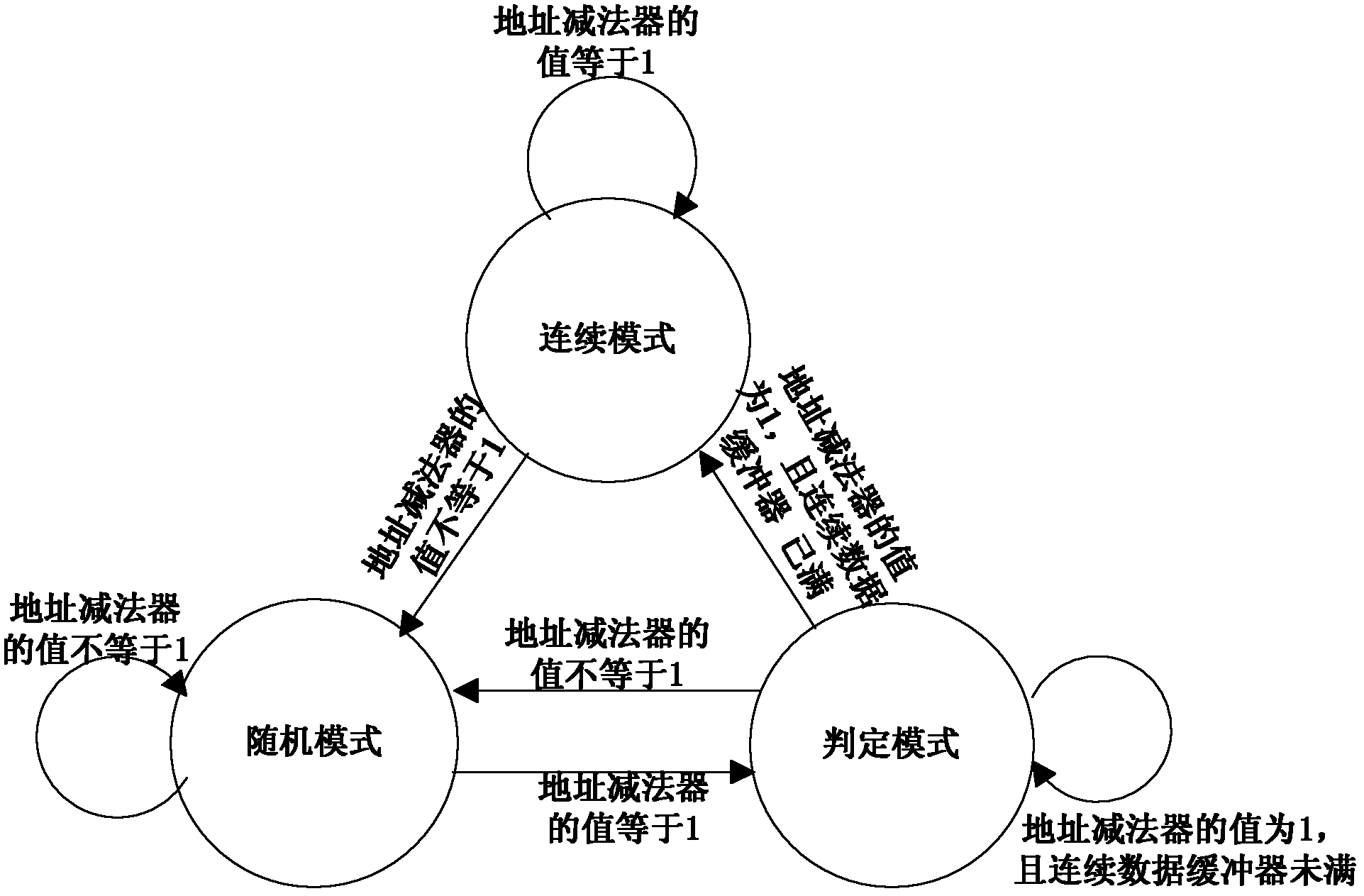

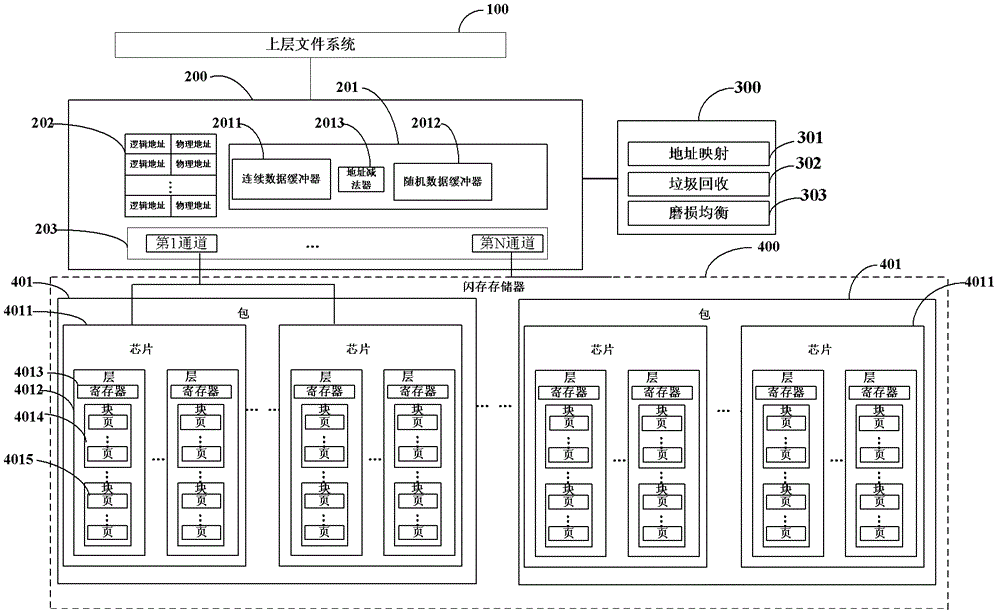

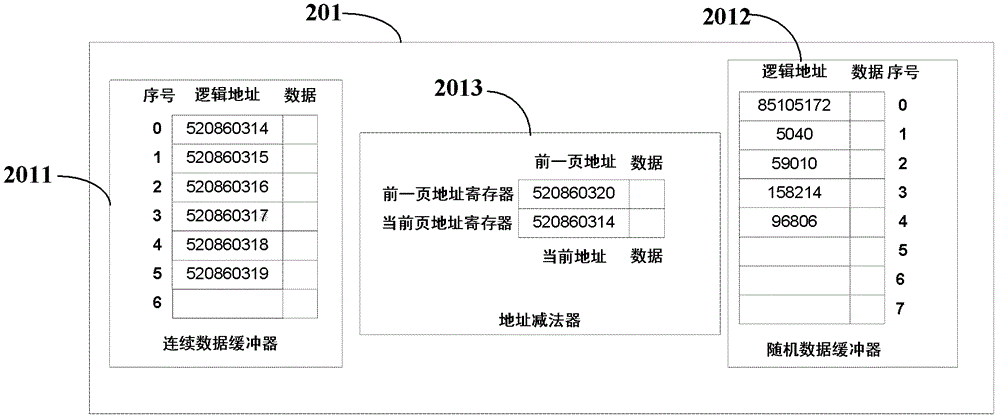

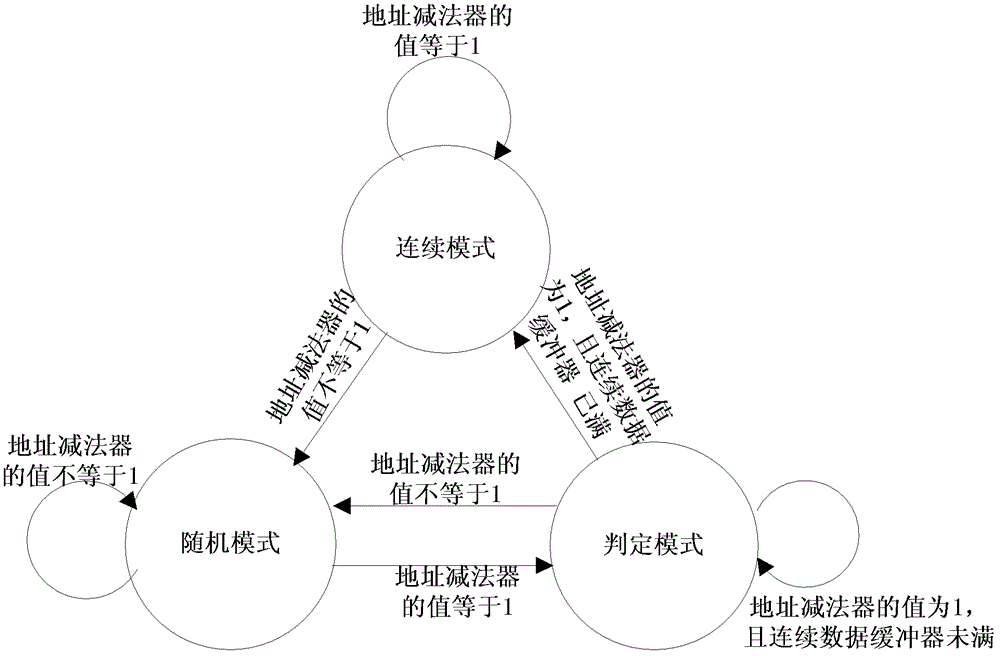

Write buffer detector, addressing method of written data and parallel channel write method

InactiveCN102521160AAvoid misjudgmentPrevent missed judgmentInput/output to record carriersMemory adressing/allocation/relocationPage address registerWrite buffer

The invention provides a solid state disk (SSD) controller based on a write buffer detector, an addressing method of written data and an optional parallel channel write method, which achieve accurate judgment on address characteristics of data, respectivelycache continuous address data and random address data, write different write strategies according to different data types, and improve write speed of random data. The write buffer detector comprises an address subtractor, a continuous data buffer and a random data buffer, wherein the address subtractor is used for conducting subtraction on current page addresses and previous page addresses and comprises a previous page address register and a current page address register, the previous page address register is used for storing data and addresses at the previous page, and the current page address register is used for storing data and addresses at the current page; the size of the continuous data buffer is set to be a parameter Sequential-Buffer-Size, the continuous data buffer is used for caching data which is probably judged to be continuous access data, and data in the continuous data buffer is judged to be continuous data if the length of data in the continuous data buffer reaches the set parameter; and the random data buffer is used for caching random access data.

Owner:SHANGHAI JIAO TONG UNIV

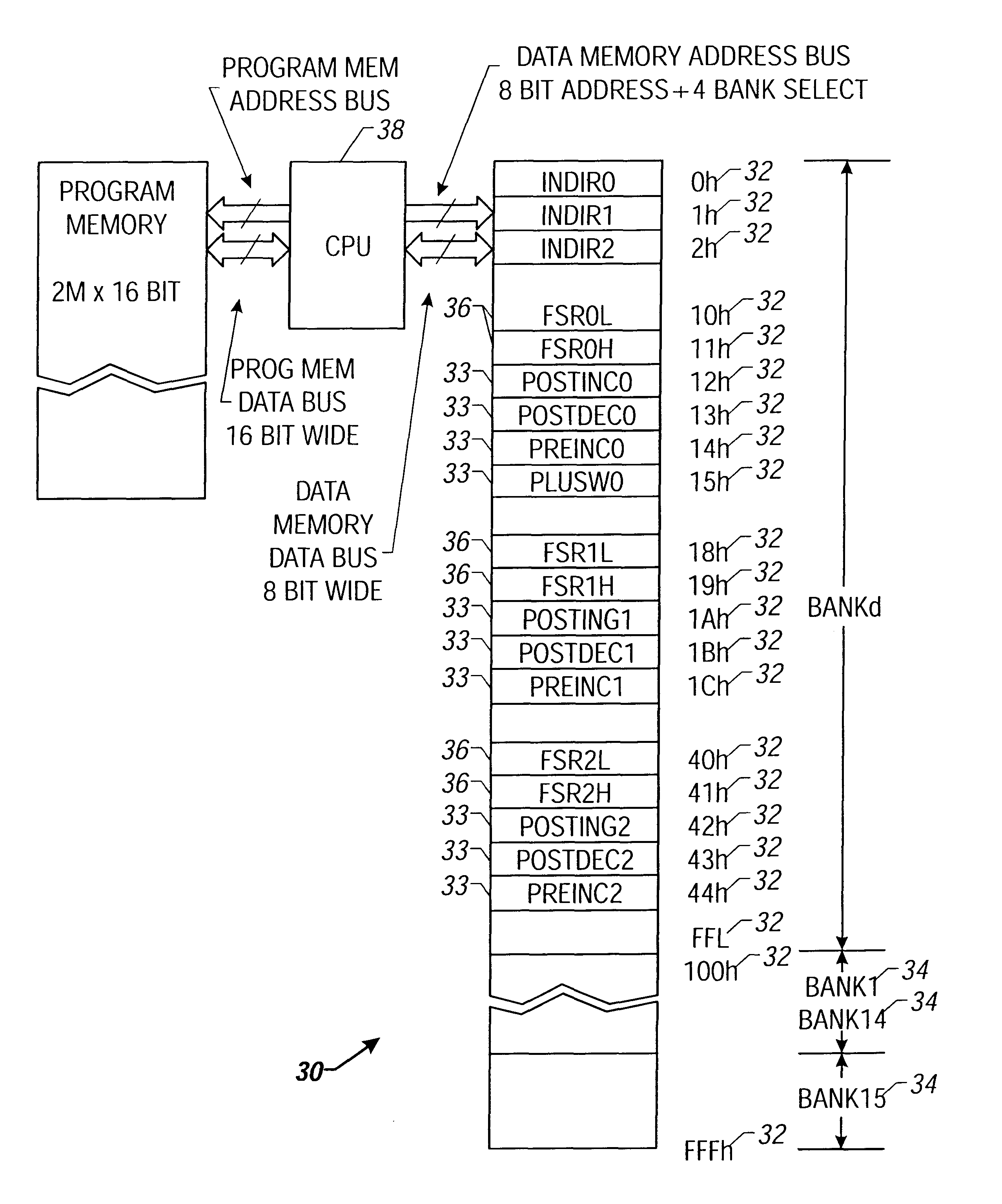

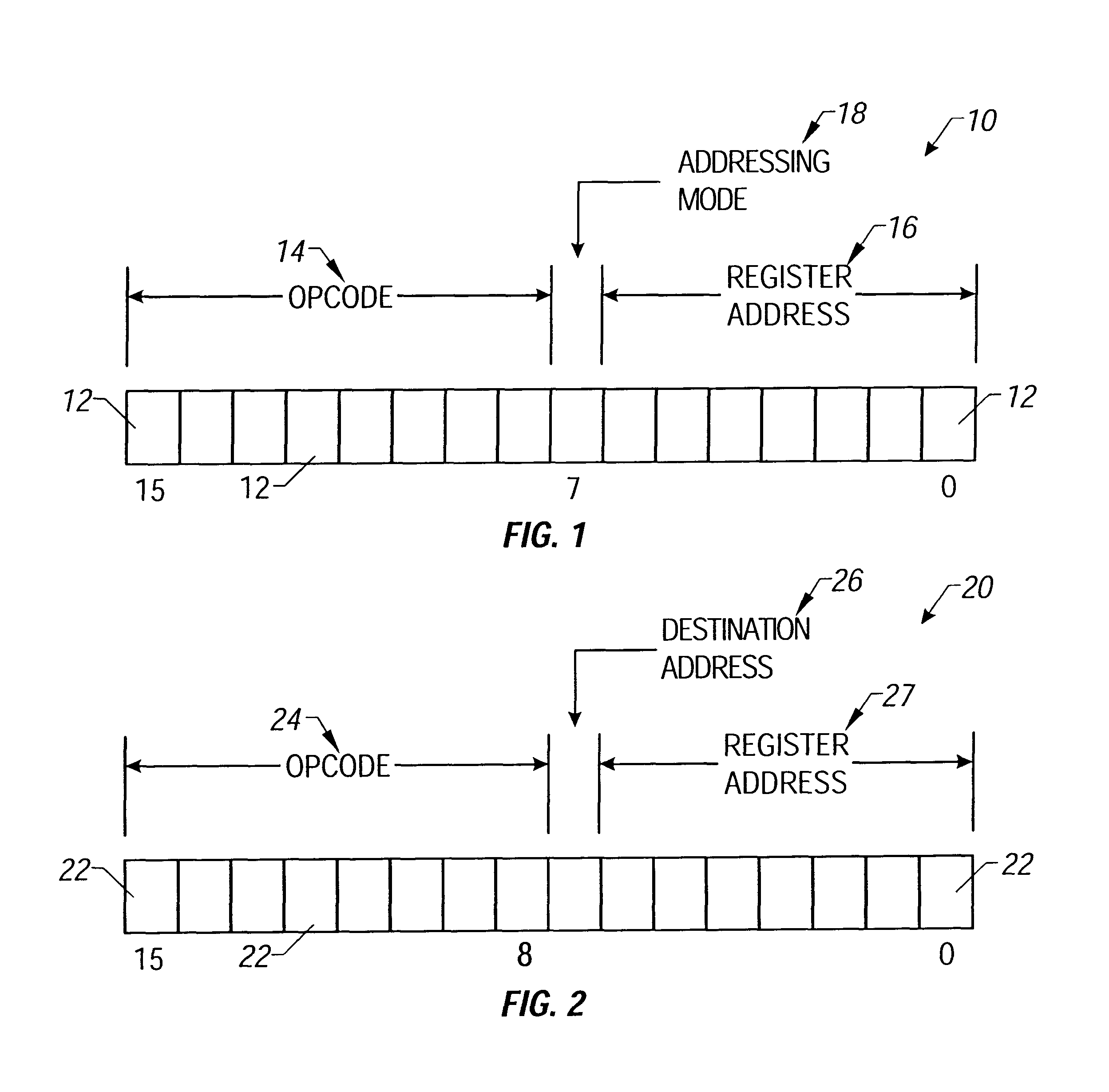

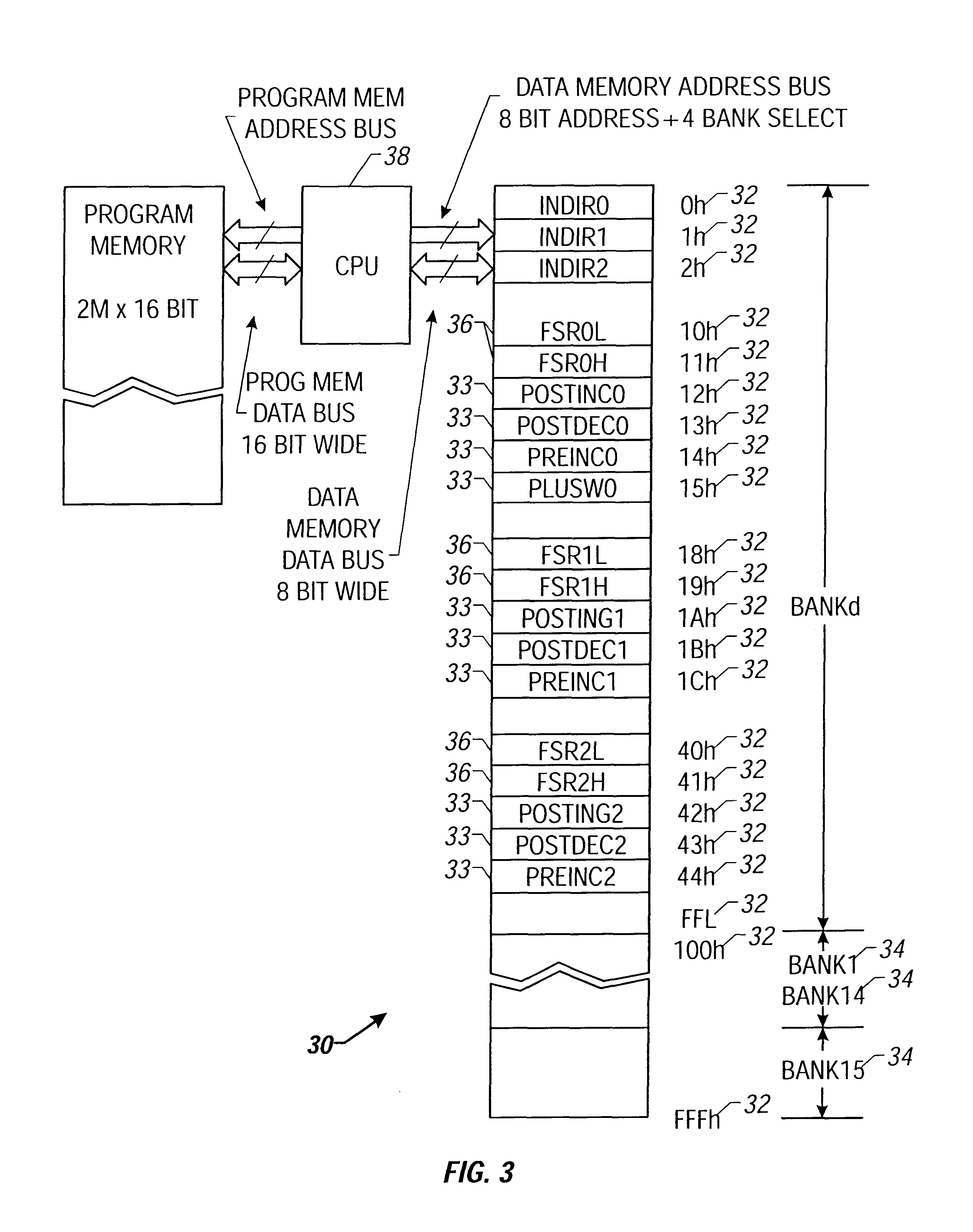

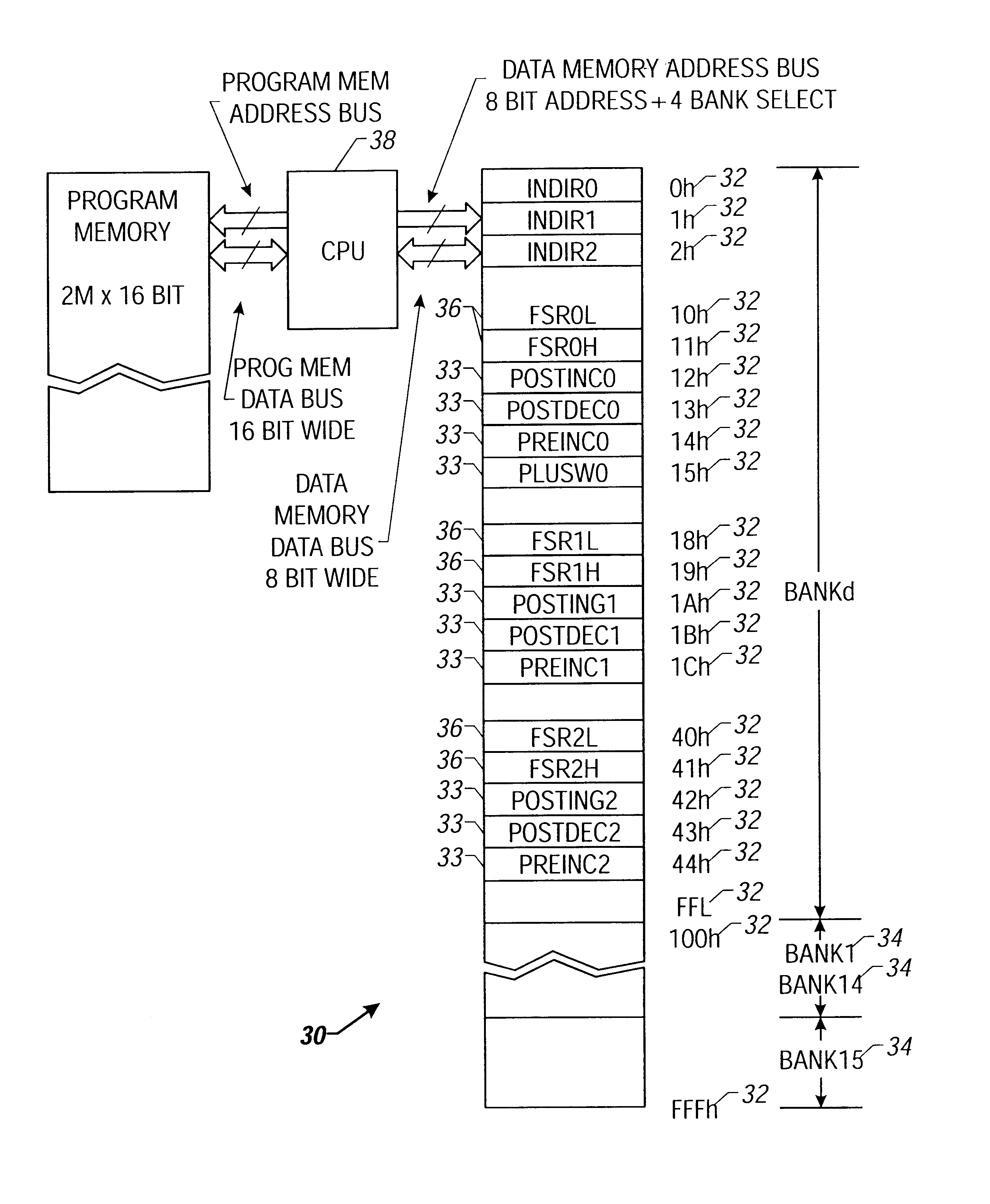

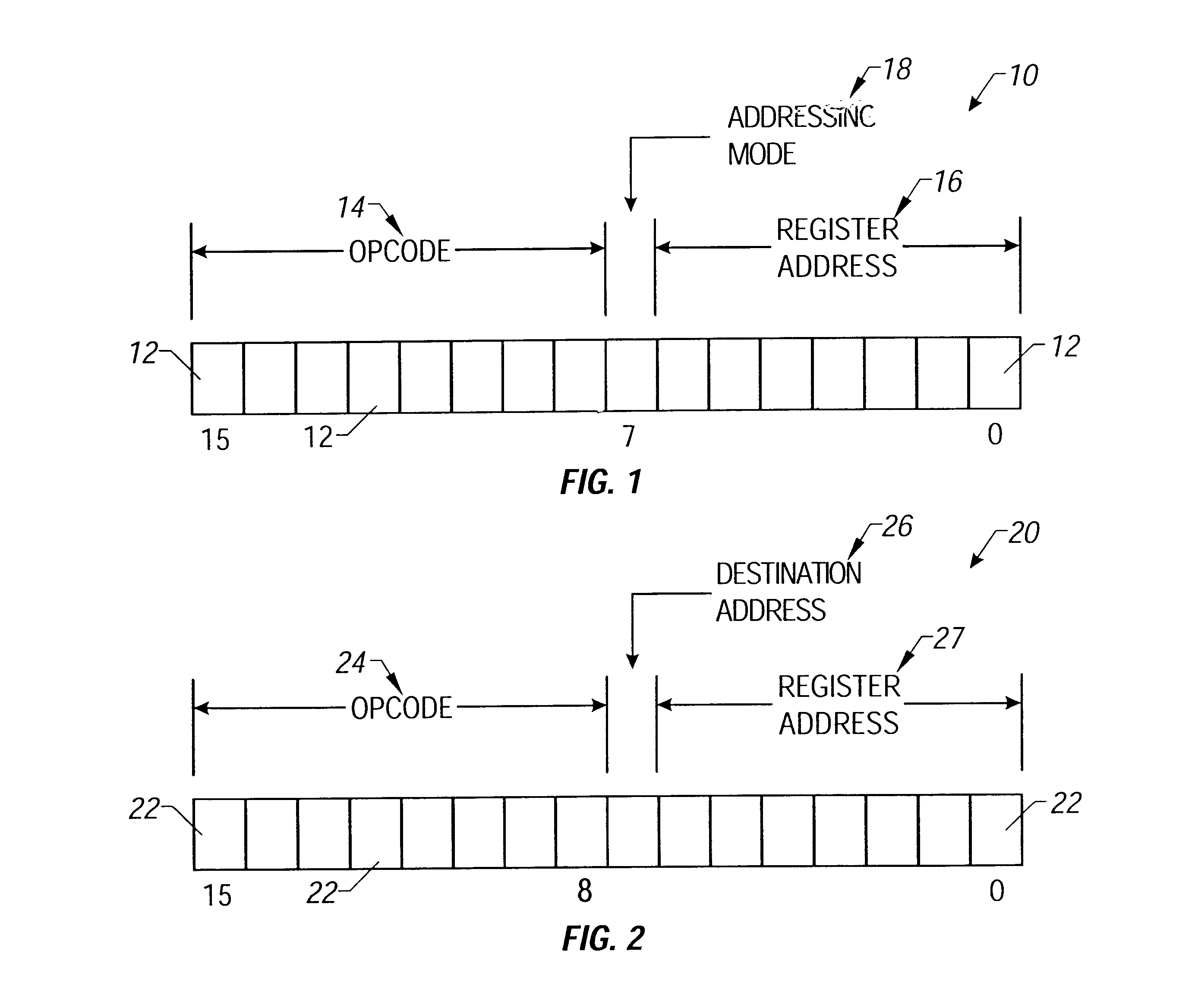

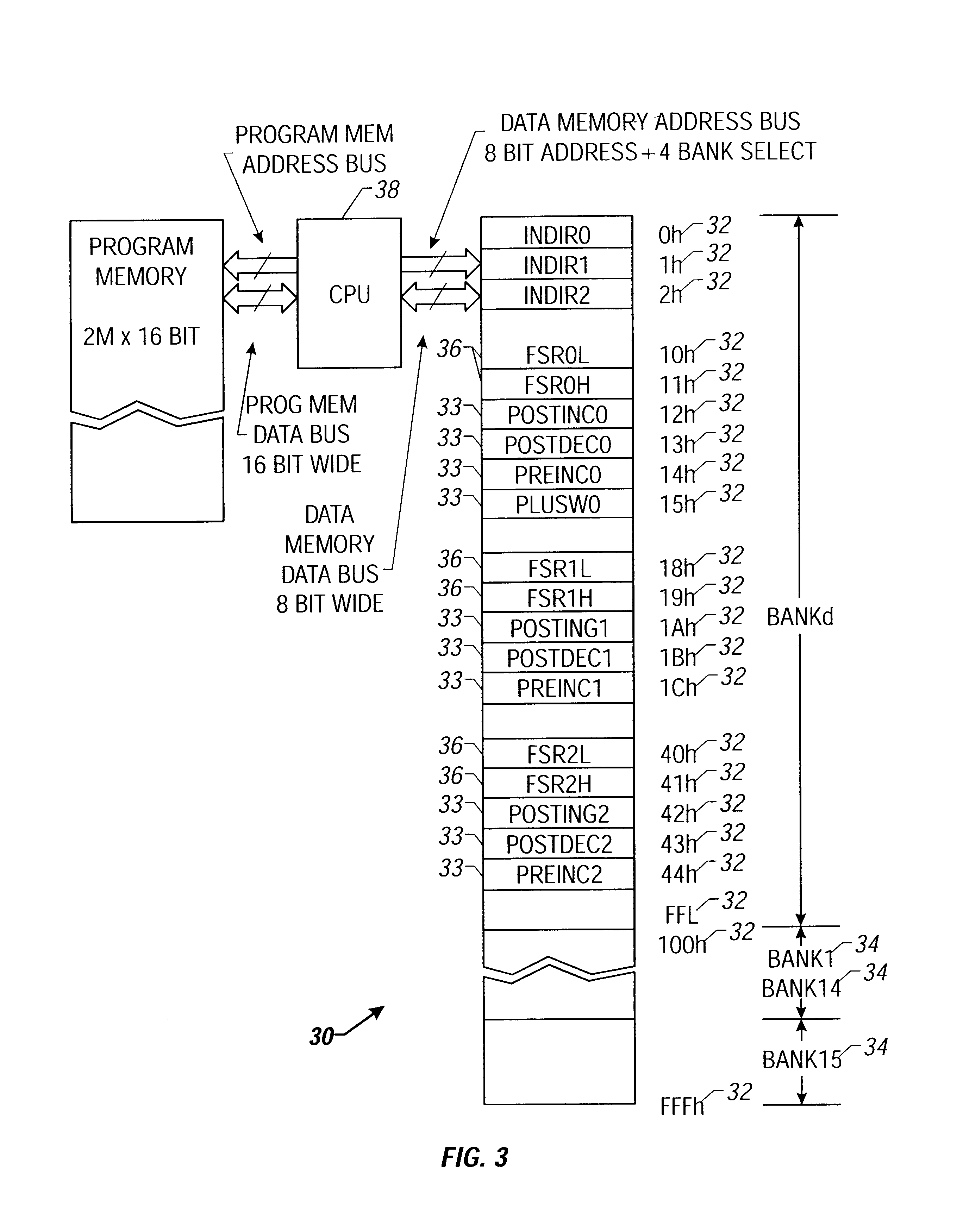

Processor architecture scheme which uses virtual address registers to implement different addressing modes and method therefor

InactiveUS6192463B1Instruction analysisGeneral purpose stored program computerPage address registerComputer architecture

A processor architecture scheme which allows for encoding of multiple addressing modes through use of virtual register addresses in order to maximize number of directly addressable registers in the processor architecture scheme. A set of virtual address register locations associated with an indirect addressing pointer is reserved in memory. The number of virtual register address locations reserved is equal to a number of indirect addressing modes associated with the indirect addressing pointer. Each of the virtual register address locations initiates an indirect addressing mode to be used with the associated indirect addressing pointer when accessed.

Owner:MICROCHIP TECH INC

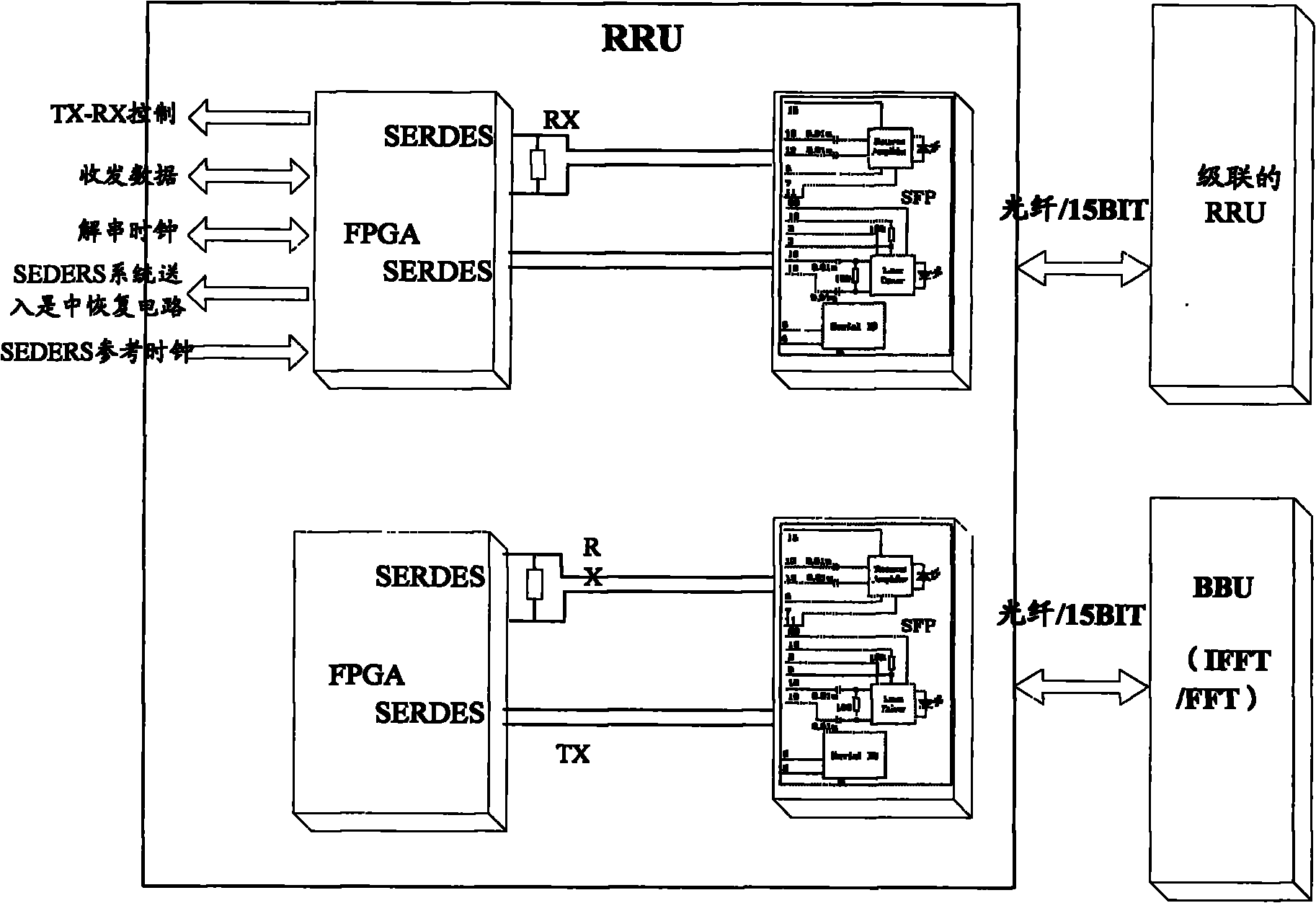

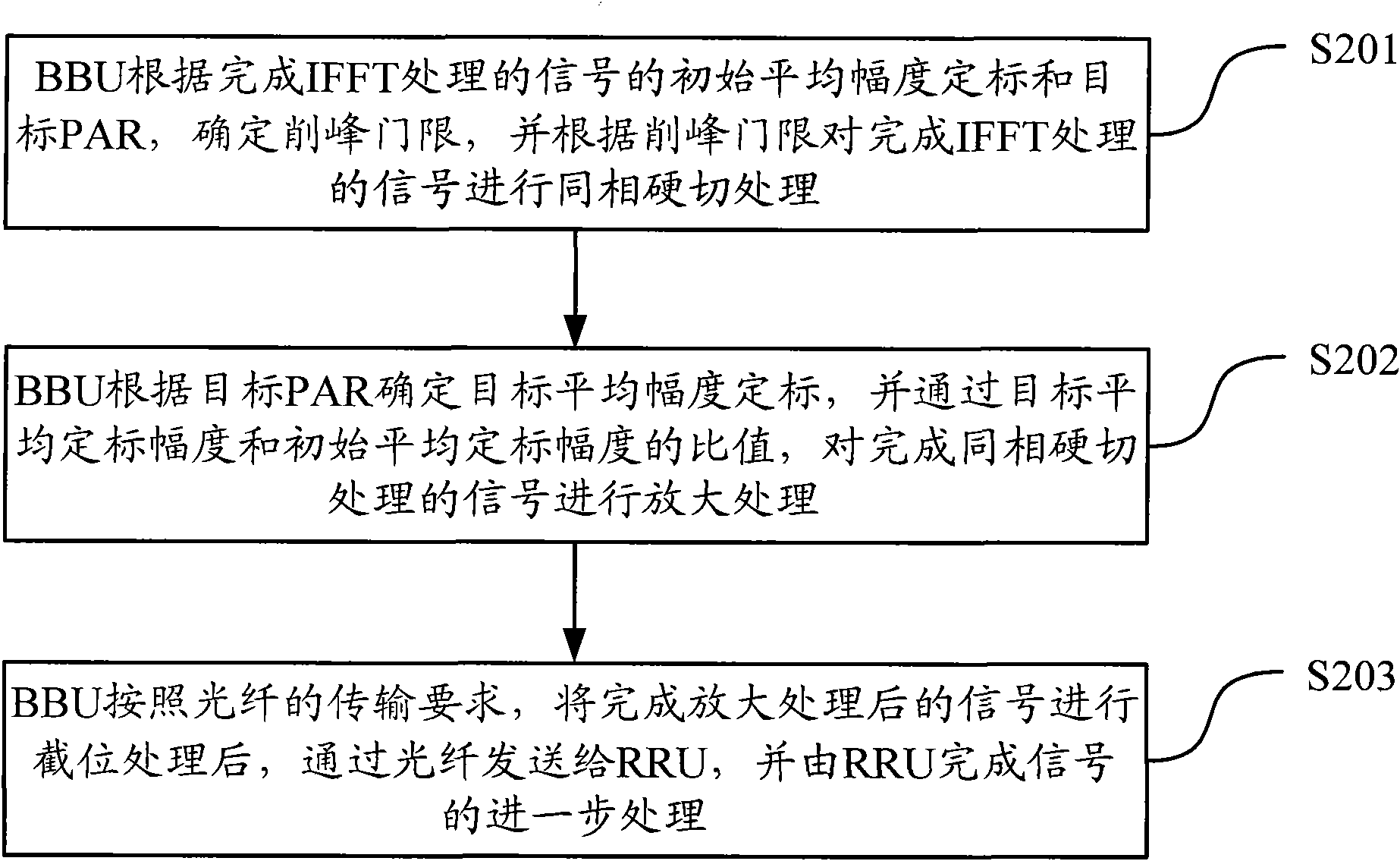

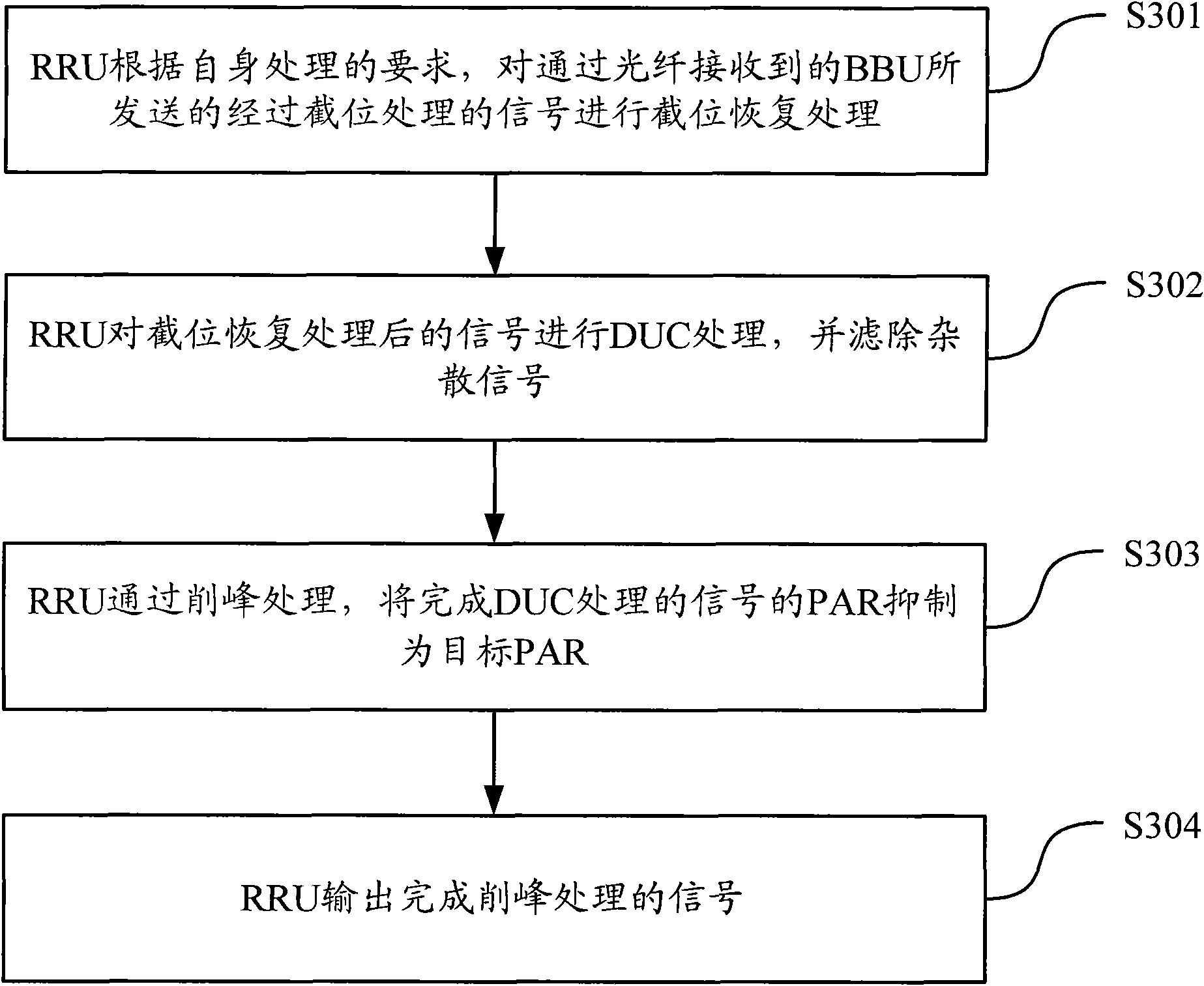

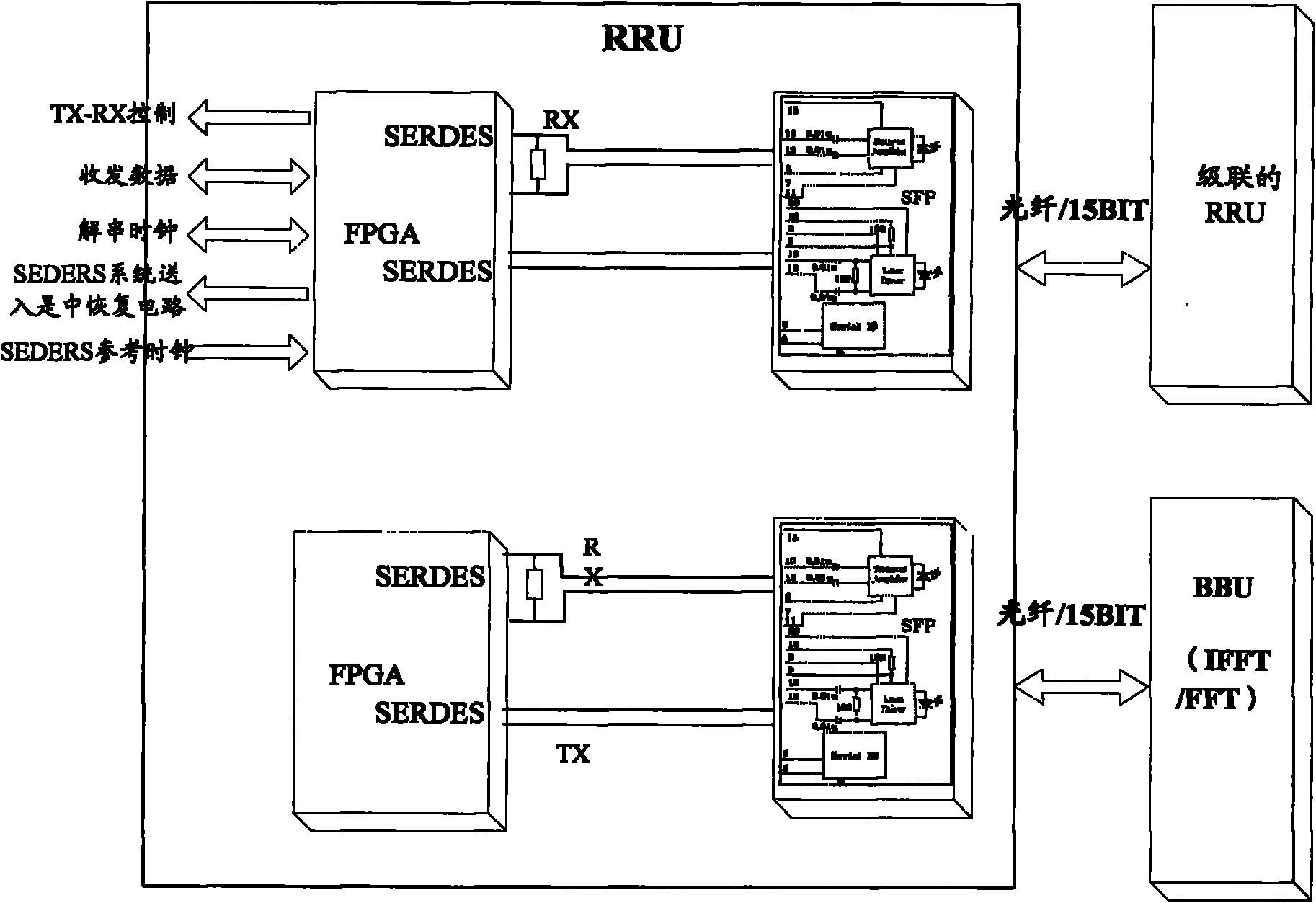

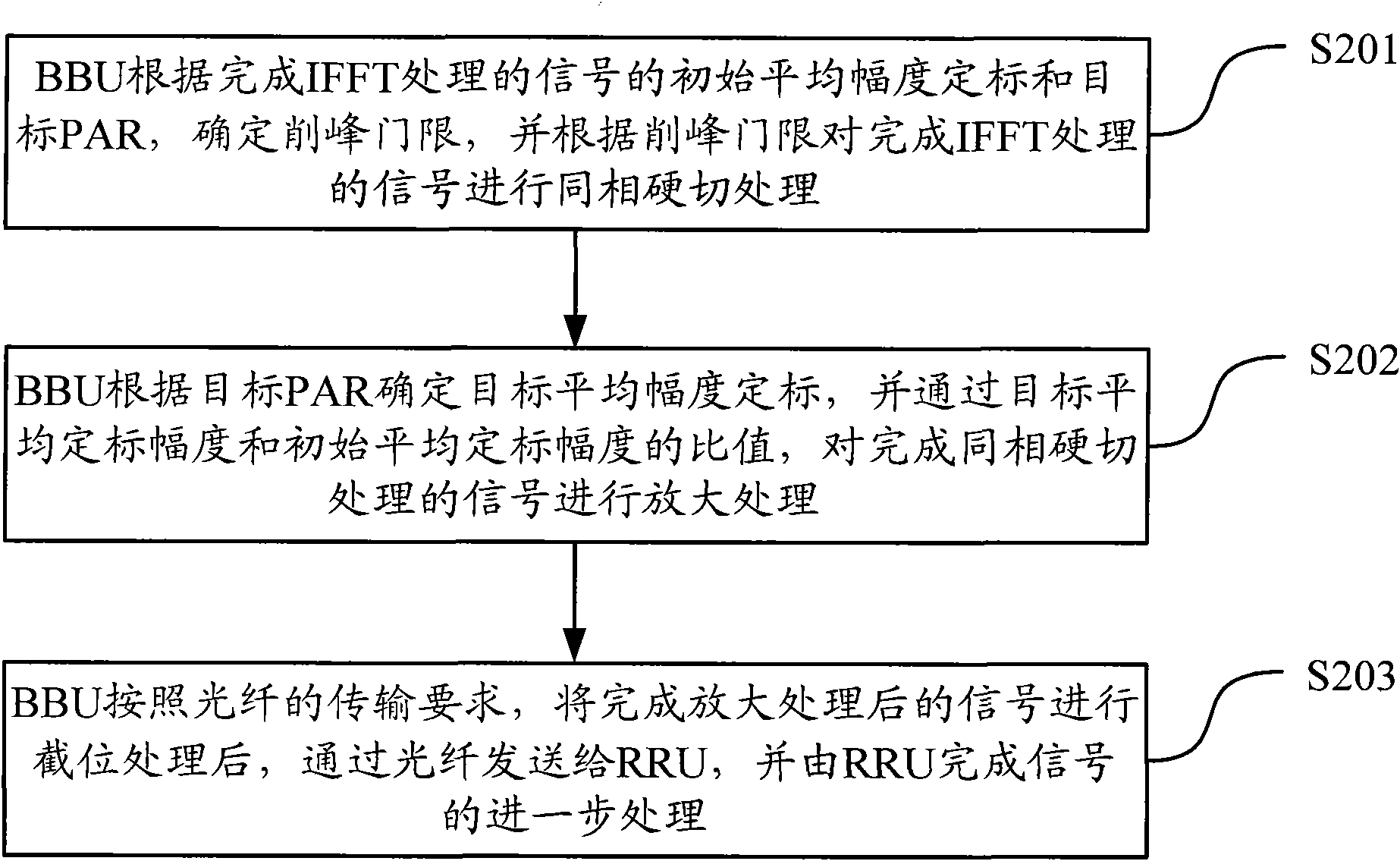

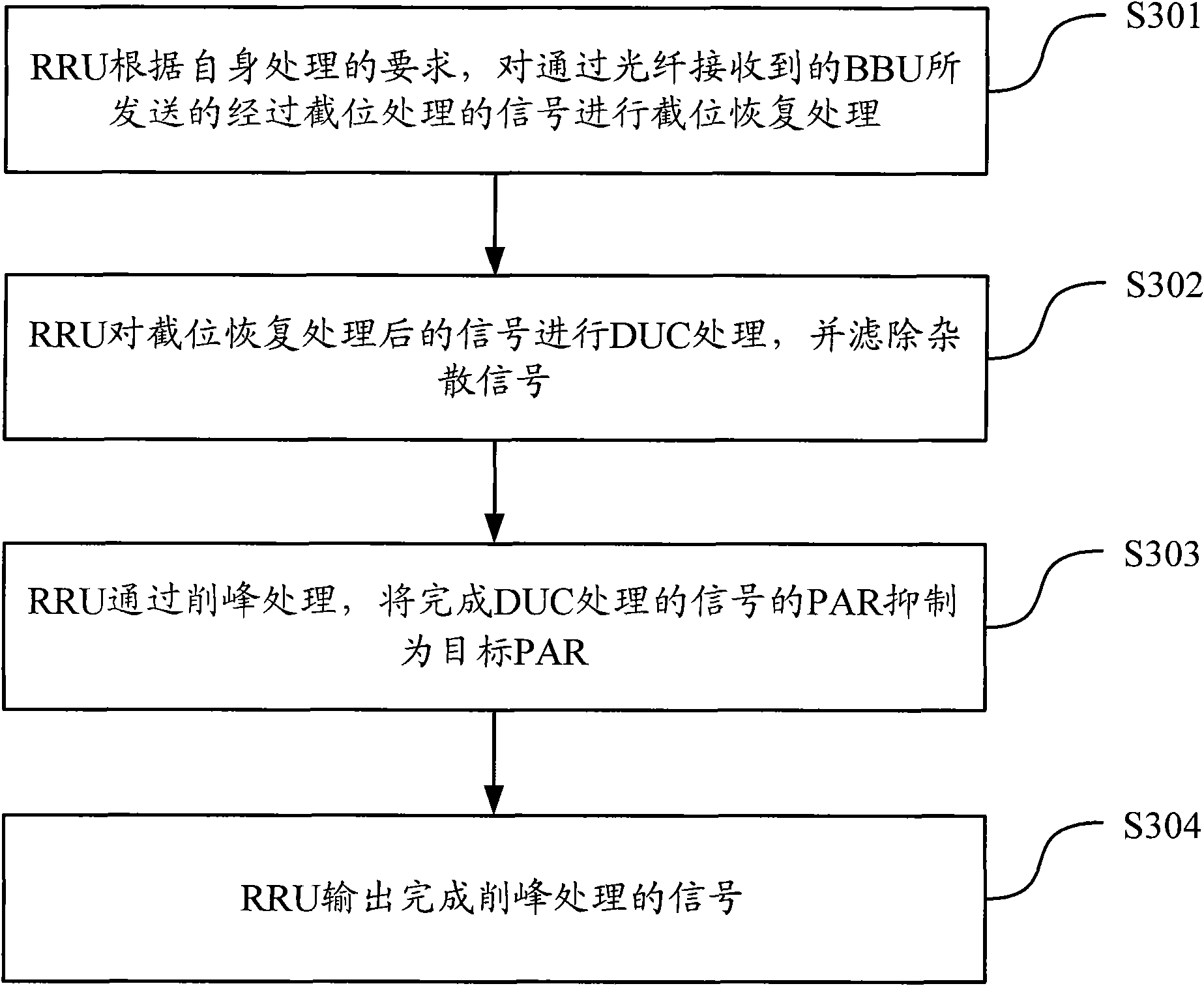

Signal transmission method, device and system in baseband remote scene

ActiveCN102340471AEnhanced inhibitory effectAddressing loss of precisionMulti-frequency code systemsElectromagnetic repeatersPage address registerFiltration

The embodiment of the invention discloses a signal transmission method, device and system in a baseband remote scene. According to the technical scheme disclosed by the embodiment of the invention, the method comprises the steps as follows: a BBU (building baseband unit) lowers the calibrated value of initial average amplitude output by a physical layer through IFFT (inverse fast Fourier transform); cutting treatment is carried out on the average amplitude according to fiber transmission requirements after carrying out in-phase hard cutting on the raising signal; and stray filtration and peak clipping treatment are carried out in an RRU (remote radio unit), so that the signal subjected to IFFT in an LTE-TDD (Long Term Evolution-Time Division Duplex) system can not overflow, and the signal accuracy is not lost when the signal is transferred through the fiber. By using the physical layer in-phase hard cutting / intermediate frequency peak clipping combined treatment scheme, the deterioration of EVM (error vector magnitude) is smaller, and the inhibitory effect on PAR (page address register) is more obvious, thereby solving the problem of overhigh average ratio of accuracy loss to signal peak in the digital signal transferring process between the BBU and the RRU in the prior art.

Owner:DATANG MOBILE COMM EQUIP CO LTD

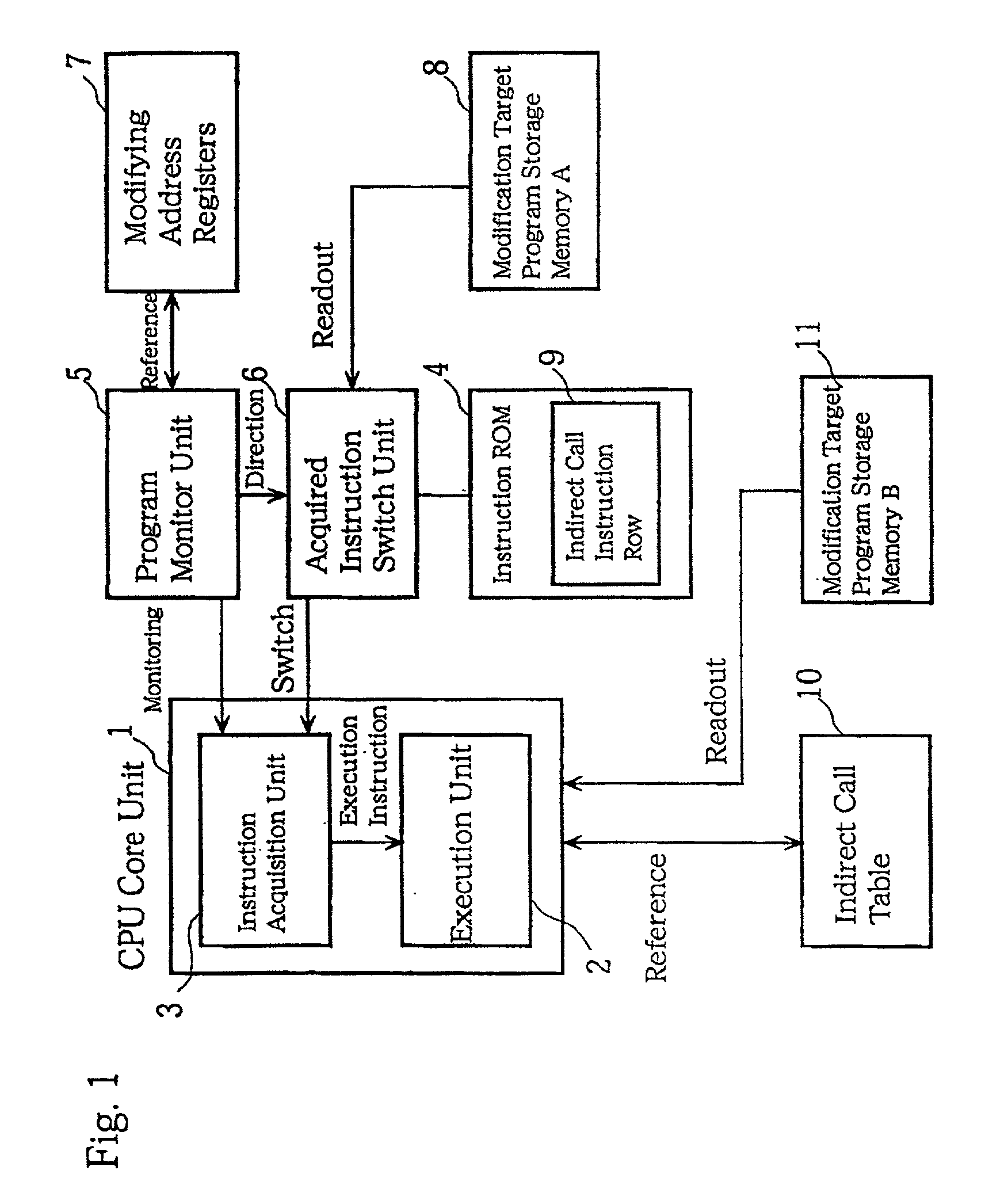

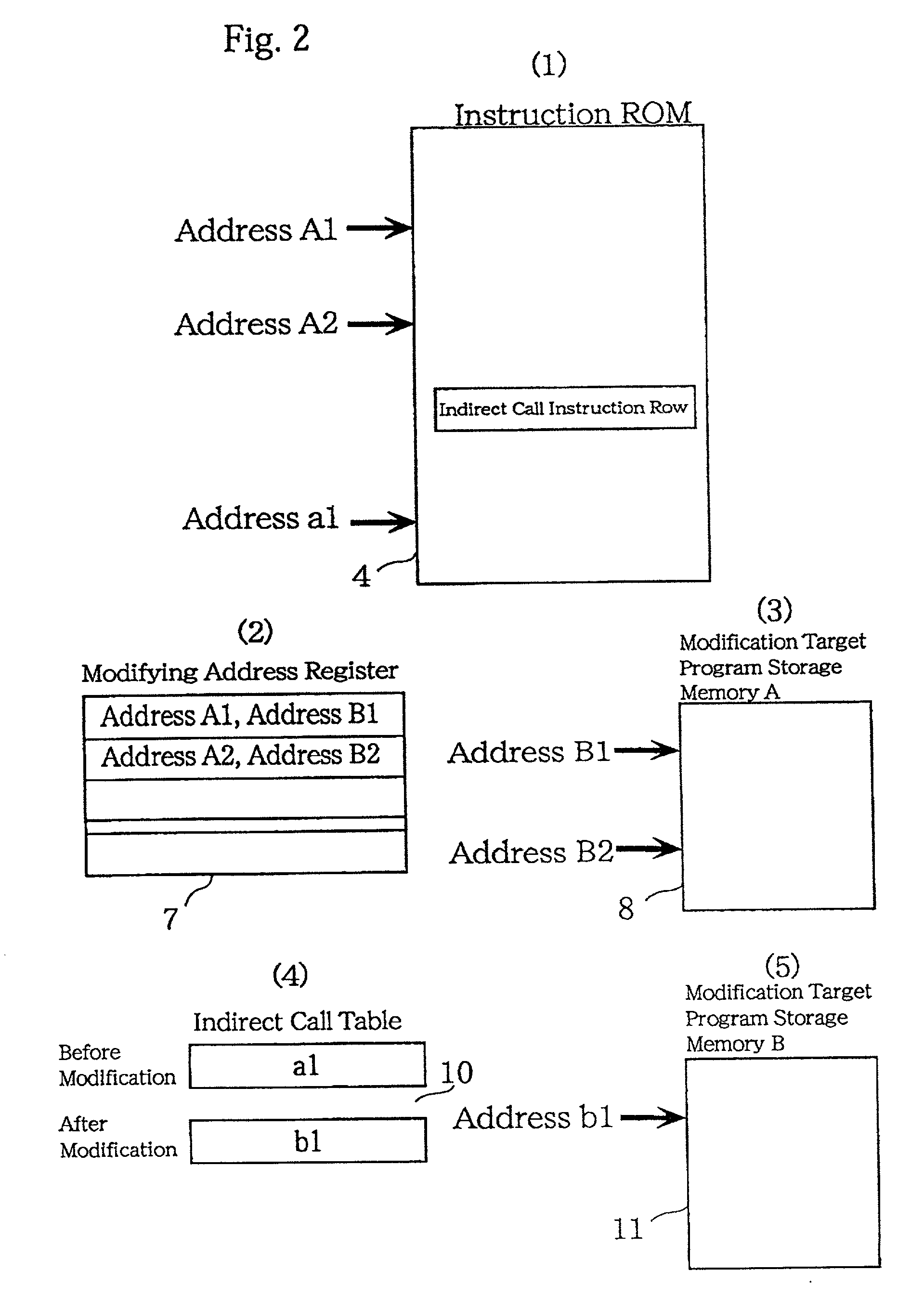

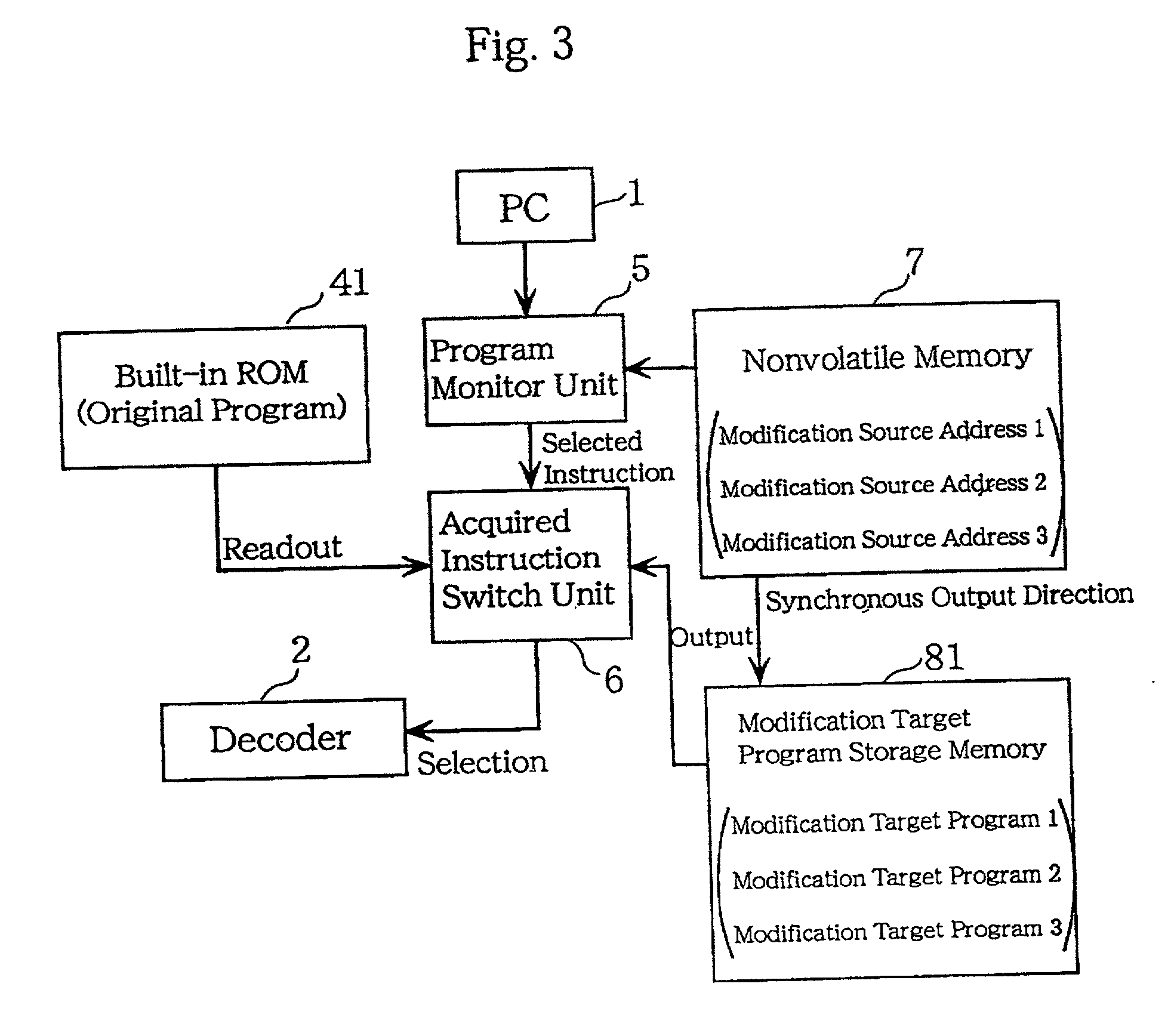

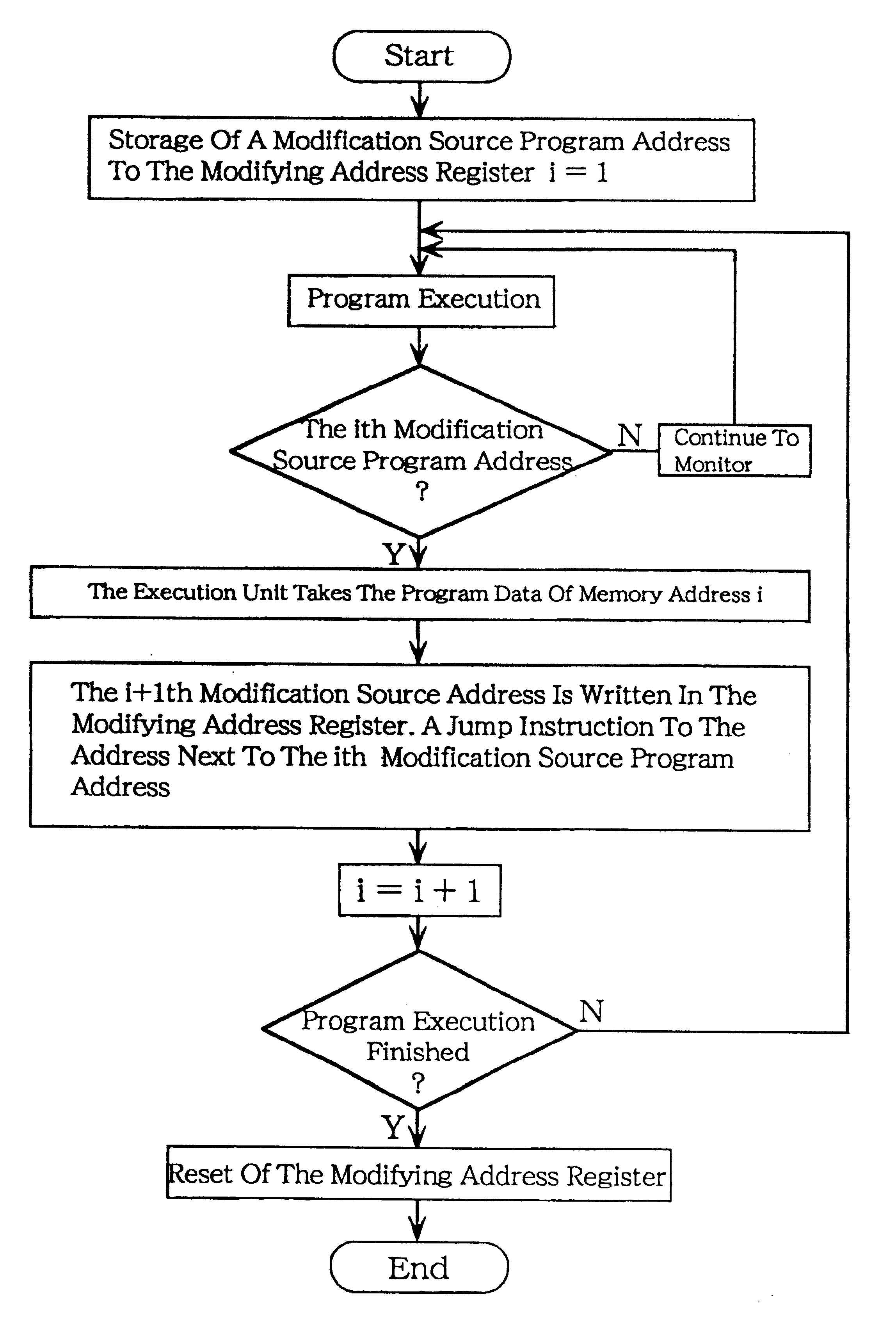

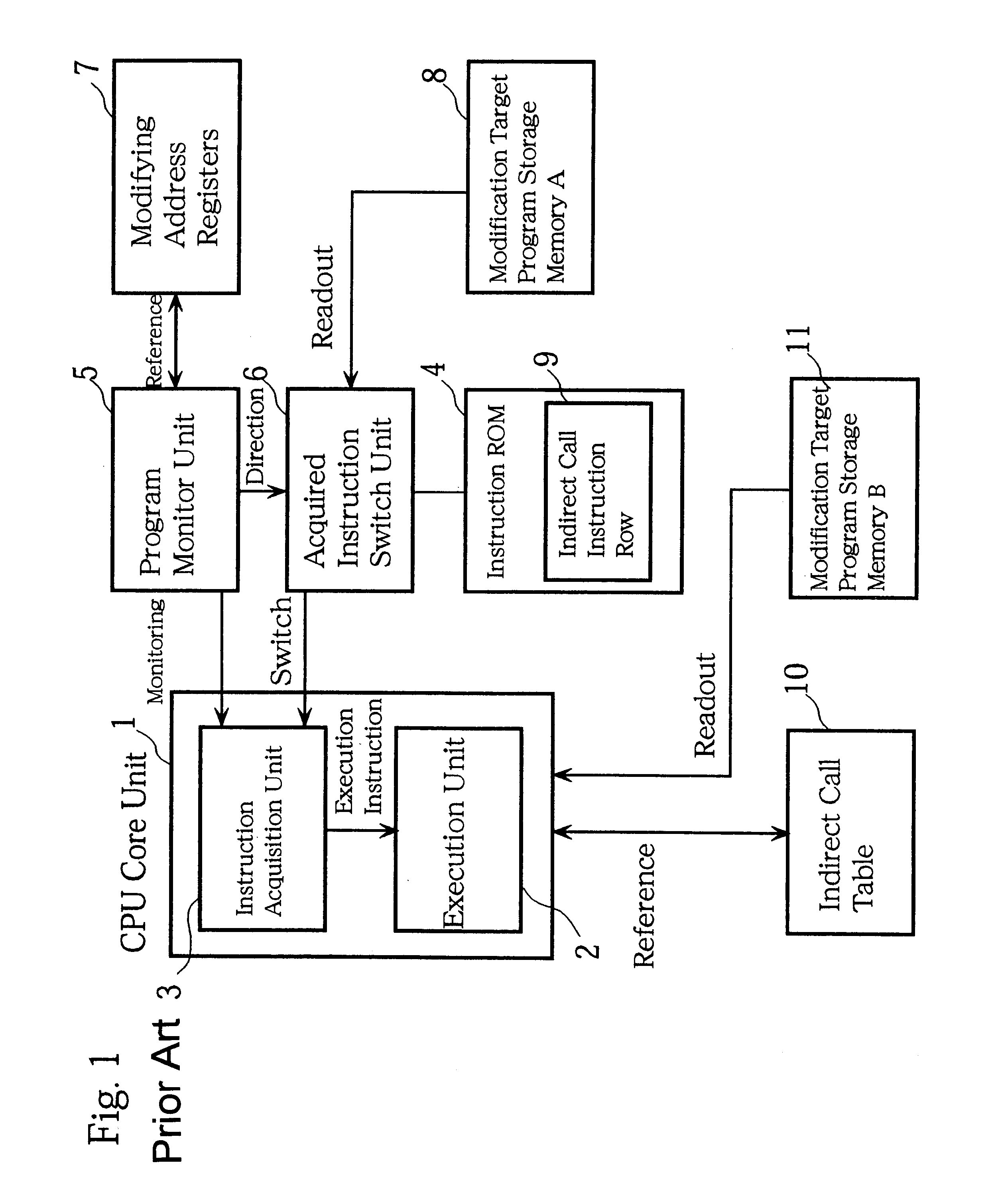

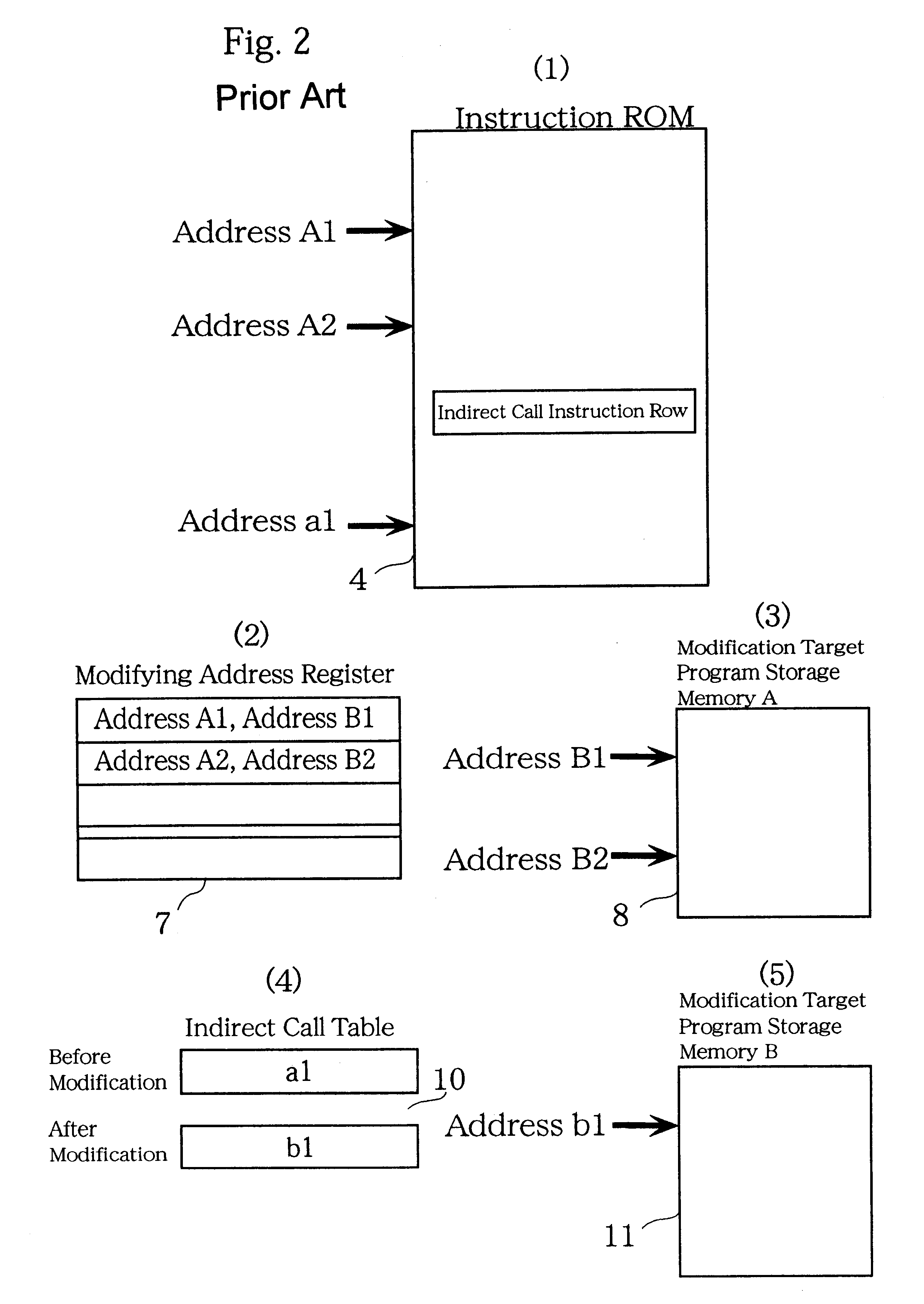

Program modification device

InactiveUS20010007124A1Program control using stored programsMemory adressing/allocation/relocationPage address registerProcessor register

In modifying a program fixedly recorded in a ROM or the like, desired positions in the program can be modified with a little hardware. In order to achieve the object, the program modification device comprises the modifying address register 17 which stores the addresses of program data to be modified prior to the execution of the data and the modifying address storage table 19 which stores all the addresses of the modification source programs to be loaded to the modifying address register 17 and all the addresses of the modification target programs in pairs, and further comprises a modification target program having instructions embedded therein so as to load necessary information from the modifying address storage table 19 to the modifying address register 17 before the program to be modified is executed.

Owner:PANASONIC CORP

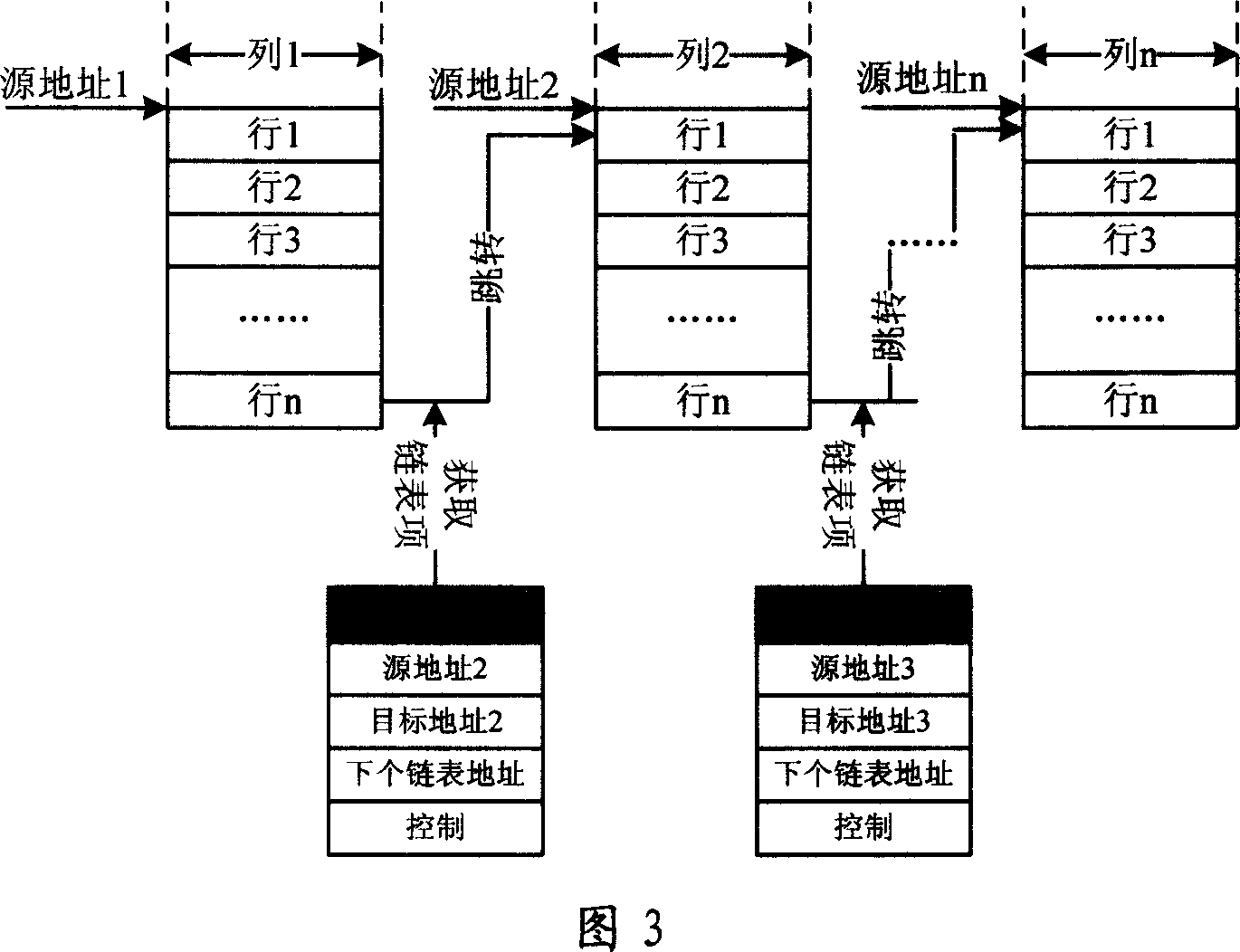

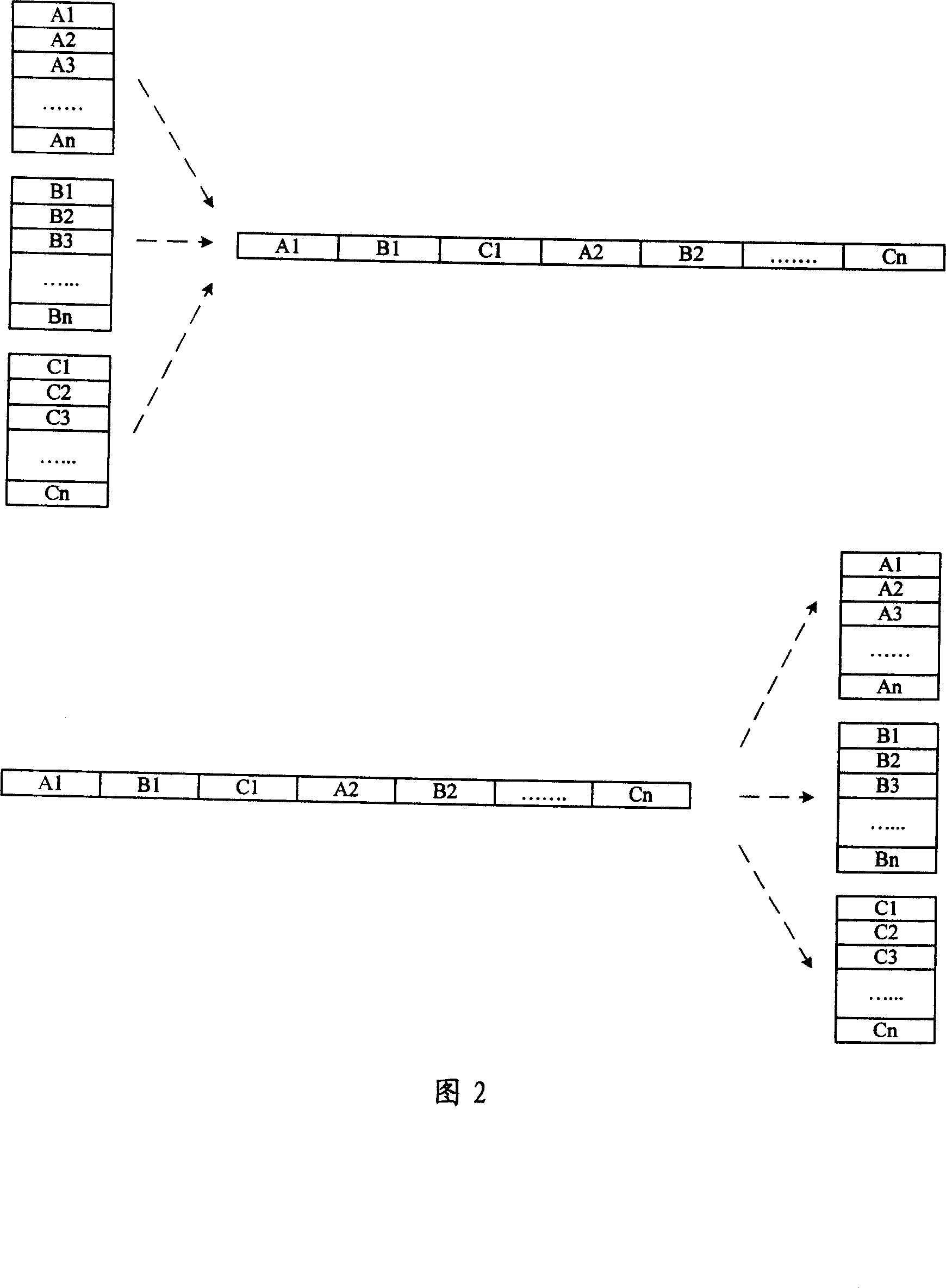

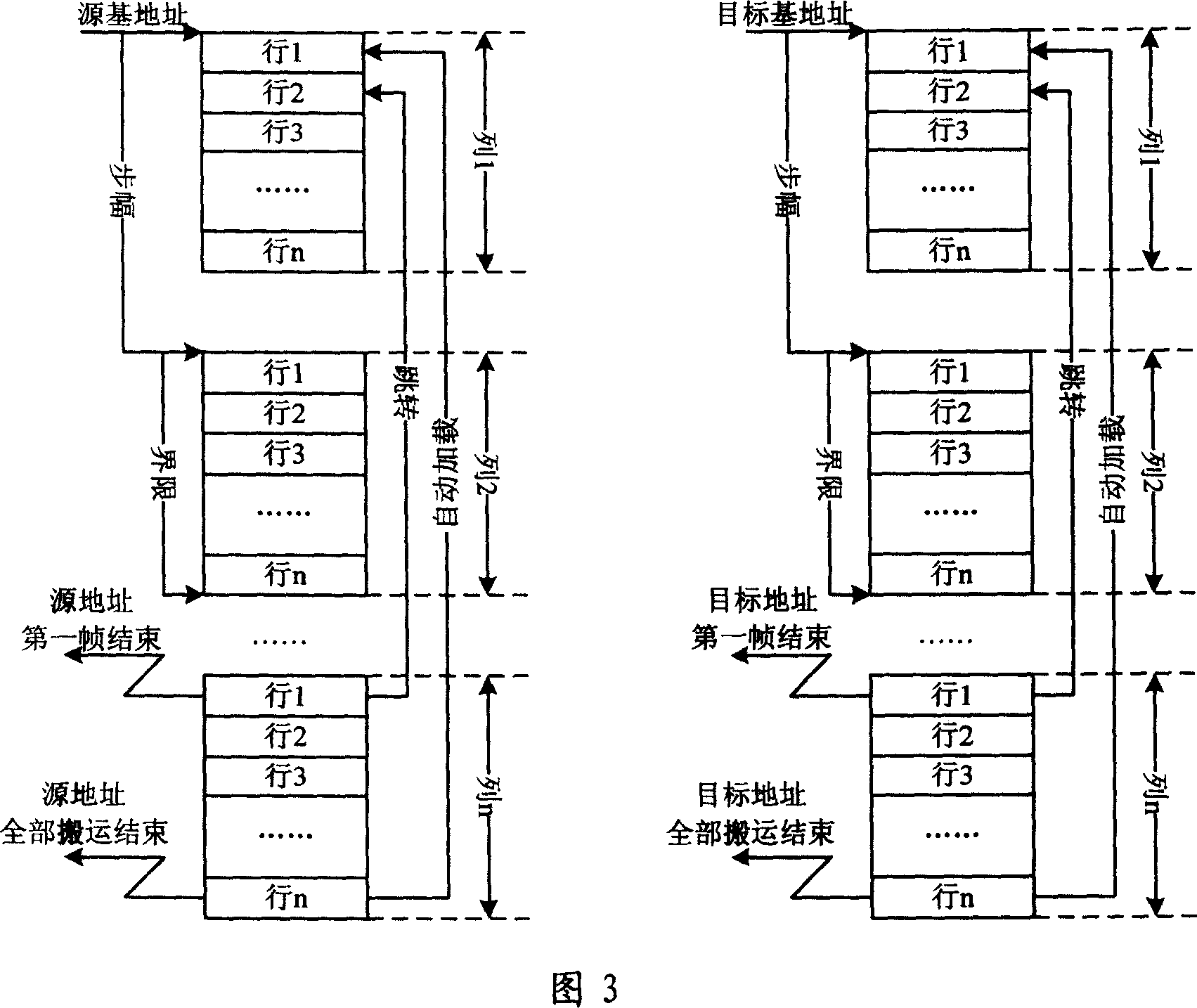

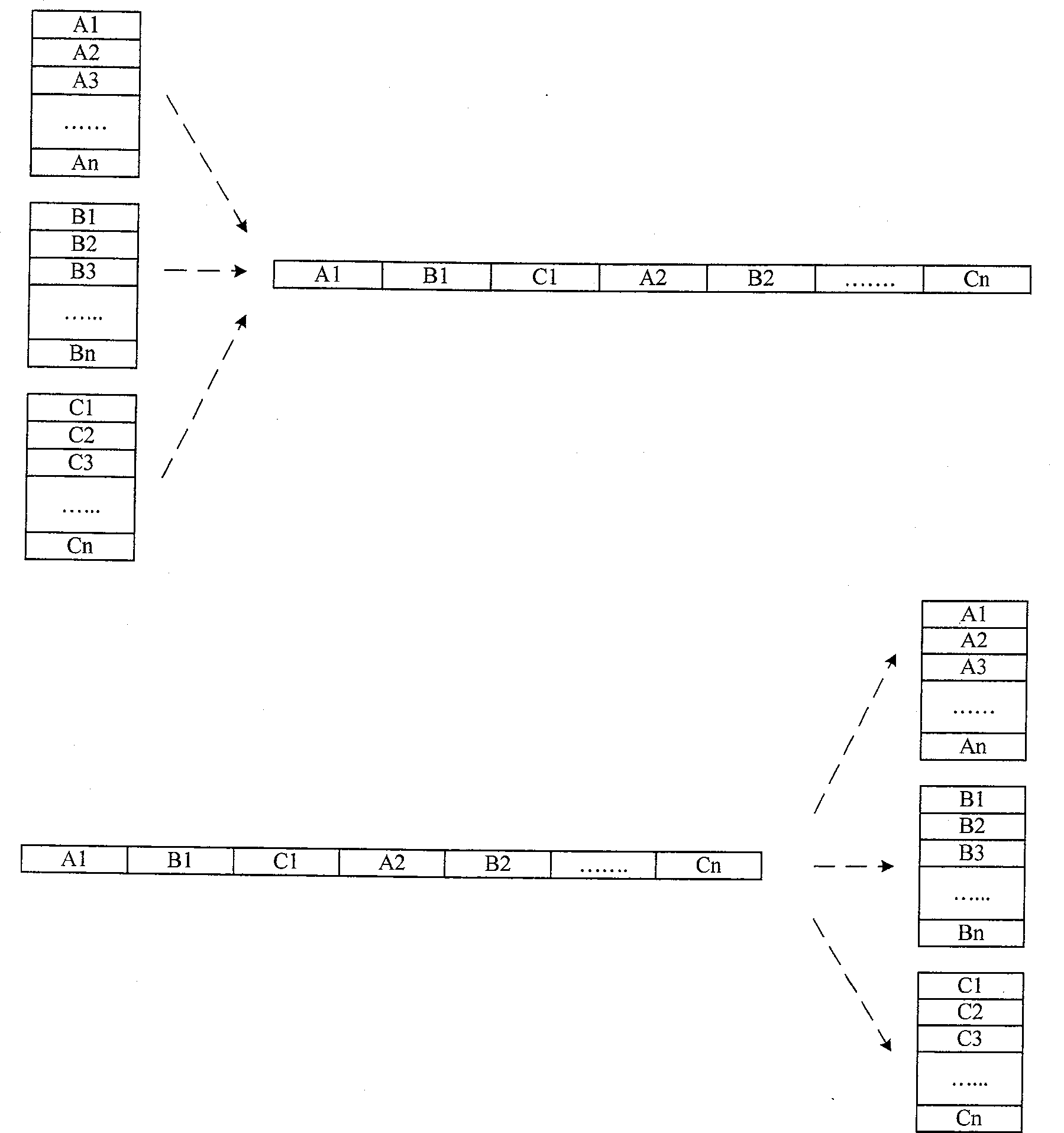

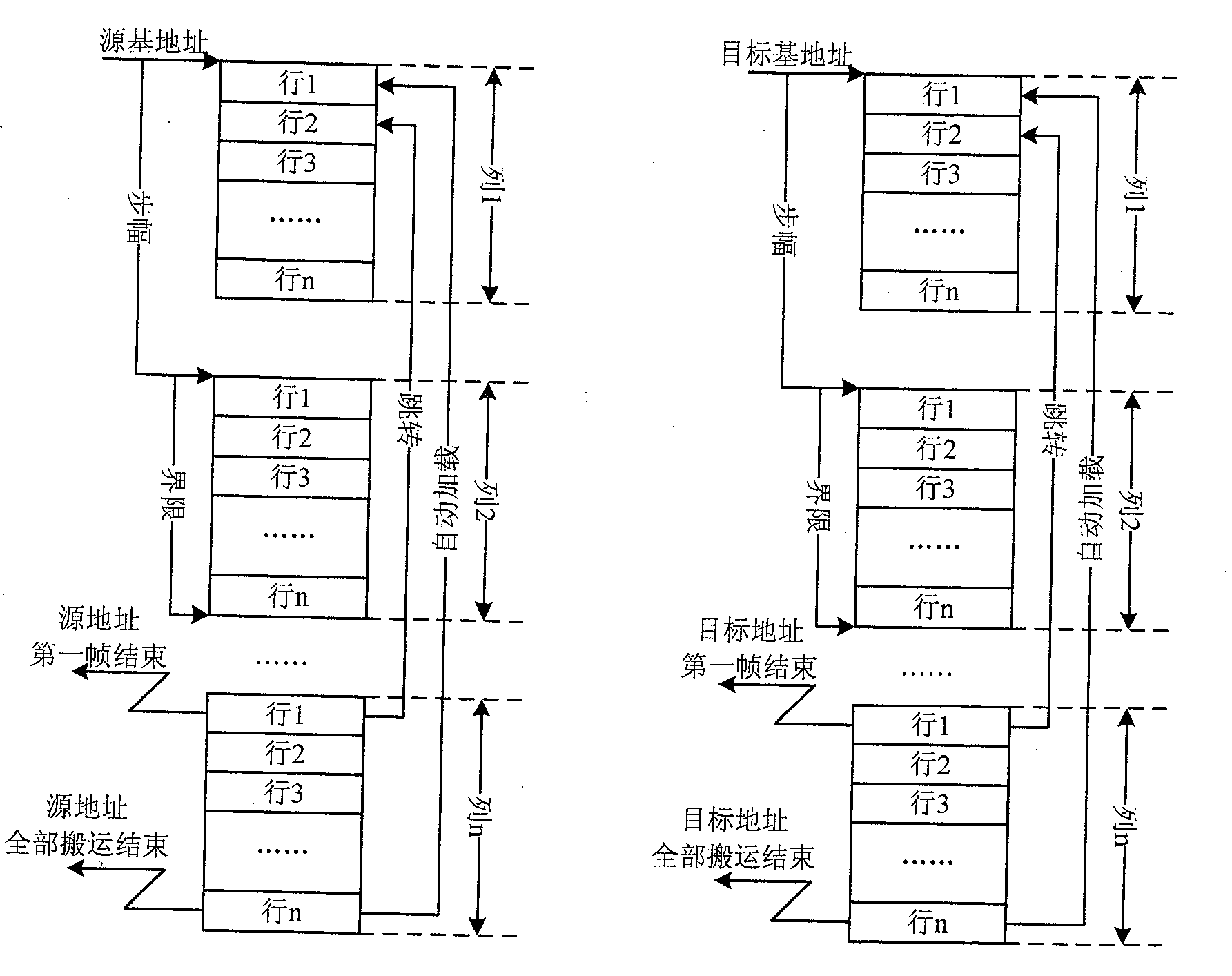

Method for implementing two-dimensional data delivery using DMA controller

InactiveCN101059785A2D data handling supportElectric digital data processingPage address registerProcessor register

The invention discloses a method for using a DMA controller to realize two-dimension transmission, wherein the DMA controller is arranged with a linked list address register. And the method comprises that valuing each register, arranging source address, target address and linked list to relative registers, according to the address of linked list, storing the values of the object memory space relative to the source address register, the target address register, the linked list address register and the control register into a memory, and the DMA controller reads out the source address from the source address register, to obtain the data stored in the address, and transmit next data with increased addresses until all data in prior memory space are transmitted. The invention uses Scatter / Gather linked list to make DMA controller support two-dimension data transmission.

Owner:ZTE CORP

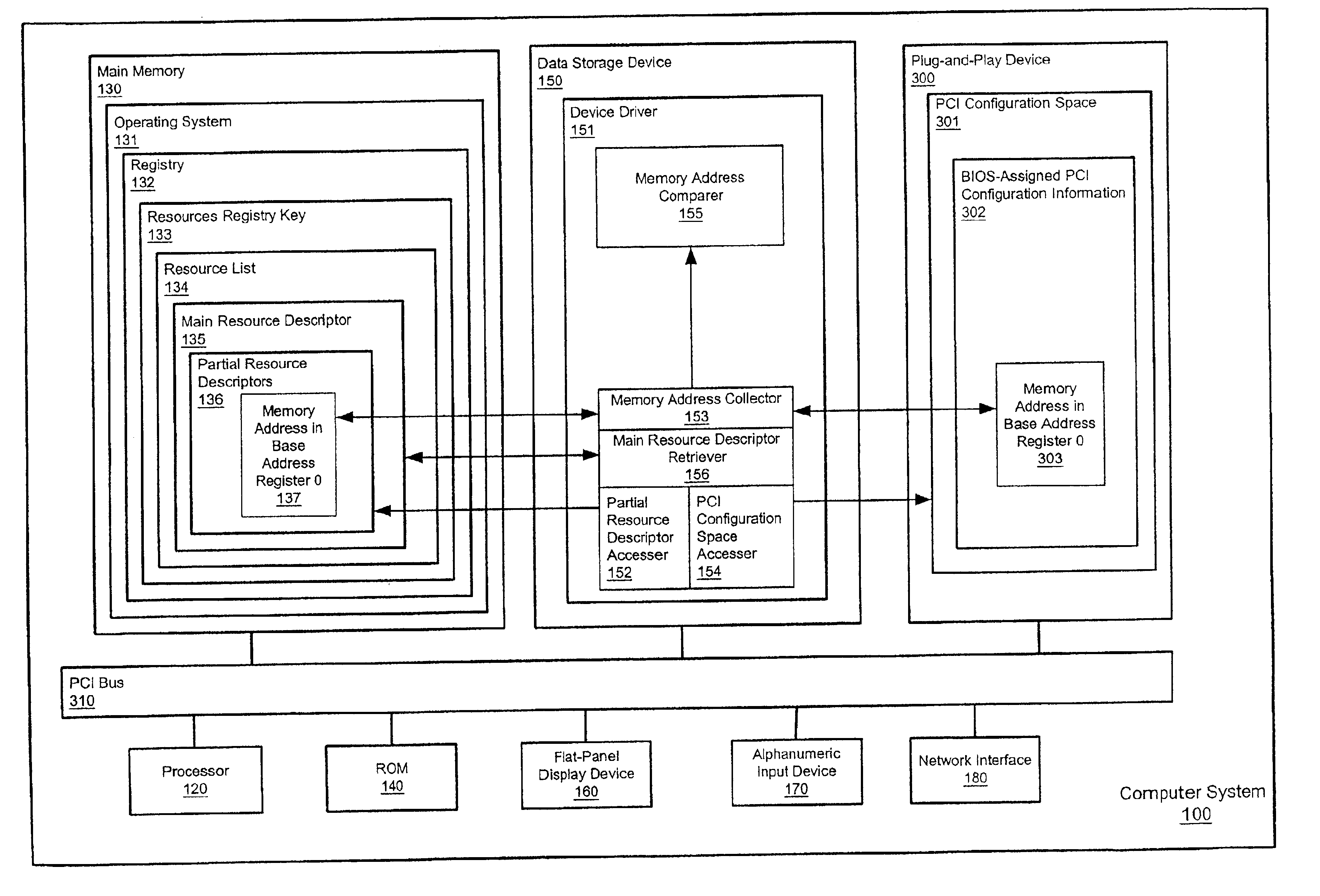

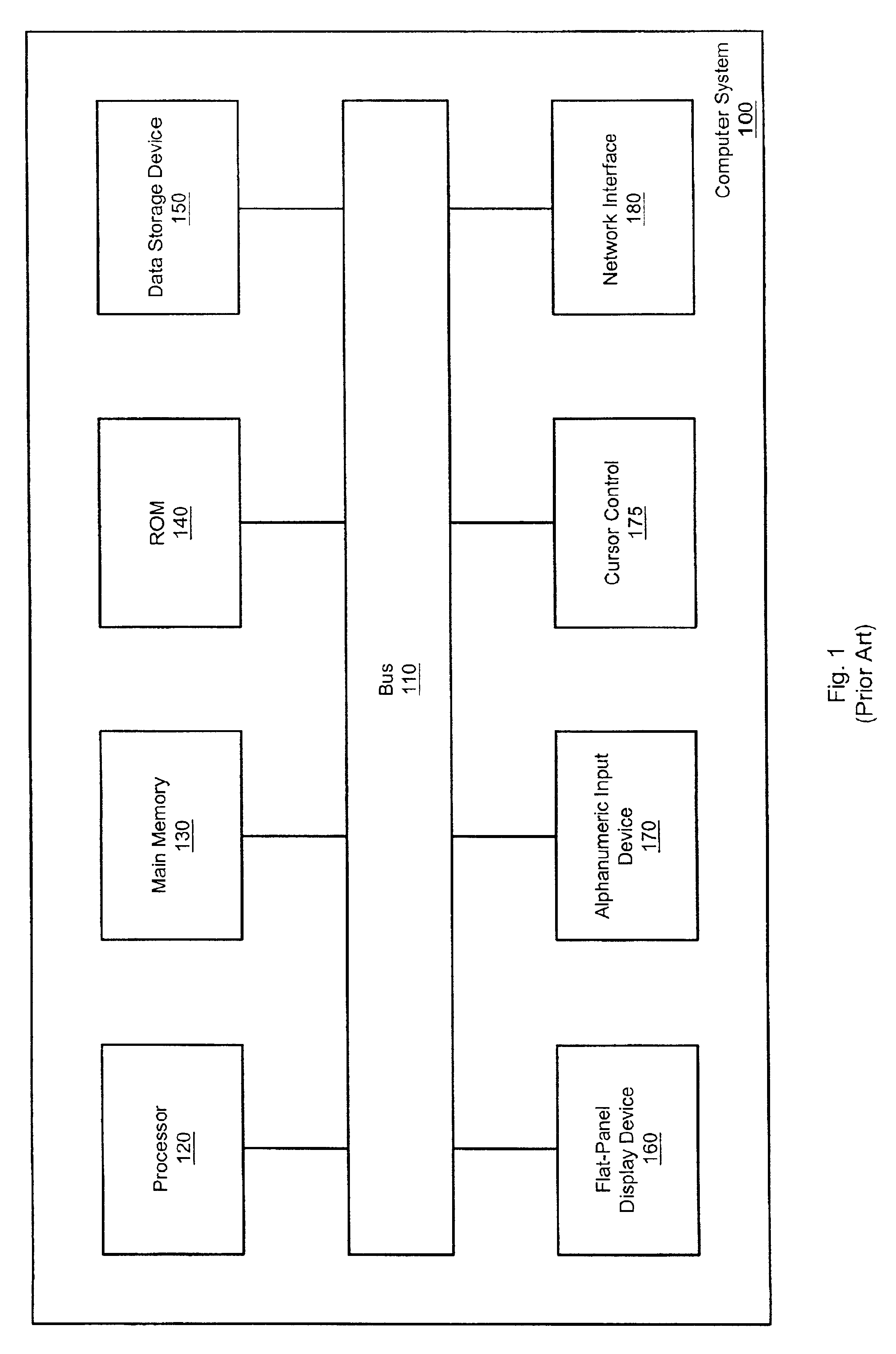

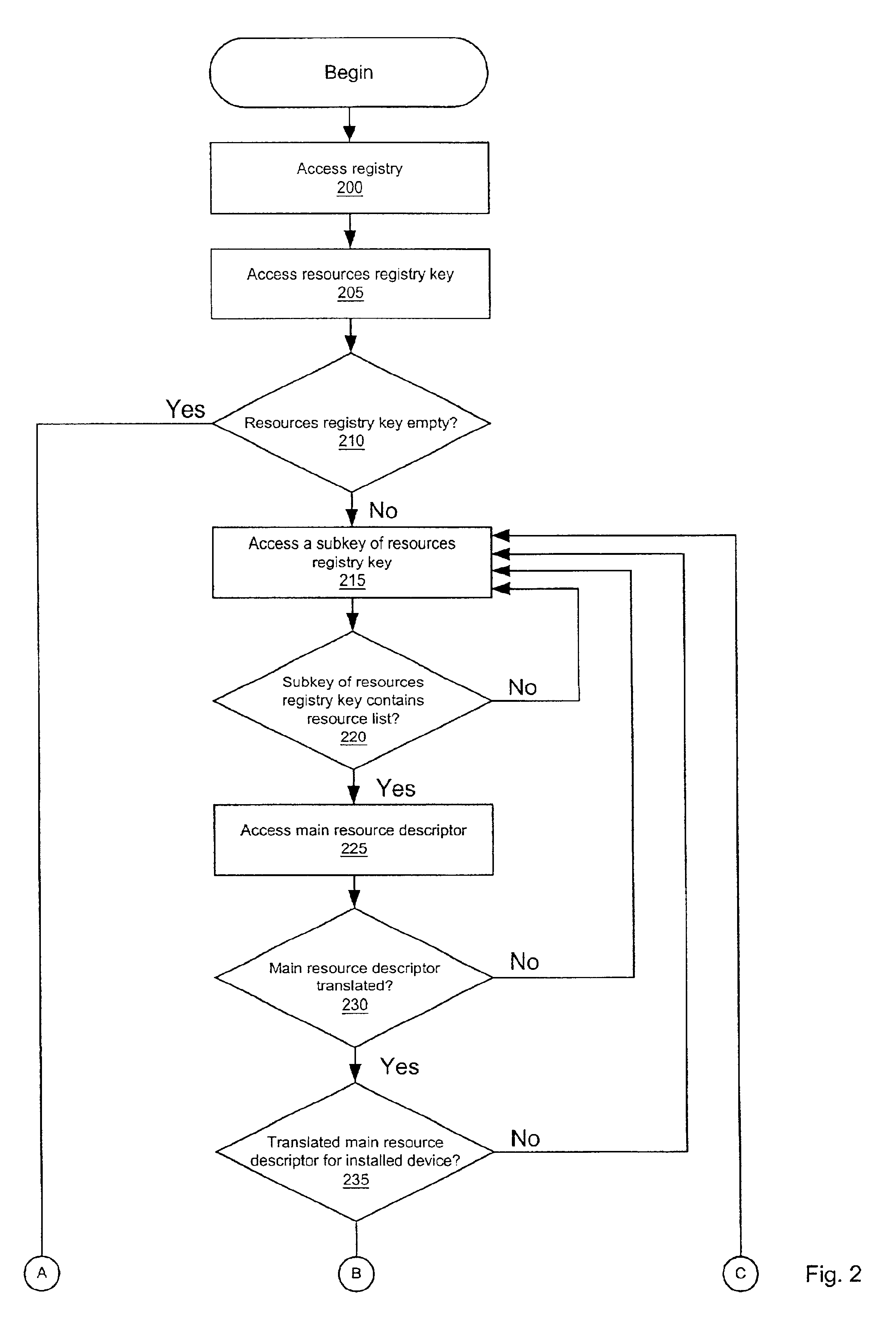

Accessing a translated resource descriptor of a hardware device

InactiveUS6931646B2Digital computer detailsProgram loading/initiatingMemory addressPage address register

A method for accessing a main resource descriptor for a hardware device. A device driver accesses a hardware device's partial resource descriptor of a translated main resource descriptor stored in an operating system registry. The device driver accesses raw BIOS-assigned configuration information for the hardware device. The device driver compares the memory address in base address register 0 of the partial resource descriptor to the memory address in base address register 0 of the BIOS-assigned configuration information. The device driver selects the translated main resource descriptor that contains the partial resource descriptor with the memory address in base address register 0 that matches the memory address in base address register 0 for the raw BIOS-assigned configuration information.

Owner:INTEL CORP

Processor architecture scheme which uses virtual address registers to implement different addressing modes and method therefor

InactiveUS6578139B1Instruction analysisDigital computer detailsPage address registerComputer architecture

A processor architecture scheme which allows for encoding of multiple addressing modes through use of virtual register addresses in order to maximize number of directly addressable registers in the processor architecture scheme. A set of virtual address register locations associated with an indirect addressing pointer is reserved in memory. The number of virtual register address locations reserved is equal to a number of indirect addressing modes associated with the indirect addressing pointer. Each of the virtual register address locations initiates an indirect addressing mode to be used with the associated indirect addressing pointer when accessed.

Owner:MUSIC BUDDHA

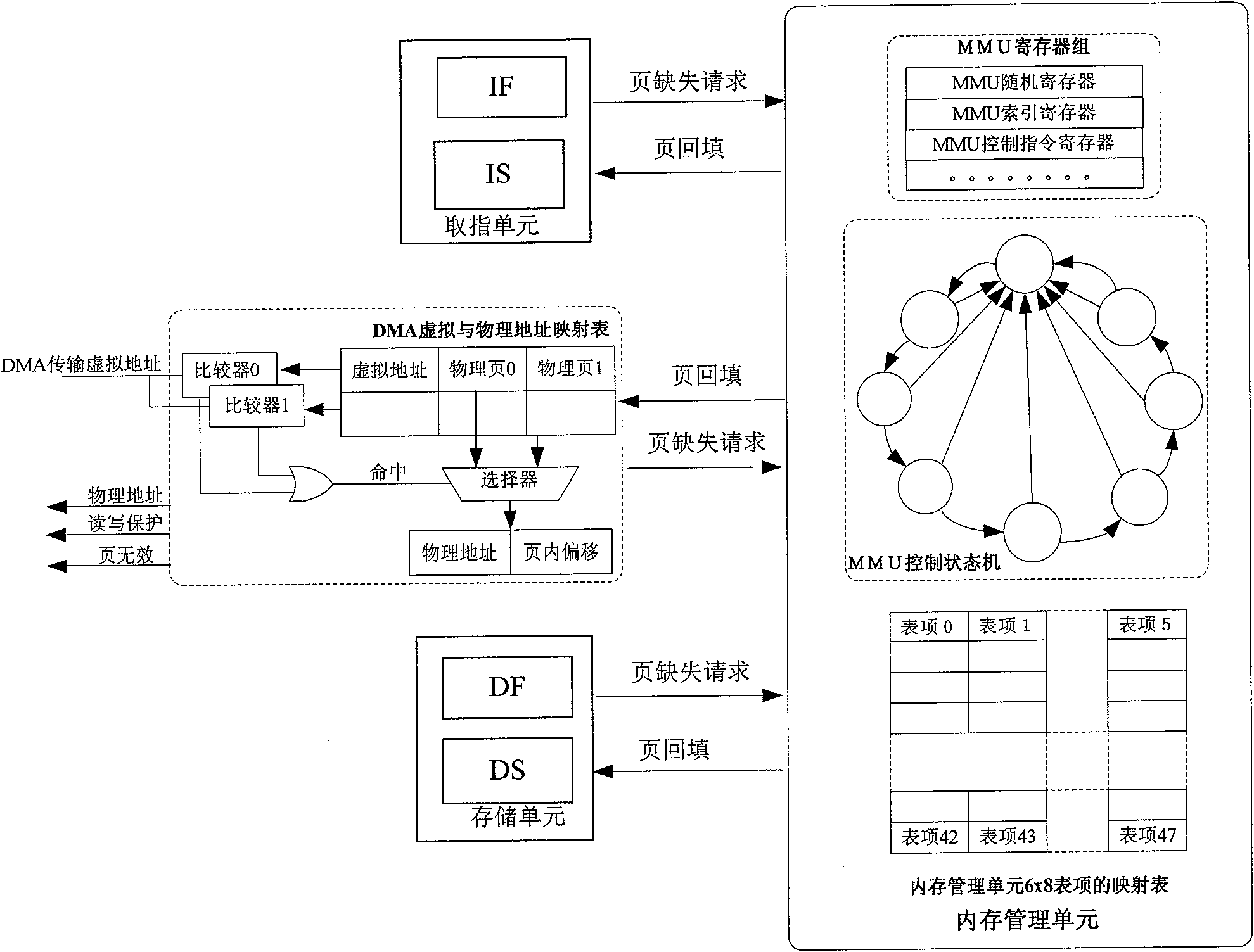

Microprocessor storage management method

ActiveCN104991869AEffective predictionAchieve mutual isolationMemory adressing/allocation/relocationPage address registerOperational system

The invention discloses a microprocessor storage management method. The method comprises: whenever a process references a logic address, a storage management unit searching in a cache index storage cell and automatically looking up in a translation lookaside buffer, if the logic address is found, translating a cache address on a chip, if the logic address is not found, executing address translation operation; adding a page frame number with last 13 bits of the logic address to obtain a physical address, if the address is in a range of a multitask protection start address register to a multitask protection end address register, virtual address translation being successful, if the address is not in a range of a start address register to the end address register, a microprocessor generating address translation out-of-range anomaly. The invention provides a novel microprocessor storage management method, and translation speed of a logic address to a physical address is accelerated. Through arranging the multitask protection start address register and the multitask protection end address register, the operating system can prevent illegal access of user programs.

Owner:苏州讯升信息科技有限公司

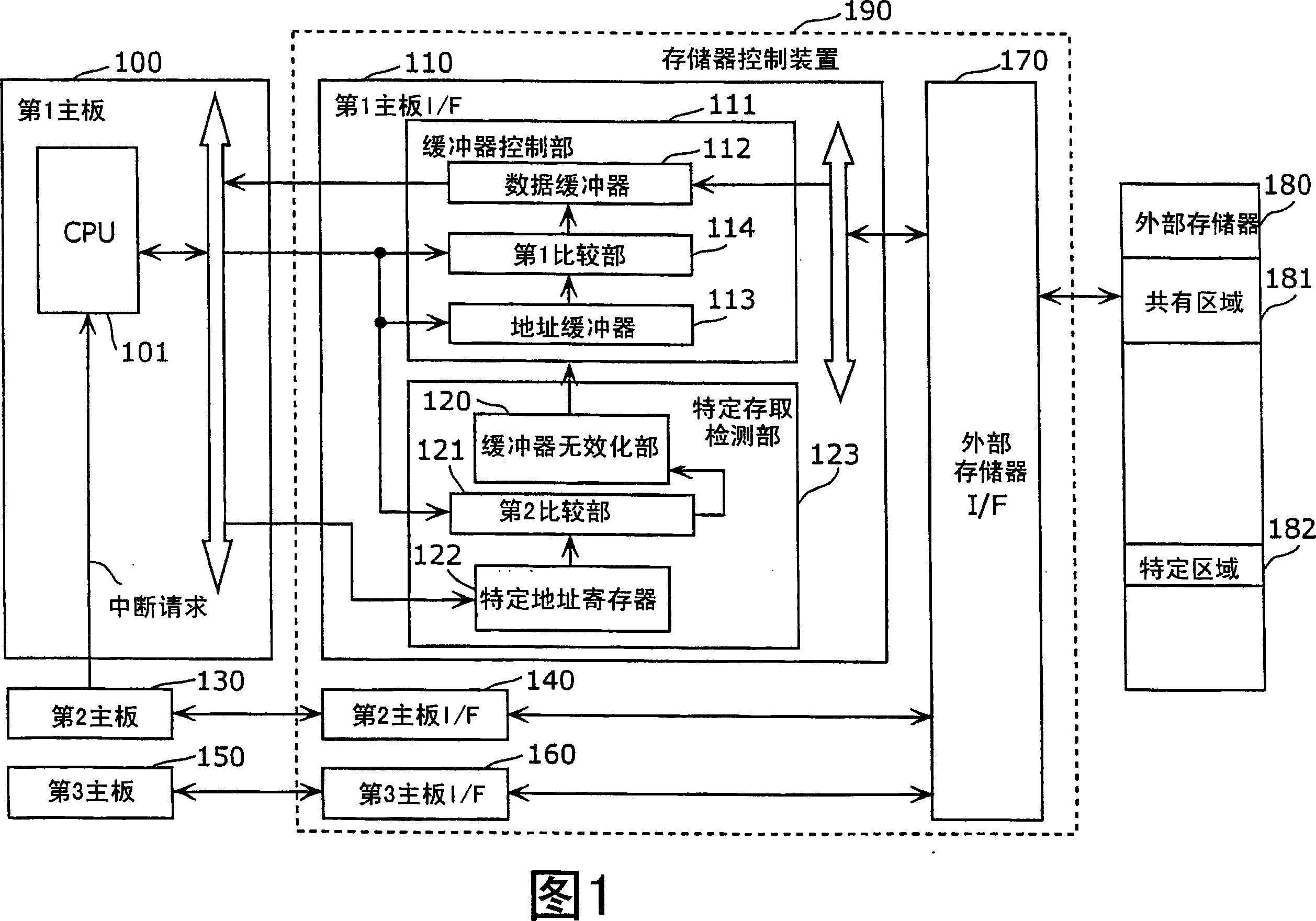

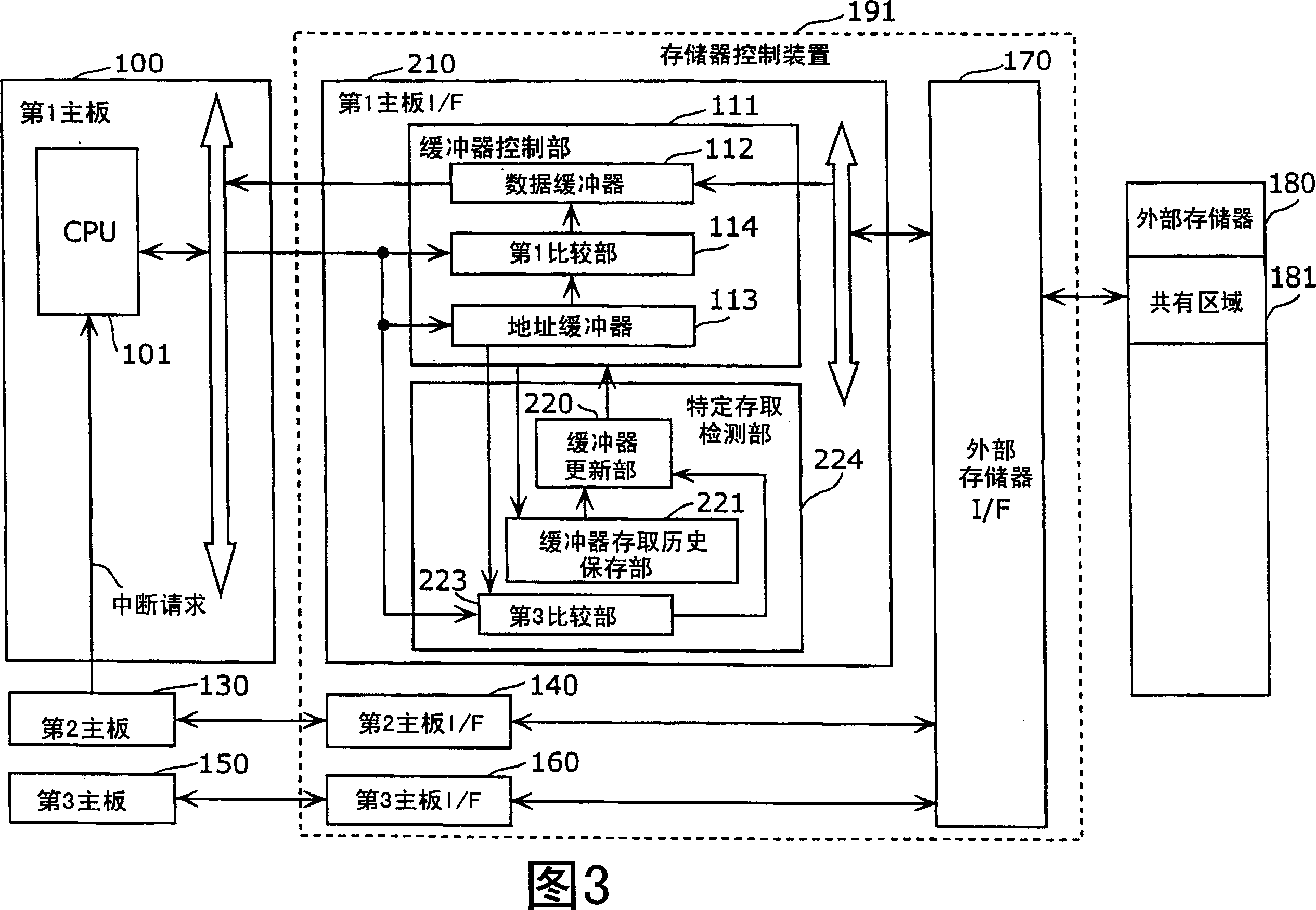

Memory control apparatus

InactiveCN1932783AAccess validHit rate decreasedMemory adressing/allocation/relocationPage address registerExternal storage

To provide a memory control device capable of surely providing consistency to an external memory while suppressing degradation of access efficiency to the external memory. This memory control device is provided with: a data buffer 112 and an address buffer 113 holding data and an address related to an access request of the past from a first master 100; a first comparison part 113 for comparing, when receiving a new access request, its address with the address in the address buffer 113; a buffer control part 111 for issuing an access request to an external memory I / F 170 according to the comparison or outputting the data in the data buffer 112 to the first master 100; and a specific access detection part 123 for negating the content of the data buffer 112 regardless of the result of the comparison in detecting the access request to the specific address held in a specific address register 122.

Owner:PANASONIC CORP

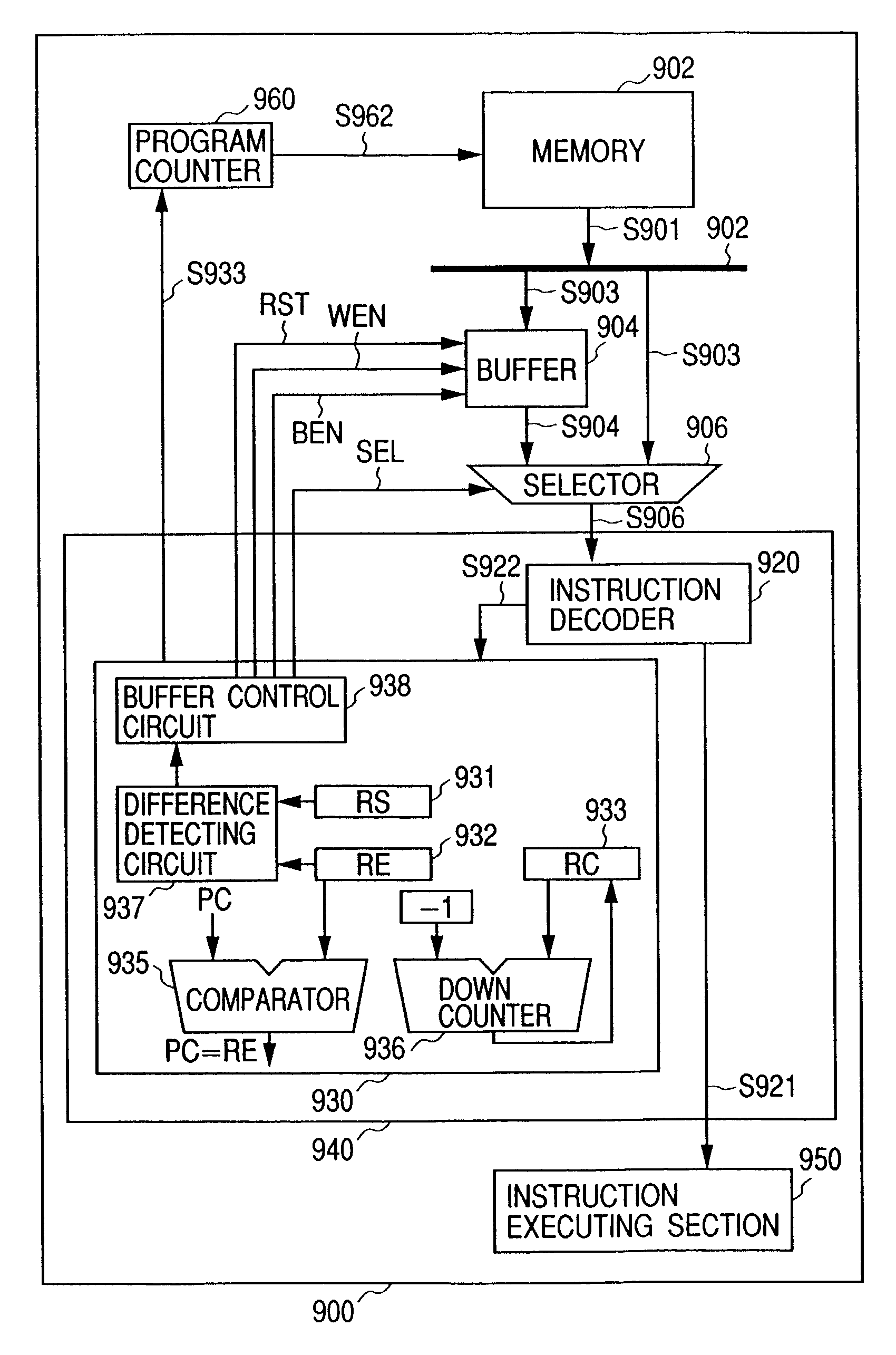

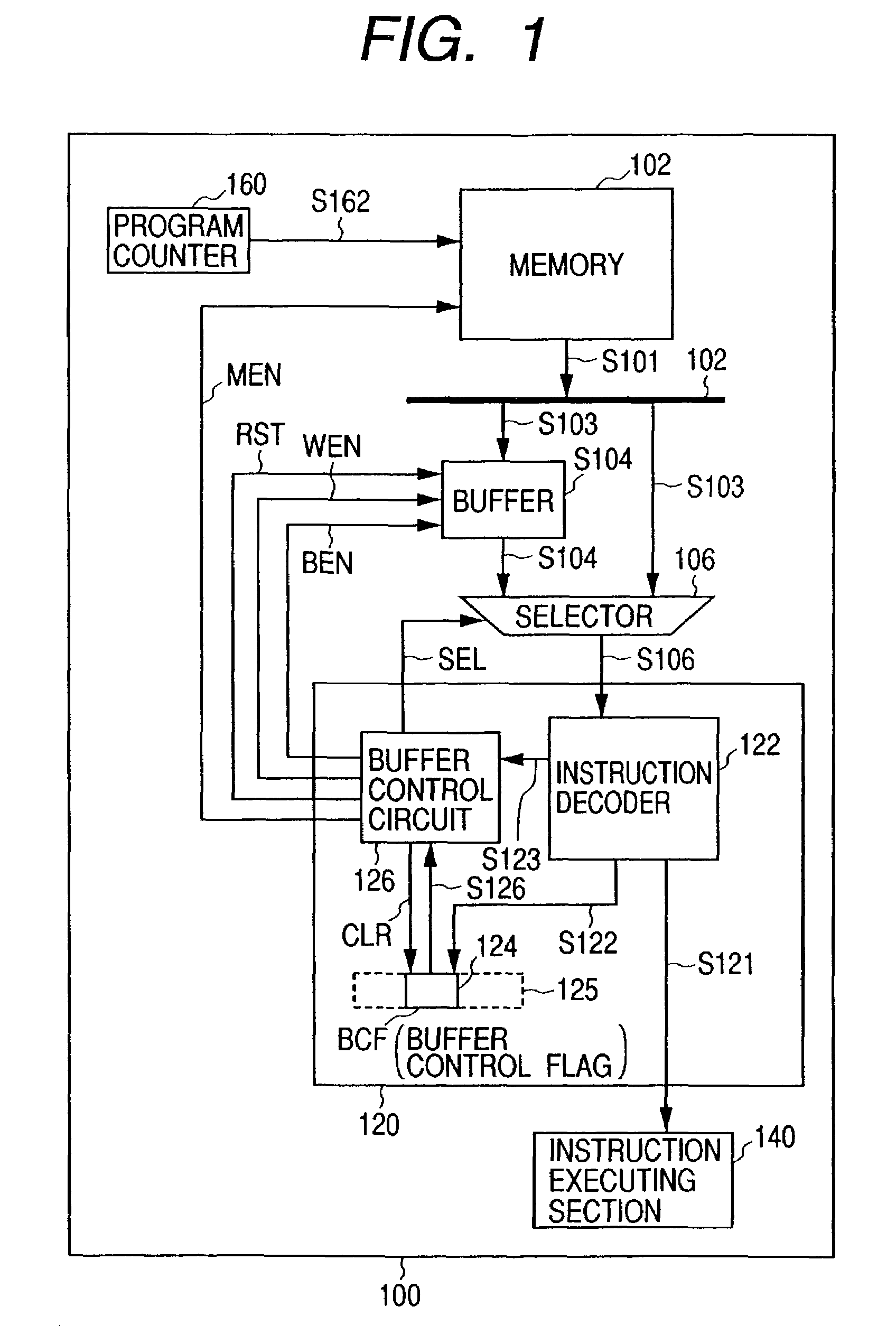

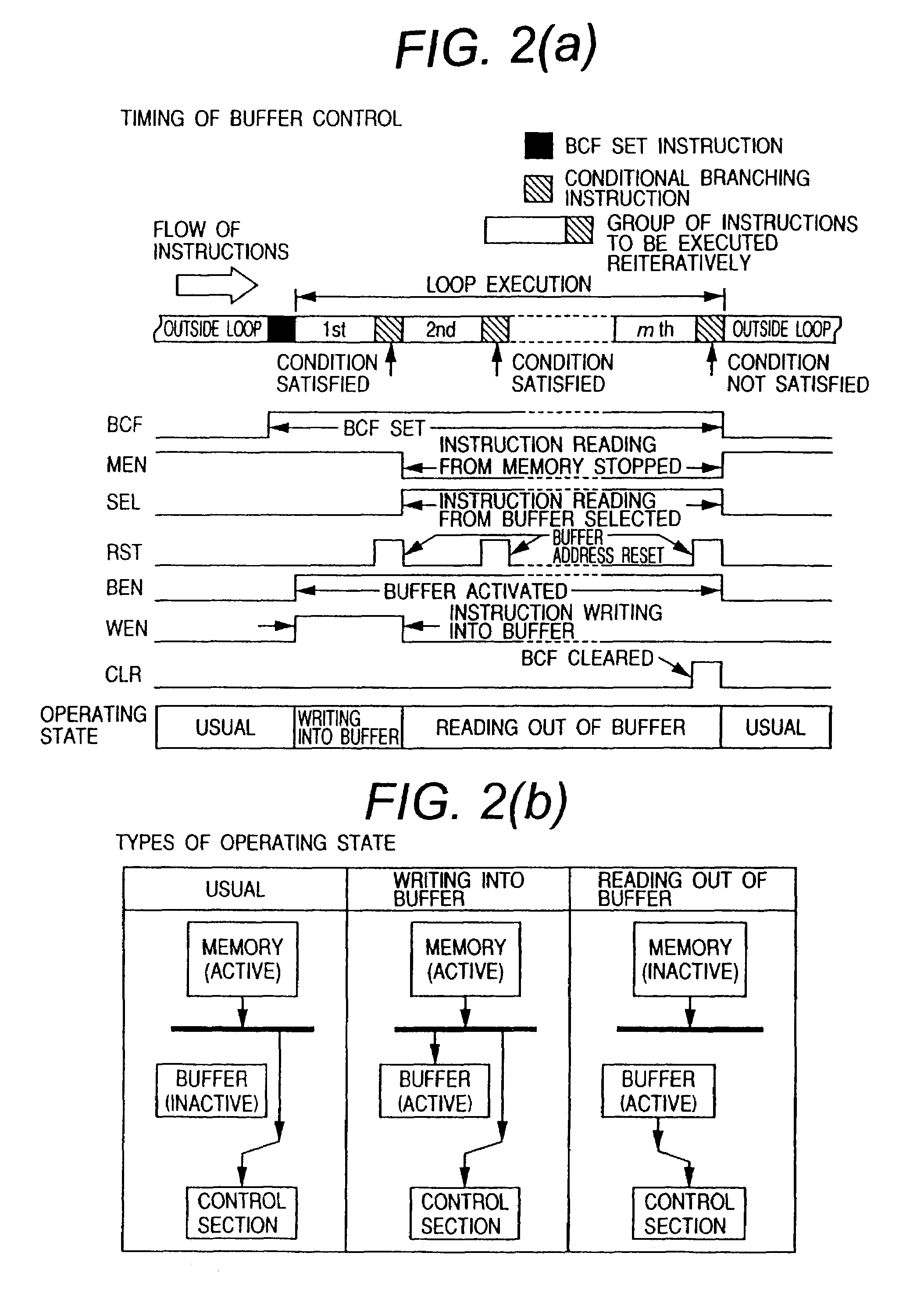

Data processing apparatus

InactiveUS7080240B2Reduce power consumptionReduce total powerDigital computer detailsNext instruction address formationInstruction memoryPage address register

Owner:HITACHI LTD

Method for implementing two-dimensional data delivery using DMA controller

ActiveCN101059784ARealize the process of supporting two-dimensional data handlingElectric digital data processingPage address registerProcessor register

The invention discloses a method for using a DMA controller to realize two-dimension data transmission, which comprises a source address register, a target address register, a boundary register, and a step register. And the method comprises that the DMA controller reads a source address from the source address register, to obtain the data stored in the address and judge if the memory space is the last memory space, or else, according to the value in the step register, calculating the following accessed resource address to be stored in the source address register, if the memory space is the last memory space, jump to the next address of a first memory space to store the address into the source address register. The invention uses two-dimension skip to make DMA controller support two-dimension data transmission.

Owner:SANECHIPS TECH CO LTD

Program modification device

InactiveUS6715051B2Program control using stored programsProgram loading/initiatingPage address registerProcessor register

In modifying a program fixedly recorded in a ROM or the like, desired positions in the program can be modified with a little hardware. In order to achieve the object, the program modification device comprises the modifying address register 17 which stores the addresses of program data to be modified prior to the execution of the data and the modifying address storage table 19 which stores all the addresses of the modification source programs to be loaded to the modifying address register 17 and all the addresses of the modification target programs in pairs, and further comprises a modification target program having instructions embedded therein so as to load necessary information from the modifying address storage table 19 to the modifying address register 17 before the program to be modified is executed.

Owner:PANASONIC CORP

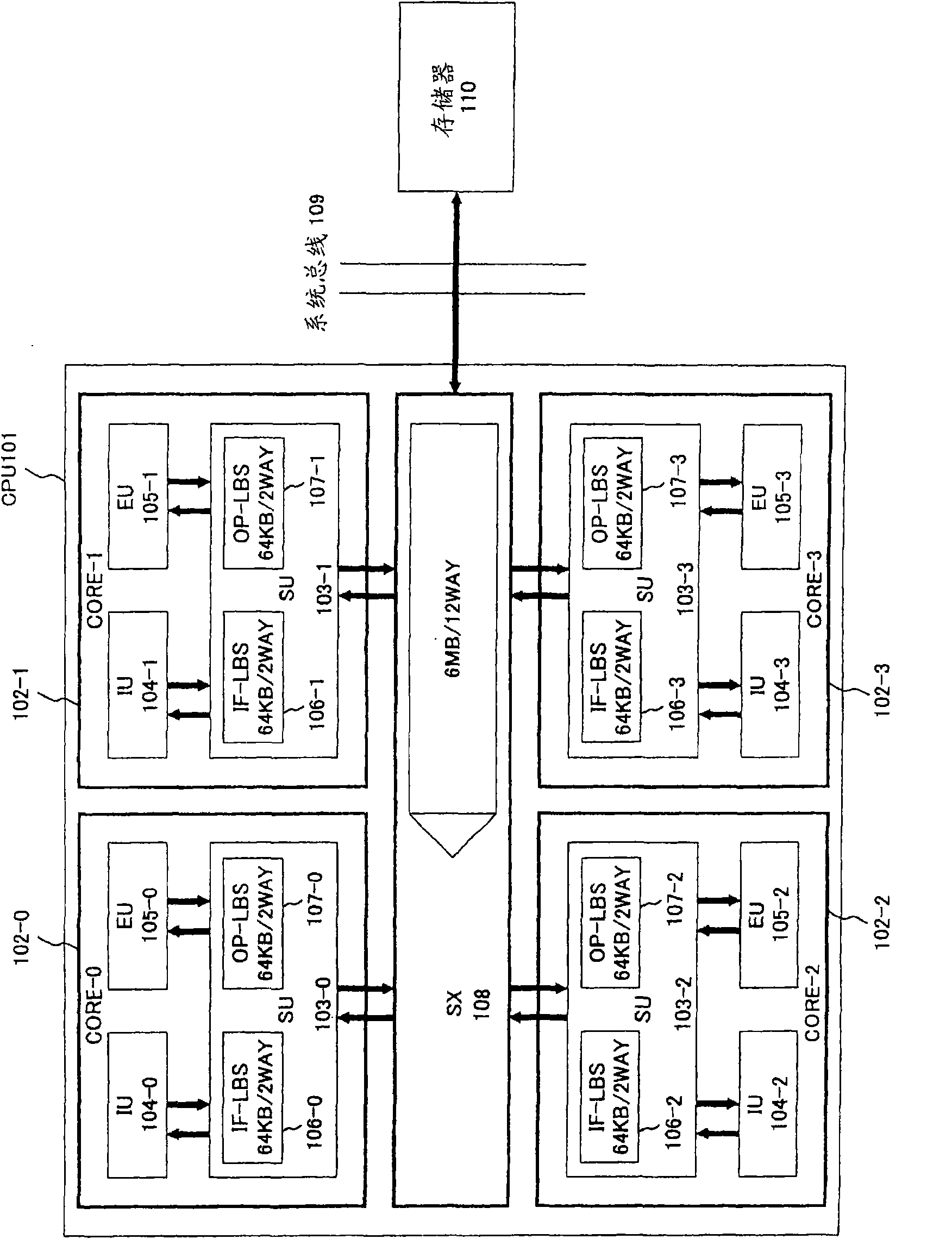

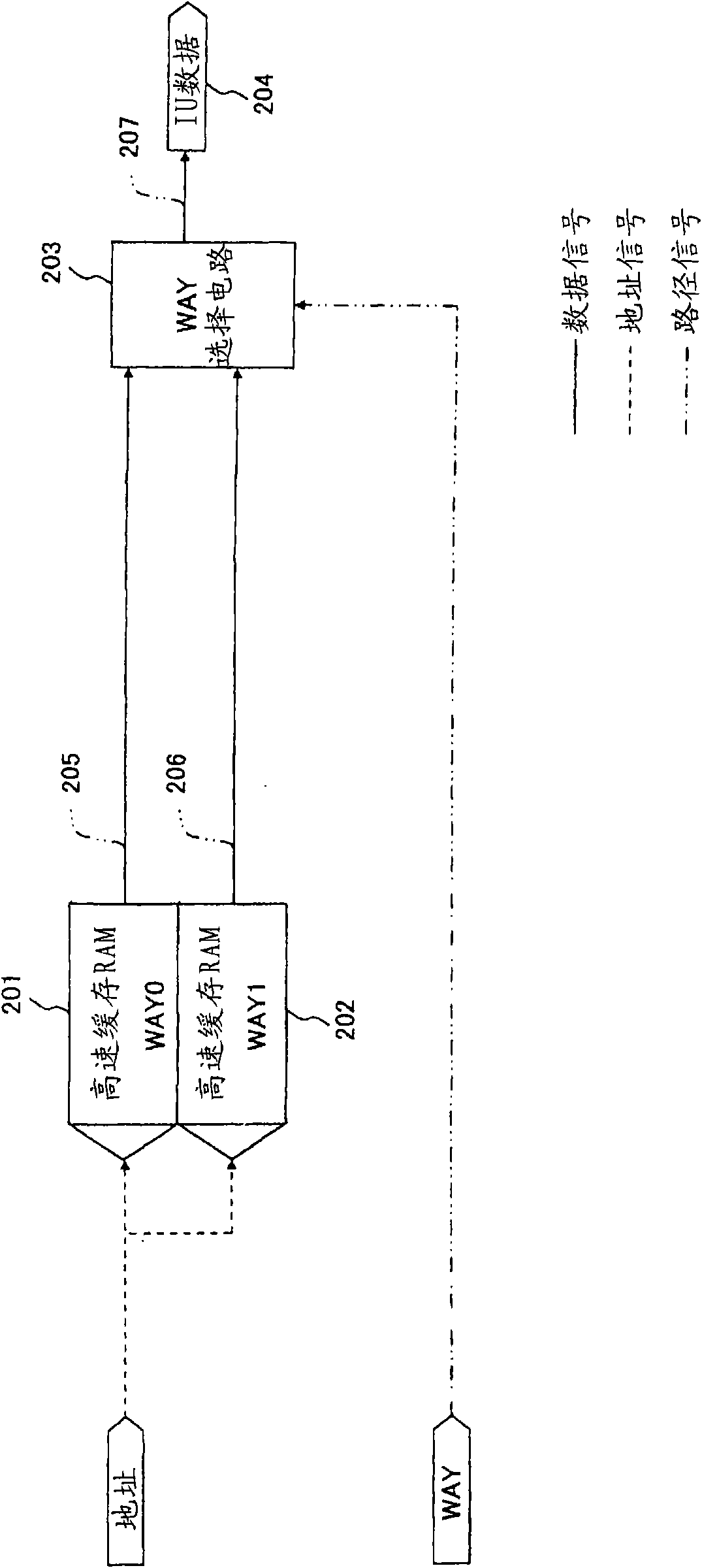

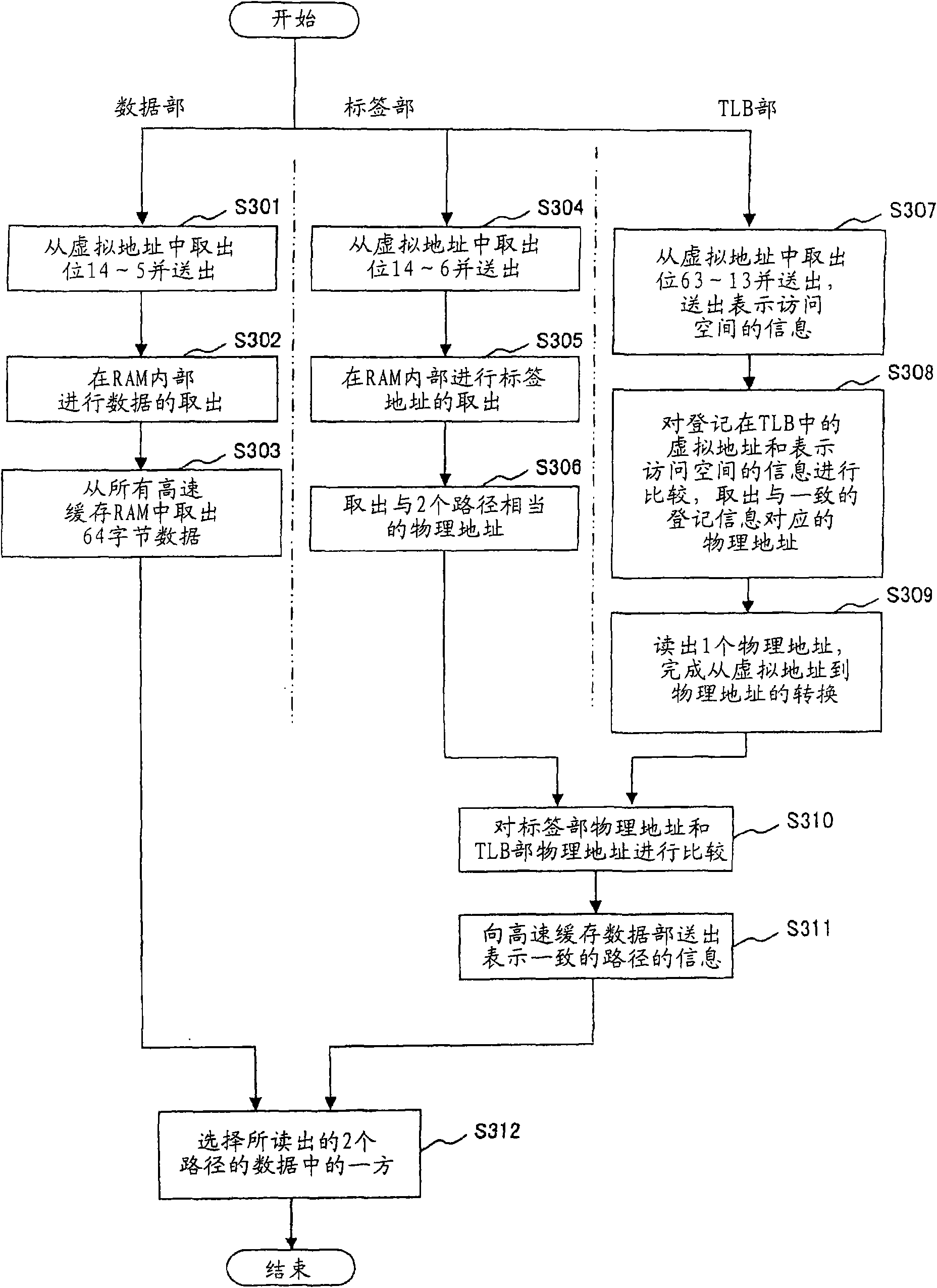

Cache memory device, arithmetic processing unit, and its control method

InactiveCN101689141ASmall sizeSmall assembly areaFault responseMemory adressing/allocation/relocationPage address registerArithmetic processing unit

The invention provides a cache memory device, an arithmetic processing unit and its control method. The cache memory device is structured to include a data holding part including a plurality of ways having a plurality of cache lines, an alternating data register for holding data for one of the cache lines of the data holding part or for part of the cache lines, an alternating address register forholding index addresses indicating a defective cache line where a failure occurs in the data holding part and a failure occurrence part in the defective cache line, an alternating way register for holding information of a way containing the failure occurrence part, an address matching circuit for comparing an index address to be used for access whenthe data holding part is to be accessed with an index address of the alternating address register, and a way matching circuit for comparing way information to be used for the access when the data holding part is to be accessed with way information held by the alternating way register.

Owner:FUJITSU LTD

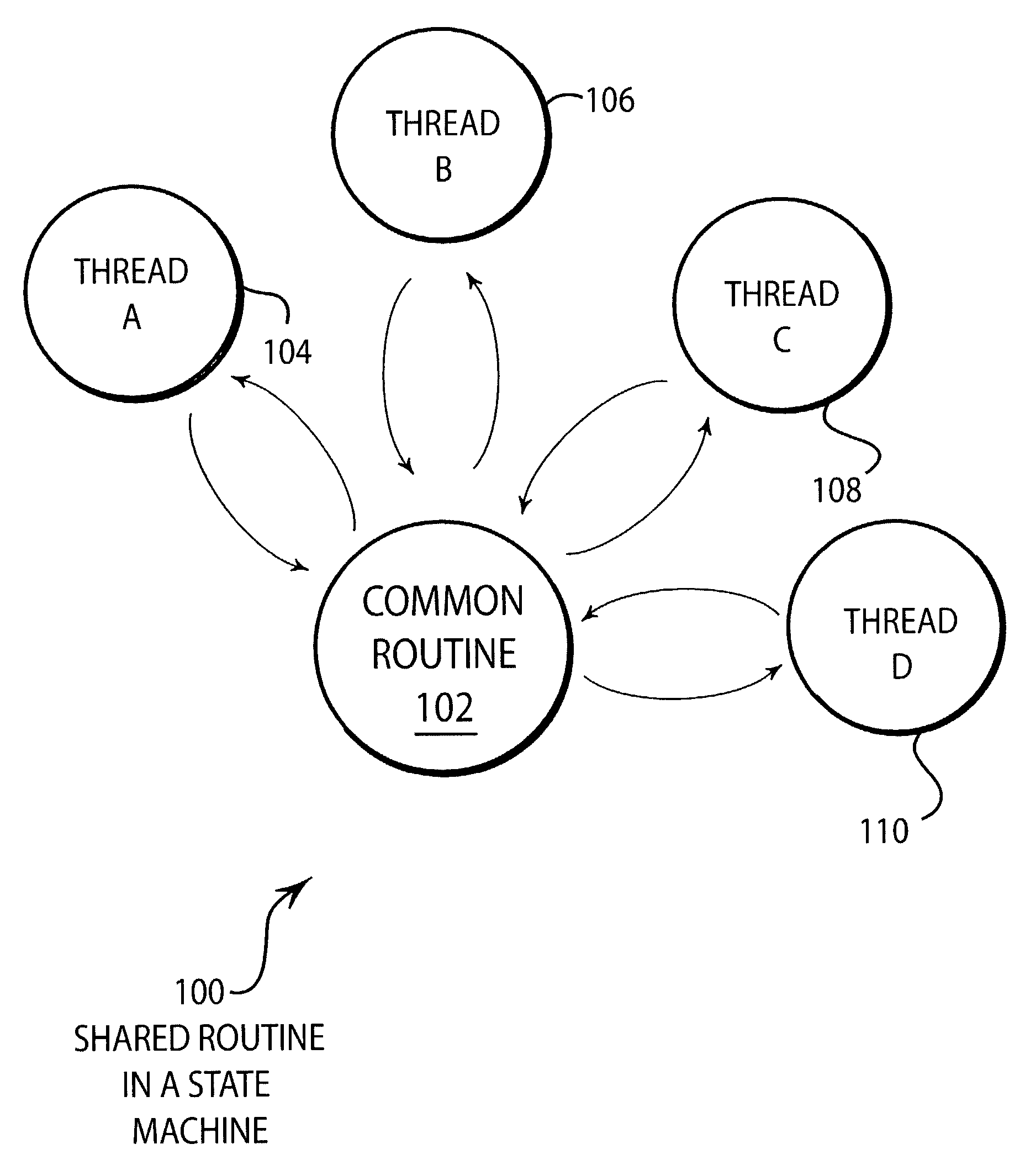

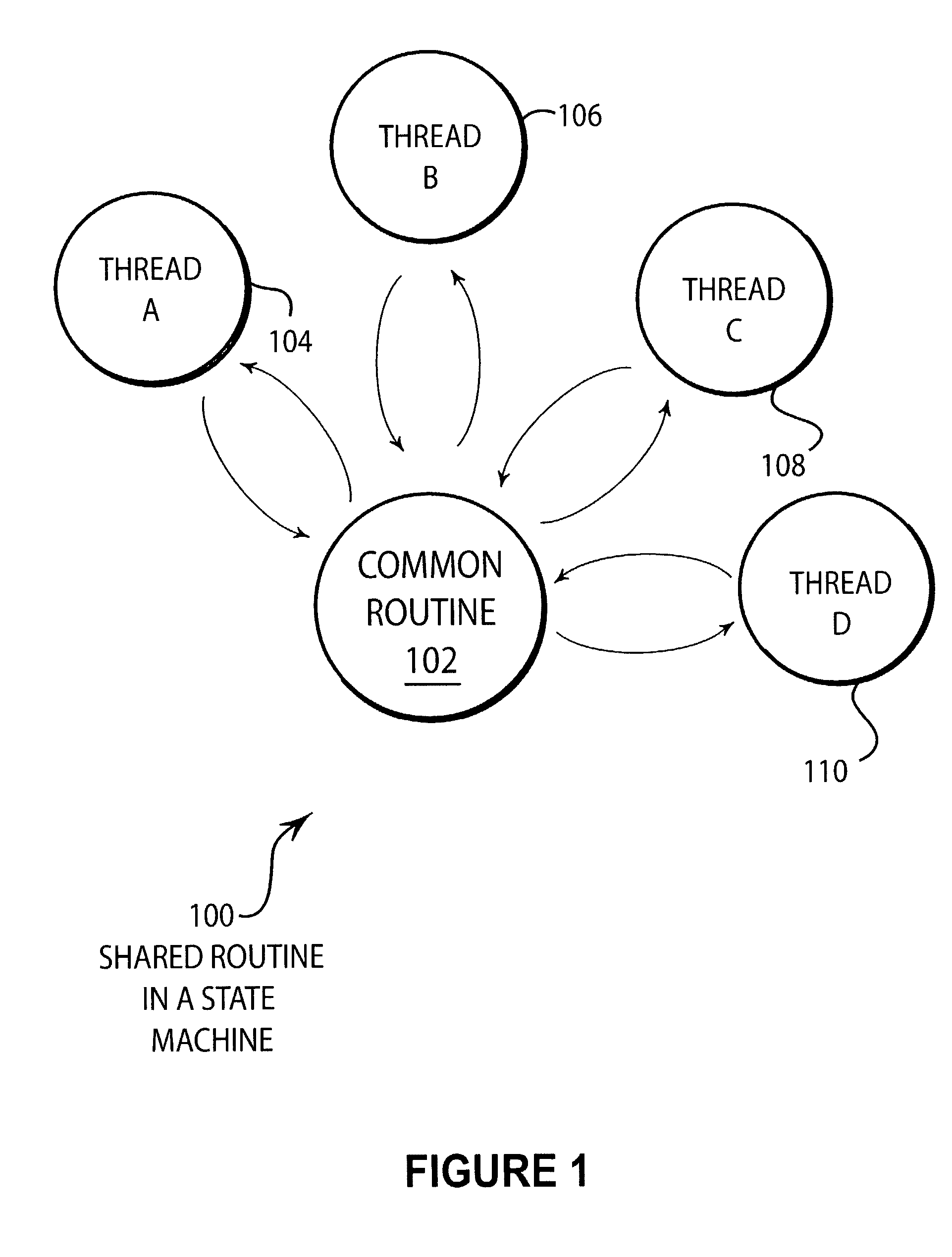

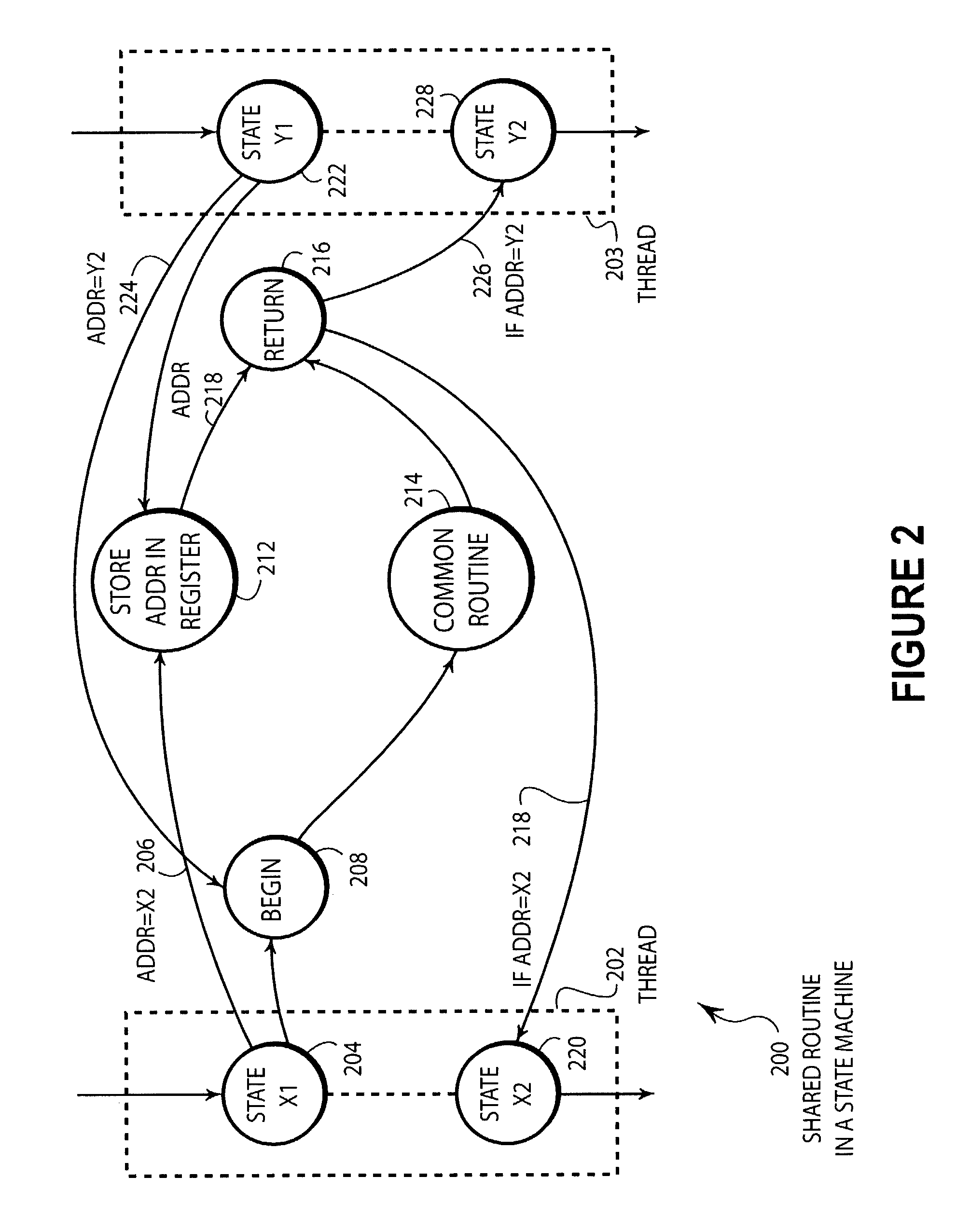

Common state sequences in a finite state machine

InactiveUS7577952B2Reduce in quantityReduce latencyDigital computer detailsMultiprogramming arrangementsPage address registerProcessor register

A state machine may have a sequence that is called by multiple threads within the state machine. Prior to calling the sequence, an address specific to the current state is stored in an address register. After the sequence has executed, the address register is queried and the thread may continue. Many different threads may call the sequence. In more complex hardware implemented state machines, the total number of gates may be reduced significantly.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

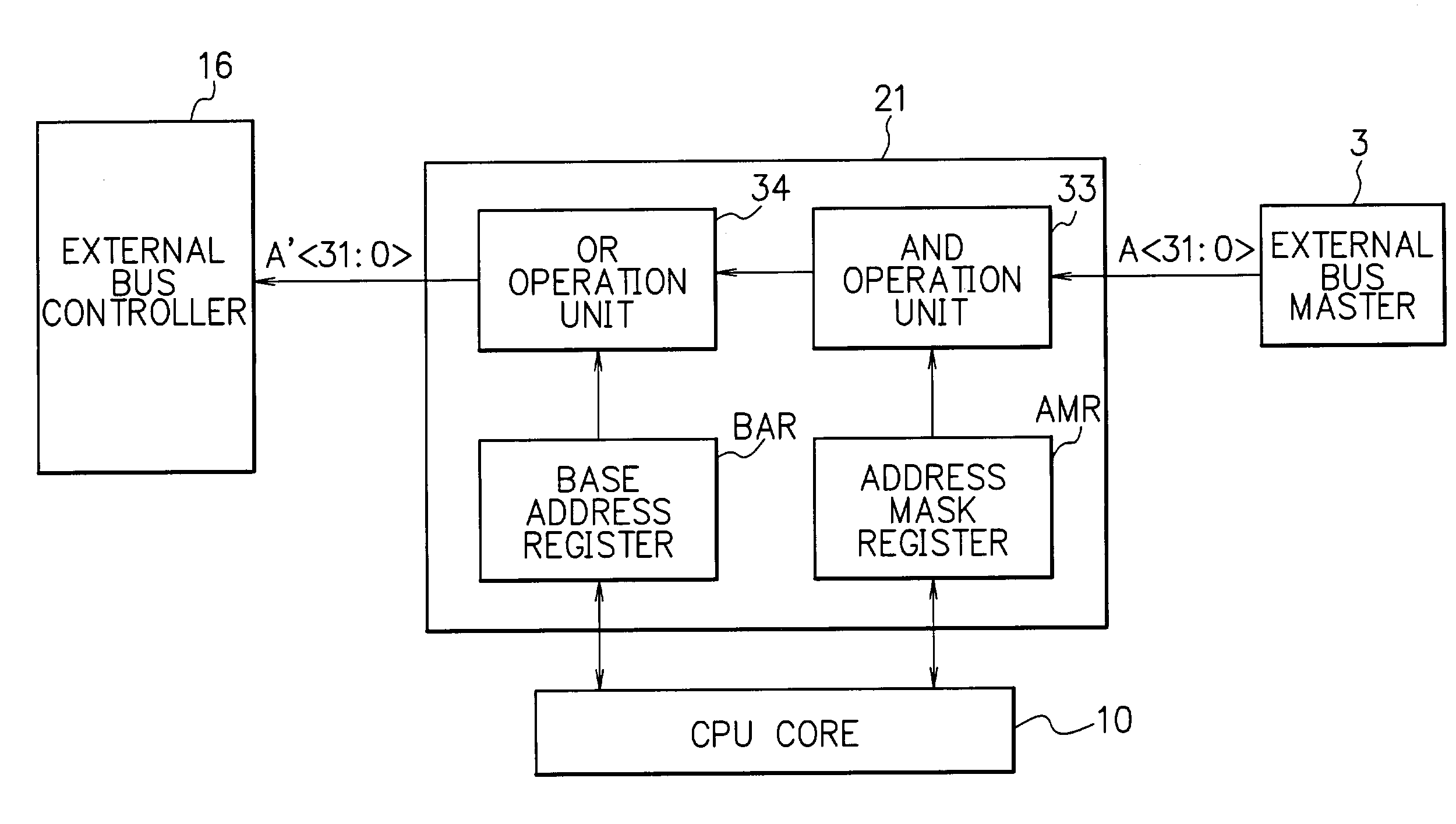

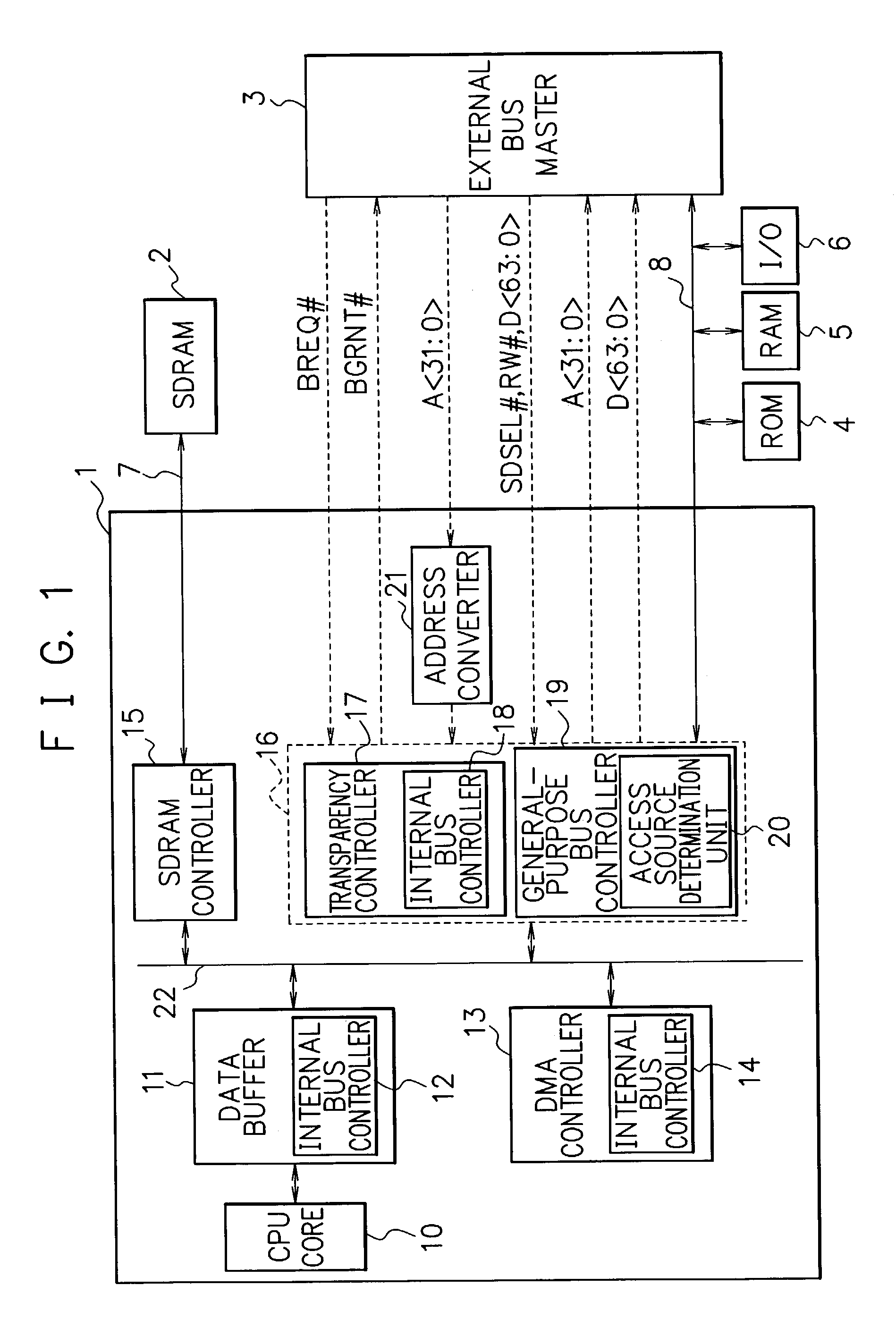

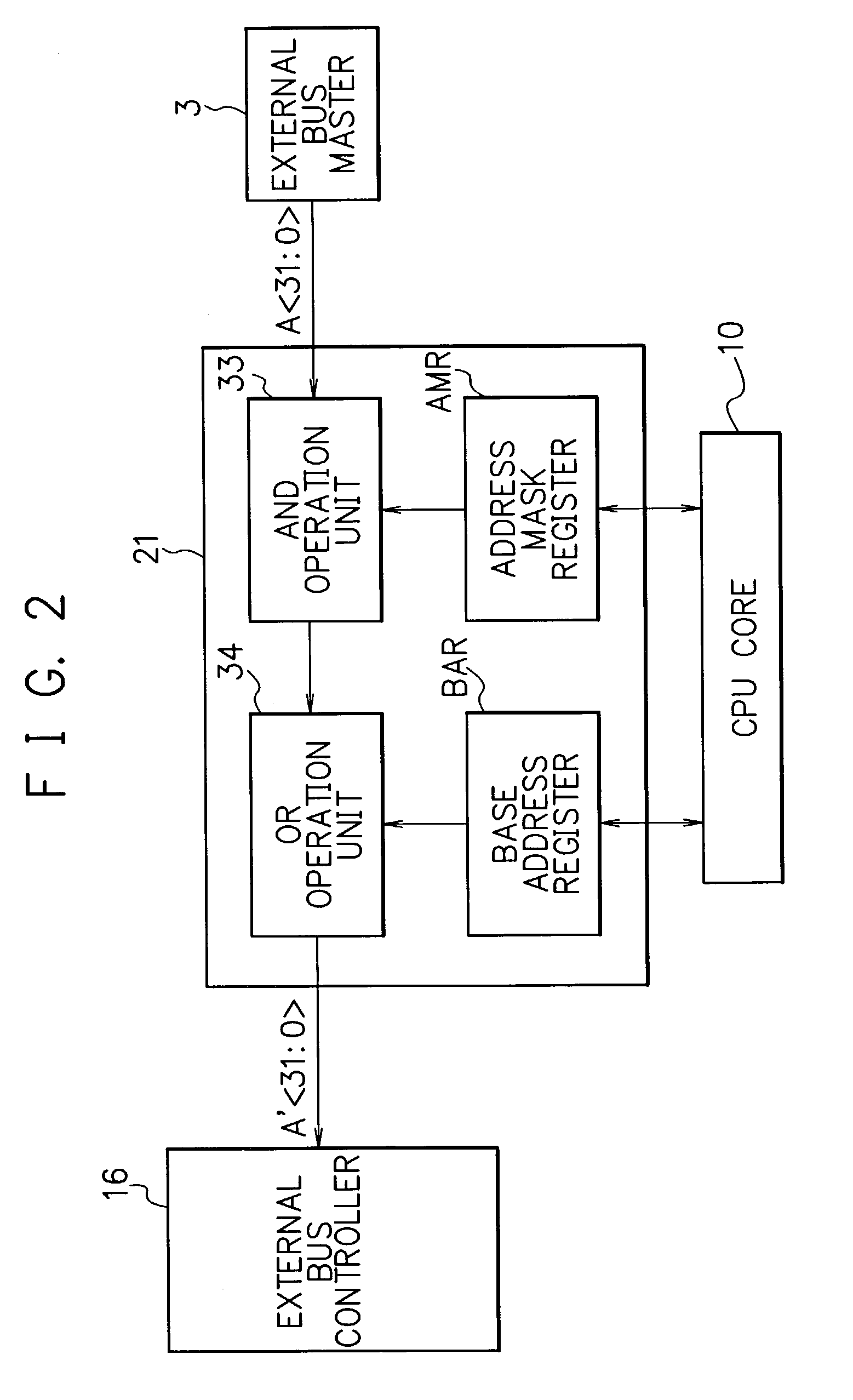

Data processing apparatus, data processing system, and access area control method

InactiveUS7178003B2Possible to connectMemory adressing/allocation/relocationMicro-instruction address formationData processing systemPage address register

An address converter has a base address register and address mask register for setting the start address and range, respectively, of a transparent mode access permitted area. By using the values of these base address register and address mask register, the address converter converts an address signal (address value) supplied from an external bus master into an address signal within a predetermined range from the start position of the transparent mode access permitted area. A transparency controller executes transparent mode access by using the converted address signal. This makes it possible to connect devices having different address bus widths to an external bus without forming any new external circuit, and to set an arbitrary transparent mode access permitted area.

Owner:FUJITSU LTD

Signal transmission method, device and system in baseband remote scene

ActiveCN102340471BEnhanced inhibitory effectAddressing loss of precisionMulti-frequency code systemsElectromagnetic repeatersPage address registerIntermediate frequency

The embodiment of the invention discloses a signal transmission method, device and system in a baseband remote scene. According to the technical scheme disclosed by the embodiment of the invention, the method comprises the steps as follows: a BBU (building baseband unit) lowers the calibrated value of initial average amplitude output by a physical layer through IFFT (inverse fast Fourier transform); cutting treatment is carried out on the average amplitude according to fiber transmission requirements after carrying out in-phase hard cutting on the raising signal; and stray filtration and peak clipping treatment are carried out in an RRU (remote radio unit), so that the signal subjected to IFFT in an LTE-TDD (Long Term Evolution-Time Division Duplex) system can not overflow, and the signal accuracy is not lost when the signal is transferred through the fiber. By using the physical layer in-phase hard cutting / intermediate frequency peak clipping combined treatment scheme, the deterioration of EVM (error vector magnitude) is smaller, and the inhibitory effect on PAR (page address register) is more obvious, thereby solving the problem of overhigh average ratio of accuracy loss to signal peak in the digital signal transferring process between the BBU and the RRU in the prior art.

Owner:DATANG MOBILE COMM EQUIP CO LTD

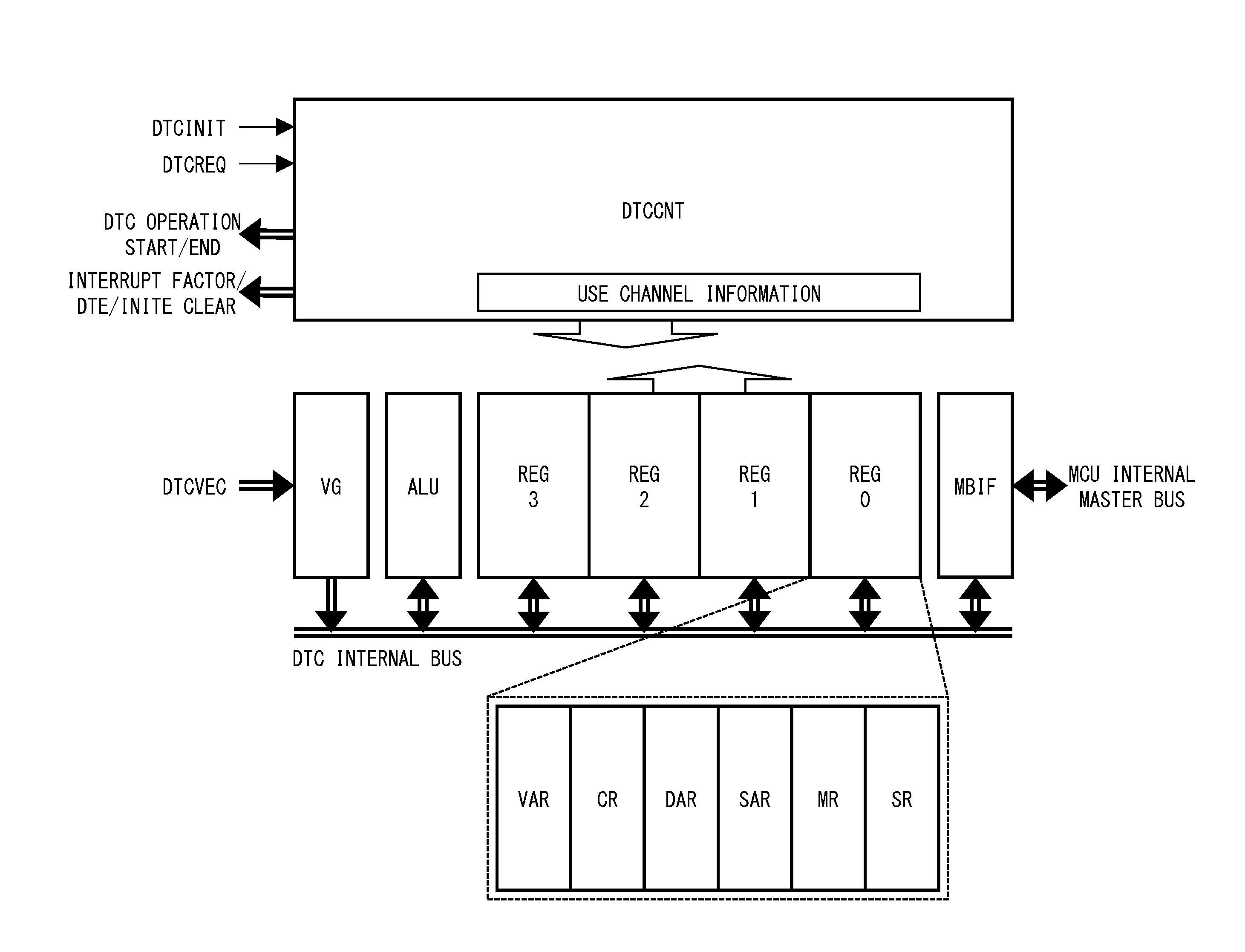

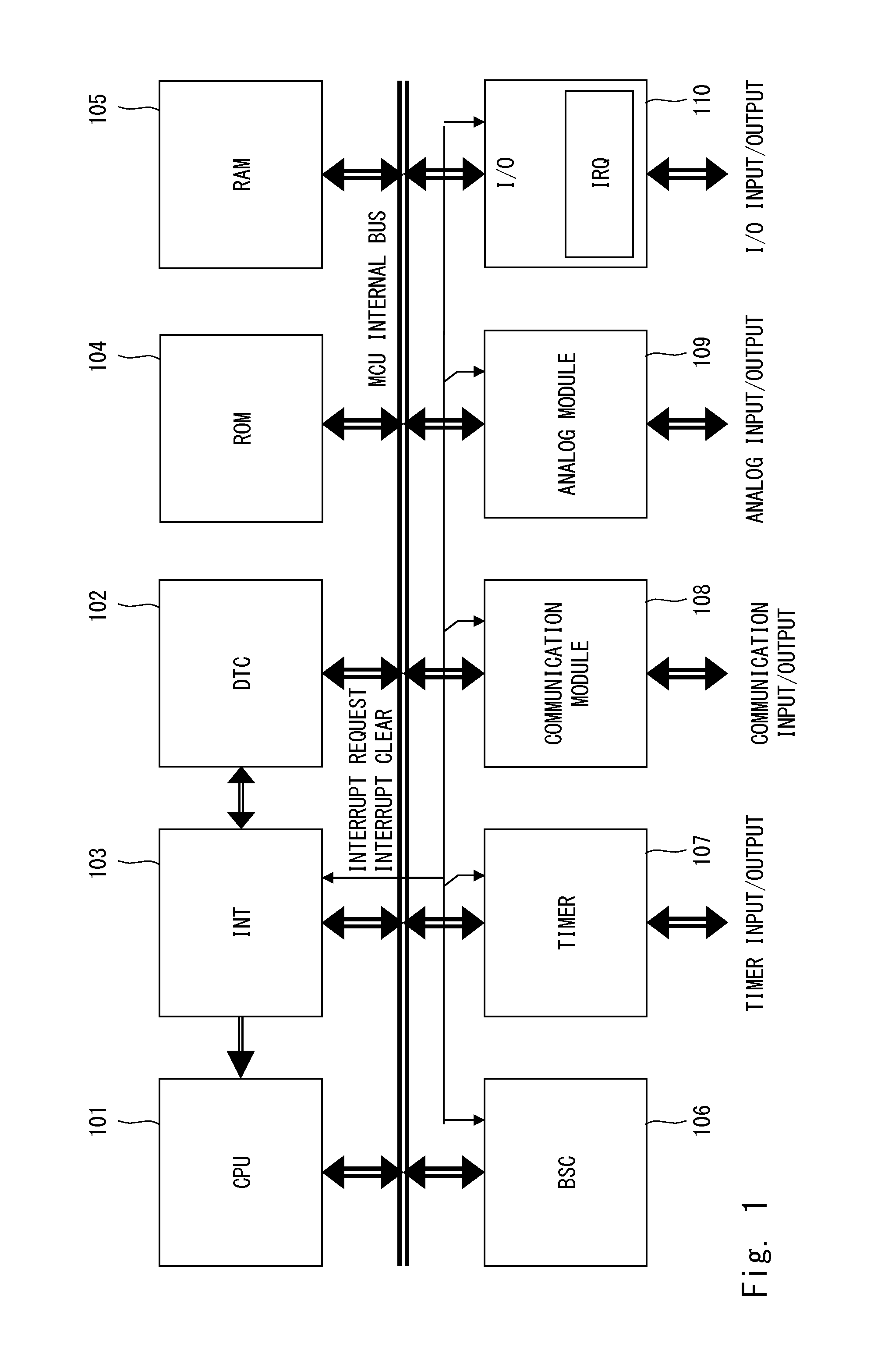

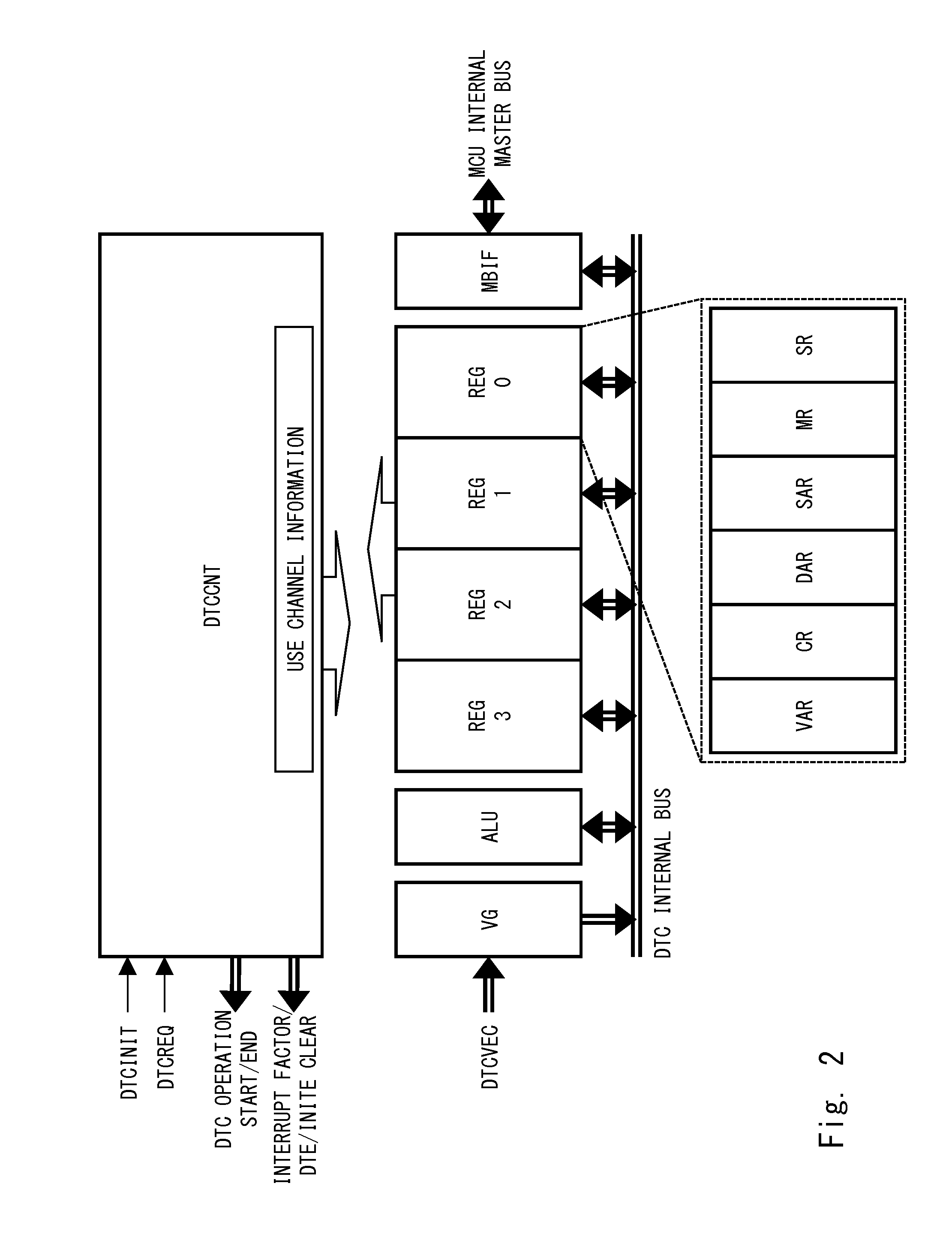

Microcomputer

ActiveUS20160048392A1Easy data transferImprove efficiencyMemory architecture accessing/allocationRegister arrangementsMicrocomputerPage address register

A microcomputer includes: a central processing unit (CPU); a data transfer apparatus (DTC); and a storage apparatus (RAM). The data transfer apparatus includes a plurality of register files each including a mode register storing the transfer mode information, an address register to which the address information is transferred, and a status register (SR) representing information that specifies the transfer information set. The data transfer apparatus checks the information of the status register, to determine whether to use the transfer information set held in the register files or to read the transfer information set from the storage apparatus and to rewrite a prescribed one of the register files. The data transfer apparatus performs data transfer based on the transfer information set stored in one of the register files.

Owner:RENESAS ELECTRONICS CORP

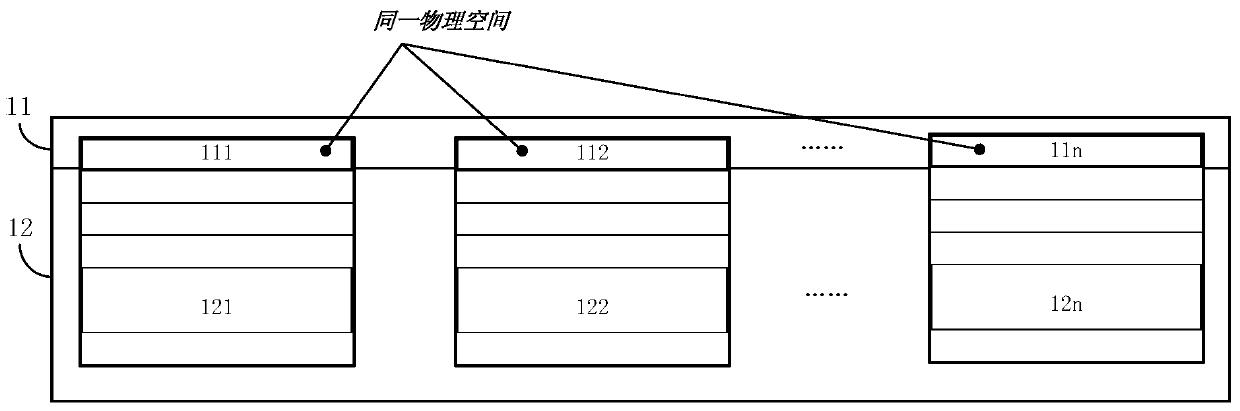

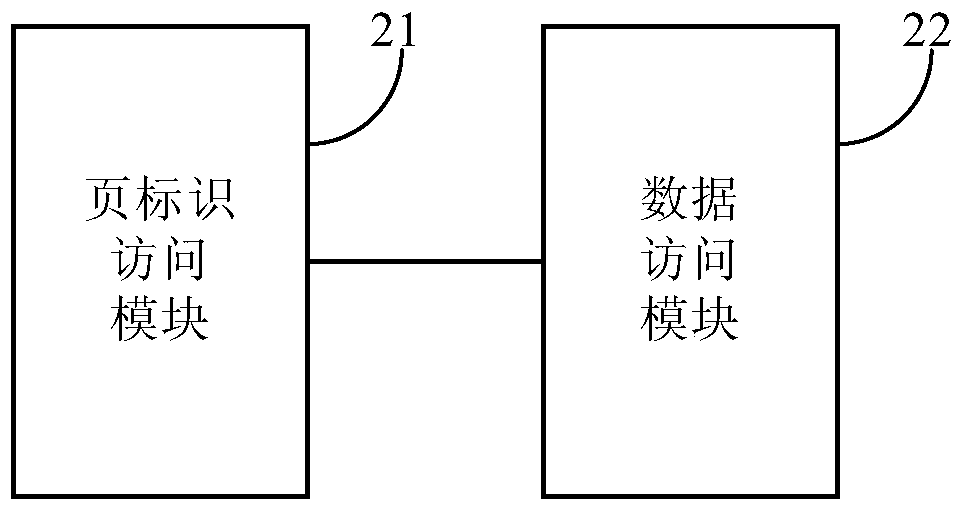

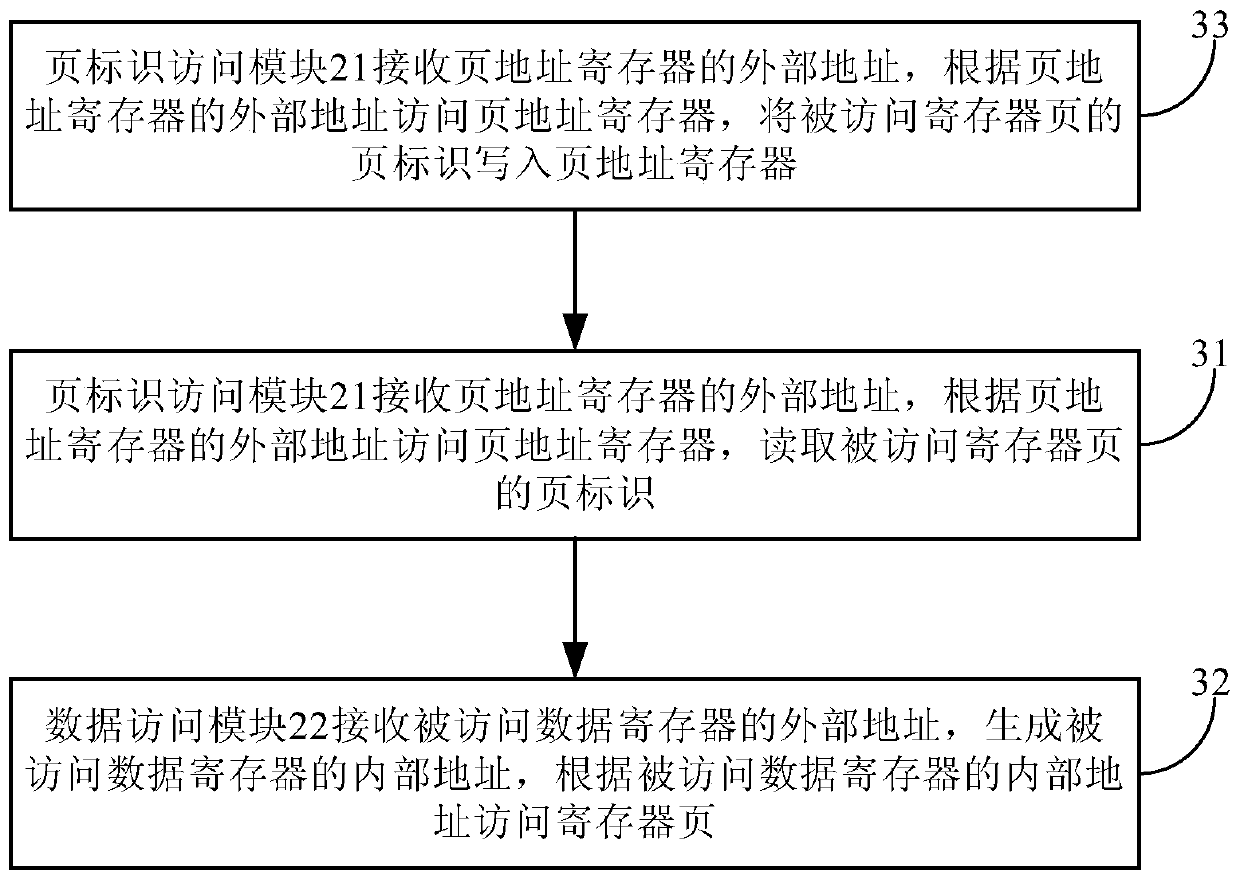

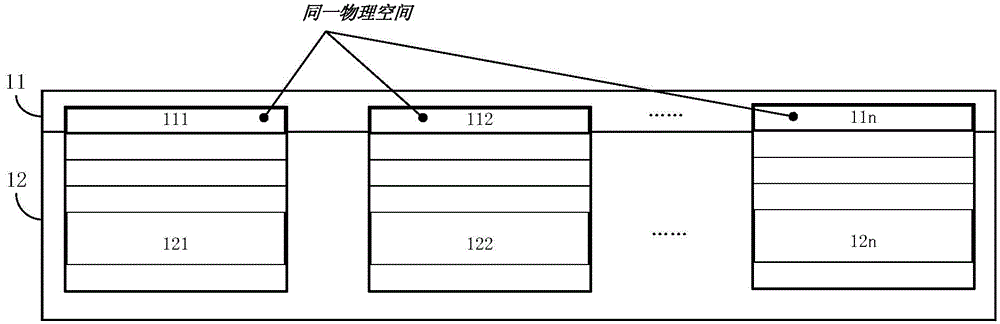

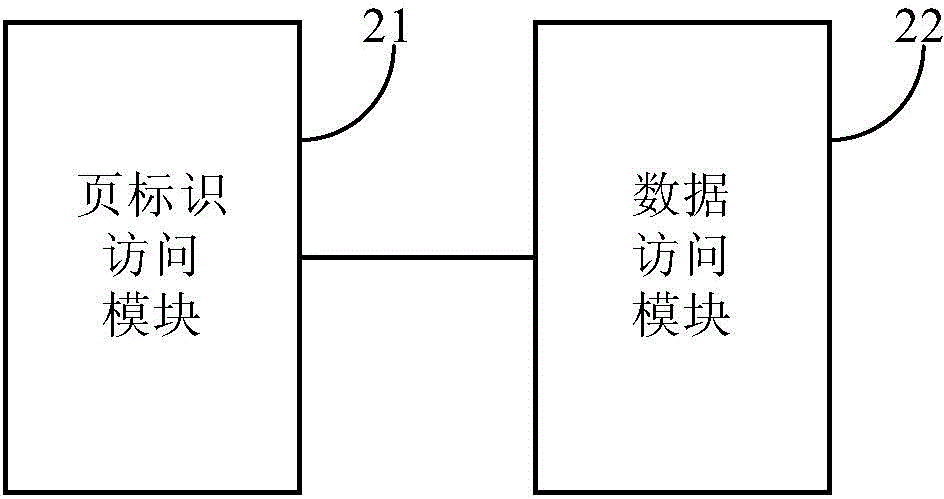

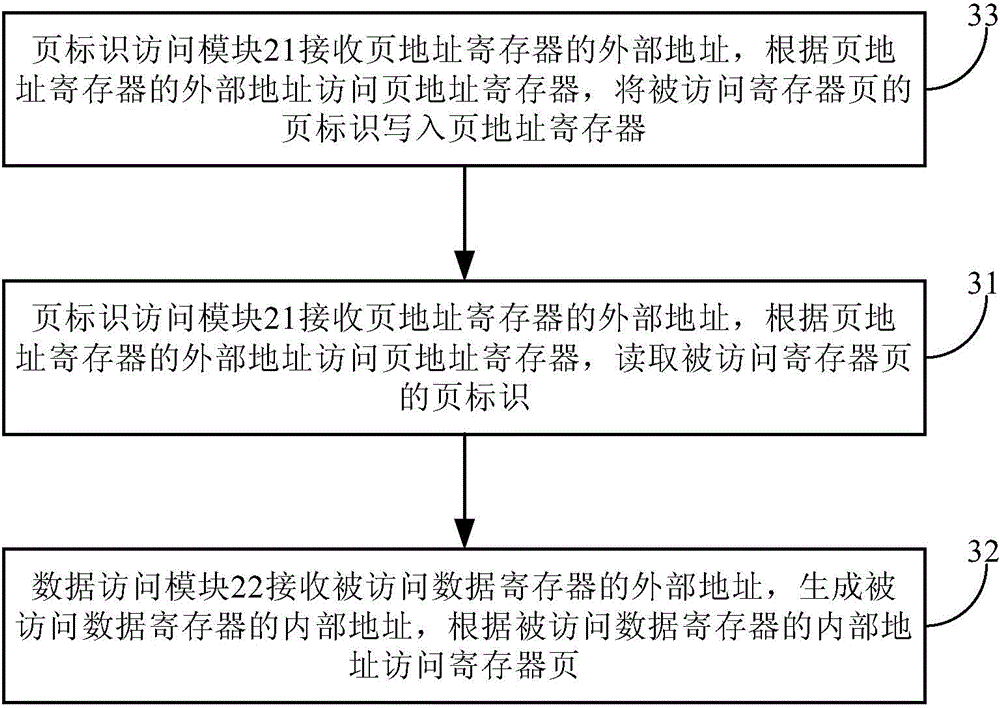

Access method and device for paging register

ActiveCN104809079BAchieve accessIncrease address space rangeMemory adressing/allocation/relocationPage address registerAccess method

The invention relates to a method and device for accessing a paging register. The paging register includes a page address register and a data register. The data register is divided into two or more register pages. The page address register is used to store the page identifier of the accessed register page. The data register uses an internal address for addressing, and the internal address includes the page of the register page. Identification and the external address of the data register, the method includes: receiving the external address of the page address register, accessing the page address register according to the external address of the page address register, reading the page identification of the accessed register page; receiving the external address of the accessed data register , generate the internal address of the accessed data register, and access the register page according to the internal address of the accessed data register. The present invention can realize that when the width of the address bus is constant, even if the number of registers to be accessed is greater than the address space range that can be allocated, all registers can be accessed.

Owner:KTMICRO ELECTRONICS

A storage management method for a microprocessor

ActiveCN104991869BEffective predictionAchieve mutual isolationMemory adressing/allocation/relocationPage address registerOperational system

Disclosed is a microprocessor storage management method: whenever a process references a logic address, a storage management unit searches in a cache index storage cell and automatically looks up in a "quick table" first; if the logic address is found, a cache address on the chip is translated; if the logic address is not found, an address translation operation is executed; a page frame number is added to last 13 bits of the logic address to obtain a physical address; if the address is in a range of a multitask protection start address register to a multitask protection end address register, virtual address translation is successful; and if the address is not in a range of the start address register to the end address register, a microprocessor generates an address translation out-of-range exception. A novel microprocessor storage management method is provided by the present invention, and translation speed of a logic address to a physical address is accelerated. The operating system can prevent illegal accesses of user programs by arranging the multitask protection start address register and the multitask protection end address register.

Owner:苏州讯升信息科技有限公司

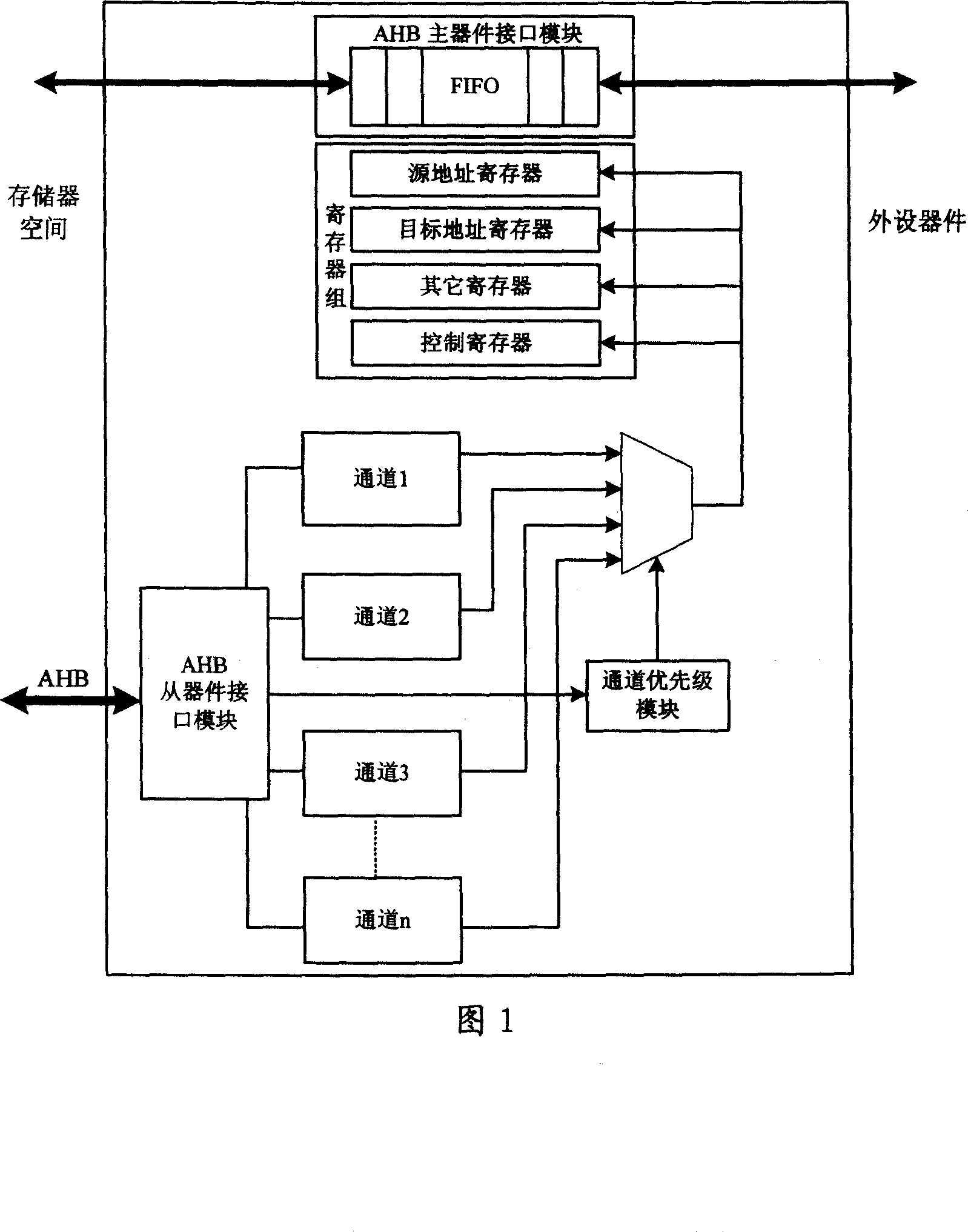

High performance DMA on embedded type processor chip

ActiveCN101556565BImprove performanceIncrease independenceElectric digital data processingPage address registerIp address

The invention relates to a high performance DMA on an embedded type processor chip. The high performance DMA comprises a data buffer used for caching the data read from an on-chip memory, the data sent to a bus interface unit, the data received from the bus interface unit, and the data written into the on-chip memory; a data big-endian and little-endian convertor; a DMA controller used for initializing a state register, a control register, an initial address register and a data size register; a DMA transmission address generating logic module used for automatically calculating the transmissionaddress of the next data on an on-chip external memory and generating chip selection and read and write signals of the on-chip memory according to the on-chip address, and simultaneously updating a data size counter till the counter changes to zero; and a bus transmission transmitter and receiver. The high performance DMA has the advantages that the development difficulty is low, the cost of thehardware is low, the transplantation is convenient, the expansibility is flexible, the data transmission speed is high, and the performance of the processor is greatly enhanced.

Owner:C SKY MICROSYST CO LTD

Method and device for accessing paging register

ActiveCN104809079AAchieve accessIncrease address space rangeMemory adressing/allocation/relocationPage address registerAccess method

The invention relates to a method and a device for accessing a paging register. The paging register comprises a page address register and a data register, wherein the data register is divided into more than two register pages; the page address register is used for storing the page identification of each accessed register page; the data register adopts an internal address to find the address, and the internal address comprises the page identification of each register page and an external address of the data register. The method comprises the following steps of receiving the external address of the page address register; according to the external address of the page address register, accessing the page address register, and reading the page identification of each accessed register page; receiving the external address of the accessed data register, generating the internal address of the accessed data register, and accessing the corresponding register page according to the internal address of the accessed data register. The method has the advantage that when the width of an address bus is set, even if the number of the accessed registers is greater than the distributed address space range, all registers can be accessed.

Owner:KTMICRO ELECTRONICS

Method for implementing two-dimensional data delivery using DMA controller

ActiveCN100511195CRealize the process of supporting two-dimensional data handlingElectric digital data processingPage address registerProcessor register

The invention discloses a method for realizing two-dimensional data transfer by using a DMA controller, which adds and sets a source base address register, a target base address register, a limit register, and a stride register, which includes the following steps: the DMA controller starts from Take out the source address from the source address register, obtain the data stored in the address, and judge whether the memory space is the last memory space, if not, calculate the next source address to be accessed according to the value in the stride register, Store it in the source address register; if yes, jump to the next address of the first memory space, and store this address in the source address register. Because the method of the invention adopts the two-dimensional jump method, the DMA controller supports the two-dimensional data transfer process.

Owner:SANECHIPS TECH CO LTD

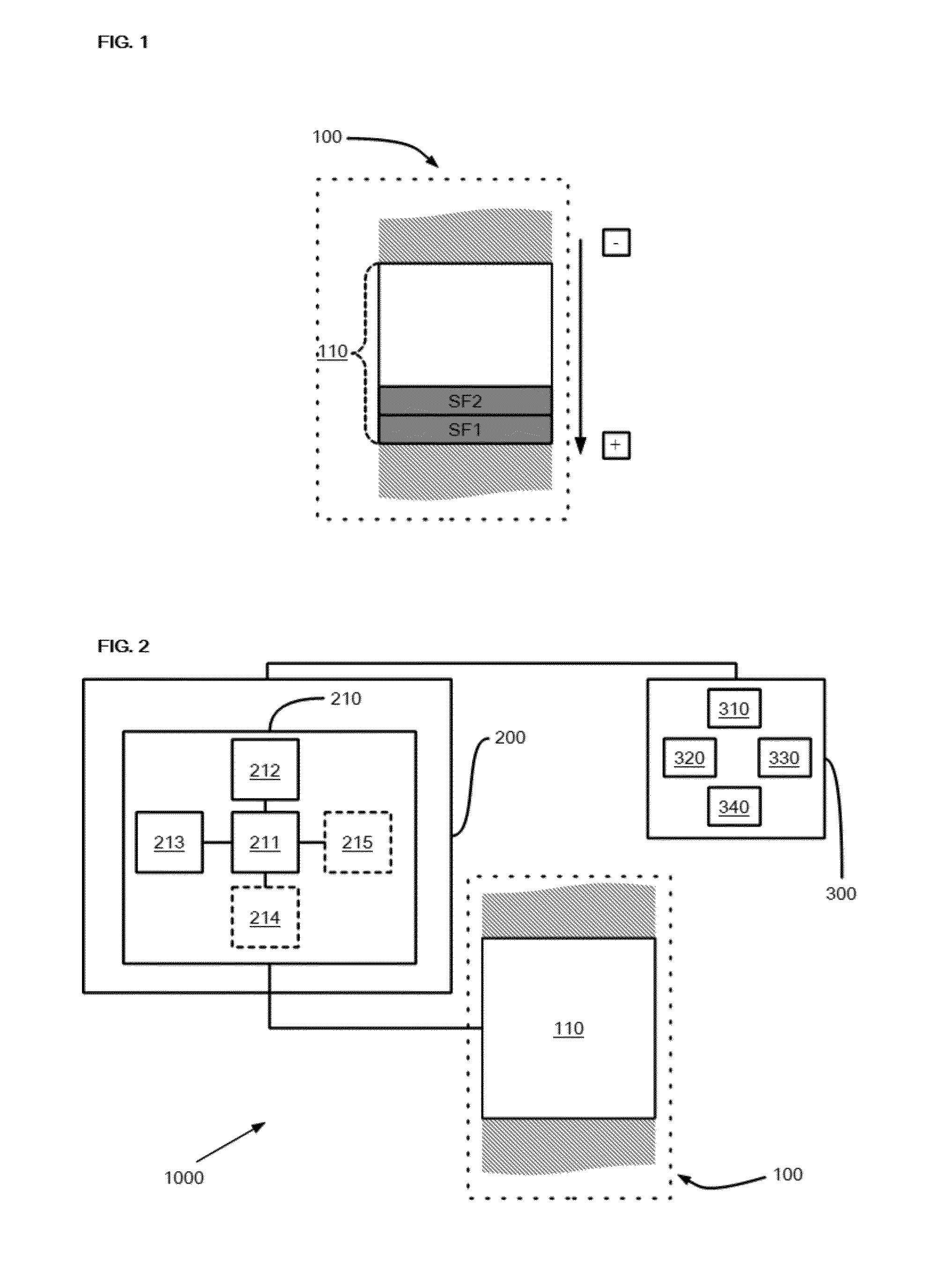

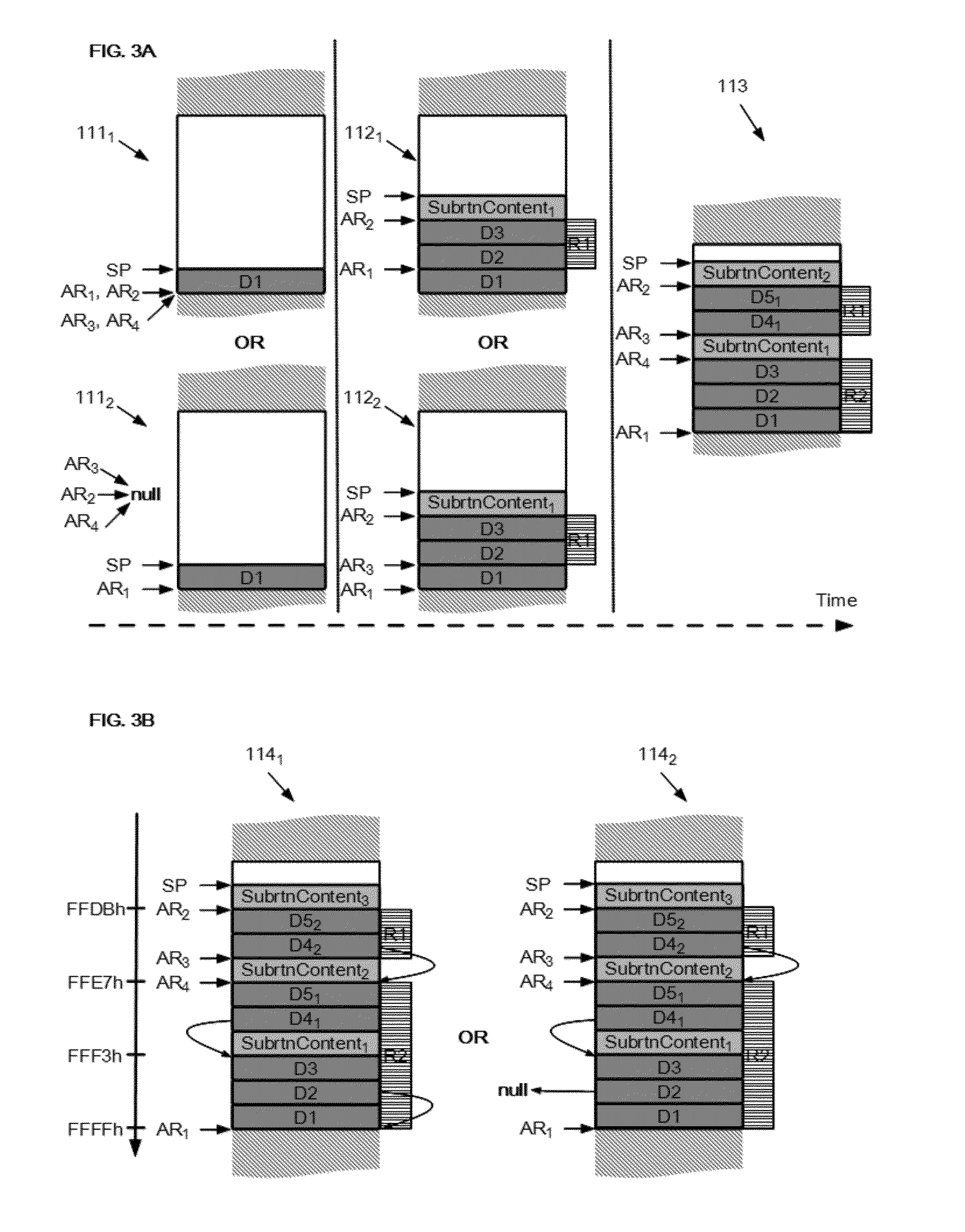

Dynamic subroutine stack protection

ActiveUS9411747B2Memory architecture accessing/allocationUnauthorized memory use protectionPage address registerProcessor register

A protection unit of a subroutine stack accessible by a CPU controlled by one main software program, for storing and removing stack frame(s), the stack protection unit being coupleable to the stack and the CPU, comprising:a processor coupled to a first and a second address register;wherein, when a first stack frame is stored onto the stack and the execution of the main software program is suspended by the CPU due to the execution of a subroutine;the processing unit is adapted to set one access rule based on the first and second address registers, preventing:the ongoing subroutine, from accessing a hardware-protected region of the stack, comprising at least one stack frame associated with a return address from which the main software program resumes execution after termination of the execution of the subroutine.A processor, a method and a computer program are also claimed.

Owner:NXP USA INC

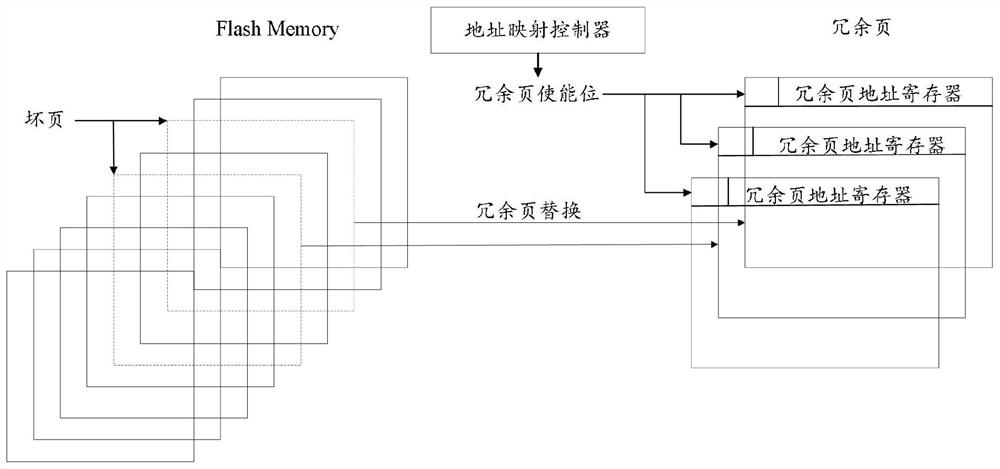

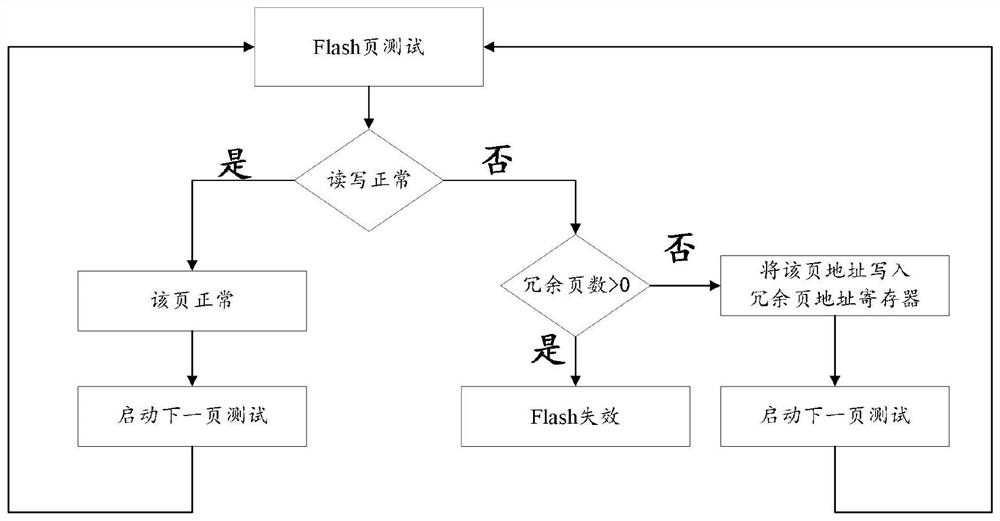

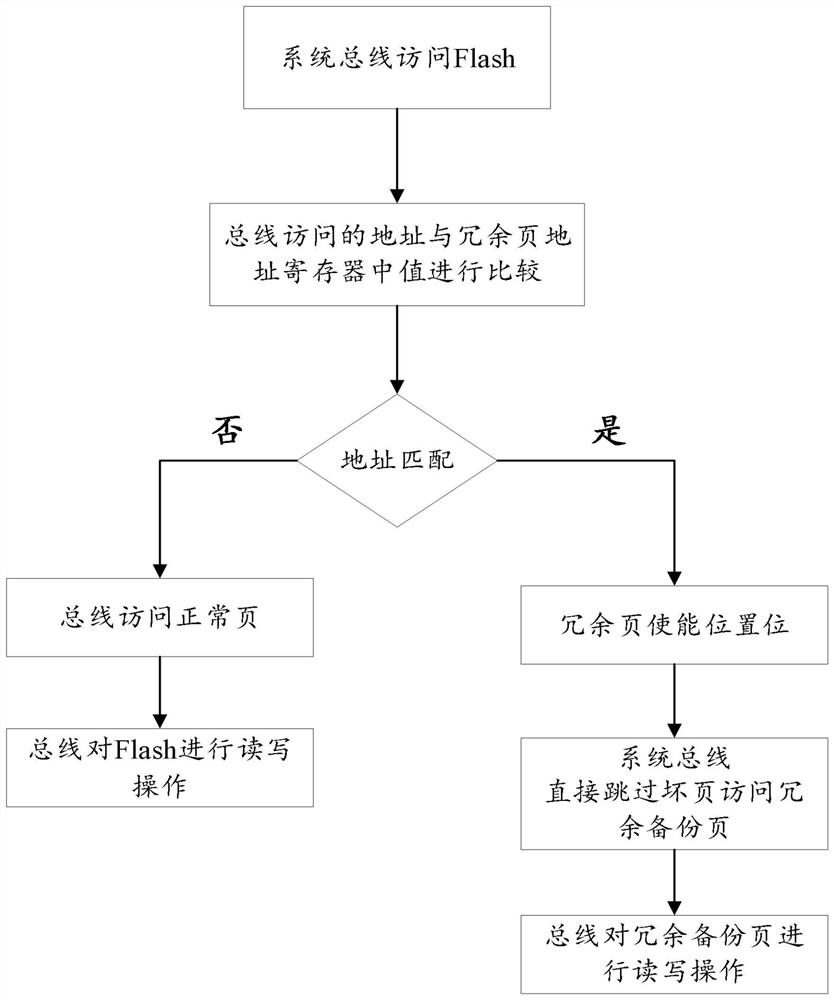

Processing method and system for improving yield of embedded Flash

PendingCN114003515AImprove yieldGuaranteed correctnessInput/output to record carriersMemory loss protectionPage address registerIntegrated circuit

The invention discloses a processing method and system for improving the yield of embedded Flash, and belongs to the field of integrated circuits. The method comprises the following steps of: after erasing the Flash, performing write operation and read operation on each page of the Flash, judging whether the page is a normal page or a bad page, and directly writing a page address of the bad page into a redundant page address register when the bad page appears; when the system bus accesses the Flash, comparing the address accessed by the system bus with the median of the address register of the redundant page, and if the comparison result is inconsistent, indicating that the system bus accesses the normal page at the moment, and the redundant page does not need to be accessed; if the comparison result is consistent, indicating that the system bus accesses a bad page at the moment, setting a redundant page enabling position, and directly skipping the bad page by the system bus to access a redundant backup page; when the enable bit of the redundant page is 1, indicating that the replacement of the bad page by the redundant page takes effect, and the read-write operation of the system bus on the Flash bad page is mapped to the redundant page.

Owner:CHINA KEY SYST & INTEGRATED CIRCUIT

Write buffer detector and parallel channel write method

InactiveCN102521160BAvoid misjudgmentImprove performanceInput/output to record carriersMemory adressing/allocation/relocationPage address registerParallel channel

The invention provides a solid state disk (SSD) controller based on a write buffer detector, an addressing method of written data and an optional parallel channel write method, which achieve accurate judgment on address characteristics of data, respectivelycache continuous address data and random address data, write different write strategies according to different data types, and improve write speed of random data. The write buffer detector comprises an address subtractor, a continuous data buffer and a random data buffer, wherein the address subtractor is used for conducting subtraction on current page addresses and previous page addresses and comprises a previous page address register and a current page address register, the previous page address register is used for storing data and addresses at the previous page, and the current page address register is used for storing data and addresses at the current page; the size of the continuous data buffer is set to be a parameter Sequential-Buffer-Size, the continuous data buffer is used for caching data which is probably judged to be continuous access data, and data in the continuous data buffer is judged to be continuous data if the length of data in the continuous data buffer reaches the set parameter; and the random data buffer is used for caching random access data.

Owner:SHANGHAI JIAOTONG UNIV