Write buffer detector, addressing method of written data and parallel channel write method

A detector and data buffer technology, applied in the direction of input/output to record carrier, memory address/allocation/relocation, etc., can solve the problems of long erasing time, limited erasing times, and inability to directly rewrite data, etc. The effect of preventing misjudgment or omission, improving performance and reducing overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

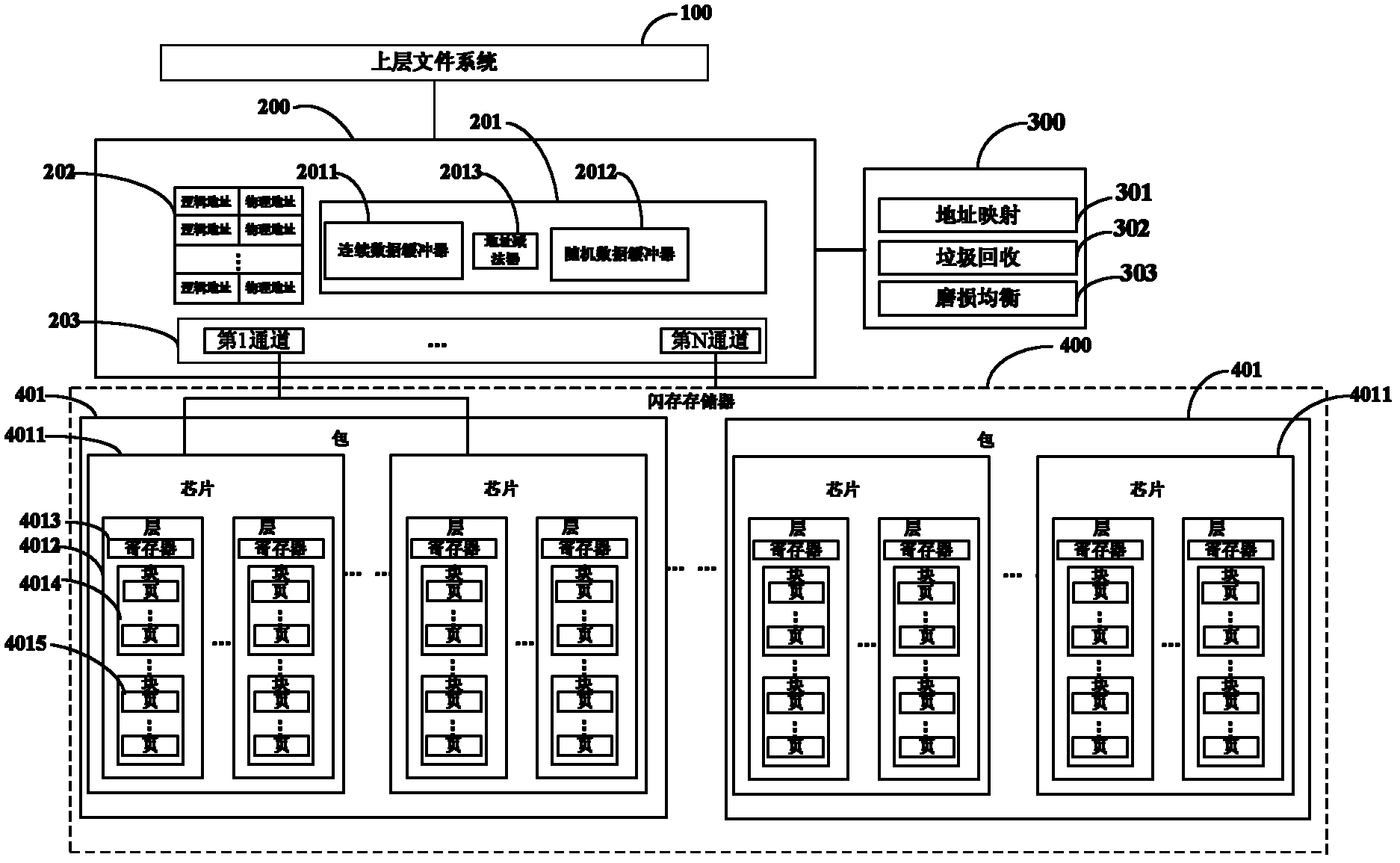

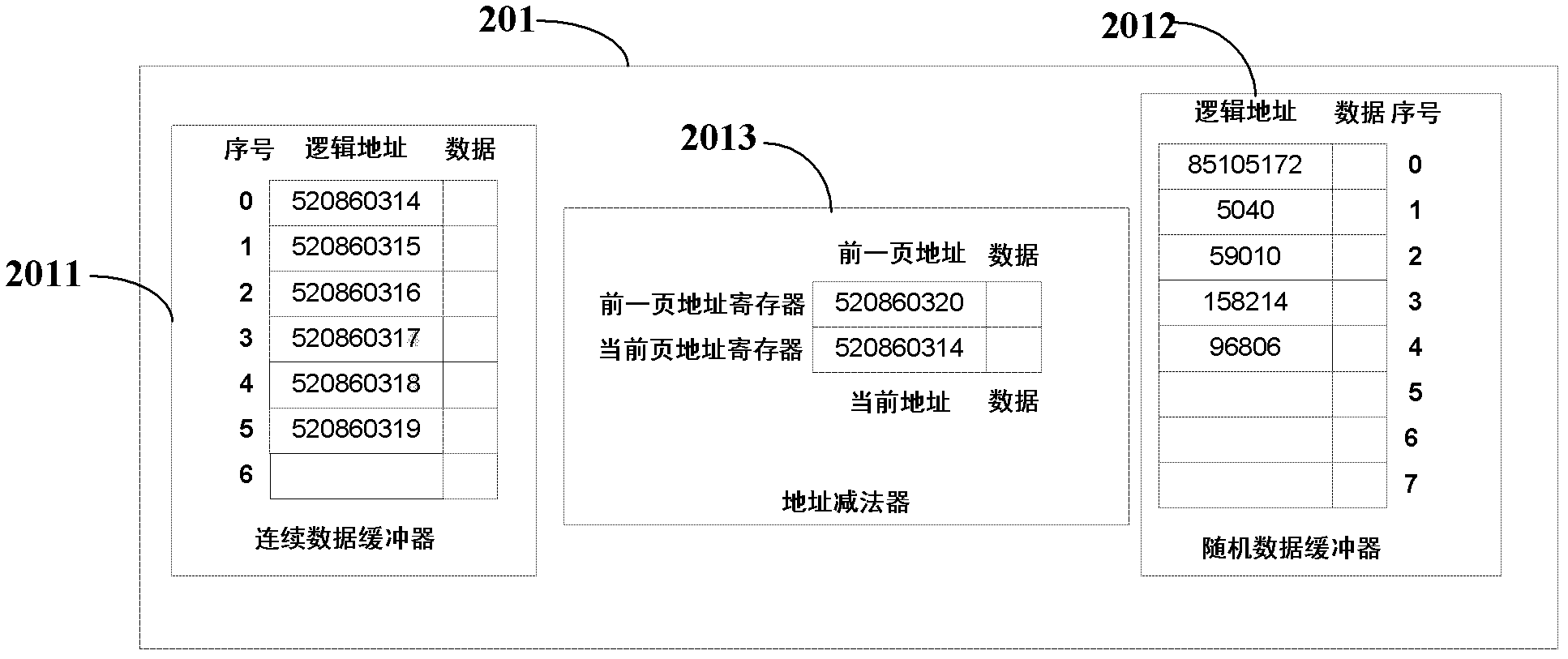

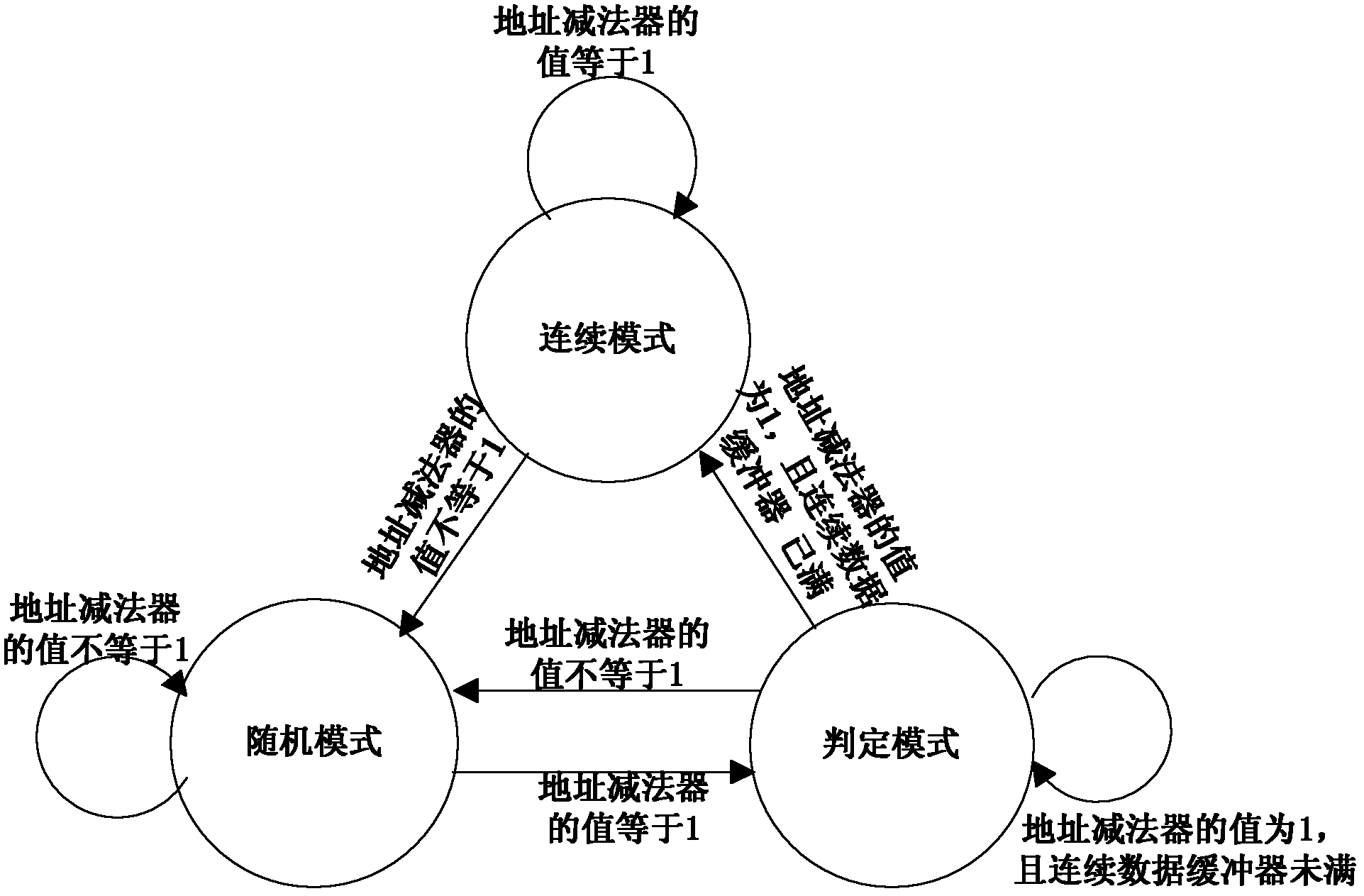

[0040] The invention is a design method of a flash memory conversion layer based on a write buffer detector, which is mainly used for realizing accurate judgment of address characteristics of write data, and respectively buffering continuous address data and random address data. Different write strategies are used for different data types. Because the writing of random data is the current bottleneck in the performance of flash memory, the present invention proposes an optional parallel multi-channel technology to effectively improve the writing performance of random data.

[0041] The technical solutions of the present invention will be described in detail below in conjunction with specific embodiments. In order to better refer to the technical solution of the present invention, please combine figure 1 A schematic structural diagram of a system including the write buffer detector of the present invention is shown. The upper file system 100 passes through the controller 200 ,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More