Memory control apparatus

A control device and memory technology, applied in the direction of instruments, memory address/allocation/relocation, electrical digital data processing, etc., can solve the problems of data buffer hit rate reduction, data buffer hit, and failure to obtain external memory matching. , to achieve effective access and prevent the reduction of hit rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 2 approach

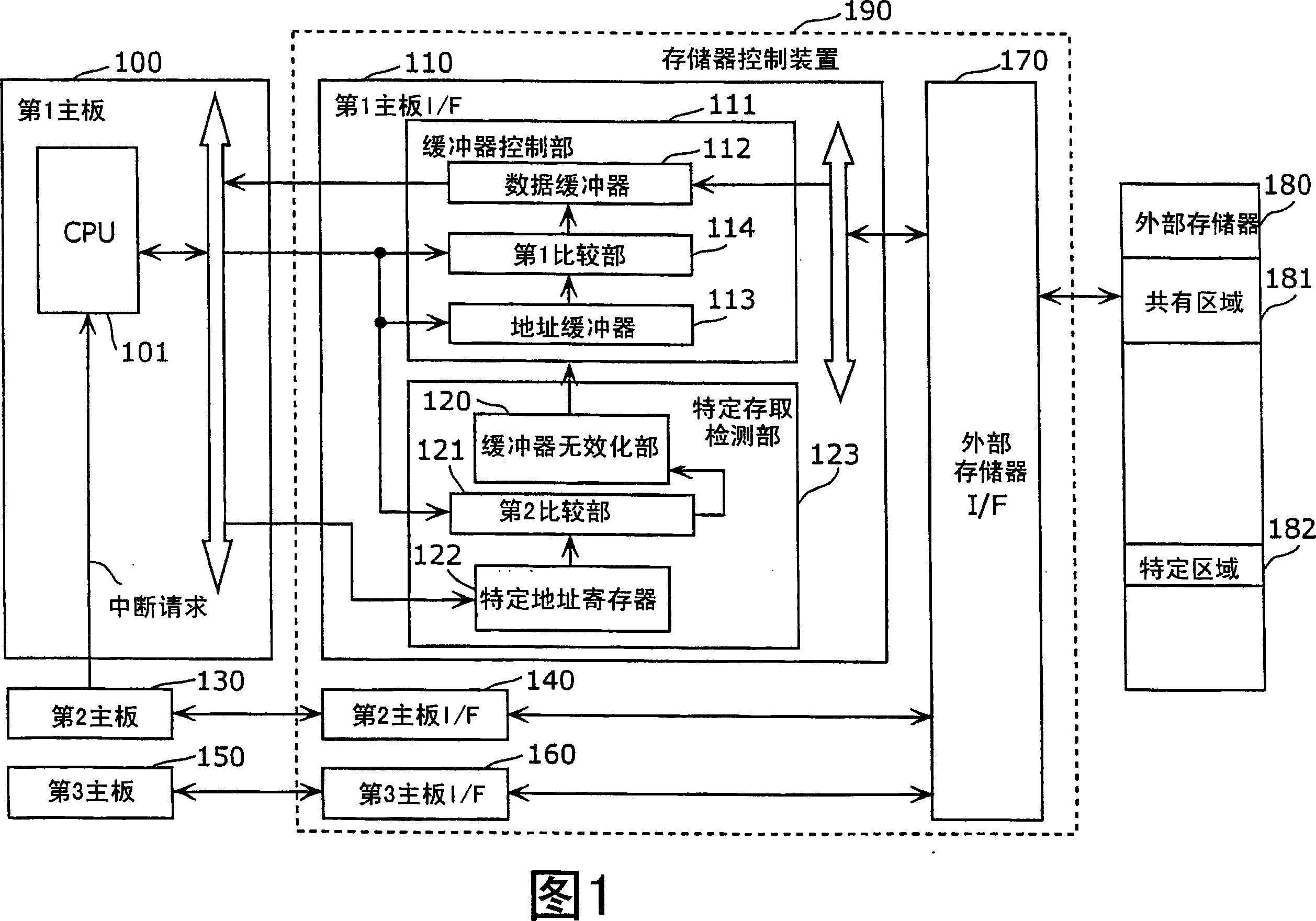

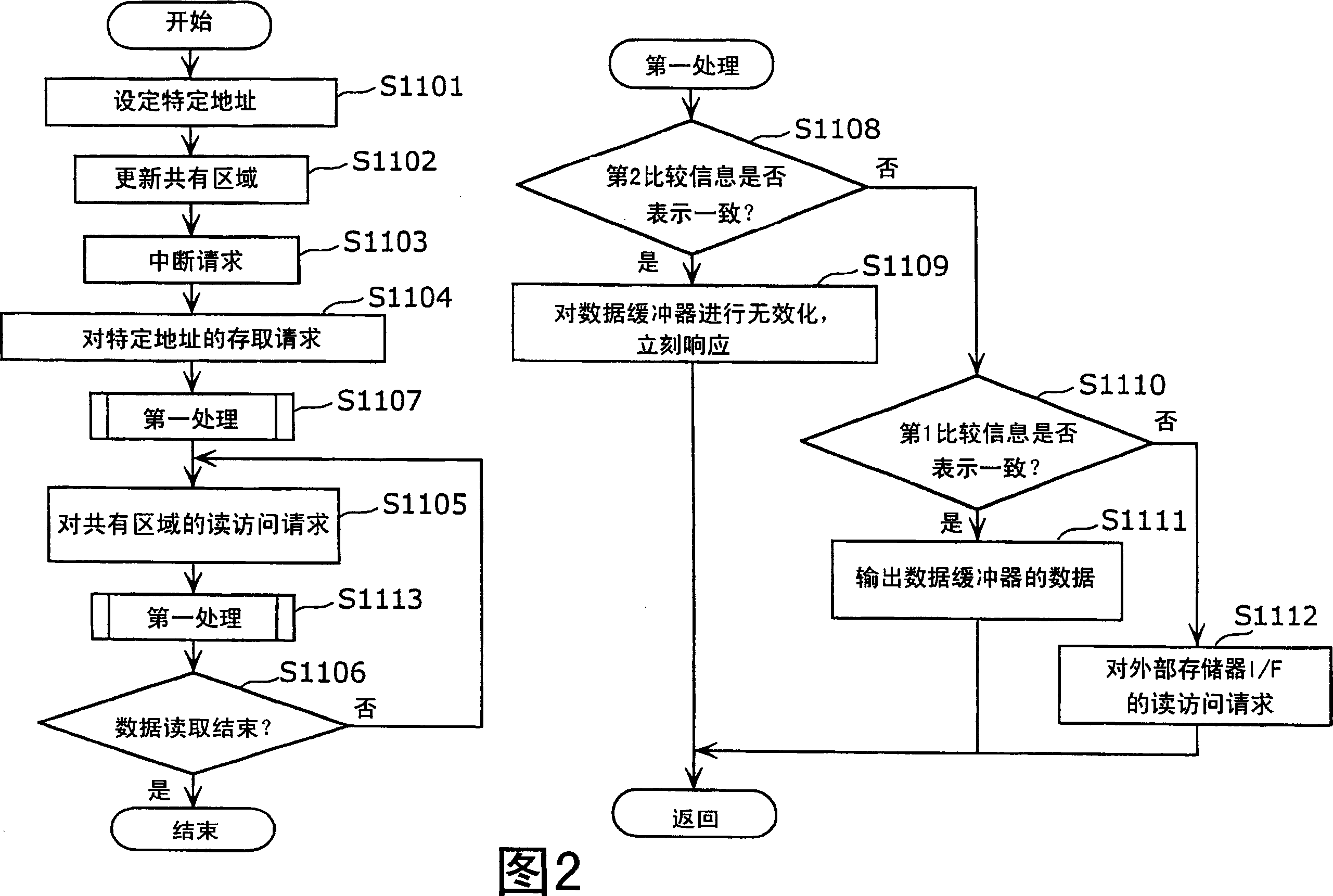

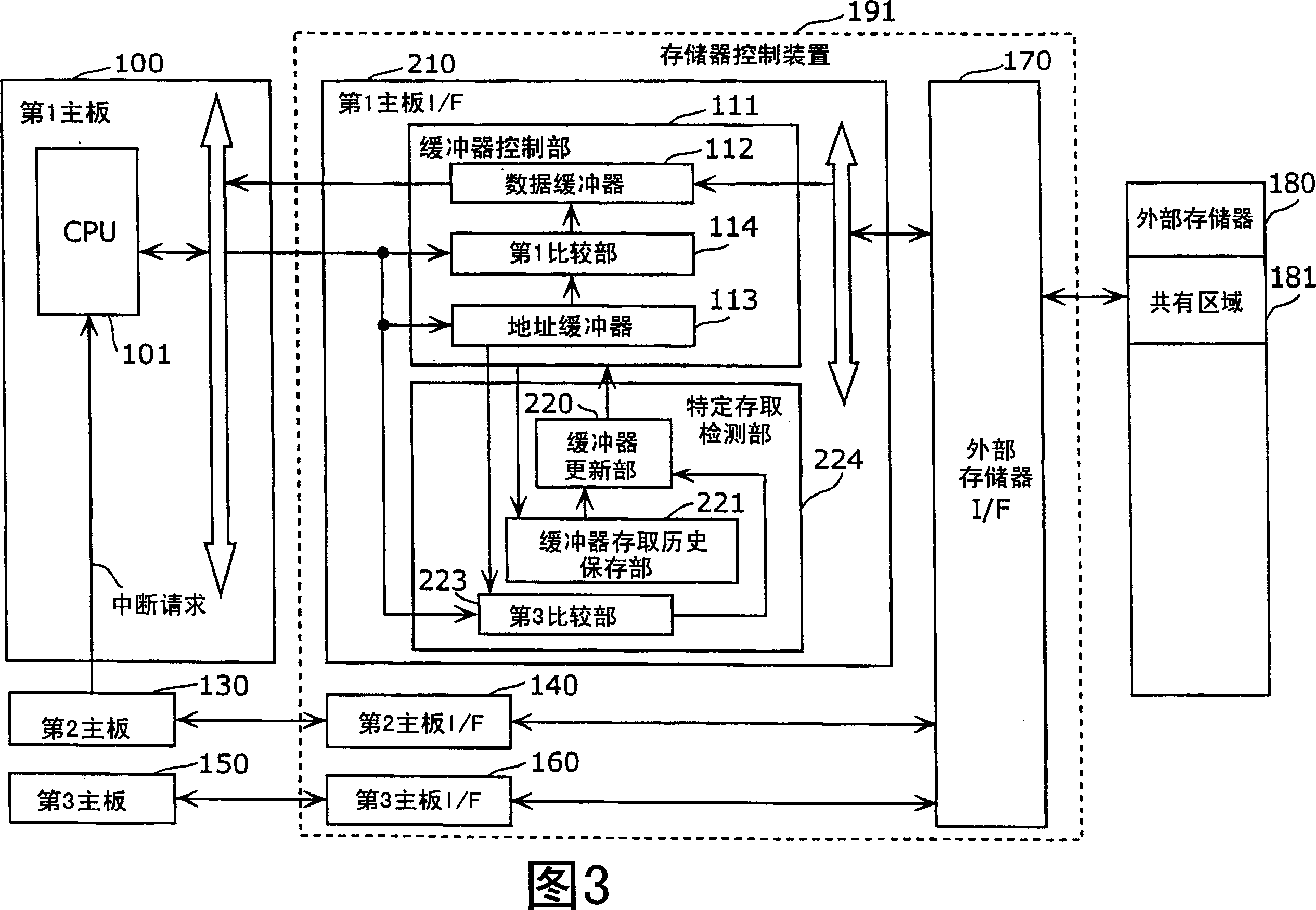

[0091] FIG. 3 is a block diagram showing an example of the functional configuration of the memory control device 191 of the second embodiment. In FIG. 3 , together with the memory control device 191 , the first motherboard 100 , the second motherboard 130 , the third motherboard 150 , and the external memory 180 are shown.

[0092] The memory control device 191 is configured by replacing the specific access detection unit 123 of the first motherboard I / F 110 of the memory control device 190 (see FIG. 1 ) described in the first embodiment with the specific access detection unit 224 . In FIG. 3 , the same function blocks as those of the access control device 190 are denoted by the same symbols, and description thereof will be omitted.

[0093] The specific access detection unit 224 is a unit that controls the buffer control unit 111 to forcibly access the external memory 180 every other time when consecutive access requests to the same address occur, and includes a buffer update...

no. 3 approach

[0116] FIG. 5 is a block diagram showing an example of the functional configuration of the memory control device 192 according to the third embodiment. In FIG. 5 , together with the memory control device 192 , the first motherboard 100 , the second motherboard 130 , the third motherboard 150 , and the external memory 180 are shown.

[0117] The memory control device 192 has a configuration in which the dummy access issuing unit 302 is added to the memory control device 190 (see FIG. 1 ) described in the first embodiment. In FIG. 5 , the same functional blocks as those of the memory control device 190 are assigned the same reference numerals, and description thereof will be omitted.

[0118] The dummy access issuing unit 302 receives an interrupt request from the second main board 130 indicating that the data in the common area 181 on the external memory 180 is updated, and issues an access to the above-mentioned specific address to the first main board I / F 110. requested unit...

no. 4 approach

[0129] Next, the configuration of the fourth embodiment will be described.

[0130] FIG. 7 is a block diagram showing an example of the functional configuration of the memory control device 193 according to the fourth embodiment. In FIG. 7 , the first main board 100 , the second main board 130 , the third main board 150 , and the external memory 180 are shown together with the memory control device 193 .

[0131] The memory control device 193 is configured by adding the dummy access issuing unit 402 to the memory control device 191 (see FIG. 3 ) described in the second embodiment. In FIG. 7 , the same blocks as those of the memory control device 191 are denoted by the same reference numerals, and description thereof will be omitted.

[0132] The dummy access issuing unit 402 is a unit that receives an interrupt request from the second main board 130 indicating that the data in the common area 181 on the external memory 180 has been updated, and issues an access request to the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More