Patents

Literature

120results about "Multistate logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

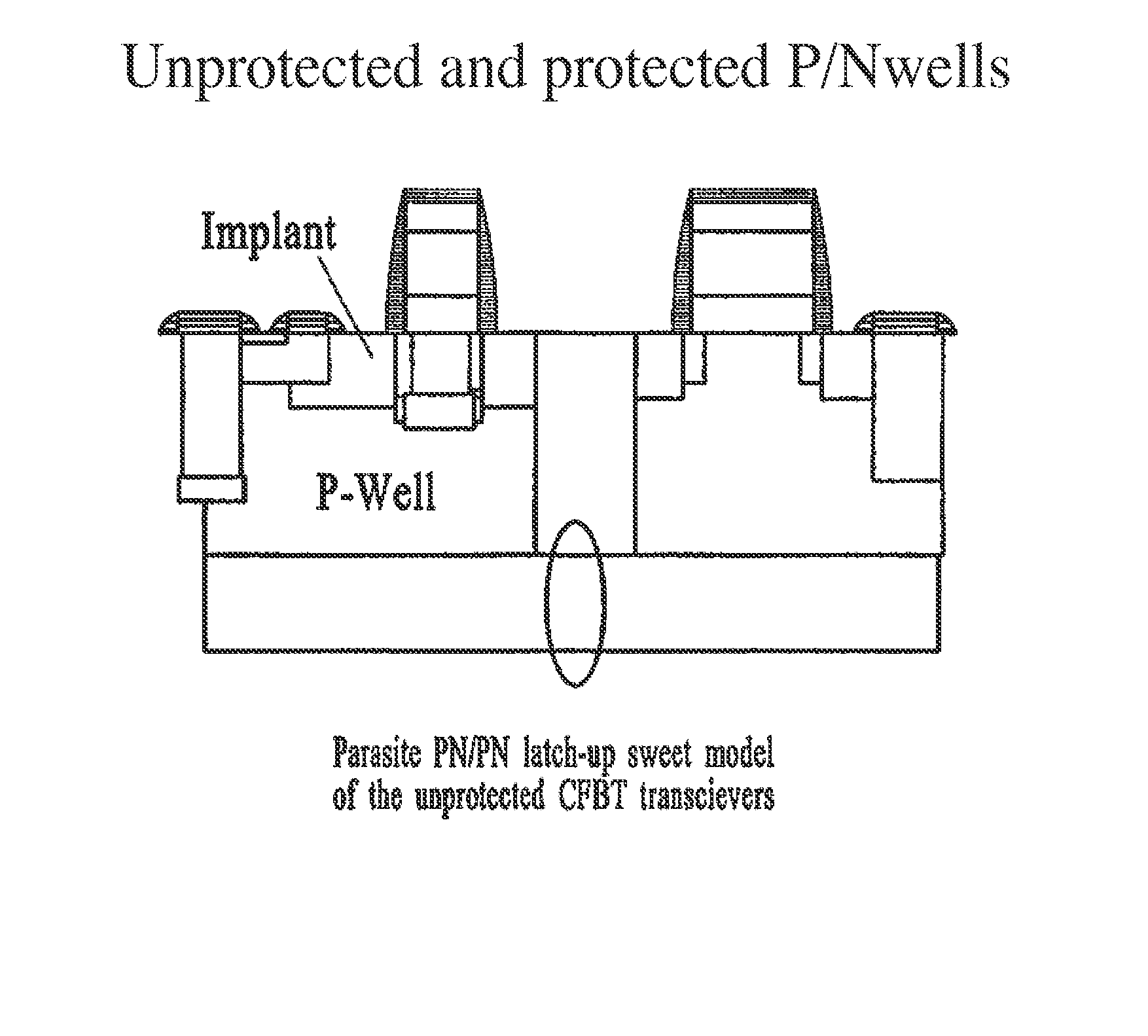

Variable threshold transistor for the Schottky FPGA and multilevel storage cell flash arrays

InactiveUS20060044018A1Low powerImprove performanceMultistate logicSolid-state devicesSchottky barrierMulti-level cell

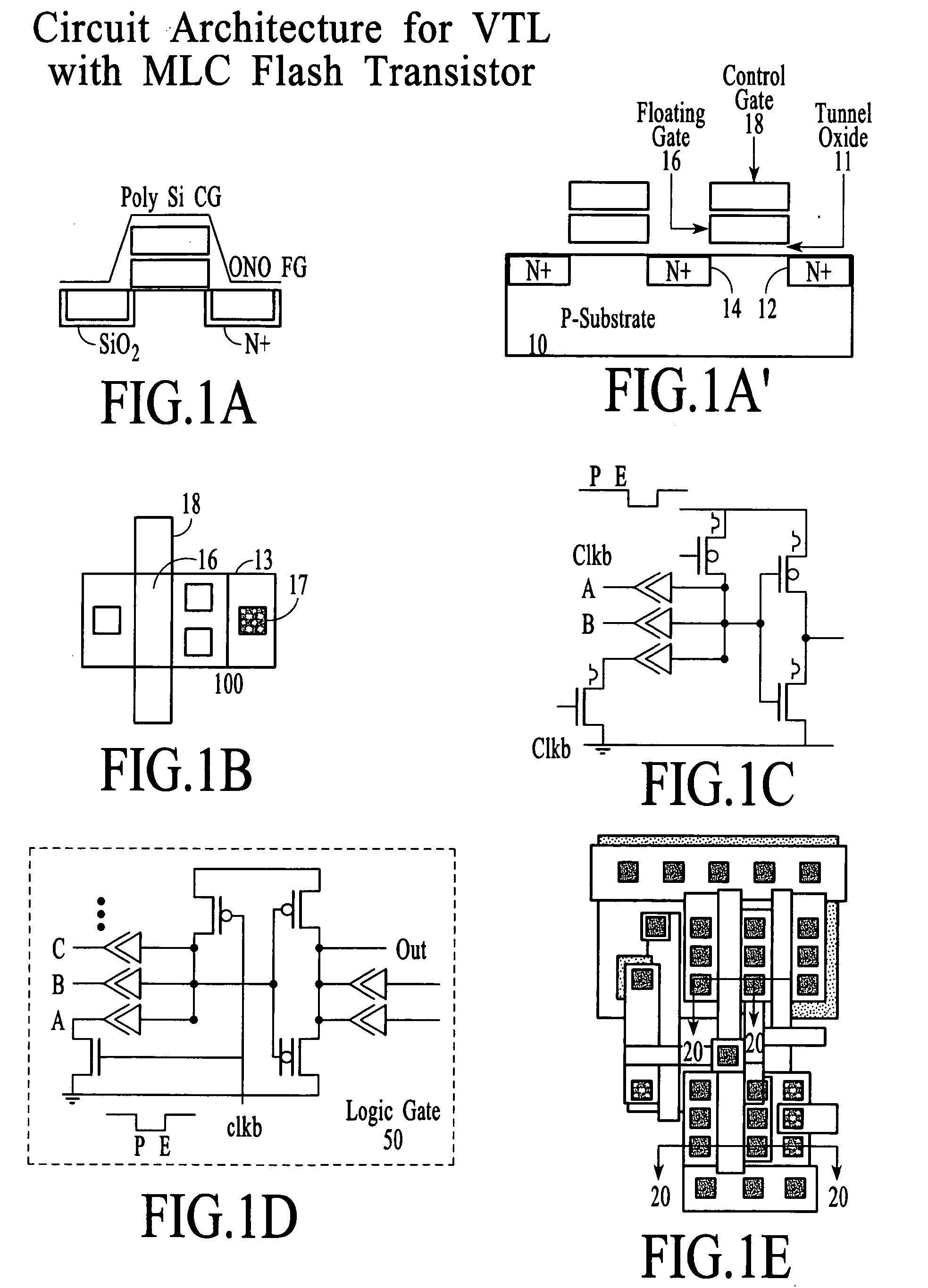

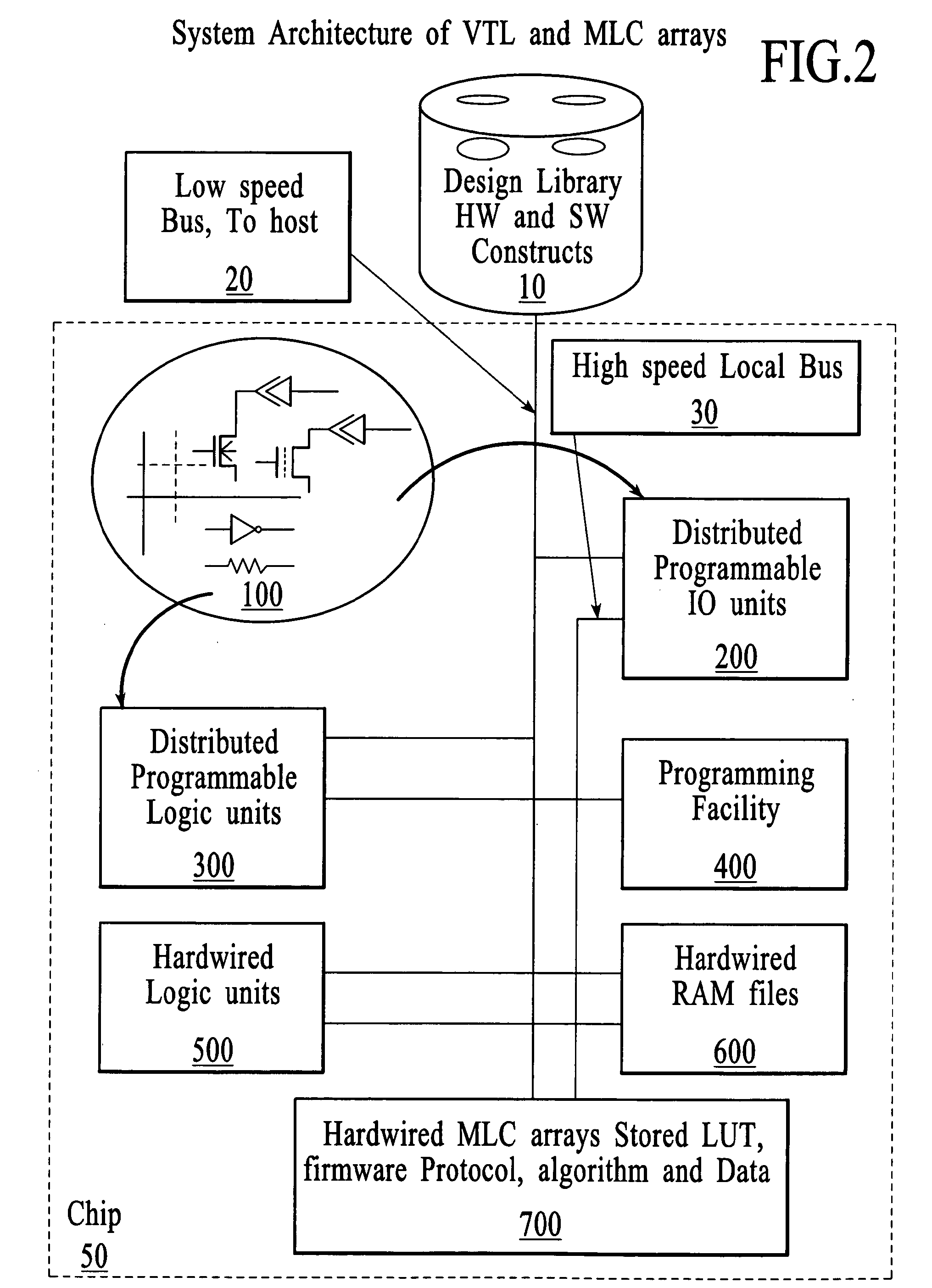

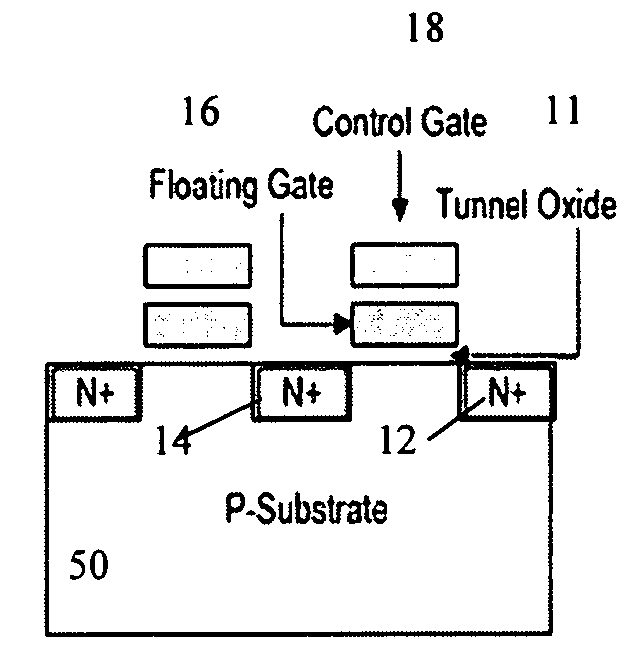

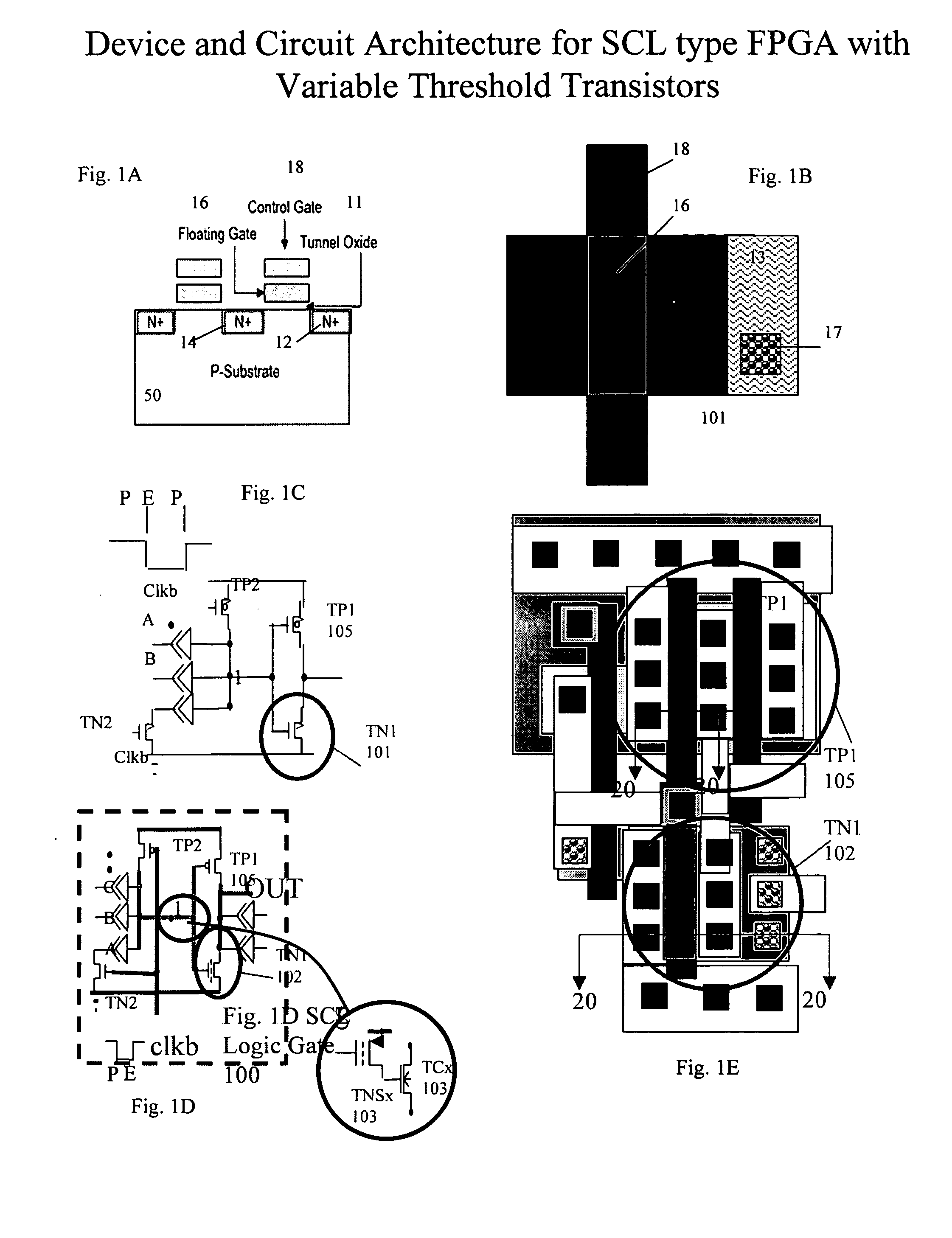

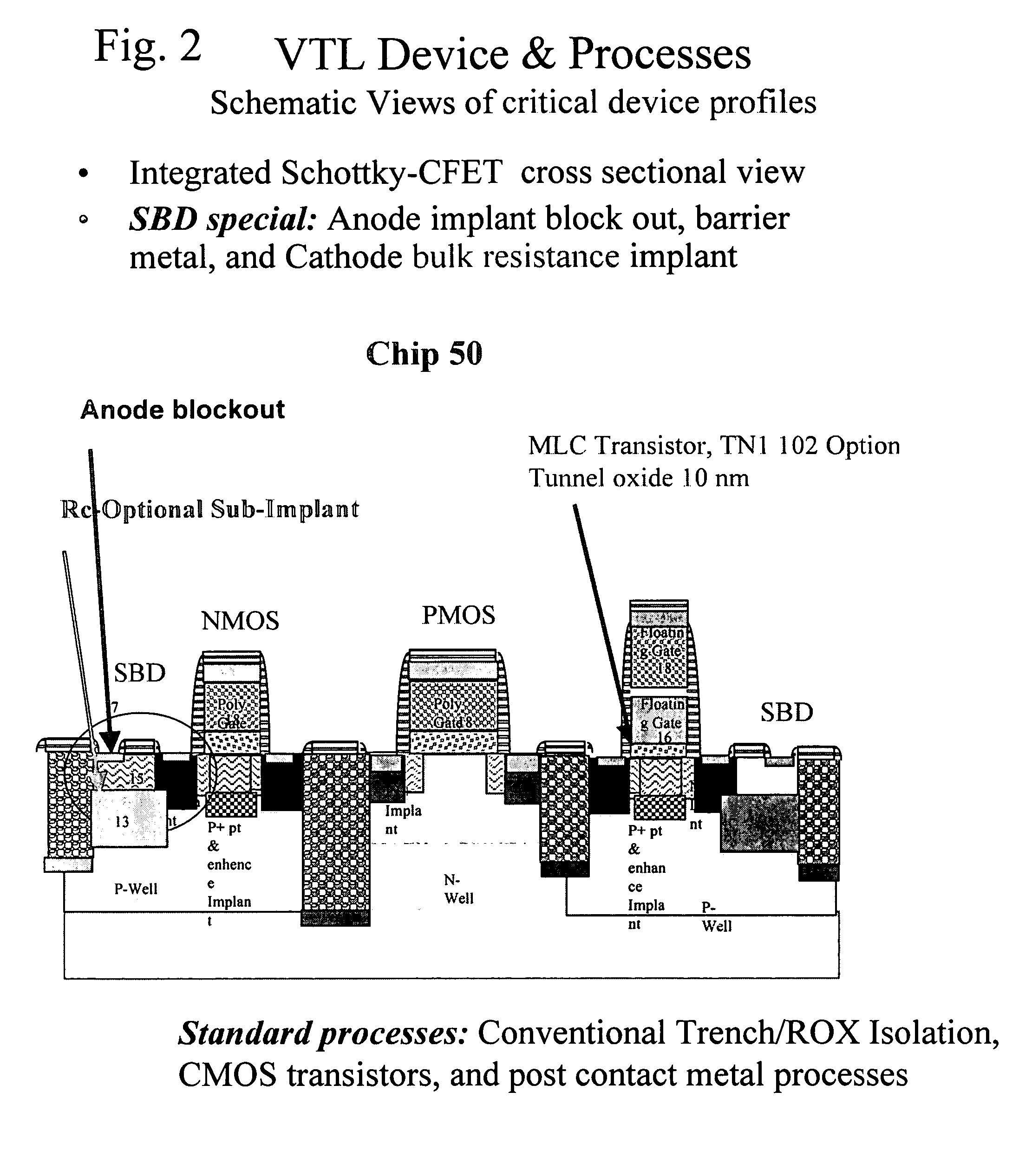

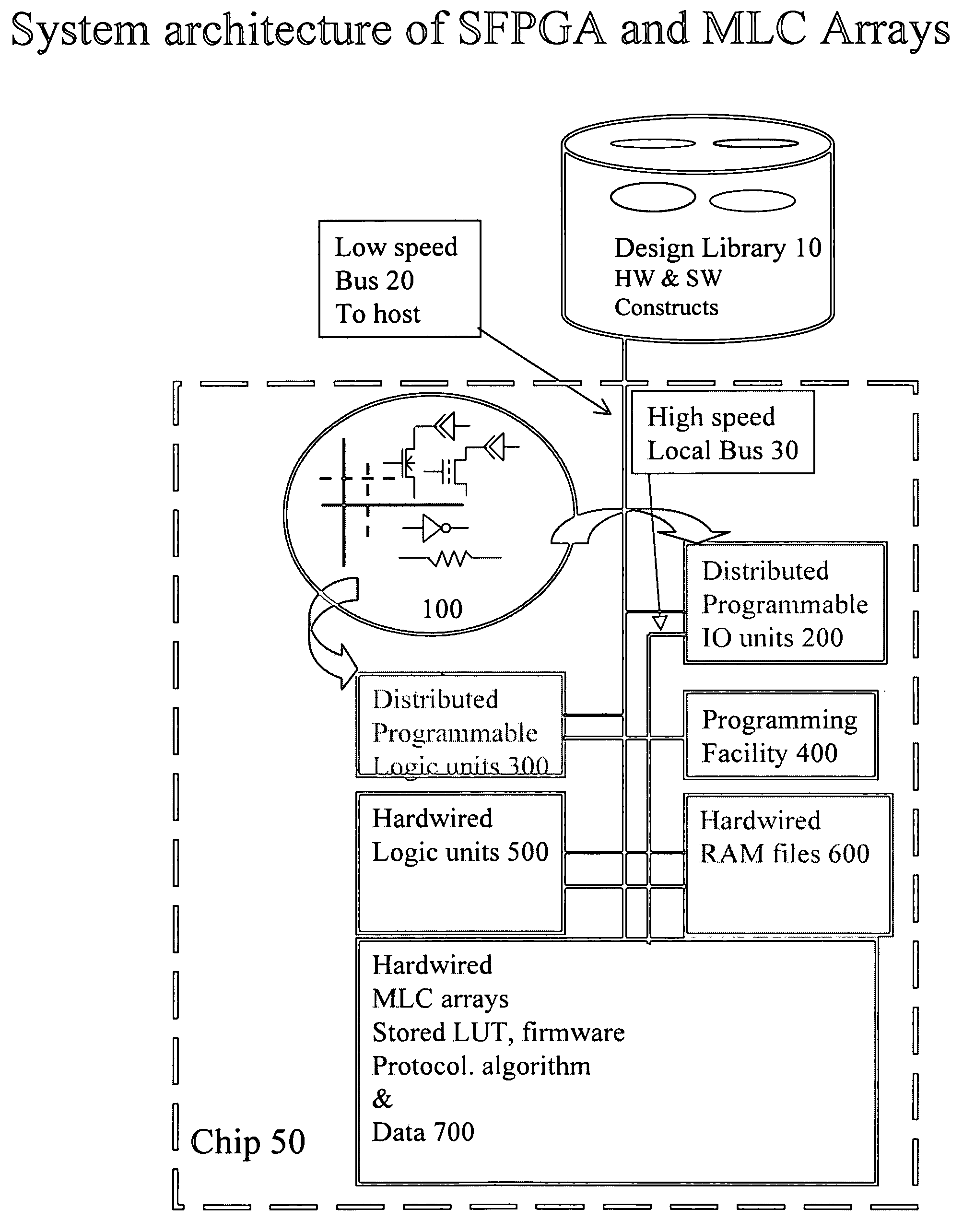

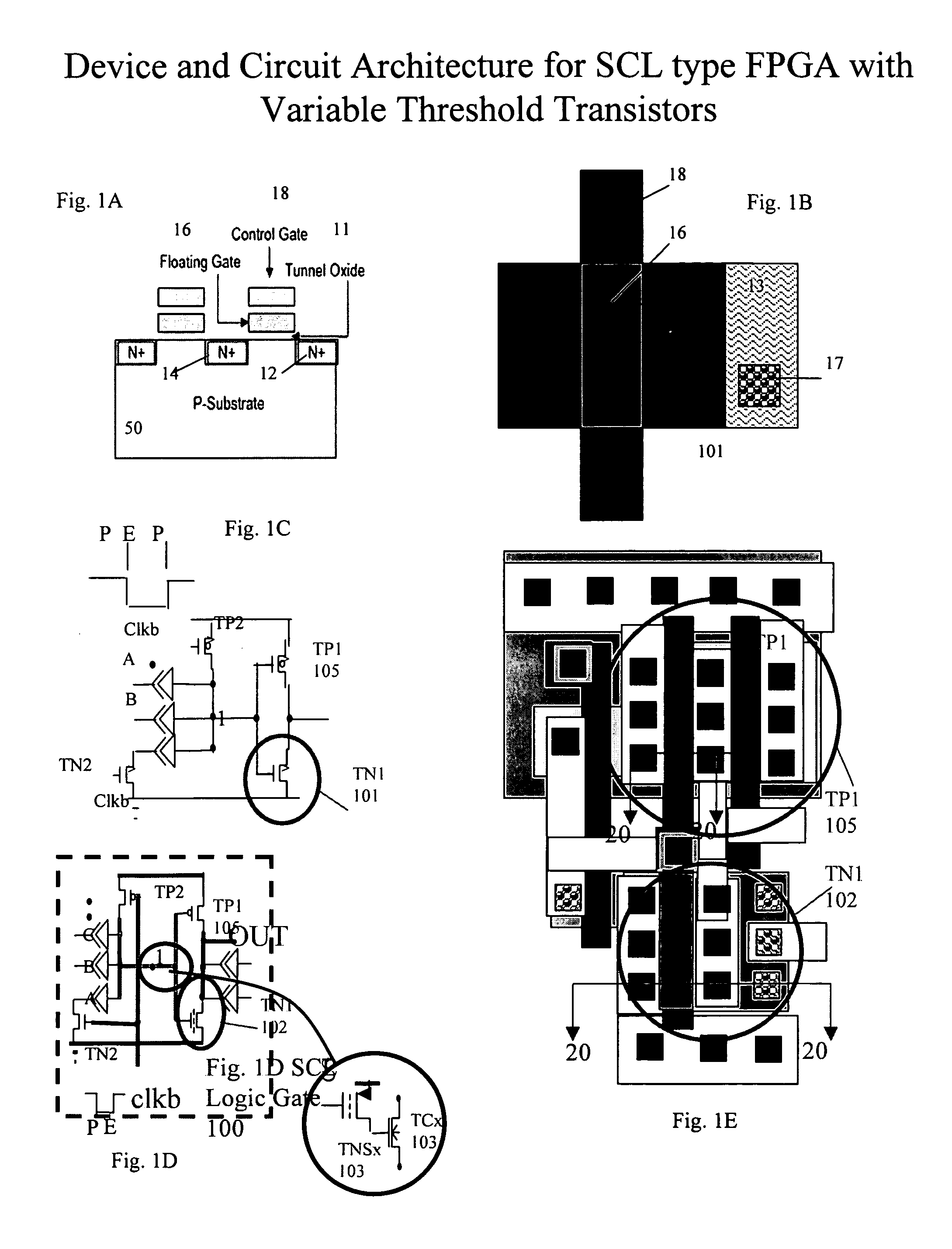

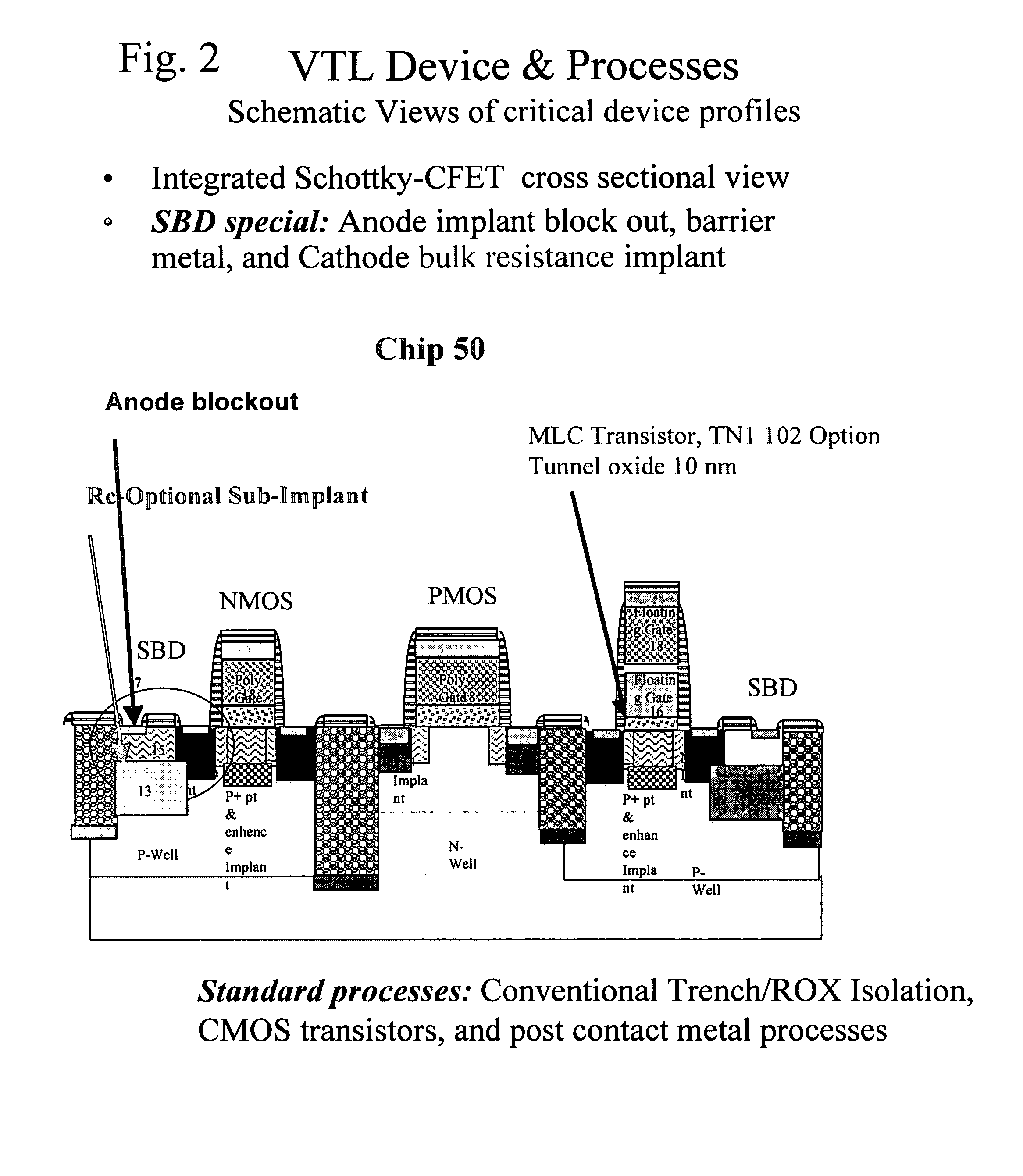

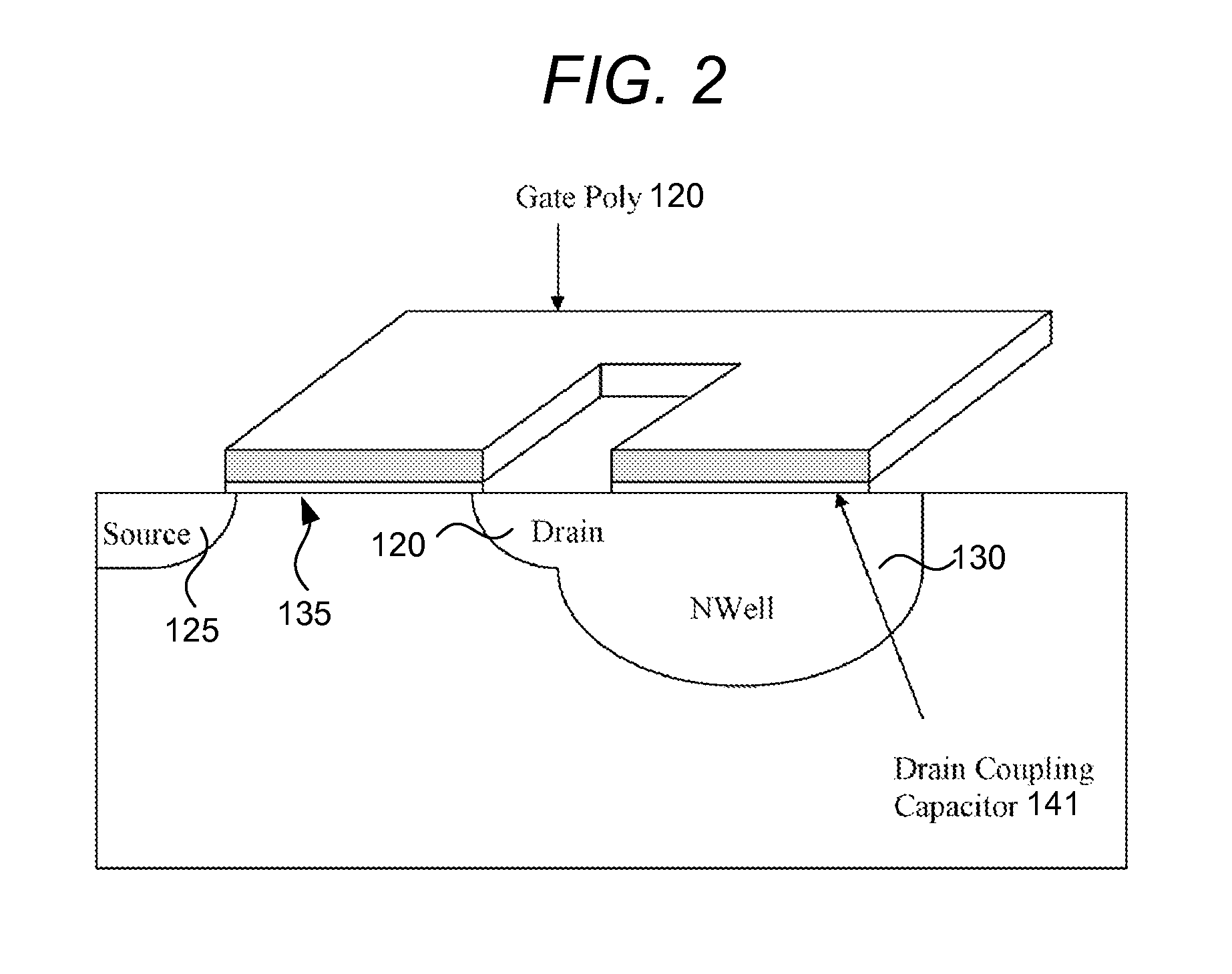

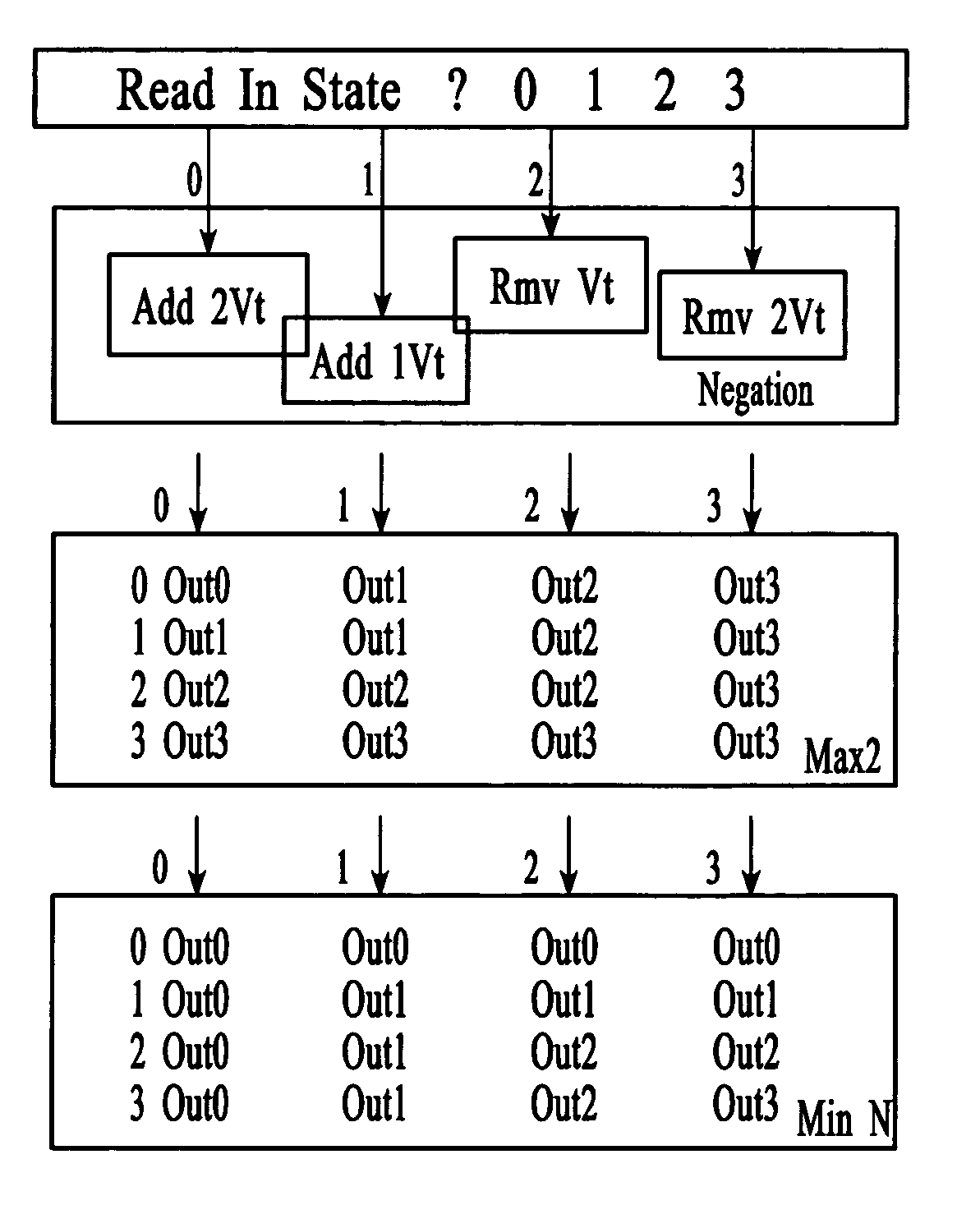

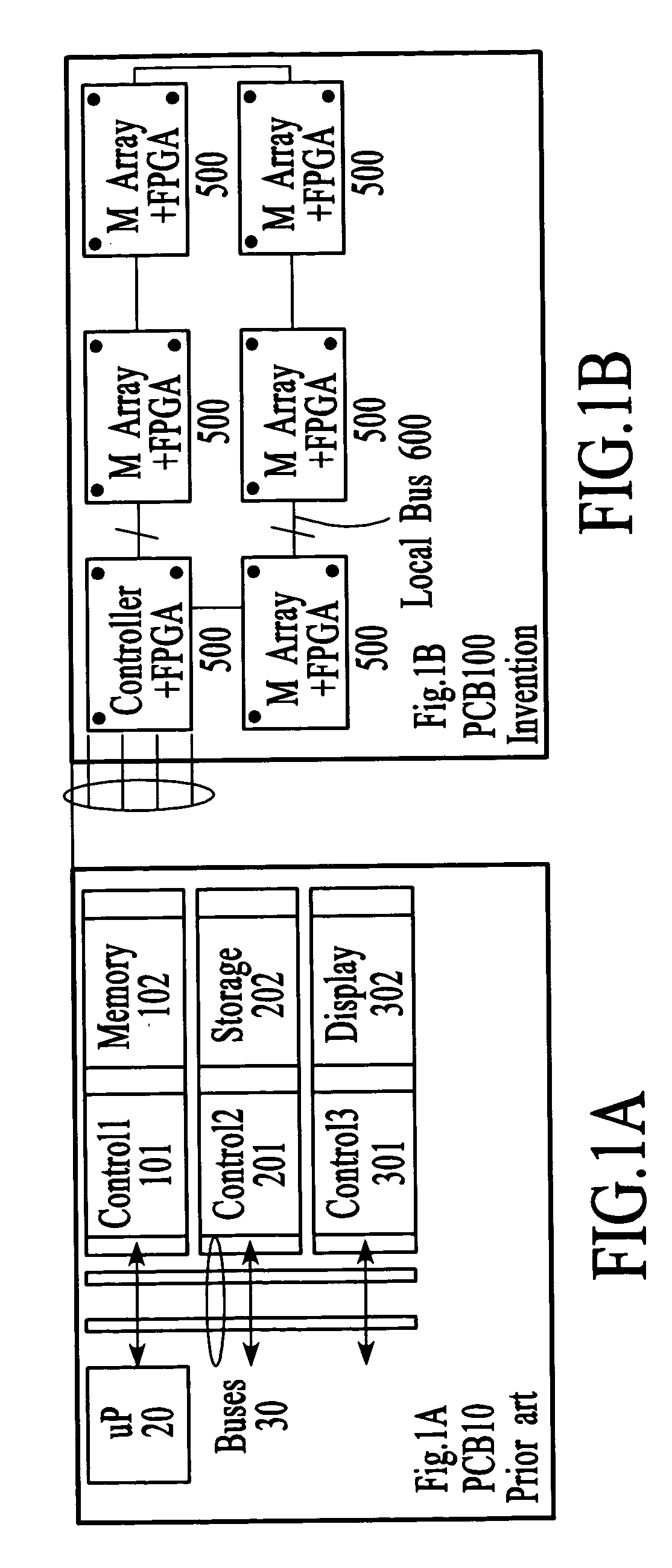

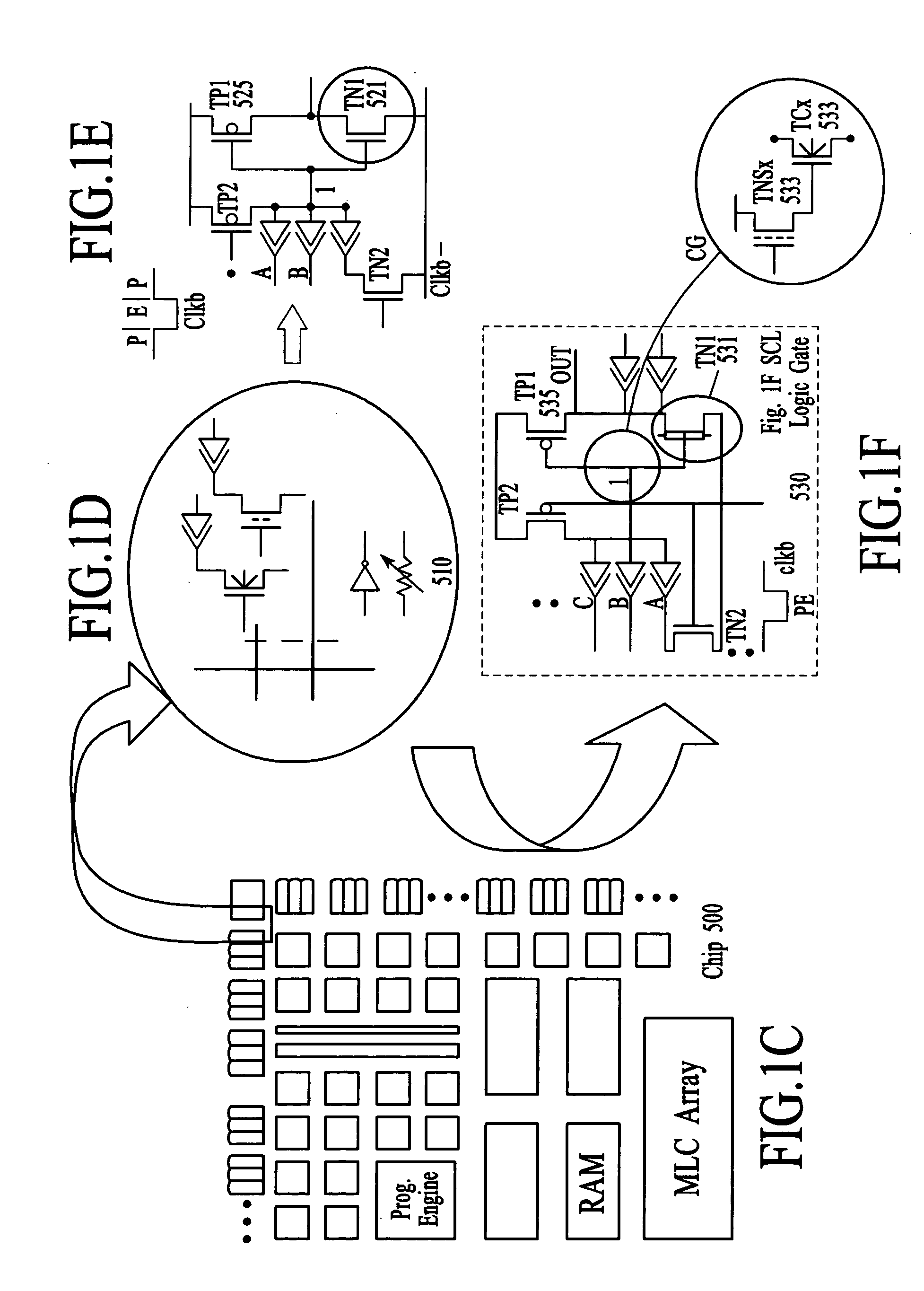

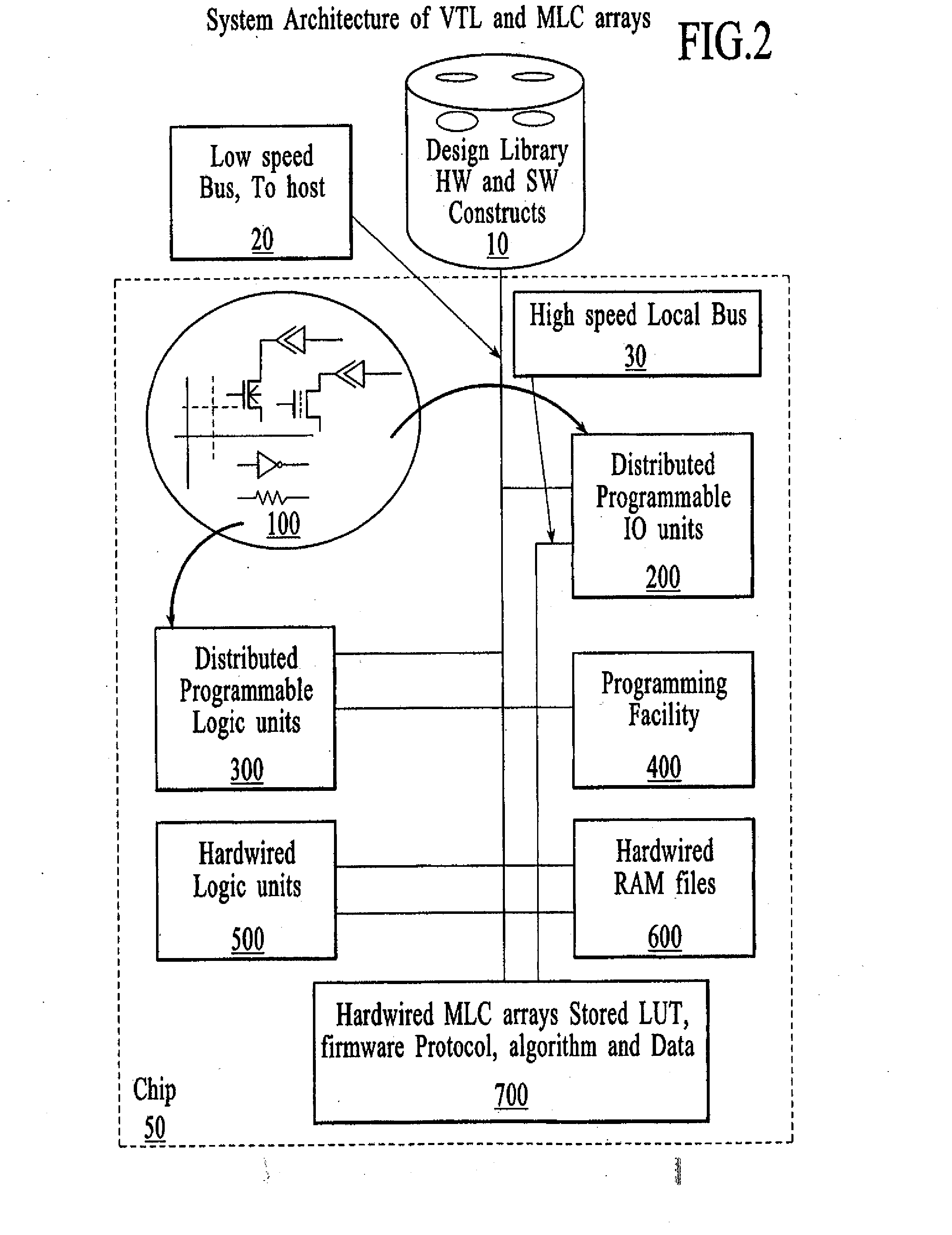

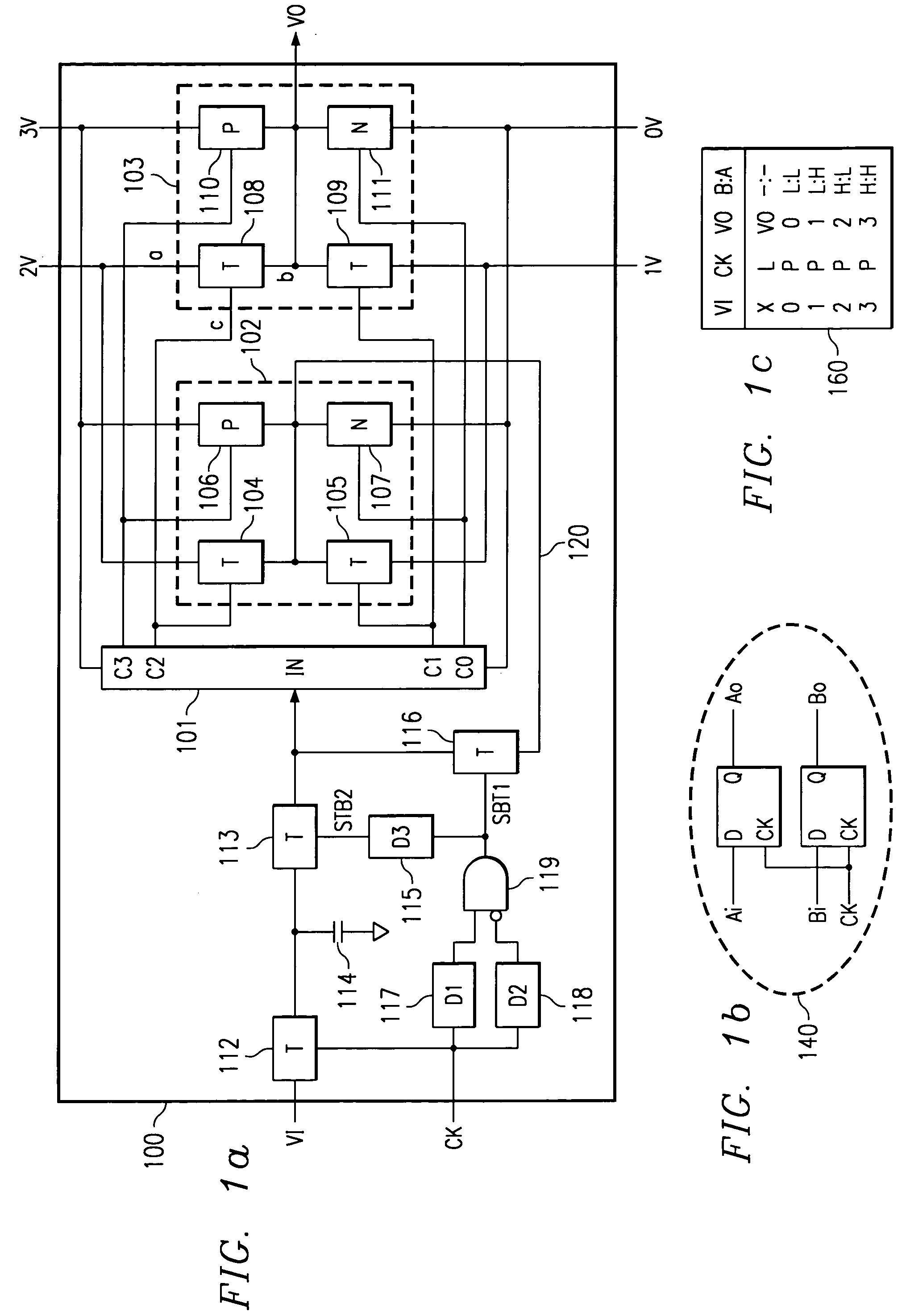

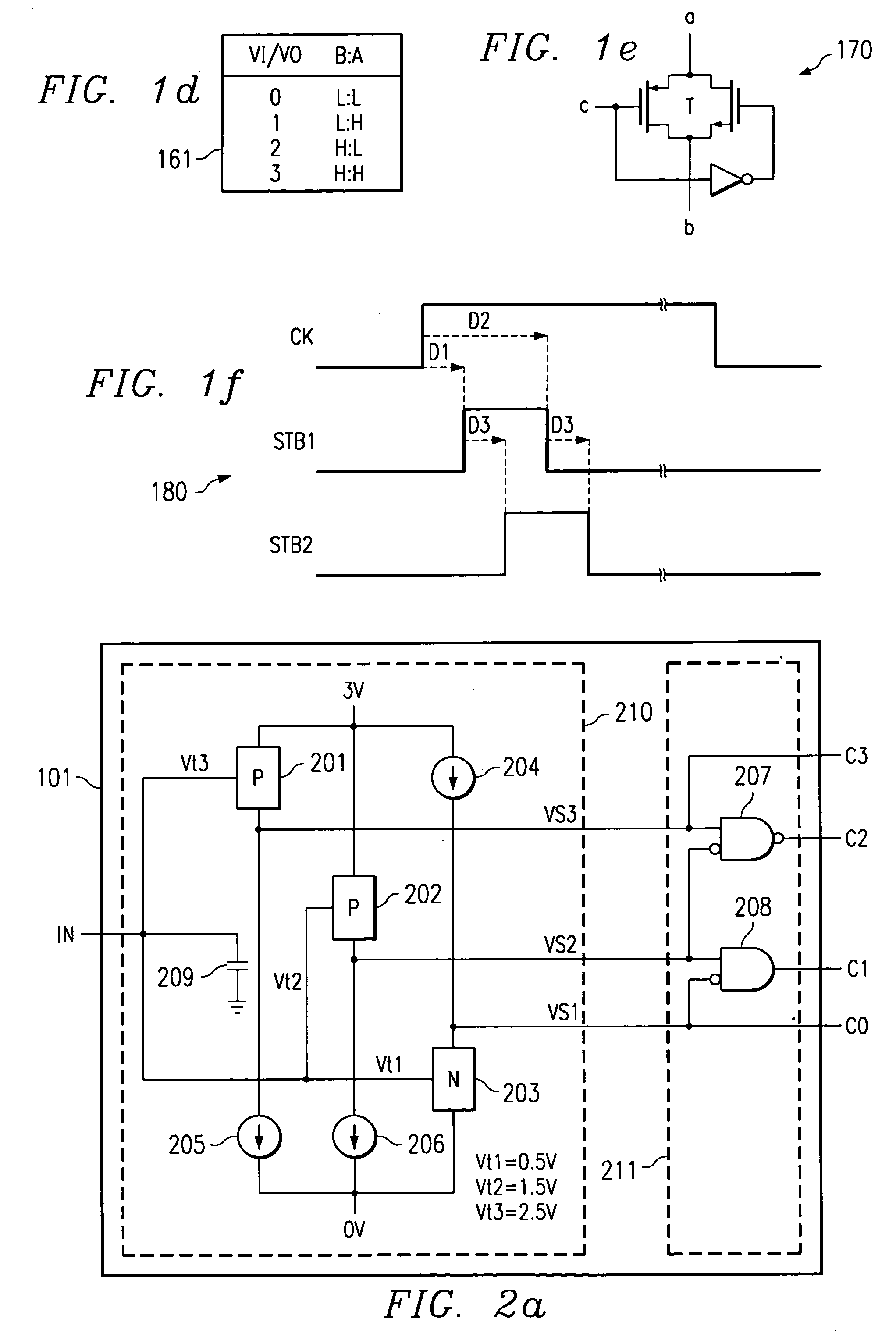

An IC solution utilizing mixed FPGA and MLC arrays is proposed. The process technology is based on the Schottky CMOS devices comprising of CMOS transistors, low barrier Schottky barrier diode (SBD), and multi-level cell (MLC) flash transistors. Circuit architectures are based on the pulsed Schottky CMOS Logic (SCL) gate arrays, wherein a variable threshold NMOS transistor may replace the regular switching transistor. During initialization windows, existing FPGA programming techniques can selectively adjust the VT of the switching transistor, re-configure the intra-connections of the simple SCL gates, complete all global interconnections of various units. Embedded hardware arrays, hardwired blocks, soft macro constructs in one chip, and protocols implementations are parsed. A wide range of circuit applications involving generic IO and logic function generation, ESD and latch up protections, and hot well biasing schemes are presented. The variable threshold transistors thus serve 3 distinctive functions. It acts as an analog device to store directly nonvolatile information in SCL gates. It couples the diode tree logic functions. Finally, it stores and operates large amount of information efficiently. The mixed SCL type FPGA and MLC storages shall emerge as the most compact logic and memory arrays in Si technology. Low power, high performance, and high capacity ICs are designed to mix and replace conventional CMOS-TTL circuits. The idea of multi-value logic composed of binary, ternary, and quaternary hardware and firmware is also introduced.

Owner:SUPER TALENT ELECTRONICS

Nonvolatile Boolean logic operational circuit and operation method thereof

ActiveCN104124960AEasy to operateMany solutionsLogic circuits characterised by logic functionMultistate logicControl engineeringLogical operations

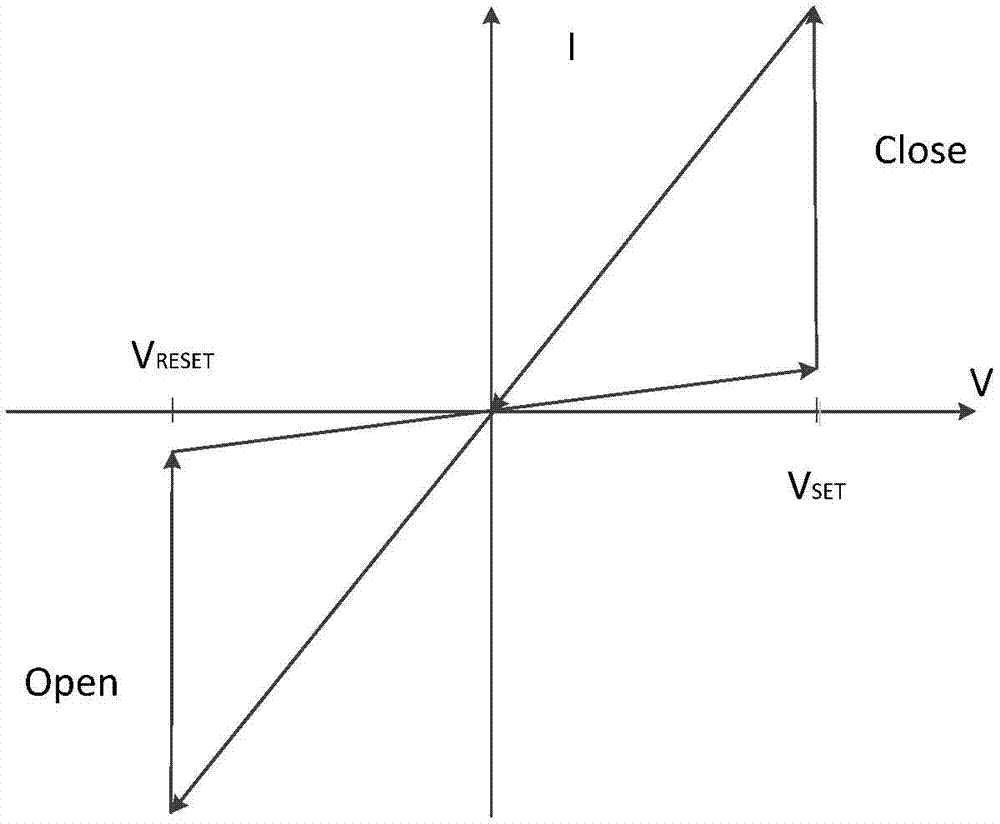

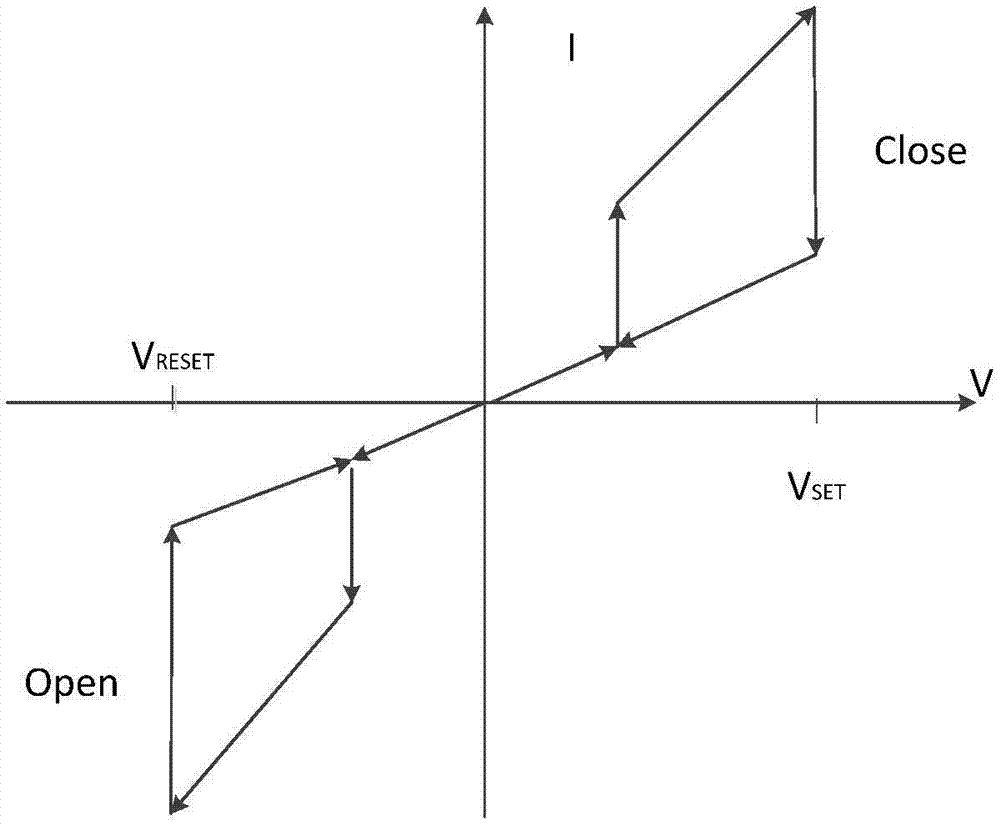

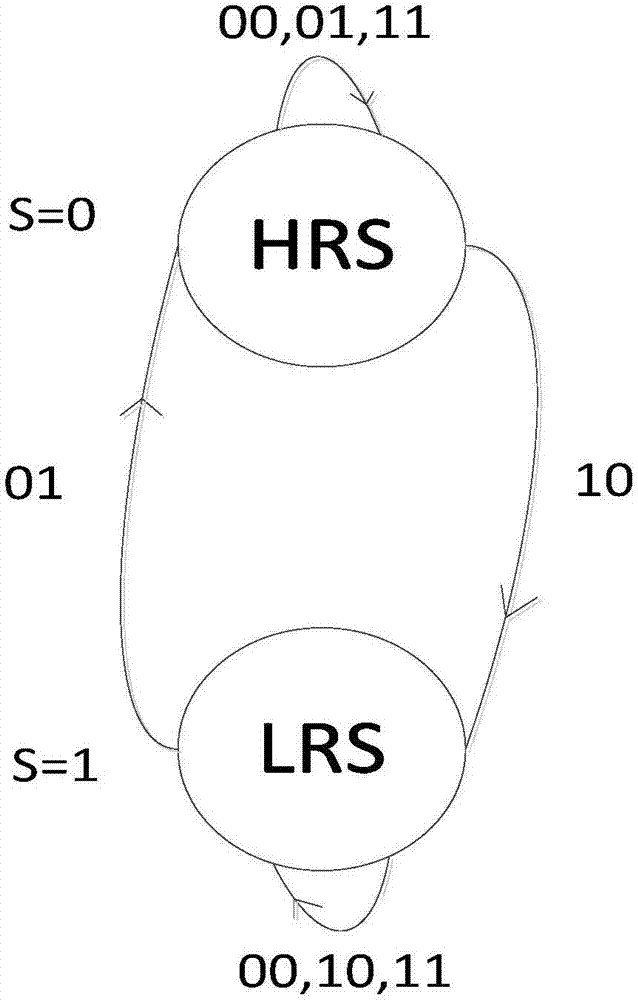

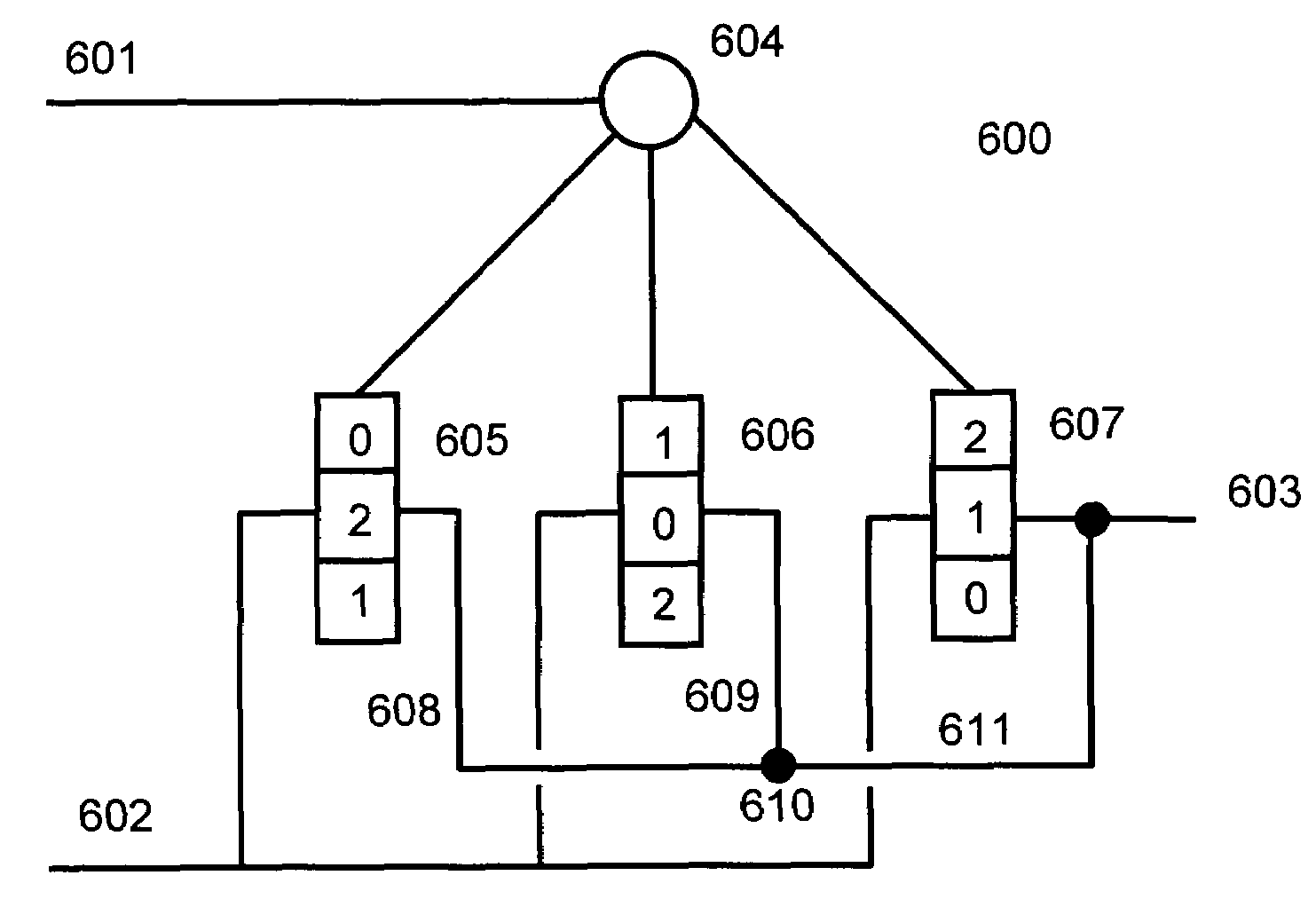

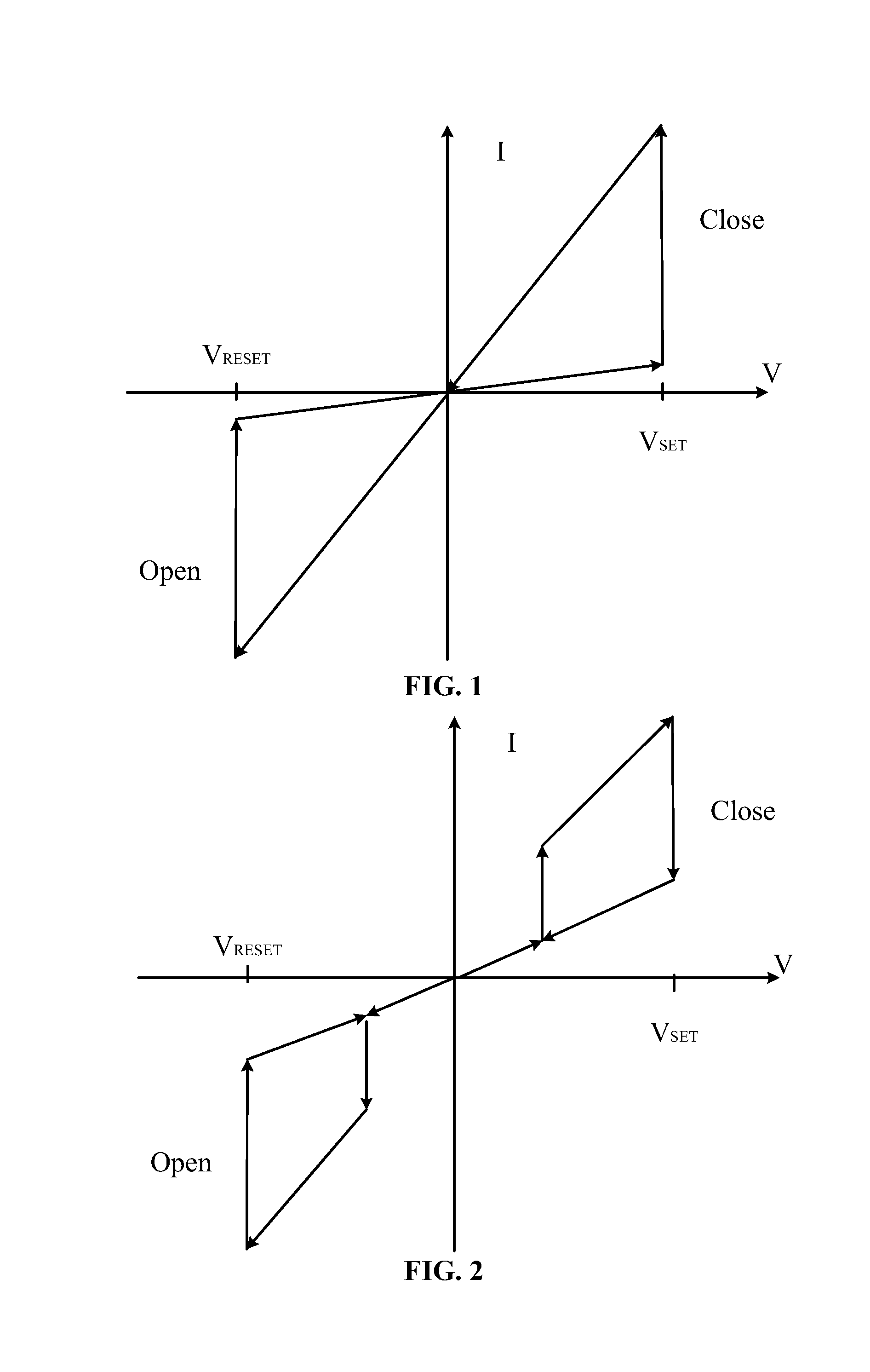

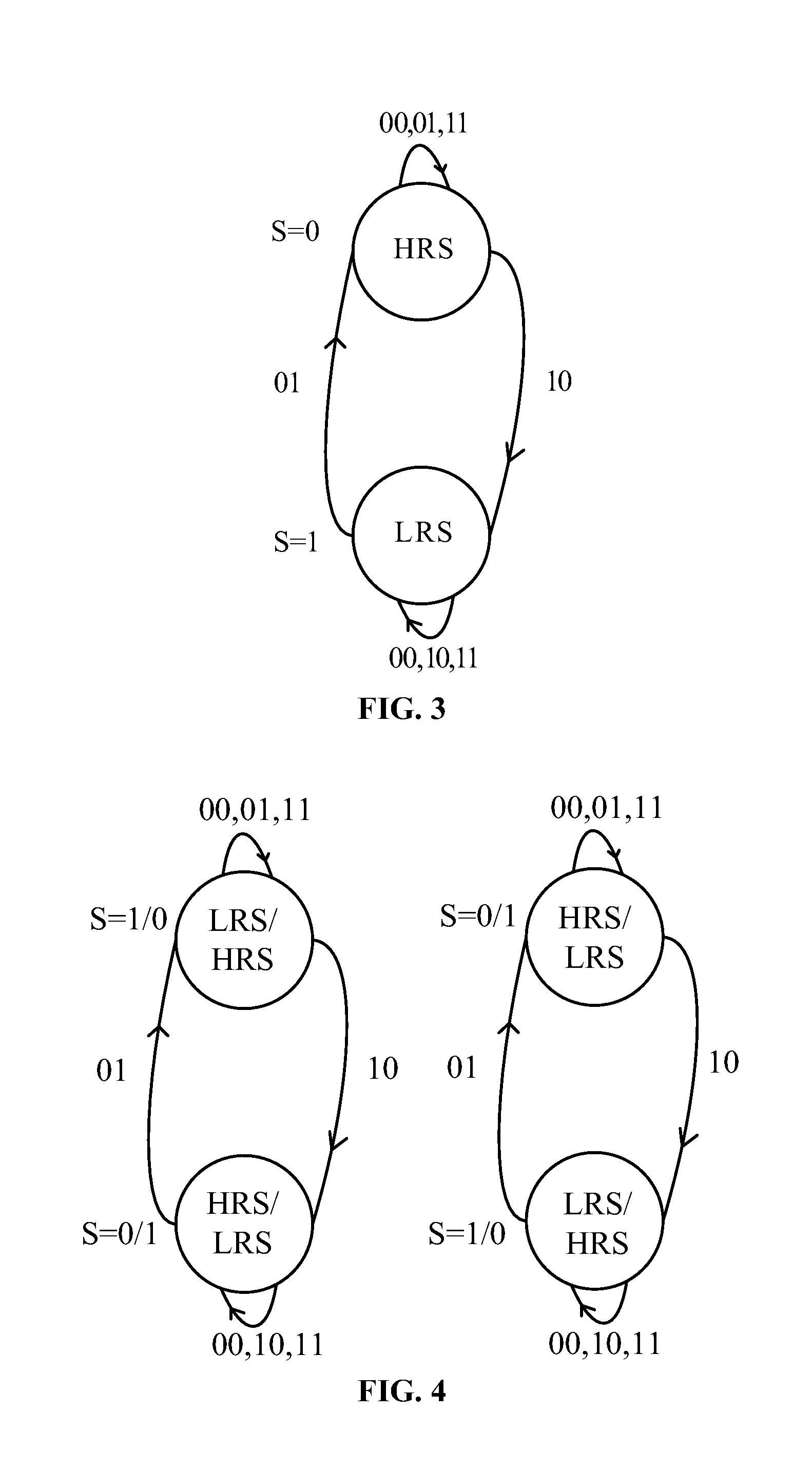

The invention discloses a nonvolatile Boolean logic operational circuit and an operation method thereof. The Boolean logic operational circuit comprises two input ends, one output end, a first variable resistance element M1 and a second variable resistance element M2; the cathode of the first variable resistance element M1 servers as the first input end of the logic operational circuit, the cathode of the second variable resistance element M2 serves as the second input end of the logic operational circuit, and the anode of the second variable resistance element M2 serves as the output end of the logic operational circuit after being connected with the anode of the first variable resistance element M1. Through operating the nonvolatile Boolean logic operational circuit, at least 16 kinds of basic Boolean logic actions can be realized. Through a logic circuit composed of two variable resistance elements, at least 16 kinds of basic Boolean logic operations can be realized according to requirements, and the logic operation results are directly stored in the resistance states of the variable resistance elements so that the calculation and storage integration is realized; the logic circuit needs a few of devices and is easy to operate, and therefore, the calculating power consumption and time can be saved, and the calculating efficiency is improved.

Owner:HUAZHONG UNIV OF SCI & TECH

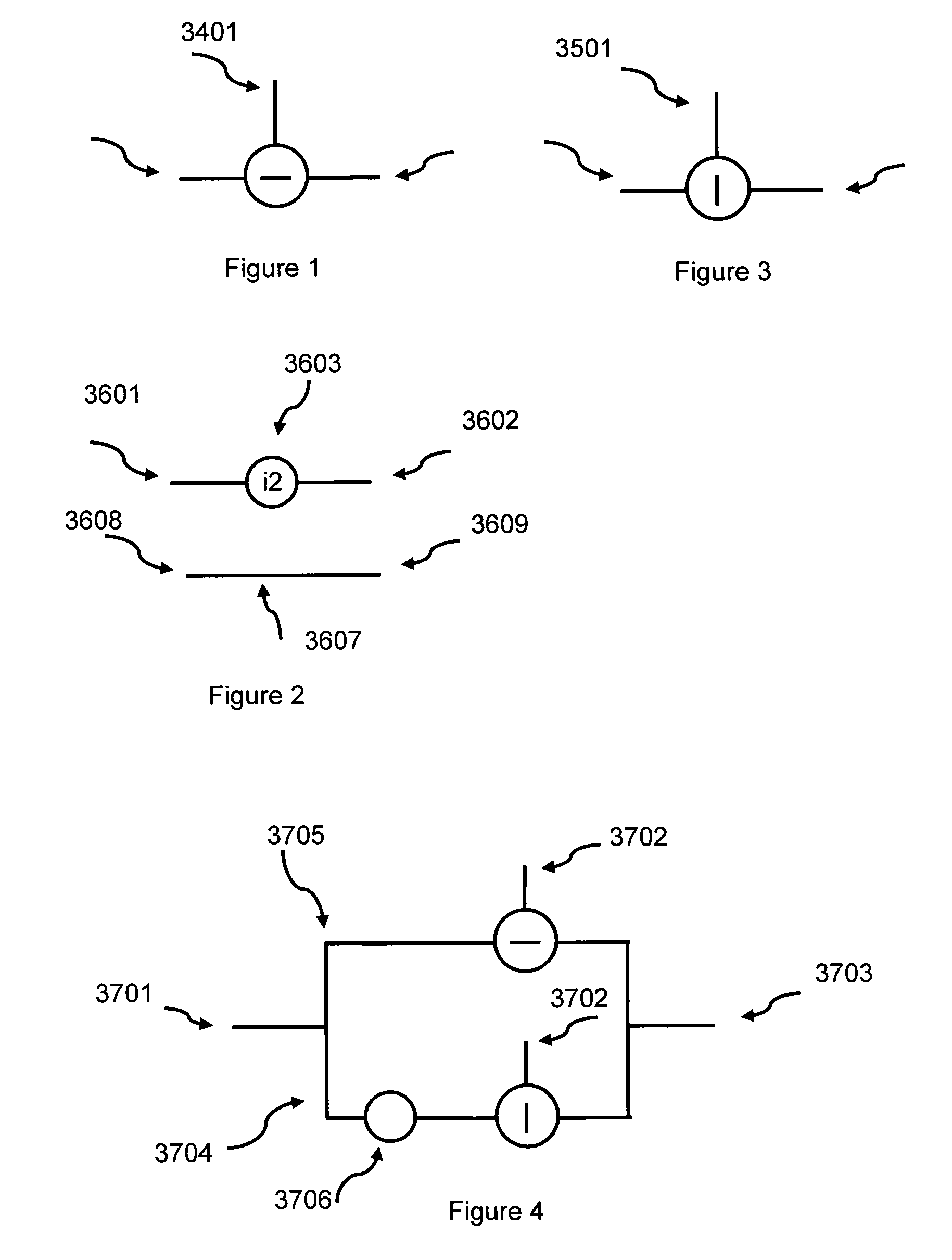

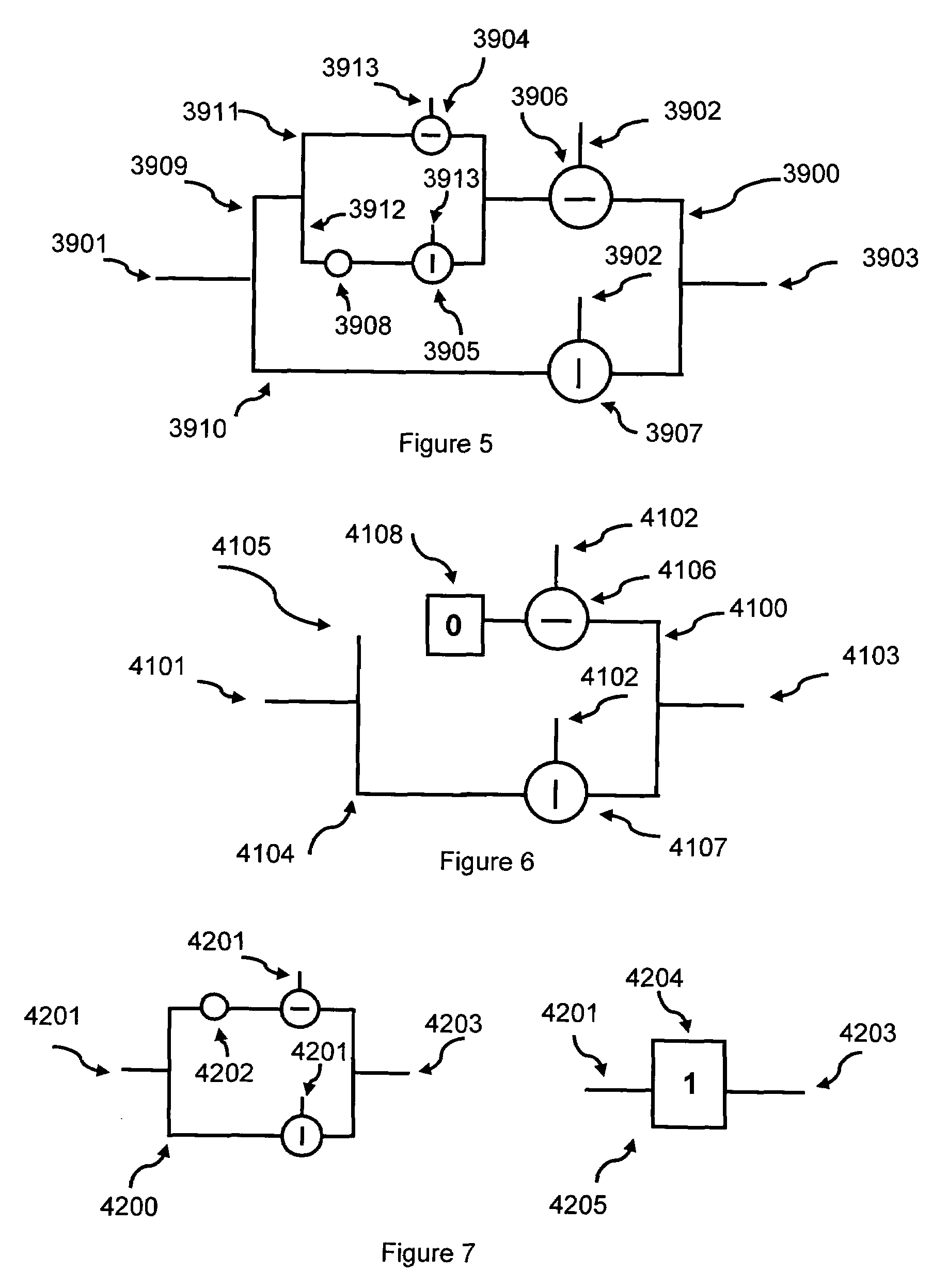

Single and composite binary and multi-valued logic functions from gates and inverters

InactiveUS7218144B2Minimum propagation timePractical to useLogic circuits characterised by logic functionMultistate logicEngineeringMany-valued logic

Owner:TERNARYLOGIC

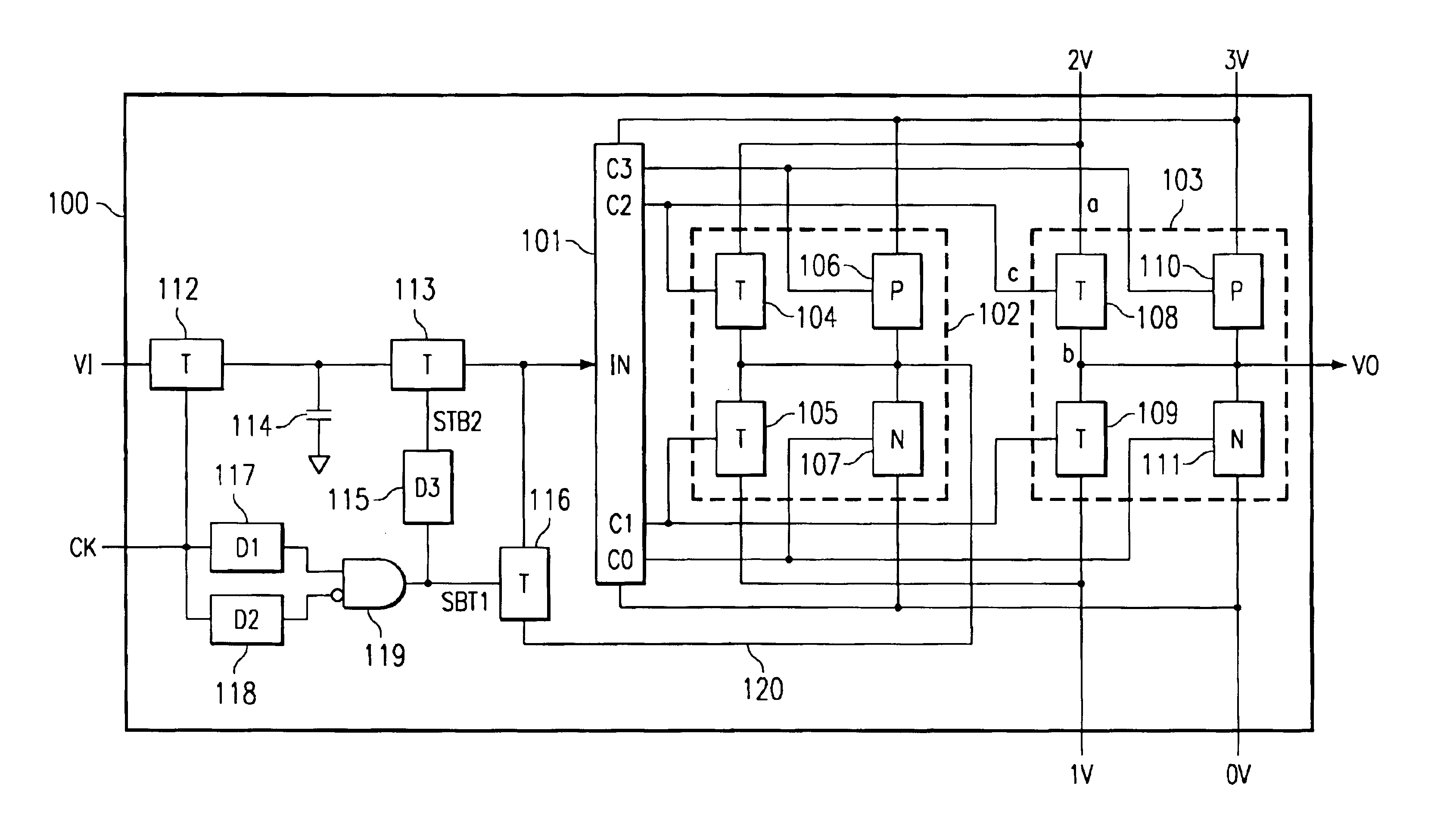

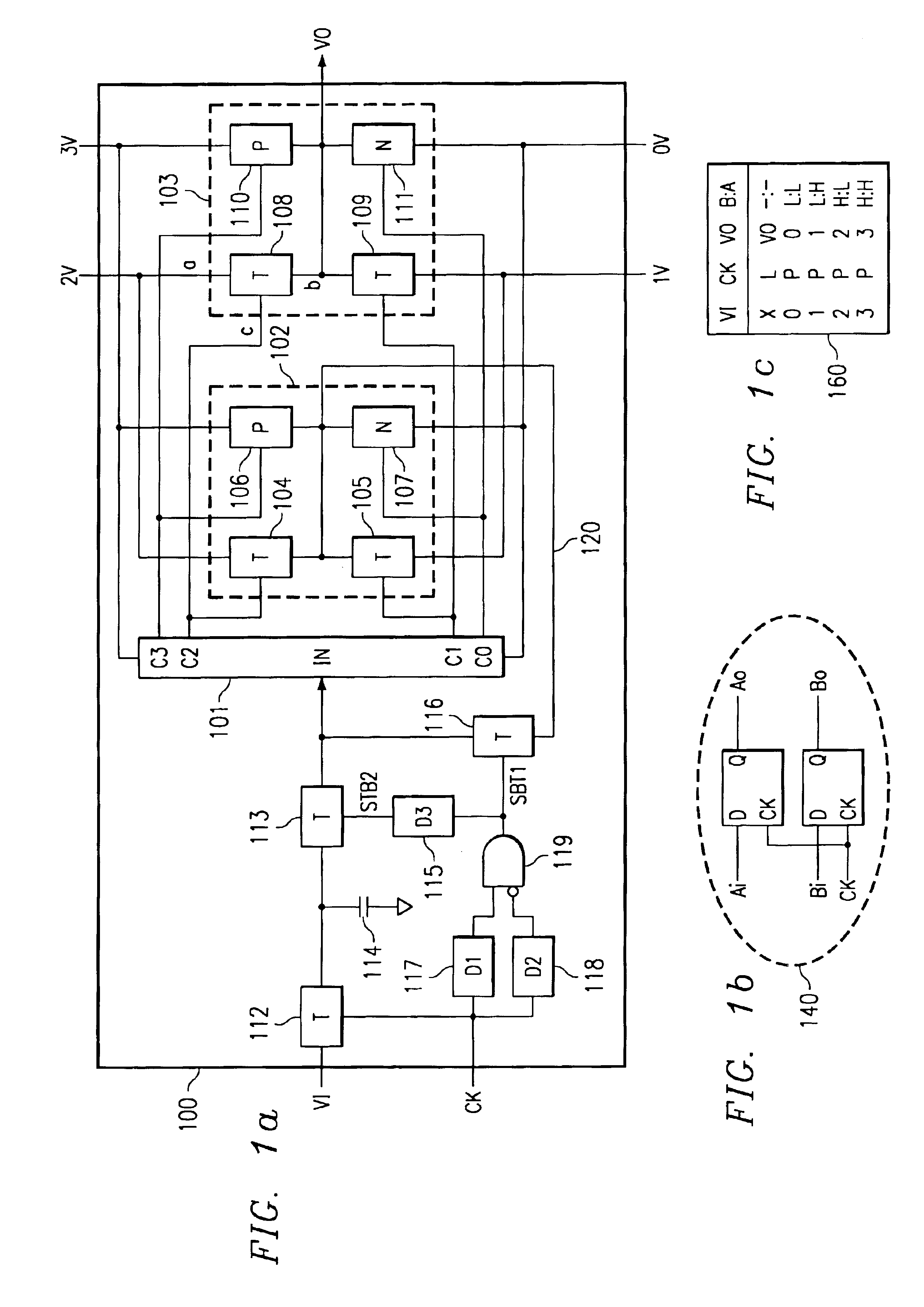

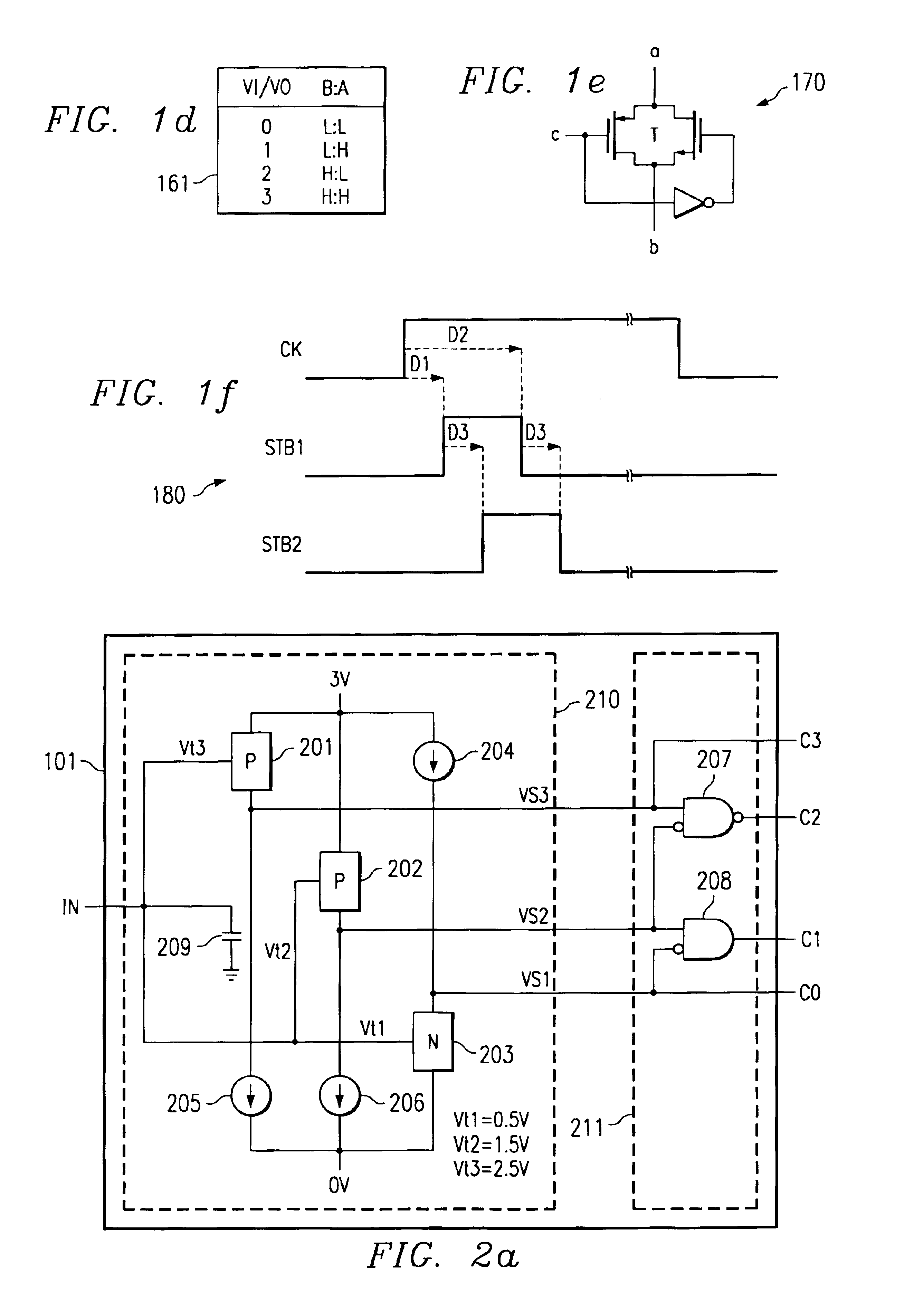

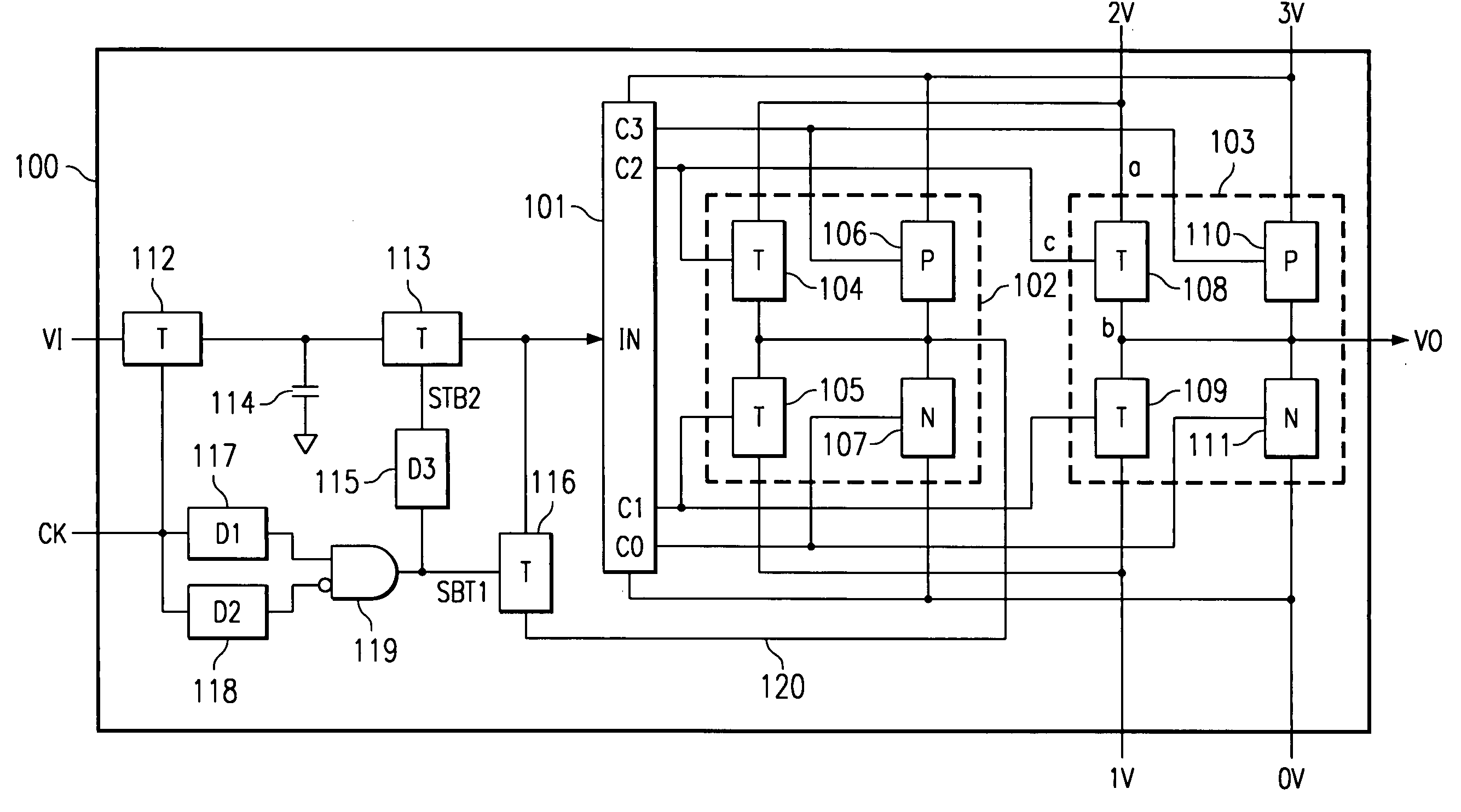

SCL type FPGA with multi-threshold transistors and method for forming same

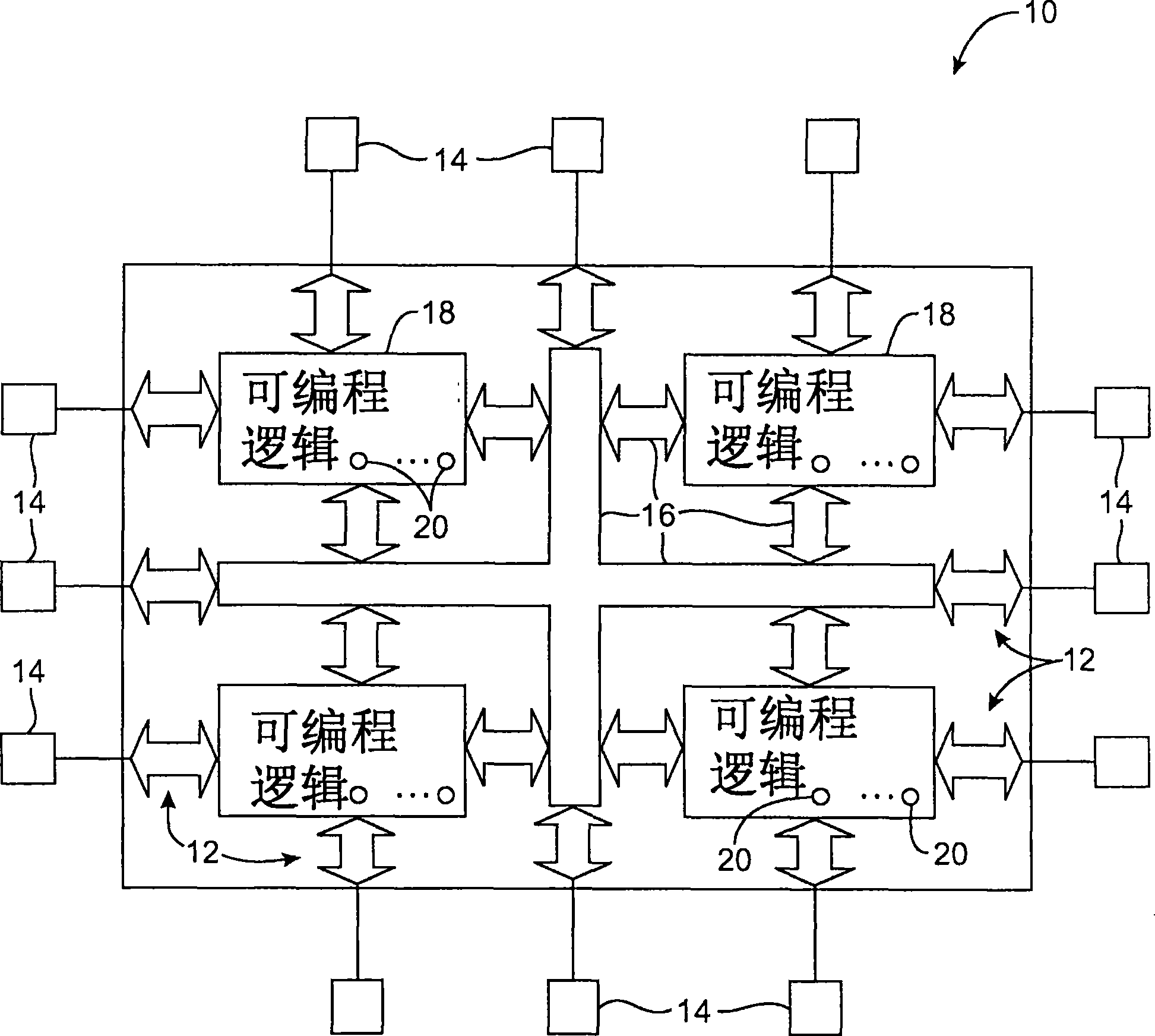

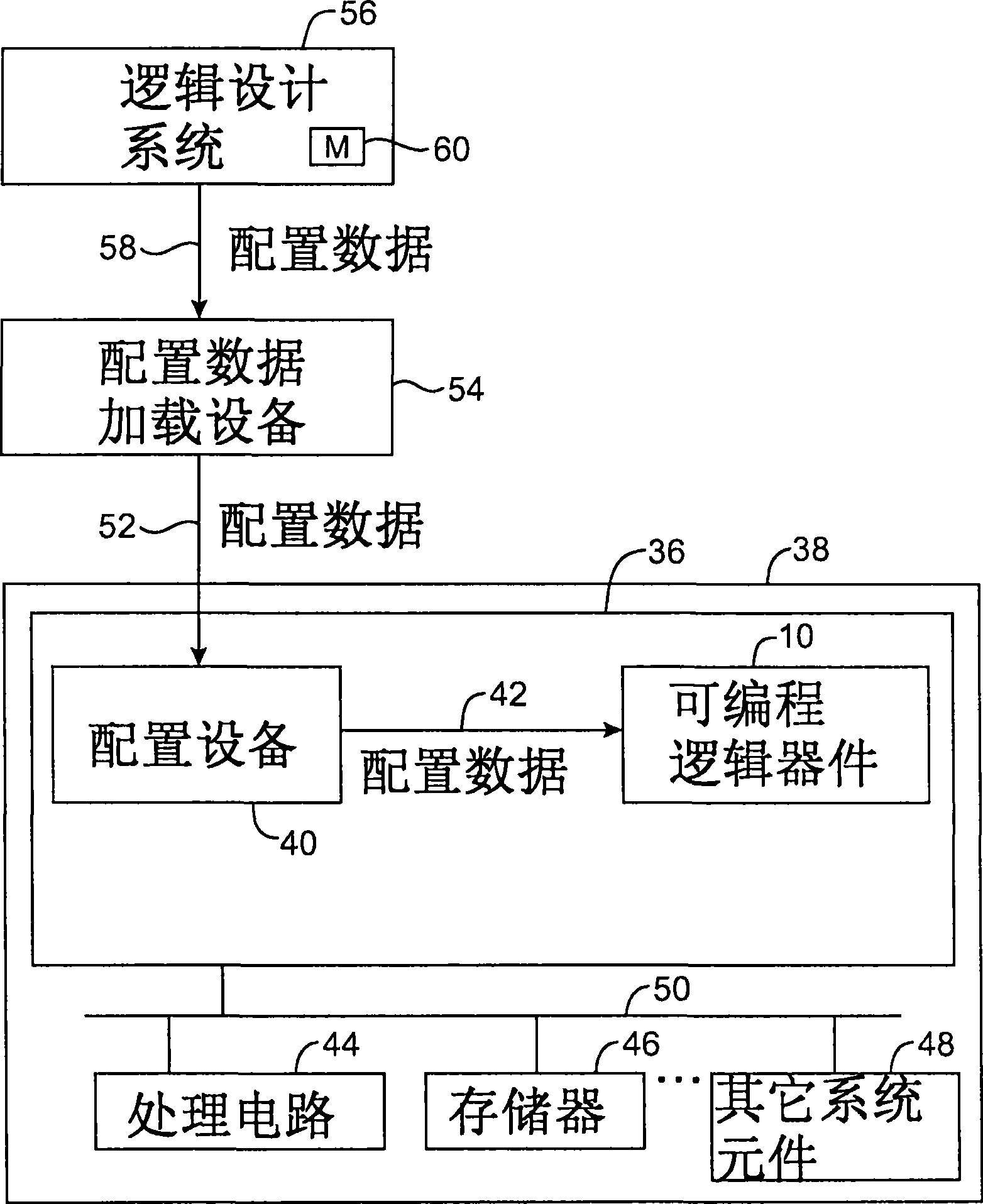

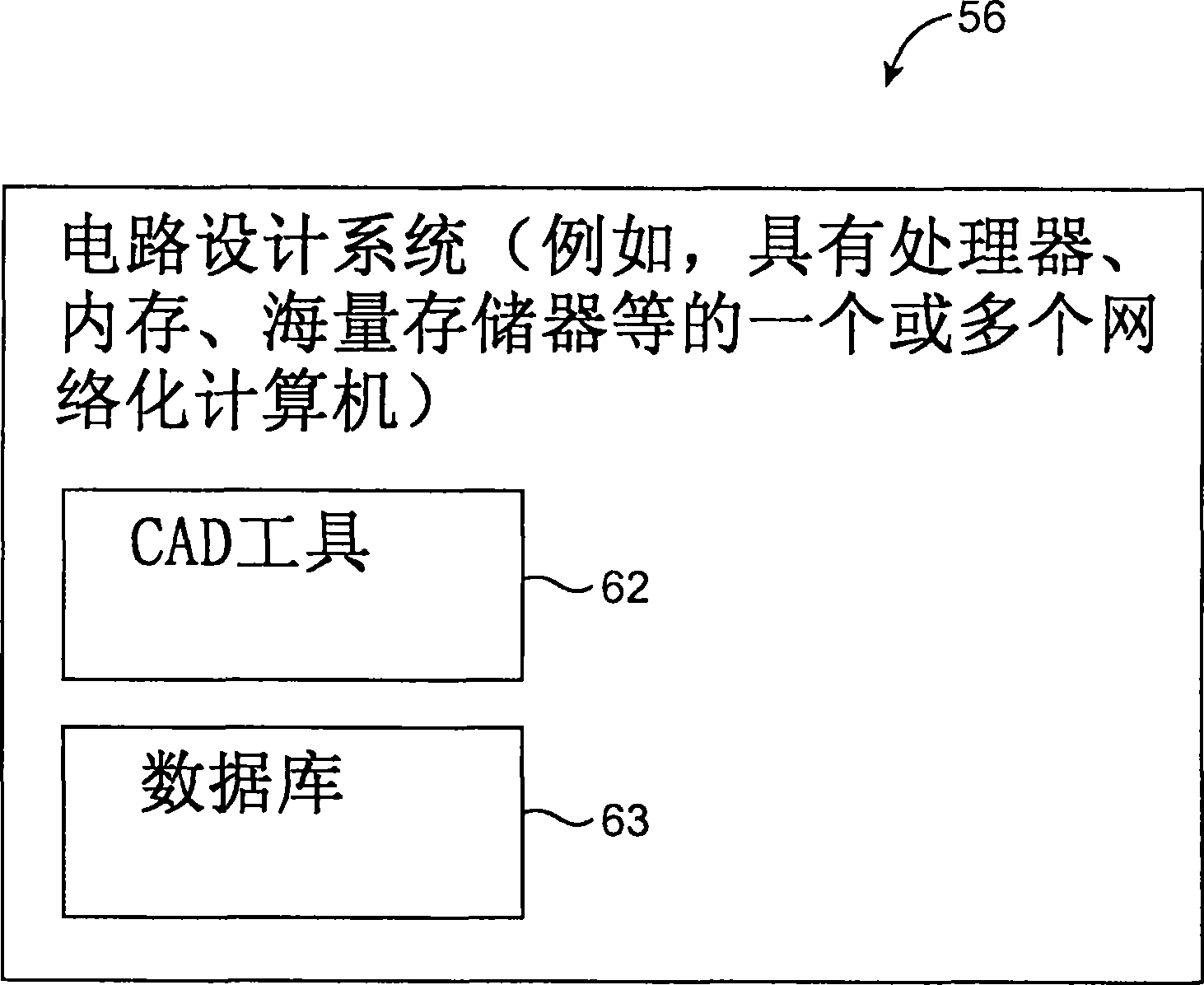

InactiveUS20050231237A1Low powerImprove performanceMultistate logicSolid-state devicesDigital converterDigital device

A new scheme of Schottky FPGA (SFPGA) IC solution is proposed. The chip is organized by embedded analog, memory, and logic units with on chip apparatus and software means to partitioning, altering selected portions of hardware. The process means is based on the combined Schottky CMOS (SCMOS, U.S. Pat. No. 6,590,800) and Flash technology. The circuit means is based on SCMOS-DTL gate arrays. Software means is based on the C++ procedures with levels of LUT. The SFPGA device supports GHz low power ASIC mixed signal product applications with embedded analog, logic, and memory array units. Several multiplexing schemes are disclosed, which accommodate tasks to vary the Vt and transmission line transmission of selected transistor or IO nets, and therefore their analog and digital device properties. A voltage doubler and supply booster and a Digital-Analog-Digital-Translator (DADT) apparatus are also disclosed in accordance with the present invention. Accordingly, the present invention includes control schemes to field program basic circuit element or any critical nets, and to alter the functionality of certain predetermined circuit units, and update array interconnections, accessing stored protocols, algorithms in all chips in the embodiment subsystem of a SFPGA chip sets.

Owner:SUPER TALENT ELECTRONICS

Semiconductor device

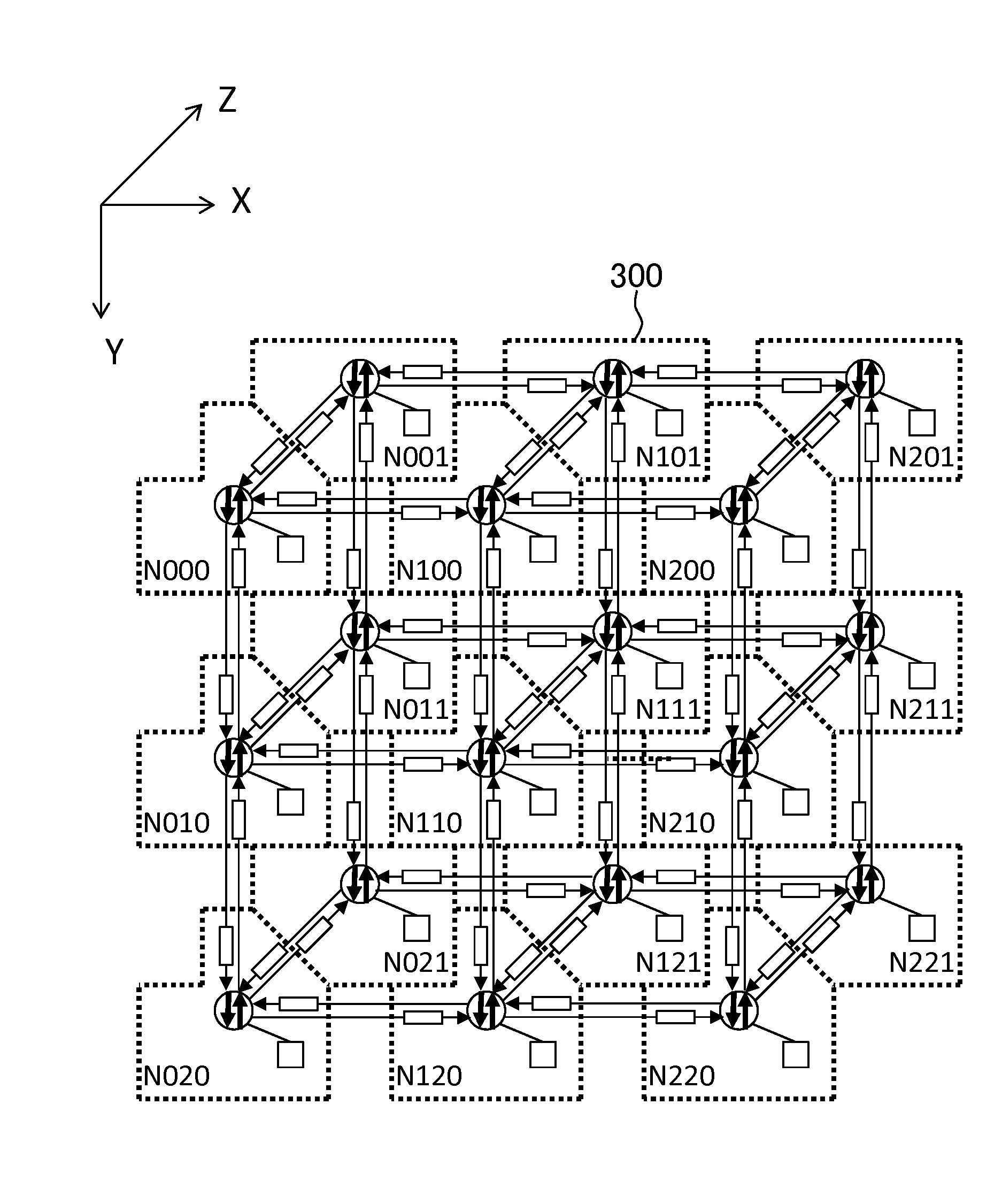

An object of the present invention is to realize an example of configuration that approximately represents a state of quantum spin in a semiconductor device where components as a basic configuration unit are arrayed so as to search a ground state of Ising model. There is disclosed a semiconductor device provided with plural units each of which is equipped with a first memory cell that stores a value which represents one spin of the Ising model by three or more states, a second memory cell that stores an interaction coefficient showing interaction from another spin which exerts interaction on the one spin and a logical circuit that determines the next state of the one spin on the basis of a function having a value which represents a state of the other spin and the interaction coefficient as a constant or a variable.

Owner:HITACHI LTD

Non-volatile boolean logic operation circuit and operation method thereof

ActiveUS20160020766A1Easy to operateSave power consumptionLogic circuits characterised by logic functionMultistate logicResistive switchingEngineering

A non-volatile Boolean logic operation circuit, including: two input ends; an output end; a first resistive switching element M1, the first resistive switching element M including a positive electrode and a negative electrode; and a second resistive switching element M2, the second resistive switching element M2 including a positive electrode and a negative electrode. The negative electrode of the first resistive switching element M1 operates as a first input end of the logic operation circuit. The negative electrode of the second resistive switching element M2 operates as a second input end of the logic operation circuit. The positive electrode of the second resistive switching element M2 is connected to the positive electrode of the first resistive switching element M1, and a connected end thereof operates as the output end of the logic operation circuit.

Owner:HUAZHONG UNIV OF SCI & TECH

SCL type FPGA with multi-threshold transistors and method for forming same

A new scheme of Schottky FPGA (SFPGA) IC solution is proposed. The chip is organized by embedded analog, memory, and logic units with on chip apparatus and software means to partitioning, altering selected portions of hardware. The process means is based on the combined Schottky CMOS (SCMOS, U.S. Pat. No. 6,590,800) and Flash technology. The circuit means is based on SCMOS-DTL gate arrays. Software means is based on the C++ procedures with levels of LUT. The SFPGA device supports GHz low power ASIC mixed signal product applications with embedded analog, logic, and memory array units. Several multiplexing schemes are disclosed, which accommodate tasks to vary the Vt and transmission line transmission of selected transistor or IO nets, and therefore their analog and digital device properties. A voltage doubler and supply booster and a Digital-Analog-Digital-Translator (DADT) apparatus are also disclosed in accordance with the present invention.Accordingly, the present invention includes control schemes to field program basic circuit element or any critical nets, and to alter the functionality of certain predetermined circuit units, and update array interconnections, accessing stored protocols, algorithms in all chips in the embodiment subsystem of a SFPGA chip sets.

Owner:SUPER TALENT ELECTRONICS

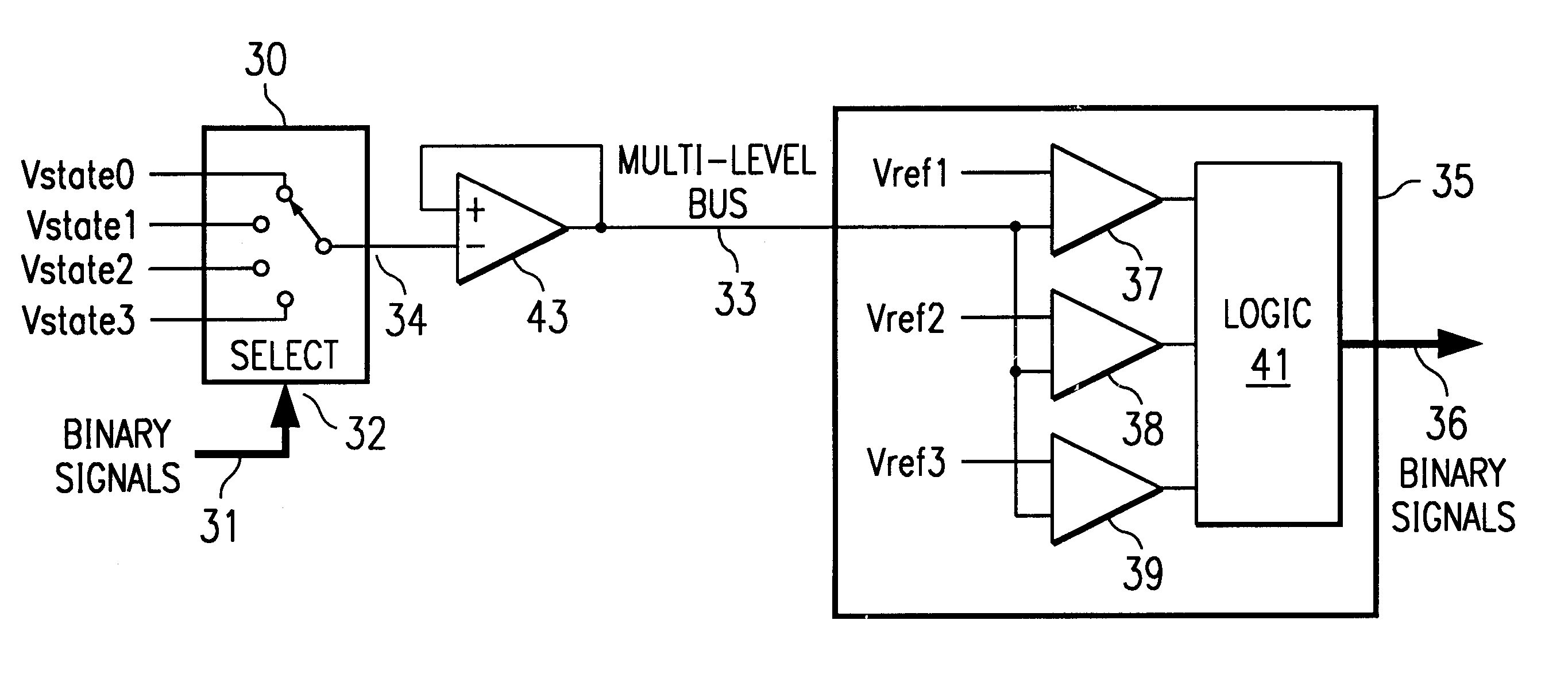

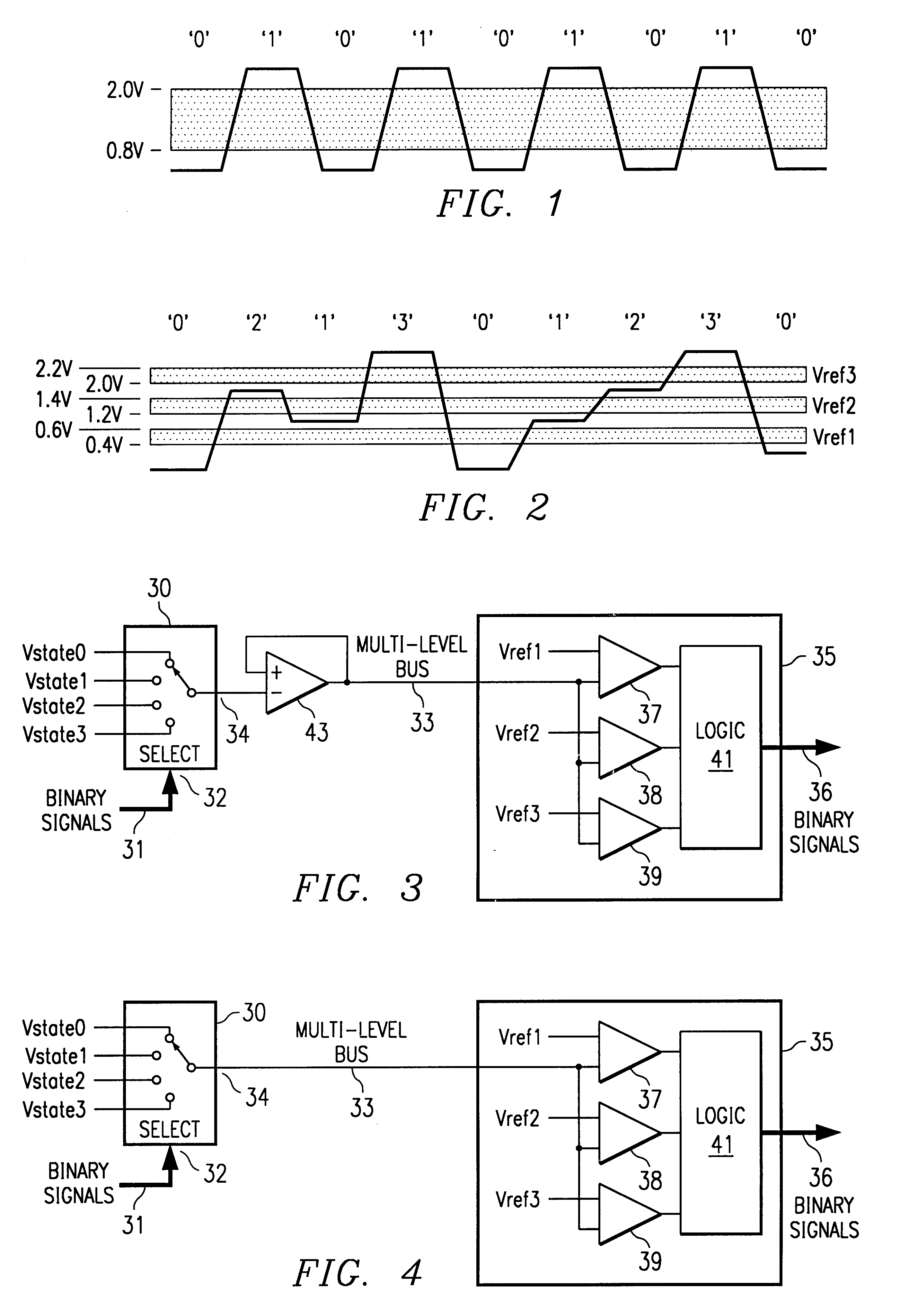

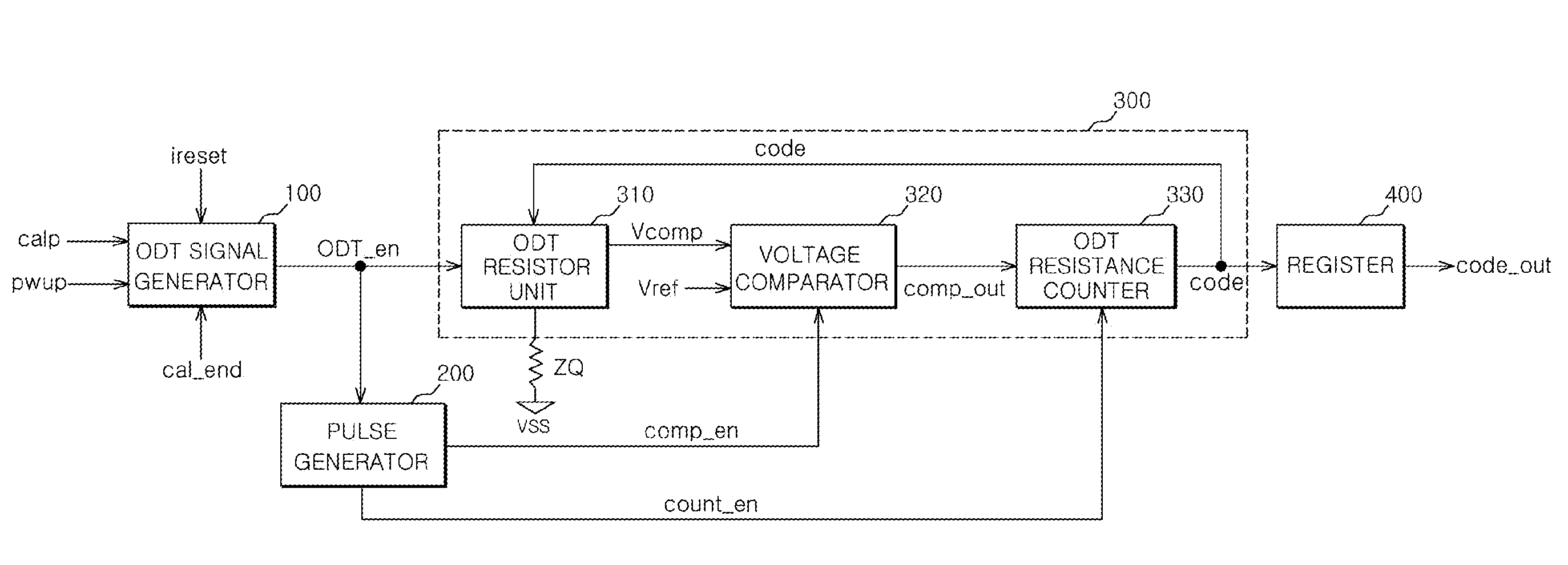

Structure and method for reduction of power consumption in integrated circuit logic

A reduced power dissipation integrated circuit. Power dissipation within a CMOS circuit is reduced by substitution of multi-level buses with several thresholds for binary state buses with a single threshold. A significant portion of an IC's power dissipation is consumed by the act of charging and discharging data and address busses within the IC because theses busses possess the highest capacitances of any of the nodes within the part. The present invention uses a series of thresholds from a minimum voltage to a maximum voltage. Below the minimum threshold voltage Vref1, the logic state would be "0". Above the maximum threshold voltage Vrefn, the logic state would be "n". A series of defined thresholds, Vref1, Vref2, . . . Vrefn, between the minimum and maximum voltages define a series of logic states 0, 1, 2 . . . n+1 between 0 and n+1.

Owner:TELOGY NETWORKS

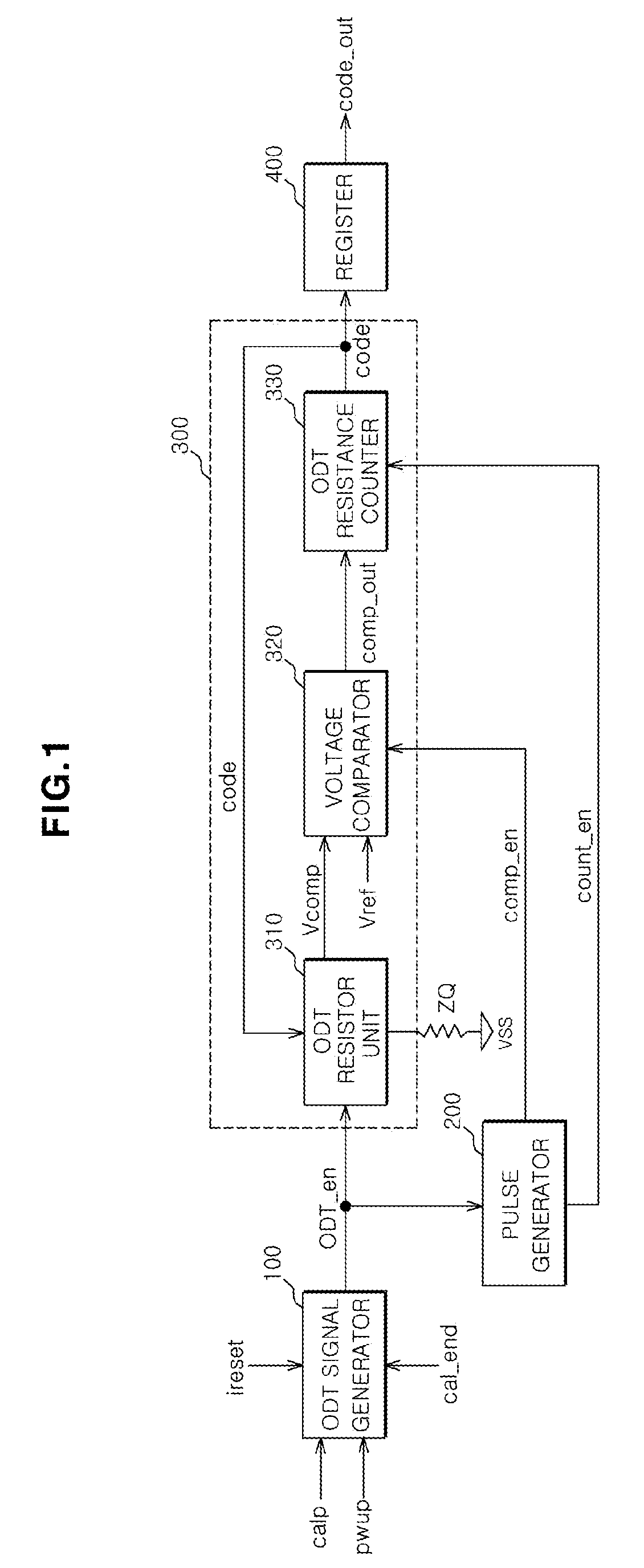

Semiconductor integrated circuit and method of controlling the same

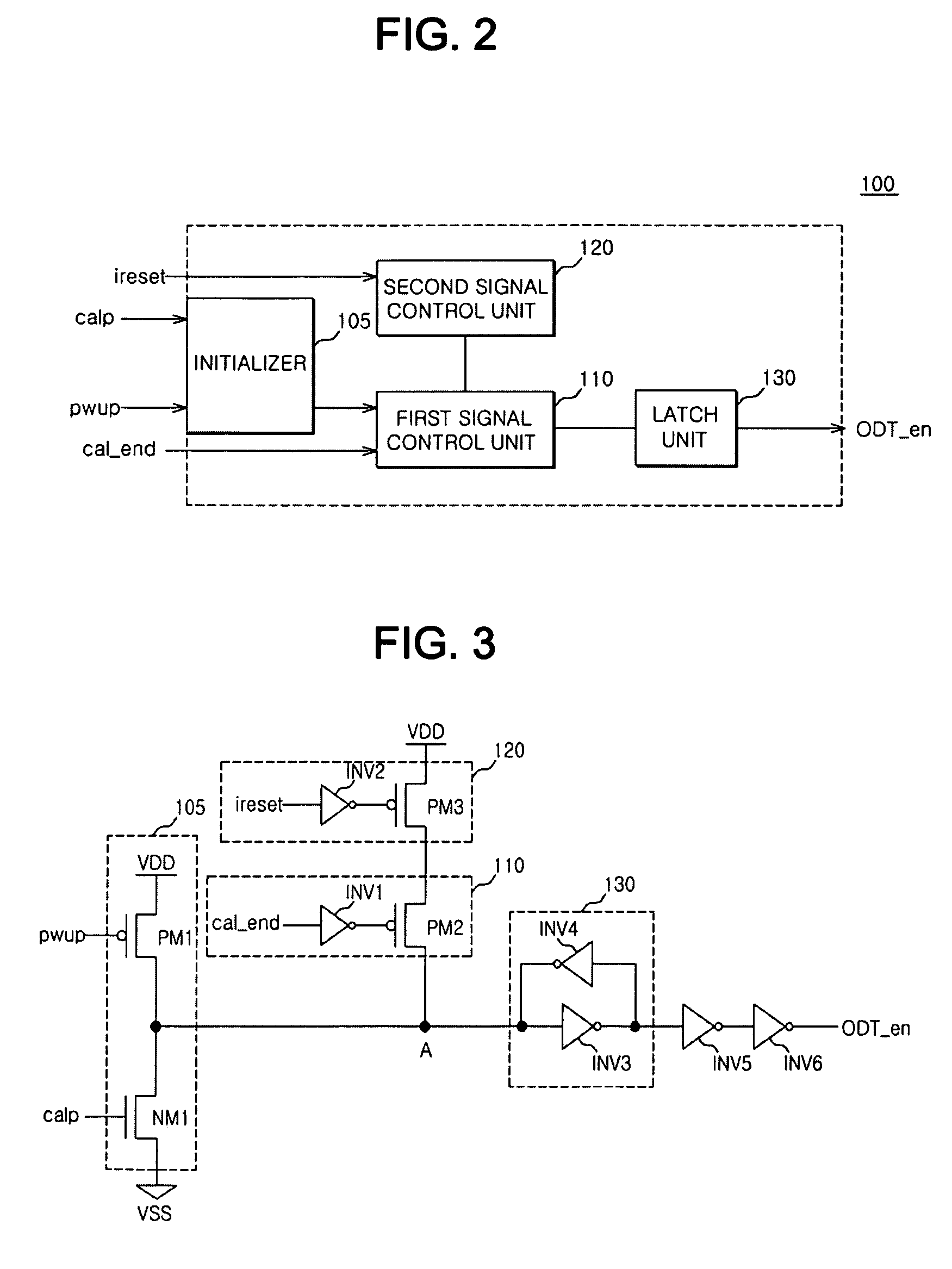

ActiveUS20080252332A1Reduce calibration timeReliability increasing modificationsMultistate logicControl signalEngineering

A semiconductor integrated circuit includes an ODT signal generator that receives an ODT command signal, an ODT reset signal, and an ODT calibration end signal to generate an ODT control signal according to the phase of the ODT calibration end signal, and an ODT resistance adjusting unit that is to perform an on-die termination operation in response to the ODT control signal.

Owner:SK HYNIX INC

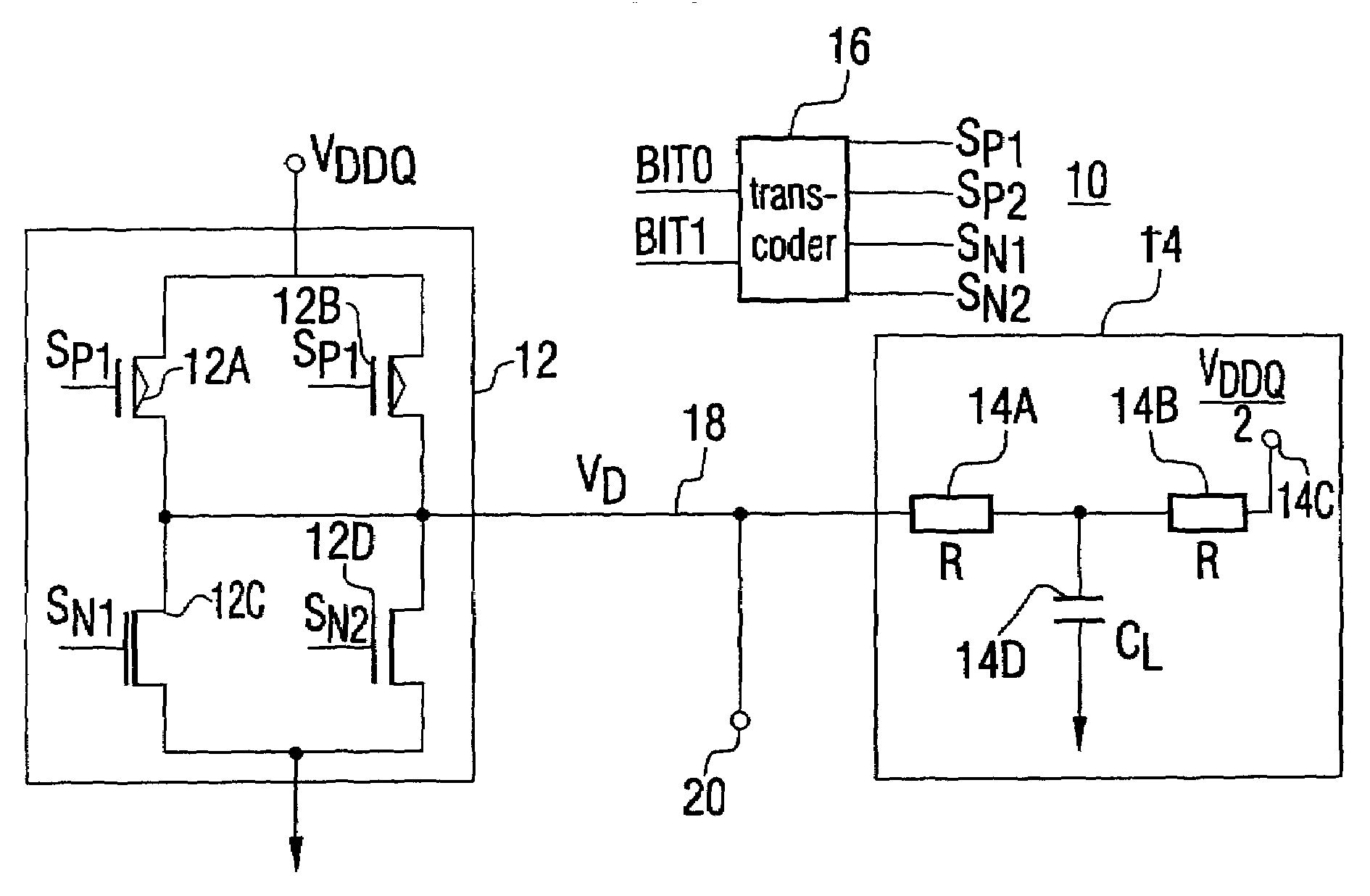

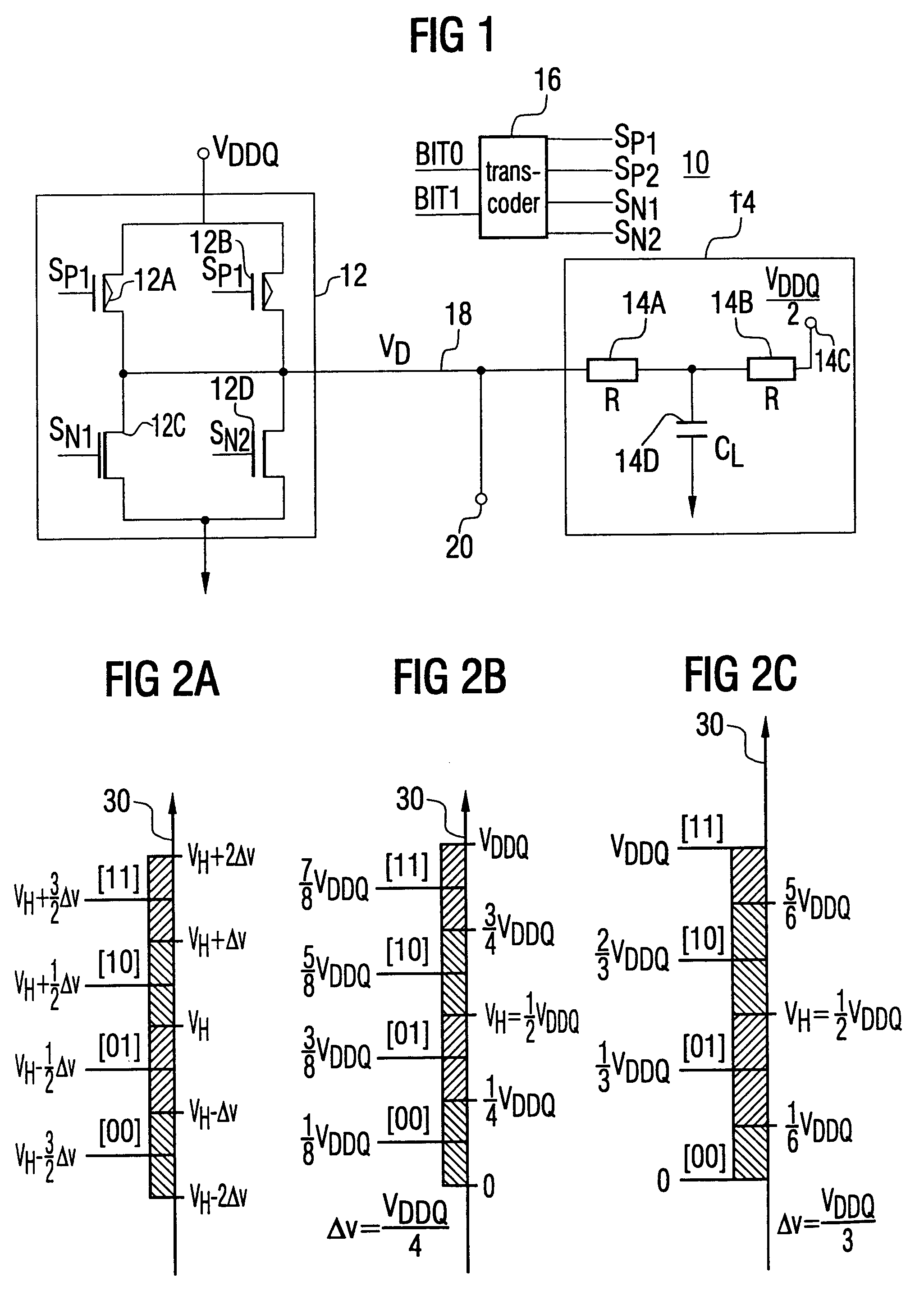

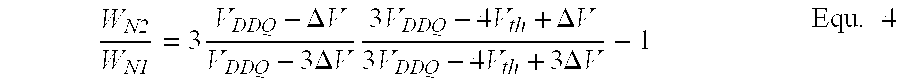

Multi-level driver stage

InactiveUS7053655B2Avoid excessive errorMultistate logicLogic circuits using specific componentsField-effect transistorChannel width

An inventive driver stage for driving an output on one of n-levels, which are each spaced from each other by a voltage difference of ΔV, includes a plurality of field effect transistors for driving the output by supplying or removing a current to or from the output, with the relationship of the channel widths of at least two field effect transistors, which both function either to lead a current to or away, being set in dependence on the value of the voltage difference.

Owner:POLARIS INNOVATIONS LTD

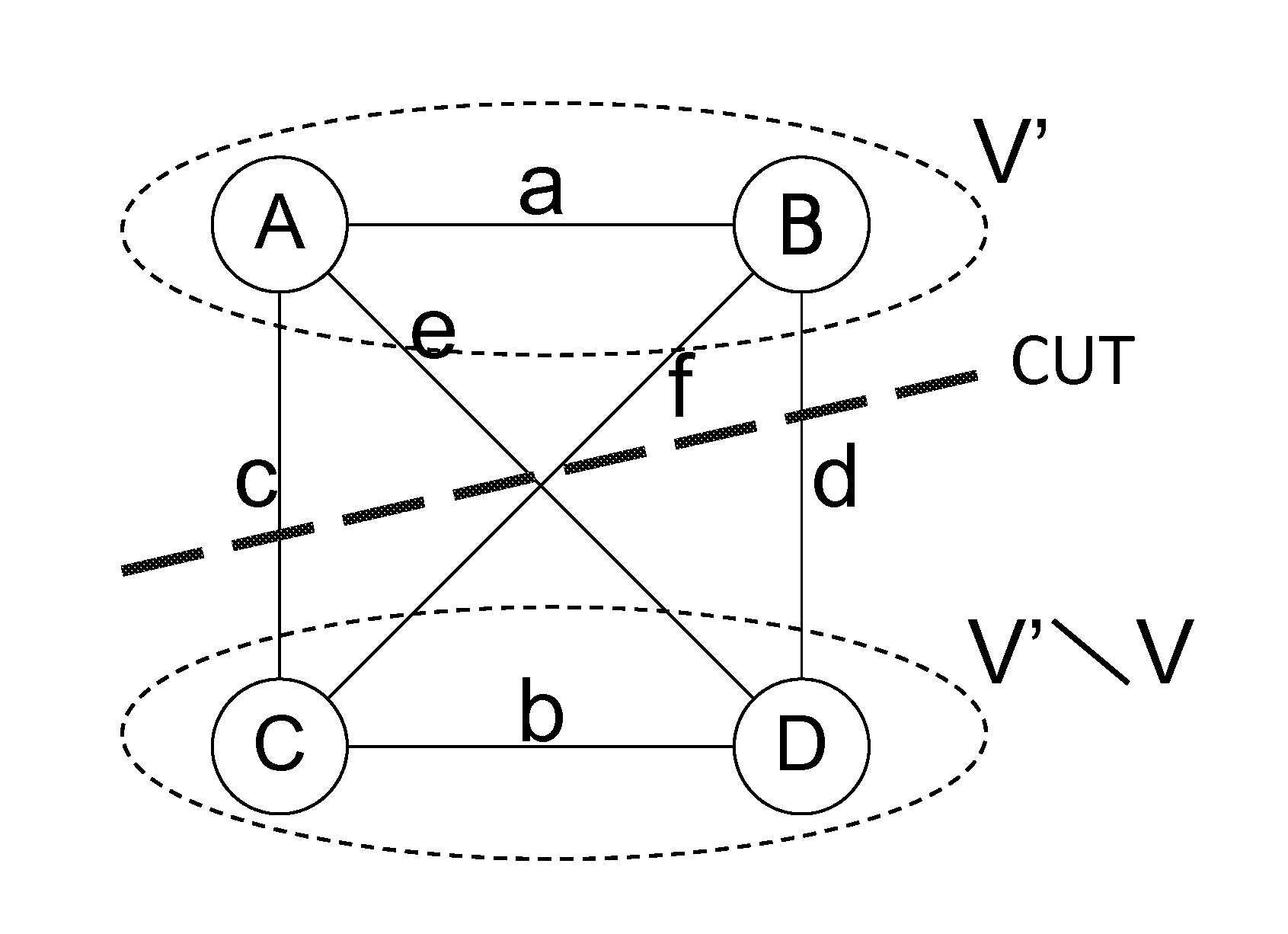

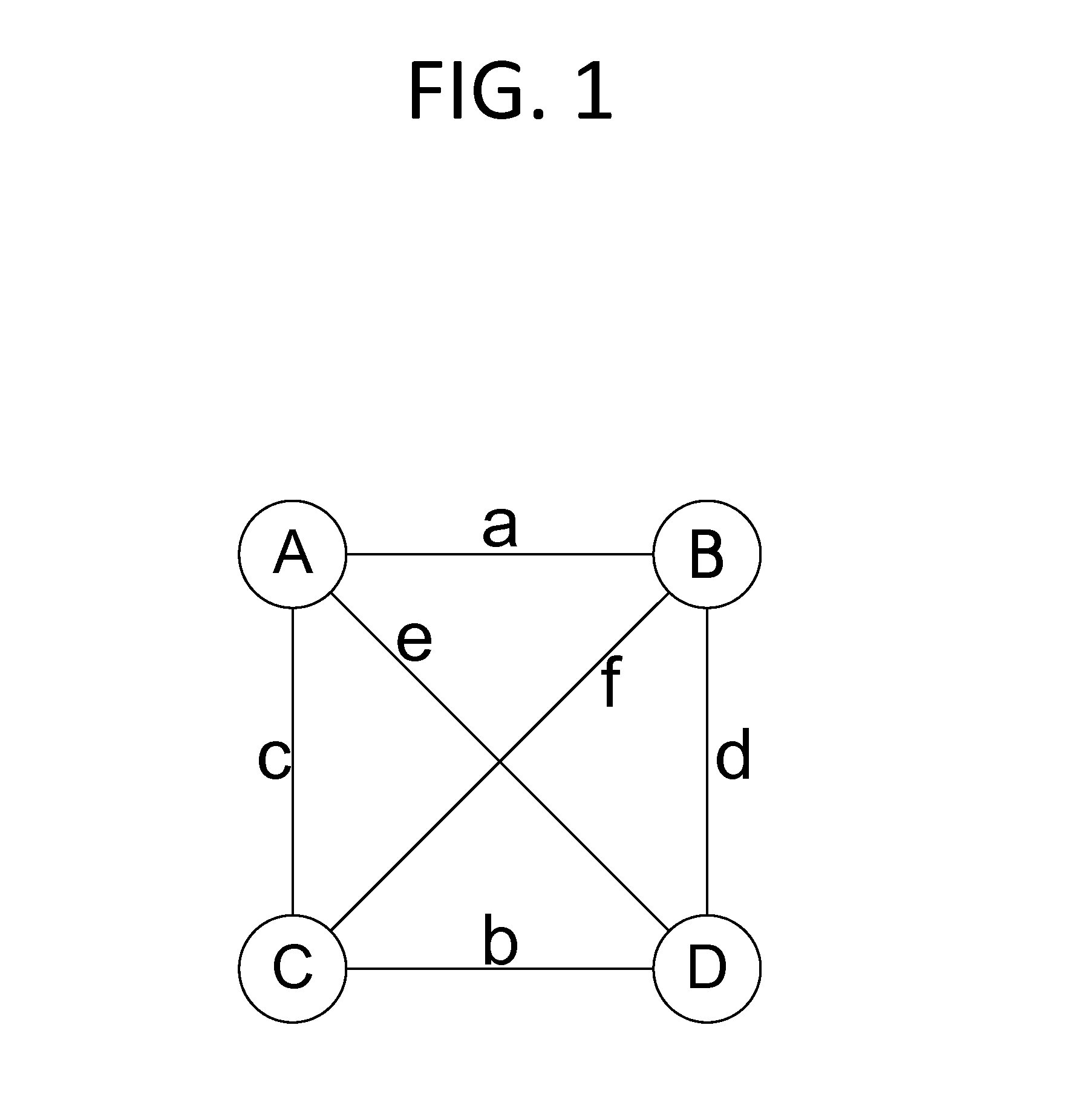

Quad state logic design methods, circuits, and systems

InactiveUS6963225B2Reduce wiring densityReduced wiring interconnectsLogic circuits characterised by logic functionMultistate logicHigh densityEngineering

Quad-state logic elements and quad-state memory elements are used to reduce the wiring density of integrated circuits. The resulting reduction in wiring interconnects between memories and logic elements results in higher speed, higher density, and lower power integrated circuit designs.

Owner:TEXAS INSTR INC

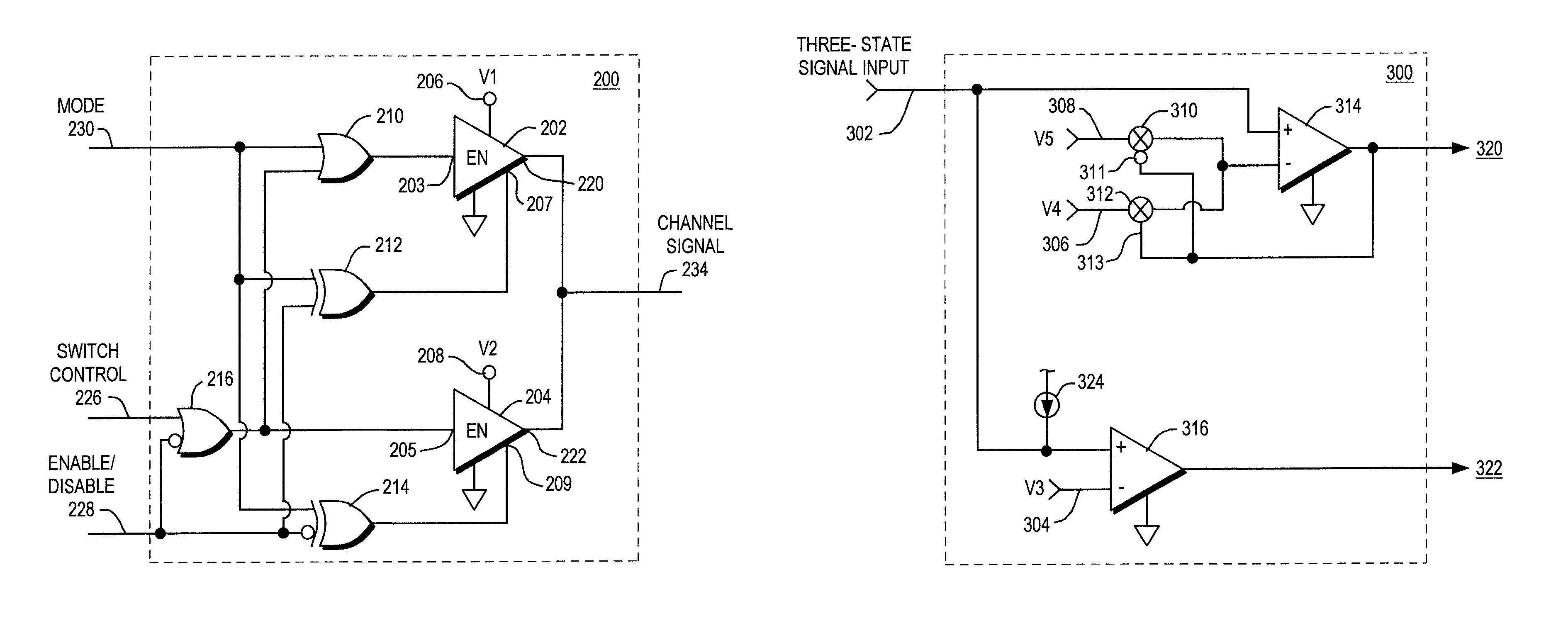

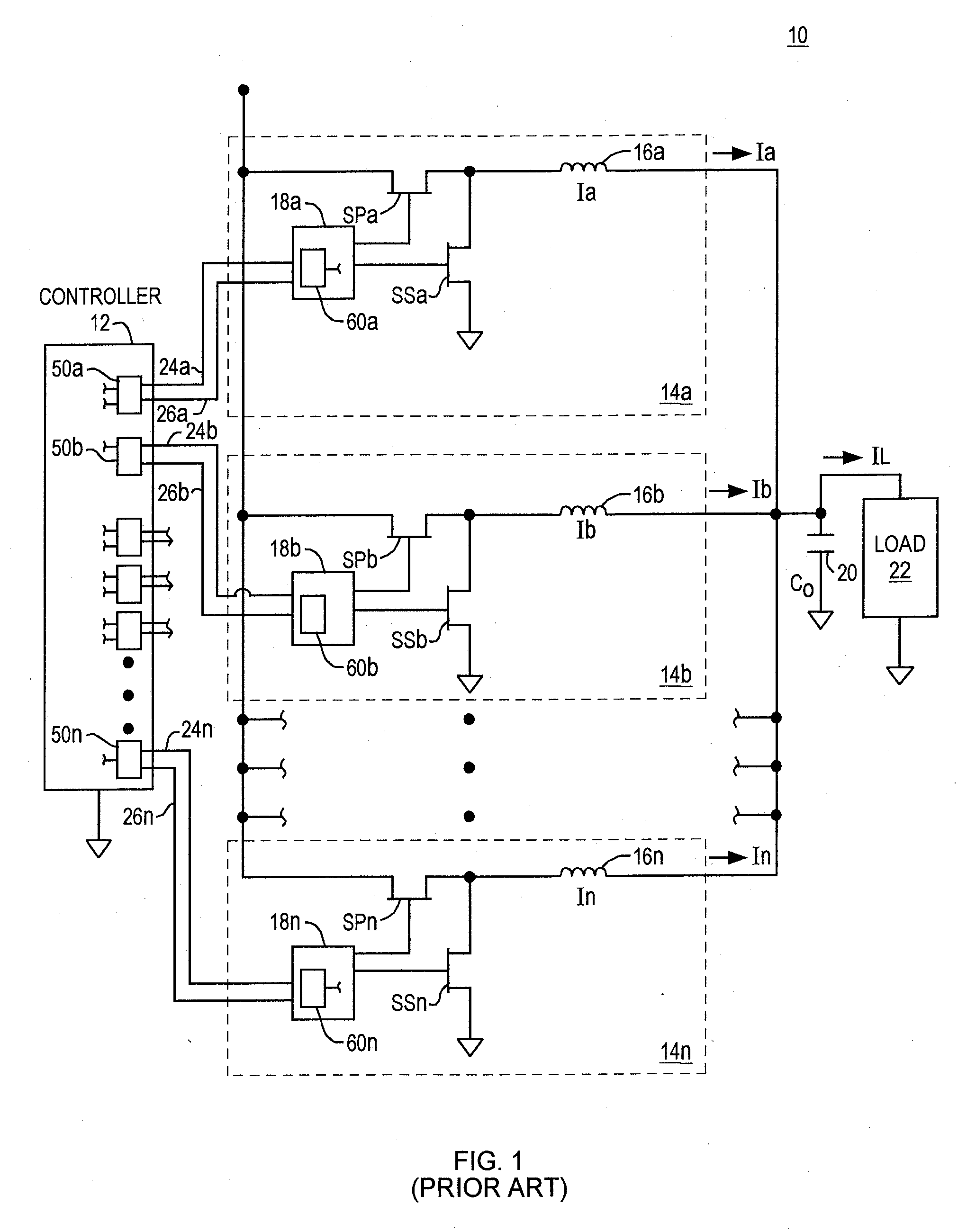

Multi-level signaling

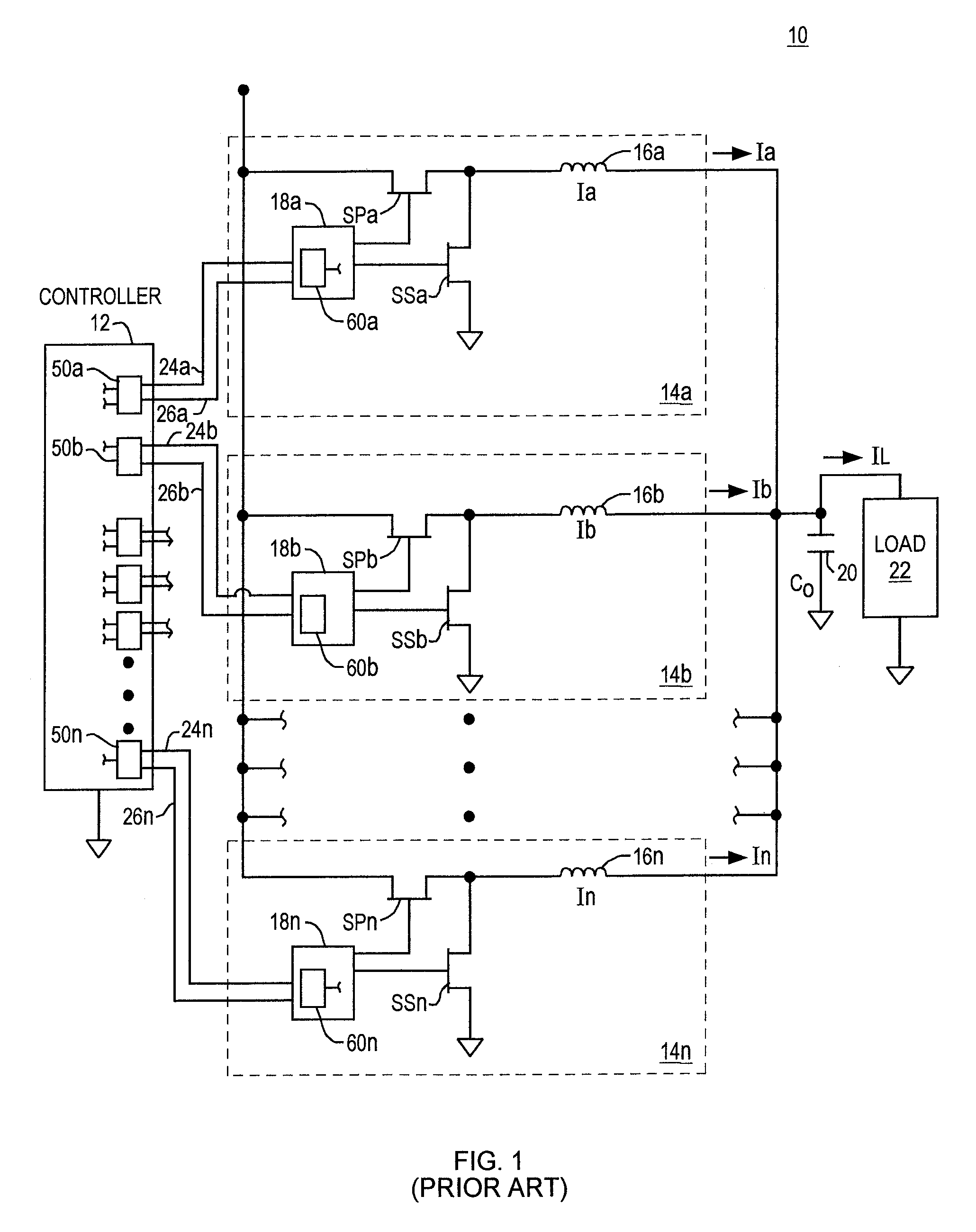

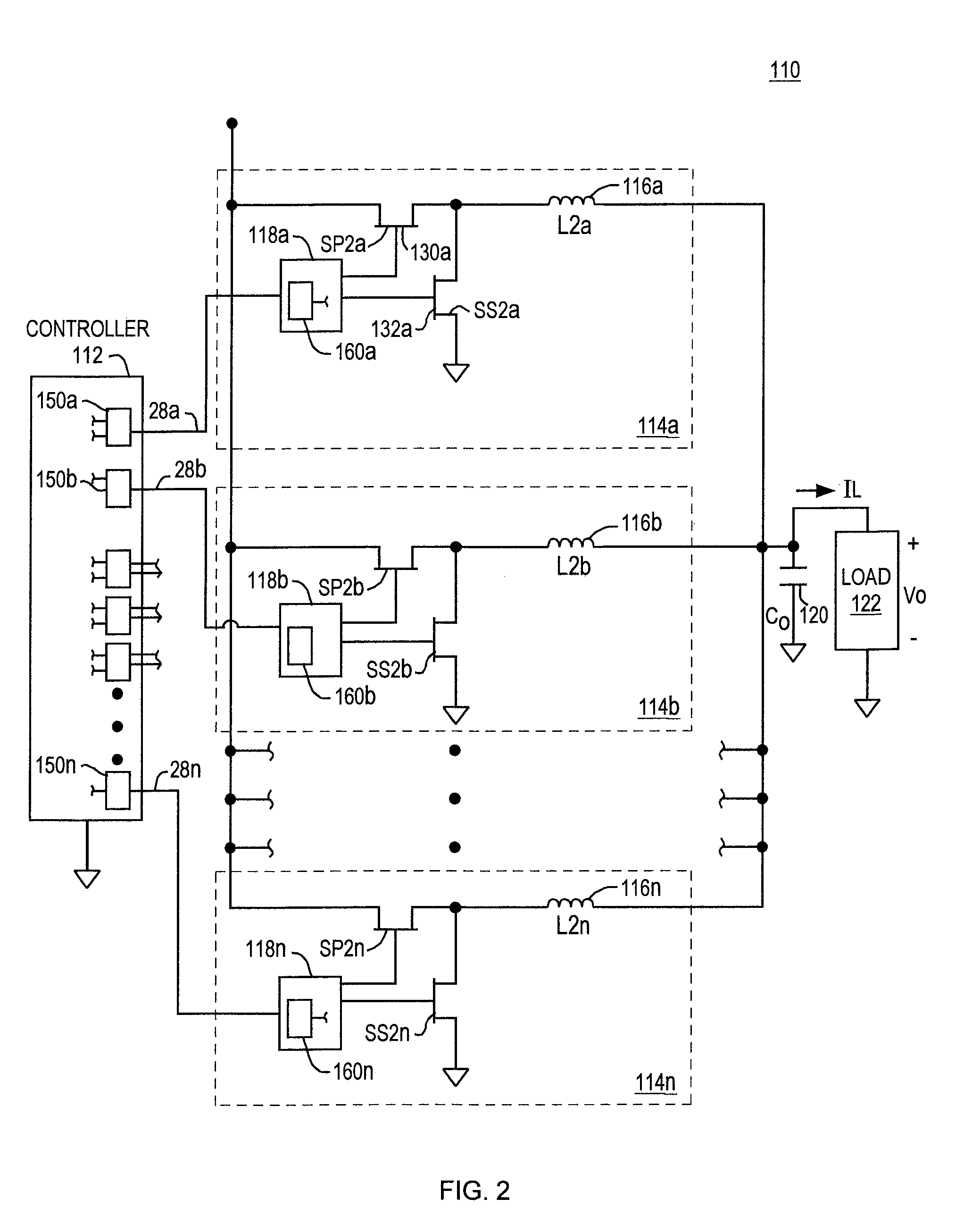

A control circuit generates an output based on the first signal and the second signal by encoding the output to be a multi-state signal having at least three states. A magnitude of the multi-state signal generated by the controller varies depending on binary states of the first signal and the second signal. The controller utilizes the output (i.e., the multi-state signal) to control a switching circuit. A driver circuit receives the output generated by the control circuit. In one embodiment, the multi-state signal has more than two different logic states. The driver decodes the multi-state signal for generating signals to control switches in the switching circuit. One signal generated by the driver circuit is a pulse width modulation signal; another signal generated by the driver circuit is an enable / disable signal.

Owner:INFINEON TECH AMERICAS CORP

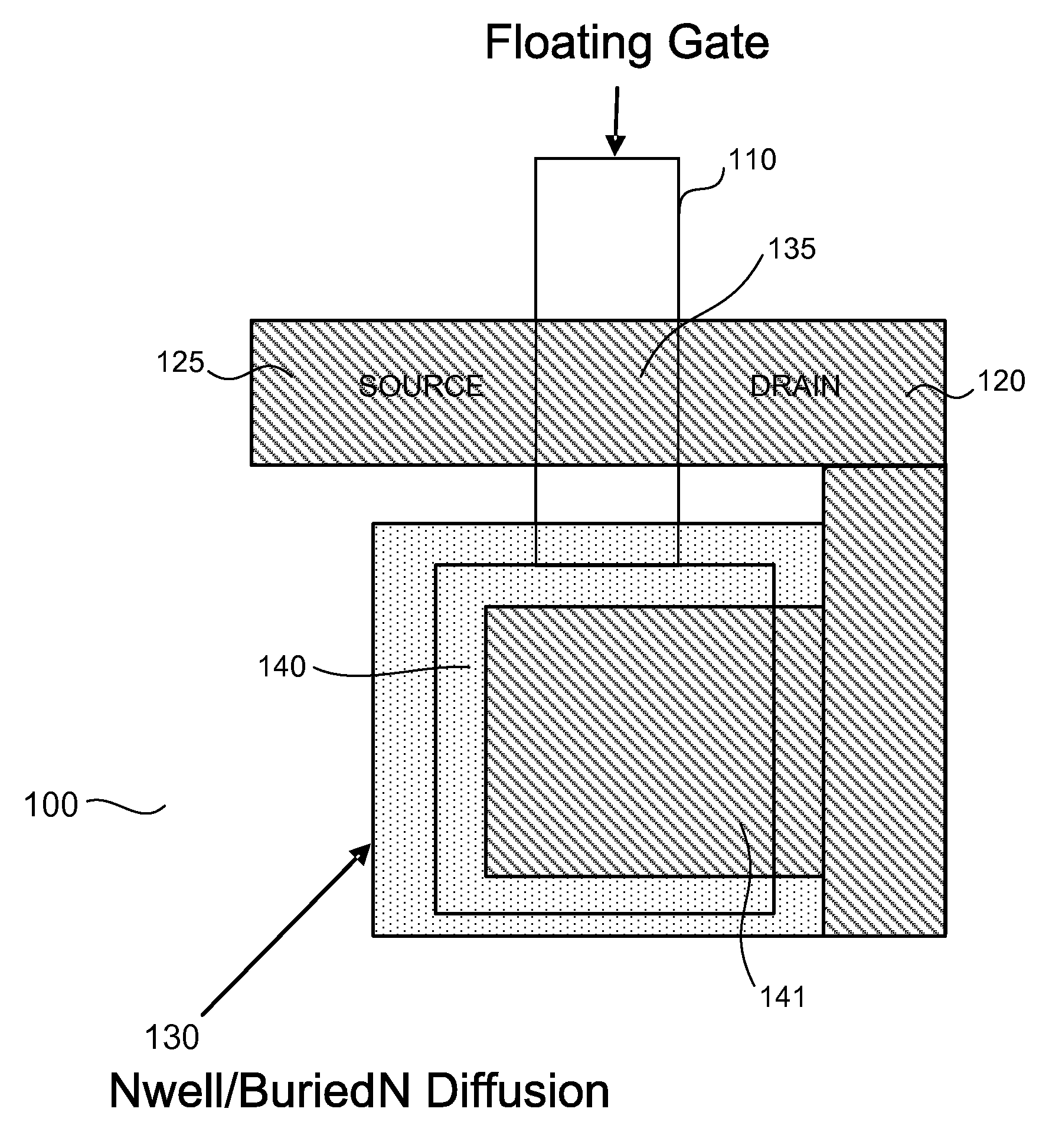

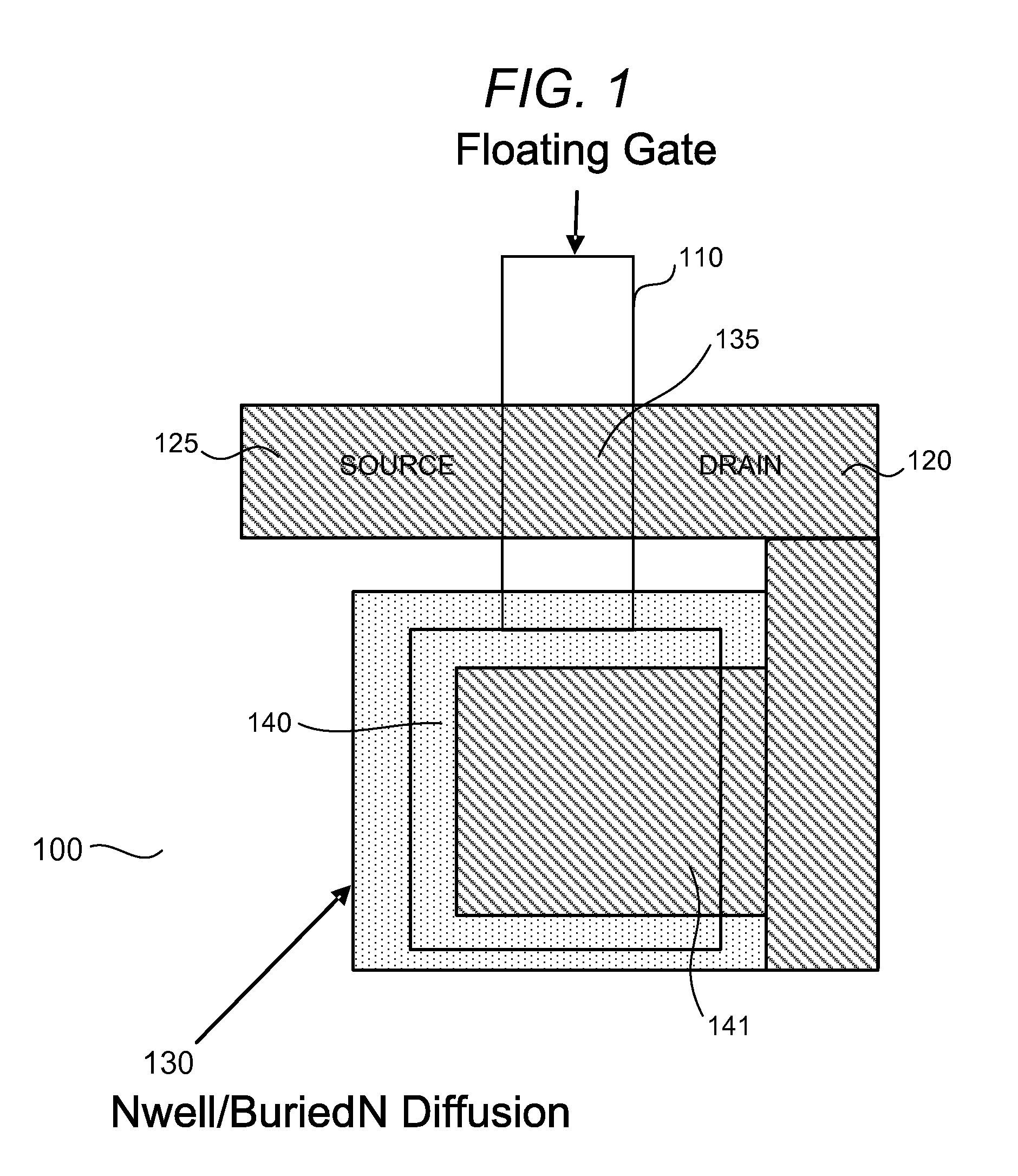

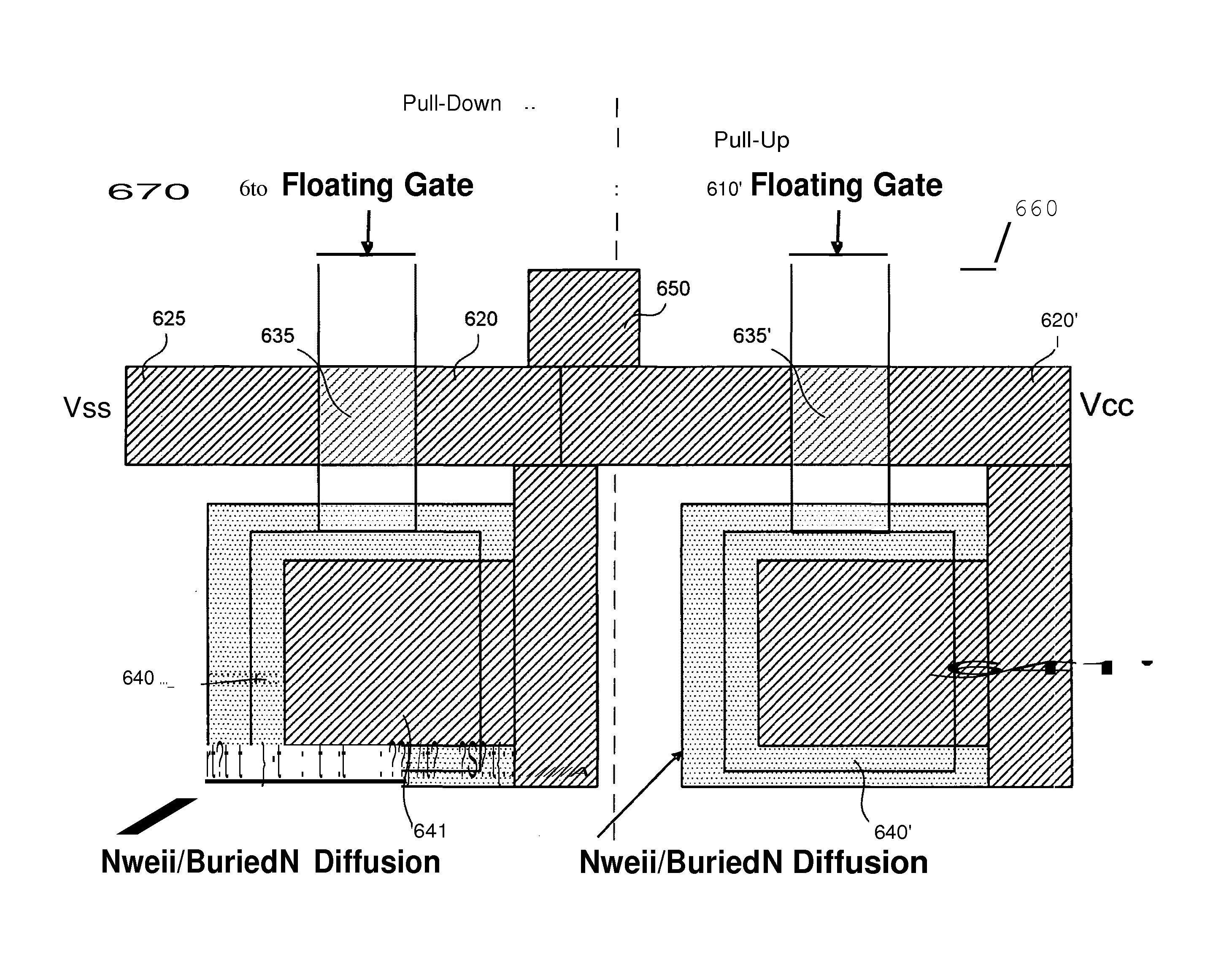

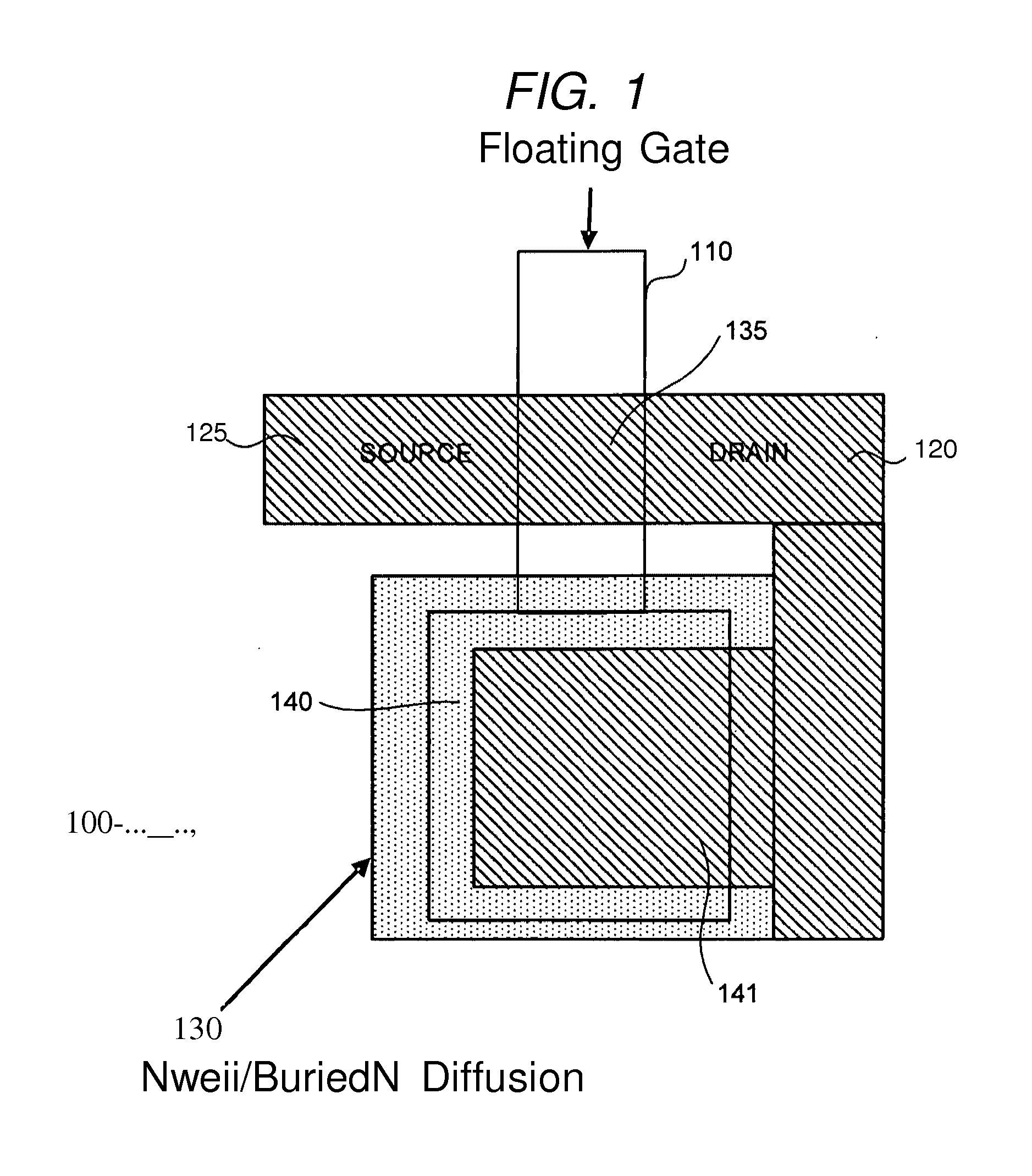

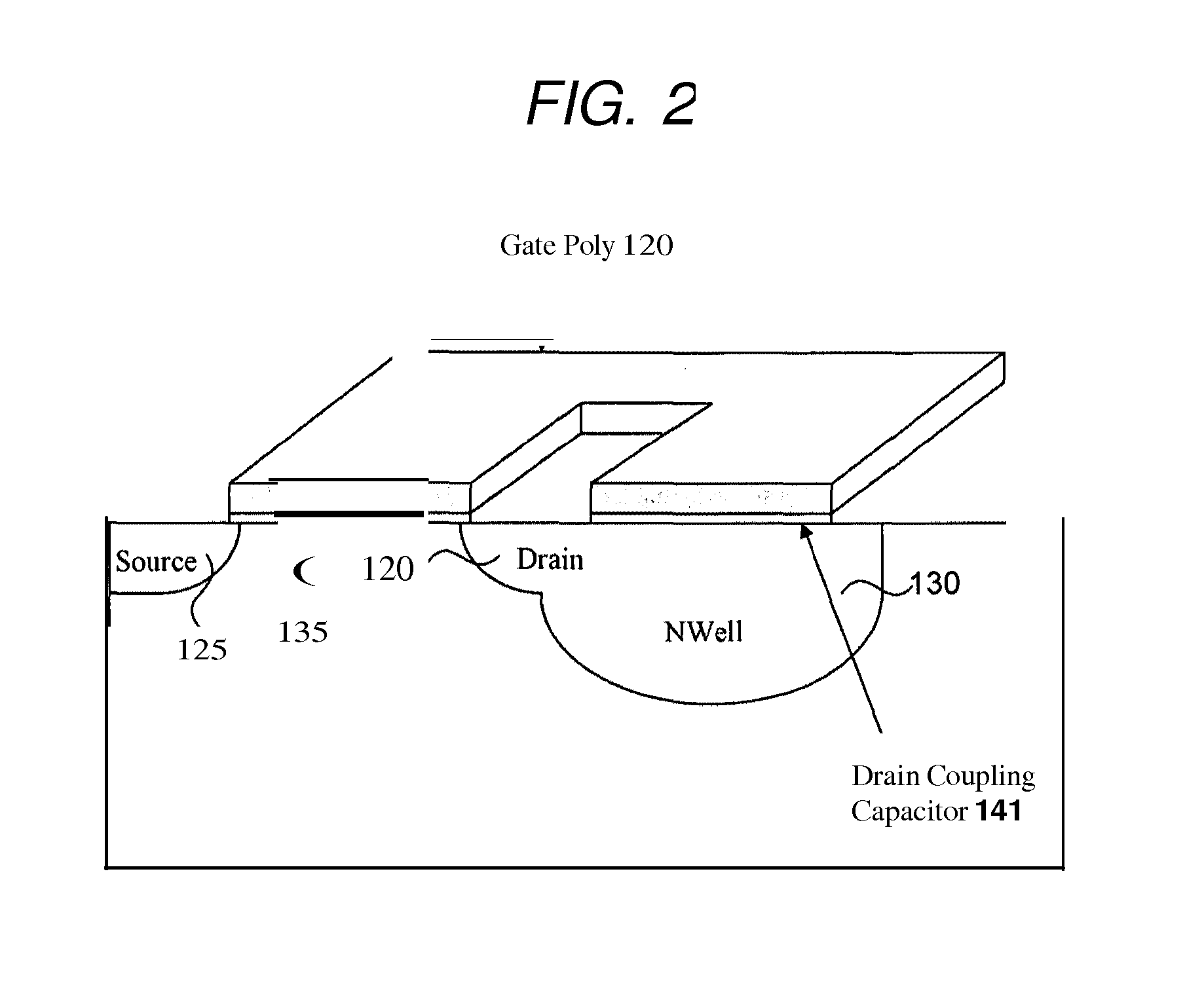

Non-volatile one-time - programmable and multiple-time programmable memory configuration circuit

A programmable non-volatile configuration circuit uses a pair of non-volatile memory devices arranged in a pull-up and pull-down arrangement. The non-volatile memory devices have floating gates that overlaps a variable portion of a source / drain region. This allows a programming voltage for the device to be imparted to the floating gate through variable capacitive coupling, thus changing the state of the device. The invention can be used in environments to store configuration data for programmable logic devices, field programmable arrays, and many other applications.

Owner:INVENSAS CORP

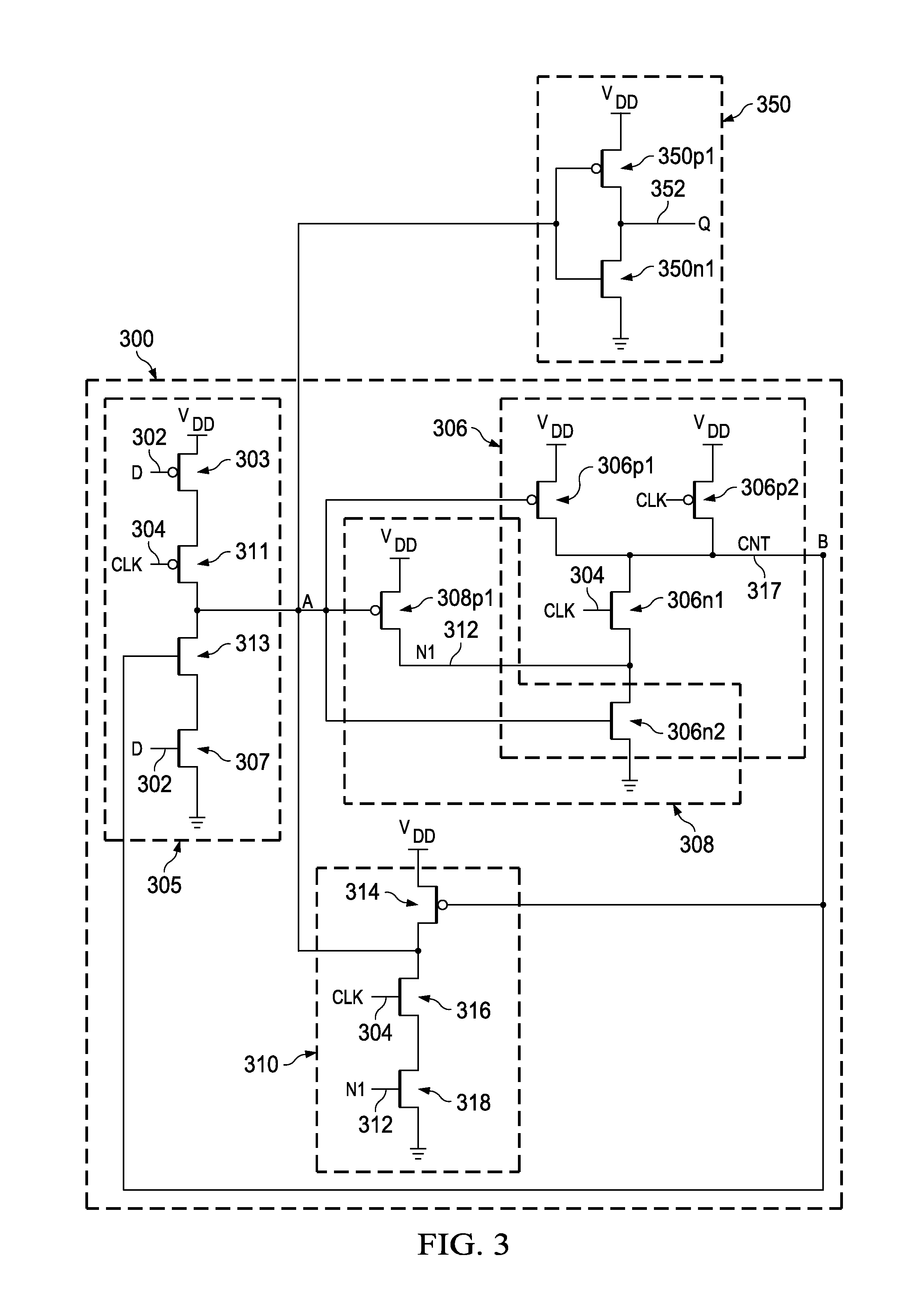

Quaternary and trinary logic switching circuits

InactiveUS20050258863A1Increase spacingIncrease powerMultistate logicSolid-state devicesCost effectivenessTime efficient

A logic circuit comprising a quaternary logic switching circuit which includes a multilevel storage cell (MLSC), and the trinary or variable threshold logic means to yield an improved space, power, and time-efficient performance device is disclosed. The present invention is used for the implementation of a customized new logic design to further improve the cost-effectiveness of the application. Advanced circuit solutions are provided using asynchronous clock controlled functional units which are field programmable. A diode capacitor ladder chain is also used on an on-chip power supply multiplier to support internal high voltage operations. A digital-to-analog-to-digital translation (DADT) apparatus is also provided utilizing the above identified circuits. Finally, a printed circuit board (PCB) net driver with a trinary signal wire provides 50% bandwidth increase over conventional binary solutions.

Owner:CHANG AUGUSTINE W +1

Multi-level signaling

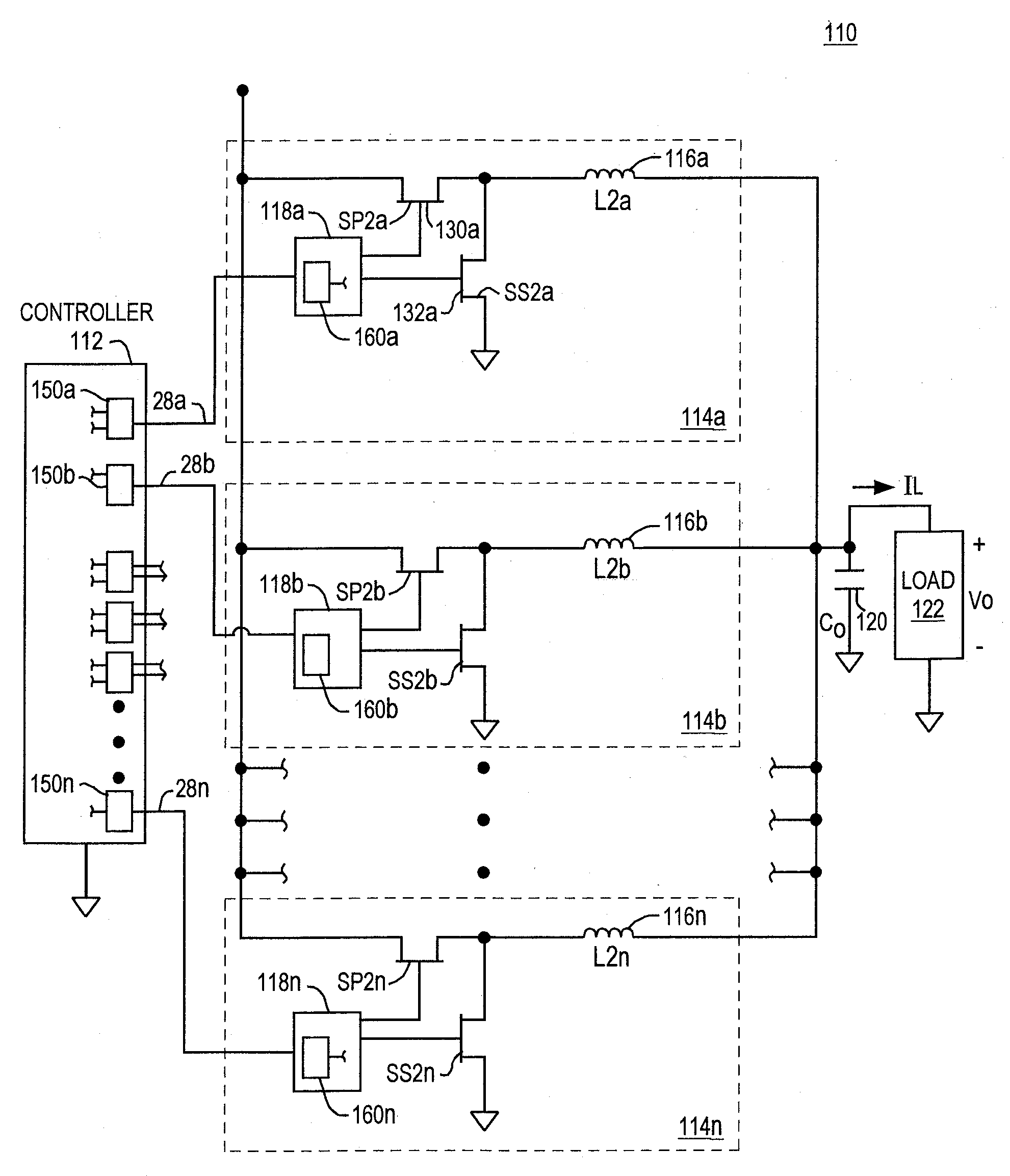

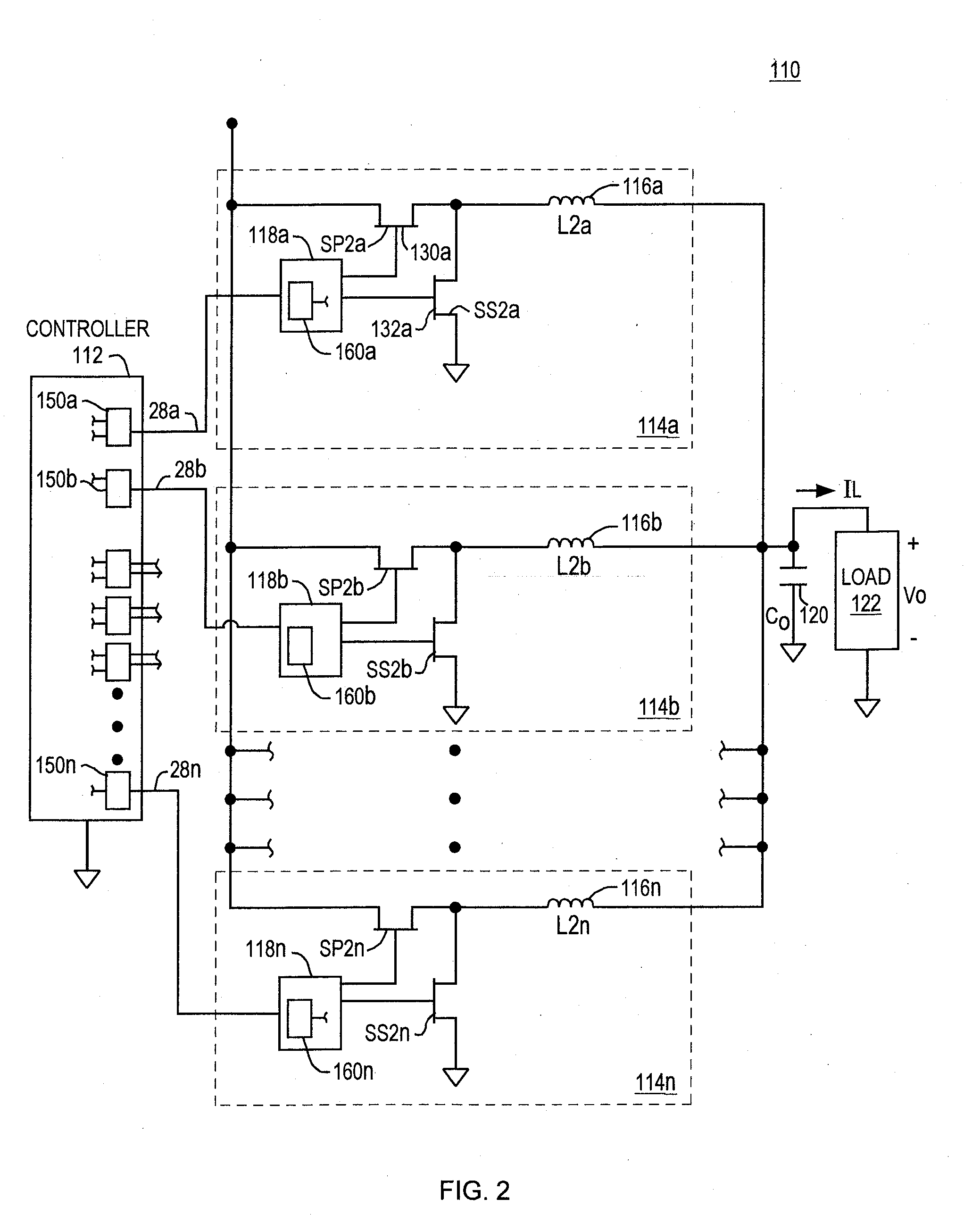

ActiveUS20100026261A1Minimizing and preventing switch conduction overlapSmooth transitionMultistate logicDc-dc conversionDriver circuitEngineering

A control circuit generates an output based on the first signal and the second signal by encoding the output to be a multi-state signal having at least three states. A magnitude of the multi-state signal generated by the controller varies depending on binary states of the first signal and the second signal. The controller utilizes the output (i.e., the multi-state signal) to control a switching circuit. A driver circuit receives the output generated by the control circuit. In one embodiment, the multi-state signal has more than two different logic states. The driver decodes the multi-state signal for generating signals to control switches in the switching circuit. One signal generated by the driver circuit is a pulse width modulation signal; another signal generated by the driver circuit is an enable / disable signal.

Owner:INFINEON TECH AMERICAS CORP

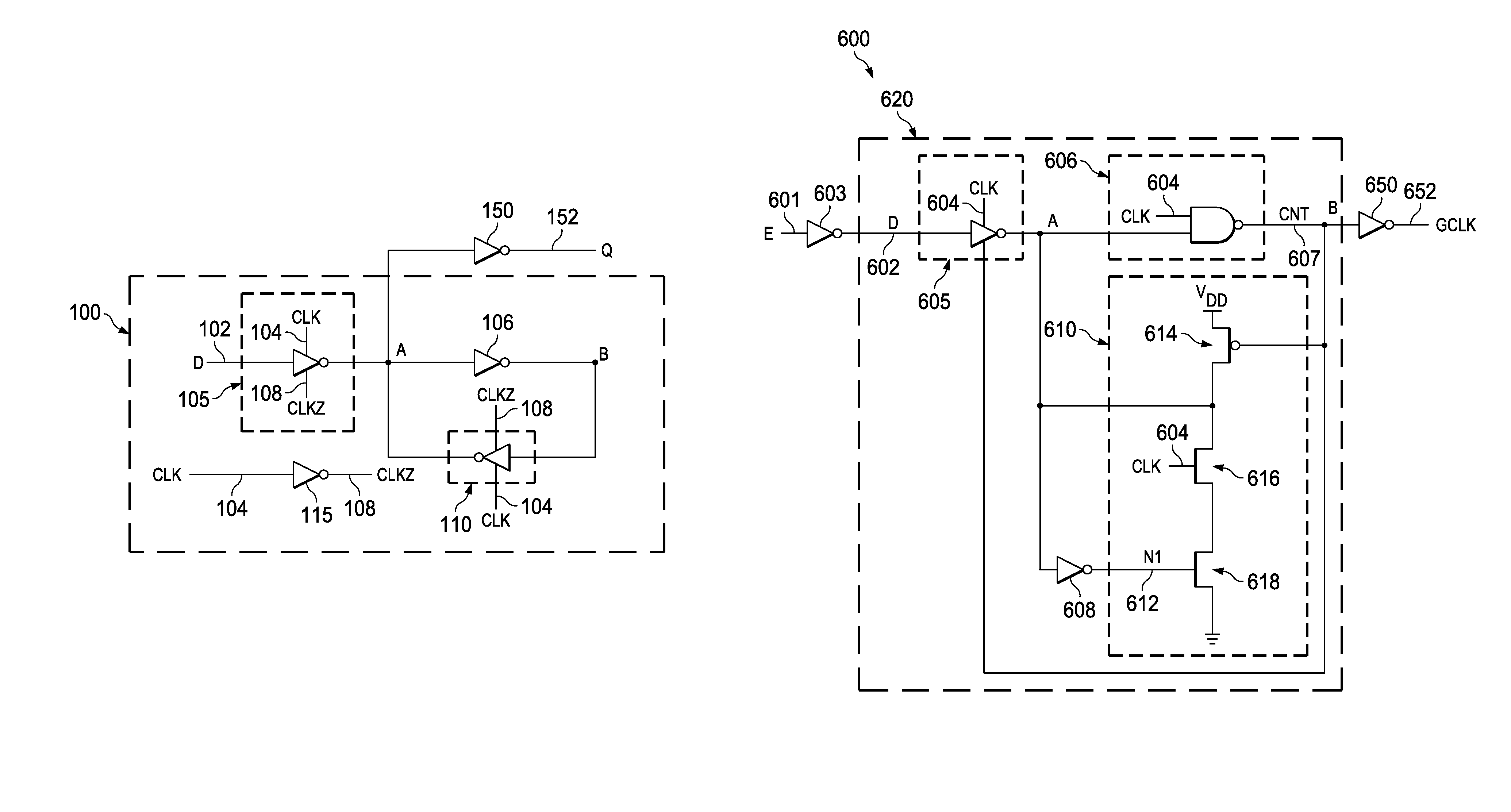

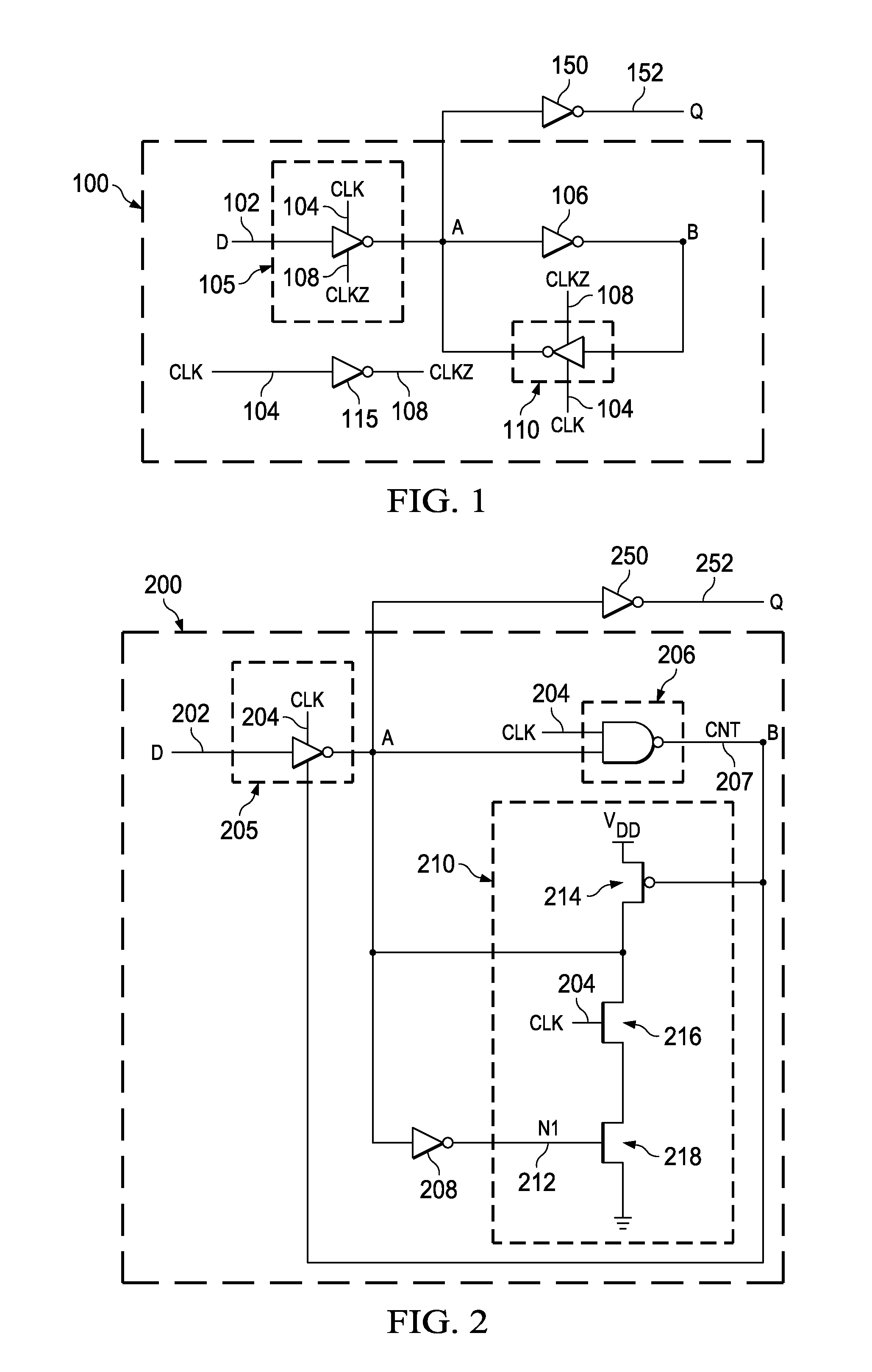

Integrated clock gating cell using a low area and a low power latch

ActiveUS9246489B1Power reduction in field effect transistorsPower reduction by control/clock signalControl signalInverter

The disclosure provides an ICG (integrated clock gating) cell that utilizes a low area and a low power latch. The ICG cell includes a first logic gate that receives an enable signal and generates a latch input. A latch is coupled to the first logic gate and receives the latch input and a clock input. The latch includes a tri-state inverter and an inverting logic gate. The tri-state inverter is activated by a control signal generated by the inverting logic gate. A second logic gate receives the control signal and generates a gated clock.

Owner:TEXAS INSTR INC

Variable threshold transistor for the schottky FPGA and multilevel storage cell flash arrays

An IC solution utilizing mixed FPGA and MLC arrays is proposed. The process technology is based on the Schottky CMOS devices comprising of CMOS transistors, low barrier Schottky barrier diode (SBD), and multi-level cell (MLC) flash transistors. Circuit architectures are based on the pulsed Schottky CMOS Logic (SCL) gate arrays, wherein a variable threshold NMOS transistor may replace the regular switching transistor. During initialization windows, existing FPGA programming techniques can selectively adjust the VT of the switching transistor, re-configure the intra-connections of the simple SCL gates, complete all global interconnections of various units. Embedded hardware arrays, hardwired blocks, soft macro constructs in one chip, and protocols implementations are parsed. A wide range of circuit applications involving generic IO and logic function generation, ESD and latch up protections, and hot well biasing schemes are presented. The variable threshold transistors thus serve 3 distinctive functions.

Owner:SUPER TALENT ELECTRONICS

Integrated circuits with adjustable body bias and power supply circuitry

ActiveCN101399537AReduce consumptionMeet the design requirementsPower reduction by control/clock signalMultistate logicComputer Aided DesignEnergy expenditure

An integrated circuit is provided with adjustable transistor body bias circuitry and adjustable power supply circuitry. The adjustable circuitry may be used to selectively apply body bias voltages and power supply voltages to blocks of programmable logic, memory blocks, and other circuit blocks on the integrated circuit. The body bias voltages and power supply voltages may be identified by computer aided design tools. The body bias voltages may be used to reduce leakage currents and power consumption when high speed circuit block operation is not required. Reduced power supply voltages may also be used to reduce power consumption when high speed circuit block operation is not required. To ensure optimum switching speeds, circuit blocks for which high-speed performance is critical can be provided with minimal body bias voltage or no body bias and can be provided with maximum power supply levels.

Owner:ALTERA CORP

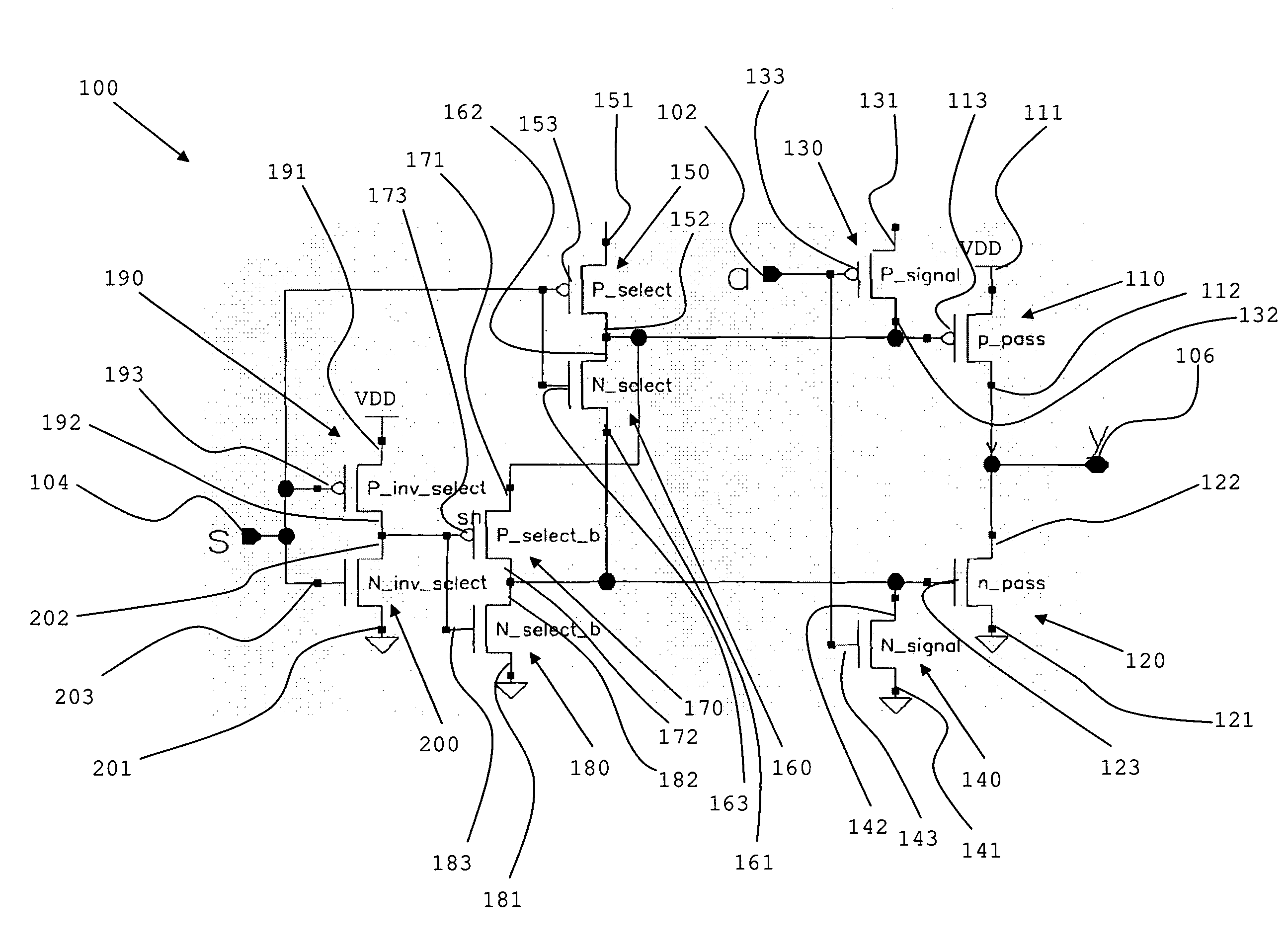

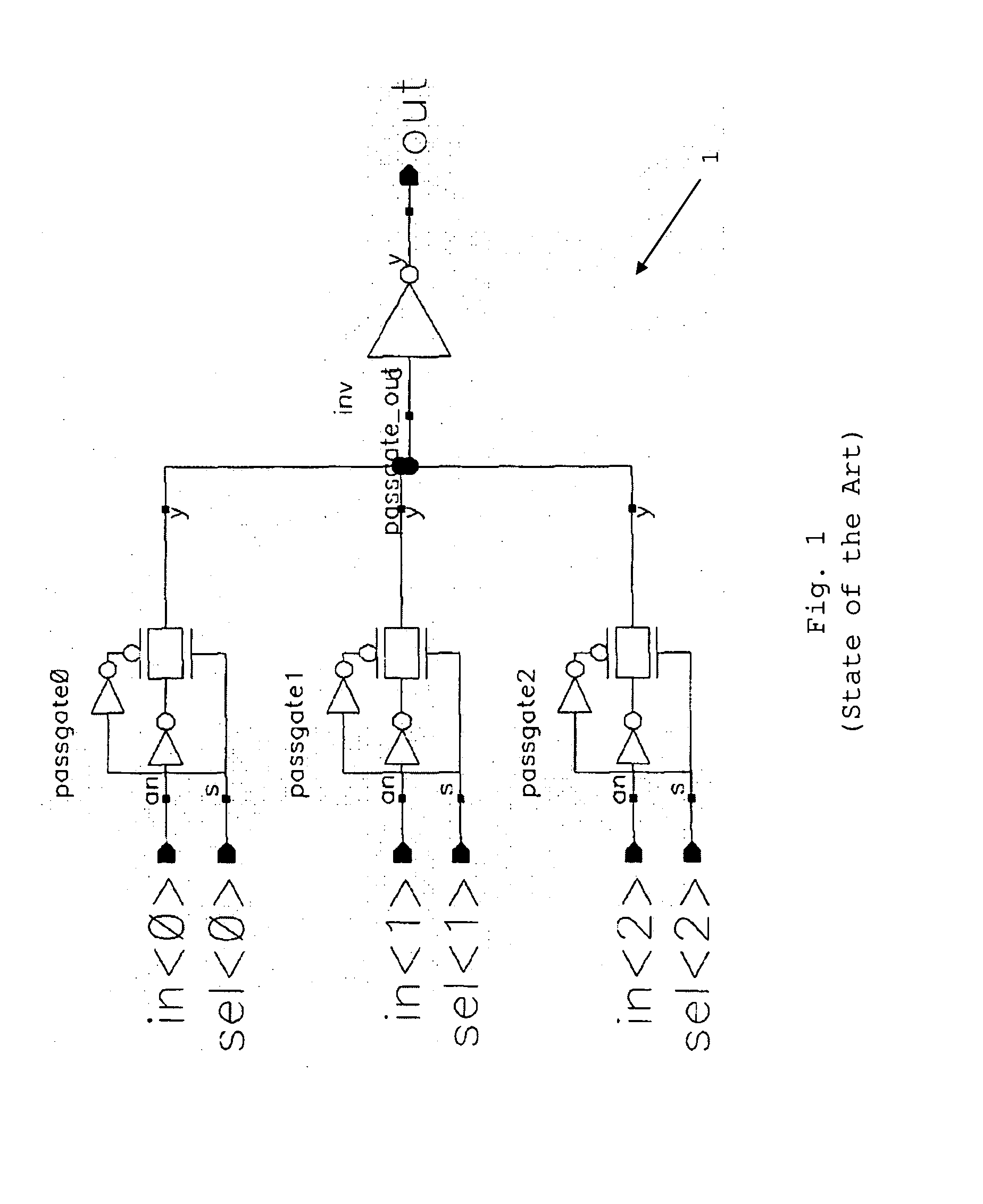

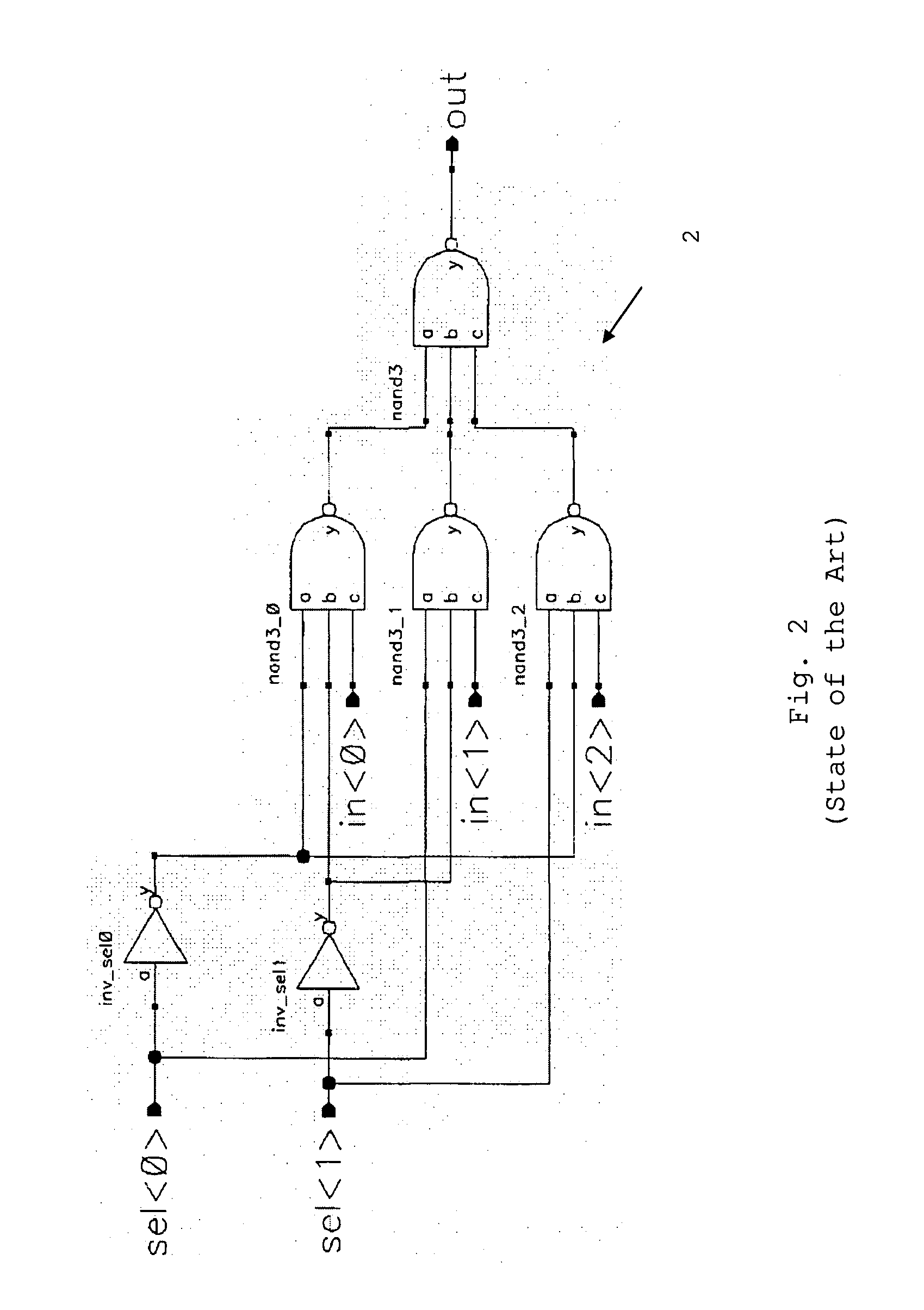

Tri-State Circuit Element Plus Tri-State-Multiplexer Circuitry

InactiveUS20080258769A1Reduce device settingsImprove performancePower reduction in field effect transistorsMultistate logicCMOSMultiplexer

A Tri-State circuit element (100) composed of Complementary Metal Oxide Semiconductor (CMOS)—devices is described. Said Tri-State circuit element (100) having a data signal input terminal (102) for receiving a data signal, an enable signal input terminal (104) for receiving an enable signal, and an output signal terminal (106) for providing an output signal. Furthermore a Tri-State-Multiplexer circuitry (300) composed of such Tri-State circuit elements (100) is described.

Owner:IBM CORP

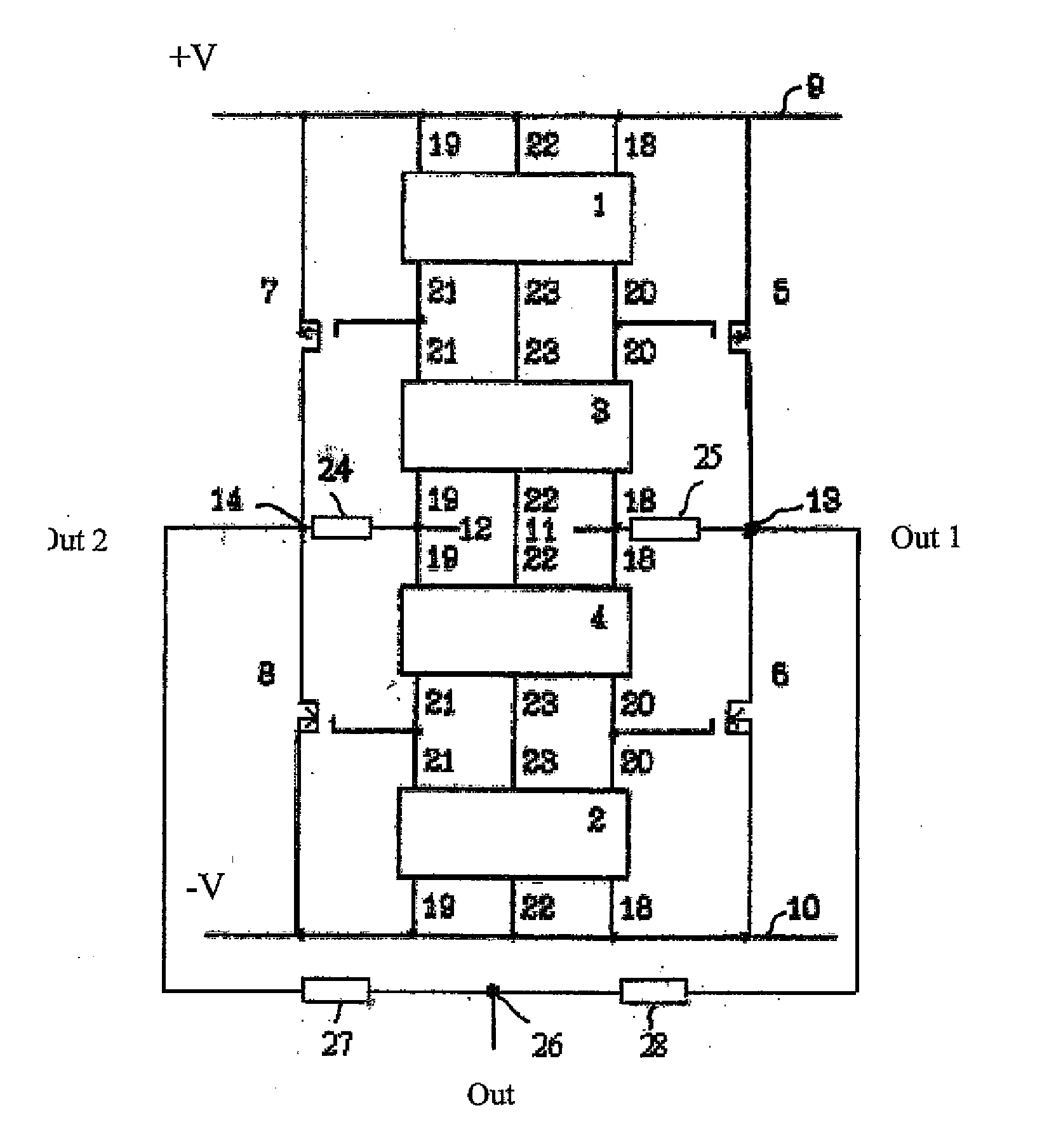

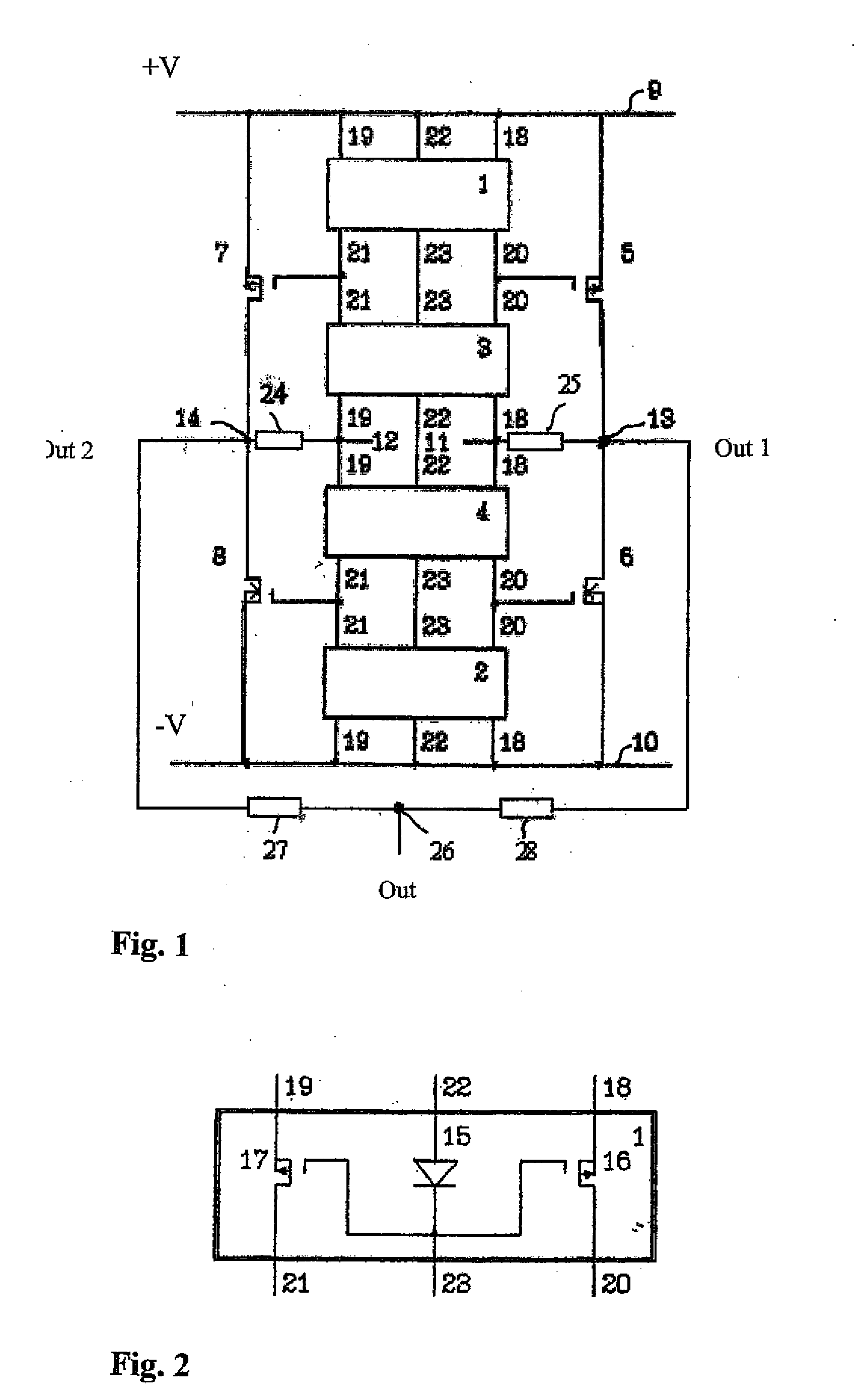

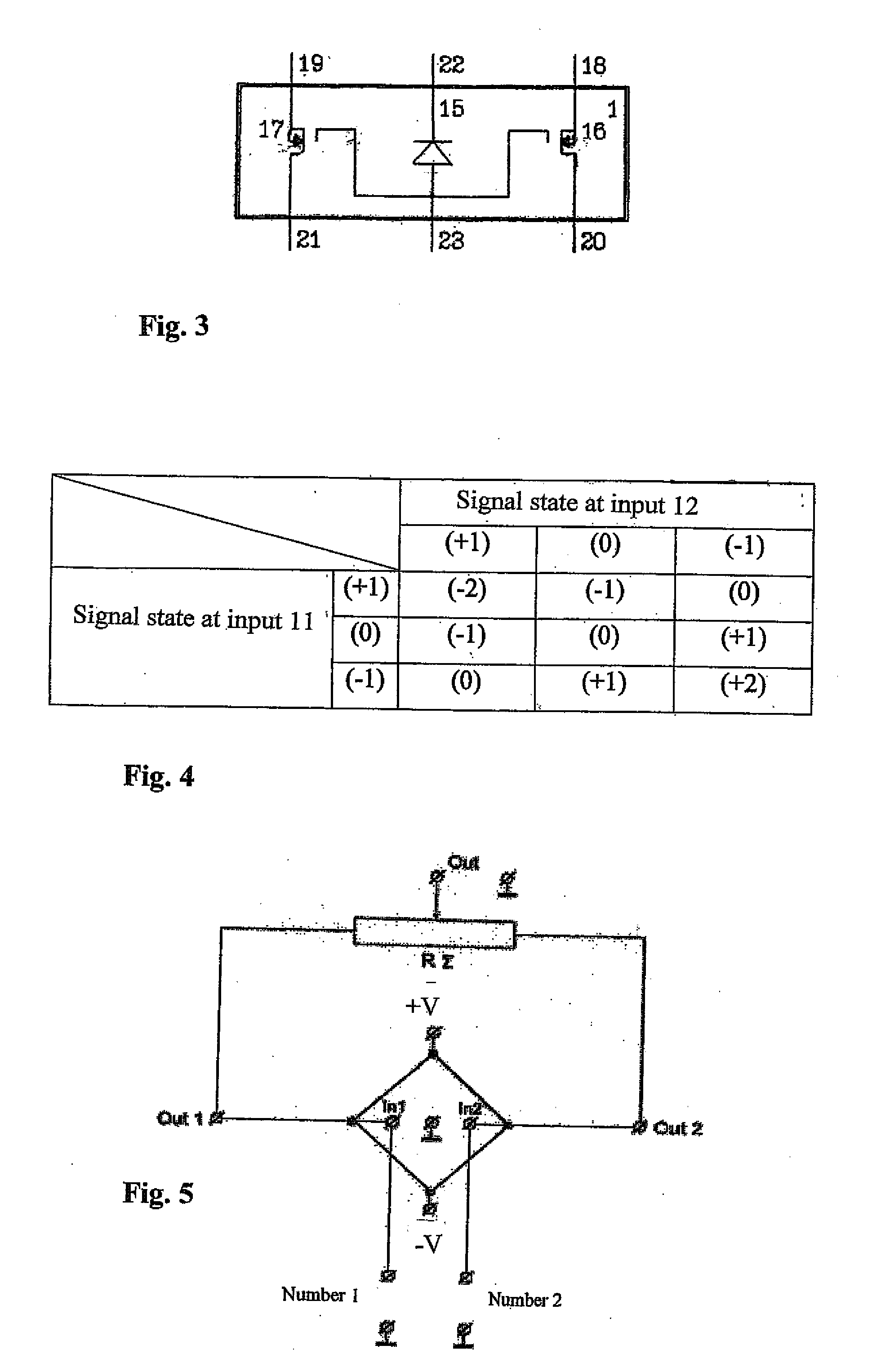

Multivalued logic circuit

InactiveUS20100164596A1Improve the protective effectSimplify workLogic circuits characterised by logic functionComputations using contact-making devicesElectrical resistance and conductancePush–pull output

In a bridge adder circuit, a first and a second complementary pair of current mirrors is connected between the input terminals and a positive and a negative supply voltage bus, respectively, to control a first and a second push-pull output stage. The outputs of the push-pull output stages are connected to the respective inputs through first resistors and to a common output node through second resistors. As a result, a universal circuit element for a multivalued logic element, such as ternary logic or 5-valued logic is provided.

Owner:FUZZY CHIP PTE

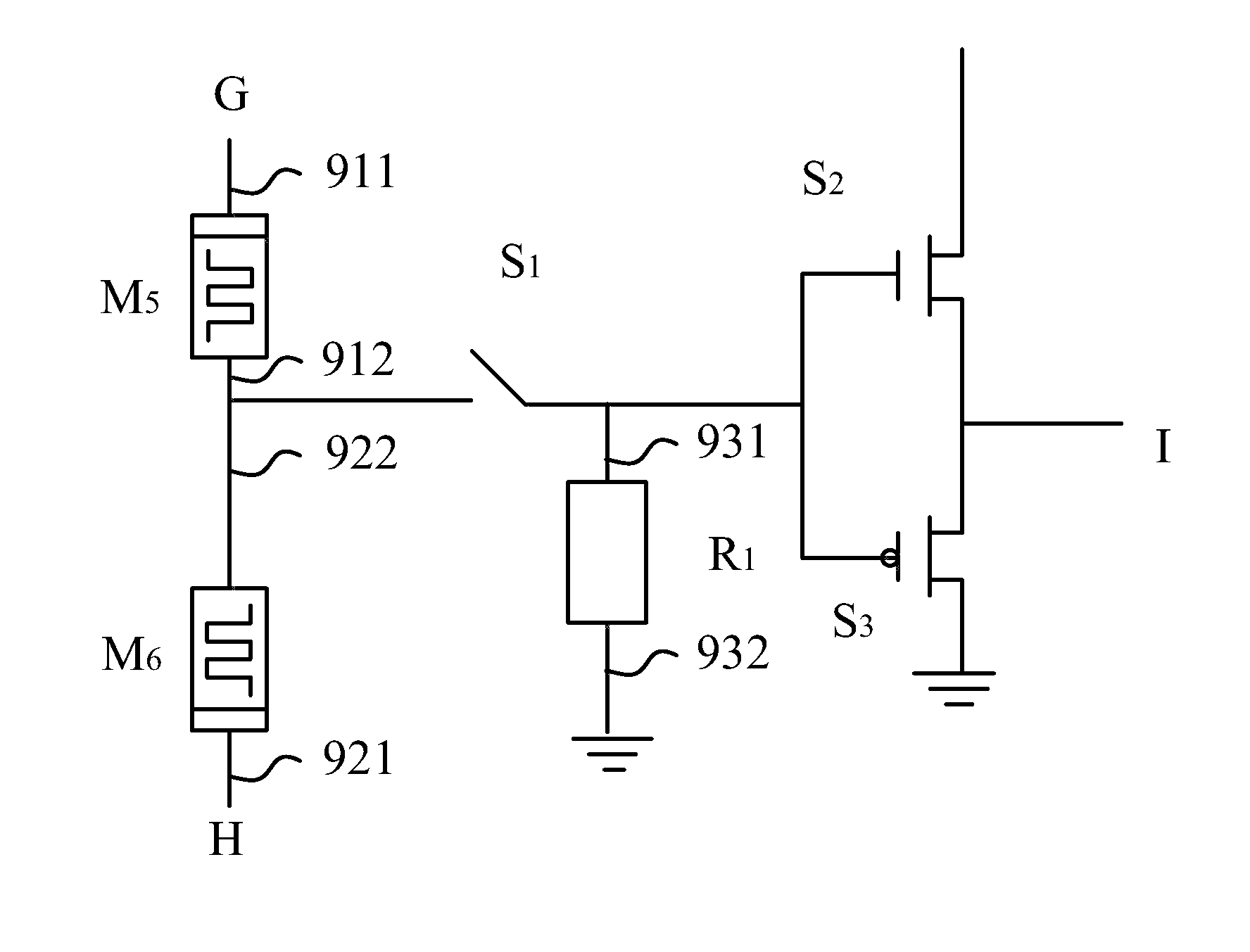

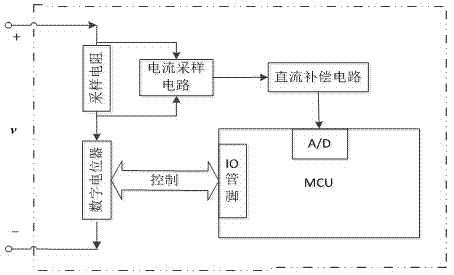

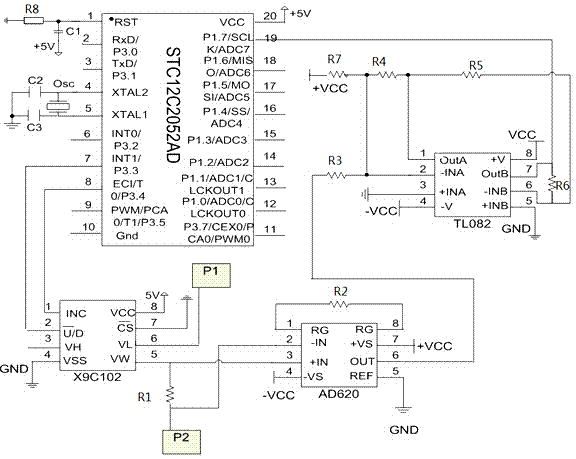

Memristor simulator circuit based on digital potentiometer

InactiveCN105450210ASimple structureEasy to debugMultistate logicDigital storageMathematical modelTheoretical computer science

The invention discloses a memristor simulator circuit based on a digital potentiometer. According to a mathematical model of a TiO2 memristor of an HP (Hewlett-Packard) laboratory, discrete analysis is performed on the mathematical model, a discrete model of the mathematical model of the memristor is obtained, and according to the obtained discrete mathematical model, the memristor model of the HP laboratory is realized by using a control circuit and the digital potentiometer. The memristor simulator provided by the invention comprises the digital potentiometer, a high quality instrumentation differential amplifier and a singlechip. Under the condition that a single isolated memristor device of a nanoscale cannot be obtained, the memristor simulator provided by the invention can replace a practical TiO2 memristor to perform design and experiment of relevant circuits of the memristor, and can also be used for other fields in need of the memristor.

Owner:HANGZHOU DIANZI UNIV

Non-volatile one-time-programmable and multiple-time programmable memory configuration circuit

A programmable non-volatile configuration circuit uses a pair of non-volatile memory devices arranged in a pull-up and pull-down arrangement. The non-volatile memory devices have floating gates that overlaps a variable portion of a source / drain region. This allows a programming voltage for the device to be imparted to the floating gate through variable capacitive coupling, thus changing the state of the device. The invention can be used in environments to store configuration data for programmable logic devices, field programmable arrays, and many other applications.

Owner:INVENSAS CORP

Multi-level output driver with adjustable pre-distortion capability

Owner:SKORPIOS TECH

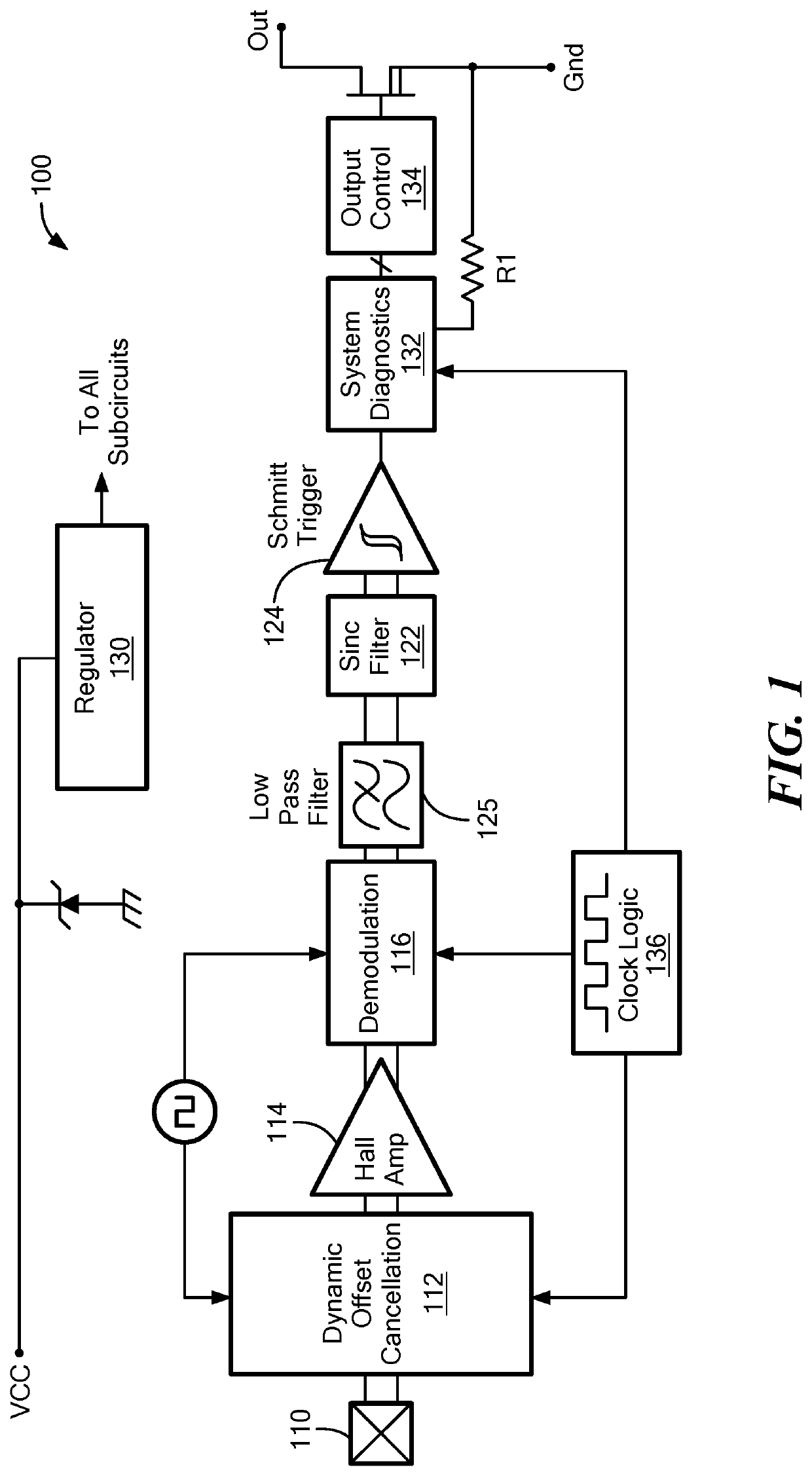

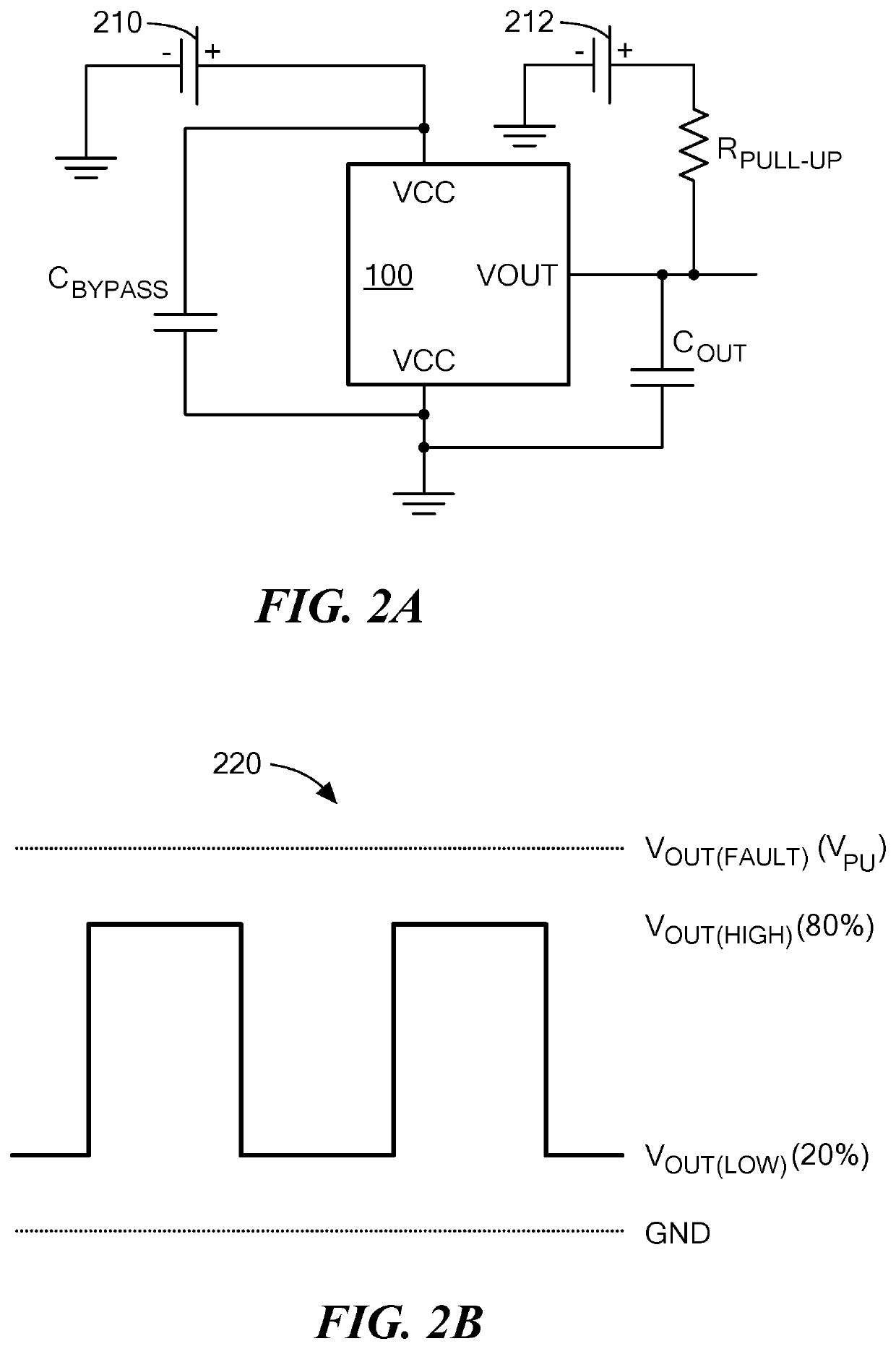

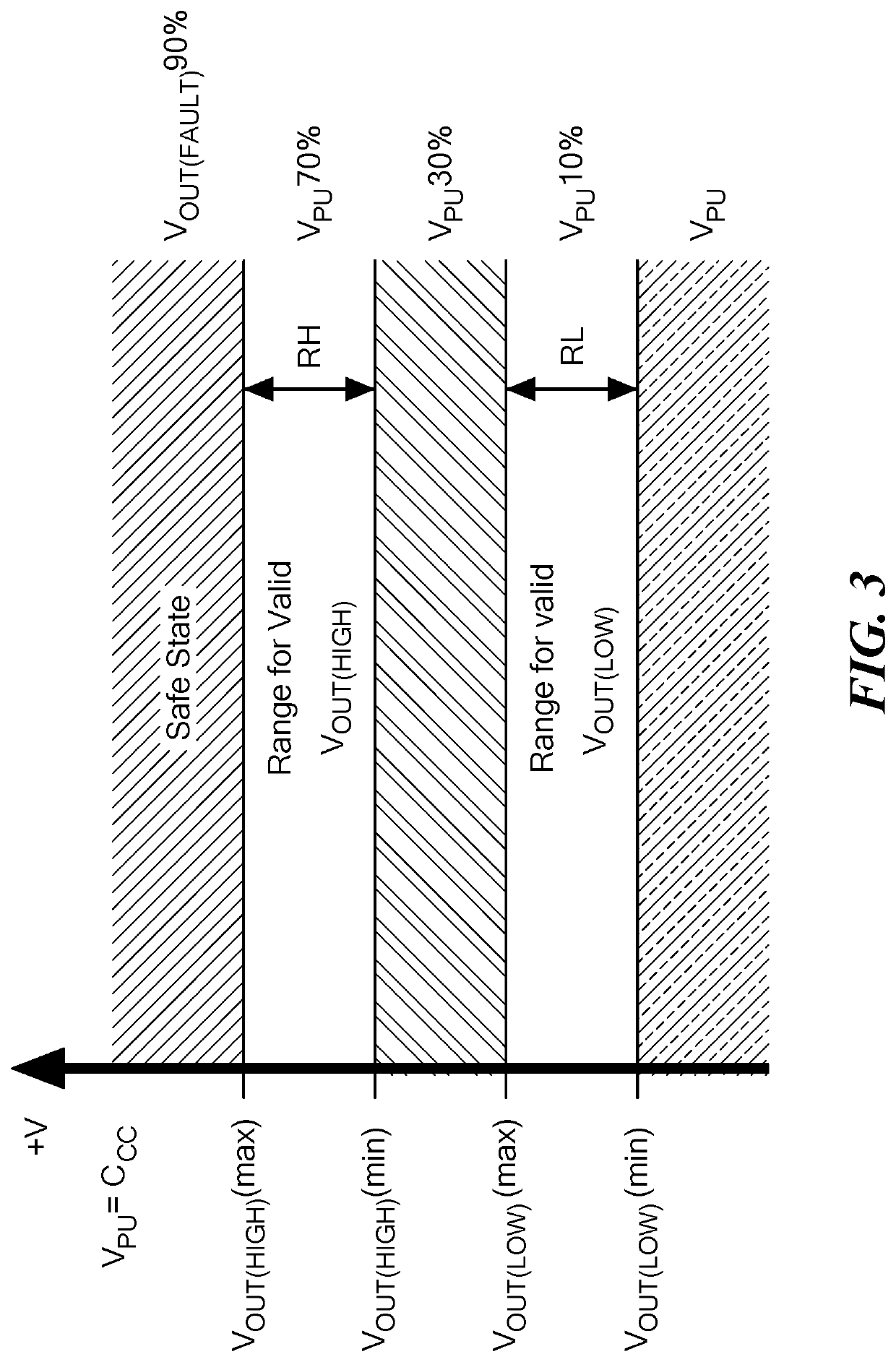

Ratiometric Sensor Output Topology And Methods

A sensor includes an output circuit configured to generate a sensor output signal based on an input signal having a logic high or low level, as may be provided by a Schmitt trigger circuit. During normal operation, the output switches between a first percentage of the supply voltage for logic high and a second percentage of the supply voltage for logic low. To convey a failure at the output, an output signal is output as either ground or the supply voltage when a fault is detected. As such, a fault can be communicated any time the output voltage is not equal to the first percentage or the second percentage of the supply voltage.

Owner:BILLGO INC +1

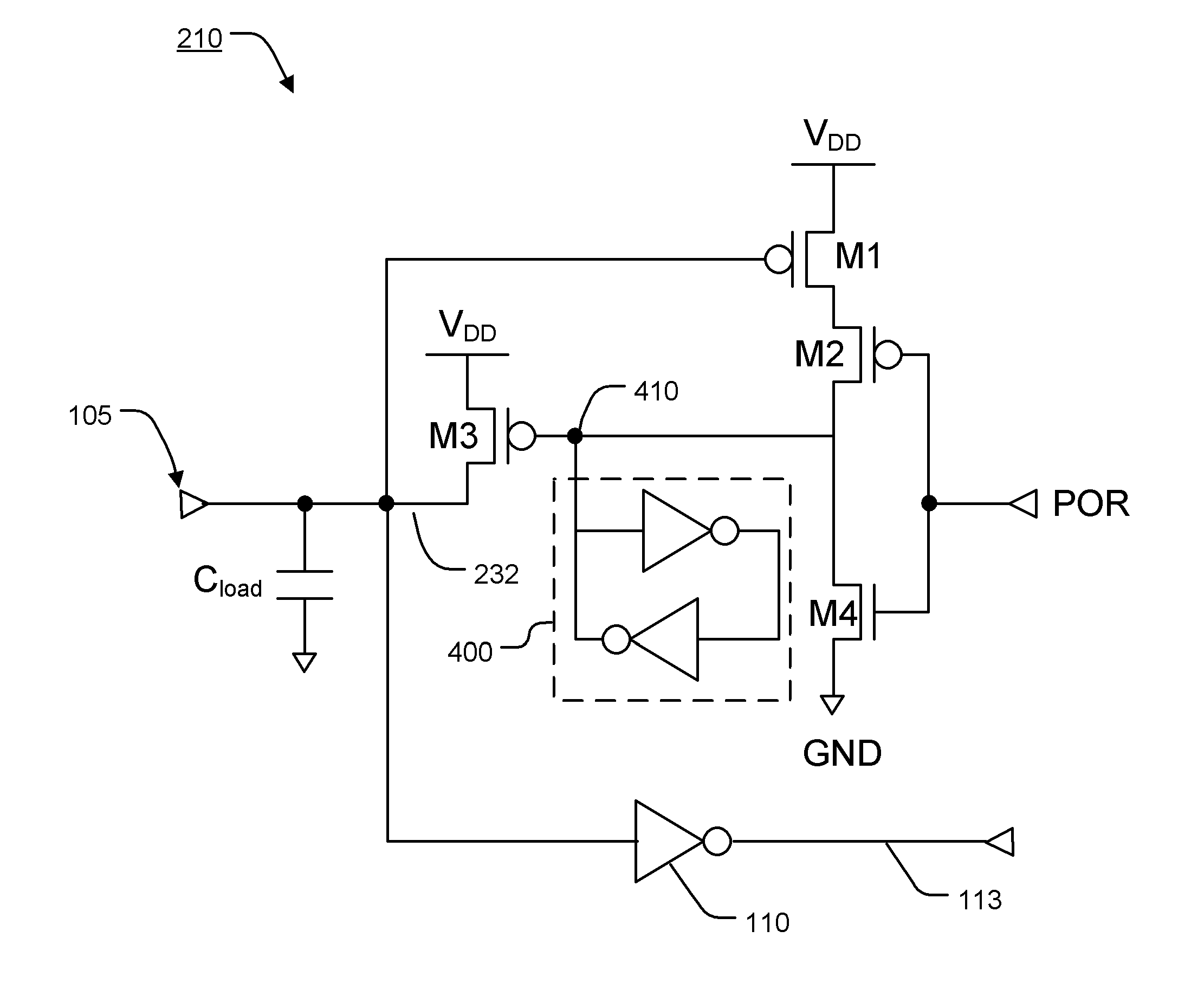

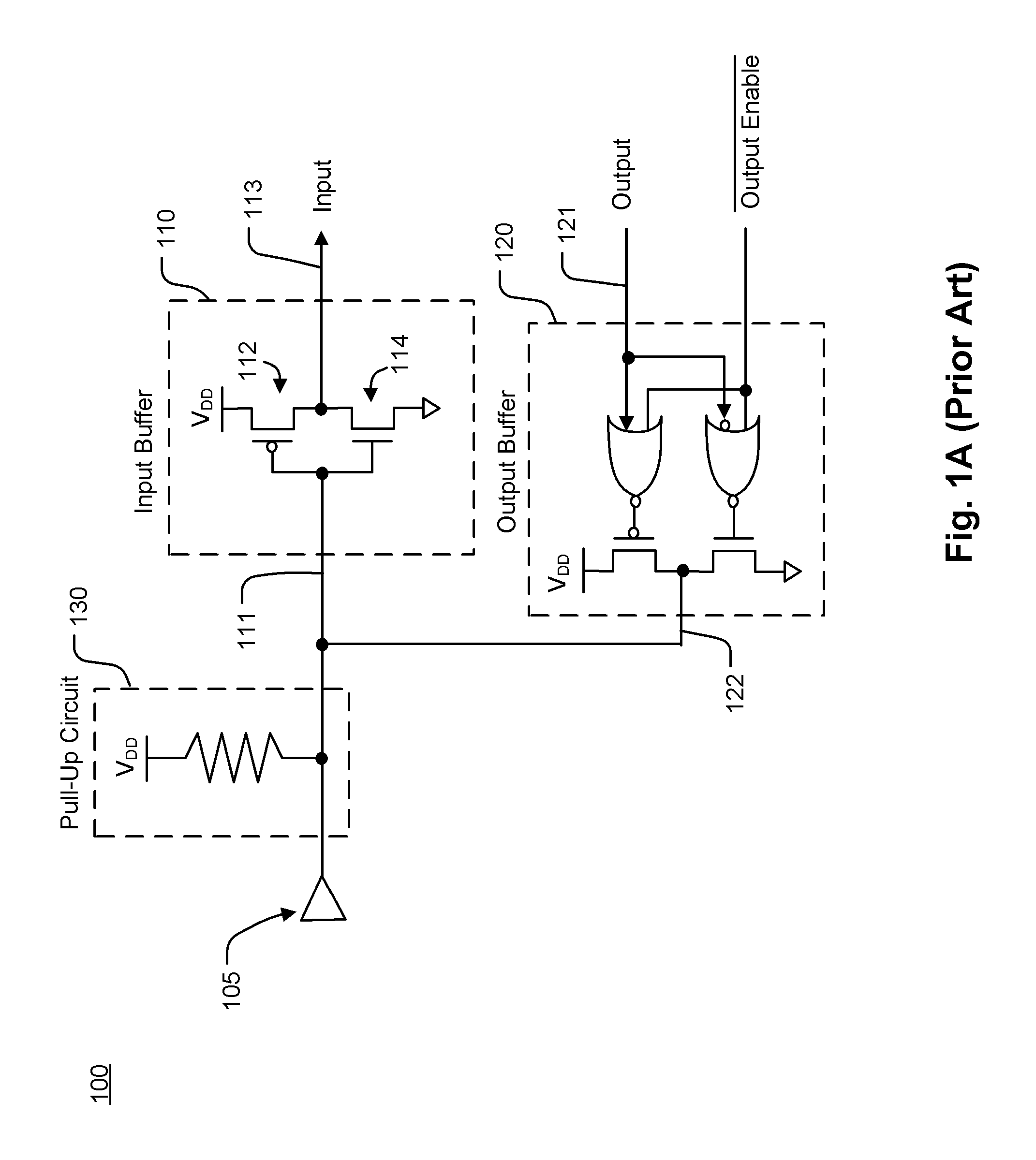

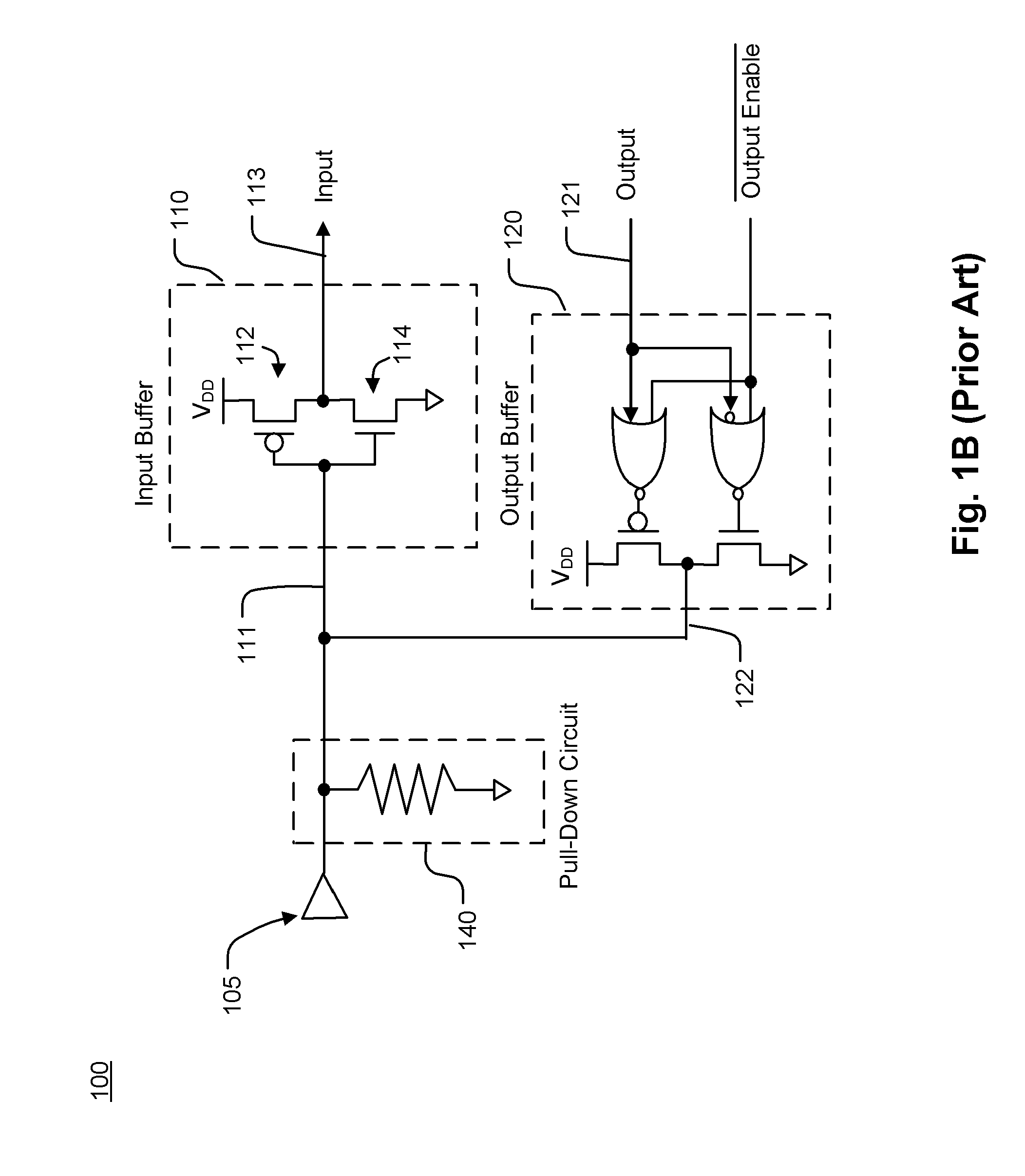

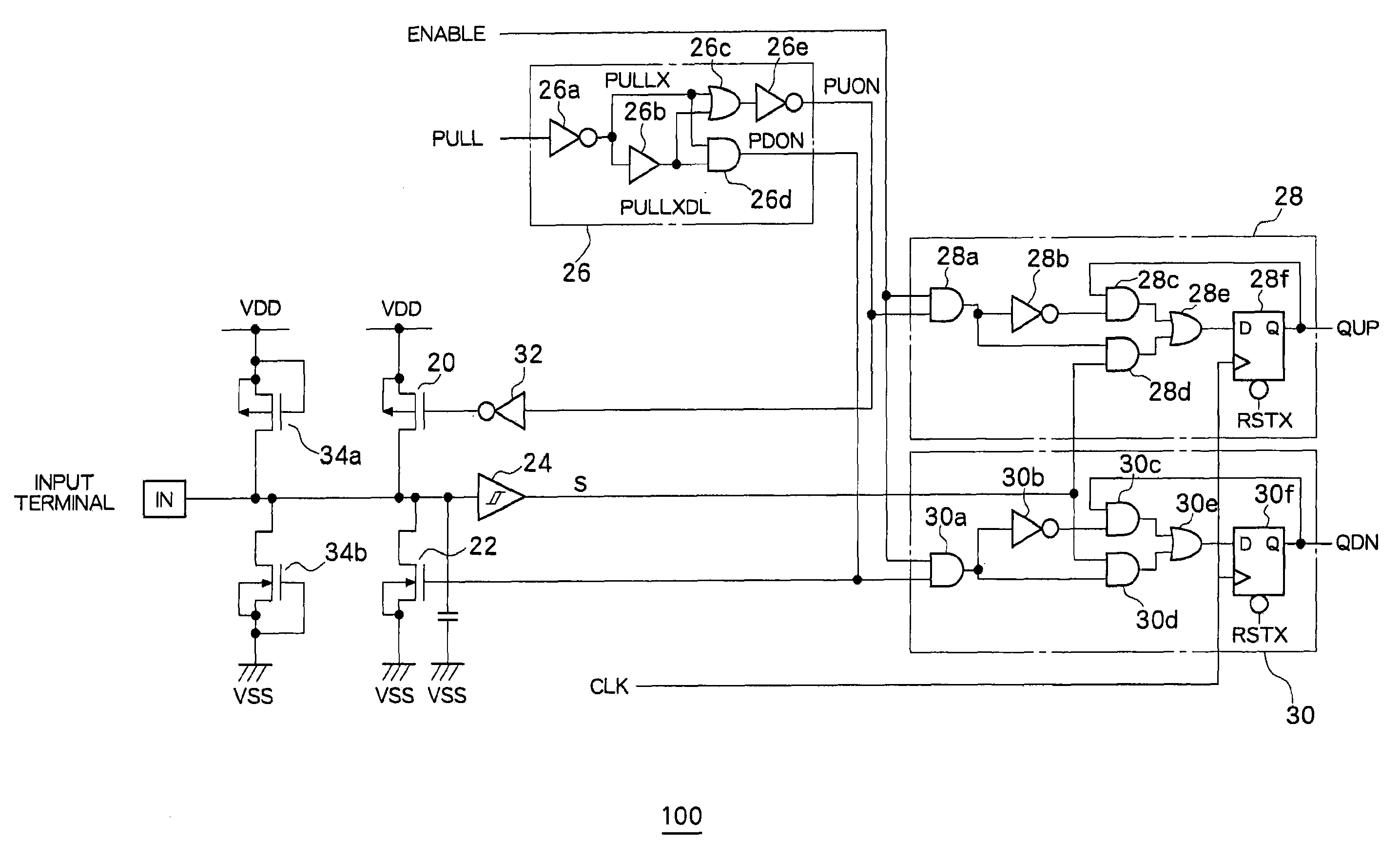

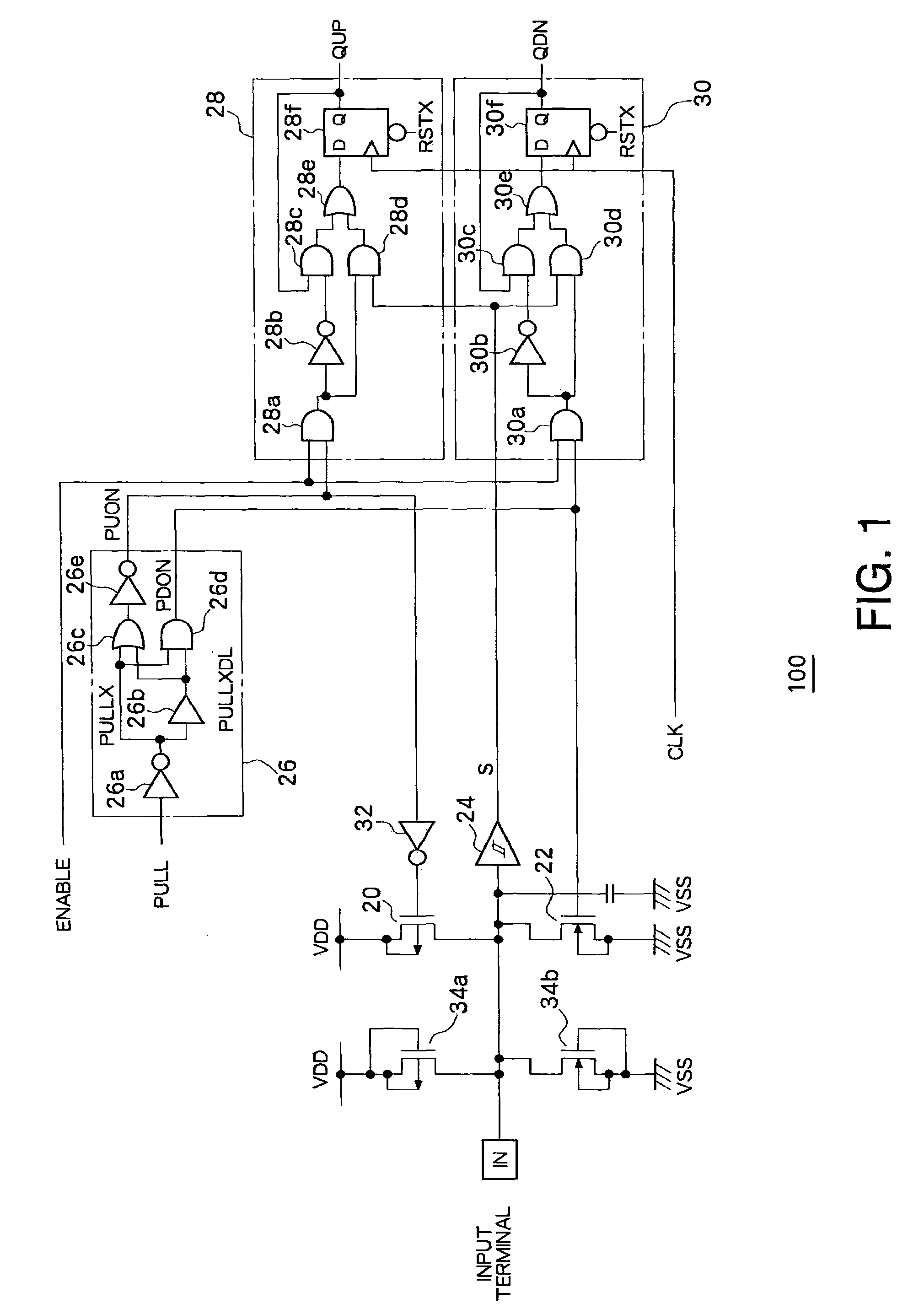

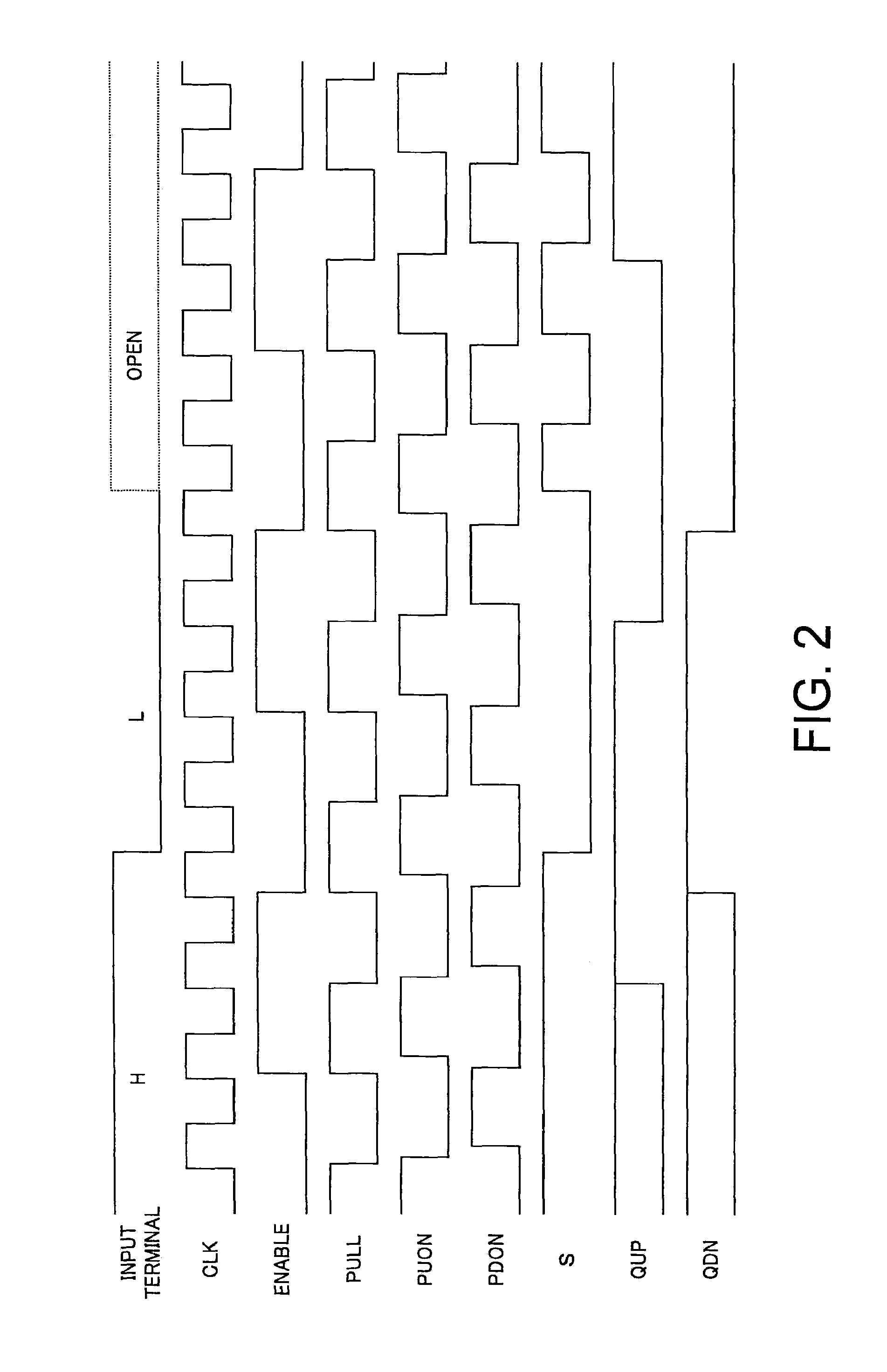

Apparatus and method to tolerate floating input pin for input buffer

ActiveUS8400190B2Prevent floatingKnowing statePulse automatic controlMultistate logicElectricityEngineering

An integrated circuit device includes a pad adapted to receive a signal from an internal or external driver, and an input buffer circuit including an input terminal coupled to the pad. The input buffer circuit includes a pass transistor having a control terminal, a first conduction terminal connected to the pad, and a second conduction terminal connected to a first voltage. The input buffer circuit also includes a latch having a terminal electrically coupled to the control terminal of the pass transistor. The input buffer circuit further includes circuitry coupled to the latch, the circuitry including a feedback transistor having a control terminal electrically coupled to the pad, a first conduction terminal electrically coupled to a second voltage, and a second conduction terminal coupled to the latch.

Owner:MACRONIX INT CO LTD

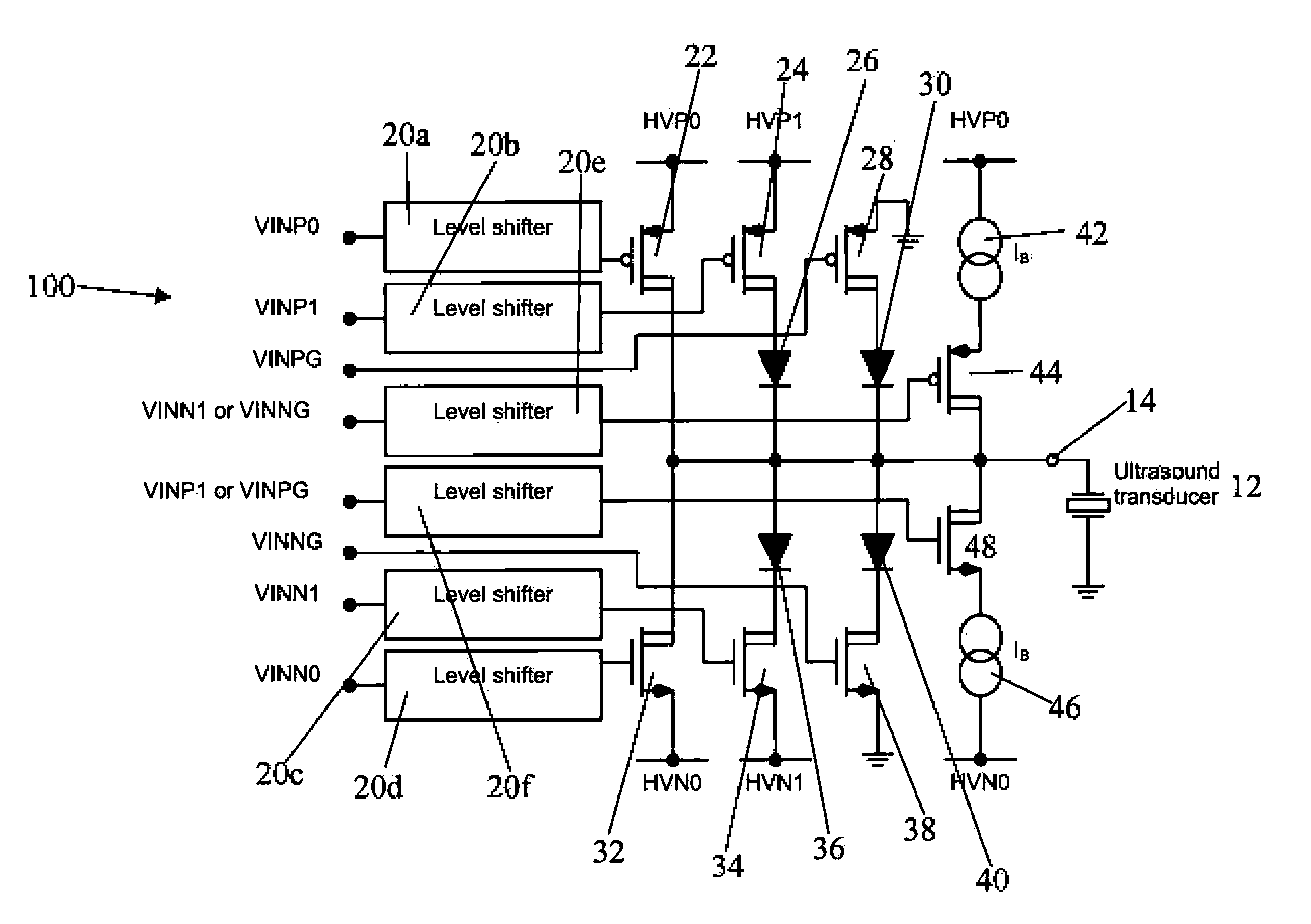

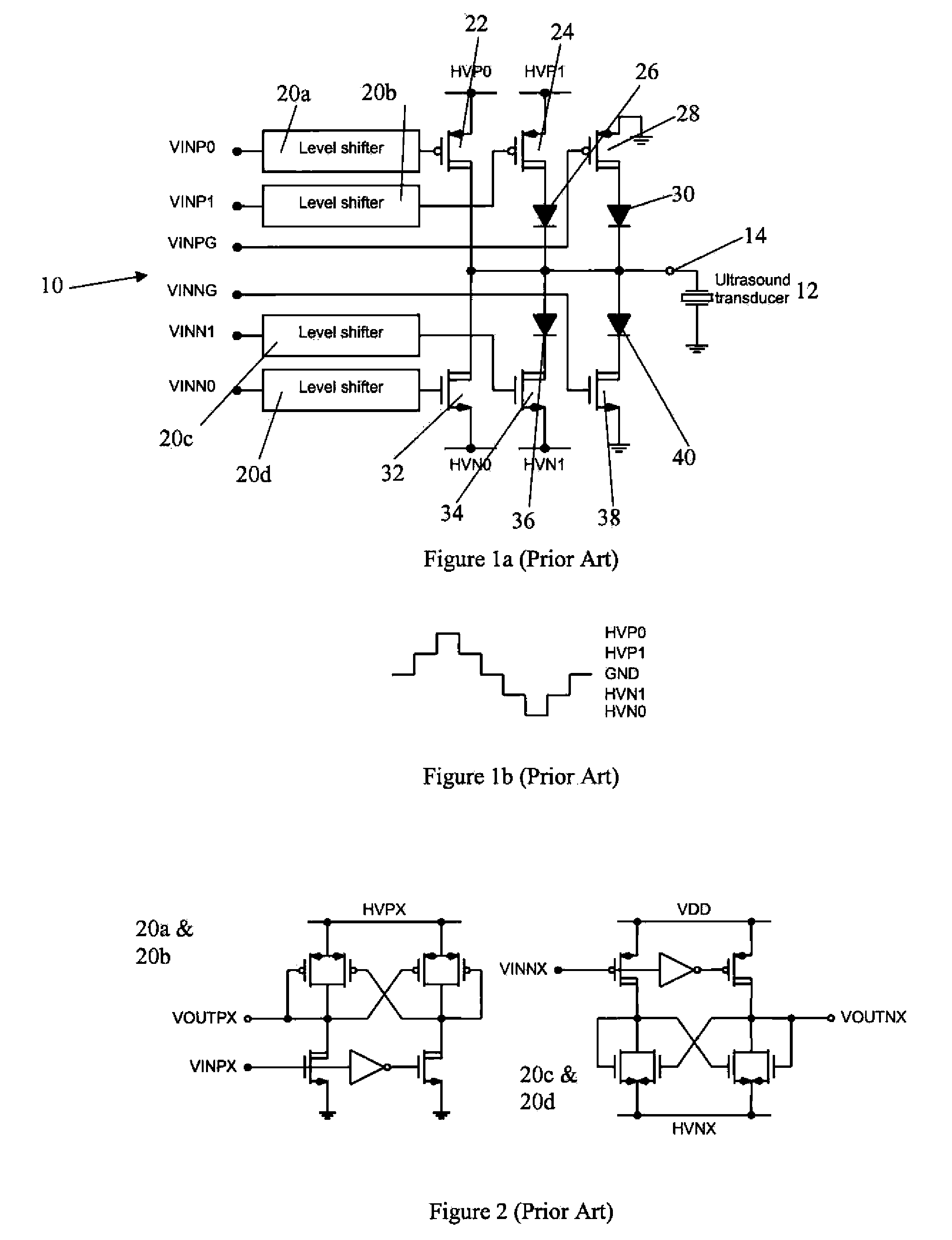

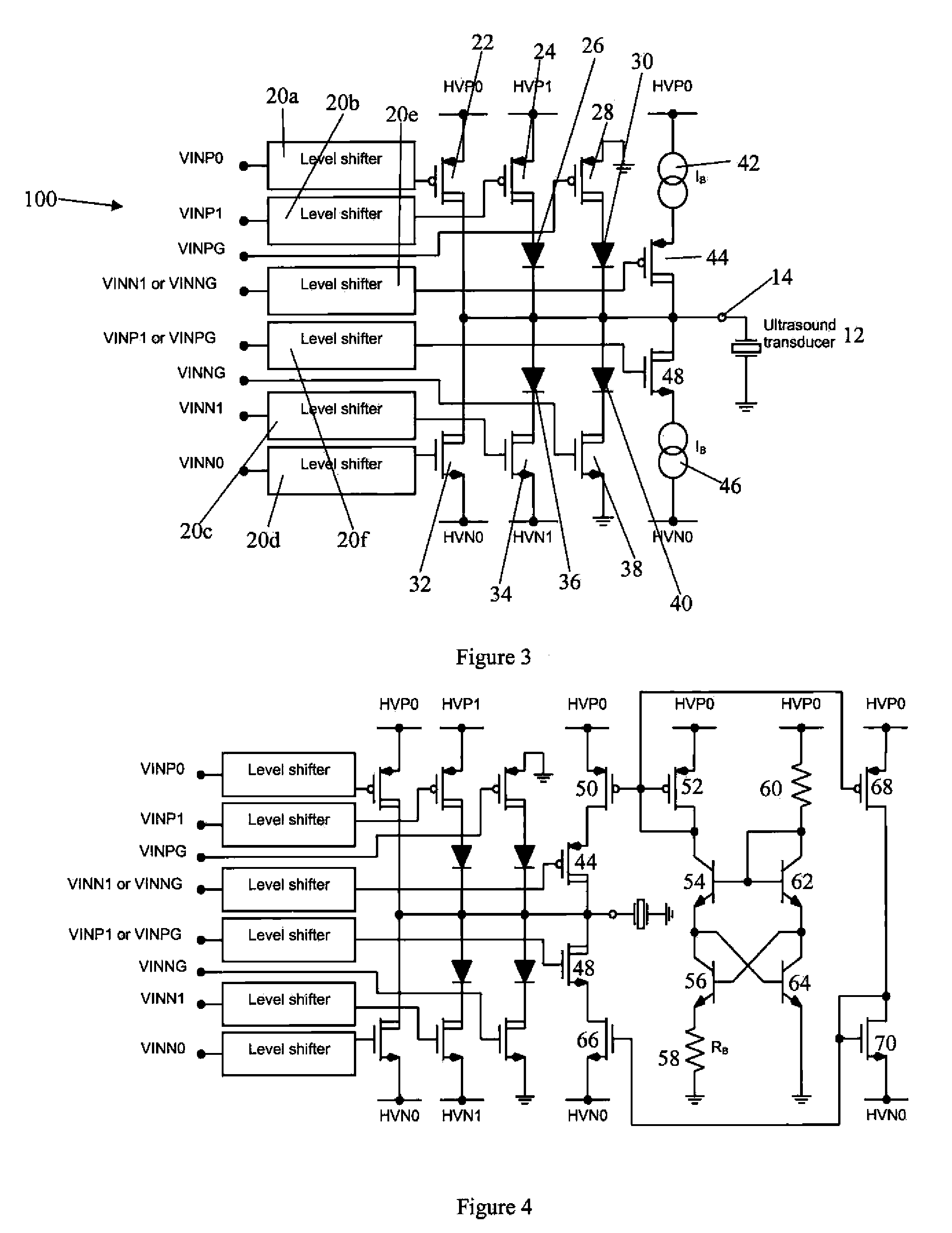

Multi-Level Transmitter Circuit Having Substantially Constant Impedance Output

A multi-level transmitter circuit with substantially constant output impedance has a capacitive transducer connected between a voltage input and ground. A first voltage path connects the voltage input to a first positive voltage source. The first voltage path is controlled by a first control signal. A second voltage path connects the voltage input to a second positive voltage source, less than the first positive voltage source. The second voltage path passes through a diode and is controlled by a second control signal. A third voltage path connects the voltage input to a third voltage source, less than ground, and is controlled by the second control signal. The impedance at the voltage input during the first control signal is substantially the same as the impedance at the voltage input during the second control signal.

Owner:MICROCHIP TECH INC

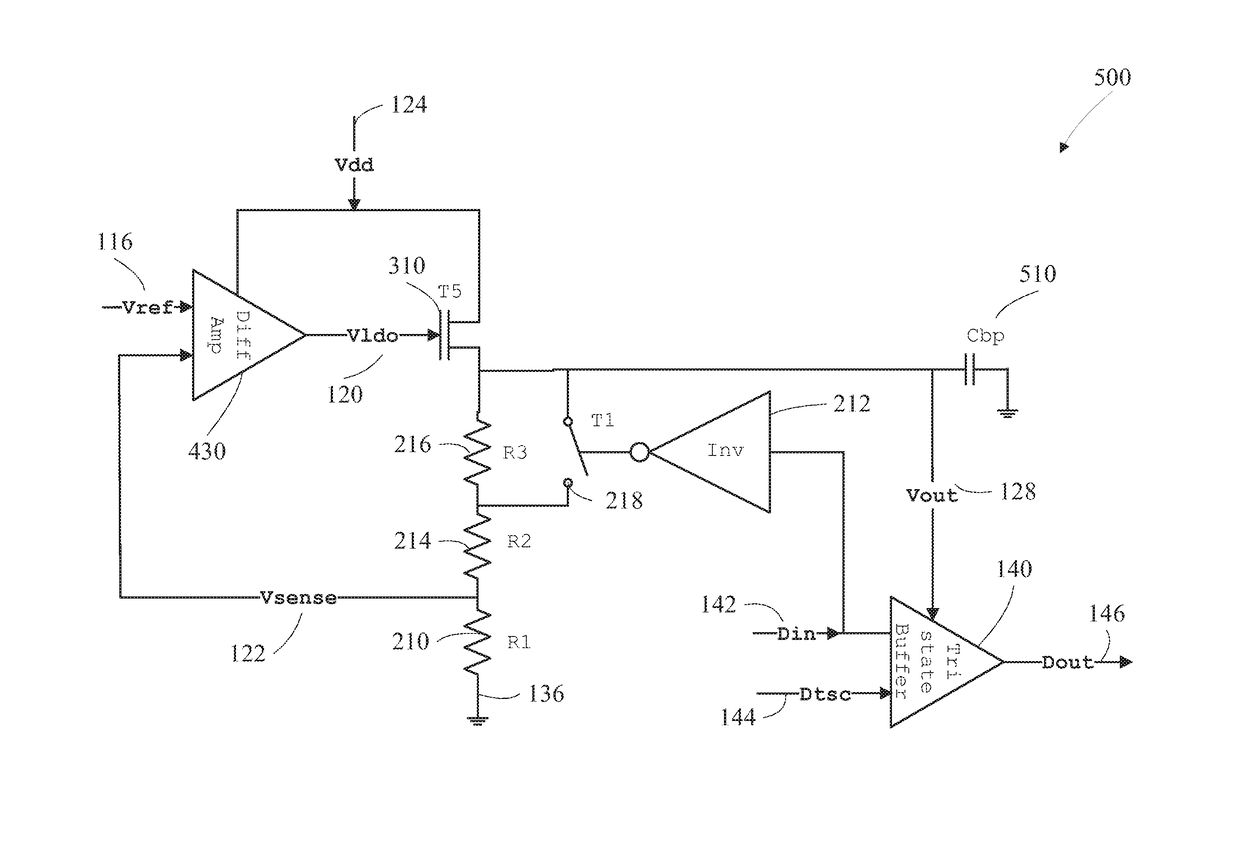

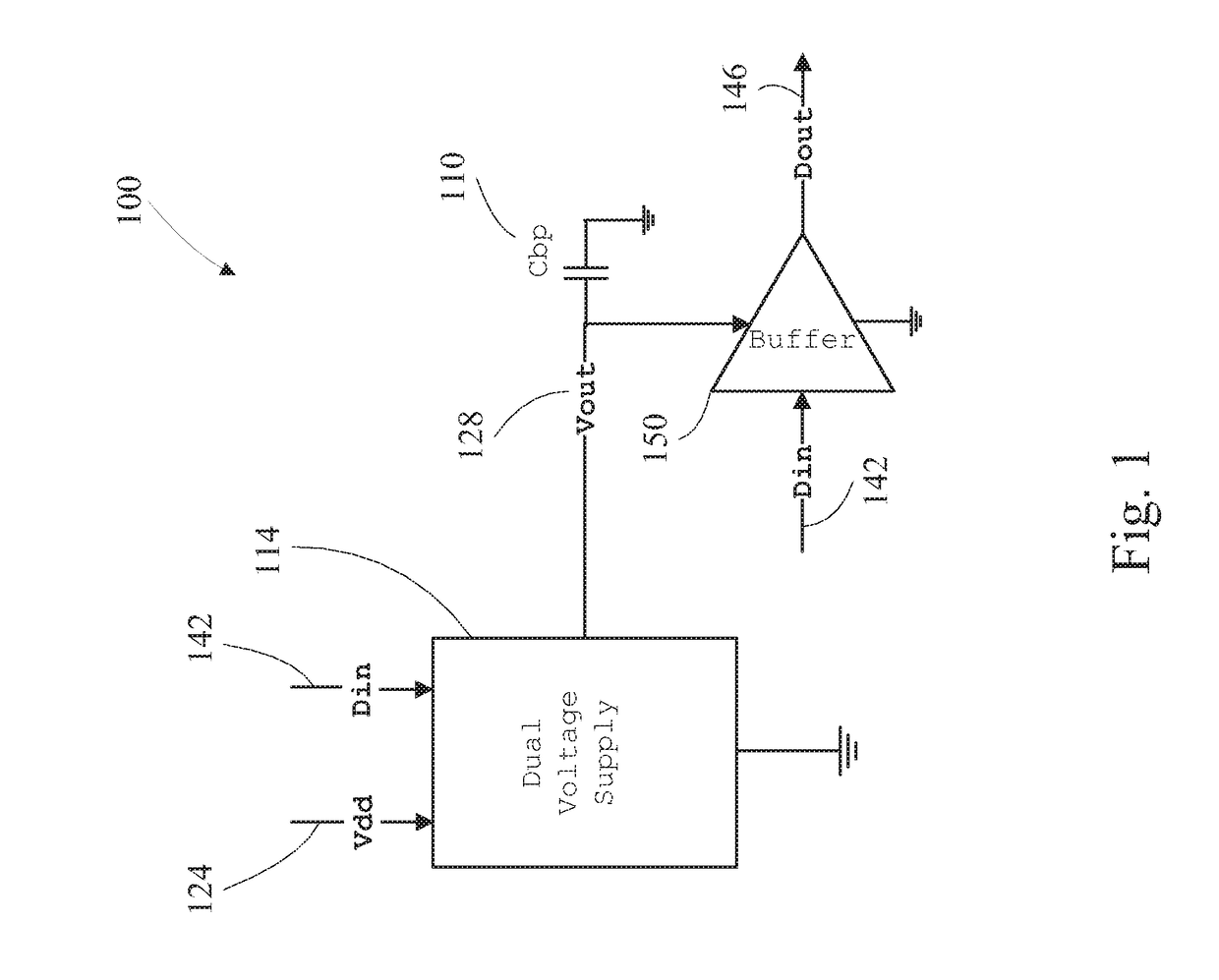

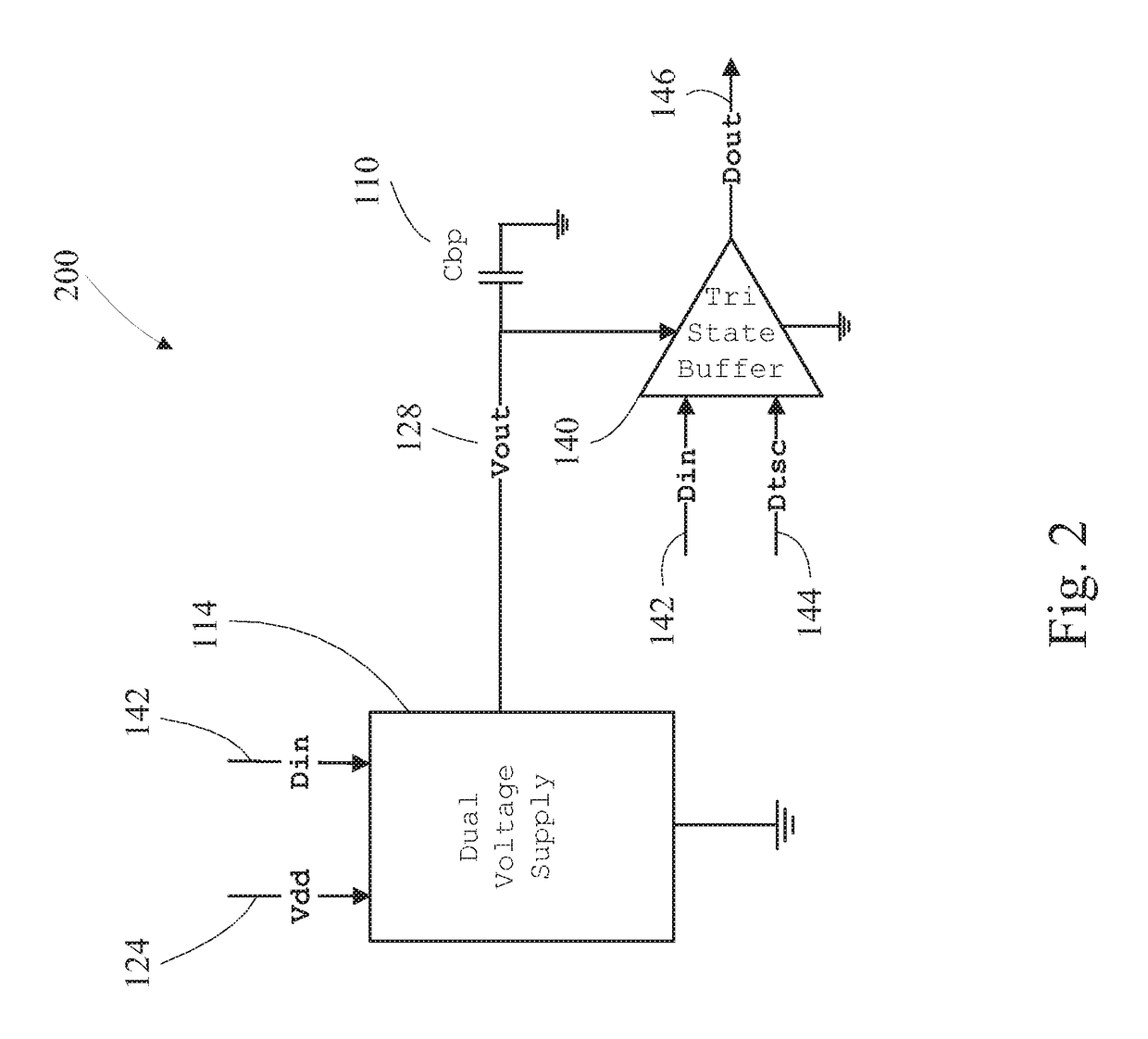

Dual voltage supply

Owner:PSEMI CORP

Quad state logic design methods, circuits, and systems

InactiveUS20050179462A1Reduce wiring densityReduced wiring interconnectsMultistate logicDigital storageHigh densityEngineering

Quad-state logic elements and quad-state memory elements are used to reduce the wiring density of integrated circuits. The resulting reduction in wiring interconnects between memories and logic elements results in higher speed, higher density, and lower power integrated circuit designs.

Owner:TEXAS INSTR INC

Semiconductor device

An object of the present invention is to realize an example of configuration that approximately represents a state of quantum spin in a semiconductor device where components as a basic configuration unit are arrayed so as to search a ground state of Ising model. There is disclosed a semiconductor device provided with plural units each of which is equipped with a first memory cell that stores a value which represents one spin of the Ising model by three or more states, a second memory cell that stores an interaction coefficient showing interaction from another spin which exerts interaction on the one spin and a logical circuit that determines the next state of the one spin on the basis of a function having a value which represents a state of the other spin and the interaction coefficient as a constant or a variable.

Owner:HITACHI LTD

Ternary valve input circuit

ActiveUS8013630B2Logic circuits characterised by logic functionMultistate logicElectrical and Electronics engineering

Owner:SEMICON COMPONENTS IND LLC

Popular searches

Electric pulse generator Semiconductor devices Logic circuits using elementary logic circuit components Securing communication Read-only memories CAD circuit design Special data processing applications Computation using denominational number representation Machine learning Logic circuit coupling/interface arrangements