Memristor simulator circuit based on digital potentiometer

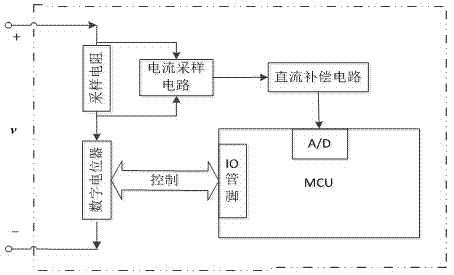

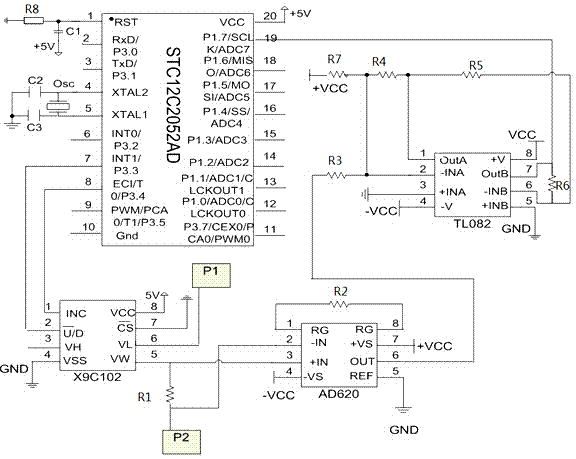

A technology of digital potentiometer and memristor, which is applied to digital memory information, logic circuits with multiple states, logic circuits, etc., can solve the problems of short memory time and difficulty in accurately simulating the non-missing memory characteristics of memristors. To achieve the effect of convenient debugging, simple structure and good simulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The present invention will be further described in detail below in conjunction with the accompanying drawings.

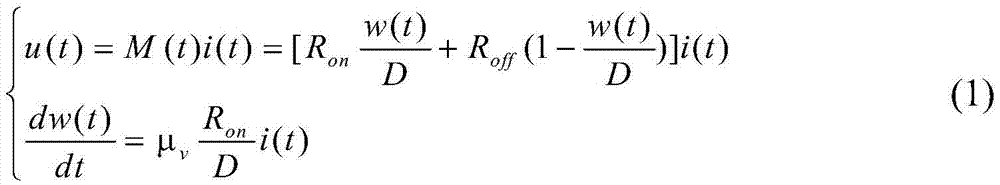

[0016] The basic characteristic equation of HP Labs TiO2 memristor is:

[0017] u ( t ) = M ( t ) i ( t ) = [ R o n w ( t ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com