Technical mapping control method, device and system based on rear-end requirements

A control method and technology, applied in the field of FPGA, can solve problems such as poor mapping results, difficulty in meeting mapping requirements, and inability to meet back-end requirements.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

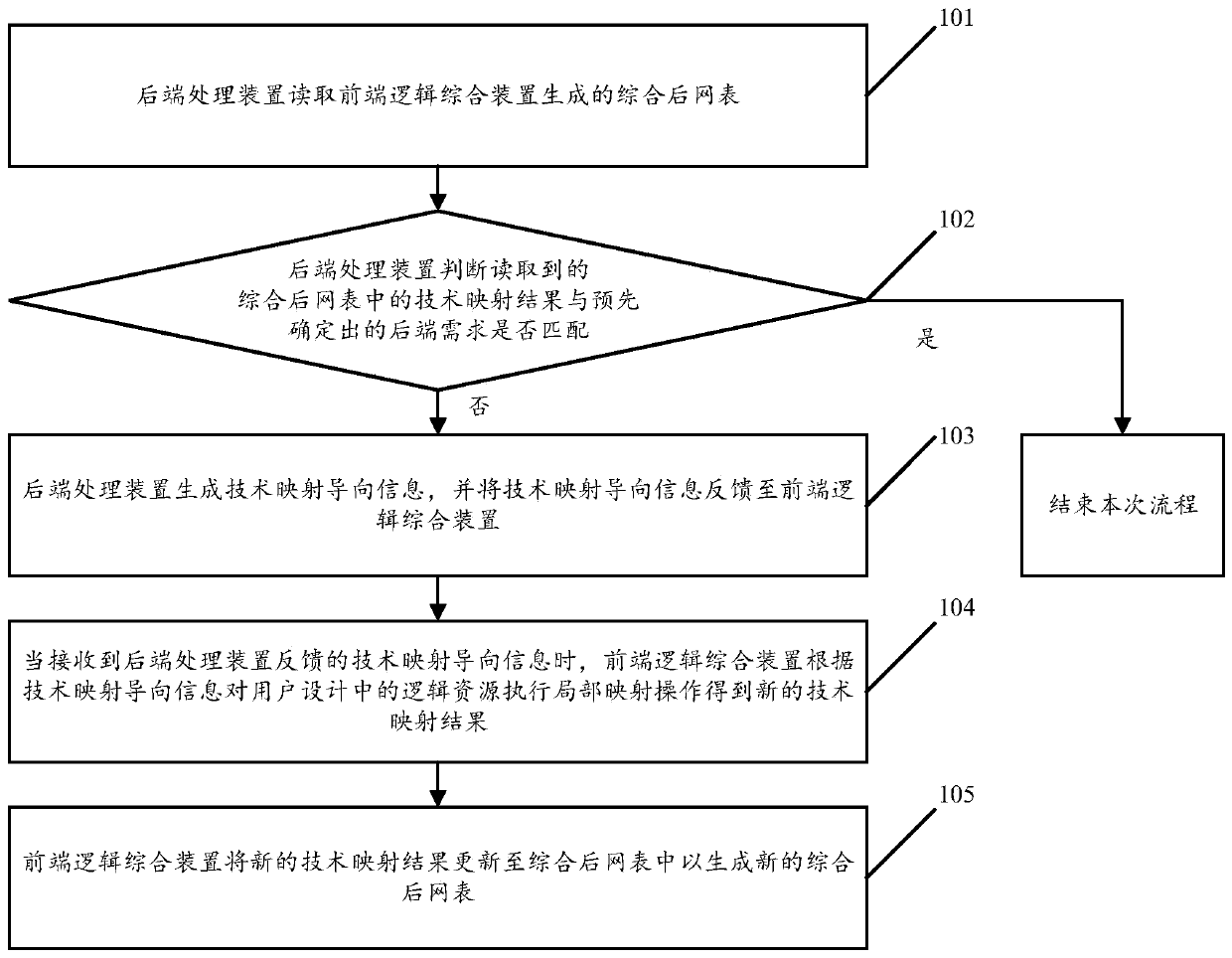

Image

Examples

Embodiment 2

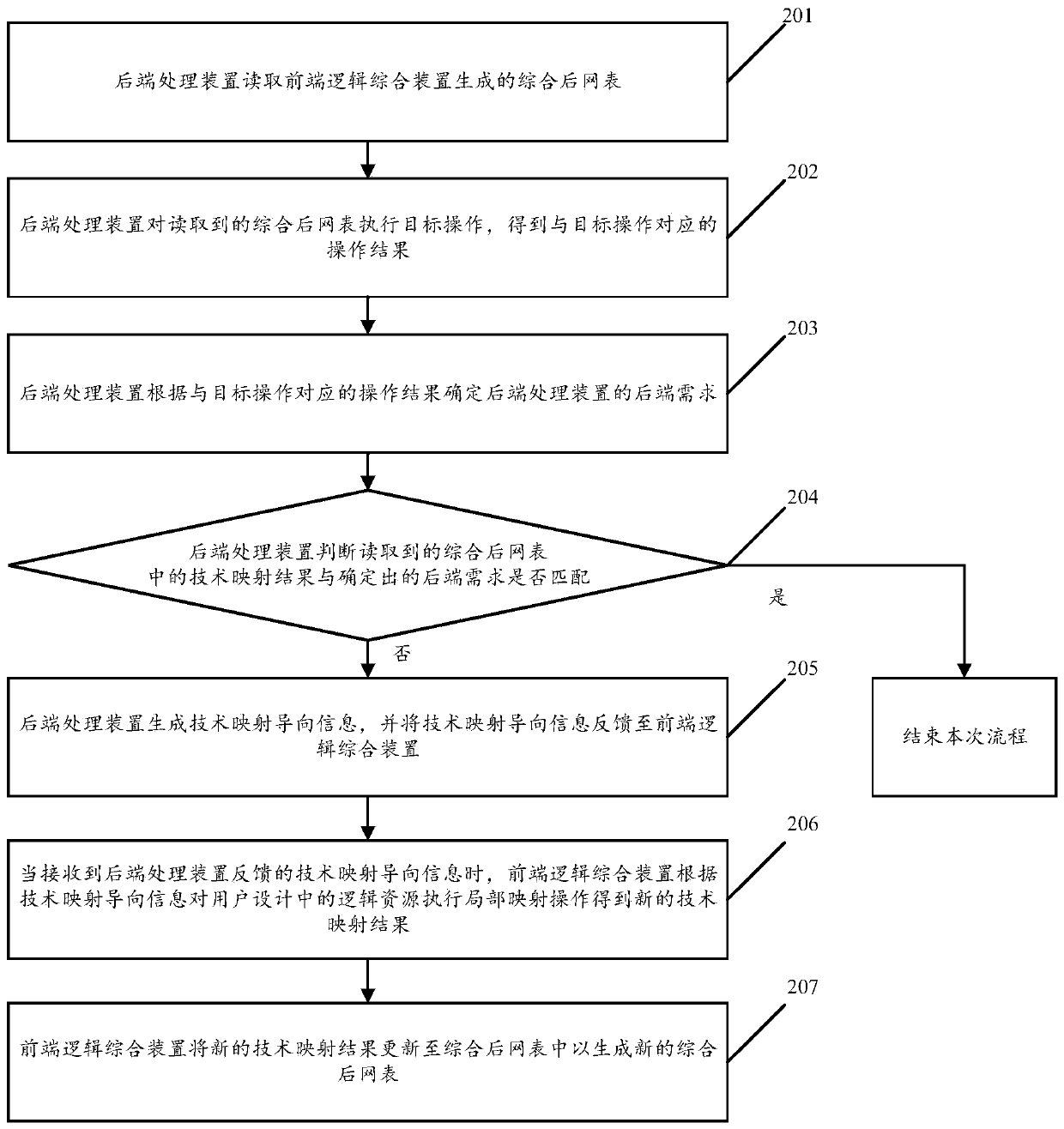

[0115] see figure 2 , figure 2 It is a schematic flowchart of another technology mapping control method based on back-end requirements disclosed in the embodiment of the present invention. in, figure 2 The described method can be applied in an EDA development tool, which at least includes a front-end logic synthesis device and a back-end processing device. Such as figure 2 As shown, the technology mapping control method based on back-end requirements may include the following operations:

[0116] 201. The back-end processing device reads the post-synthesis netlist generated by the front-end logic synthesis device.

[0117] 202. The back-end processing device executes a target operation on the read integrated netlist, and obtains an operation result corresponding to the target operation.

[0118] 203. The back-end processing device determines the back-end requirements of the back-end processing device according to the operation result corresponding to the target operat...

Embodiment 3

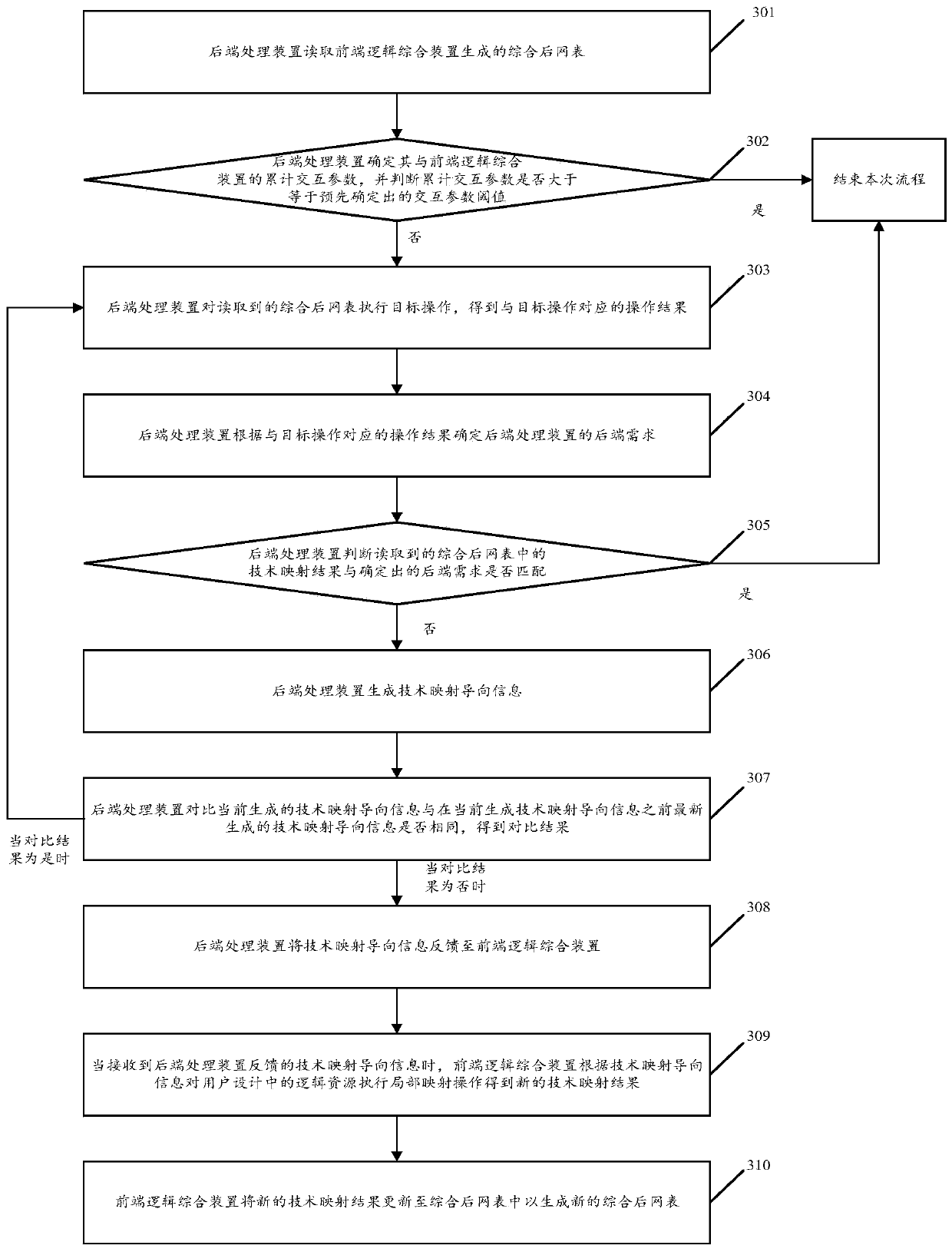

[0142] see image 3 , image 3 It is a schematic flowchart of another technology mapping control method based on back-end requirements disclosed in the embodiment of the present invention. in, image 3 The described method can be applied in an EDA development tool, which at least includes a front-end logic synthesis device and a back-end processing device. Such as image 3 As shown, the technology mapping control method based on back-end requirements may include the following operations:

[0143] 301. The back-end processing device reads the post-synthesis netlist generated by the front-end logic synthesis device.

[0144] 302. The back-end processing device determines the cumulative interaction parameters between itself and the front-end logic synthesis device, and judges whether the cumulative interaction parameters are greater than or equal to a predetermined interaction parameter threshold. When the judgment result in step 302 is yes, this process can be ended. When t...

Embodiment 4

[0162] The embodiment of the present invention discloses another technology mapping control method based on back-end requirements. The method is applied to the front-end logic synthesis device included in the EDA development tool. The method may include the following operations:

[0163] The front-end logic synthesis device generates a synthesized netlist, wherein the synthesized netlist generated by the front-end logic synthesis device is used to provide the back-end processing device to trigger the back-end processing device to judge the technology mapping in the read synthesized netlist Whether the result matches the pre-determined back-end requirements, and when a mismatch is judged, generate technology mapping guidance information and feed it back to the front-end logic synthesis device;

[0164] The front-end logic synthesis device detects whether the technology mapping guidance information fed back by the back-end processing device is received; when the detection result ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More