Technology mapping method by utilizing carry chain

A carry chain and carry output technology, applied in the field of process mapping using carry chain, can solve problems such as long delay and multiple logic resources, and achieve the effect of reducing delay and saving logic resources.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

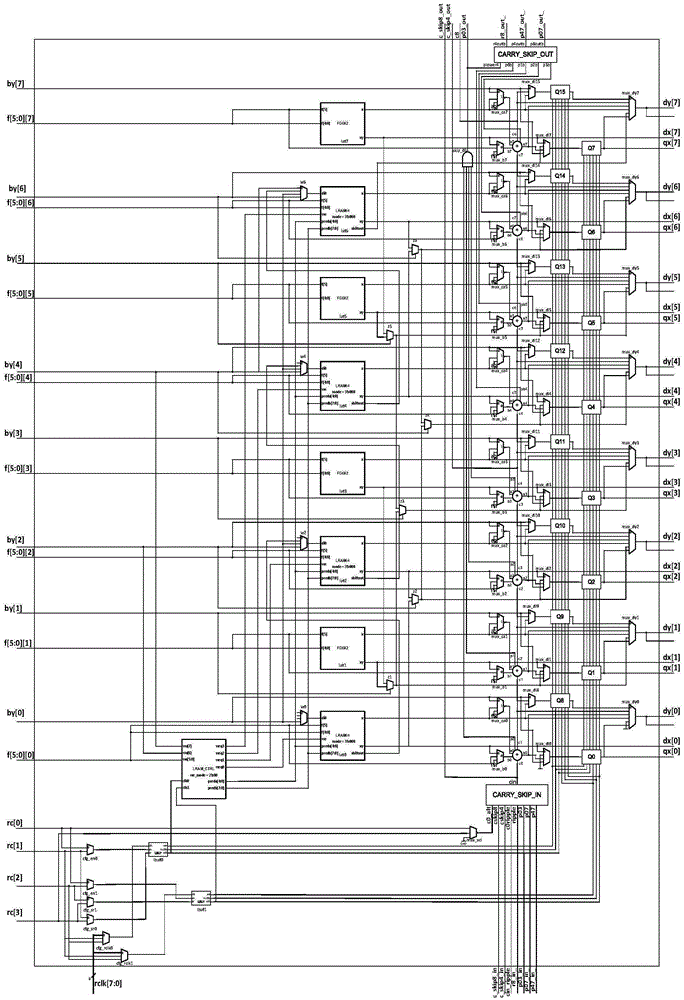

[0027] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is a part of embodiments of the present invention, but not all embodiments.

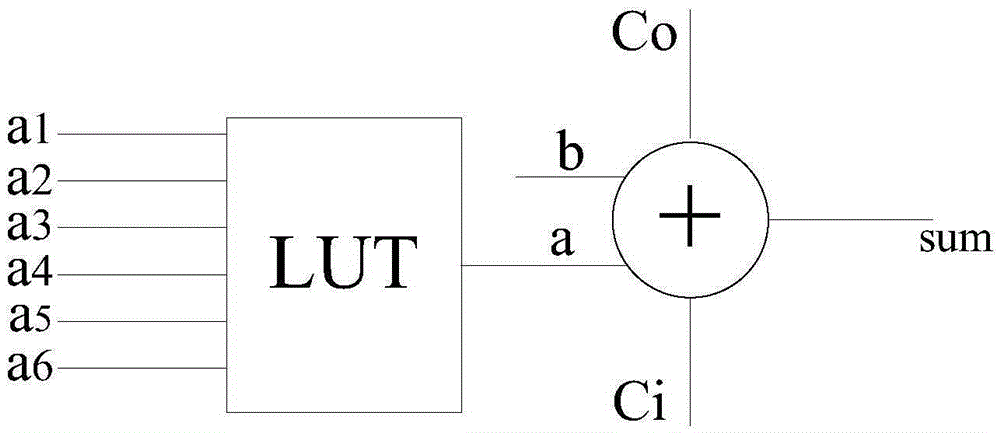

[0028] The invention provides a process mapping method using carry chains. The present invention realizes the process mapping of longer-width AND-OR logic by using a process mapping method combining a look-up table and an adder, which can save chip logic resources and greatly reduce the delay in realizing the logic.

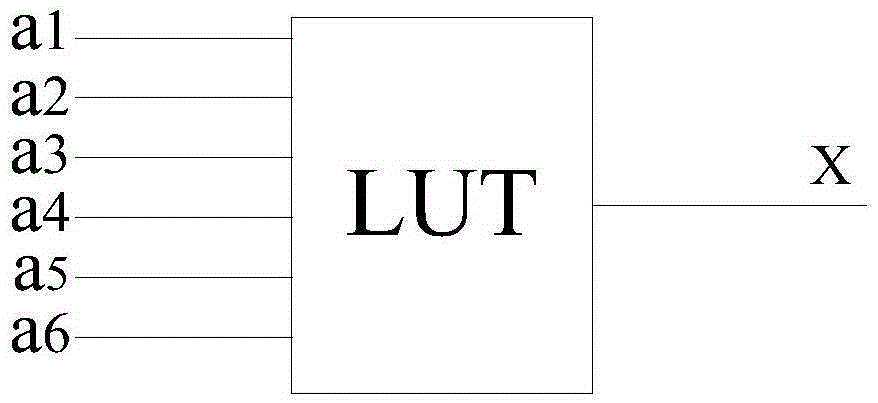

[0029] The methods in the following embodiments of the present invention are realized based on the CME-C1 series FPGA devices. To better understand the technical solutions provided by the embodiments of the present invention, the archi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More