Patents

Literature

91 results about "High-level synthesis" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

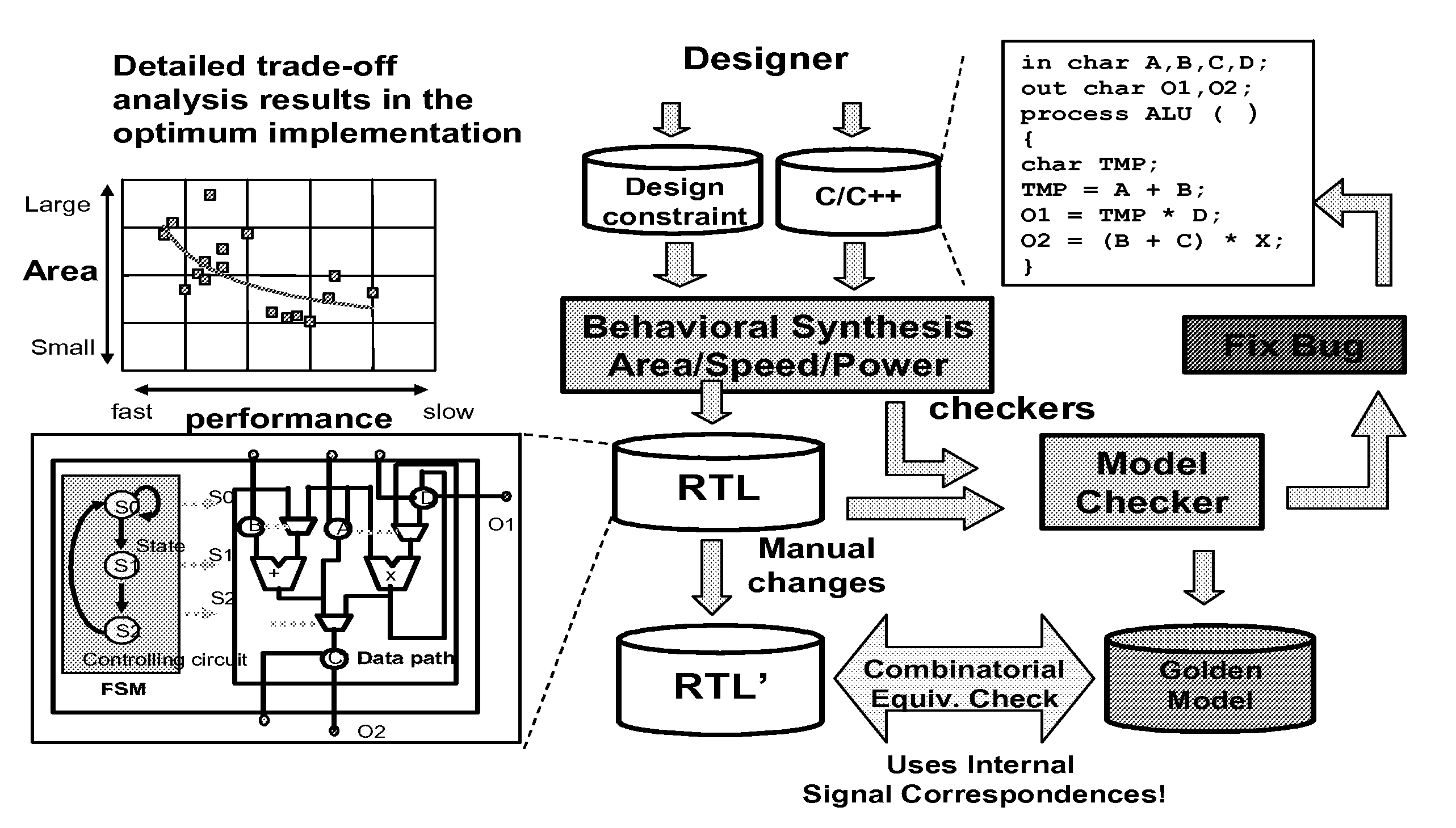

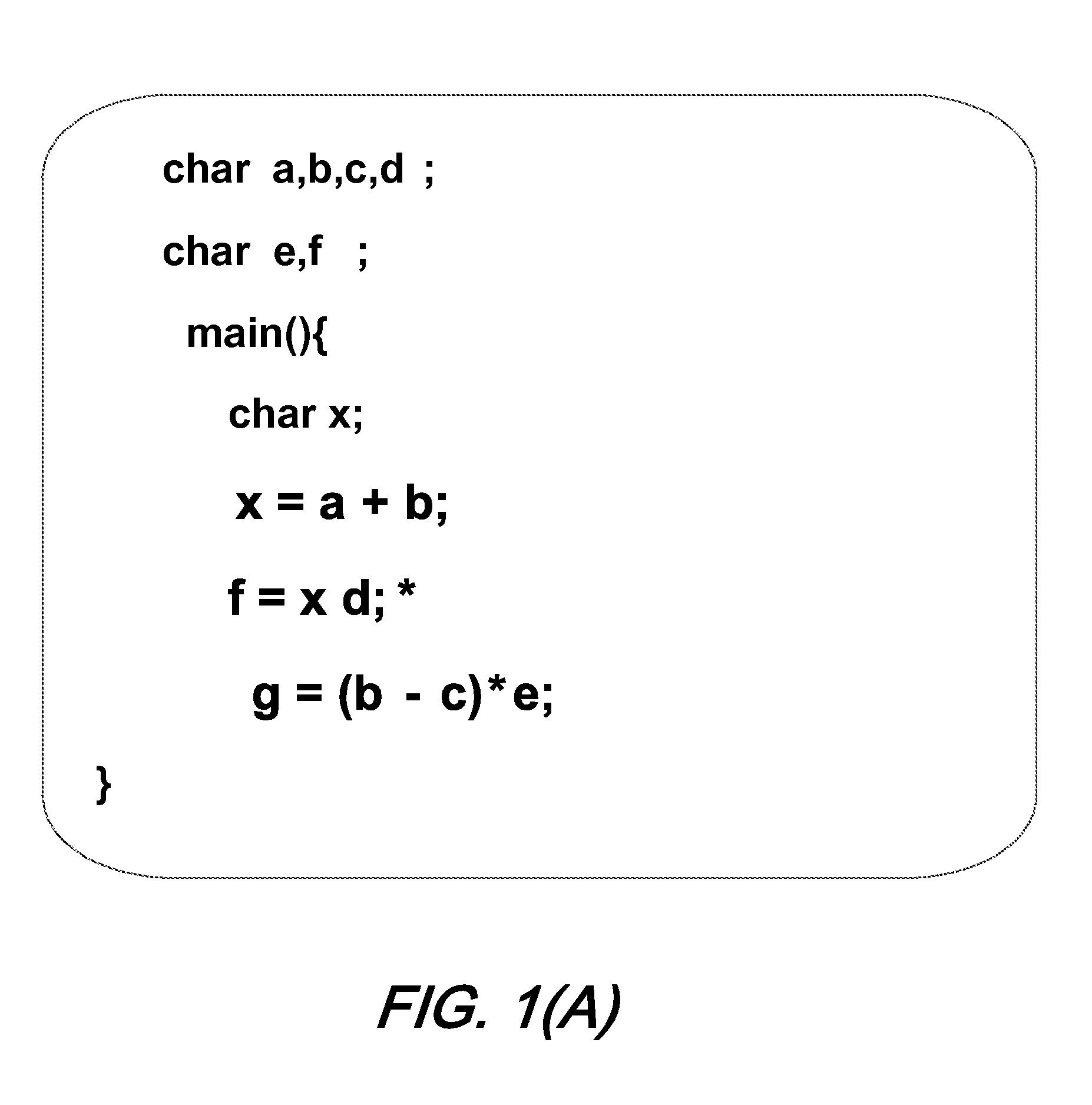

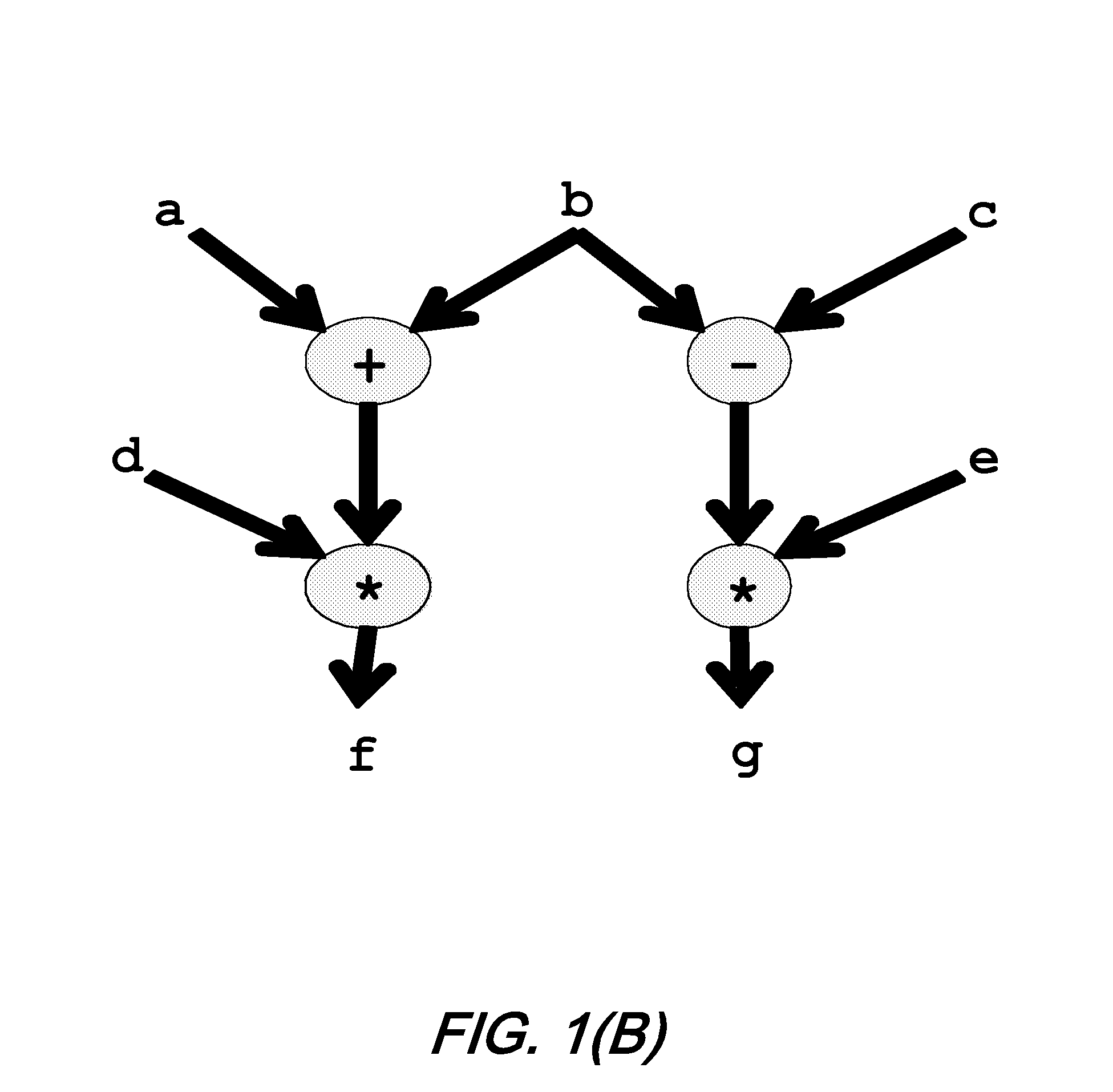

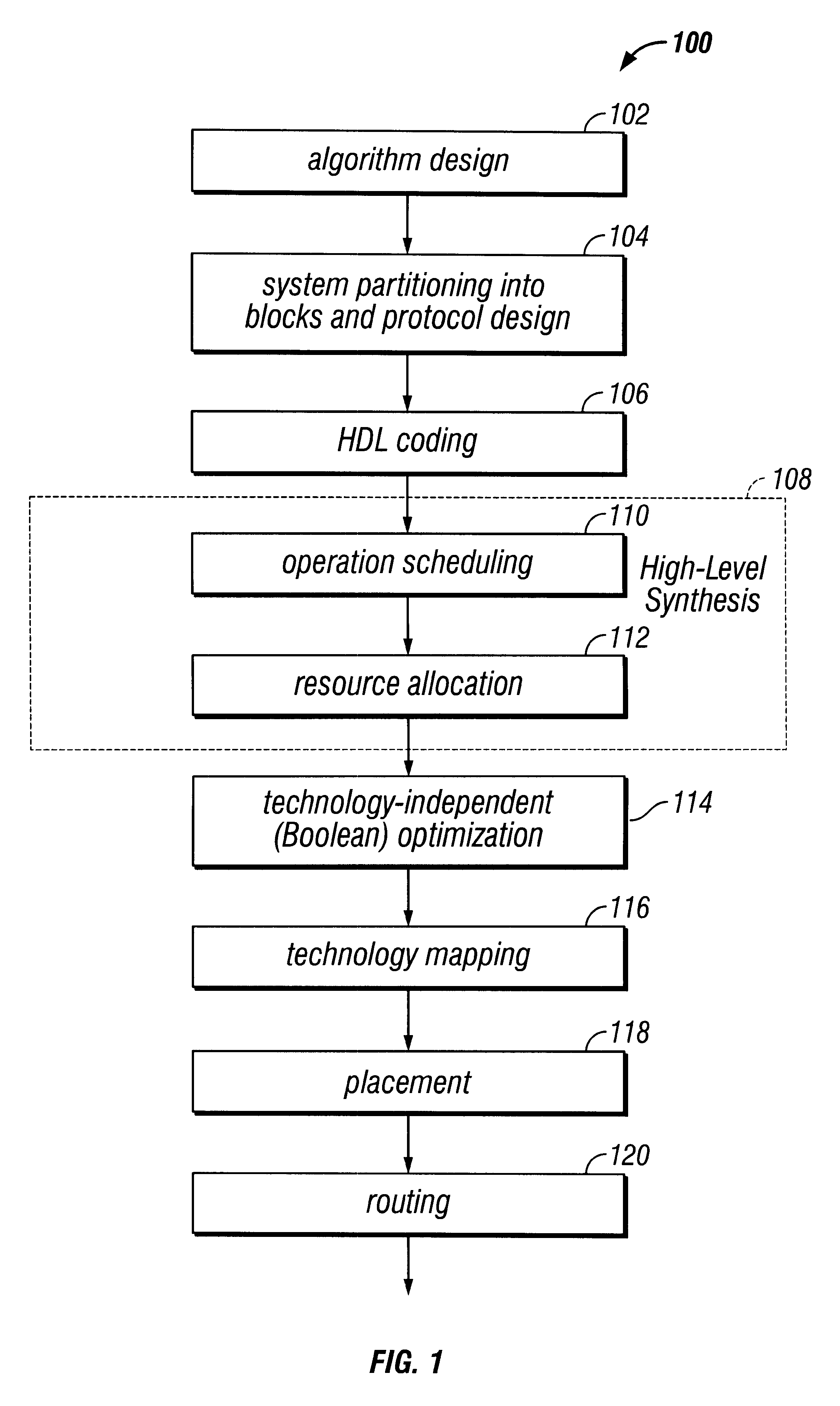

High-level synthesis (HLS), sometimes referred to as C synthesis, electronic system-level (ESL) synthesis, algorithmic synthesis, or behavioral synthesis, is an automated design process that interprets an algorithmic description of a desired behavior and creates digital hardware that implements that behavior. Synthesis begins with a high-level specification of the problem, where behavior is generally decoupled from e.g. clock-level timing. Early HLS explored a variety of input specification languages., although recent research and commercial applications generally accept synthesizable subsets of ANSI C/C++/SystemC/MATLAB. The code is analyzed, architecturally constrained, and scheduled to transcompile into a register-transfer level (RTL) design in a hardware description language (HDL), which is in turn commonly synthesized to the gate level by the use of a logic synthesis tool. The goal of HLS is to let hardware designers efficiently build and verify hardware, by giving them better control over optimization of their design architecture, and through the nature of allowing the designer to describe the design at a higher level of abstraction while the tool does the RTL implementation. Verification of the RTL is an important part of the process.

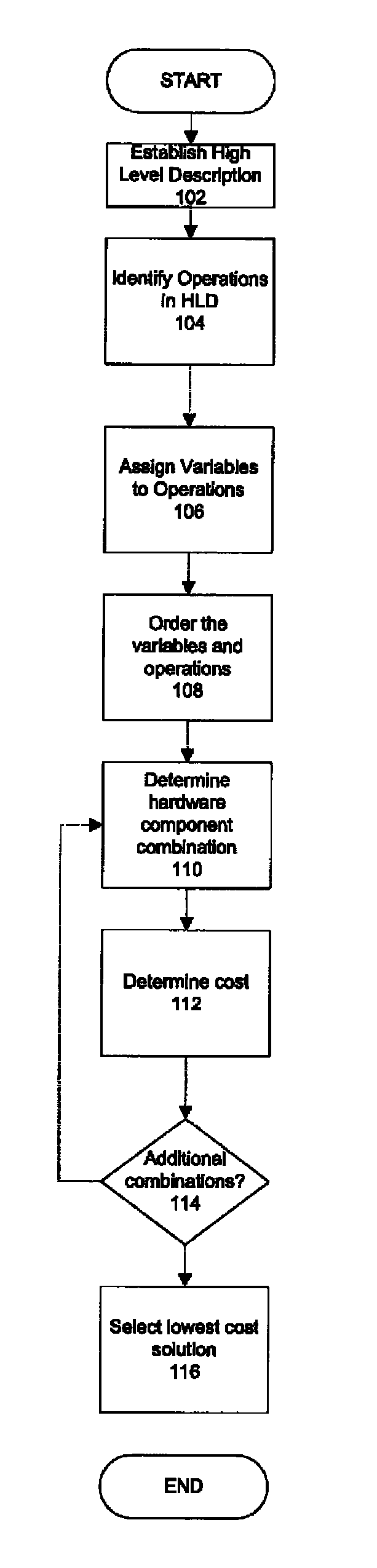

Method and apparatus for designing circuits using high-level synthesis

InactiveUS20050193359A1CAD circuit designSpecial data processing applicationsComputer architectureThird phase

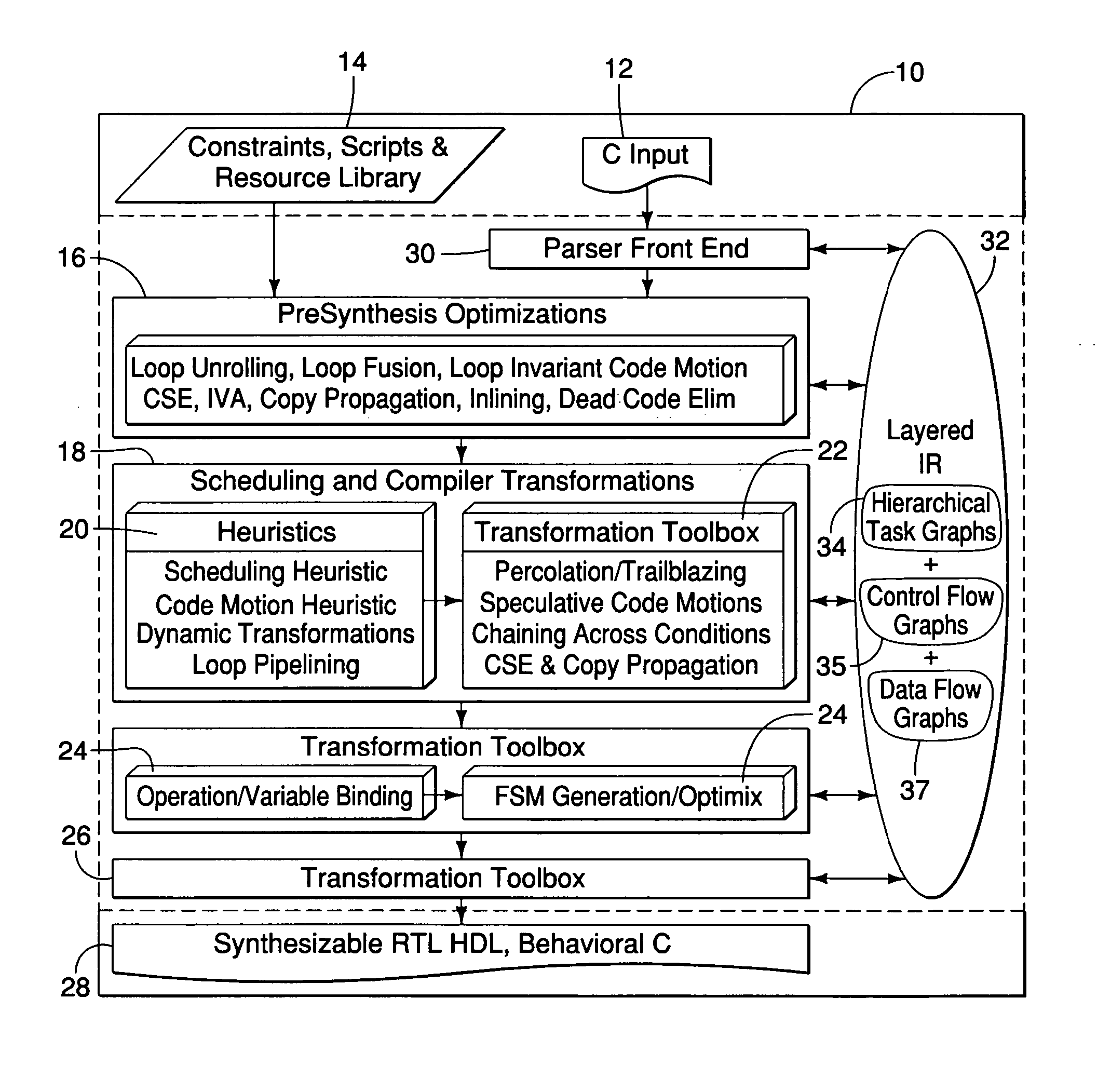

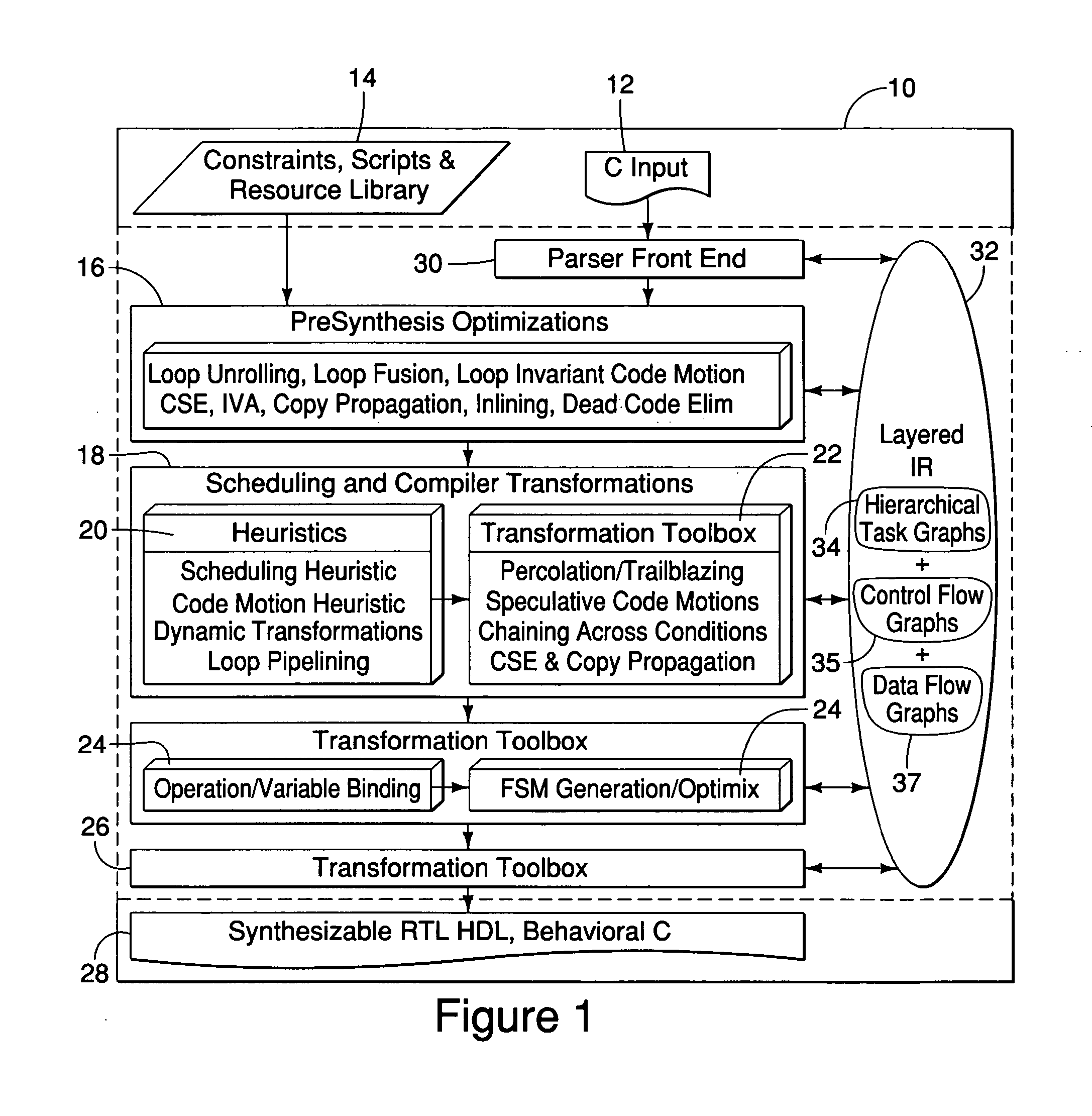

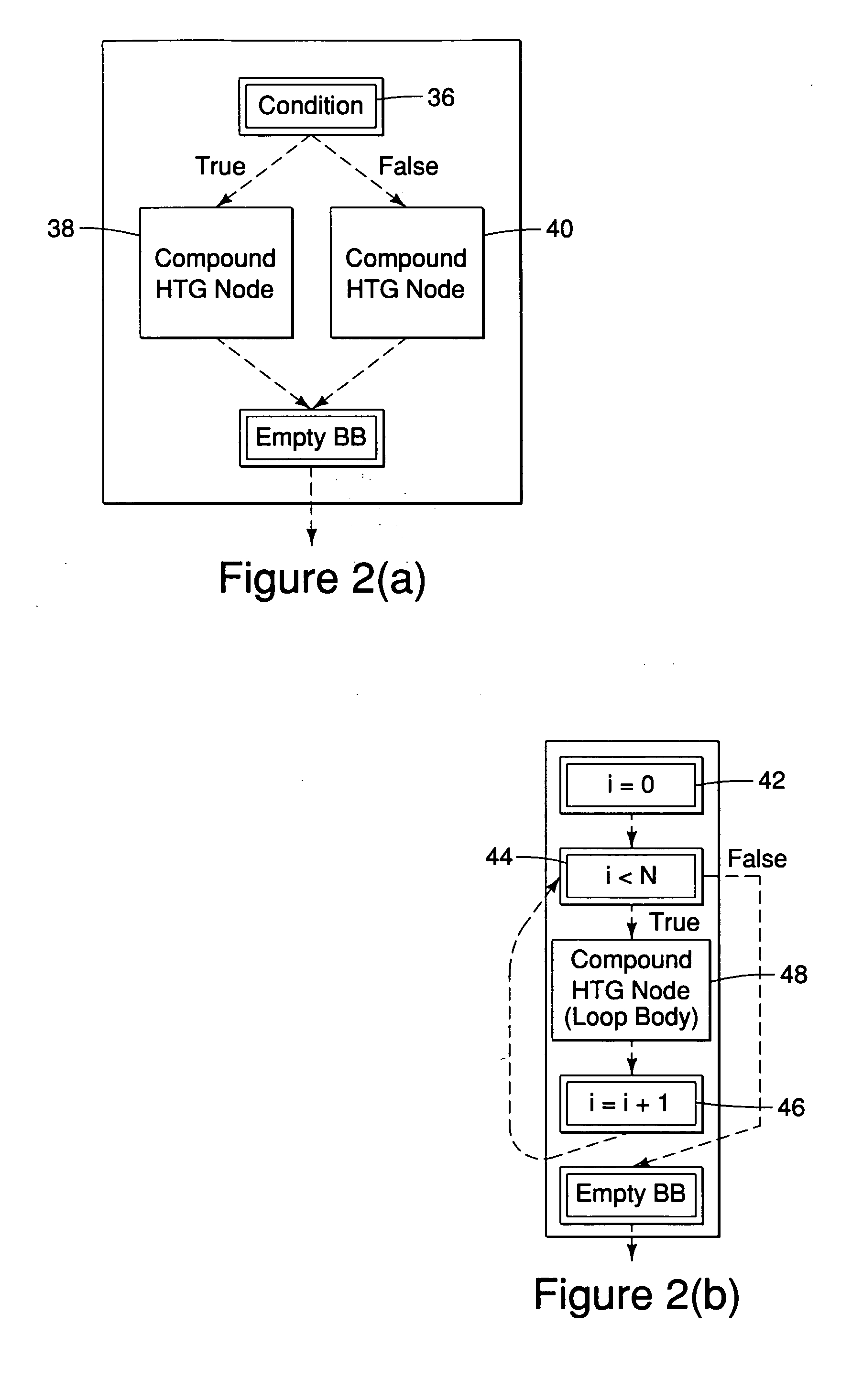

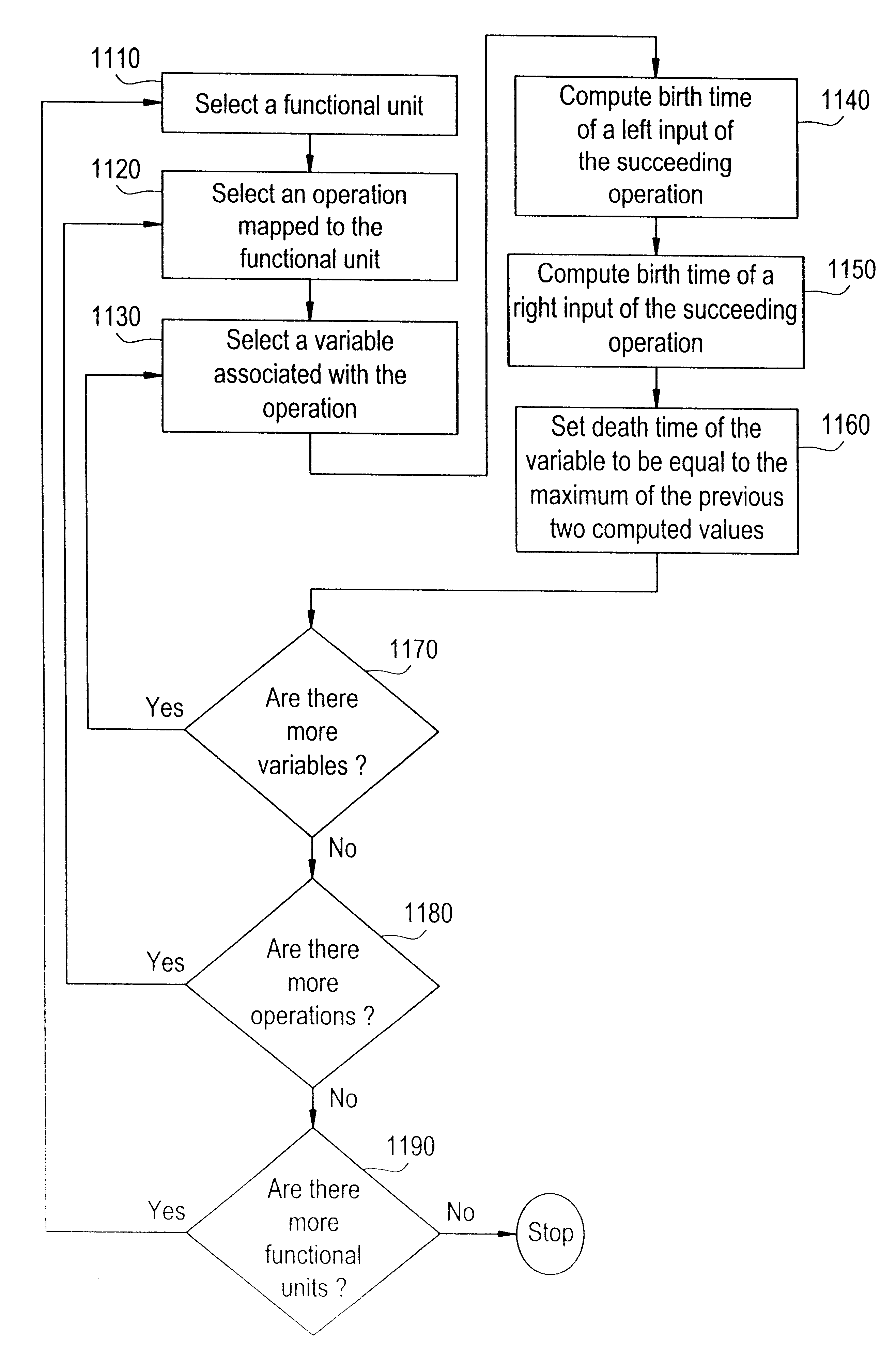

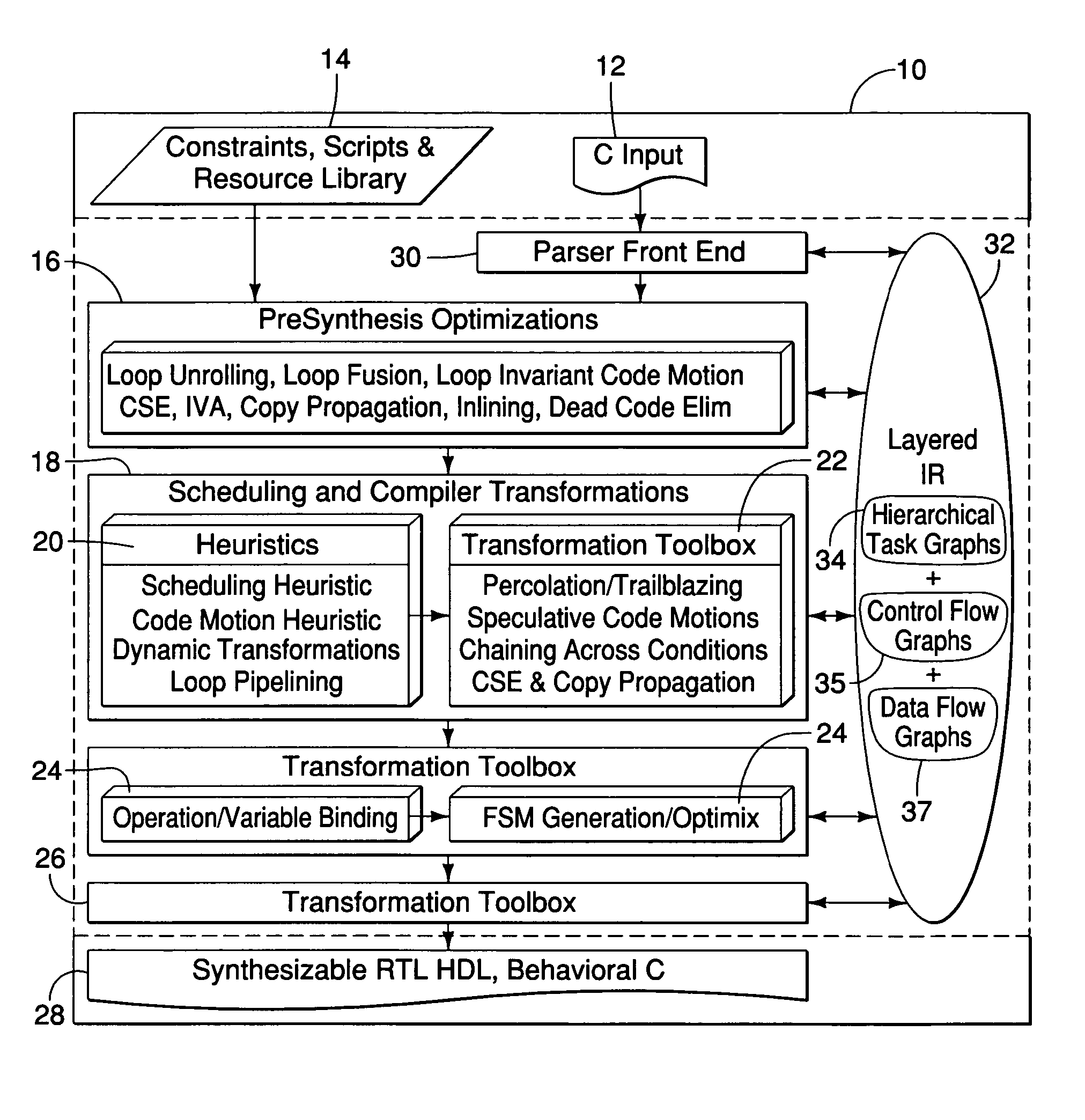

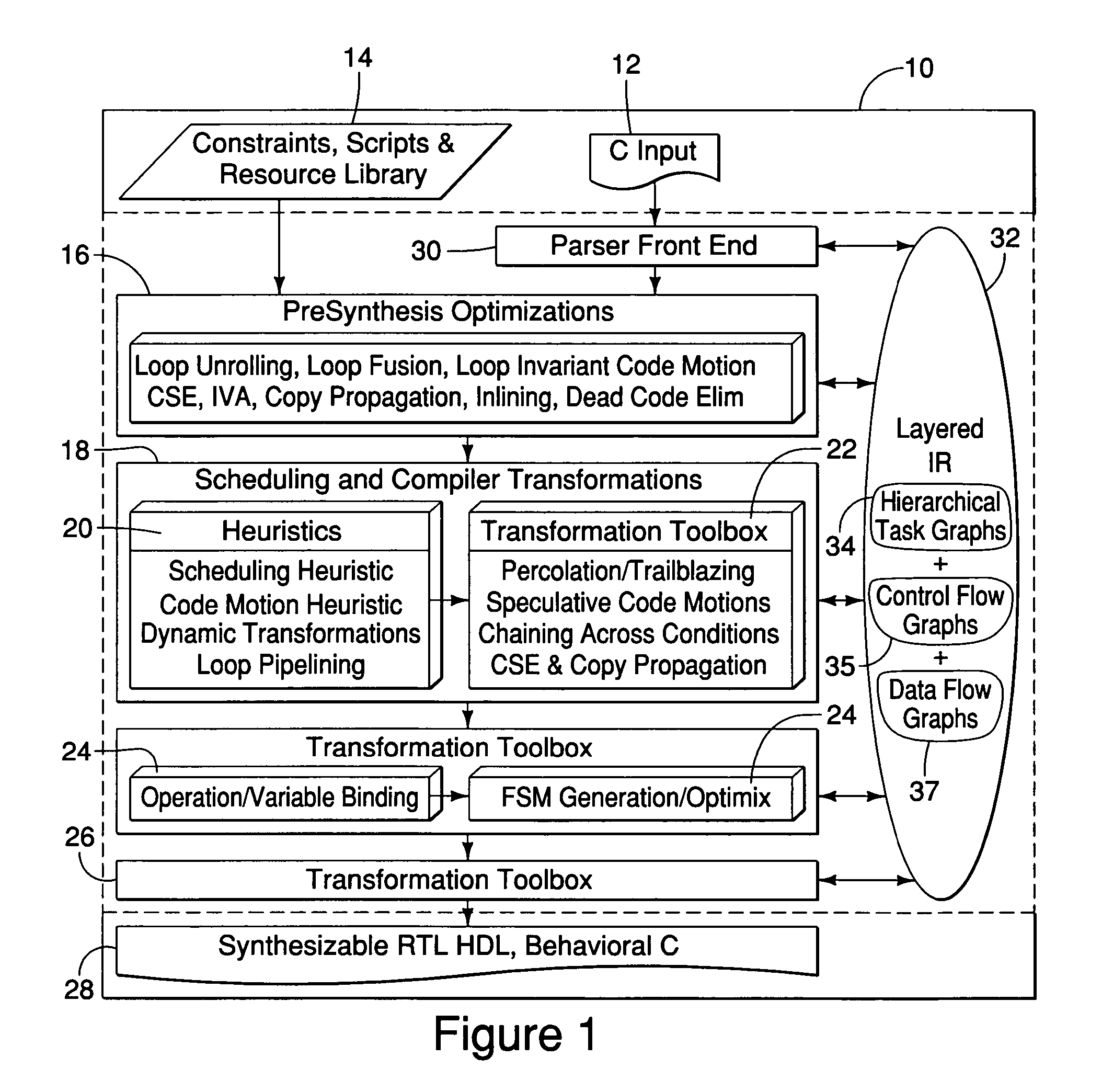

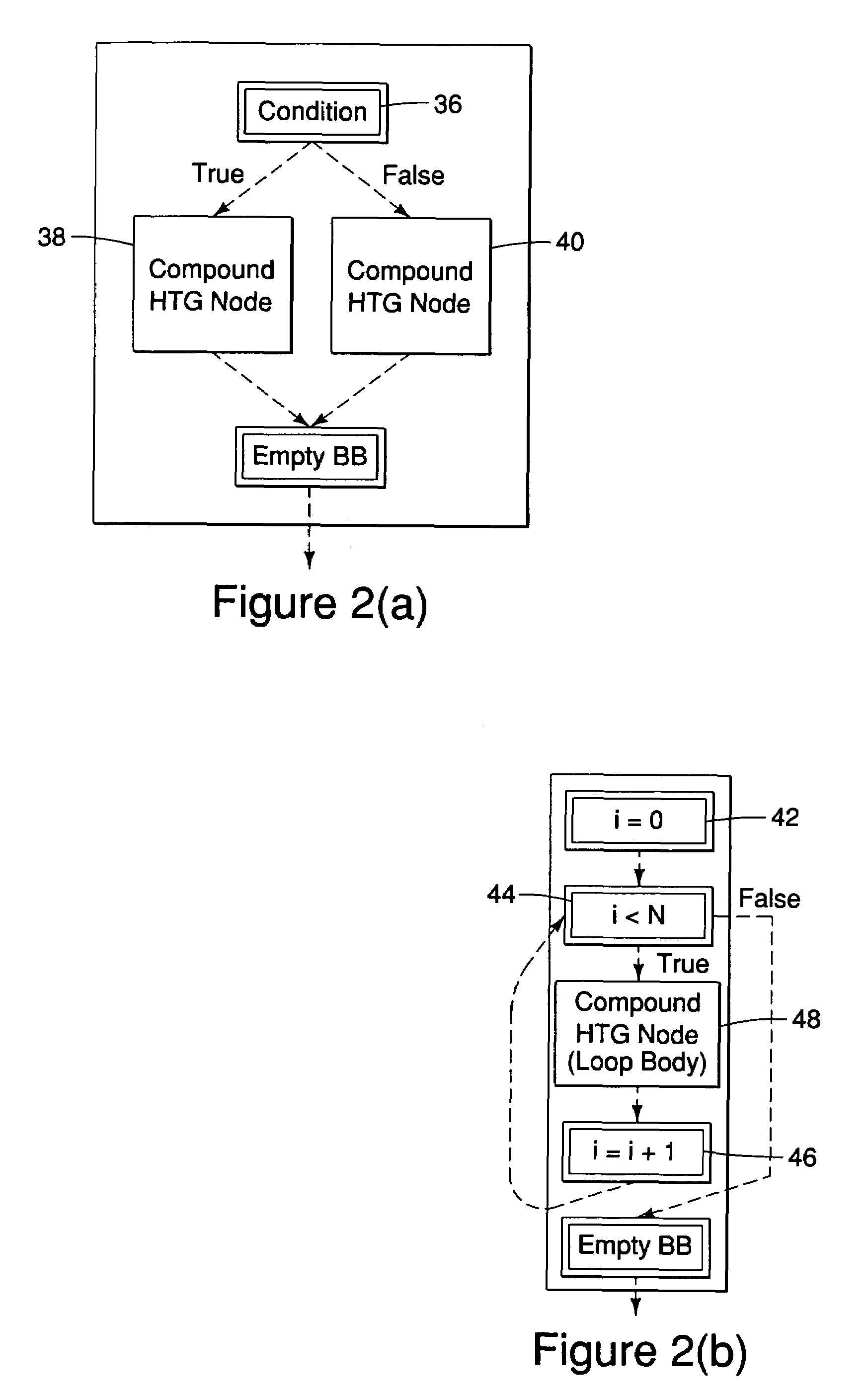

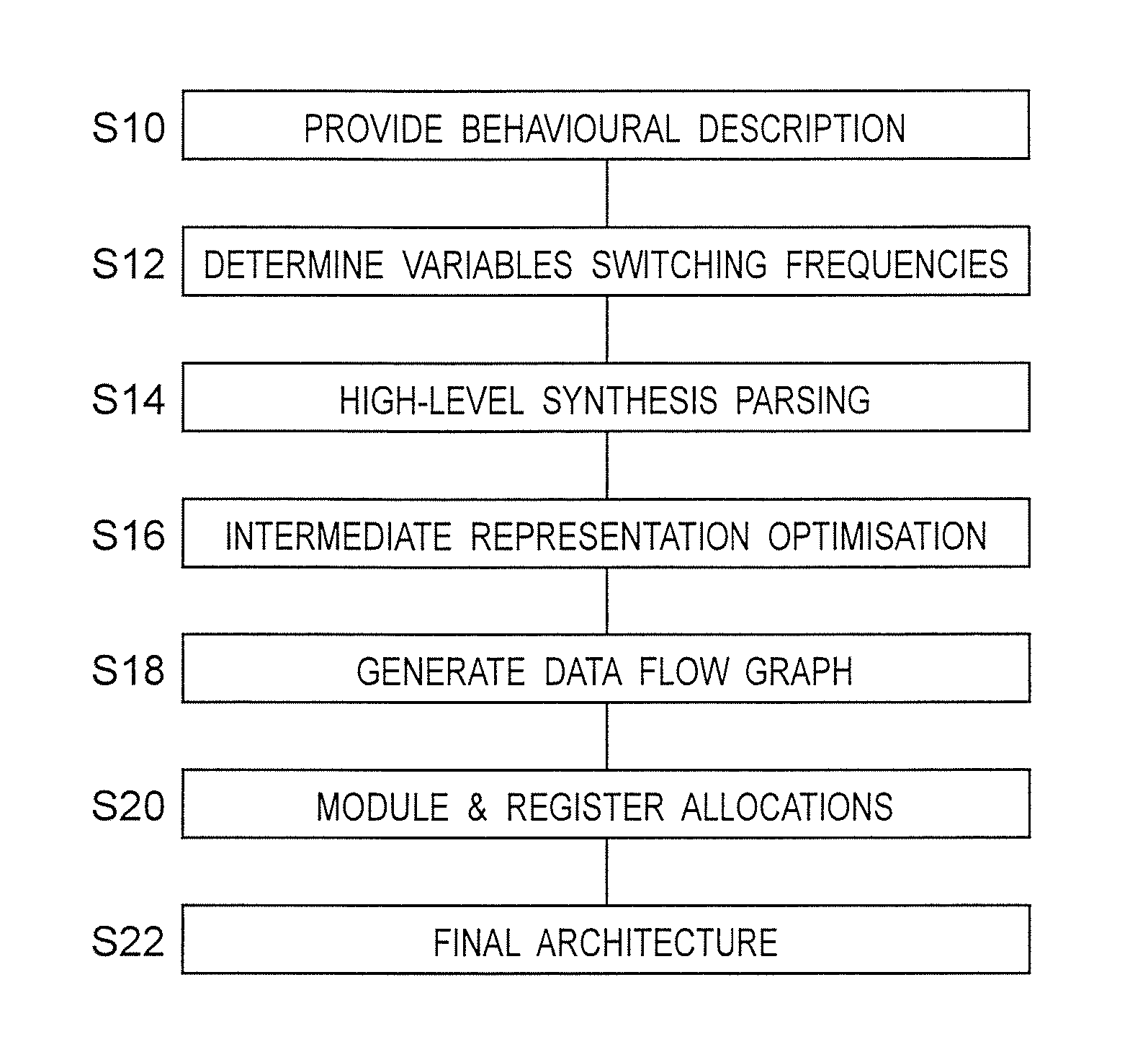

A method for performing high-level synthesis (HLS) of a digital design includes a first phase for performing transformations on a behavioral description of the design, and a second phase for selecting a transformation from a plurality of transformations for transforming the behavioral description. The method further includes a third phase for implementing the transformed behavioral description using lower level primitives, and a fourth phase for generating implementation codes for the design.

Owner:RGT UNIV OF CALIFORNIA

Constrained register sharing technique for low power VLSI design

InactiveUS6195786B1Reduce power consumptionReduced activitySemiconductor/solid-state device manufacturingCAD circuit designComputer architectureProcessor register

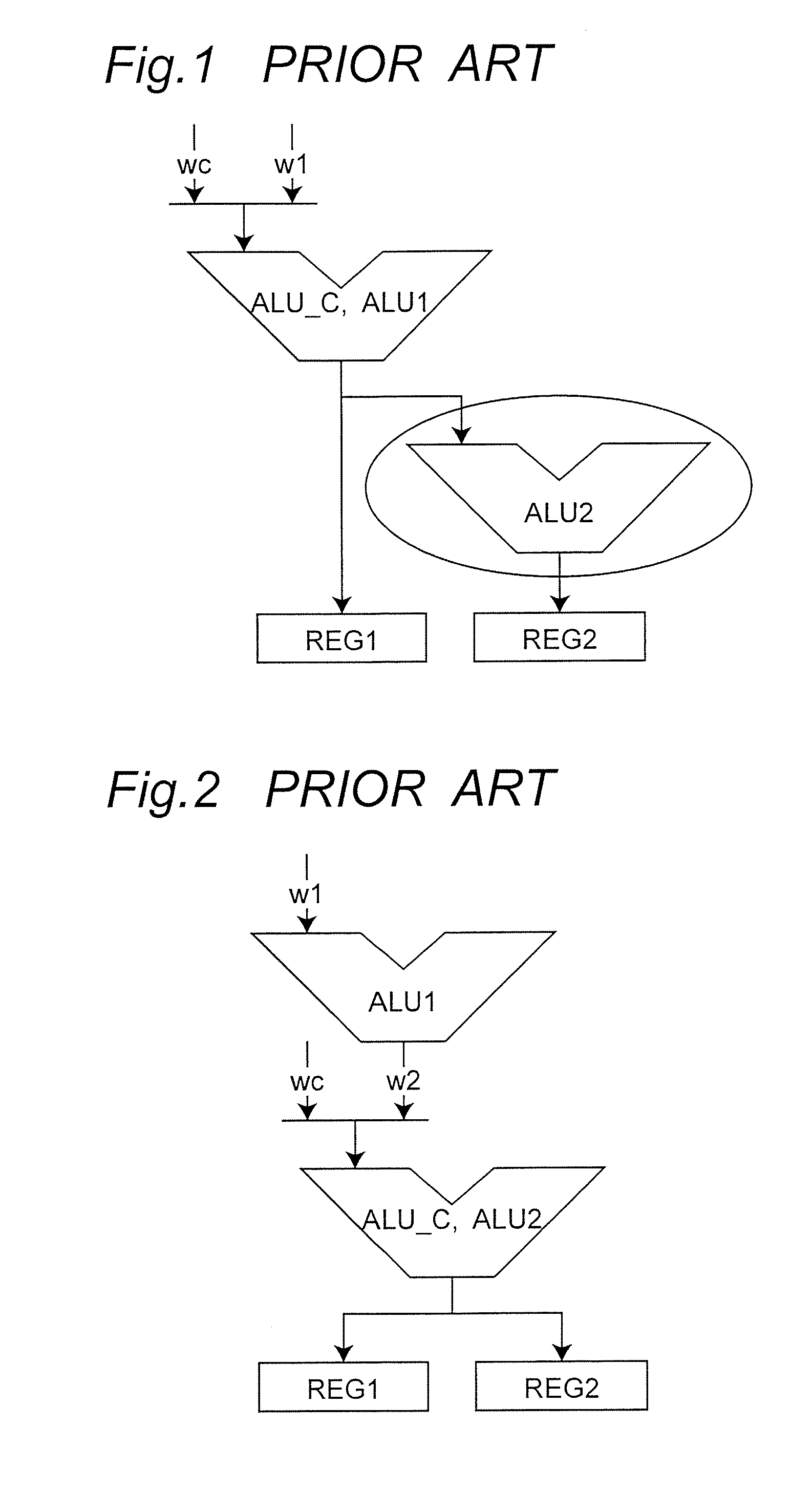

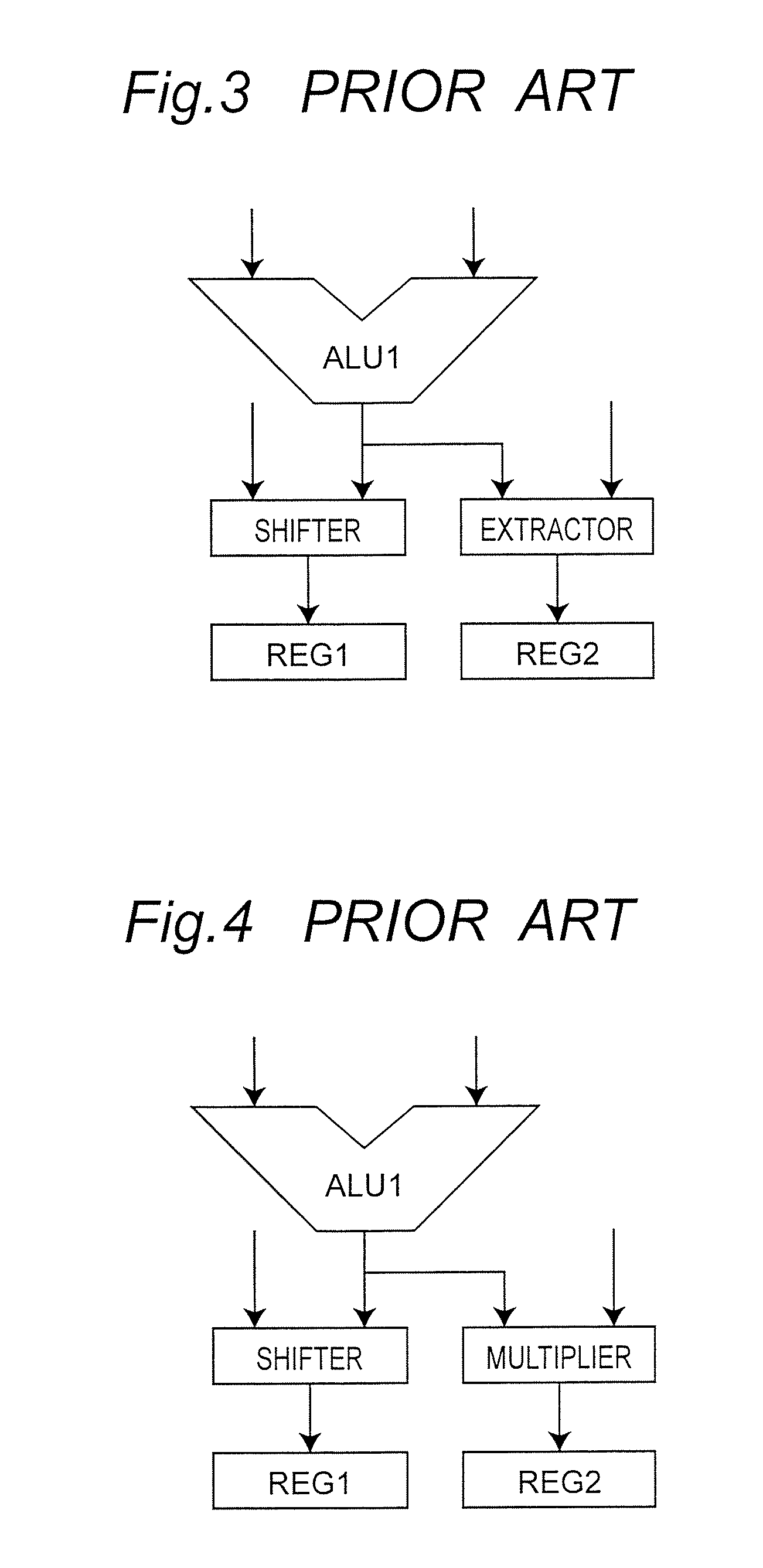

A power management method and system targeted toward high-level synthesis of data-dominated behavioral descriptions. The method of the present invention is founded on the observation that variable assignment can significantly affect power management opportunities in the synthesized architecture. Based on this observation, a procedure for constraining variable assignment is provided so that the functional units in the synthesized architecture do not execute any spurious operations.

Owner:PRINCETON UNIV +1

High level synthesis method for semiconductor integrated circuit

InactiveUS20050289499A1Efficient sharingLess attractiveCAD circuit designSoftware simulation/interpretation/emulationGraphicsData stream

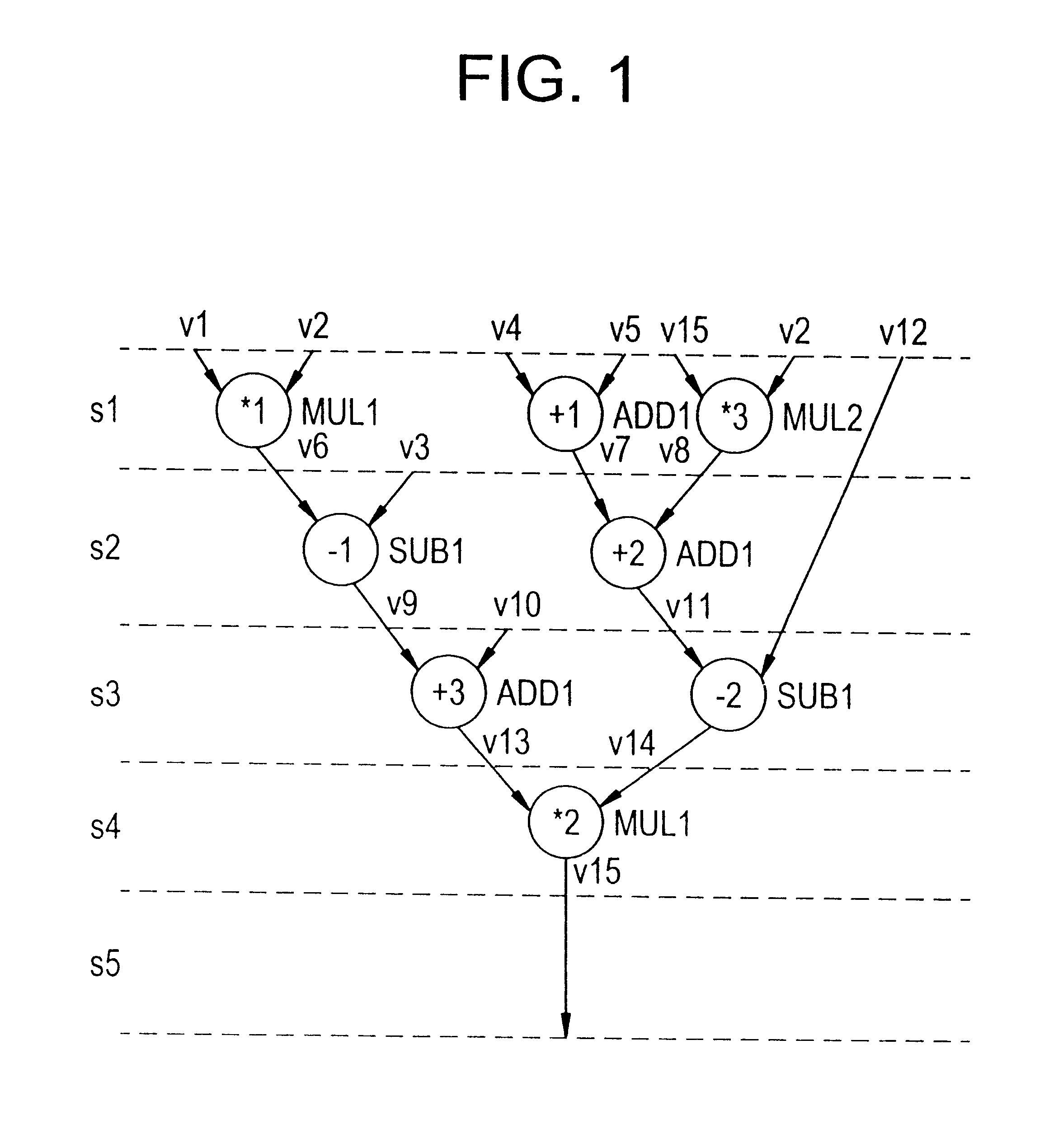

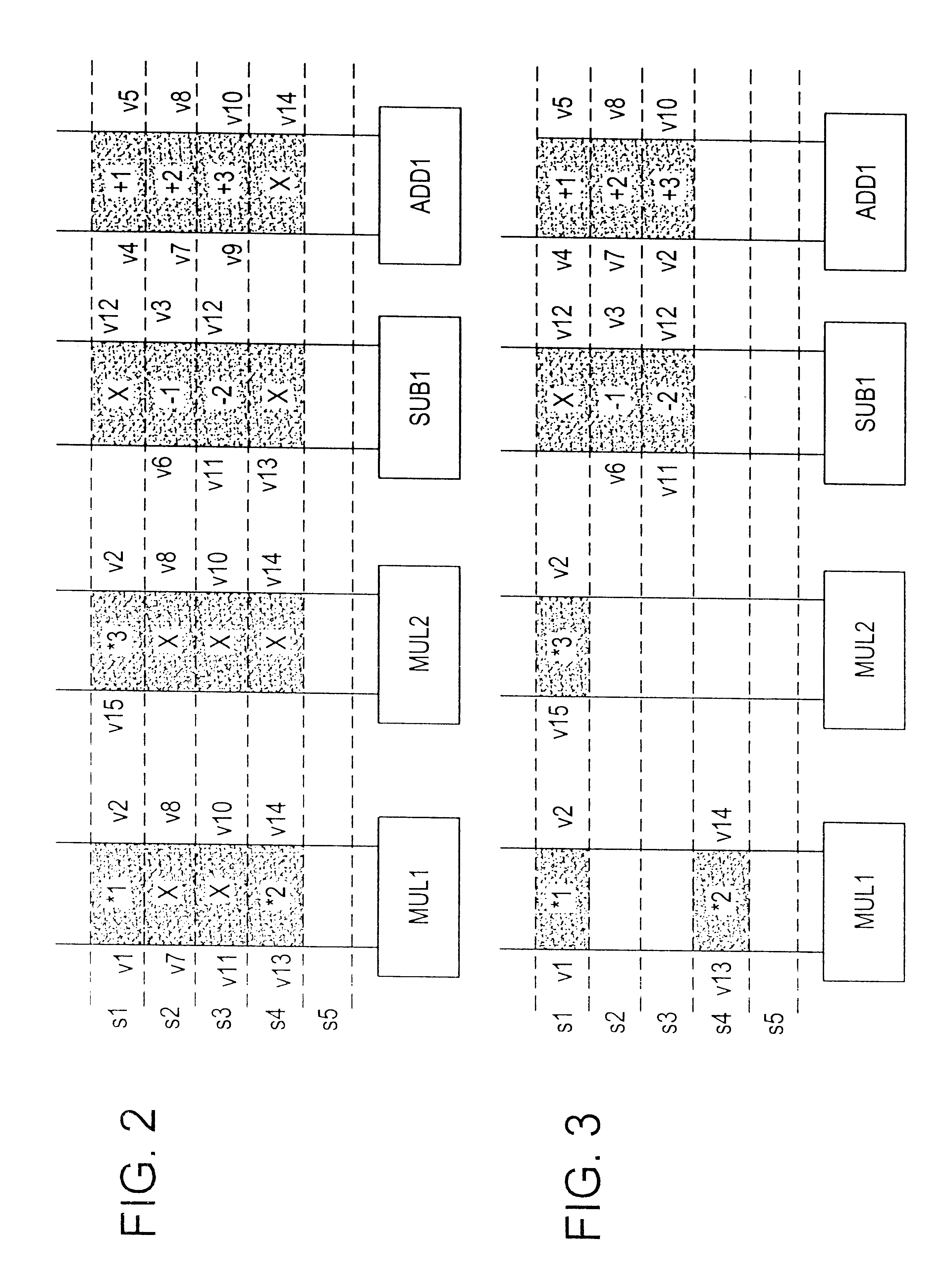

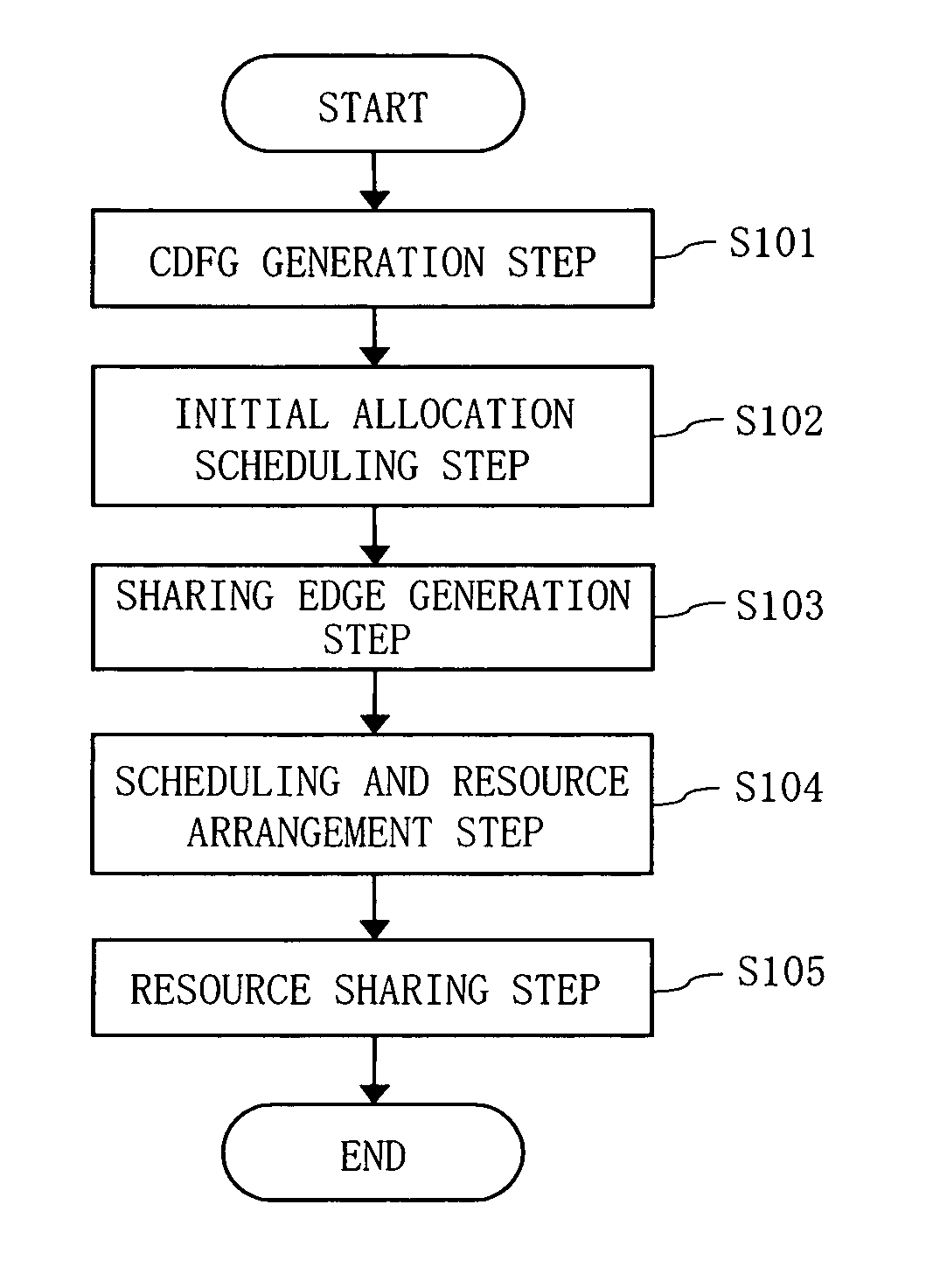

A CDFG which is a graph representing calculations and a data flow included in the design specifications of a circuit is generated S101, a clock cycle required for the processing is obtained and thus an allocated resource connection graph is generated S102. When the allocated resource connection graph includes nodes to which hardware resources having the same function are allocated, a sharing edge for controlling sharing of the nodes is added between the nodes S103. A provisional layout of the allocated resource connection graph having the sharing edge added thereto is provided S104, and the nodes of the allocated resource connection graph are shared based on the layout result S105. The sharing edge is provided with attribute or weight such as attraction or repulsion. Thus, the distance between the nodes in the layout result is controlled and the degree at which the resources are shared is controlled.

Owner:SOCIONEXT INC

Method and apparatus for designing circuits using high-level synthesis

InactiveUS7383529B2CAD circuit designSpecial data processing applicationsComputer architectureHigh-level synthesis

A method for performing high-level synthesis (HLS) of a digital design includes a first phase for performing transformations on a behavioral description of the design, and a second phase for selecting a transformation from a plurality of transformations for transforming the behavioral description. The method further includes a third phase for implementing the transformed behavioral description using lower level primitives, and a fourth phase for generating implementation codes for the design.

Owner:RGT UNIV OF CALIFORNIA

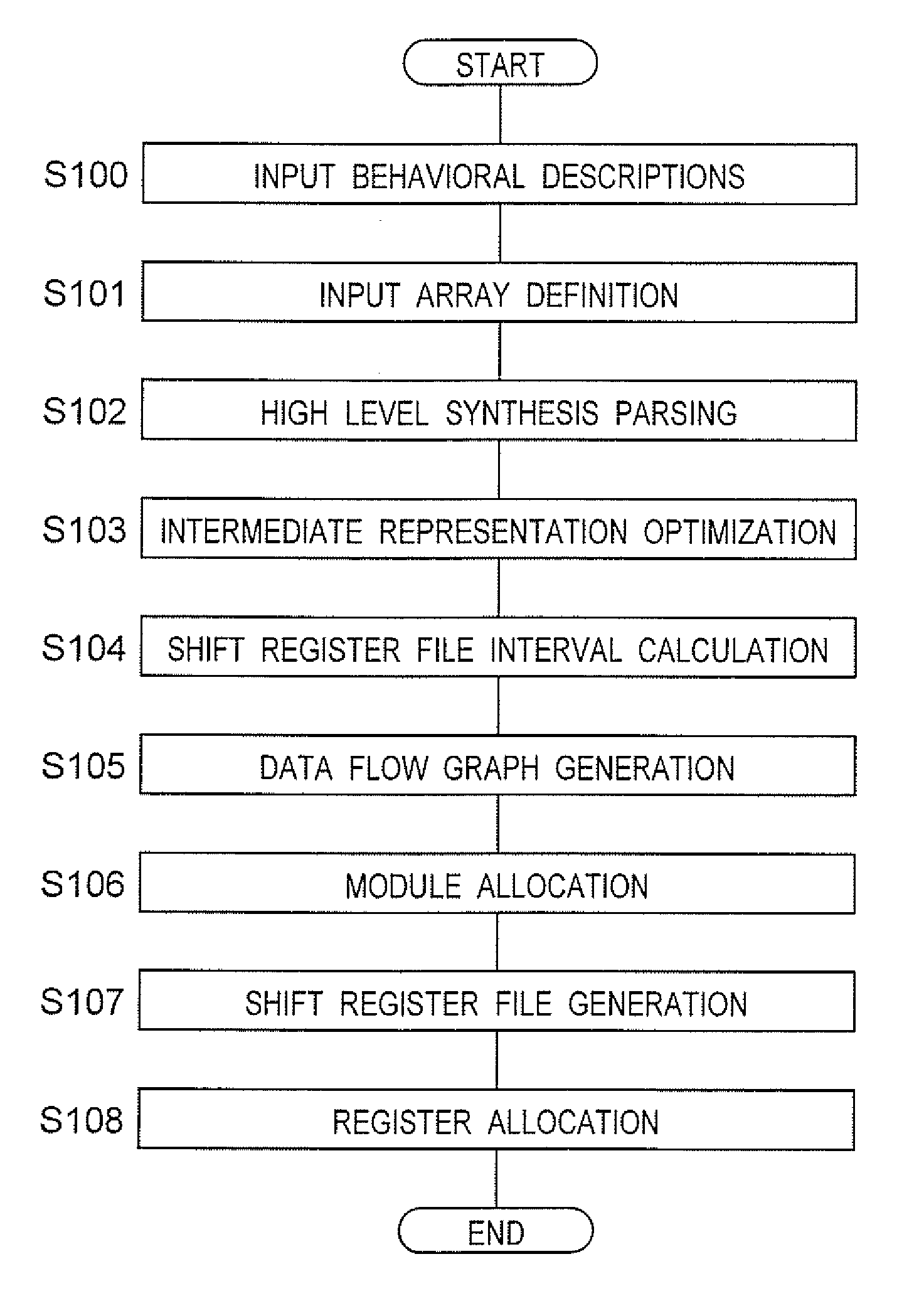

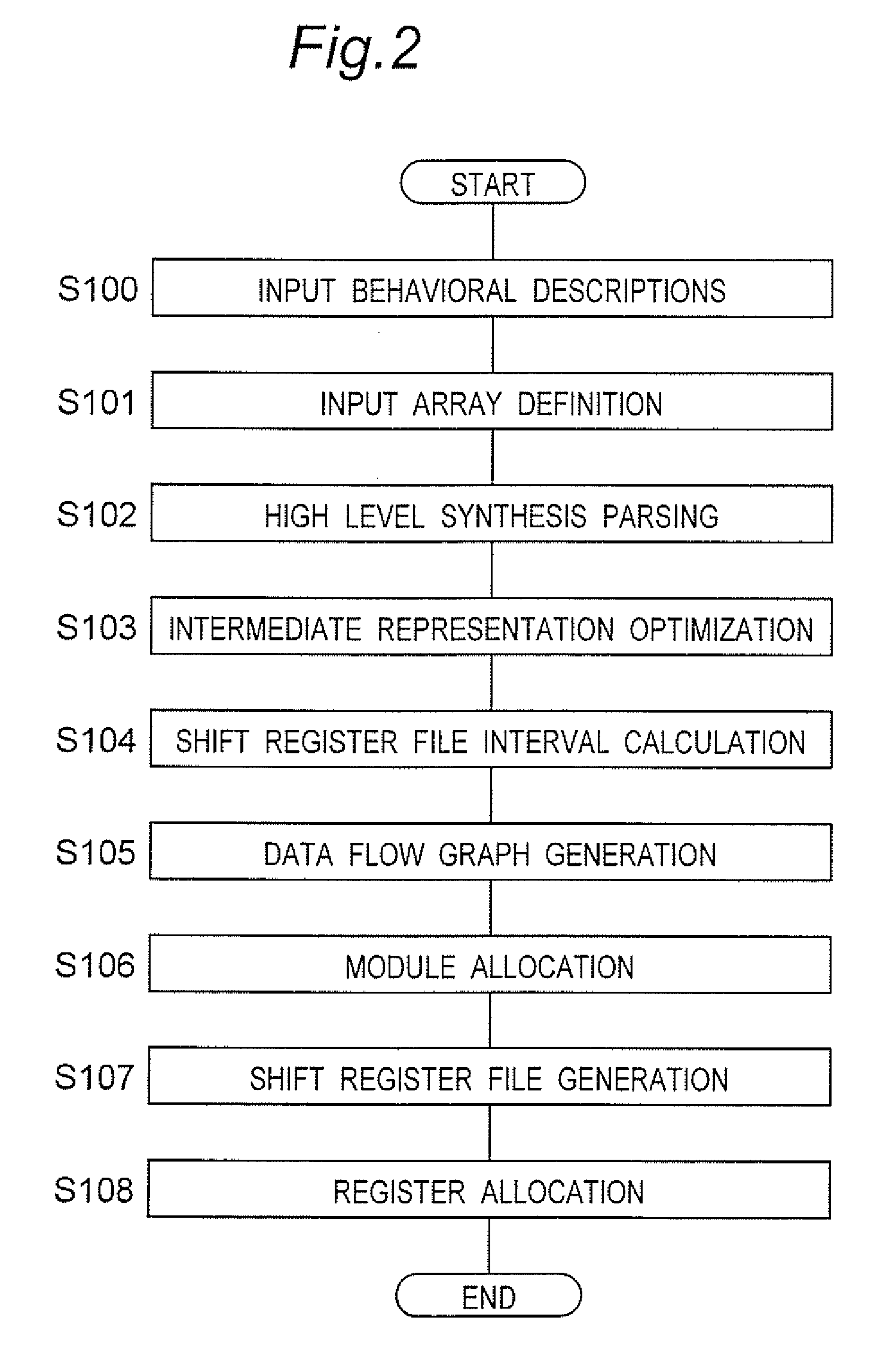

Method and apparatus for auto-generation of shift register file for high-level synthesis compiler

A method and apparatus for auto-generation of shift register file for high-level synthesis compiler includes parsing input source codes for specific definition of shift register file, a plurality of compiler directives to indicate the shift register file name, shift register file size, shift register file read access order, and shift register file write timing of the specific shift register file. The invention also includes determining the shifting interval of shift register file with specific definition after each reading or writing automatically. The invention further includes determining if the shift register file with specific definition has been generated, generating shift register file with specific definition if it has not been generated, and generating shift register file control signals to access the shift register file with specific definition. The invention additionally includes accessing shift register file with specific definition for reading or writing both in a one-dimensional or two-dimensional manner.

Owner:PANASONIC CORP

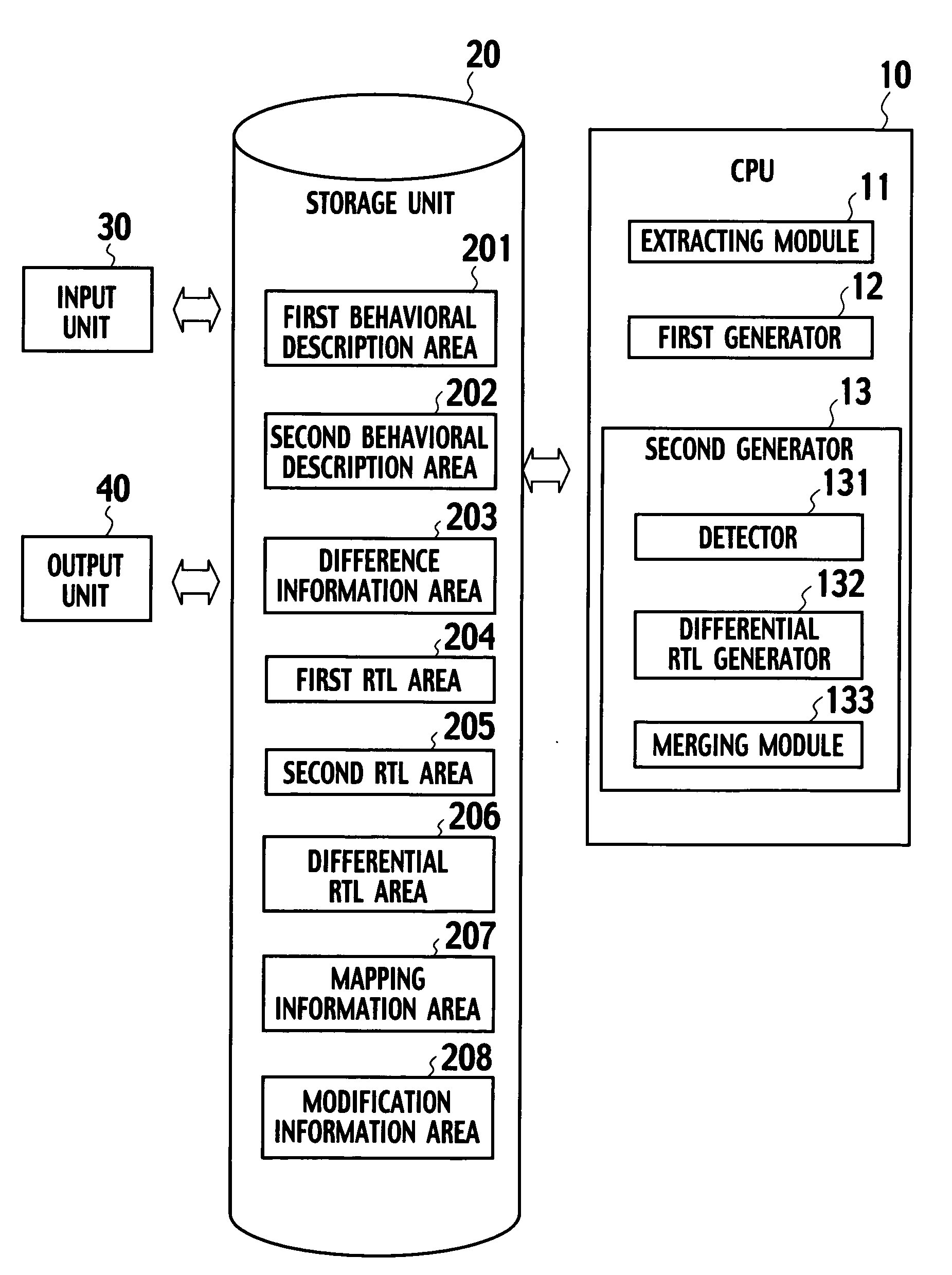

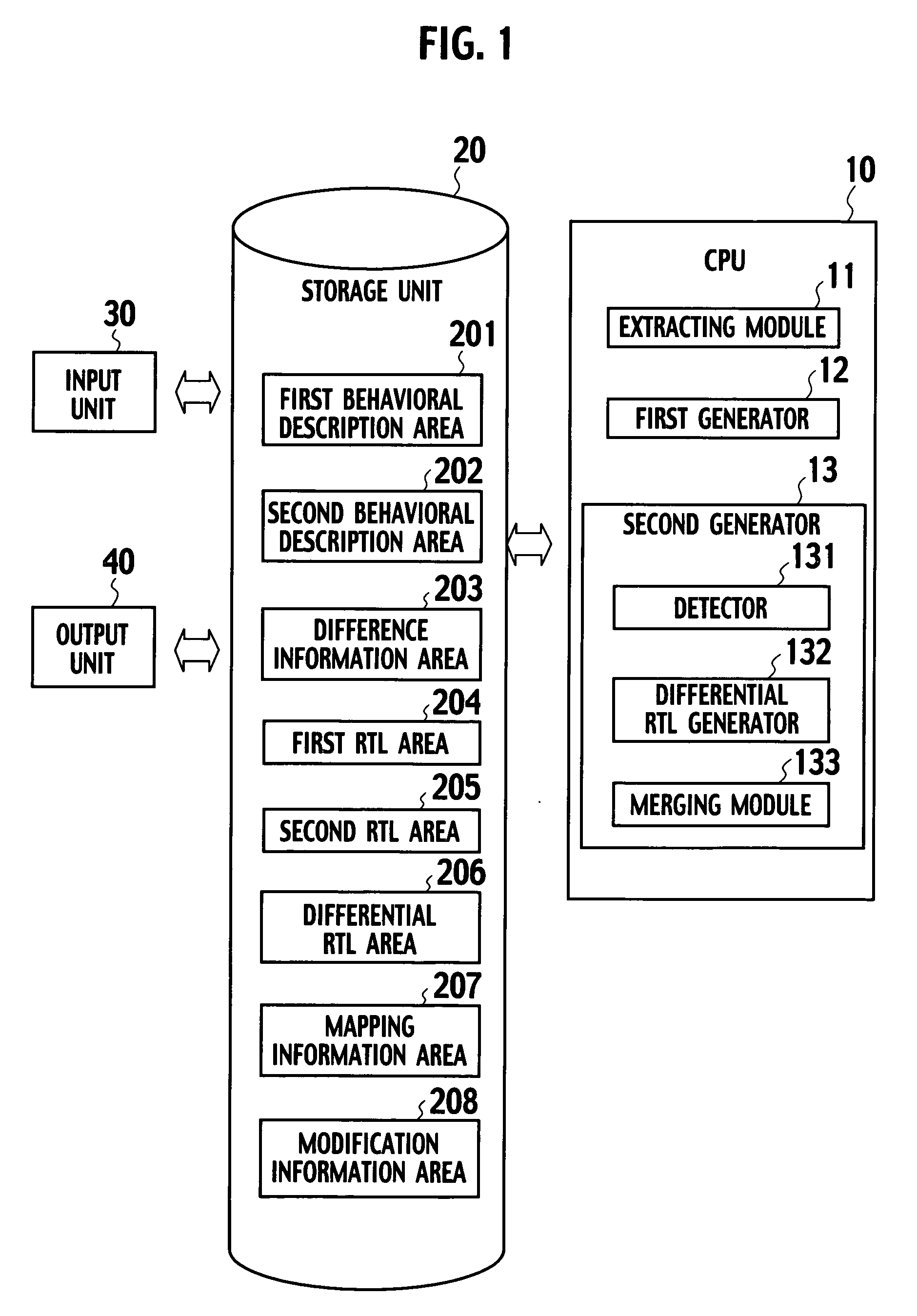

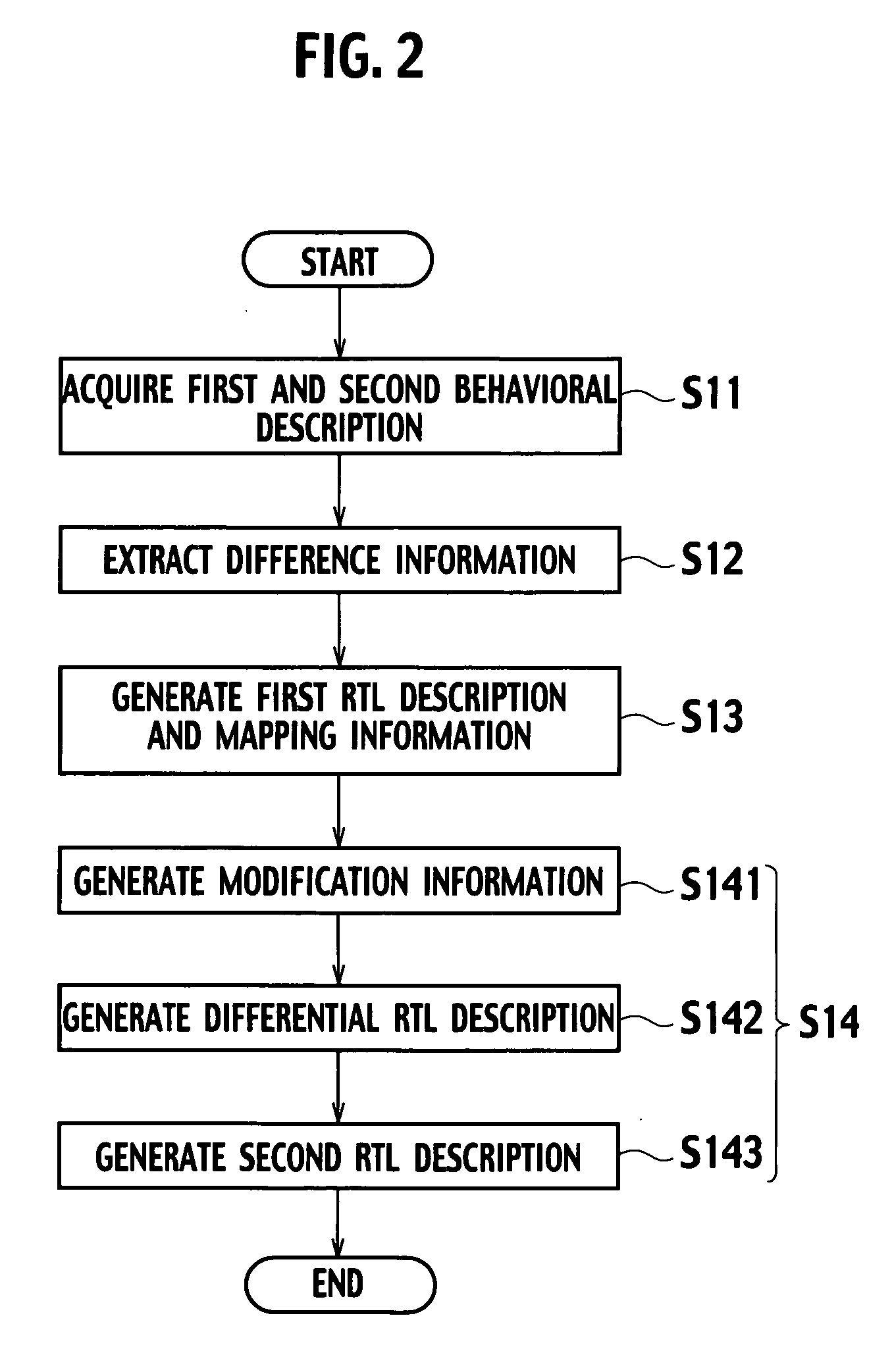

Method and program for high-level synthesis, and method for verifying a gate network list using the high-level synthesis method

InactiveUS20070028204A1CAD circuit designSoftware simulation/interpretation/emulationComputer architectureSynthesis methods

A method for high-level synthesis includes extracting difference information of a first and a second behavioral description, generating a first register transfer level description from the first behavioral description while generating mapping information of the first behavioral description and the first register transfer level description, modifying the first register transfer level description based on the difference information and the mapping information, and generating a second register transfer level description of a logic behavior equivalent to the second behavioral description.

Owner:KK TOSHIBA

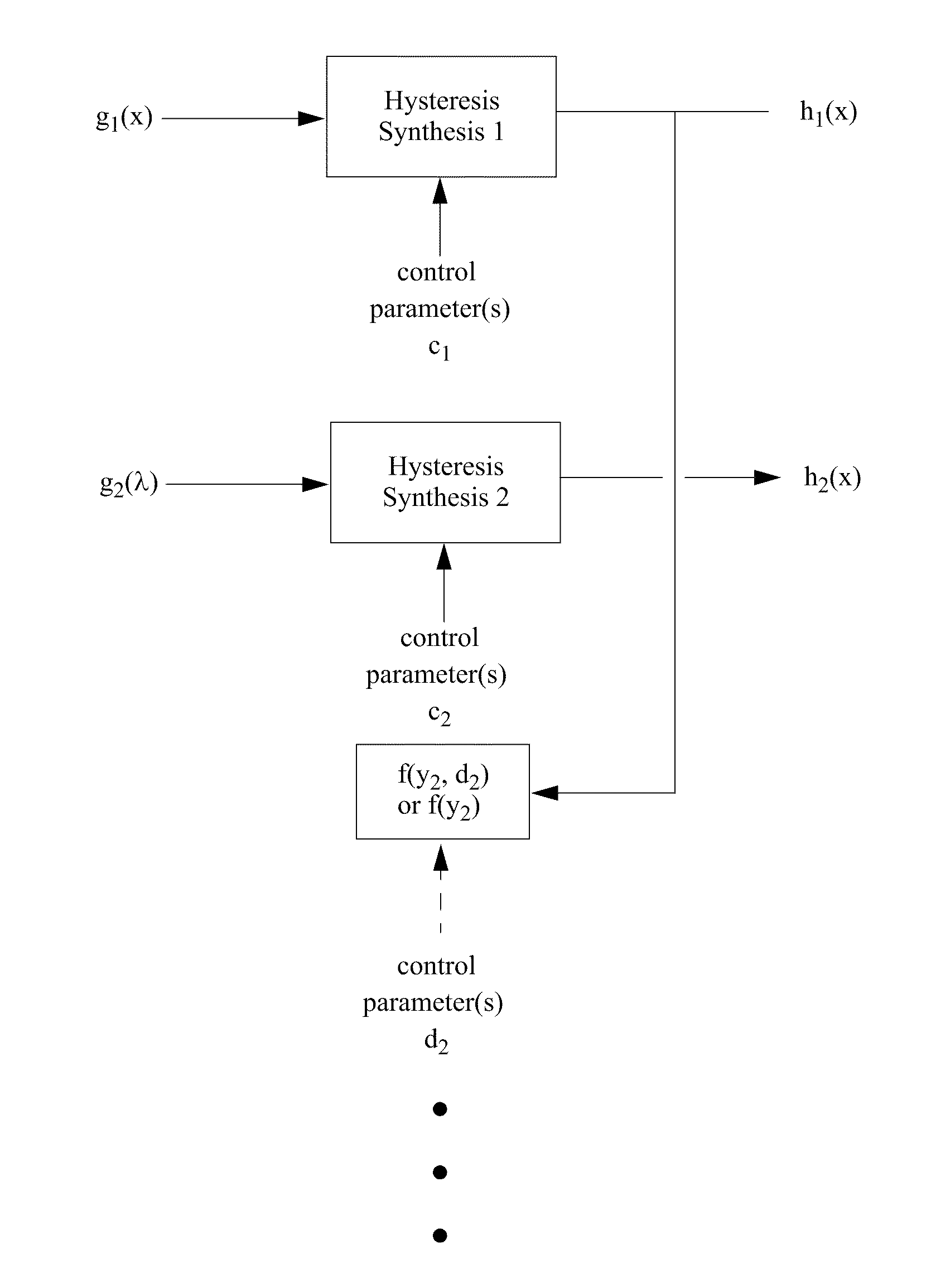

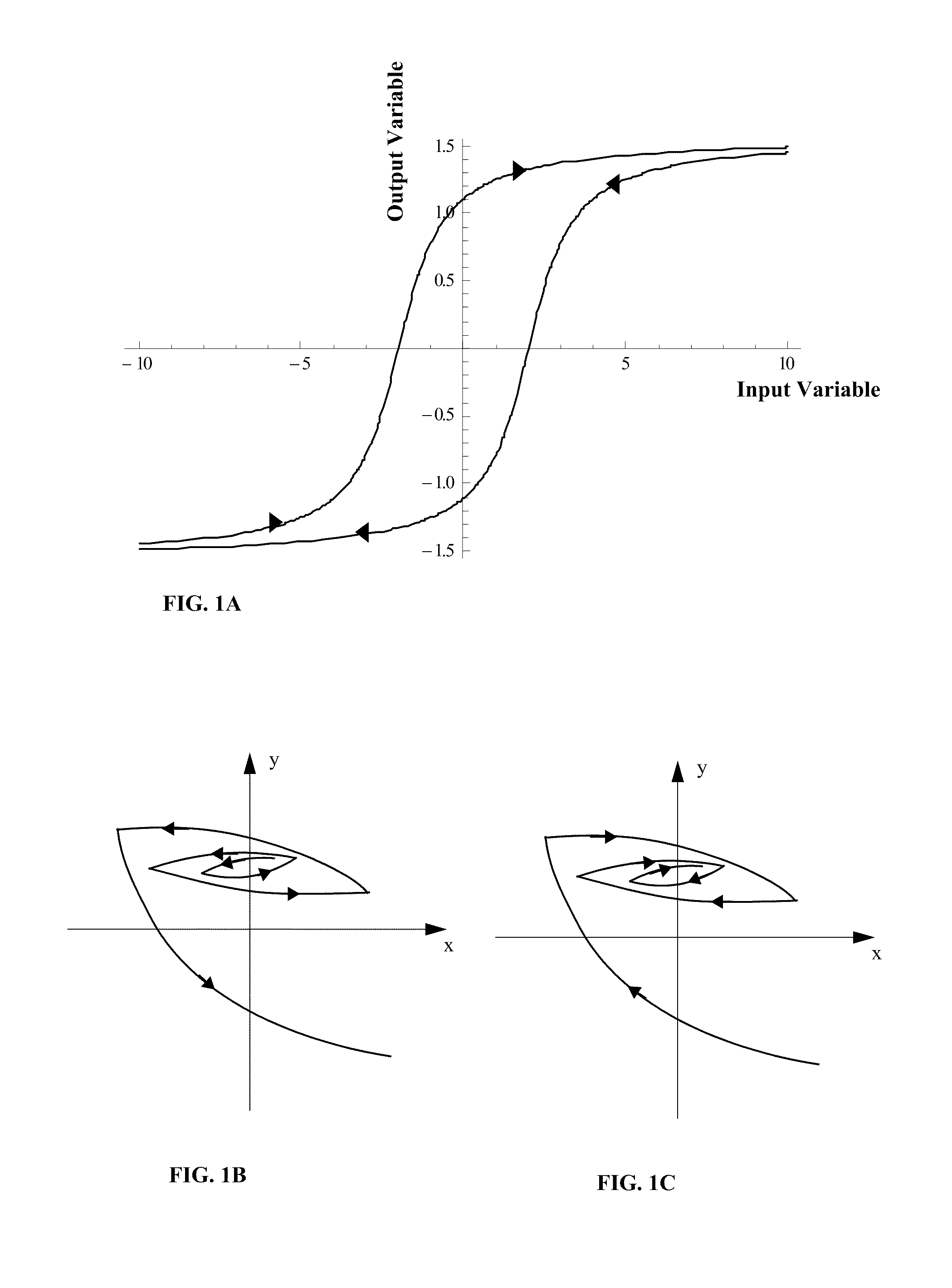

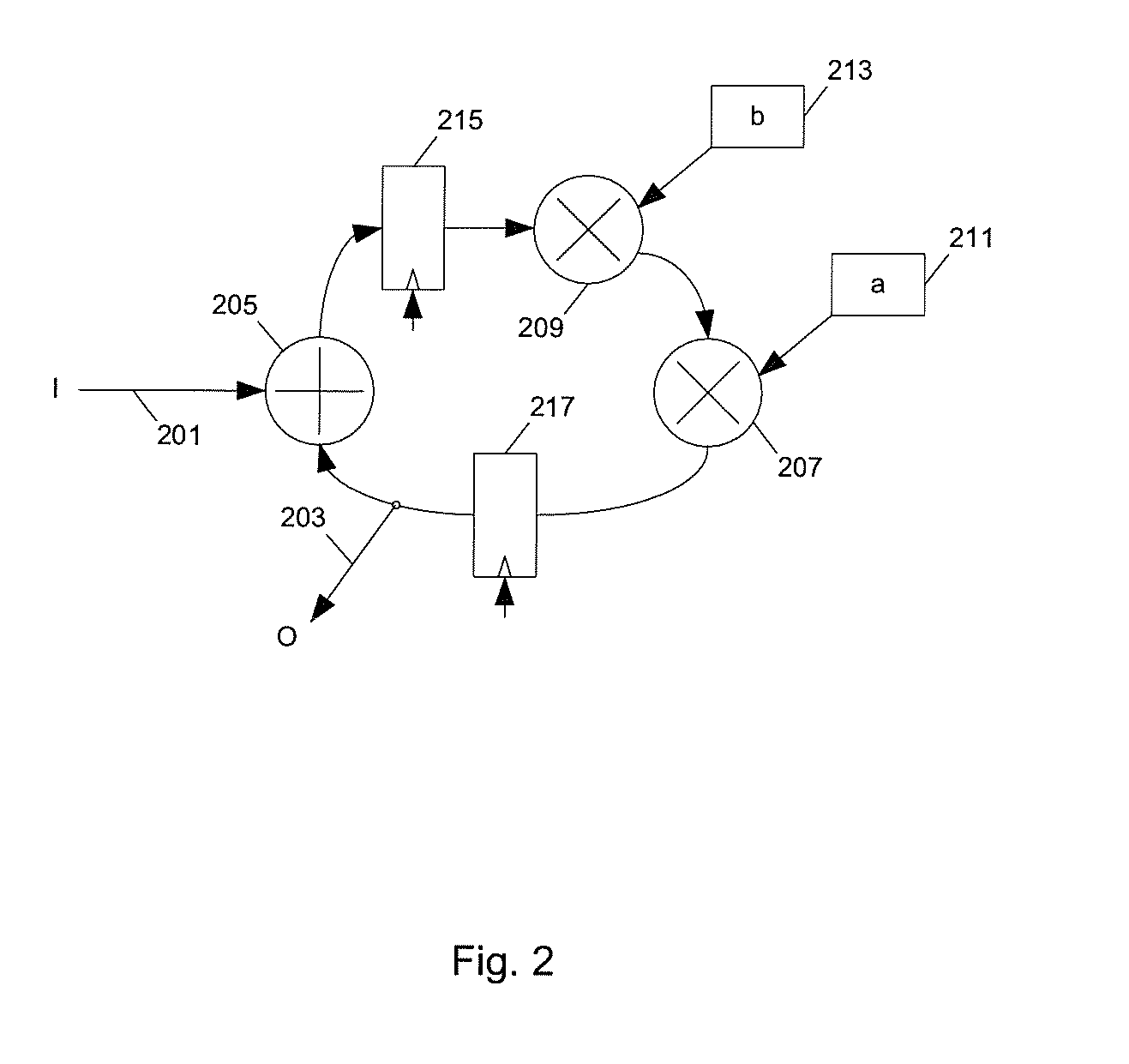

Advanced synthesized hysteresis for signal processing, controllers, music, and computer simulations in physics, engineering, and economics

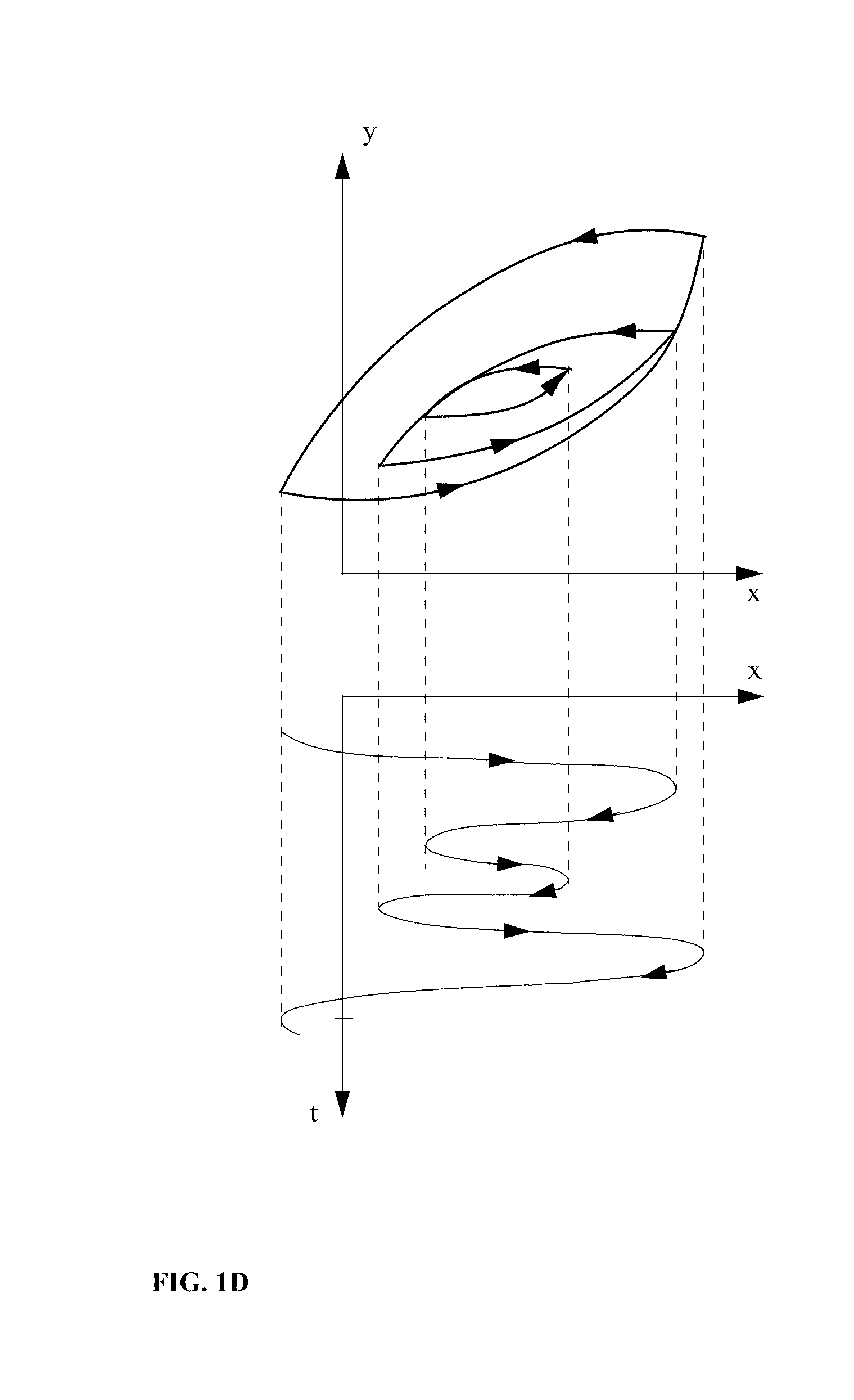

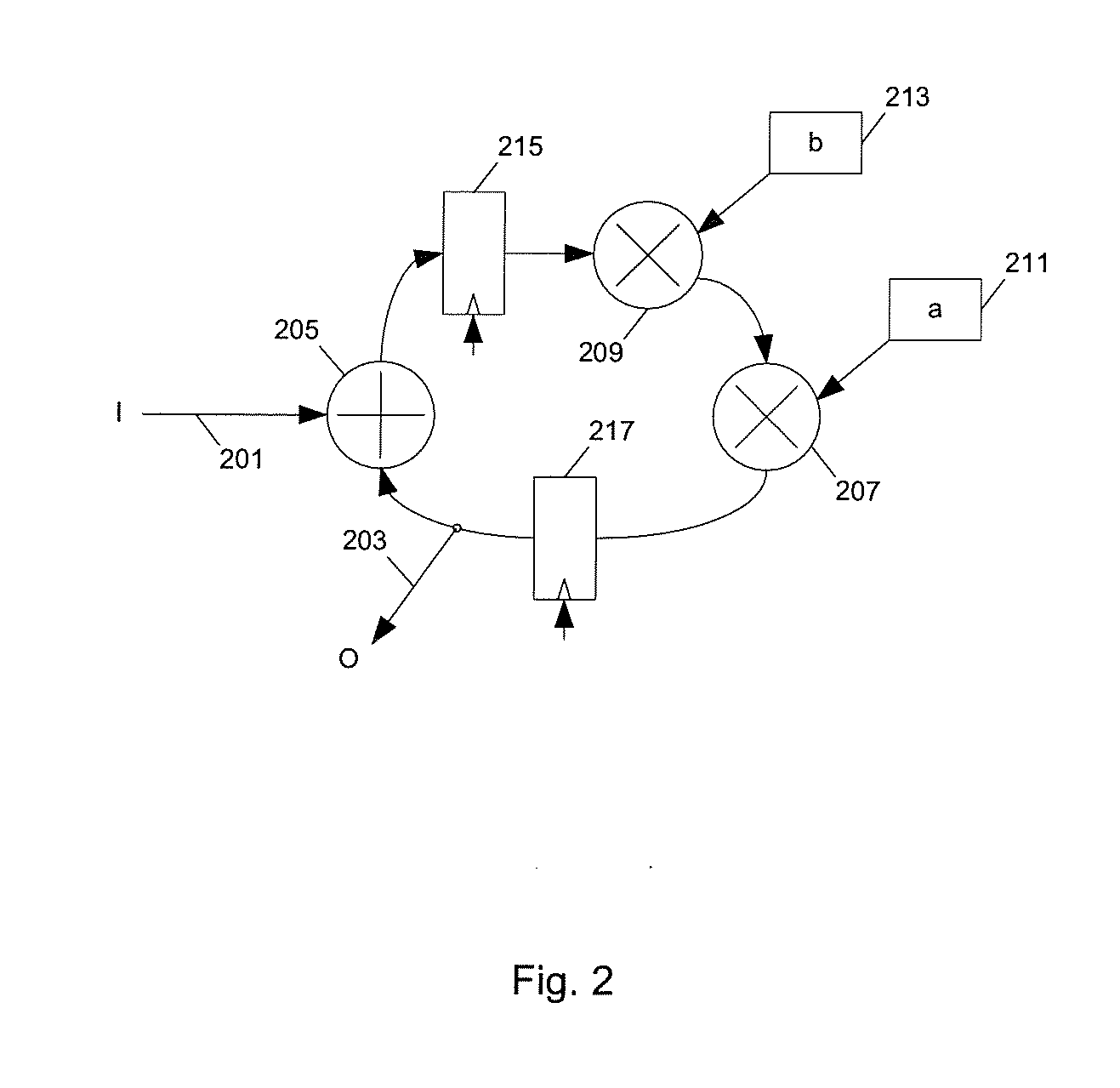

A method for synthesis of a hysteresis function of a plurality of inputs is described. The method includes receiving and processing of a plurality of input signals with at least a parameterized multivariable nonlinearity, the parameterized multivariable nonlinearity serving as a parameterized hysteron, to produce at least one output signal. The plurality of input signals is also processed by at least a controller function, the controller function comprising memory and producing at least one control signal responsive to at least one of the plurality of input signals, the at least once control signal for controlling the parameterized hysteron. The at least one control signal is used to control the parameterized hysteron so as to create a hysteretic response to at least one of the plurality of input signals.

Owner:NRI R&D PATENT LICENSING LLC

High-level synthesis for efficient verification

InactiveUS20070226666A1Use minimizedLimiting stepComputer aided designSoftware simulation/interpretation/emulationGuidelineExternal storage

Verification friendly models for SAT-based formal verification are generated from a given high-level design wherein during construction the following guidelines are enforced: 1) No re-use of functional units and registers; 2) Minimize the use of muxes and sharing; 3) Reduce the number of control steps; 4) Avoid pipelines; 5) Chose functional units from “verification friendly” library; 6) Re-use operations; 7) Perform property-preserving slicing; 8) Support “assume” and “assert” in the language specification; and 8) Use external memory modules instead of register arrays.

Owner:NEC CORP

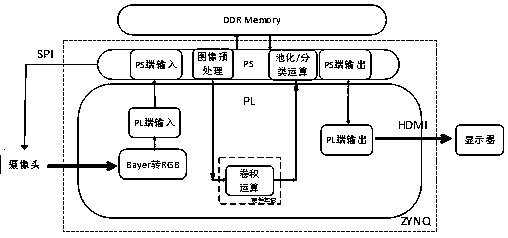

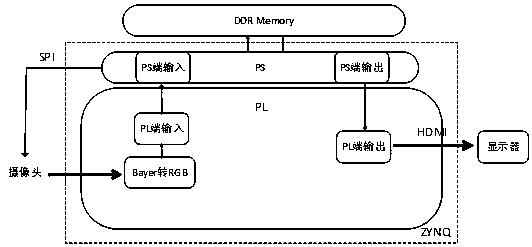

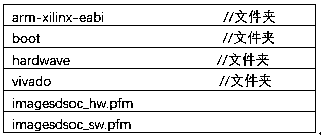

Convolutional neural network algorithm design implementation method based on heterogeneous calculation

InactiveCN108256636ARapid designQuick implementationDesign optimisation/simulationNeural architecturesSystem requirementsNetwork model

The invention belongs to the technical field of heterogeneous calculation and image identification, and particularly relates to a convolutional neural network algorithm design implementation method based on heterogeneous calculation. According to the method, an implemented hardware platform is a Xilinx ZYNQ-7020 programmable SoC (system on a chip), an FPGA (field programmable gate array) and an ARM (advanced RISC machine) processor are arranged in the hardware platform, an implemented software platform is an SDSoC, and high-level synthesis and software definition connecting frame are combinedtogether, so that a HLS (high-level synthesis) result can be seamlessly connected to a software application. According to the method, a network model and a training network model are designed on a PC(personal computer), a network model parameter is extracted on the PC, software and hardware code partition is rapidly performed on a convolutional neural network algorithm on the SDSoC, inputted dataimage preprocessing, a pooling layer and a classification algorithm are implemented on an ARM terminal, convolution operation with maximum calculated amount is mapped to the FPGA and implemented, andperformance and area required by a system are met. According to the method, a convolutional neural network algorithm is rapidly implemented by the aid of a heterogeneous platform, the efficiency of the algorithm is greatly improved, and power consumption is greatly reduced when accuracy of the convolutional algorithm is ensured.

Owner:CHENGDU UNIVERSITY OF TECHNOLOGY

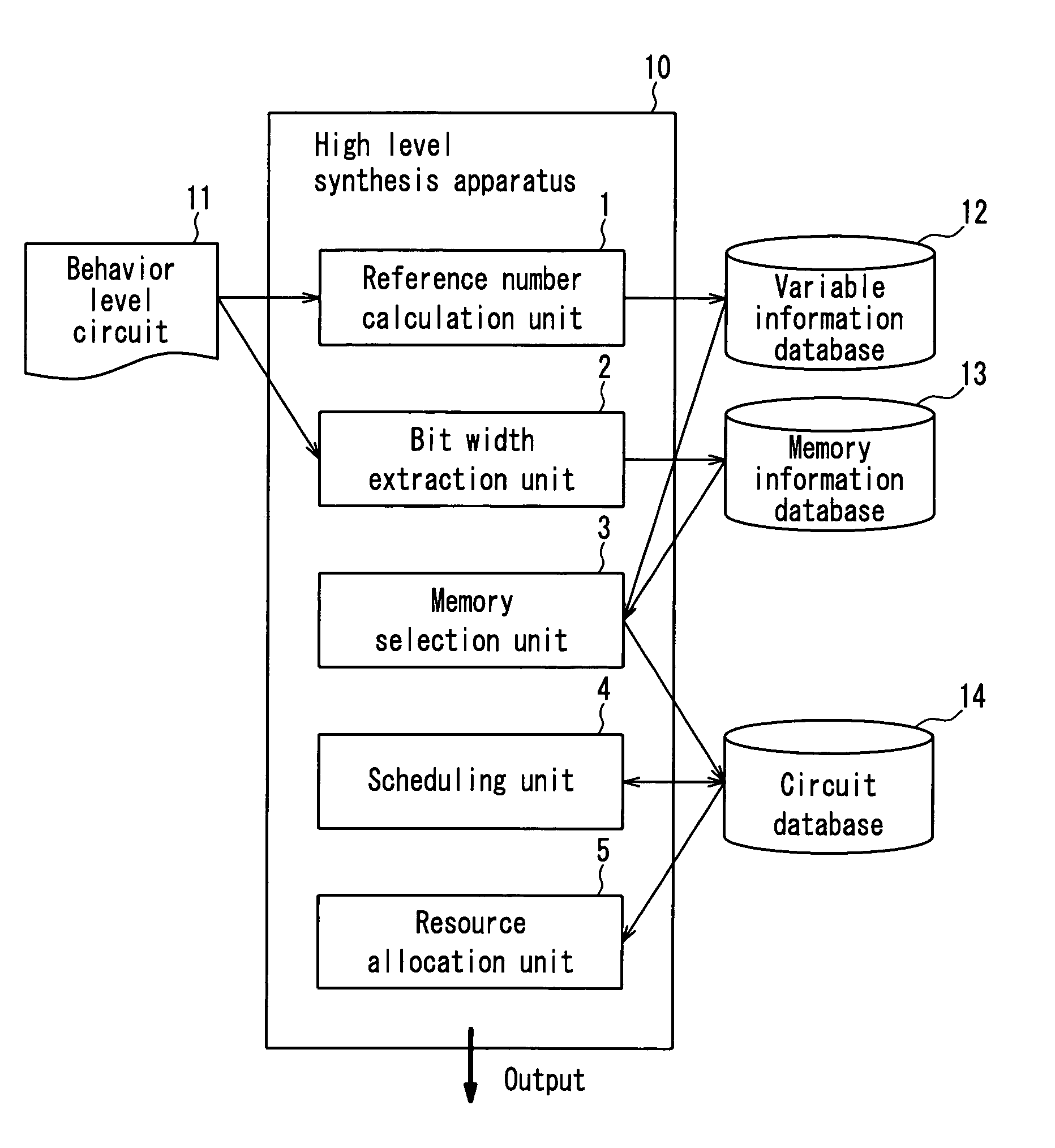

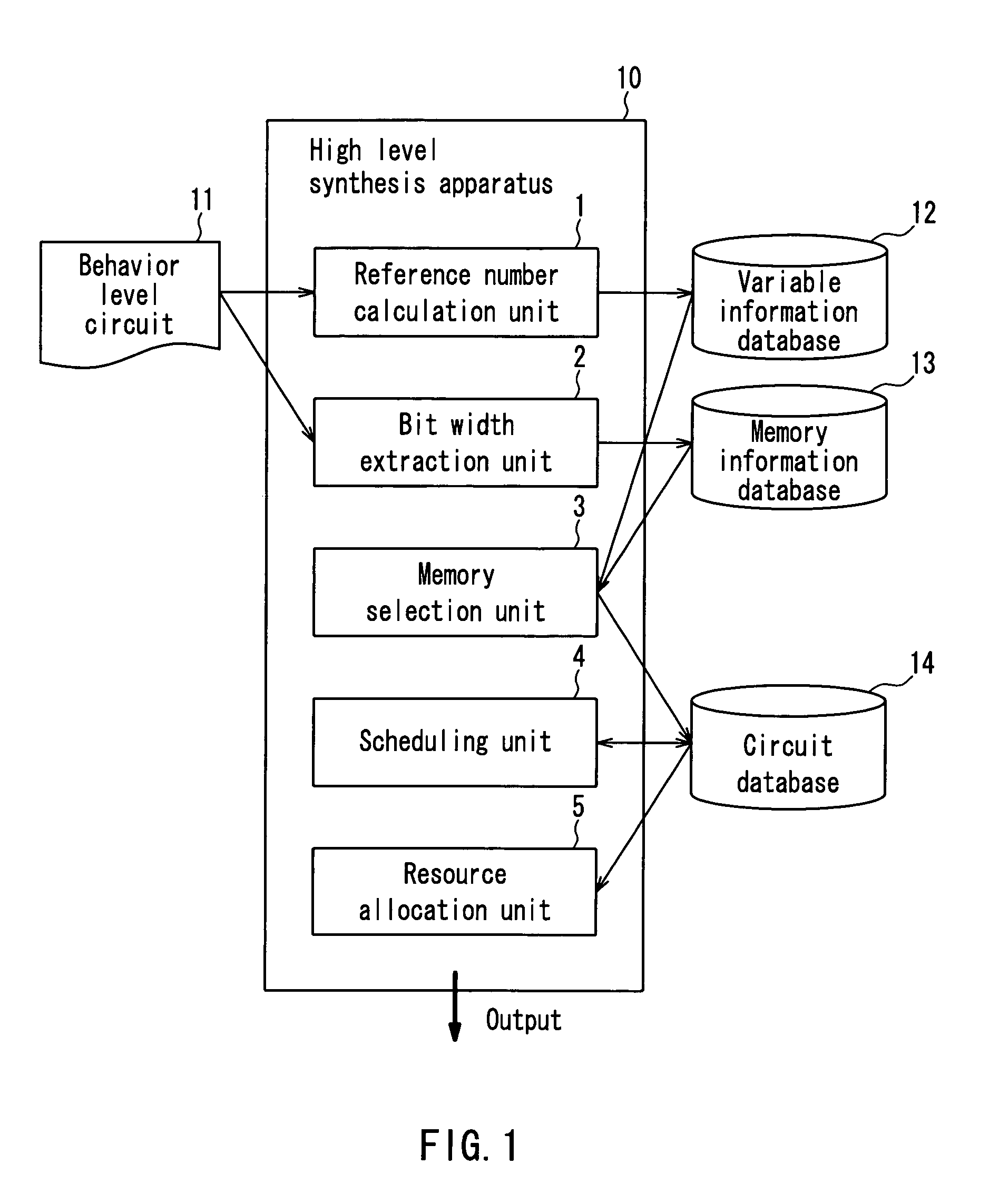

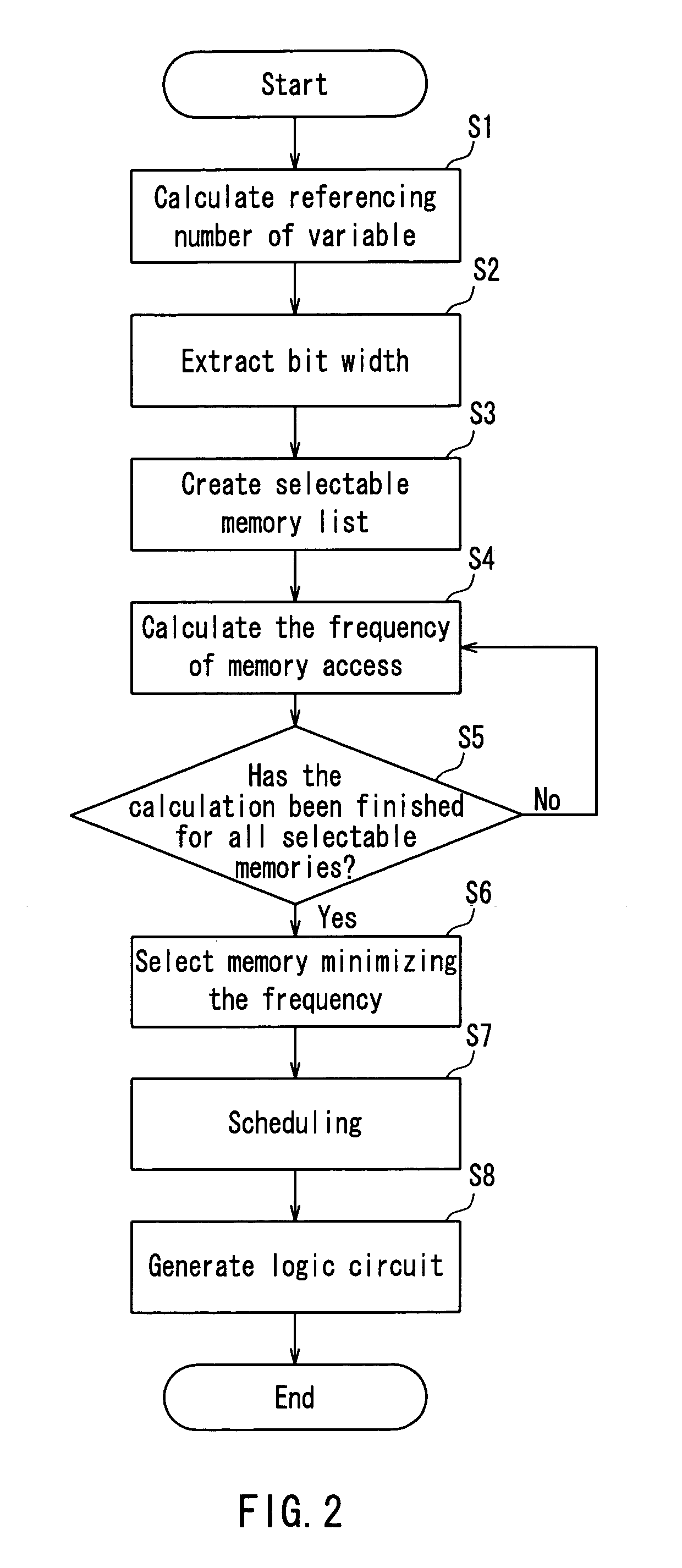

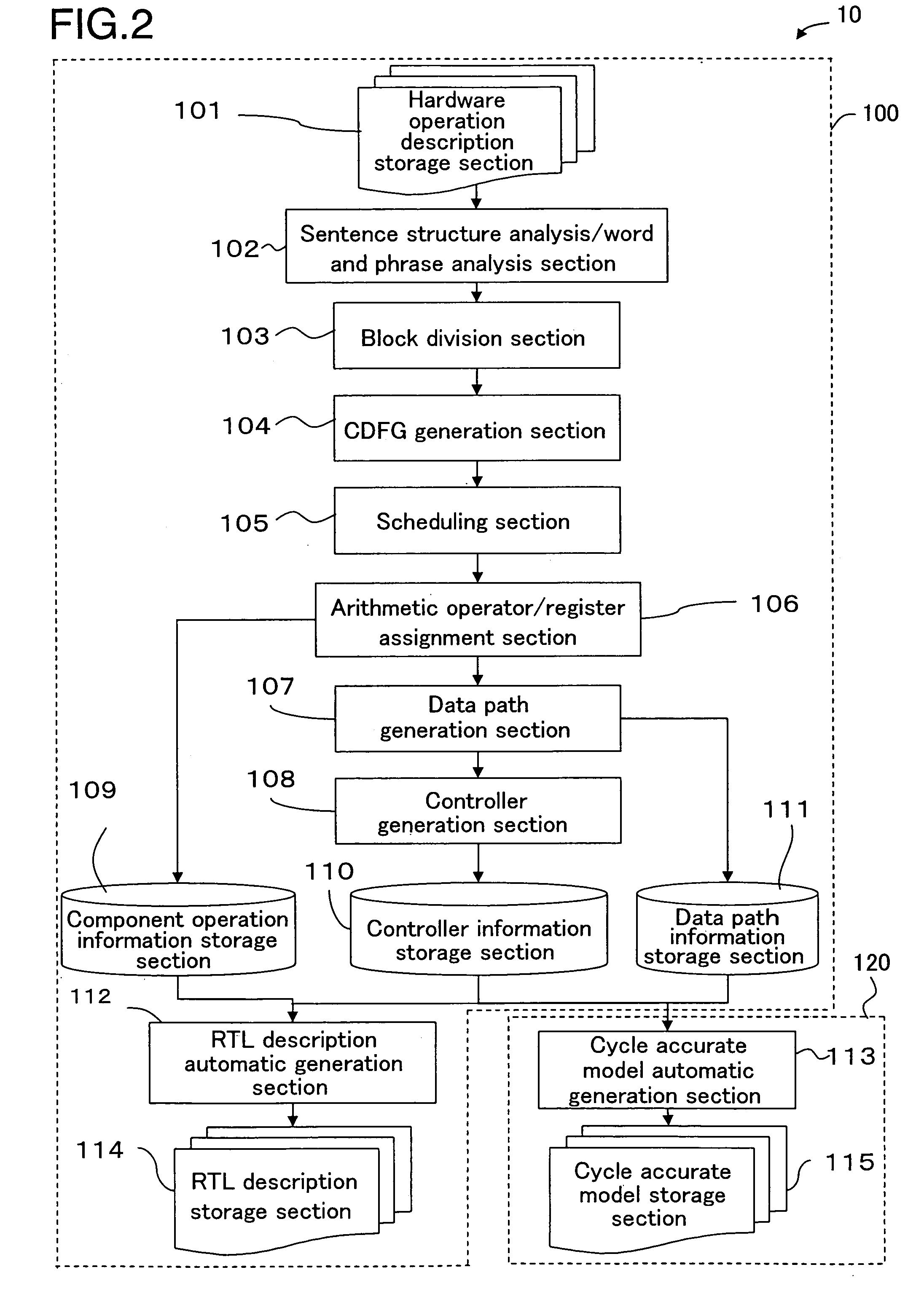

High level synthesis method and high level synthesis apparatus

InactiveUS7194724B2High frequencyCAD circuit designSoftware simulation/interpretation/emulationSynthesis methodsOperating system

Owner:SOCIONEXT INC

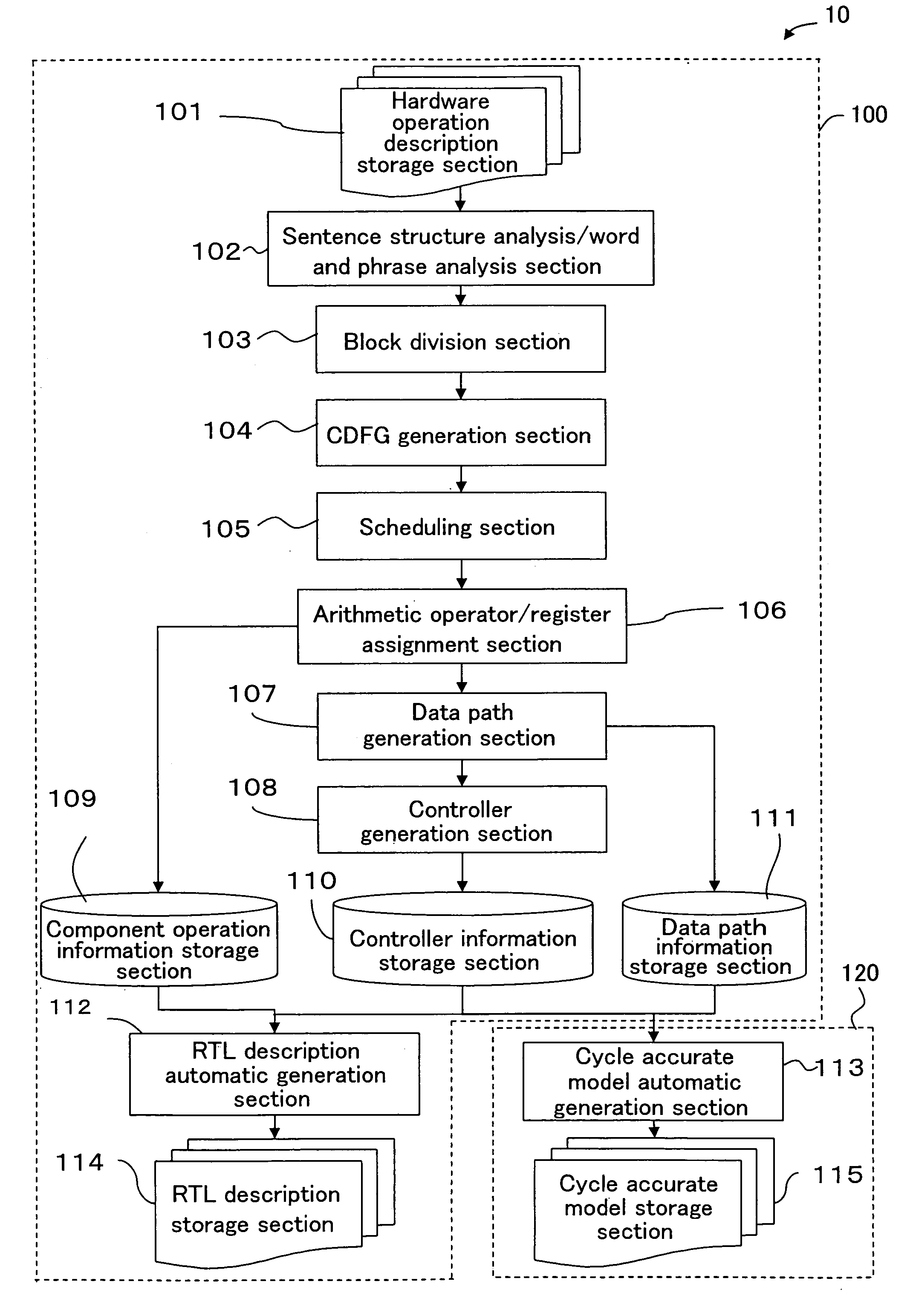

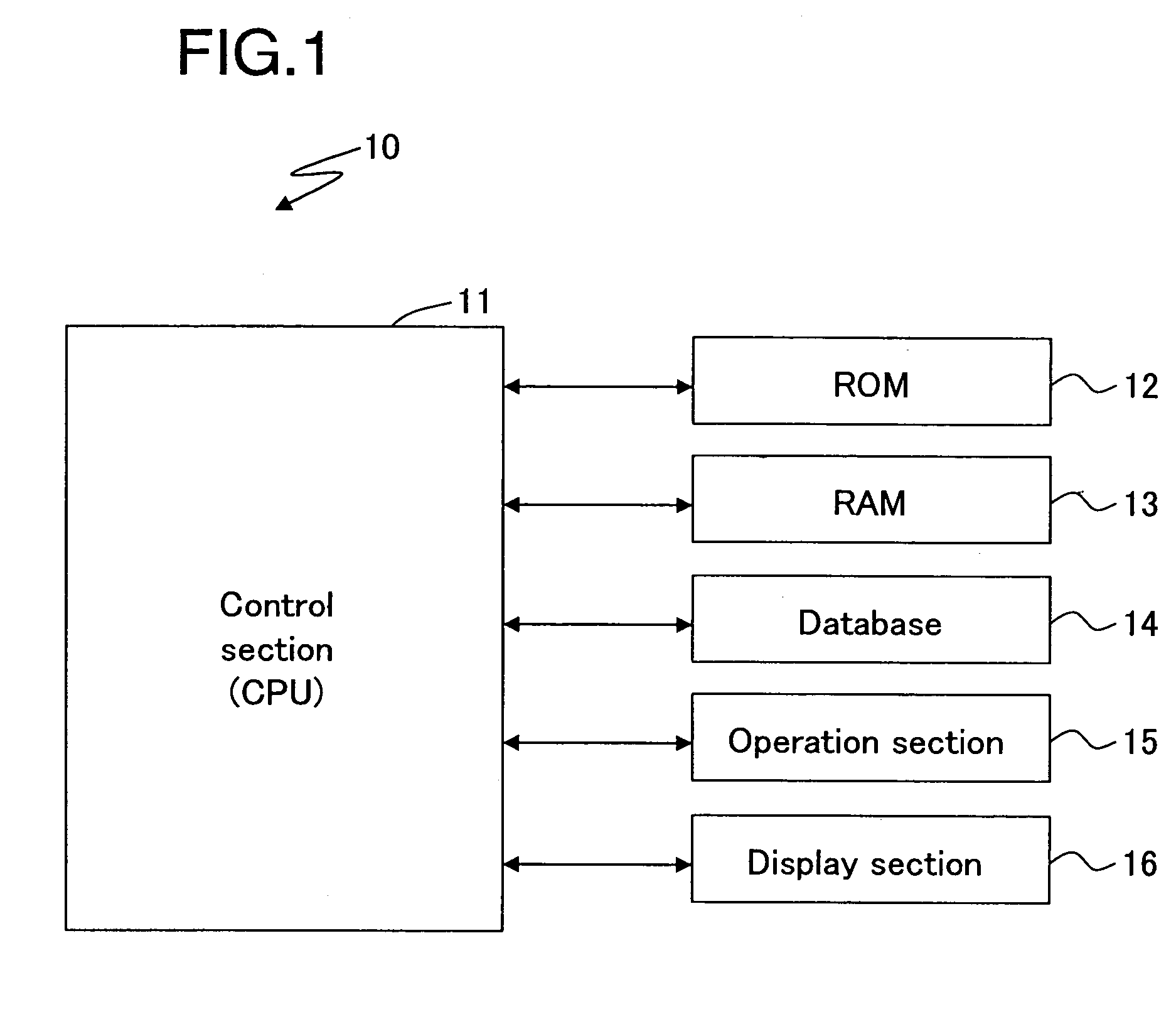

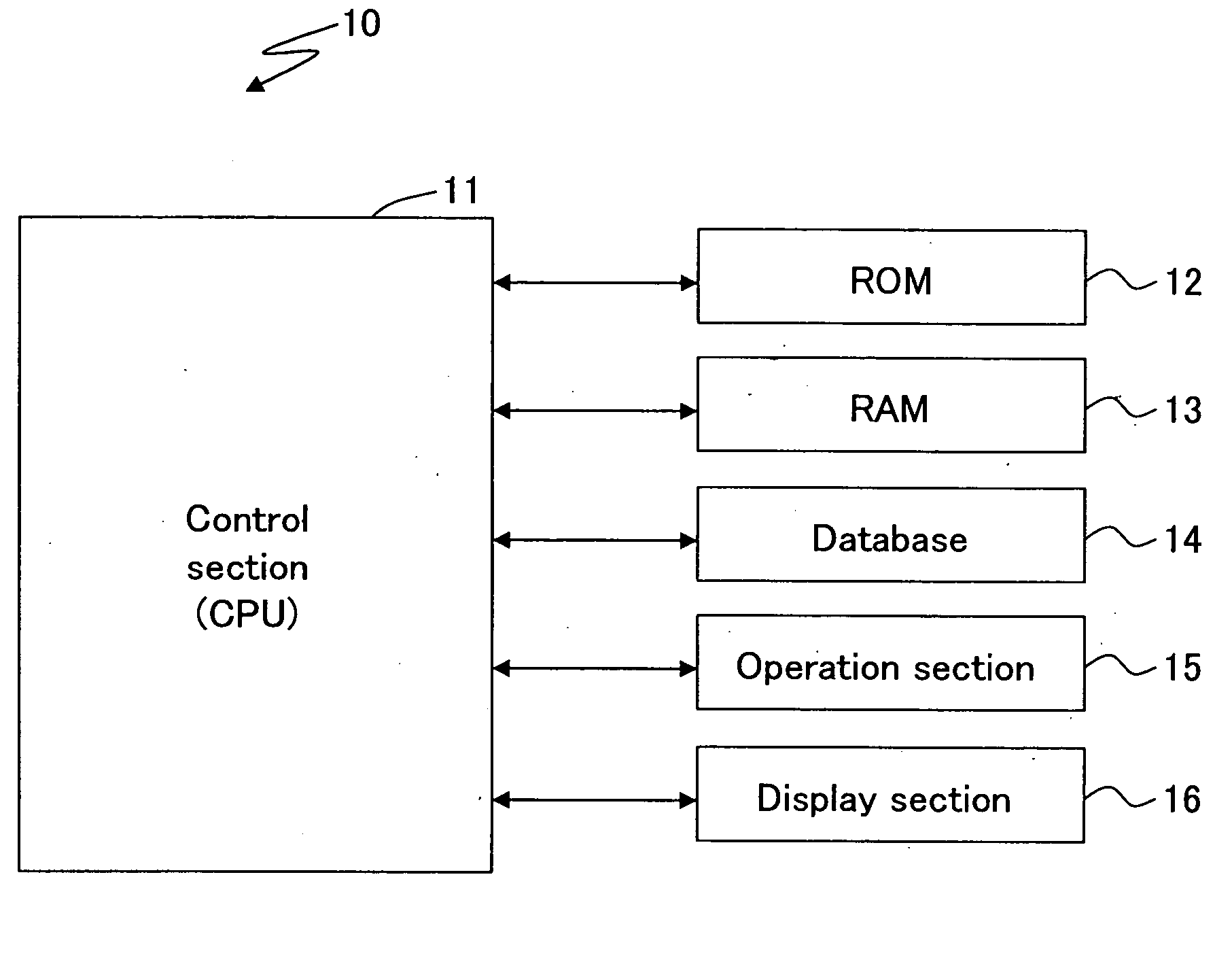

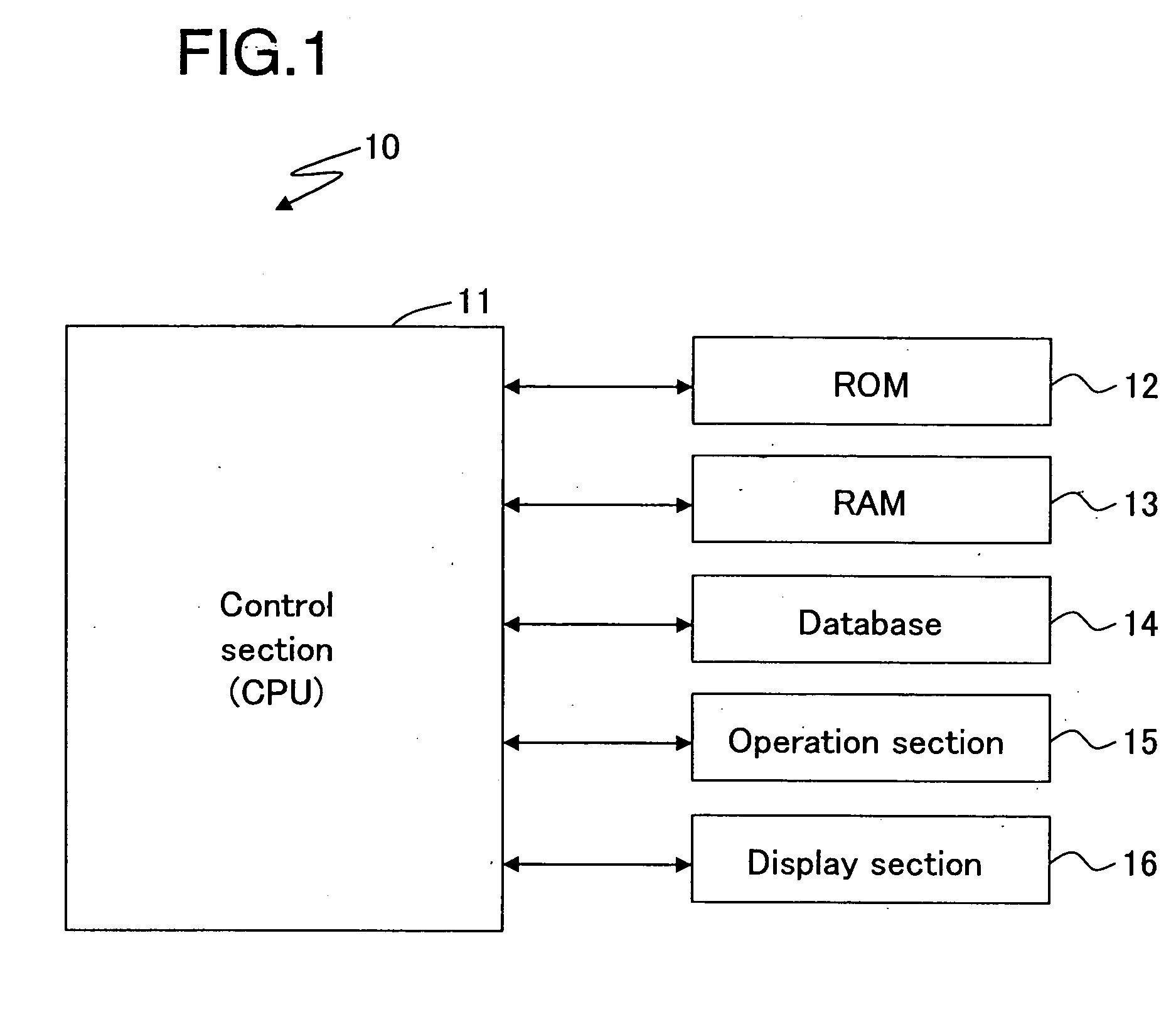

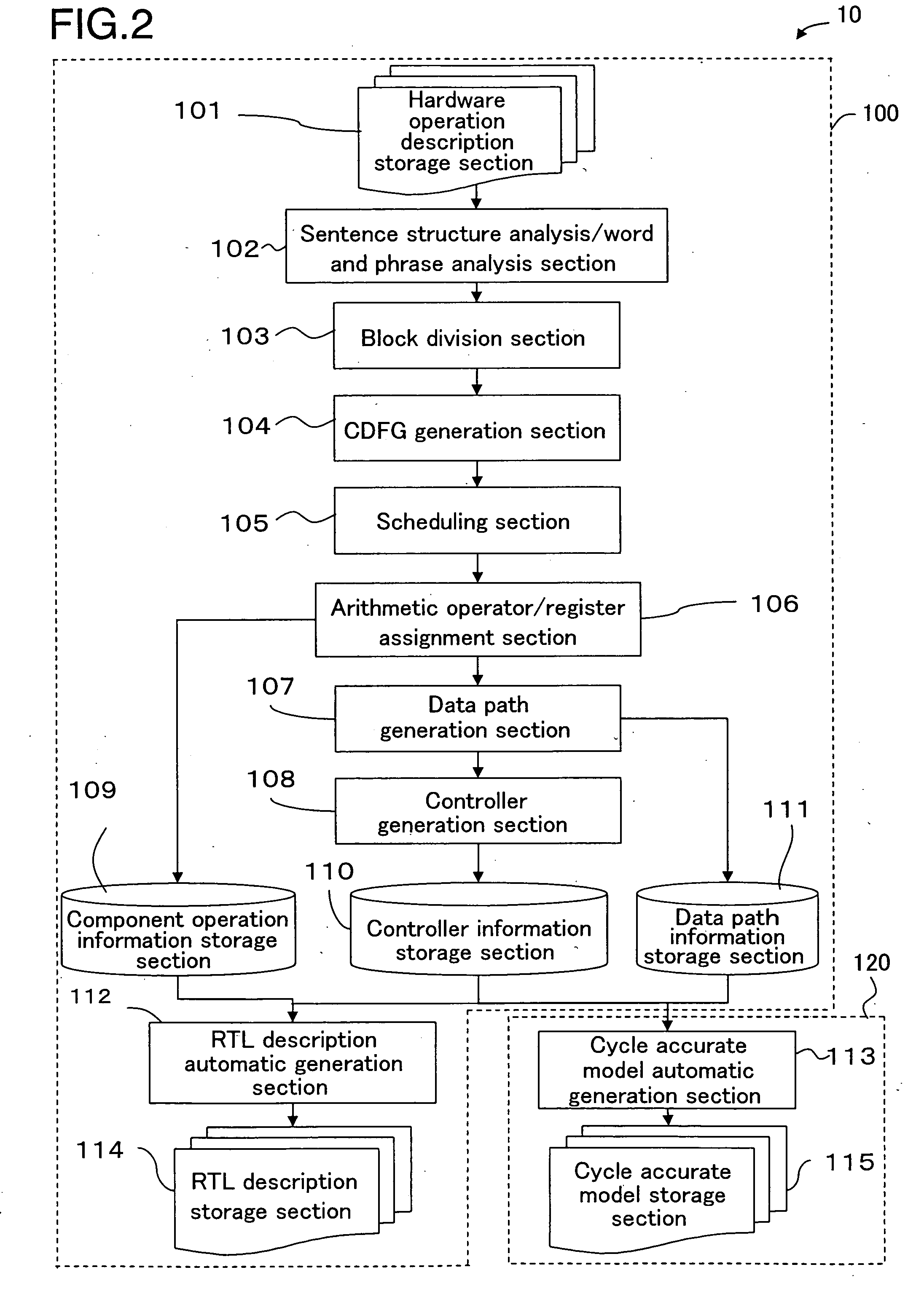

High level synthesis device, method for generating a model for verifying hardware, method for verifying hardware, control program, and readable recording medium

ActiveUS7266791B2Improve performanceSimple designCAD circuit designSoftware simulation/interpretation/emulationComputer hardwareHigh-level synthesis

A high level synthesis device includes a high level synthesis section and a cycle accurate model. The high level synthesis section may perform high level synthesis of hardware including a plurality of components and a controller for controlling the plurality of components. The cycle accurate model may be configured to verify a state of at least one of the plurality of components and the controller at a cycle accurate level, with a general-purpose programming language.

Owner:SHARP KK

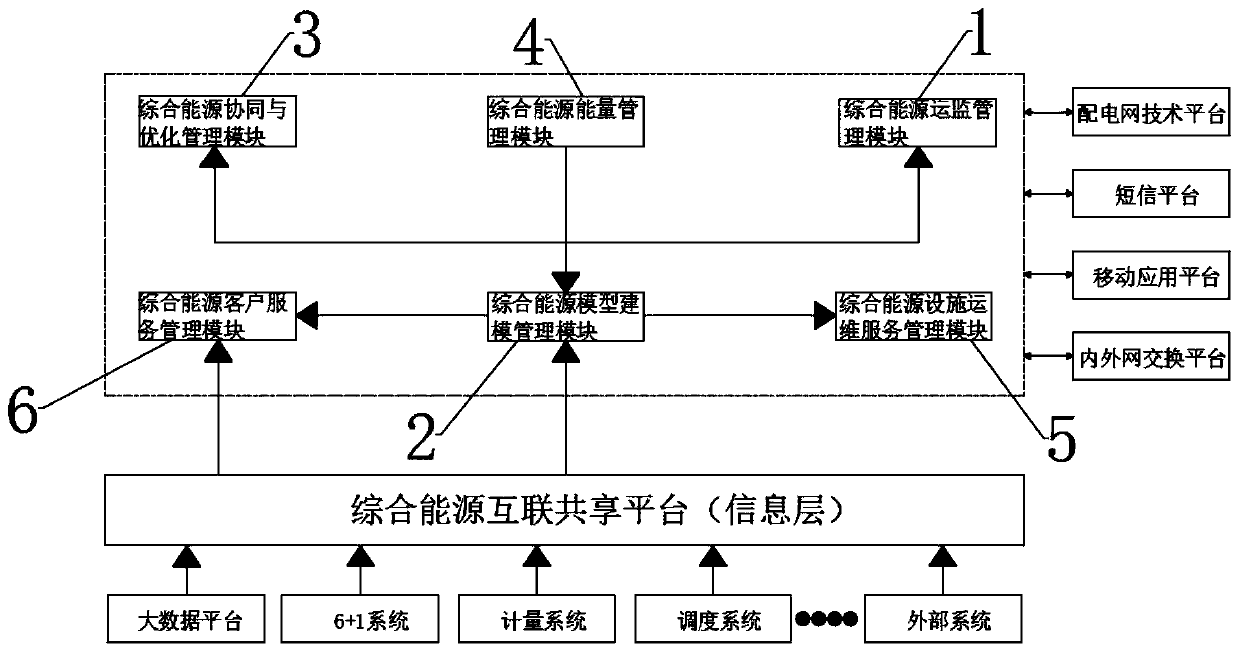

User-oriented intelligent information interaction platform for comprehensive energy system

PendingCN110414849AAchieve transformationRealize the cultivation of related industriesEnergy industryResourcesNew energyTotal energy

The invention discloses a user-oriented intelligent information interaction platform for a comprehensive energy system. The platform comprises a comprehensive energy system intelligent information interaction platform based on a micro-service architecture, a big data analysis technology and a container technology. An advanced comprehensive energy application system is arranged on the comprehensiveenergy system intelligent information interaction platform; according to the invention, interconnection and sharing of various kinds of energy information in the park are realized; the requirements of operation management and service of various energy sources in the park are met; an integrated information interaction platform of a comprehensive energy station and a park high-reliability power grid is constructed; a basis is provided for park energy facility operation management and public energy service; finally, the distributed renewable energy sources are vigorously popularized, the energystructure of the demonstration area is optimized, the safety is high when the user uses the system, the energy utilization rate can be increased, the total energy consumption is reduced, demonstrationarea energy transformation and related industry cultivation are achieved, healthy development of a new energy industry chain and business model innovation are promoted, and the application prospect is wide.

Owner:GUANGDONG POWER GRID CO LTD +1

Method and apparatus for improving the interconnection and multiplexing cost of circuit design from high level synthesis using ant colony optimization

ActiveUS20120084743A1Strengthen interconnectionImproving multiplexing costComputer aided designSoftware simulation/interpretation/emulationNODALMultiplexing

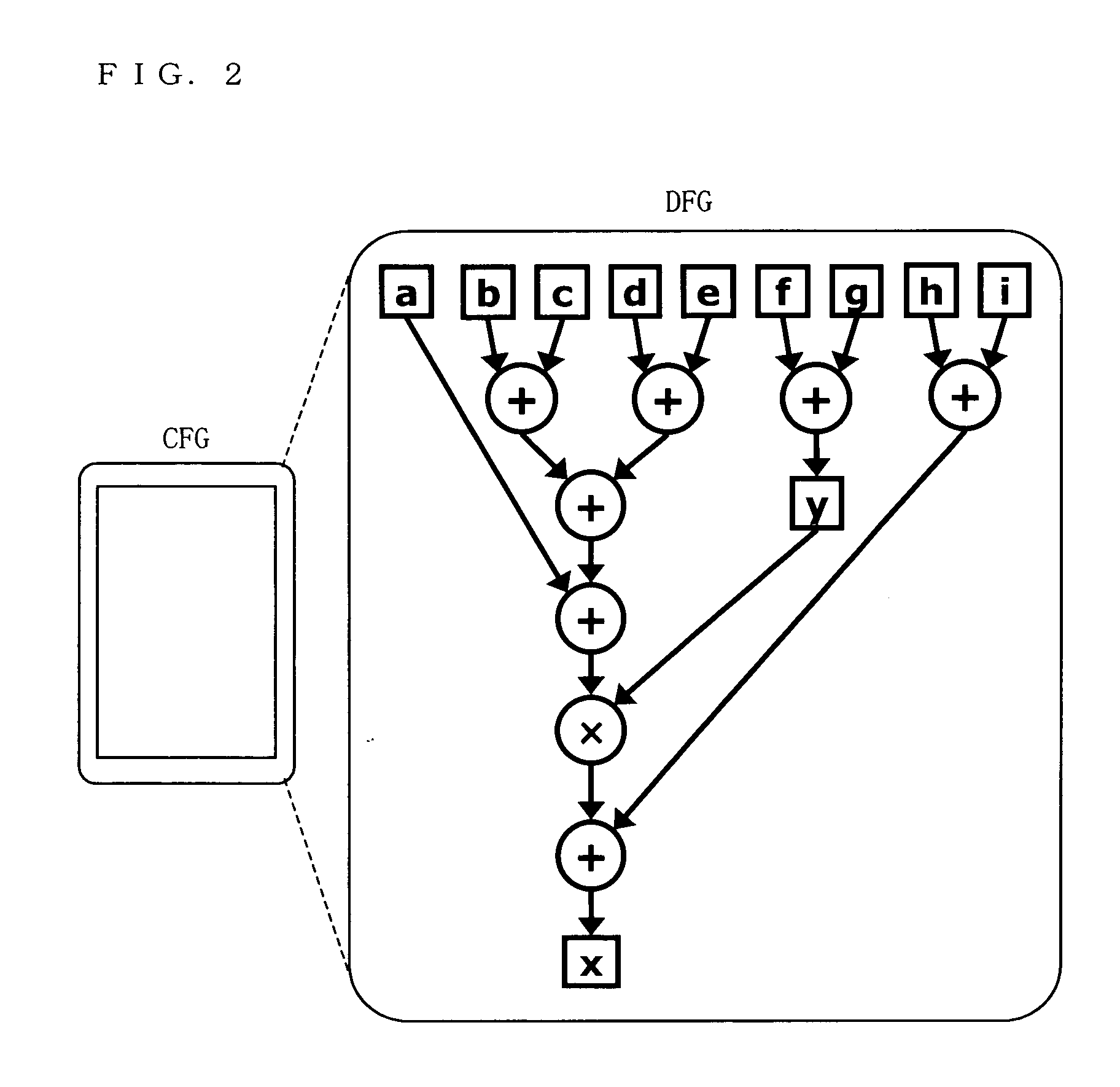

A method and apparatus for improving the interconnection and multiplexing cost of circuit design from high level synthesis using ant colony optimization is described. In one example, a plurality of hardware components for performing an operation is represented with a data flow graph having edges and nodes. A plurality of solutions are simulated for performing the operation as hardware component and schedule combinations represented as paths on the data flow graph. For each solution, cost including a number of edges and nodes traversed on the data flow graph and an interconnection cost related to the number of different hardware components in the path is determined. A pheromone trail is associated with each path, the pheromone trail including a cost of the respective scheduling solution, and a solution is selected with the highest value pheromone trail as a hardware component and schedule combination for a circuit.

Owner:SYNOPSYS INC

Method and apparatus for allocating data paths to minimize unnecessary power consumption in functional units

InactiveUS20070028198A1Minimum unnecessary power consumptionReduce unnecessary power consumptionCAD circuit designSoftware simulation/interpretation/emulationRegister transfer level designComputer architecture

A method and apparatus to produce high-level synthesis Register Transfer Level designs utilises power management formulations can be used to gear the allocation process to generate hardware architecture of minimal spurious switching. Bipartite weighted Assignment is used to determine the sharing of functional units, through cost formulations and the Hungarian Algorithm.

Owner:PANASONIC CORP

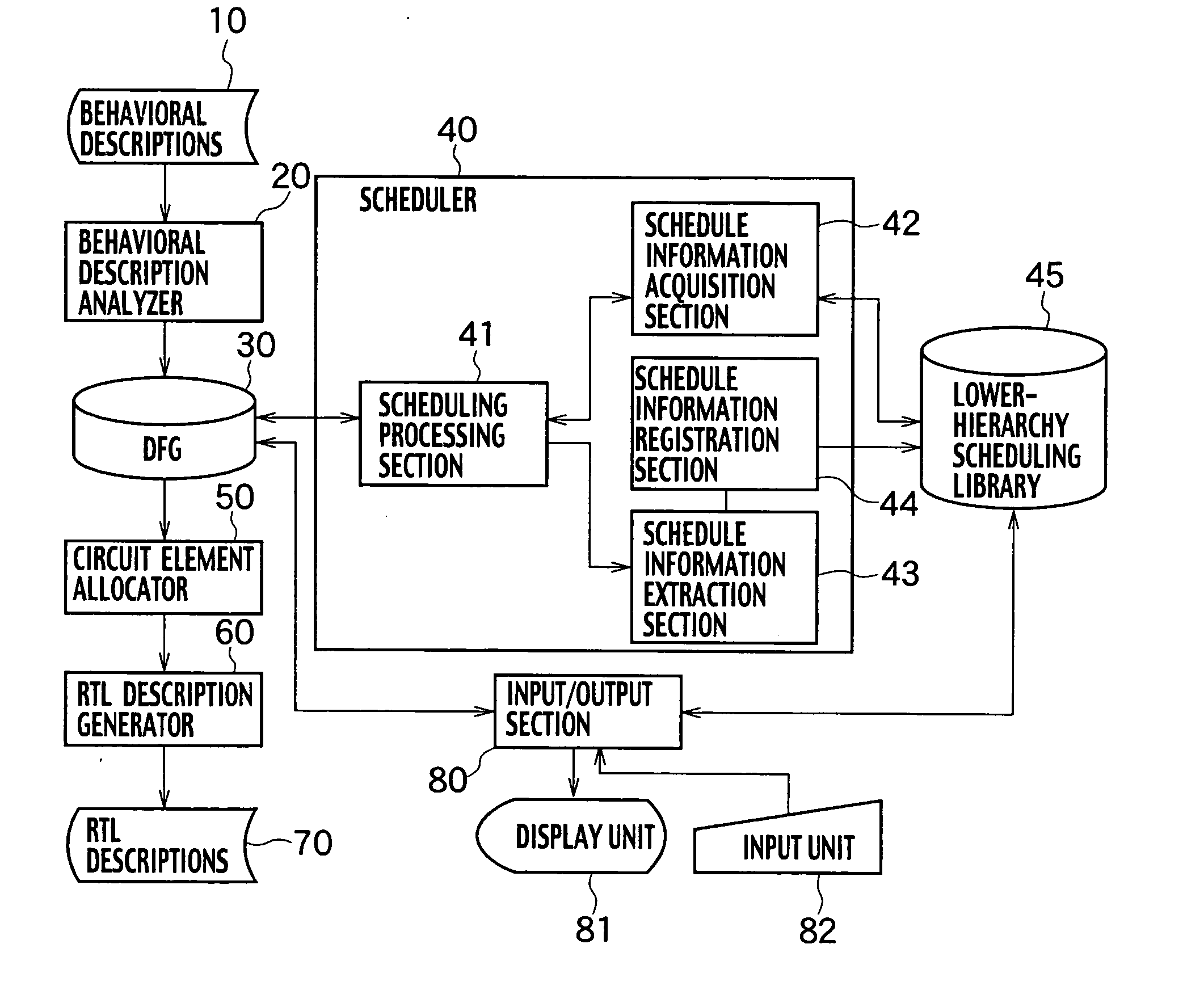

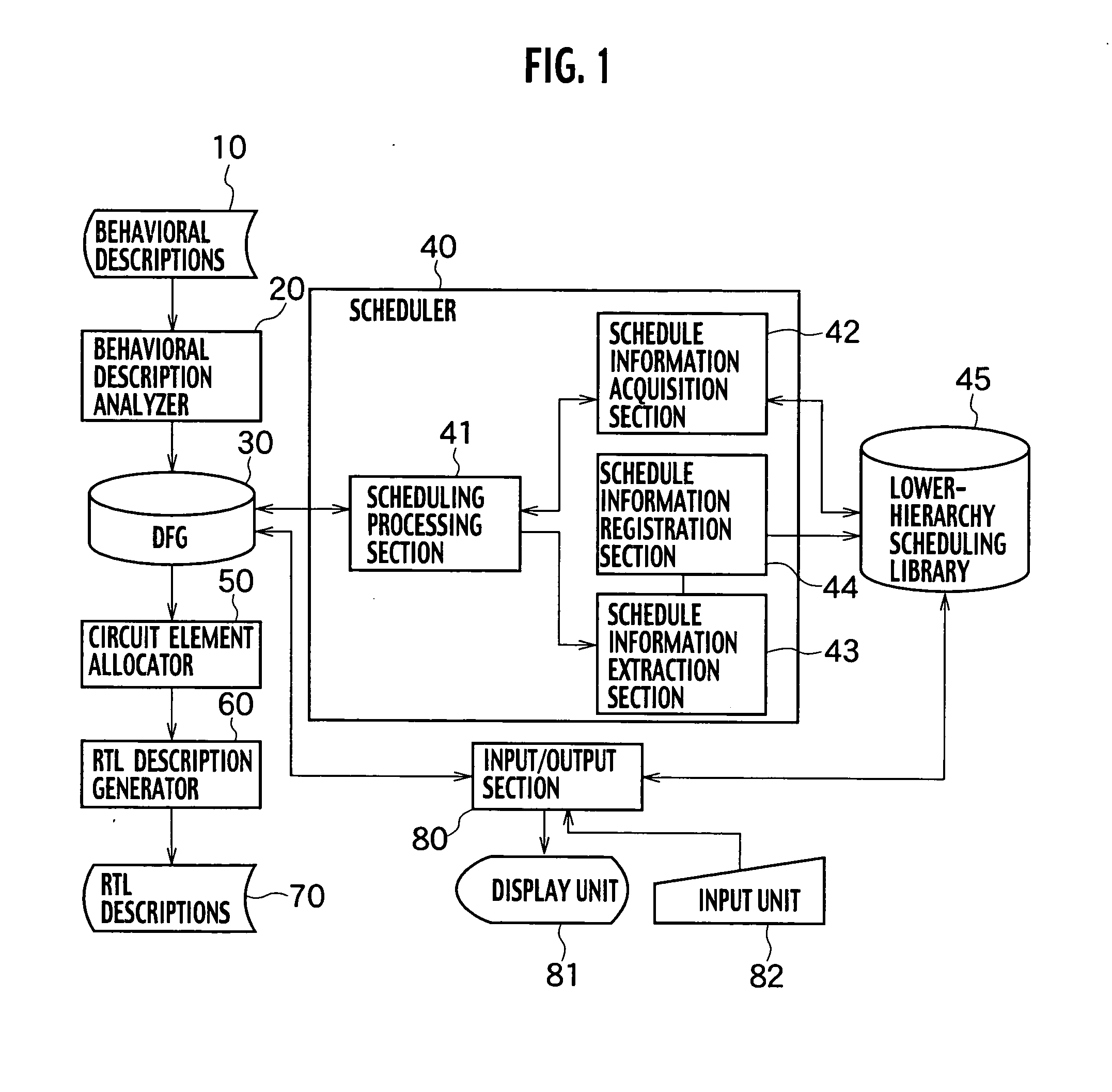

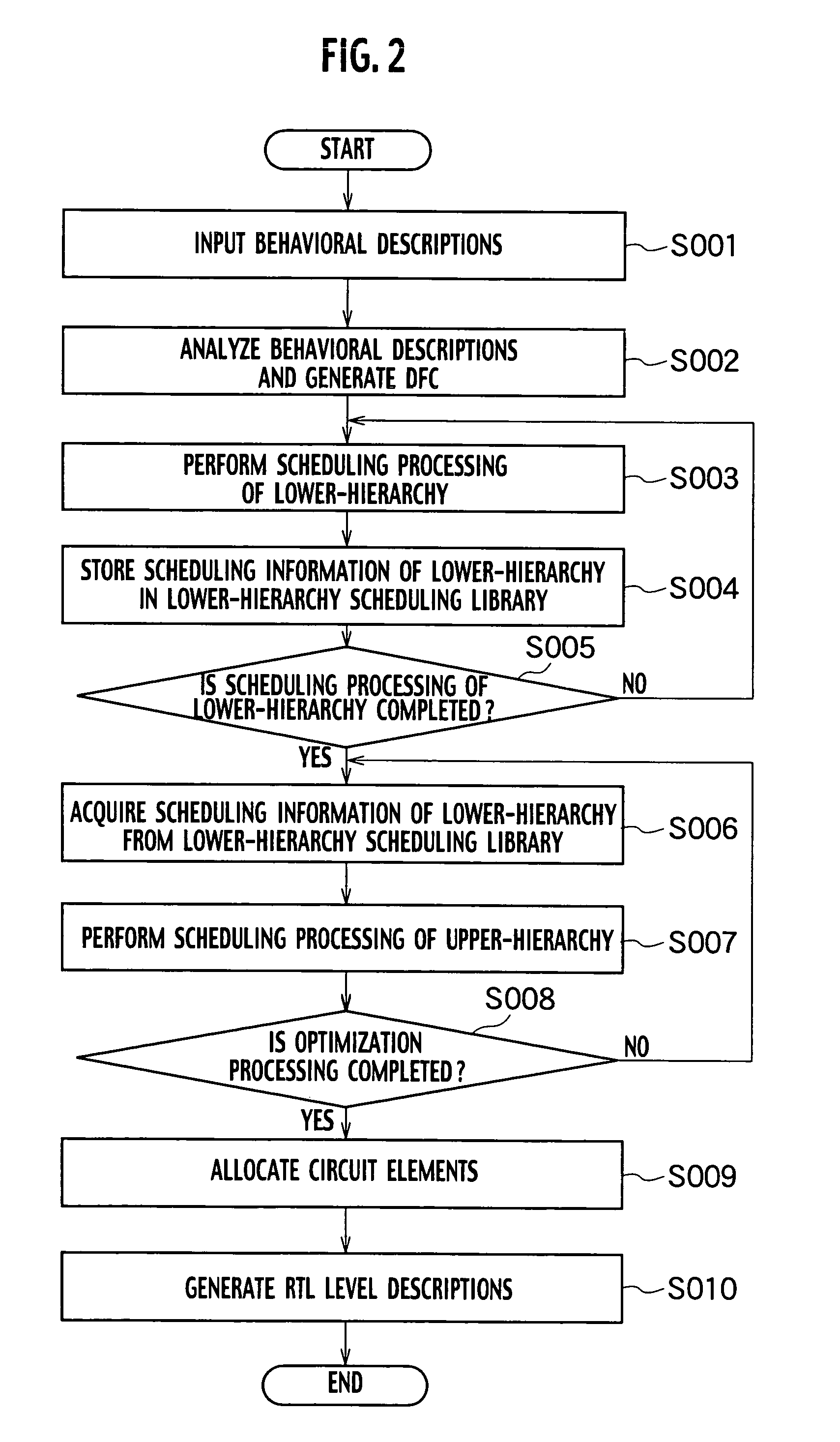

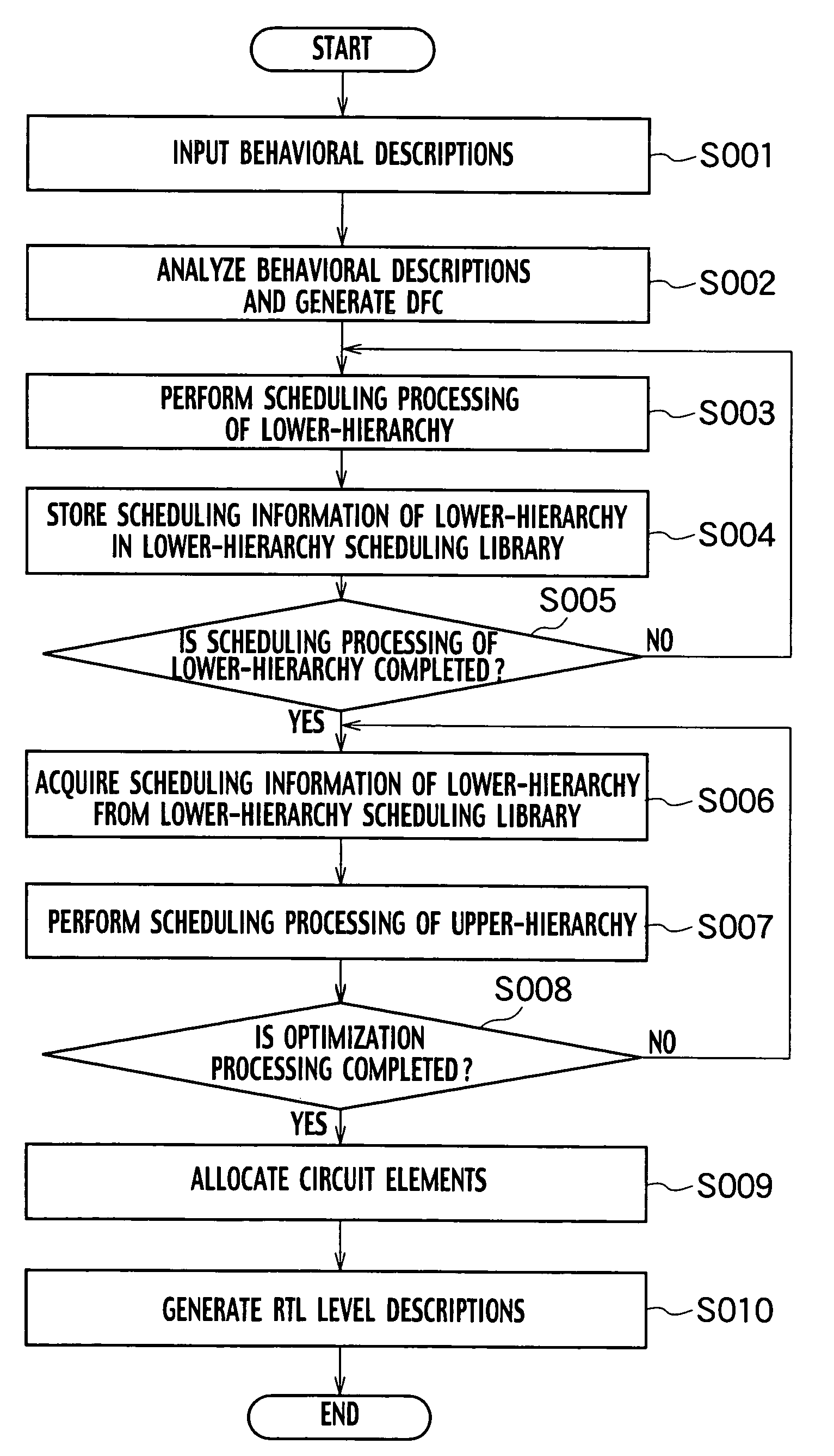

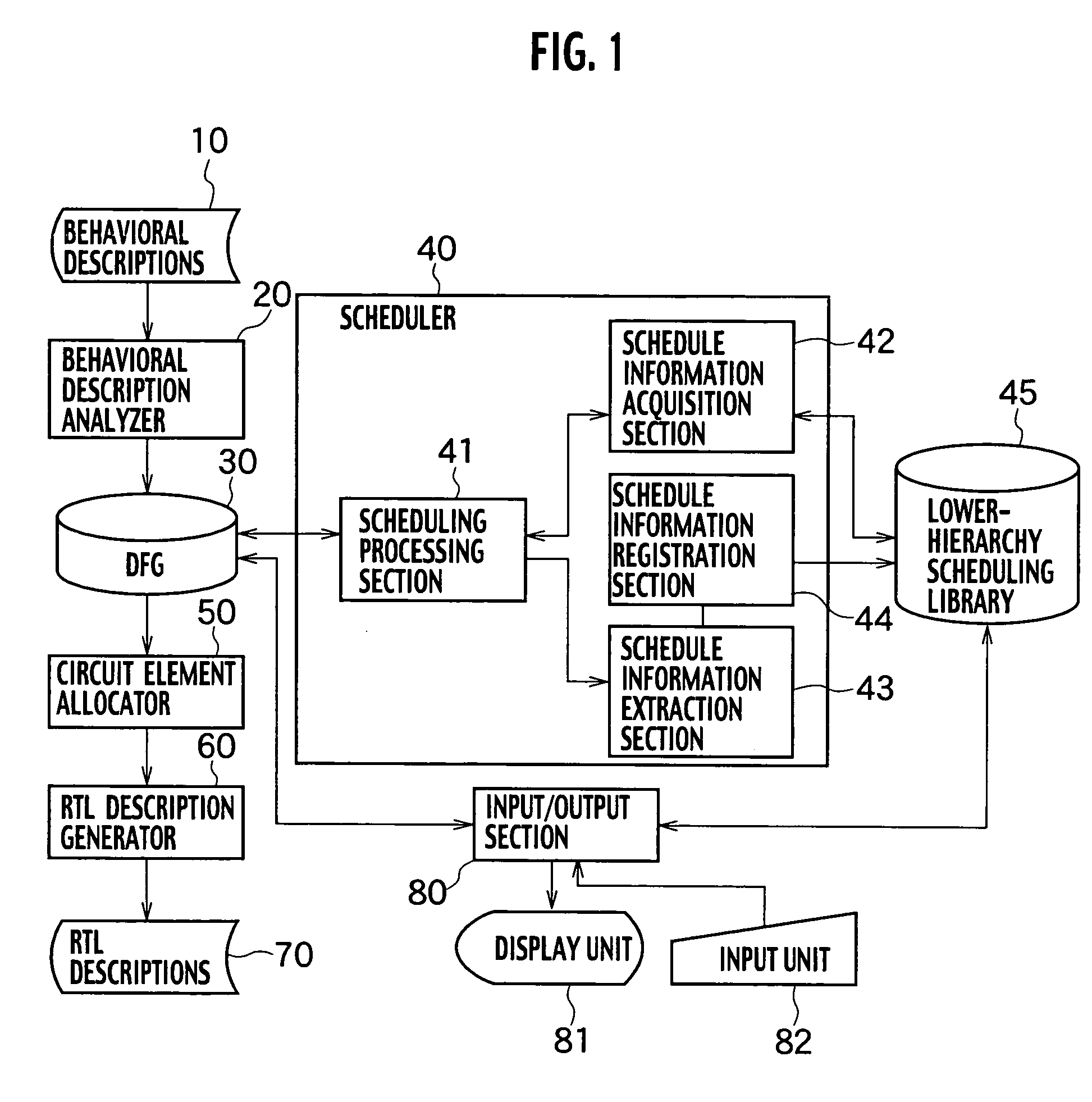

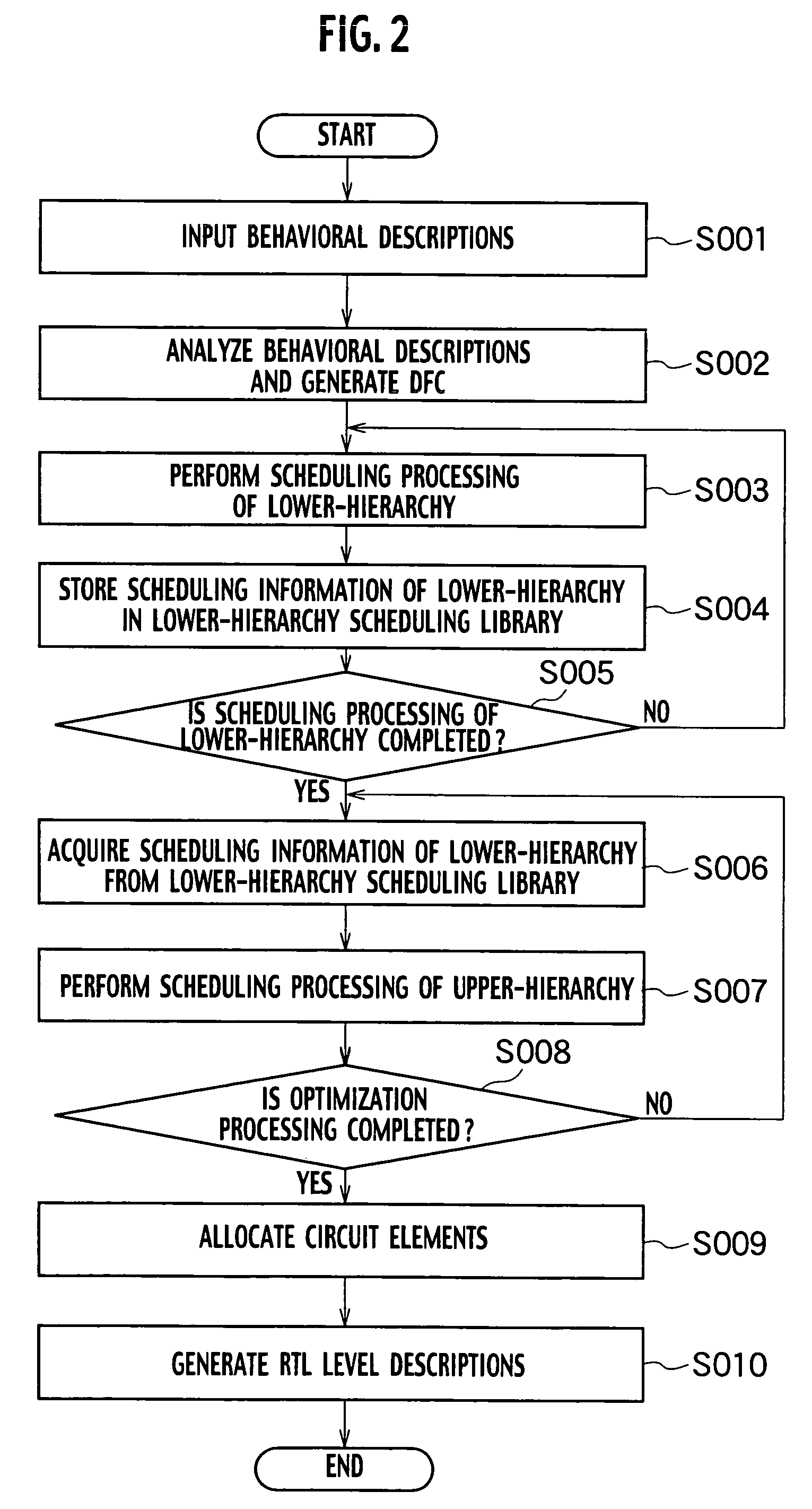

Scheduler, method and program for scheduling, and apparatus for high-level synthesis

InactiveUS20050144581A1CAD circuit designSoftware simulation/interpretation/emulationParallel computingInformation acquisition

A scheduler includes: a schedule information acquisition section configured to acquire the number of first clock cycles and the number of second clock cycles as schedule information of a function belonging to a lower-hierarchy, the number of the first clock cycles being the number of clock cycles after an execution of the function is started until an input data of the function is used, the number of the second clock cycles being the number of clock cycles after an output data of the function is outputted until the execution of the function is completed; and a scheduling processing section configured to obtain operations executable in the first clock cycles and operations executable in the second clock cycles from among operations belonging to an upper-hierarchy for calling the function, based on the acquired schedule information, and to schedule the upper-hierarchy ensure that the obtained operations execute in parallel with the function.

Owner:KK TOSHIBA

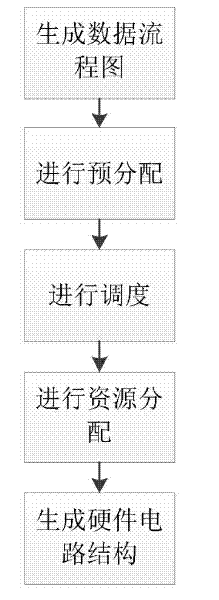

High-level synthesis method and system

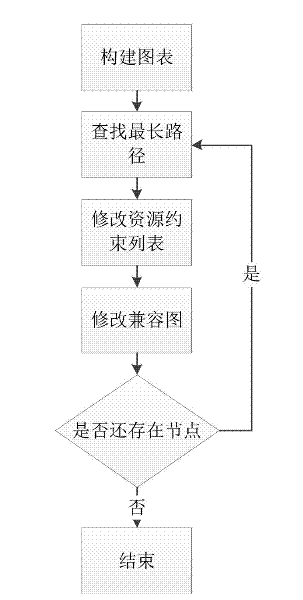

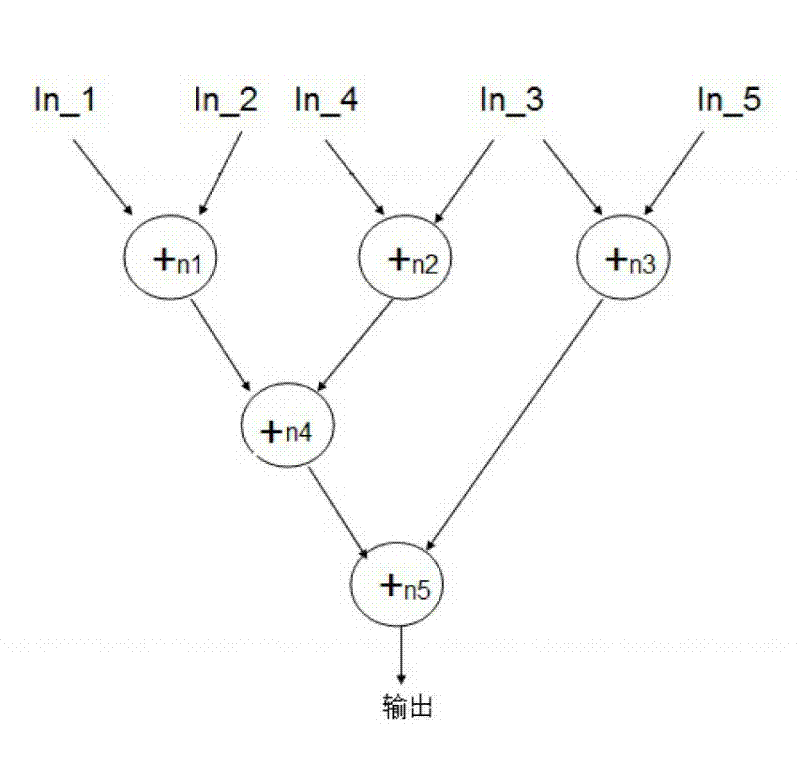

InactiveCN102419789AQuick buildReduce interconnect overheadSpecial data processing applicationsComputer architectureInterconnection

The invention discloses a high-level synthesis method and a high-level synthesis system. The system comprises a data flow chart generation unit, a pre-allocation unit, a scheduling unit, a resource allocation unit and a circuit generation unit. The method comprises the following steps of: firstly, acquiring behavior description of a digital circuit; secondly, generating a data flow chart; thirdly, pre-allocating hardware resources; fourthly, generating a resource constraint list; sixthly, performing scheduling and resource allocation; and finally, generating a hardware circuit structure. By adoption of the method and the system, during the scheduling, number information of the hardware resources is scheduled, information of hardware interconnection is also scheduled, and manual determination of schedule restraints can be avoided, therefore, the hardware circuit structure can be generated more quickly, and the interconnection overhead in the hardware circuit structure is effectively reduced. The high-level synthesis method and the high-level synthesis system are widely applied in the field of designing the hardware circuit structure.

Owner:SUN YAT SEN UNIV

High-level synthesis apparatus, high-level synthesis system and high-level synthesis method

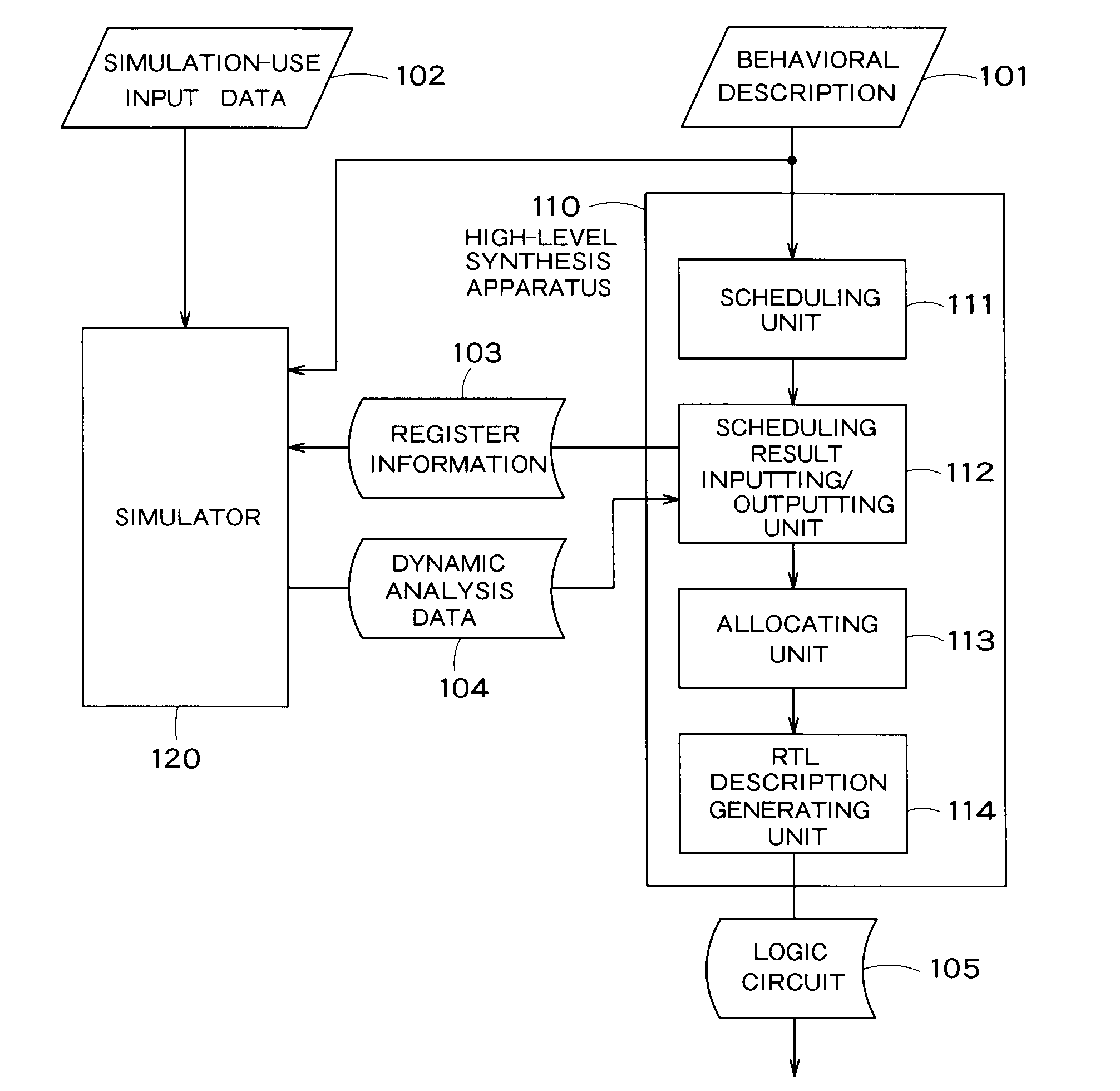

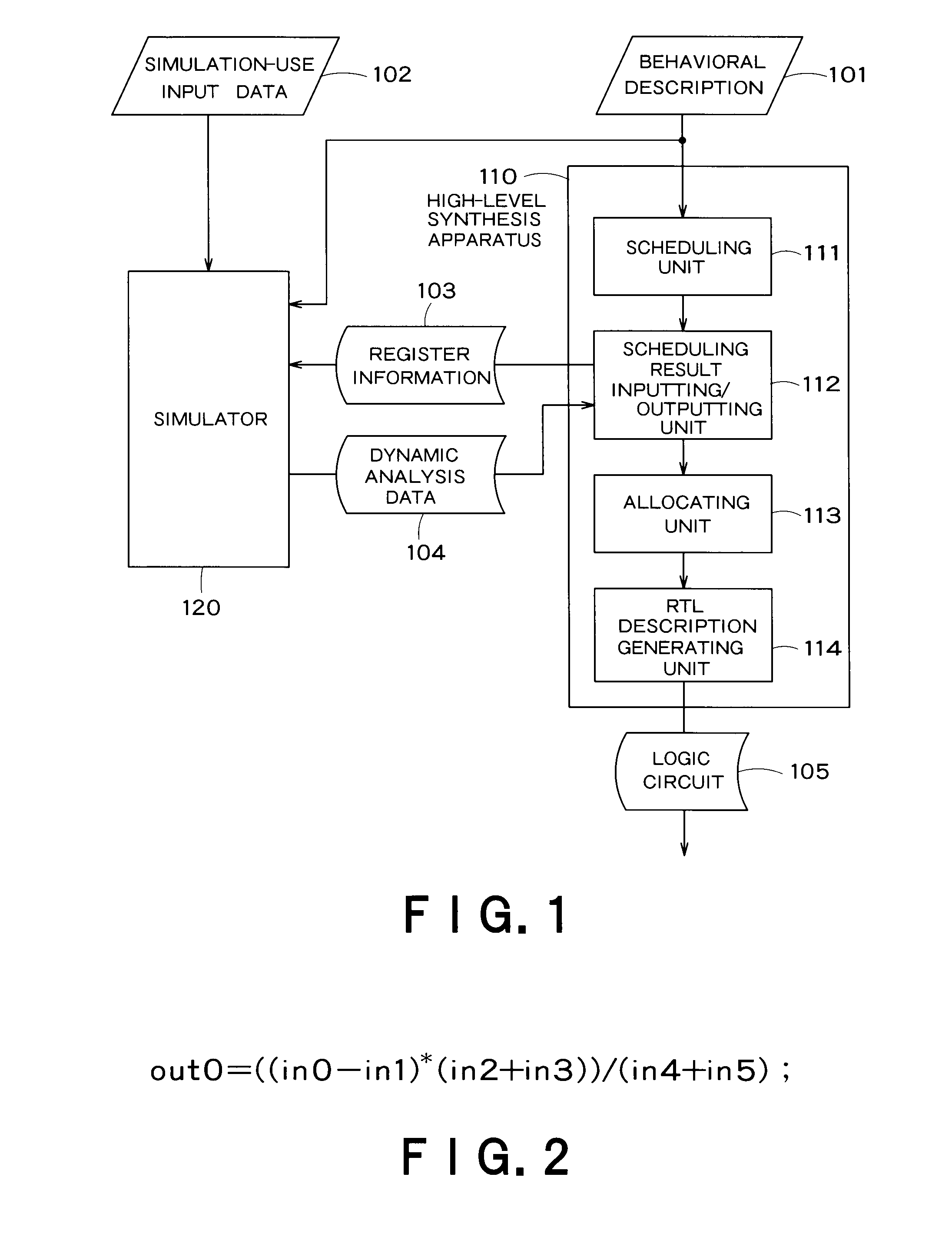

InactiveUS20090164967A1Detecting faulty computer hardwareCAD circuit designAnalysis dataProcessor register

A high-level synthesis apparatus for automatically generating a register transfer level (RTL) logic circuit from a behavioral description has a scheduling unit configured to perform data flow analysis and scheduling to generate a data flow graph showing an operation cycle of an operation from the behavioral description, a scheduling result inputting / outputting unit configured to extract a point to be allocated to a register from the data flow graph and output register information indicating the point, the scheduling result inputting / outputting unit being provided with dynamic analysis data that includes at least one of the number of times that data at the point has been substituted and the number of times that a value stored at the point has changed by a predetermined simulation, an allocating unit configured to consult dynamic analysis data and allocate circuit elements to the behavioral description, and an RTL description generating unit configured to generate the logic circuit based on the allocation of circuit elements by the allocating unit.

Owner:KK TOSHIBA

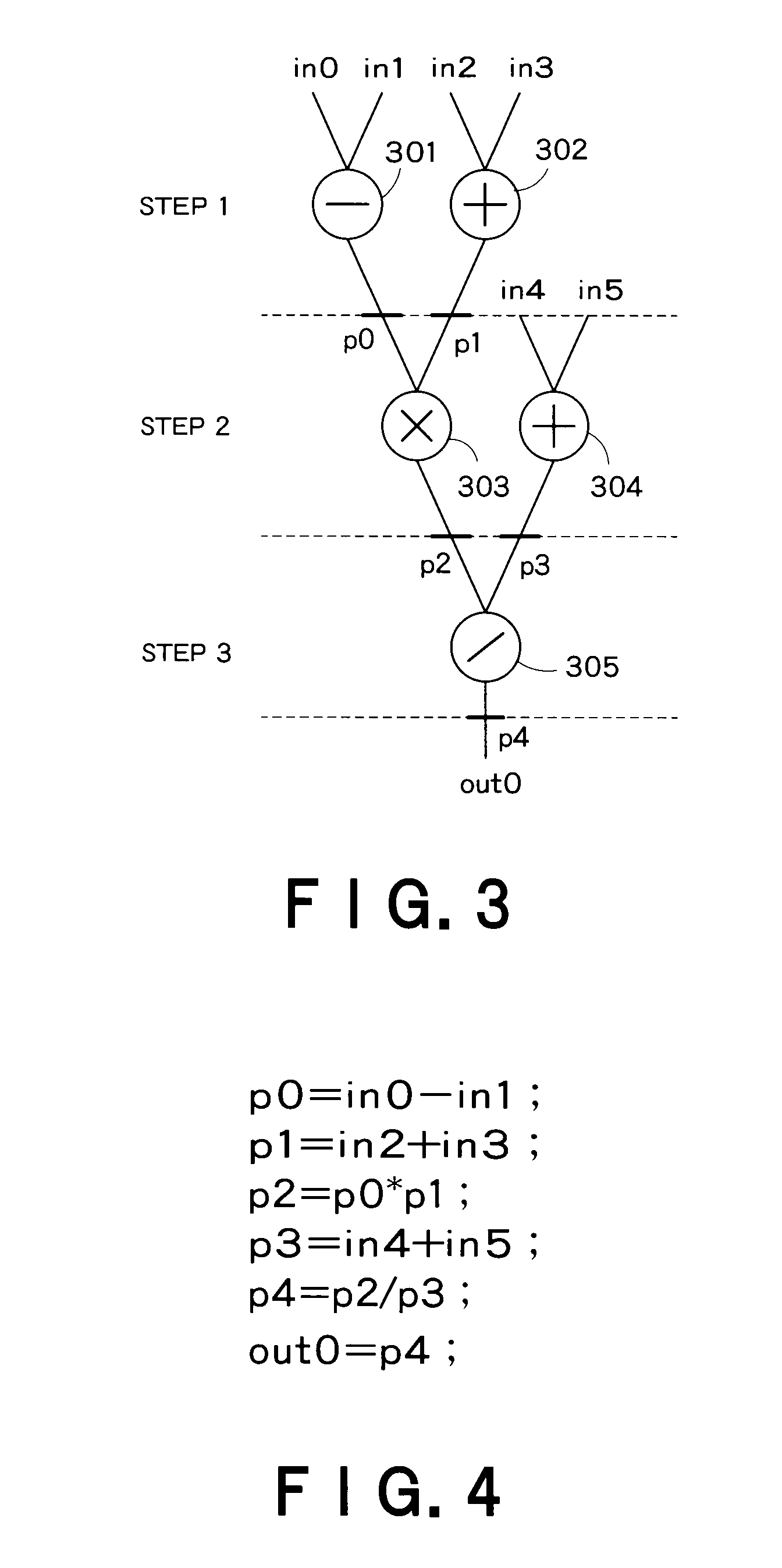

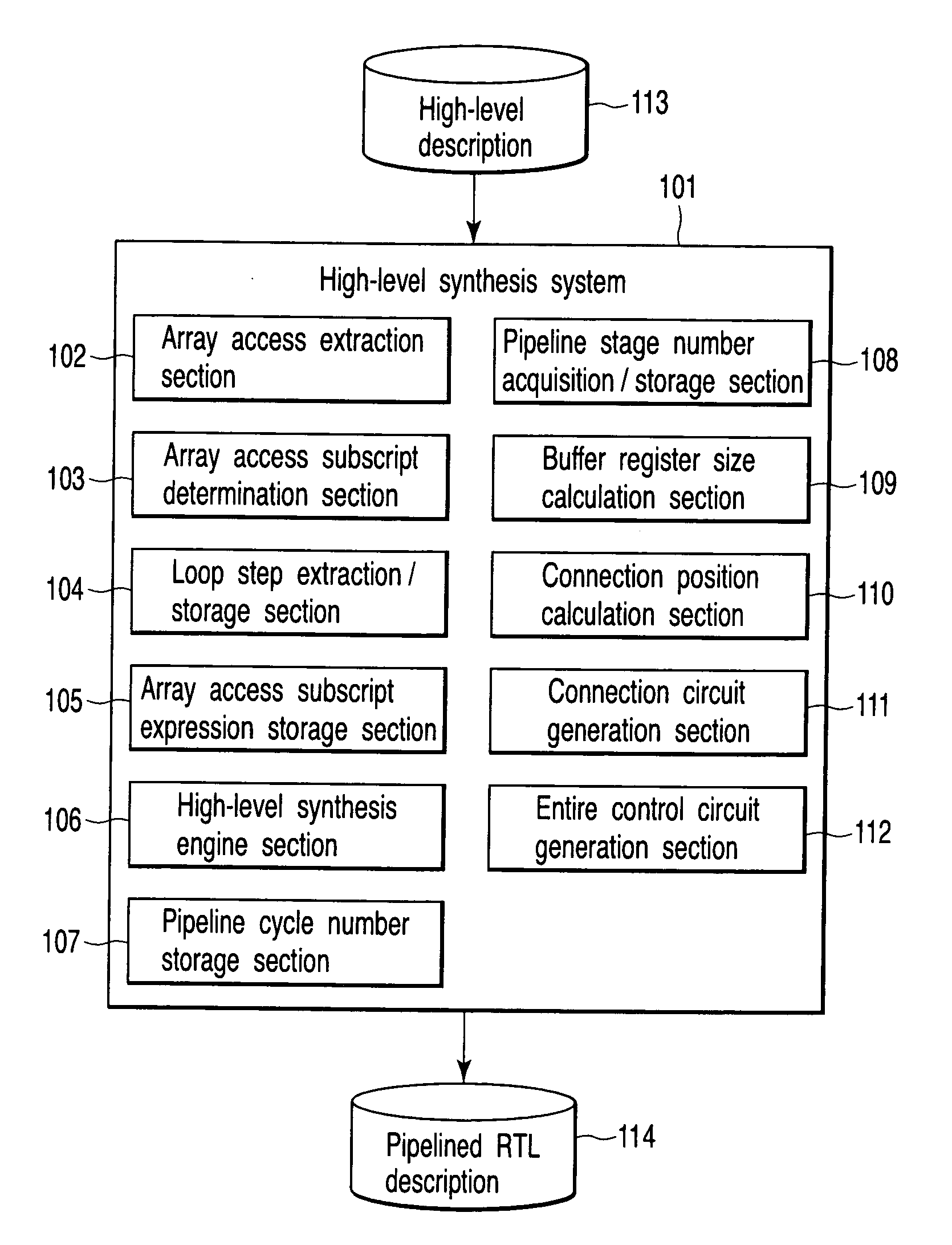

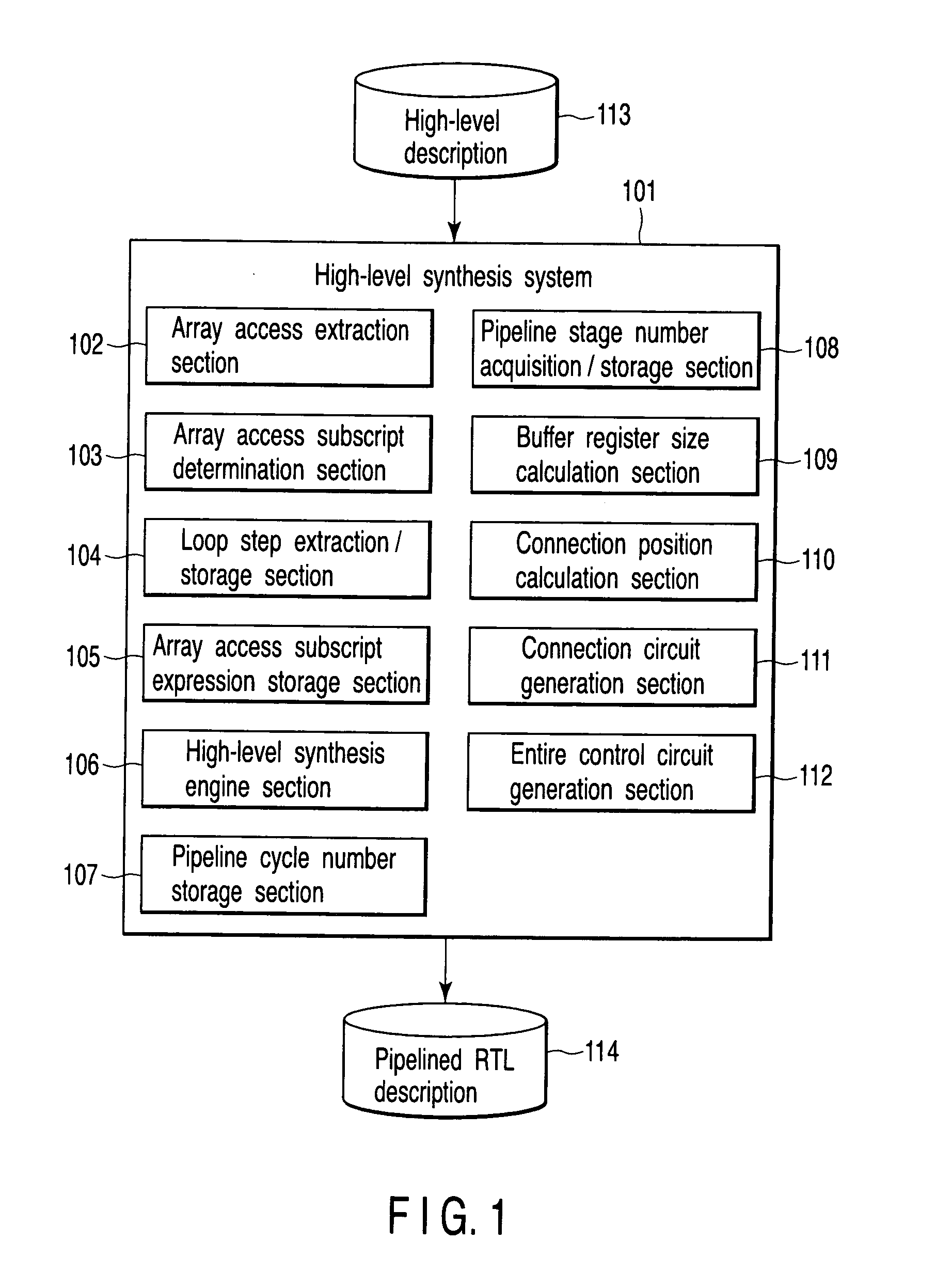

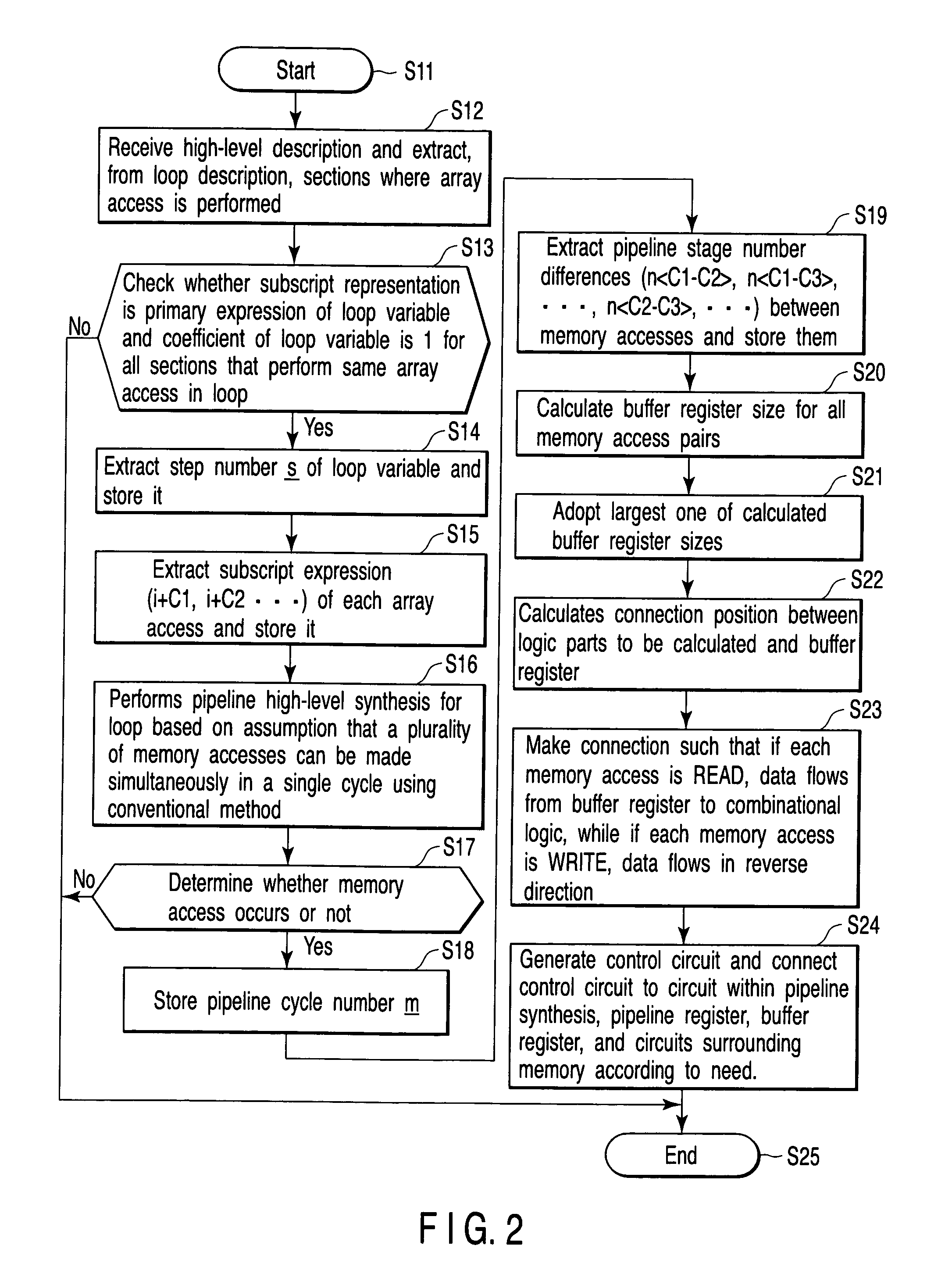

Pipeline high-level synthesis system and method

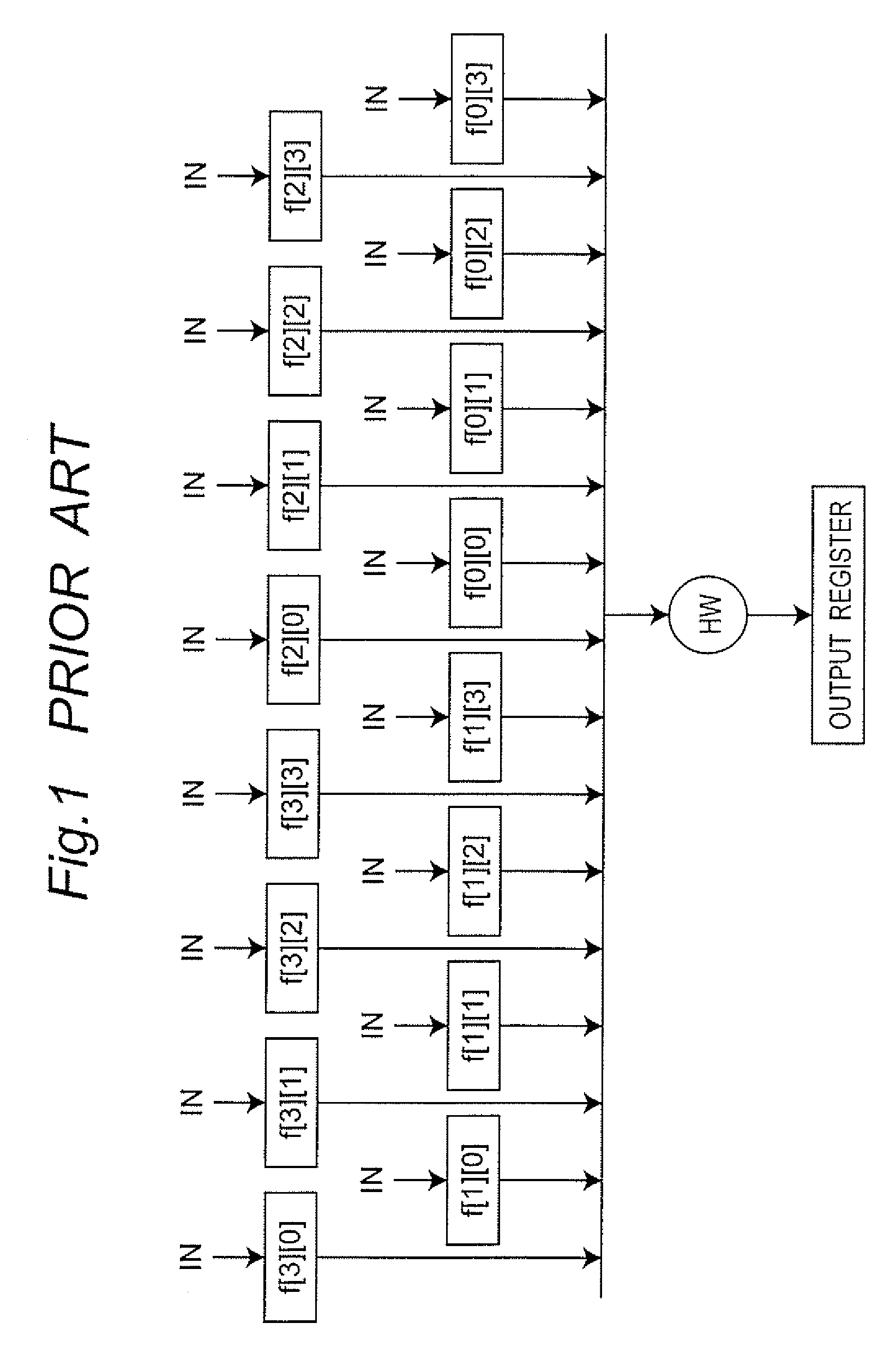

InactiveUS20070234267A1Computer aided designSpecial data processing applicationsShift registerParallel computing

According to one embodiment, a pipeline high-level synthesis system receives a high-level description and performs pipeline high-level synthesis for its loop description part to generate a pipelined circuit having a structure in which a plurality of combinational logic parts serially arranged are separated by pipeline registers. If a memory access conflict is caused by a plurality of combinational logic parts including memory accesses in the circuit generated by the first circuit section, the system allows the logic parts in which a memory access conflict occurs to access a memory through a shift register having a size corresponding to the combinational logic parts.

Owner:KK TOSHIBA

High level synthesis device, method for generating a model for verifying hardware, method for verifying hardware, control program, and readable recording medium

ActiveUS20050010387A1Increase speedSimple designCAD circuit designSoftware simulation/interpretation/emulationComputer hardwareHigh-level synthesis

A high level synthesis device includes a high level synthesis section for performing high level synthesis of hardware including a plurality of components and a controller for controlling the plurality of components; and a cycle accurate model generation section for generating a cycle accurate model, capable of verifying a state of at least one of the plurality of components and the controller at a cycle accurate level, with a general-purpose programming language.

Owner:SHARP KK

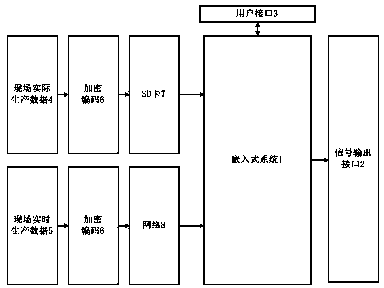

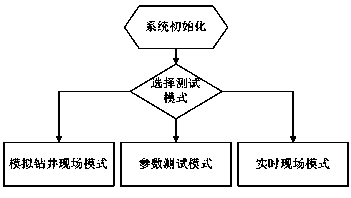

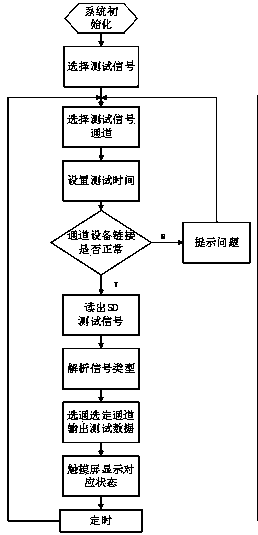

Method for debugging comprehensive logging instrument by means of simulating scene sensor signal

The invention discloses a method for debugging a comprehensive logging instrument by means of simulating a scene sensor signal. A method for simulating scene common station signals and outburst station signals and providing scene real-time data signals is provided, and the technical problem that a signal required by developing and debugging the comprehensive logging instrument and testing response capability of the comprehensive logging instrument to the sudden accident lacks is solved. The method is mainly and technically characterized by comprising the steps that scene practical production data are collected and summarized, the data are stored in an SD card through encryption and encoding, the data are processed through an embedded type system, and the data are output through a signal output interface; according to the scene real-time production data, the real-time data are transmitted to the embedded type system through a proprietary network after encryption and encoding, and the data are output through the signal output interface after being processed through the embedded type system. The situation is created for developing and debugging the comprehensive logging instrument, comprehensively testing the testing response capability of the comprehensive logging instrument to the sudden accident and developing the advanced comprehensive logging instrument.

Owner:SOUTHWEST PETROLEUM UNIV

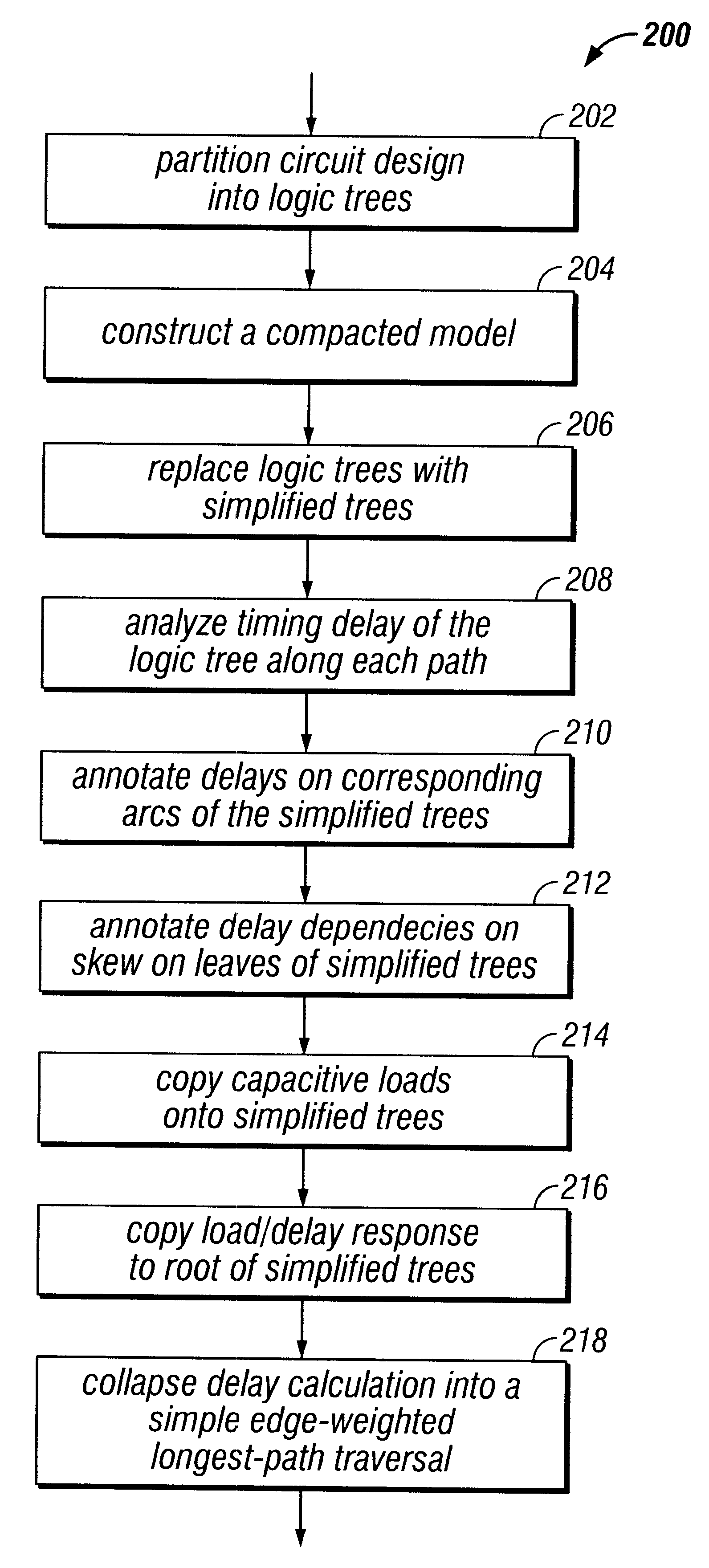

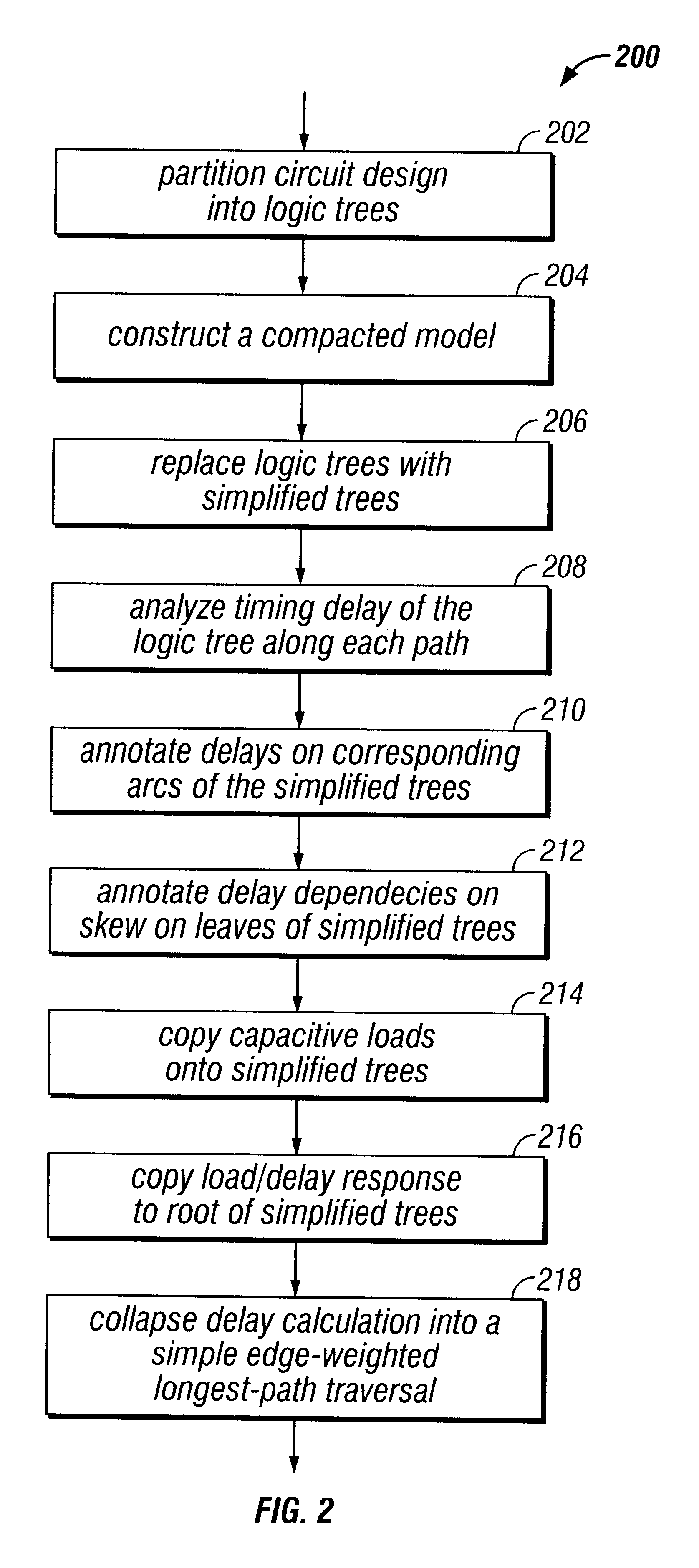

Method for timing analysis during automatic scheduling of operations in the high-level synthesis of digital systems

InactiveUS6516453B1Quicker timeCAD circuit designSoftware simulation/interpretation/emulationPropagation delayCapacitance

A design-timing-determination process for an electronic design automation system approximates the timing of a whole design quickly and on-the-fly. Such allows a scheduling system to construct operation schedules that are ultimately realizable. A timing analysis is applied each time an individual operation is scheduled, and may be called many times to get a single operation scheduled. A graph representing combinational logic is partitioned into a collection of logic trees with nodes that represent gates and terminals, and arcs that represent connections. A compacted model of each logic tree is constructed by replacing them with equivalent trees having no interior nodes. The timing of the original circuit is analyzed along each path from the leaves to the roots. A propagation delay for each path is determined, and such is annotated onto each corresponding arc of the simplified tree. Any dependency of the propagation delay in the original circuit on the slew rate of their input signals is annotated onto the corresponding leaf of the simplified tree. Capacitive loads can also be copied from the logic-tree leaves and annotated on the simplified-tree leaves. Any load / delay response curves of the output gate at the apex of the logic tree and is copied to the root of the simplified tree. The entire delay calculation is collapsed into a simple edge-weighted longest-path traversal, and is much simpler than trying to compute the slew rates and delays for each cell in a circuit.

Owner:CADENCE DESIGN SYST INC

Scheduler, method and program for scheduling, and apparatus for high-level synthesis

InactiveUS7181714B2CAD circuit designSoftware simulation/interpretation/emulationParallel computingInformation acquisition

Owner:KK TOSHIBA

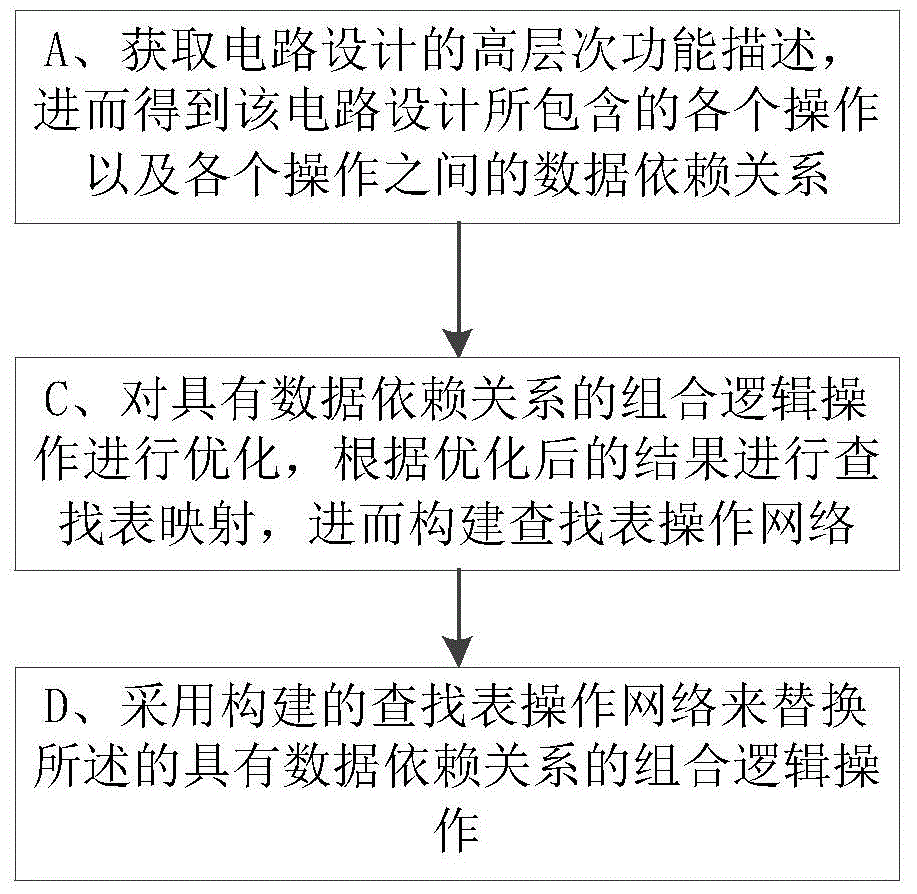

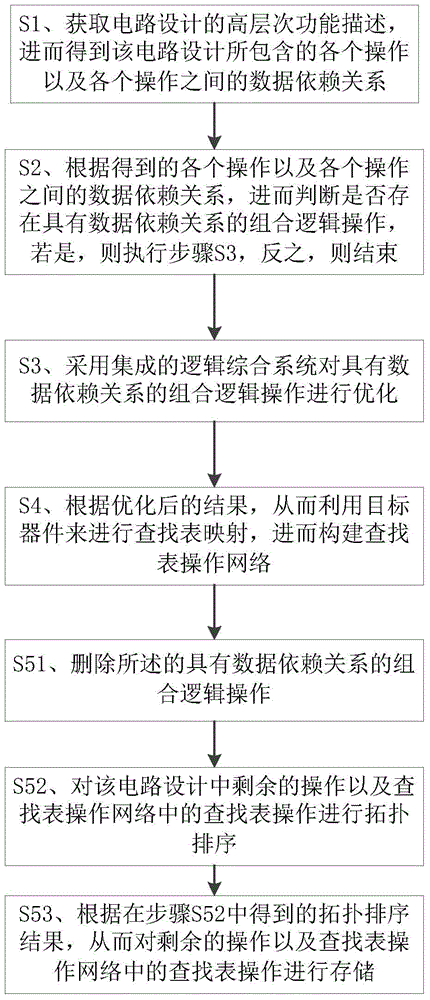

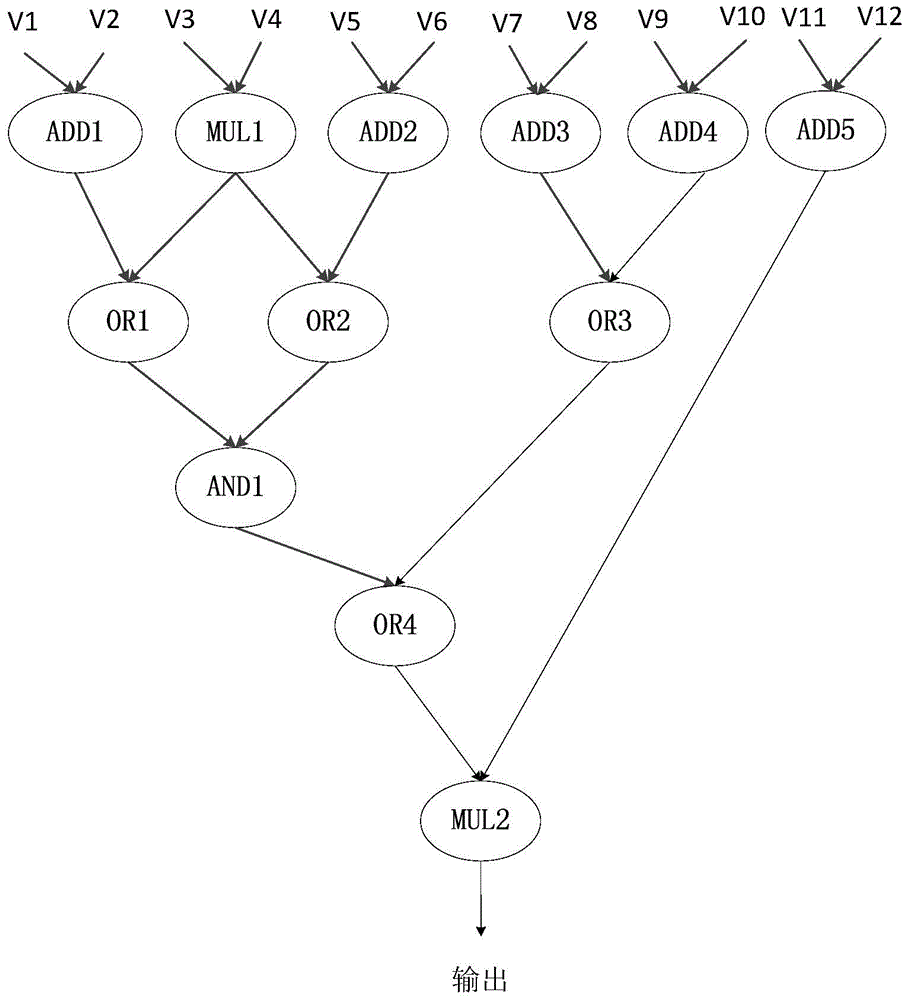

Combinational logic optimization method and system in high-level synthesis

ActiveCN104408232AExcellent build performanceReduce redundancySpecial data processing applicationsLogic optimizationTheoretical computer science

The invention discloses a combinational logic optimization method and system in high-level synthesis. The combinational logic optimization system in the high-level synthesis comprises an obtaining unit, a combinational logic optimization mapping unit and a reconstruction unit. The combinational logic optimization method in the high-level synthesis comprises the following steps of obtaining operations designed in a circuit and a data dependence relationship between the operations; optimizing the combinational logic operations having the data dependence relationship, performing lookup table mapping according to an optimized result, and accordingly constructing a lookup table operation network; replacing the combinational logic operations having the data dependence relationship with the lookup table operation network. The combinational logic optimization method and system in the high-level synthesis can optimize the designing combinational logic in a high-level synthesis stage, remove redundant combinational logic calculations, introduce bottom layer hardware information to the high-level synthesis by adding the lookup table operation, provide more accurate combinational logic time delay and resource expenditure information for a follow-up high-level synthesis step, are beneficial to improvement of performance of each high-level synthesis tool, and can be widely applied to the hardware design field.

Owner:SUN YAT SEN UNIV

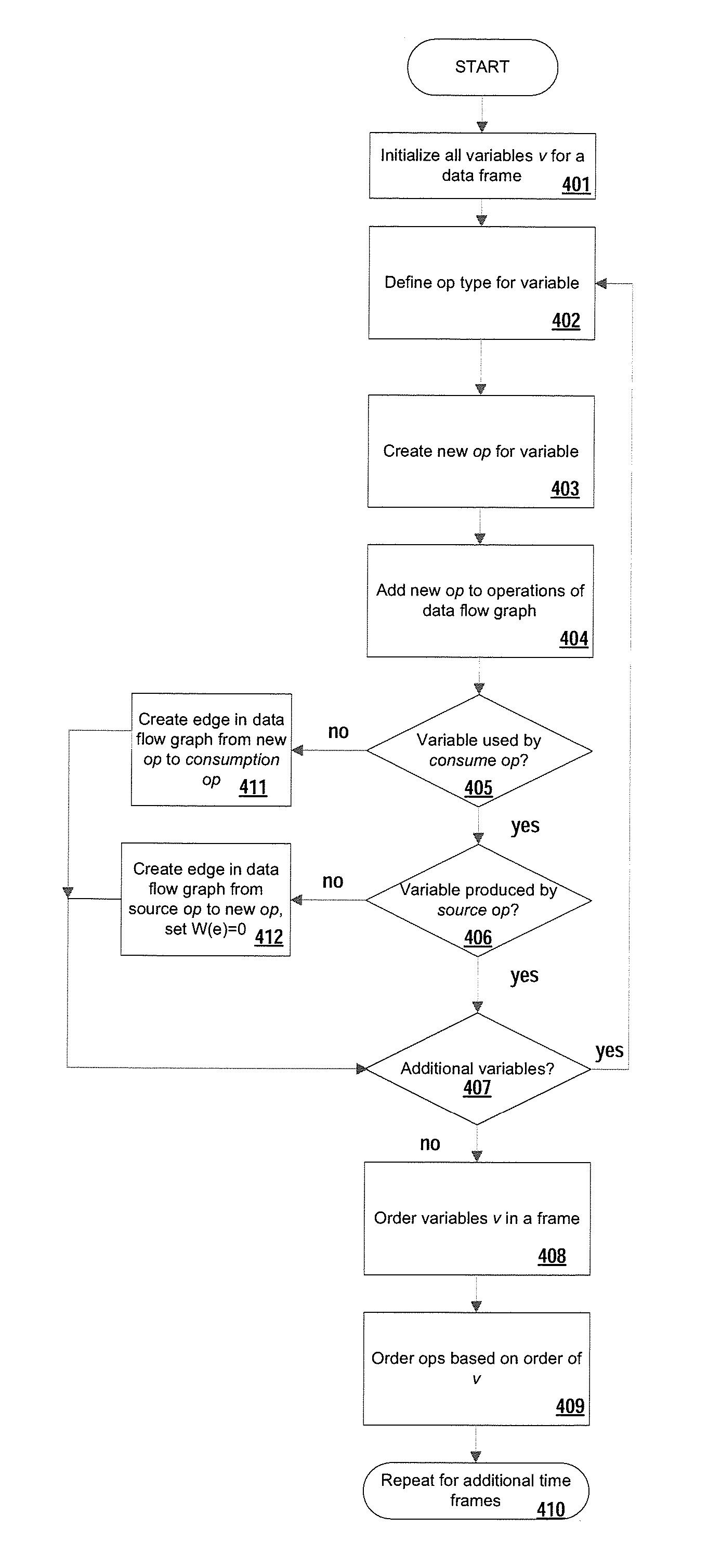

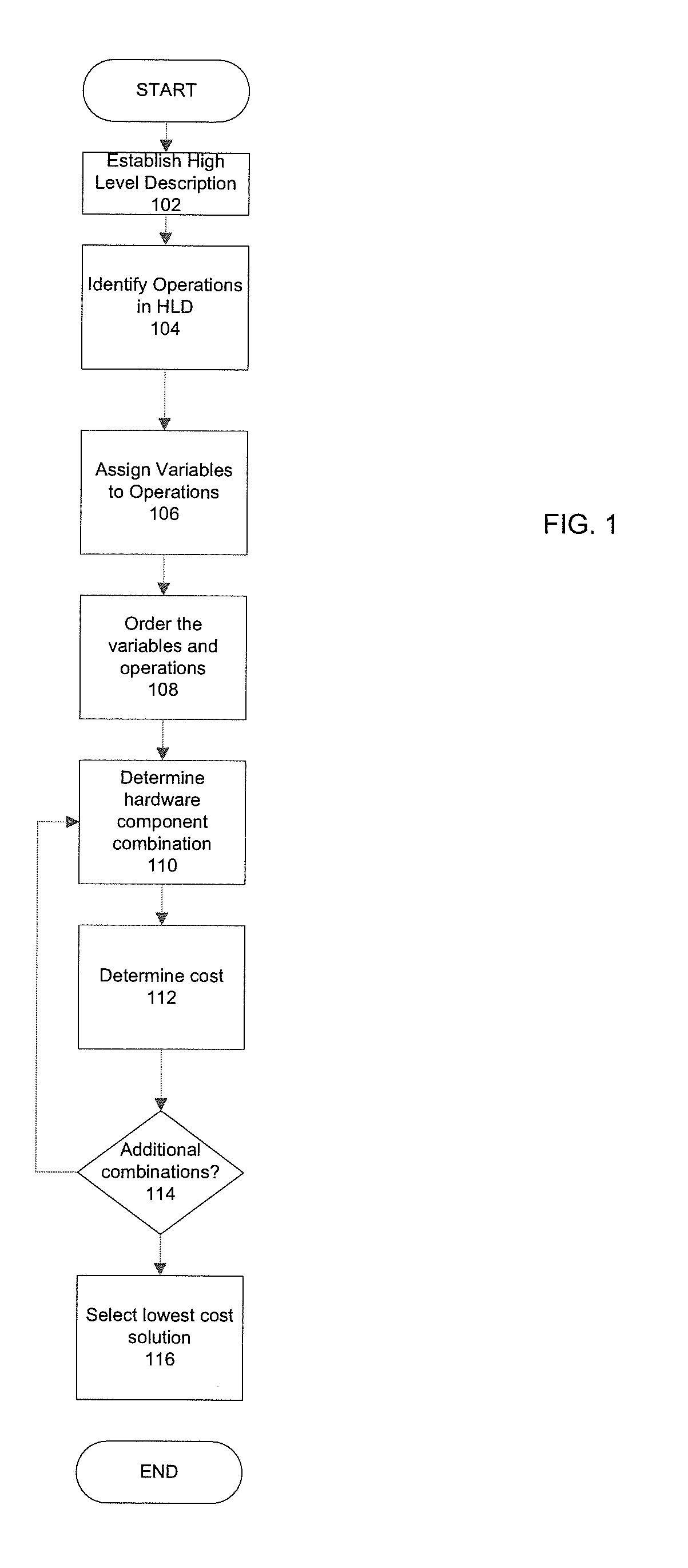

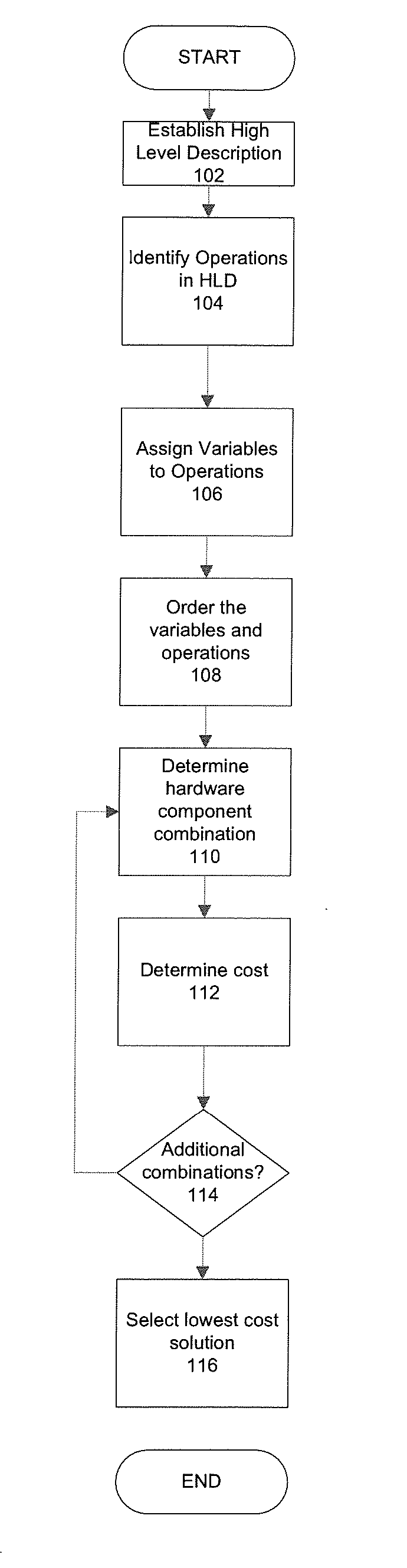

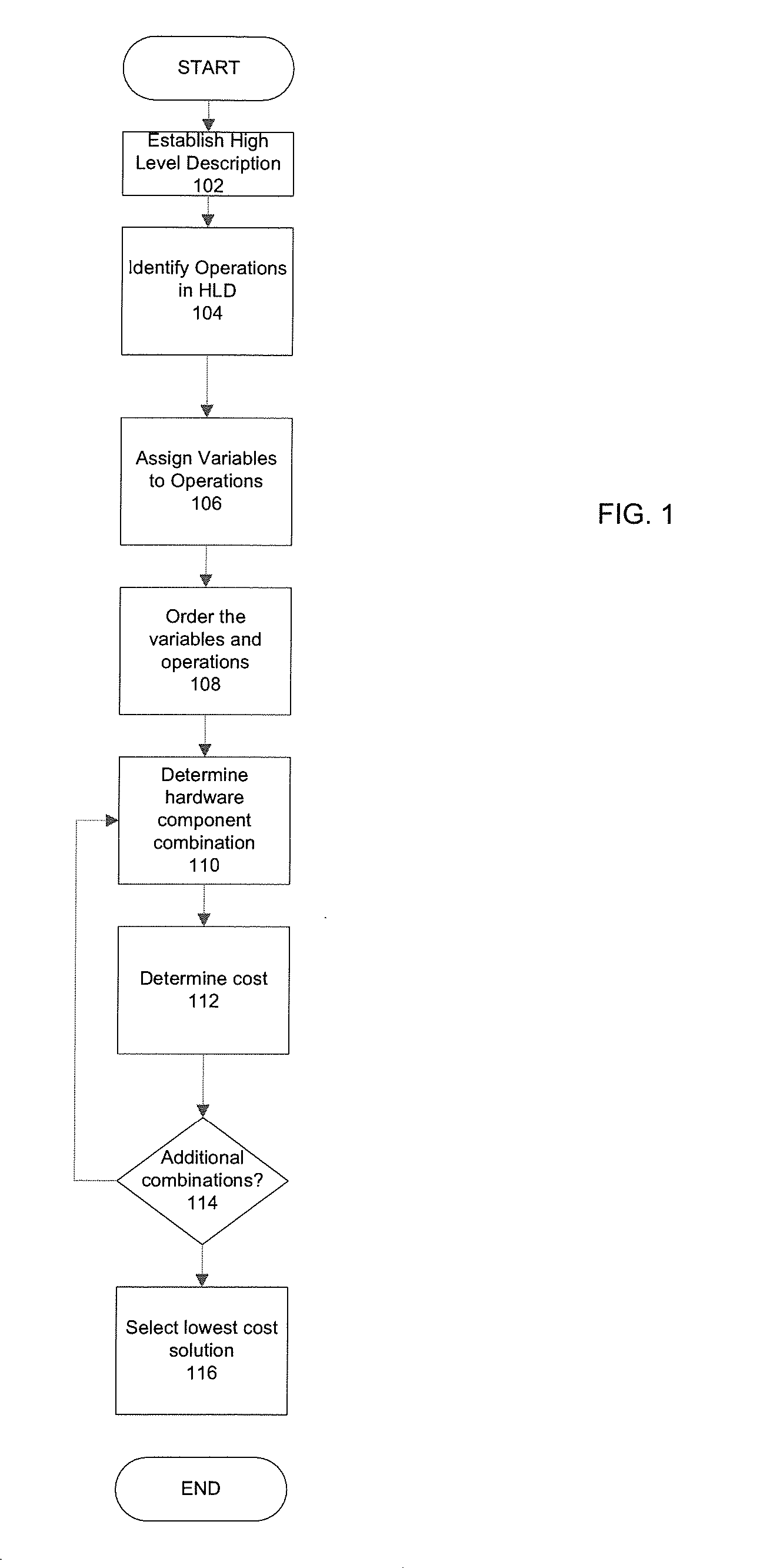

Method and apparatus for synthesizing pipelined input/output in a circuit design from high level synthesis

ActiveUS8296713B2Computer aided designSoftware simulation/interpretation/emulationTheoretical computer scienceHigh-level synthesis

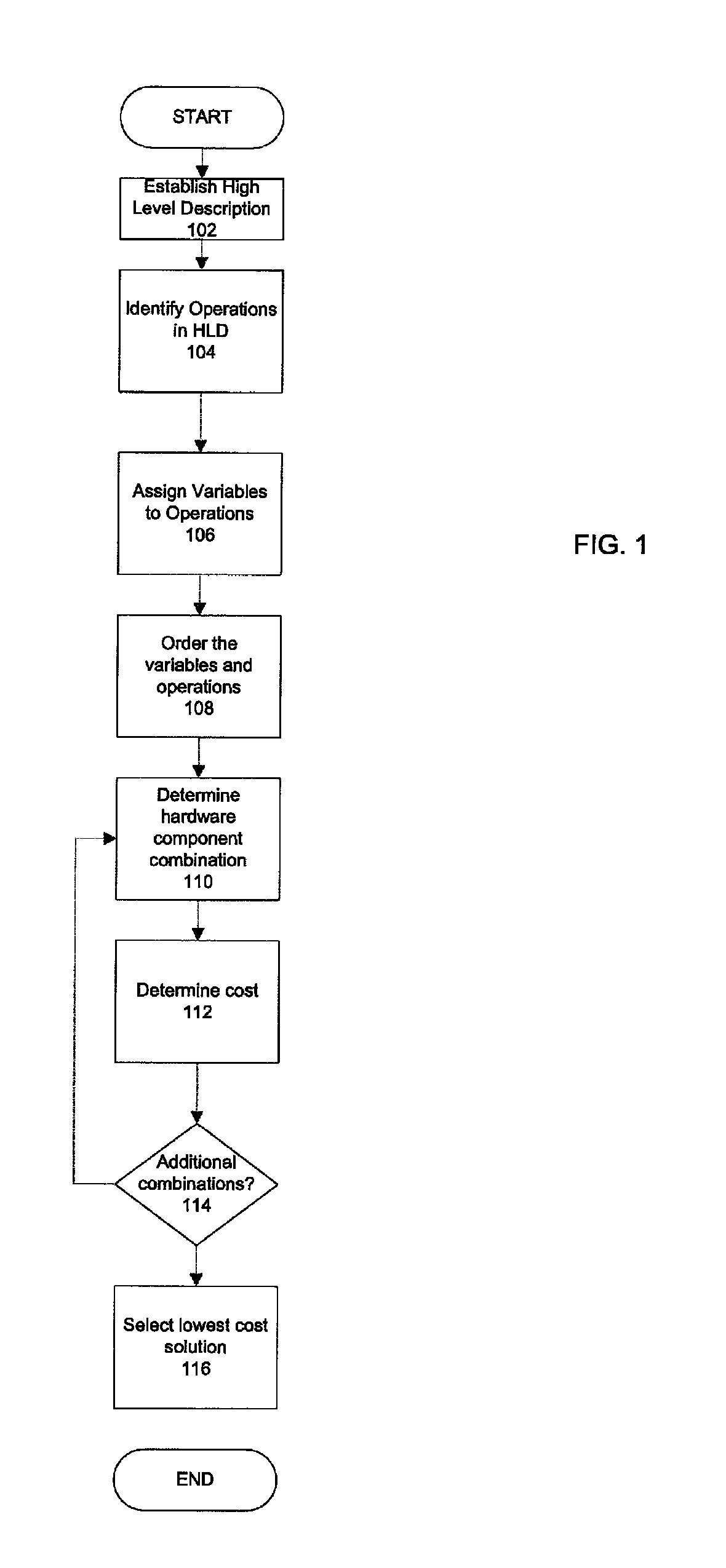

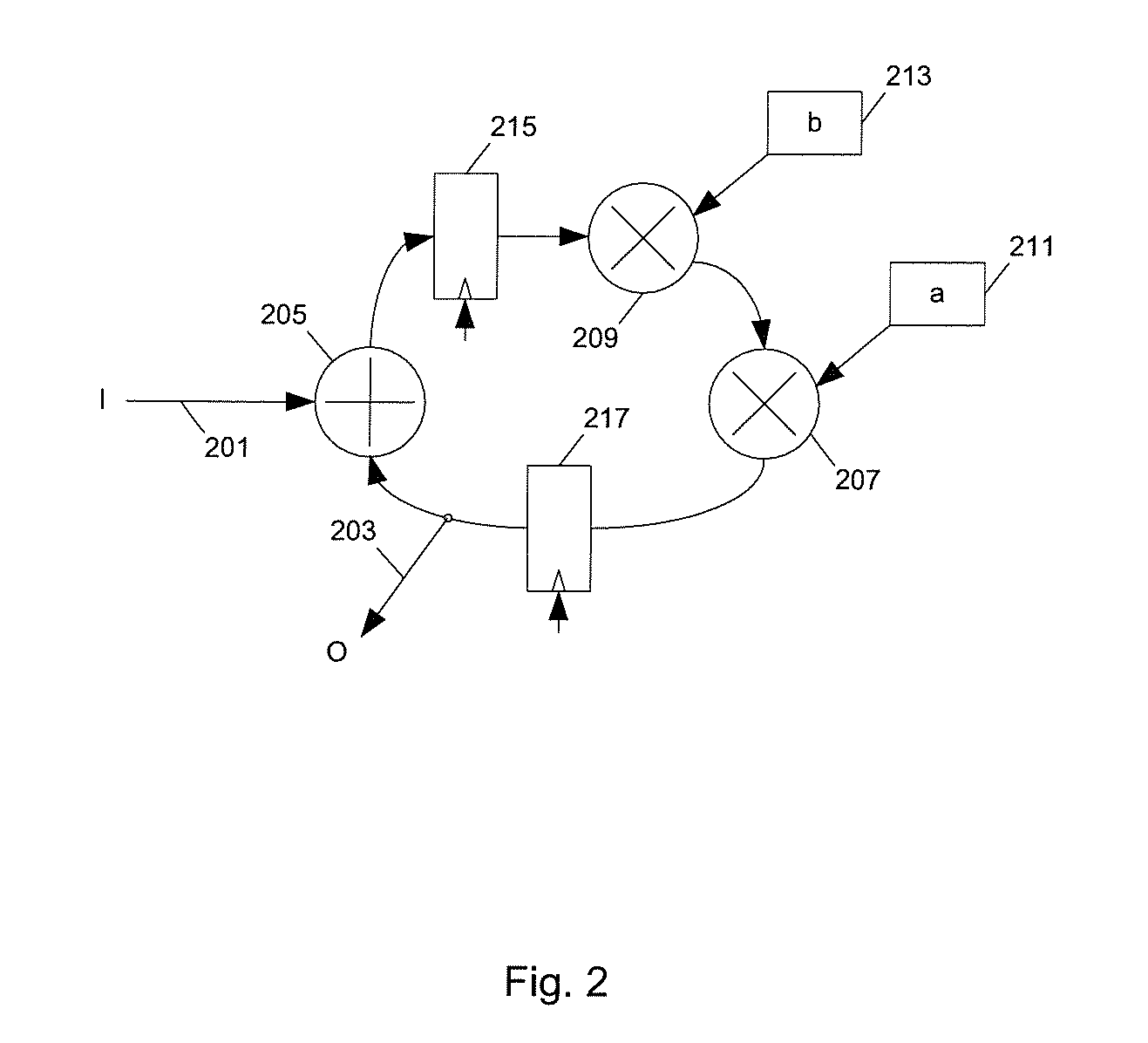

A method and apparatus for synthesizing pipelined input / output in a circuit design from high level synthesis is described. In one example, an operation is selected to be performed by a circuit, the operation including a plurality of partial operations of different types. The partial operations are ordered based on the ordering of the variables. A plurality of hardware components for performing the operations are represented with a data flow graph having edges and nodes, the edges and nodes being connected based on the ordering of partial operations. A plurality of solutions are simulated for performing the operations as hardware component combinations represented as paths on the data flow graph. For each solution, a cost including a number of edges and nodes traversed on the data flow graph is determined, and a solution is selected with the lowest cost as a hardware component combination for a circuit.

Owner:SYNOPSYS INC

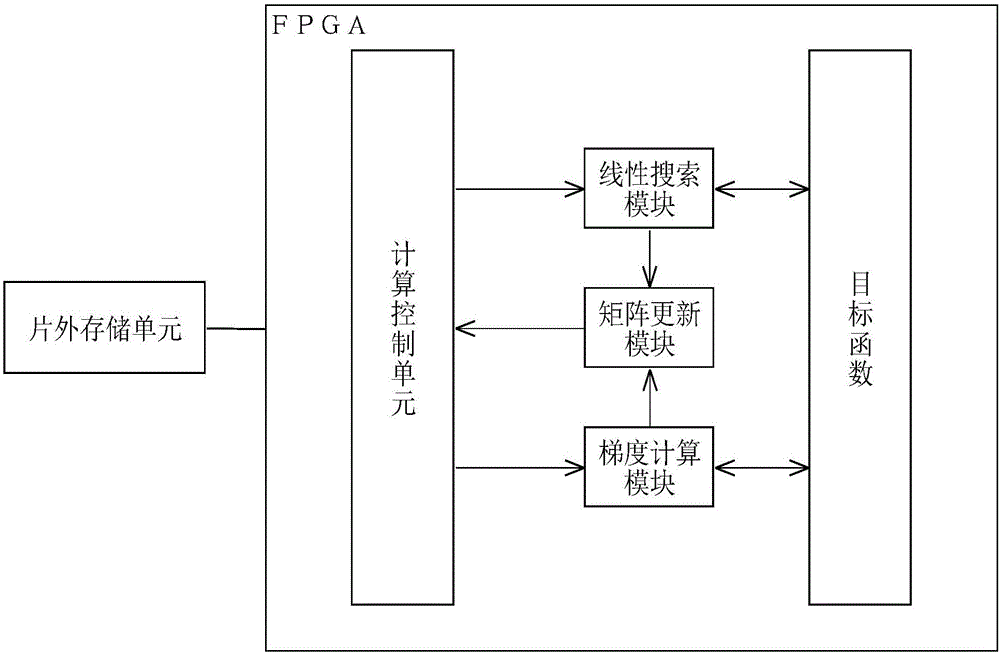

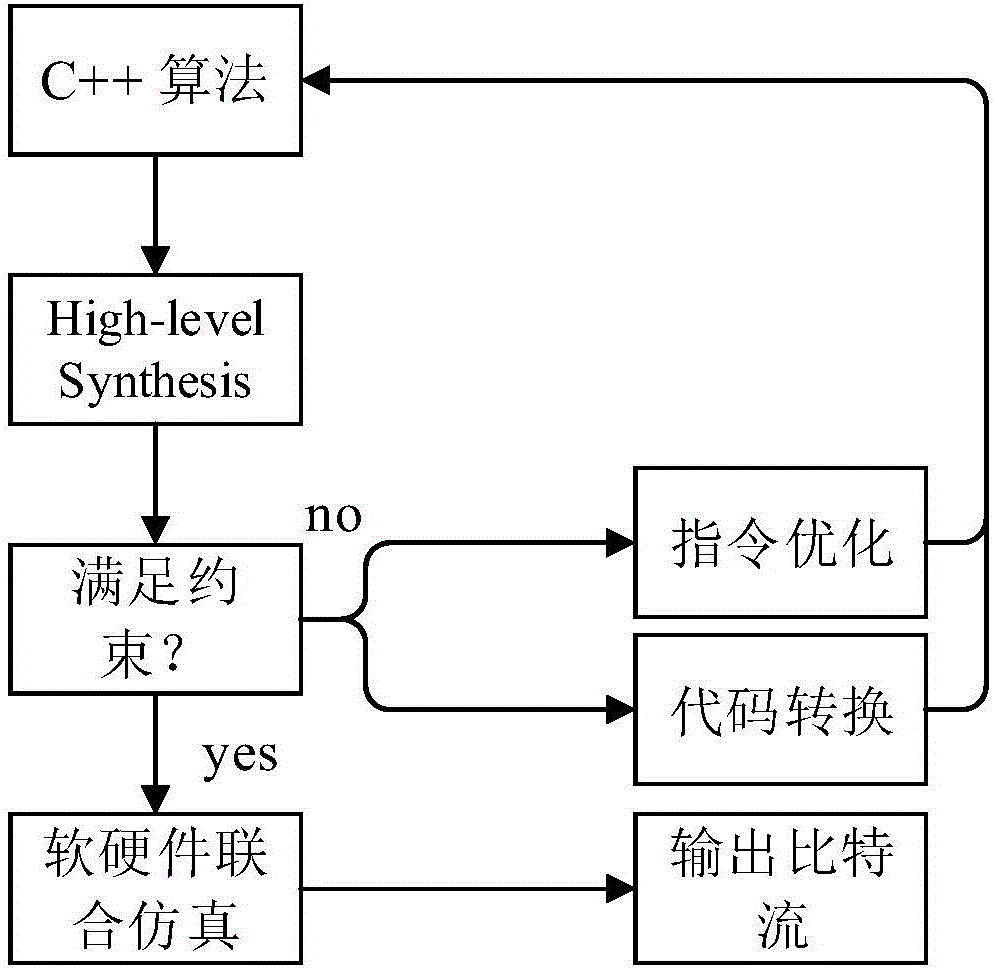

Method for achieving quasi-Newton algorithm acceleration based on high-level synthesis of FPGA

InactiveCN106775905AReduce development difficultyImprove versatilitySoftware engineeringProgram controlFpga implementationsLogical part

The invention discloses a method for achieving quasi-Newton algorithm acceleration based on high-level synthesis of an FPGA. The method comprises the steps that 1, functions of a quasi-Newton algorithm are analyzed, and main calculation modules of the quasi-Newton algorithm are divided; 2, advanced languages C and C++ are utilized to achieve modules in the step 1, and the correctness of the functions of the algorithm are verified; 3, the quasi-Newton algorithm with the functions correct through function verification in the step 2 serves as an input file, a high-level synthesis tool is utilized to convert the advanced languages into RTL-level languages, and generated RTL codes are verified; 4, the generated RTL codes are manufactured into bitstream files, and the files are downloaded to the configurable logical parts of the FPGA. Starting from the quasi-Newton algorithm acceleration, high-level synthesis is utilized to achieve the quasi-Newton algorithm, quasi-Newton algorithm acceleration is achieved through the FPGA, and the FPGA development difficulty is reduced.

Owner:TIANJIN UNIV

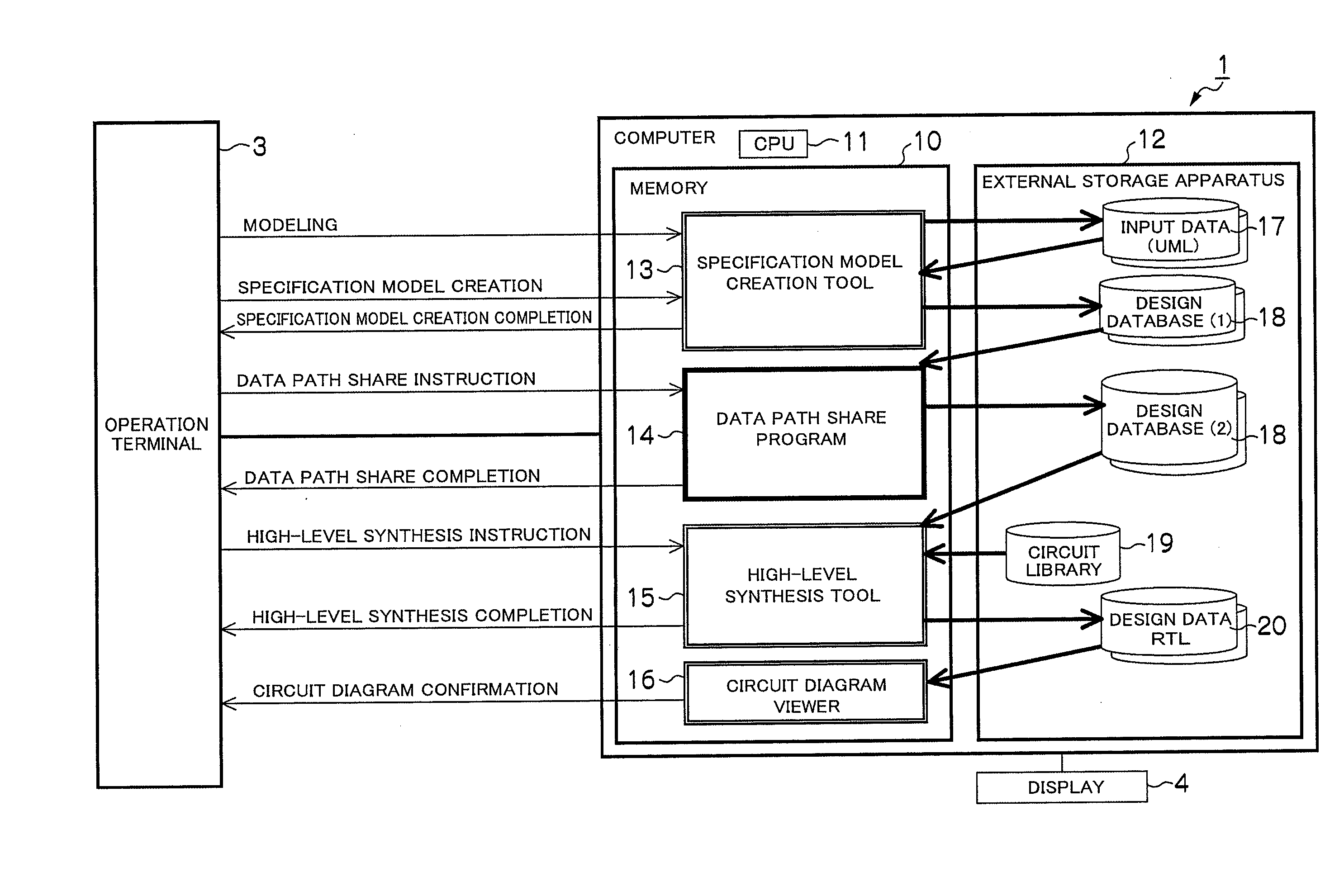

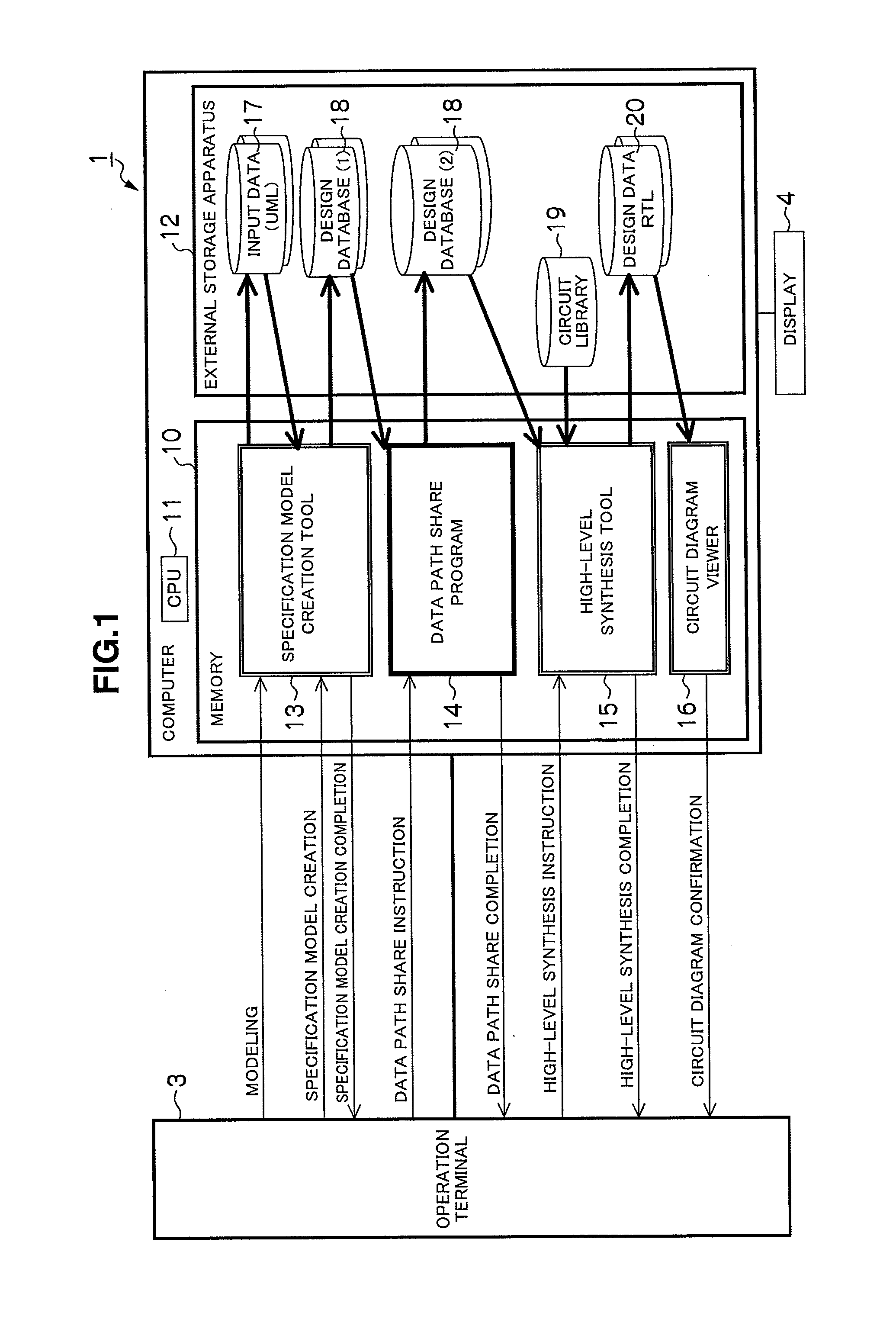

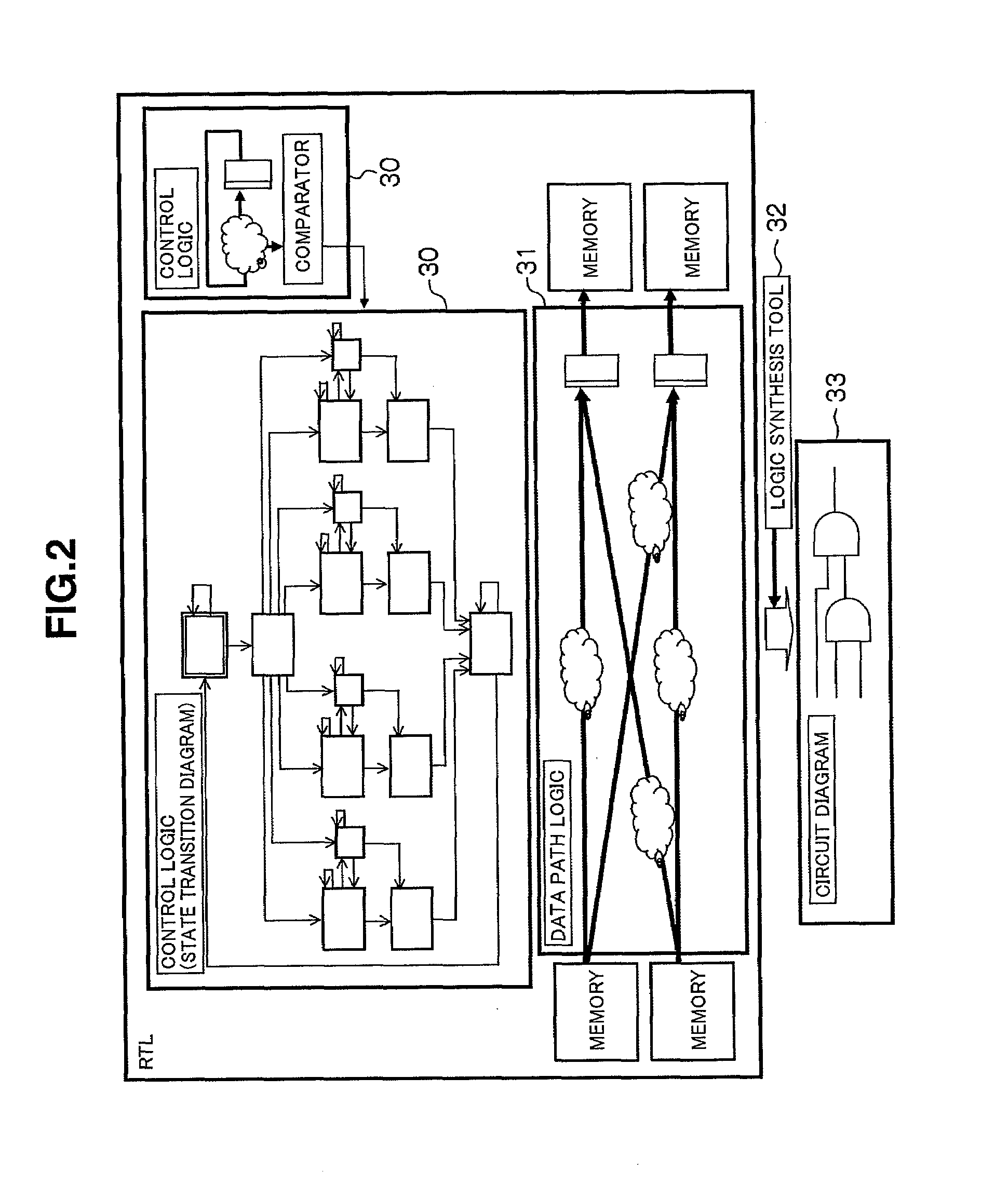

Design Apparatus, Design Method, and Program

InactiveUS20090031276A1High-quality circuit designImprove readabilityCAD circuit designProgram controlComputer architectureControl system

A design apparatus, a design method, and a program, which enable the design of a small-scale circuit that is high in serviceability and quality are provided. Plural commands described at a behavior level are separated into control system behaviors that are behaviors concerning control and data system behaviors that are behaviors concerning data transfer, the data system behaviors for the commands are integrated into one or more behaviors, and both the control system behaviors for the commands and the behavior obtained by integrating the data system behaviors for the commands are subjected to high-level synthesis.

Owner:HITACHI LTD

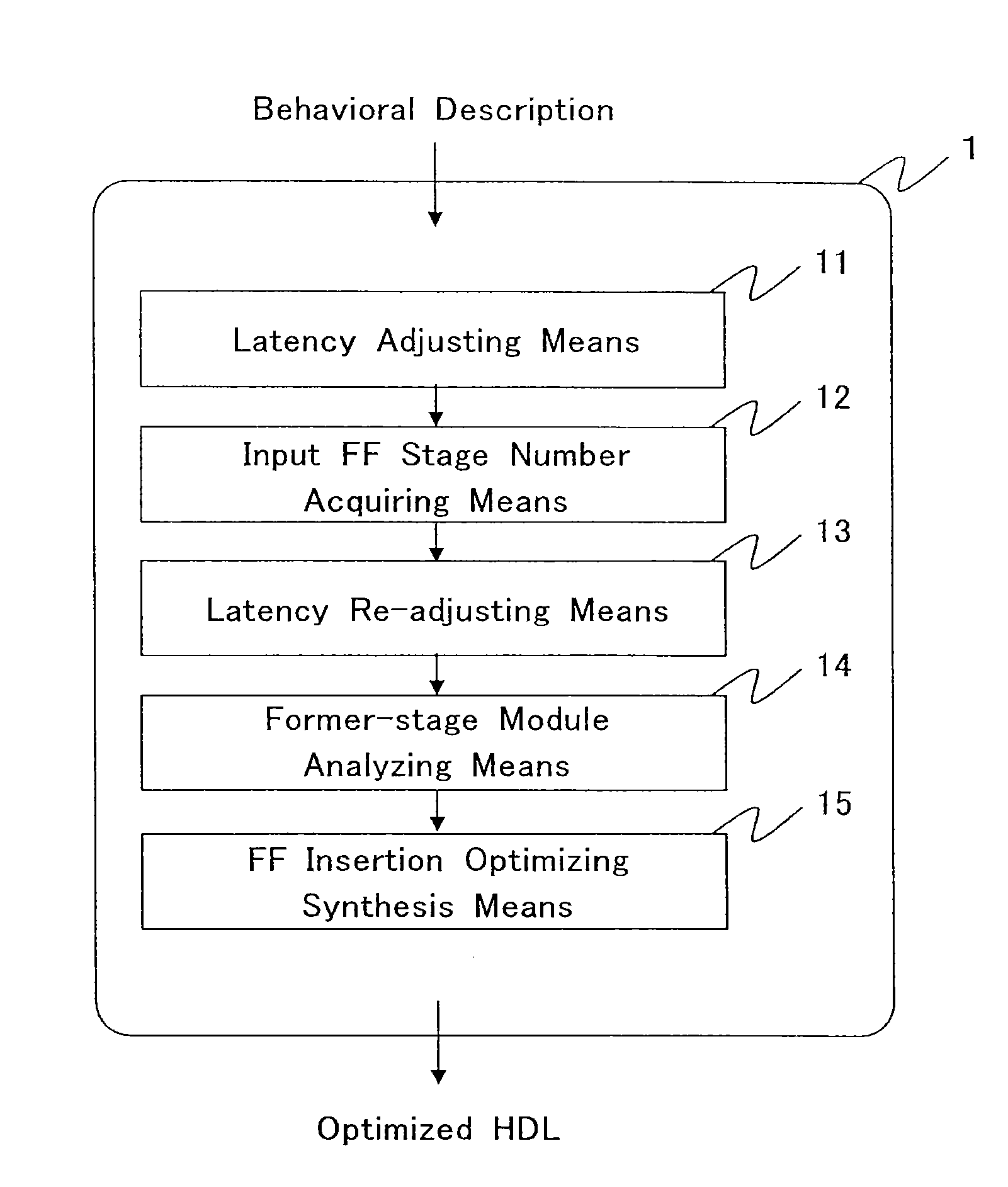

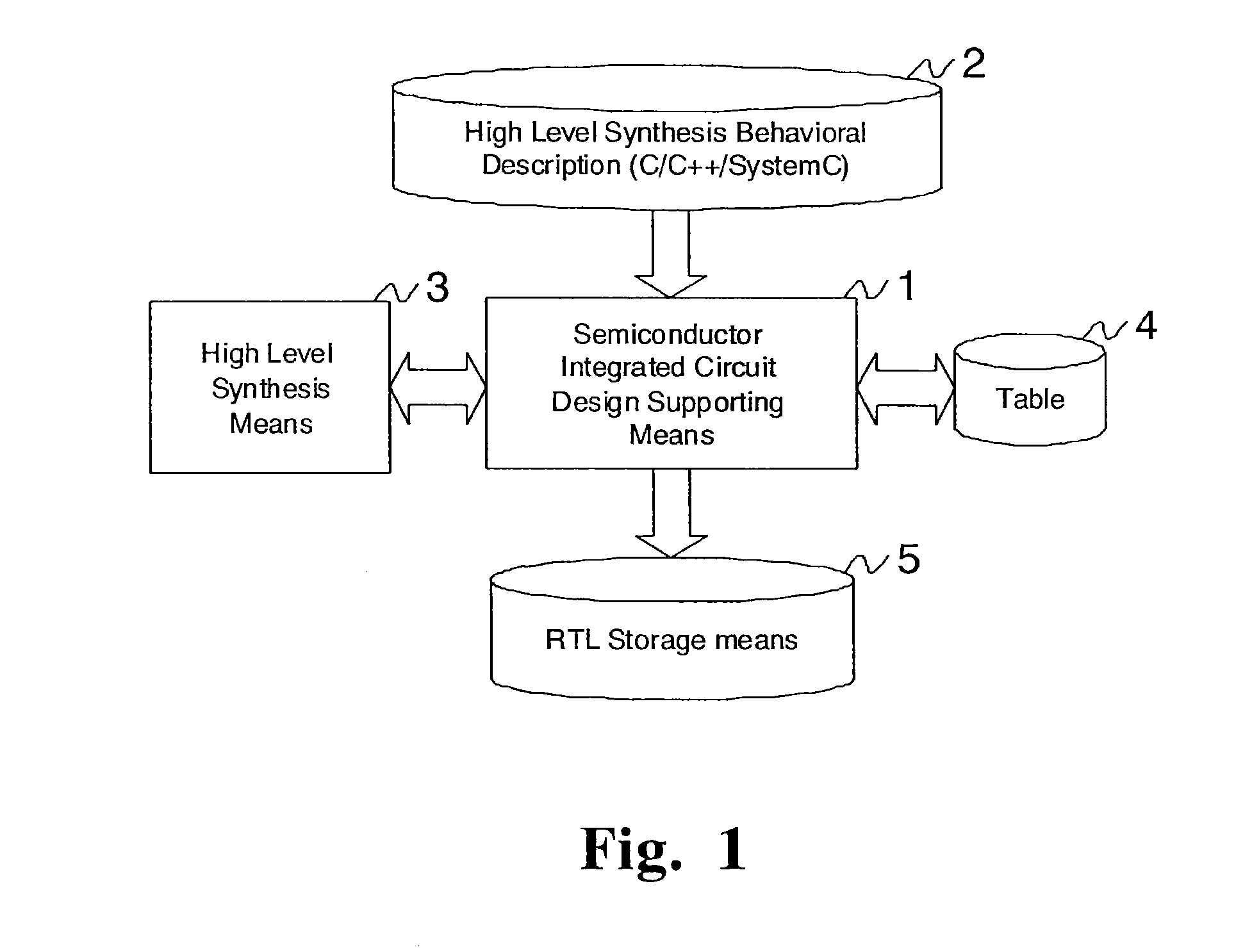

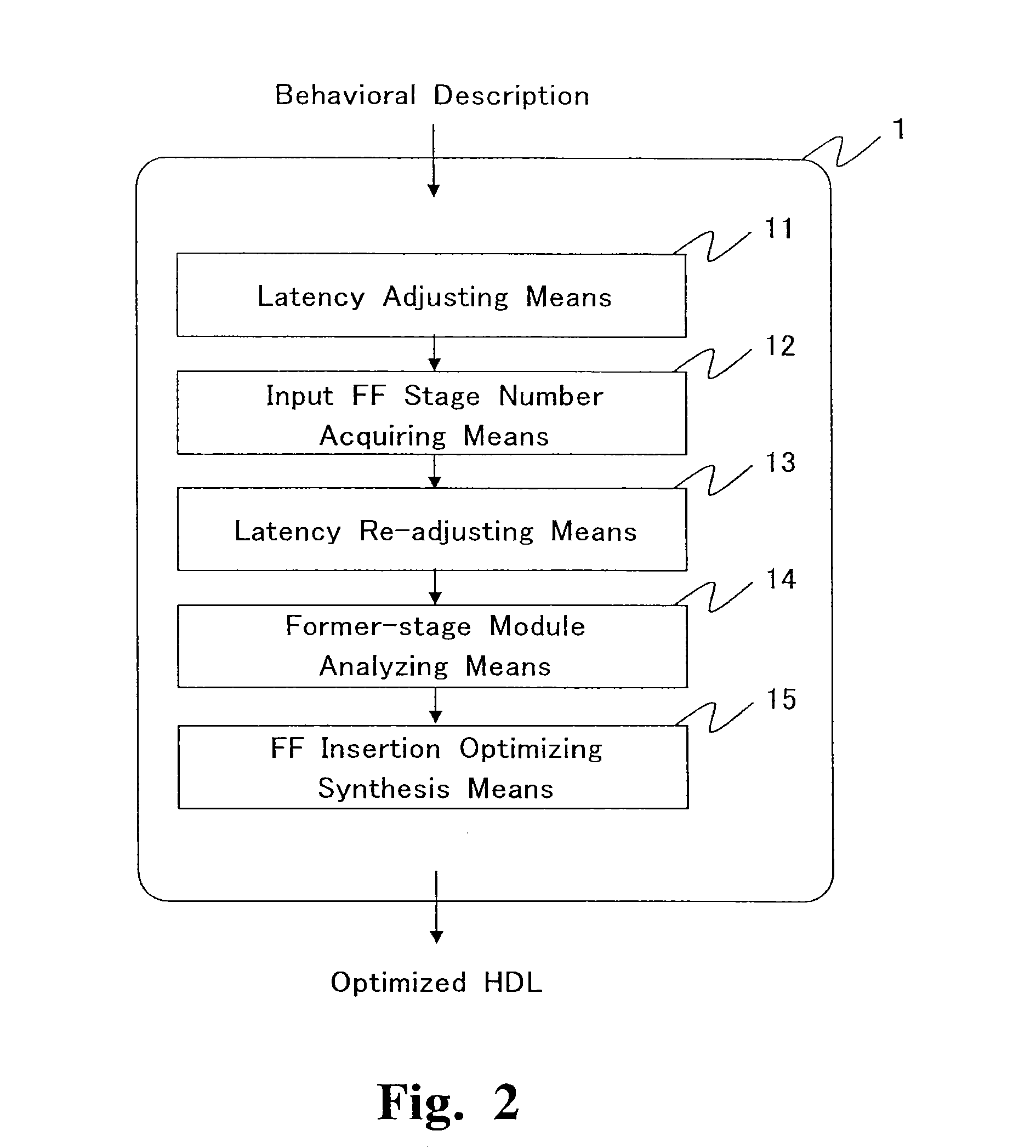

Semiconductor integrated circuit design supporting apparatus, method, and program

ActiveUS20140189633A1Short timeSmall configurationComputer aided designSoftware simulation/interpretation/emulationComputer moduleComputer science

A latency adjusting part calculates a necessary delay based on the number of FFs that are required to be inserted between respective modules through high level synthesis of a behavioral description. An input FF stage number acquiring part extracts a pin having an input that receives an FF, and acquires the number of stages of input FFs of FF reception. A latency re-adjusting part obtains an optimum delay based on the above-mentioned necessary delay and input delay. A former-stage module analyzing part detects, based on the above-mentioned synthetic log or HDL, a state having a minimum total number of FFs. An FF insertion optimizing synthesis part subjects an entire circuit to high level synthesis again based on the above-mentioned optimum delay and an FF inserting position obtained based on the state having the minimum number of FFs, to thereby obtain optimized HDL.

Owner:MITSUBISHI ELECTRIC CORP

Method and apparatus for using entropy in ant colony optimization circuit design from high level synthesis

A method and apparatus for using entropy in ant colony optimization circuit design from high level synthesis is described. In one example, an operation to be performed by a circuit is selected. A plurality of hardware components for performing the operation are represented with a data flow graph having edges and nodes. A plurality of solutions for performing the operation are simulated as hardware component combinations represented as paths on the data flow graph. For each solution the cost including a number of edges and nodes traversed on the data flow graph and a supplemental sub-integer cost is determined and a solution is selected with the lowest cost as a hardware component combination for a circuit.

Owner:SYNOPSYS INC

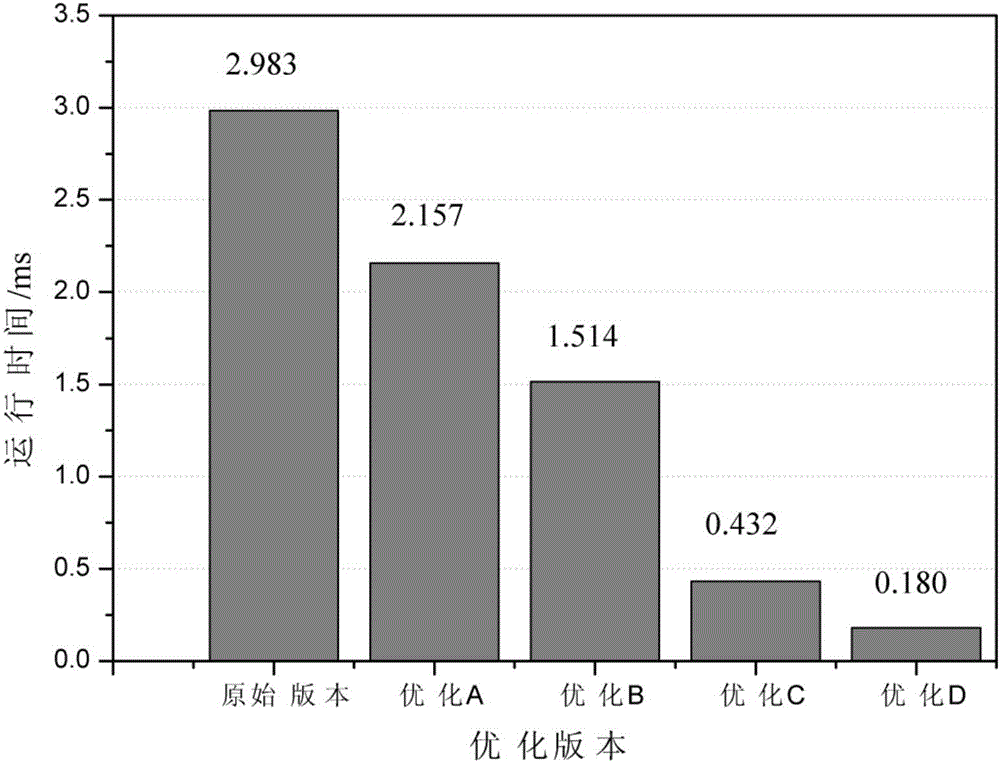

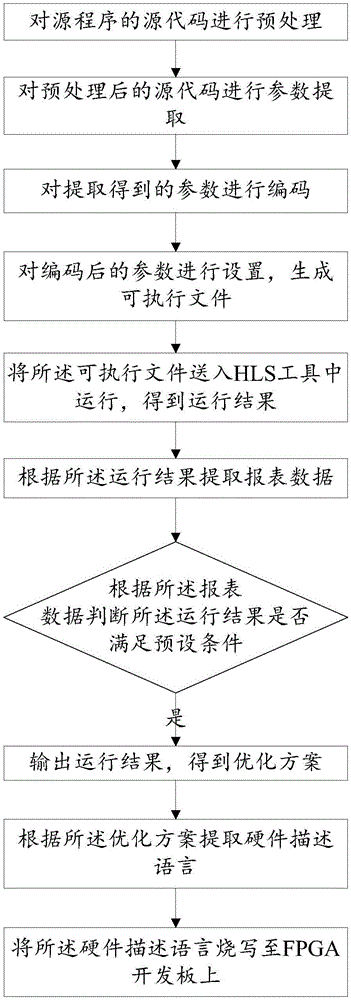

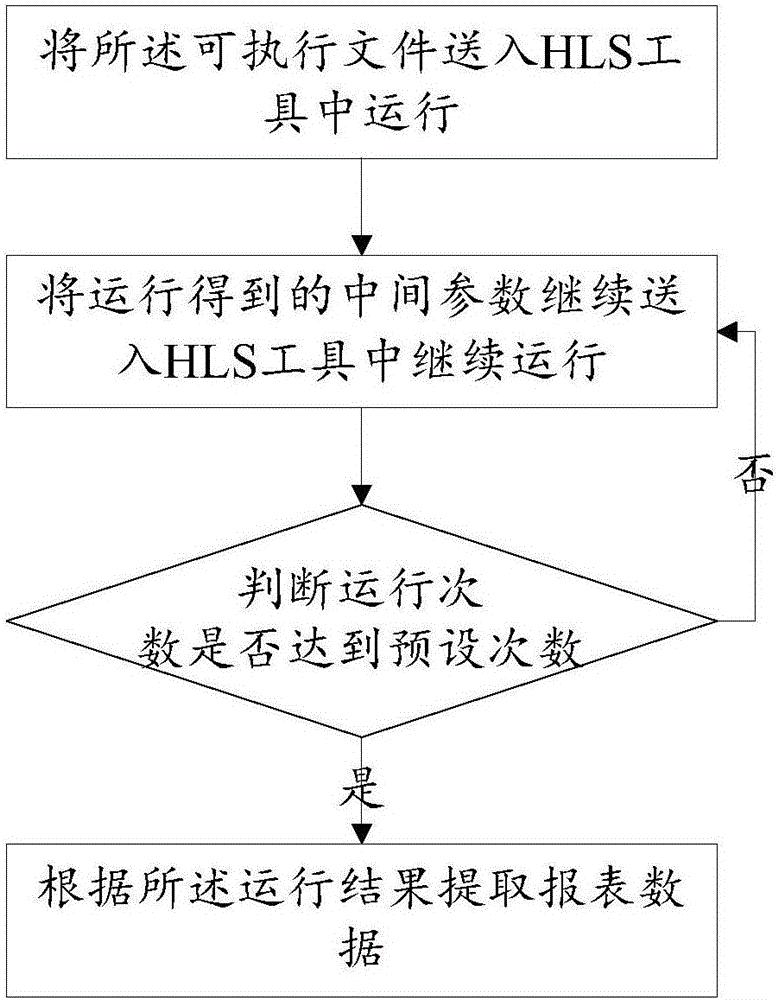

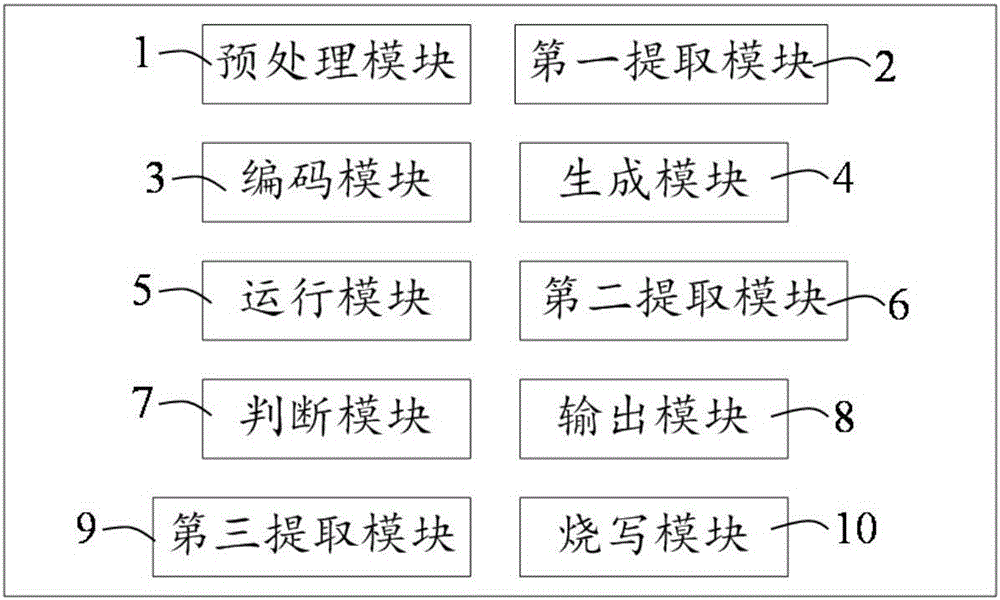

Method of optimization based on FPGA (Field Programmable Gate Array) high level synthesis (HLS) instructions and system thereof

InactiveCN107179932AMeet the versatilityImprove developmentSoftware engineeringProgram controlSource codeHardware acceleration

The invention discloses a method of optimization based on FPGA (Field Programmable Gate Array) high level synthesis (HLS) instructions and a system thereof. The method includes: preprocessing source code of a source program; carrying out parameter extraction on the preprocessed source code; encoding parameters obtained by extraction; setting the encoded parameters, and generating an executable file; sending the executable file into an HLS tool to run to obtain a running result; extracting report-form data according to the running result; judging whether the running result meets a preset condition according to the report-form data; if yes, outputting the running result to obtain an optimization scheme; extracting a hardware description language according to the optimization scheme; and burning the hardware description language onto an FPGA development board. According to the method and the system, the generalities of various algorithms that need hardware acceleration can be met, carrying out relevant development by hardware and software developers can be facilitated, a development cycle of an FPGA hardware engineering project can be greatly reduced, and defects of traditional hardware description languages can be avoided.

Owner:FUJIAN NORMAL UNIV

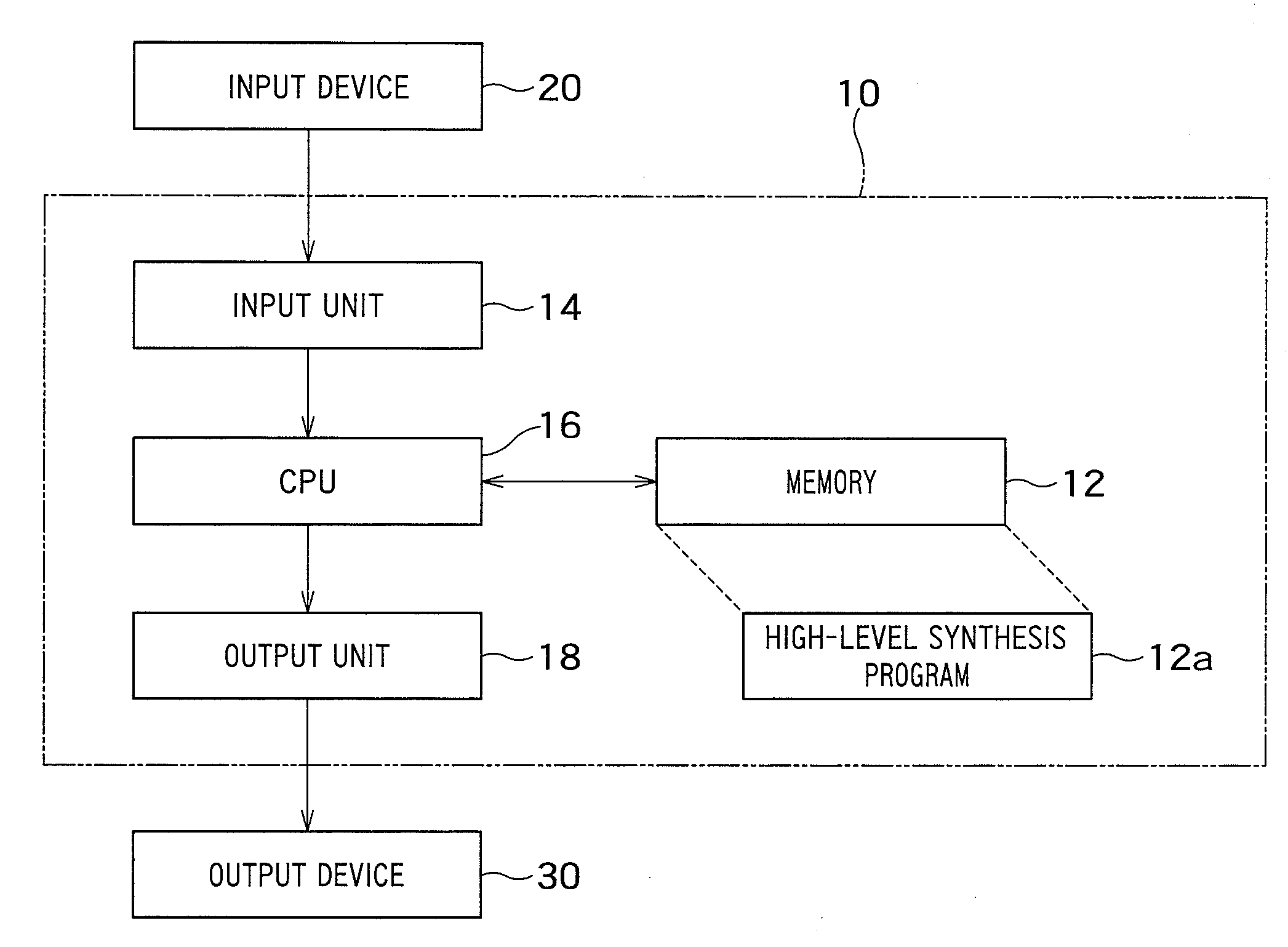

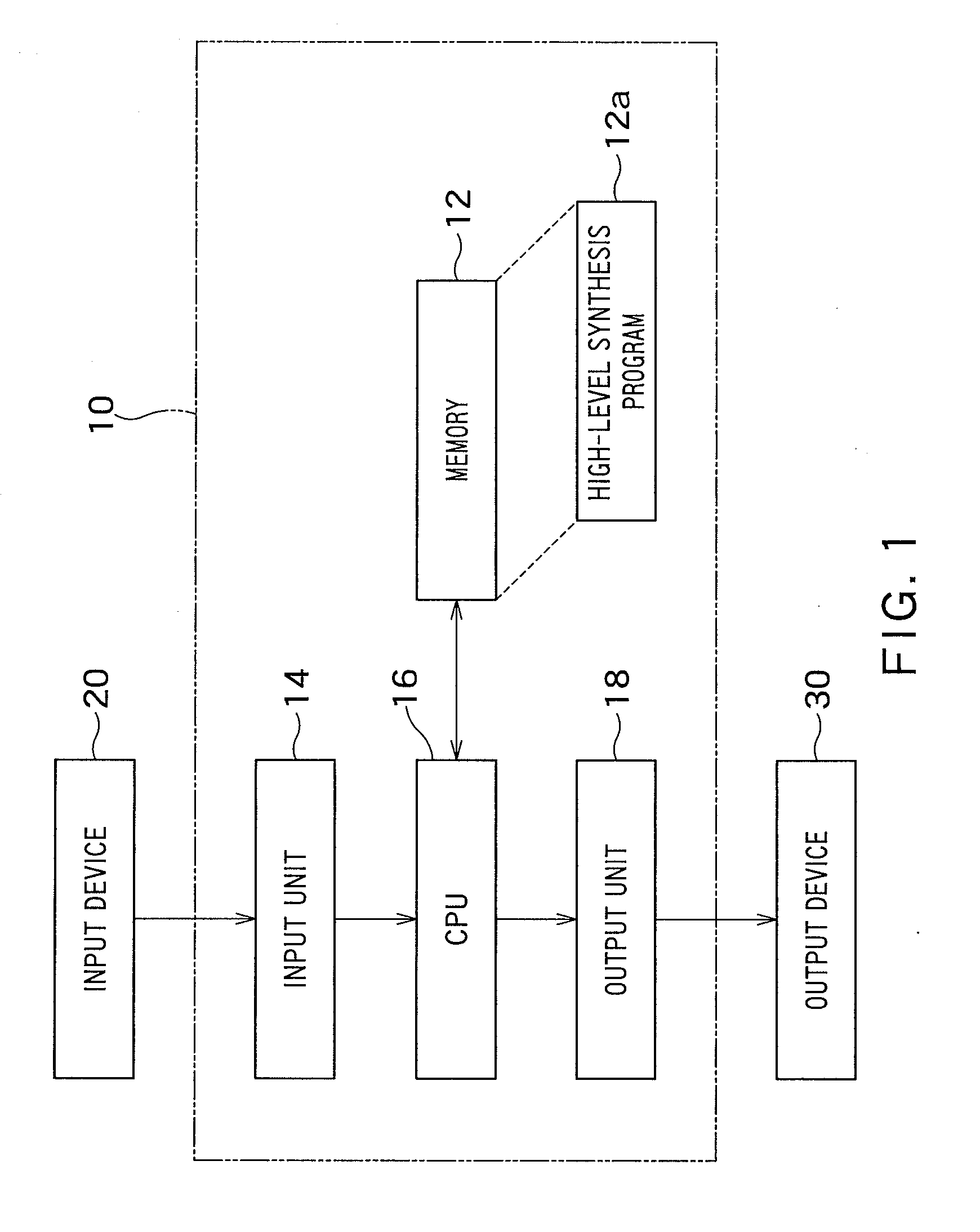

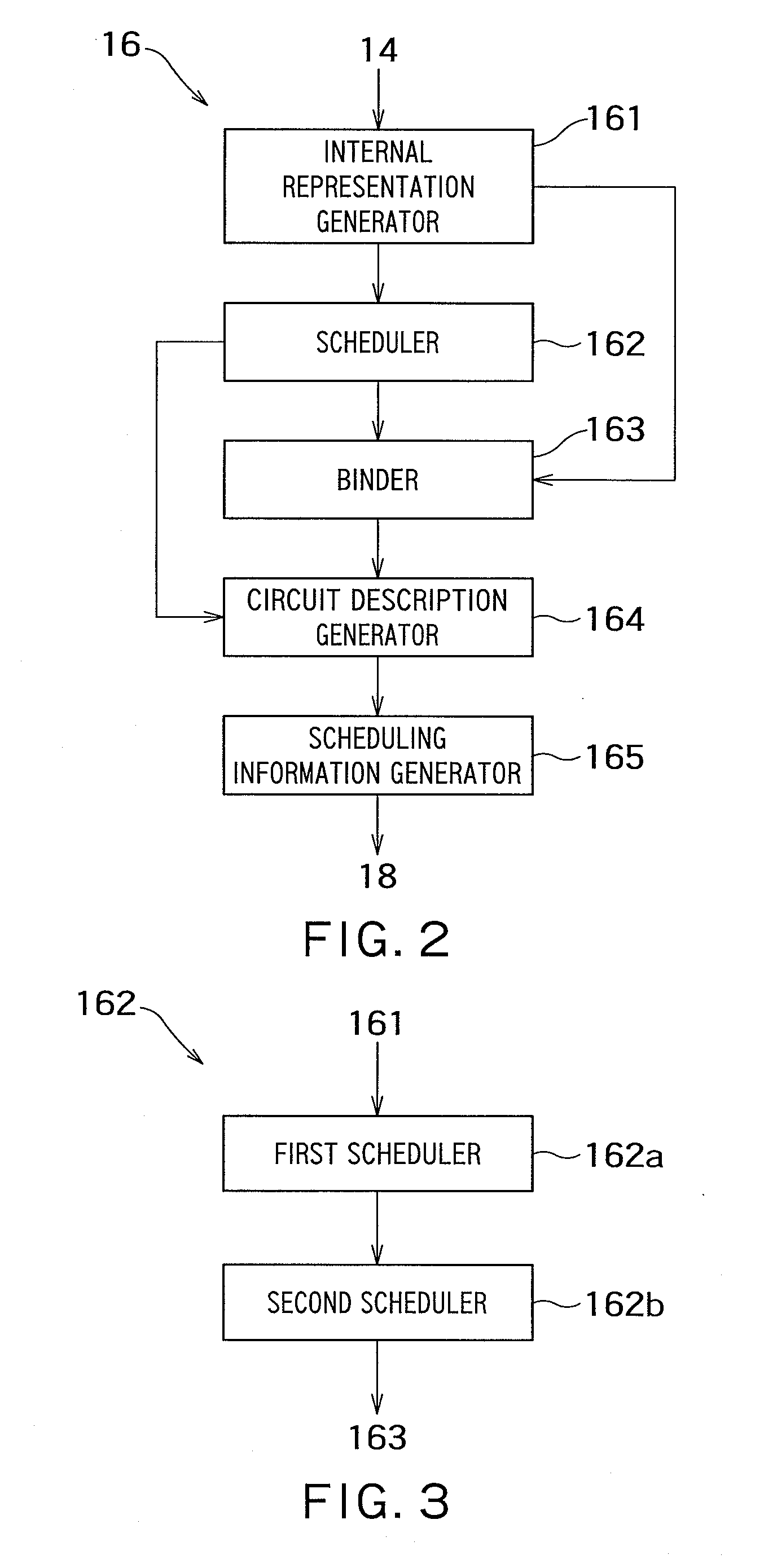

High-level synthesis apparatus, high-level synthesis method, and computer readable medium comprising high-level synthesis program

InactiveUS20110061032A1Computer aided designSpecial data processing applicationsSynthesis methodsTheoretical computer science

A high-level synthesis apparatus includes an input unit inputting a behavioral description indicating a behavior of a semiconductor integrated circuit comprising a plurality of functional units, an internal representation generator generating an internal representation based on the behavioral description, the internal representation showing a data flow in the behavioral description and an order in which operations are to be performed in the behavioral description, a scheduler performing scheduling for the operations in the internal representation generated in such a manner that non-operating cycles of the functional units continue, a binder performing binding for determining a configuration of the semiconductor integrated circuit operates scheduled operations on the internal representation generated, a circuit description generator generating a circuit description based on a scheduled result and a bound result, and an output unit outputting the internal representation and the circuit description.

Owner:KK TOSHIBA