Method of optimization based on FPGA (Field Programmable Gate Array) high level synthesis (HLS) instructions and system thereof

A technology of high-level synthesis and optimization method, which is applied in the field of optimization method and its system based on FPGA high-level synthesis instruction, which can solve problems such as increased development difficulty, unknown instruction effect, and numerous adjustable parameters of HLS instruction, so as to shorten the development time. The effect of cycle and convenient development

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

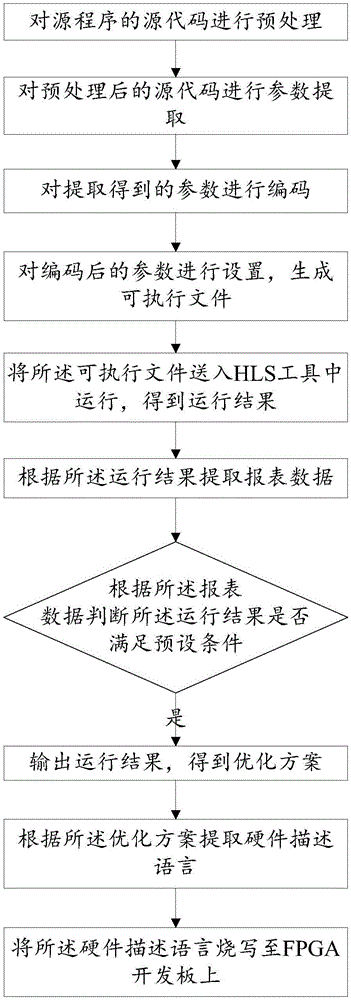

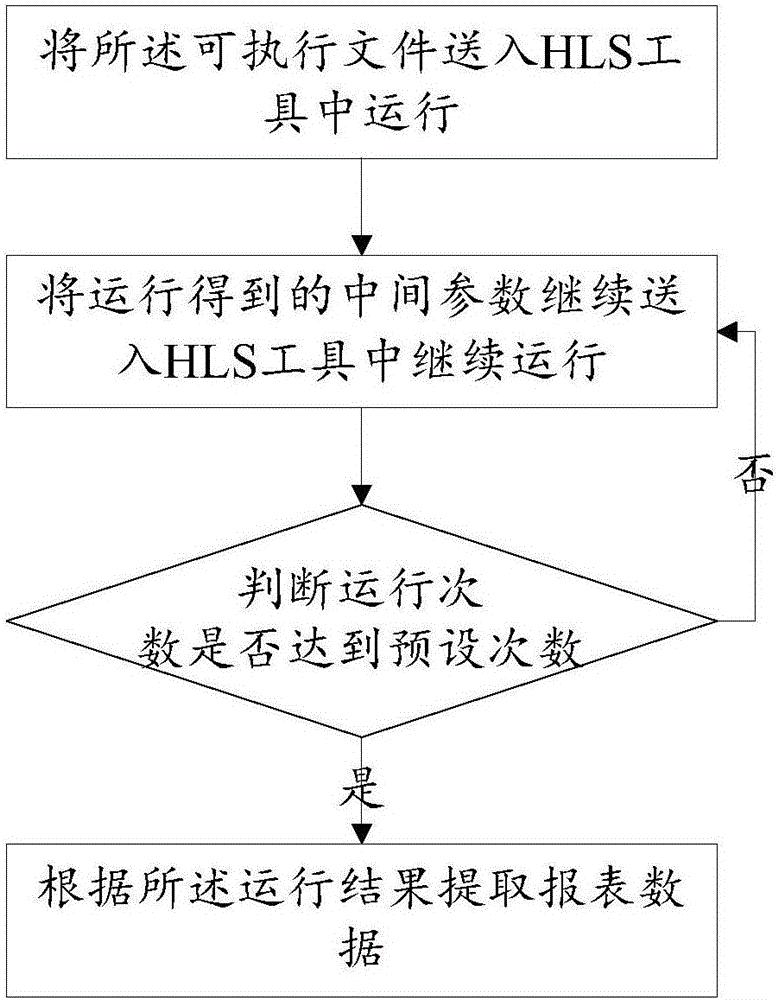

[0091] Please refer to figure 1 and figure 2 , Embodiment 1 of the present invention is:

[0092] An optimization method based on FPGA high-level synthesis instructions, which can meet the versatility of various algorithms that require hardware acceleration, including:

[0093] S1. Preprocessing the source code of the source program. For example, through intelligent analysis and modification of source code, certain optimization strategies are adopted to remove dependencies to meet the requirements of parallel processing. HLS can be expanded in parallel within the loop and between functions. Since the logic operation and function parallelization between for loops will not be implemented during the scheduling process, in order to achieve parallel processing, it can only be placed in different functions. In addition, the processing of inline functions and data structures are all placed in the preprocessing optimization strategy.

[0094] S2. Perform parameter extraction on t...

Embodiment 2

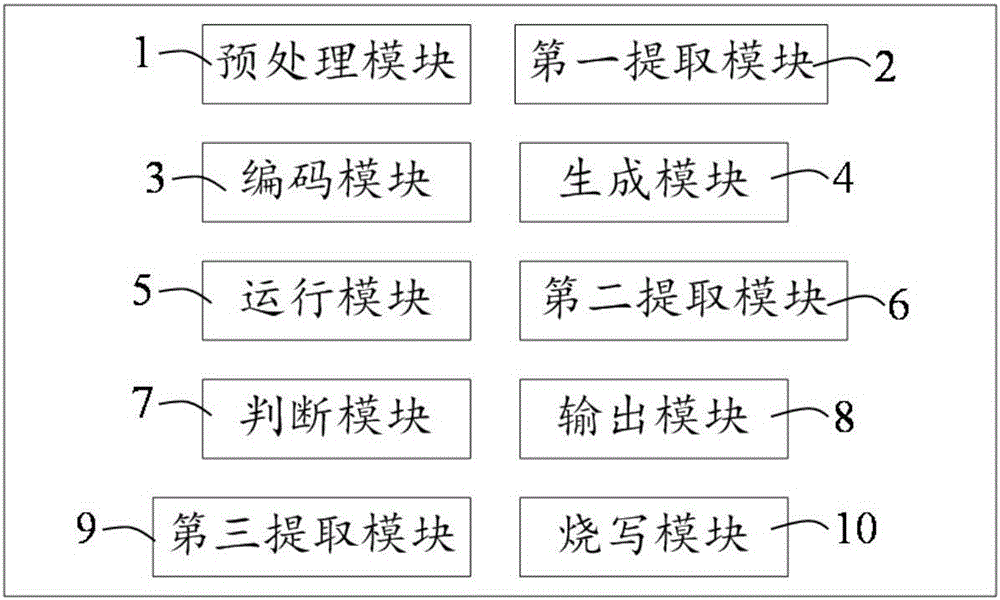

[0110] Please refer to Figure 4 , Embodiment two of the present invention is a kind of optimization system based on FPGA high-level synthesis instruction, corresponding to the method of above-mentioned embodiment one, comprising:

[0111] The preprocessing module 1 is used to preprocess the source code of the source program;

[0112] The first extraction module 2 is used to extract parameters from the preprocessed source code;

[0113] An encoding module 3, configured to encode the extracted parameters;

[0114] Generating module 4, is used for setting the parameter after encoding, generates executable file;

[0115] Running module 5 is used to send the executable file into the HLS tool to run, and obtain the running result;

[0116] The second extracting module 6 is used to extract report data according to the operation result;

[0117] A judging module 7, configured to judge whether the operation result satisfies a preset condition according to the report data;

[0118...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More