Combinational logic optimization method and system in high-level synthesis

A high-level synthesis and combinational logic technology, applied in the field of combinational logic optimization methods and systems in high-level synthesis, can solve the problems of redundant combinational logic operations, reduce the parallelism of hardware design, affect the running speed of hardware, etc. redundancy, the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

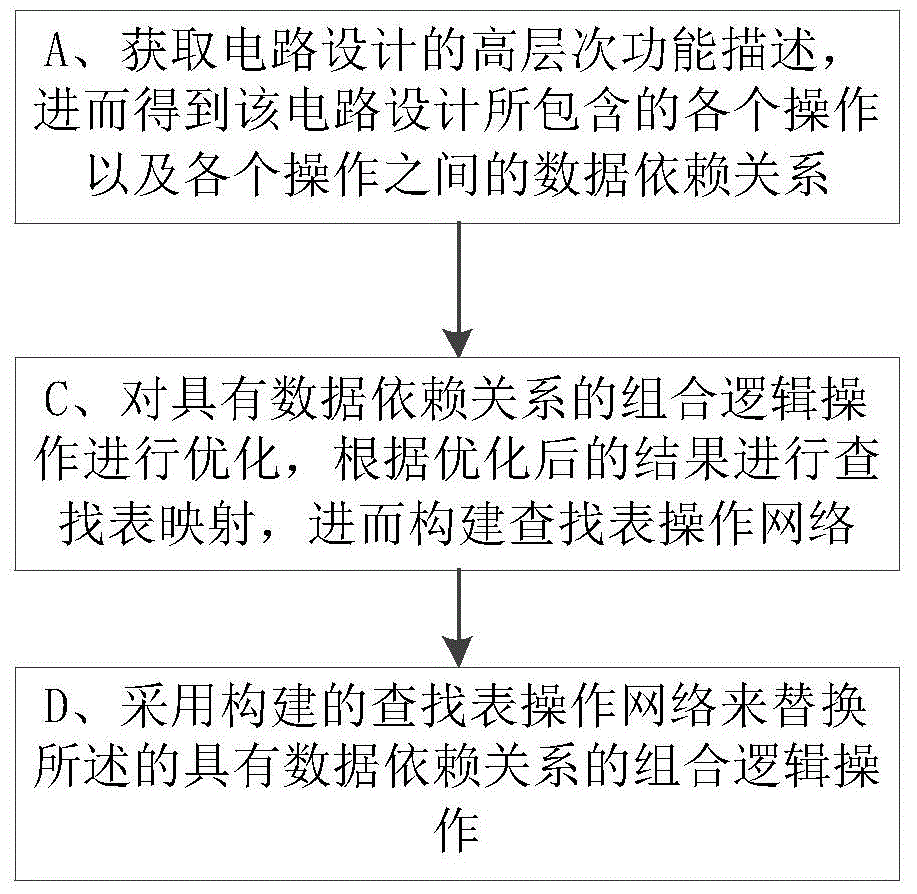

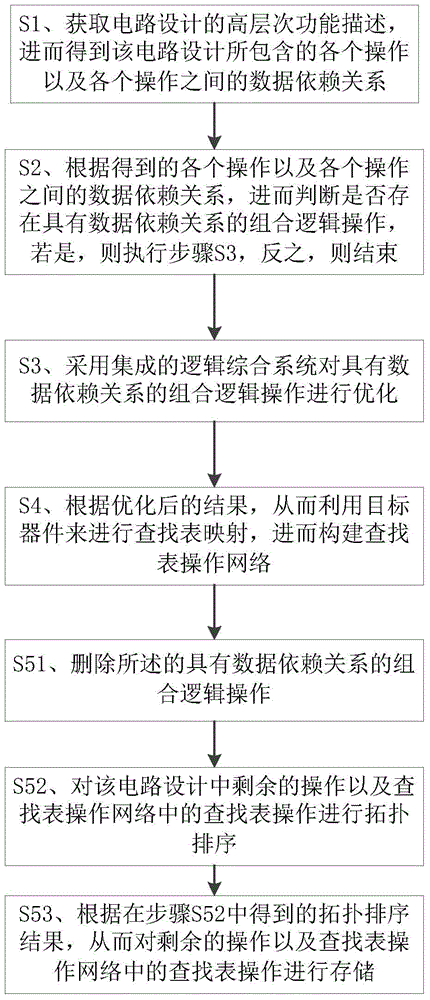

[0039] Such as figure 1 As shown, a combinatorial logic optimization method in high-level synthesis, the method includes:

[0040] A. Obtain the high-level functional description of the circuit design, and then obtain the various operations contained in the circuit design and the data dependencies between each operation;

[0041] C. Optimize the combinatorial logic operations with data dependencies, perform lookup table mapping according to the optimized results, and then build a lookup table operation network;

[0042] D. Use the constructed lookup table operation network to replace the combinational logic operations with data dependencies, so as to realize the reconstruction of operations.

[0043] According to different actual conditions, the lookup table operation network includes one lookup table operation, or the lookup table operation network includes more than two lookup table operations.

[0044] Further as a preferred embodiment, the step D includes:

[0045] D1. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More