Technology Mapping Method of Adder with Optimum Layout Structure Based on FPGA

A technology of process mapping and layout structure, which is applied in the fields of instrumentation, calculation, electrical digital data processing, etc., can solve problems such as inability to use adders to calculate, and achieve the effect of optimizing chip layout structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

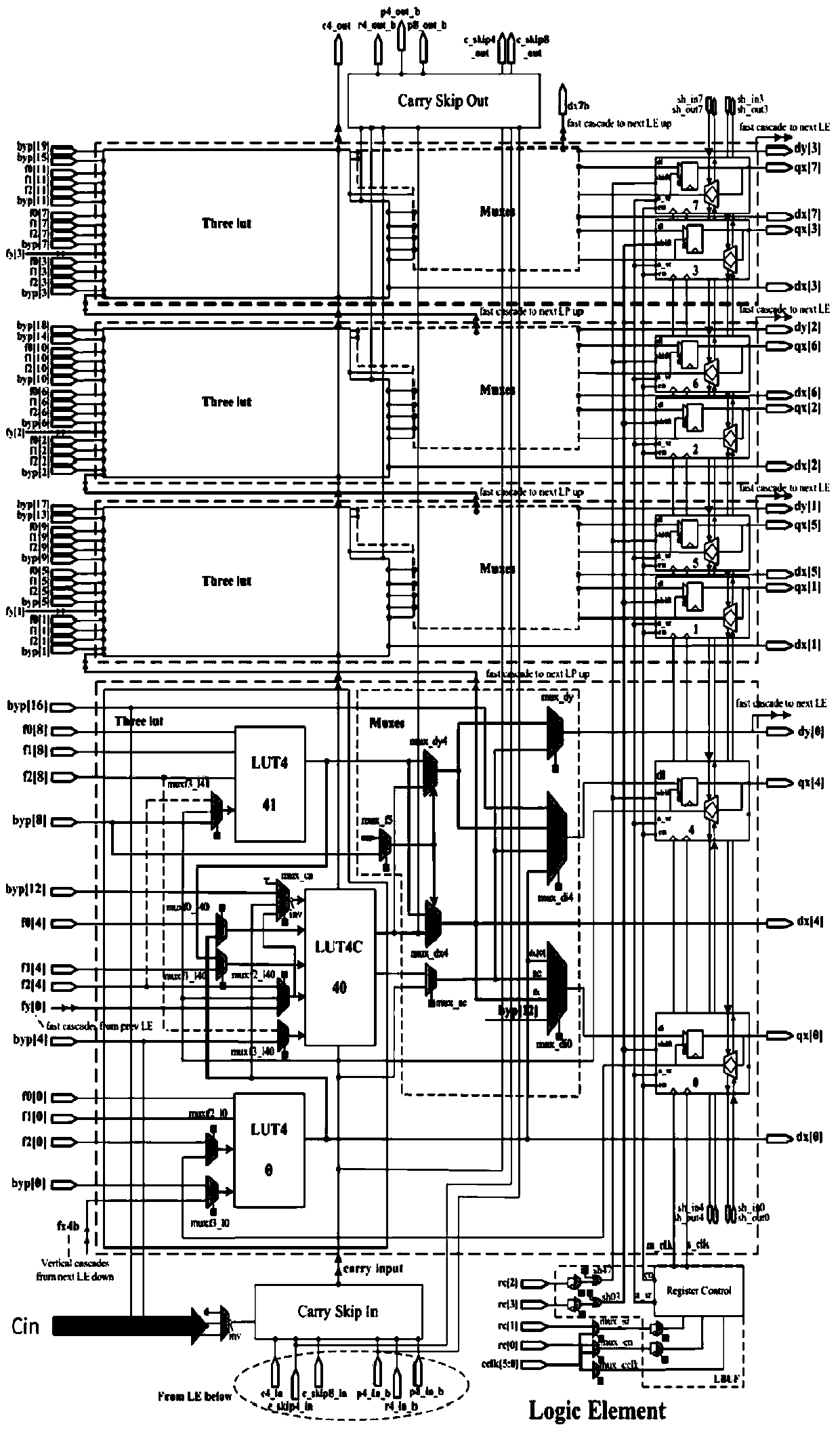

Image

Examples

Embodiment 1

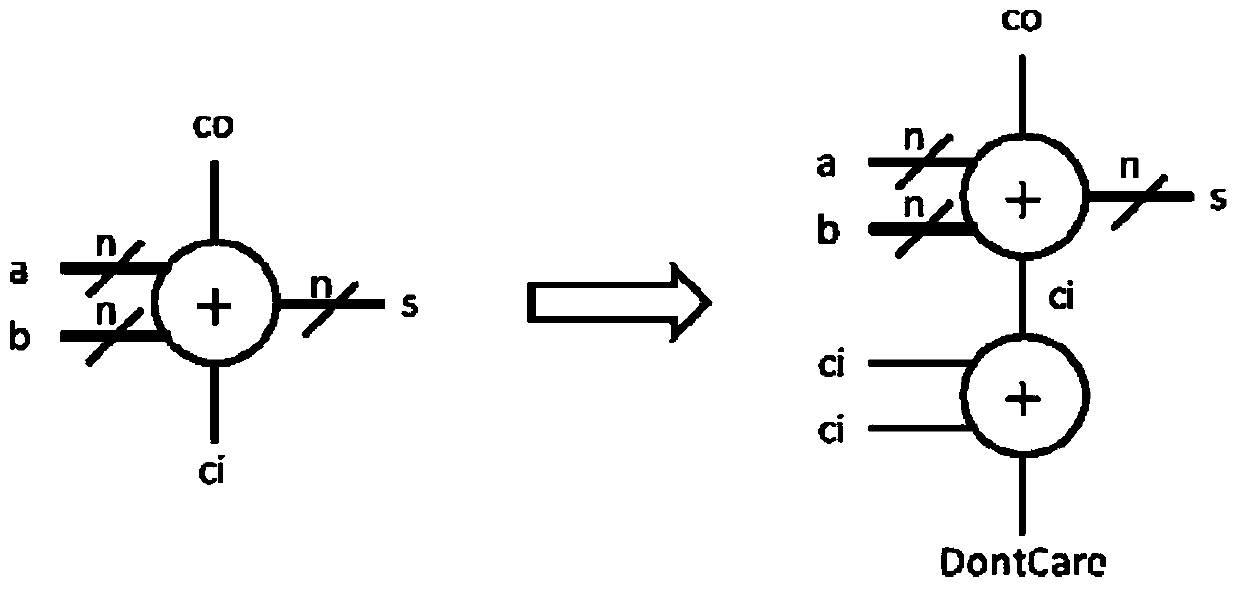

[0028] In this embodiment, a process mapping method of an n-bit full adder with an optimized layout structure is taken as an example for illustration. Logic diagram such as image 3 shown.

[0029] The addition logical operation of the present embodiment is: calculate the sum s (n bits) of the first addend a of n bits and the second addend b of n bits, wherein the carry input signal of the lowest bit of the addition is ci, and the addition operation The carry out signal is co. n is an integer and not less than 1.

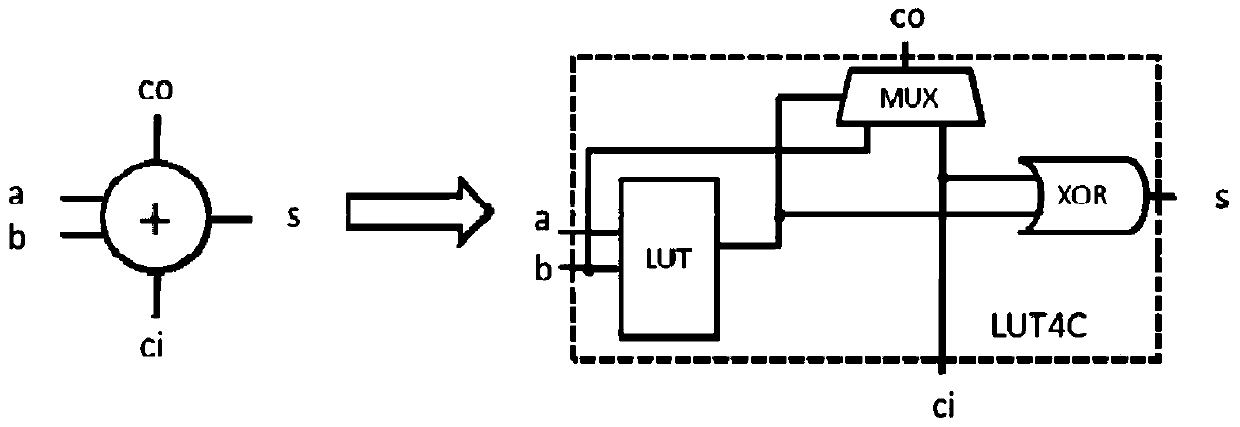

[0030] In this embodiment, the carry input ci is realized by the logic operation of a single one-bit adder. Specifically:

[0031] The two input terminals of an adder (implemented by LUT4C) respectively input the carry input signal ci of the lowest bit of the addition, that is, the logic for calculating ci+ci. When ci=0, no matter the carry input signal of the adder is 1 or 0, its carry output signal is 0; when ci=1, no matter the carry input signal of the adde...

Embodiment 2

[0037] In this embodiment, a process mapping method in which an m-bit full adder with an optimized layout structure and an n-bit full adder are cascaded through a LUT4C is taken as an example for illustration. Logical map such as Figure 5 shown.

[0038] Wherein, the addition logic operation of the n-bit full adder is: calculate the sum sa (n-bit) of the first addend a of n-bit and the second addend b of n-bit, wherein the carry input signal of the lowest bit of addition is cia , the carry output signal of the addition operation is coa. n is an integer and not less than 1.

[0039] The addition logic operation of the m-bit full adder is: calculate the sum sb (m-bit) of the first addend c of m-bit and the second addend d of m-bit, wherein the carry input signal of the lowest bit of the addition is cib, and the addition The carry output signal of the operation is cob. m is an integer and not less than 1.

[0040] The process mapping method provided by the above embodiments...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More