Patents

Literature

402 results about "Electronic design automation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

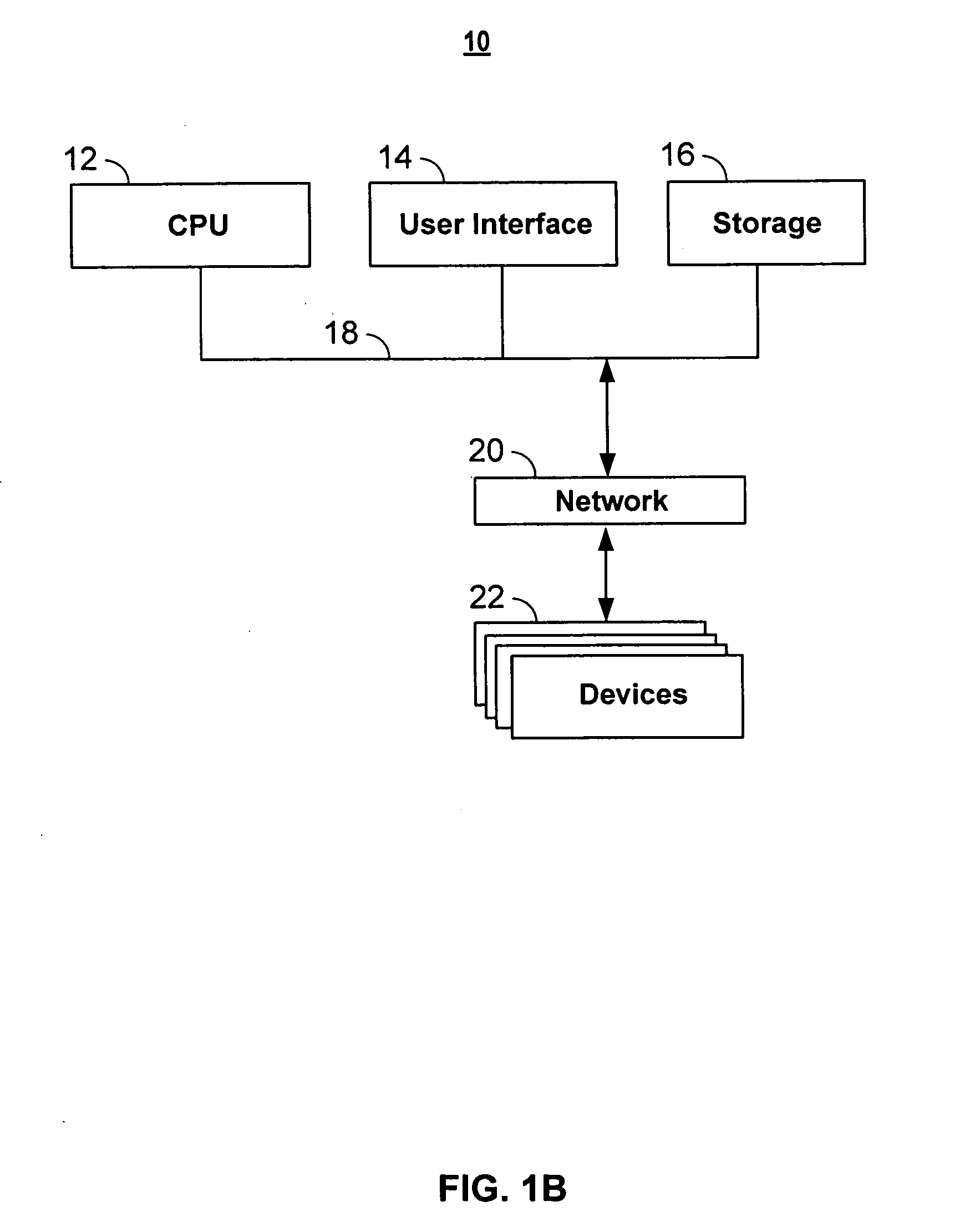

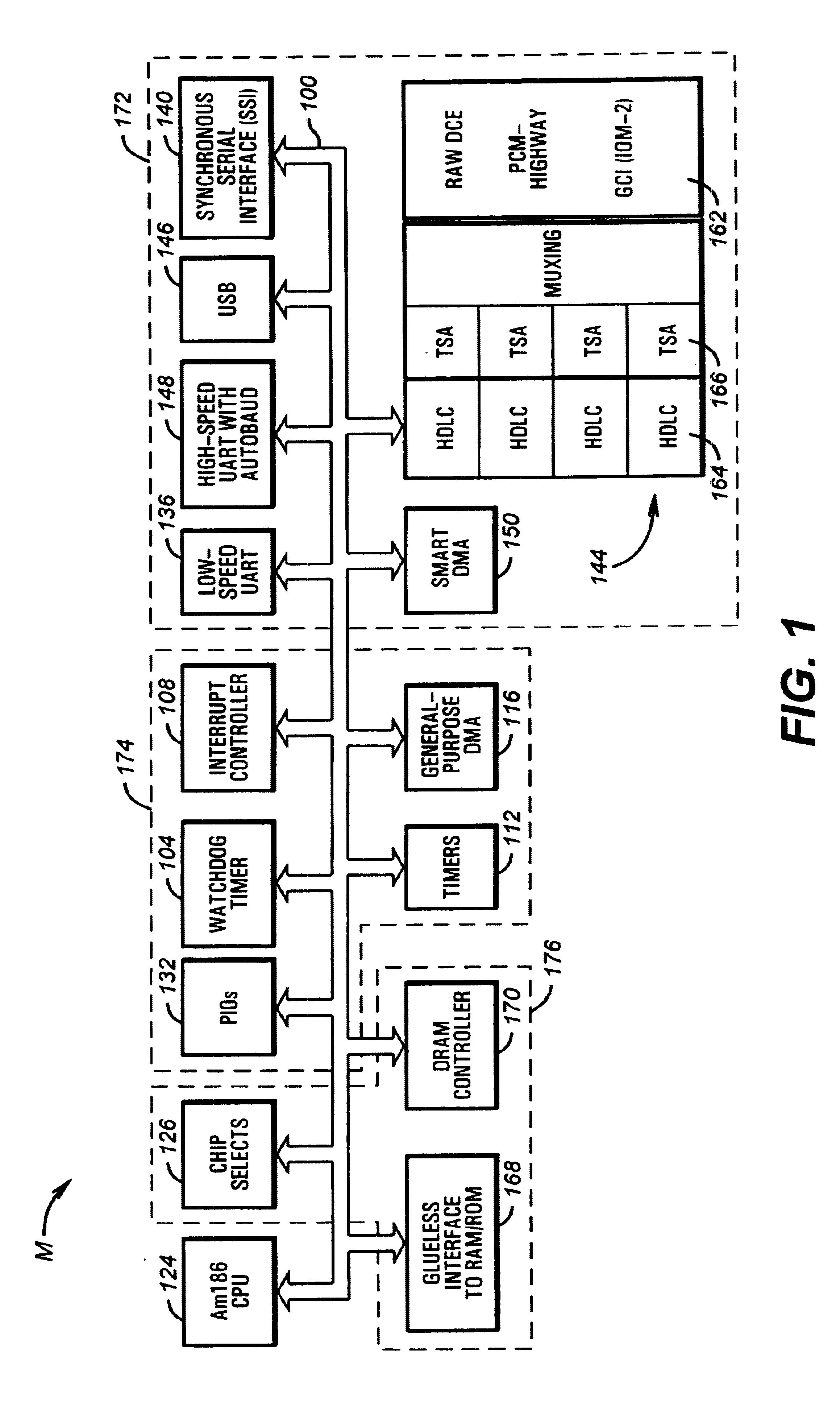

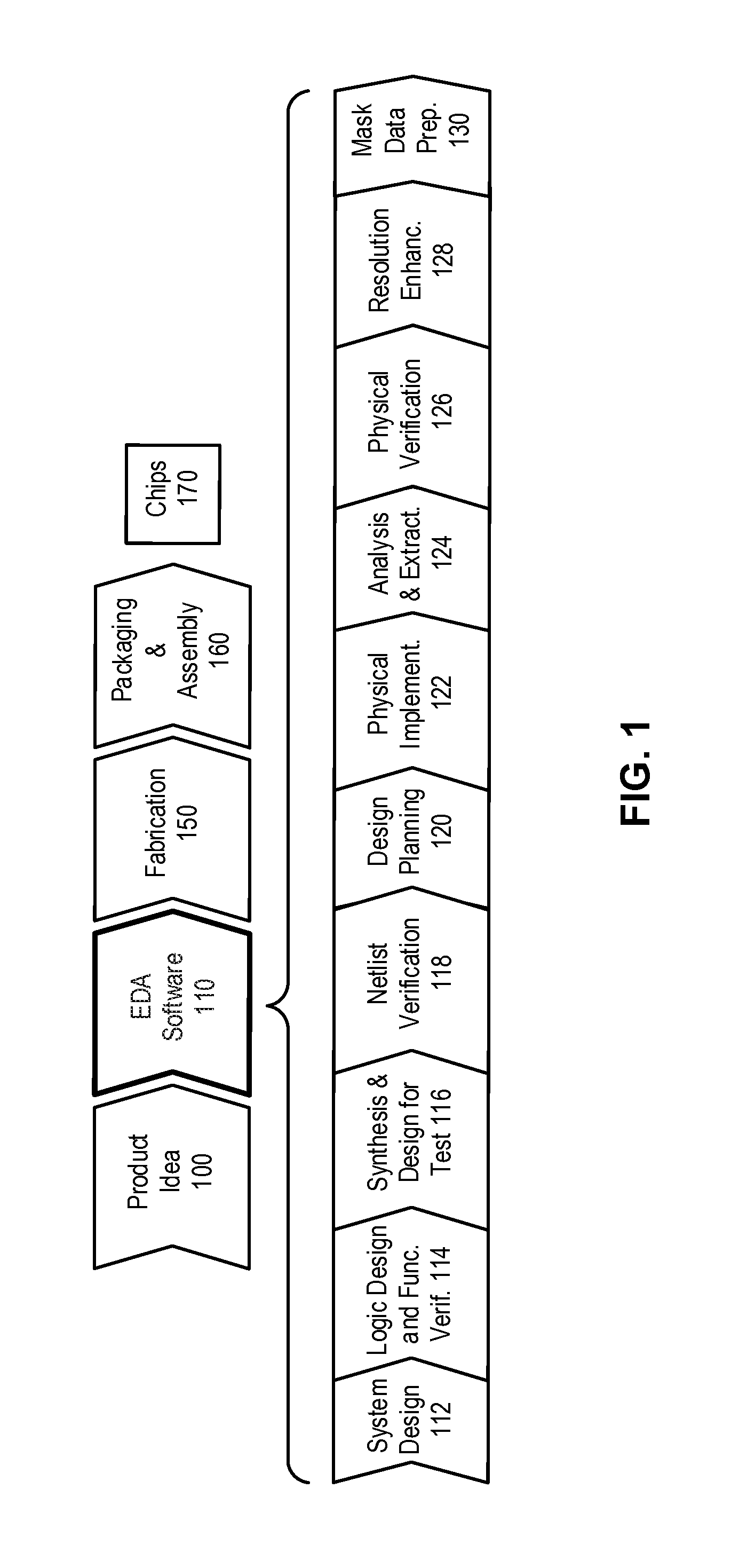

Electronic design automation (EDA), also referred to as electronic computer-aided design (ECAD), is a category of software tools for designing electronic systems such as integrated circuits and printed circuit boards. The tools work together in a design flow that chip designers use to design and analyze entire semiconductor chips. Since a modern semiconductor chip can have billions of components, EDA tools are essential for their design.

Distributed electronic design automation environment

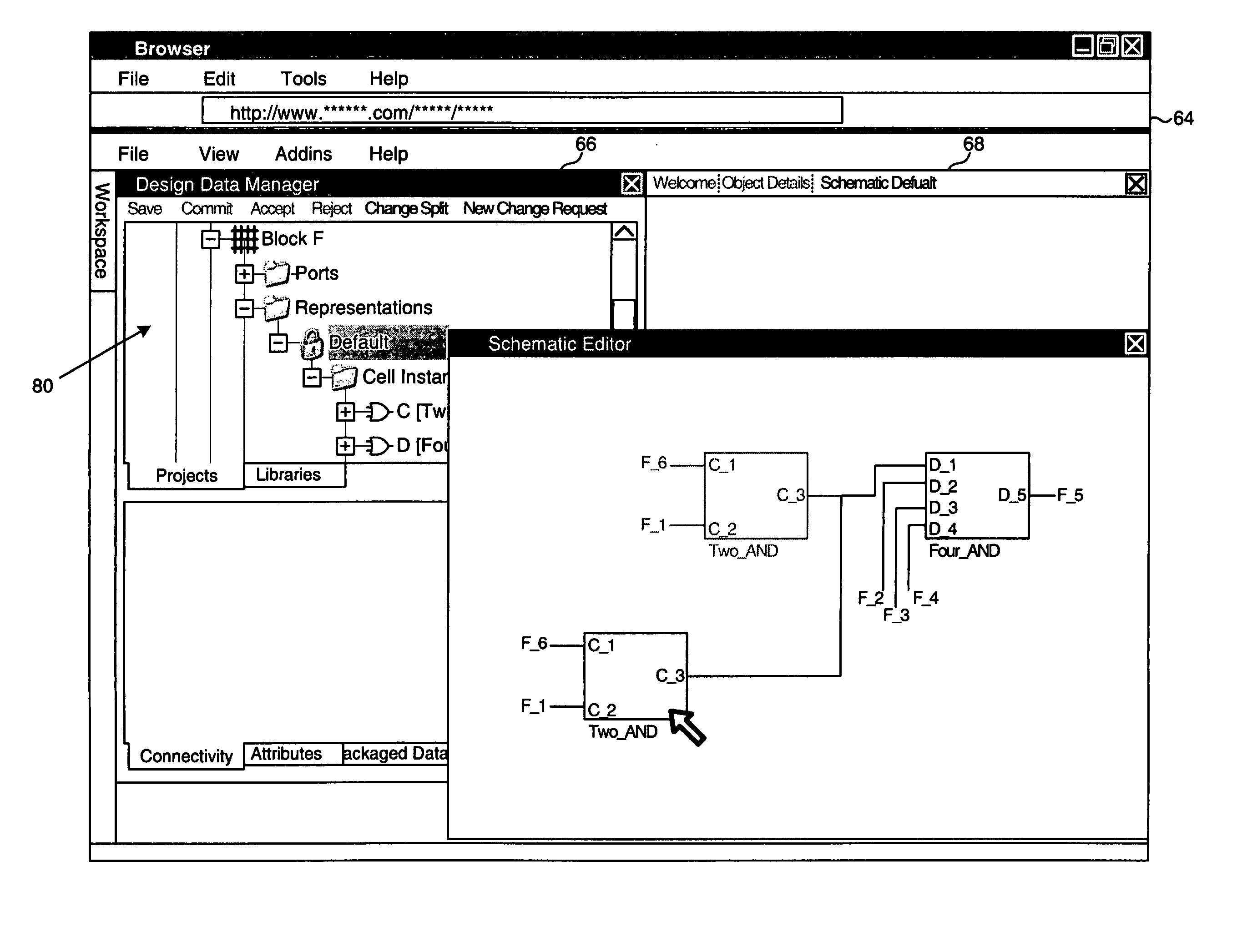

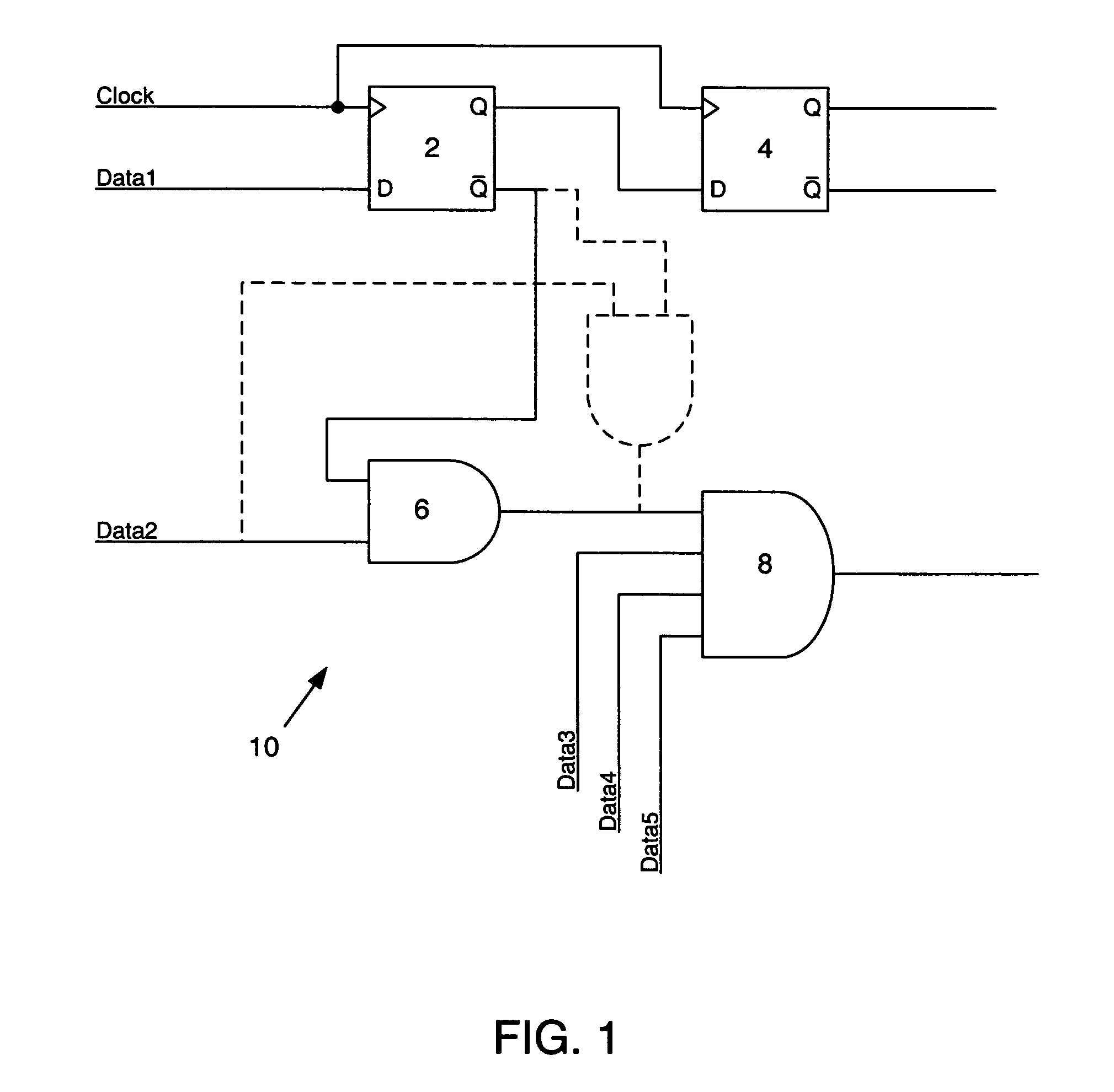

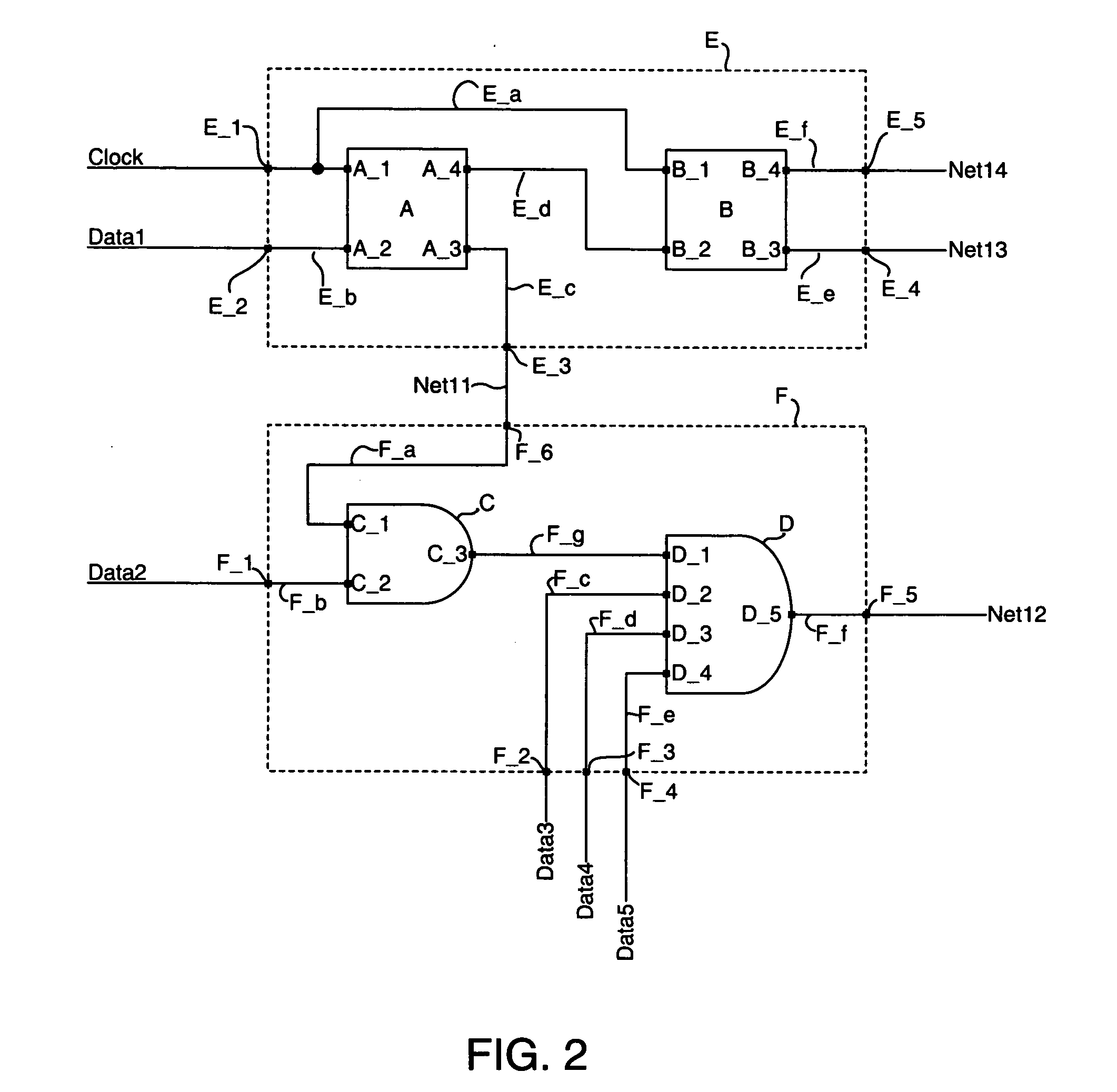

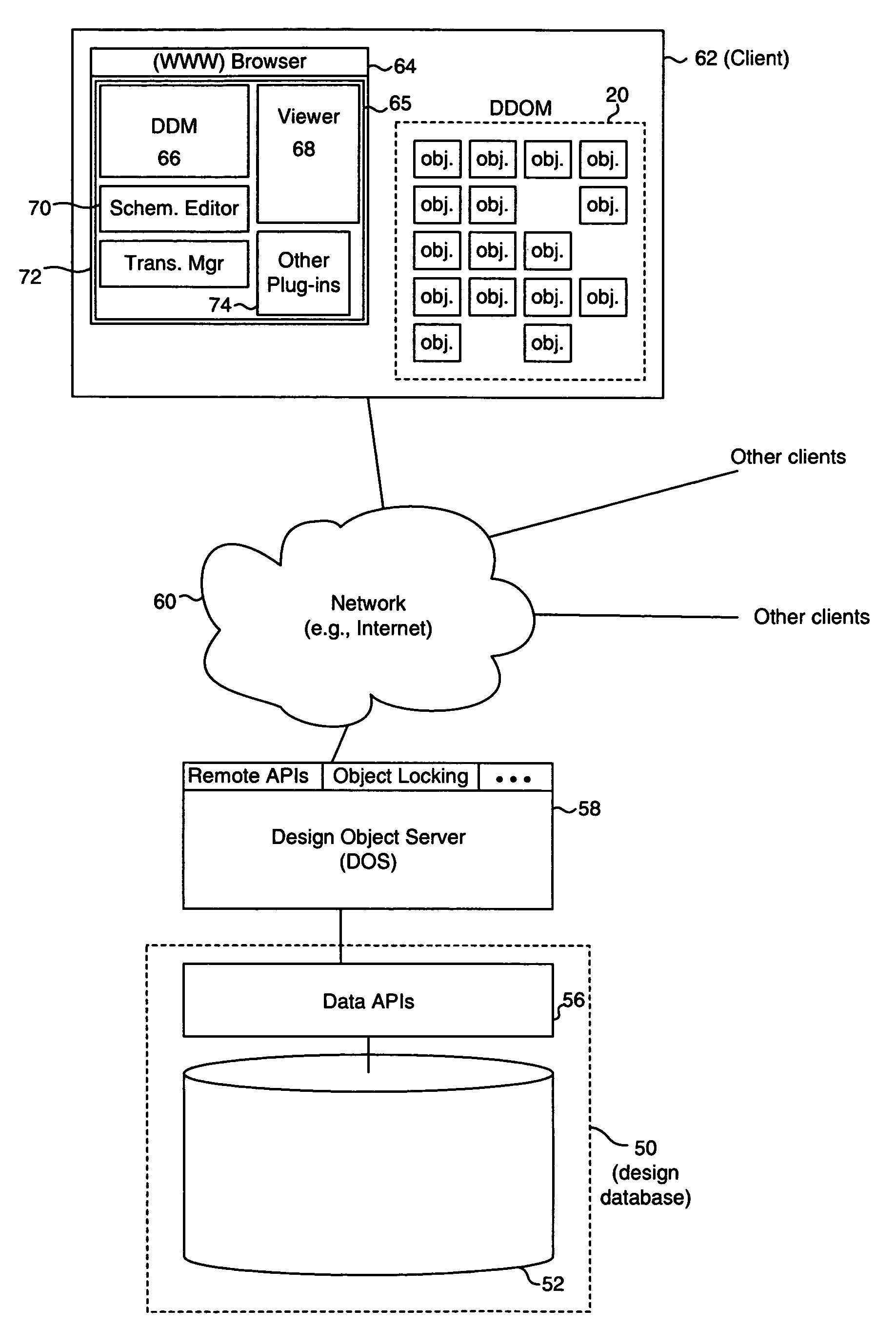

InactiveUS20060101368A1Readily apparentCAD network environmentComputer programmed simultaneously with data introductionWeb browserConfigfs

PCB Logical design data is stored in a database according to a connectivity-based data model. Circuit functional blocks, inputs and outputs of functional blocks, and signals are stored as separate data structures. Those structures may be edited by users at separate clients during concurrent editing sessions. Profile data for each of multiple users specifies logical design data elements accessible by, and PCB design software to be provided to, that user. The PCB design software may be plug-ins executable within a web browser at a client, and the client computers may communicate with the database via the Internet. Layout data may also be stored in the database, with elements of the layout data mapped to elements of the logical design data. Constraint data may also be stored in the database, with elements of the constraint data being mapped to elements of the layout data.

Owner:MENTOR GRAPHICS CORP

Distributed electronic design automation environment

ActiveUS7546571B2CAD network environmentComputer programmed simultaneously with data introductionWeb browserDesign software

PCB Logical design data is stored in a database according to a connectivity-based data model. Circuit functional blocks, inputs and outputs of functional blocks, and signals are stored as separate data structures. Those structures may be edited by users at separate clients during concurrent editing sessions. Profile data for each of multiple users specifies logical design data elements accessible by, and PCB design software to be provided to, that user. The PCB design software may be plug-ins executable within a web browser at a client, and the client computers may communicate with the database via the Internet. Layout data may also be stored in the database, with elements of the layout data mapped to elements of the logical design data. Constraint data may also be stored in the database, with elements of the constraint data being mapped to elements of the layout data.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

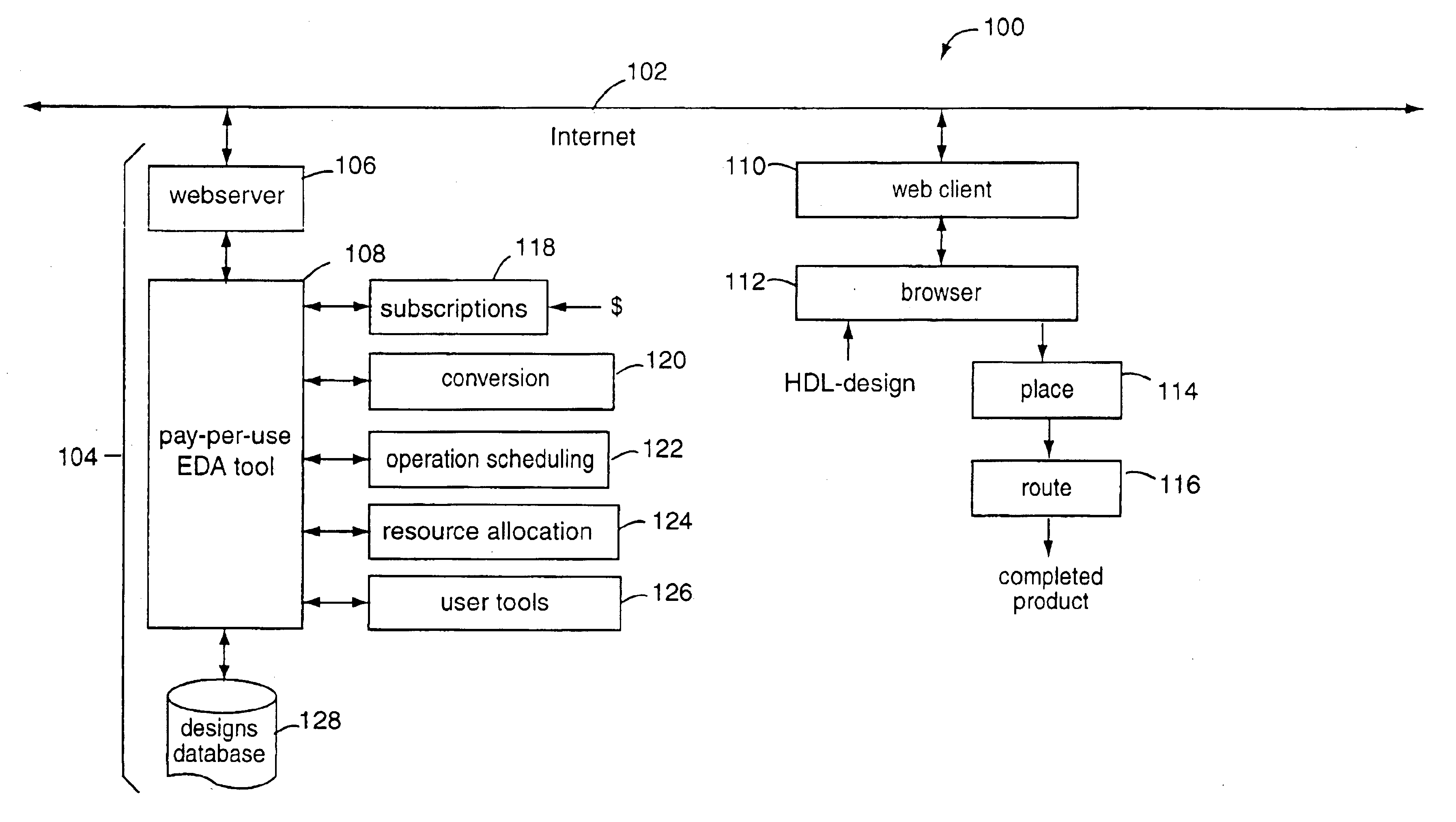

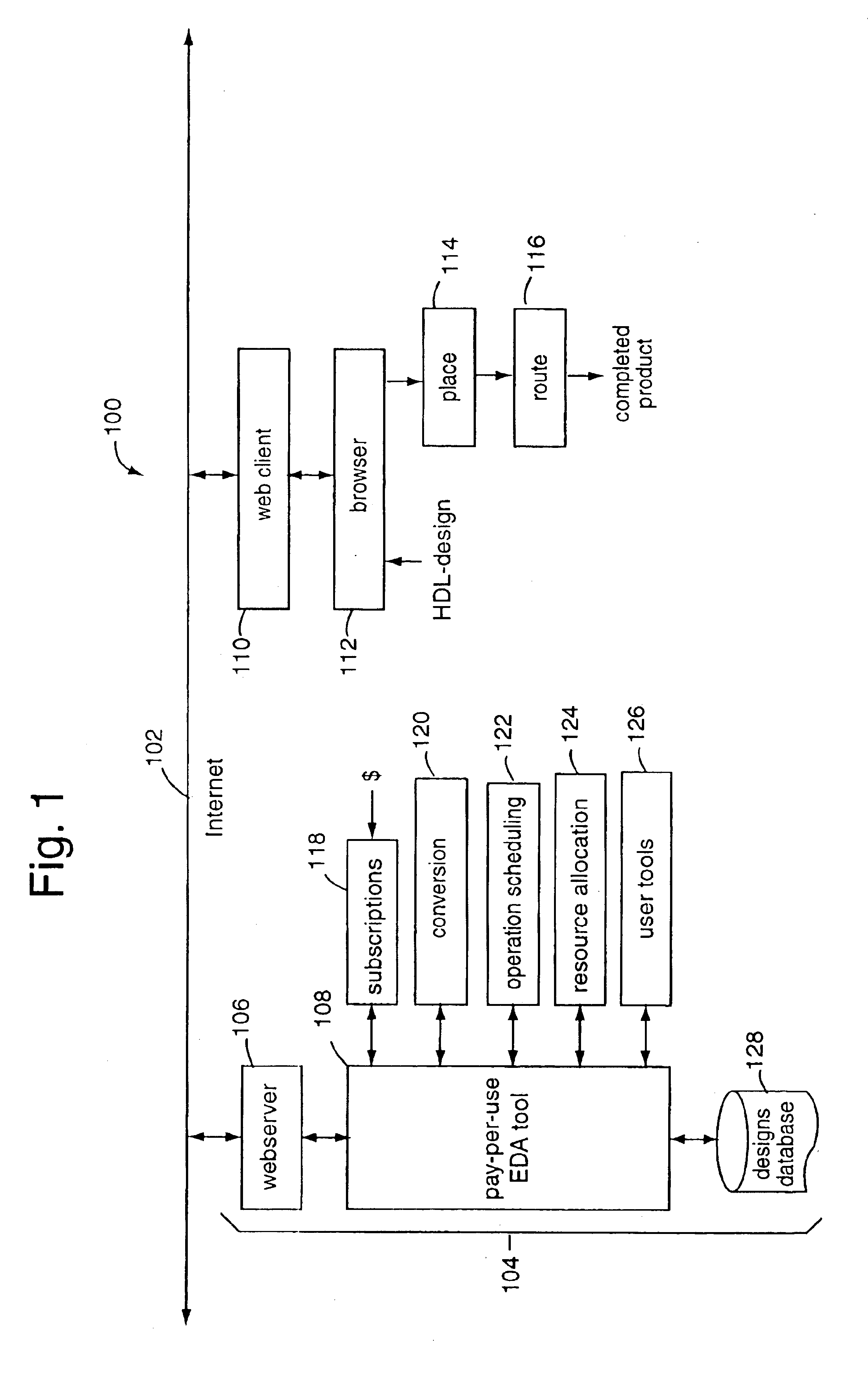

Behavioral-synthesis electronic design automation tool business-to-business application service provider

InactiveUS6782511B1Distributed efficiently and easilyCAD circuit designSoftware simulation/interpretation/emulationWeb serviceIntellectual property

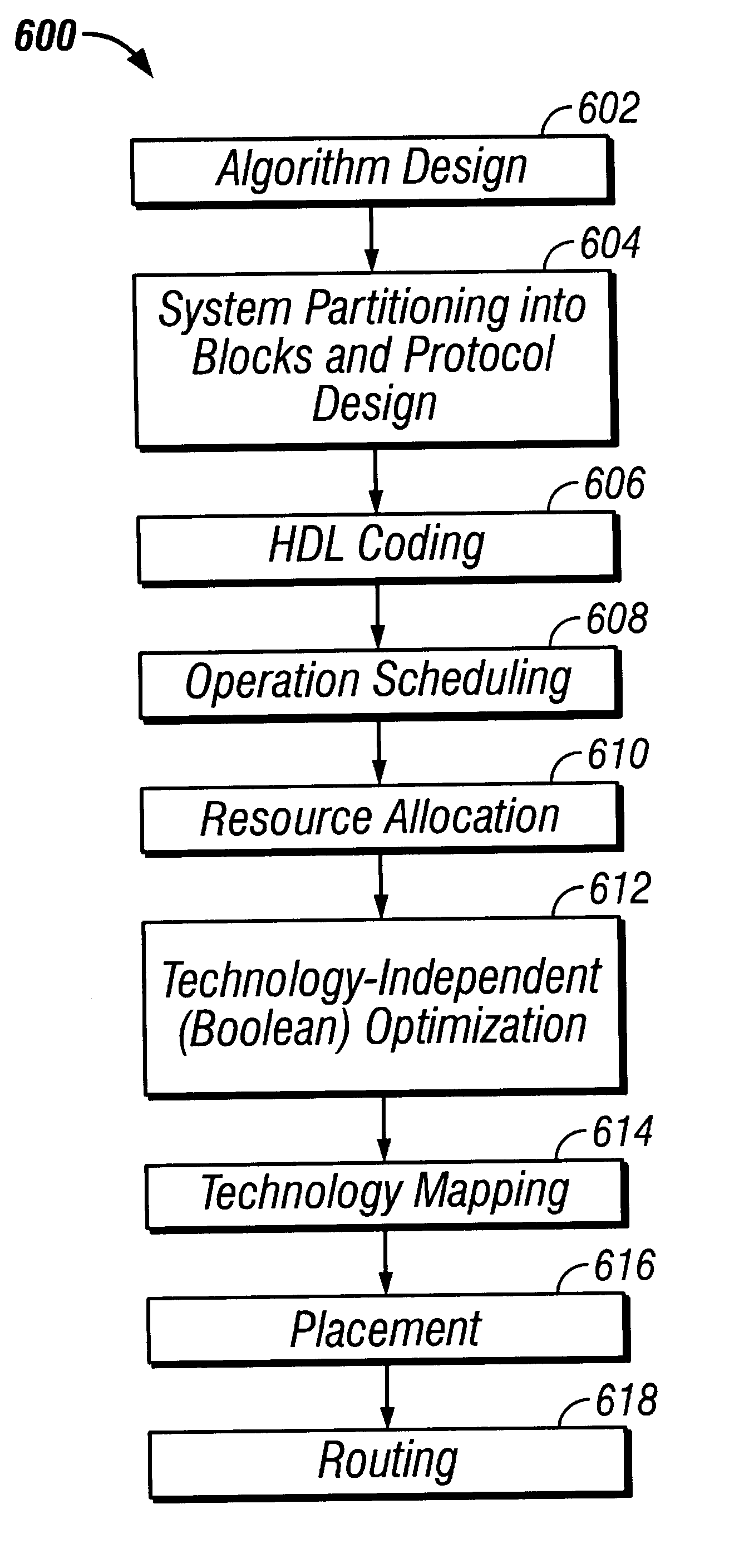

A business-to-business application service provider includes an Internet website and webserver with EDA-on-demand solutions for system-on-a-chip designers. Such website allows electronic designs in hardware description language to be uploaded into a front-end EDA design environment. A behavioral model simulation tool hosted privately on the webserver tests and validates the design. Such tool executes only in the secure environment of the business-to-business application service provider. The validated solution is then downloaded back over the Internet for a pay-per-use fee to the customer, and in a form ready to be placed and routed by a back-end EDA tool. Such validated design solutions are also downloadable to others in exchange for other designs, or available in technology libraries. The intellectual property created can be re-used, sold, shared, exchanged, and otherwise distributed efficiently and easily from a central for-profit clearinghouse.

Owner:CADENCE DESIGN SYST INC

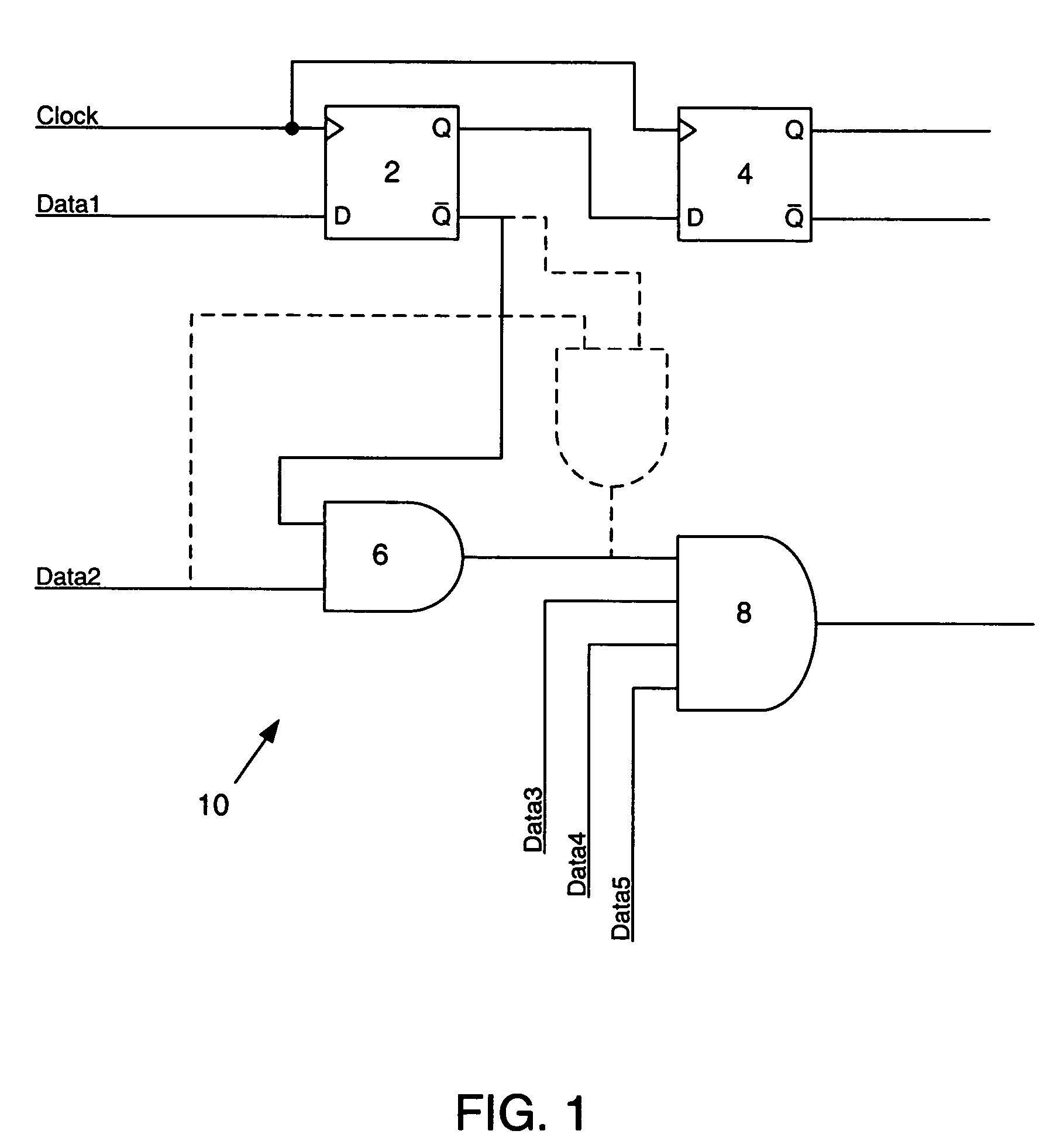

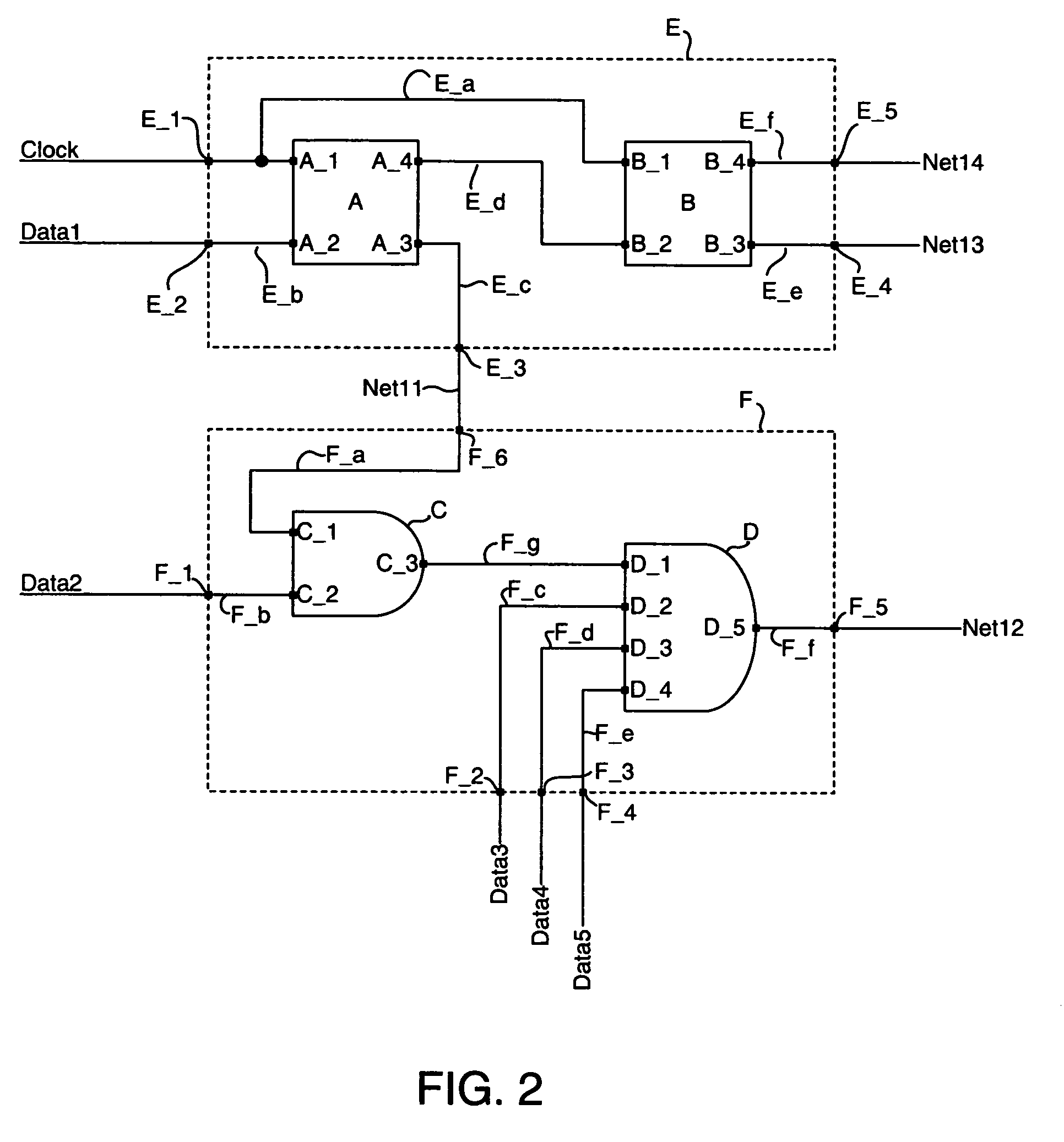

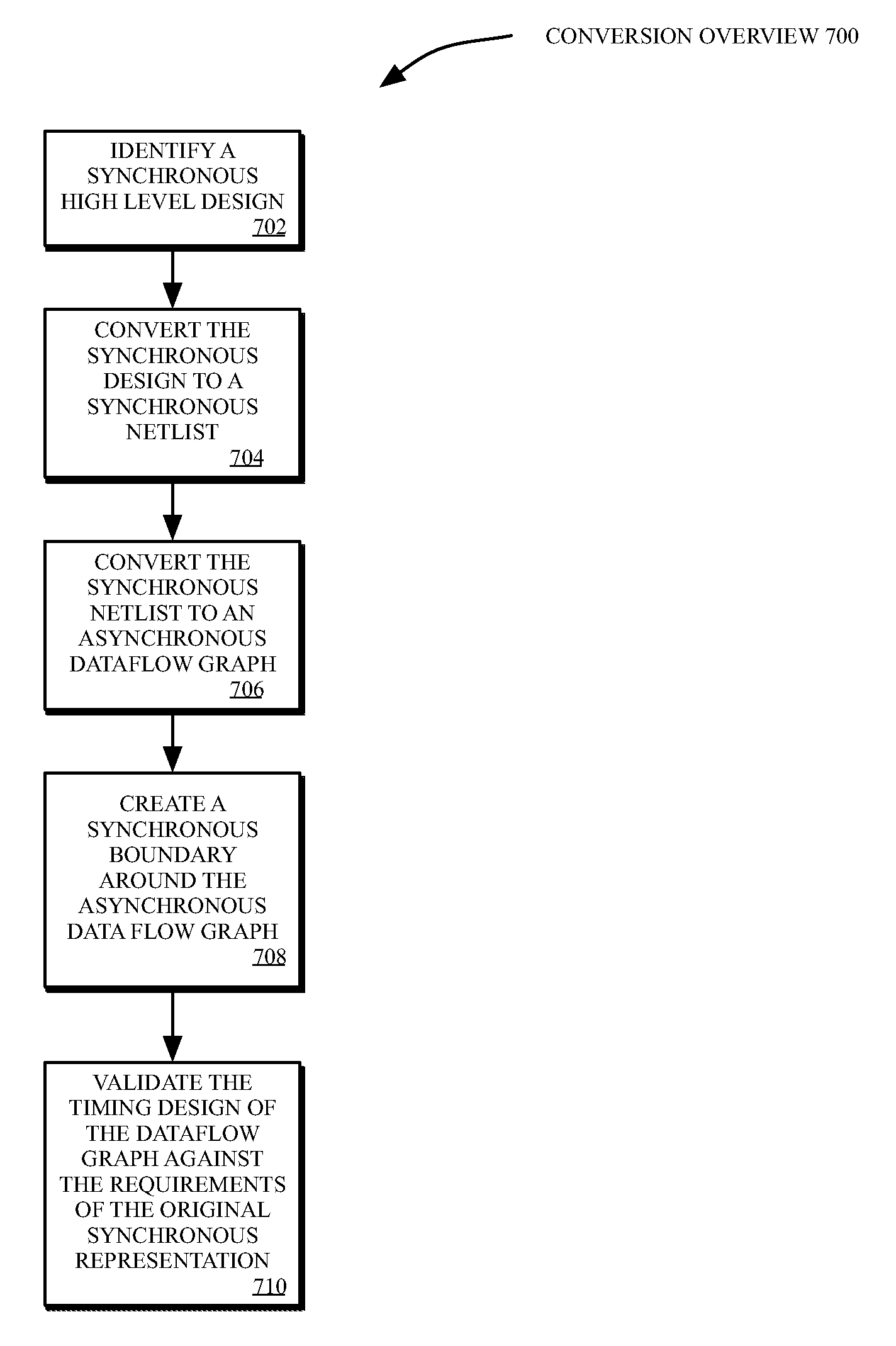

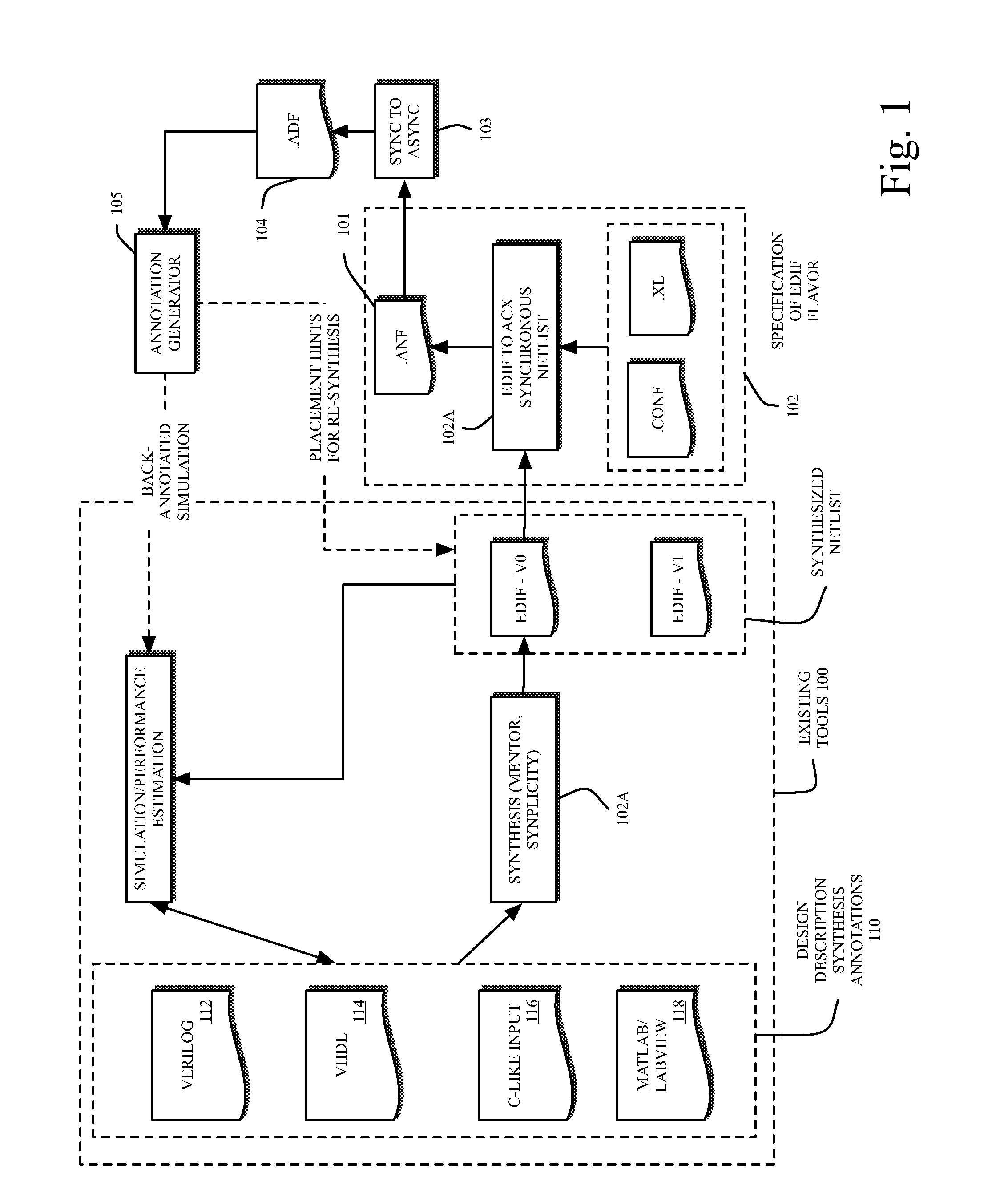

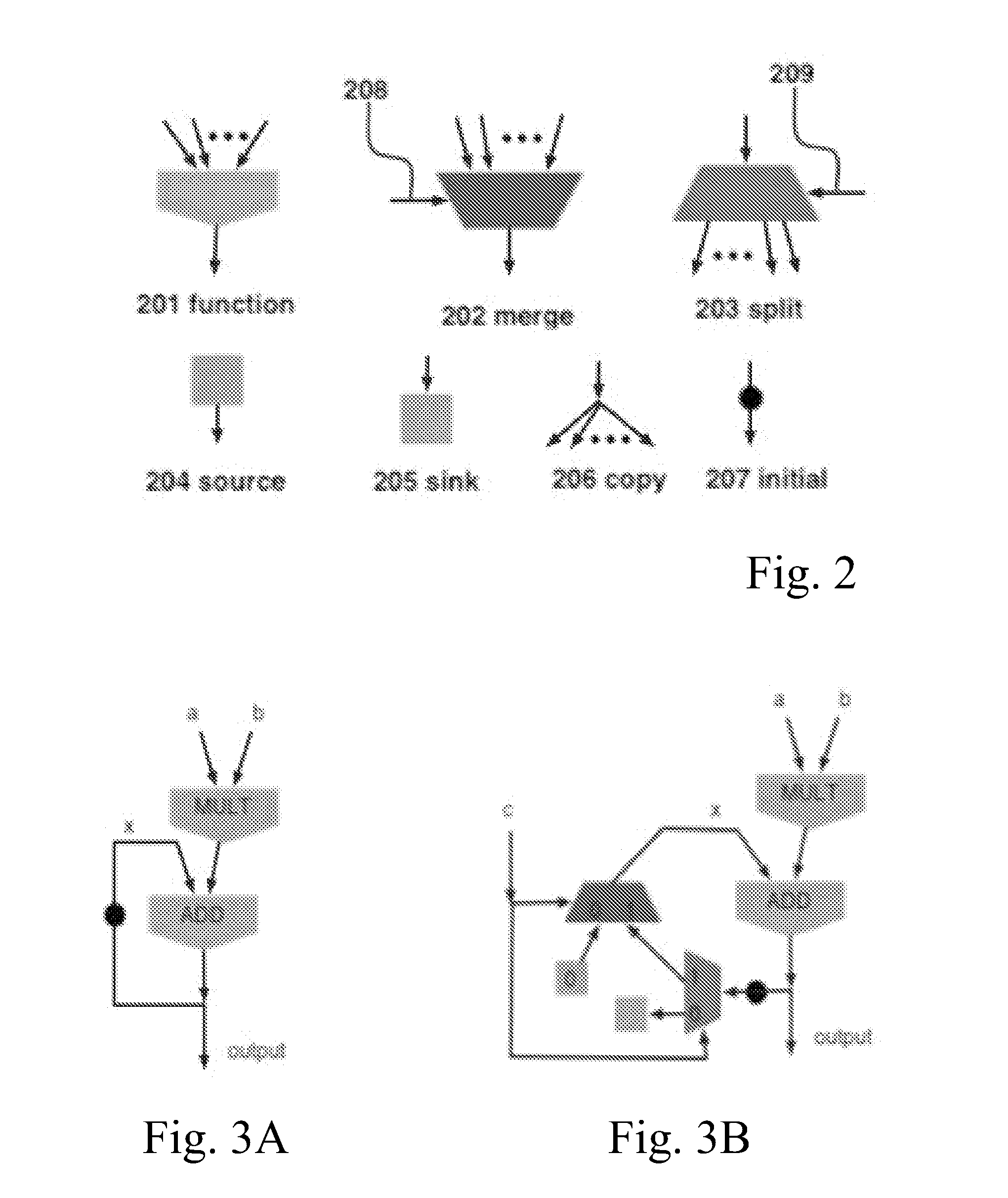

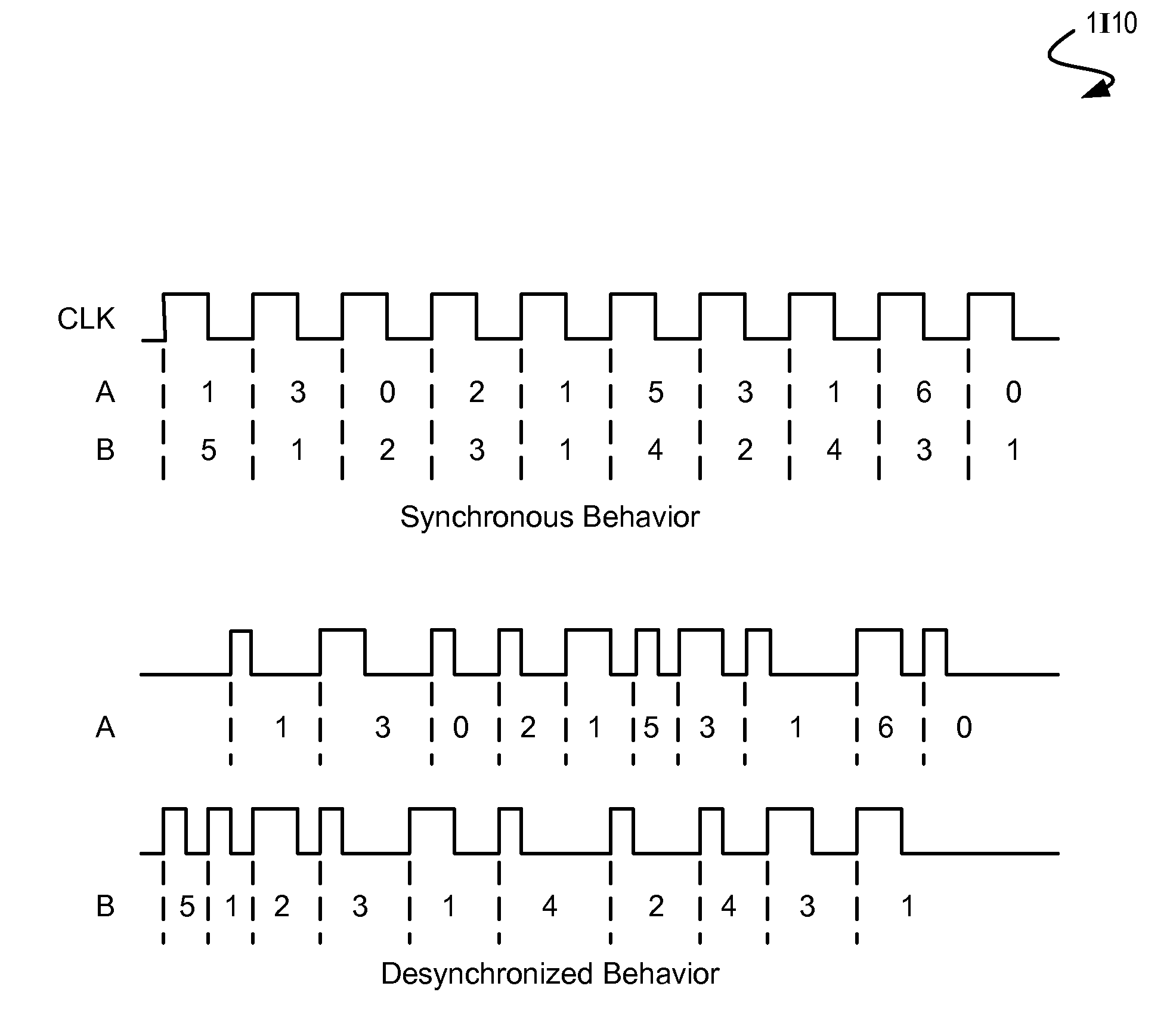

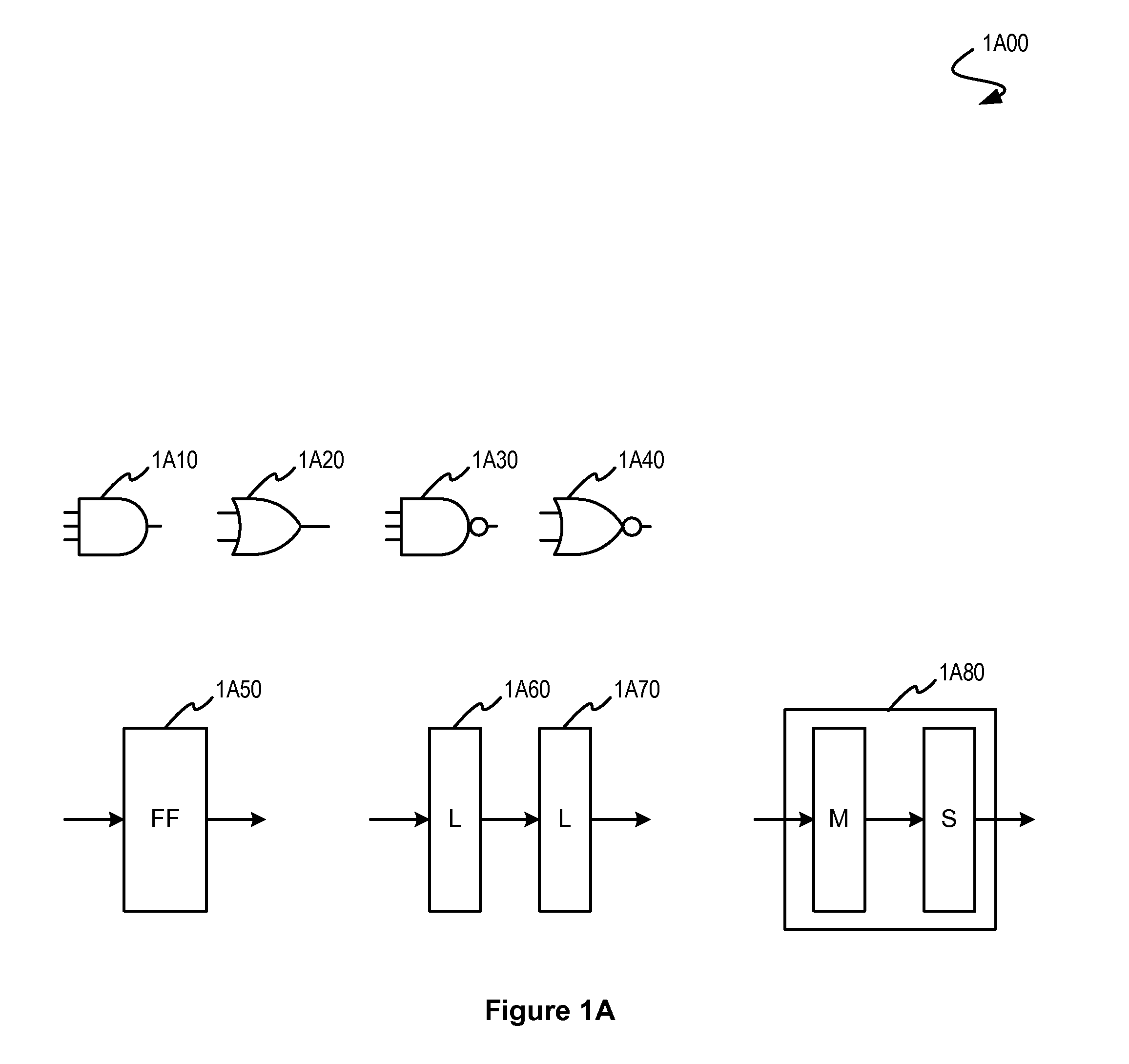

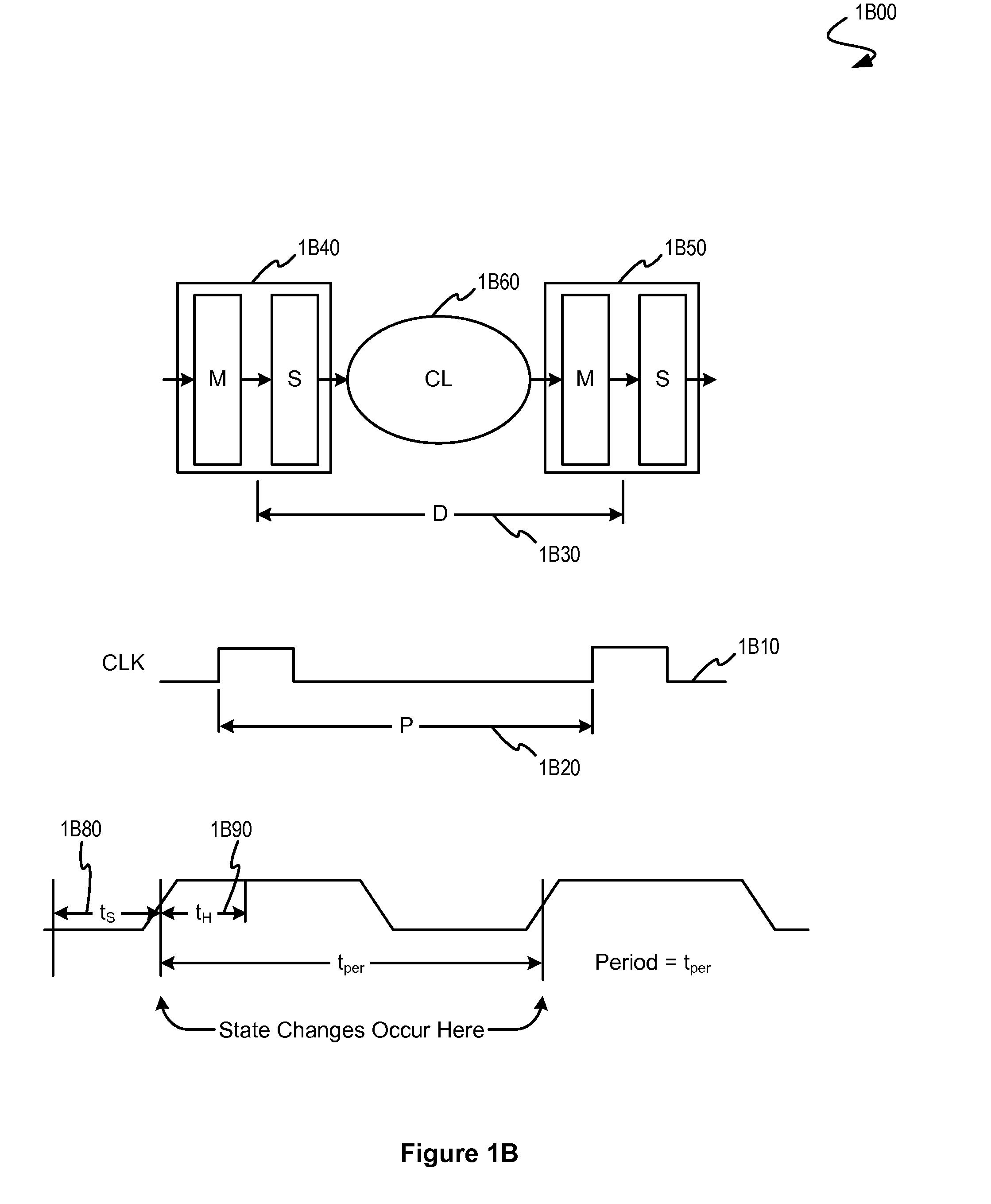

Systems and methods for performing automated conversion of representations of synchronous circuit designs to and from representations of asynchronous circuit designs

ActiveUS20070256038A1Easy to FeedbackCAD circuit designSoftware simulation/interpretation/emulationComputer architectureAsynchronous circuit design

Methods and systems automate an approach to provide a way to convert a circuit design from a synchronous representation to an asynchronous representation without any designer or user interaction or redesign of the synchronous circuit. An optimized, automated, non-Interactive conversion of representations of synchronous circuit designs to and from representations of asynchronous circuit designs, facilitating traditional electronic design automation (EDA) tools to process and manipulate asynchronous designs while allowing synchronous designs to be implemented using asynchronous hardware solutions. The invention also facilitates feedback to synchronous design tools in synchronous representation for optimization and iteration of the design process by engineers, eliminating the need for engineers to be aware of the underlying asynchronous architecture of the underlying hardware implementation.

Owner:ACHRONIX SEMICON CORP

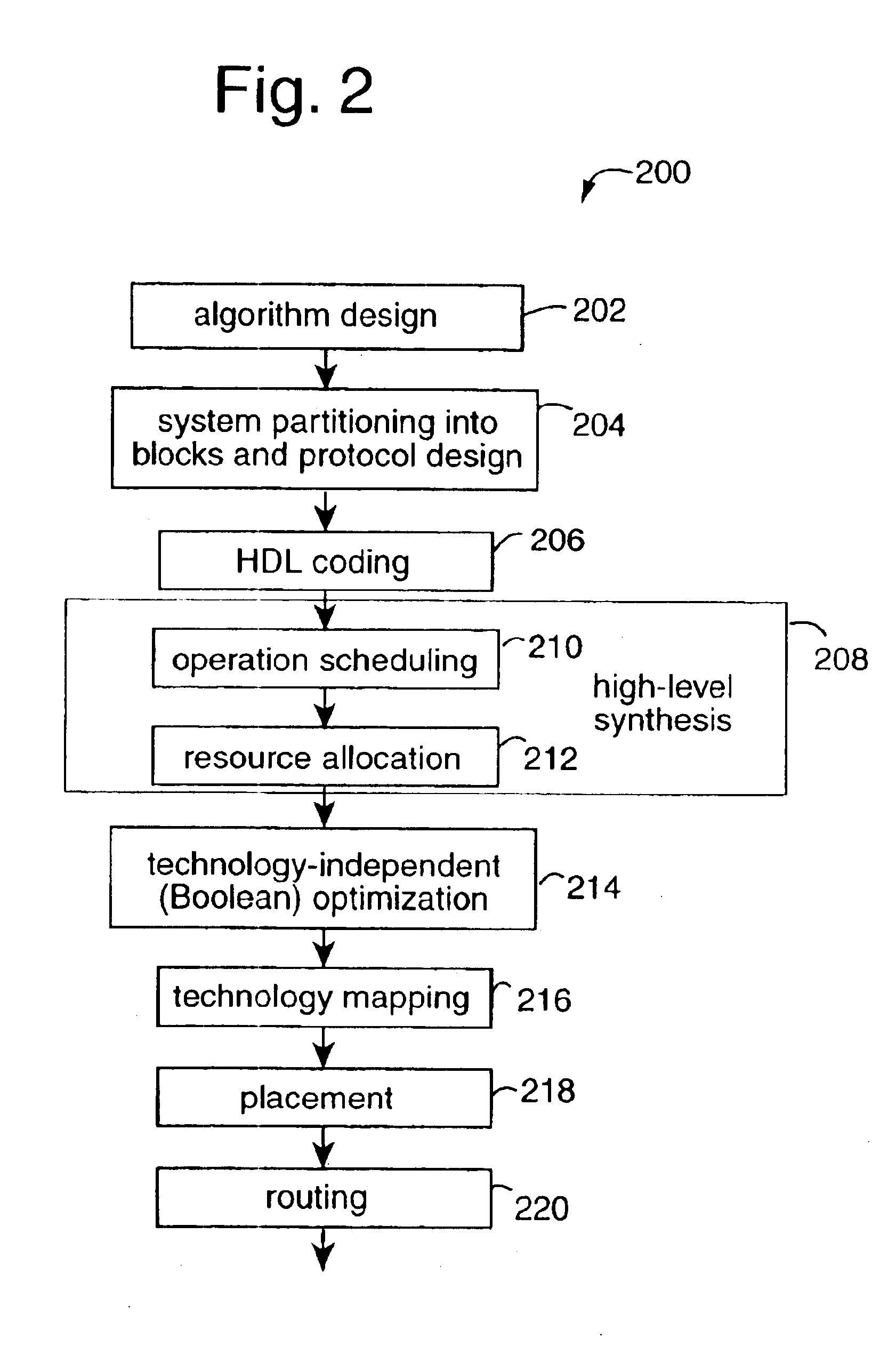

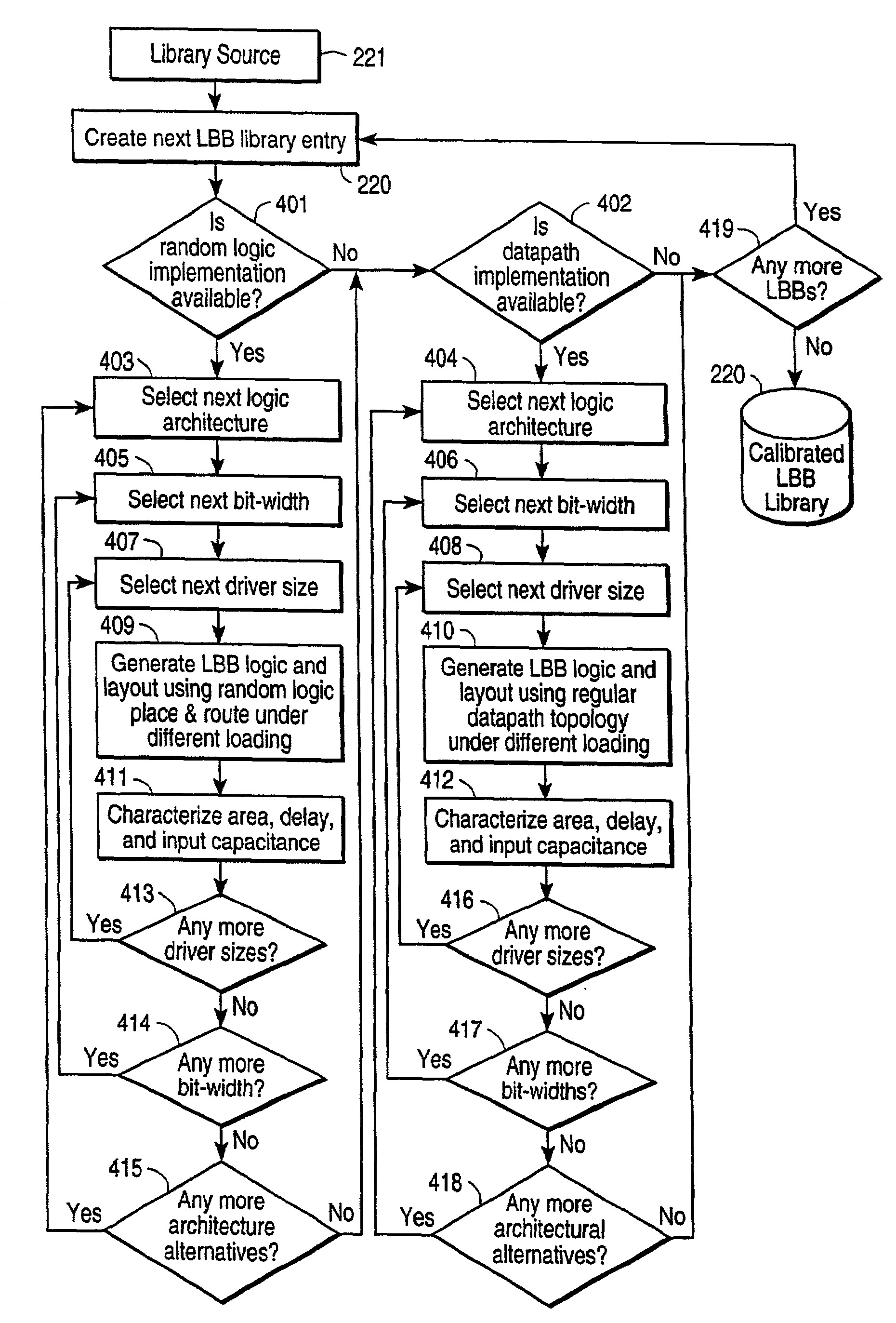

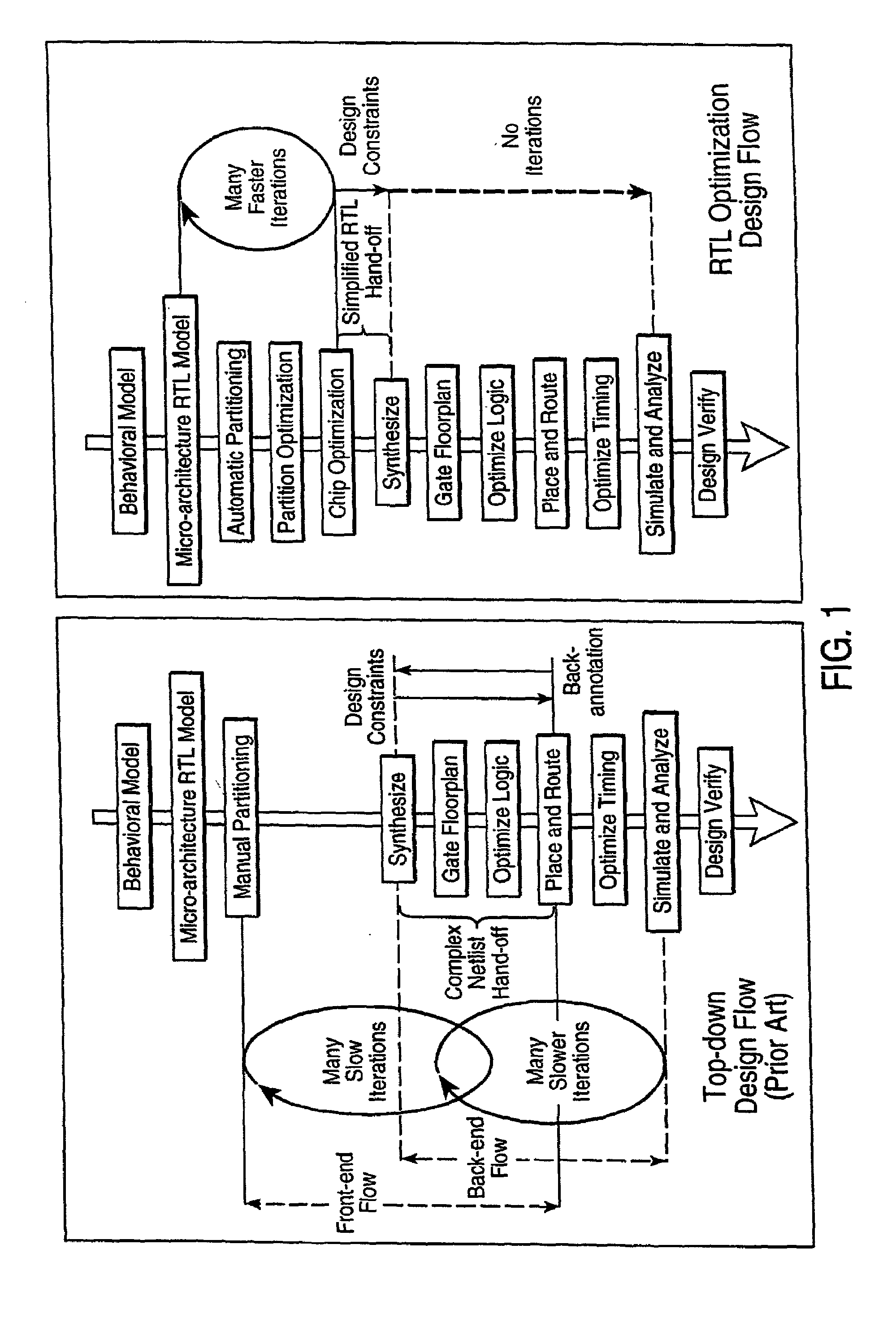

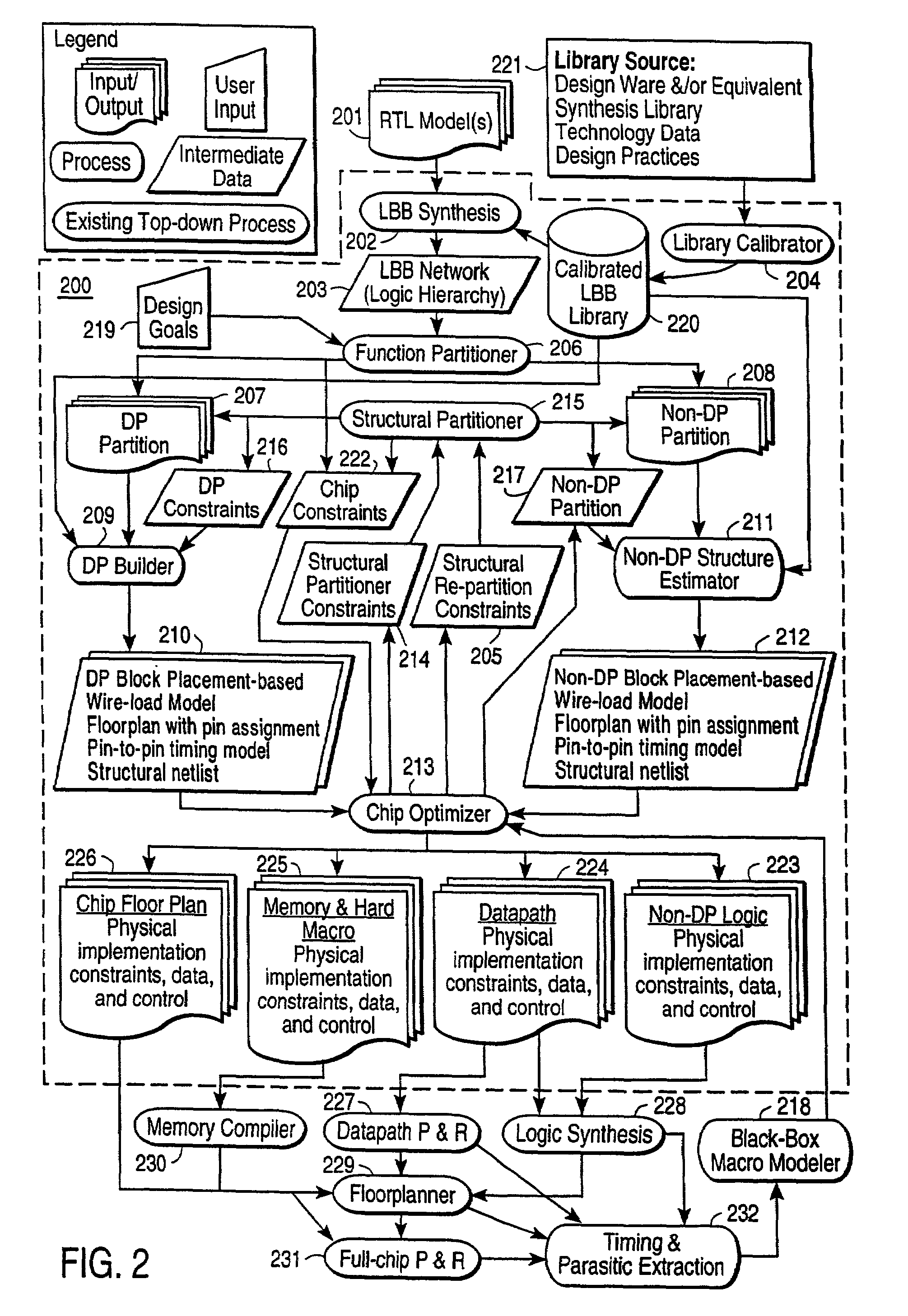

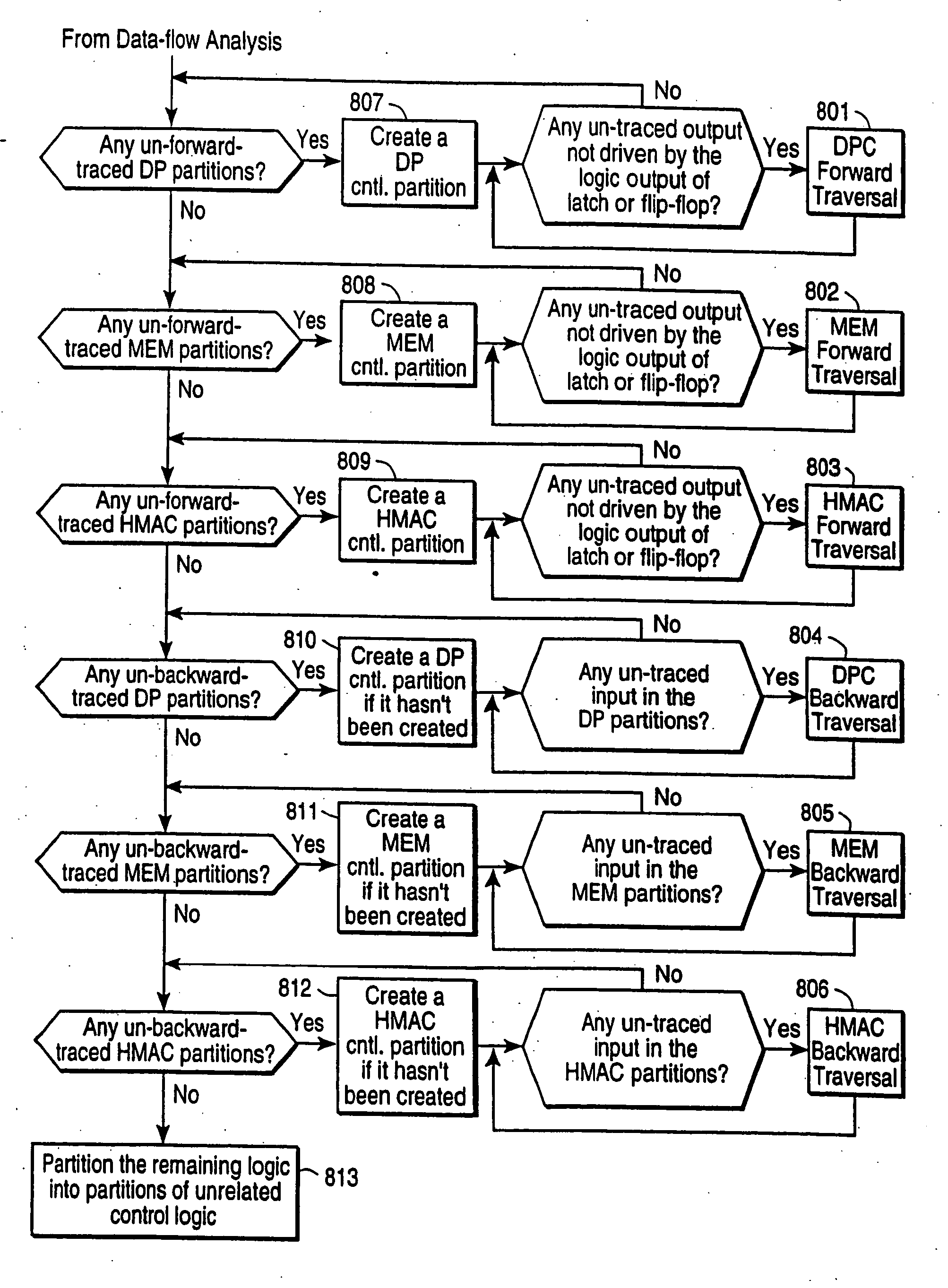

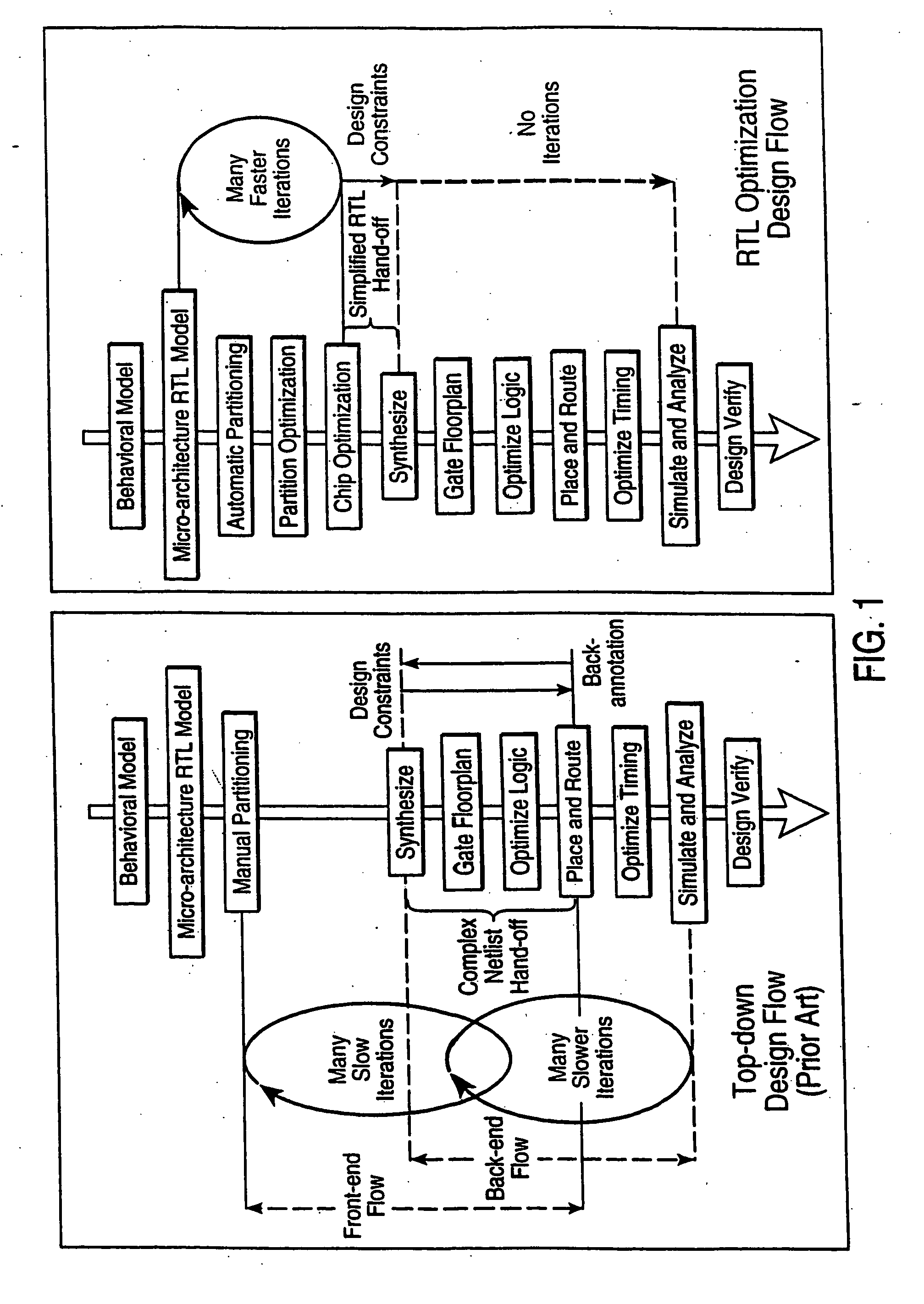

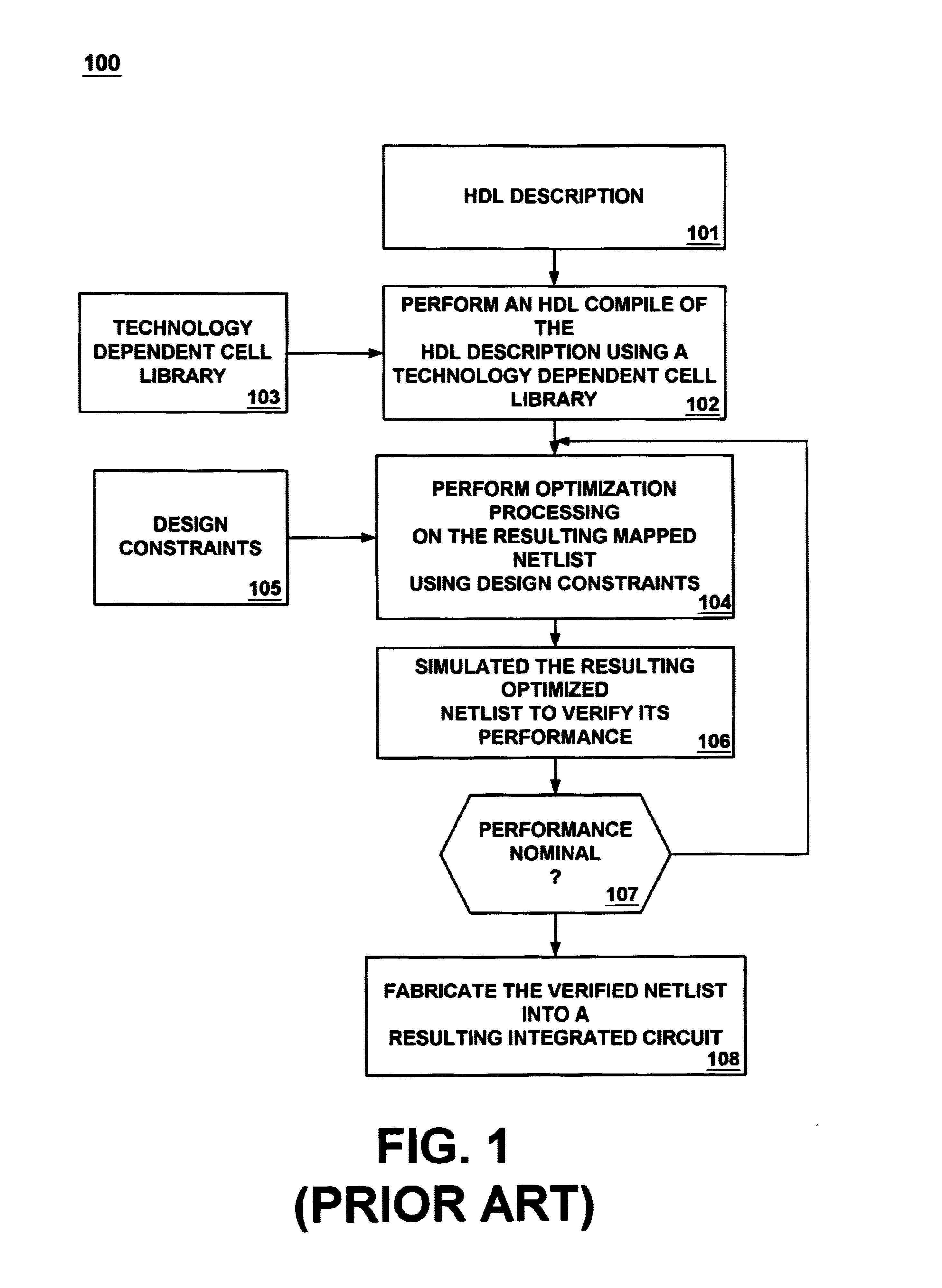

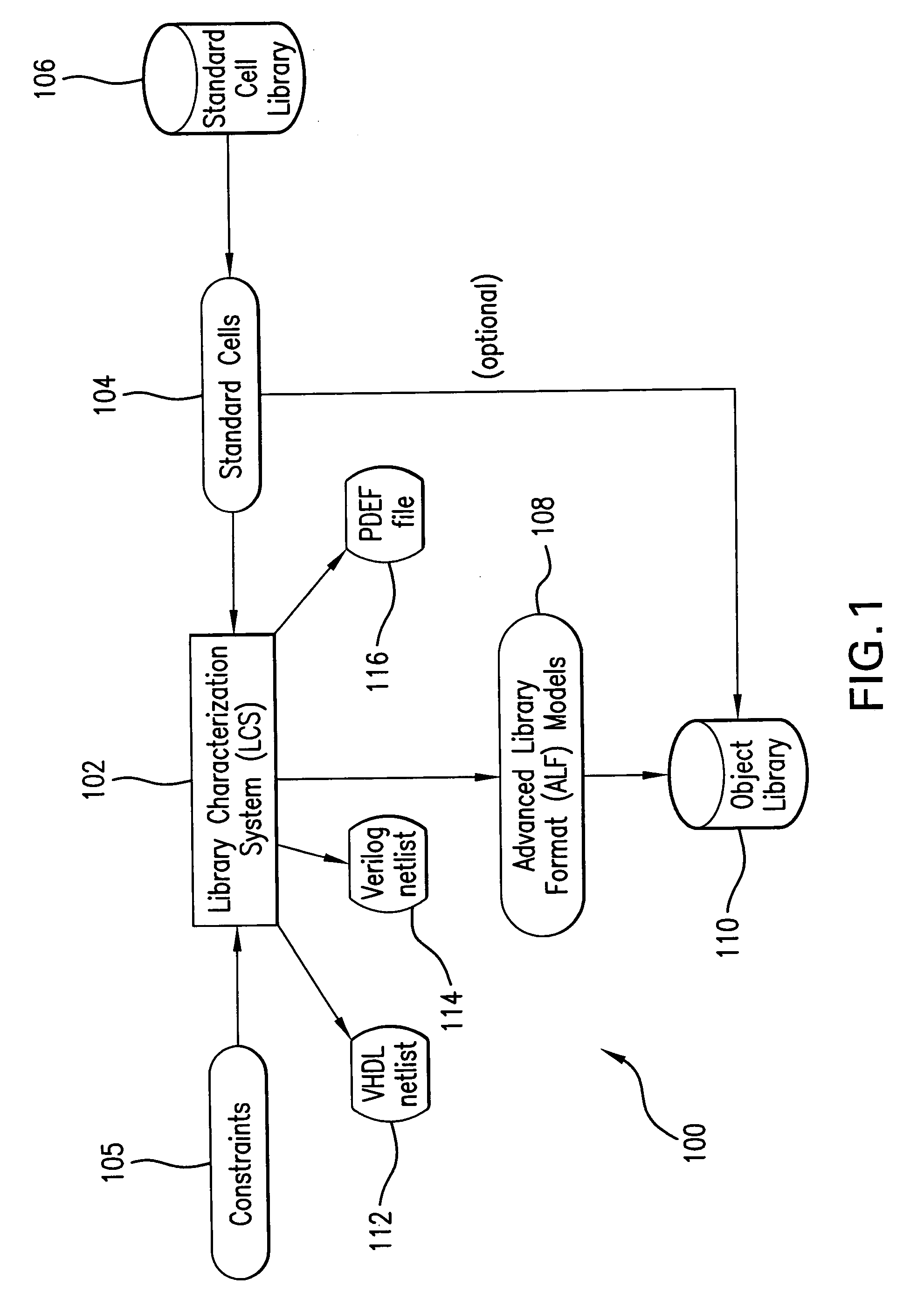

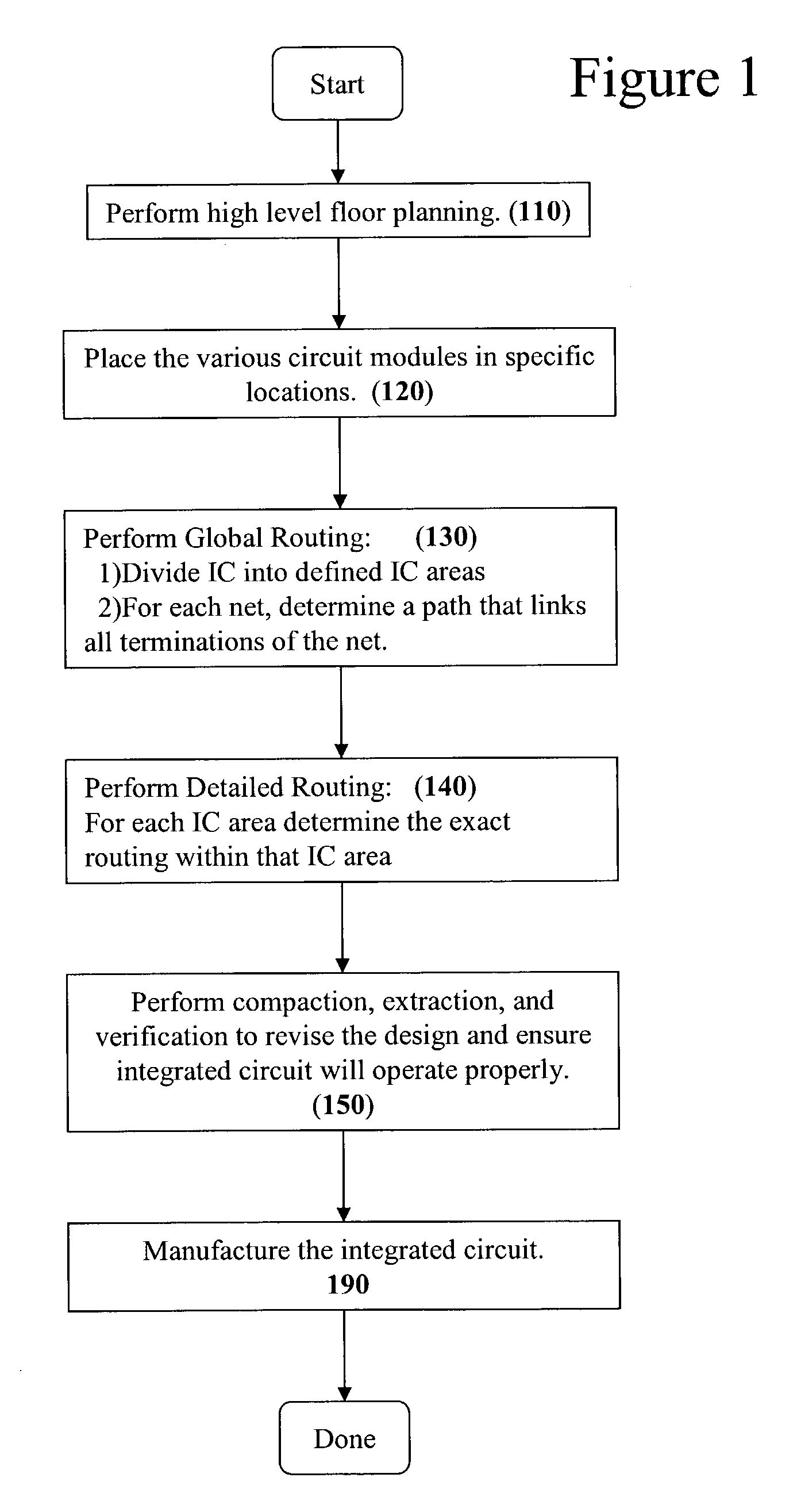

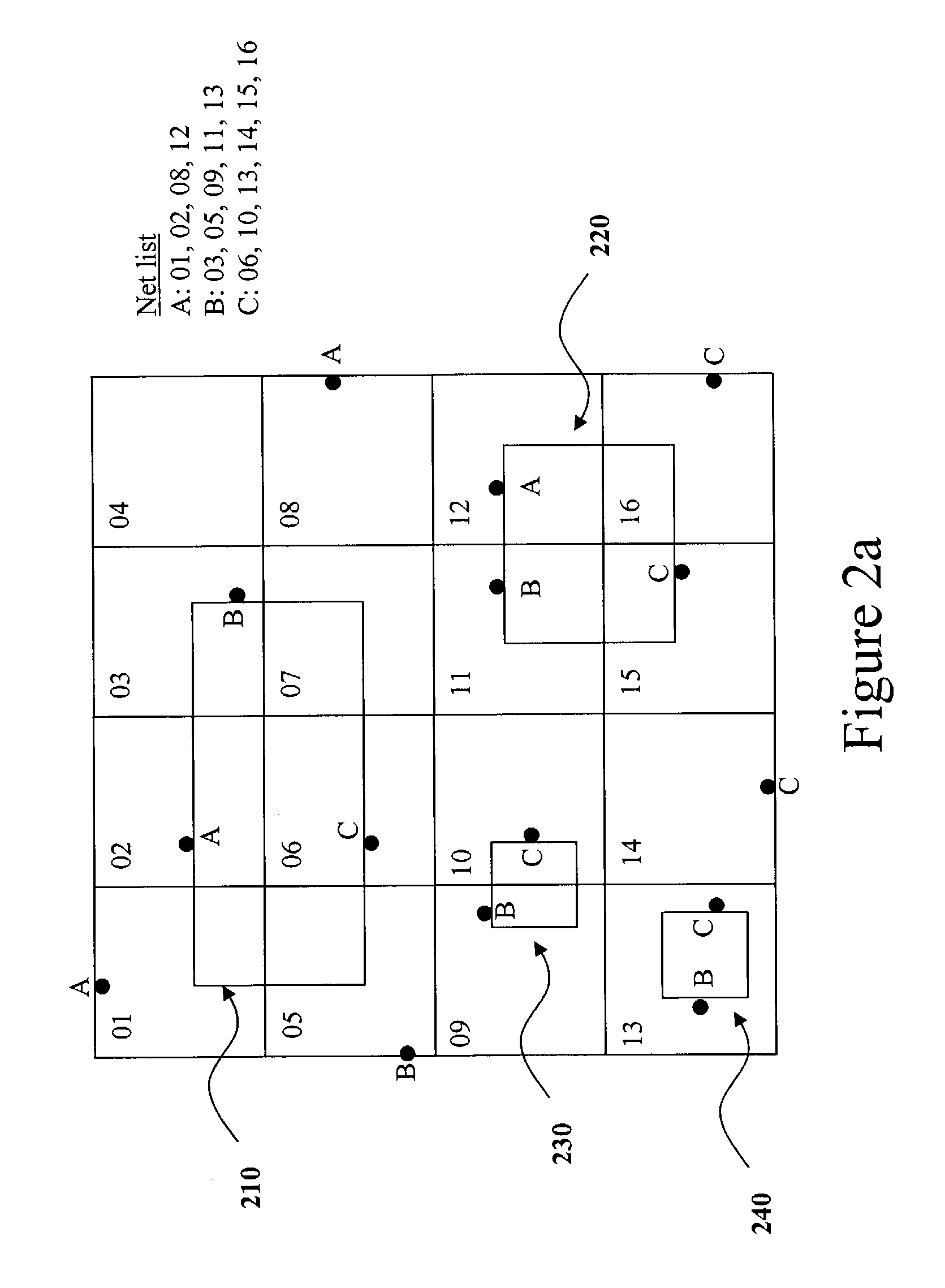

Creating optimized physical implementations from high-level descriptions of electronic design using placement-based information

InactiveUS7143367B2Enhances existing top-down EDA systemsHigh densityDetecting faulty computer hardwareCAD circuit designComputer architectureLoad model

Owner:SYNOPSYS INC

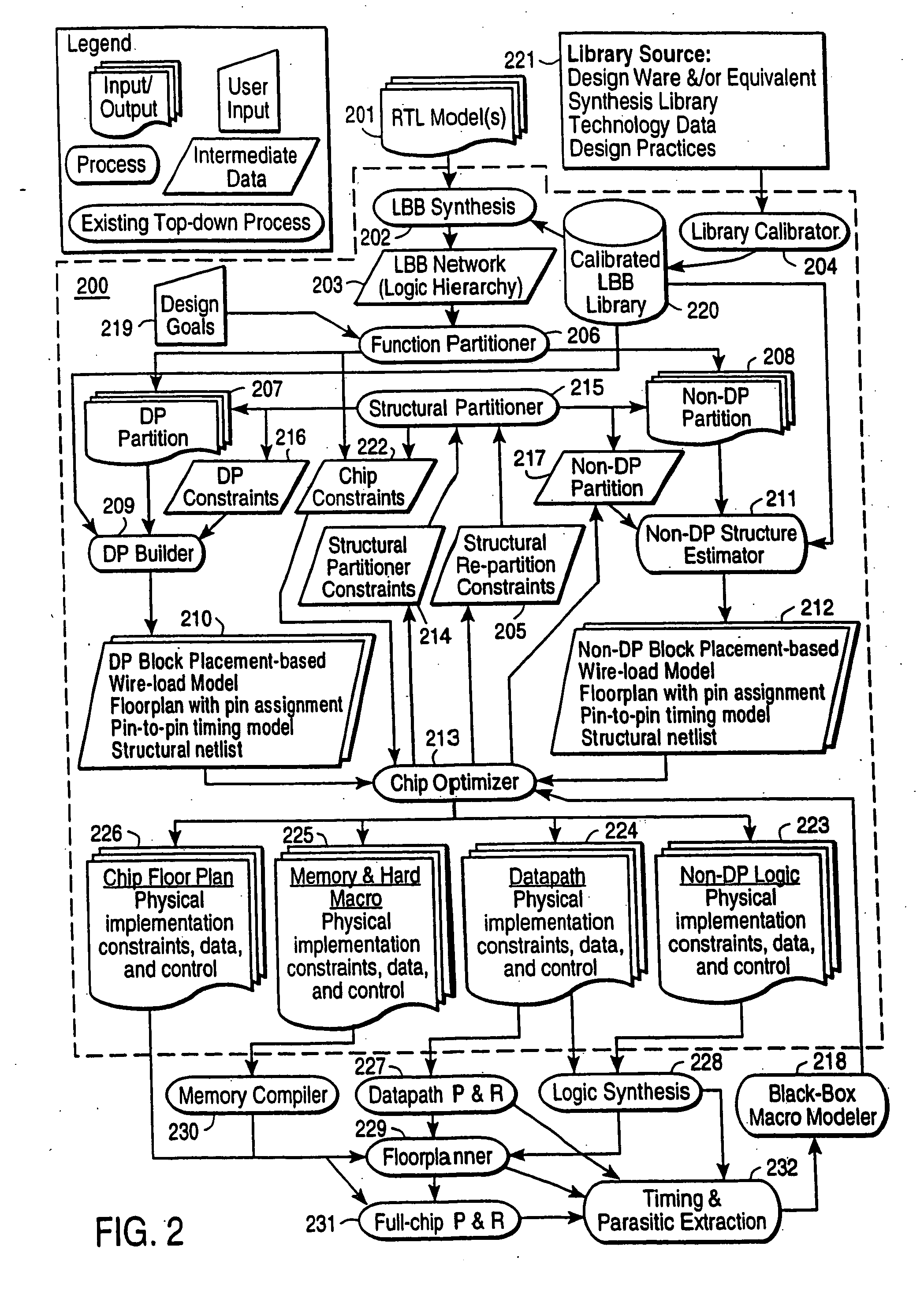

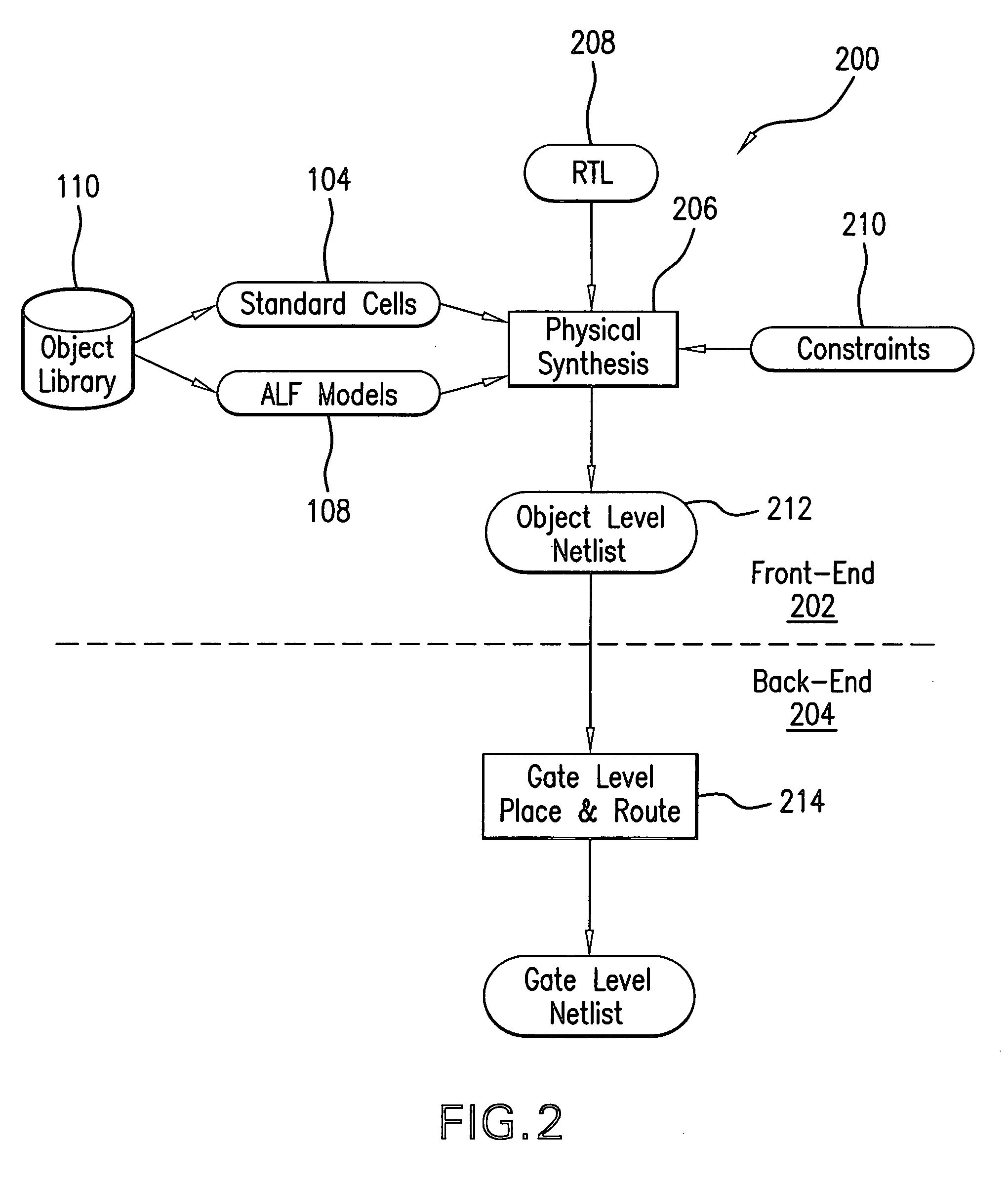

Creating optimized physical implementations from high-level descriptions of electronic design using placement-based information

InactiveUS20060053396A1Improve performanceHigh densityCAD circuit designSoftware simulation/interpretation/emulationComputer architectureData file

An electronic design automation system provides optimization of RTL models of electronic designs, to produce detailed constraints and data precisely defining the requirements for the back-end flows leading to design fabrication. The system takes a RTL model of an electronic design and maps it into an efficient, high level hierarchical representation of the hardware implementation of the design. Automatic partitioning partitions the hardware representation into functional partitions, and creates a fully characterized performance envelope for a range of feasible implementations for each of the partitions, using accurate placement based wire load models. Chip-level optimization selects and refines physical implementations of the partitions to produce compacted, globally routed floorplans. Chip-level optimization iteratively invokes re-partitioning passes to refine the partitions and to recompute the feasible implementations. In this fashion, a multiple-pass process converges on an optimal selection of physical implementations for all partitions for the entire chip that meet minimum timing requirements and other design goals. The system outputs specific control and data files which thoroughly define the implementation details of the design through the entire back-end flow process, thereby guaranteeing that the fabricated design meets all design goals without costly and time consuming design iterations.

Owner:MAGMA DESIGN AUTOMATION

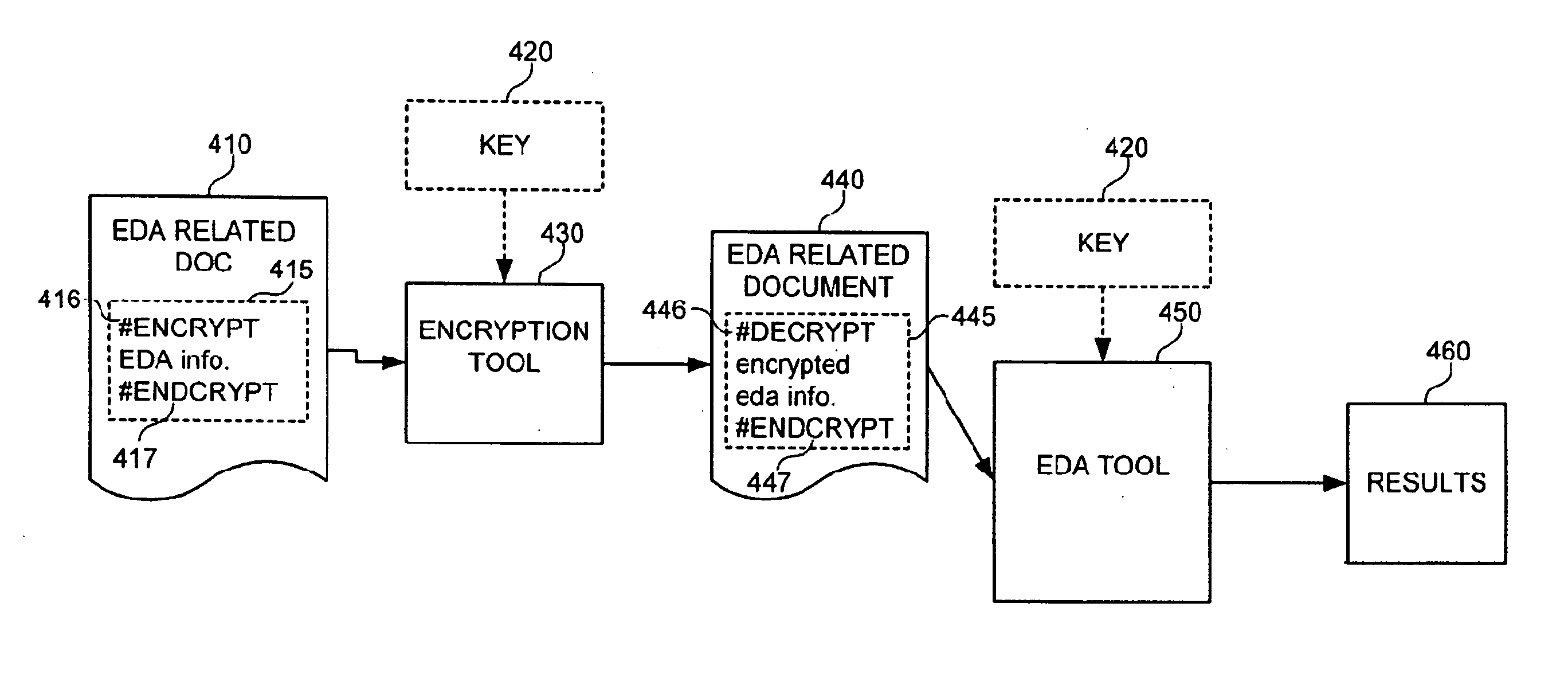

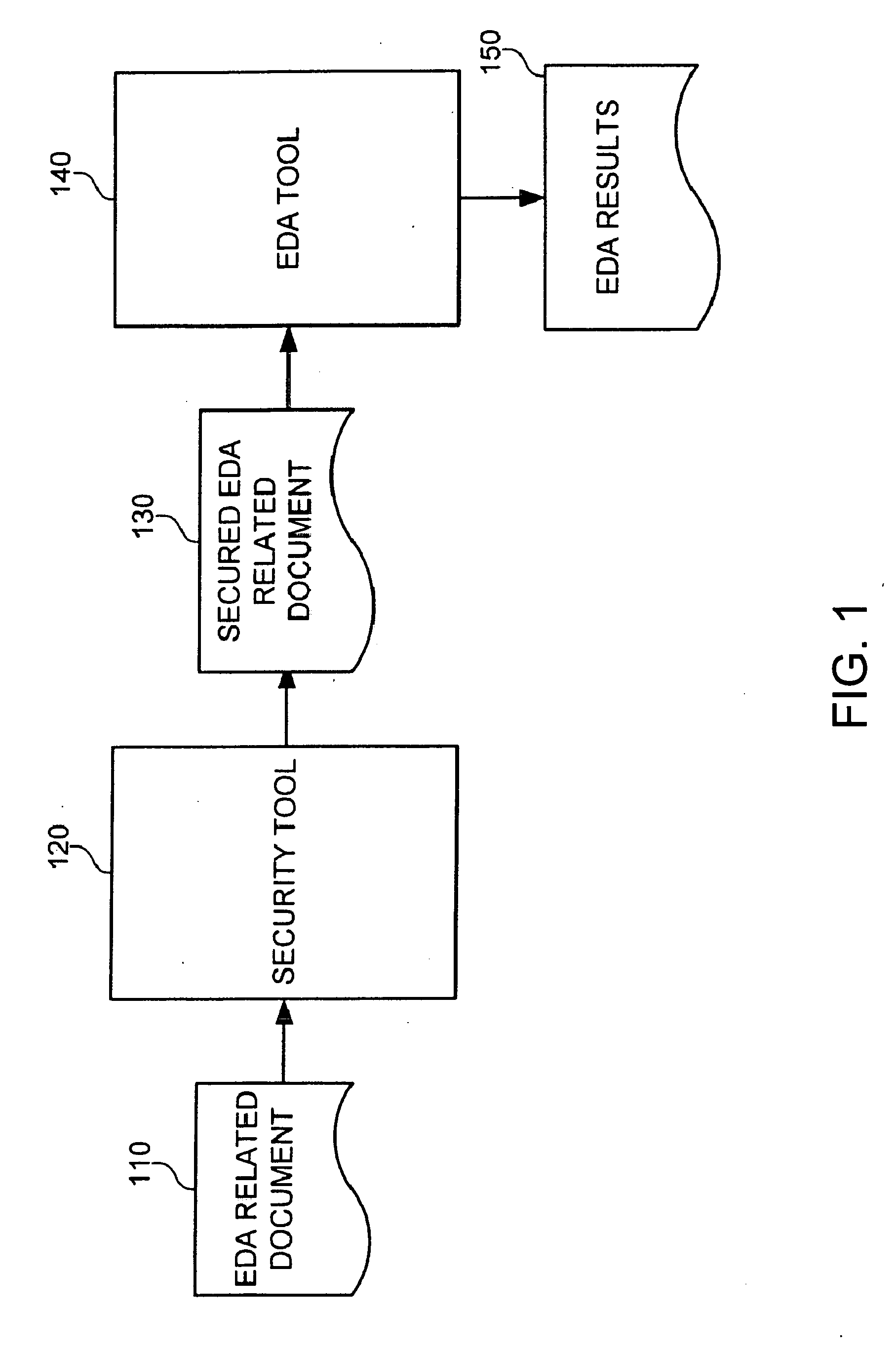

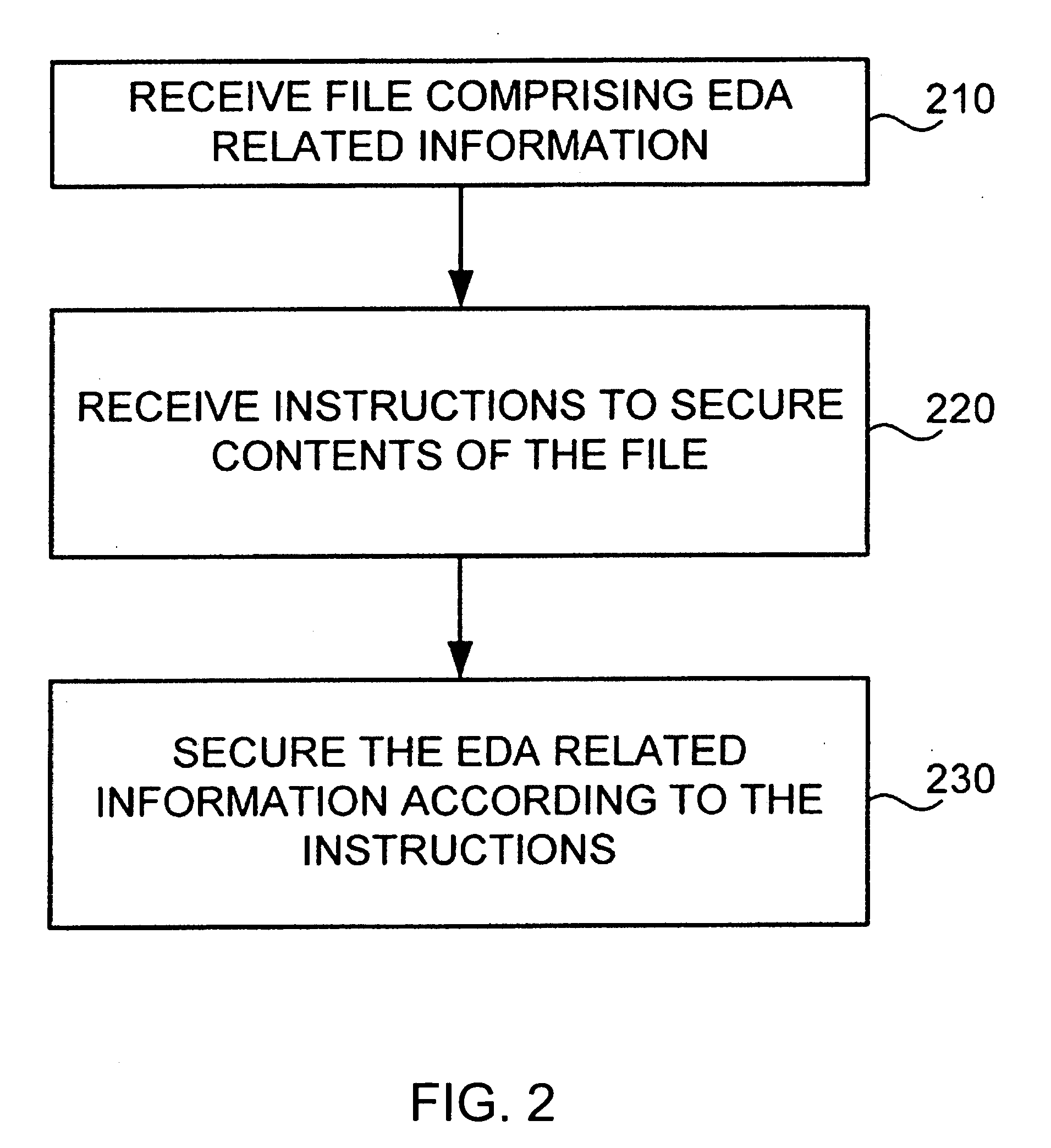

Concealment of information in electronic design automation

InactiveUS20070055892A1Digital data processing detailsUser identity/authority verificationEngineeringInformation hiding

An electronic design automation tool may receive information related to electronic design automation that contains secured information, such as physically secured information, and annotations to indicate the secured portions of the information. Upon receiving such information, the electronic design automation tool may identify those portions of the information comprising secured information related to electronic design automation, and unlock the secured information for processing. The electronic design automation tool may process at least some of the secured electronic design automation information without revealing that secured information to unauthorized persons, tools, systems, or otherwise compromising the protection of that secured information. That is, the design automation tool may process the secured electronic design automation information so that the secured information is concealed both while it is being processed and by the output information generated from processing the secured information.

Owner:MENTOR GRAPHICS CORP

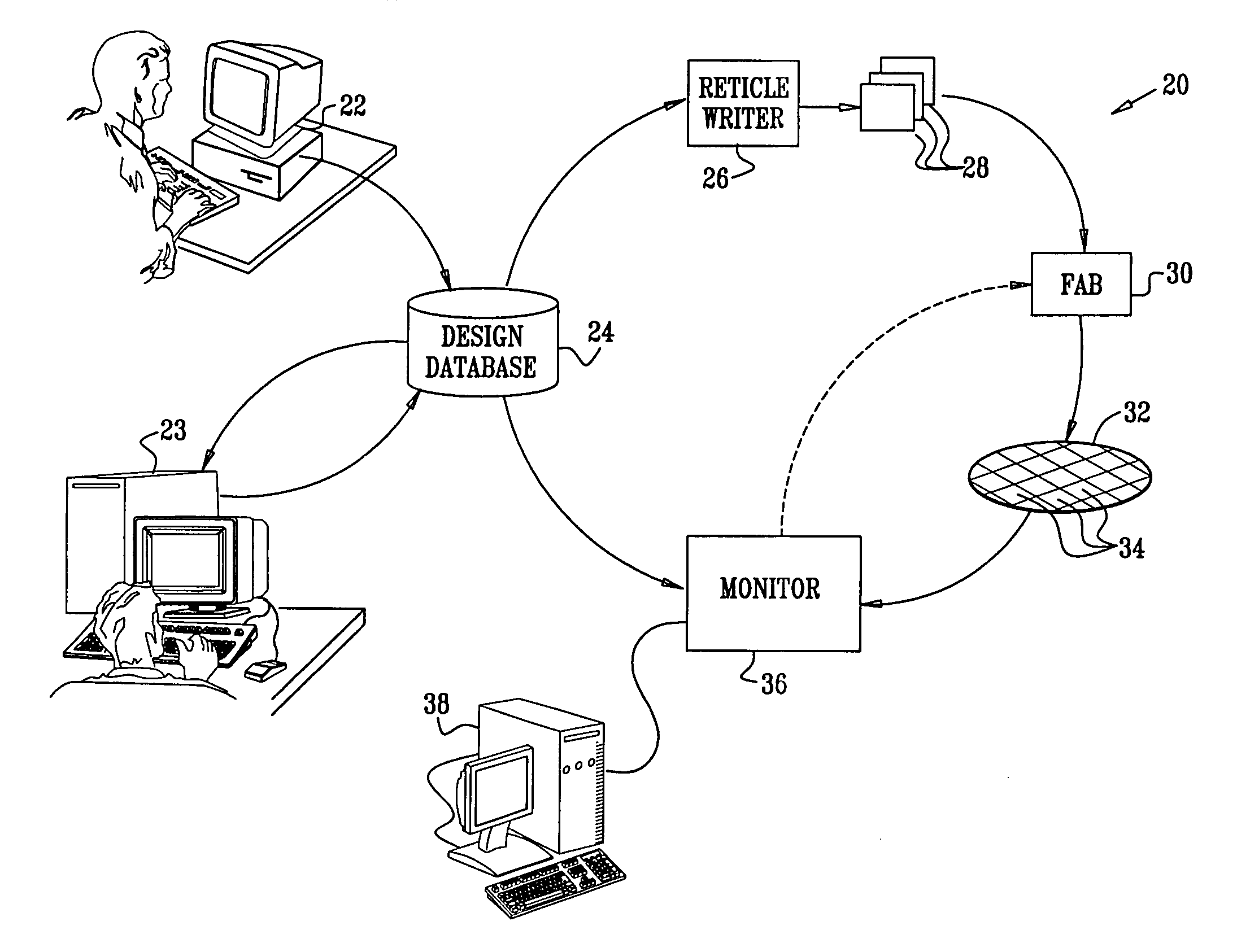

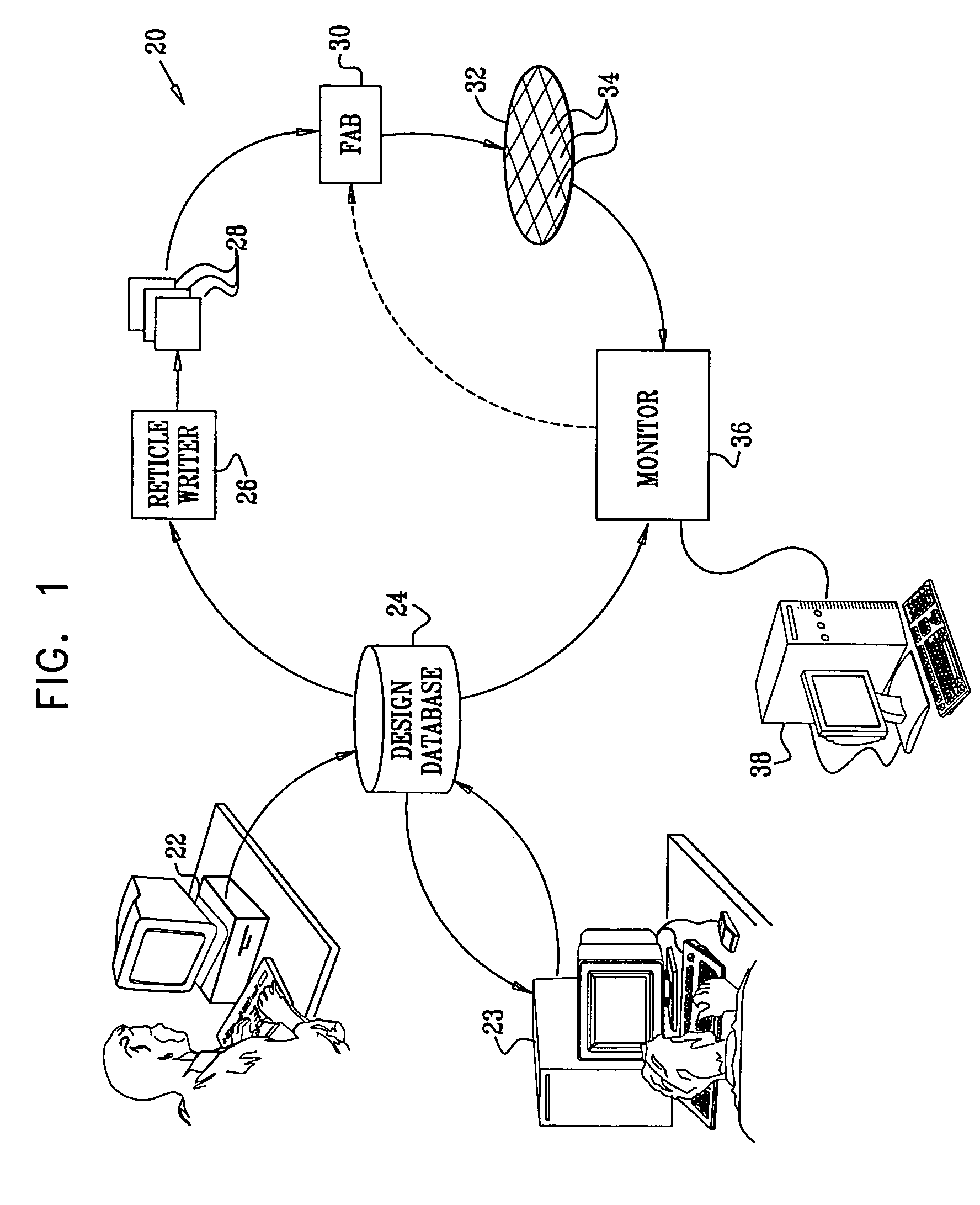

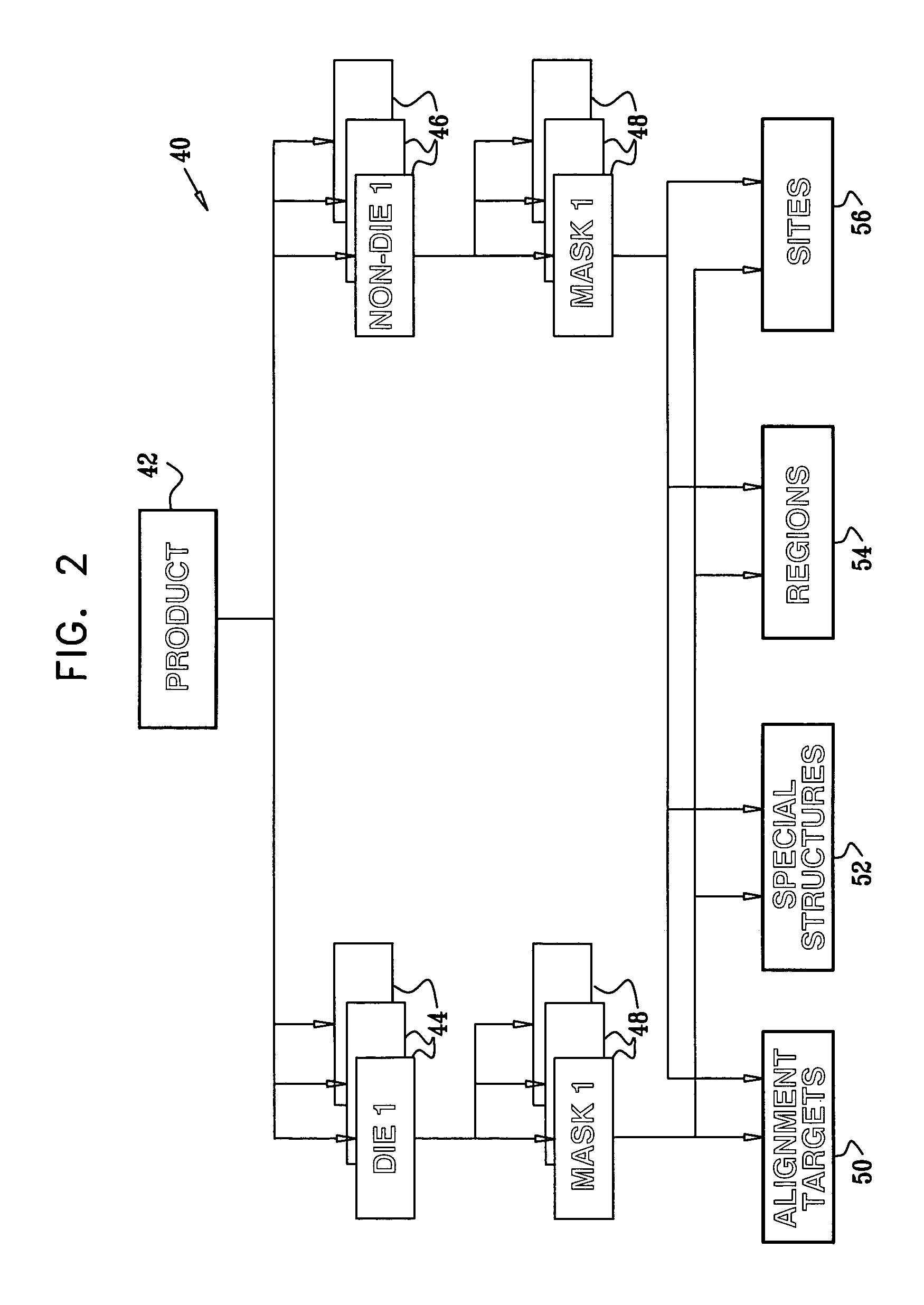

Design-based monitoring

ActiveUS7135344B2Maximize sensitivityMinimize impactSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A method for monitoring fabrication of an integrated circuit (IC) on a semiconductor wafer includes generating a product design profile (PDP) using an electronic design automation (EDA) tool, the PDP comprising an indication of a site in at least one layer of the IC that is susceptible to a process fault. Upon fabricating at least one layer of the IC on the wafer, a process monitoring tool is applied to perform a measurement at the site in at least one layer responsively to the PDP.

Owner:APPL MATERIALS ISRAEL LTD

Method for delay-optimizing technology mapping of digital logic

InactiveUS6470486B1CAD circuit designSoftware simulation/interpretation/emulationTheoretical computer scienceArrival time

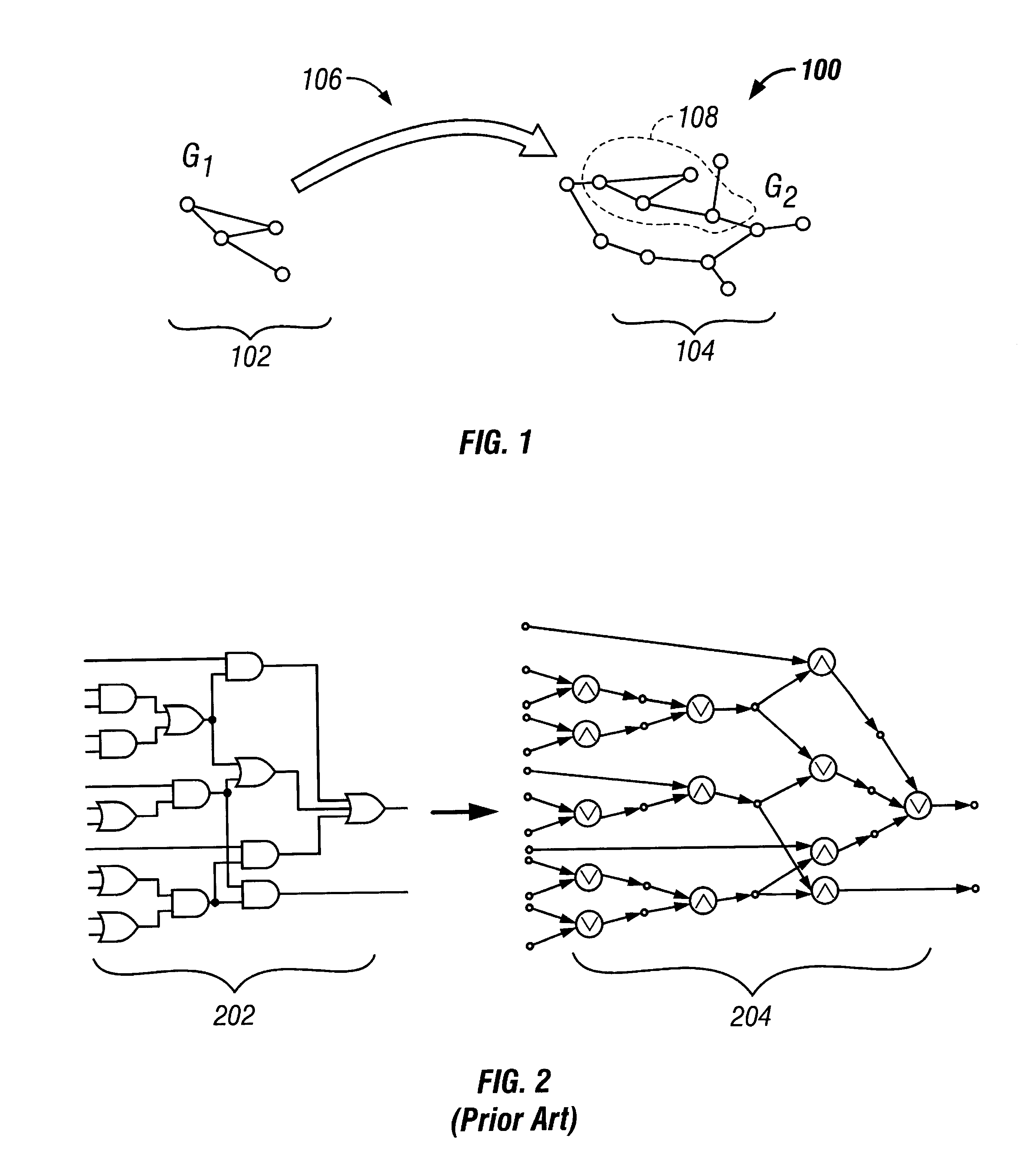

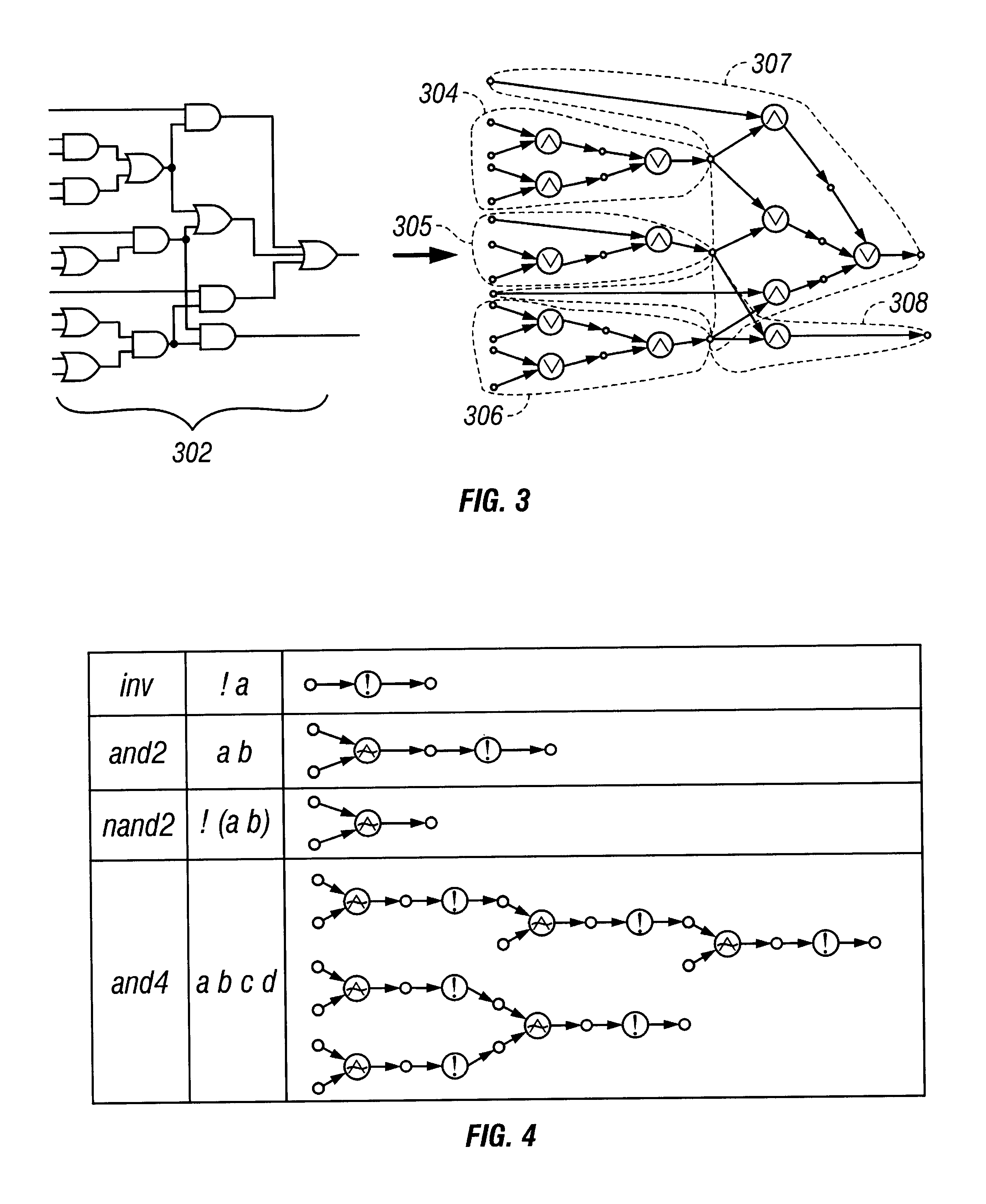

A delay-optimizing technology-mapping process for an electronic design automation system selects the best combination of library devices to use in a forward and a backward sweep of circuit trees representing a design. A technology selection process in an electronic design automation-system comprises the steps of partitioning an original circuit design into a set of corresponding logic trees. Then, ordering the set of corresponding logic trees into an ordered linear list such that each tree-T that drives another ordered tree precedes the other ordered tree, and such that each ordered tree that drives the tree-T precedes the tree-T. Next, sweeping forward in the ordered linear list while computing a set of Pareto-optimal load / arrival curves for each of a plurality of net nodes that match a technology-library element. And, sweeping backward in the ordered linear list while using the set of Pareto-optimal load / arrival curves for each of the net nodes and a capacitive load to select a best one of the technology-library elements with a shortest signal arrival time. Wherein, only those net nodes that correspond to gate inputs are considered, and any capacitive loads are predetermined.

Owner:CADENCE DESIGN SYST INC

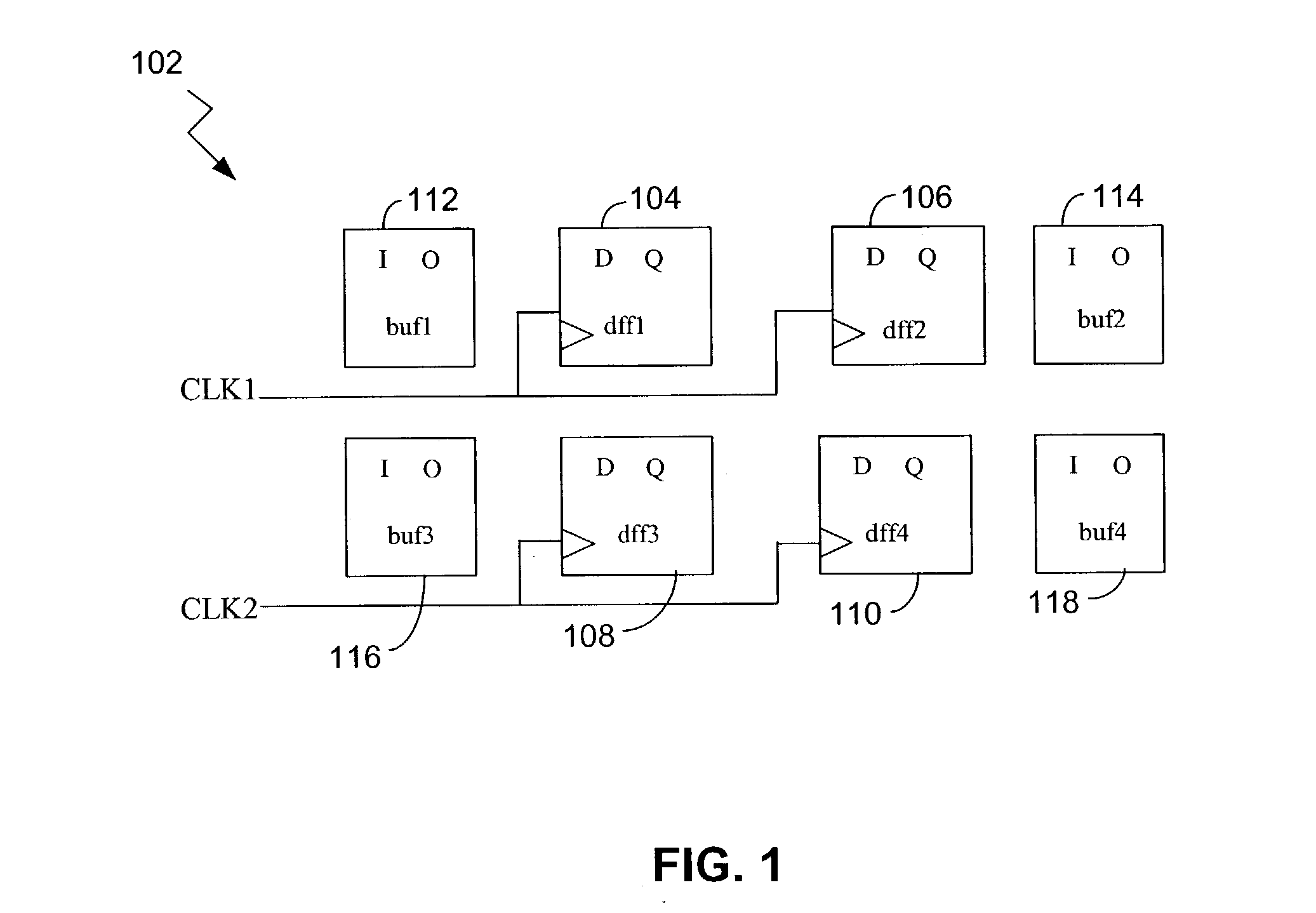

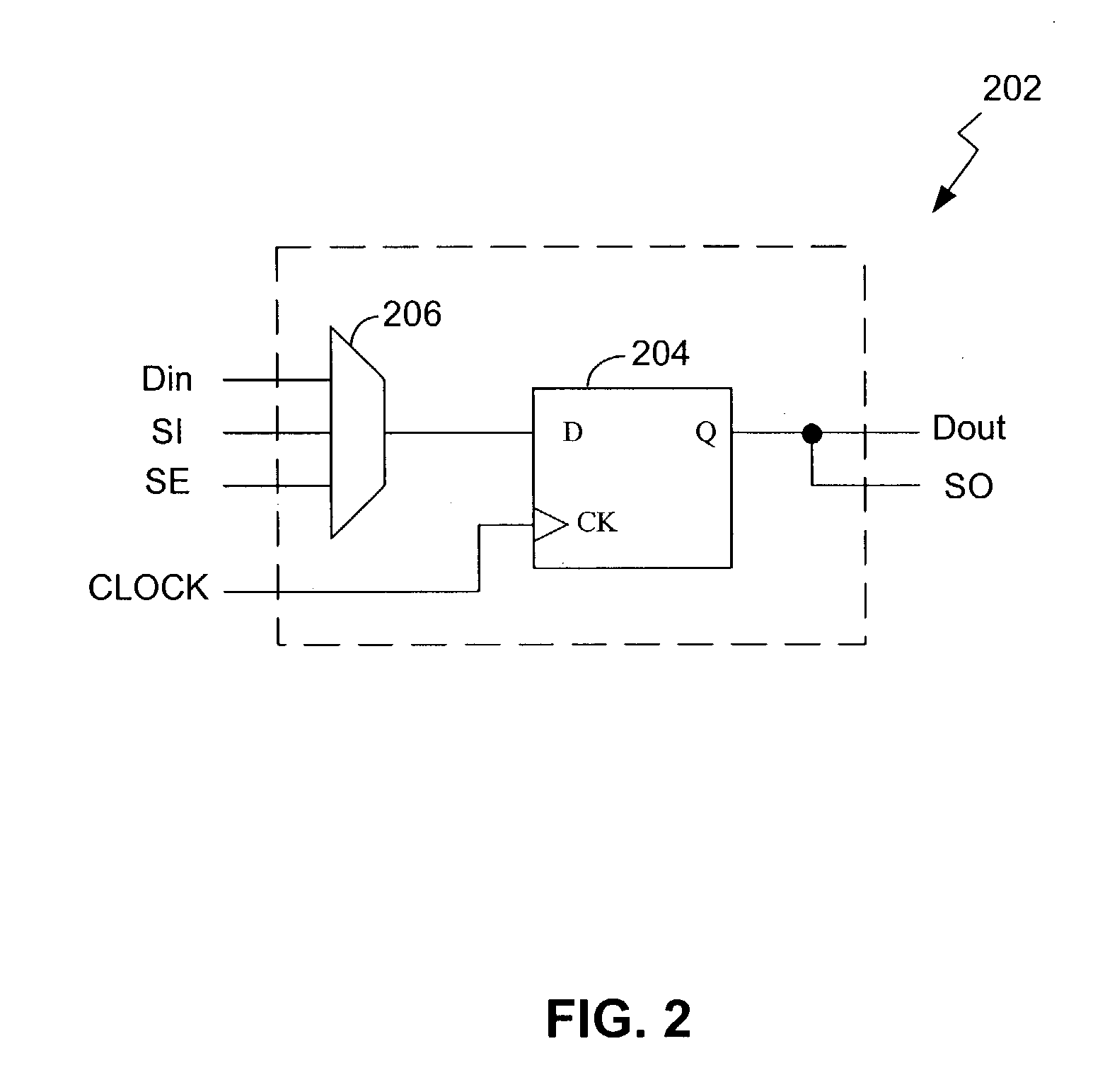

Timing based scan chain implementation in an IC design

InactiveUS7127695B2Reduce time impactEasy to placeElectrical testingCAD circuit designComputer architectureNetlist

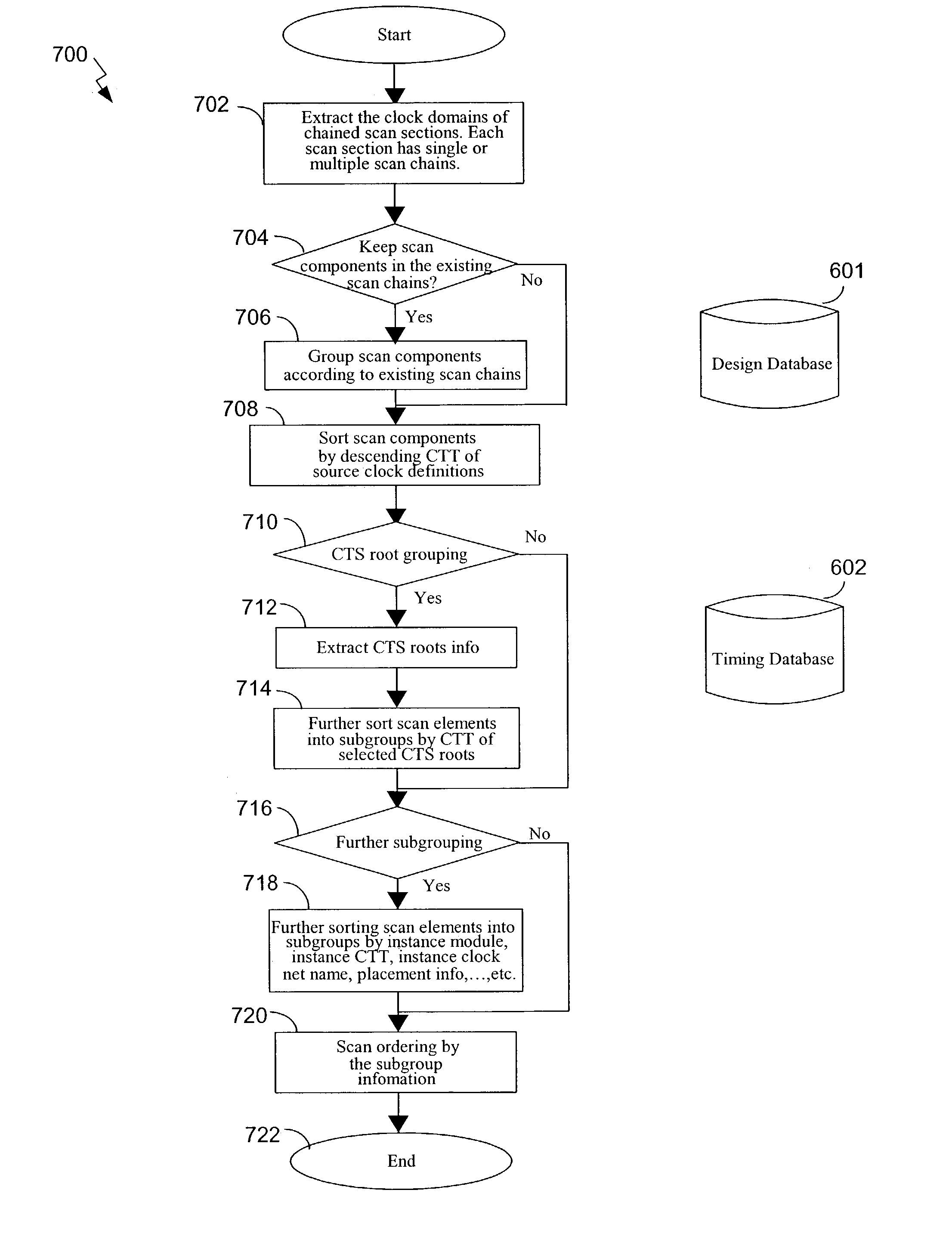

For use with a design database and a timing database, a computer implemented process for electronic design automation comprising: receiving a netlist that includes cells interconnected by circuit paths, wherein a plurality of the cells are scan cells connected in at least one scan chain; ordering the scan cells according to a prescribed scan cell ordering rule so as to produce a plurality of ordering relationships among scan cells; assigning respective weights from a first category of one or more weights to respective prescribed scan cell order relationships among scan cells of the netlist; assigning respective weights from a second category of one or more weights to prescribed circuit path relationships among cells of the netlist; and determining a physical placement of the cells of the netlist, including the scan cells, using a cost function that places the cells according to the assigned weights.

Owner:INCENTIA DESIGN SYST

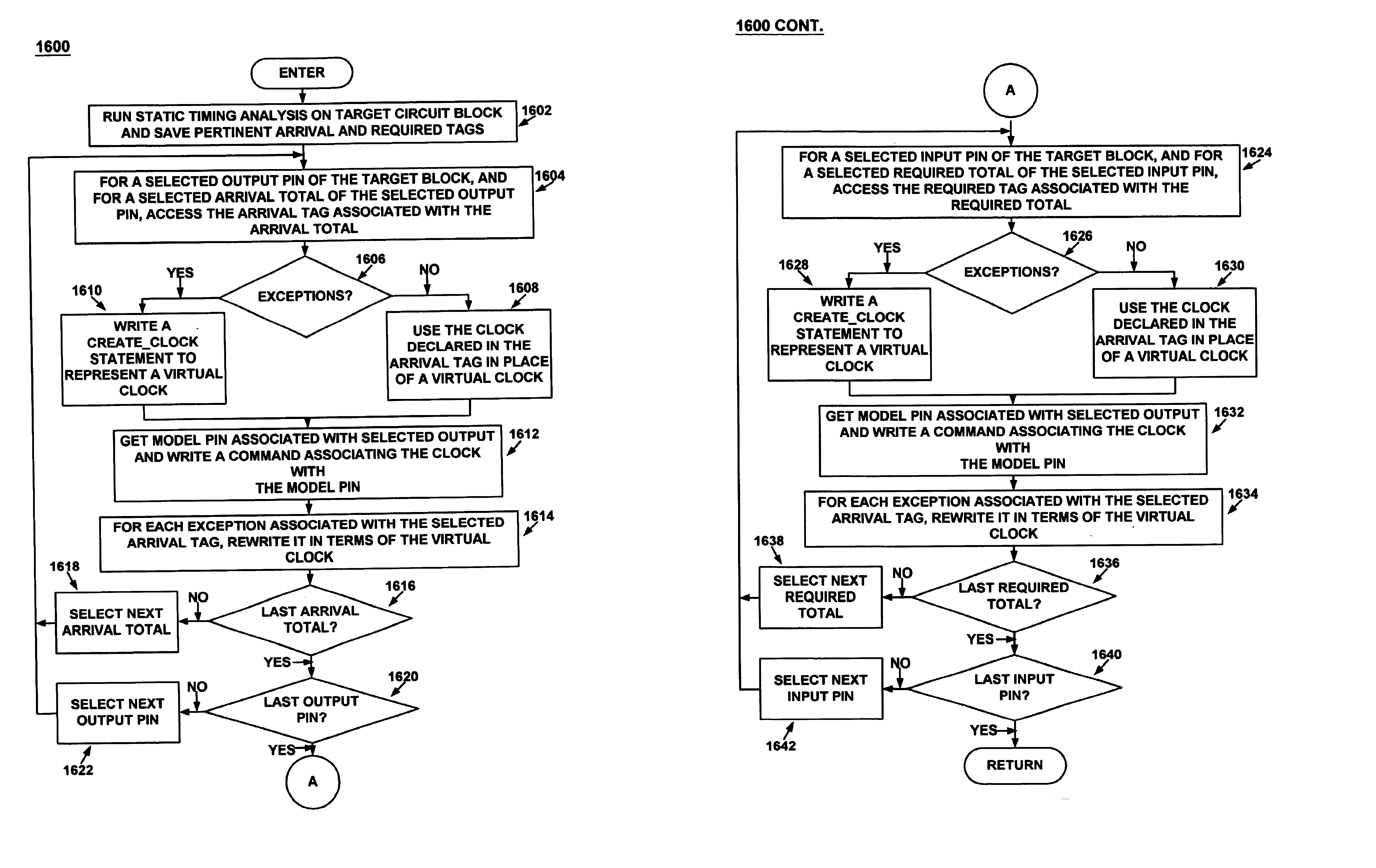

Integrated circuit models having associated timing exception information therewith for use with electronic design automation

InactiveUS6678644B1Computer aided designSoftware simulation/interpretation/emulationCircuit modelsComputer memory

Integrated circuit models having associated timing and tag information therewith for use with electronic design automation to effectively model timing exception information. The present invention includes a circuit block model which allows automated circuit optimization to be performed on extremely large circuits without the need to load all of the details of the circuit into computer memory. The circuit models of the present invention effectively model timing including timing exception information. The model of the present invention is associated with command information, e.g., textual commands, that describe tags (which model exceptions) and arrival and required times associated with the tags. Specifically, for the input pins of a circuit to be modeled, the present invention writes out a command defining each unique required tag associated with an input pin and also writes out commands associating each required tag with its input pin. For the output pins of a circuit to be modeled, the present invention writes out a command defining each unique arrival tag associated with an output pin and also writes out commands associating each arrival tag with its output pin. The tag, arrival and required information is then associated with the model. Timing exceptions are thereby effectively and efficiently modeled using this process. The present invention also includes various circuit optimization processes that utilize the above described circuit model with command information. These circuit optimizations can be used for incremental optimization of a large circuit.

Owner:SYNOPSYS INC

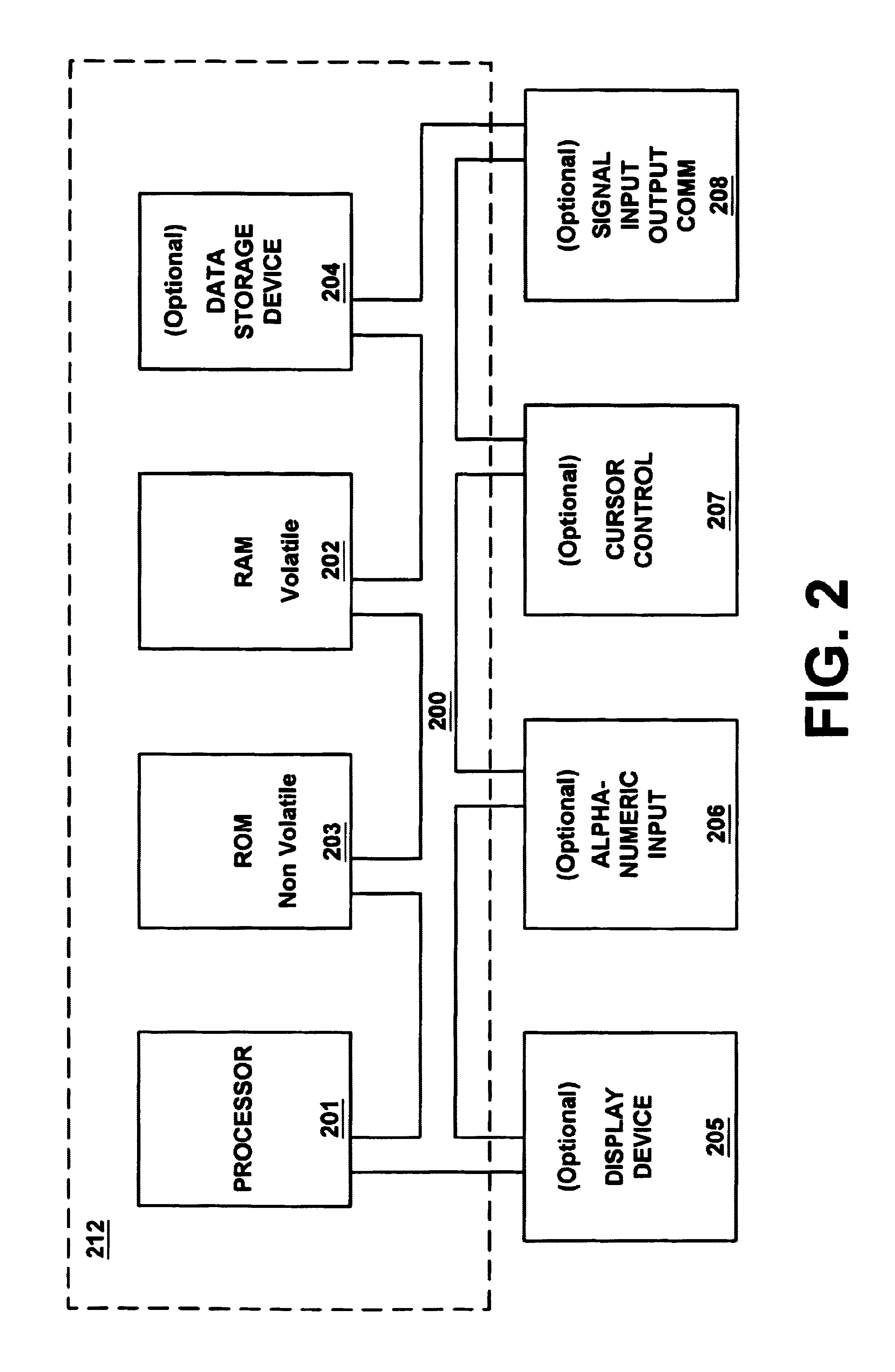

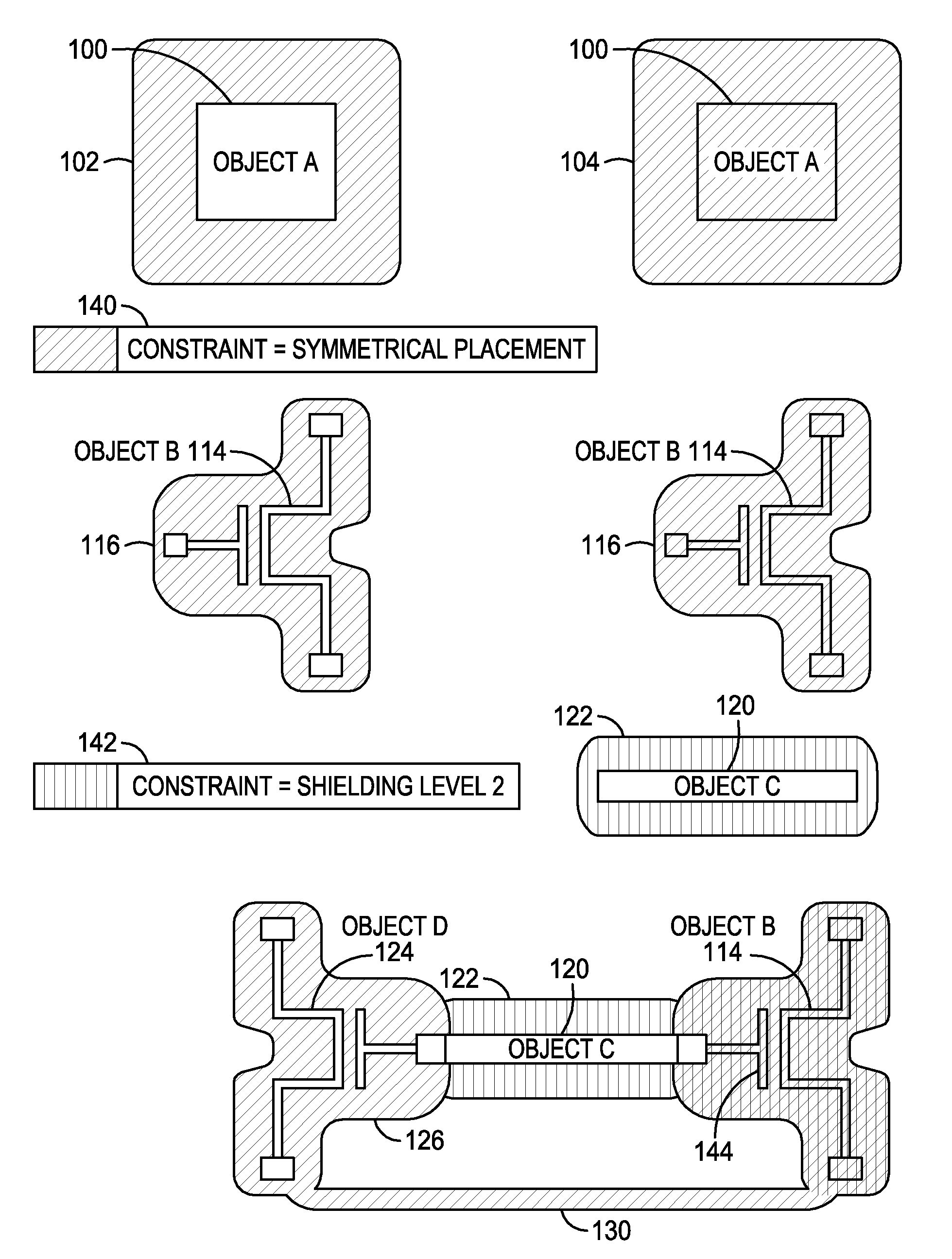

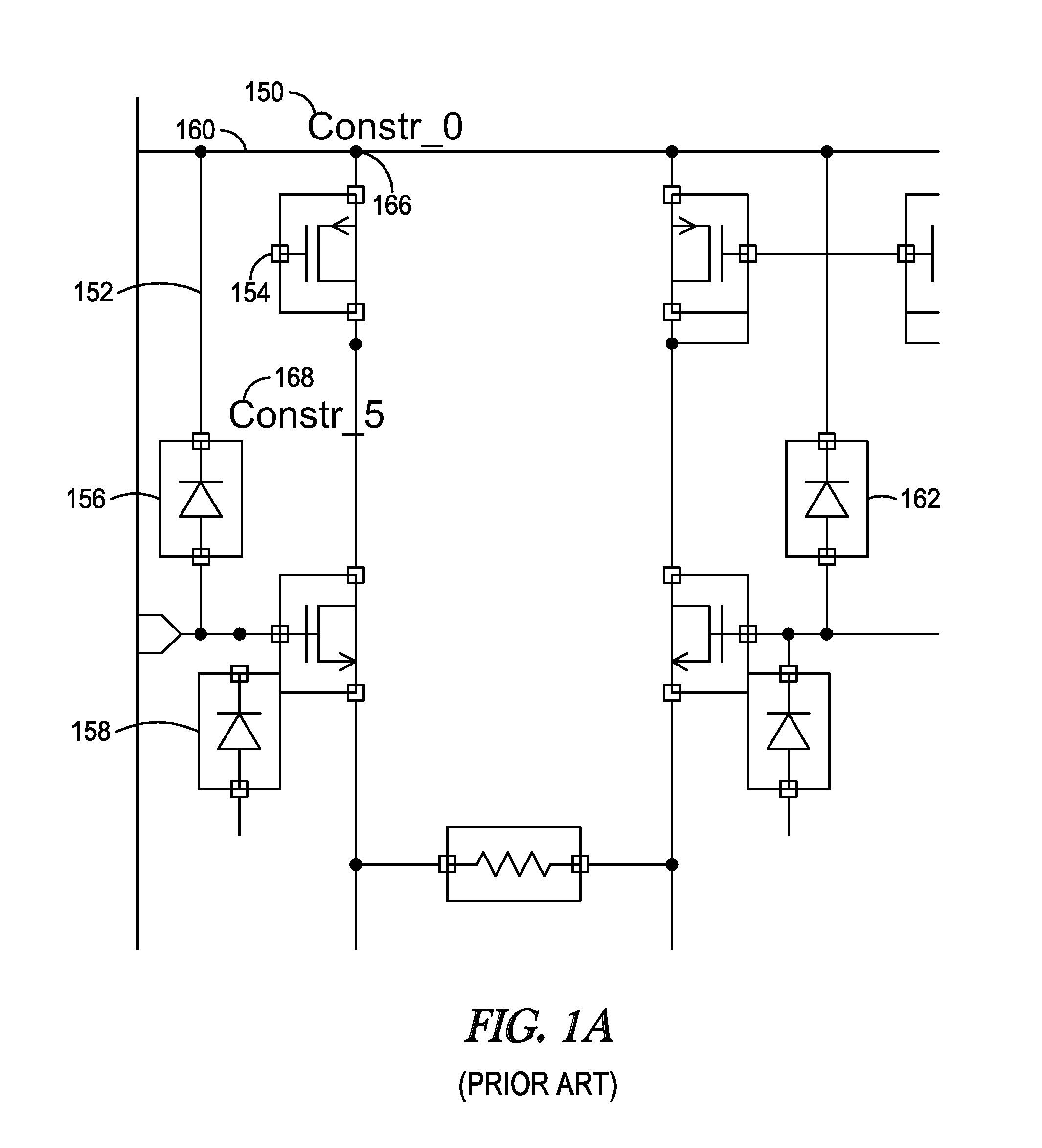

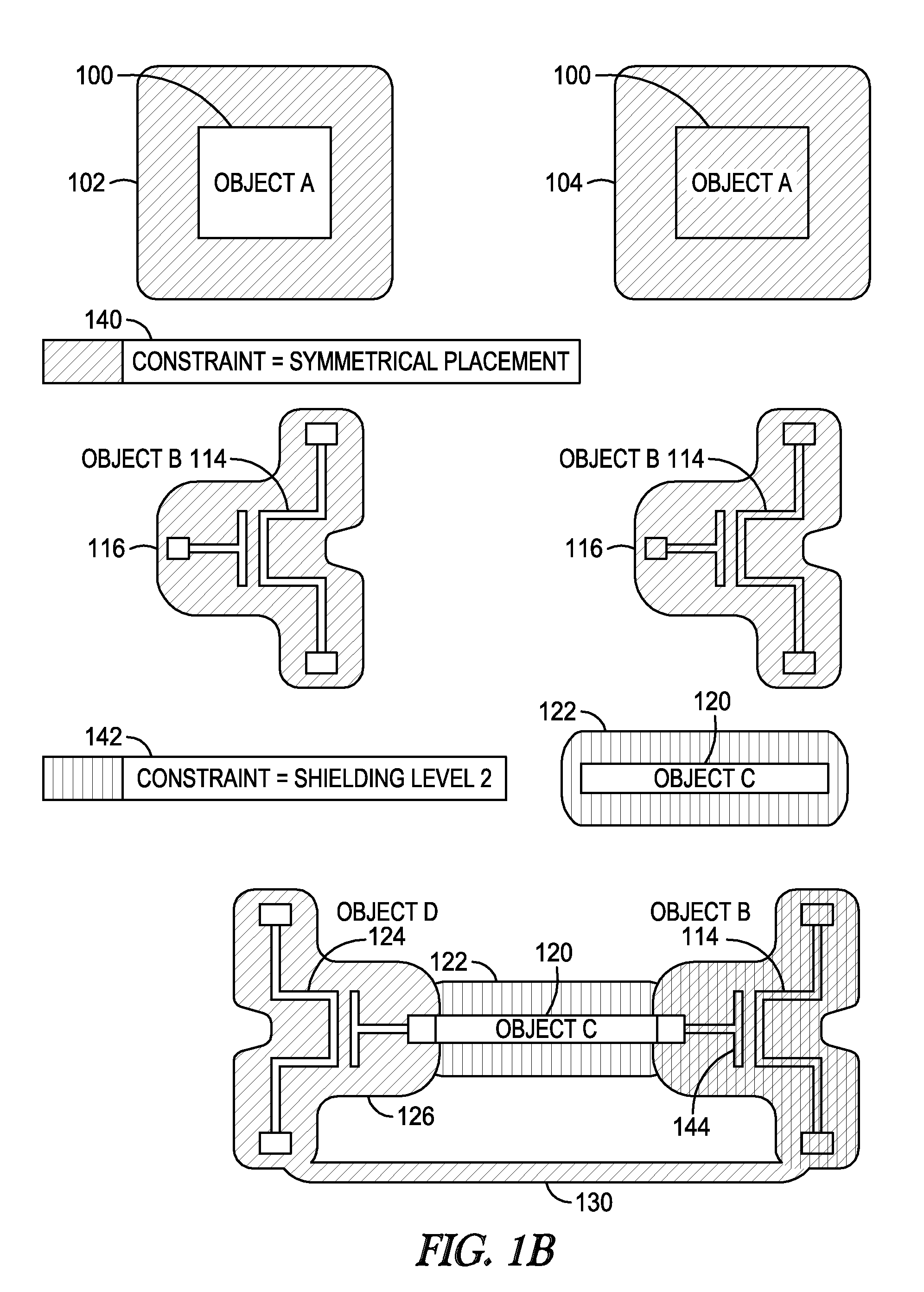

System and method for improved visualization and debugging of constraint circuit objects

Features are provided for graphically representing constraints on design objects in an Electronic Design Automation tool. A particular constraint on one or more circuit objects is displayed as a highlighted region that extends to each visible circuit object to which the constraint applies. Attributes of the highlighted region, such as density and thickness, may proportionally represent attributes of the constraint, such as a strength or distance specified by the constraint. The highlighted region is superimposed on or around circuit objects. The highlighted region may be a halo, which is a partially transparent region filled with a color. Multiple regions that represent the same type of constraint or relationship are connected by line segments, providing the ability to visualize groups of constrained objects, including groups that span levels of a hierarchical design. Intersecting highlighted regions are blended together using techniques such as alpha blending.

Owner:CADENCE DESIGN SYST INC

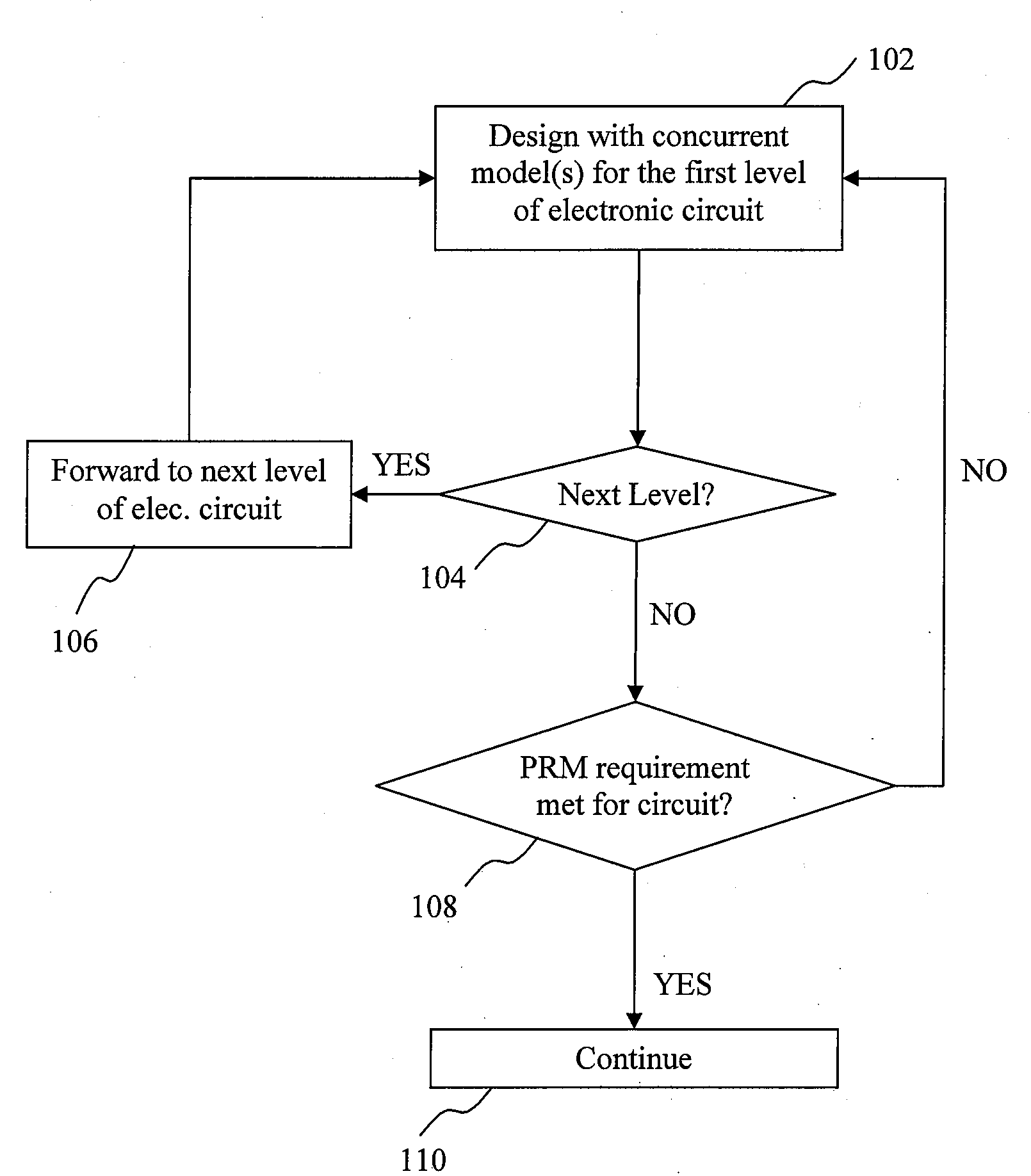

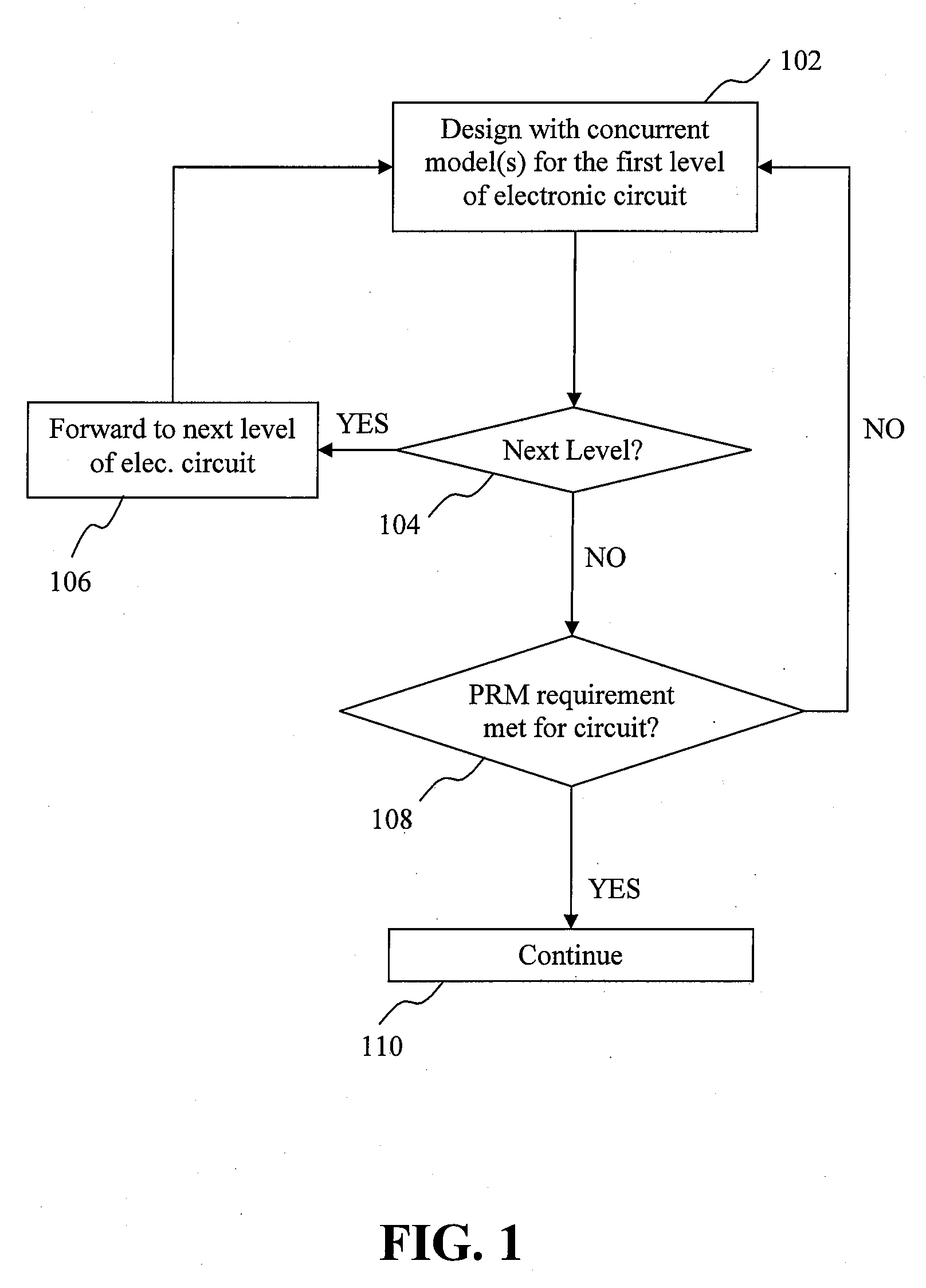

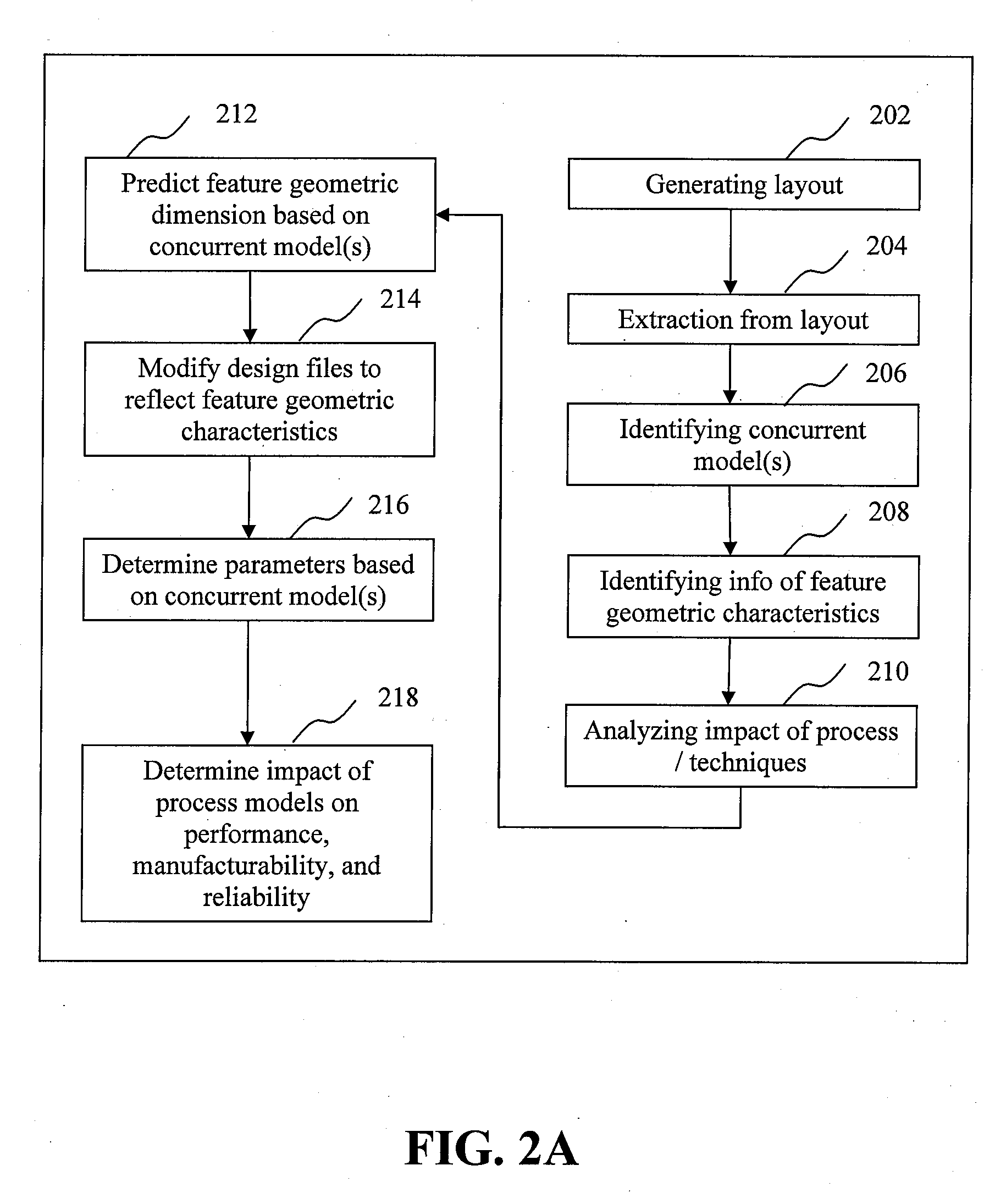

Method, system, and computer program product for concurrent model aided electronic design automation

InactiveUS20080162103A1Effective and accurate methodologyAccurate predictionAnalogue computers for electric apparatusPhotomechanical apparatusComputer architectureGenerative Design

Disclosed are improved methods, systems, and computer program products for predicting performance, manufacturability, and reliability (PMR) using concurrent model analyses for electronic designs. Various embodiments of the present invention disclose a method for predicting PMR with concurrent process model analysis in which a method with concurrent model(s) generate a design for the one or more layers in the electronic circuit. The method then analyzes the impact of the processes or techniques for feature geometric characteristic predictions or PMR evaluations, based upon the concurrent models. Results may be reported to the users, or the method may modify the designs to accommodate the variations and determines one or more parameters based upon the concurrent models. One embodiment determines the impact of concurrent model on one or more of performance, manufacturability, and reliability criteria.

Owner:CADENCE DESIGN SYST INC

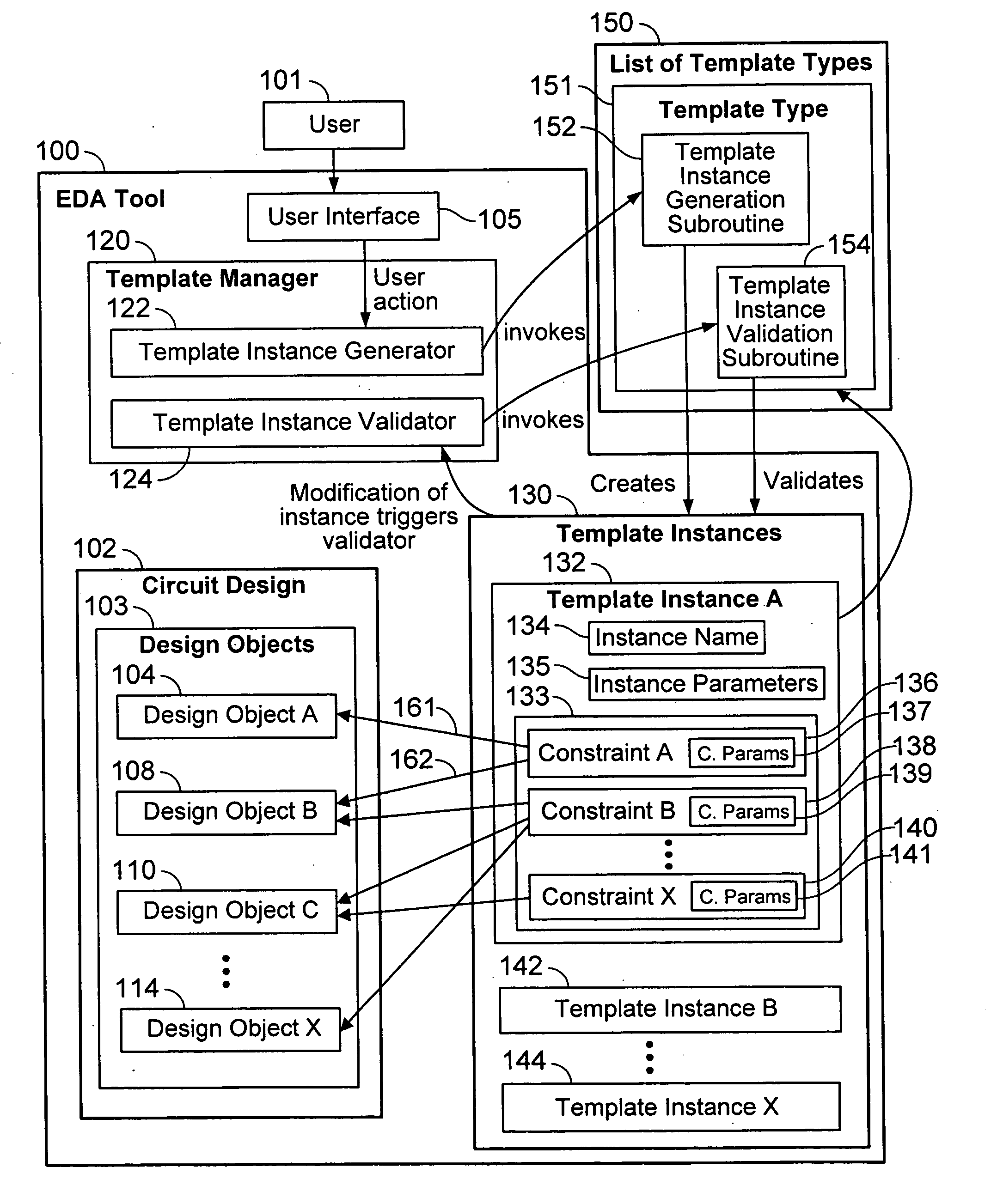

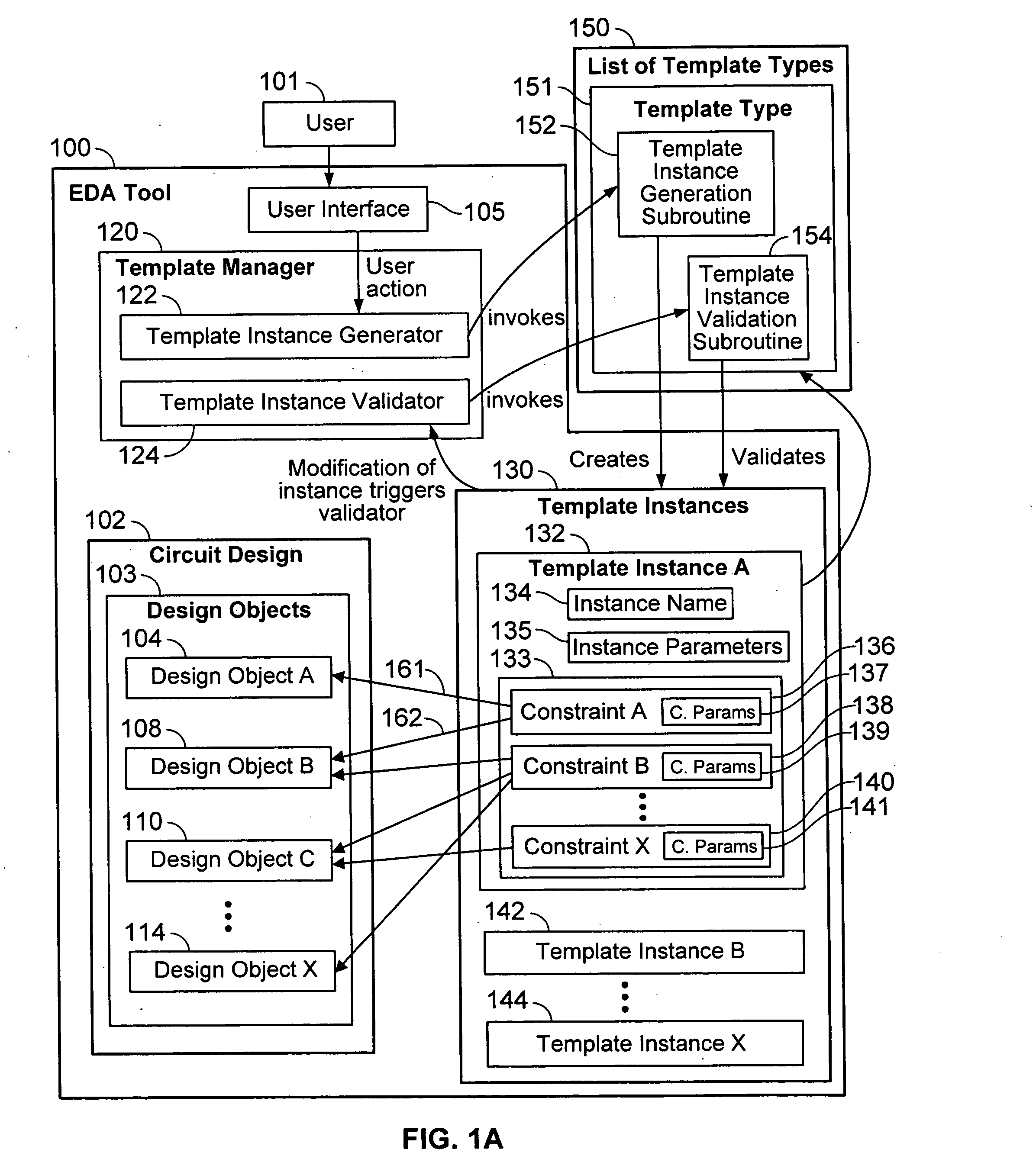

Generalized constraint collection management method

ActiveUS20080077901A1Computer programmed simultaneously with data introductionCAD circuit designCollection managementElectronic design automation

Techniques are provided to allow users of Electronic Design Automation (EDA) tools to define constraint template types for efficiently associating constraints with design objects to specify design intent. Processes for creating and validating the constraints are provided by user-defined plug-ins, thereby allowing users to annotate circuit designs with constraints for proprietary layout and fabrication processes without exposing the constraints to tool vendors or competitors. The constraints are re-created from the template types whenever the circuit design is loaded into the EDA tool, so that the constraints are based upon the latest version of the template type. The constraints are also re-created when validation fails. Constraint groups are reusable in different designs, technology nodes, and processes because they automatically expand to provide the specific constraints to achieve a goal. The specific constraints in a template type can be modified as technology changes, and the modification will automatically be applied to the design objects.

Owner:CADENCE DESIGN SYST INC

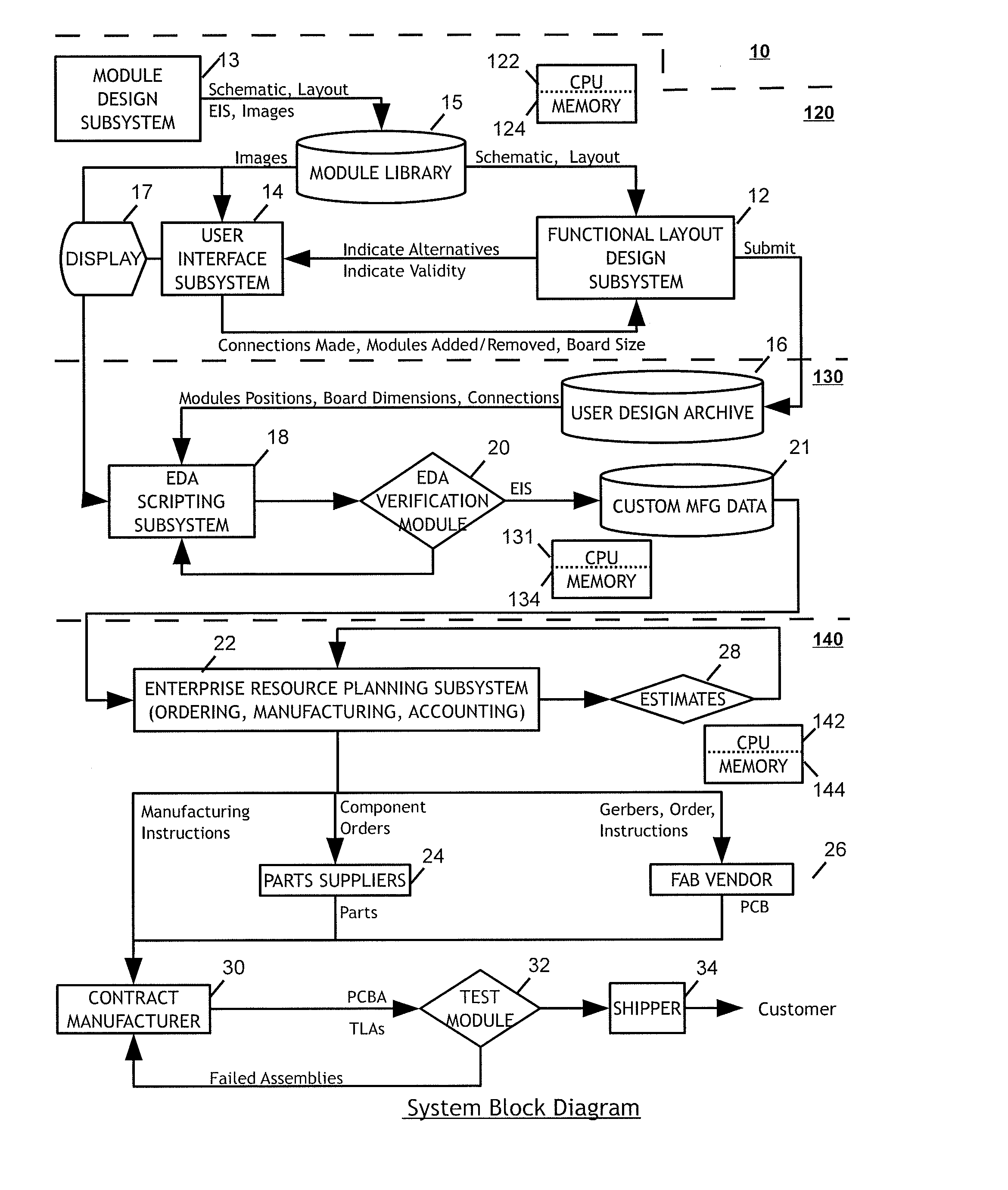

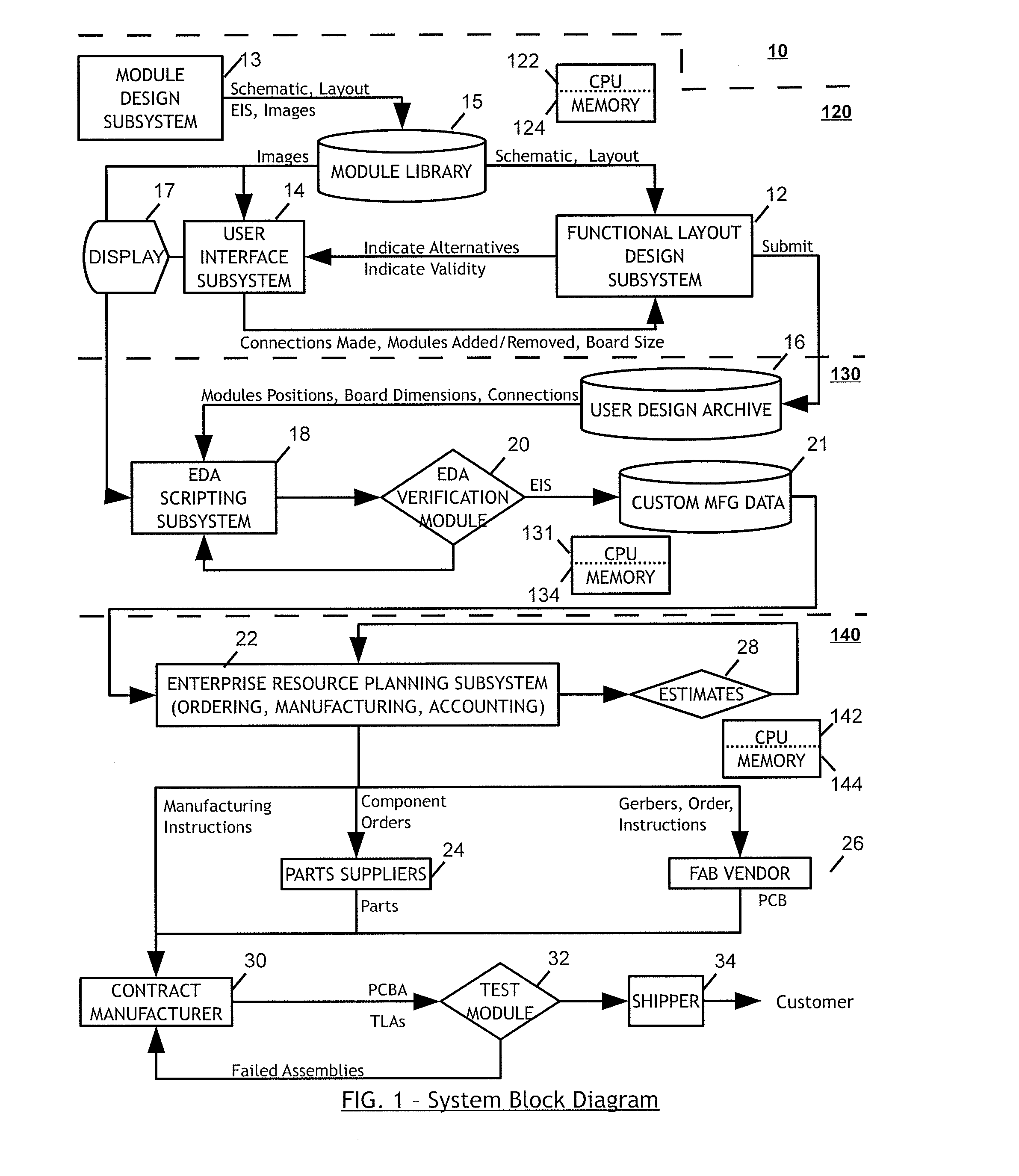

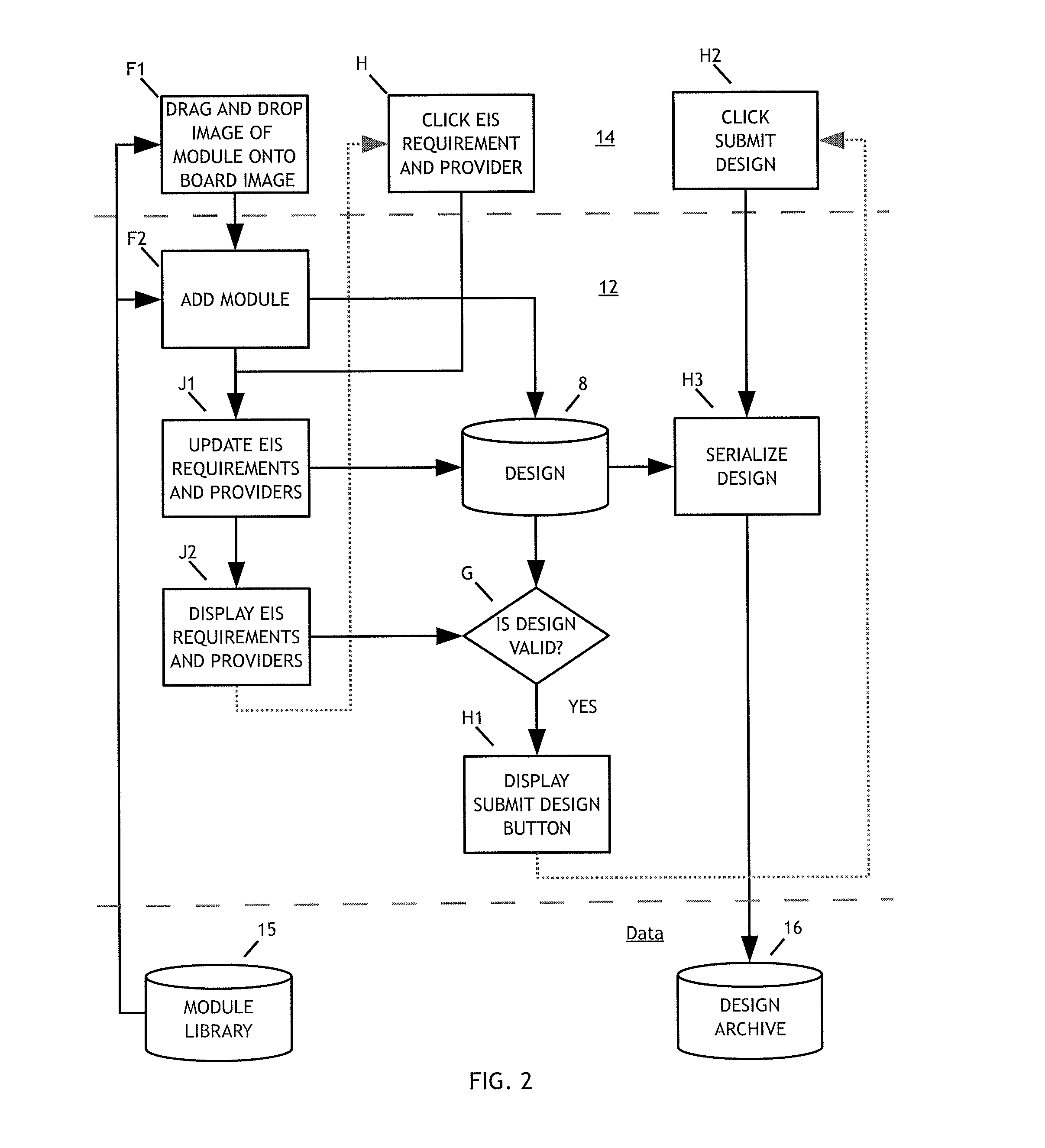

Integrated electronic design automation system

ActiveUS20130326457A1Minimal human interventionEliminate needConfiguration CADTotal factory controlManufacturing execution systemElectronic design automation

An electronic design automation system combines features of discrete EDA / CAD systems and manufacturing systems into a monolithic system to enable a layperson to efficiently design, construct and have manufactured a specific class of custom electronic device, namely a computer processing unit with embedded software. A Graphical User Interface (GUI) is provided as the front-end to a Computer Aided Design (CAD) server that generates sophisticated control and manufacturing instructions that are delivered to a fabrication supply chain, which produces a specified device that is then transported via managed logistics into inventory and ordering systems at vendors for delivery to a designated customer.

Owner:ALTIUM LLC

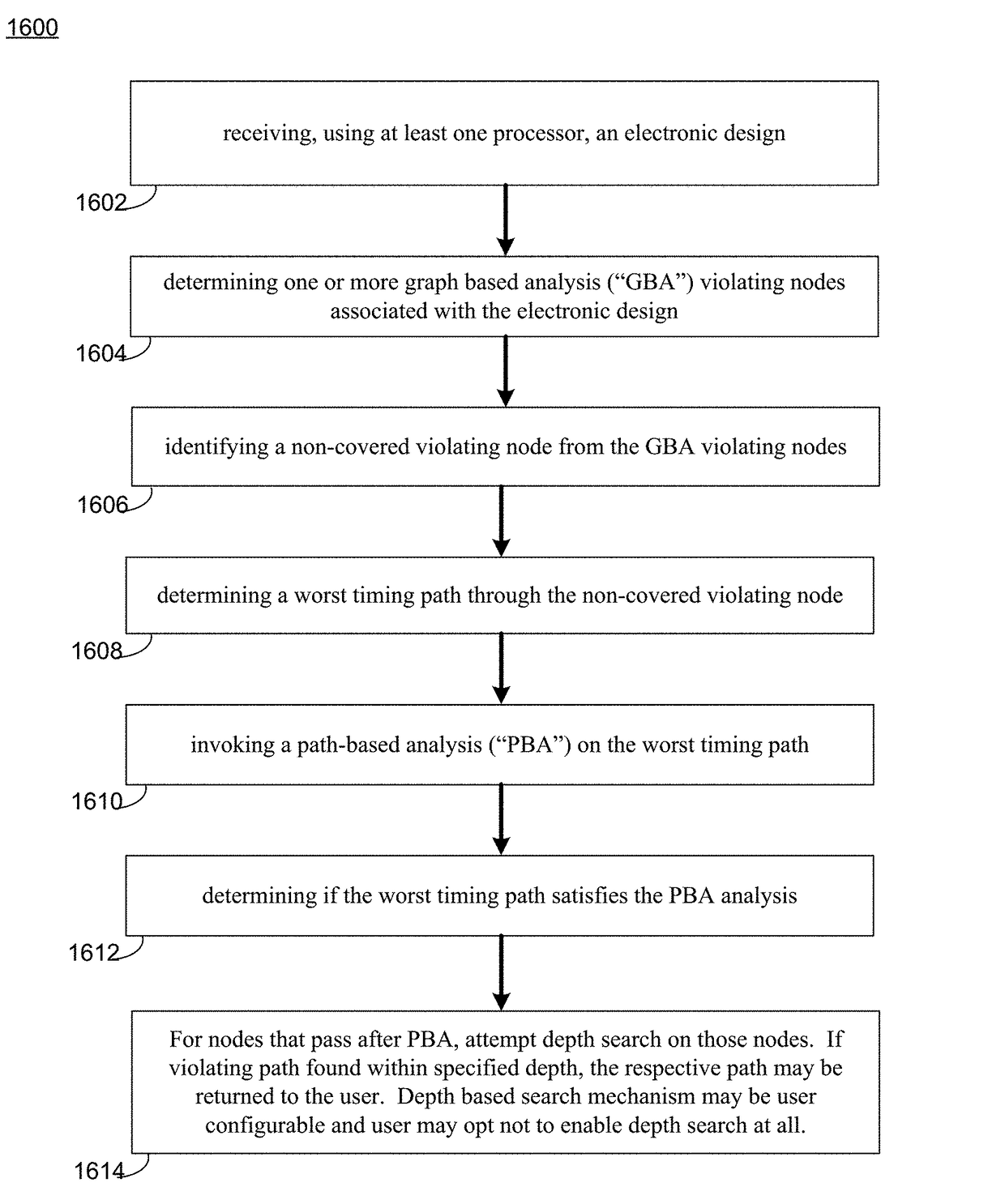

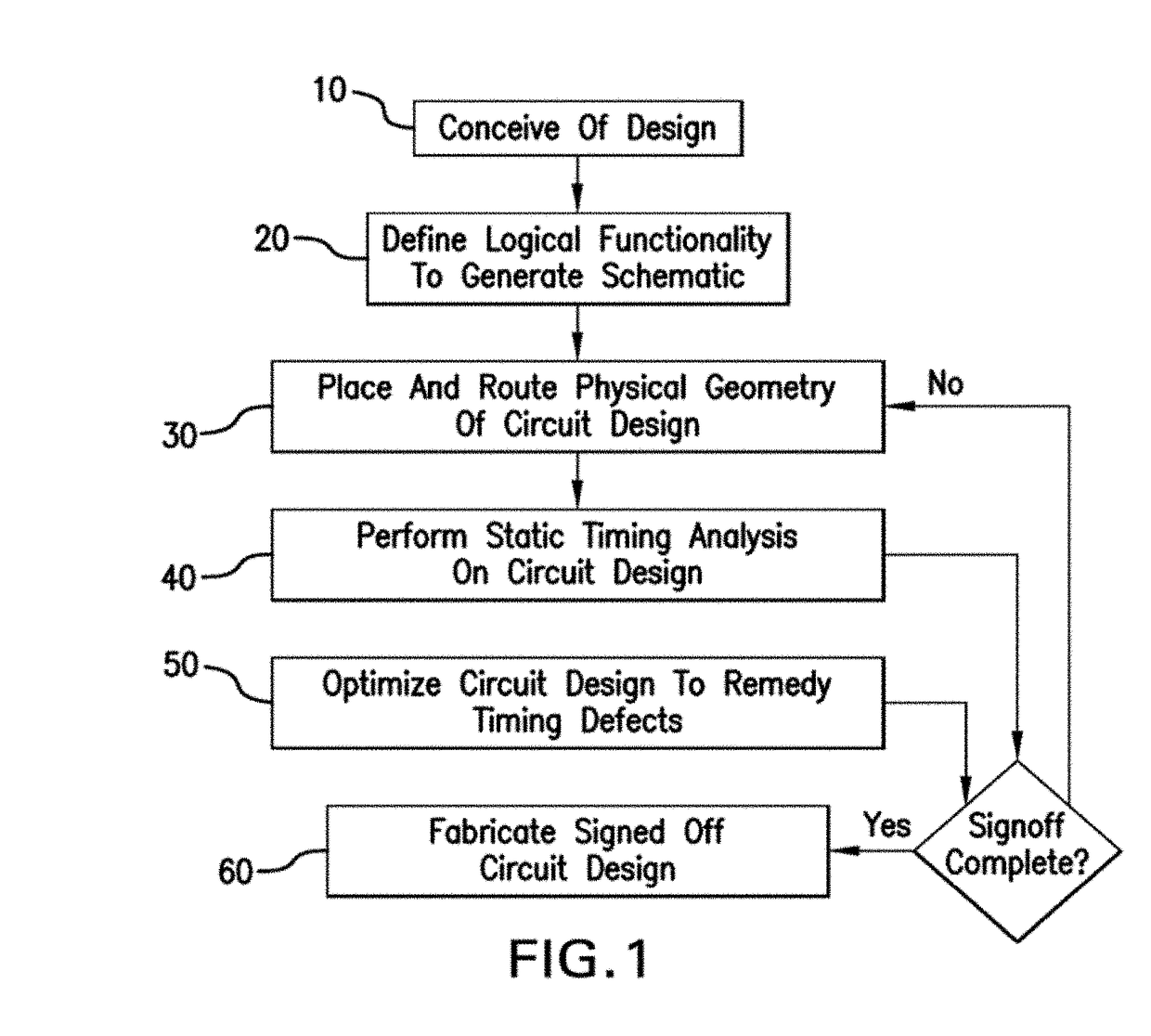

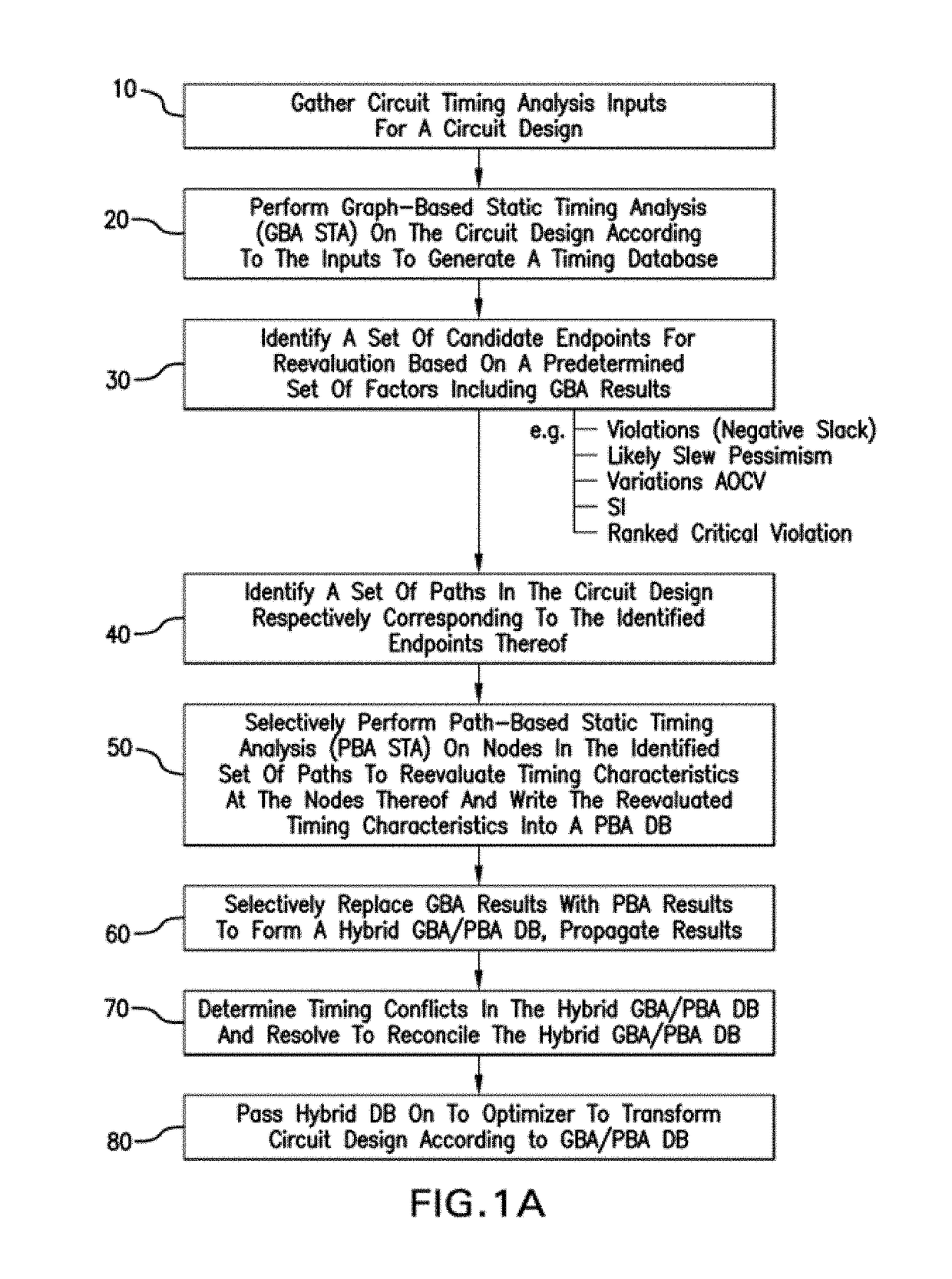

Comprehensive path based analysis process

ActiveUS9875333B1Computer aided designSpecial data processing applicationsElectronic designComputer science

The present disclosure relates to a system and method for electronic design automation. Embodiments may include receiving, using at least one processor, an electronic design and determining one or more graph based analysis (“GBA”) violating nodes associated with the electronic design. Embodiments may include identifying a non-covered violating node from the GBA violating nodes and determining a worst timing path through the non-covered violating node. Embodiments may further include invoking a path-based analysis (“PBA”) on the worst timing path and determining if the worst timing path satisfies the PBA analysis.

Owner:CADENCE DESIGN SYST INC

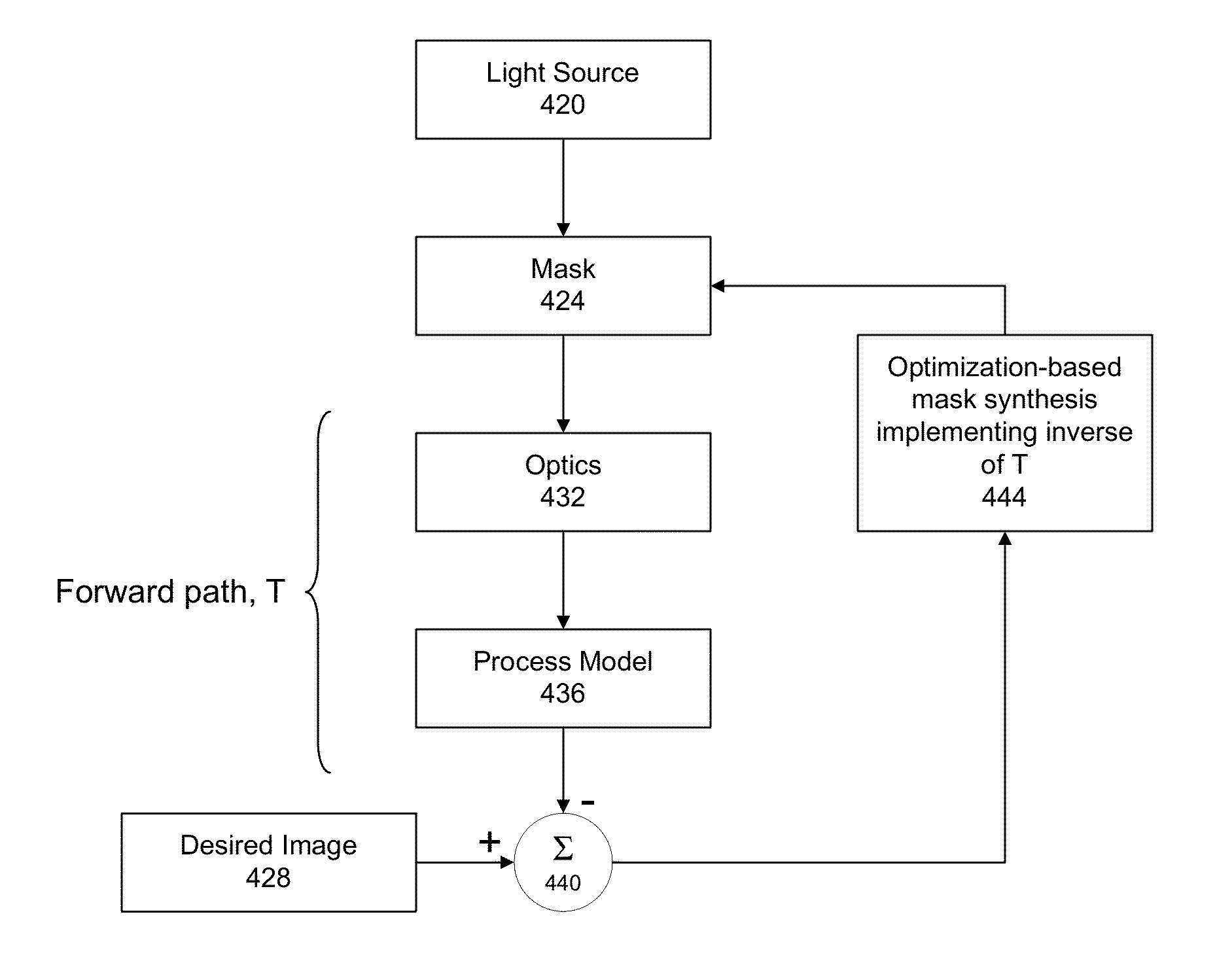

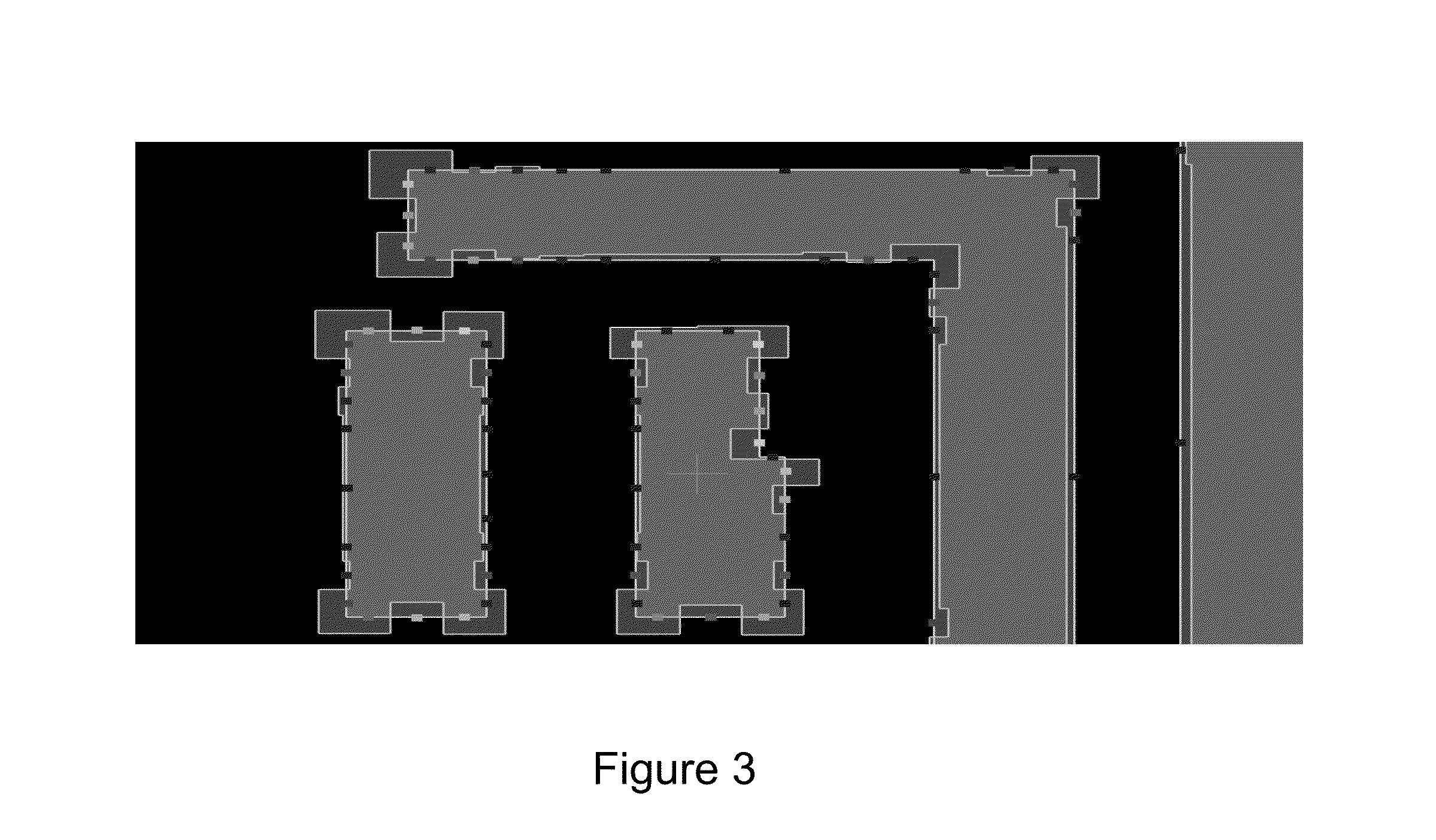

Techniques of optical proximity correction using GPU

ActiveUS8490034B1Enhanced MaskingPhotomechanical apparatusCAD circuit designFine structureGraphics processing unit

Computationally intensive electronic design automation operations are accelerated with algorithms utilizing one or more graphics processing units. The optical proximity correction (OPC) process calculates, improves, and optimizes one or more features on an exposure mask (used in semiconductor or other processing) so that a resulting structure realized on an integrated circuit or chip meets desired design and performance requirements. When a chip has billions of transistors or more, each with many fine structures, the computational requirements for OPC can be very large. This processing can be accelerated using one or more graphics processing units.

Owner:D2S

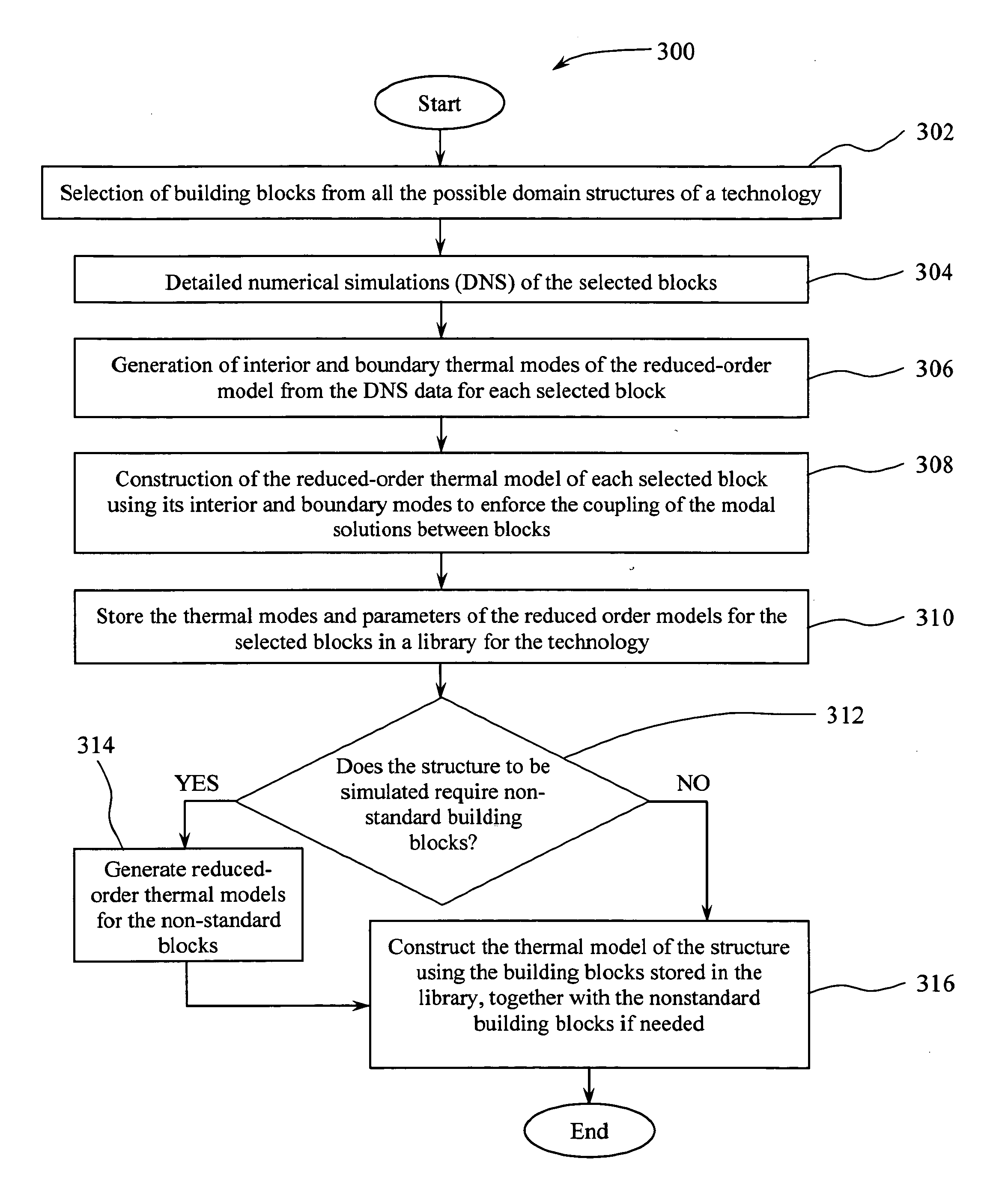

Method for thermal simulation

InactiveUS8539408B1Reduce computing timeWork efficiently and accuratelyComputer aided designSoftware simulation/interpretation/emulationPhysical spaceSemiconductor chip

The invention of novel methods is described for efficient and accurate thermal simulation of a structure that can be primarily constructed using building blocks. These structures may include, but not limited to, semiconductor chips, photovoltaic / solar panels, battery packs, etc. The methods are formulated in hierarchical function spaces, rather than the physical space and provide three-dimensional (3D) steady-state and transient temperature profiles of the structure, which are as detailed as full-scale numerical simulation, using substantially less computational degrees-of-freedom (DOF). The number of DOF required is comparable to that of lumped thermal models, yet no ad-hoc modeling assumptions related to geometry, dimensions, temperature profiles, or heat flow paths are required. The methods can be applied to evaluate temperature profiles at different levels of granularity. The methods can also be implemented in various computer-aided-design (CAD) or electronic-design-automation (EDA) tools for different technologies to perform electro-thermal simulations.

Owner:CLARKSON UNIVERSITY

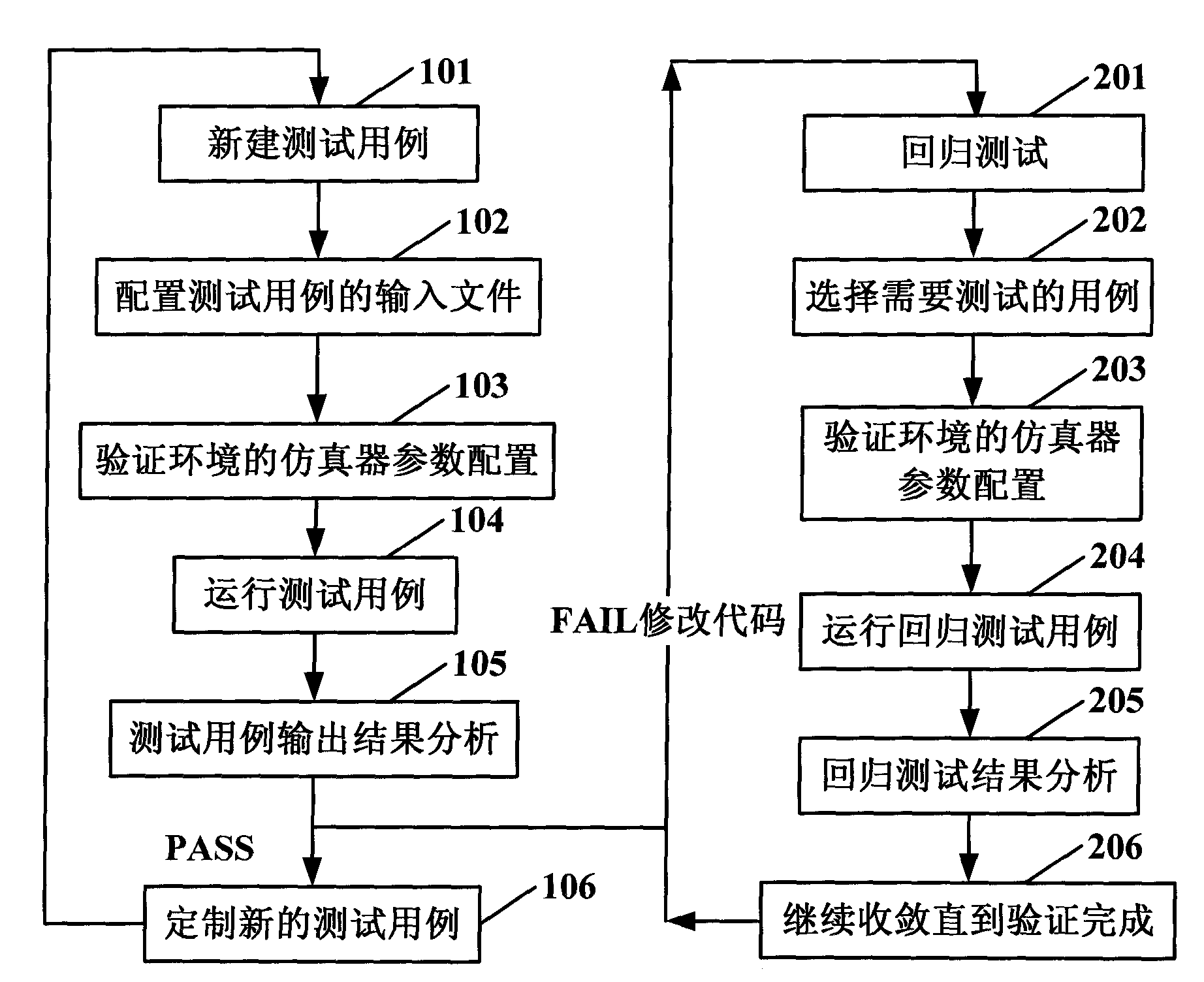

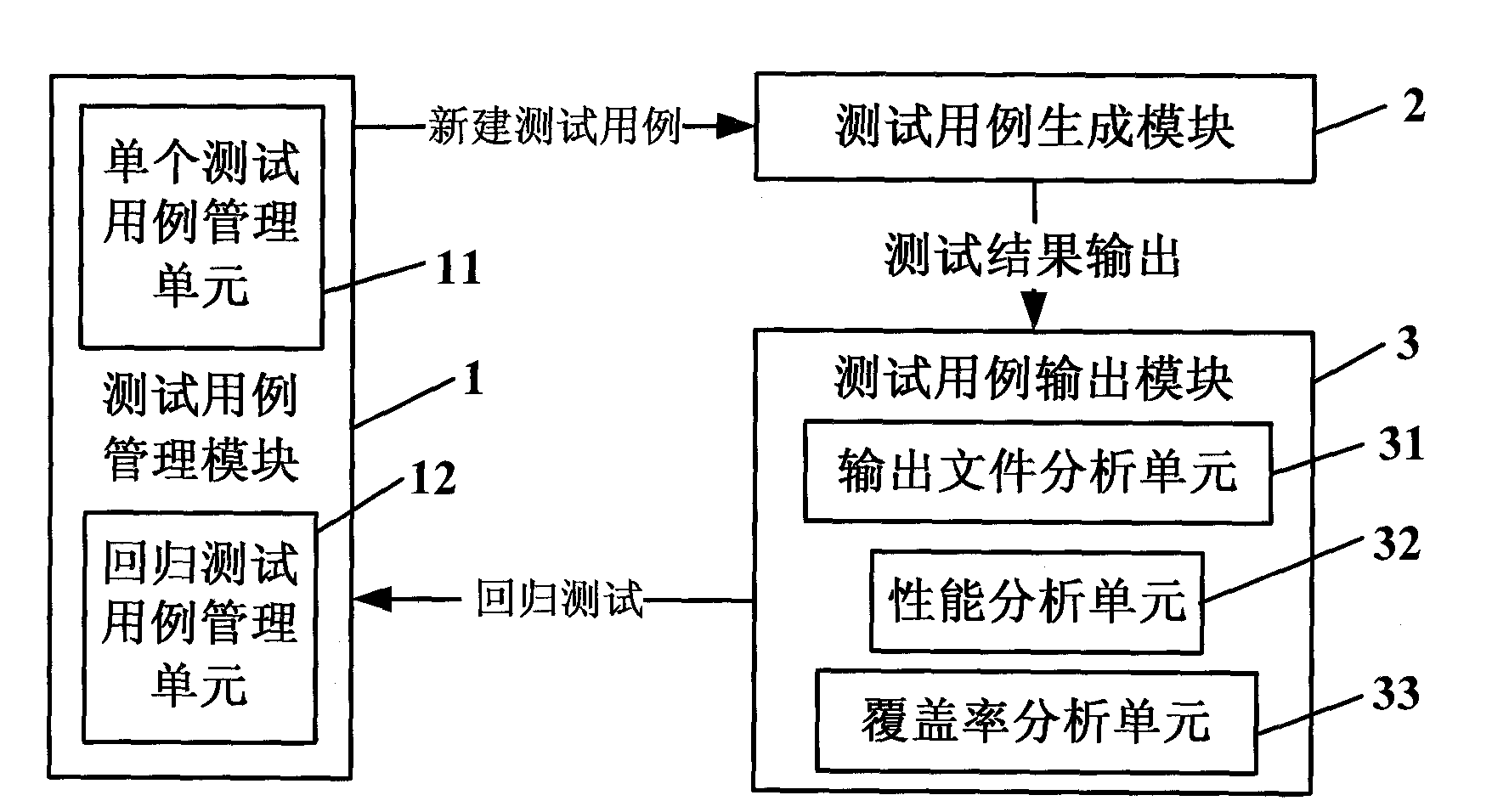

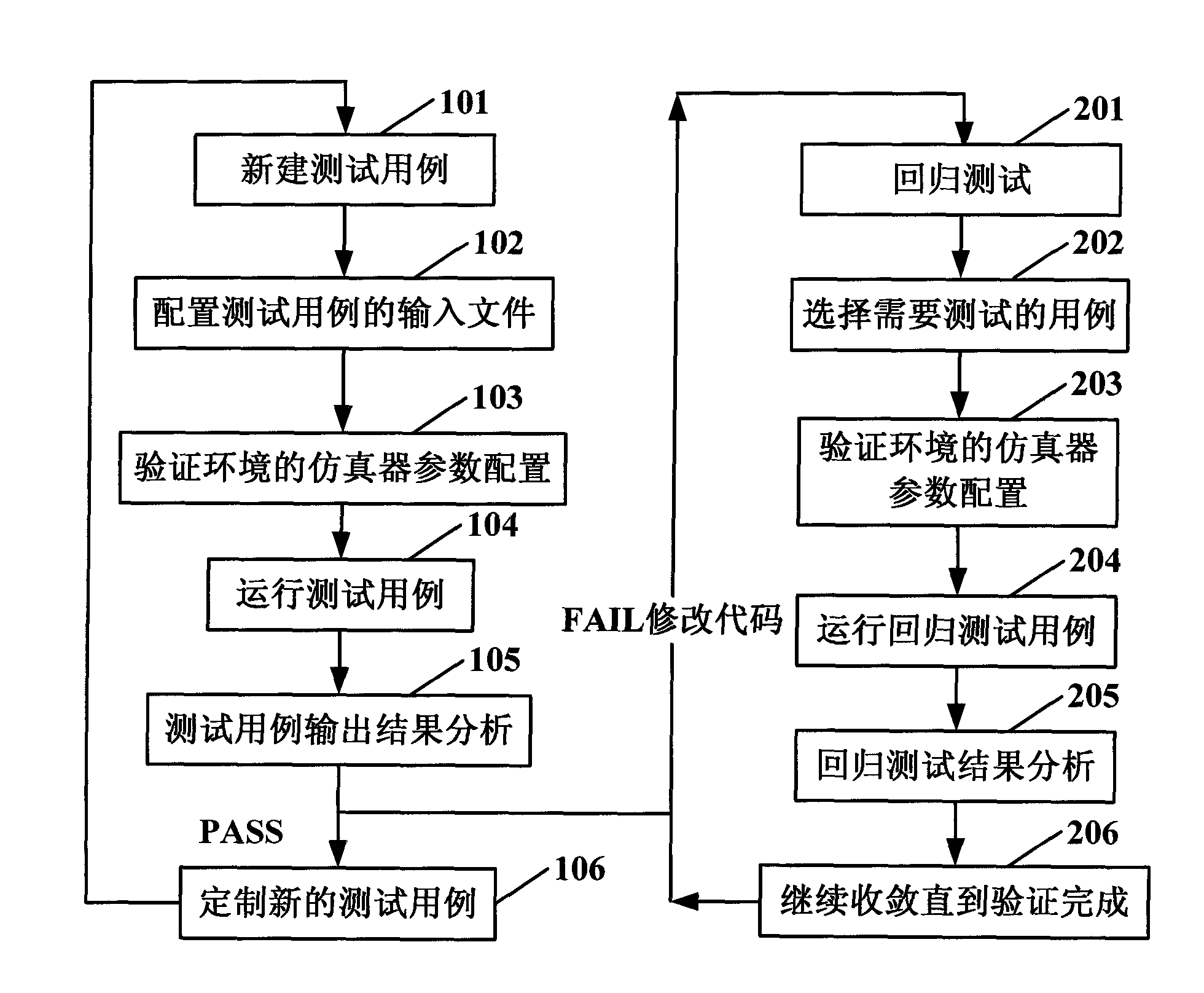

Verifying environment patterned chip verifying method and device

ActiveCN102156784AEasy to operateRealize managementSpecial data processing applicationsRegression testingFunctional testing

The invention discloses verifying environment patterned chip verifying method and device, and relates to the field of electronic design automation (EDA) verification in a chip designing process. The method comprises the following steps: establishing a new test sample, grouping test points according to functions, automatically generating an input document required by chip verification in a patterning mode, and configuring parameters of a simulator; running the test sample, directly interacting with the simulator, and displaying encoding and simulating information of the simulator in a graph mode; observing the test result, verifying the next test sample if the test is successful; and performing regression testing after codes are modified if a fault sample is found. By utilizing the method,the patterning operation and management of chip verification can be realized, the time spent in studying new verification language by testing staff is saved, and the chip verification process becomessimple and intuitive, so that the studying cost of the testing staff is reduced, the chip verification period is greatly shortened, and the efficiency of chip verification is improved.

Owner:FENGHUO COMM SCI & TECH CO LTD

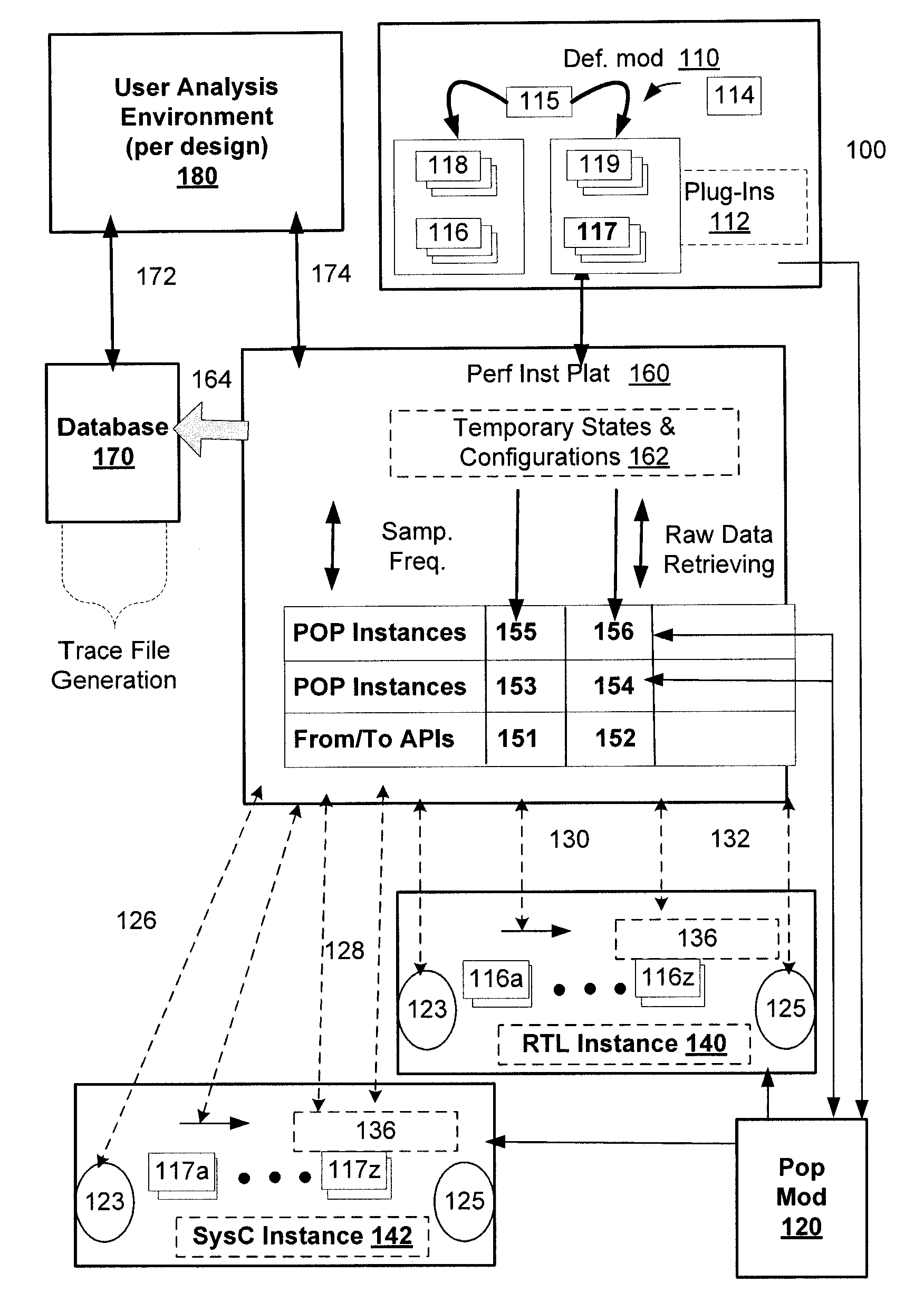

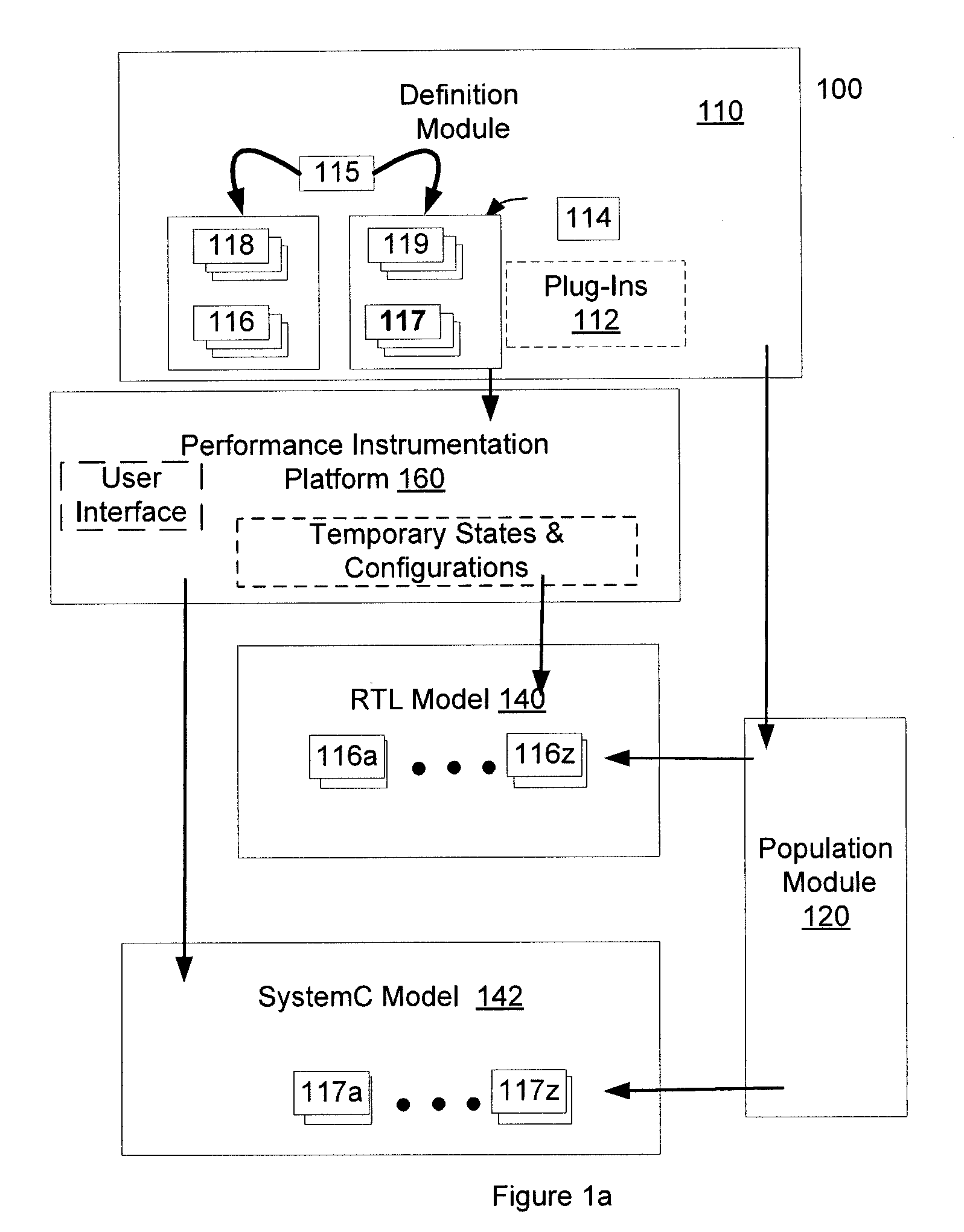

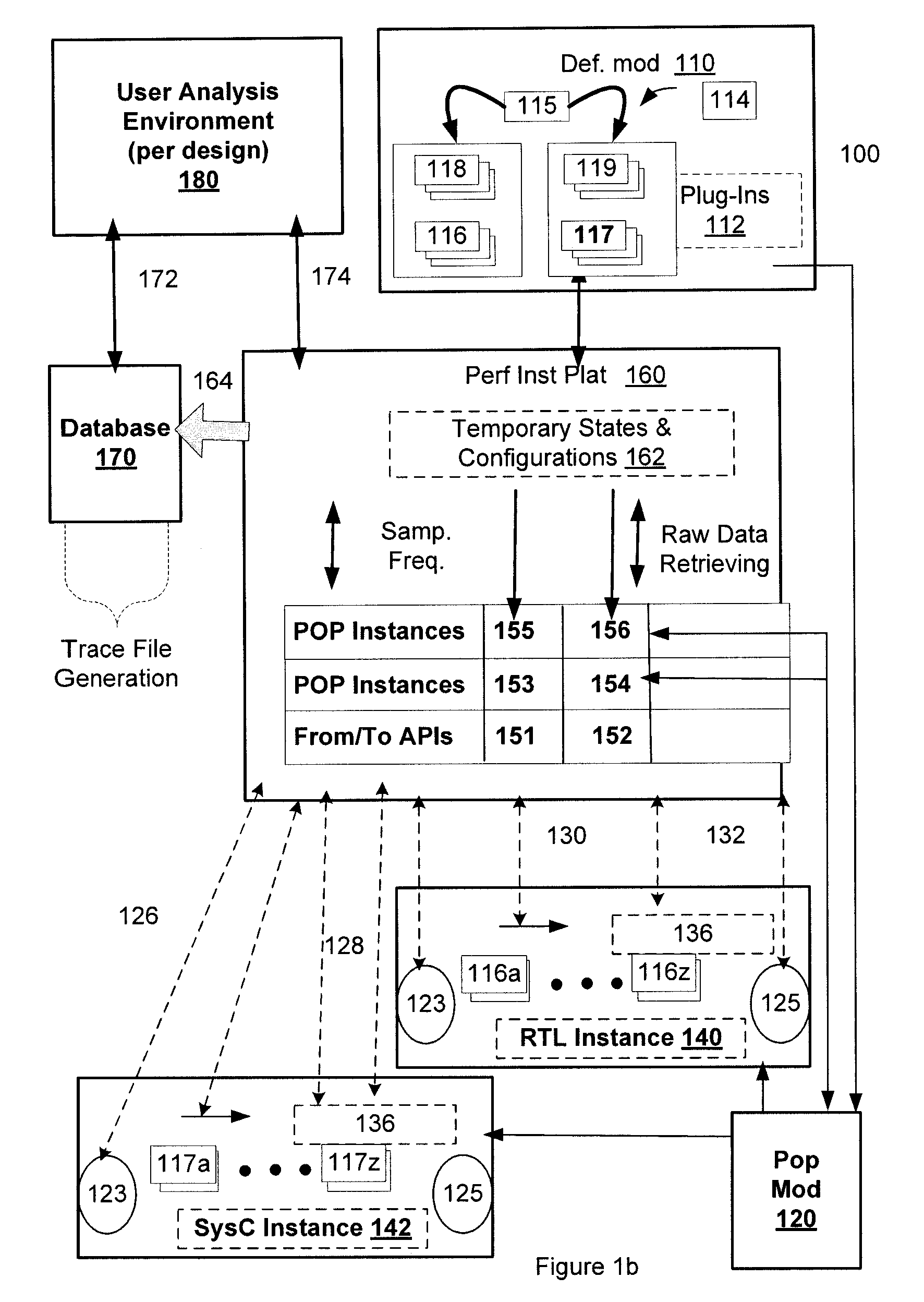

Performance software instrumentation and analysis for electronic design automation

ActiveUS20090150857A1Error detection/correctionElectrical testingSoftware engineeringElectronic design

Various methods and apparatuses are described that provide instrumentation and analysis of an electronic design. A method for providing performance instrumentation and analysis of the electronic design includes defining a first and second set of intended software instrumentation test points and an associated first and second set of performance analysis units. The method further includes instrumenting the first and second sets of software instrumentation test points and the associated first and second sets of performance analysis units to a first model and a second model, respectively. The method further includes creating a first and a second set of software instances associated with the first and second sets of intended software instrumentation test points and associated sets of performance analysis units during run time of a first simulation and a second simulation of the electronic design associated with the first model and second model, respectively.

Owner:META PLATFORMS TECH LLC

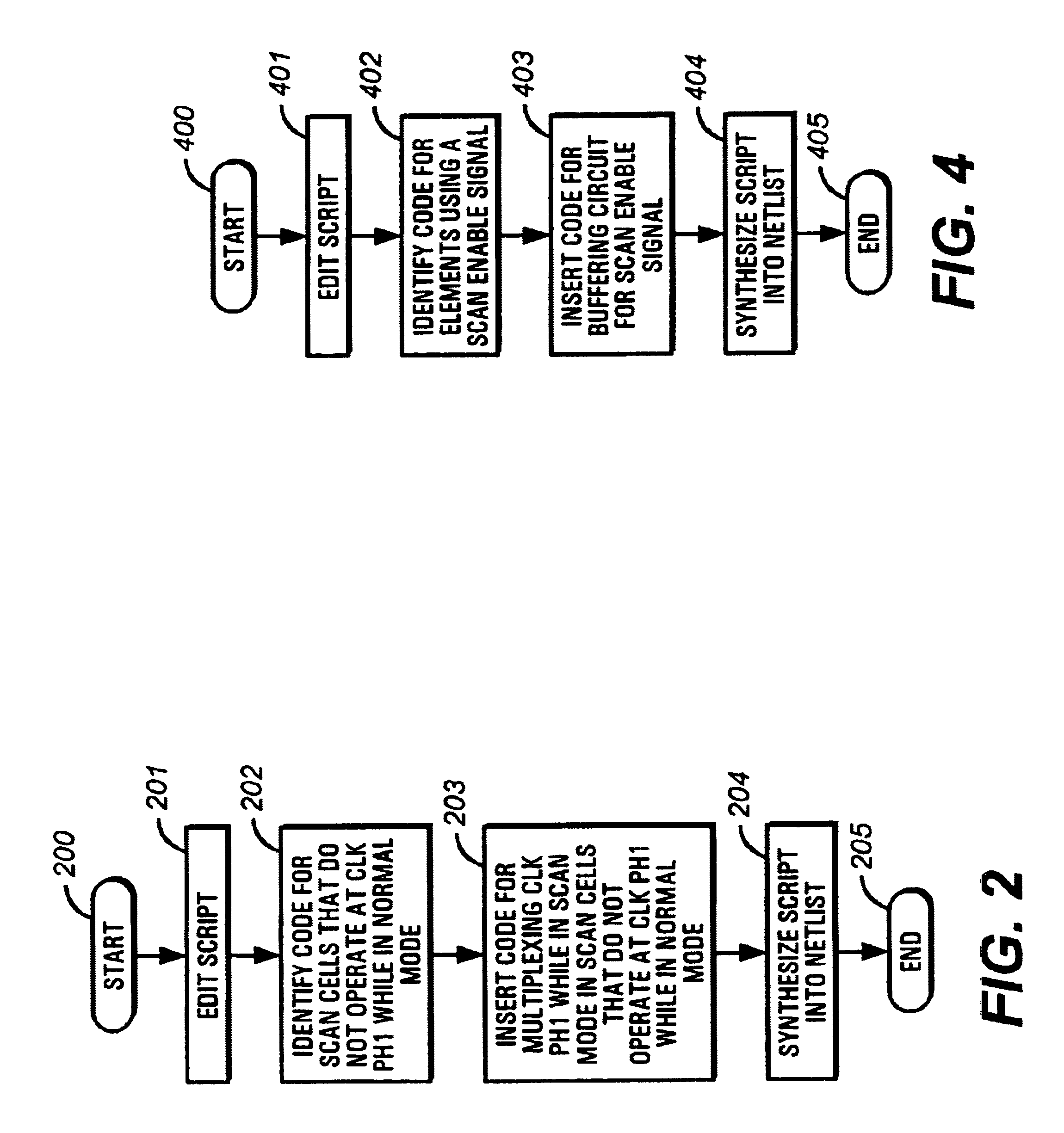

Insertion of scan hardware

InactiveUS6675364B1Electronic circuit testingSoftware simulation/interpretation/emulationMicrocontrollerEngineering

According to the present invention, a method for inserting scan hardware into Integrated Circuits (IC) such as microcontrollers is disclosed. Custom scripts used by electronic design automation (EDA) tools are configured to accommodate those microcontroller designs that operate with multiple clocks and legacy cores. Furthermore, according to the present invention, custom script are used to provide buffering circuits to drive the scan hardware.

Owner:GLOBALFOUNDRIES INC

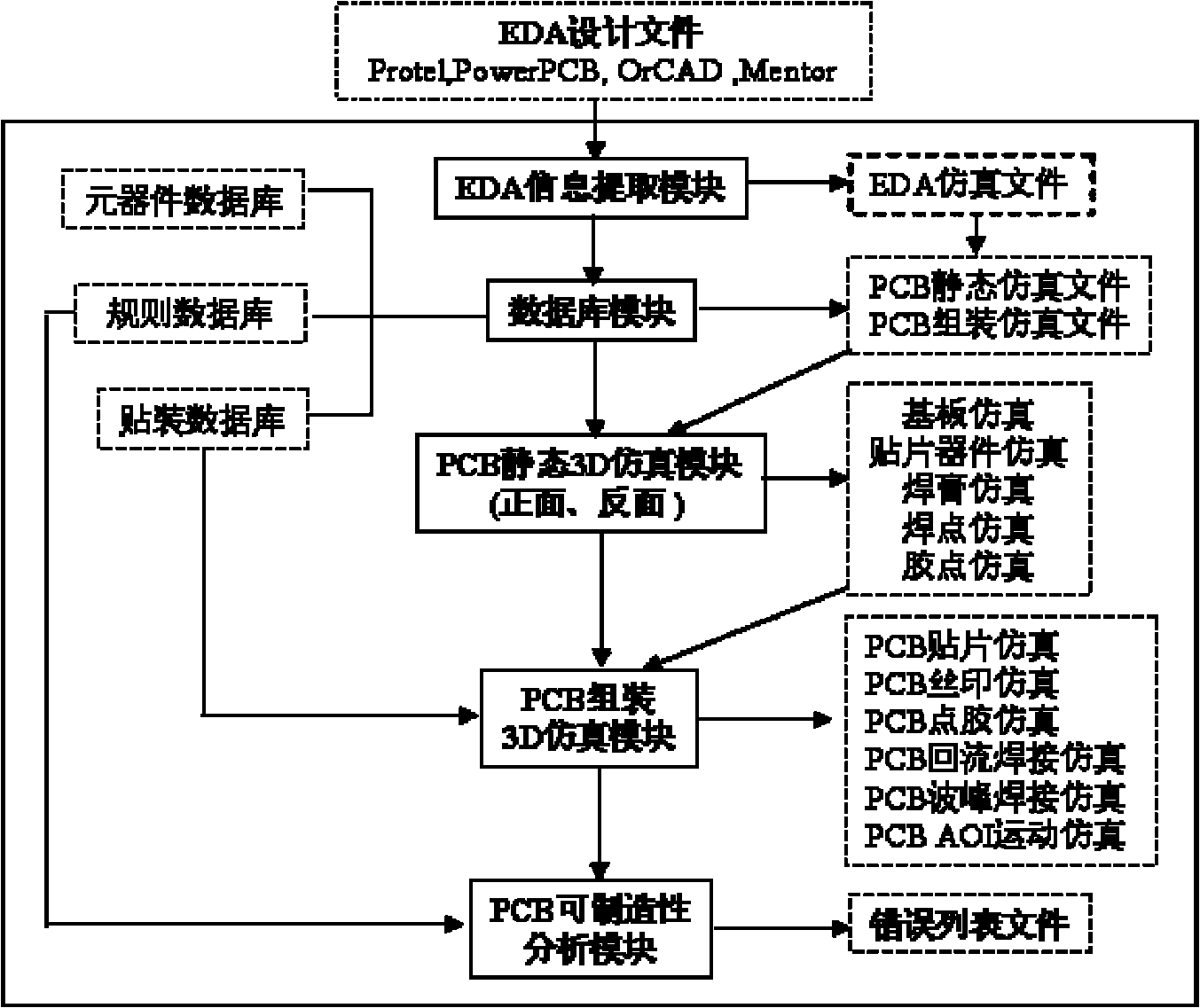

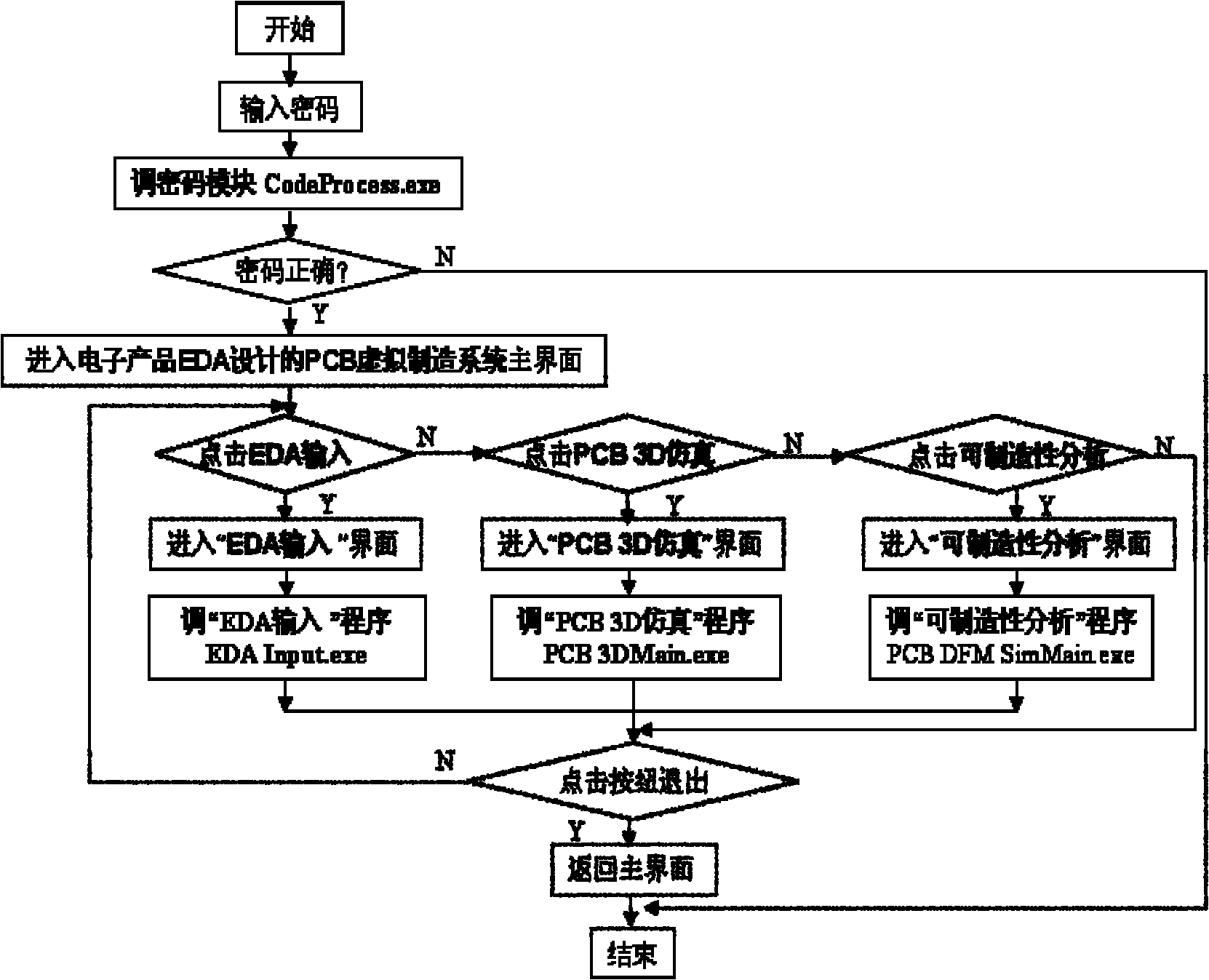

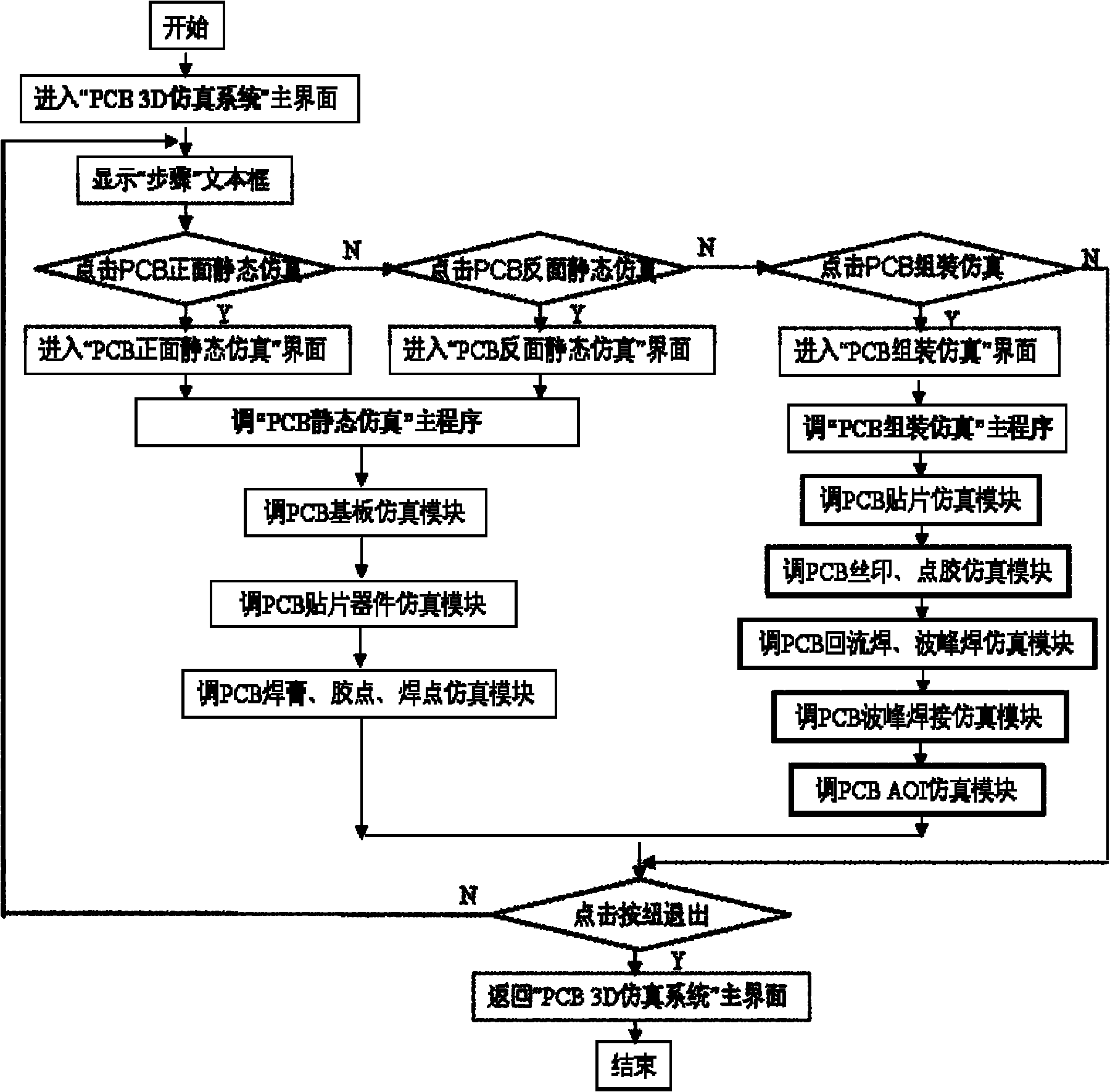

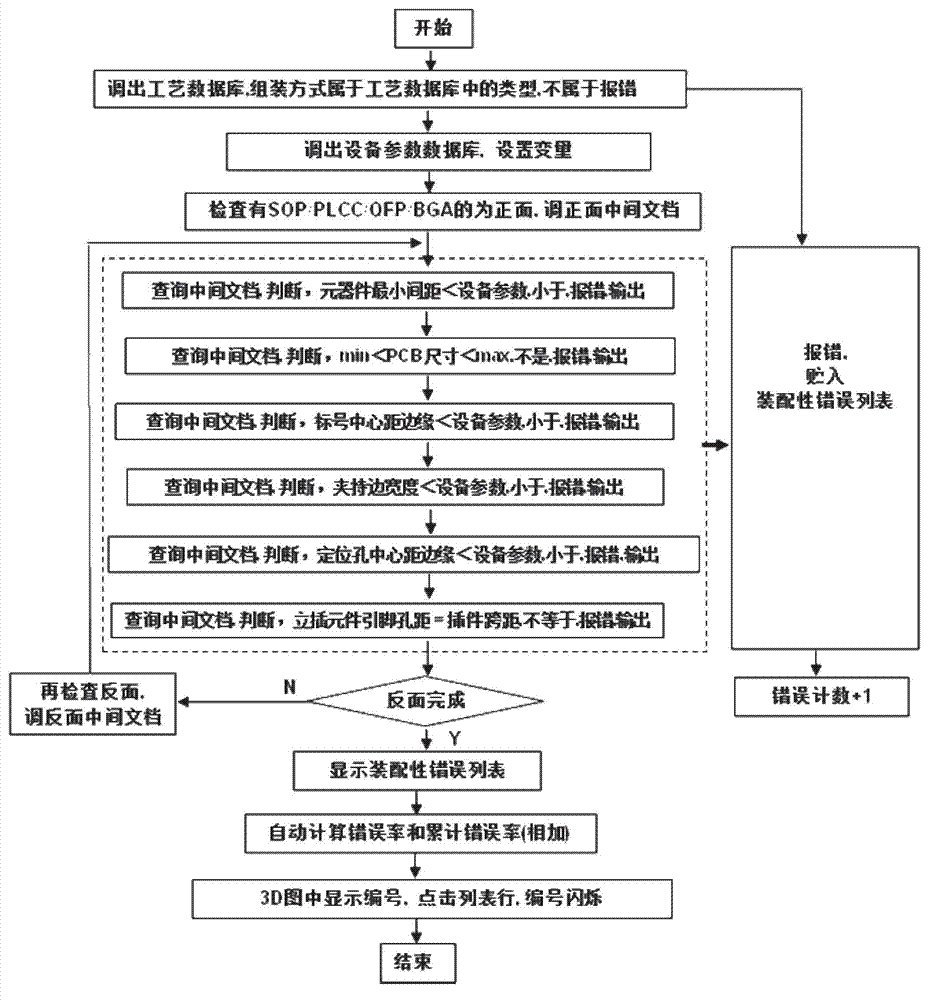

Printed circuit board virtual manufacturing system of electronic design automation of electronic product and realization method thereof

InactiveCN101986316ASave time and costSave production costSpecial data processing applicationsReal time displayPrinted circuit board

The invention relates to a printed circuit board (PCB) virtual manufacturing system of the electronic design automation (EDA) of the electronic product and a realization method thereof. The realization method comprises the following steps: all types of EDA design files can be extracted and converted to an EDA simulation file with the same format and data are input in a database; the PCB static (three-dimensional) 3D simulation and assembly 3D simulation are performed under the VC++ 6.0 environment; and finally PCB manufacturability analysis is performed to extract the simulation information and the judgement parameters of each element, the judgement parameters of each element are detected one by one according to the manufacturability design criteria in a rule database, and the PCB physical parameter error and assembly error of the EDA of the electronic product are displayed and filed instantly. By adopting the method of the invention, the relationship between the PCB design and the manufacture of the isolated island can be built and the visual basis can be provided for the data modification of the EDA optimal deign in the shortest time, thus the aim of optimizing the development cycle and the cost and maximizing the production efficiency can be achieved.

Owner:CHANGZHOU AUTOSMT INFORMATION TECH

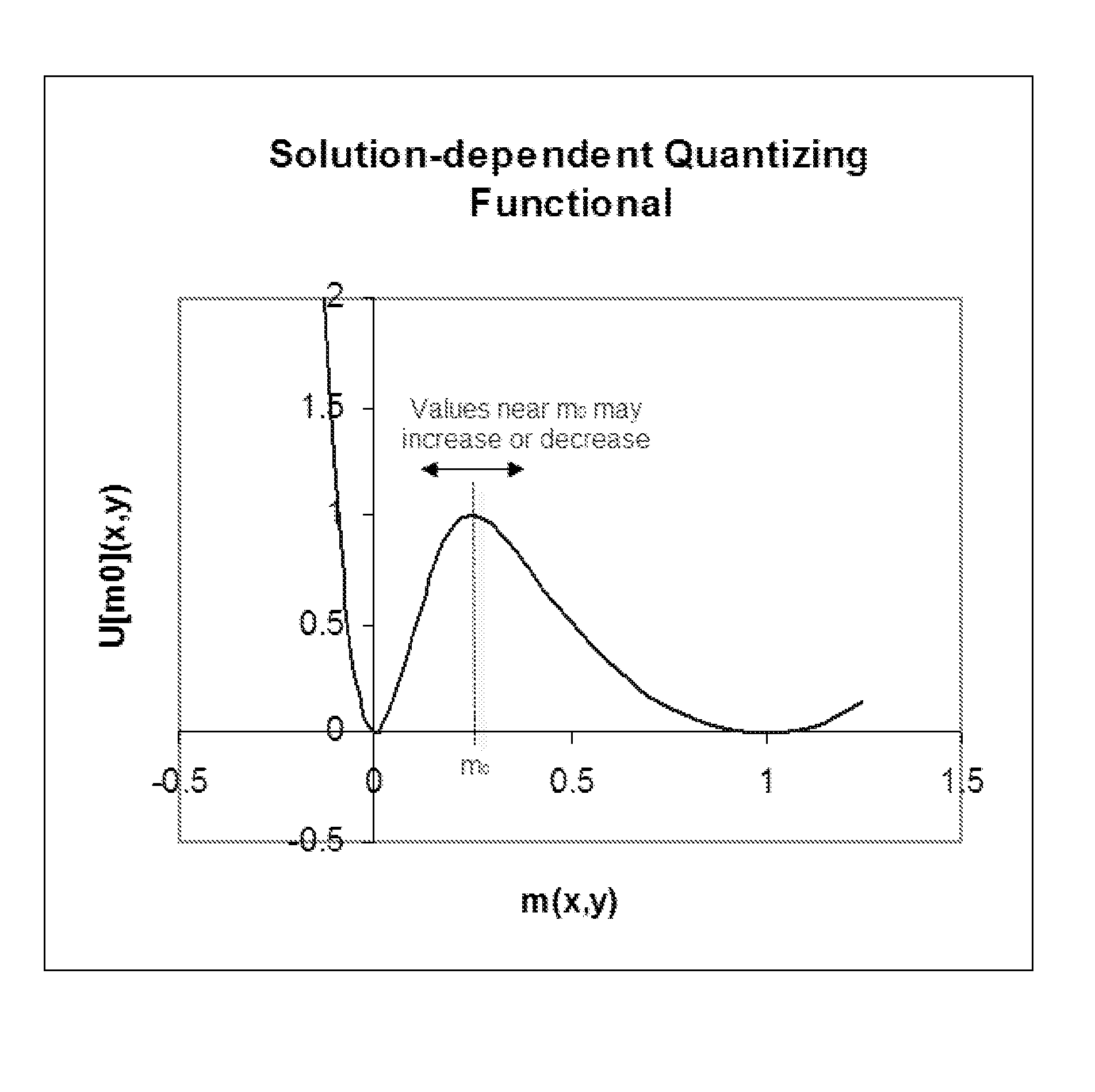

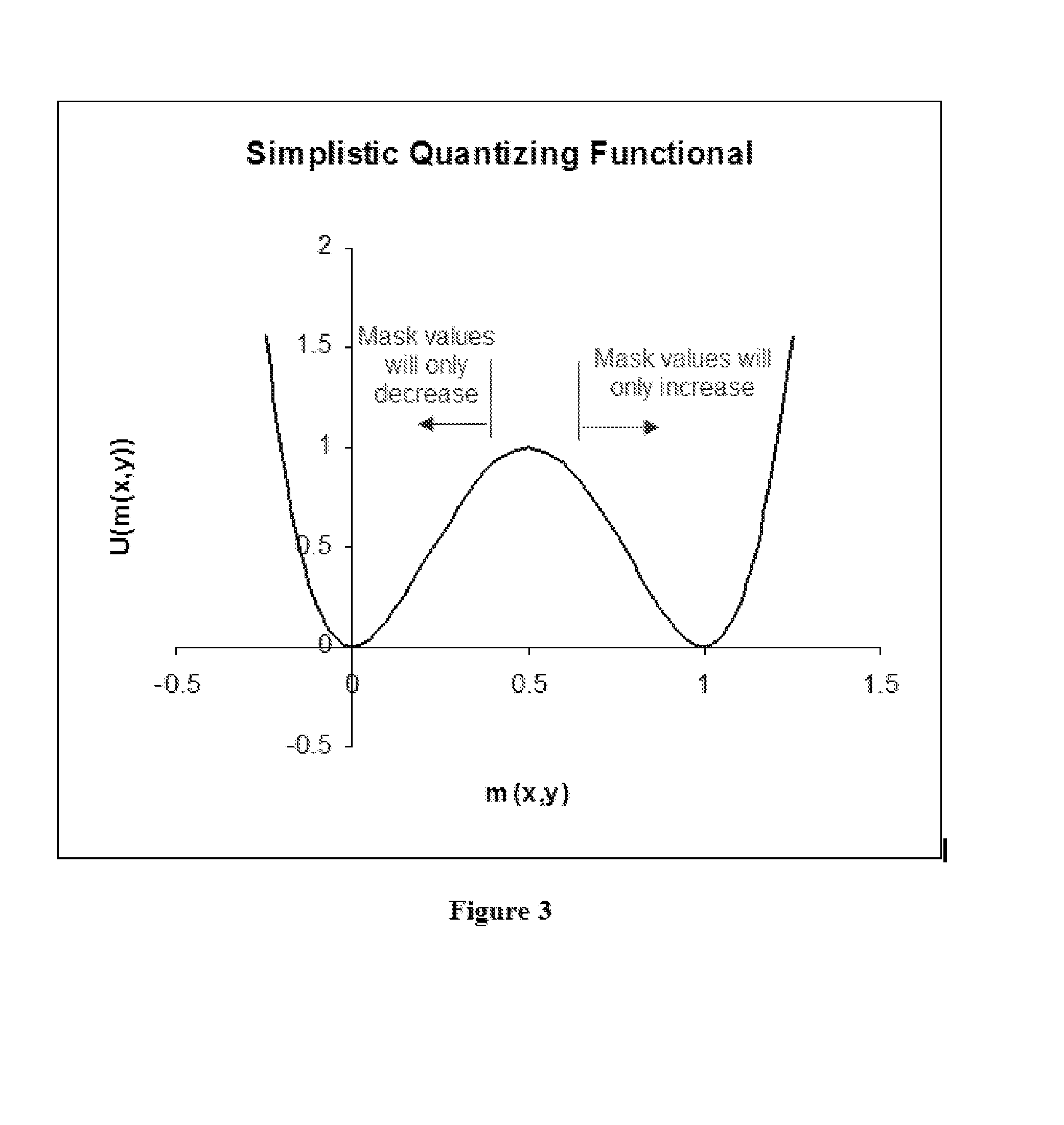

Solution-dependent regularization method for quantizing continuous-tone lithography masks

ActiveUS7716627B1Large fractionNatural language data processingCAD circuit designContinuous toneEngineering

In an electronic design automation technique for optical proximity correction, an optimized mask function that has values other than those allowed for a particular mask type, such as 0 and 1 for a chrome-on-glass binary mask, evolves it to a solution restricted to these values or narrow intervals near them. The technique “regularizes” the solution by mixing in a new cost functional that encourages the mask to assume the desired values. The mixing in may be done over one or more steps or even “quasistatically,” in which the total cost functional and the mask is brought from pure goodness-of-fit to the printed layout for given conditions to pure manufacturability by keeping the total cost functional minimized step-by-step. A goal of this gradual mixing-in is to do thermodynamically optimal work on the mask function to bring it to manufacturable values.

Owner:D2S

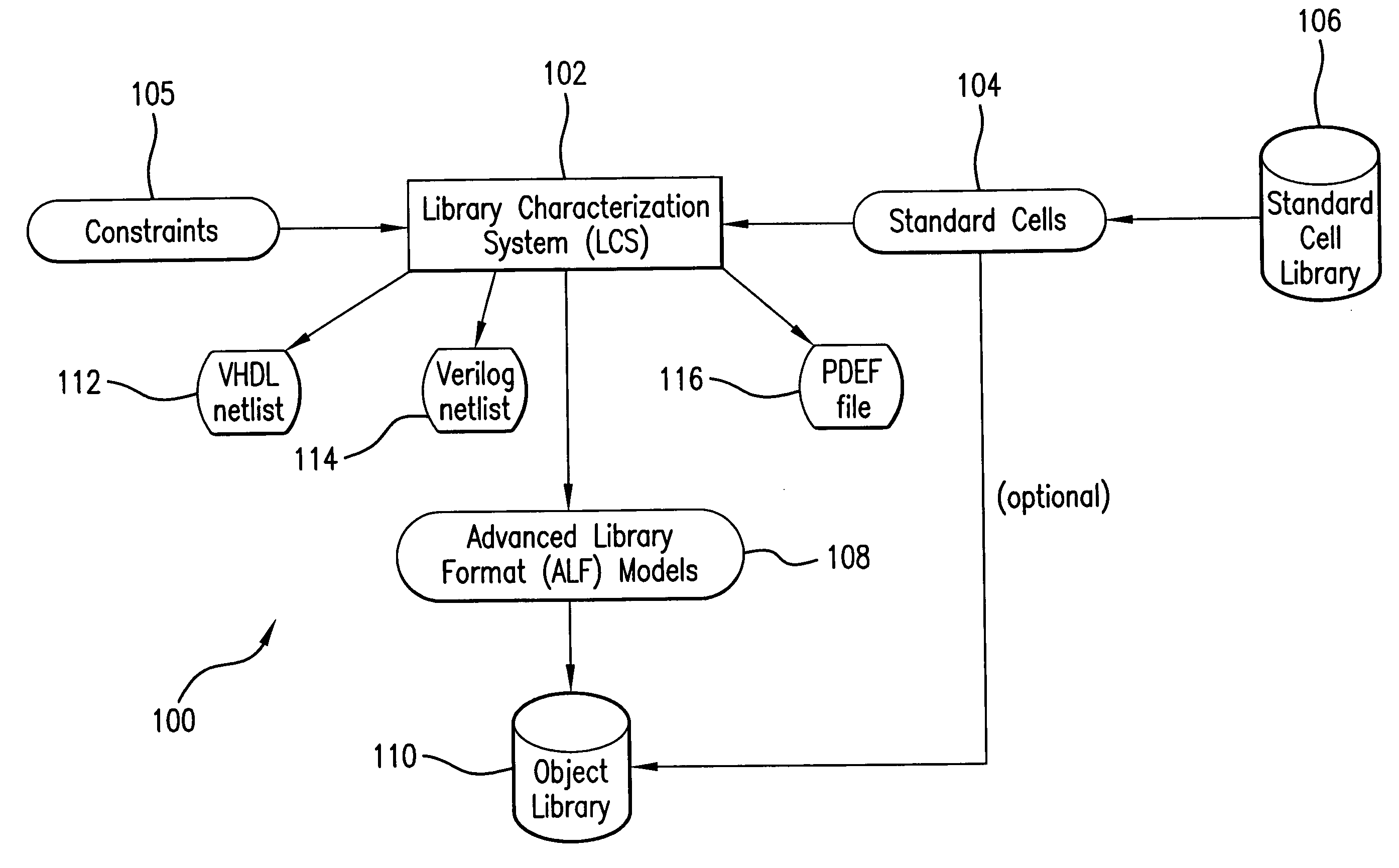

Methods and systems for structured ASIC electronic design automation

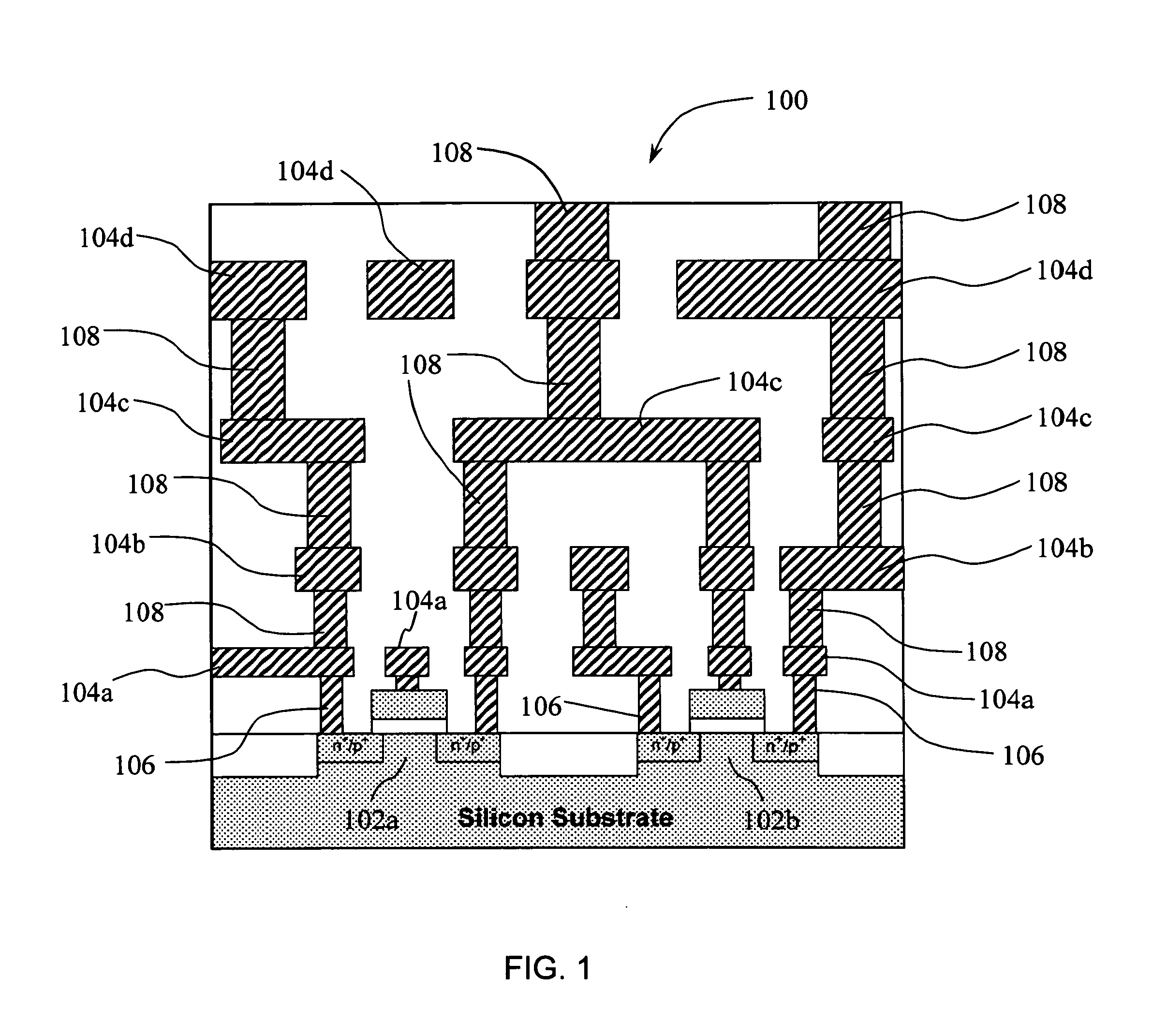

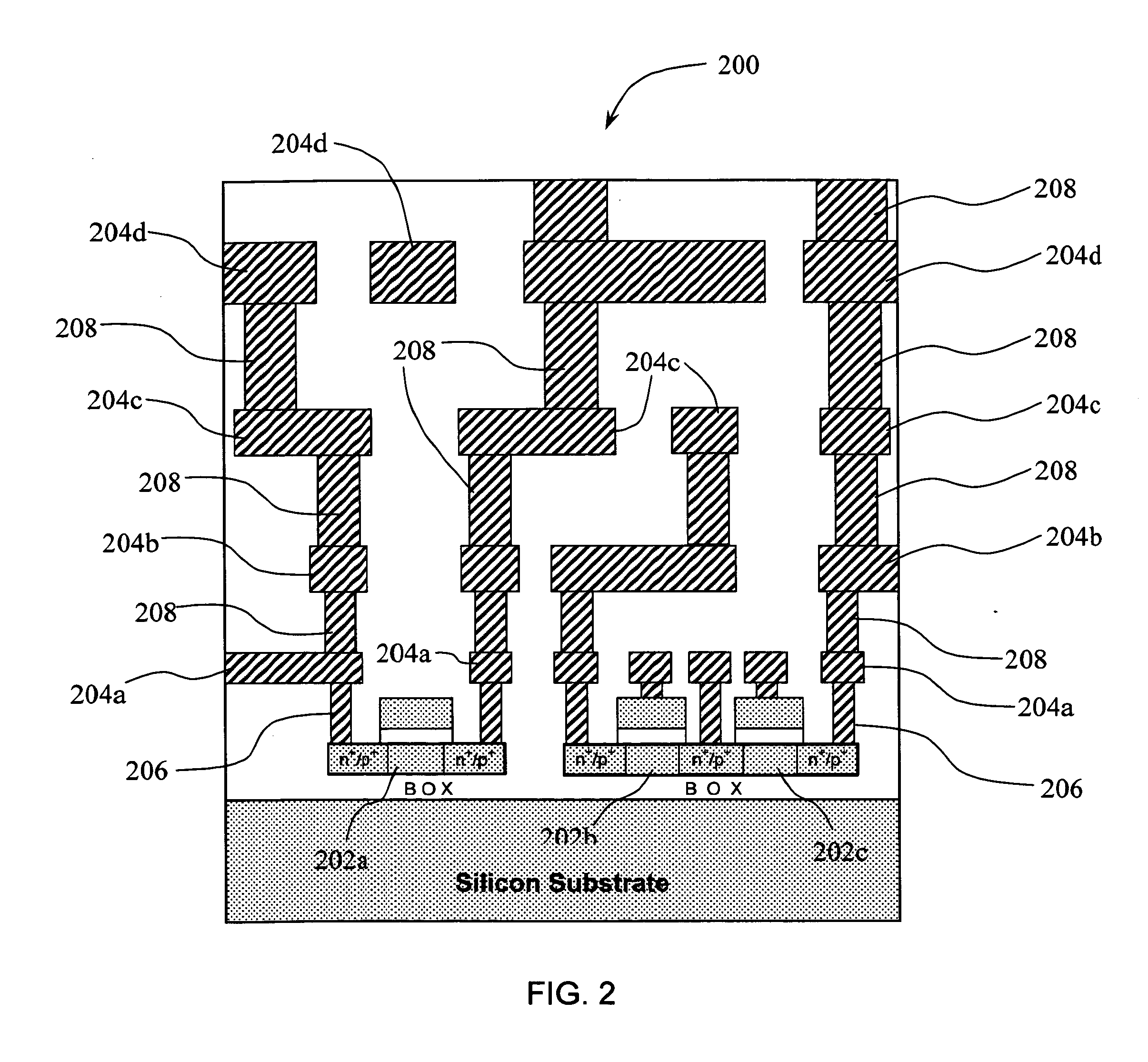

InactiveUS20050268268A1Minimize the numberCAD circuit designProgram controlComputer architectureMemory object

Electronic design automation (“EDA) methods and systems for structured ASICs include accessing or receiving objects representative of source code for a structured ASIC. The objects are flattened to remove hierarchies associated with the source code, such as functional RTL hierarchies. The flattened objects are clustered to accommodate design constraints associated with the structured ASIC. The clustered objects are floorplanned within a design area of the structured ASIC. The objects are then placed within the portions of the design areas assigned to the corresponding clusters. The objects optionally include logic objects and one or more memory objects and / or proprietary objects, wherein the one or more memory objects and / or proprietary objects are placed concurrently with the logic objects.

Owner:TERA SYST

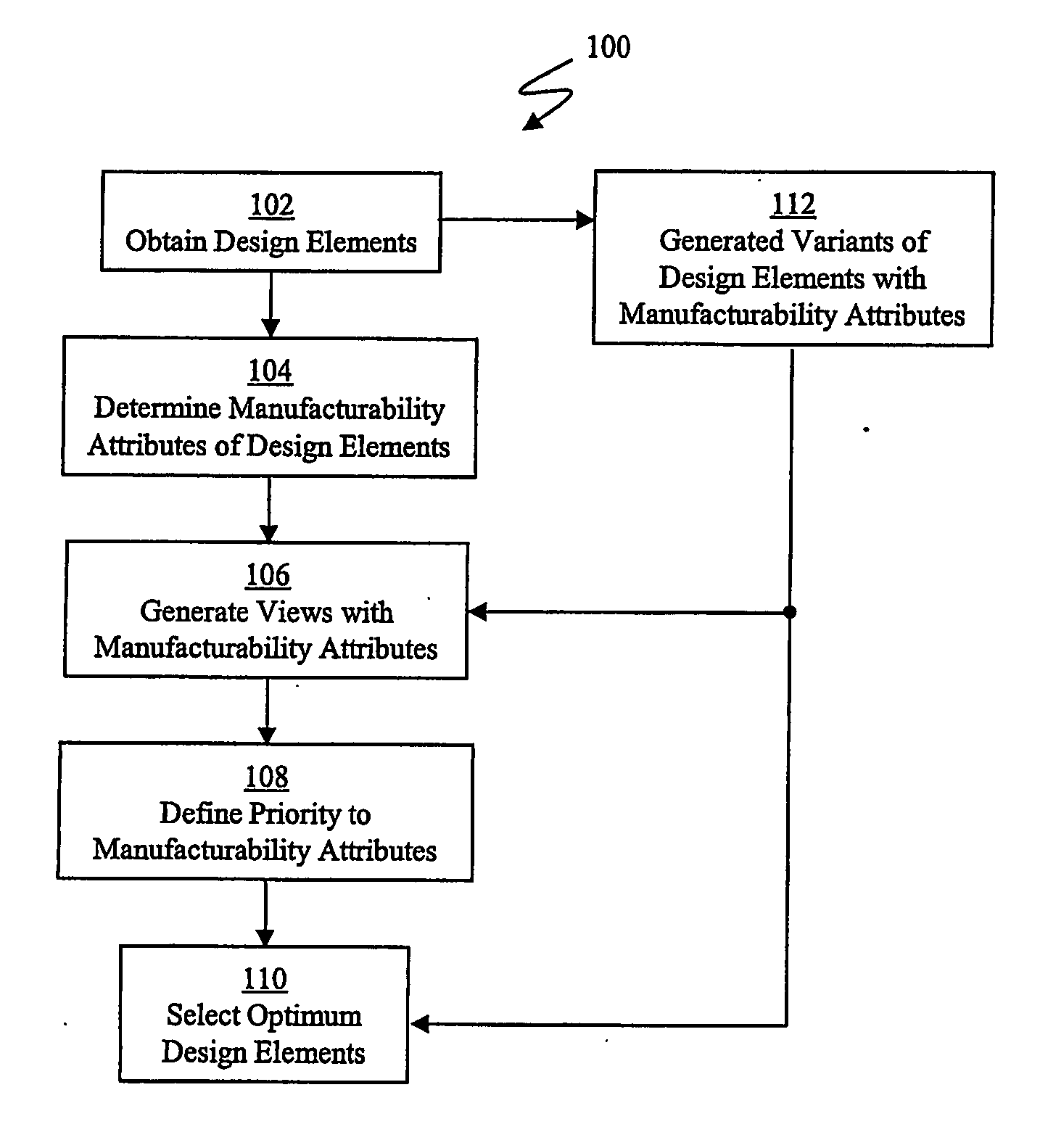

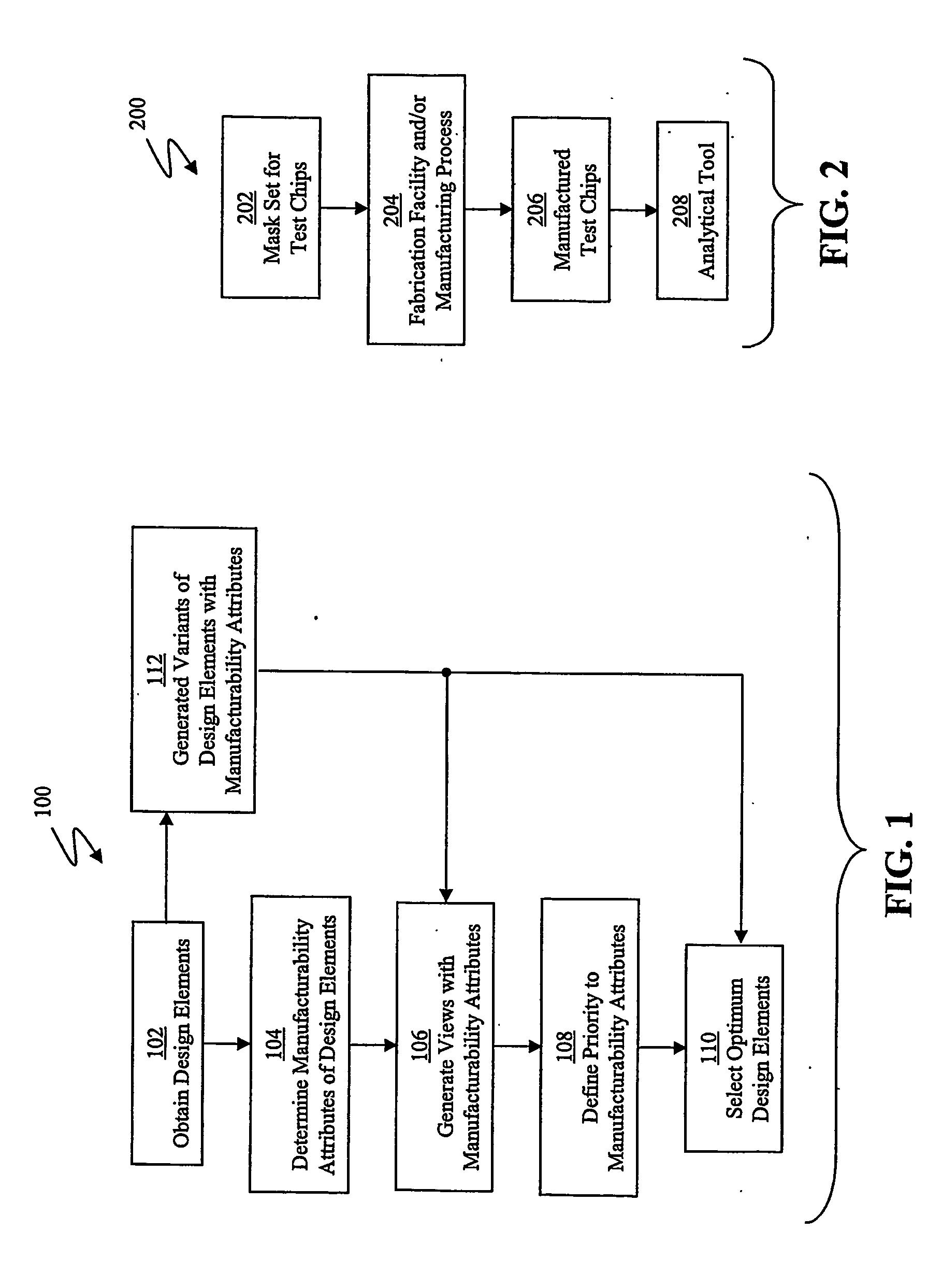

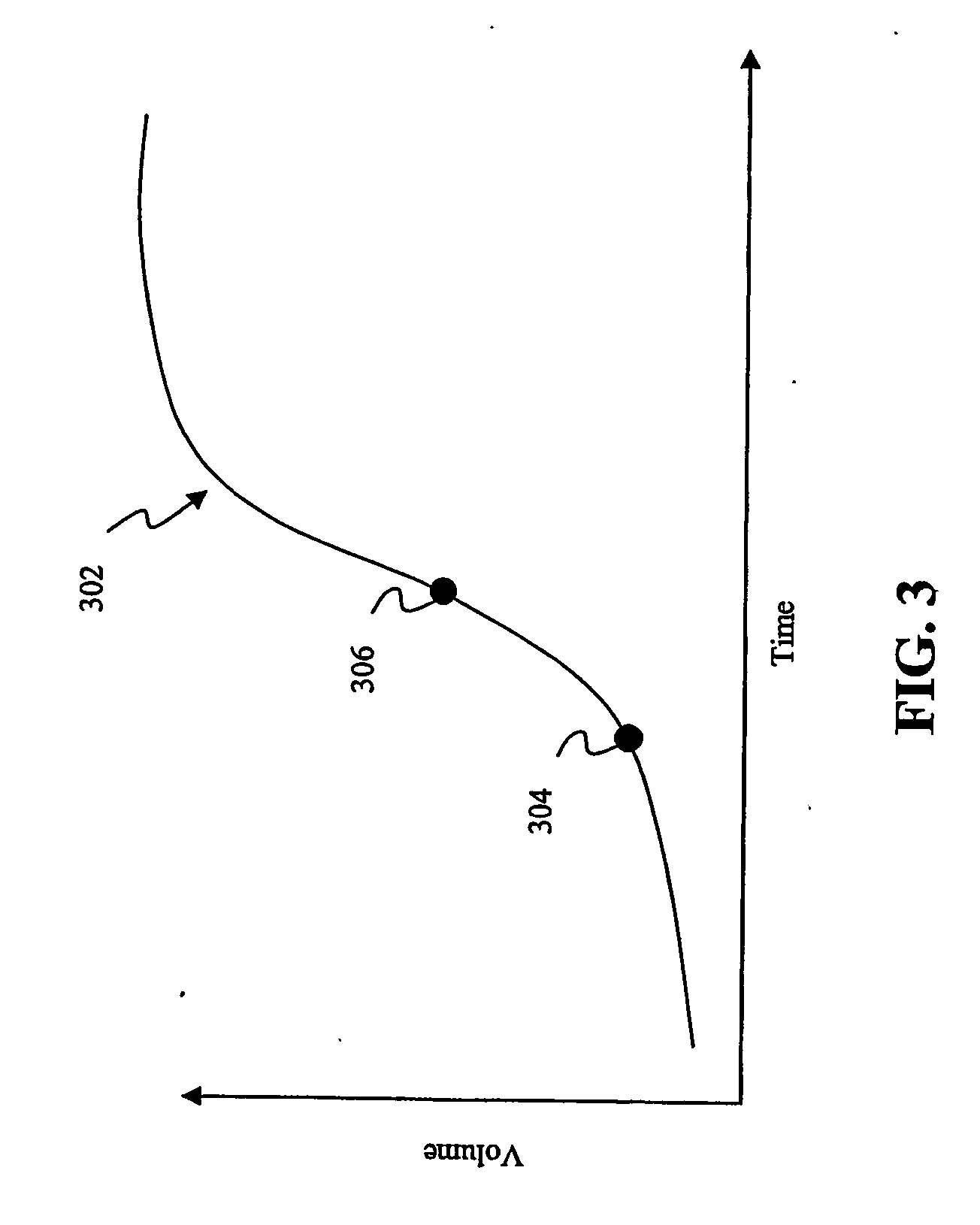

Integrated circuit design to optimize manufacturability

InactiveUS20060253810A1CAD circuit designSpecial data processing applicationsEngineeringElectronic design automation

Library design elements (102) are analyzed for manufacturability to be used in designing an IC chip to be manufactured using a particular manufacturing process. The library design elements from a library are obtained. Manufacturability attributes (104) of the library design elements are determined for the particular manufacturing process, where manufacturability attributes include yield-related attributes. Library views (106) with manufacturability attributes for the library design elements are then generated, which are utilizing by an electronic design automation (EDA) tool.

Owner:PDF SOLUTIONS INC

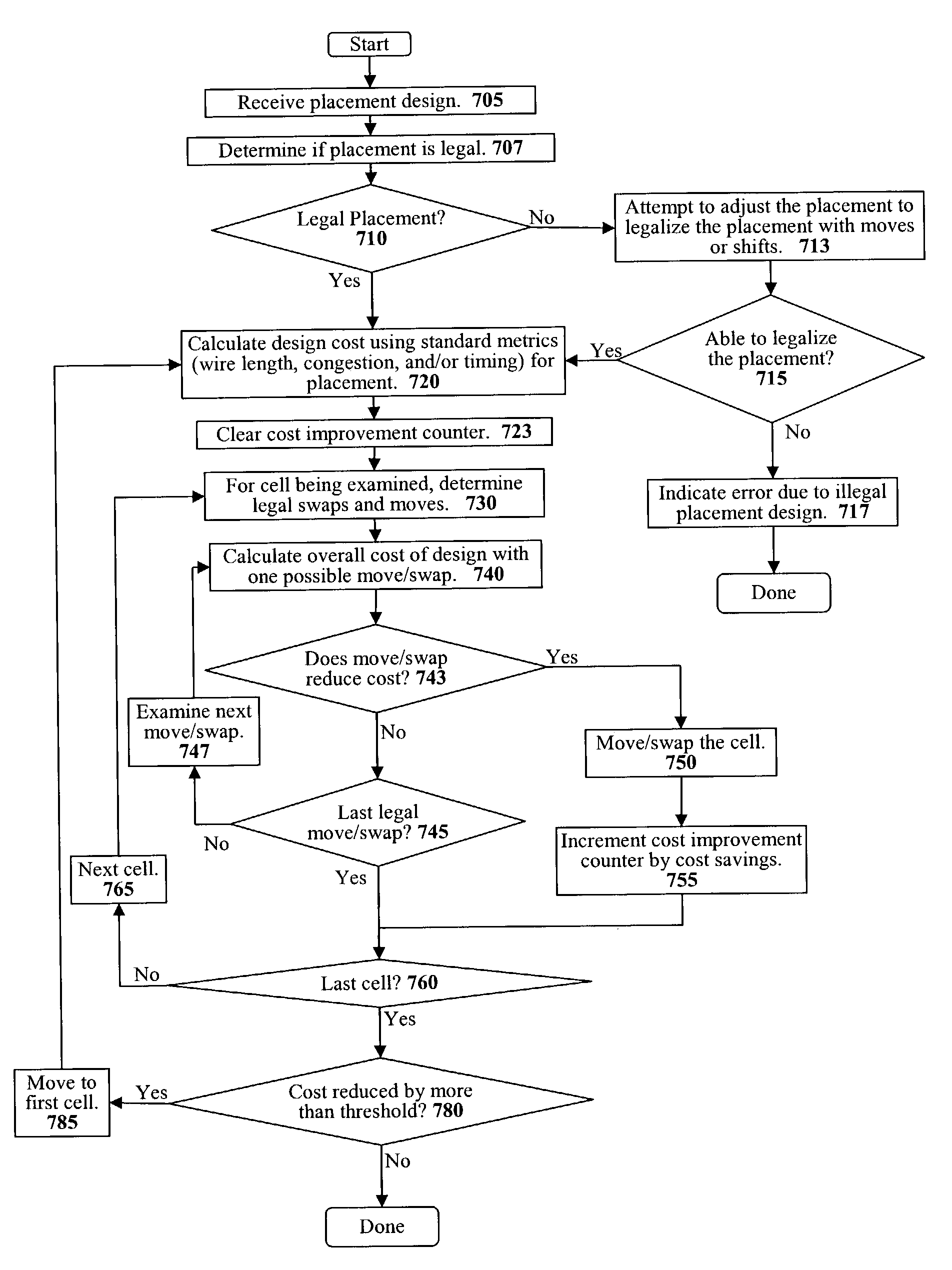

Post processor for optimizing manhattan integrated circuits placements into non manhattan placements

InactiveUS7013445B1Improve routing densityDie sizeComputer aided designSoftware simulation/interpretation/emulationPost processorFloor plan

The present invention introduces methods of creating floor plans and placements for non Manhattan integrated circuits with existing electronic design automation tools. To create a floor plan, an existing Manhattan based floor planning tool is used. The die size for the floor plan is reduced to take into account the improved wiring density of non Manhattan wiring. A non Manhattan global router is then used on the floor plan to create pin placements. The floor plan may create a floor plan having circuit modules with beveled corners to take advantage of diagonal wiring. To create a placement, an existing Manhattan based placer is first used to create an initial placement. The initial placement is then processed by a non Manhattan aware post processor. The post processor performs local optimizations on the initial placement to improve the placement for a non Manhattan routed integrated circuit.

Owner:CADENCE DESIGN SYST INC

Variability-Aware Asynchronous Scheme for High-Performance Delay Matching

InactiveUS20090119631A1Logic circuits characterised by logic functionPulse automatic controlMathematical modelComputer science

A system for automatically transforming a given synchronous circuit description into an equivalent and provably correct desynchronized circuit description. Included in the automated transformation are techniques for synthesizing a variability-aware controller using a two-phase protocol, techniques for synthesizing a variability-aware controller using gated clocks and testability circuits, techniques for synthesizing a variability-aware controller optimized for performance, techniques for initializing the synthesized controller, techniques for dynamically minimizing power requirements, and techniques for interfacing the desynchronized circuit with external synchronous circuits. Also disclosed are techniques for implementing a system for automatically transforming a synchronous circuit description into an equivalent and provably correct desynchronized circuit description within the context of an electronic design automation design flow. Exemplary circuits used in the application of the aforementioned techniques are provided. Application of mathematical models and techniques used for proving equivalence between the input description and the resulting desynchronized circuit are presented and explained.

Owner:CO INVERSION NEOTEC +1

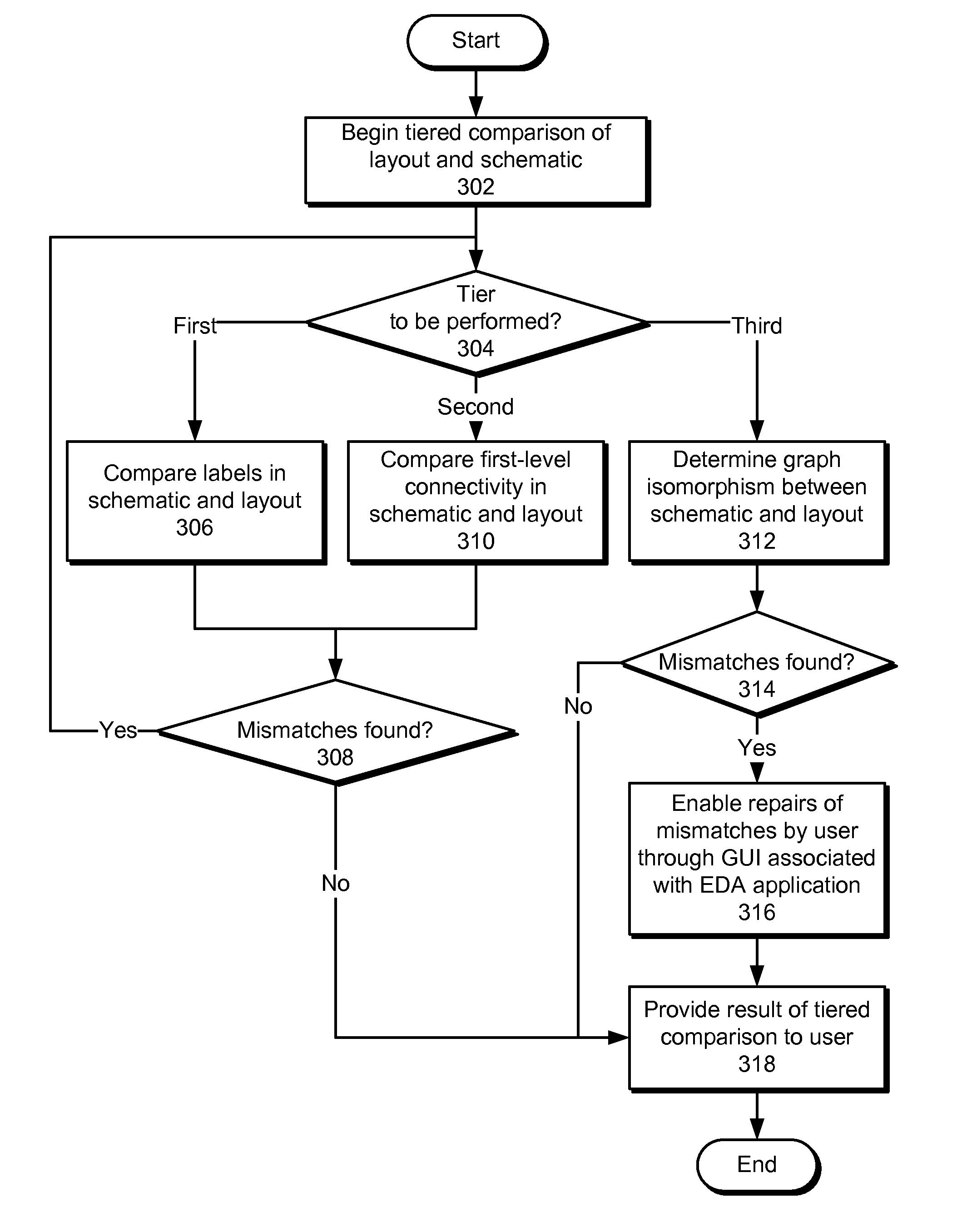

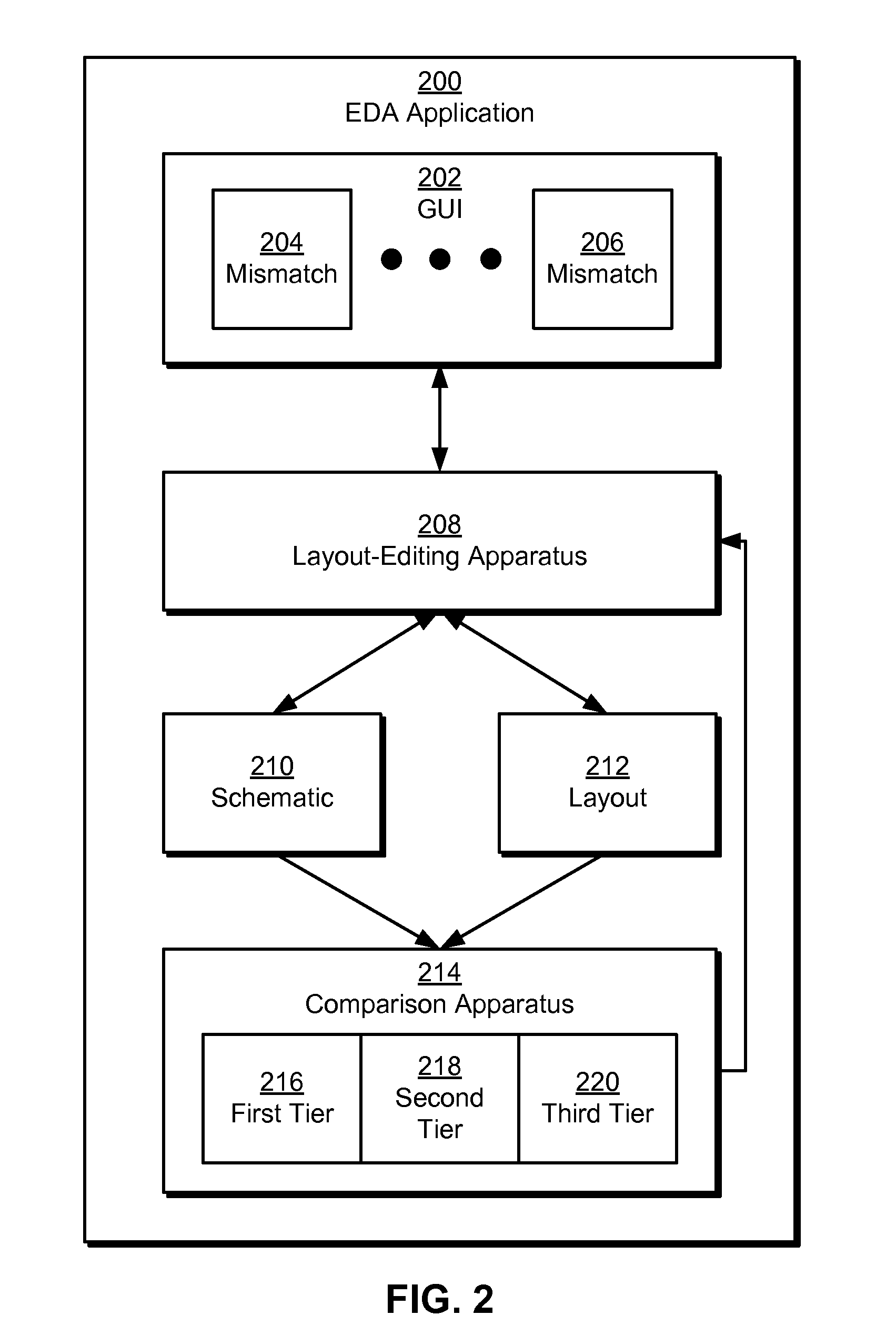

Tiered schematic-driven layout synchronization in electronic design automation

ActiveUS20110107281A1Easy to createComputer programmed simultaneously with data introductionSoftware simulation/interpretation/emulationGraphicsSchematic-driven layout

Some embodiments provide a system that facilitates the creation of a layout from a schematic in an electronic design automation (EDA) application. During operation, the system performs a tiered comparison of the schematic and the layout. The tiered comparison includes a first tier that compares labels in the schematic and the layout. The tiered comparison also includes a second tier that compares first-level connectivity in the schematic and the layout. The tiered comparison further includes a third tier that determines a graph isomorphism between the schematic and the layout. After the tiered comparison is completed, the system provides a result of the tiered comparison to a user of the EDA application. Finally, the system enables repairs of mismatches in the result by the user through a graphical user interface (GUI) associated with the EDA application.

Owner:SYNOPSYS INC

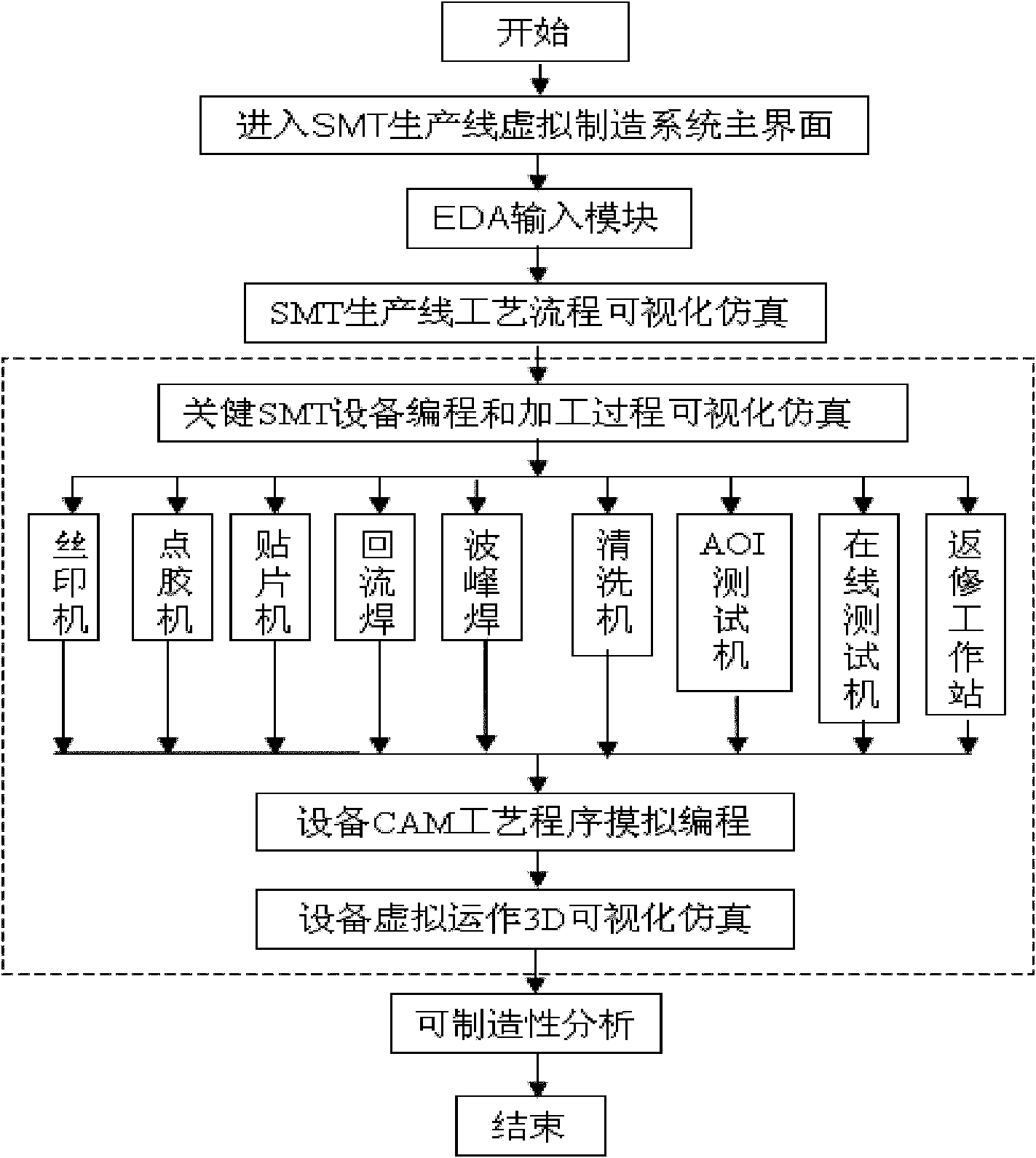

Electronic whole set surface mounting technology production line virtual manufacturing system and realization method thereof

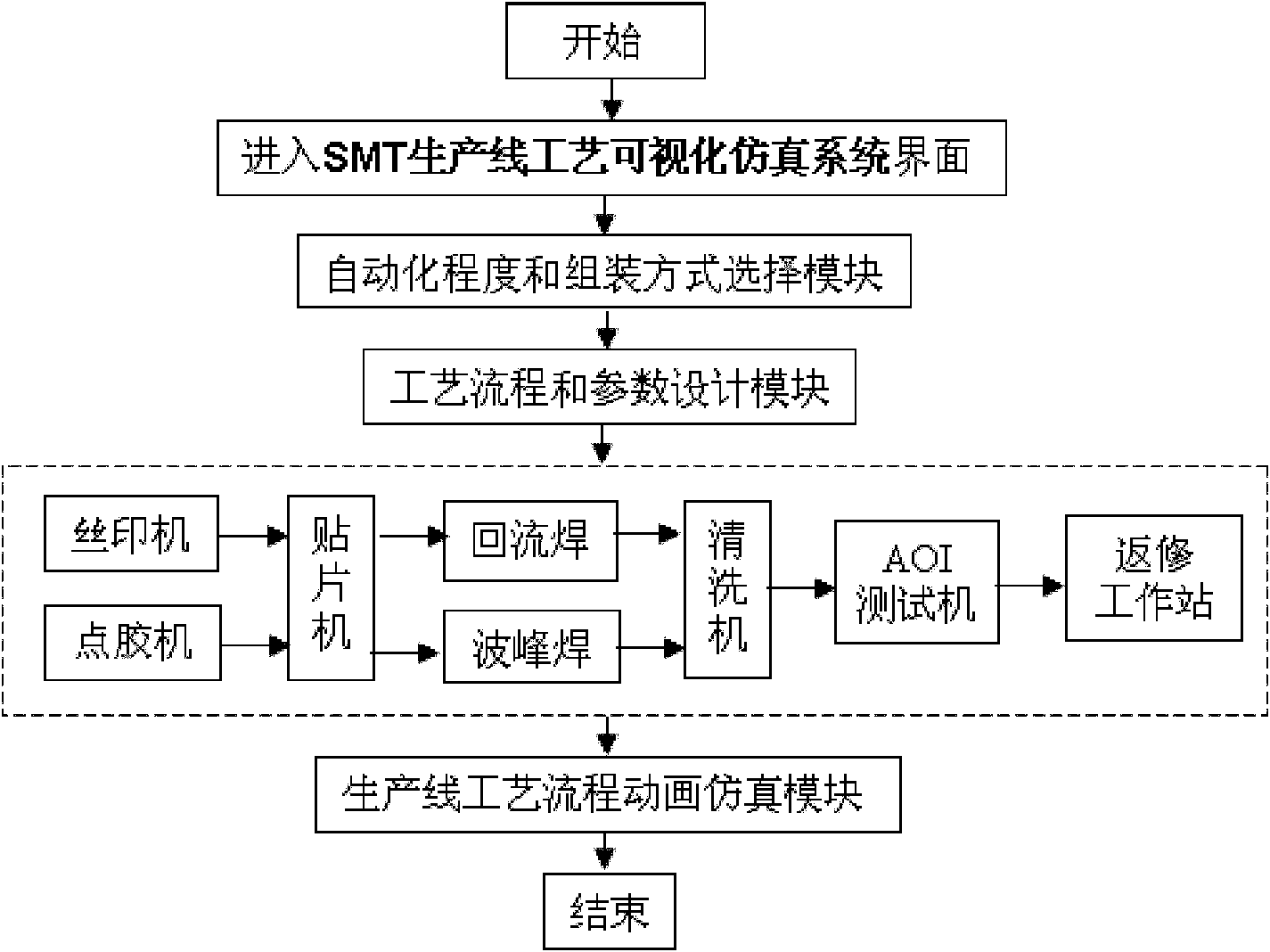

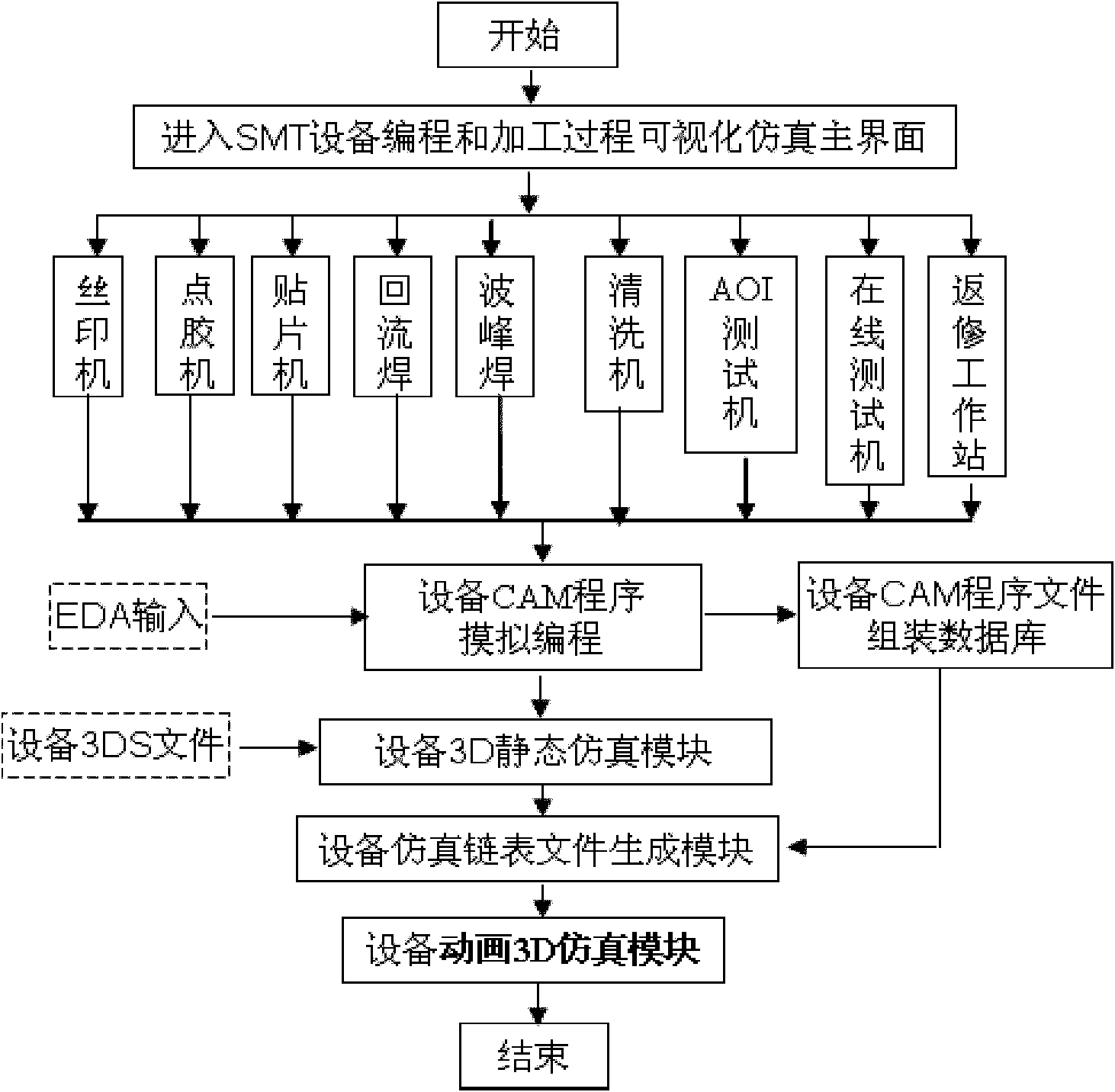

InactiveCN101986317ASave time and costSave production costSpecial data processing applicationsSurface-mount technology3d simulation

The invention relates to an electronic whole set surface mounting technology (SMT) production line virtual manufacturing system and a realization method thereof. The realization method comprises the following steps: according to the assembly mode and the degree of automation, the process flow and parameters of the SMT production line are designed, a three-dimensional (3D) animation is used to display the process flow of the SMT production line; the electronic design automation (EDA) design file is read, the simulation programming of the key equipment of the mainstream machine in market is performed, then the data are input in an assembly database; the object oriented technology and the OpenGL technology are adopted to perform the 3D simulation of the working process of the SMT key equipment under the VC++ 6.0 environment; and manufacturability analysis can also be performed automatically. By adopting the method of the invention, the visual basis can be provided for the data modification of the program design of the SMT production line and the key equipment in the shortest time, thus the aims of short development cycle, low cost and high production efficiency can be achieved.

Owner:CHANGZHOU AUTOSMT INFORMATION TECH

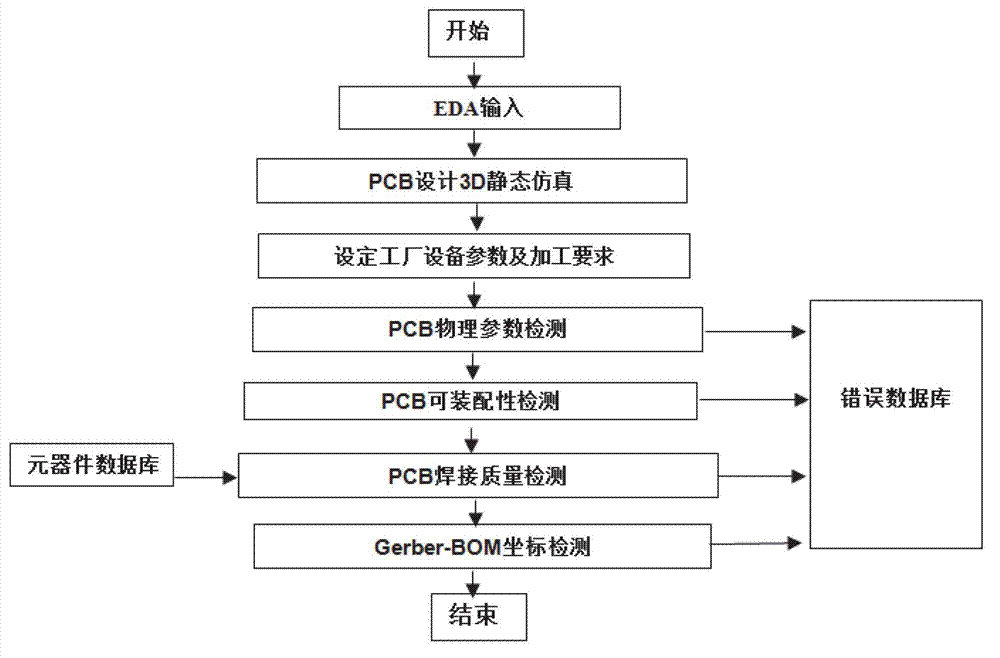

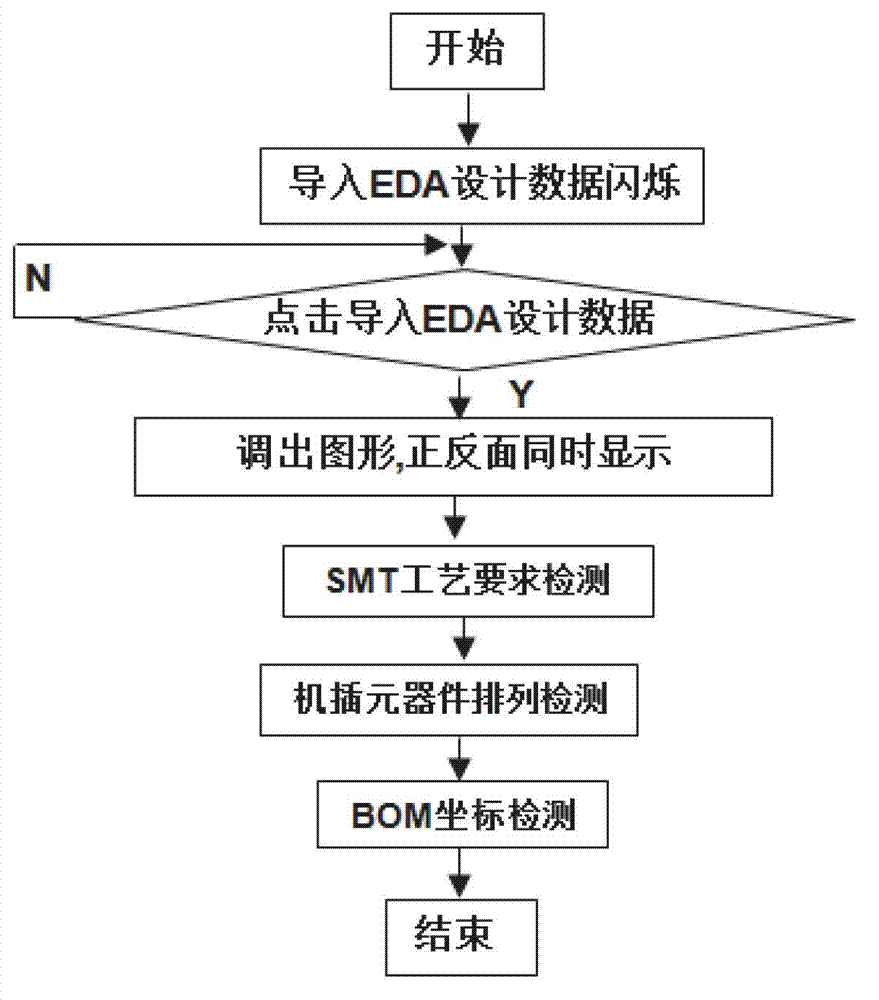

Visualization detection method of electronic product electronic design automation (EAD) design manufacturability

ActiveCN102930114AImprove efficiencyQuality improvementSpecial data processing applicationsInformation processingGraphics

The invention discloses a visualization detection method of electronic product electronic design automation (EDA) design manufacturability. Printed circuit board (PCB) three dimensional (3D) simulation of an EDA design document is conducted, PCBphysical parameter detection, PCB assembling ability, PCB welding quality detection and Gerber bill of material (BOM) coordinate detection are conducted in sequence, and specific error positions and types of former four steps of detection are displayed in visualization mode on a PCB 3D figure. On the basic of complete actual production experiences, the visualization detection method and a system of the EAD design manufacturability are developed according to international standard of information processing center (IPC), the PCB physical parameter detection, the PCB assembling ability, the PCB welding quality detection and the gerber BOM coordinate detection which are all designed by EDA are integrated, the various actual problems which are the contradictions of manufacture and design of PCB and are faced by enterprises are resolved, and efficiency and quality of electronic manufacture in particular to an original equipment manufacturer (OEM) are improved.

Owner:CHANGZHOU AUTOSMT INFORMATION TECH