Patents

Literature

39 results about "Library design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

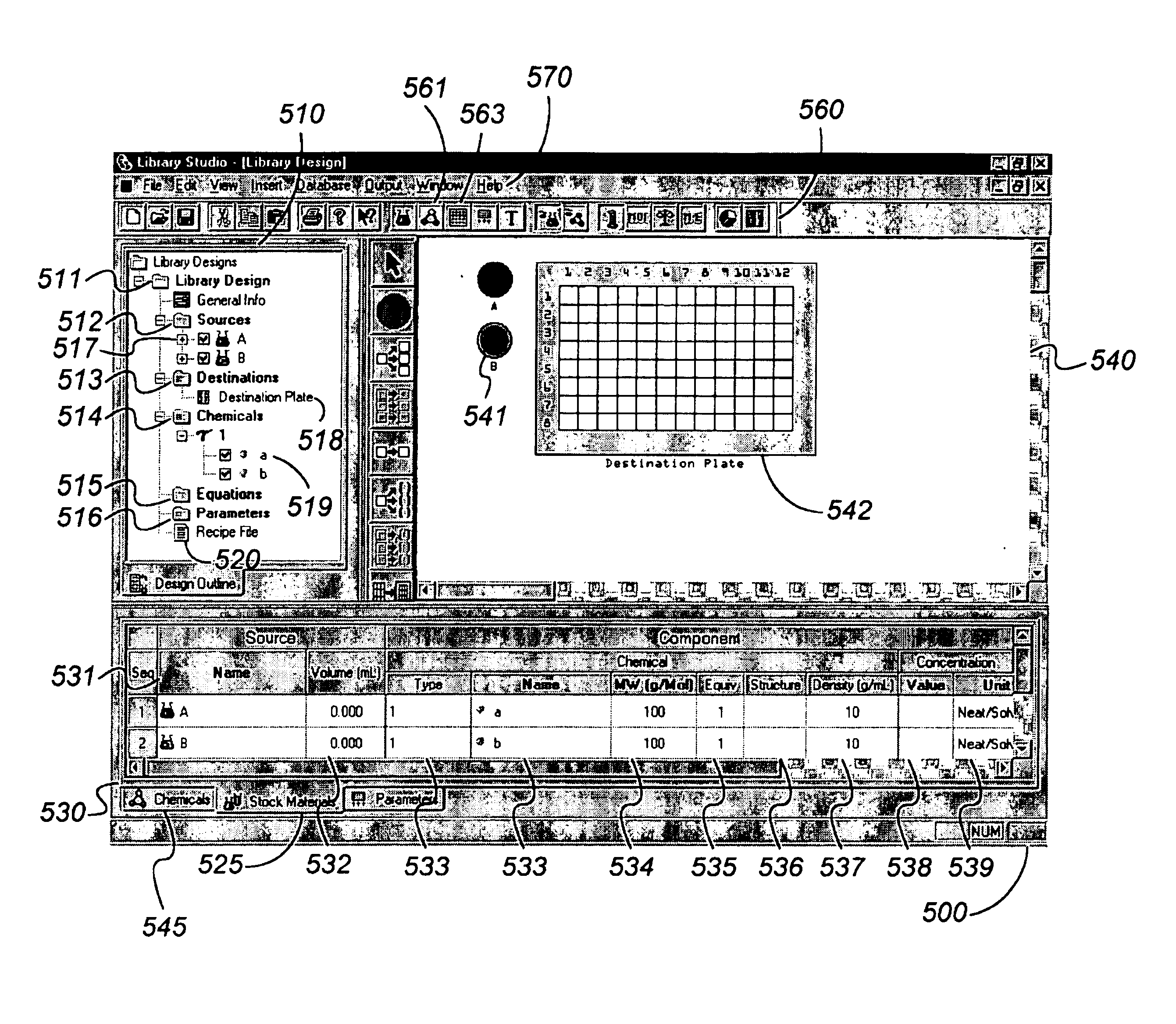

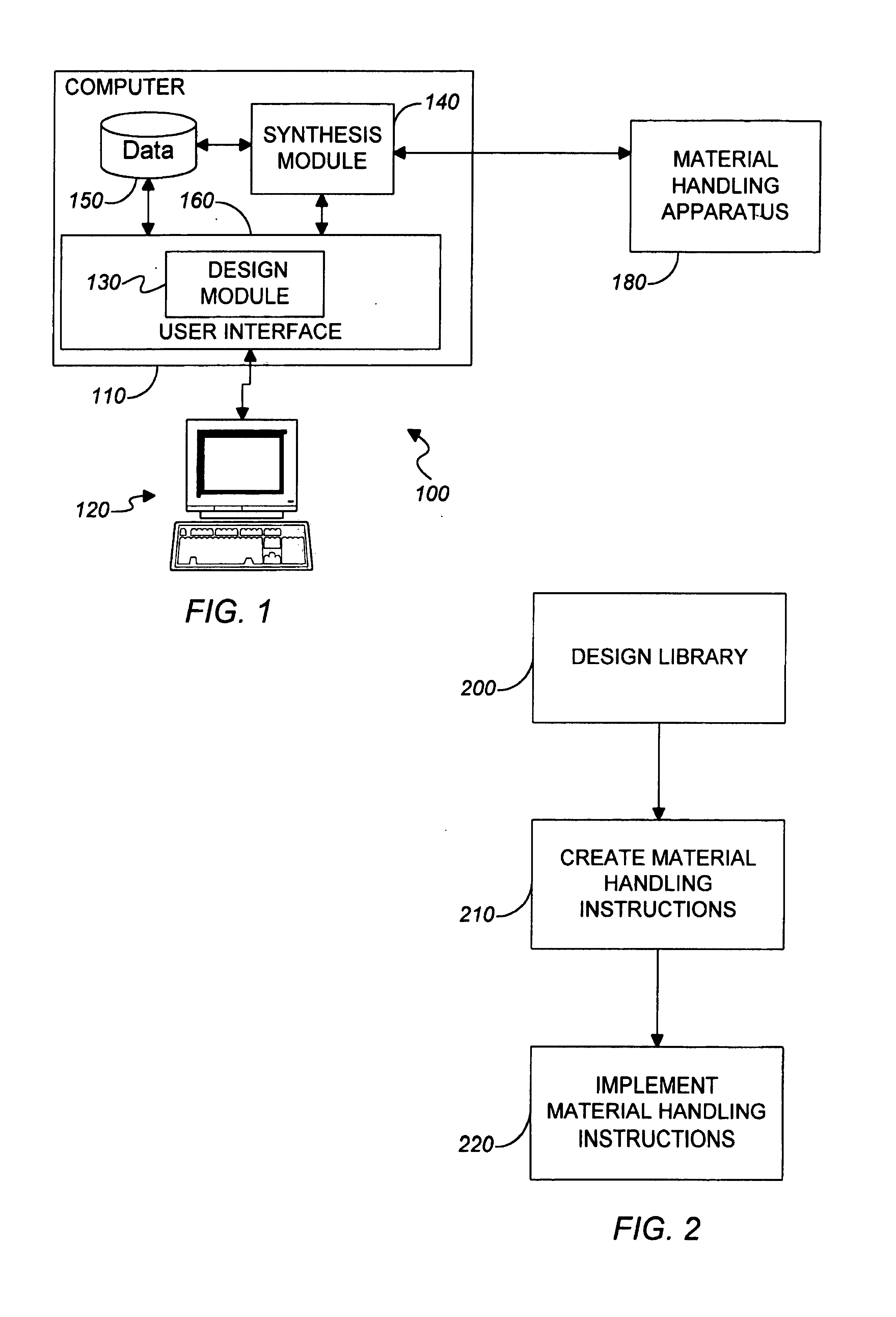

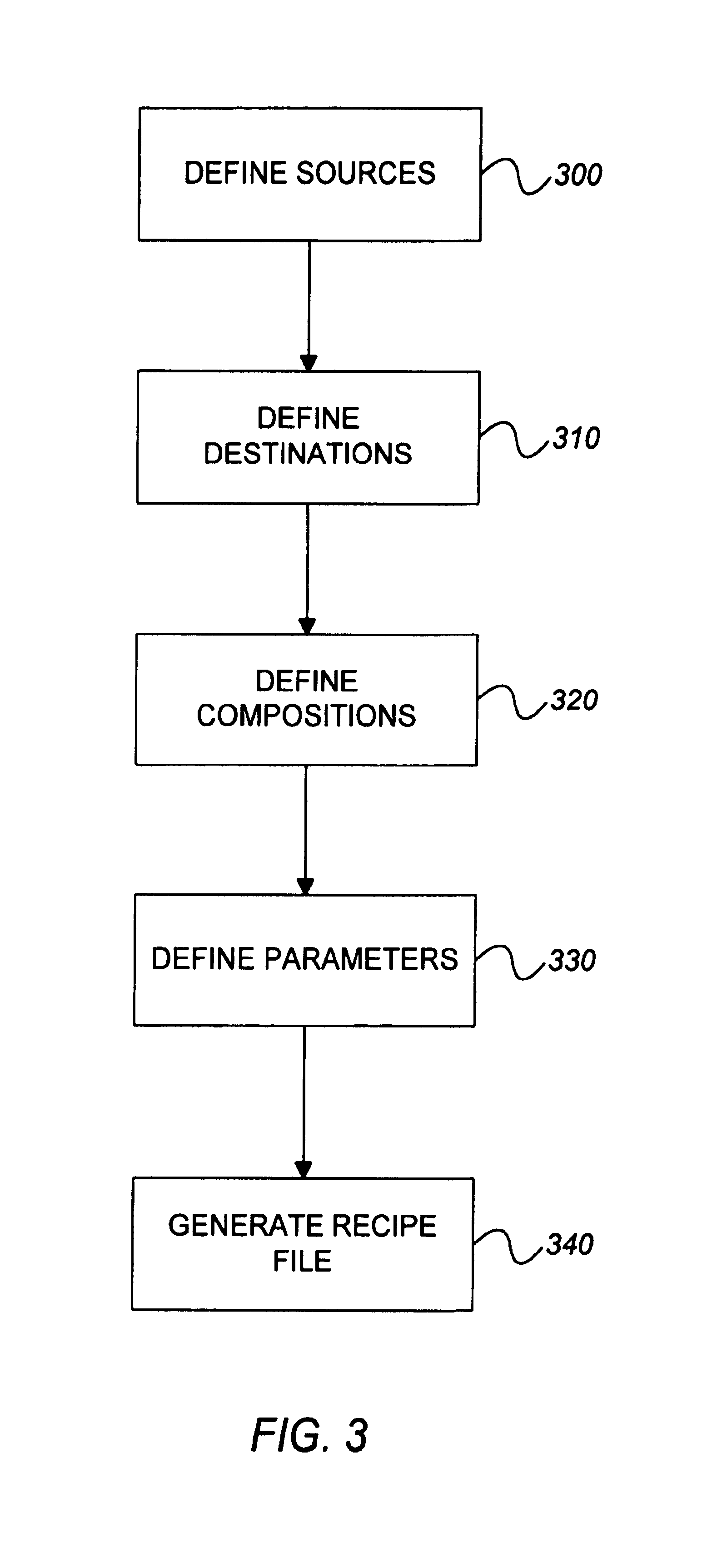

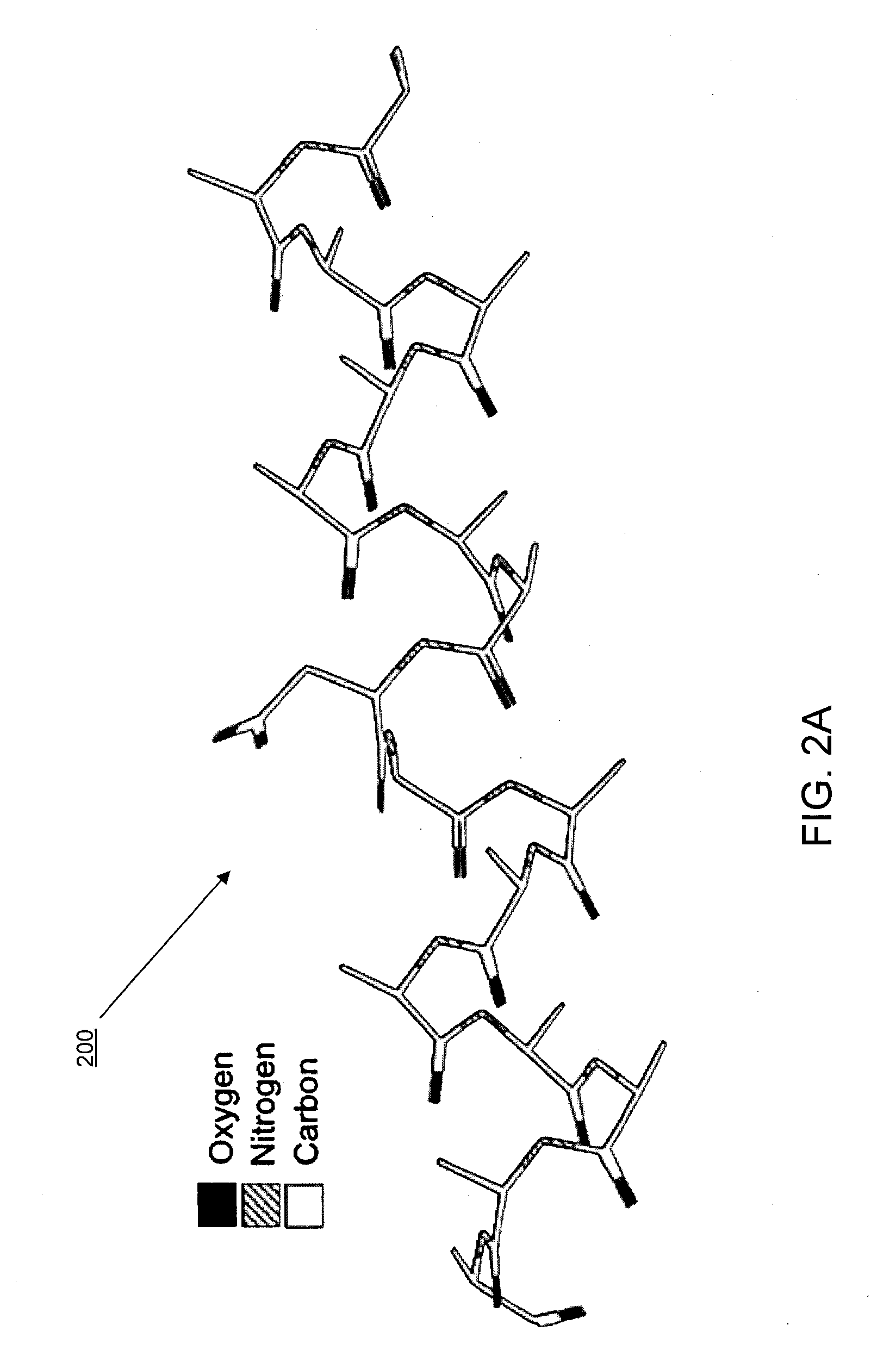

Graphic design of combinatorial material libraries

InactiveUS7199809B1Flexible definitionSpeed up library designOrganic chemistry methodsLibrary screeningGraphicsData file

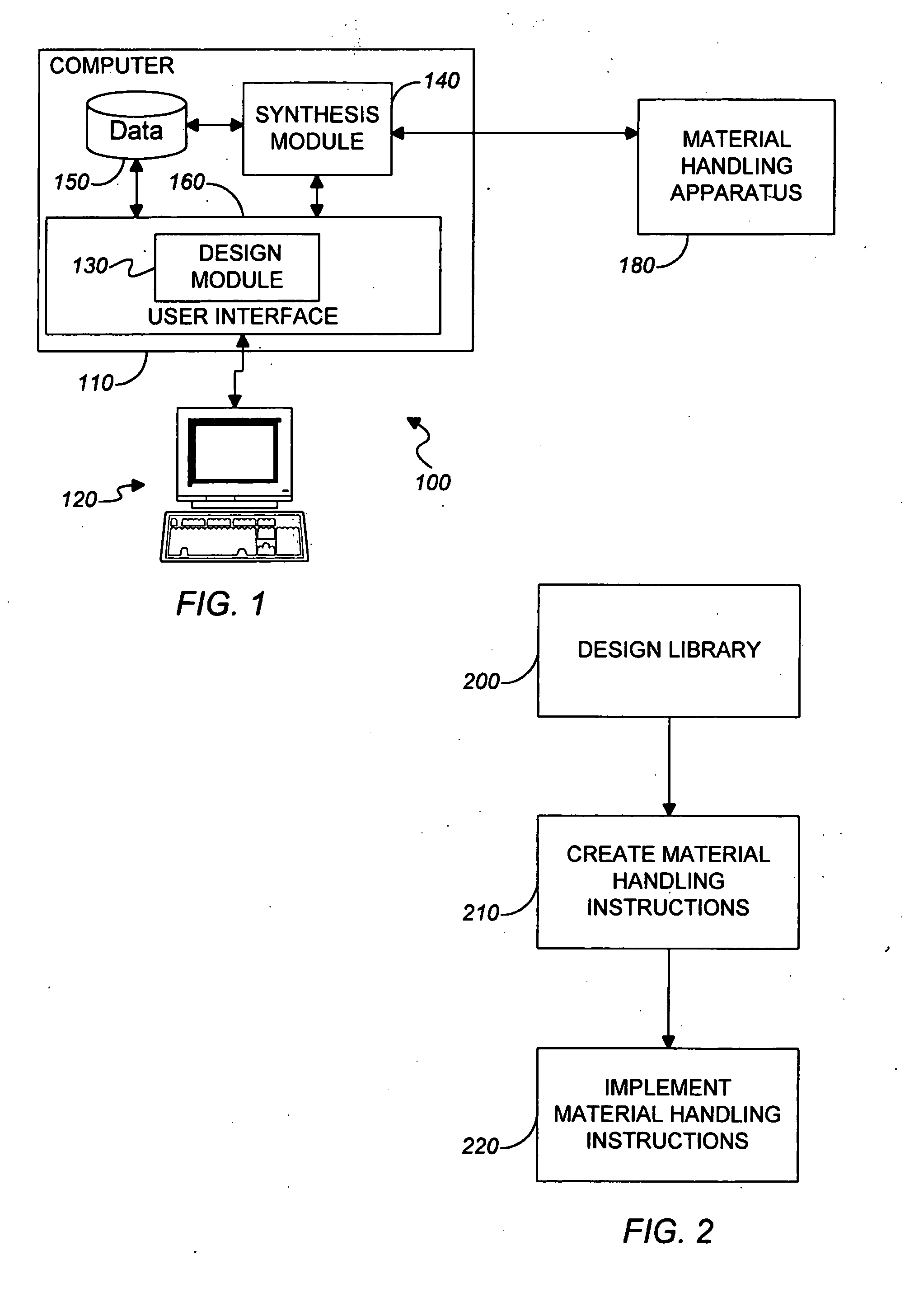

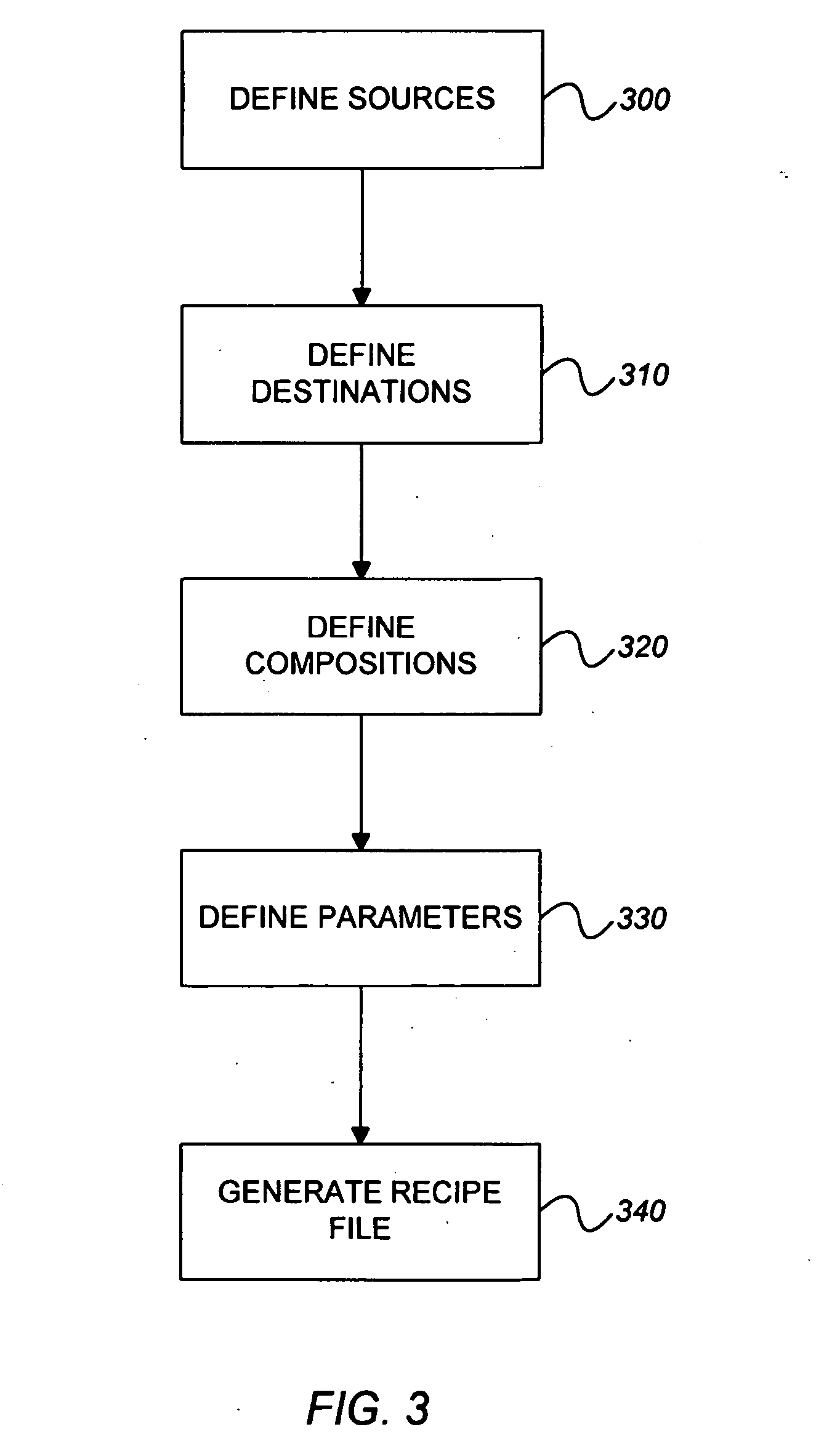

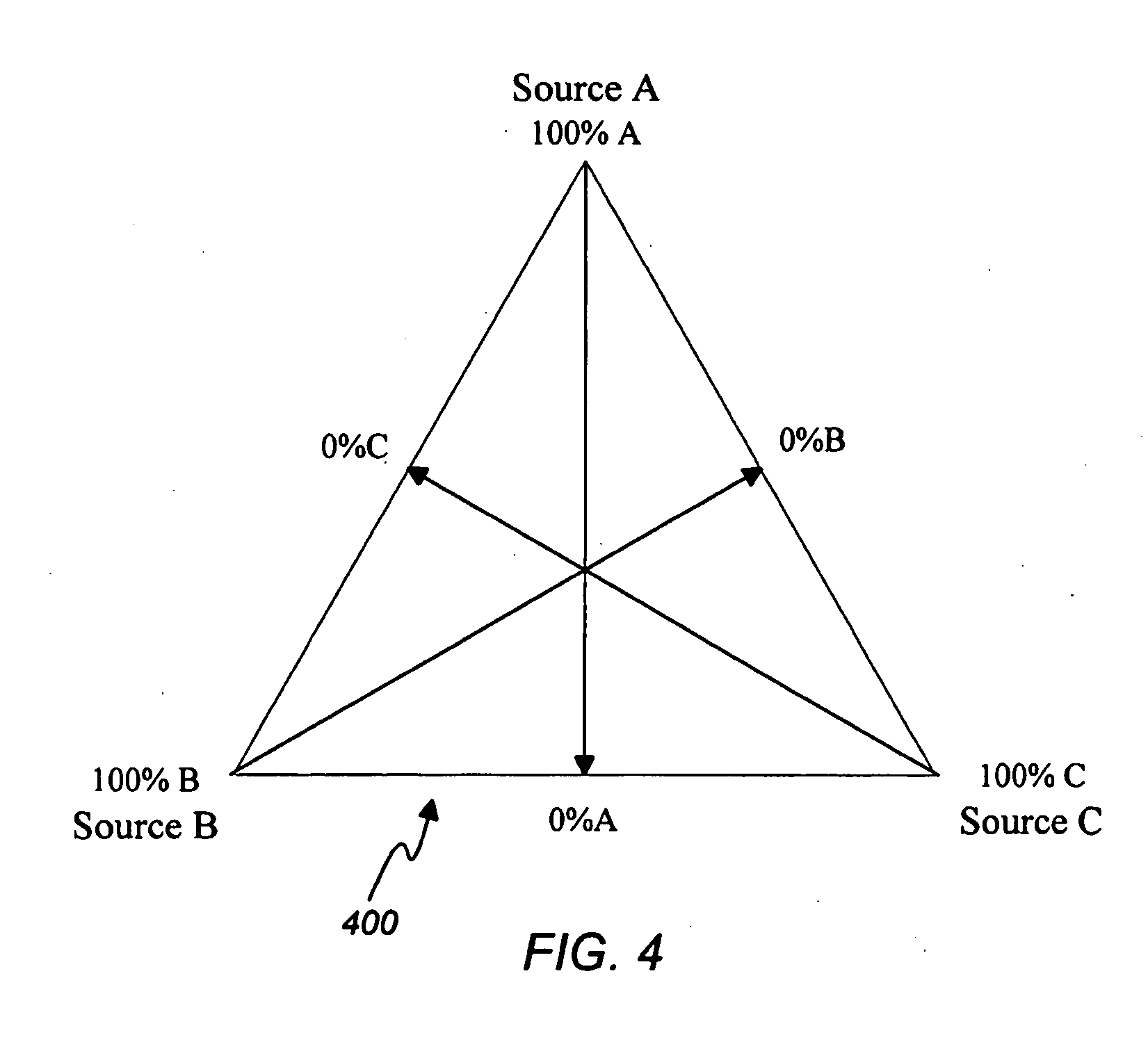

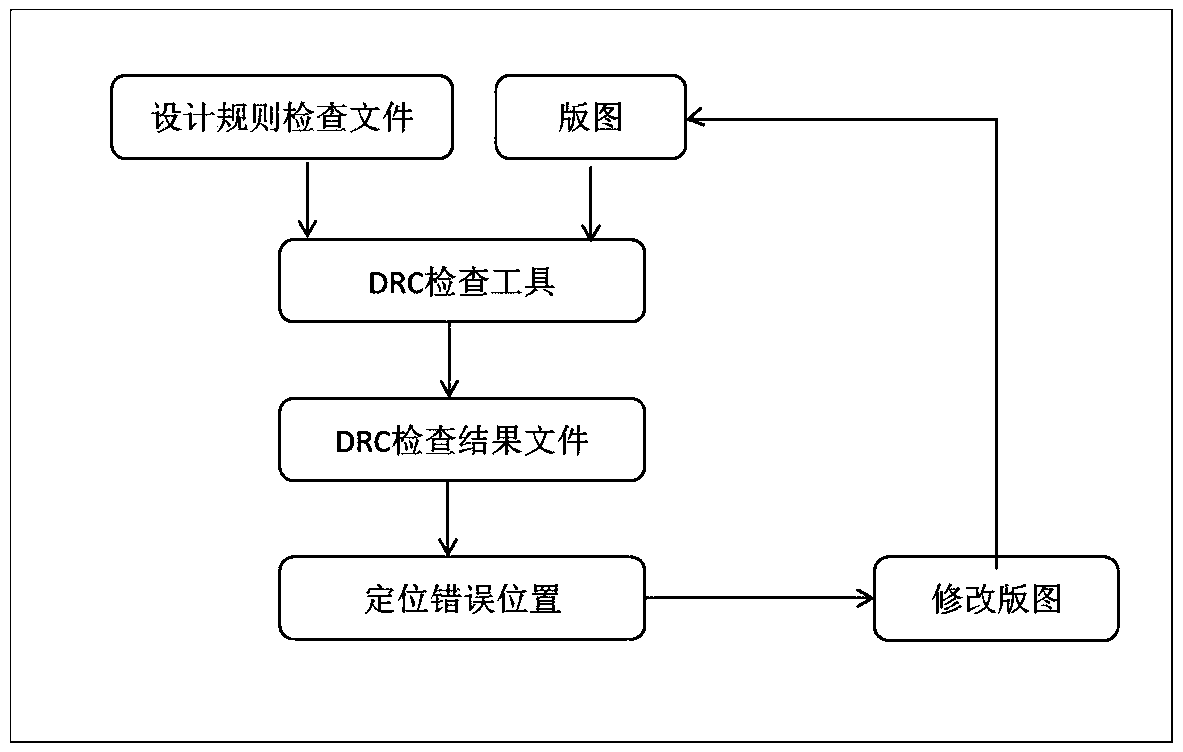

Computer-implemented methods, programs and apparatus for generating a library design for a combinatorial library of materials. A library design includes a set of sources representing components to be used in preparing the combinatorial library, destinations replying arrangements of cells and mappings, defining one or more distribution patterns for assigning components to cells in the destination arrangement or arrangements. Mappings include gradients and sets of user-defined equations, and are used to calculate the amount of on components to be assigned to a cell or cells in an arrangement. A library design can also include one or more process parameters defined to vary over time or across a plurality of destination cells. The invention outputs a data file defining the library design, including electronic data representing the sources, the destinations and the mapping, in a format suitable for implementing manually or using automated material handling apparatus.

Owner:UNCHAINED LABS

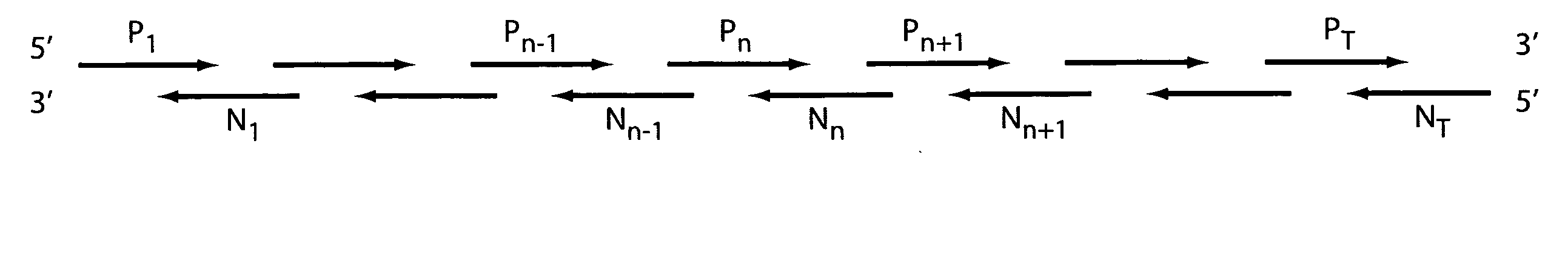

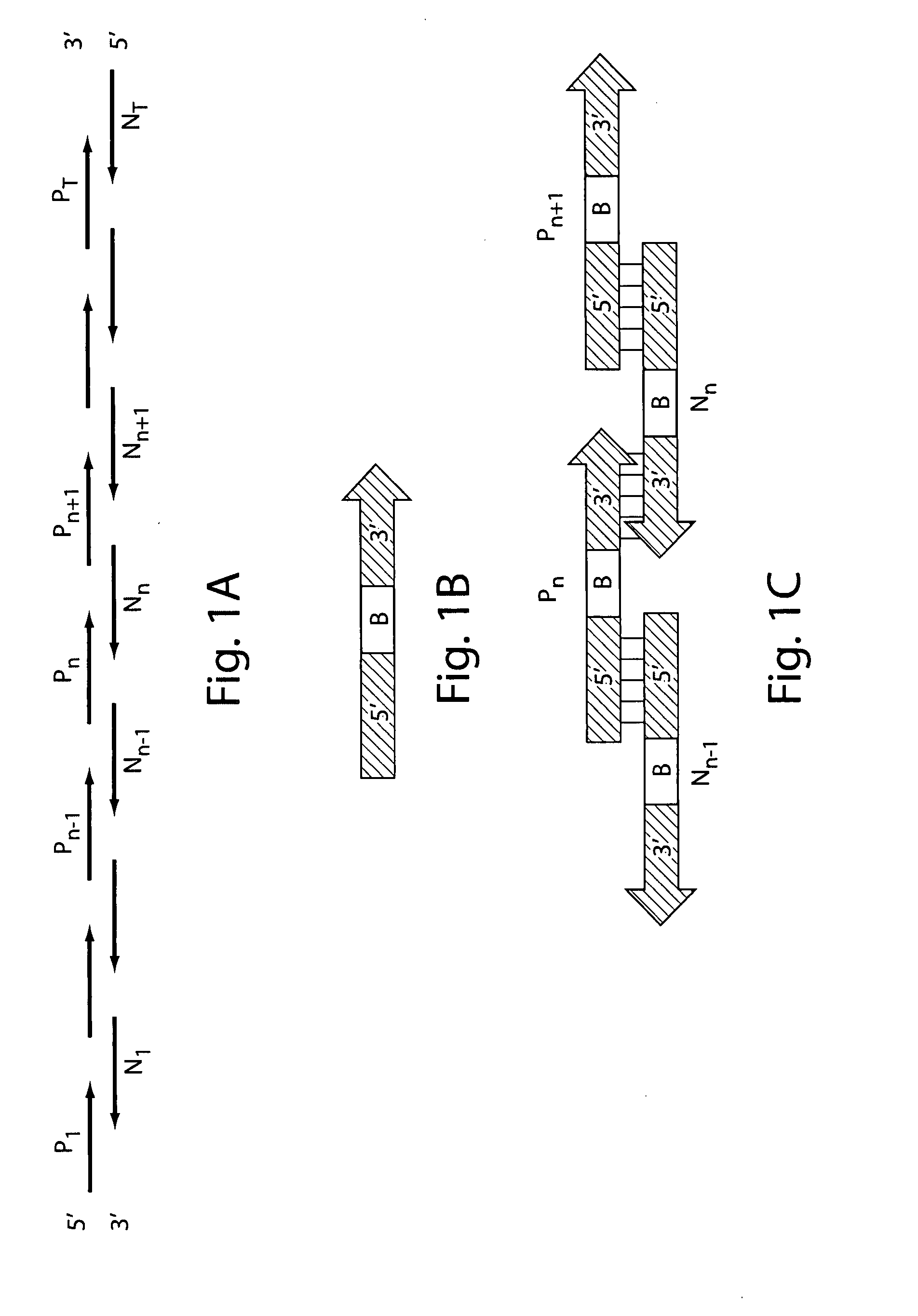

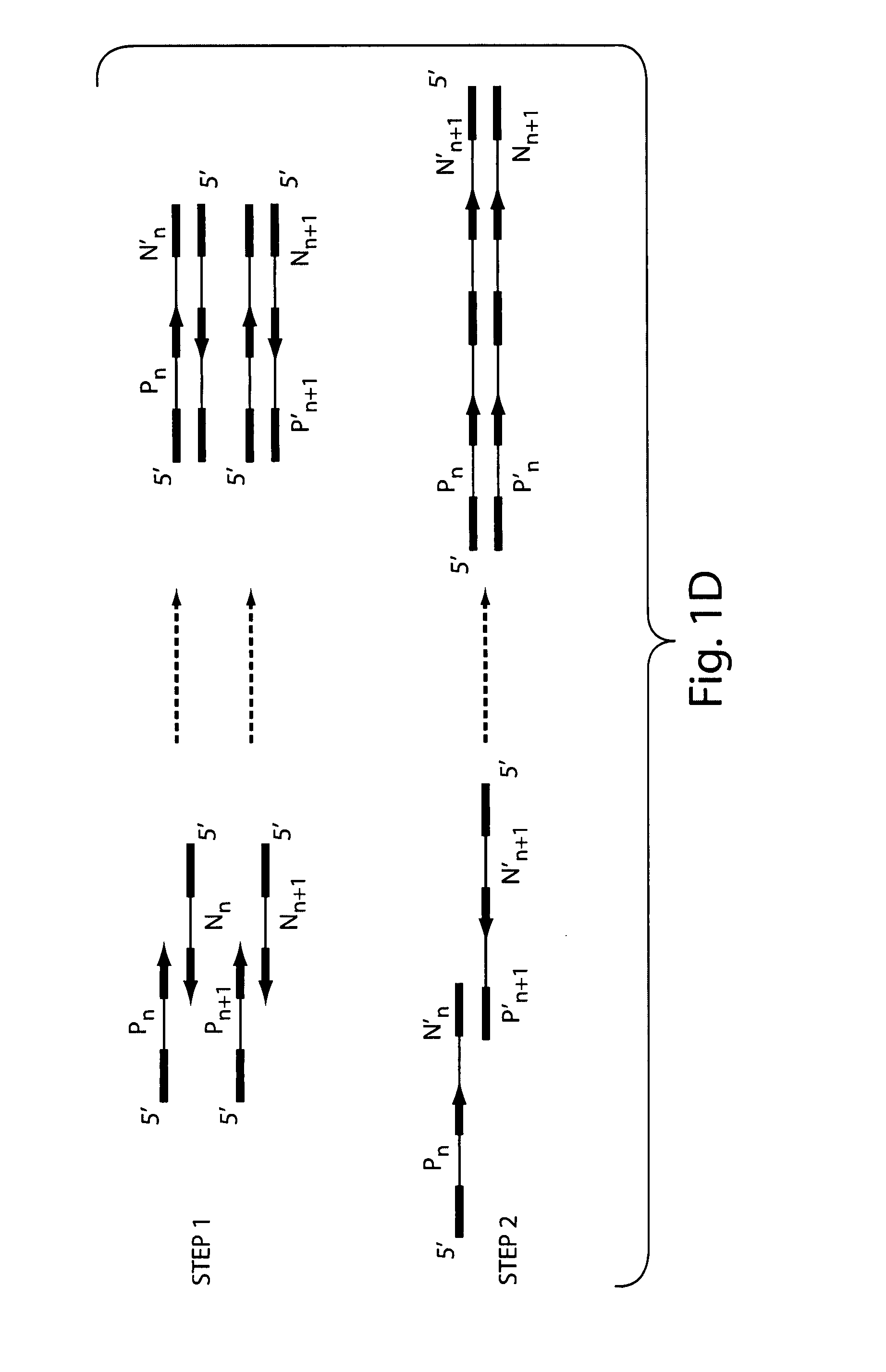

Nucleic acid library design and assembly

InactiveUS20080064610A1Reduce solubilityImproving immunogenicityVector-based foreign material introductionLibrary creationSolubilityENCODE

Owner:CODON DEVICES

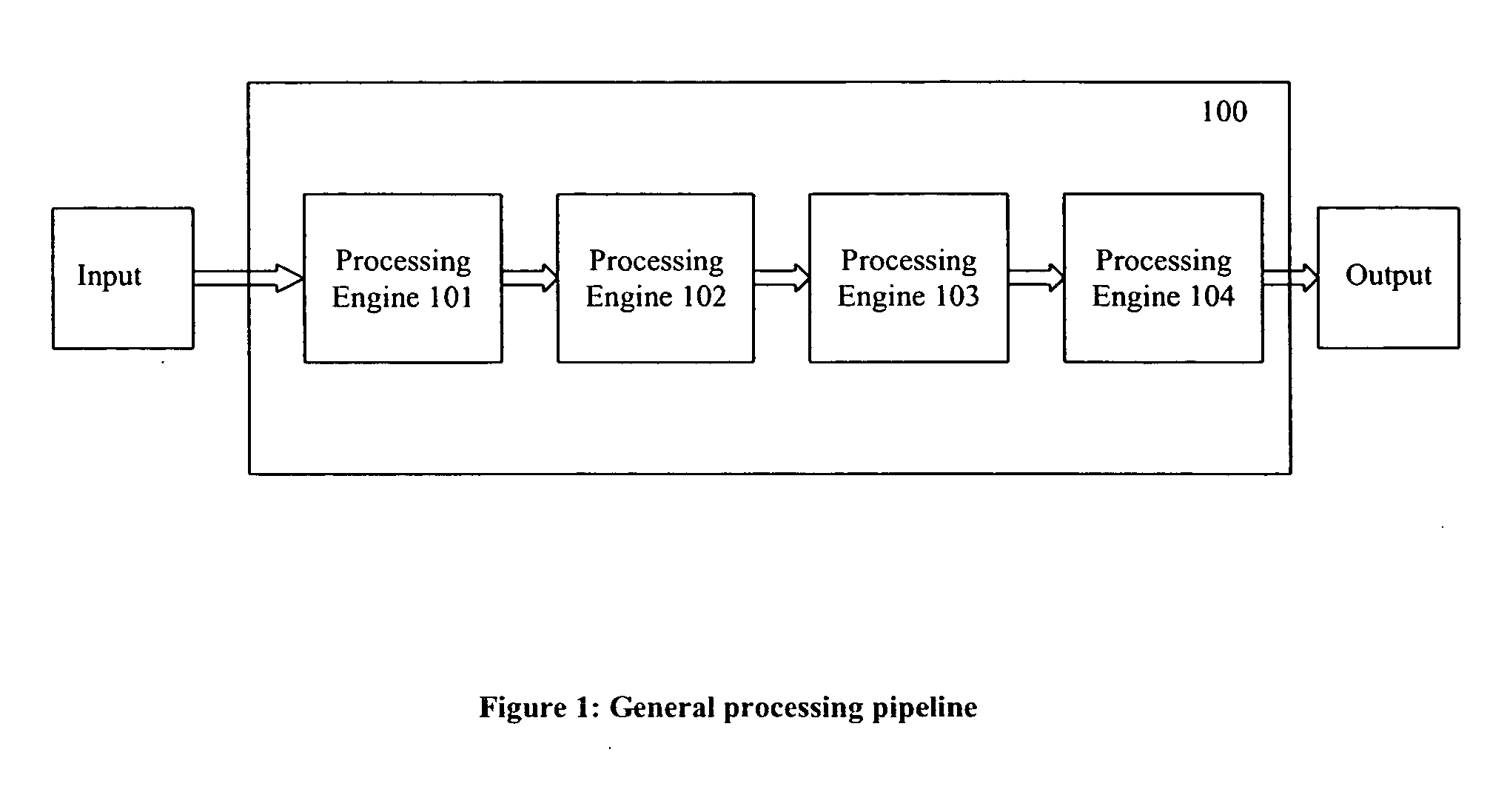

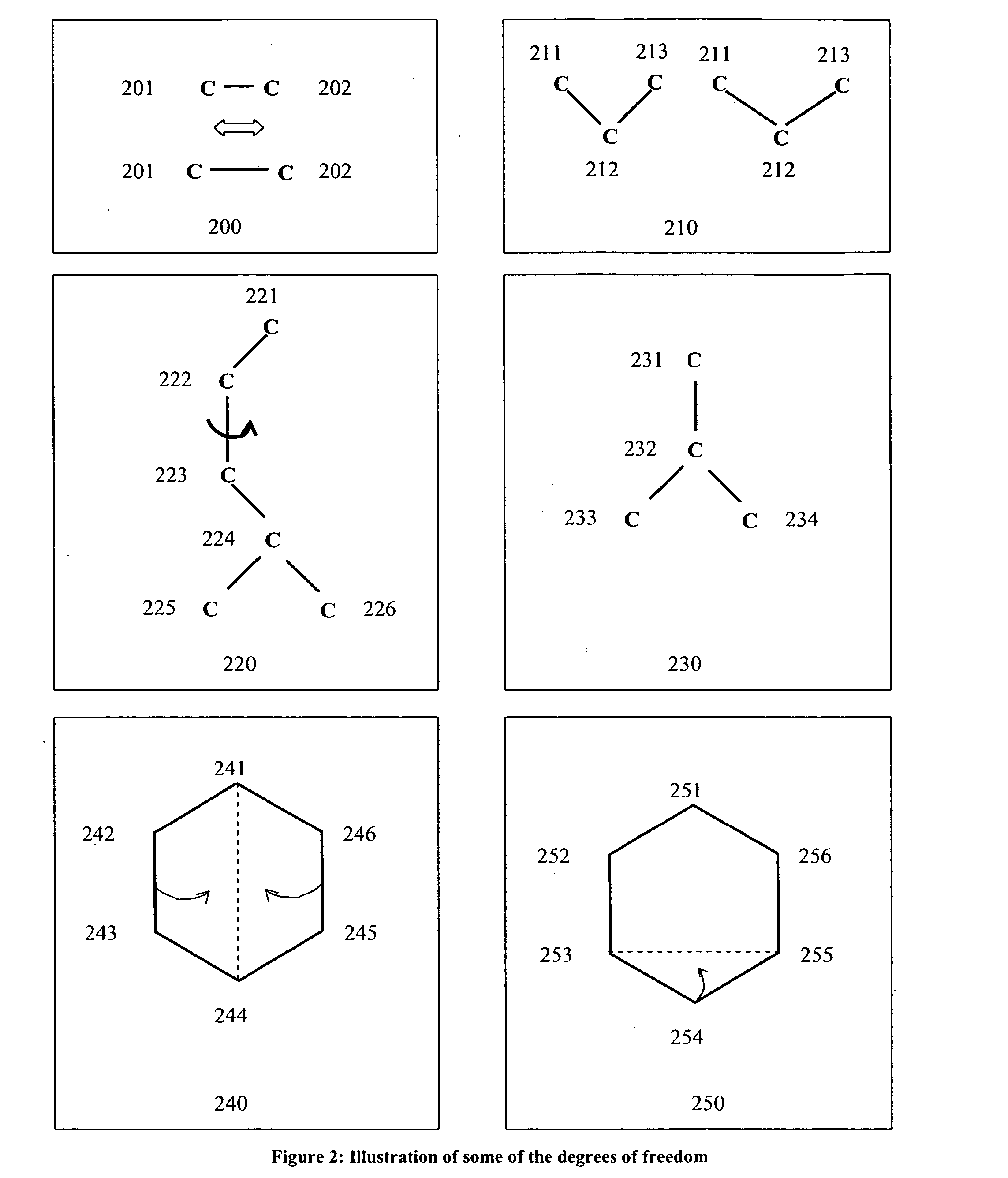

Method and device for partitioning a molecule

ActiveUS20050228592A1Efficient and fast transmissionWide range of usesMolecular designDigital data processing detailsComputer scienceDrug discovery

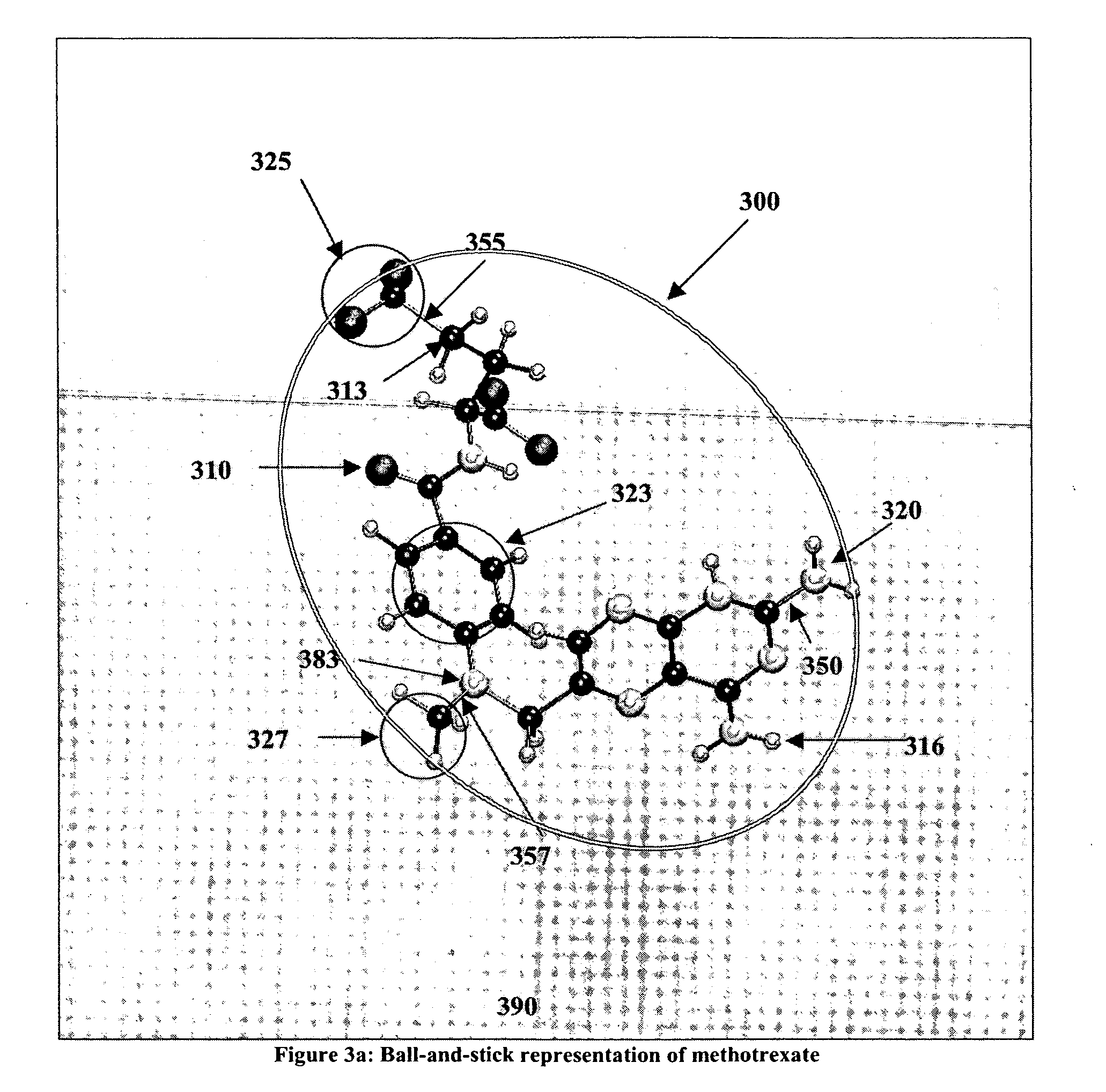

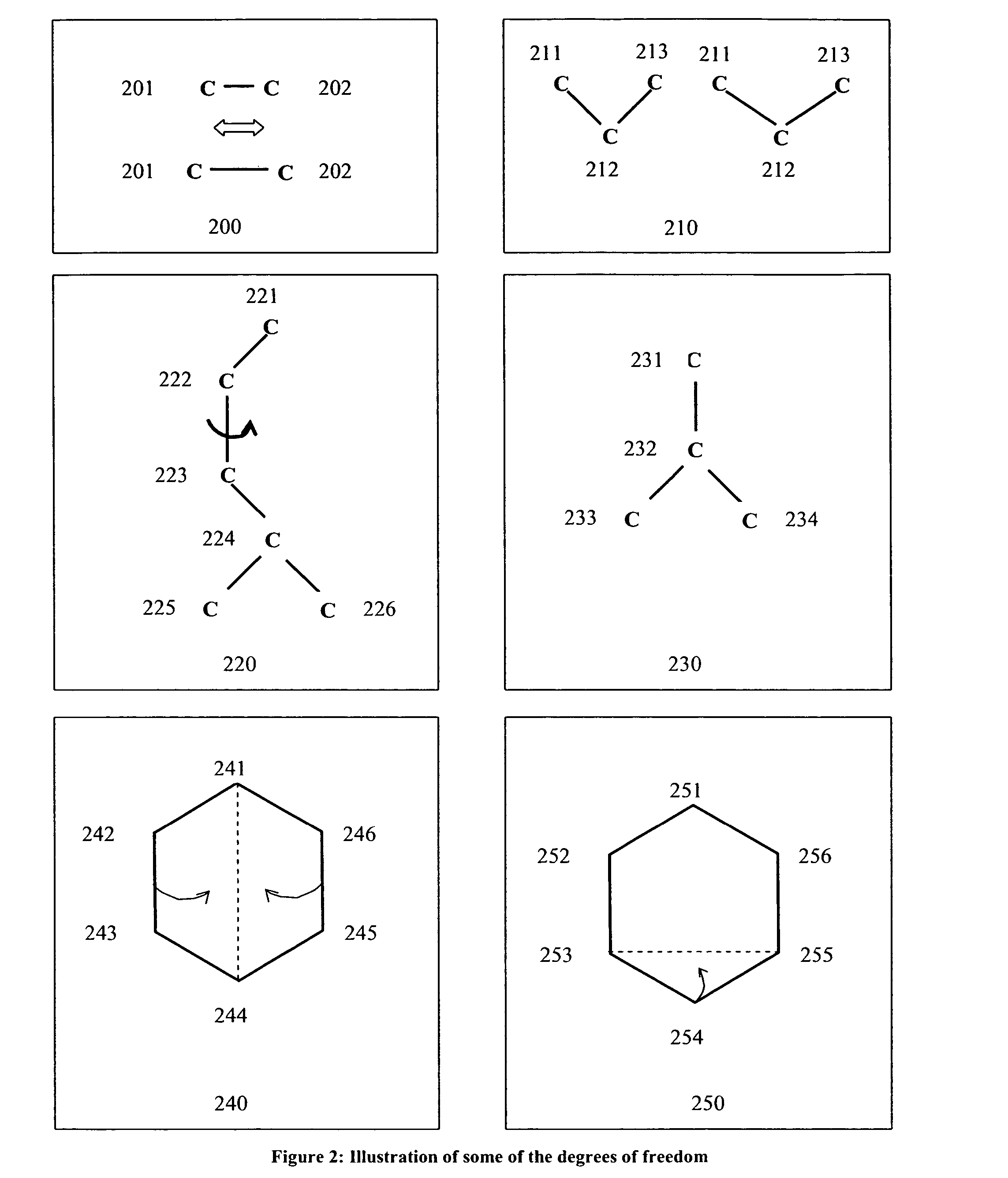

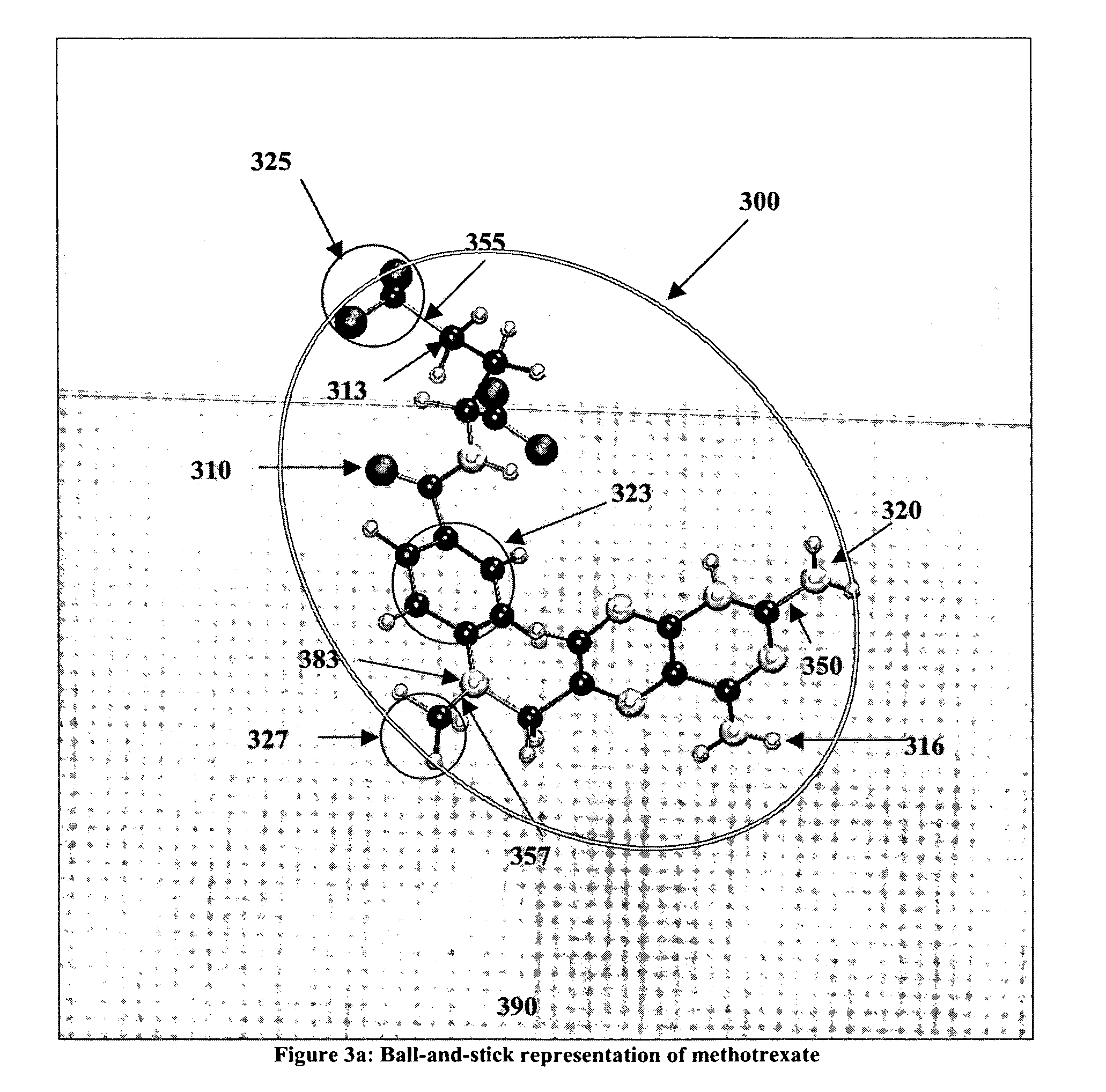

A method for partitioning a molecular subset is described. The partitioning method takes into account molecular structure and its manner of storage and transmission, transformations to be applied to the molecular subset and their implementation, and constraints imposed by the implementation of the partitioning method. Using this method, a molecular subset can be stored, transmitted, and processed more efficiently. The resulting efficiency makes it possible to design and run applications which require complex molecular processing, such as rational drug discovery, virtual library design, etc.

Owner:VERSEON INT CORP

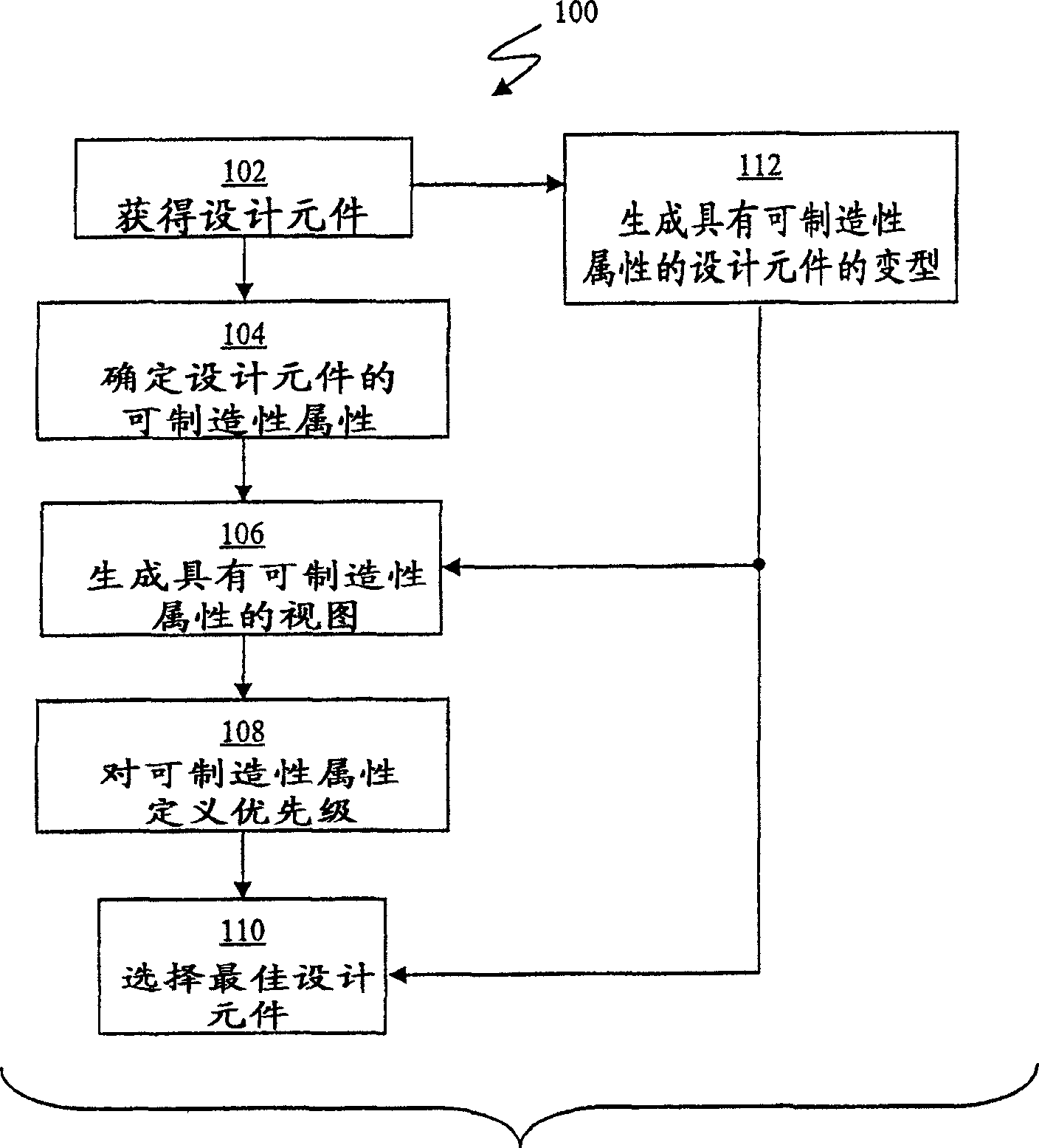

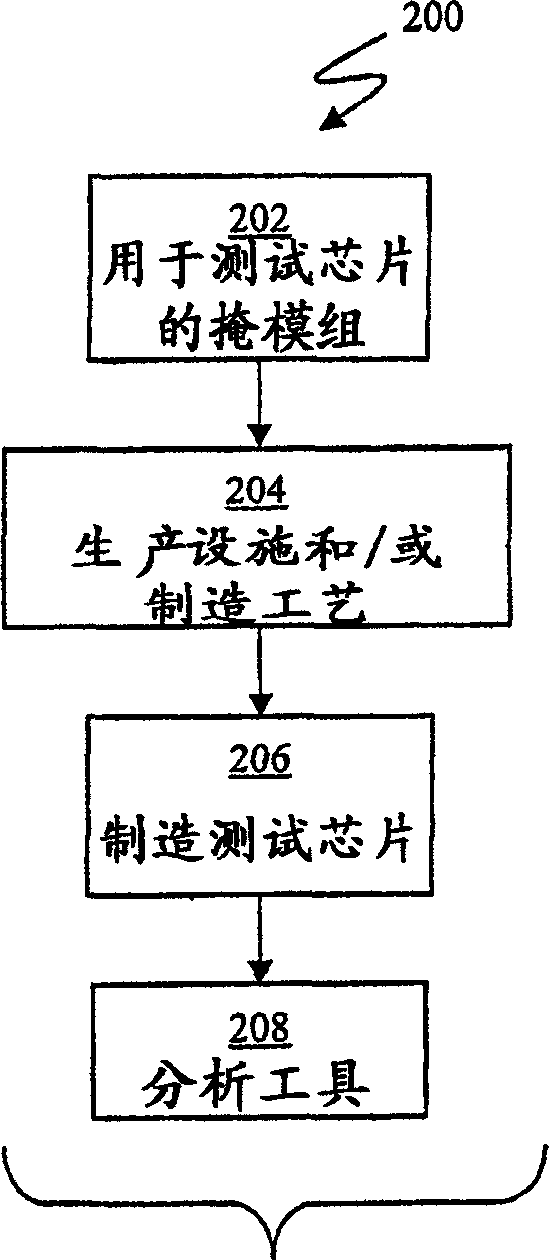

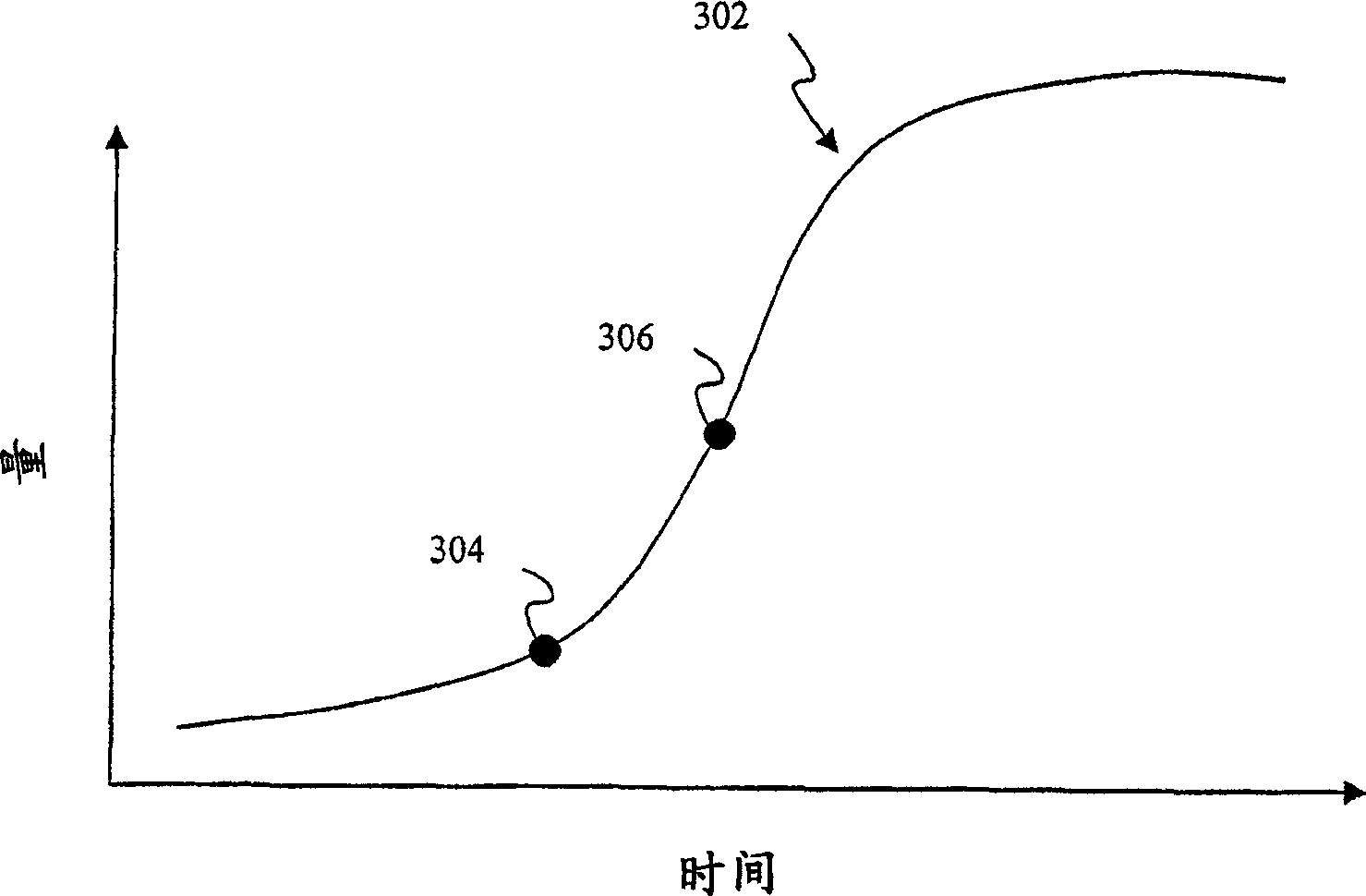

Integrated circuit design to optimize manufacturability

InactiveUS20060253810A1CAD circuit designSpecial data processing applicationsEngineeringElectronic design automation

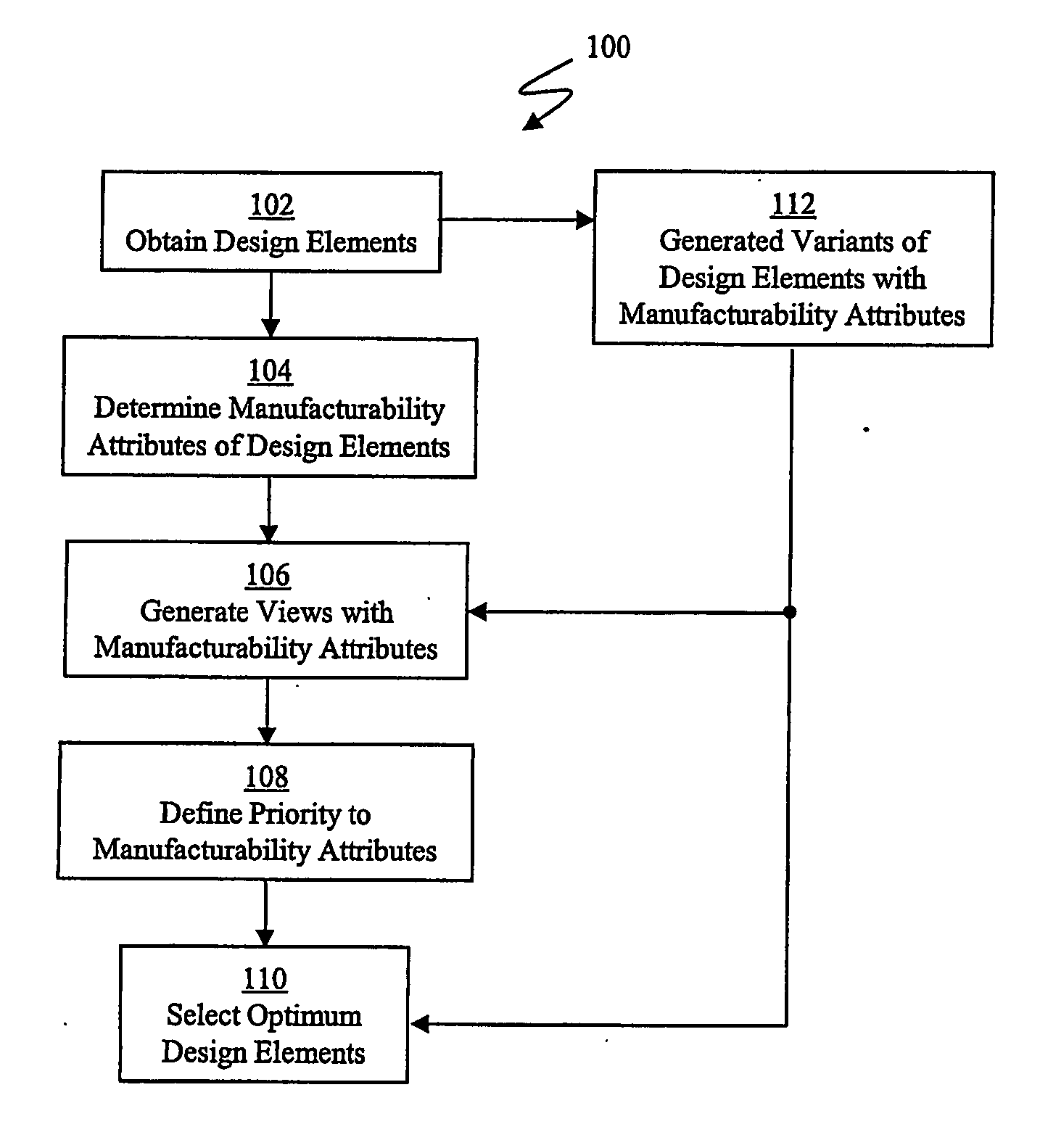

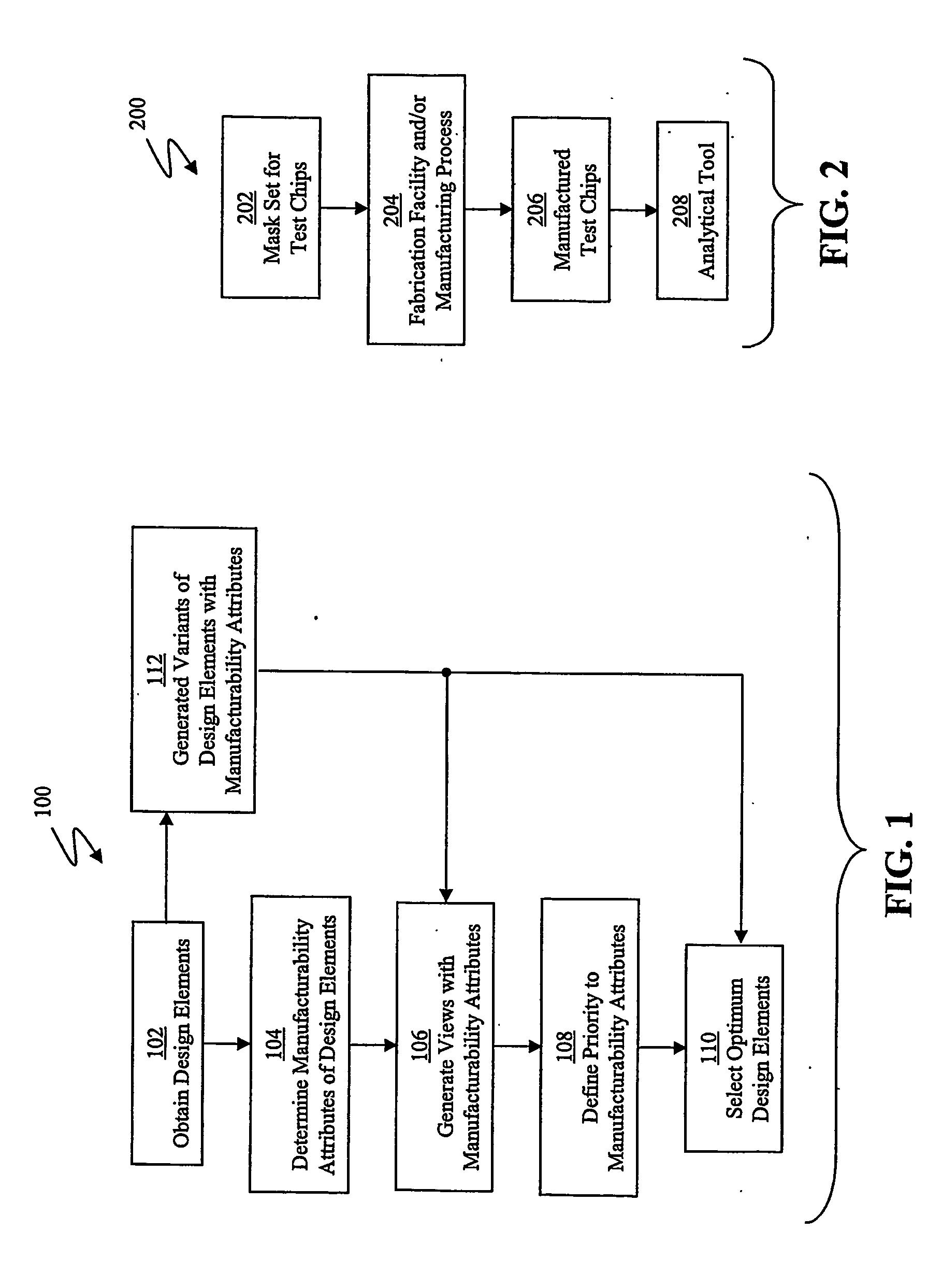

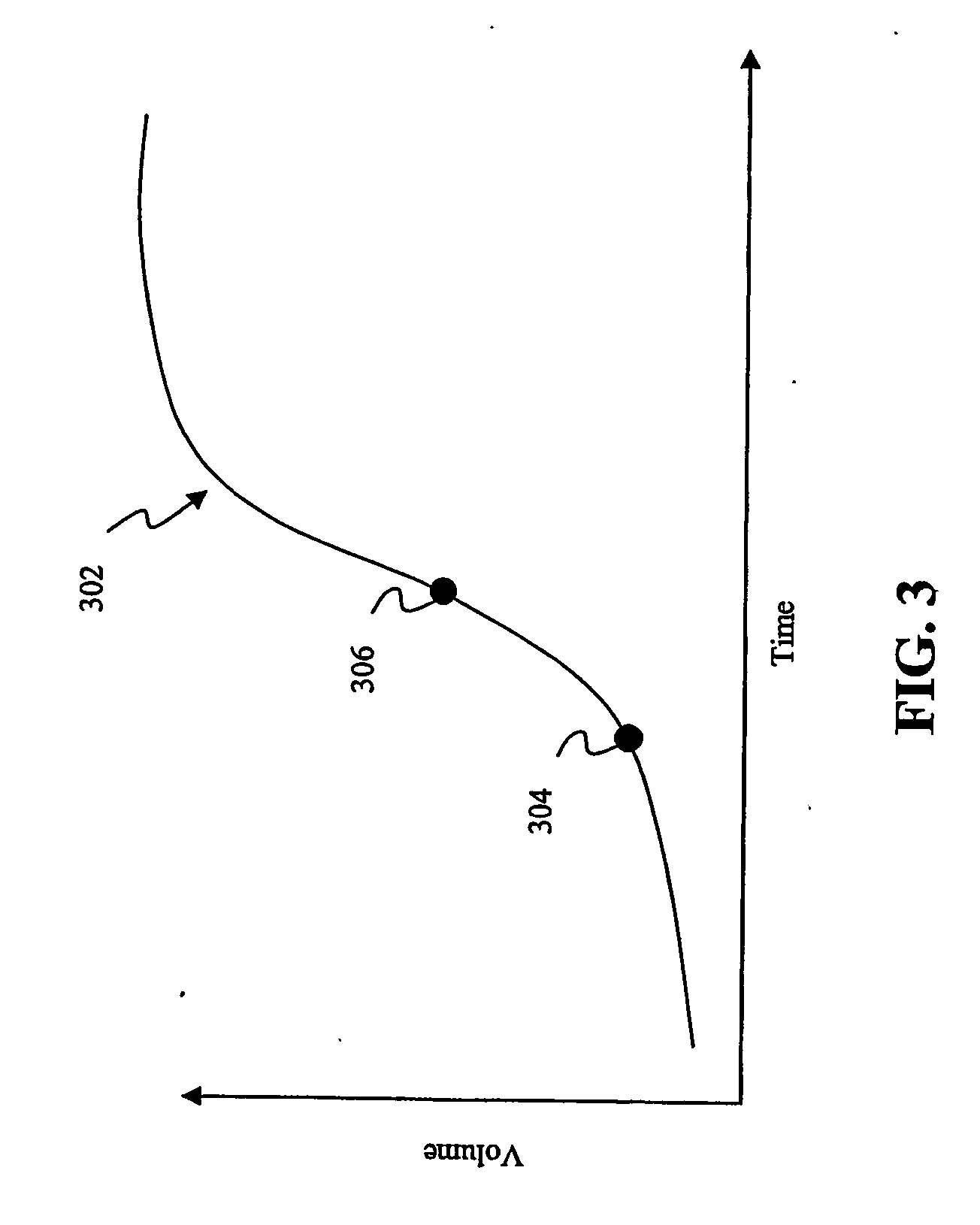

Library design elements (102) are analyzed for manufacturability to be used in designing an IC chip to be manufactured using a particular manufacturing process. The library design elements from a library are obtained. Manufacturability attributes (104) of the library design elements are determined for the particular manufacturing process, where manufacturability attributes include yield-related attributes. Library views (106) with manufacturability attributes for the library design elements are then generated, which are utilizing by an electronic design automation (EDA) tool.

Owner:PDF SOLUTIONS INC

Graphic design of combinatorial material libraries

Computer-implemented methods, programs and apparatus for generating a library design for a combinatorial library of materials. A library design includes a set of sources representing components to be used in preparing the combinatorial library, destinations representing arrangements of cells and mappings, defining one or more distribution patterns for assigning components to cells in the destination arrangement or arrangements. Mappings include gradients and sets of user-defined equations, and are used to calculate the amount of one or more components to be assigned to a cell or cells in an arrangement. A library design can also include one or more process parameters defined to vary over time or across a plurality of destination cells. The invention outputs a data file defining the library design, including electronic data representing the sources, the destinations and the mapping, in a format suitable for implementing manually or using automated material handling apparatus.

Owner:FREESLATE

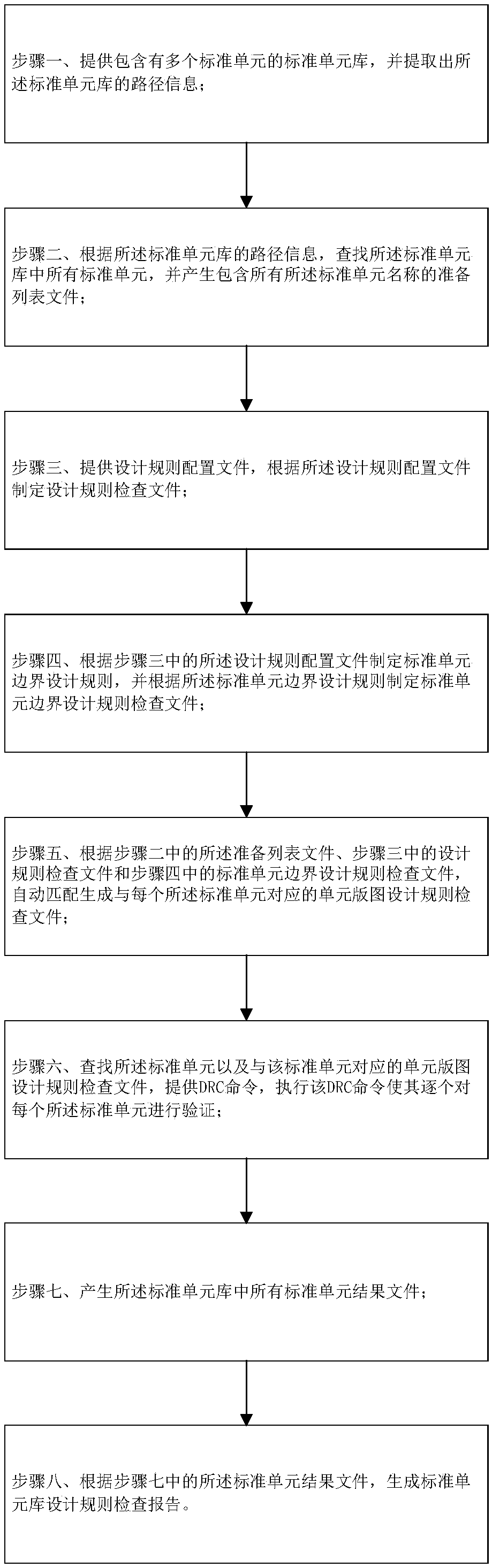

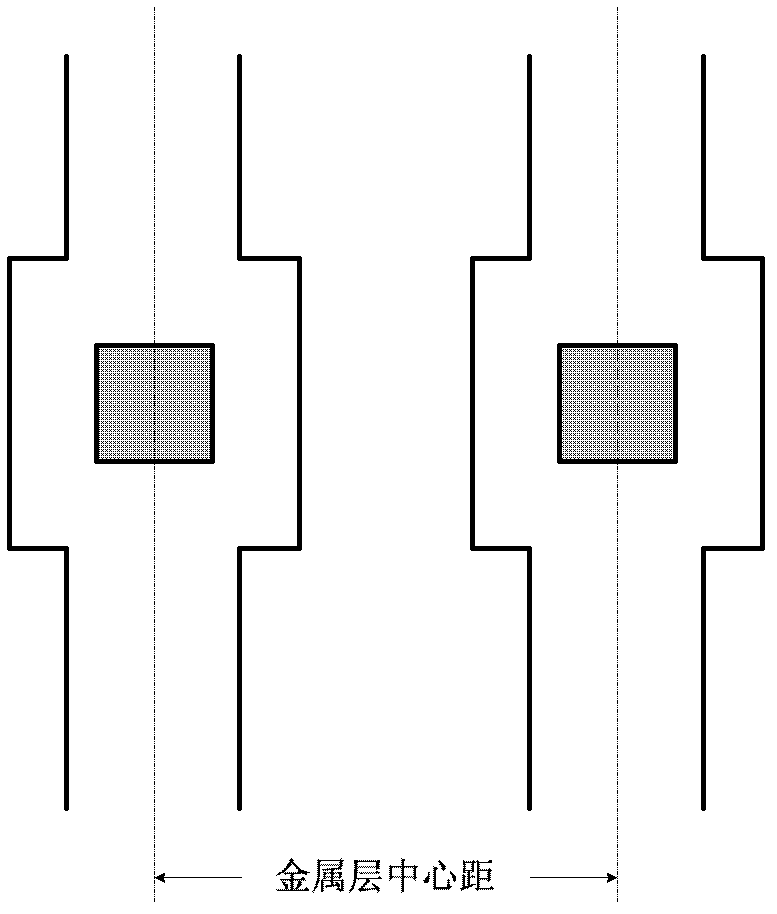

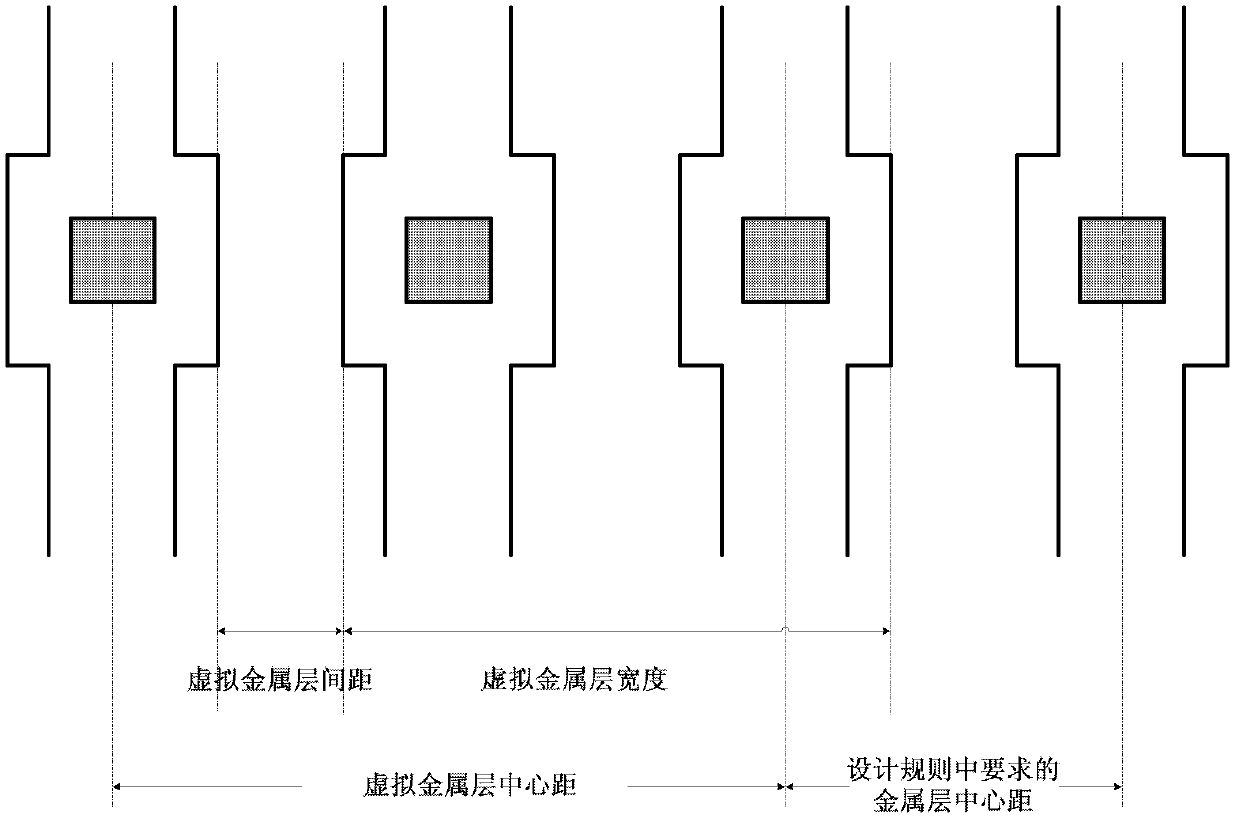

A standard cell library layout design rule verification method

PendingCN109684707ADesign rule verification is fastEfficient design rule verificationSpecial data processing applicationsComputer architectureValidation methods

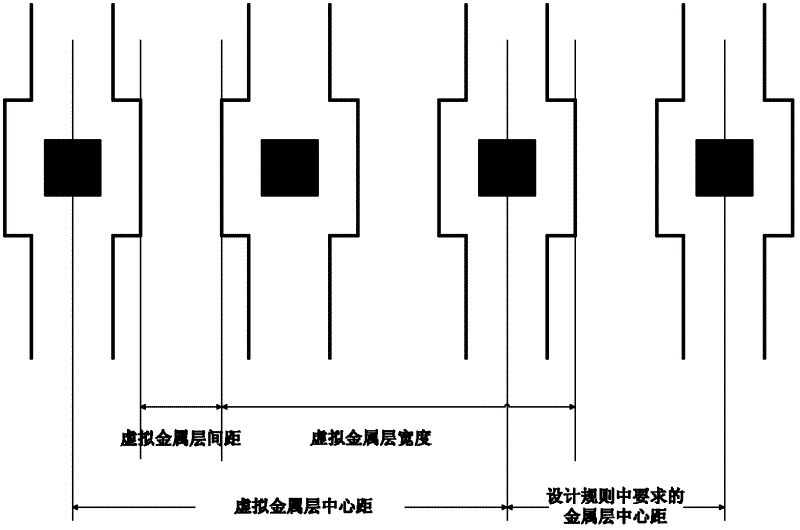

The invention provides a standard cell library layout design rule verification method. The method comprises the steps that path information of a standard cell library is extracted; Searching all standard units in the standard unit library, and generating a preparation list file; Providing a design rule configuration file, and formulating a design rule checking file; Formulating a standard unit boundary design rule and a corresponding standard unit boundary design rule check file; Automatically generating a unit layout design rule check file according to the preparation list file, the design rule check file and the standard unit boundary design rule check file; Standard units and unit layout design rule inspection files corresponding to the standard units are searched for, and program commands are executed to verify the standard units; And generating a standard unit result file and generating a standard unit library design rule inspection report. According to the method, the layout violation design rule after standard unit splicing is avoided. Therefore, rapid, efficient and accurate design rule inspection and verification of the standard cell library are realized.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

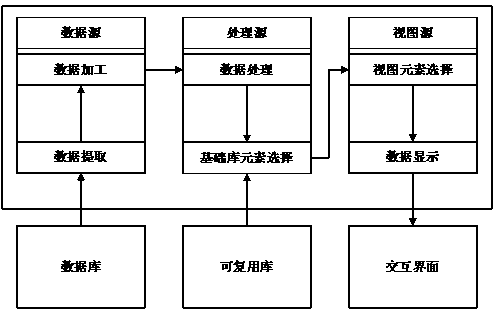

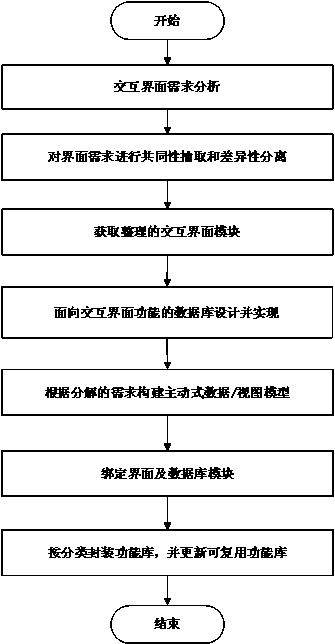

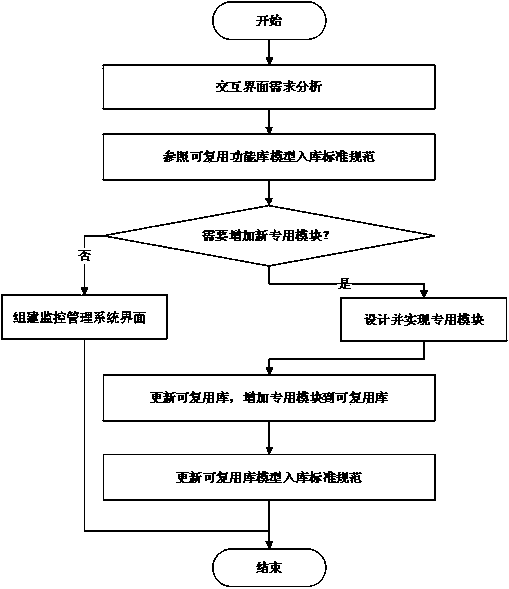

Interactive-interface fast implementation method based on reusable library

InactiveCN103914307AImprove effectivenessImprove usabilitySpecific program execution arrangementsView modelSoftware engineering

The invention provides an interactive-interface fast implementation method based on a reusable library. The interactive-interface fast implementation method comprises correlating data and interface elements by virtue of active data / view model design, constructing a reusable basic element library, a universal function library and a special function library according to the characteristics of an interactive interface and then constructing a reusable library, and finally raising model into-library standard specifications, thereby providing a unified standard interface a configuration path, a database table from and a data / view model binding specification. The method is suitable for a development platform based on remote access of WEB and based on local interactive interfaces of tools such as QT and VS; the method is capable of realizing various types of interfaces needing to be interacted based on the reusable library, and has the characteristics of simple function library design rule, high reusability, quick interface molding and the like; besides, the effectiveness of the reusable library and the usability of the interactive interfaces can be further improved by improving and optimizing the standard specifications of the reusable library.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

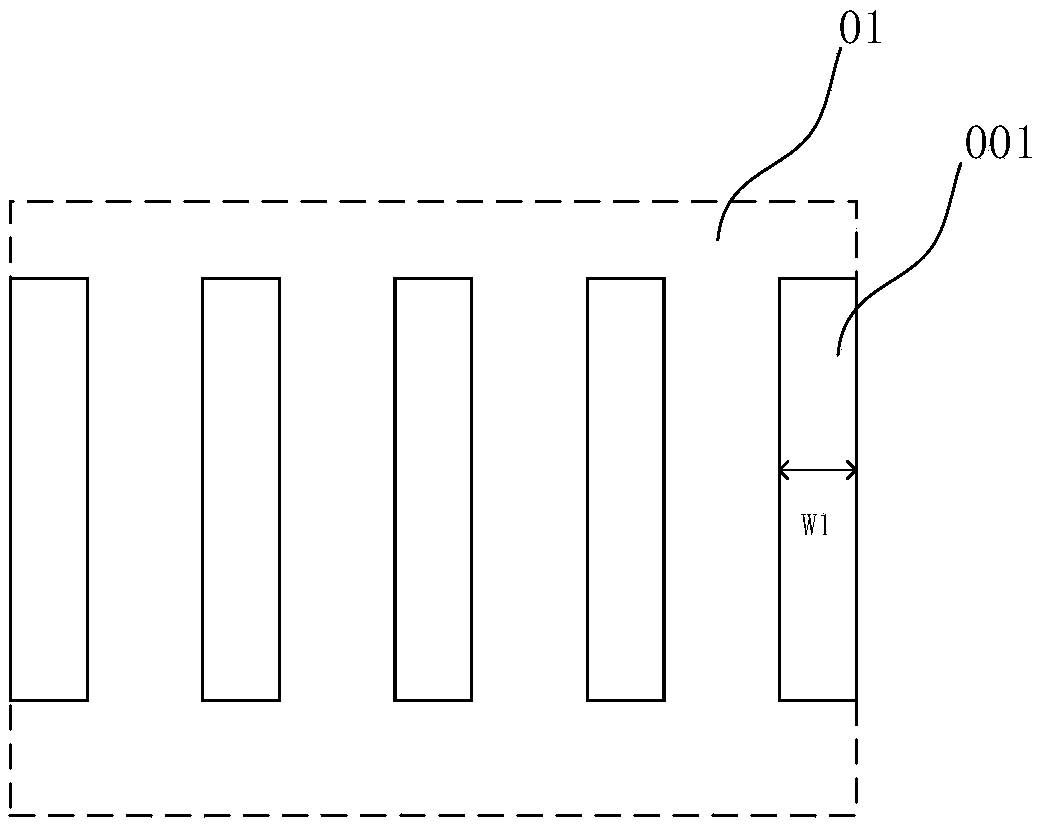

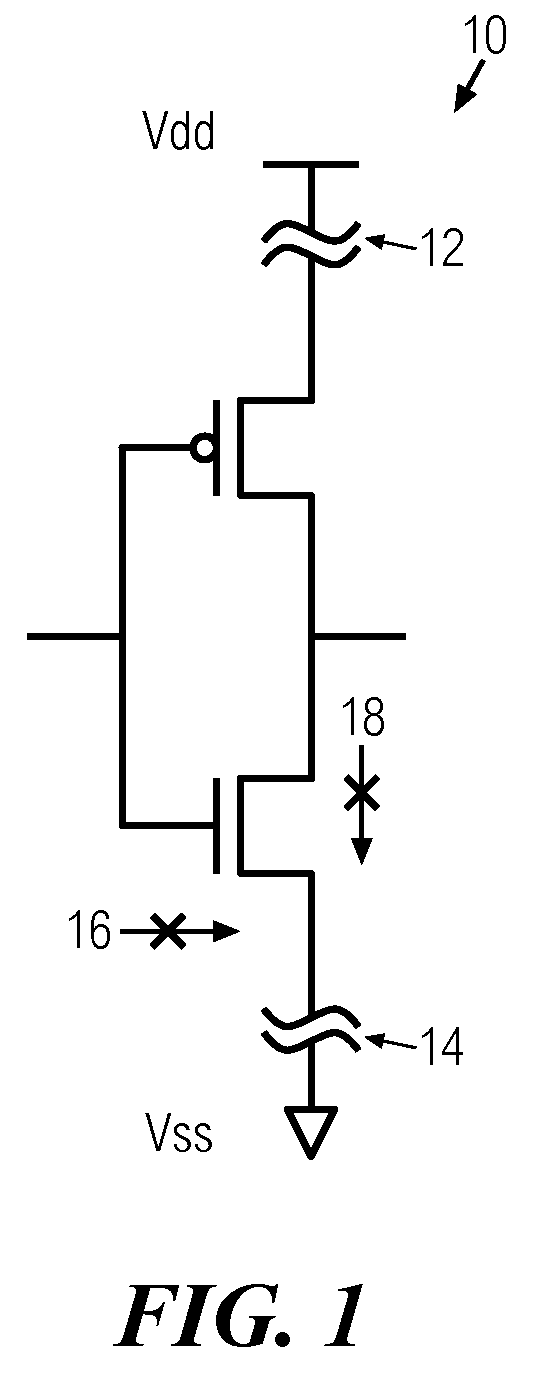

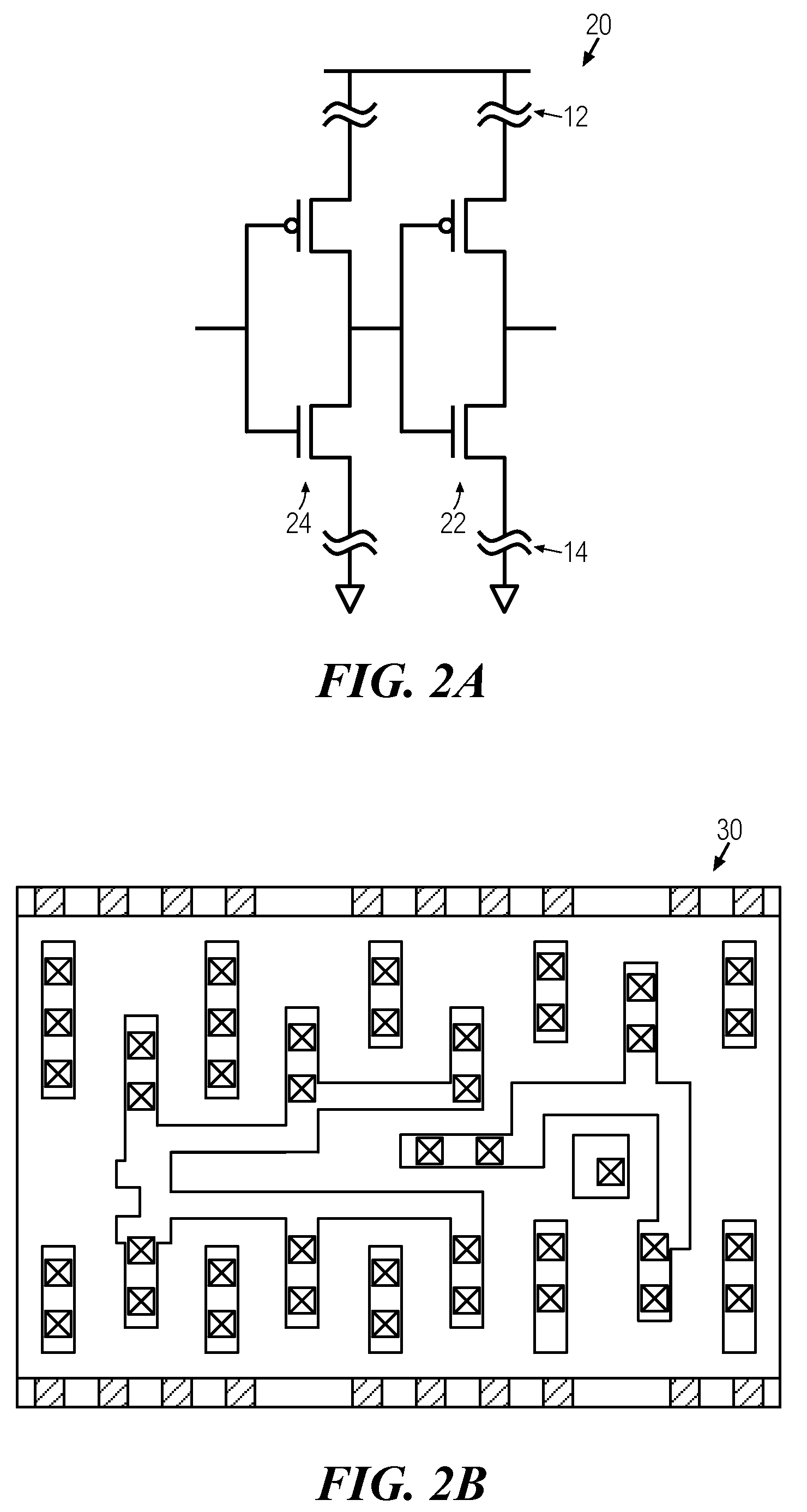

Spare cell library design for integrated circuit

InactiveUS20100231256A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringIntegrated design

A cell based design layout of an application specific integrated circuit (ASIC) having a function has reduceddecreased power leakage because functionally unconnected additional cells or spare cells of the integrated design layout are unconnected to the power supplies Vdd and Vss.

Owner:FREESCALE SEMICON INC

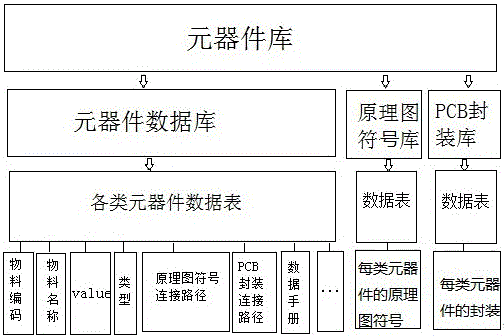

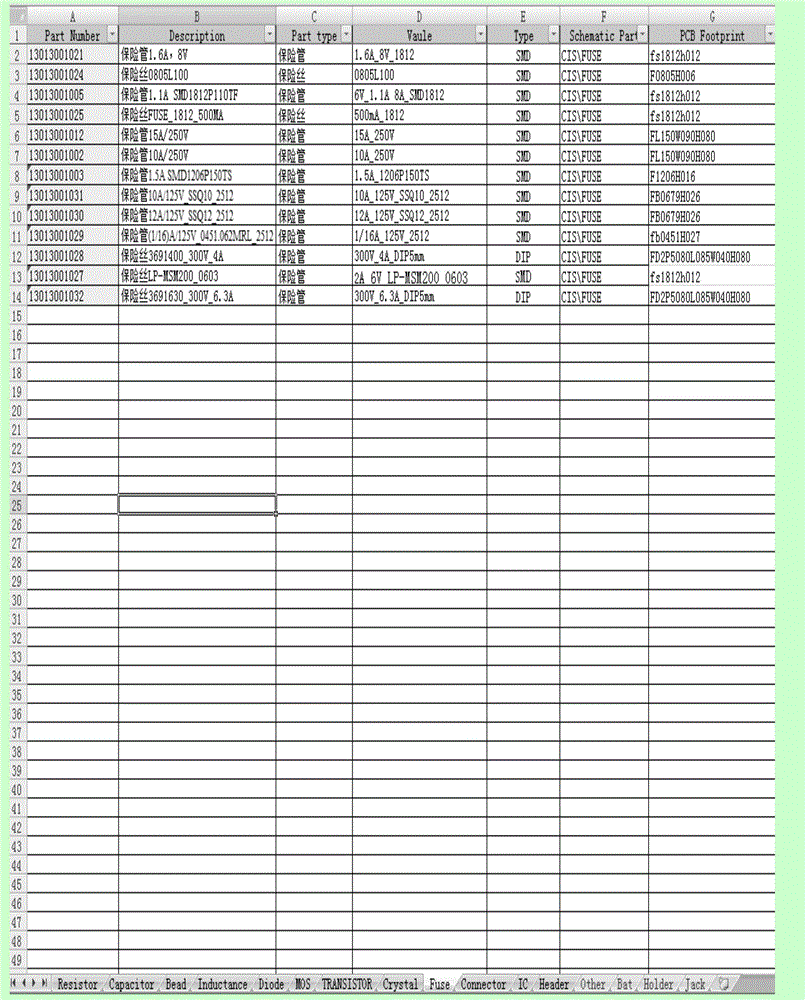

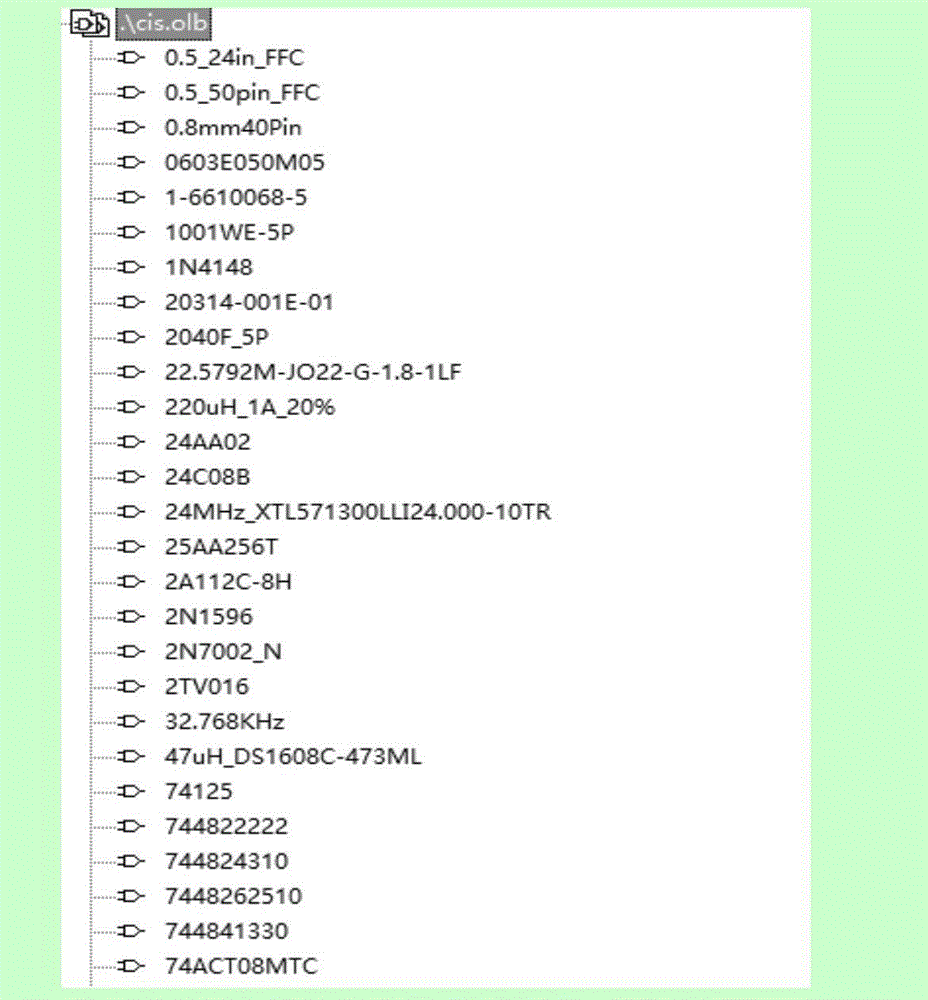

Method for configuring component library in PCB

InactiveCN105045980AImprove efficiencyImprove the quality of useSpecial data processing applicationsSoftware engineeringQuality by Design

The present invention discloses a method for configuring a component library in a PCB and belongs to the field of component library design and configuration. According to the method for configuring the component library in the PCB, a plurality of data tables containing component information are arranged to separately correspond to PCB component libraries; and the corresponding data table of the PCB component library is loaded according to a user demand, and the PCB component library required by the user is configured, so that the problems of library management efficiency and quality caused by that different users use different libraries and different projects use different libraries are better solved, the error rate is reduced, and the design quality and efficiency are improved.

Owner:INSPUR GROUP CO LTD

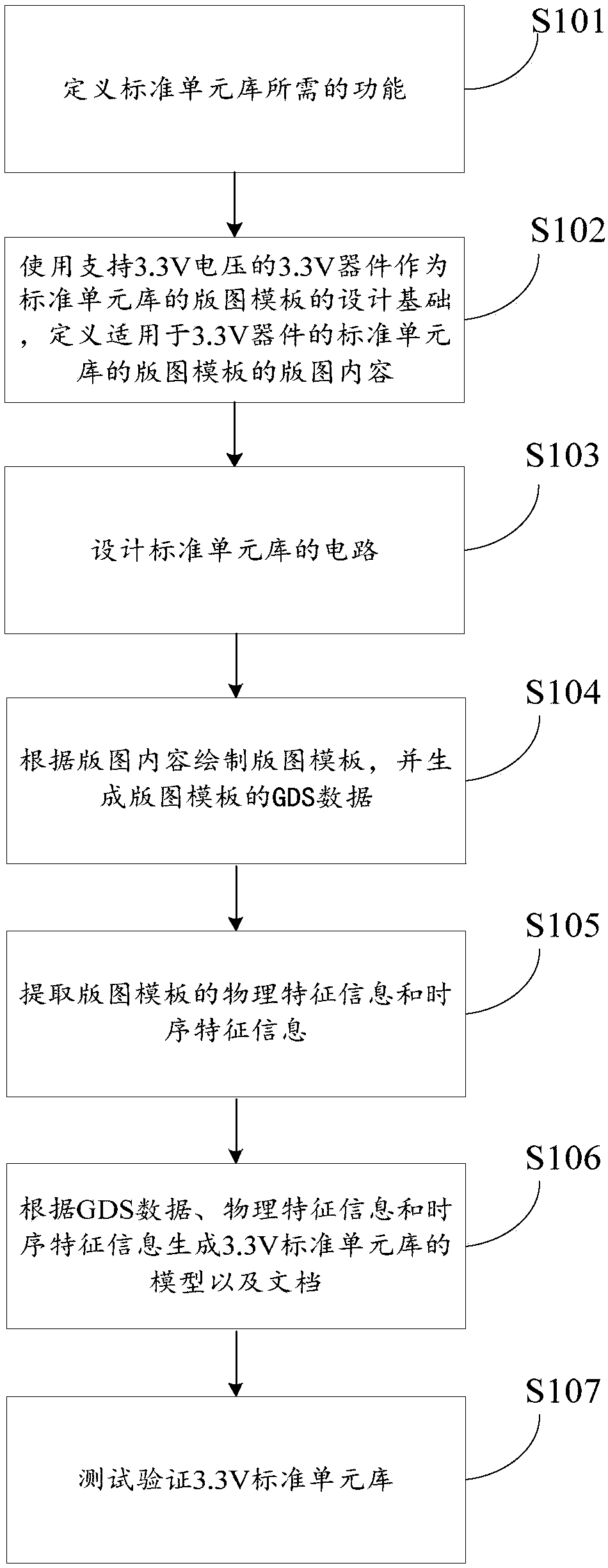

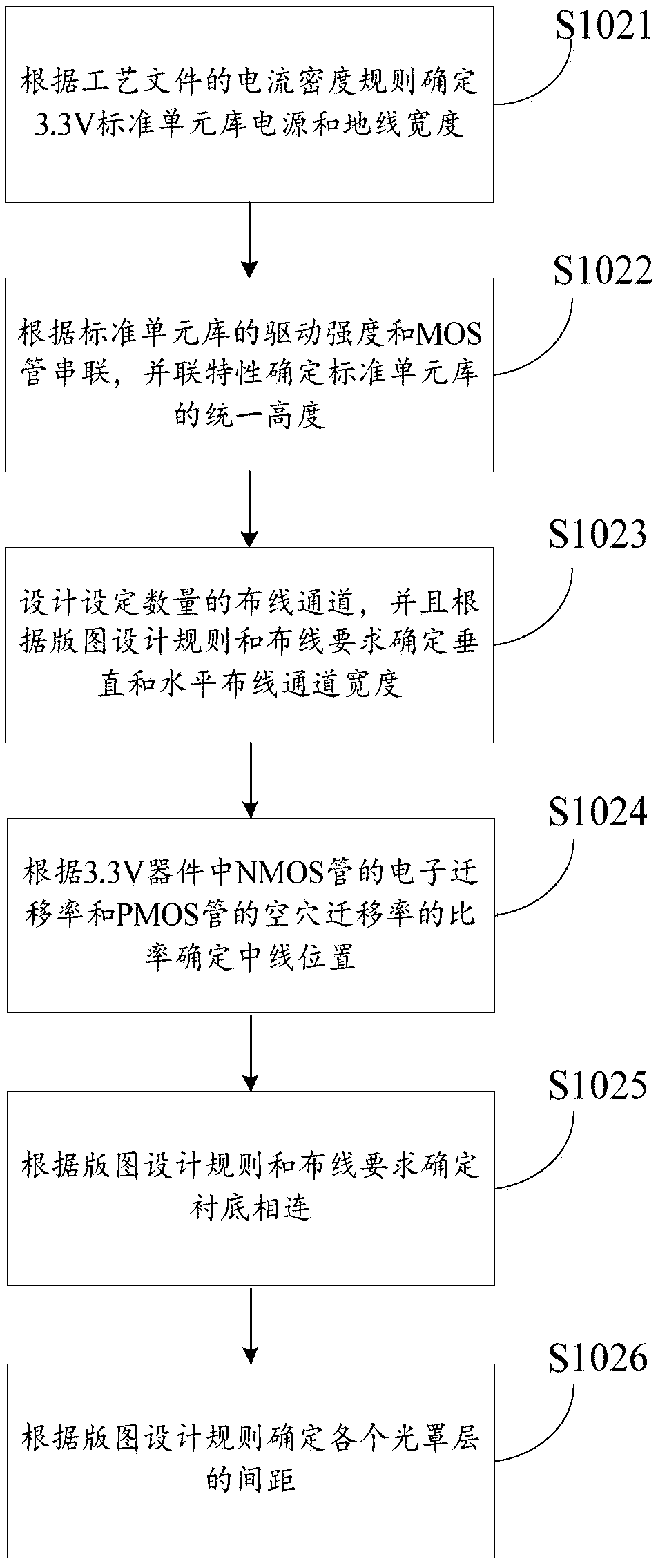

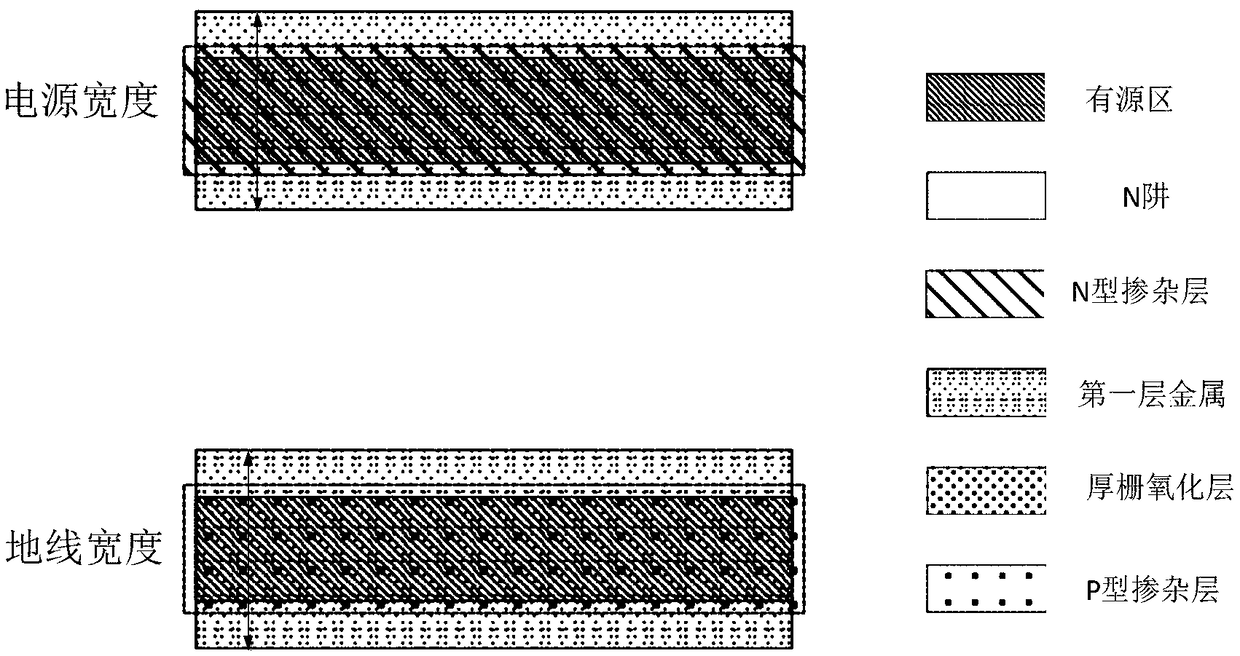

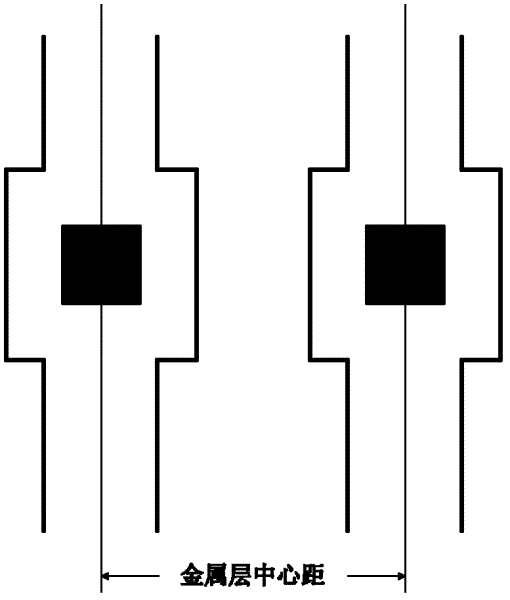

Standard cell library design method, design device, standard cell library and CMOS image sensing chip

ActiveCN108647390AImprove stabilityReduce lossSpecial data processing applicationsEngineeringProcess design

The invention provides a standard cell library design method, a design device, a standard cell library and a CMOS image sensing chip. The method comprises the steps that the functions of the standardcell library are defined; a 3.3V device supporting 3.3V voltage is used as a design basis of a layout template of the standard cell library, and layout content suitable for the layout template of thestandard cell library of the 3.3V device is defined; a circuit of the standard cell library is designed; the layout template is drawn according to the layout content; physical feature information andtime sequence feature information of the layout template are extracted; according to GDS data, the physical feature information and the time sequence feature information, a model and a document of thestandard cell library are generated; and the standard cell library is verified through a test. Through the method, communication between a peripheral circuit and a core circuit of the CMOS image sensing chip based on digital logic process design can be realized, speed and precision losses brought by a level switching circuit are reduced, and system speed and performance stability are improved.

Owner:SHENZHEN UNIV

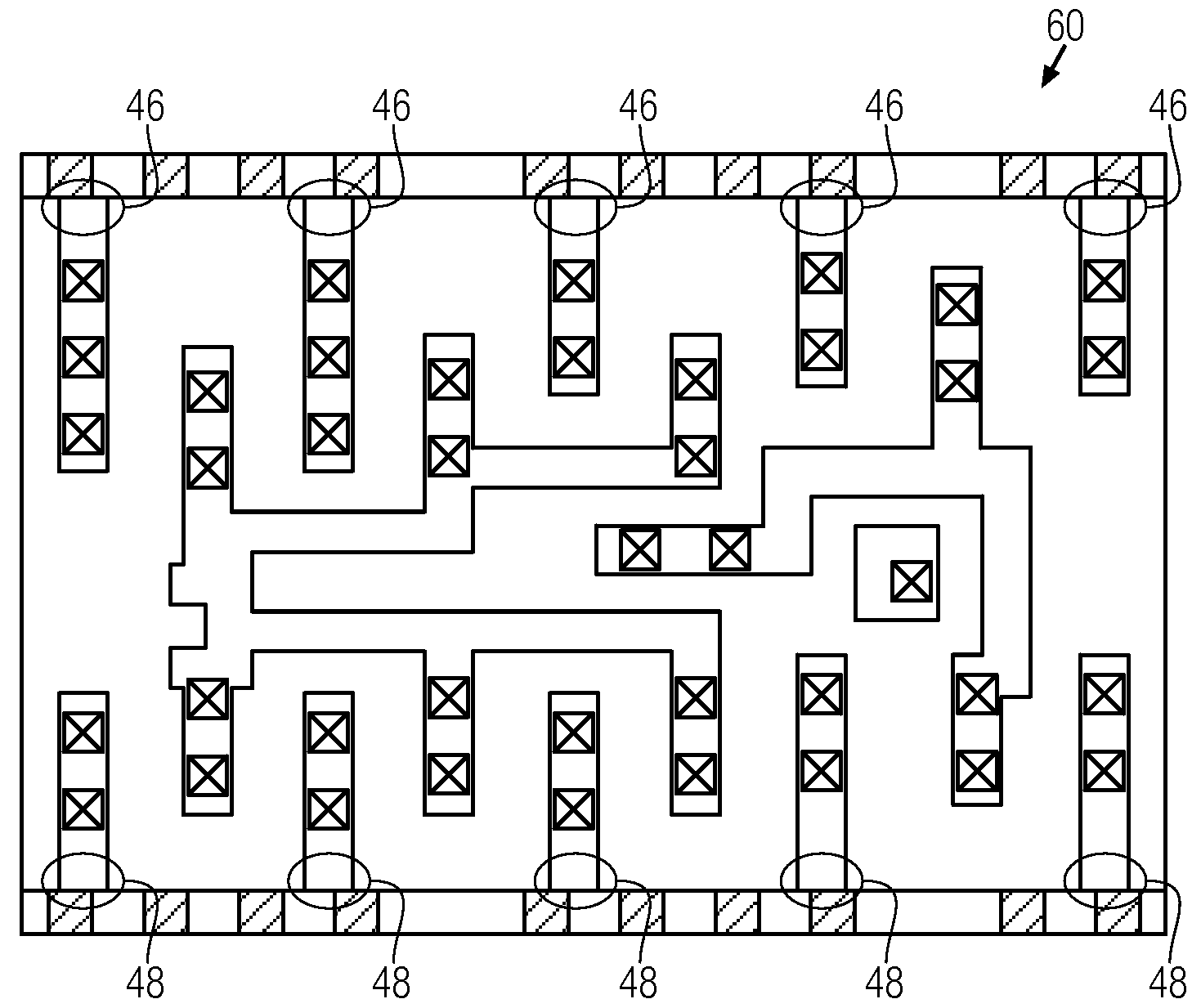

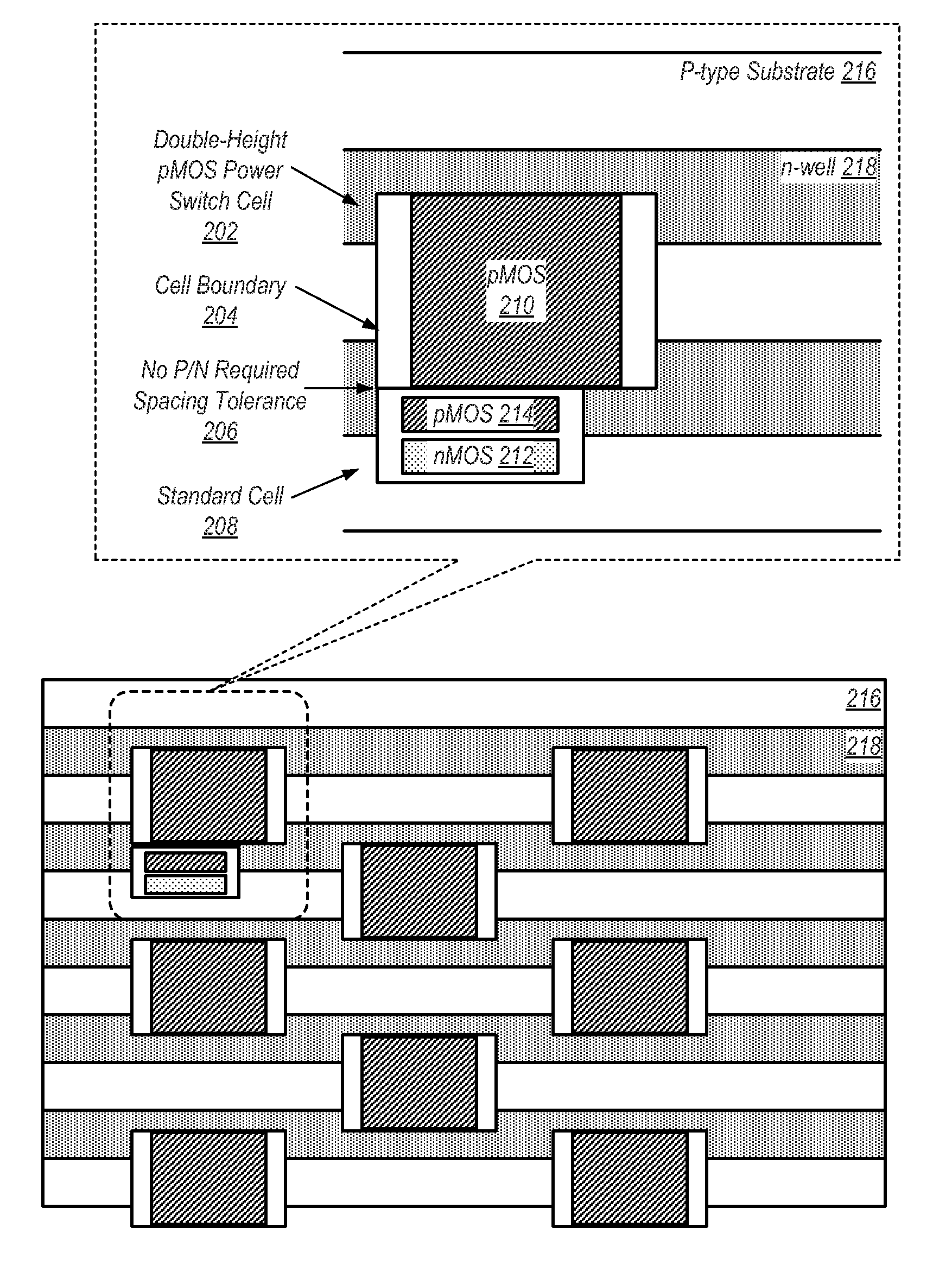

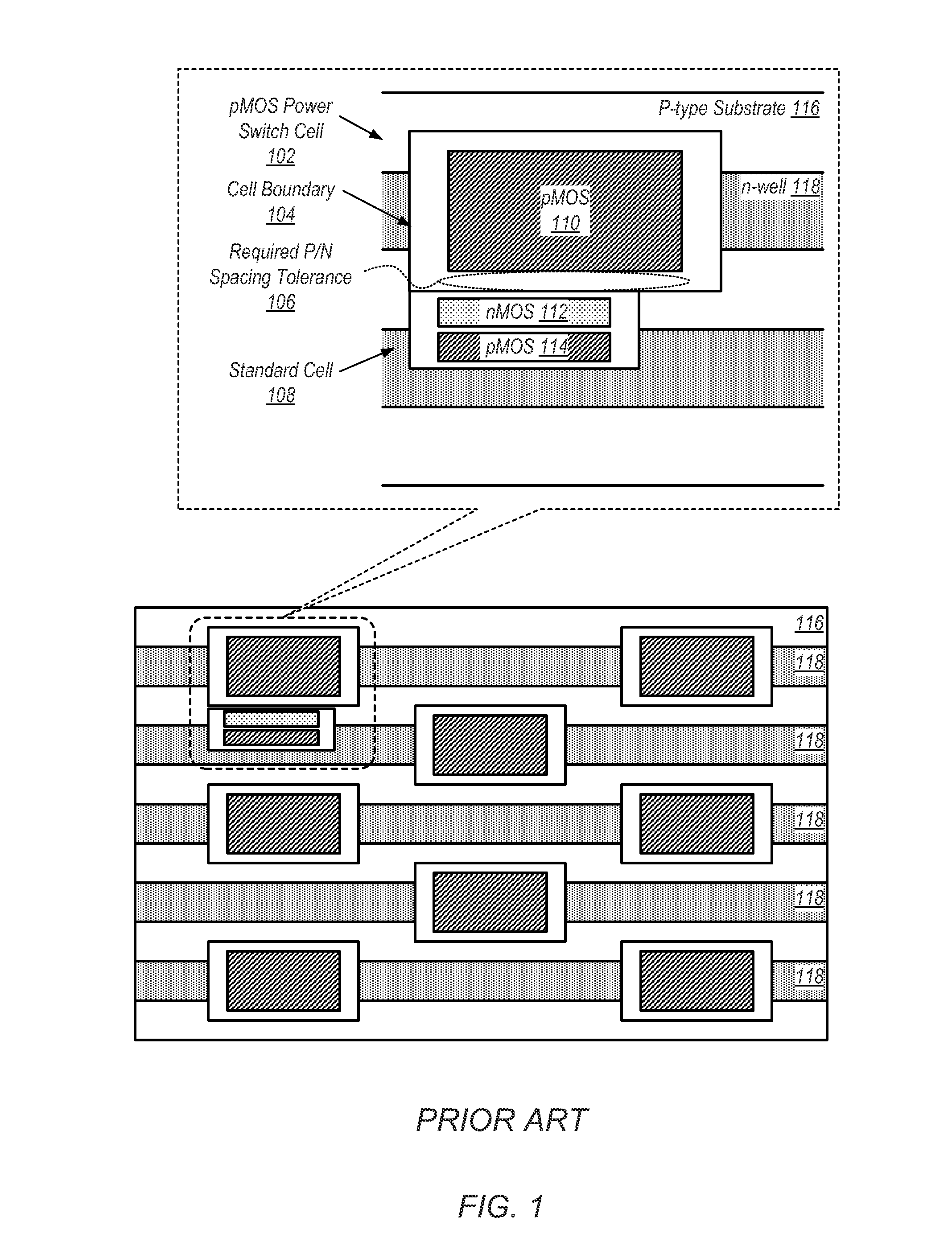

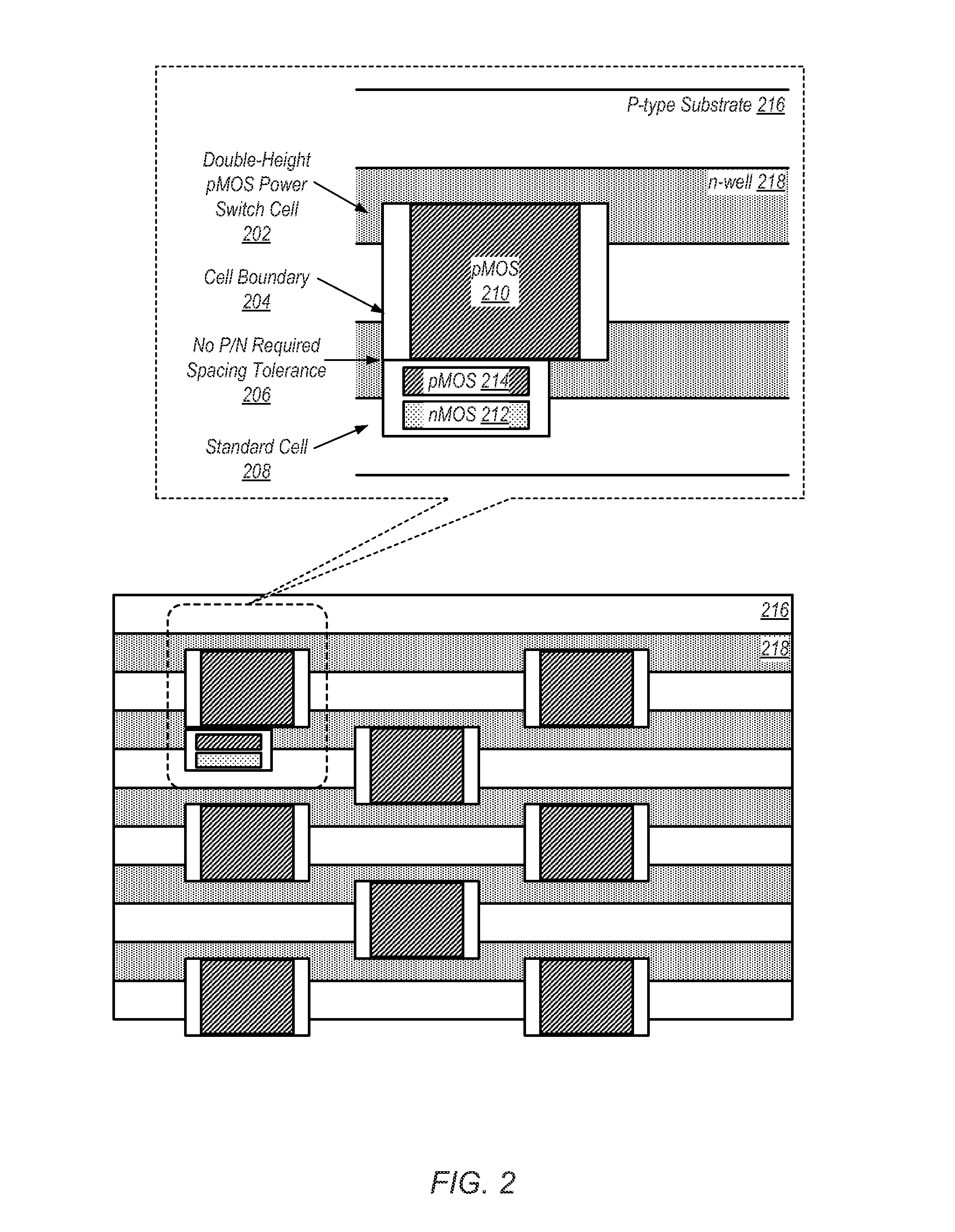

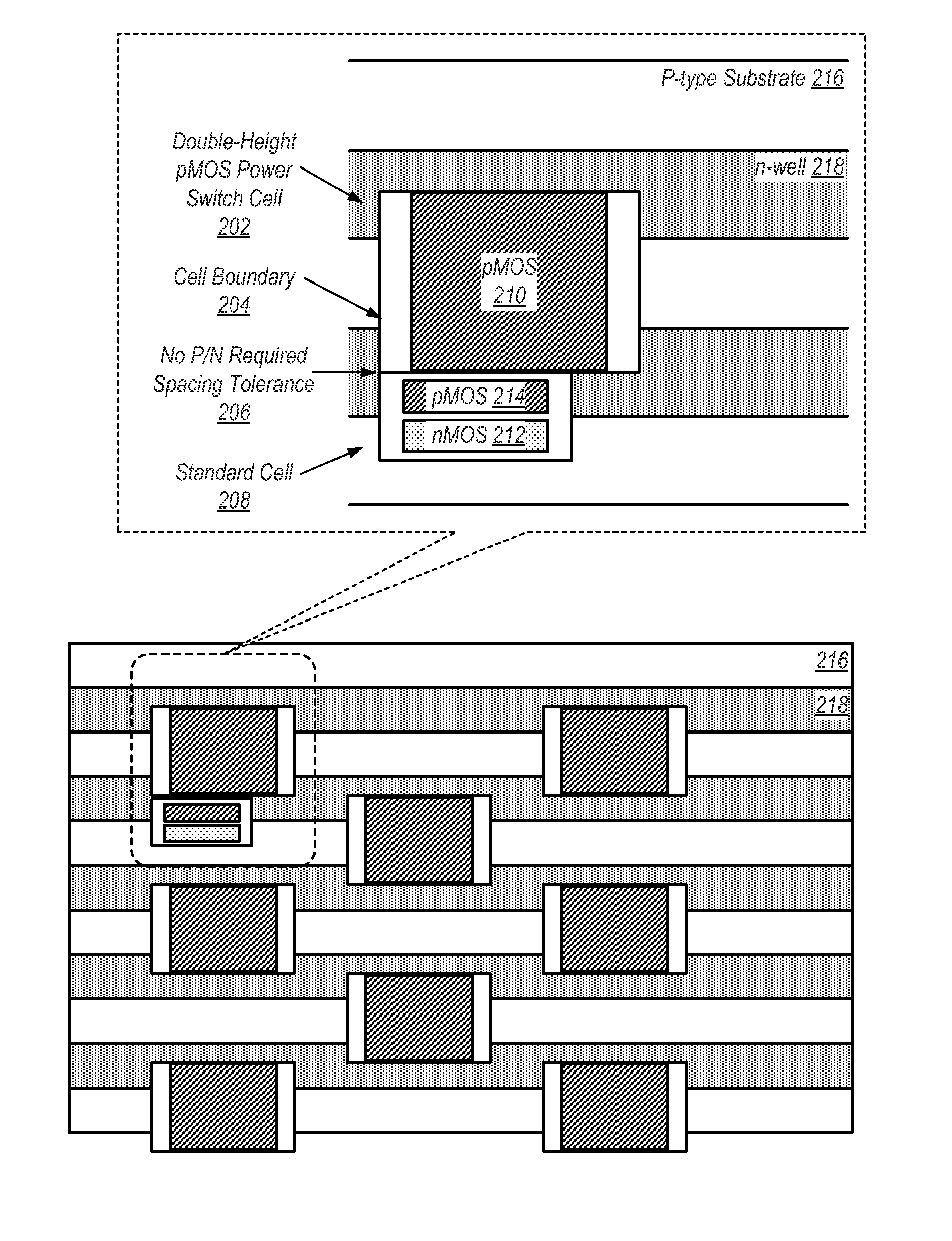

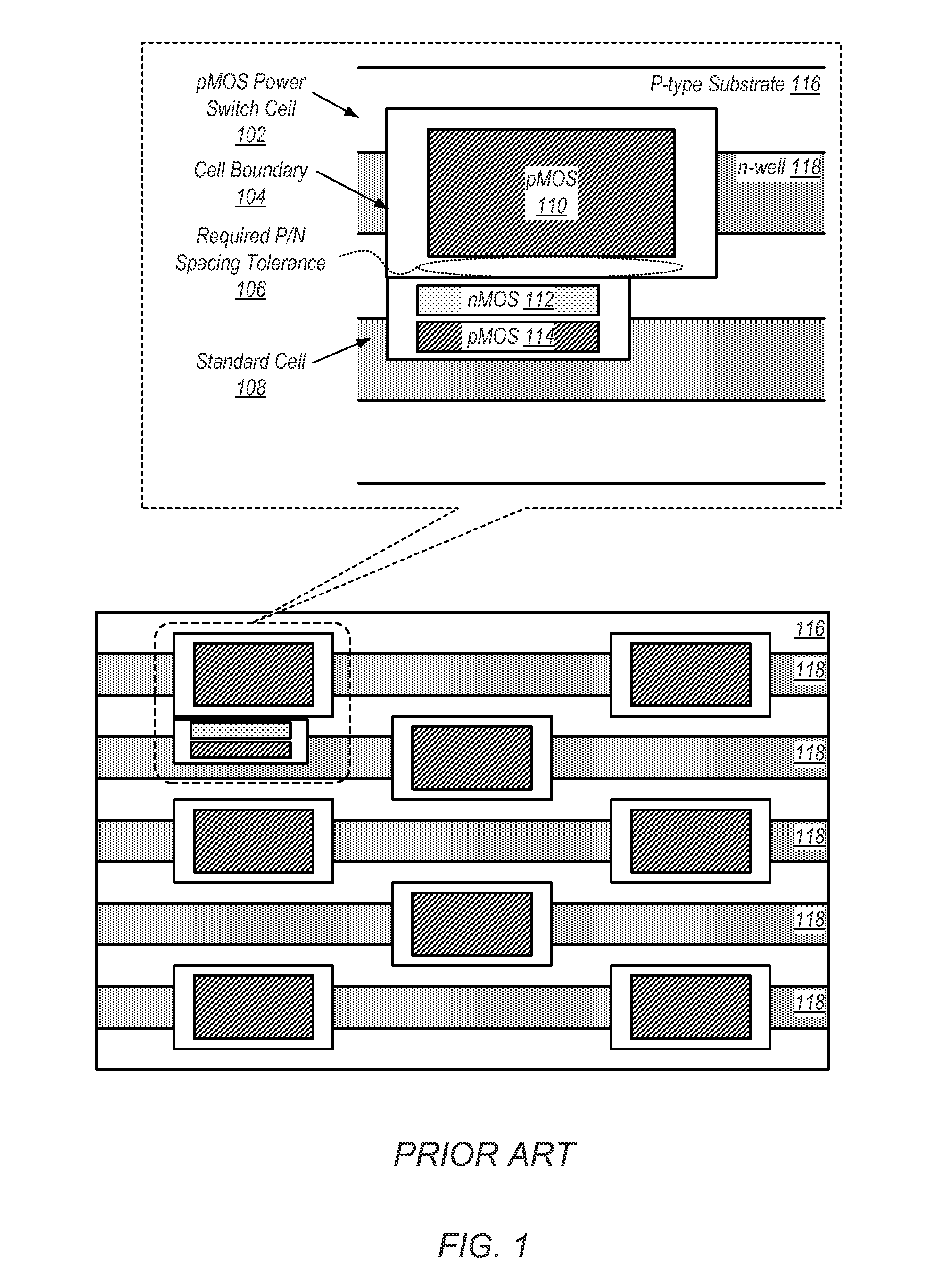

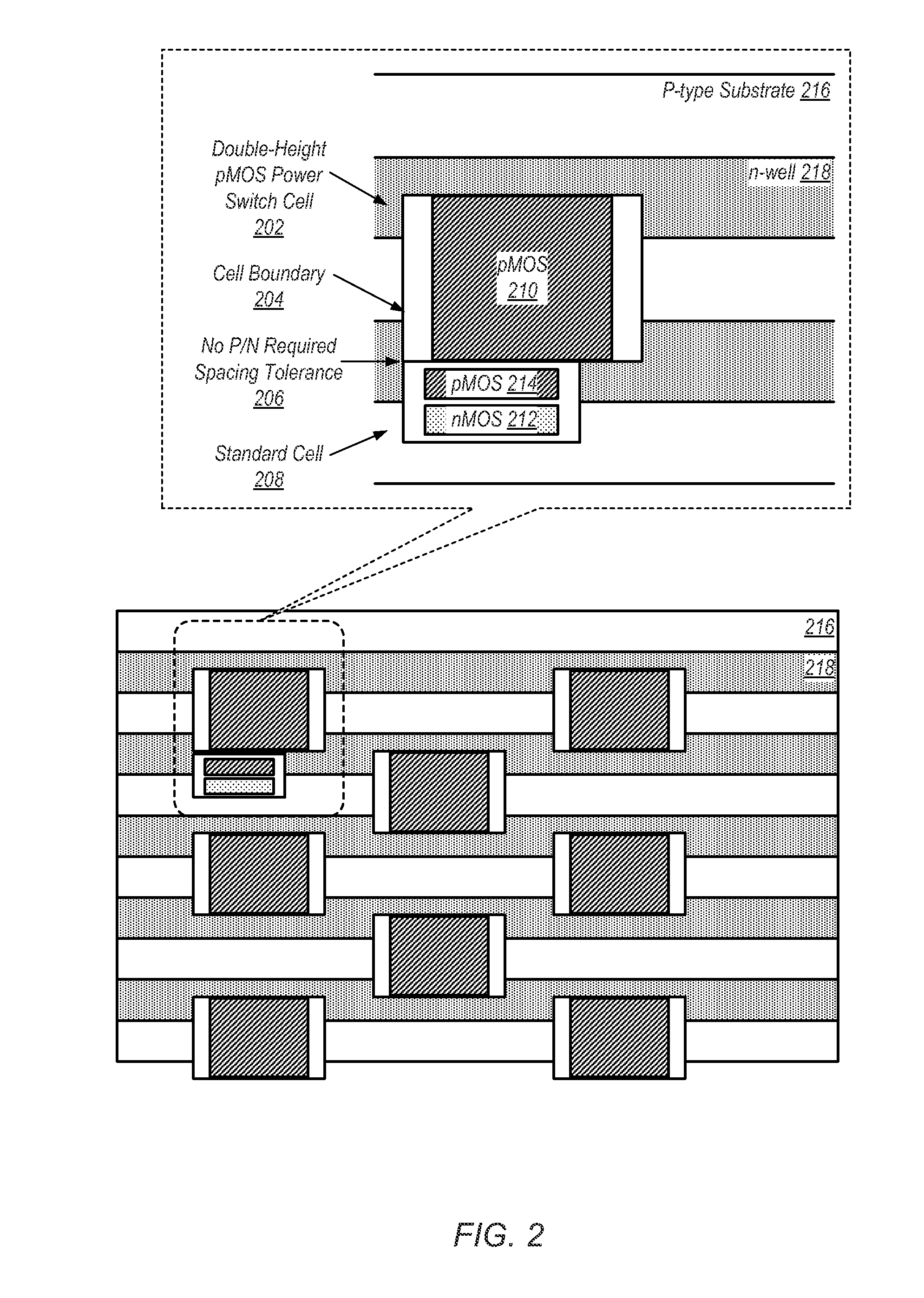

Area efficient power switch

InactiveUS8726216B2Computer aided designSpecial data processing applicationsEffective powerEngineering

A method of generating an area efficient power switch cell includes receiving, by a cell library design tool, a specification of a power switch circuit to be established as a power switch cell in a cell library. The cell library design tool also receives one or more attributes of the power switch cell including a height of the cell boundary and receiving, by the cell library design tool, a layout placement constraint requiring the power switch cell to be placed in a semiconductor layout so as to bridge two parallel rows of doped wells. The parallel rows of doped wells are interleaved with doped substrate and the doping of the wells is of a different type than that of the substrate. Based on the specification of the power switch circuit, the one or more attributes, and the layout placement constraint, the cell library design tool generates the power switch cell.

Owner:APPLE INC

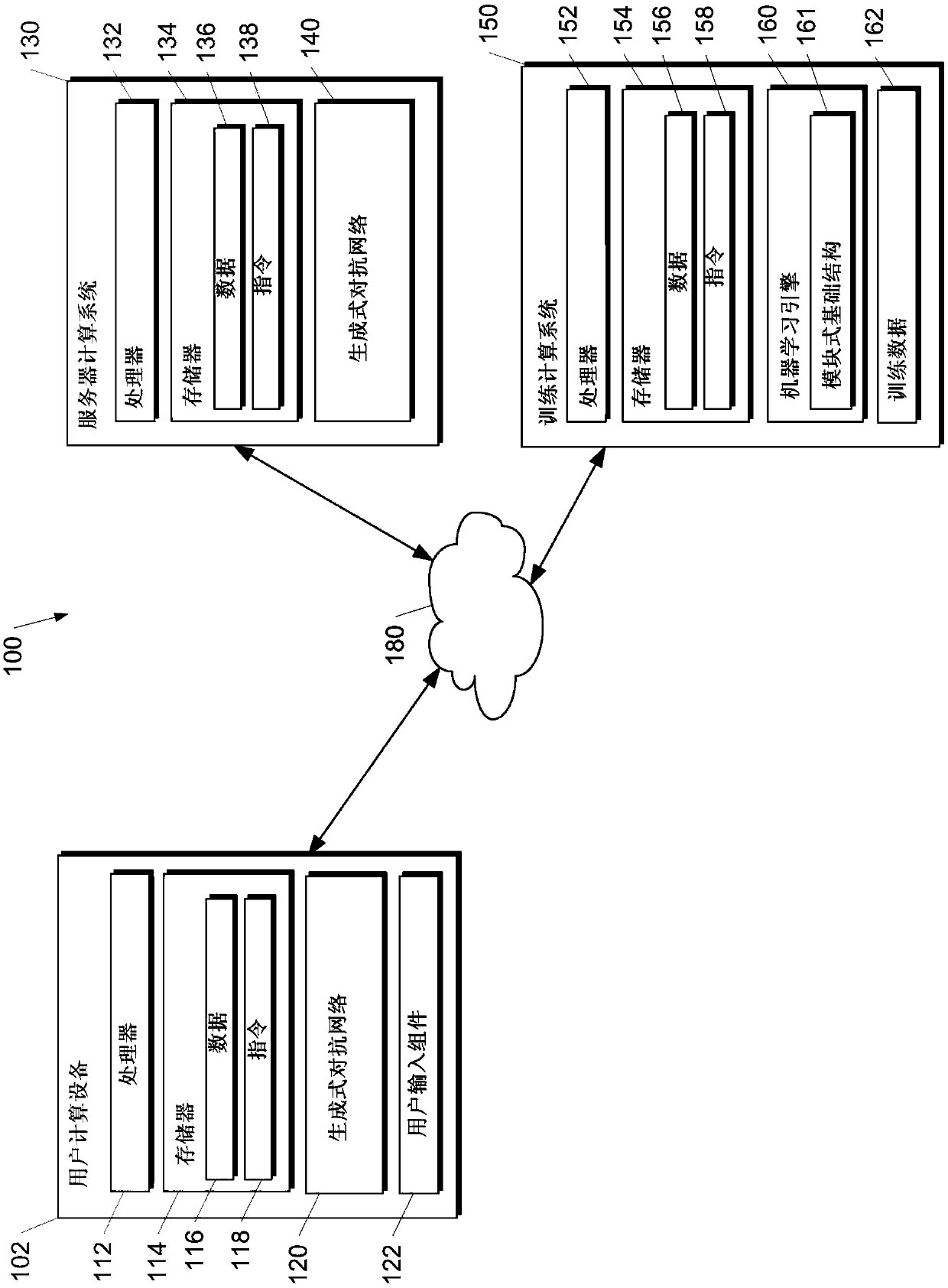

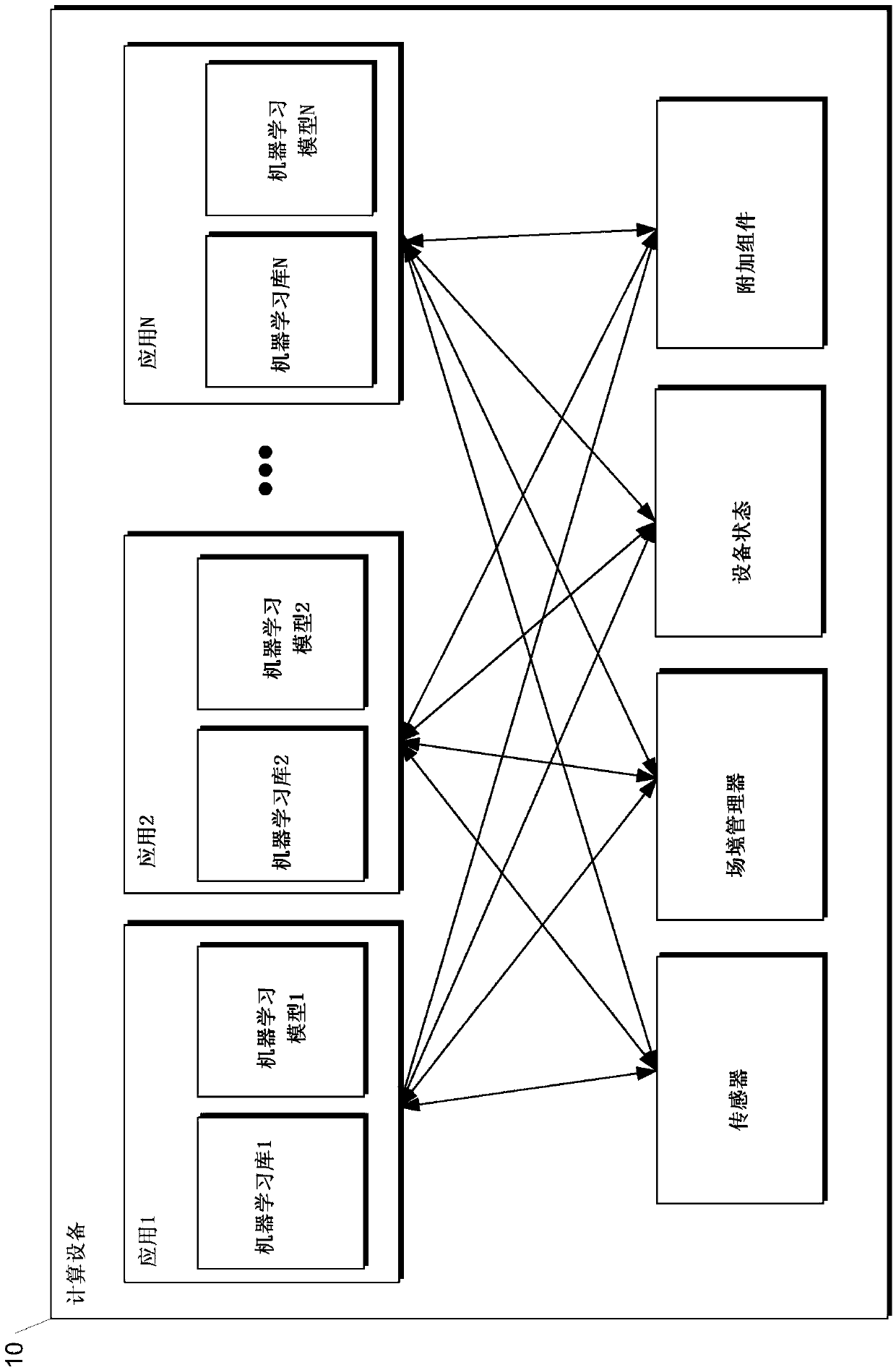

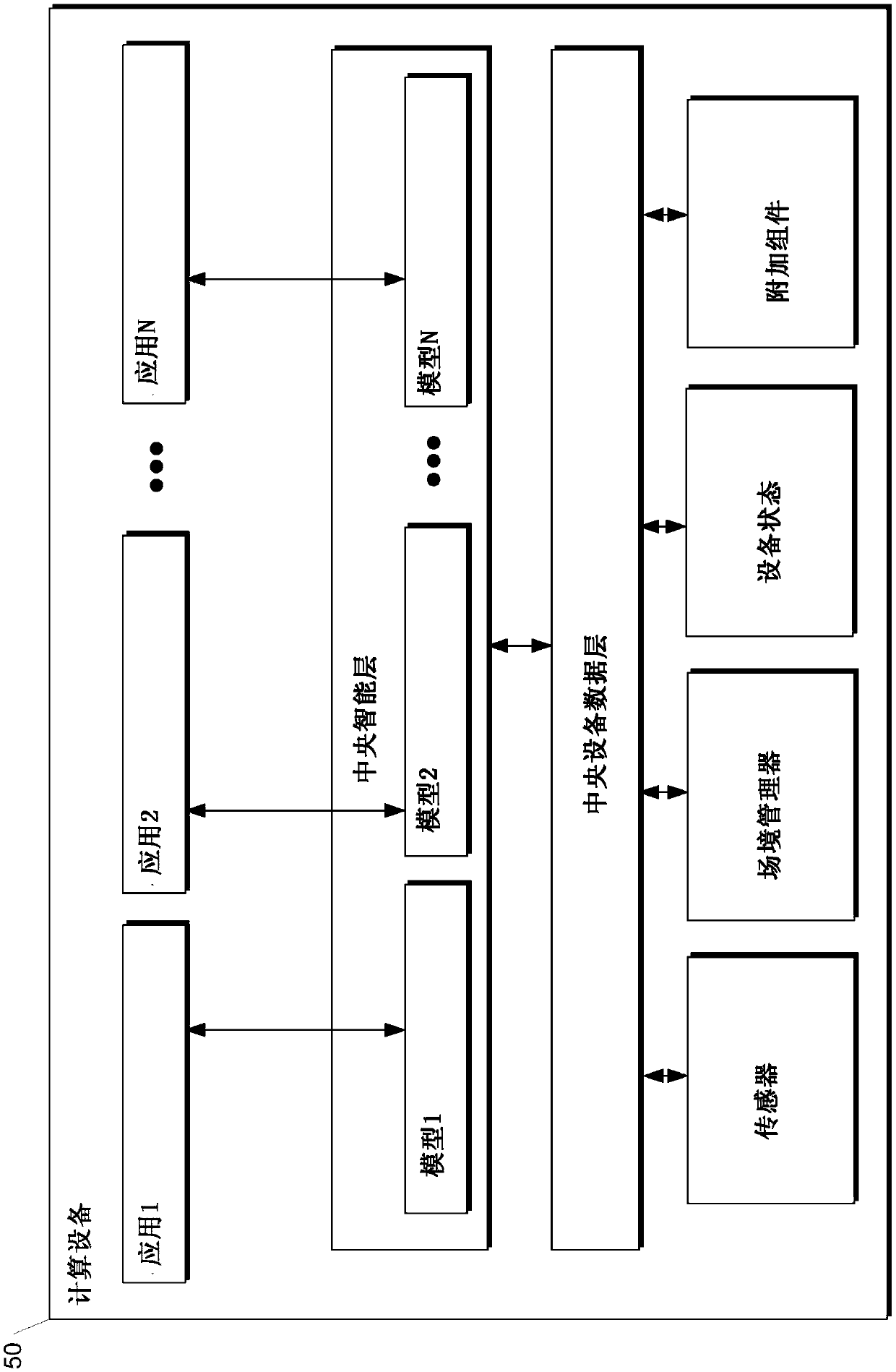

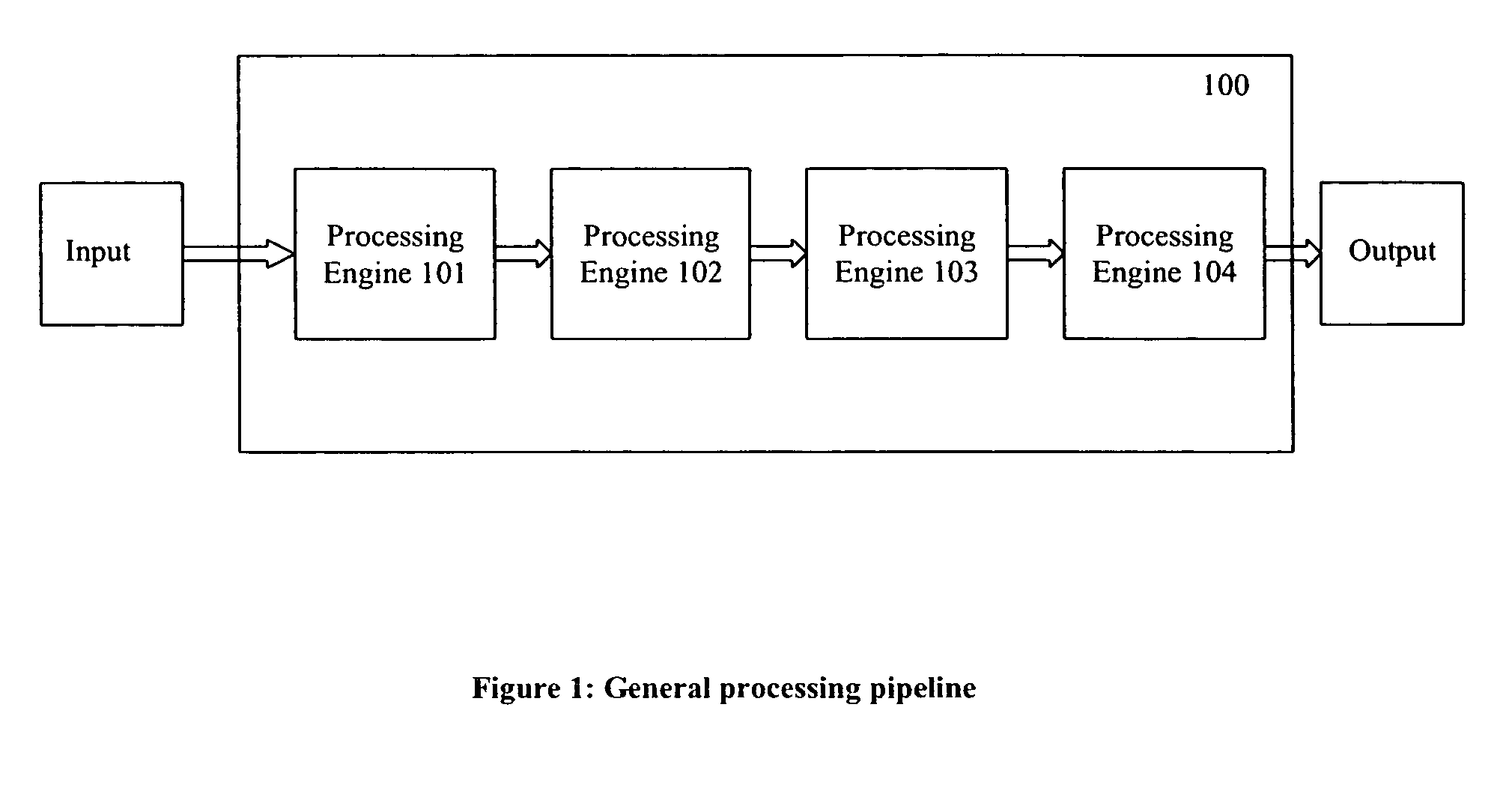

Computing systems with modularized infrastructure for training generative adversarial networks

PendingCN109754088AExecution paradigmsMachine learningTheoretical computer scienceGenerative adversarial network

The application relates to computing systems with modularized infrastructure for training generative adversarial networks. Example aspects of the present disclosure are directed to computing systems that provide a modularized infrastructure for training Generative Adversarial Networks (GANs). For example, the modularized infrastructure can include a lightweight library designed to make it easy totrain and evaluate GANs. A user can interact with and / or depend on the modularized infrastructure to easily train GANs. According to one aspect of the present disclosure, the modularized infrastructure can include a number of distinct sets of code that handle various stages of and operations within the GAN training process. The sets of code can be modular. That is, the sets of code can be designedto exist independently yet be easily and intuitively combinable. Thus, the user can employ some or all of the sets of code or can replace a certain set of code with a set of custom-code while still generating a workable combination.

Owner:GOOGLE LLC

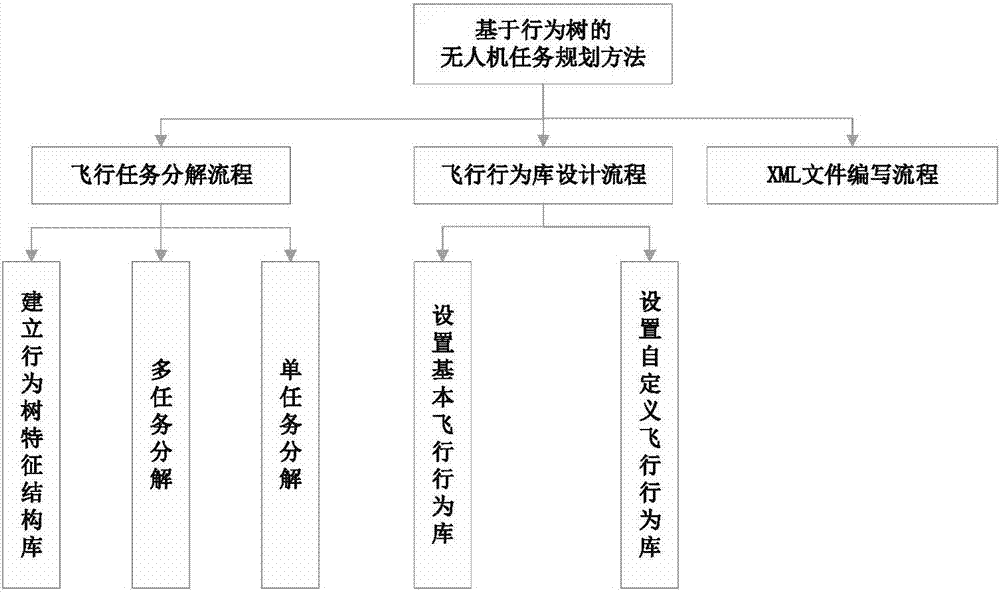

Multi-unmanned aerial vehicle complex task planning method

InactiveCN106933246ASolve practical problemsOptimization principlePosition/course control in three dimensionsDecompositionTheoretical computer science

The invention relates to a multi-unmanned aerial vehicle complex task planning method and belongs to the unmanned aerial vehicle field. The method includes a flight task decomposition flow, a flight behavior library design flow and an XML file editing flow; according to the task decomposition flow, behavior tree decomposition is performed on a multiple-task under execution, and behavior tree decomposition is performed on obtained single tasks; according to the flight behavior library design flow, basic behavior library and customized behavior library design is performed according to flight behaviors required in the single tasks; and according to the XML file editing flow, a customized XML format language is adopted to edit behavior tree knots obtained through decomposition. With the multi-unmanned aerial vehicle complex task planning method adopted, a user can be facilitated to plan a whole task process; task decomposition is performed according to task levels; task execution is performed according to actual conditions; and the practical problem of multi-unmanned aerial vehicle complex tasks can be solved. The method has the advantages of simple principles, flexible planning, high practicability, excellent implementation effects and the like.

Owner:XIAMEN UNIV

Method and device for partitioning a molecule

ActiveUS9317664B2Wide range of usesImprove efficiencyMolecular designDigital data processing detailsComputer scienceLibrary design

A method for partitioning a molecular subset is described. The partitioning method takes into account molecular structure and its manner of storage and transmission, transformations to be applied to the molecular subset and their implementation, and constraints imposed by the implementation of the partitioning method. Using this method, a molecular subset can be stored, transmitted, and processed more efficiently. The resulting efficiency makes it possible to design and run applications which require complex molecular processing, such as rational drug discovery, virtual library design, etc.

Owner:VERSEON INT CORP

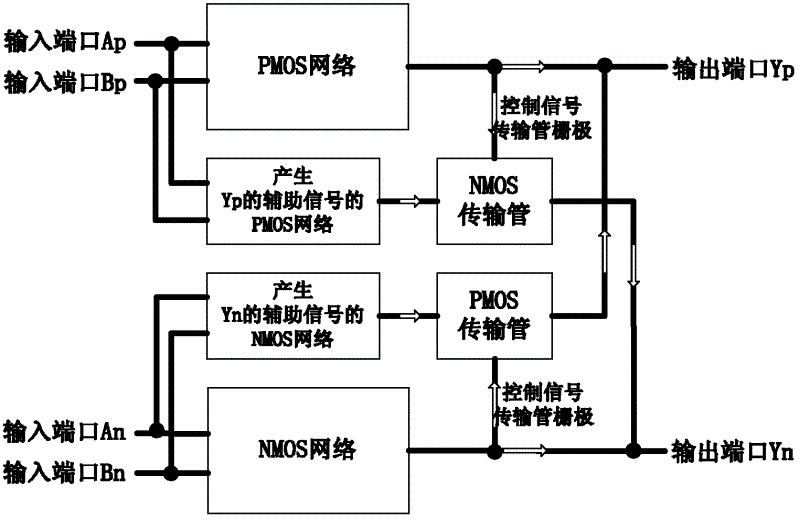

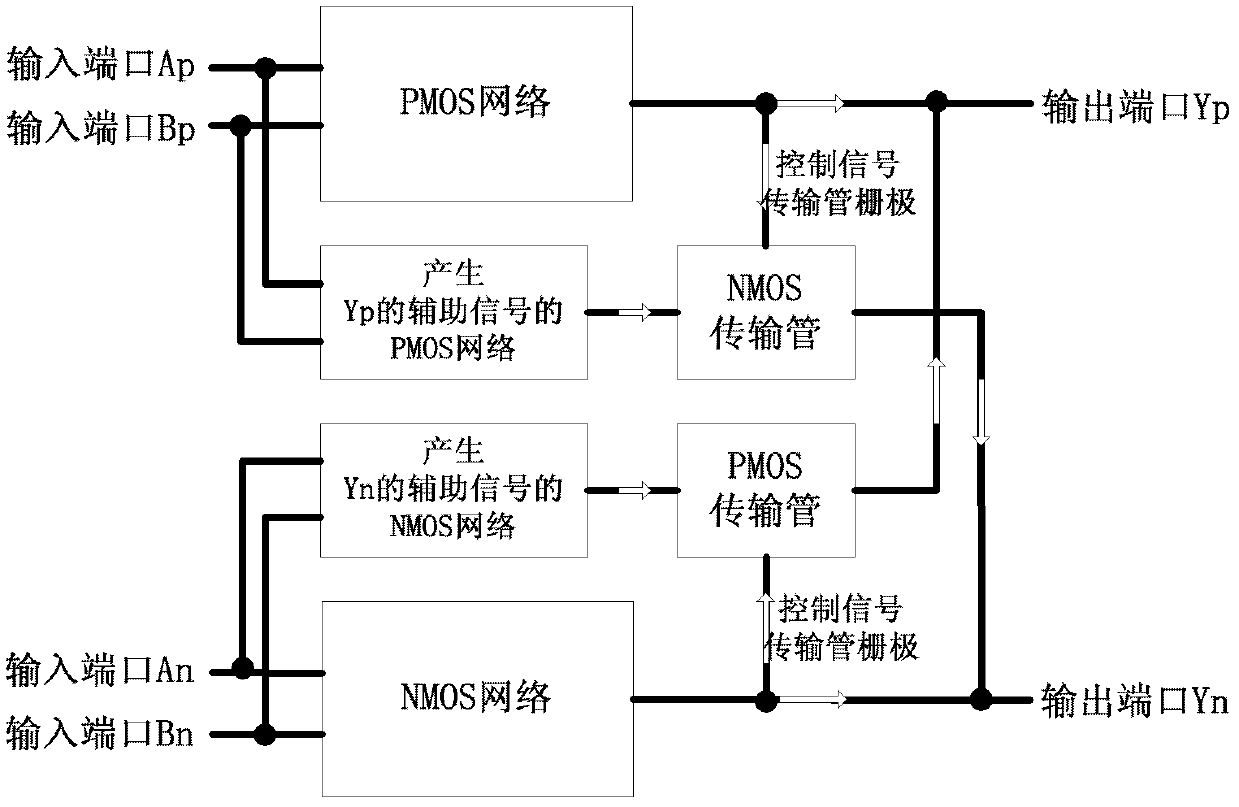

Method for designing complementary data redundancy structure type CMOS (Complementary Metal Oxide Semiconductor) standard cell circuit physical library model

ActiveCN102622481AImprove design efficiencySpecial data processing applicationsEngineeringElectronic design automation

The invention discloses a method for designing a complementary data redundancy structure type CMOS (Complementary Metal Oxide Semiconductor) standard cell circuit physical library model. The method comprises the steps as follows: according to a cell library design flow, finishing the design of a cell circuit diagram and a layout with isolated input and output signals of a PMOS (P-channel Metal Oxide Semiconductor) network and an NMOS (N-channel Metal Oxide Semiconductor) network; virtually connecting the input and output ports of the PMOS network and the NMOS network in the circuit diagram and the layout respectively through auxiliary lines and auxiliary layers; designing a circuit diagram and a layout with functions of not distinguishing the input and output ports of the PMOS network and the NMOS network; and according to the method for designing the physical library model, extracting from the layout added with auxiliary connections to obtain the physical library model satisfying the EDA (Electronic Design Automation) tool format requirements, and setting special grid points and special wiring tracks in technology files at the same time. According to the method, the ultra-large-scale integrated circuit designed by adopting the complementary data redundancy structure type CMOS can be finished by using the semi-custom design based on the standard cell, so that the design efficiency of the circuit is improved.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

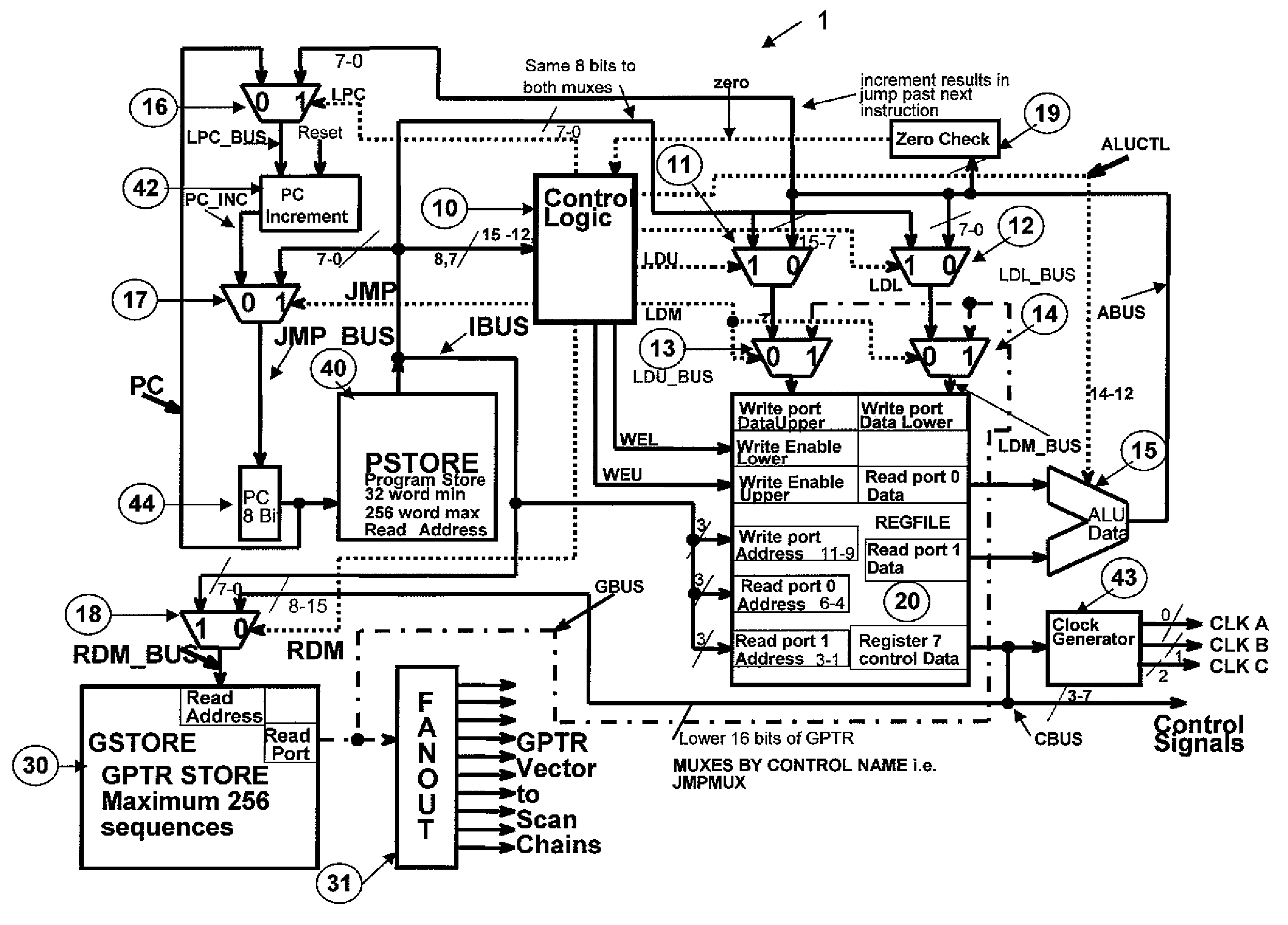

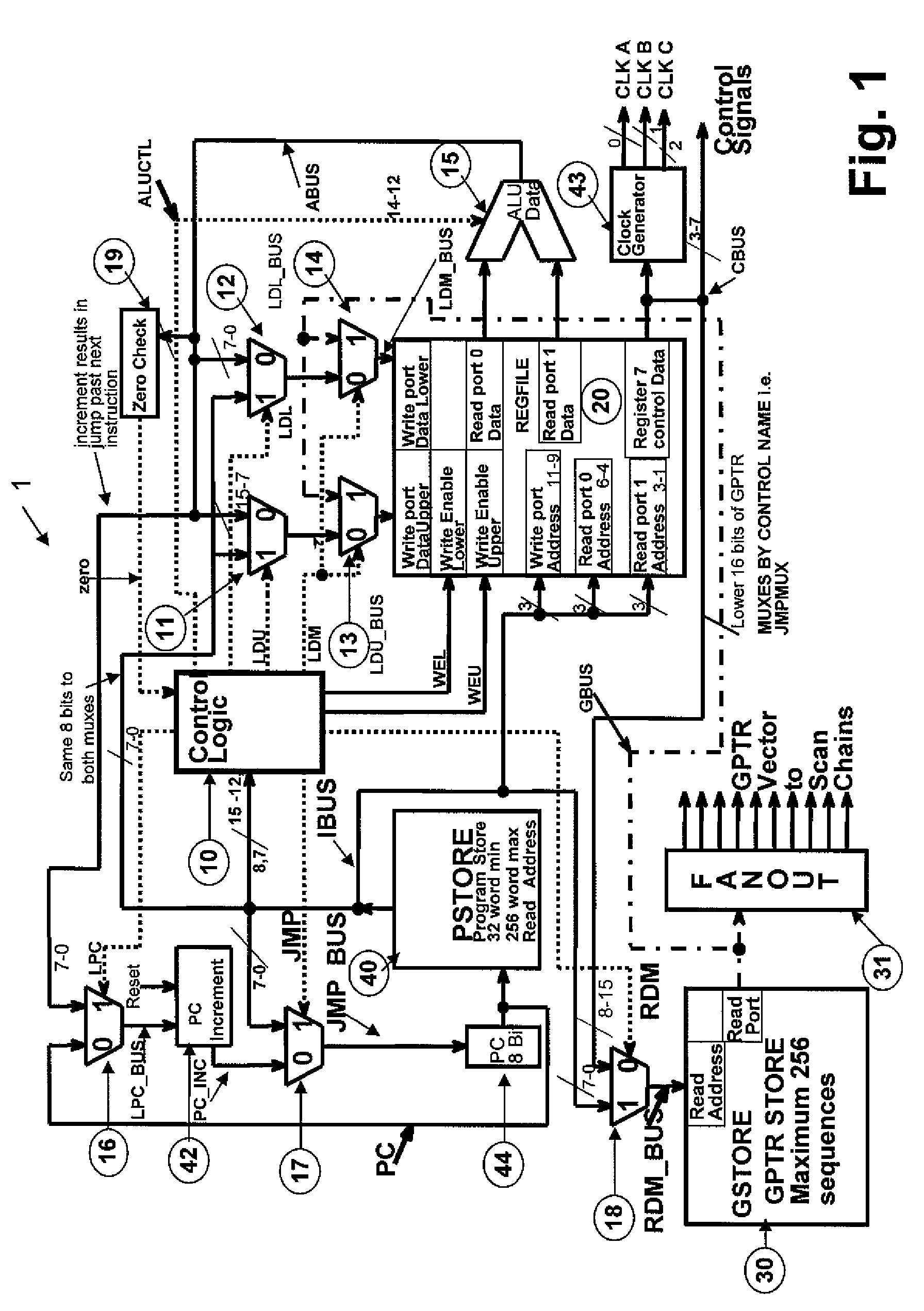

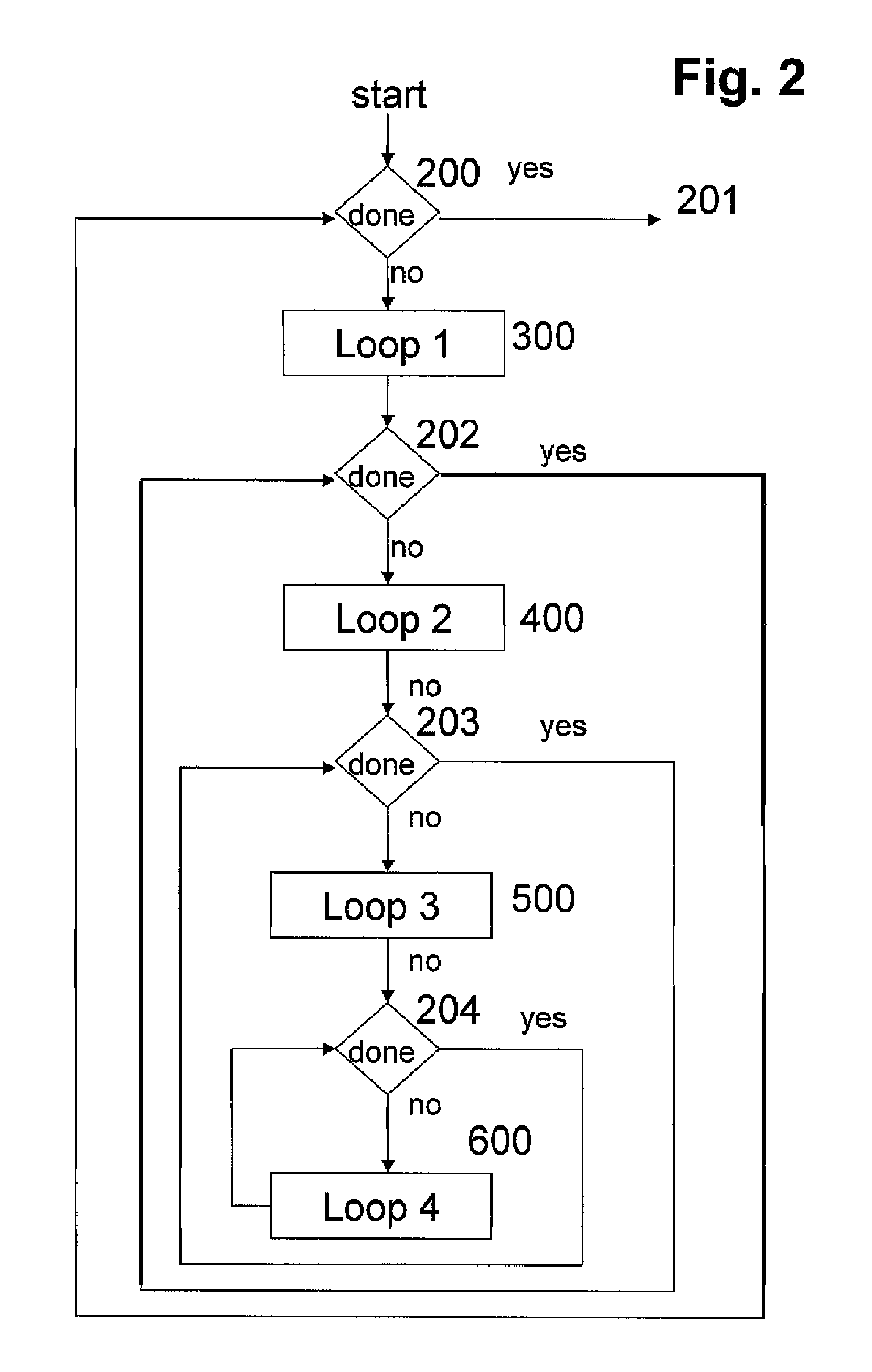

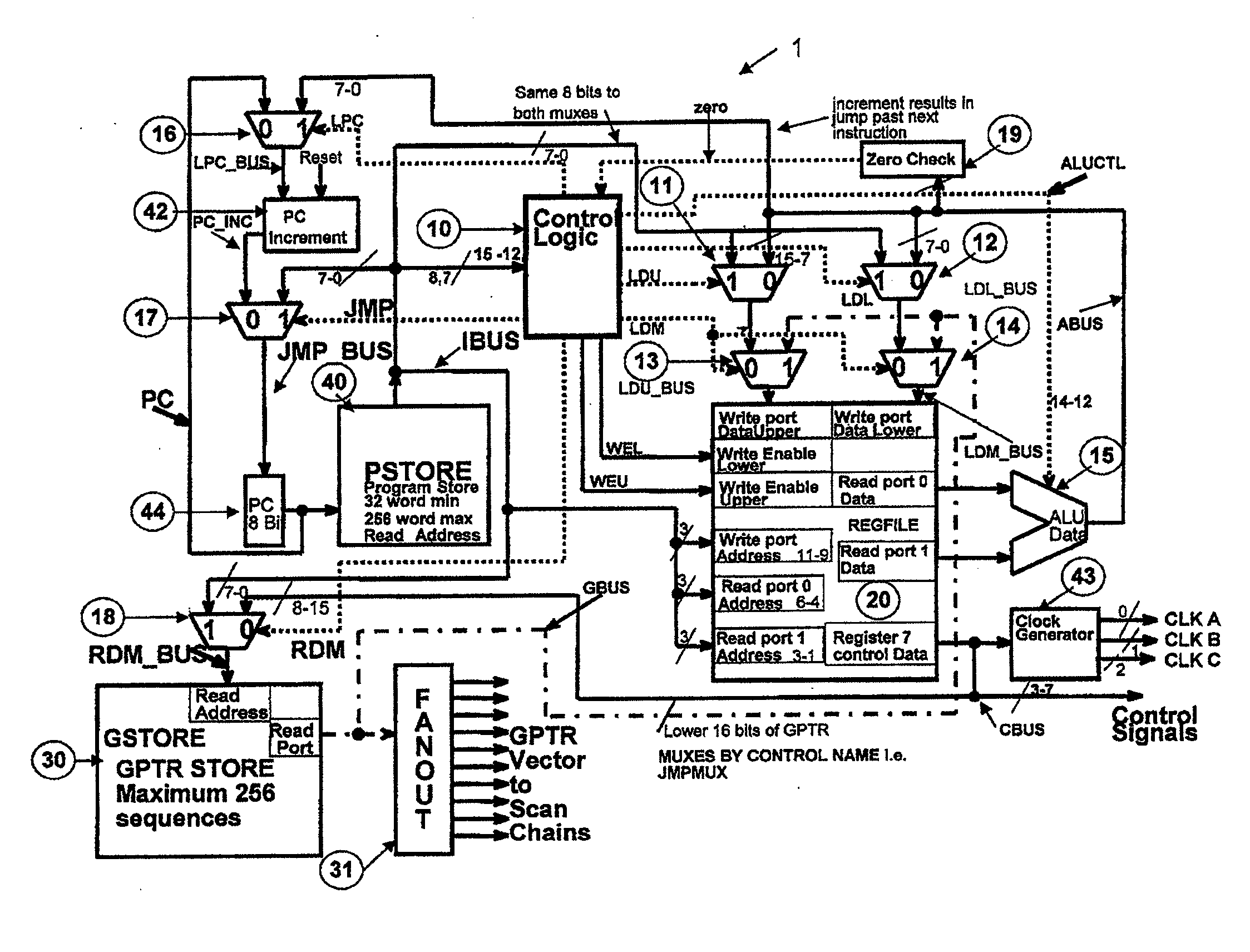

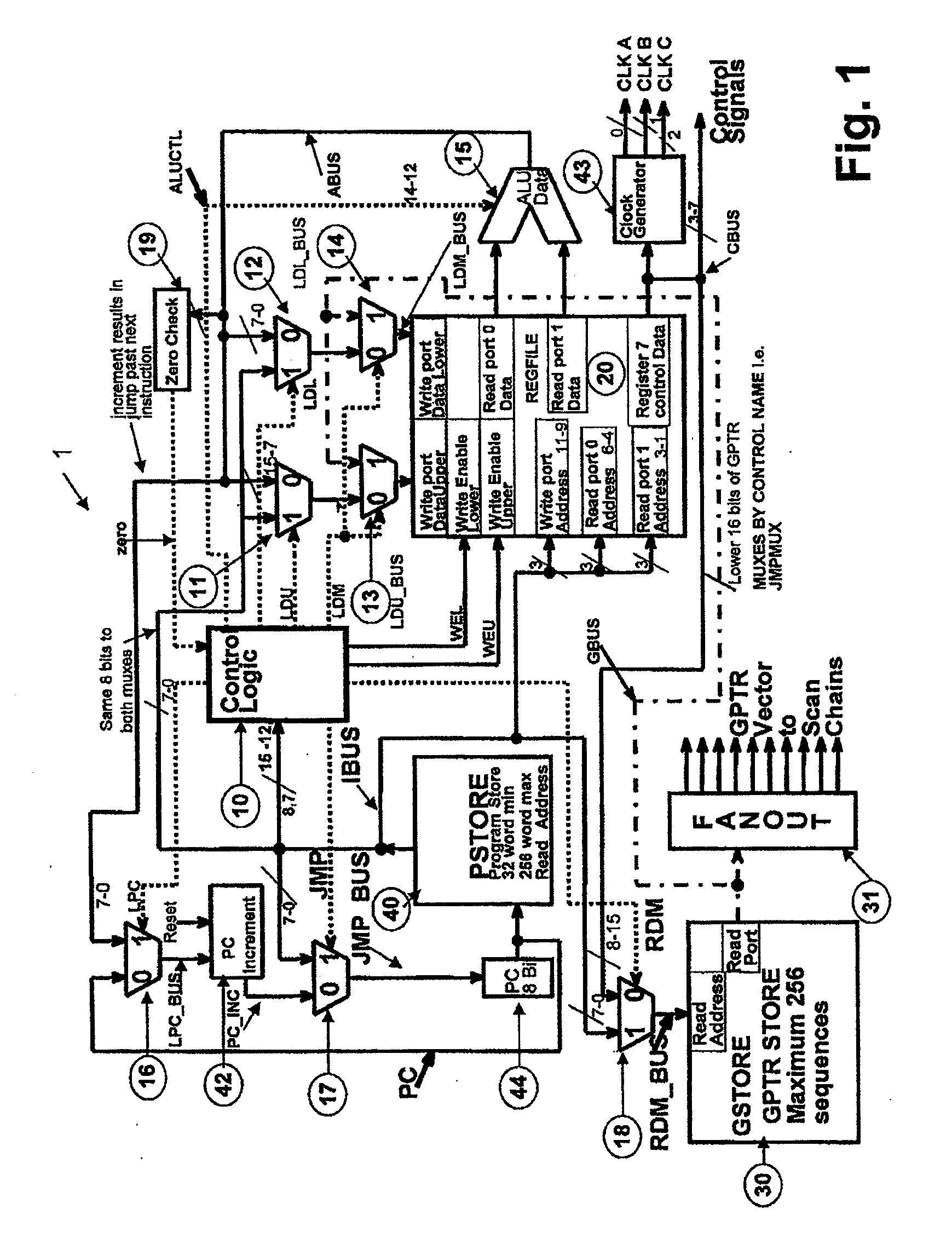

Microcontroller for logic built-in self test (LBIST)

Built-in self-test (BIST) microcontroller integrated circuit adapted for logic verification. Microcontroller includes a plurality of hardware description language files representing a hierarchical description of the microcontroller, the plurality of hardware description language files including a library of circuit design elements, a plurality of library design circuit elements adapted to store a uniquely defined set of input and output signals to enable a logic BIST, and a plurality of latches adapted to store a plurality of values corresponding to a behavioral profile of a test clock.

Owner:MARVELL ASIA PTE LTD

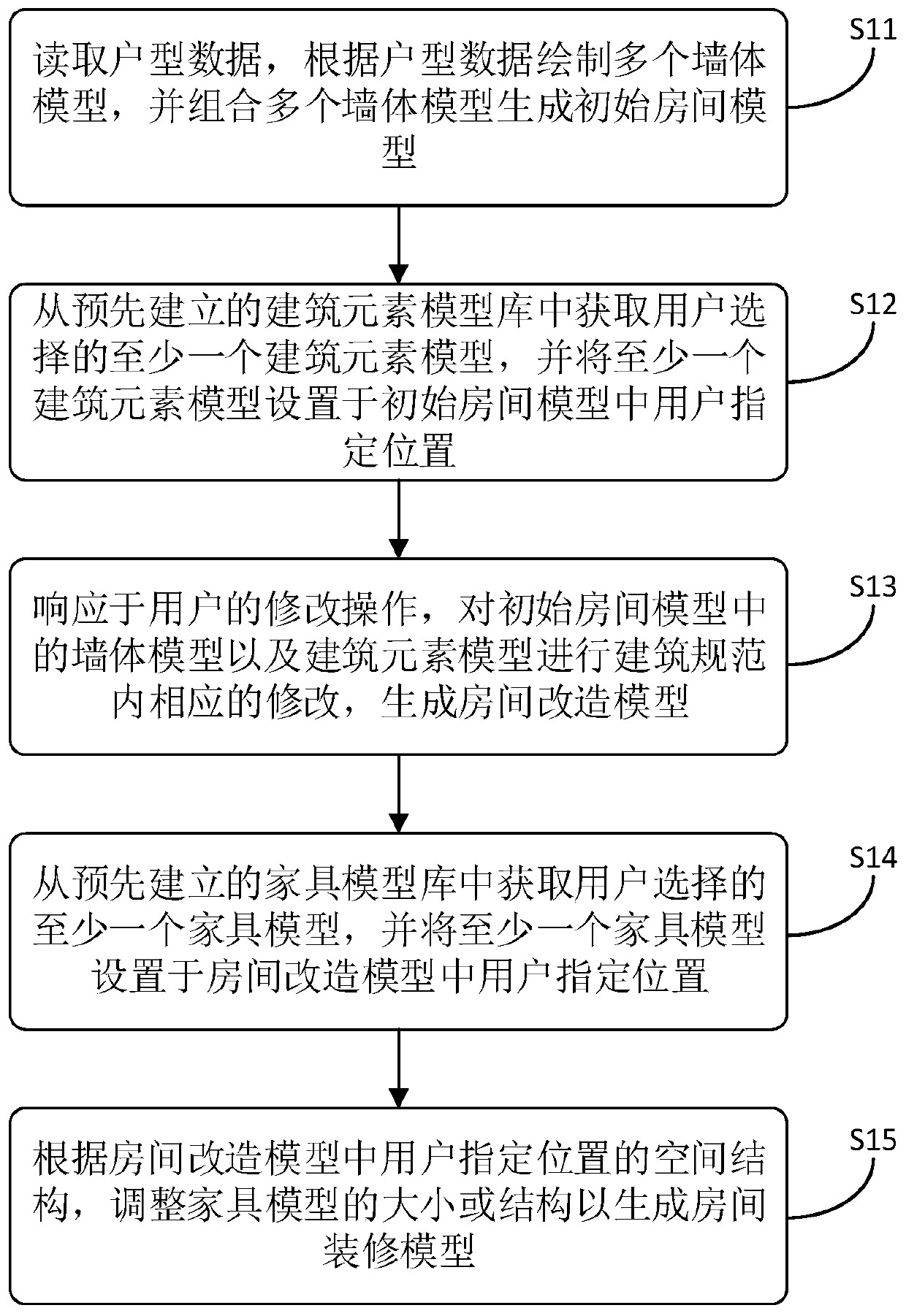

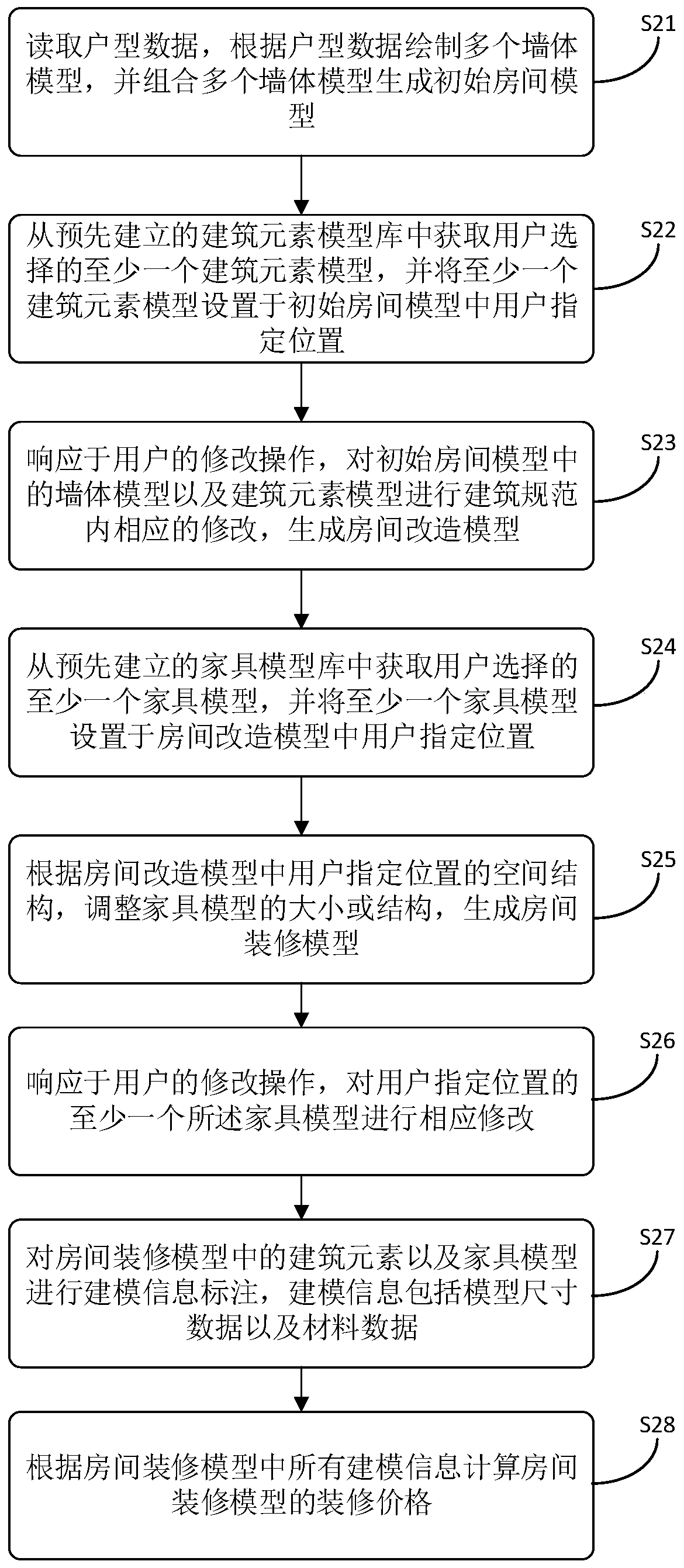

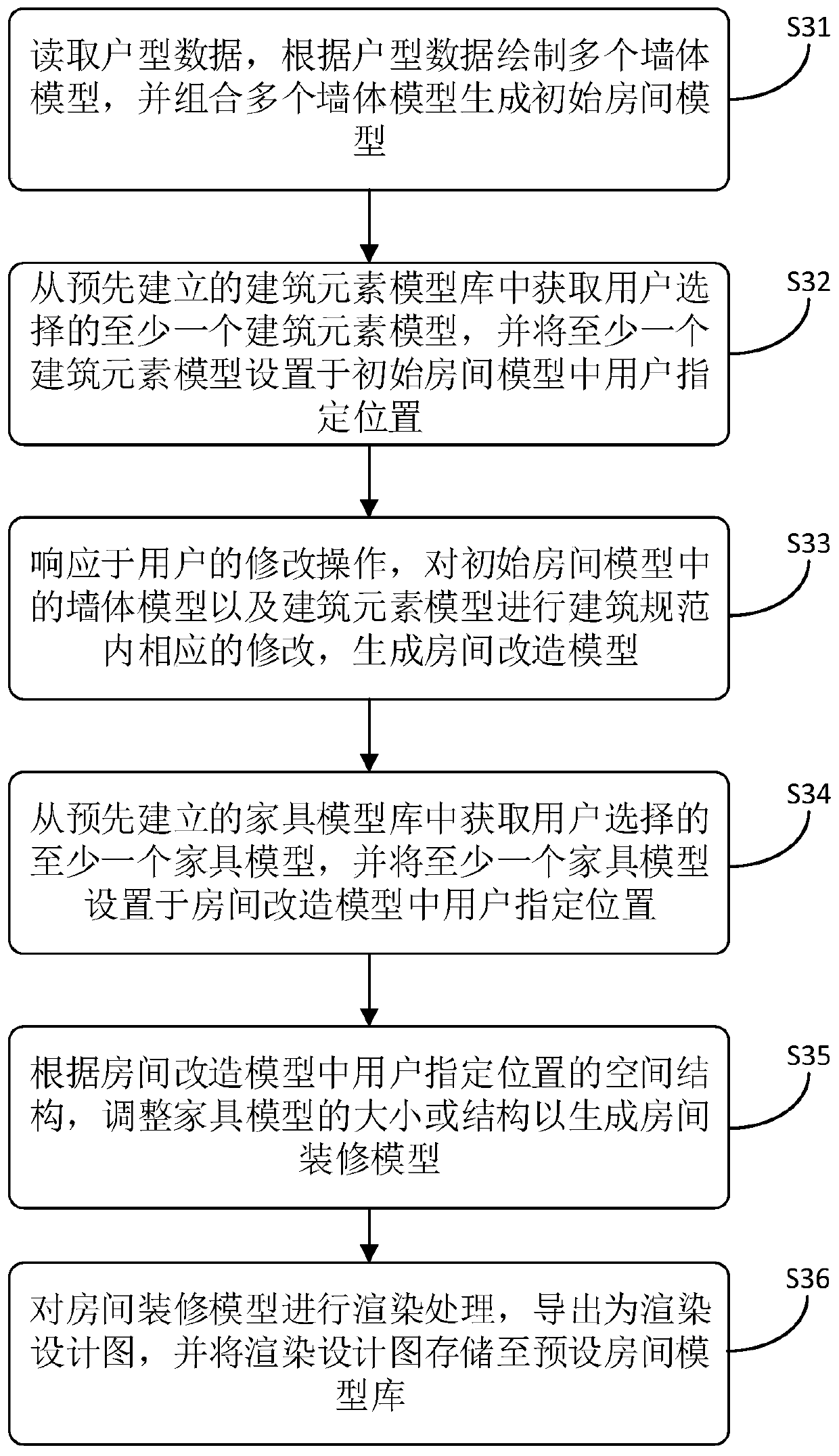

Room model drawing method and device and computer device

The invention provides a room model drawing method and device and a computer device, and the room model drawing method comprises the steps of reading the house type data, drawing a plurality of wall body models according to the house type data, and combining the plurality of wall body models to generate an initial room model; obtaining a building element model selected by a user from a pre-established building element model library, and setting the building element model at a specified position in the initial room model; in response to the modification operation of a user, performing the corresponding modification within the building specification on the wall model and the building element model of the initial room model to generate a room modification model; obtaining a furniture model selected by the user from a pre-established furniture model library, and setting the furniture model at a specified position in the room transformation model; and adjusting the size or structure of thefurniture model according to the space structure at the specified position to generate a room decoration model. According to the room model drawing method, the model making time can be shortened, a model library designed by the user himself / herself is provided, the design difficulty is reduced, and the user experience is improved.

Owner:GUANGDONG SANWEIJIA INFORMATION TECH CO LTD

Standard cell library design inspection method and system and readable storage medium

ActiveCN111709213AReduce repetitive workRepeated work hasComputer aided designSpecial data processing applicationsAlgorithmStandard cell

The invention discloses a standard cell library design inspection method and system and a readable storage medium. The method comprises the following steps: setting a verification condition, selectingstandard units in a standard unit library by using a random selection mode, splicing and placing the standard units on a layout according to a random splicing mode until the verification condition ismet, and finally carrying out design inspection on the randomly spliced layout of the formed standard unit library. By means of the standard cell library design checking method, high-coverage-rate rule checking can be completed in the design stage of a standard cell layout, repeated work in the standard cell library building process is reduced, due to the fact that the method has full randomness,the coverage rate of the technical scheme is higher than that of the scheme in the prior art, and the probability of problems occurring when the standard cell library is used for splicing in the later period can be effectively reduced.

Owner:CHENGDU LIGHT COLLECTOR TECH

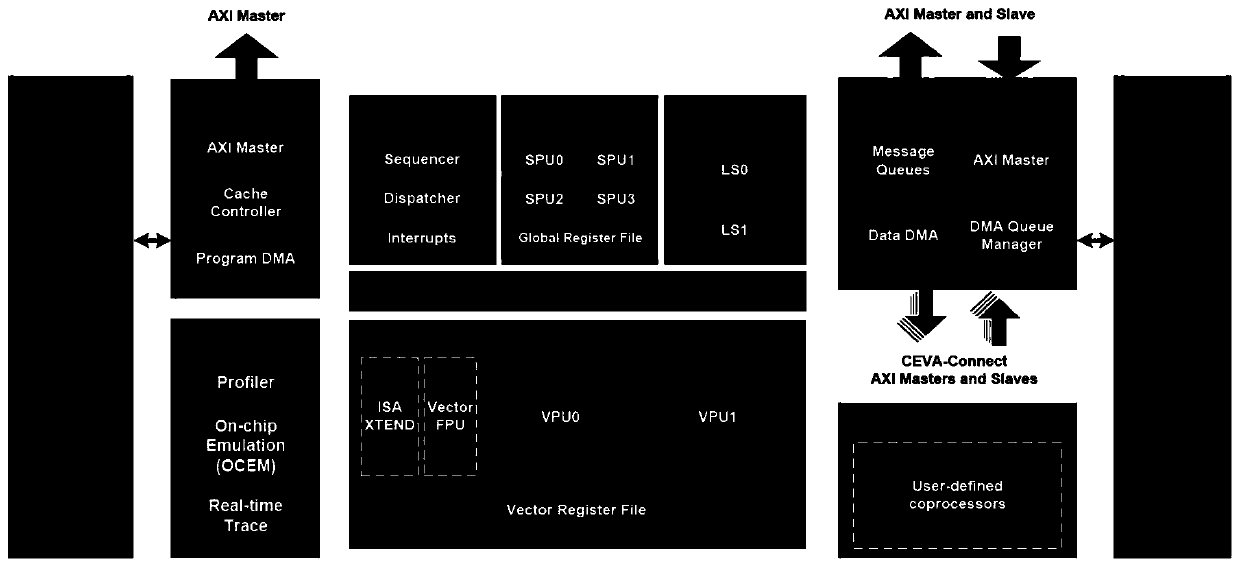

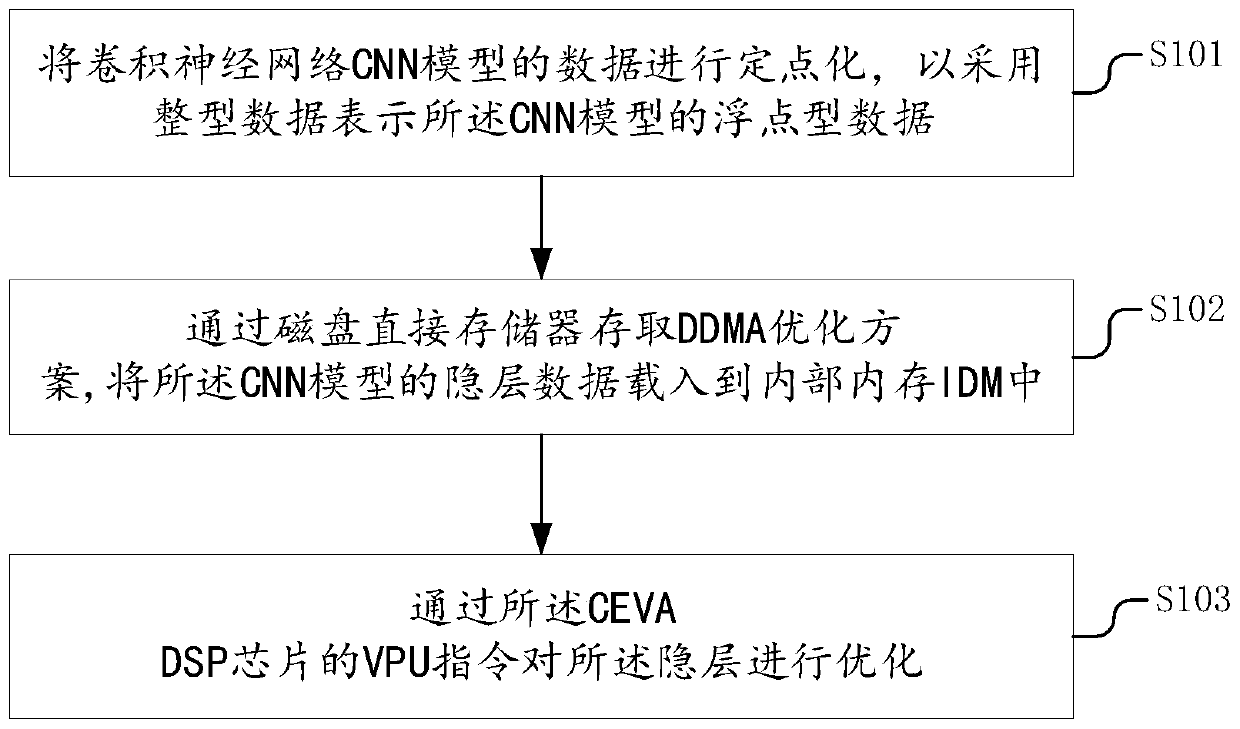

Acceleration library design method, terminal equipment and storage medium

The invention is suitable for the technical field of computers, and provides an acceleration library design method, terminal equipment and a storage medium, and the method comprises the steps: carrying out the fixed-point processing of the data of a CNN (Convolutional Neural Network) model, and employing integer data to represent the floating point type data of the CNN model; loading hidden layerdata corresponding to a hidden layer of the CNN model into an internal memory IDM through a disk direct memory access DDMA optimization scheme; and according to the hidden layer data loaded into the IDM, calculating the hidden layer data through a vector processing unit VPU of the CEVA DSP chip so as to optimize the CNN model. The acceleration library is optimized through the DDMA technology and the VPU instruction, most operation of the CNN model is supported, the acceleration library can be transplanted into an existing forward reasoning engine, the existing forward reasoning engine supportsDSP optimization, and a new forward reasoning framework is developed on the basis of the acceleration library.

Owner:TP-LINK

Microcontroller for logic built-in self test (LBIST)

Built-in self-test (BIST) microcontroller integrated circuit adapted for logic verification. Microcontroller includes a plurality of hardware description language files representing a hierarchical description of the microcontroller, the plurality of hardware description language files including a library of circuit design elements, a plurality of library design circuit elements adapted to store a uniquely defined set of input and output signals to enable a logic BIST, and a plurality of latches adapted to store a plurality of values corresponding to a behavioral profile of a test clock.

Owner:MARVELL ASIA PTE LTD

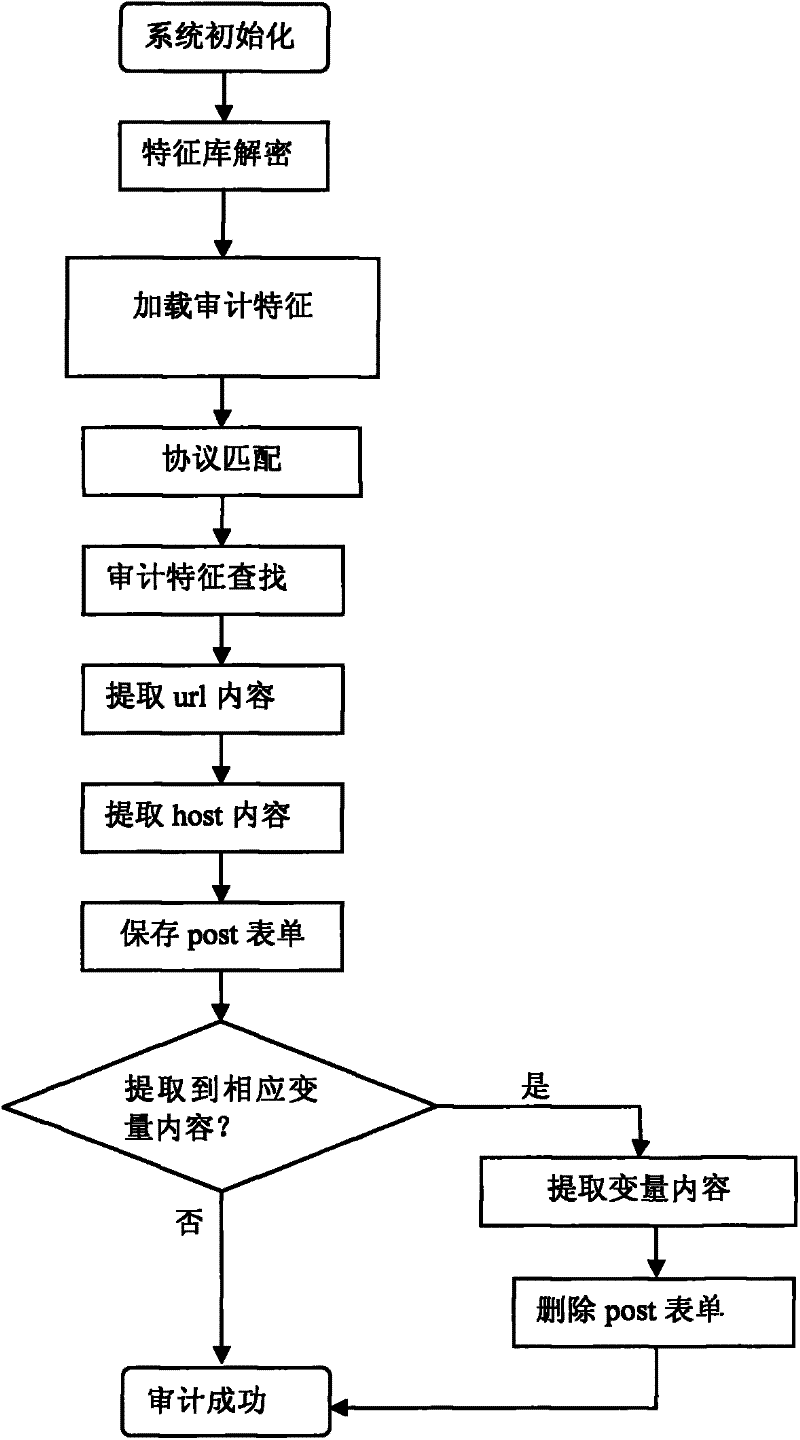

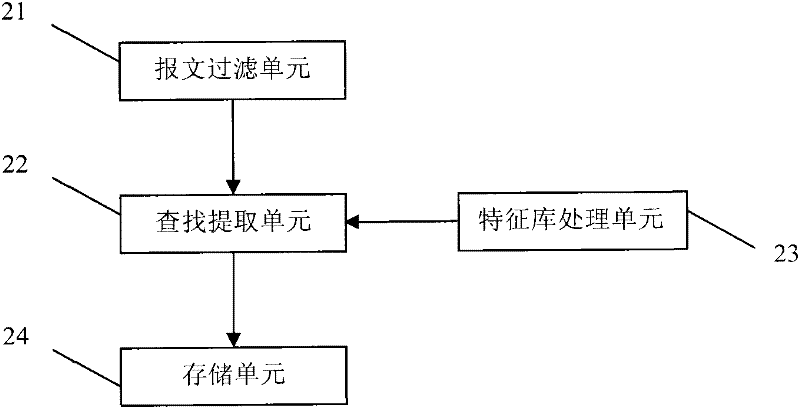

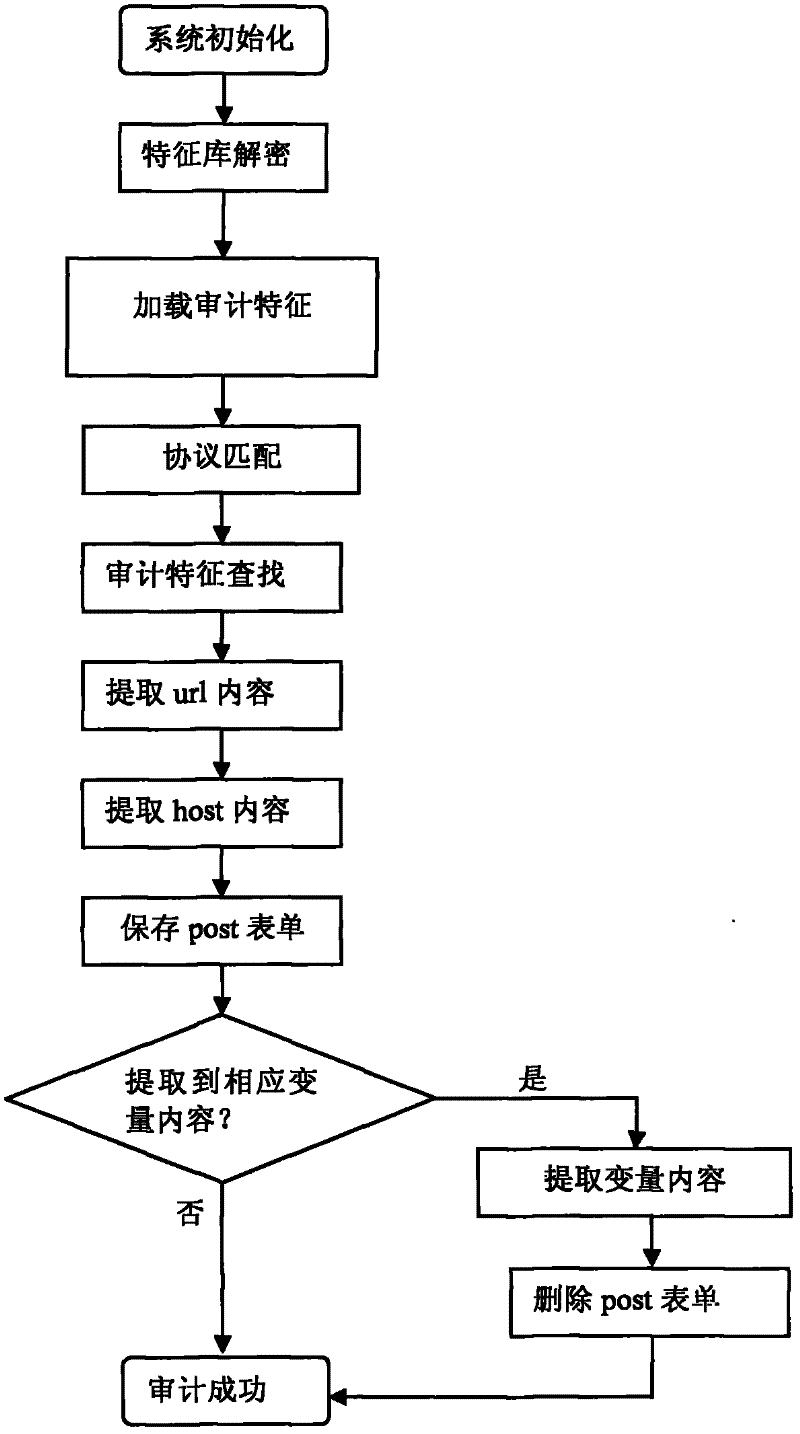

A method and device for auditing BBS messages

The invention provides a solution for auditing BBS messages, which is applied to network equipment and used for auditing BBS messages. The present invention firstly defines the general BBS protocol features, and filters out the BBS messages from the Internet messages flowing through the network equipment accordingly; Extract the corresponding variable content in the text and save it. On this basis, the present invention further provides the design of the dynamic loading feature library. The invention can improve the efficiency of forum auditing, is more convenient for users to use, and can effectively reduce the workload of developers.

Owner:HANGZHOU DPTECH TECH

IC design to optimize manufacturability

Library design elements (102) are analyzed for manufacturability to be used in designing an IC chip to be manufactured using a particular manufacturing process. The library design elements from a library are obtained. Manufacturability attributes (104) of the library design elements are determined for the particular manufacturing process, where manufacturability attributes include yield-related attributes. Library views (106) with manufacturability attributes for the library design elements are then generated, which are utilizing by an electronic design automation (EDA) tool.

Owner:PDF SOLUTIONS INC

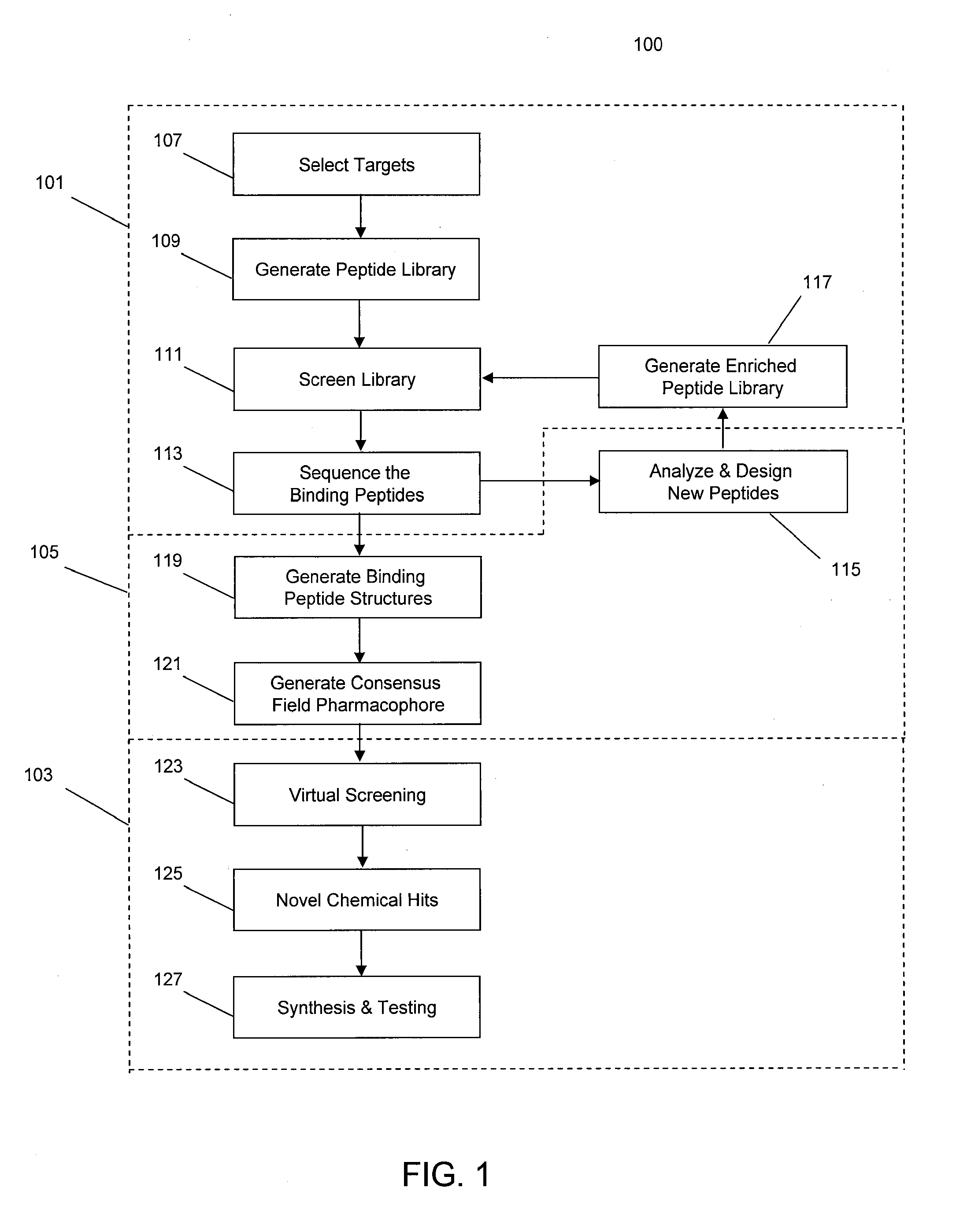

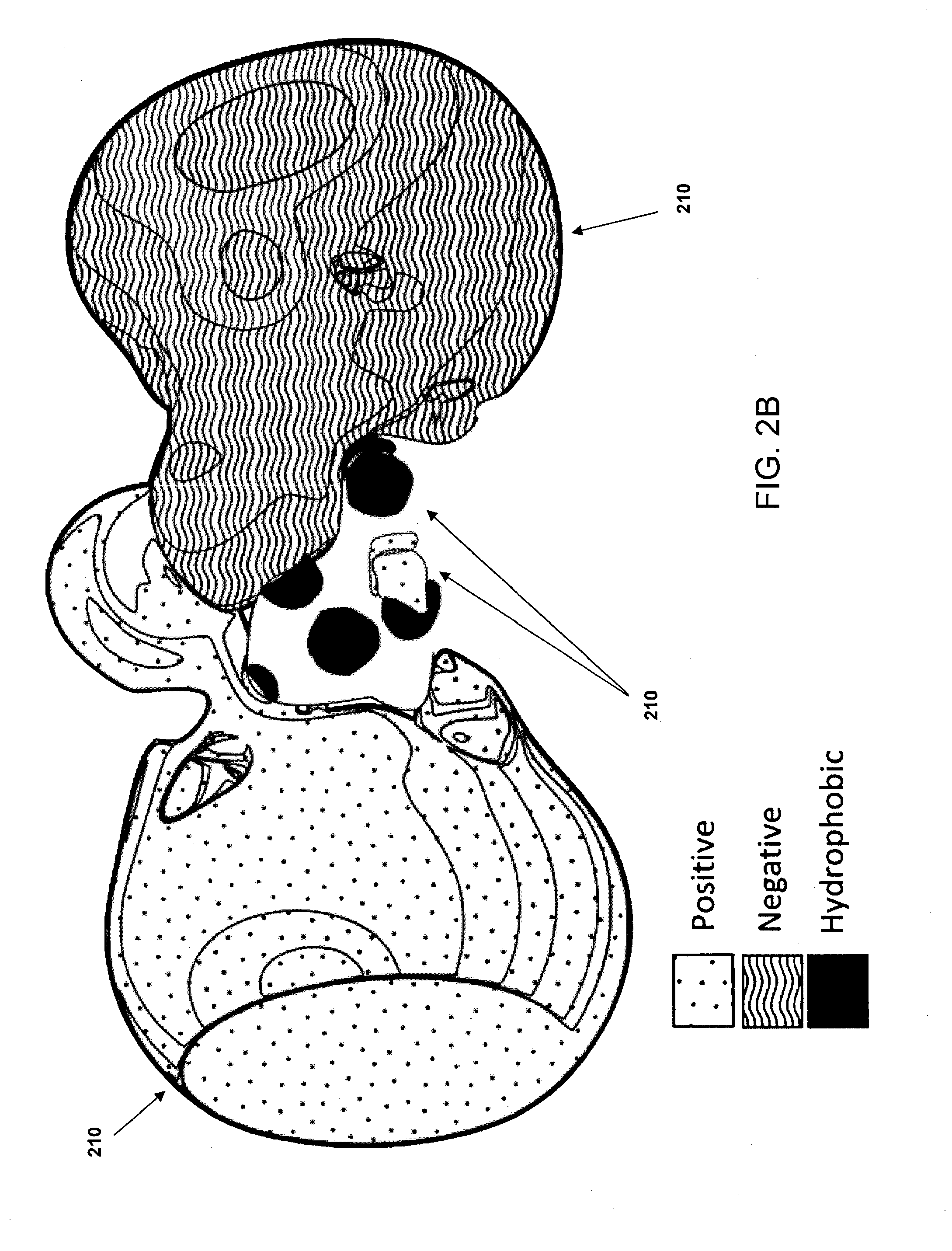

Methods and systems for optimization of peptide screening

The invention provides systems and methods for improved peptide screening library design. In some implementations the systems and methods utilize screening data relating to a plurality of peptides used in a peptide screen against a target molecule to construct a consensus binding sequence alignment using least a subset of the plurality of peptides. For one or more positions of the sequence alignment an observed distance matrix is constructed, the matrix describing a distance between the relative binding activity of pairwise comparisons of each amino acid in a given position. The observed distance matrix is then compared to a plurality of molecular field-based amino acid substitution matrices so as to identify one or more preferred amino acids for use in the design of novel predicted binding peptide sequences for a subsequent peptide screen.

Owner:BIOLAUNCHER

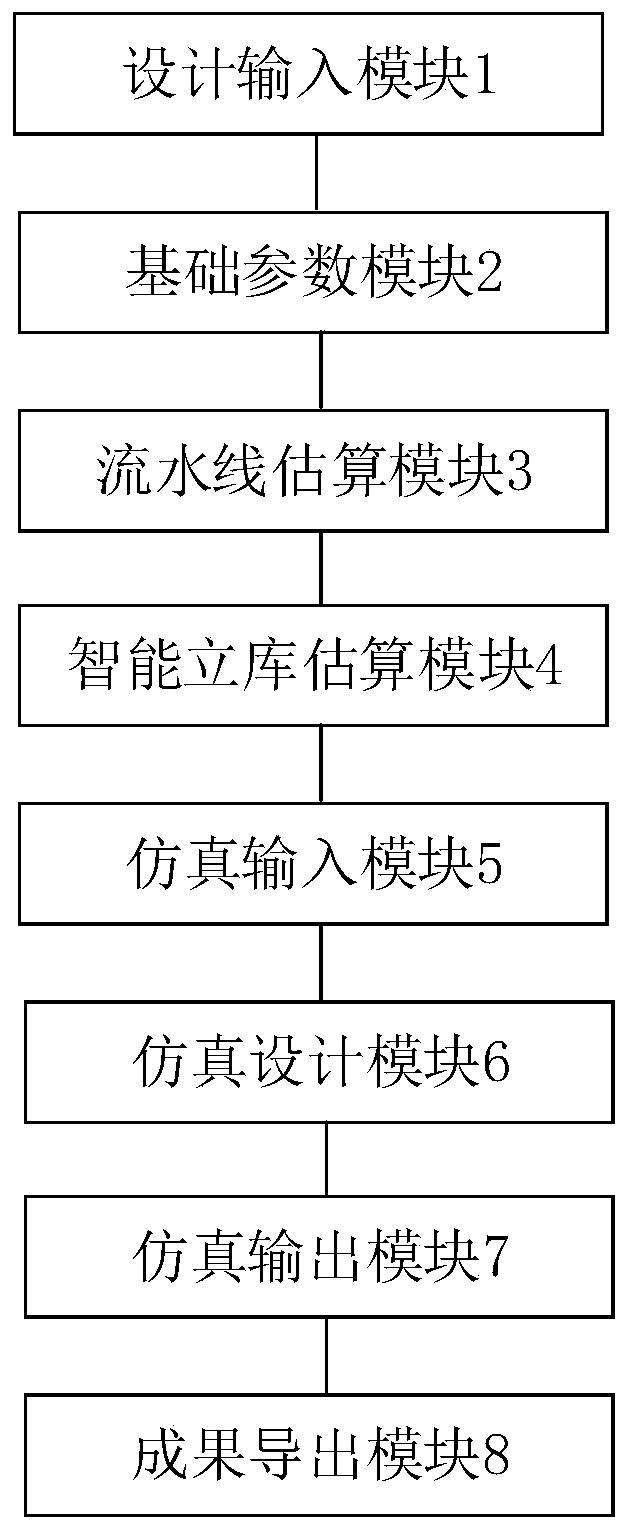

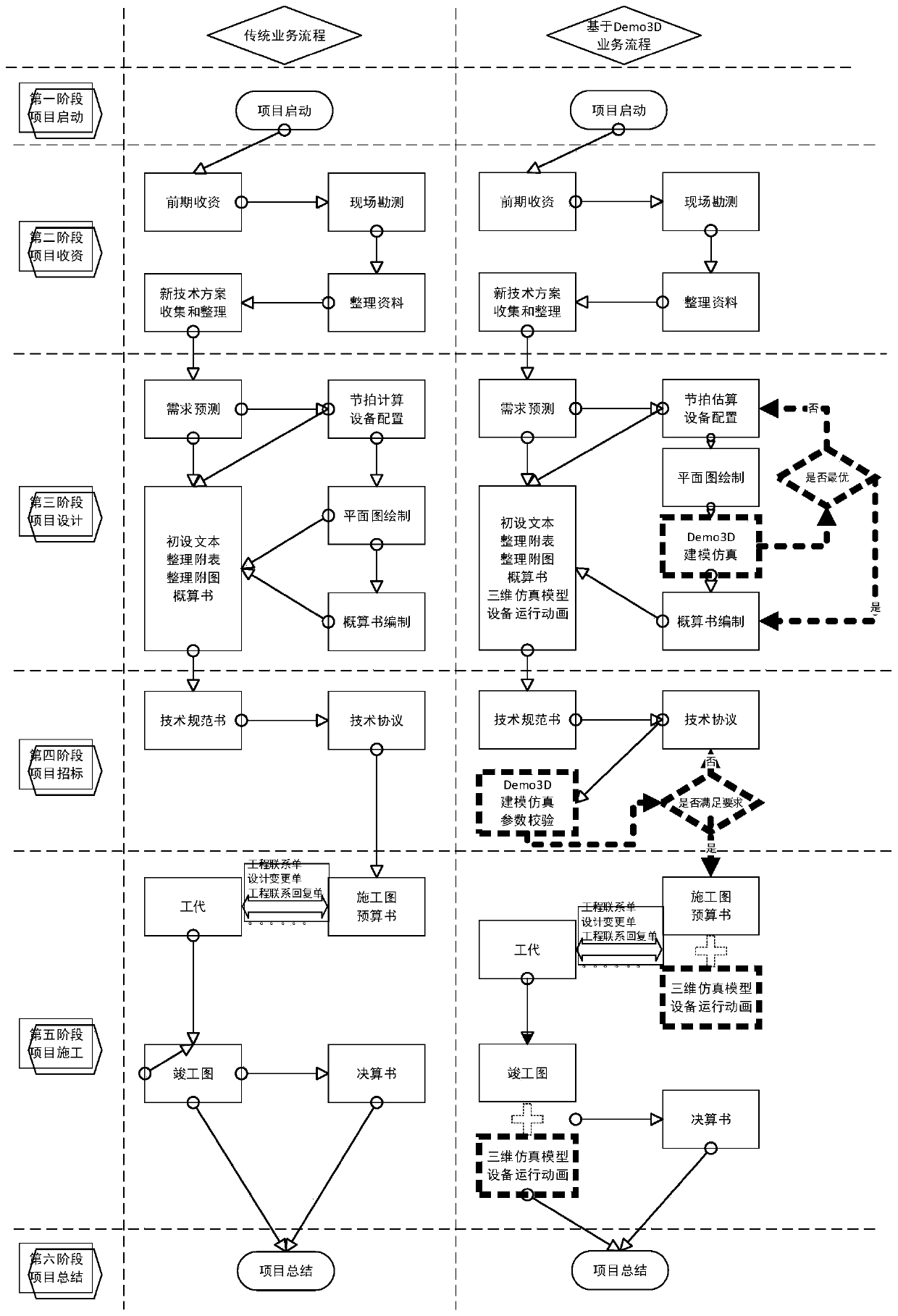

Four-line one-library design management system based on Demo3D simulation

ActiveCN110516408ARealize the whole process managementHigh feasibilitySpecial data processing applicationsAssembly lineComputer science

The invention discloses a four-line one-library design management system based on Demo3D simulation. The four-line one-library design management system comprises a design input module, a basic parameter module, an assembly line estimation module, an intelligent library estimation module, a simulation input module, a simulation design module, a simulation output module and an achievement export module. According to the invention, scattered, dynamic and changeable related data can be systematically associated together, and the whole process management of the design scheme is realized, so that the feasibility, scientificity and economy of the design scheme are effectively improved.

Owner:CHINA ENERGY ENG GRP GUANGDONG ELECTRIC POWER DESIGN INST CO LTD

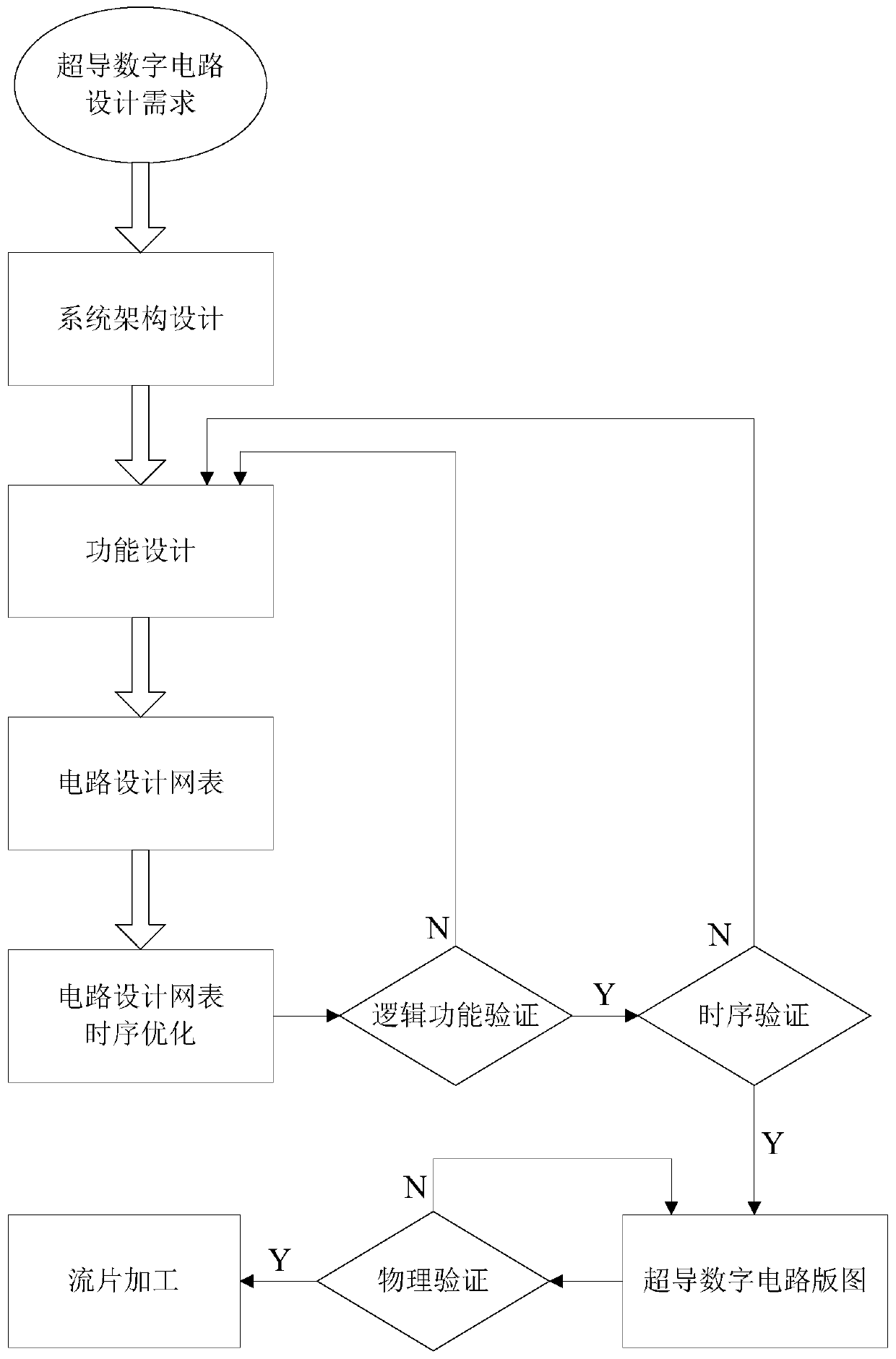

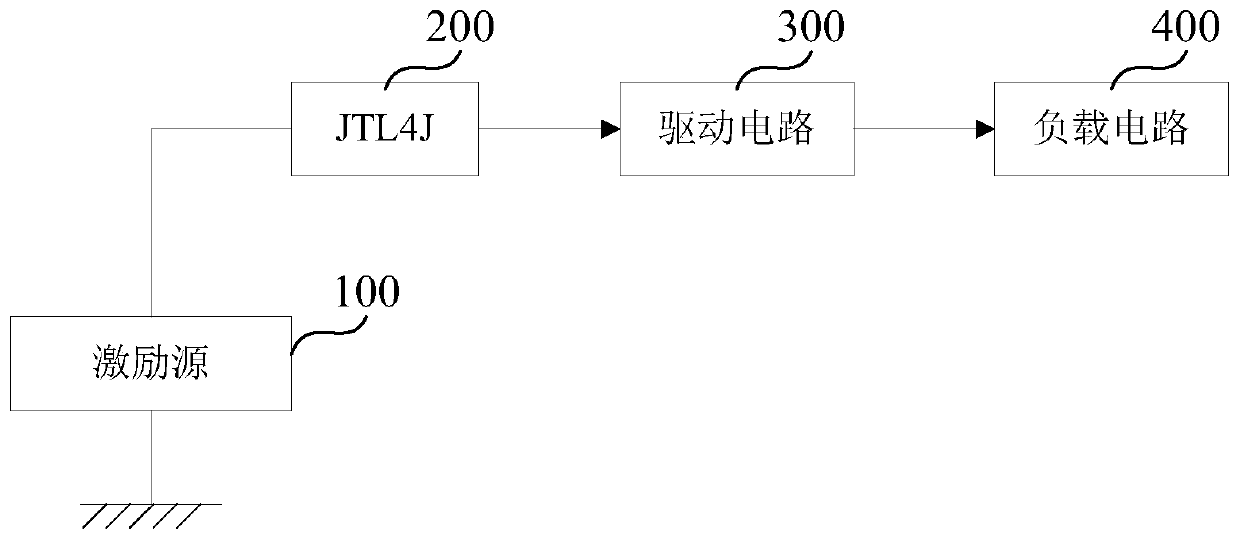

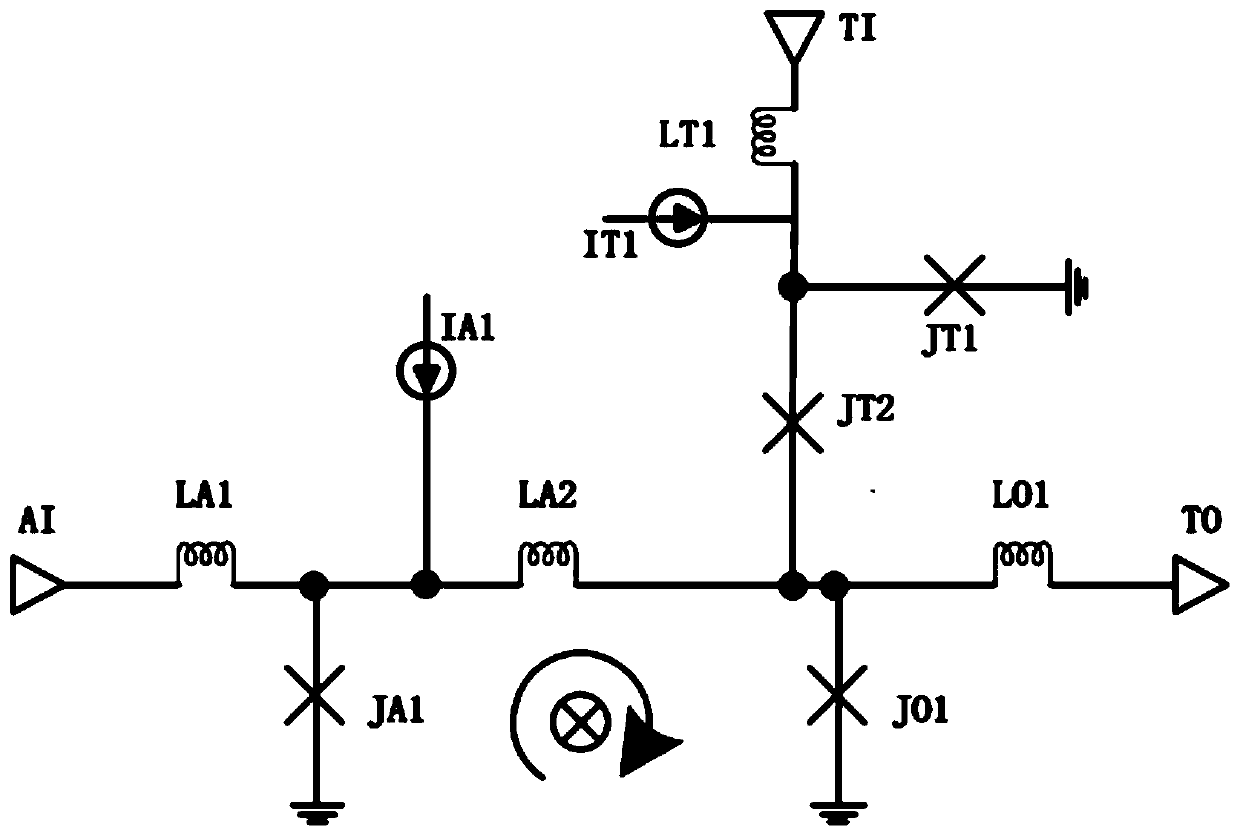

Superconducting digital circuit design method

ActiveCN110032792ATiming stabilityOptimize timingSpecial data processing applicationsSystem architecture designEngineering

The invention provides a superconducting digital circuit design method. The method comprises the steps of performing system architecture design and function design based on design requirements of a superconducting digital circuit, and then generating a circuit design netlist; performing magnetic flux storage capacity detection on all ports of all unit circuits on any data path in the circuit design netlist, and when the ports have the magnetic flux storage capacity, adding a buffer unit at the port to optimize the time sequence of the circuit design netlist, thereby obtaining a terminal circuit design netlist; and performing logic function verification and time sequence verification on the terminal circuit design netlist to generate a superconductive digital circuit layout, and performingphysical verification on the superconductive digital circuit layout to complete the design of the superconductive digital circuit. According to the invention, the problem that the time sequence analysis accuracy of the superconducting digital circuit is lower due to the fact that different loads are connected behind the same superconducting digital unit circuit when the superconducting digital circuit is designed by adopting a unit library design method in the prior art is solved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Artificial intelligence updating method of digital aircraft simulation model

PendingCN109002661ASmart correction worksReduce workloadGeometric CADDesign optimisation/simulationSimulationModel revision

The invention discloses an artificial intelligence correction method of a digital aircraft simulation model, comprising the following steps: (1) knowledge base design and maintenance; (2) the design and maintenance of the method library; (3) algorithm library design and maintenance; (4) Result presentation process: analysis and correction results automatically generate analysis report. The invention can solve the problem of aircraft simulation model revision by simulating the process of human revision of the simulation model, and improves the efficiency and correctness of the simulation modelrevision.

Owner:BEIHANG UNIV

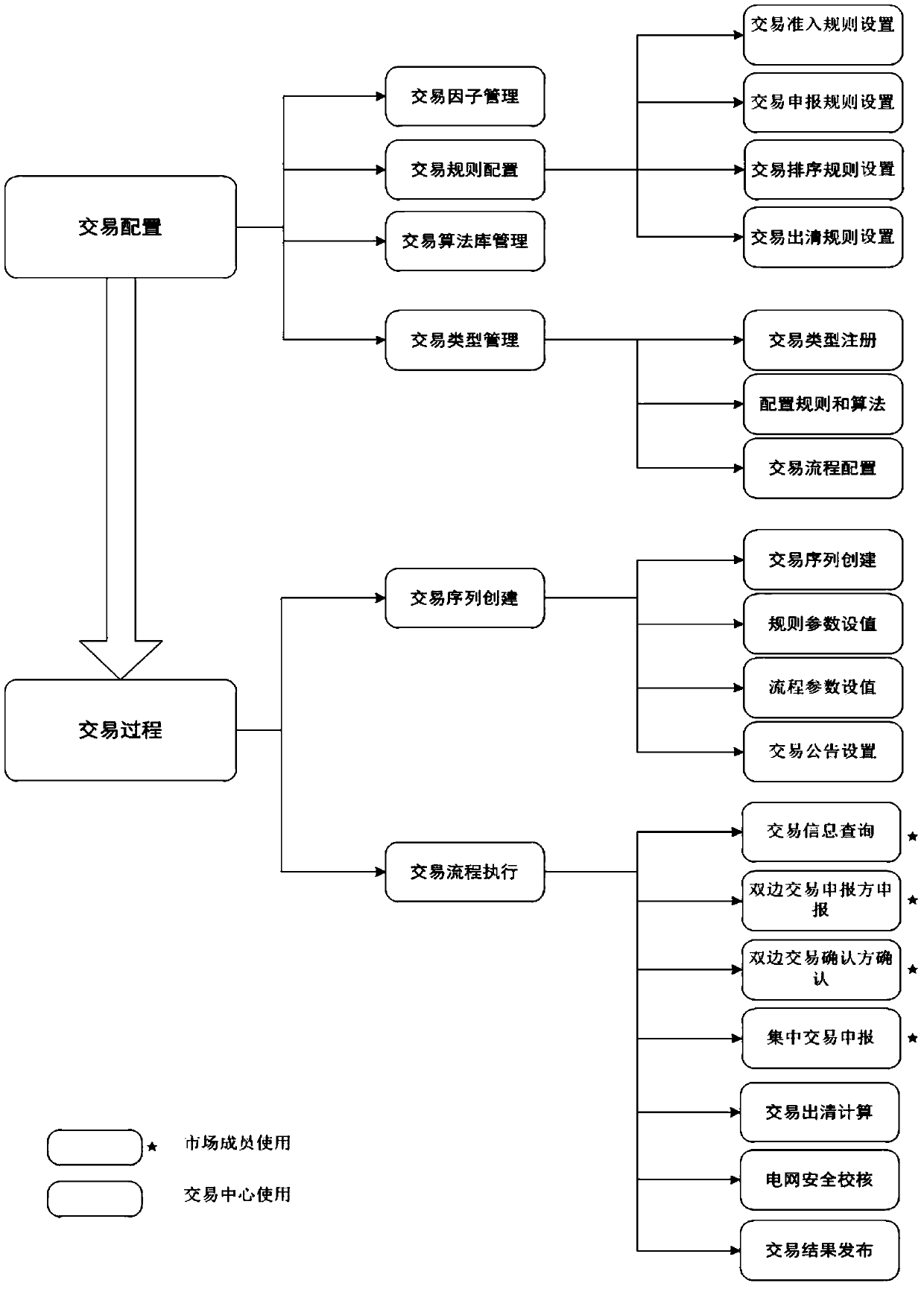

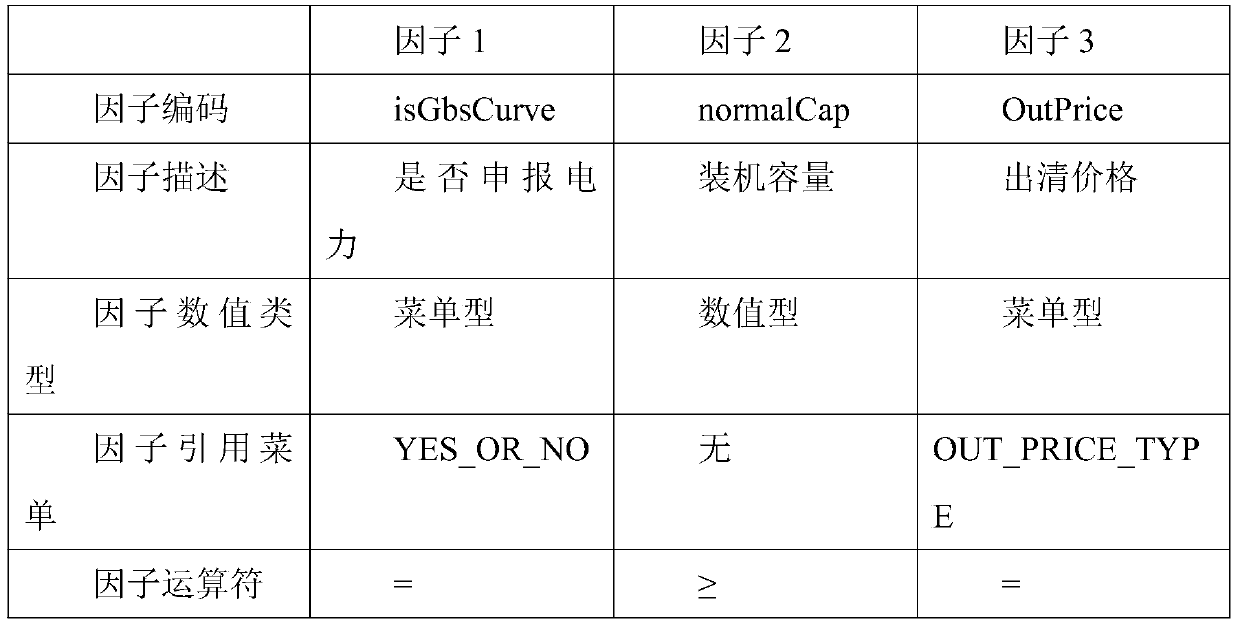

Power transaction management method based on multi-factor combination modeling and power transaction management system thereof

InactiveCN105512895AQuick supportFlexible to adapt to changes in trading rulesCommercePower marketComputer science

The invention relates to a power transaction management method based on multi-factor combination modeling and a power transaction management system thereof. The method comprises the following steps: (1) describing the characteristic parameters of a variety of transactions based on a transaction factor model; (2) selecting transaction factors, setting the operation logic between the factors, and forming access rules, declaration rules, sorting rules and clearing rules; (3) providing four standard transaction clearing algorithms based on a component library design idea, and supporting online registration of new algorithms; (4) registering transaction types, associating rules and algorithms, and configuring a process; and (5) releasing a transaction sequence, and conducting a transaction in accordance with the process. According to the invention, a power transaction factor combination modeling method is adopted, factors affecting the transaction process are converted into parameters and combined into declaration rules, access rules, sorting rules and clearing rules, and a transaction management system is established based on a transaction standard algorithm and process management. The method and the system can adapt to the demand for a national unified power market, support multiple transaction varieties, and adapt to the change of transaction rules.

Owner:STATE GRID CORP OF CHINA +1

Area efficient power switch

A method of generating an area efficient power switch cell includes receiving, by a cell library design tool, a specification of a power switch circuit to be established as a power switch cell in a cell library. The cell library design tool also receives one or more attributes of the power switch cell including a height of the cell boundary and receiving, by the cell library design tool, a layout placement constraint requiring the power switch cell to be placed in a semiconductor layout so as to bridge two parallel rows of doped wells. The parallel rows of doped wells are interleaved with doped substrate and the doping of the wells is of a different type than that of the substrate. Based on the specification of the power switch circuit, the one or more attributes, and the layout placement constraint, the cell library design tool generates the power switch cell.

Owner:APPLE INC

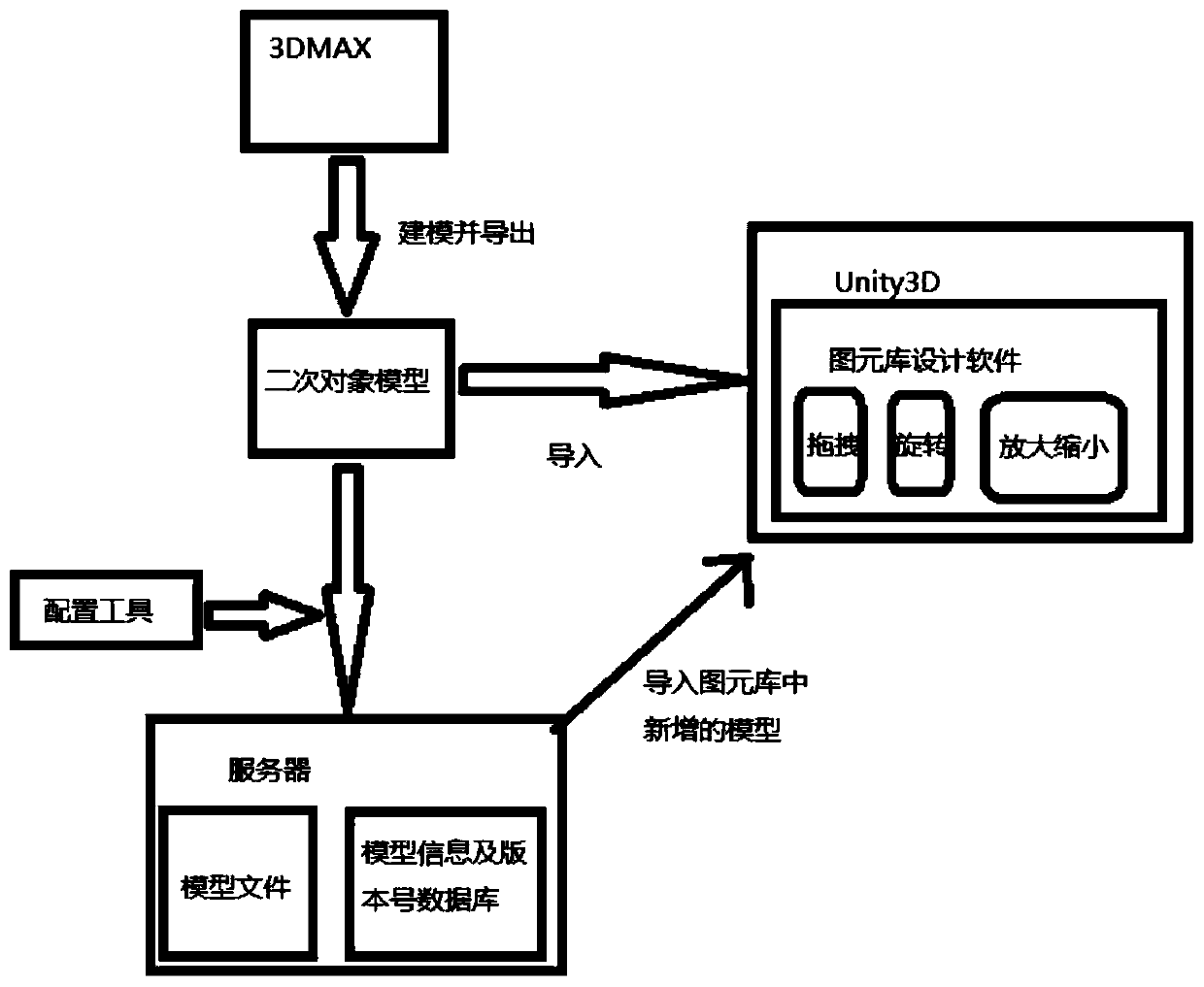

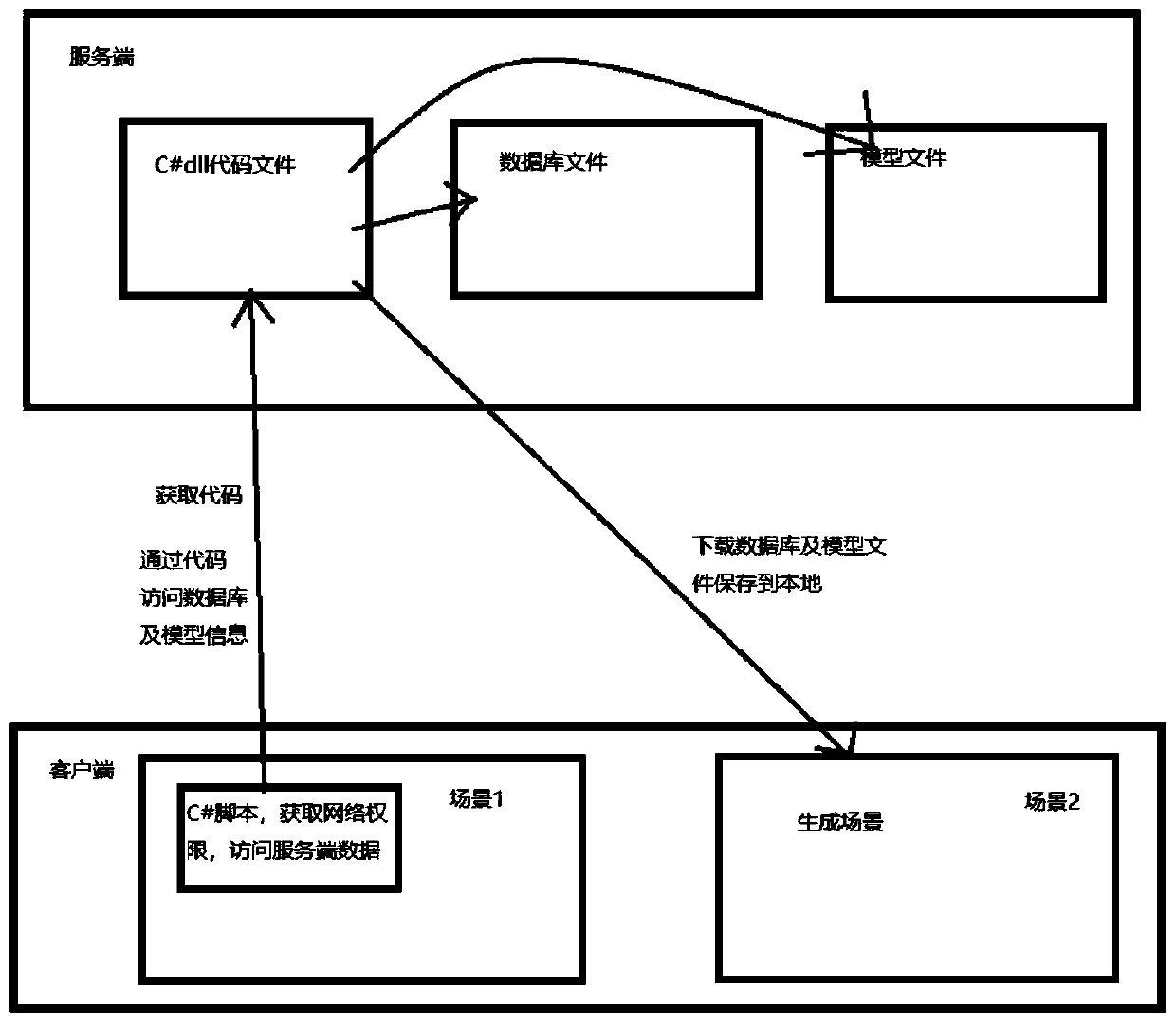

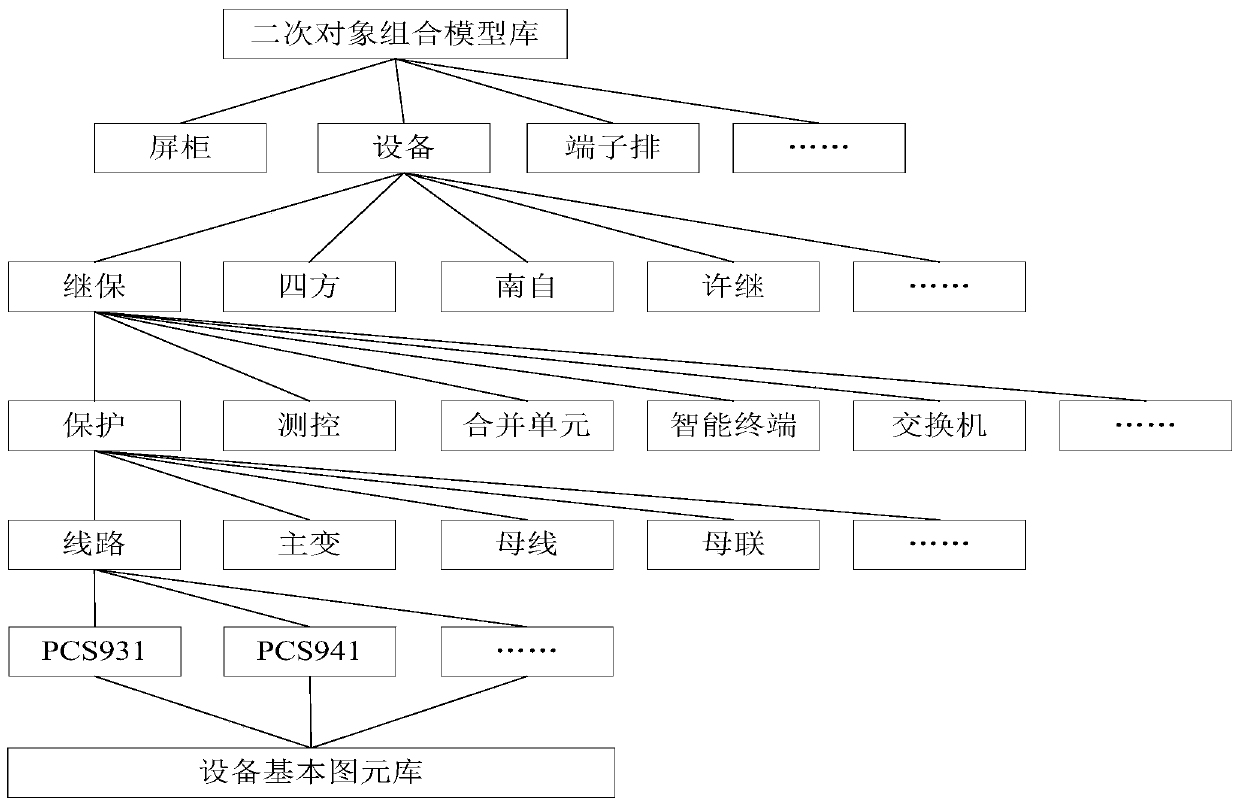

Secondary object primitive library design system of intelligent substation

PendingCN110766567AClear scopeClear depthData processing applicationsDesign optimisation/simulationSoftware engineeringInformation data

According to the method, the problems that the model adaptability of various secondary objects of the transformer substation is poor, and the cost is high due to the fact that product library equipment types among manufacturers are different are solved. The invention discloses a secondary object primitive library design system of an intelligent substation. The system comprises a local server and acloud server, wherein a model file library and a model information database are established in the local server; a primitive library design platform, in communication connection with the server; a configuration tool, embedded in the 3Dmax in a sleeving manner. The primitive library design platform is used for carrying out assembly debugging on secondary object primitives by taking Unity 3D software as a support, the primitive library design platform is provided with a model controller which is used for controlling edited models, and the model controller is used for carrying out attribute position adjustment on unassembled primitives and carrying out compatible mixed assembly on secondary object models.

Owner:STATE GRID XINJIANG ELECTRIC POWER CO ECONOMIC TECH RES INST +1

Method for designing complementary data redundancy structure type CMOS (Complementary Metal Oxide Semiconductor) standard cell circuit physical library model

ActiveCN102622481BImprove design efficiencySpecial data processing applicationsEngineeringElectronic design automation

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH