Method for designing complementary data redundancy structure type CMOS (Complementary Metal Oxide Semiconductor) standard cell circuit physical library model

A standard cell and data redundancy technology, applied in the direction of electrical digital data processing, special data processing applications, calculations, etc., can solve the problem that the application of standard cells is difficult to promote, and achieve the effect of improving design efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

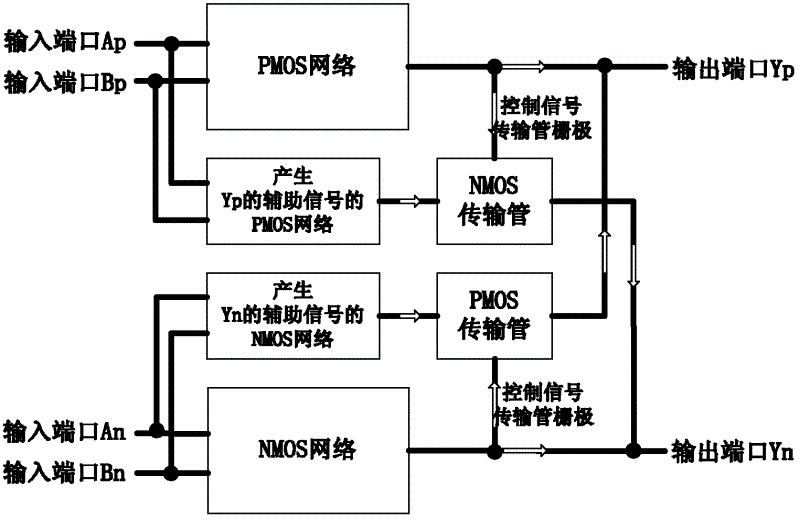

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be described in detail below in conjunction with the accompanying drawings.

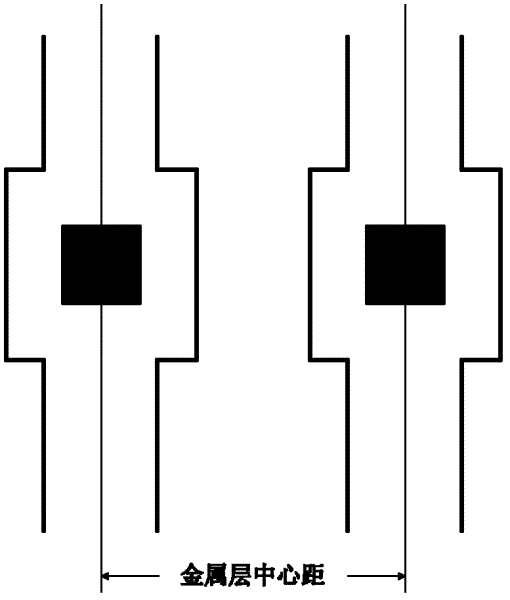

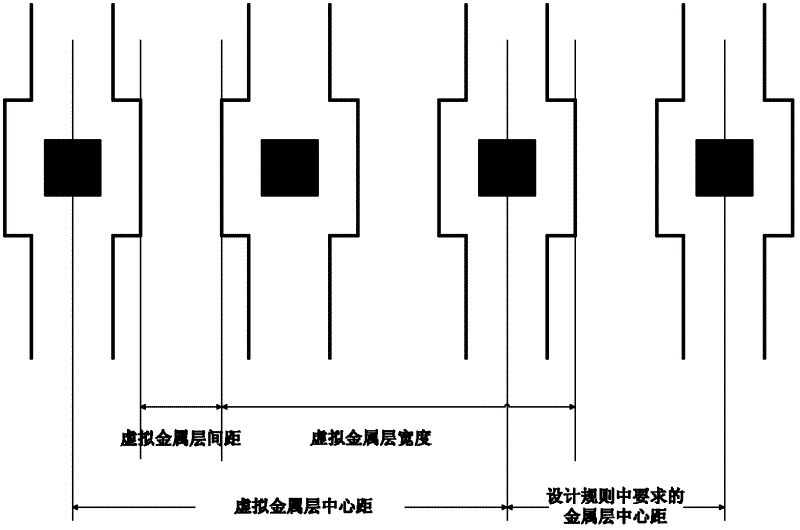

[0024] In order to clearly express the content of the invention, the layout design, design rules, metal layers, vias, connection vias, standard cell library and library model, comprehensive library model, physical library model, standard cell library design process, and metal layer center are firstly clarified. Definition of distance, grid point, wiring track, standard unit height, and standard unit minimum width.

[0025] Layout design:

[0026] In the manufacturing process of semiconductor integrated circuits, the planar design work of each real physical level in the complex manufacturing process, such as aluminum or copper interconnection lines, polycrystalline gates, etc., and graphics for impurity implantation regions, etc. The process of separation is called layout design, and the result of layout design is in the form of two-dimensional graphics, which are us...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More